# 國立交通大學

# 材料科學與工程學研究所 碩士論文

覆晶銲錫凸塊高度對無鉛銲錫電遷移破壞時 間及破壞模式之影響

Effects of Bump Height on Electromigration Failure Time and Failure Modes of Eutectic SnAg Solder Joints

研究生: 顧旻峰

指導教授:陳 智博士

中華民國 九十七 年 六 月

## 覆晶銲錫凸塊高度對無鉛銲錫電遷移破壞時間及破壞模式之影響

# Effects of Bump Height on Electromigration Failure Time and Failure Modes of Eutectic SnAg Solder Joints

研究生: 顧旻峰 Student: Min-Feng Ku

指導教授:陳 智 Advisor: Chih Chen

> 國立交通大學 材料科學與工程學系

#### A Dissertation

Submitted to Department of Materials Science and Engineering National Chiao Tung University in Partial Fulfillment of the Requirements for the Degree of Master in

Materials Science and Engineering

June 2008

Hsinchu 30050, Taiwan, ROC

中華民國九十七年六月

# 覆晶銲錫凸塊高度對無鉛銲錫電遷移破壞時間及 破壞模式之影響

研究生:顧旻峰 指導教授:陳智 博士

# 國立交通大學 材料科學與工程研究所

# 摘要

隨著產品追求輕薄短小的趨勢,覆晶封裝技術也有微小化的趨勢;因此本研究將討論銲錫球高度下降的時候,對電遷移試片可靠度的影響;我們製備了兩組試片:有相同的結構但銲錫接點高度不同,銲錫球高度分別為75μm的高銲錫球,與25μm的低銲錫球。分將他們放置於150℃之加熱板上通以0.9A的電流,使用四點量測紀錄電子流向下的銲錫球之電阻,並定義破壞時間為當電子流方向向下的銲錫球之電阻上升20%為破壞。經過電遷移測試我們發現高銲錫球有較長的平均破壞時間。造成此差異的原因將在本研究中有詳盡的探討。

**Effects of Bump Height on Electromigration Failure Time**

and Failure Modes of Eutectic SnAg Solder Joints

Student: Min-Feng Ku

Advisor: Dr. Chih Chen

Department of Materials Science and Engineering

National Chiao Tung University

**Abstract**

As the size of the microelectronic devices continues to shrink, the size and the bump height

of solder joints continue to decrease. Effects of bump height on electromigration failure

time and failure modes have not been studied for Pb-free SnAg solder joints. In this study,

we fabricated two kinds of solder joints with different bump heights: low-bump-height

(LBH) of 25 µm, and high-bump-height (HBH) of 75µm. Both sets of solder joints were

subjected to electromigration tests by 0.9A at 150°C. We measured the changes of bump

resistance with Kelvin bump probes. We define the bump failure when the bump resistance

increased 20% of its initial value. According to the temperature results measured by

infrared microscope, we found different Joule heating increase in the two solder joints, is

responsible for the difference in failure time.

ii

## 誌謝

首先我要感謝我的指導教授陳智博士,老師悉心的教導使我得以一窺電遷移領域的深奧,不時的討論並指點我正確的方向,無論在專業領域的研究或是待人處世,都讓我獲益良多,老師更積極鼓勵與補助我們出國參加研討會並拓展國際觀。老師對學問的嚴謹更是我輩學習的典範,在此我要對陳智老師致上我最高的謝意。

實驗室裡要首要感謝聖翔學長,在我剛進實驗室的時候,帶我了解實驗室中所有 大小事,讓我快速的融入實驗室的生活,還有 simulation 很厲害的大包,每次都要幫 我們去清大做 IR 的翔耀,每天都喊肚子餓的筱芸,做事認真的程昶,新實驗室一哥 宗寬,外表很老實的詠煌,連到紐奧良也是天天跑步的健民,要一起畢業的宗憲、ppp, 還有漢文、緯安、建志、岱霖,謝謝你們的陪伴與幫忙,讓我碩士班生涯過的多彩多 姿。

#### 1896

女朋友靜雯在背後的默默支持更是我前進的動力,靜雯的體諒、包容,是我這兩年的生活進步的原動力,最後要感謝我的家人,在你們的支持和鼓勵下,讓我能順利完成研究與學業,並帶給我人生莫大的喜悅。

# 目錄

| 中文摘要                               | i    |

|------------------------------------|------|

| 英文摘要                               | ii   |

| 誌謝                                 | iii  |

| 目錄                                 | iv   |

| 圖目錄                                | vi   |

| 表目錄                                | viii |

|                                    |      |

| 第一章、序論                             | 1    |

| 1-1 電子封裝簡介                         | 1    |

| 1-2 無鉛議題                           | 2    |

| 1-3 研究動機                           | 4    |

| 第二章、文獻回顧                           | 11   |

| 2-1 電遷移理論                          | 11   |

| 2-2 覆晶接點內的電遷移現象                    | 13   |

| 2-3 平均破壞時間(Mean-Time-to-Failure)分析 | 14   |

| 2-3-1 電流集中效應                       | 15   |

| 2-3-2 焦耳熱效應                        | 15   |

| 2-4 試片長度對電遷移的影響                    | 16   |

| 2-5 無鉛銲錫的電遷移測試                     | 17   |

| 第三章、實驗方法與步驟                        | 30   |

| 3-1 試片製備                           | 30   |

| 3-2 凱文結構                           | 31   |

| 3-3 電遷移測試條件與電阻變化量測                 | 31   |

|   | 3-4 試片微結構觀察      | - 33 |

|---|------------------|------|

|   | 3-5 試片破壞分析       | - 33 |

| 芽 | <b>常四章、結果與討論</b> | 38   |

|   | 4-1 平均破壞時間結果     | 38   |

|   | 4-2 微結構變化分析      | - 39 |

|   | 4-3 溫度對平均破壞時間的影響 | - 45 |

|   | 4-4 銲錫球內的電流密度分佈  | - 49 |

|   | 4-5 平均破壞時間分析     | - 50 |

|   | 4-6 結論           | - 52 |

| 夕 | 冬老文獻             | 72   |

# 圖目錄

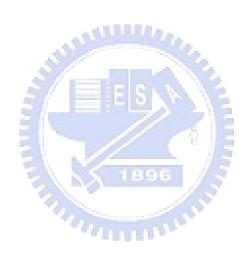

| 圖 1-1  | 電子封裝層級示意圖                                                   | ,  |

|--------|-------------------------------------------------------------|----|

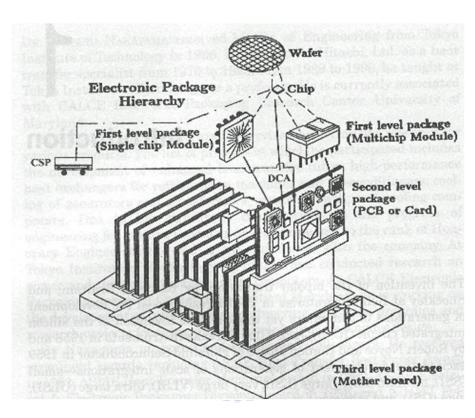

| 圖 1-2  | 打線接和技術                                                      | ;  |

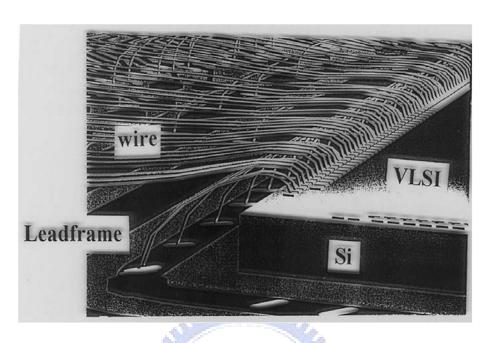

| 圖 1-3  | 覆晶接合示意圖                                                     | ;  |

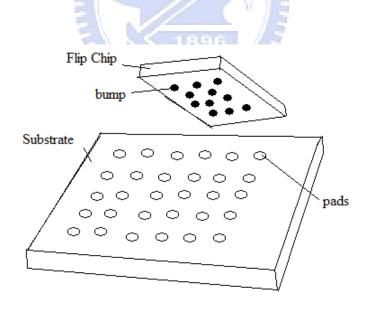

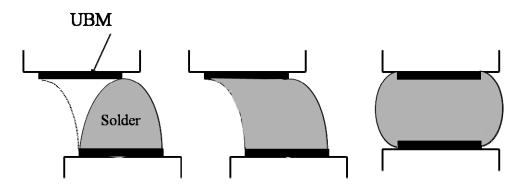

| 圖 1-4  | 覆晶銲錫自組裝示意圖                                                  | (  |

| 圖 1-5  | 錫晶鬚導致元件短路                                                   | (  |

| 圖 1-6  | Kelvin structure 在半導體電性量測示意圖                                | 10 |

| 圖 2-1  | 原子受電子流驅動遷移示意圖                                               | 19 |

| 圖 2-2  | Blech 首創之電遷移試片,圖中鋁線沉積在氮化鈦層上                                 | 19 |

| 圖 2-3  | 鋁線(熱處理 500℃, 0.5 小時)之平均漂流速度                                 | 20 |

| 圖 2-4  | 電流方向改變,導致電流集中效應                                             | 2  |

| 圖 2-5  | 模擬在銲錫球內因電流方向改變,造成電流集中效應                                     | 22 |

| 圖 2-6  | 電流通過鋁導線因焦耳熱效應造成溫升,                                          |    |

|        | (a)未通電流,(b)通入電流,(c)溫度分佈                                     | 2  |

| 圖 2-7  | 電流進入銲錫求內導致銲錫球內部溫度上升                                         | 24 |

| 圖 2-8  | (a)試片三明治結構示意圖,不同長度之共晶錫鉛試片,                                  |    |

|        | (b)75μm <sup>,</sup> (c)25μm                                | 2: |

| 圖 2-9  | 在 150℃下通入 10 <sup>4</sup> A/cm <sup>2</sup> 電流密度,三天後表面起伏情況, |    |

|        | (a) $75\mu m$ , (b) $25\mu m$                               | 2  |

| 圖 2-10 | 在使用銅 UBM 之銲錫接點的電遷移破壞變化                                      |    |

|        | (a)電遷移測試初期(b)孔洞生成(c)裂縫擴展(d)接點斷路                             | 2  |

| 圖 2-11 | 在使用鎳 UBM 之銲錫接點的電遷移破壞變化                                      |    |

|        | (a)空洞生成初期(b)孔洞擴展沿著介金屬化合物與銲錫介面                               |    |

|        | (c)介金屬化合物與孔洞成長(d)接點斷路                                       | 2  |

| 圖 2-12 | 在(a)115℃、(b)130℃、(c)140℃與(d)150℃矽基板溫度下                      |    |

|        | 通入 1.01A 電流大小,其介金屬化合物生成厚度對時間關係圖                             | 2  |

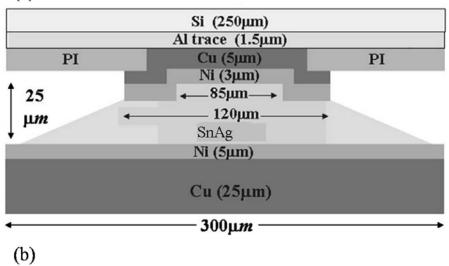

| 圖 3-1  | (a) 低銲錫球橫截面示意圖 (b) 高銲錫球橫截面示意圖                               | 3  |

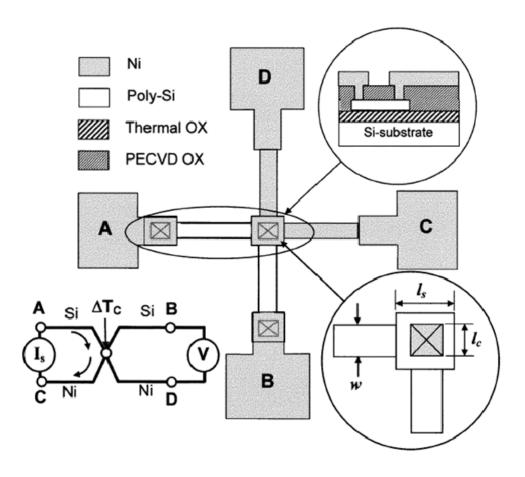

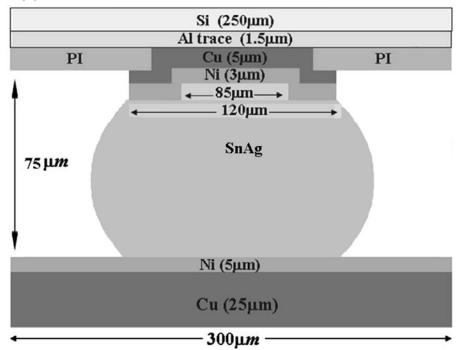

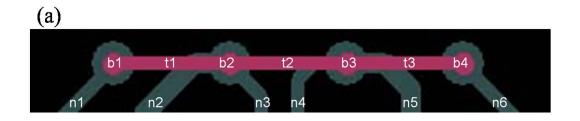

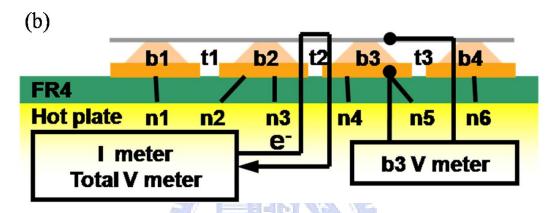

| 圖 3-2  | (a) 凱文結構俯視圖 (b) 凱文結構剖面示意圖                                   | 3  |

| 圖 3-3  | 試片研磨方向示意圖                                   |

|--------|---------------------------------------------|

| 圖 3-4  | (a) 紅外線顯像技術 (b) 使用紅外線顯像技術的實驗裝置              |

|        | 示意圖,晶片端朝上                                   |

| 圖 4-1  | 在 150°C下通入 0.9A,通電時間對電阻變化曲線圖,               |

|        | (a)高銲錫接點,通電時間 405h,(b)低銲錫接點,通電時間 184h       |

| 圖 4-2  | 在 150°C 下通入 0.9A, B3 電阻上升 20%時之 B2 SEM 剖面圖, |

|        | (a)高銲錫接點,通電時間 405h,(b)低銲錫接點,通電時間 184h       |

| 圖 4-3  | 在 150°C 下通入 0.9A, b3 電阻上升 20%時之 b3 SEM 剖面圖, |

|        | (a)高銲錫接點,通電時間 380h, (b)低銲錫接點,通電時間 118h      |

| 圖 4-4  | 在 150°C 下通入 0.9A, b3 電阻上升 50%時之 b3 SEM 剖面圖, |

|        | (a)高銲錫接點,通電時間 405h,(b)低銲錫接點,通電時間 184h       |

| 圖 4-5  | 低銲錫接點內介金屬化合物成分分析                            |

| 圖 4-6  | (a)高銲錫接點斷路時,紅外線顯熱儀結果                        |

|        | (b)低銲錫接點斷路時,紅外線顯熱儀結果                        |

| 圖 4-7  | (a)高銲錫接點 (b)低銲錫球斷路時橫截面 SEM 圖                |

| 圖 4-8  | 低銲錫球斷路時(a)橫截面 SEM 圖 (b) EDX 成分分析結果          |

| 圖 4-9  | (a)低銲錫接點斷路電阻變化對通電時間曲線圖                      |

|        | (b)圖(a)中紅框位置放大圖                             |

| 圖 4-10 | (a)高銲錫接點橫截面通入 0.45A 之溫度分佈結果                 |

|        | (b)低銲錫接點橫截面通入 0.45A 之溫度分佈結果                 |

| 圖 4-11 | 簡化試片示意圖                                     |

| 圖 4-12 | 100℃下通入 0.9A 電流鋁導線與銲錫球內部平均溫度                |

| 圖 4-13 | 高低銲錫接點鋁導線電阻對溫度變化圖                           |

| 圖 4-14 | 銲錫接點通過 0.9A 電流之模擬結果,                        |

|        | (a)高銲錫接點(b)低銲錫接點                            |

| 圖 4-15 | 銲錫接點通過 0.9A 電流之模擬結果,                        |

|        | (a)高銲錫球內(b)低銲錫球內                            |

| 圖 4-16 | 高銲錫凸塊電阻上升 20%之橫截面 SEM 影像圖                   |

|        | 通電時間(a)293h, (b) 375h, (c) 339h             |

# 表目錄

| 表 4-1 | 不同條件下,高低銲錫接點的平均破壞時間         | 70                                       |

|-------|-----------------------------|------------------------------------------|

| 表 4-2 | 計算溫差所使用之資料                  | 70                                       |

| 表 4-3 | 利用鋁導線電阻結合鋁電阻溫度係數,所求得知銲錫球內溫原 | ·<br>··································· |

# 第一章、序論

## 1-1 電子封裝簡介

電子封裝技術可以分成三種不同的層級 (level)[1],如圖 1-1 所示, 第一層封裝是將 IC 晶片接合到封裝的導線並完成其中的電路連線與密封 保護之製程 (Chip to Module);第二層級是將第一層級完成封裝的元件組 合於印刷電路板上之製程 (Module to Board);第三層級則是把數個電路板 組裝於主機板上 (Board to Mother Board)。近年來覆晶技術的發展,更使 得銲錫接點技術層次更加地提升。在以往電子產品中,銲錫接點是用在已 封裝完成的電子元件與基板間,而目前的覆晶技術則是直接用在積體電路 與基板的連接。隨著電子產品微小化、快速化發展,第一層級封裝技術勢 必面對許多挑戰,為了達成縮小晶片體積與提高 I/O 數的目標,傳統的打 線接合 (wire bonding)方式如圖 1-2[A]所示,因為僅可在晶片周圍連接導 線,接點數目與晶片邊長有關,隨著晶片尺寸的微小化,打線接合方式因 無法提高使用接點密度將無法使用於高性能的晶片上,然而覆晶方式接合 (Flip chip)如見圖 1-3 所示,利用銲錫凸塊朝下的方式接合,可提高接點 的密度。覆晶製程首先由 IBM 在 1962 年推出,主要應用於陶瓷基板上 做為固態邏輯技術。在 1970 年,IBM 把這項技術開發成 IC 所用的連 接技術,稱為 C4(Control-collapse Chip Connection) [2] 的技術。積體電路

晶片與基板的連結,是以晶片上的銲料凸塊和在基材上的連接材料所形成的電路連結。此技術其優點為體積小、單位面積下具高 I/O 數、低訊號遲滯性、散熱好、自組裝特性 (Self-alignment))(圖 1-4)、良好的電性。鉛在銲錫凸塊中提供良好的延展性以抵抗外在衝擊,同時由於共晶錫鉛對銅的接觸角小,可以避免發生剝離(spalling)的現象,在電子產業中常用具備優異潤濕效果、機械強度、可靠度與低熔點等優點的共晶錫鉛作為晶片與基板接著媒介。

### 1-2 無鉛議題

長久以來,銲錫中所用到的銲料都是以錫鉛合金為主,因為含鉛銲錫具有以下優點:一、鉛提供良好的延展性及表面光澤;二、鉛可使銲錫有效降低表面能跟介面能;三、共晶錫鉛的熔點為 183℃相對於純鉛(232℃)與純錫(327℃)有較低的熔點;四、95Pb5Sn 高鉛銲錫的液相點與固相點溫差大約為 10℃,可被當為高溫銲錫使用。因此,具有低熔點的共晶錫鉛焊錫和具有高熔點的高鉛銲錫可被運用為複合銲錫。然而鉛具有毒性,近年來開始有禁用或限制使用的呼聲。歐盟議會通過了 RoHS [3] (Restriction of Hazardous Materials) 法案,規定成員國必須在 2006 年7月1日以後禁止大部分鉛的使用。日本[4]的 JEIDA (Japanese Electronic Industry Development Association) 也訂定出無鉛銲料的使用時程,規定有

鉛銲料在 2005 年以後只能用在部分特例上。之後許多國家相繼跟進禁鉛 的計畫,也宣告無鉛銲料時代的來臨。此外,除了環境污染的因素外,含 鉛銲錫有可能含少量的 Pb<sup>210</sup> 同位素,它會衰退成 Pb<sup>206</sup> 而轉變成 Bi 和發 射出 α 粒子,當這些粒子通過矽晶片時會產生電子電洞對,而這些電子 電洞再結合前,會對元件中電容造成電荷累積現象使元件產生"soft error" 而失效。另一方面,以工業的角度來看,低成本並且與現有設備有良好匹 配性的銲料也是非常重要。無鉛銲料的要求對各項產業帶來非常大的衝 擊,因此發展國家非常重視無鉛銲料的研究,紛紛訂定各自的發展計畫, 期望可以找到適當的無鉛銲料,把衝擊減到最低。因此選用之無鉛銲錫須 具備含鉛銲錫的特性且不具毒性。近年來無鉛銲錫開發已成為微電子工業 相當重要的一項研發工作,無鉛銲錫選擇須考慮以下幾點:一、熔點須低 於 260℃,因為目前基板為高分子基板無法承受過高的迴銲溫度,二、良 好的熱、電和機械性質,三、合理的價格以及容易取得,四、無毒性與環 境汙染之虞,五、易於生產製造。美國的 NCMS (National Center for Manufacturing Sciences ) NEMI (National Electronics Manufacturing Initiative)、歐盟的 BRITE-EURAM、日本的 NEDO (New Energy and Industrial Technology Development Organization)等機構,各自提出多種不 同合金組成的銲料,例如 Sn-Cu、Sn-Ag、Sn-Zn、Sn-Ag-Bi、Sn-Ag-Cu 等, 而目前最被看好的銲料,則是以錫銀銅合金為主的無鉛銲料。無鉛銲料的

開發與研究是目前非常熱門的議題,新組成的銲料必須有良好的性質。

#### 1-3 研究動機

四十年前,摩爾提出預測半導體成長趨勢的摩爾定律 (Moore's Law),每 十八個月電路的複雜度會增加一倍;加上高科技新產品不斷追求輕薄短 小,使得晶片的尺寸與線寬不斷縮小;銲接技術已發展了數千年,但是隨 著不同應用的拓展,各種問題仍然持續發生。軟銲在科學與工業應用上, 仍然是非常具有挑戰性的主題。1998 年美國太空總署(NASA)所發射 的軌道衛星 Galaxy IV 發生故障,經過調查後發現衛星的兩個控制處理 器都已損壞,其中一個控制處理器的故障原因,是由一條寬度比頭髮還要 細的錫鬚(圖 1-5)所造成的。錫鬚是細長針狀的錫結晶,若是達到一定長 度而與其他接腳接觸,會造成元件的短路。錫鬚一般認為是內部壓縮應力 及表面氧化所造成的,它的成長是釋放應力的管道,我們可以想像成麵條 由撐滿麵糰的塑膠袋破洞中擠出來的情形。衛星的造價十分昂貴,卻會因 為銲點的問題而付之一炬。而且環保因素也是另一重點;電子產業界不斷 尋找錫鉛銲錫的替代品。此外先前也有當試片尺寸縮小時對共晶錫鉛焊料 電遷移破壞的影響[5]。 在電性量測方面,在積體電路中凱文銲錫結構 (Kelvin bump probes)很早就被利用,如圖 1-6 所示,該結構可針對欲量 測的指令範圍做電性的觀測,且可避除接點的接觸電阻對電性量測的影

響,故長久以來一直都是電性量測的首選工具之一。而在過去利用凱文結 構做電遷移觀測的相關研究則可回溯到 70 年代,在 Al stripe 上利用凱文 結構做詳細的電性分析。到目前為止,覆晶銲錫接點電遷移研究中的電性 觀測,大多都是利用雛菊花環結構(Daisy chain structure),直接定義電 路開路時為銲錫接點破壞的時間,可是這樣的實驗方式會產生不少問題, 首先,因為銲錫接點本身的電阻通常大約為幾個 mΩ 僅佔總迴路的極為小 部份,或是迴路的總電阻就已經超過銲錫電阻的大小,故雛菊花環結構對 於覆晶銲錫接點內的微小變化極不敏感無法對於銲錫接點電阻變化做精 確的觀測,僅僅可偵測到銲錫接點的破壞;第二,由於製程上的方便,迴 路上的鋁導線與欲研究的焊錫點之幾何結構差異極為可觀,負載電子流流 動的截面差異百倍以後並不少見,在此情況下,總迴路上承受電遷移能力 最差的點不一定在銲錫接點本身,鋁導線也很有可能是造成電路開路的原 因,一但這種情況發生,就很有可能造成覆晶銲錫接點電遷移破壞時間分 析上的錯誤。儘管雛菊花環結構有上述的重大缺點,但因為試片設計與製 作過程上的方便,截至目前為止在覆晶銲錫接點的相關研究中,雛菊花環 結構一直都還是最常見也最容易被利用的結構,由於覆晶銲錫接點中的凱 文結構因為還沒有一定的設計規範,且試片設計的門檻也較高,故將凱文 結構利用在覆晶銲錫電性的相關研究一直都很少見。先前研究的結果顯 示,凱文銲錫凸塊結構的精確性符合研究孔洞生成與成長的需求,而且可 以利用電阻變化量確實分辨出電遷移造成的不同階段孔洞成長[6]。因此本篇研究選用無鉛共晶錫銀銲錫作為電遷移測試接點,並使用凱文結構量測單顆銲錫凸塊的電阻變化,來討論當銲錫凸塊高度下降時對電遷移壽命 與破壞模式的影響。

圖 1-1 電子封裝層級示意圖 [1]

圖 1-2 打線接合技術 [A]

圖 1-3 覆晶接合示意圖

圖 1-4 覆晶銲錫自組裝示意圖

圖 1-5 錫晶鬚導致元件短路 [B]

圖 1-6 Kelvin structure 在半導體電性量測示意圖

# 第二章、文獻回顧

#### 2-1 電遷移理論

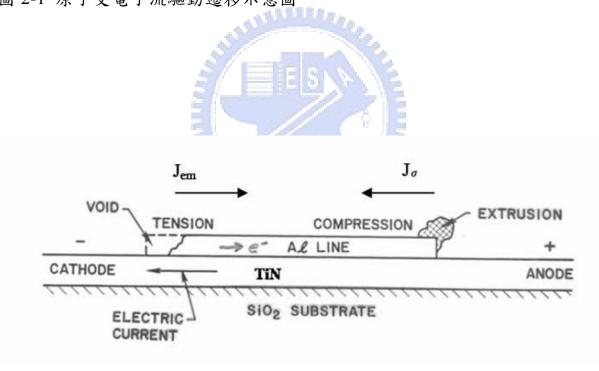

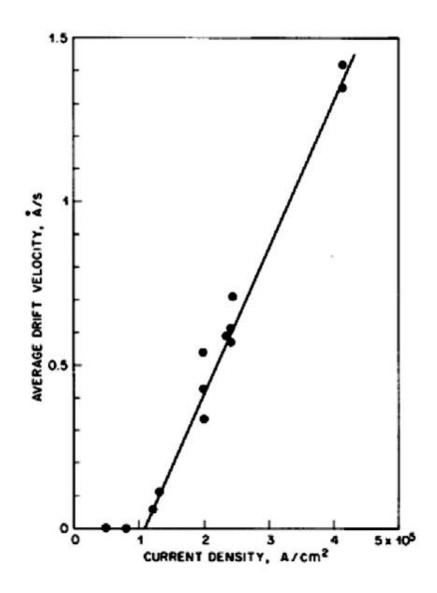

在金屬材料中施加一電場所造成原子移動稱為電遷移,這是一種因為 電場作用下產生的擴散現象,這個現象被 Geradin (1861)在熔化的錫鉛和 汞鈉中第一次被發現;而在 1914 年,Skaupy 提出電子風(electron wind) 的觀念,如圖 2-1 所示,來量化電遷移所造成的質量傳送。電遷移被廣泛 的研究在 1960 年代末期,首先發現在積體電路的導線上發生電遷移的損 壞,之後開始有許多關於電遷移的研究。而電遷移所造成薄膜金屬中質量 的移動可以由漂移速率模式來直接的研究,這個模式稱為 "saddle movement experiment",它是由 Blech 在 1976 年中第一次提出爾後被廣 泛的應用在原子漂移速率,活化能和電遷移的參數的研究中,圖 2-2 為飄 流速率實驗的試片結構圖,然後我們在氮化鈦層中通入電流,而電流會由 氮化鈦層流入鋁線中,因為鋁有較低的電阻。而鋁的門檻電流密度可由此 實驗測得,如圖 2-3,且 Blech 發現門檻電流密度與試片長度成反比的關 係,而隨著溫度增加而減小[7][8]。金屬材料的電遷移,則是由 Paul S. Ho 與 Thomas Kwok[9]最先提出研究。Seith 與 Wever 也以定位點(marker) 的運動,來量測遷移的位移量。此方式後來成為測量電遷移的標準方式。

電遷移造成質量的移動是由於電場與電荷載子所造成,電遷移的驅動

力由電場作用力與電子風力組合而成,電子風力主要是移動中的電子與離子之間的動量轉換[10];當電流流經試片時電子流也可視為一種對於原子擴散的摩擦力,這個摩擦力通常稱為電子風力。當我們對一個金屬薄膜通一個大的電流時,電子會撞擊在陰極端的原子會使得電子和擴散原子之間有動量交換,這個現象主要由兩個不同的交互作用力造成的:一、庫倫靜電力(electrostatic field force),二、電子風力(electron wind force)。原子擴散流(atomic diffusion flux)可表示成下列的式子[11]

$$J = -D\frac{\partial C}{\partial X} + \sum_{i} CM_{i}F_{i} \tag{1}$$

第一項代表的是化學能梯度而第二項表示的是所有不同驅動力的總合,對於一個純金屬而言原子之間不存在著化學能梯度,因此第一項為零,而第二項就像先前討論的是電場作用力與電子與擴散原子之間動量交換的總和,因此我們可以將第二項表示成[11]:

$$\sum_{i} CM_{i}F_{i} = F_{el} + F_{wd} \tag{2}$$

藉由比較兩者的數量級,我們得知電子風力遠大於電場作用力,因此原子會被由陰極端往陽極端推動,此外 Fmu 項可被表示成:

$$F_{wd} = EZ * e \tag{3}$$

E 是電場大小,Z\*是有效電荷數(effective charge number),Z\*表示原子因電遷移作用下如何移動,因此,Z\*的值會隨著不同的金屬原子而有所不

同,我們再將式1與式2結合

$$J = CMF_{wd} \tag{4}$$

M 是原子的移動率(mobility),C 為原子濃度,由 Nerst-Einstein equation 原子移動率可表示成

$$M = \frac{D}{kT} \tag{5}$$

D是原子擴散率(diffusivity),k是波茲曼常數(Boltzmann's constant),T是絕對溫度;因此我們將式 3、式 4 和式 5 結合,我們可得到電遷移的驅動力如下列所示:

$$J_{em} = CMF_{wd} = C\frac{D}{kT}Z * eE$$

(6)

# 2-2 覆晶接點內的電遷移現象

在金屬與積體電路的研究中,K. N. Tu 發表於 JAP. 2003[7]有系統的介紹現今電遷移的起源。現在由於積體電路的尺寸縮小,而使得銲錫的電流密度增加,因此電遷移在銲錫凸塊中是一個重要的可靠度議題。在大多數高效能元件上 在一個晶片上約有 7000 個銲錫接點假設每個銲錫接點的直徑為 50µm 當通過一個 0.2A 的電流時電流密度約為  $10^4$  A/cm² 這樣的電流密度約比通過銅導線或鉛導線的電流密度小兩個數量級。但是在這樣小的電流密度下電遷移現象仍然會因為晶格擴散而發生[12,13]。目前所

知會影響銲錫電遷移現象的因素是:(一)、銲錫的合金成分;因為銲錫中主要的擴散元素是鉛或錫,因此這兩種元素在銲錫中所含的比例會影響電遷移的速率,同時因為合金成分不同,造成微結構的差異也是另一個原因;(二)、電流密度:電流密度分布不均勻造成的電流集中效應也會造成電遷移破壞;(三)、通電時銲錫內的溫度;電流通過時,電子與周圍原子激烈碰撞,所產生的焦耳熱效應,提高了銲點的溫度,因為銲料主要是低熔點的金屬,升溫會顯著加速銲點中的界面反應。上述的這些因素對電遷移的破壞時間或成因都有很大的影響。

# 2-3 平均破壞時間(Mean-Time-to-Failure, MTTF)分析

工業界通常使用平均破壞時間(MTTF)來代表元件的壽命,在 1969 年 Black 提出了一個式子來分析鋁導線因為電遷移的平均破壞時間,如下列 所示[14]:

$$MTTF = A \frac{1}{j^{n}} \exp\left(\frac{E_{A}}{kT}\right)$$

(7)

MTTF表示平均破壞時間,j為導線內平均電流密度, $E_A$ 為活化能,T為 銲錫內的溫度,k是波茲曼常數(Boltzmann's constant)。這個式子主要由 估計空孔在鋁導線中形成的速率推導出來,但是也可以應用於我們估計覆 晶銲錫的平均破壞時間;由此方程式我們可以發現,有兩個外在的因素會 影響平均破壞時間,一個是電流密度,另一項是通過電流後銲錫中的平均

温度。下列就這兩個因素對平均破壞時間的影響就討論。

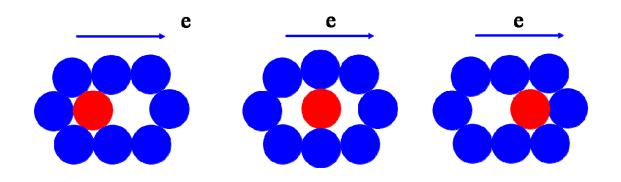

## 2-3-1 電流集中效應(Current Crowding Effect)

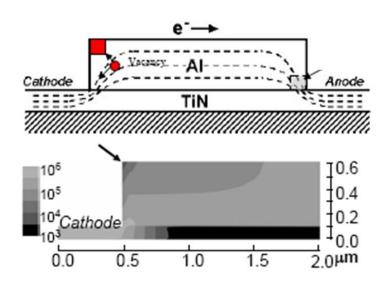

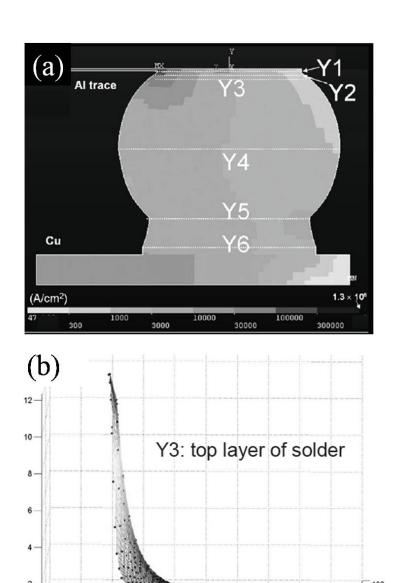

當電子流的路徑改變時,會造成電子在某些位置擁擠的現象,使那些 位置的電流密度大於試片的其他位置,我們稱為電流集中效應,如圖 2-4 所示。相同的情形也會發生於覆晶銲錫接點中。當電子流由導線進入銲錫 凸塊時,因為兩者之間介面橫截面面積的大小不同,但通過相同的電流大 小,因此在介面處會有相當大的電流密度改變,這樣的改變導致電流集中 在電流進入銲錫凸塊的入口處,此處的電流密度大約比整個銲錫凸塊內的 平均電流密度大了兩個數量級左右;根據先前的報導[15],利用有限元素 模擬分析法在銲錫凸塊內的電流密度分布 發現銲錫內的最大電流密度大 於銲錫內部的平均電流密度,如圖 2-5 所示,此一現象通常發生在銲錫與 UBM 界面附近,作為一空孔流分歧平面和支援電遷移在那個位置發生。 大多數的電流會傾向靠近鋁導線與銲錫凸塊的開口處之後,再進入銲錫凸 塊;而不是均匀的散佈於介面處,再一起跨越介面進入銲錫凸塊;因此, 這樣高的電流密度的結果導致電流集中擁擠影響的結果,導致銲錫接點入 口處更有發生電遷移破壞的傾向。

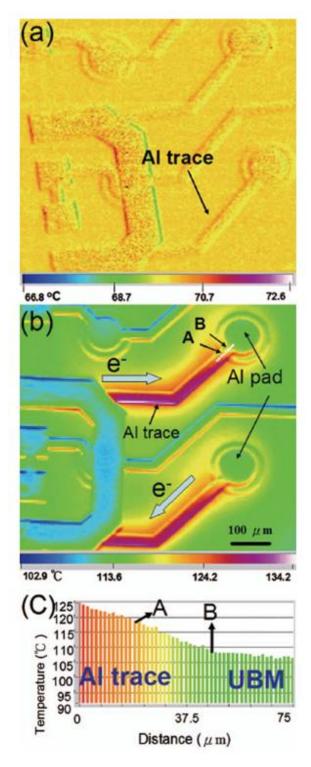

### 2-3-2 焦耳熱效應

焦耳熱效應是因為當電子在金屬中移動時,電子的動能因為與周圍原 子的碰撞轉變為熱能,這個熱能可以被表示成

$$P = I^2 R = j^2 \rho V \tag{8}$$

P表示熱能,I是電流,R為電阻,I是電流密度,V表示金屬的體積,P是金屬的電阻率;經由電遷移測試,假設通過覆晶銲錫接點的電流大小大約為 IA 或甚至更大,那麼焦耳熱效應就變成一個不可忽略的因素[16]。此外,通常連接覆晶銲錫的鋁導線長度約為幾百微米至幾千微米,其電阻值約為幾百個微歐姆;另一方面,通常一個銲錫接點的電阻大約為幾個微歐姆而下方的銅墊層與銅導線的電阻也甚小,所以最主要的熱源是來自鋁導線[17],如圖 2-6 所示。因此電遷移測試時銲錫凸塊內的溫度可能會因為焦耳熱效應而比外圍環境的溫度高的許多,如圖 2-7 所示。

因為電流集中效應與焦耳熱效應的影響,杜經寧教授將 Black 的平均破壞時間公式,加以改變,如下所示:

$$MTTF = A \frac{1}{(cj)^n} \exp\left(\frac{E_A}{k(T + \Delta T)}\right)$$

(9)

其中 c 為電流壅擠指數(crowding ratio),是將銲錫內的最大電流密度除上 銲錫內平均電流密度,cj 即是最大電流密度。 $\Delta T$  是因為焦耳熱效應在銲 錫內產生的升溫,因此( $T+\Delta T$ )可用來表示電遷移測試時銲錫內的實際溫 度。經過這個式子的修正,對於我們對平均破壞時間的估計能有準確的預 測。

## 2-4 試片長度對電遷移的影響

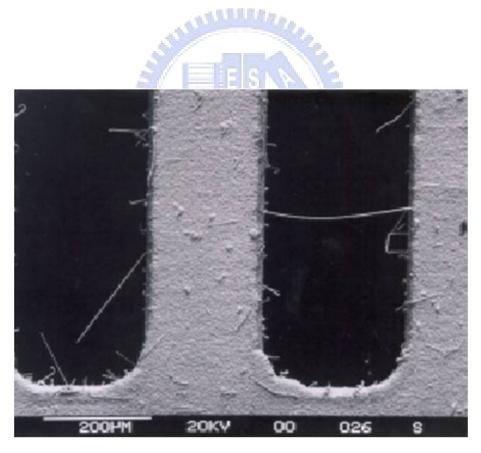

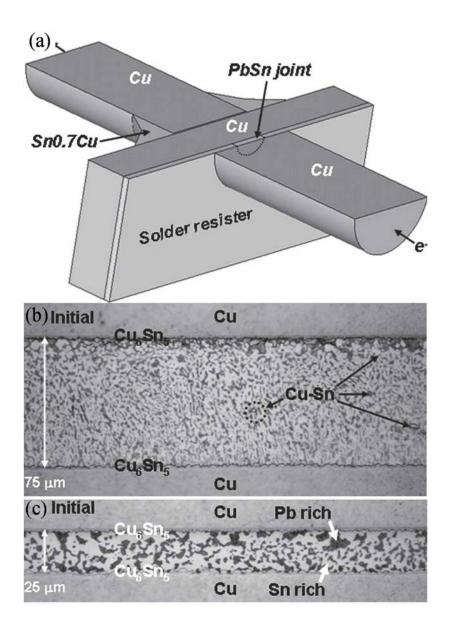

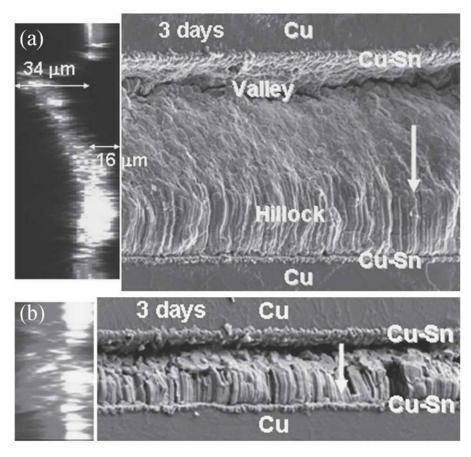

A. Lee 等人報導[5],在共晶錫鉛中,試片長度的不同對電遷移測試後,微結構與表面形態的改變。他們是利用三明治的結構(圖 2-8),並控制試片厚度在 75μm 和 25μm,並在 150°C 下通以 10<sup>4</sup>A/cm² 的電流密度。他們發現相粗化的現象受到電子流驅動的影響,粗化的趨勢由陽極端往陰極端減少,在特定的溫度下通過電流,會導致相分離的情況出現,富鉛相出現在陽極富錫相出現在陰極,表面的原子受到電子流的驅動而移動,因此在陽極端出現突出物(hillock),在陰極端出現空孔(valley),如圖 2-9 所示,深度與高度與通電的時間和接點厚度有關。但因為其試片結構的非實際的覆晶銲錫試片,且他們排除了電流集中效應與焦耳熱效應,因此本篇研究將會著重於覆晶銲錫在電遷移測試下,因為電流集中效應與焦耳熱效應,對於平均破壞時間的影響。

#### 2-5 無鉛銲錫的電遷移測試

隨著環保的意識抬頭,今年來許多人對無鉛銲錫投入研究  $[18][19][20] \circ 根據 \ Brook \ Chao 等人[21]的研究,在 150℃的溫度下,銅在 <math display="block">Cu_3Sn\ volume{1}{0} v$

Seung-Hyun Chae 等人[22]報導,共晶錫銀銲錫若使用的是銅的

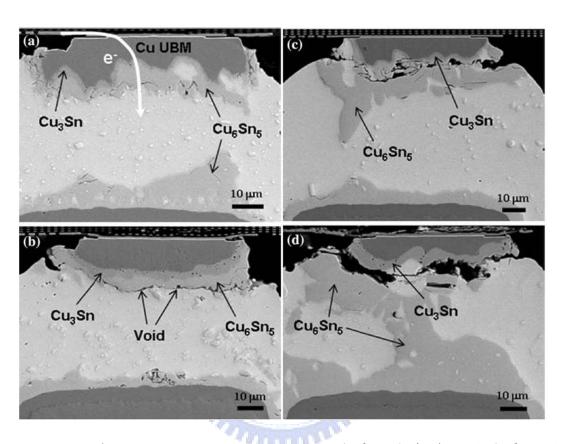

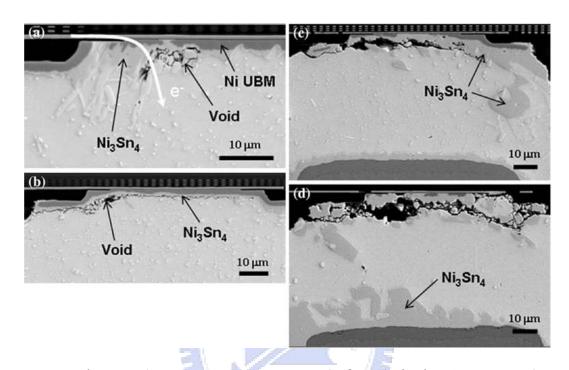

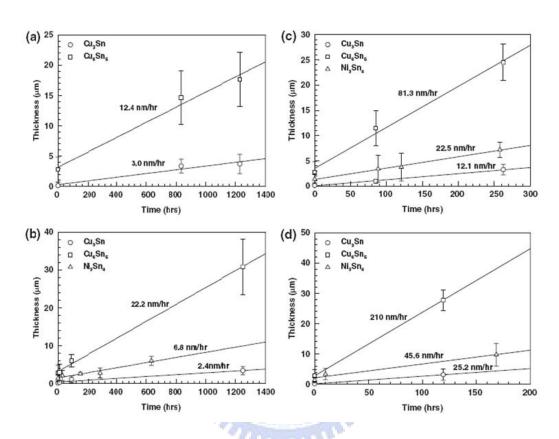

UBM,通常孔洞會先形成於 Cu<sub>6</sub>Sn<sub>5</sub>與銲錫的介面在電遷移測試的初期,但是導致試片形成斷路的孔洞則會沿著 Cu<sub>6</sub>Sn<sub>5</sub>與 Cu<sub>3</sub>Sn 的介面擴展(圖2-10);而共晶錫銀銲錫使用的是鎳的 UBM 時,孔洞在電遷移測試的初期會沿著 Cu<sub>3</sub>Sn<sub>4</sub>與銲錫的介面形成,最後擴展開始銲錫接點形成斷路(圖2-11)。介金屬化合物的生長是藉由電子流的驅動,遵循著線性關係的成長動力學(圖2-12),而介金屬化合物的成長伴隨著體積的收縮,這一結果加速了破壞的發展在電遷移測試下。

圖 2-1 原子受電子流驅動遷移示意圖

圖 2-2 Blech 首創之電遷移試片,圖中鋁線沉積在氮化鈦層上

圖 2-3 鋁線(熱處理 500℃, 0.5 小時)之平均漂流速度

圖 2-4 電流方向改變,導致電流集中效應

圖 2-5 模擬銲錫凸塊內因電流方向改變,造成電流集中效應

Position (µm)

圖 2-6 電流通過鋁導線因焦耳熱效應造成溫升, (a) 未通電流,(b)通入電流,(c)溫度分佈

圖 2-7 電流進入銲錫求內導致銲錫凸塊內部溫度上升

圖 2-8 (a)試片三明治結構示意圖,不同長度之共晶錫鉛試片  $SEM \; \hbox{$\mathbb{B}$} \; , (b) \; 75 \mu m \; , (c) \; 25 \mu m$

圖 2-9 在  $150^{\circ}$ C 下通入  $10^4 A/cm^2$  電流密度,三天後表面起伏情况,(a)  $75 \mu m$ ,(b)  $25 \mu m$

圖 2-10 在使用銅 UBM 之銲錫接點的電遷移破壞變化(a)電遷移測 試初期(b)孔洞生成(c)裂縫擴展(d)接點斷路

圖 2-11 在使用鎮 UBM 之銲錫接點的電遷移破壞變化(a)空洞生成初期(b)孔洞擴展沿著介金屬化合物與銲錫介面(c)介金屬化合物與孔洞成長(d)接點斷路

圖 2-12 在(a)115°C、(b)130°C、(c)140°C與(d)150°C矽基板溫度 下通入 1.01A 電流大小下,其介金屬化合物生成厚度 對時間關係圖

## 第三章、實驗方法與步驟

### 3-1 試片製備

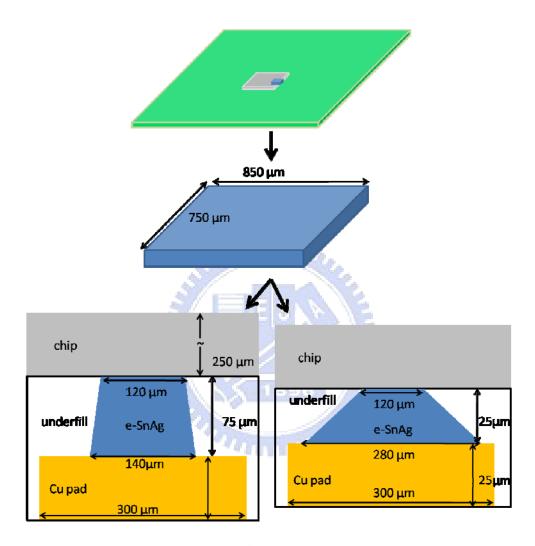

本實驗中的試片由米輯科技所提供的共晶錫銀覆晶封裝試片,試片結 構橫截面示意圖如圖 3-1 所示。本篇研究在探討銲錫凸塊高度對電遷移測 試的影響,因此準備兩組試片,他們的 UBM 結構、銲錫凸塊成分與體積、 板端基材皆相同,僅在銲錫凸塊高度有所不同。上端鋁導線的寬度與厚度 分別為 100 μm 和 1.5 μm。所使用的 UBM (under-bump-metallization)分別 為 Ti 0.5 μm / Cu 0.5 μm / Cu 5 μm / Ni 3 μm, 其中上端的鈦層和銅層是用 電子槍蒸鍍而成,厚度5 µm 的銅和3 µm 的鎳則是用電鍍形成。以黃光 顯影的方式定義出開口大小,再用濕式蝕刻法訂出 UBM opening 直徑為 120μm, 而 passavation opening 直徑為 85μm。銲料為共晶錫銀成分是 96.5Sn3.5Ag。基板採用 FR5 基板,其上方接著的銅墊層厚度為 25 μm , 直徑為 300 μm。銅墊層上方為 5 μm 厚的無電鍍鎳與 1μm 厚的金。因為 兩個基板墊層定義知開口大小不同,導致兩種不同的銲錫凸塊高度;低銲 錫凸塊(Low-bump-height solder bump)因為定義開口較大,板端接觸面積 增加,使得共晶錫銀銲錫迴銲上去時較為扁平,呈現出扁平的形狀非一般 常見的凸塊型,因此銲錫凸塊高度下降,僅有 25 μm,見圖 3-1(a);高銲 錫凸塊(High-bump-height solder bump)的高度則有 75 μm, 見圖 3-1(b)。當

試片尺寸縮小時,除了銲錫凸塊的高度會下降以外體積也會減少,使用這 組試片的好處在於,我們先固定兩者的體積僅在銲錫凸塊高度上做變化, 減少一個實驗上的變因以利後續研究結果的探討。

#### 3-2 凱文結構

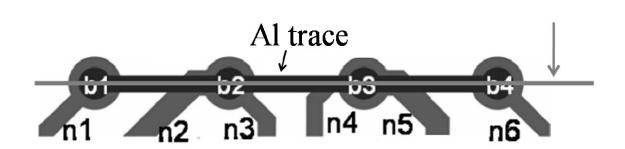

圖 3-2 所示為本實驗中所使用之凱文結構示意圖,研究中將利用此結構觀測銲錫受電遷移影響時的電阻變化。結構中包含四顆銲錫凸塊,此四顆銲錫凸塊由一條 3150µm 長的鋁導線連接四個鋁墊層,並標示著 b1 到b4 如圖。銲錫凸塊與銲錫凸塊間距為 1mm,此外在基板上有六條銅導線連接到此四顆銲錫凸塊,並依序標上 n1 到 n6,導線走向如圖所示。本研究中,我們定義電子流方向由板端往晶片端為 B2,而電子流由晶片端往基板端為 B3。電子流由 n3 進入通過 B2 至晶片,跨越鋁導線往下至 B3,最後由 N4 流出如圖中箭頭所示。銲錫 B2 的電壓變化可由 n1 與 n2 測量得到,而銲錫 B3 的電壓變化可由 n5 與 n6 測量得到,連接 B2 與 B3 的上端鋁導線電阻可由 n1 與 n6 測量得到。利用這樣的測量方式可在電遷移發生的同時測量兩顆電子流方向相反的銲錫凸塊與連接兩顆銲錫凸塊的鋁導線的電阻變化。

### 3-3 電遷移測試條件與電阻變化量測

本研究中所使用的電源供應器與量測儀器為電流源 Agilent [23]3646a

與資料交換器(Data switch)Agilent [24]E34970A 配合有二十個獨立頻道的 Agilent E34901A 模組,這兩組儀器在測量時間小於 90 天、100mV 的測量範圍下,電壓的測量精準度範圍約為 5μV。研究中兩組試片的初始電阻分別大約為 0.4mV (400μV)與 0.9mV (900μV),而在破壞產生的的電壓變化約 20~40μV,固此兩者儀器在本實驗的測量範圍內提供足夠的精準度,且上述兩儀器皆符合通用儀器通訊協定同時支援序列阜與 GPIB 控制介面,配合適當的軟體可對量測做穩定與長期的連續控制。在本研究中即利用美國國家儀器公司[25]所開發的圖形化儀器控制軟體 LabVIEW,做為資料擷取儀器控制的工具。

為了做加速的電遷移測試,我們將覆晶錫銀試片置於 150℃的加熱板上並分別通以 0.8 和 0.9 安培的電流;加熱方式是將試片以晶片端朝上的方式平貼於加熱板上,並以耐熱膠帶固定,靜置試片到試片內部的溫度達到平衡才開始通入電流測量。試片 passavation 直徑為 85μm, UBM 開口大小直徑 120μm,以 UBM 開口大小推出其通電電流所對應的電流密度分別為 7073 A/cm²和 7958 A/cm²,通電方向如圖所示。我們定義兩種破壞時間:(一)、當銲錫 B3 的電阻上升至初始電阻值的 1.2 倍時為破壞;(二)、當整個迴路斷路時定義為破壞。目的是要比較兩組不一樣的試片的破壞時間是否與定義不同而所改變。另外,為了觀察試片的微結構變化,我們做了電阻變化不同階段的微結構觀察,分別是銲錫 B3 電阻上升至初始值的

1.06、1.2、1.5、2 倍和斷路時停止通電,取下試片觀察微結構比較兩組試 片的差異。

### 3-4 試片微結構觀察

得到不同通電條件下,所需的破壞時間後。依序以不同號數的 SiC 砂紙 120、400、1000、1500、2000、4000 做研磨,再用 Al<sub>2</sub>O<sub>3</sub> 顆粒 1μm、0.3μm 作研磨拋光,研磨方向如圖 3-3 所示。為了觀察通電後試片微結構的變化,藉由光學顯微鏡(Optical Microscopy, OM)、電子顯微鏡(Scanning Electron Microscopy, SEM),來觀察其破壞後橫截面的影像。同時配合『能量散佈光譜儀』(Energy Dispersive Spectroscopy, EDX)來鑑定其特定區域的組成,以了解經過電遷移測試之後不同位置的組成變化。

### 3-5 試片破壞分析

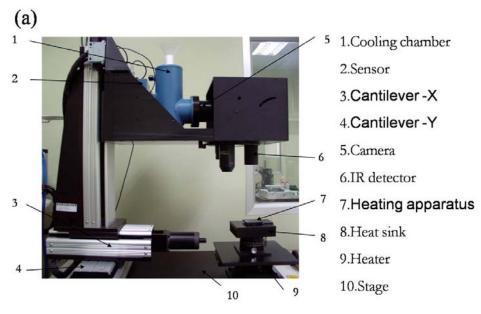

分析平均破壞時間的差異,分為熱分析與電分析;熱分析的部分,利用紅外線顯像技術 (infrared microscopy) 圖 3-4,分別對通入不同電流下的試片,來收集表面輻射的溫度資訊,來推測銲錫通電時的溫度上升。為了瞭解通入電流時銲錫內部的溫度分佈,我們先將試片研磨拋光至中心,因為試片已先研磨剩下一半的截面積,只通以實際通電條件下一半的電流大小,以符合實際通電時的電流密度大小。

為比較與深入了解通電過程中銲錫凸塊內的電流分佈,研究中利用

ANSYS 模擬軟體建立三維的數值分析模型。觀察通電初期,電流分布的狀況,分析破壞前,電阻上升之後,其內部電流的分佈,推測破壞階段中,導致電阻上升與破壞發生的原因。ANSYS 的模擬分為三個步驟:前處理、求解、後處理。前處理為建立物體、定義材料、網格化,求解為施加邊界條件、初始條件、求解,後處理為顯示結果。模擬結果分為列表(list)與繪圖(plot)兩種方式。觀察的方式分為兩種;(1)觀察節點(node)的結果,如節點上的電位、電場;(2)觀察元素(element)上的結果,如電流密度。

圖 3-1 (a) 低銲錫凸塊橫截面示意圖

(b) 高銲錫凸塊橫截面示意圖

圖 3-2 (a) 凱文結構俯視圖

(b) 凱文結構剖面示意圖

圖 3-3 試片研磨方向示意圖

圖 3-4 (a) 紅外線顯像技術

(b) 使用紅外線顯像技術的實驗裝置示意圖,晶片端朝上

## 第四章、結果與討論

## 4-1 平均破壞時間結果

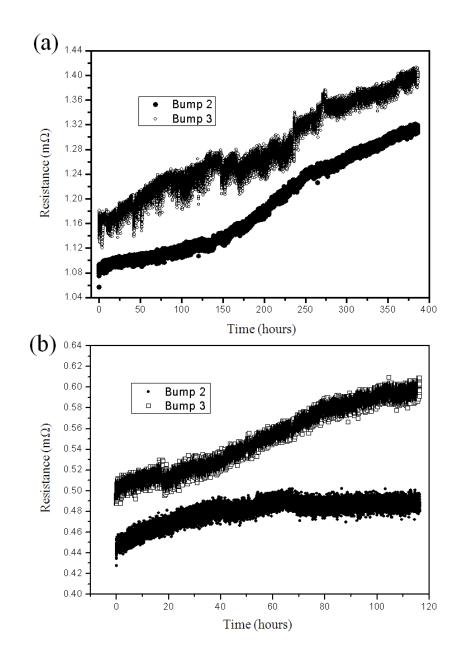

從表 4-1 列出的平均破壞時間,我們發現當試片通以 0.9 A 的電流, 低銲錫接點的平均破壞時間比高銲錫接點來的短;即使是在通過較低的電 流下,如 0.8 A,高銲錫接點仍然有較長的平均破壞時間;這是當我們定 義破壞時間為B3的電阻上升20%;假如我們更進一步的延長電遷移測試 時間至 B3 的電阻上升為 1.5 倍時, 高銲錫接點仍然有較長的破壞時間。 圖 4-1 為在 150℃下通入 0.9 A 的電流, B2 和 B3 的電阻變化對通電時間 的曲線圖;圖 4-1(a)為高銲錫接點在電遷移測試 380 小時下當 B3 電阻到 達 1.2 倍時的通電曲線;圖 4-1(b)則為低銲錫接點在 118 小時 B3 電阻到 達 1.2 倍時後的電阻變化曲線。根據兩組試片的通電電阻變化曲線圖,我 111111 們發現 B3 的電阻皆緩慢的上升至 1.2 倍,有不同的是兩組試片的 B2 電 阻變化曲線。由圖 4-1(a)中我們發現除了 B3 的電阻隨著時間增長而上升, B2 的電阻也有隨著時間上升的趨勢;但在圖 4-1(b)中低銲錫接點的 B2 電 阻並沒有隨著通電時間增加而上升。

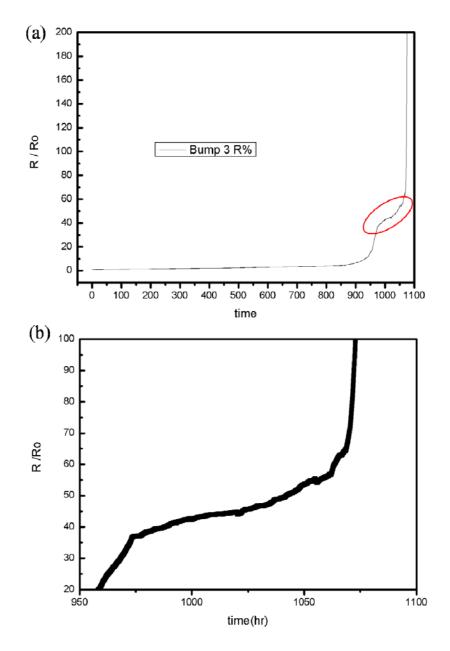

因為本研究中所使用的覆晶銲錫接點,根據先前發表的結果[26];高 銲錫凸塊的單顆電阻約為  $1m\Omega$  左右,而低銲錫凸塊的單顆電阻約為 0.4  $m\Omega$ ,為了探討是否因為兩者之間初始電阻值不同,而造成電遷移平均破 壞時間上的差異,我們更進一步的將試片通入電流直到斷路,同時記錄 B3 的電阻變化。進一步比較高銲錫接點與低銲錫接點破壞時間的差異。 表 4-1 顯示出低銲錫接點斷路的時間約為 1000 小時,高銲錫接點斷路的時間約為 1500 小時。雖然低銲錫接點的破壞時間仍然較高銲錫短,但如果以 B3 電阻上升為 1.2 倍為破壞時,低銲錫的平均破壞時間約是高銲錫的三分之一,若以此比例與低銲錫的斷路破壞時間推估,高銲錫接點斷路的時間應該超過 2000 小時,但實驗的結果卻顯示高銲錫接點在 1500 小時左右即斷路,造成此差異的原因在下一節微結構變化中加以探討。

## 4-2 微結構變化分析

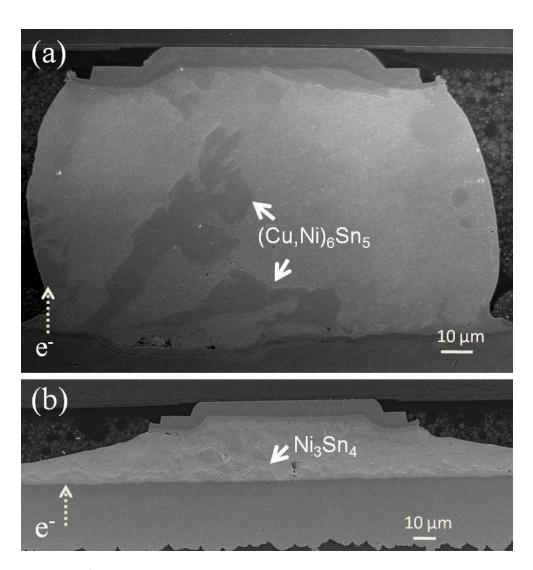

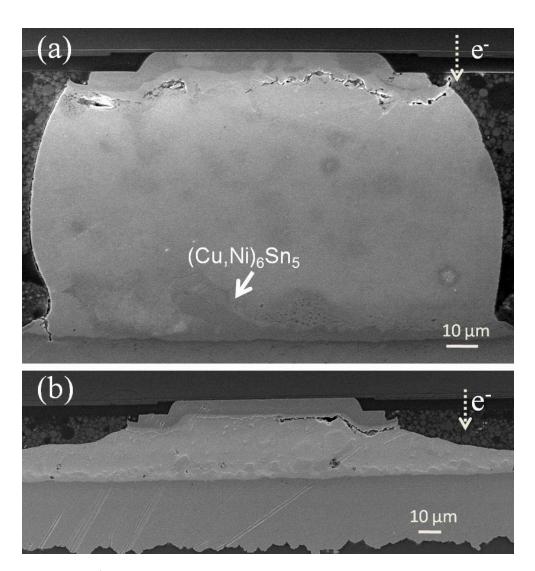

圖 4-2 則是相對應圖 4-1 電阻變化曲線中 B2 的 SEM 橫截面圖。圖 4-2(b)中顯示的是高銲錫接點 B2 橫截面的 SEM 影像,圖中電子流由左下端進入銲錫,我們發現電子流進入端的無電鍍鎳遭到破壞,銅墊層中的銅原子隨著電子流的驅動擴散進入銲錫內部,形成大量的介金屬化合物,根據 EDX 分析,此介金屬化合物的成分為(Cu,Ni)6Sn5。由低銲錫接點 B2 的橫截面 SEM 圖顯示,在低銲錫中並沒有出現像高銲錫凸塊中無電鍍鎳層遭到破壞,並在內部形成大量介金屬化合物形成的現象,僅有在板端的Ni3Sn4介金屬化合物變厚,如圖 4-2(b)所示。這一結果也跟電阻變化曲線紀錄到的結果相符合;高銲錫接點的 B2 電阻隨著通電時間增加而上升,

內部的無電鍍鎳遭到破壞銅原子進入銲錫內部形成大量的介金屬化合物;而低銲錫僅有板端的介金屬化合物因通電下變厚,因此電阻僅有些微上升。造成此一差異的原因是因為,先前提到因為我們要使銲錫高度下降,讓板端的開口變大,接觸面積增加,降低銲錫高度,此一結果導致高銲錫接點和低銲錫接點中電子流方向向上的 B2 電流密度不同。因為高銲錫接點的板端 opening 的直徑約為 140μm,而低銲錫接點板端 opening 的直徑約為 280μm,使得高銲錫接點板端的接觸面積僅有低銲錫接點的四分之一,因此由板端進入低銲錫的電流密度大約只有高銲錫的四分之一,而電遷移破壞與電流密度有相當大的關聯性。此一結果解釋為何兩者的B2 電阻變化曲線呈現出如此大的差異。這是跟板端開口與電流密度有關,但本篇的重點在於銲錫凸塊高度對電遷移破壞的影響,因此接下來的討論將著重於電子流方向向下的B3。

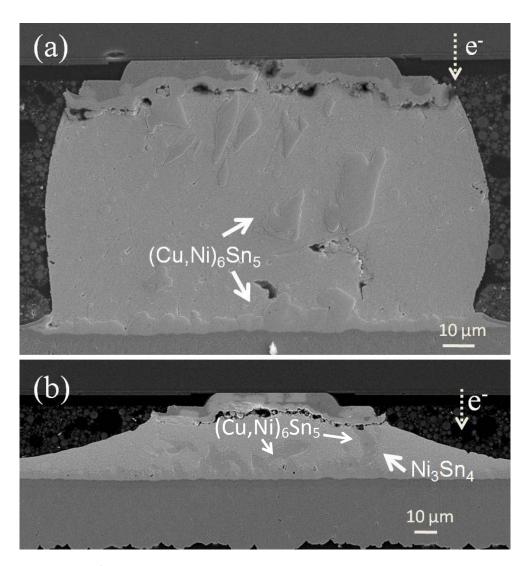

圖 4-3 是相對應圖 4-1 電阻變化曲線中 B3 的 SEM 橫截面圖。圖 4-3(a) 為高銲錫接點中 B3 橫截面的 SEM 影像,電子流由右上方進入銲錫如圖中箭頭所示;當銲錫凸塊電阻上升至 1.2 倍時,我們可以很明顯的發現孔洞沿著介金屬化合物與共晶錫銀銲錫的介面擴展,不只在電子流進入的右端生成空孔,在 UBM 的左端介金屬化合物與共晶錫銀的介面也出現孔洞,而我們也發現銅 UBM 的銅原子隨著電子流的驅動,由晶片端移向板端,並在板端與鎳反應形成介金屬化合物,經過 EDX 成分分析,我們可

發現此介金屬化合物的成分為(Cu,Ni)<sub>6</sub>Sn<sub>5</sub>,而錫原子進入銅 UBM 中形成 Cu<sub>6</sub>Sn<sub>5</sub>的介金屬化合物;反觀我們發現低銲錫接點中的 B3,當電阻上升 20%時,僅有在右上角電子流進入端的地方形成一個很大的空洞,而整個 銅的 UBM 層也保持完好,在共晶錫銀銲錫的內部也沒有大量的介金屬化 合物生成,如圖 4-3(b)所示;我們延長通電的時間使 B3 的電阻上升 50%, 再觀察其微結構變化。圖 4-4(a)為高銲錫凸塊經過 410 小時電遷移測試之 後,電阻上升 50%的 SEM 横截面影像。因為電子流進入銲錫受到幾何形 狀的改變造成電流集中效應,在入口處的位置形成最大電流密度區,此處 也是空洞最先形成的位置,當孔洞形成後電子流被迫改變路徑,向前及向 左右擴散,根據先前模擬的結果顯示[6],向前的電流密度較向左右分流 的電流密度大,因此孔洞繼續向前沿著介金屬化合物與共晶錫銀的介面擴 展,因此孔洞的延伸的長度較電阻上升 20%時長,而銅 UBM 也更大量的 消耗,除了在原本板端形成的介金屬化合物變厚,在銲錫內部也形成大量 的介金屬化合物,成長方向沿著電子流的的方向呈現長條狀,此介金屬化 合物經 EDX 分析為(Cu,Ni)<sub>6</sub>Sn<sub>5</sub>;當孔洞沿著介金屬化合物與共晶錫銀的 介面由兩端往中間擴展,使得電子流最後由 UBM 的中央進入銲錫內部, 此時的接觸面變小,使得電流密度變大,銅原子也因為電子流的驅動進入 銲錫內部,因此銅 UBM 中間的銅原子電子流帶走形成孔洞在 UBM 中。 圖 4-4(b)為低銲錫凸塊經過 185 小時電遷移測試之後,電阻上升至 1.5 倍

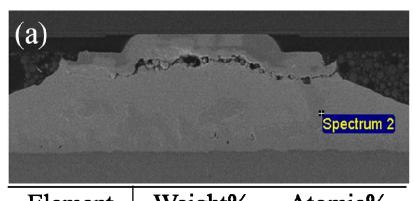

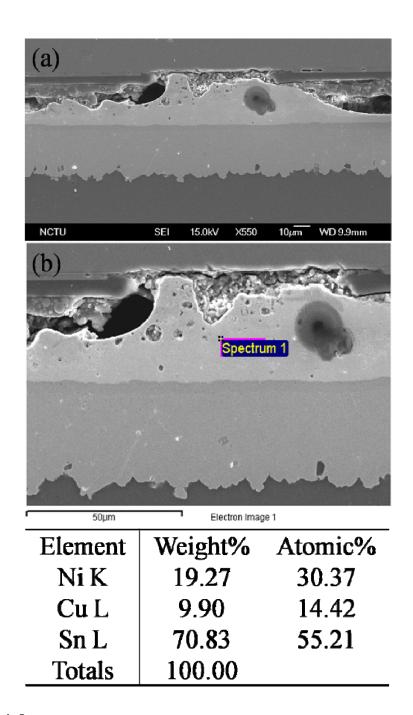

的 SEM 橫截面影像。結果與高銲錫凸塊的結果大致相同,孔洞一樣是沿 著介金屬化合物與共晶錫銀銲錫的介面擴展,但是雖然有大量的銅 UBM 被消耗,但是在低銲錫凸塊的內部並沒有出現像高銲錫凸塊中大量介金屬 化合物生成的情况,而在板端形成的介金屬化合物經過成分分析為 (Cu,Ni)<sub>6</sub>Sn<sub>5</sub>,我們認為是因為低銲錫的擴散路徑比較短,在電遷移測試 下,被電子流驅動的銅原子可以迅速擴散到板端並在板端與鎳和錫形成介 金屬化合物。另外,我們發現在電子流進入的右端,形成一條介金屬化合 物橋,將晶片端與板端連結起來,而經過 EDX 成分分析,此介金屬化合 物為 Ni<sub>3</sub>Sn<sub>4</sub>, 圖 4-5 分別為兩個不同的低銲錫凸塊試片, 在電阻上升至 1.5 倍時的橫截面 SEM 影像。在低銲錫凸塊內的介金屬化合物有形成連接晶 片端與板端的 Ni<sub>3</sub>Sn<sub>4</sub> 介金屬化合物橋及板端變厚的(Cu,Ni)<sub>6</sub>Sn<sub>5</sub> 與高銲錫 凸塊只觀察到(Cu,Ni)<sub>6</sub>Sn<sub>5</sub>在銲錫凸塊內形成與板端變厚的情況不同。我們 認為不管是高銲錫凸塊或是低銲錫凸塊(Cu,Ni)<sub>6</sub>Sn<sub>5</sub> 都是由於晶片端原本 3μm 厚的鎳層遭到電遷移破壞後,使得銅原子被電子流驅動進入銲錫與 錫和鎳反應。而低銲錫凸塊中的 Ni<sub>3</sub>Sn4 介金屬化合物橋是因為晶片端 Ni<sub>3</sub>Sn<sub>4</sub>受到電子流驅動變厚,以及板端原本的 Ni<sub>3</sub>Sn<sub>4</sub>受到通電過程中的焦 耳熱效應導致的熱時效作用而變厚,使兩端連接起來。

從橫截面的 SEM 影像看來,高銲錫凸塊無論是在電阻上升 20%或是 50%電遷移破壞似乎比較嚴重,主要是因為我們定義他們的破壞時間為電

阻上升至 1.2 倍時為破壞,但是因為高銲錫凸塊的單顆電阻約為 1mΩ 左右,而低銲錫凸塊的單顆電阻約為 0.4 mΩ,當兩者皆增加 20%時,高銲錫凸塊電阻需要上升的量比低銲錫凸塊多,因此高銲錫凸塊的內部大量孔洞生成、銅 UBM 部分溶解並在內部形成大量的介金屬化合物,才使得高銲錫凸塊的電阻上升 20%。跟高銲錫凸塊相比低銲錫凸塊的電阻上升 20%,就像是高銲錫凸塊電阻上升的初期,因此僅在電子流進入端形成一個很大的孔洞。但就電阻上升的絕對值而言,高銲錫凸塊上升 20%的電阻值大約與低銲錫凸塊上升 50%的電阻值大小相等,而就微結構的觀察上來說,當高銲錫凸塊的電阻上升為 1.2 倍時的破壞的嚴重情形與低銲錫凸塊電阻上升 1.5 倍時相等。但就單純以兩組試片電阻上升的絕對值相比,上升相同的電阻值,低銲錫接點的平均破壞時間仍然較高銲錫接點短。

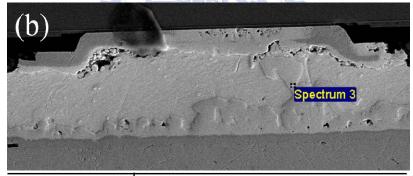

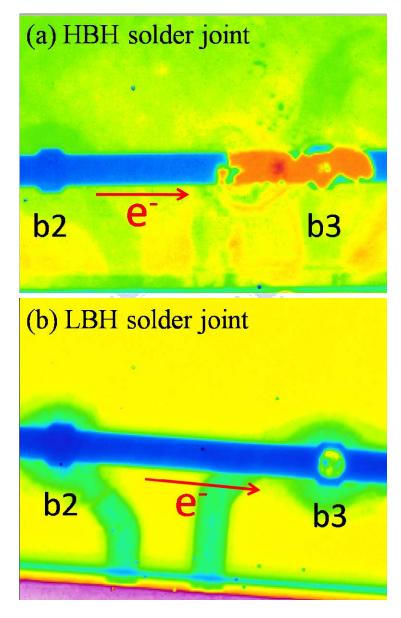

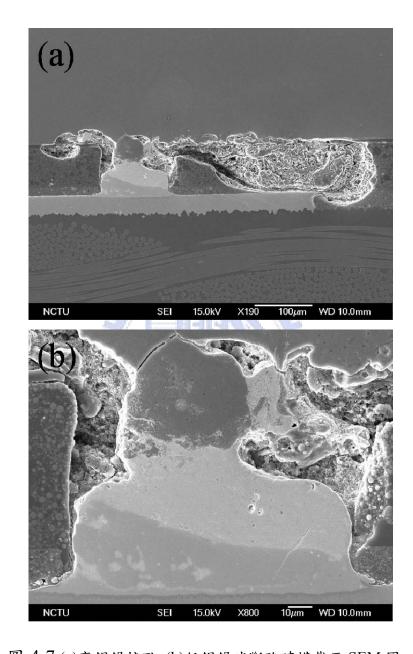

我們將高低銲錫接點斷路的試片,放置於紅外線熱像儀上,不通過電流僅加熱,利用不同材料有不同的熱反射率來觀察內部的破壞情況,圖4-6中六角型的地方為銲錫凸塊上方之鋁墊層,連接六角型與六角型之間的長條狀為鋁導線,圖4-6(a)顯示長條狀的鋁導線呈現不連續表示當高銲錫接點形成斷路時,是因為鋁導線燒毀,圖4-6(b)中鋁導線完好但在六角形的鋁墊層中有缺口,表示低銲錫形成斷路時,銲錫接點與鋁導線接著介面完全斷開。雖然高低銲錫接點到最後斷路時,鋁導線都出現毀損的情況,但造成斷路的原因不大相同,在通電的過程中鋁導線上的平均電流密

度為  $6 \times 10^5 \, \text{A/cm}^2$ , 在超過  $1000 \, 3$  小時的電遷移測試後, 鋁導線也許出 現劣化,導致電流密度提高,加上焦耳熱效應的影響,使鋁導線在高銲錫 接點尚未斷路之前提早毀損;而低銲錫接點中的鋁導線是因為通電後期, 因孔洞擴展的關係,使得進入銲錫接點得電流密度變大,因為電流集中導 致嚴重的焦耳熱產生,使銲錫凸塊上端的鋁導線燒毀,導致高銲錫接點的 斷路破壞時間比預期短,由圖 4-7 是高銲錫接點斷路的 SEM 剖面圖,也 發現鋁導線嚴重燒毀,因此我們認為高銲錫接點斷路的原因是因為鋁導線 燒毀,若非鋁導線燒毀,高銲錫接點的斷路時間應該會超過 2000 小時。 圖 4-8 是低銲錫接點斷路的 SEM 剖面圖,可發現上端鋁導線燒毀,根據 EDX 成分分析,剩下的共晶銲錫皆反應成介金屬化合物。根據通電過程 中記錄的時間對電阻變化曲線,我們發現在通電的最後階段,電阻上升的 趨勢有減緩,到最後又急遽上升,如圖 4-9 所示,根據 SEM 與 EDX 的結 果我們推論,因為低銲錫凸塊內的共晶錫銀與銅、鎳 UBM 完全反應成介 金屬化合物,而我們知道介金屬化合物與銲錫相比有較好的抵抗電遷移能 力,因此當銲錫凸塊內完全形成介金屬化合物時,較能抵抗電遷移,導致 雷阻上升得較緩慢,減緩電遷移破壞速度,但到最後階段因為孔洞擴展整 個介面,使電流密度大幅上升,導致低銲錫接點斷路。因此根據斷路的結 果,在高銲錫接點斷路時,是因為鋁導線燒毀,高銲錫凸塊的介面或許尚 未完全斷開;而在低銲錫接點中,因為孔洞擴展,使電流進入面積變小,

電流密度變大,使低銲錫接點斷路。

### 4-3 溫度對平均破壞時間的影響

由下列的平均破壞時間的公式,我們來探討熱對平均破壞時間的影響;

$$MTTF = A \frac{1}{j^{n}} \exp\left(\frac{E_{A}}{kT}\right) \tag{7}$$

由於我們使用的兩組試片,他們有相同的 UBM 結構與相同的銲錫成分,我們假設他們的材料常數 A 與活化能  $E_A$  都相同,因此影響兩組試片平均破壞時間差異的是電流密度與銲錫內的平均溫度,但因為他們擁有相同的鋁導線尺寸與 UBM 開口,我們假設其銲錫內平均電流密度大小相同,我們可以將平均破壞時間公式簡化成下列所示:

$$MTTF \propto \exp\left(\frac{1}{T}\right)$$

(10)

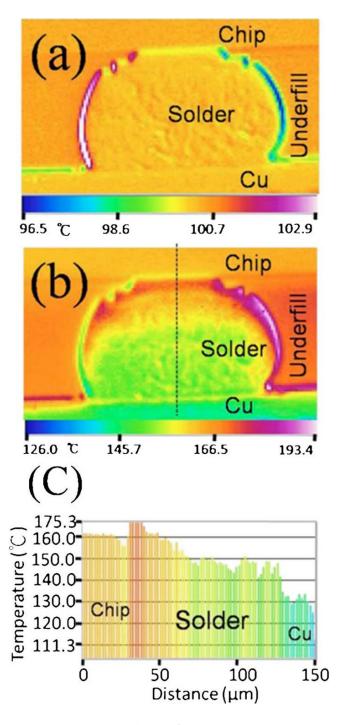

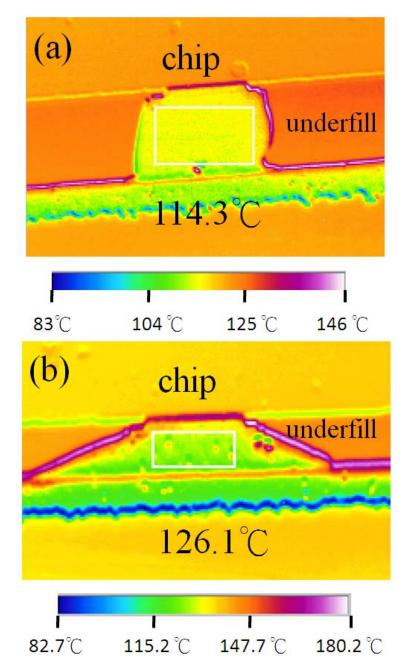

由此可知平均破壞時間與試片中的溫度成反比關係,若銲錫內部的平均溫度越高,則平均破壞時間越短。為了檢驗兩組試片的溫度差異,我們使用紅外線熱像儀來檢查通電條件下銲錫內部的溫度變化。試片先研磨至中心並仔細拋光,因為截面積僅剩下原本的一半,因此我們通過 0.45A 的電流大小,以符合原本完整銲錫凸塊通過 0.9A 電流時的電流密度大小。圖 4-10 中所顯示的是兩組試片研磨之中心並在 100℃下通過 0.45A 電流,

所顯示的溫度分佈,我們再經由軟體計算圖中白光方框中的溫度,作為銲錫凸塊內的平均溫度。從圖中得知,高銲錫凸塊內的平均溫度為 114.3℃,低銲錫凸塊內平均溫度 126.1℃;這表示通入電流後,低銲錫凸塊內部的升溫明顯大於高銲錫凸塊。這符合我們先前的推斷,低銲錫凸塊內的平均溫度大於高銲錫凸塊,因而導致低銲錫接點的平均破壞時間小於高銲錫接點。

接下來討論是甚麼因素導致兩組試片如此大的溫度差異,因為很明顯的看出溫度的差異嚴重的影響兩組試片的平均破壞時間。首先,根據下列式子

$$Q = mC_p \Delta T \tag{11}$$

Q是淨熱量,表示吸熱與散熱之間的差值;m是物體質量;Cp為熱含量; ΔT 是溫度差,表示吸收淨熱之後的溫度上升。對於我們的試片而言,熱源來自板端加熱試片的加熱板與通電過程中鋁導線所產生的焦耳熱,而熱量則由上端的矽晶片散失;因為兩組試片的結構一樣,我們假設所吸收的熱量與所散失的熱量一樣,因此高銲錫接點與低銲錫接點得到相同的淨熱量,假如我們將兩組試片的 mCp 的值分別算出來,那我們就可以得到兩組試片的加熱後的溫升。為了計算方便,我們先將試片加以簡化;首先,因為銲錫凸塊彼此之間的間距為 850μm,而銲錫接點排與排的間隔為750μm,因此我們將試片切成 850μm×750μm×1mm 的長方體大小。因為

試片的結構複雜,包含了許多部分,我們將體積較少的部分去除,例如: 銅 UBM、一開始回銲形成一層很薄的  $Ni_3Sn_4$  介金屬化合物,因此將試片 簡化成四大部分:矽晶片、共晶錫銀銲錫、銅墊層與高分子填充物 (underfill),如圖 4-11 所示。表 4-2 列出用來計算試片溫升的所有資料。 將表內的資料帶入式(10),我們計算出高銲錫凸塊與低銲錫凸塊內部升溫 的比例為:

$$\frac{\Delta T_{LBH}}{\Delta T_{HBH}} = \frac{\sum (mC_P)_{HBH}}{\sum (mC_P)_{LBH}} = 1.15$$

此一結果顯示出低銲錫凸塊內的升溫較高銲錫凸塊高,與圖 4-10 中所呈現的紅外線熱像儀中的結果一致。導致兩者溫升不同的原因,我們認為是銲錫凸塊與凸塊之間的高分子填充物體積的差異所造成。因為兩組試片在一開始的時候就是以體積大小相同的共晶錫銀銲錫凸塊迴銲形成覆晶接點。而上端的矽晶片與板端的銅墊層體積也是一樣大小,兩者唯一的差異就是在高分子填充物的體積差異,當銲錫凸塊的高度下降至原本的三分之一時,整個試片的高度也會下降,原本銲錫凸塊之間的空間就會減少,可填充的高分子填充物的體積也會跟著減少,因此,試片因電遷移測試被加熱時,兩組試片吸收的一樣的熱量,但是低銲錫接點試片的總體積較少,因此低銲錫凸塊接點的升溫會比較高,使得銲錫凸塊內部的平均溫度上升,導致低銲錫接點的平均破壞時間較高銲錫接點短。

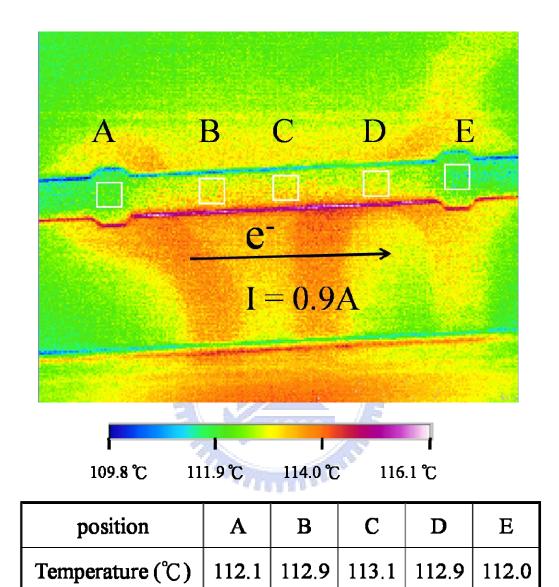

在本研究中,其熱源來自兩個地方,(一)、下端加熱試片的加熱板其溫度維持在 150℃;(二)、電流通過鋁導線形成焦耳熱效應導致試片溫度提高。我們在 150℃之環境通入電流,因焦耳熱效應的影響,會使得試片內的實際溫度略高於環境溫度。圖 4-12 為銲錫接點在 100℃下通以 0.9A的電流大小,晶片端朝上放置的紅外線熱像儀的結果,從圖中的結果,我們可以發現到銲錫凸塊內部的溫度與鋁導線的溫度大致相同。因此,接下來希望以鋁導線電阻溫度係數 (temperature coefficient of resistance, TCR)來校正銲錫內實際溫度。首先,金屬熱電阻的電阻值和溫度一般可以用以下的近似關係式表示,即:

$$R = R_0 \big[ 1 + \alpha \big( T - T_0 \big) \big]$$

式中,R 為溫度 T 時的電阻值; $R_0$  為溫度  $T_0$  時對應電阻值; $\alpha$  為電阻溫度系數。將其展開:

$$R = R_0 + R_0 \alpha T - R_0 \alpha T_o$$

其中  $T_0=0^{\circ}$ 、因此將  $R_0\alpha T_0$  項省略,再將  $R_0\alpha$  合併為  $\alpha'$ 得到:

$$R = R_0 + \alpha' T$$

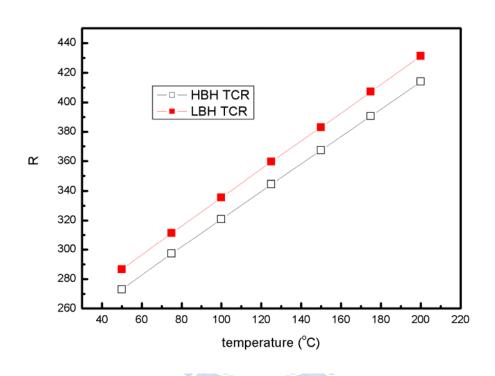

此方程式表示電阻對溫度的變化。因此我們將試片放置於加熱爐中,通以 0.2A的電流,改變加熱爐的溫度,從50℃到200℃,每隔25℃記錄鋁導 線相對應的電阻,通入小電流的目的是要去除鋁導線本身因通電的焦耳熱 效應而發熱,使記錄到的鋁導線電阻與加熱爐之溫度相對應。鋁導線電阻 對加熱爐溫度變化的趨勢如圖 4-13 所示,再利用線性迴歸求得此直線之方程式,我們就可求得鋁導線的鋁導線電阻溫度係數。高低銲錫的電阻對溫度變化的方程式分別為  $R_H=226.7+0.938T_H$ 與  $R_L=238.7+0.963T_L$ 。分別將通電時我們量得之高低銲錫接點鋁導線電阻帶入,求得通電時銲錫內部的實際溫度,如表 4-3 所列。高低銲錫凸塊的溫升分別為 14.1℃與 27.2℃,與紅外線熱像儀所觀察的結果相同,高銲錫接點內的溫升低於低 銲錫接點。

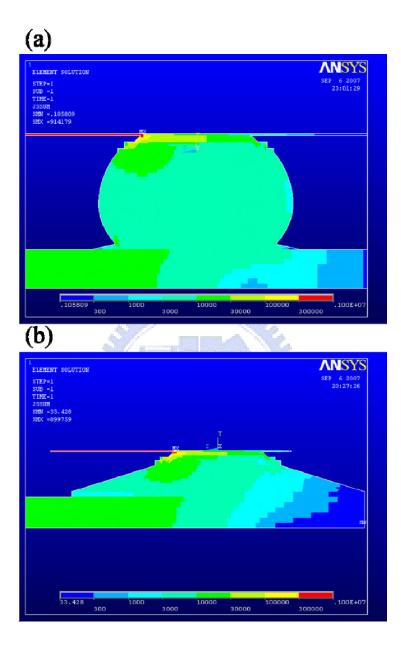

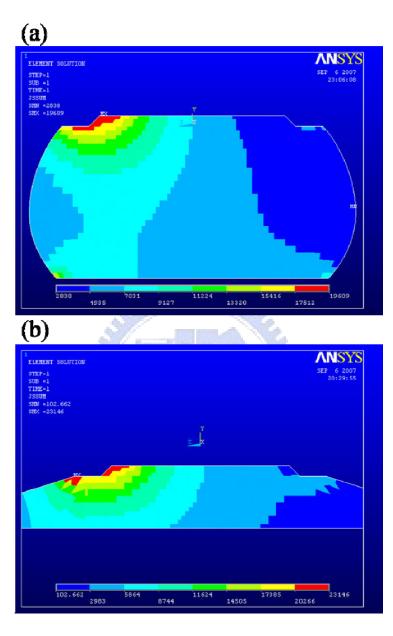

## 4-4 銲錫凸塊內的電流密度分佈

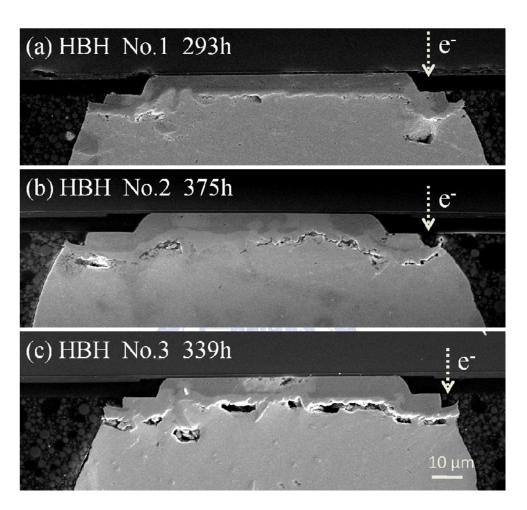

圖 4-14 是我們利用 ANSYS 有限元素分析法對高低銲錫凸塊的模擬結果。模擬通以 0.9A 的電流下其銲錫內的電流分佈情形。圖 4-14 是整個銲錫接點包含鋁導線的模擬結果;不論是高銲錫凸塊或是低銲錫凸塊,電子流由左上端進入左下端流出,與實際實驗中通電的方向一致。由圖中的分佈情形我們發現到在電子流由鋁導線向下進入銲錫凸塊的位置都有嚴重的電流集中情形,鋁導線上的電流密度都比銲錫凸塊內的電流密度大。圖 4-15 是共晶錫銀內部的電流分佈情形。值得注意的是,在高銲錫凸塊中除了在左上端電子流進入端有較大的電流密度外,在遠離電子流進入端的右上端也有一個電流集中的地方,如圖 4-15(a)所示,我們回顧當高銲錫凸塊的 B3 電阻上升至 1.2 倍時,孔洞除了在電子流進入端形成外,在

遠離電子流進入的那一端也有孔洞的生成,如圖 4-16 所示,此為三組不 同之試片當電阻上升至 1.2 倍時的 SEM 橫面影像,在遠離電子流進入端 都出現孔洞形成與 UBM 溶解的現象。這個模擬結果也可以解釋此處為何 有空洞形成的原因。圖 4-15(b)是低銲錫凸塊的電流分佈情形。在低銲錫 凸塊中就沒有發現像高銲錫凸塊中在遠離電子流進入端的第二電流集中 區,電流密度的大小分佈隨著離電子流進入端越遠而下降。除了在銲錫凸 塊上端的電流密度分佈不太相同,高低銲錫凸塊的內部電流密度分佈大致 相同,電流密度隨著越接近板端而遞減。根據模擬的結果高銲錫凸塊內的 最大電流密度為 19609 A/cm<sup>2</sup>,而低銲錫凸塊內的最大電流密度為 23146 A/cm<sup>2</sup>。因為高銲錫凸塊在遠離電流進入端的地方有出現第二個電流集中 區,分散了電流,因此高銲錫凸塊的最大電流密度略小於低銲錫凸塊。因 為我們使用的是厚膜銅 UBM,當電流由鋁導線進入高銲錫凸塊時,因為 方向向下進入銲錫凸塊的電阻比橫向往銅 UBM 的電阻大,因此有一部分 電子流會先散佈於銅 UBM 上,再向下進入高銲錫凸塊,因而出現第二電 流密度集中區的電流分流的情況;而低銲錫凸塊因為電阻較小,因此當電 子流由鋁導線進入低銲錫凸塊之後,不會散佈於銅 UBM,而是直接向下 進入低銲錫凸塊內,所以低銲錫凸塊的最大電流密度較高銲錫凸塊大。

## 4-5 平均破壞時間分析

根據我們實驗的結果,在一開始定義破壞時間為電阻上升 1.2 倍為破壞的 平均破壞時間,高銲錫凸塊與低銲錫凸塊的平均破壞時間比值

$$\frac{t_{HBH}}{t_{LBH}} \cong 3.04$$

分別將我們利用鋁導線電阻求得銲錫凸塊內的溫度與有限元素模擬分析得到最大電流密度代入平均破壞時間公式內運算,其中 n=1.8、 $E_A=0.9$  eV,我們到理論上的平均破壞時間比值

$$\frac{t_{HBH}}{t_{LBH}} = \frac{\frac{A}{j_{HBH}}^{n} \exp\left(\frac{E_{A}}{kT_{HBH}}\right)}{\frac{A}{j_{LBH}}^{n} \exp\left(\frac{E_{A}}{kT_{LBH}}\right)} = 2.7$$

此結果與我們實驗求得的值相當接近,因此我們認為影響高低銲錫接點有不同的平均破壞時間是因為:一、銲錫內的升溫,因為銲錫凸塊高度下降,其周圍包覆的高分子填充物體積減少,在相同的吸收熱之下,使得整體溫升增加;二、因為單顆銲錫凸塊的電阻大小不同,使得高銲錫內有電子流分流形成第二電流集中區,使最大電流密度下降,因此低銲錫凸塊內的最大電流密度較大。綜合兩種因素,低銲錫接點有較短的平均破壞時間。

若我們將溫度與電流密度對平均破壞時間的影響分別討論,首先我們 將利用鋁導線溫度電阻效應所求得之銲錫球內實際溫度代入平均破壞時 間公式,而電流密度為定值,所得之結果如下所示:

$$\frac{t_{HBH}}{t_{LBH}} = \frac{\frac{A}{j^{n}} \exp\left(\frac{E_{A}}{kT_{HBH}}\right)}{\frac{A}{j^{n}} \exp\left(\frac{E_{A}}{kT_{LBH}}\right)} = 2.01$$

若固定溫度為基板溫度 150℃,再將模擬結果之最大電流密度帶入平均破壞時間公式,可得:

$$\frac{t_{HBH}}{t_{LBH}} = \frac{\frac{A}{j_{HBH}^{n}} \exp\left(\frac{E_{A}}{kT}\right)}{\frac{A}{j_{LBH}^{n}} \exp\left(\frac{E_{A}}{kT}\right)} = 1.35$$

上列之結果顯示,溫度對平均破壞時間的影響大於電流密度,因此我們認為造成低銲錫接點有較短的平均破壞時間,最主要的因素是低銲錫接點內的溫度大於高銲錫接點。

#### 4-6 結論

在相同的通電條件下,低銲錫接點的平均破壞時間均小於高銲錫接點。根據紅外線熱像儀的結果,通電時低銲錫接點內的平均溫度高於高銲錫接點,主要因素是銲錫凸塊高度下降,使問圍填充高分子填充物體積下降,通入電流後在相同的吸熱條件之,使得整個銲錫接點溫升增加;再者,因為單顆銲錫凸塊的電阻大小不同,電流進入高銲錫凸塊之後,部分電子流會先散佈於銅 UBM 上,在向下進入高銲錫凸塊內,使得高銲錫內有電

子流分流形成第二電流集中區,使最大電流密度下降,因此低銲錫凸塊內 的最大電流密度較大。綜合以上因素,低銲錫接點有較短的平均破壞時間。

我們利用鋁導線通電時的電阻變化結合電阻溫度係數求得銲錫凸塊 內的實際溫度,加上模擬出的做大電流密度,代入平均破壞時間公式,所 求的結果與實驗值大致吻合。

圖 4-1 在 150℃下通入 0.9A, 通電時間對電阻變化曲線圖, (a)高銲 錫接點,通電時間 405h, (b)低銲錫接點,通電時間 184h

圖 4-2 在 150℃下通入 0.9A, B3 電阻上升至 1.2 倍時之 B2 SEM 剖面圖, (a)高銲錫接點,通電時間 405h, (b)低銲錫接點,通電時間 184h

圖 4-3 在 150℃下通入 0.9A,B3 電阻上升至 1.2 倍時之 B3 SEM 剖面圖, (a)高銲錫接點,通電時間 380h,(b)低銲錫接點,通電時間 118h

圖 4-4 在 150°C下通入 0.9A,B3 電阻上升至 1.5 倍時之 B3 SEM 剖面圖, (a) 高銲錫接點,通電時間 405h,(b)低銲錫接點,通電時間 184h

| Element | Weight% | Atomic% |

|---------|---------|---------|

| Ni K    | 23.71   | 38.59   |

| Sn L    | 76.29   | 61.41   |

| Totals  | 100.00  | E       |

| Element | Weight% | Atomic% |

|---------|---------|---------|

| Ni K    | 22.88   | 37.49   |

| Sn L    | 77.12   | 62.51   |

| Totals  | 100.00  |         |

圖 4-5 低銲錫接點內介金屬化合物成分分析

圖 4-6 (a)高銲錫接點斷路時,紅外線顯熱儀結果

(b)低銲錫接點斷路時,紅外線顯熱儀結果

圖 4-7 (a)高銲錫接點 (b)低銲錫球斷路時橫截面 SEM 圖

圖 4-8 矮銲錫球斷路時(a)橫截面 SEM 圖 (b) EDX 成分分析結果

圖 4-9 (a) 低銲錫接點斷路電阻變化對通電時間曲線圖

# (b) 圖(a)中紅框位置放大圖

圖 4-10 (a) 高銲錫接點橫截面通入 0.45A 之溫度分佈結果

(b) 低銲錫接點橫截面通入 0.45A 之溫度分佈結果

圖 4-11 簡化試片示意圖

圖 4-12 100℃下通入 0.9A 電流鋁導線與銲錫凸塊內部平均溫度

圖 4-13 高低銲錫接點鋁導線電阻對溫度變化圖

圖 4-14 銲錫接點通過 0.9A 電流之模擬結果,

(a) 高銲錫凸塊(b)低銲錫凸塊

圖 4-15 銲錫接點通過 0.9A 電流之模擬結果, (a)高銲錫凸塊內(b)低銲錫凸塊內

圖 4-16 高銲錫凸塊電阻上升 20%之横截面 SEM 影像圖 (a) 293h, (b) 375h, (c) 339h 之通電時間

表 4-1 不同條件下,高低銲錫接點的平均破壞時間

| Temperature Applied current |     | 1.2R <sub>e</sub> as<br>failure time (h) |       |       | 1.5R <sub>e</sub> as failure time (h) |      | Failure time<br>(open circuit) (h) |  |

|-----------------------------|-----|------------------------------------------|-------|-------|---------------------------------------|------|------------------------------------|--|

| (6)                         | (A) | HBH                                      | LBH   | HBH   | LBH                                   | HBH  | LBH                                |  |

| 150                         | 0.9 | 335.8                                    | 110.6 | 404.5 | 190.5                                 | 1521 | 1077                               |  |

|                             | 0.8 | 909                                      | 235   | _     |                                       |      |                                    |  |

表 4-2 計算溫差所使用之資料

|                 | Volume<br>(μm³)      | Density<br>(g/mm³) | Mass<br>(g)                    | Cp<br>(J/g. ℃) |

|-----------------|----------------------|--------------------|--------------------------------|----------------|

| Si Chip         | ~1.6x10 <sup>g</sup> | 2.33               | ~3.7 <b>×</b> 1 <b>0</b> -4    | 0.7            |

| SnAg solder     | 8500                 | 7.36               | 6.3×10 <sup>-8</sup>           | 0.2            |

| Underfill (HBH) | ~6.5x10 <sup>7</sup> | 1.34               | ~8.7×10 <sup>-5</sup>          | 1.13           |

| Underfill (LBH) | ~3.3x10 <sup>7</sup> | 1.34               | ~4.4 <b>x</b> 10 <sup>-5</sup> | 1.13           |

| Cu pad          | ~2.1x10 <sup>6</sup> | 8.96               | ~1.9×10 <sup>-5</sup>          | 0.385          |

表 4-3 利用鋁導線電阻結合鋁電阻溫度係數,所求得知銲錫凸塊內溫度

| Solder joint number | Lifetime (hours) | Al trace resistance $(m\Omega)$ | Temperature in solder (°C) |

|---------------------|------------------|---------------------------------|----------------------------|

| HBH #1              | 293              | 379.8                           | 163.2                      |

| #2                  | 375.1            | 381.7                           | 165.2                      |

| #3                  | 339.4            | 380.3                           | 163.7                      |

| <b>HBH</b> average  | 335.8            | 380.6                           | 164.1                      |

| LBH #1              | 88.1             | 411.6                           | 179.5                      |

| #2                  | 106.4            | 410.2                           | 178.1                      |

| #3                  | 137,4            | 406.3                           | 174                        |

| LBH average         | 110.6            | 409.4                           | 177.2                      |

# 參考文獻

- [A] R.J. Wassink, Soldering in Electronics, Electrochemical Pub. Ltd., pp. 99, 1984.

- [B] K. N. Tu A Chih Chen A Albert T. Wu, J Mater Sci: Mater Electron, 18, pp.269-281, 2007

- [1] Intel Technology Journal, 9, pp. 110, 2005.

- [2] V. B. Fiks, Soviet Physics Solid State, **1**, pp. 14-28, 1959.

- [3] European Union Waste in Electrical and Electronic Equipment (WEEE) Directive, 3rd Draft, May 2000.

- [4] Japanese Ministry of Health and Welfare Waste Regulation on Un-Reusable Pb, June 1998.

- [5] A. Lee, C.E. Ho, and K.N. Subramanian, J. Mater. Res., 22, pp. 3266, 2007

- [6] S. W. Liang, Y. W. Chang, T. L. Shao, and Chih Chen, Appl. Phys. Lett, 89,pp. 022117, 2006

- [7] K. N. Tu. J. Appl. Phys., 94, pp. 5451-5473, 2003

- [8] Christian Witt. Electromigration transport mechanisms and back flow in Al interconnects, first year report, Max-Planck-Institute fur Metallforschung Stuttgart,91 July, 1998

- [9] Paul S. Ho and Thomas Kwok, Electromigration in metals, Rep. Prog. Phys. **52**, pp. 301-348, 1989

- [10] H. B. Huntington and A.R. Grone, J. Phy. & Chem. Solids, 20, 76, 1961

- [11] K. N. Tu, J. W. Mayer and L.C. Feldman, "Electronic Thin Film Science," Macmillan, New York, 1992

- [12] C. Y. Liu, C. Chen, C. N. Liao, and K. N. Tu, Appl. Phys. Lett. 75, pp. 58 1999

- [13] C. Y. Liu, C. Chen, and K. N. Tu, J. Appl. Phys. 88,pp. 5703 2000

- [14] J. R. Black, Proceedings of the IEEE, **57**, pp. 1587-1594, 1969

- [15] T. L. Shao, S. W. Liang, T. C. Lin, and Chih Chen, J. Appl. Phys., 98, pp. 044509, 2005

- [16] T. Y. T. Lee, T. Y. Lee, and K. N. Tu, Proceedings of the 51<sup>st</sup> Electronic Components and Technology Conference, IEEE Components, Packaging, and Manufacturing Technology Society, Orlando, Florida, USA, p. 558, 2001

- [17] T. L. Shao, S. H. Chiu, Chih Chen, D.J. Yao, and C.Y. Hsu, Journal of Electronic Materials, 33, pp. 1350-1354, 2004.

- [18] Brook Chao, Seung-Hyun Chae, and Paul S. Ho J. Appl. Phys. 100, pp. 084909, 2006

- [19] M. Ding, Guotao Wang, Brook Chao, and Paul S. Ho J. Appl. Phys. 99, pp. 094906, 2006

- [20] Y.H. Chen, T.L. Shao, P.C. Liu, and Chih Chen, J. Mater. Res., 20, pp. 2432-2442, 2005

- [21] Brook Chao, Seung-Hyun Chae, Xuefeng Zhang, Kuan-Hsun Lu, Jay Im\_and P.S. Ho, Acta Materialia, **55**, pp. 2805-2814, 2007,

- [22] Seung-Hyun Chae, Xue-feng Zhang, and Paul S. Ho, Mater Sci: Mater Electron, **18**, pp. 247-258, 2006

- [23] 關於吉時利科技公司相關資訊請參閱其官方網站,網址: http://www.keithley.com/

- [24] 關於安捷倫科技公司相關資訊請參閱其官方網站,網址: http://www.home.agilent.com/

- [25] 關於美國國家儀器公司相關資訊請參閱其官方網站,網址: http://www.ni.com/

- [26] S.W. Liang, Y.W. Chang, C. Chen, Y.C. Liu, K.H. Chen, and S.H. Lin, Journal of Electronic Materials, 35, pp. 1647-1654, 2006