# 國 立 交 通 大 學 材料科學與工程學系 博士 論 文

磁阻式元件之磁阻抗及氧化鎢電阻式記憶體的研究

Study of Magneto Impedance for Magneto Resistive Memory and Tungsten Oxide for Resistive Memory

研究生:簡維志

指導教授 :林鵬 教授 姚永德 教授

中華民國九十九年三月

# 磁阻式元件之磁阻抗及氧化鎢電阻式記憶體的 研究

博士生: 簡維志

指導教授:林鵬 教授 姚永德 教授

#### 國立交通大學

材料科學與工程學系

# 摘要

本論文主要研究磁阻式元件之磁阻抗行為及氧化鎢記憶體特性,以求對於電阻式記 憶體的物理特性能有更深入地了解。

磁阻式元件是磁性隨機存取記憶體中扮演相當重要的角色,其中包含類自旋閥元件 及穿隧式磁阻元件。磁阻式元件的直流電性行為已經被廣泛的研究,然而關於交流電性 的行為則是很少被研究。因此在本篇論文的前半部分我們主要探討磁阻式元件的交流特 性。

我們提供了一個藉由類自旋閥的交流特性,來對奈米氧化層在類自旋閥的貢獻做非 破壞性的分析。此外我們以等效電路模型來解釋穿隧式磁阻元件的交流特性,並且在穿 隧式磁阻元件 Ru (5nm) /Cu (10nm) /Ru(5nm) /IrMn(10nm) /CoFeB(4nm) /Al(1.2nm)-oxide /CoFeB (4nm) /Ru (5nm) 發現在很高的交流頻率 17.7 百萬赫茲,此元件的虛部磁阻抗, 有非常劇烈的變化可達 17000%,這個發現使的磁穿隧元件有潛力應用於高頻的感應式元 件。

本論文的後半部分,研究有關於氧化鎢電阻式隨機存取記憶體。由於電阻式隨機存 取記憶體,具有極佳的微縮能力及具備做成三維元件的可能性,所以一直被看好能取代 電子式儲存的記憶體;然而其基礎理論並不完備,且元件的表現還有待更進步。因此我

i

們提出了一個具新穎性的氧化鎬電阻式隨機存取記憶體,其製作方式只需在現有半導體 製程多一道曝光程序,並且完全符合 CMOS 製程。我們以快速氧化技術所製備的氧化鎬 電阻式隨機存取記憶體,可表現出極佳的元件特性,例如低電流操作、極短時間操作、 好的記憶維持能力及可達百萬次的操作次數。

對於氧化鎬電阻式隨機存取記憶體,我們進一步發現頂部電極的功函數大小可以改 變傳導機制,在低功函數頂部電極其電流傳導機制符合空間電荷限制電流的理論,而在 高功函數頂部電極其電流傳導機制符合熱離子發射理論。此研究提供了藉著改變頂部電 極,有機會改善元件的特性表現。所以根據這個發現,我們設著去研究利用鎳當頂部電 極的氧化鎬電阻式隨機存取記憶體。此新元件表現出非常好的特性,如低於200 微安培 的操作電流、大於100 倍的阻值變化及在攝氏 85 度的環境下,大於300 年的記憶維持 能力。

# Study of Magneto Impedance for Magneto Resistive Memory and Tungsten Oxide for Resistive Memory

Student : Wei-Chih Chien

Advisor : Prof. Pang Lin Prof. Yeong-Der Yao

Department of Materials Science and Engineering National Chiao Tung University

### ABSTRACT

This dissertation is devoted to study the magneto impedance effect of magneto resistive elements, and tungsten oxide resistive memory extensively for providing in-depth their physical understanding.

The magneto resistive elements such as pseudo spin valve (PSV) and magneto tunneling junction (MTJ) play a role for magneto random access memory (MRAM). The DC behaviors for magneto resistive elements have been widely studied, but the AC behaviors are still rare. Thus, in the first half of this dissertation we focus on the AC behaviors of magneto resistive elements.

By using AC characteristics, we provide a new non-destructive analysis method to study the nano-oxide layer effects of PSV. Besides, the equivalent circuit model is used to describe the AC behaviors for MTJ. For Ru (5nm) /Cu (10nm) /Ru(5nm) /IrMn(10nm) /CoFeB(4nm) /Al(1.2nm)-oxide /CoFeB (4nm) /Ru (5nm) system, a huge imaginary part of magneto impedance ratio more than 17000% is observed at high frequency 17.7MHz. Magneto impedance effect of the MTJ is potentially a sensitive sensor for high frequencies.

In the second half of this dissertation, tungsten oxide resistive random access memory is

studied extensively. Although resistive random access memory (RRAM) is forecasted to be the promising solutions to replace the electron storage memory due to its excellent scalability and 3D possibility, up to now, the fundamental understanding is still very limited and device performance is required to improve. Thus, we proposed a novel WO<sub>X</sub> for the RRAM system, because it requires only one extra mask under standard CMOS process. By using rapid thermal oxidation (RTO) for the WO<sub>X</sub> RRAM, we have demonstrated its good performance such as low switching current, fast programming speed, good thermal stability, and high endurance > 1M times for nonvolatile memory.

Under this study, we further find the work function (WF) of the electrode is a key element determining the conduction mechanism for WO<sub>X</sub> RRAM. SCLC (space charge limit current) mechanism and thermionic emission mechanism are identified for low WF and high WF electrodes, respectively. These studies imply that the device performance may be significantly improved by selecting the proper electrode. With this guideline, Ni/WO<sub>X</sub>/W device is investigated. The new Ni/WO<sub>X</sub>/W device shows very good performance that operates at <200uA switching current, a 100X resistance ratio window, and extremely good data retention of > 300 years at 85 °C.

#### 誌謝

在交大三年多求學的日子,我得到很多人的幫忙及支持,使的我在攻讀博士的生涯 能克服層層的阻礙,並且對於未來的挑戰更有信心去面對。所以這本論文是代表著我對 您們獻上我由衷的感謝,及對我們一起走過不可抹滅的足跡。

首先我要感謝我的母親芳如,您真的很辛苦,獨自一人將我撫養長大,沒有您的支 持讓我無後顧之憂,我今日無法完成我的博士學業,我的學位有一半是屬於您的。我也 要感謝我的叔叔,謝謝您總是對我視如已出也很照顧我母親,您是我決定續續升學的關 鍵,真的很感激您,希望在後半輩子我能好好孝順您和母親。我還要感謝我最摯愛的外 公外婆,我有接近一半的的時間是由您們將我辛苦帶大,看著您們的背影,我學習到人 生其實也可以過的平凡又幸福。

接下來要感謝我的指導教授姚永德老師,從碩士班到博士班這五年多來,很謝謝您 對我的指導及照顧,謝謝您總是對我未來的發展細心的著想,我從您的身上學習到了很 多身為師長的態度,我希望我以後若是有這個機會身為他人的師長,我也能和您看齊。

我要感謝旺宏電子對我的栽培,博士生涯能在前瞻實驗室做研究真的是一件很幸福 的事,有一群很好的夥伴,互相幫忙、互相切磋,這對我的研究,有莫大無比的幫助。 更謝謝逸舟及 Rich 對我博士生涯的磨練及指導,我從您們的身上學習到如何做研究及 做研究該有的態度,也期望在未來我能和前瞻實驗室的夥伴們並肩而立。

我還要感謝一個對我來說很特別的團體,交大羽球隊,謝謝這支球隊提供我一個轉 換心情的場所,能適度排解讀書及工作的壓力,雖然說有時候也會常常測試我的極限, 在我忙不過來的時候,火上加油一番,不過跟你們在一起打球是很快樂的,也謝謝廖威 彰教練對我的指導及照顧,我從您的身上學到了許多做事負責任的道理。

最後要謝謝我的女友巧愛,謝謝妳七年多來的陪伴,讓我在求學生涯有溫柔的避風 港,也多謝妳的鼓勵,讓我在一次接一次的挫折中,能快速的爬起來,我相信在我們未 來的日子裡,我們一定能互相扶持,繼續往我們的人生大步邁進。

我誠摯的感謝曾經幫助過我的人,我以這本論文,代表我對您們獻上的敬意。

v

# LIST OF CONTENTS

# Page

| Abstract (Chinese)                                                                                                                                                      | i                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Abstract (English)                                                                                                                                                      | iii                        |

| Acknowledgement (Chinese)                                                                                                                                               | v                          |

| List of Contents                                                                                                                                                        | vi                         |

| List of Figures                                                                                                                                                         | xi                         |

| Chapter 1: Introduction<br>1.1 Background and Motivation                                                                                                                | 1                          |

| 1.2 Thesis Organization                                                                                                                                                 | 3                          |

| Chapter 2: Basic of MRAM and RRAM                                                                                                                                       | 4                          |

| 2.1 Magnetoresistive Random Access Memory (MRAM)                                                                                                                        | 4                          |

|                                                                                                                                                                         |                            |

| 2.1.1 Magnetoresistance Effect                                                                                                                                          | 4                          |

| 2.1.1 Magnetoresistance Effect      2.1.2 Magneto Impedance Theory                                                                                                      | 4<br>11                    |

|                                                                                                                                                                         |                            |

| 2.1.2 Magneto Impedance Theory                                                                                                                                          | 11                         |

| <ul><li>2.1.2 Magneto Impedance Theory</li><li>2.1.3 Field Driven Magnetization Switching Designs</li></ul>                                                             | 11<br>13                   |

| <ul><li>2.1.2 Magneto Impedance Theory</li><li>2.1.3 Field Driven Magnetization Switching Designs</li><li>2.1.4 Spin Torque Transfer Driven Switching Designs</li></ul> | 11<br>13<br>16             |

| <ul> <li>2.1.2 Magneto Impedance Theory</li></ul>                                                                                                                       | 11<br>13<br>16<br>20       |

| <ul> <li>2.1.2 Magneto Impedance Theory</li></ul>                                                                                                                       | 11<br>13<br>16<br>20<br>20 |

| Chapter 3: Magneto Impedance Study for Pseudo Spin Valves                   | 25 |

|-----------------------------------------------------------------------------|----|

| 3.1 Introduction                                                            | 25 |

| 3.2 Experiments                                                             | 26 |

| 3.3 Magneto Impedance Behavior and Its Equivalent Circuit Analysis of a     |    |

| Co/Cu/Co/Py Pseudo Spin Valve with a Nano-Oxide Layer                       | 26 |

| 3.3.1 Equivalent Circuit for Pseudo Spin Valve                              | 26 |

| 3.3.2 Magneto Impedance Behavior for Pseudo Spin Valve                      | 29 |

| 3.3.3 Annealing Effect                                                      | 32 |

| 3.3.4 Conclusion                                                            | 35 |

| 3.4 Characterization of a Nano-Oxide Layer in a Pseudo Spin Valve by Comple |    |

| Magneto-Impedance Spectroscopy                                              | 36 |

| 3.4.1 Magneto Impedance Study for Different Thickness of Bottom Nano-Oxide  | 36 |

| Layer                                                                       |    |

| 3.4.2 Double Nano-Oxide Layers Effect                                       | 40 |

| 3.4.3 Conclusion.                                                           | 42 |

| 3.5 Summary                                                                 | 42 |

# Chapter 4: Magneto Impedance Study for Magneto Tunneli

| Junctions                                                               | 44 |

|-------------------------------------------------------------------------|----|

| 4.1 Introduction                                                        | 44 |

| 4.2 Experiments                                                         | 44 |

| 4.3 Enhancement and Inverse Behaviors of Magneto Impedance in a Magneto |    |

| Tunneling Junction by Driving Frequency                                 | 45 |

| 4.3.1 Equivalent Circuit for Magneto Tunneling Junction                 | 45 |

| 4.3.2 Frequency Dependence for Magneto Tunneling Junction               | 46 |

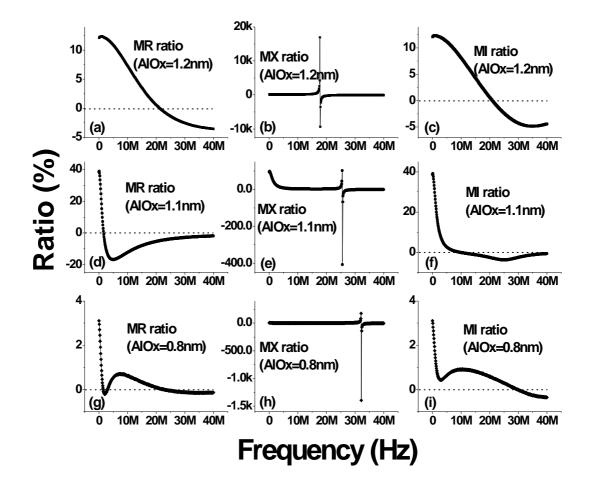

| 4.3.3 MR, MX, and MZ Ratios                                             | 51 |

| 4.3.4 Conclusion                                                                        | 51 |

|-----------------------------------------------------------------------------------------|----|

| 4.4 Oscillating Voltage Dependence of High Frequency Impedance in Magnetic              |    |

| Tunneling Junctions                                                                     | 52 |

| 4.4.1 Oscillating Voltage Versus Effective Capacitance                                  | 52 |

| 4.4.2 Oscillating Voltage Versus MI Ratio                                               | 54 |

| 4.4.3 Conclusion                                                                        | 55 |

| 4.5 Magneto impedance study in magneto tunneling junctions with different               |    |

| thickness of its barrier layer                                                          | 55 |

| 4.5.1 Magneto Impedance Study for Different Barrier Thickness                           | 55 |

| 4.5.2 Conclusion                                                                        | 63 |

| 4.6 Summary                                                                             | 64 |

| STATISTICS .                                                                            |    |

| Chapter 5: WO <sub>x</sub> RRAM Using Down Stream Plasma Oxidation.                     | 65 |

| 5.1 Introduction                                                                        | 65 |

| 5.2 Device Fabrication                                                                  | 66 |

| 5.3 Bipolar Switching Characteristics for Self-Aligned DSPO WO <sub>x</sub> Resistance  |    |

| RAM (R-RAM) with Multi-Level Operation                                                  | 67 |

| 5.3.1 Cell Operation                                                                    | 67 |

| 5.3.2 Device Reliability                                                                | 72 |

| 5.3.3 Conclusion                                                                        | 75 |

| 5.4 Unipolar Switching Characteristics for Self-Aligned DSPO WO <sub>x</sub> Resistance |    |

| RAM (R-RAM)                                                                             | 76 |

| 5.4.1 Sample Preparation and Analysis                                                   | 76 |

| 5.4.2 Unpolar Switching Characteristics                                                 | 79 |

| 5.4.3 Device Reliability                                                                | 82 |

| 5.4.4 Conclusion                                                                        | 82 |

|                                                                                         |    |

| 5.5 Summary                                                          | 84  |

|----------------------------------------------------------------------|-----|

| <b>Chapter 6:</b> WO <sub>x</sub> RRAM Using Rapid Thermal Oxidation | 85  |

| 6.1 Introduction                                                     | 85  |

| 6.2 Experiments                                                      | 86  |

| 6.3 High-Speed Multilevel Resistive RAM Using RTO WO <sub>X</sub>    | 87  |

| 6.3.1 Basic Electrical Characteristics                               | 87  |

| 6.3.2 Device Performance                                             | 90  |

| 6.3.3 Transient Effect                                               | 91  |

| 6.3.4 Multi-Level Operation                                          | 94  |

| 6.3.5 Switching Mechanism Supposition                                | 96  |

| 6.3.6 Conclusion                                                     | 98  |

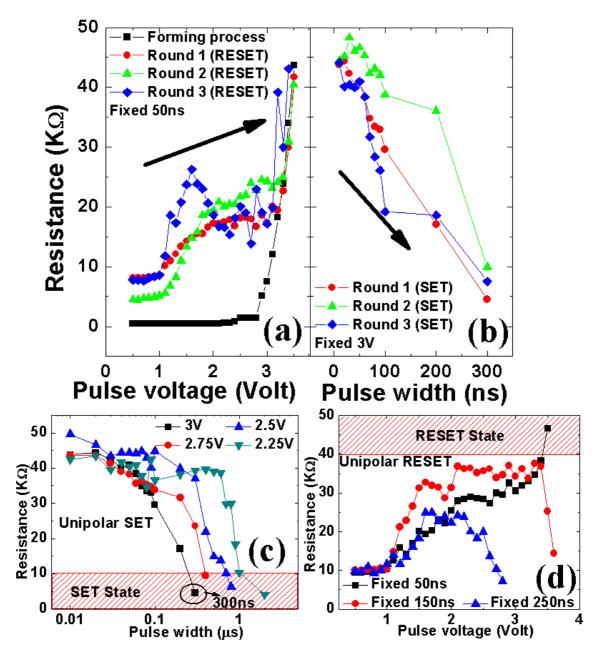

| 6.4 Unipolar Switching Behaviors of RTO WO <sub>X</sub> RRAM         | 99  |

| 6.4.1 Pulse Voltage and Pulse Width Dependence                       | 99  |

| 6.4.2 IV Characteristics                                             | 101 |

| 6.4.3 Performance                                                    | 103 |

| 6.4.4 Conclusion                                                     | 103 |

| 6.5 A Study of Top Electrodes Effect for WO <sub>X</sub> RRAM        | 104 |

| 6.5.1 Conduction Mechanism                                           | 104 |

| 6.6 Summary              | 116 |

|--------------------------|-----|

| 6.5.3 Conclusion         | 115 |

| 6.5.2 Device Performance | 111 |

| Chapter 7:      | Conclusions                | 117 |

|-----------------|----------------------------|-----|

| 7.1 Summary of  | Findings and Contributions | 117 |

| 7.2 Suggestions | for Future Works           | 118 |

| Reference                          | 119 |

|------------------------------------|-----|

| VITA                               | 130 |

| Publication List of Wei-Chih Chien | 131 |

# LIST OF FIGURES

Page

| 4  |

|----|

|    |

| 5  |

| 7  |

|    |

| 7  |

| 10 |

|    |

| 10 |

|    |

| 10 |

|    |

| 11 |

|    |

|    |

| 12 |

|    |

|    |

| 14 |

|    |

|    |

15

magnetization reversal starts at the center of the element with quasi-coherent magnetization rotation. The reversed region expands towards the ends as the reversal completes.

[Fig. 2.12] Schematic drawing of the memory element array. Each memory element is connected to a field effect transistor for read addressing. A grid of x-y conducting wires, known as the digital lines (wires along the x-direction) and word lines (wires along the y-direction), is placed over and below the memory elements for providing the magnetic field for the write operation. Each memory element is located at a cross in the x-y wire grid. The lower bottom shows the switching field threshold contour, known as the Stoner–Wohlfarth switching astroid. The magnetization of the storage layer will remain unchanged if the field applied is located within the enclosed region of the astroid. Otherwise, the magnetic moment will irreversibly switch to the ESN direction of the word line field.

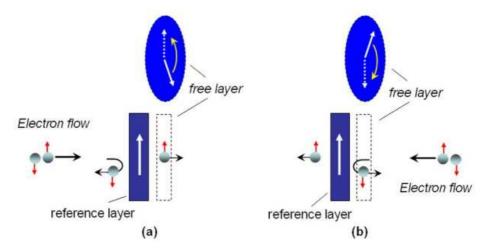

[Fig. 2.13] Illustration of spin torque transfer. Injecting a current through a ferromagnetic layer of a "fixed" magnetization, the current will be spin polarized. Placing a free layer nearby, the spin polarized current will result in a torque that will act to rotate free-layer magnetization away from the equilibrium orientation. The sign of spin polarization direction outside of the "fix" layer reverses with reversing direction of current.

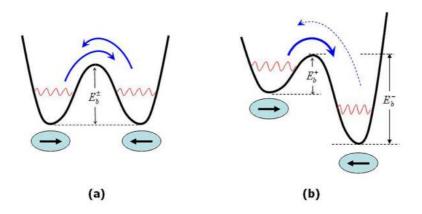

[Fig. 2.14] Illustration of (a) thermally excited magnetization switching and (b) thermally assisted magnetization switching in which the energy barrier is lowered due to the presence of either a magnetic field or a spin torque transfer by injected spin polarized current.

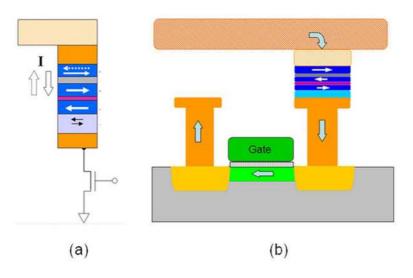

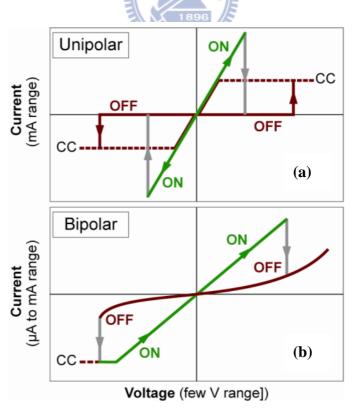

[Fig. 2.15] Illustration of a spin torque transfer MRAM memory cell. (a) Schematic 19 view and (b) illustration of the memory cell with addressing transistor on a Si wafer. [Fig. 2.16] Unipolar and bipolar switching schemes. CC denotes the compliance

15

17

19

| current, often needed to limit the ON current                                                                   | 20 |

|-----------------------------------------------------------------------------------------------------------------|----|

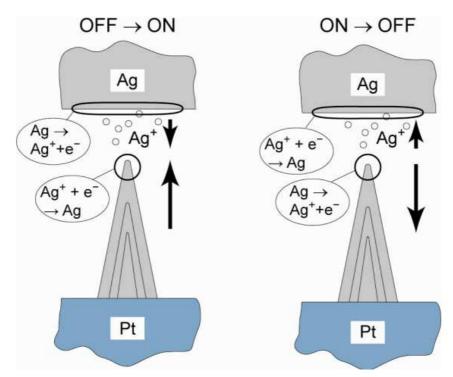

| [Fig. 2.17] Sketch of a resistive switching effect based on the electrochemical                                 |    |

| metallization process.                                                                                          | 22 |

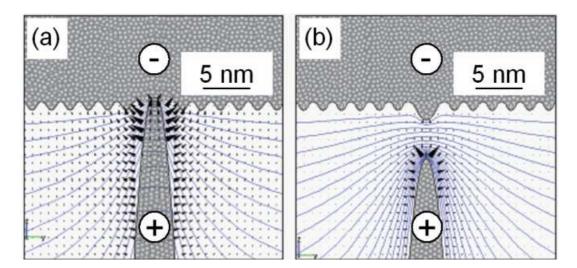

| [Fig. 2.18] Field simulation of the front-most Ag dendrite and the Ag electrode; (a)                            |    |

| late ON state; (b) early OFF state.                                                                             | 22 |

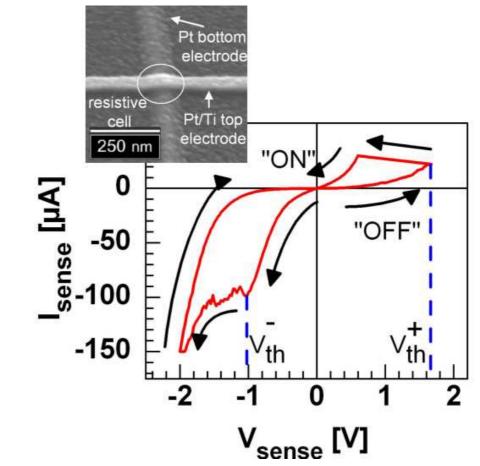

| [Fig. 2.19] I-V measurement of a 100 x 100 nm <sup>2</sup> Pt/TiO <sub>2</sub> /Ti/Pt resistive switching cell. |    |

| The SEM picture shows the single cell in cross junction configuration (C. Kügeler et                            |    |

| al., unpublished data).                                                                                         | 23 |

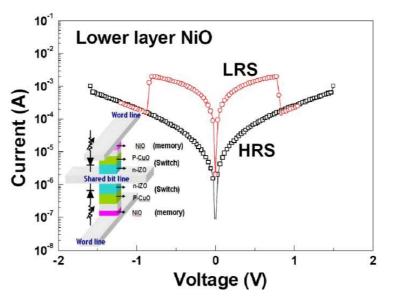

| [Fig. 2.20] 2-stack 1D-1R cross-point structure with oxide diodes as switch elements.                           | 24 |

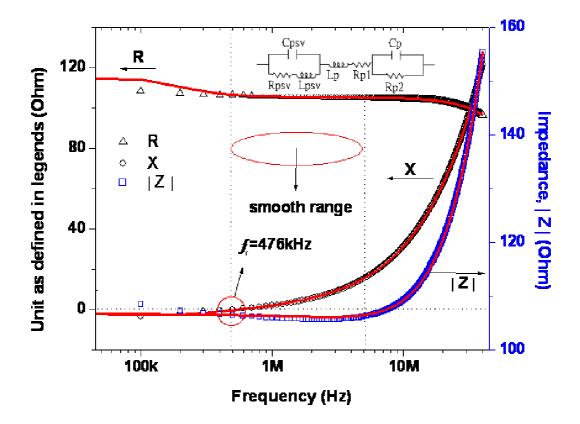

| [Fig. 3.1] The frequency dependences of $ Z $ , R and X for the PSV at zero field. The                          |    |

| resonance frequency (fr) is found at 476 kHz, where X vanishes. The experimental                                |    |

| data (open symbols) are very close to the theoretical result (solid curves) calculated                          |    |

| from the equivalent circuit shown in the inserted panel.                                                        | 27 |

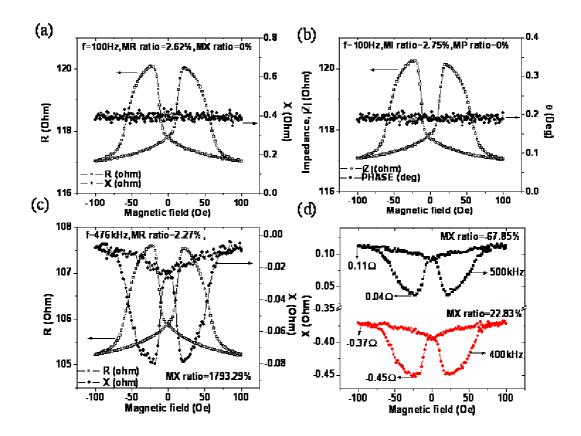

| [Fig. 3.2] (a), and (b) magneto impedance at 100 Hz. At this low frequency, the                                 |    |

| magneto transport property can be regarded as DC. (c) at resonance frequency $f_r$ (476                         |    |

| kHz), MX shape of loop reverse to MR loop. (d) The value of MX is negative at f $<$                             |    |

| $f_r$ , and switches to positive at $f > f_r$ .                                                                 | 29 |

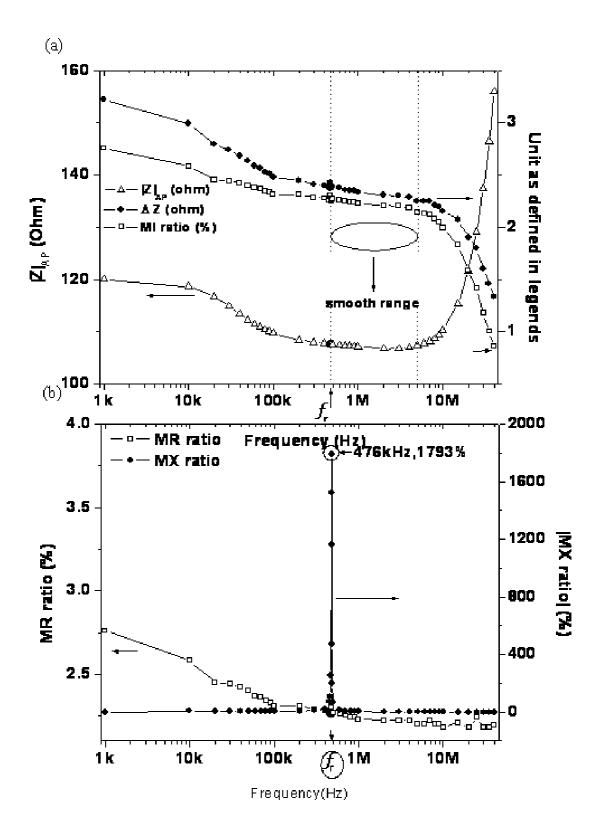

| [Fig. 3.3] (a) The frequency dependences of $ Z _{AP},\ \bigtriangleup Z$ and MI ratios. (b) The                |    |

| frequency dependences of MR and  MX ratio .                                                                     | 30 |

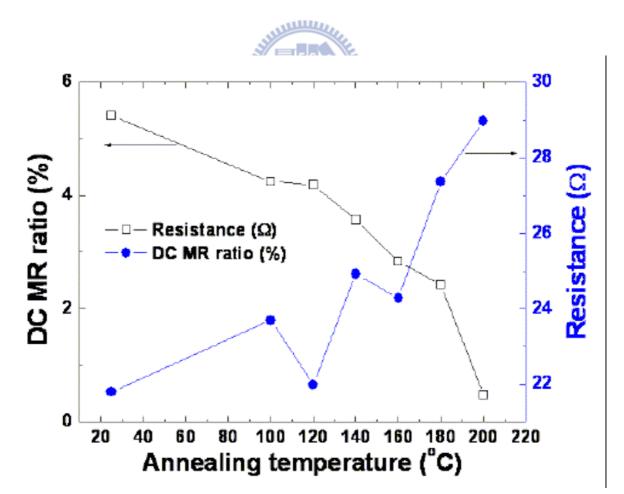

| [Fig. 3.4] The DC MR ratio and resistance (R) of the PSV are functions of the                                   |    |

| annealing temperature.                                                                                          | 32 |

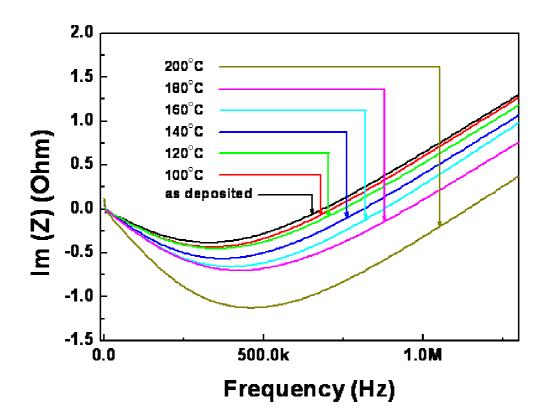

| [Fig. 3.5] Imaginary part of impedance curves for PSV with different AT                                         |    |

| temperatures ranging from $R_T$ to 200°C.                                                                       | 33 |

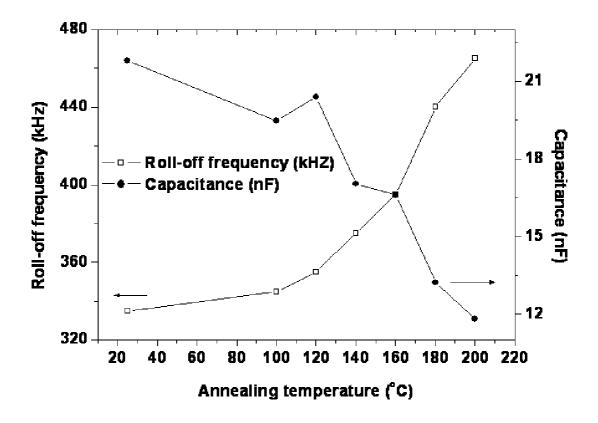

| [Fig. 3.6] The roll-off frequency and effective capacitance of the PSV are functions                            |    |

| of the annealing temperature.                                                                                   | 34 |

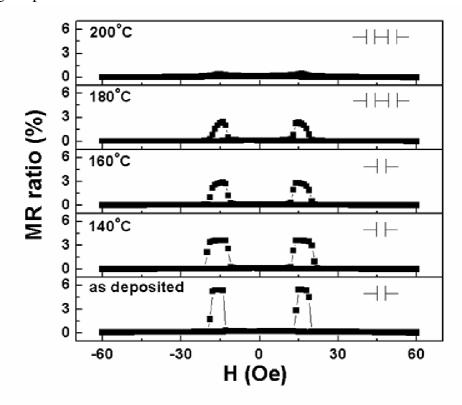

| [Fig. 3.7] The hysteresis loops of the PSV with AT temperatures $R_T$ , 140°C, 160°C,                           |    |

|                                                                                                                 |    |

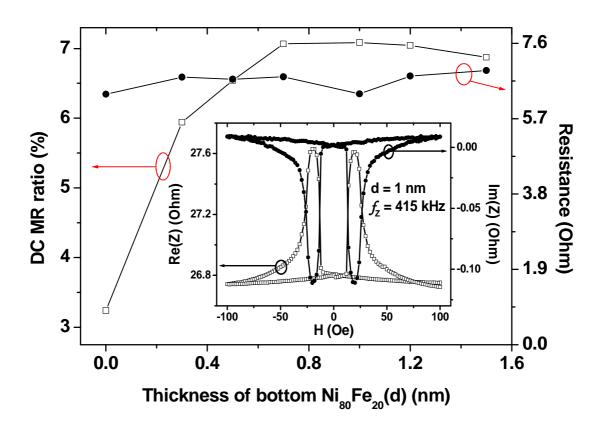

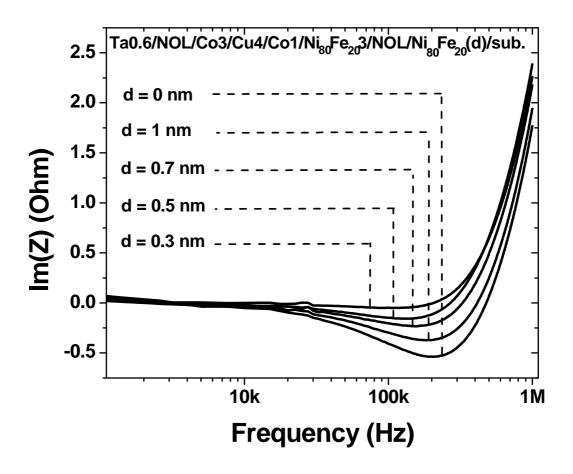

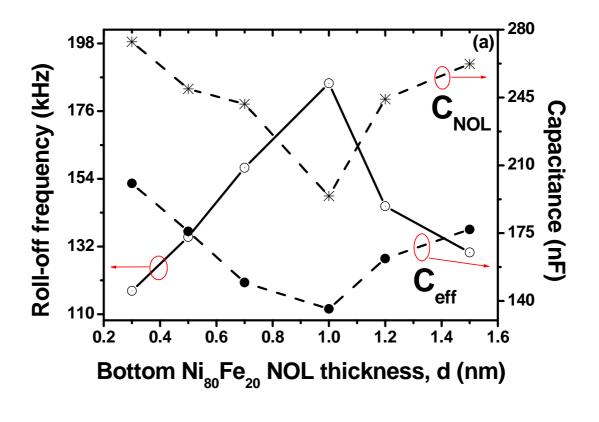

45

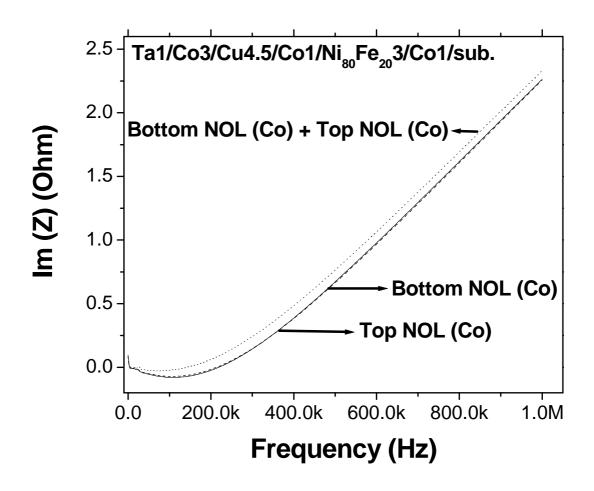

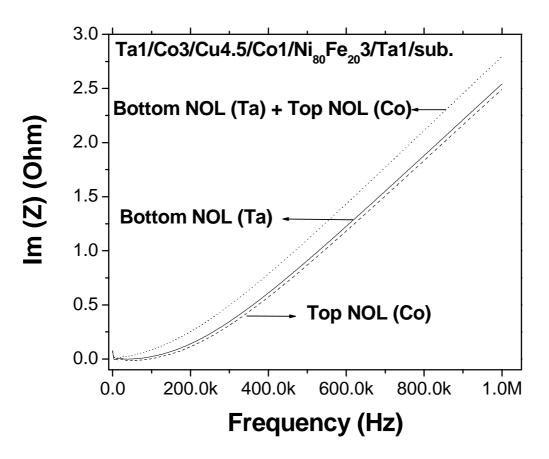

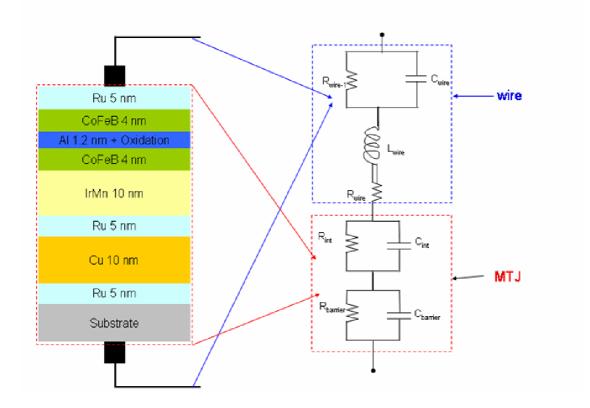

180°C, 200°C, respectively. The inset panels show the equivalent capacitor modes. 34 [Fig. 3.8] The dependences on MR ratio, resistance, and thickness of the bottom  $Ni_{80}Fe_{20}$  in the structure of Ta 0.6 / NOL / Co 3 / Cu 4 / Co 1 /  $Ni_{80}Fe_{20}$  3 / NOL /  $Ni_{80}Fe_{20}$  (d) / substrate, in which the bottom  $Ni_{80}Fe_{20}$  was naturally oxidized for ten minutes. The inset panel shows the magneto impedance at frequency 415 kHz for PSV with d = 1 nm, the shape of MZ<sub>Im</sub> loop is reversed to that of MZ<sub>Re</sub>. 37 [Fig. 3.9] The imaginary parts of impedance curves for PSV with different thicknesses of the bottom Ni<sub>80</sub>Fe<sub>20</sub> NOL ranged from 0 to 1 nm at zero fields. Except the PSV without Ni<sub>80</sub>Fe<sub>20</sub> NOL, the roll-off frequencies increases as the thickness of the Ni<sub>80</sub>Fe<sub>20</sub> NOL increasing. 38 [Fig. 3.10] (a) The roll-off frequency and calculated effective and NOL capacitance are functions of the thickness of the bottom Ni<sub>80</sub>Fe<sub>20</sub> NOL thickness. (b) The equivalent circuit of the measurement is a complex RLC combination. 39 [Fig. 3.11] The imaginary part of impedance curve for PSV with different NOL structures at zero fields. The film structure is Ta / (Co NOL) /Cu /Co /Ni<sub>80</sub>Fe<sub>20</sub> / (Co NOL) /sub. 40 [Fig. 3.12] The imaginary part of impedance curve for PSV with different NOL structures at zero fields. The film structure is Ta / (Co NOL) /Cu /Co /Ni<sub>80</sub>Fe<sub>20</sub> / (Ta NOL) /sub. 41 [Fig. 4.1] (a) The structure of the magneto tunneling junctions is Ru (5nm) /Cu

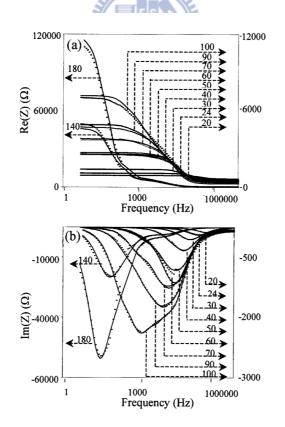

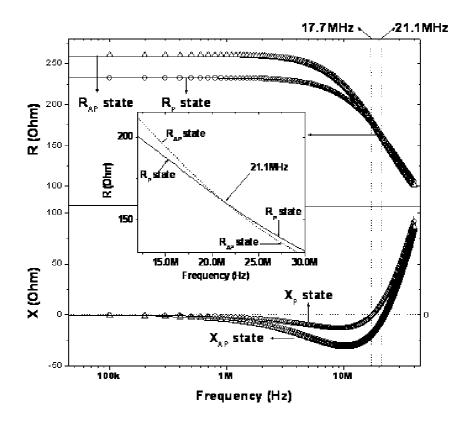

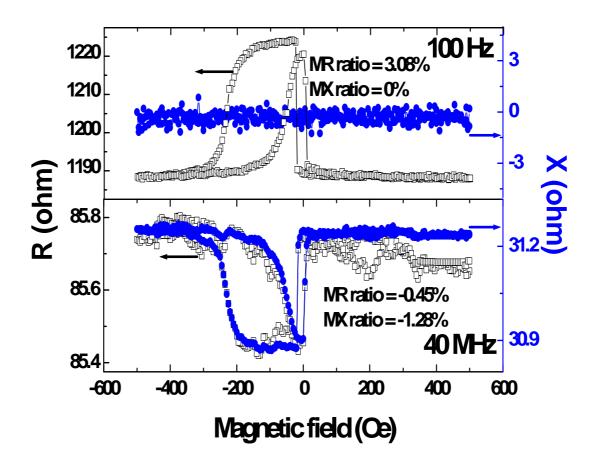

(10nm) /Ru(5nm) /IrMn(10nm) /CoFeB(4nm) /Al(1.2nm)-oxide /CoFeB (4nm) /Ru (5nm) and equivalent circuit with contributions from magneto tunneling junctions. [Fig. 4.2] The frequency dependences of the real part of the impedance (R) and the imaginary part of the impedance(X) for the magneto tunneling junctions in the parallel or anti-parallel states. The inset panel shows the crossover frequency of the real part of the impedance, which indicates that the magnetic behavior of MTJ is

xiv

| changed by the driving frequency.                                                                | 47 |

|--------------------------------------------------------------------------------------------------|----|

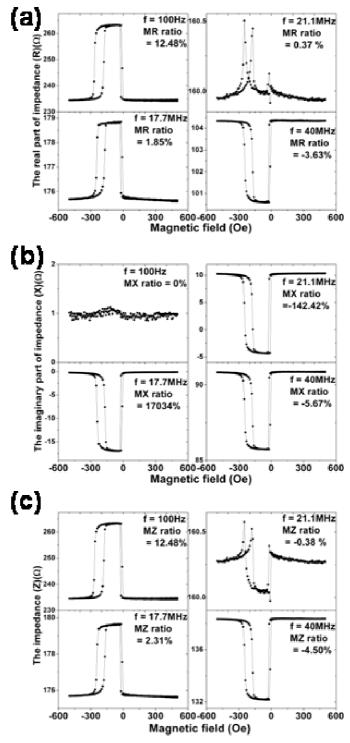

| [Fig. 4.3] (a) The real part of the impedance (R) curves at frequencies of 100Hz,                |    |

| 17.7MHz (resonance frequency), 21.1MHz (crossover frequency), and 40MHz for                      |    |

| the magneto tunneling junctions. (b) The imaginary part of the impedance (X) curves              |    |

| at frequencies of 100Hz, 17.7MHz (resonance frequency), 21.1MHz (crossover                       |    |

| frequency), and 40MHz for the magneto tunneling junctions. (c) The impedance (Z)                 |    |

| curves at frequencies of 100Hz, 17.7MHz (resonance frequency), 21.1MHz                           |    |

| (crossover frequency), and 40MHz for the magneto tunneling junctions.                            | 49 |

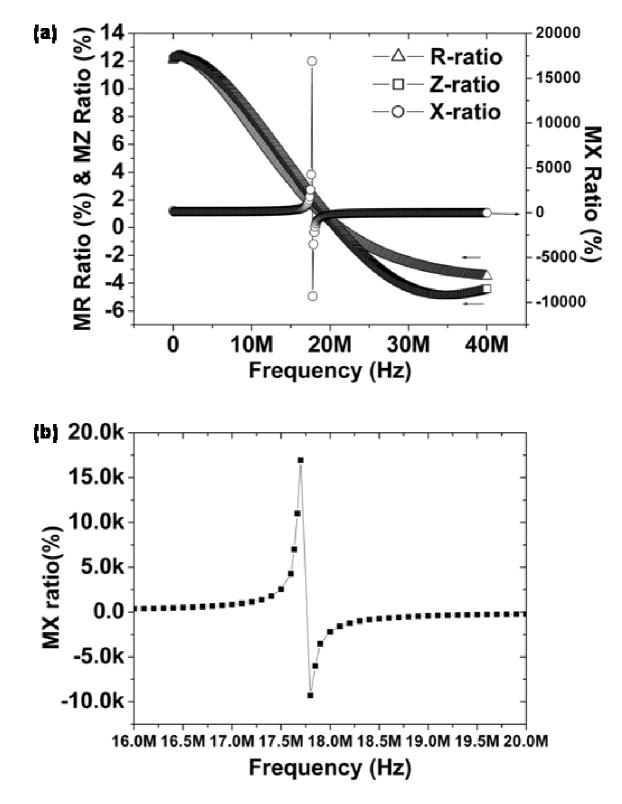

| [Fig. 4.4] (a) The frequency dependences of MR, MX, and MZ ratios. (b) The zoom                  |    |

| in panel of the MX ratio changed; the frequency ranges from 16 to 20 MHz.                        | 50 |

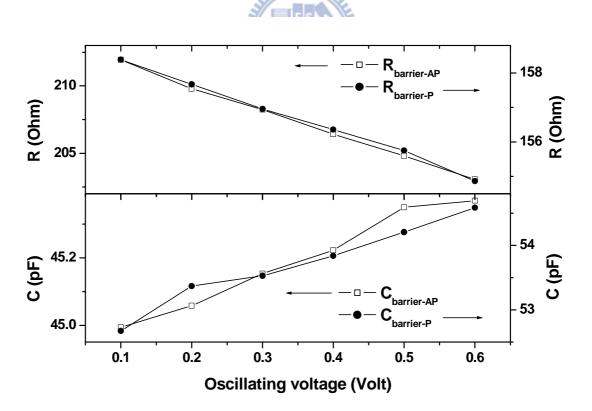

| [Fig. 4.5] The resistance and capacitance reduced by barrier effect at parallel and              |    |

| anti-parallel states are functions of the oscillating voltage.                                   | 52 |

| [Fig. 4.6] The resistance and capacitance reduced by interface effect at parallel and            |    |

| anti-parallel states are functions of the oscillating voltage.                                   | 53 |

| [Fig. 4.7] The MI ratio of the MTJ with different oscillating voltage ranged from                |    |

| 100Hz to 40 MHz. The inset panel shows the MI ratio at 1MHz and 40MHz.                           | 54 |

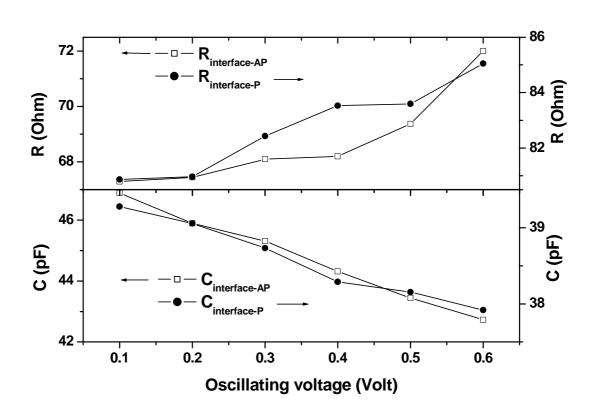

| [Fig. 4.8] It shows the hysteresis behavior of the MTJ $Ru(5)$ / $Cu(10)$ / $Ru(5)$ / $IrMn(10)$ |    |

| /CoFeB(4) /A1 (0.8)-oxide /CoFeB(4) /Ru(5) at frequencies 100Hz, and 40MHz,                      |    |

| respectively.                                                                                    | 56 |

| [Fig. 4.9] The frequency dependences of the real part of the impedance (R) and the               |    |

| imaginary part of the impedance (X) for the magneto tunneling junctions in the                   |    |

| anti-parallel (a), (b), and parallel states (c), (d).                                            | 57 |

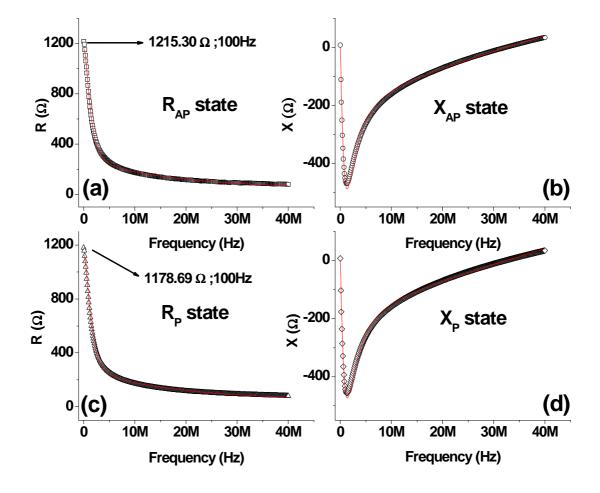

| [Fig. 4.10] shows the frequency dependence of the MR, MX, and MI ratio behaviors                 |    |

| with different barrier layer AlOx thickness 0.8, 1.1, 1.2nm.                                     | 59 |

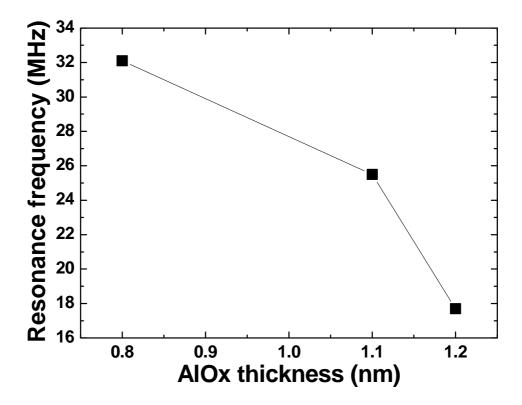

| [Fig. 4.11] The resonance frequency $(F_r)$ of the MTJ is a function of the thickness of         |    |

| barrier layer.                                                                                   | 60 |

|                                                                                                  |    |

xv

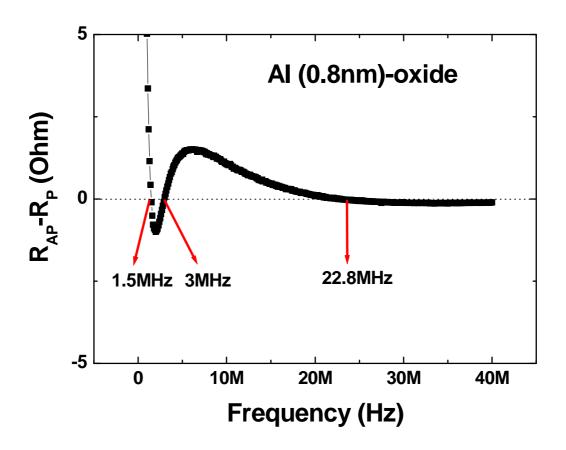

| [Fig. 4.12] The resistance difference between the anti-parallel state and the parallel             |    |

|----------------------------------------------------------------------------------------------------|----|

| state $(R_{AP}-R_P)$ as a function of the frequency between 100Hz to 40MHz for sample              |    |

| with $x = 0.8$ nm.                                                                                 | 61 |

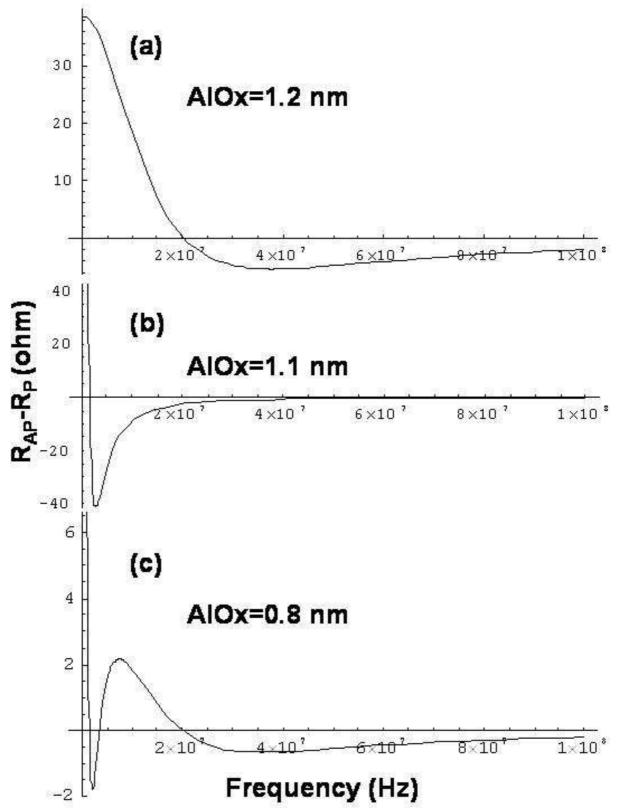

| [Fig. 4.13] Simulation results for $R_{AP}$ - $R_P$ with different barrier thickness 0.8, 1.1, and |    |

| 1.2nm at the frequency ranging from 100Hz to 100MHz.                                               | 62 |

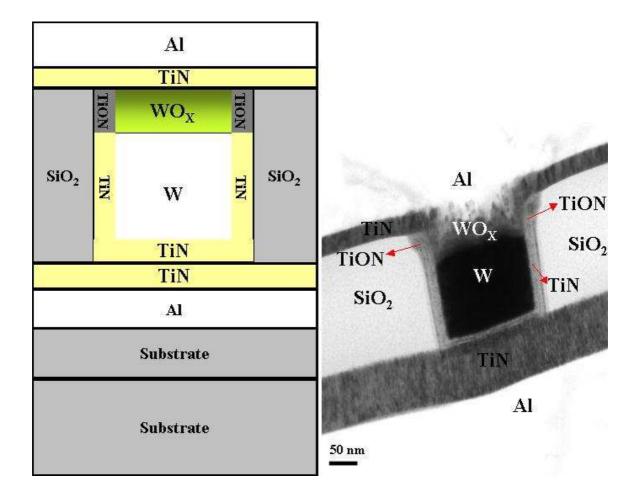

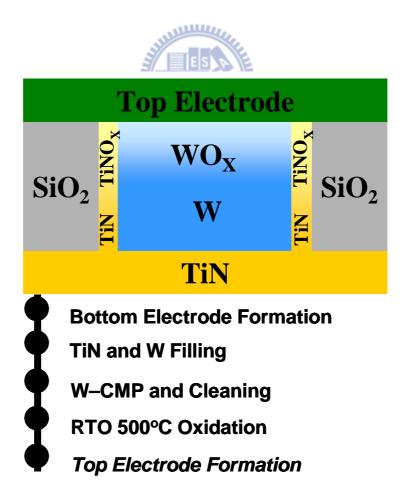

| [Fig. 5.1] Cell structure, cross-sectional TEM image and the process flow of the                   |    |

| WO <sub>X</sub> RRAM                                                                               | 66 |

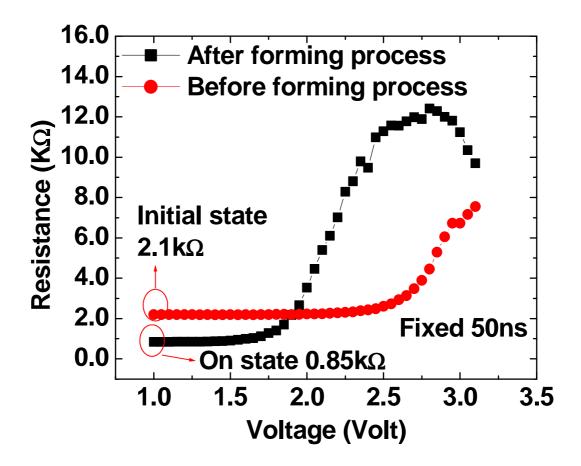

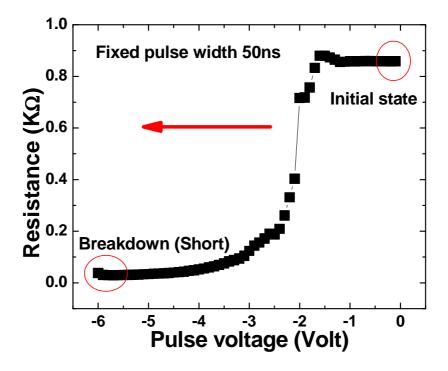

| [Fig. 5.2] R-V characteristics using fixed pulse width (50ns) before and after forming             |    |

| process. A forming process helps reducing the RESET voltage.                                       | 67 |

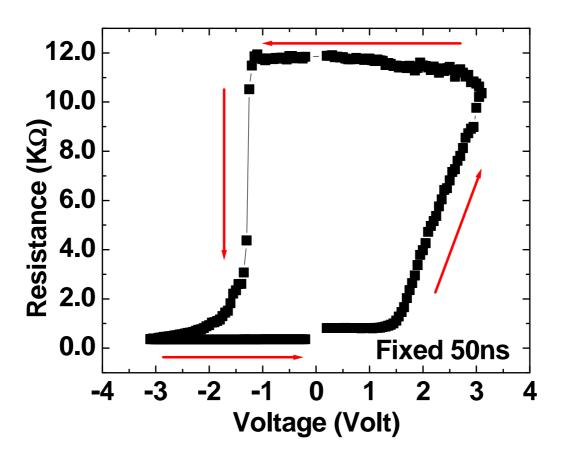

| [Fig. 5.3] Hysteresis loop between $3V$ and $-3V$ with a fixed pulse width of 50ns. The            |    |

| resistance increases gradually and linearly from 1.5V to ~3V, but decreases suddenly               |    |

| at –1.2V.                                                                                          | 68 |

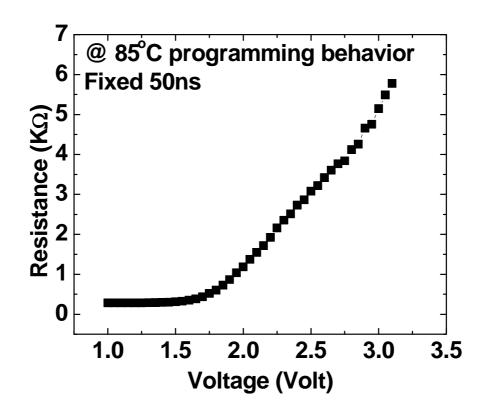

| [Fig. 5.4] Resistance dependence on pulse voltage with fixed pulse width 50ns at                   |    |

| 85°C. It again shows a well behaved linear region suitable for MLC programming.                    | 69 |

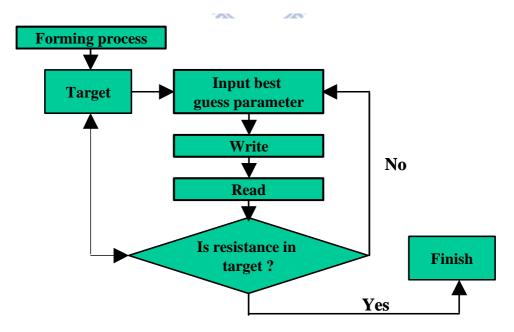

| [Fig. 5.5] The MLC operation algorithm. Two operation methods may be selected to                   |    |

| control the resistance states of the WO <sub>X</sub> RRAM: (1) varying the pulses voltage, (2)     |    |

| changing the pulse number. R-V plots (Fig. 4) are used to decide the initial                       |    |

| parameters. If the resistance does not reach the target value, the programming voltage             |    |

| is increased.                                                                                      | 69 |

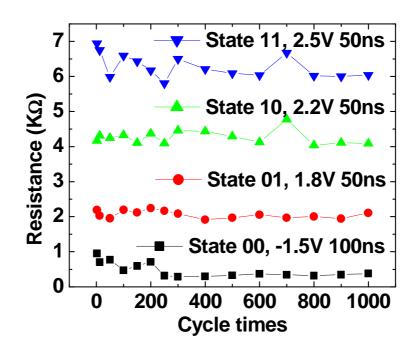

| [Fig. 5.6] 4-level cycling test of the WOx RRAM. 1,000 cycles are achieved. 3                      |    |

| RESET states (01,10,11) are programmed by different voltage positive pulses and the                |    |

| SET level (00) is programmed by a negative pulse.                                                  | 70 |

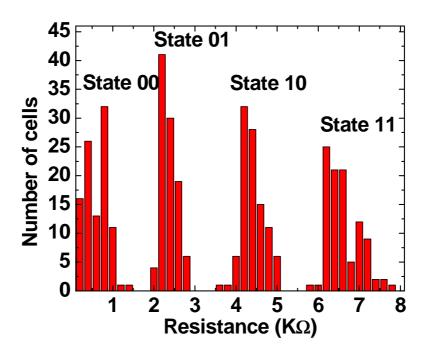

| [Fig. 5.7] 100 cells are programmed into 4 levels using the same programming                       |    |

| conditions in Fig. 5.6. The levels are well distinguished.                                         | 70 |

| [Fig. 5.8] Cycling test for 8 levels. Although there was no window closing after                   |    |

| cycling, the window between adjacent logic levels is too narrow. For 3-bit/cell                    |    |

| operation the total window needs to be further enlarged.                                         | 71 |

|--------------------------------------------------------------------------------------------------|----|

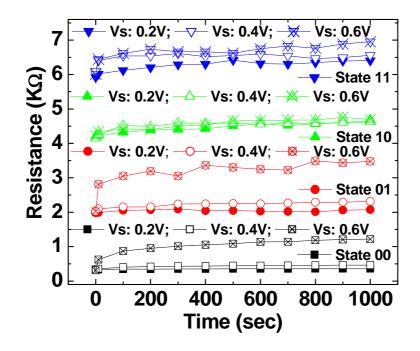

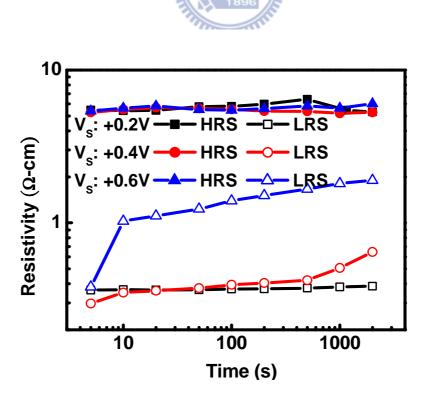

| [Fig. 5.9] Read disturb test for $WO_X$ RRAM. The states 10, and 11 are not affected             |    |

| by the read bias ranging from 0.2V to 0.6V. The states 00, and 01 are immune to read             |    |

| disturb under 0.4V.                                                                              | 71 |

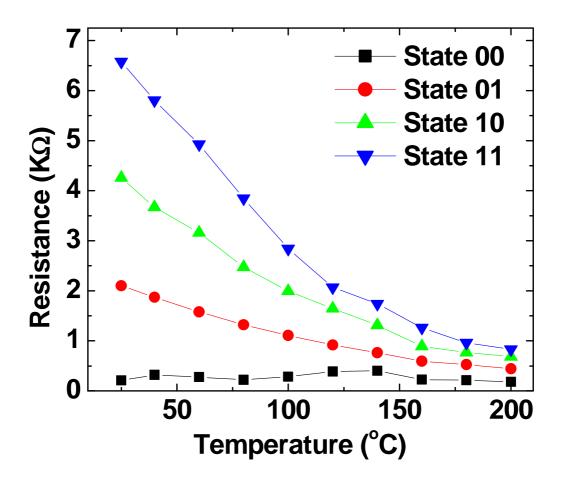

| [Fig. 5.10] Device resistance dependence on temperature from 25 to 200°C. The                    |    |

| resistances of RESET states 01, 10, and 11 decrease with increasing temperature. The             |    |

| strong temperature dependence may limit application range.                                       | 72 |

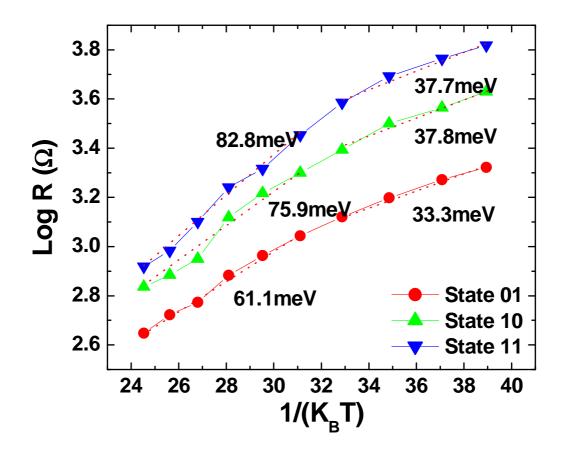

| [Fig. 5.11] The log R vs. $1/k_BT$ plot for states 01, 10, and 11. The activation energies       |    |

| are not constant but are similar for all states.                                                 | 73 |

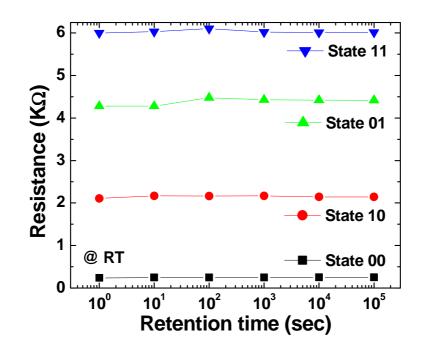

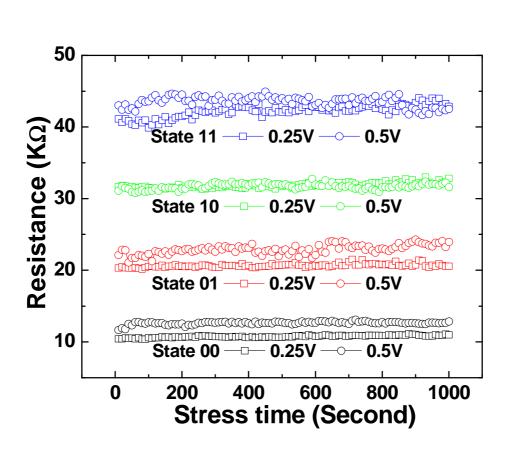

| [Fig. 5.12] Resistance stability of the WO <sub>X</sub> RRAM at room temperature. All 4 states   |    |

| show stable resistance.                                                                          | 74 |

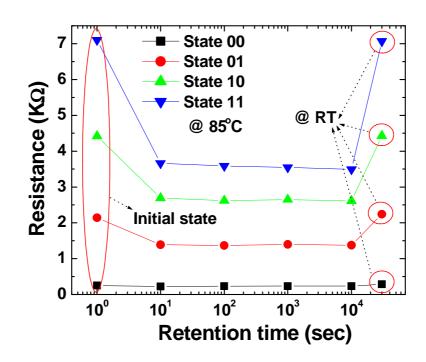

| [Fig. 5.13] The resistance stability at $85^{\circ}$ C. The high resistance states maintain > 1k |    |

| $\Omega$ of window after stressing.                                                              | 74 |

| [Fig. 5.14] Thermal stability test for WO <sub>X</sub> RRAM at 150°C. Each state survives well   |    |

| beyond 106 sec.                                                                                  | 75 |

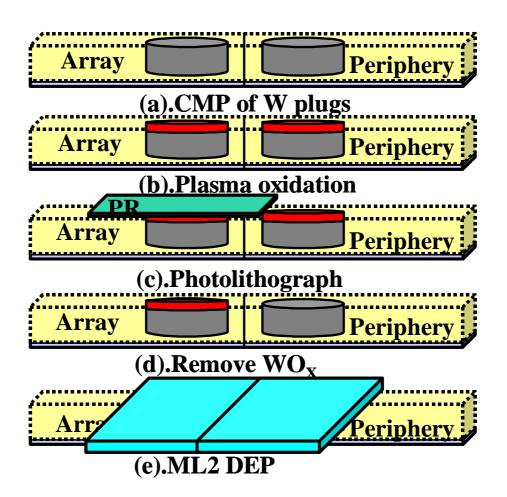

| [Fig. 5.15] Major processes for self-aligned $WO_X$ RRAM: (a) CMP of W plugs, (b)                |    |

| plasma oxidation, (c) photolithography to expose peripheral circuits, (d) remove                 |    |

| $WO_X$ from W plugs in periphery, (e) top electrode deposition and patterning.                   | 76 |

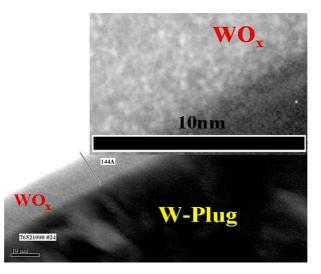

| [Fig. 5.16] Cross-sectional TEM for the WO <sub>X</sub> RRAM cell. HR-TEM (inset) shows          |    |

| that the $WO_X$ is amorphous.                                                                    | 77 |

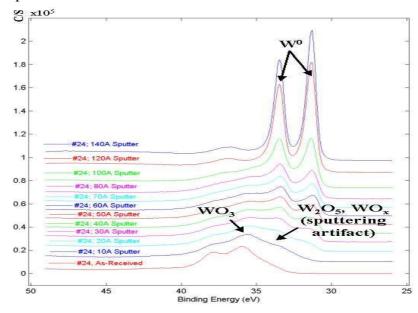

| [Fig. 5.17] XPS spectra for $WO_X$ fabricated by 1600s of oxidation. The film                    |    |

| thickness is about 140Å.                                                                         | 77 |

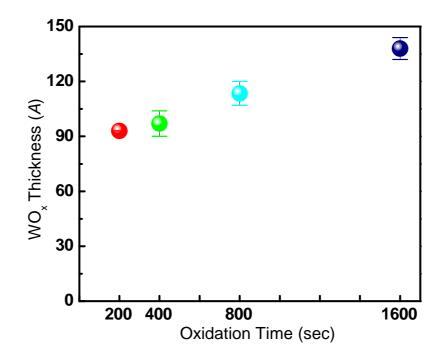

| [Fig. 5.18] Thickness of $WO_X$ film as a function of oxidation time. The film                   |    |

| thickness increases slowly after a fast initial growth. However, the film composition            |    |

| varies considerably with the oxidation time.                                                     | 78 |

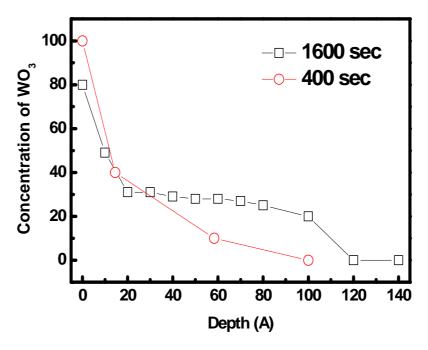

| [Fig. 5.19] Comparison of $WO_X$ composition after short (400s) and long (1600s)                 |    |

|                                                                                                  |    |

| oxidation. The 400s oxidation produces steeply graded $WO_3$ suitable for bipolar              |    |

|------------------------------------------------------------------------------------------------|----|

| switching (Ref. 4). After 1600s of oxidation, the WO <sub>3</sub> penetrates through the oxide |    |

| and film is suitable for unipolar switching (See Fig. 5.21).                                   | 78 |

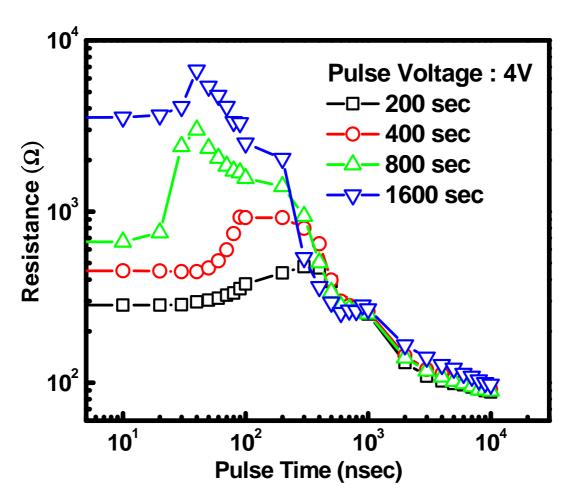

| [Fig. 5.20] Unipolar switching for fresh devices with various oxidation time. Short            |    |

| oxidation time gives poor unipolar switching capability, while long oxidation time             |    |

| produces films with good unipolar switching property.                                          | 79 |

| [Fig. 5.21] Unipolar switching characteristics of a 1600s device. A short (20-50ns)            |    |

| positive pulse switches the resistivity from LRS to HRS, while long positive pulses            |    |

| (200-500ns) switch the resistivity from HRS back to LRS. Both operations are fully             |    |

| reversible.                                                                                    | 80 |

| [Fig. 5.22] Negative pulses, however, do not produce reversible unipolar switching             |    |

| on 1600s samples. At higher voltages, negative pulses can switch the $WO_X$ device             |    |

| from HRS to LRS once, but the device cannot be switched back to HRS anymore.                   | 81 |

| [Fig. 5.23] Temperature dependence of the conduction currents for both the LRS and             |    |

| HRS indicating semiconducting behavior.                                                        | 81 |

| [Fig. 5.24] Cycling characteristics of the WO <sub>X</sub> memory cell. RHS/LHS resistance     |    |

| window keeps well separated up to $> 1000$ cycles.                                             | 82 |

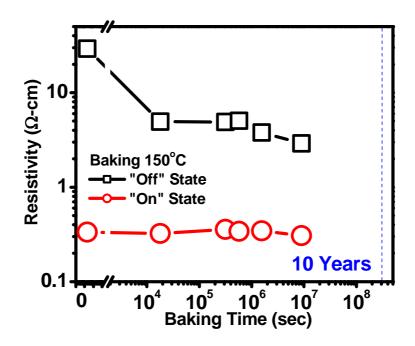

| [Fig. 5.25] Thermal stability test of $WO_X$ memory cell at 1500C. The HRS decreases           |    |

| slowly while the LRS keeps almost constant. A 10X resistivity ratio is maintained up           |    |

| to 2500 hours of baking.                                                                       | 83 |

| [Fig. 5.26] Read disturb test on $WO_X$ devices. The HRS is not affected by the read           |    |

| bias of 0.2-0.6V. LRS is immune to read disturb under bias $< 0.4$ V.                          | 83 |

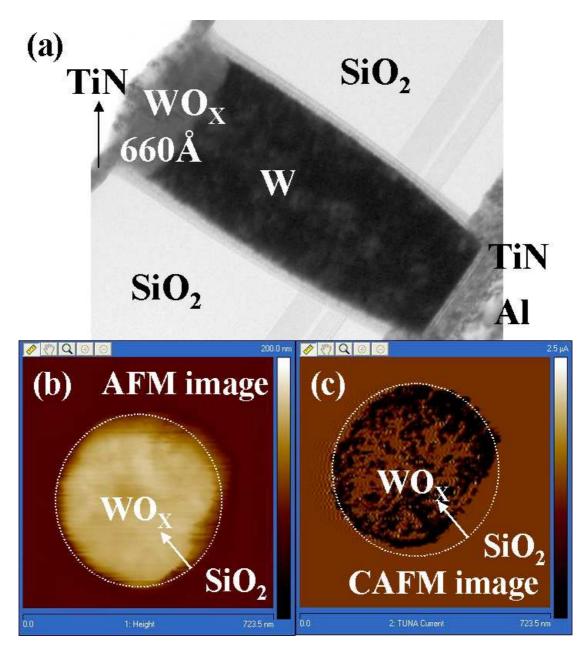

| [Fig. 6.1] (a). Cross-sectional TEM image for WO <sub>X</sub> RRAM. (b) and (c). AFM and       |    |

| Conductive-AFM images of WO <sub>X</sub> cell surface.                                         | 86 |

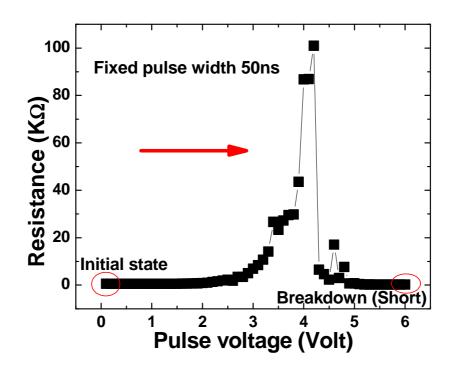

| [Fig. 6.2] The resistance state can be enhanced by positive pulse. At high voltage, the        |    |

| device becomes shorted.                                                                        | 88 |

|                                                                                                |    |

| [Fig. 6.3] Negative pulses, even at higher voltages, do not reset the device.                | 88 |

|----------------------------------------------------------------------------------------------|----|

| [Fig. 6.4] R-V characteristics after the forming process. Forming process is useful to       |    |

| reduce the switching voltage.                                                                | 89 |

| [Fig. 6.5] The resistance window increases for smaller contact area. The devices are         |    |

| treated with a forming process using a 4V/ 50ns pulse first.                                 | 89 |

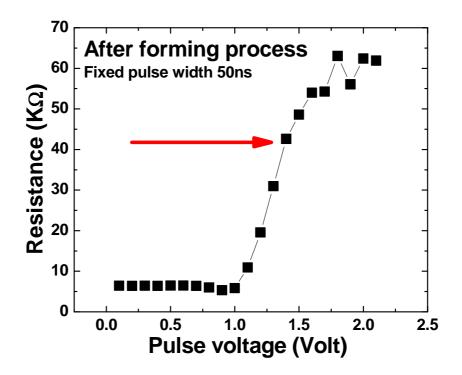

| [Fig. 6.6] Voltage distribution for HRS and LRS of 50 memory cells.                          | 90 |

| [Fig. 6.7] Cycling characteristics of the WO <sub>X</sub> memory cell. RHS/LHS resistance    |    |

| window is well separated at 50k $\Omega$ /10k $\Omega$ up to > 10 <sup>8</sup> cycles.       | 91 |

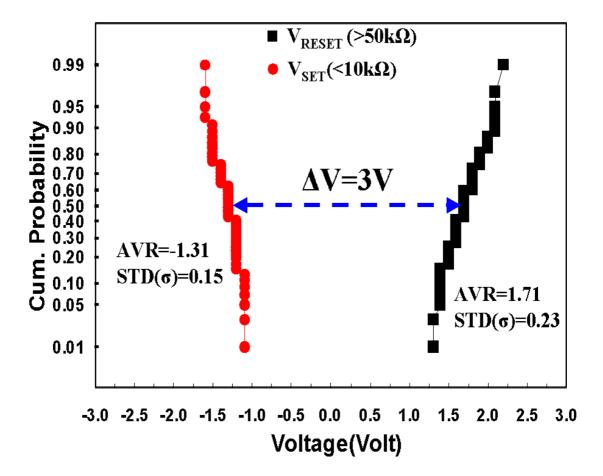

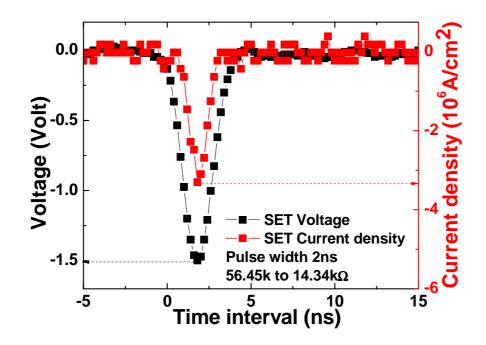

| [Fig. 6.8] Time resolved voltage and current traces of RESET operation. The input            |    |

| pulse width is 2ns. The RESET current density is about $3.4 \times 10^6$ A/cm <sup>2</sup> . | 92 |

| [Fig. 6.9] J-t and V-t curves of SET operation. It also shows high speed erase               |    |

| capability (~2ns). The SET current density is about $3.3 \times 10^6$ A/cm <sup>2</sup> .    | 92 |

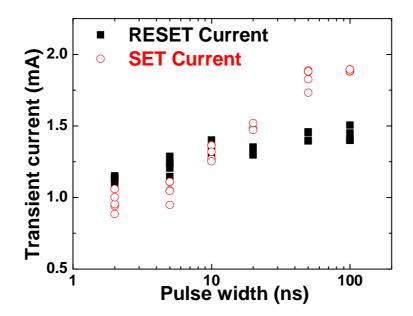

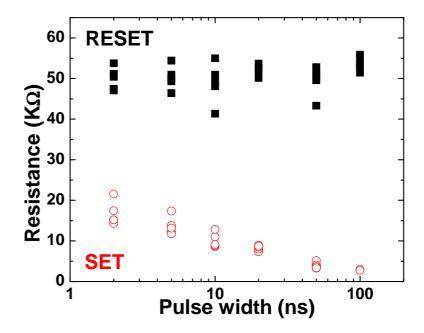

| [Fig. 6.10] Transient currents for RESET and SET using various pulse widths.                 | 93 |

| [Fig. 6.11] Corresponding RESET and SET states for various pulse widths.                     | 93 |

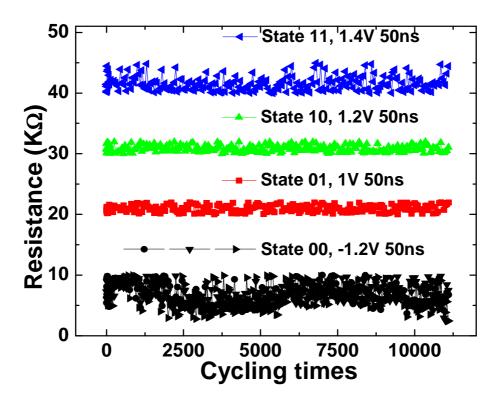

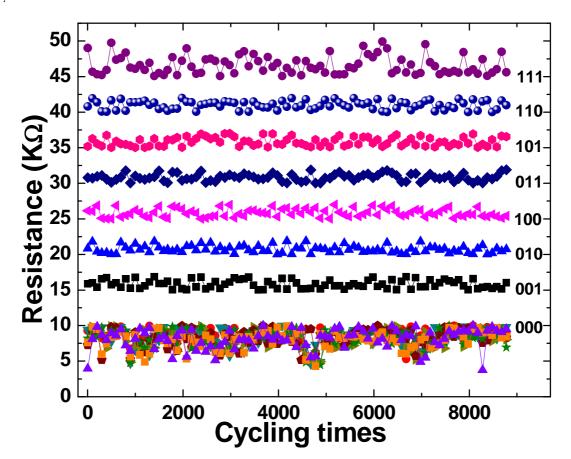

| [Fig. 6.12] 4-level cycling test beyond $10^4$ cycles with verification. Three RESET         |    |

| states (01,10,11) are programmed by different voltage positive pulses and the SET            |    |

| level (00) is programmed by a negative pulse.                                                | 94 |

| [Fig. 6.13] Read disturb test. All states show acceptable read disturb up to 0.5V.           | 95 |

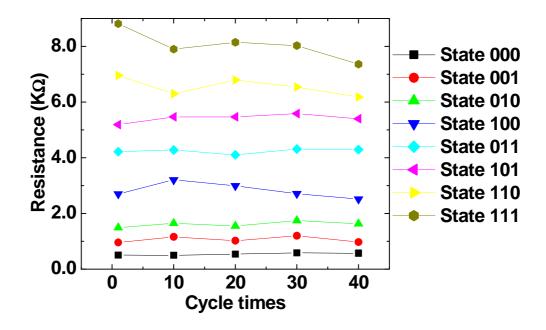

| [Fig. 6.14] 8-level cycling test of more than 8k cycles with verification. Well              |    |

| distinguishable resistance windows are maintained for each states.                           | 96 |

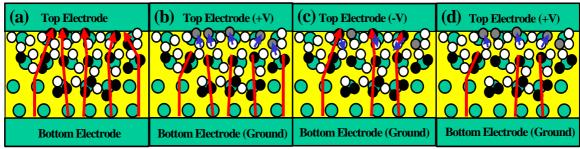

| [Fig. 6.15] Schematics for proposed $WO_X$ RRAM switching mechanism. (a) Right               |    |

| after the RTO $WO_X$ formation and top electrode process, many oxygen vacancies are          |    |

| present in the $WO_X$ film leaving easy electron hopping paths. The initial resistance is    |    |

| below $1k\Omega$ due to these conduction paths (sometimes referred to as filaments). (b)     |    |

| During the forming process, the positive voltage drives oxygen into vacancies near           |    |

| the top electrode. This cuts off the conduction paths and the resistance increases           |    |

| dramatically. (c) When a large enough negative voltage is applied, oxygen is                         |     |

|------------------------------------------------------------------------------------------------------|-----|

| separated from shallow vacancy traps. Thus some of the conduction paths are                          |     |

| reconnected and the resistance drops (SET). (d) A positive voltage drives oxygen                     |     |

| back into shallow vacancies and disrupt the conduction paths (RESET).                                | 97  |

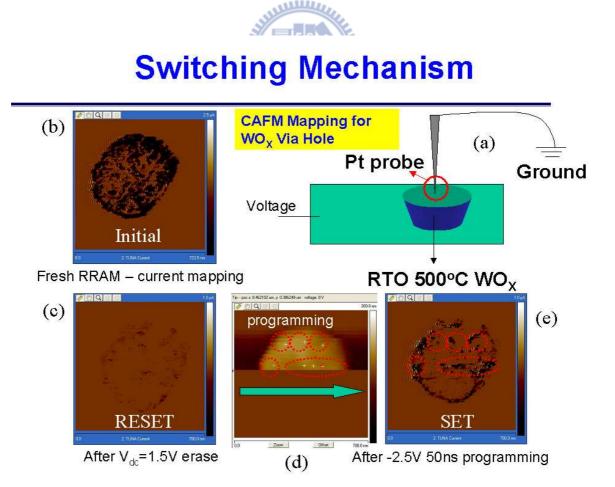

| [Fig. 6.16] C-AFM images of the WO <sub>X</sub> cell surface.                                        | 98  |

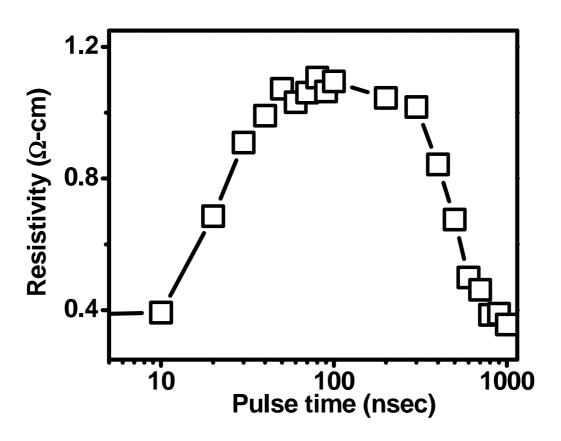

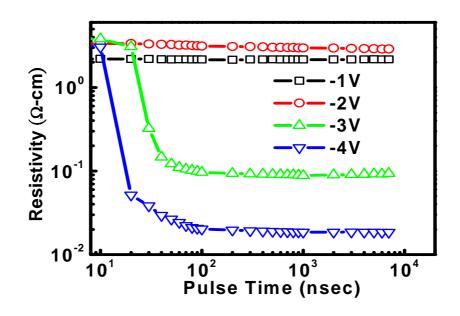

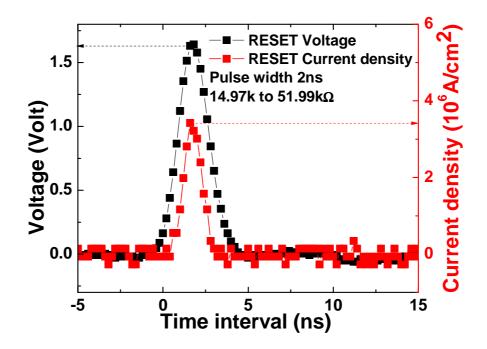

| [Fig. 6.17] (a). Unipolar RESET for pulse R-V curves and (b) SET for pulse R-t                       |     |

| curves. (c) Pulse width dependence of unipolar SET with varied positive voltage and                  |     |

| (d) voltage dependence of unipolar RESET with varied pulse width.                                    | 100 |

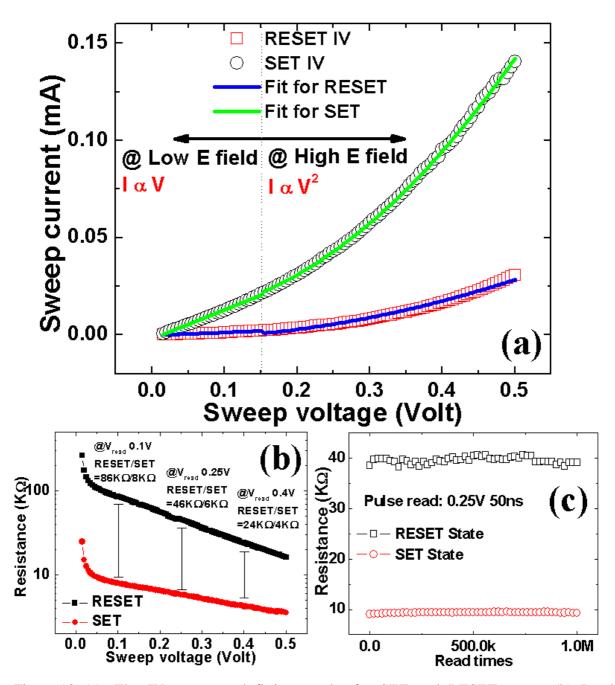

| [Fig. 6.18] (a). The IV curves and fitting results for SET and RESET states. (b) Read                |     |

| dependence for RESET and SET states. (c). 1 M read times for 0.25V pulse read                        |     |

| voltage.                                                                                             | 101 |

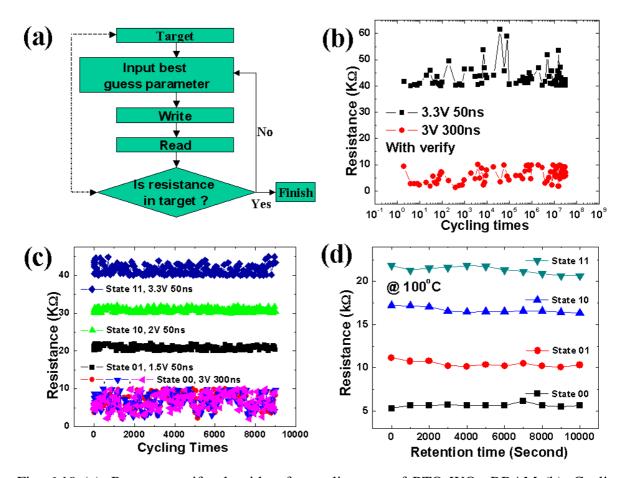

| [Fig. 6.19] (a). Program-verify algorithm for cycling test of RTO WO <sub>X</sub> RRAM (b).          |     |

| Cycling characteristics of the RTO $WO_X$ RRAM cell with unipolar operation.                         |     |

| RESET/SET resistance window of $40k\Omega/10k\Omega$ is well maintained up to $10^7$ cycles.         |     |

| (c). 4-levels cycling test for 9000 cycles. Three RESET states (01,10,11) are                        |     |

| programmed by positive pulses of different voltage and the SET level (00) is                         |     |

| programmed by a positive pulse with long pulse width. (d). Retention test for RTO                    |     |

| $WO_X$ RRAM with 100°C baking. The resistance values are lower indicating the                        |     |

| semiconductor behaviors.                                                                             | 102 |

| [Fig. 6.20] $WO_X$ RRAM structure and process flow.                                                  | 104 |

| [Fig. 6.21] Formulas for SCLC and thermionic emission.                                               | 105 |

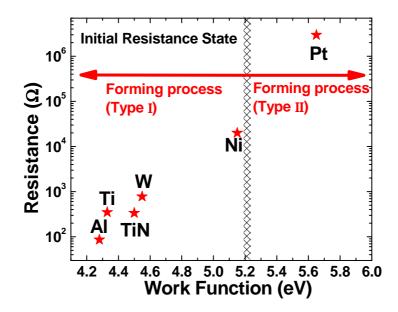

| [Fig. 6.22] Fig. 6.20. The initial resistance increases with the WF of the TE. Two                   |     |

| types of forming process (I and II) are observed.                                                    | 105 |

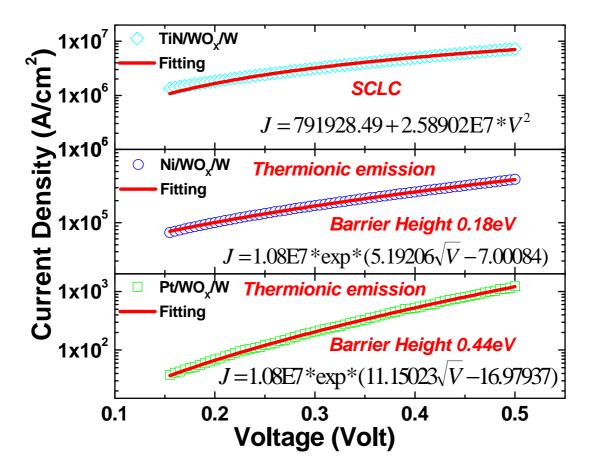

| [Fig. 6.23] IV curves and fitting results for initial states of $Pt/WO_X/W$ , Ni/WO <sub>X</sub> /W, |     |

| and TiN/WO <sub>X</sub> /W. Thermionic emission describes the behaviors for Pt and                   |     |

| Ni/WO <sub>X</sub> /W well, but not TiN TE.                                                          | 106 |

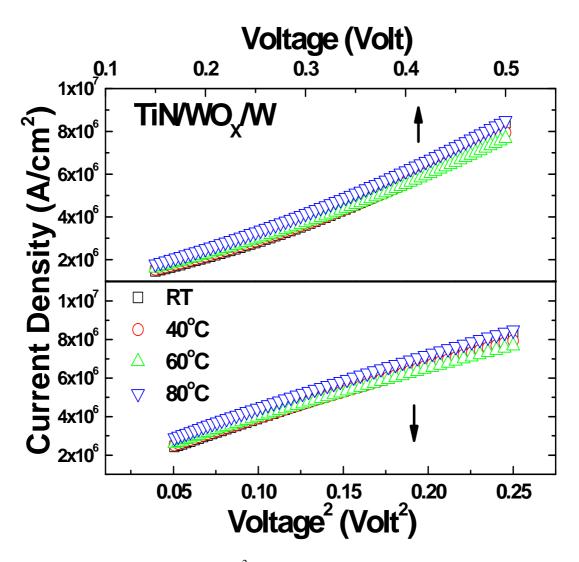

| [Fig. 6.24] IV curves and J versus $V^2$ curves for TiN/WO <sub>X</sub> /W at different                                                                                                                                                                                                                                                                                                                                     |            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| temperatures RT, 40, 60, and $80^{\circ}$ C. J is proportional to V <sup>2</sup> indicating the SCLC                                                                                                                                                                                                                                                                                                                        |            |

| behaviors.                                                                                                                                                                                                                                                                                                                                                                                                                  | 107        |

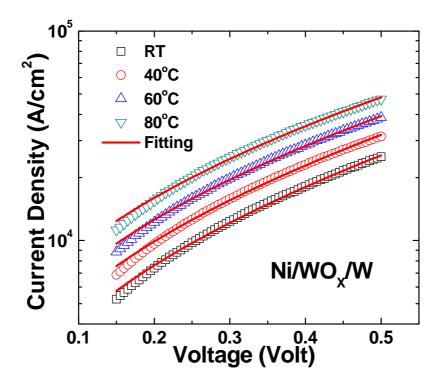

| [Fig. 6.25] IV curves and thermionic emission fitting results for initial state of                                                                                                                                                                                                                                                                                                                                          |            |

| Ni/WO <sub>X</sub> /W at different temperatures RT, 40, 60, and $80^{\circ}$ C.                                                                                                                                                                                                                                                                                                                                             | 108        |

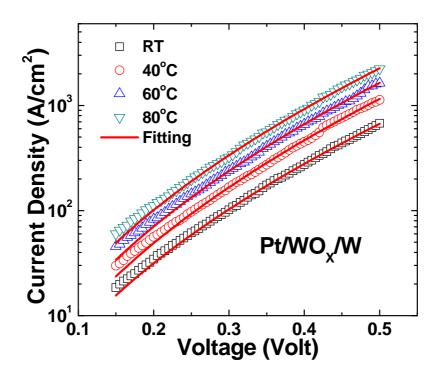

| [Fig. 6.26] IV curves and thermionic emission fitting results for initial state of                                                                                                                                                                                                                                                                                                                                          |            |

| Pt/WO <sub>X</sub> /W at different temperatures RT, 40, 60, and $80^{\circ}$ C.                                                                                                                                                                                                                                                                                                                                             | 108        |

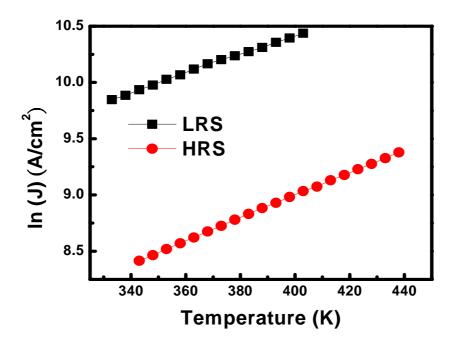

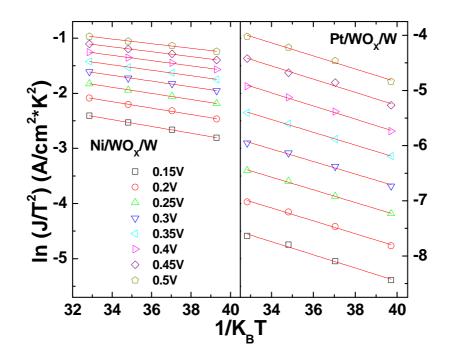

| [Fig. 6.27] ln (J/T <sup>2</sup> ) versus 1/k <sub>B</sub> T curves for Ni/WO <sub>X</sub> /W and Pt/WO <sub>X</sub> /W with bias                                                                                                                                                                                                                                                                                           |            |

| between 0.15V to 0.5V. The linear trend indicates the thermionic emission behaviors                                                                                                                                                                                                                                                                                                                                         | 109        |

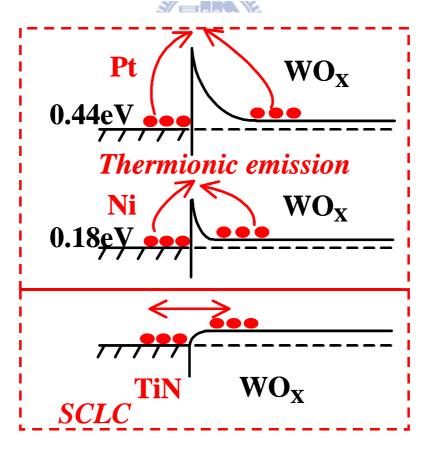

| [Fig. 6.28] Schematics for conduction mechanism for Pt, Ni, and TiN/WO <sub>X</sub> /W.                                                                                                                                                                                                                                                                                                                                     | 109        |

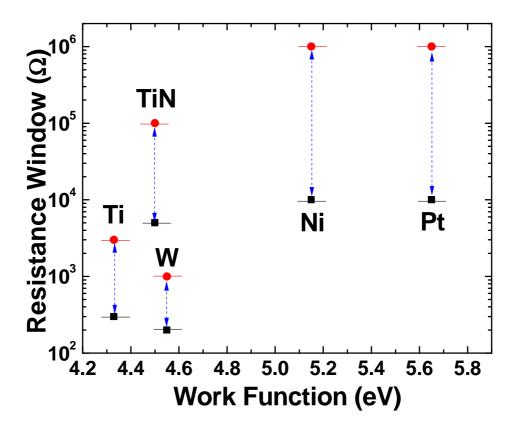

| [Fig. 6.29] High WF TE produces large resistance window. Both Pt/WO <sub>X</sub> /W and                                                                                                                                                                                                                                                                                                                                     |            |

| Ni/WO <sub>X</sub> /W show 100X window and higher RESET resistance.                                                                                                                                                                                                                                                                                                                                                         | 110        |

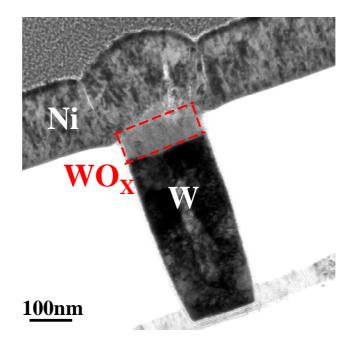

| [Fig. 6.30] Cross sectional TEM image of Ni/WO <sub>x</sub> /W RRAM.                                                                                                                                                                                                                                                                                                                                                        | 111        |

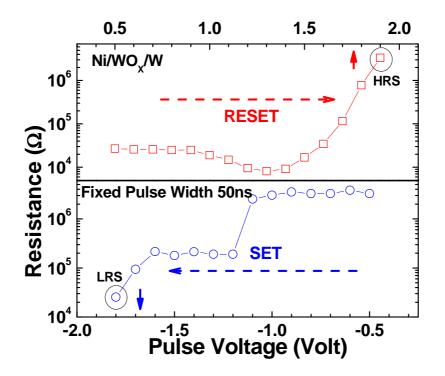

| [Fig. 6.31] RESET and SET pulse R-V curves for Ni/WO <sub>X</sub> /W after reverse forming                                                                                                                                                                                                                                                                                                                                  |            |

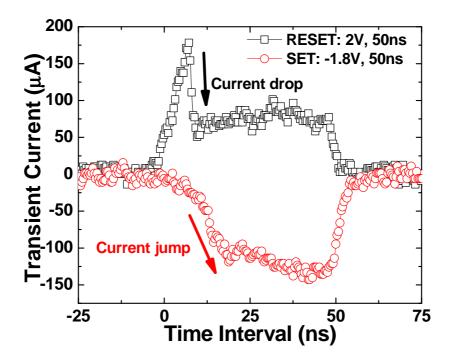

| process.                                                                                                                                                                                                                                                                                                                                                                                                                    | 112        |

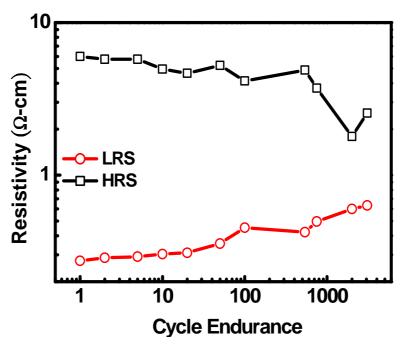

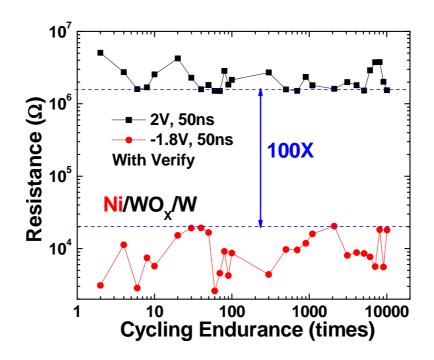

| [Fig. 6.32] Transient I-t curves of RESET and SET operation of Ni/WO <sub>X</sub> /W cell. The                                                                                                                                                                                                                                                                                                                              |            |

| RESET current is about 180uA, and SET current is about 150uA.                                                                                                                                                                                                                                                                                                                                                               | 112        |

| [Fig. 6.33] Cycling characteristics of the Ni/WO <sub>X</sub> /W cell. RESET/SET resistance                                                                                                                                                                                                                                                                                                                                 |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                             | 113        |

| window is well separated at $1M\Omega/10k\Omega$ for > 10k cycles.                                                                                                                                                                                                                                                                                                                                                          |            |

| window is well separated at $1M\Omega / 10k\Omega$ for > 10k cycles.<br>[Fig. 6.34] Read disturb test. Both RESET and SET states show good read disturb                                                                                                                                                                                                                                                                     |            |

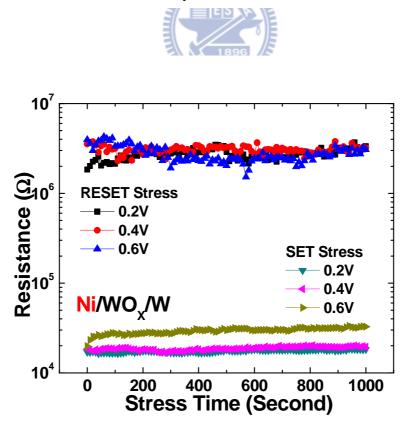

|                                                                                                                                                                                                                                                                                                                                                                                                                             | 113        |

| [Fig. 6.34] Read disturb test. Both RESET and SET states show good read disturb                                                                                                                                                                                                                                                                                                                                             | 113        |

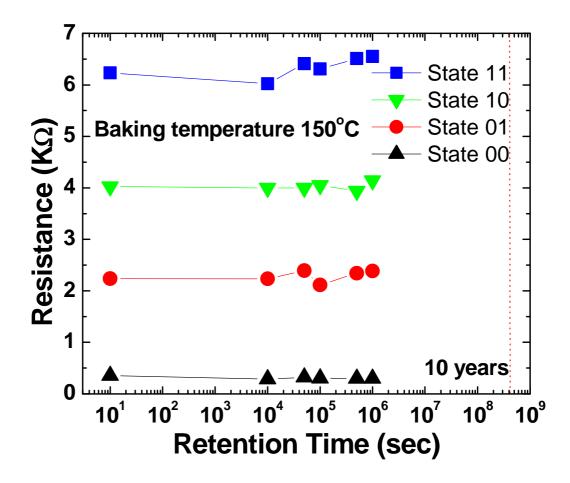

| [Fig. 6.34] Read disturb test. Both RESET and SET states show good read disturb resistance up to 0.6V.                                                                                                                                                                                                                                                                                                                      | 113<br>114 |

| <ul> <li>[Fig. 6.34] Read disturb test. Both RESET and SET states show good read disturb resistance up to 0.6V.</li> <li>[Fig. 6.35] Thermal stability test for Ni/WO<sub>X</sub>/W cell at 150°C. Both RESET and SET</li> </ul>                                                                                                                                                                                            |            |

| <ul> <li>[Fig. 6.34] Read disturb test. Both RESET and SET states show good read disturb resistance up to 0.6V.</li> <li>[Fig. 6.35] Thermal stability test for Ni/WO<sub>X</sub>/W cell at 150°C. Both RESET and SET states survive well beyond 10<sup>6</sup> sec with at least 10X resistance window.</li> </ul>                                                                                                         |            |

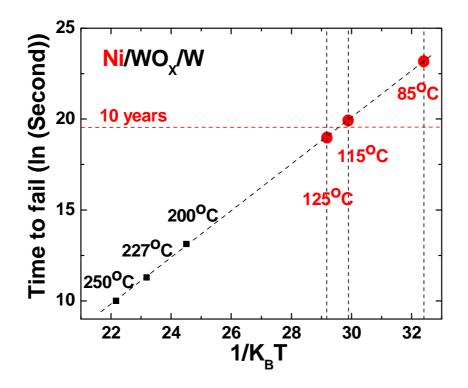

| <ul> <li>[Fig. 6.34] Read disturb test. Both RESET and SET states show good read disturb resistance up to 0.6V.</li> <li>[Fig. 6.35] Thermal stability test for Ni/WO<sub>X</sub>/W cell at 150°C. Both RESET and SET states survive well beyond 10<sup>6</sup> sec with at least 10X resistance window.</li> <li>[Fig. 6.36] Arrhenius plot for retention test of Ni/WO<sub>X</sub>/W cell. Ea is ~ 1.34eV. The</li> </ul> |            |

[Fig. 6.37] Comparison for TiN, Pt, and Ni/WO<sub>X</sub>/W cells. Ni/WO<sub>X</sub>/W cell shows promising performance for memory application with low operation current, large resistance window, and excellent thermal stability. 115

### **CHAPTER 1**

### Introduction

#### **1.1 Background and Motivation**

Non-volatile memories have drawn much attention in the world. The applications for portable and electronics such as digital still camera (DSC), cellular phone, digital audio machines (MP3 player), memory cards, routers, and so on are indispensable in our life. At the present the electron storage memories like conventional floating gate flash memories, NOR and NAND flash, are popular for non-volatile memory that drive the progress of the world around forty years. Recently, in order to keep corresponding to the market of non-volatile semiconductor memories, owing to its high density and low cost, both for NOR and NAND flash are the most important electronic devices. Up to now, flash memories could scale down to 32nm technology node. However, beyond 32nm technology node, the flash memories face the scaling issues due to physical limitation. Therefore, finding the way to replace the electronic storage memory is a hot and interesting topic for memory research.

Resistive storage memory plays a key role for memory research due to its potential to replace the electronic storage memory. For the purposes of Phase change memory (PCM), magnetic random access memory (MRAM), and resistive random access memory (RRAM) are considered in place of the electronic storage memory because good performance such as high endurance, random access and high operation speed.

MRAM has been developed more than twenty years. This technology always can find new ways to overcome the hinder of technology issues. For instance, the spin transfer torque technique was used to solve the scaling issue for conventional field driven MRAM. Although the operation architecture changes a lot for MRAM evolution, the basic magneto resistive elements are used and dominate the performance of either conventional MRAM or STT MRAM.

The DC behaviors for magneto resistive elements such as pseudo spin valve (PSV), and magneto tunneling junction (MTJ) have been widely studied, but the AC behaviors are rare. This motivates us to investigate the AC behaviors for PSV and MTJ. In this thesis, the magneto impedance behaviors of the PSV and MTJ are studied. By using the AC analysis, the nano-oxide layer (NOL) effects of PSV could be modeled. Moreover, the equivalent circuit model was used to describe the AC behaviors for the MTJ.

Recently, resistance-based memory has attracted much attention for high-density memory applications because of its simple structure, small cell size, high speed, and low power consumption. Resistance switching memories including transition metal oxides (TMO) and programmable metallization cell (PMC), such as  $TiO_X$  [72],  $NiO_X$  [67],  $MoO_X$  [73],  $CuO_X$ ,  $TaO_X$ ,  $CoO_X$  [74], and  $Cu/WO_X$  [75] have been studied extensively. Although a lot of groups devote to study the RRAM for its conducting mechanism, switching mechanism, and device performance, up to now, their switching and conducting mechanisms are still not clear due to the complexity of the many oxides.

Compatibility with the CMOS process is a major criterion in choosing the metal oxide for RRAM design. Tungsten oxide ( $WO_X$ )-based RRAM is attractive because it requires only one extra mask without contamination issue, new equipment or new material to the standard CMOS process. The device performances of  $WO_X$ -based RRAM are further studied. The  $WO_X$  converting by rapid thermal oxidation (RTO) provides the suitable performance such as low switching current, high resistance window, fast programming speed, good thermal stability, and high endurance for nonvolatile memory. Besides the conducting mechanism is also investigated by using different work function electrodes connecting with  $WO_X$  elements.

#### **1.2 Thesis Organization**

This thesis consists seven chapters.

At first, chapter 1 gives a brief introduction and organization for this dissertation. Chapter 2 reviews the previous literatures of emerging resistive memories such as PCM, MRAM, and RRAM.

In chapter 3, the magneto impedance behavior of the PSV is addressed. The NOL effect of the PSV is studied. The new non-destructive analysis method via the magneto impedance spectroscopy for investigate the PSV with different thickness of NOL is provided. Also, the magneto impedance behavior study for MTJ is shown in chapter 4. The equivalent circuit model can well describe the AC phenomenon of the MTJ.

In chapter 5 and 6, the main discussion shifts to RRAM research. The tungsten oxide RRAM by using down stream plasma oxidation (DSPO) is proposed in chapter 5. The device analysis and performance are introduced. Chapter 6 shows the further improved  $WO_X$  device by using rapid thermal oxidation (RTO) process. The first time transient effect study for  $WO_X$  device is demonstrated, and it reveals ultra fast program speed for RTO  $WO_X$  RRAM. Moreover the performance, operation method, and conduction mechanism are explained in detail.

Finally, the summary and future prospects will be given in chapter 7, respectively.

### **CHAPTER 2**

## **Basic of MRAM and RRAM**

#### 2.1 Magnetoresistive Random Access Memory (MRAM)

#### 2.1.1 Magnetoresistance Effect

In this section, we will discussion the magnetoresistance, include pseudo spin valve effect and tunneling magnetoresistance effect.

The pseudo spin valve is composed of a hard magnetic layer, HM, and a soft magnetic layer, SM, magnetically separated with a nonmagnetic layer, NM. The HM has a larger coercivity than the SM. A prototype pseudo spin valve film proposed by Shinjo et al. is  $[NiFe(3)/Cu(5)/Co(3)/Cu(5)]^{15}$  multilayered film [1]. NiFe is used for the SM and Co is used for the HM. This multilayered film showed a MR ratio of ~8%. The magnetocrystalline anisotropy energy, E<sub>a</sub>, for the films having cubic symmetry is given as

$E_a = K_1/8(1 - \cos 4\theta) + \dots$

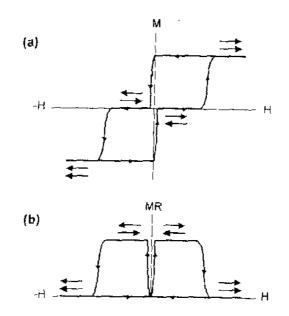

Fig. 2.1. (a) Magnetization curve and (b) MR curve of the pseudo-spin-valve, where the magnetization directions of the SM and the HM are denoted with gray and black arrows, respectively.

When the magnetization rotates in the (100) plane, where  $\theta$  is the angle between the magnetization direction and the [010] axis. The K<sub>1</sub> is the negative for fcc NiFe and Co. Therefore, the NiFe and Co layers have the easy axis along the [011] direction. This is the reason why the magnetization reversal of the NiFe and Co layers take place. These characteristics are suitable for the application of pseudo-spin-valve to MRAM devices, as the magnetization reversal of the HM(=Co) layers is used for the data writing and that of SM(=NiFe) layers is used for data reading, The switching field of SM is lower than that of the HM layers. The schematic magnetization curve and the MR curve of the pseudo-spin-valve are shown in Fig. 2.1(a) and (b). With the application of a small magnetic field that causes magnetization reversal of the SM, but not of the HM, the magnetization directions of the SM and the HM take an antiparallel configuration. Then, the pseudo-spin-valve shows high resistance. With the application of a large magnetic field that causes magnetization reversal of the HM, the magnetization directions of the SM and HM take a parallel configuration and the pseudo-spin-valve shows low resistance. Pseudo-spin-valve shows a symmetric MR curve with the magnetic field direction, while the exchange-biased spin valves show a nonsymmetric one as shown in Fig. 2.2, as the HM in the pseudo-spin-valve has uniaxial anisotropy, while the pinned magnetic layer (PL)/ antiferromagnetic (AF) in the exchange-bias spin valve has unidirectional anisotropy.

Fig. 2.2. MR curve for the single spin valve, where the magnetization directions of the FM and the PL are denoted with gray and black arrows, respectively.

The exchange-biased spin valve shows a reversible MR curve with the magnetic field. But the pseudo-spin-valve shows an irreversible one. This is a disadvantage of pseudo-spin-valve for application to MR heads. However, pseudo-spin-valves are studied for application to MRAM (magnetic random access memory) devices [2,3].

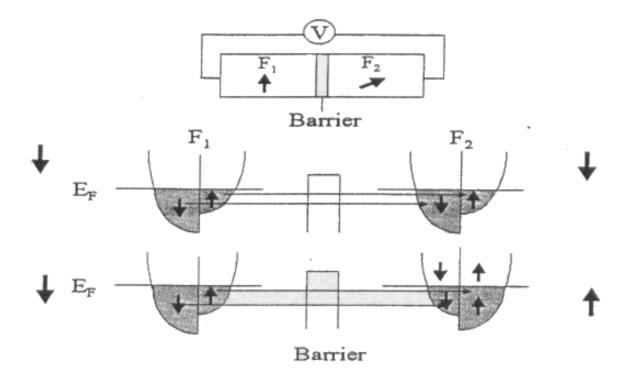

Tunneling magnetoresistance (TMR) is observed for ferromagnetic spin tunneling junctions (MTJ) consisting of ferromagnetic-insulator- ferromagnetic layers [4-6]. When the insulating layer, usually referred to as the barrier layer, is very thin (the order of 1nm), electrons can tunnel through this forbidden region as a result of the wave-like nature of electrons for a voltage applied between the two electrodes, and can only be described in terms of quantum mechanics. The basic principle of TMR is the dependence of the tunneling probability on the relative orientation of magnetization in the two ferromagnetic electrodes. The tunneling conductance is spin dependent due to the spin dependent density of states (DOS) at the Fermi level for ferromagnets. When the applied voltage is small enough for electrons near the Fermi level to tunnel, the tunneling conductance G in the MTJ can be written as (2.1.1)-(2.1.2) by neglecting the spin dependency of the tunneling probability [7],

$$G = R^{-1} = \sum_{\sigma} |T|^2 D_{1\sigma}(E_F) D_{2\sigma}(E_F) \dots (2.1.1)$$

$$|T|^2 \exp(-2s\chi) \dots (2.1.2)$$

$$\chi = \left[8\pi^2 m \times (\varphi - E_F)/h^2\right] \dots (2.1.3)$$

where R, T,  $D_{i\sigma}(E_F)$  are the junction resistance, tunneling probability, DOS at the Fermi level for spin  $\sigma$  band of the i-th ferromagnet, respectively, and $\phi$ ,s,  $\chi$  and h are the barrier height and thickness, electron wave vector in the barrier and the Planck constant, respectively. The TMR is defined as

where  $R_P$  and  $R_{AP}$  are the resistance for parallel and antiparallel spin configurations of two ferromagnetic electrodes, respectively. If we assume that spin is conserved during tunneling as shown Fig. 2.3, (2.1.1)-(2.1.4) lead to Julliere's model [4],

Fig. 2.3. A schematic model for spin dependent tunneling

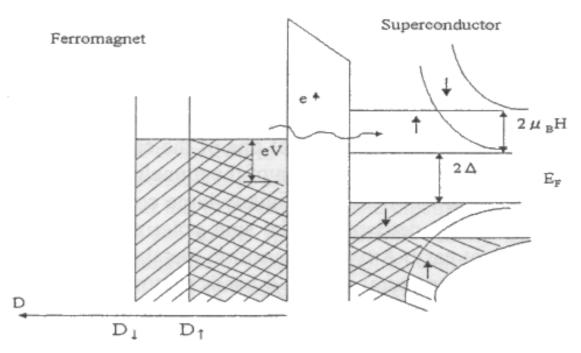

Fig. 2.4. Probing the spin polarization of tunneling electrons from the ferromagnet to the superconductor

Pi is the spin polarization of tunneling electrons of ferromagnet i and given by

TMR can vary over a wide range depending on the P values of ferromagnets as verified by (2.1.5) and (2.1.6). For vanishing polarization of one of the electrodes the magnetoresistance disappears, while for full polarization of the tunneling electrons of both electrodes ( $P_1=P_2=1$ ) the effect will become infinitely large corresponding to a value of 1 in (2.1.5). Unfortunately, determining the spin polarization at the Fermi energy of a ferromagnet is not easy. A typical transition metal ferromagnet has two components to its electronic structure; narrow d-bands that may be fully or partially spin polarized and broad s-bands with a lesser degree of spin polarization due to hybridization with the d-bonds. The value of P is controlled by extending to which these s- and d-bonds cross the Fermi energy. If the orbital character at the Fermi surface of the ferromagnetic metal is primarily d-like, then the spin polarization will be high. If the orbital character, however, is s-like or s-d hybridized, then the spin polarization can be low or high depending on the detail of the electronic structure. The magnetization of a material may show that all the electronic spins associated with the d orbits are aligned but the spin polarization at E<sub>F</sub> can de depressed. On the other hand, metallic oxide ferromagnets, for example, have a greater opportunity for high spin polarization because of the predominance of the d orbital character at E<sub>F</sub>.

Measuring the spin polarization requires a spectroscopic technique that can discriminate between the spin-up and spin-down electrons near  $E_F$  spin polarized photoemission spectroscopy is technically capable of providing the most direct measurement of P, but lacks the necessary energy resolution (~1meV). An effective alternative to photoemission is the use of spin polarized tunneling in a planar junction geometry which does allow the electronic spectrum near  $E_F$  to be probe with sub-meV energy resolution.

Tedrow and Meservey pioneered this technique by marking superconductor/insulator/ferromagnet junctions and Zeeman splitting the superconductor's strongly peaked single-particle excitation spectrum by the application of a magnetic field [8]. The spin-splitting of the quasiparticle density of states in a superconductor by the application of a magnetic field allows probing the spin polarization of tunneling electrons from the ferromagnet, which is schematically shown in Fig. 2.4. The resulting spectrum of the superconductor roughly corresponds to two fully spin polarized peaks (neglecting spin-orbit coupling effects) that can be used to detect the spin polarization of a current from the ferromagnetic film. Another method of measuring spin polarization of a metal was developed recently [9], which is a metallic point contact between the point contact measures the conversion between superconducting pairs and the single particle charge carriers of the metal. The conversion of normal current to supercurrent at a metallic interface is called Andreev reflection.

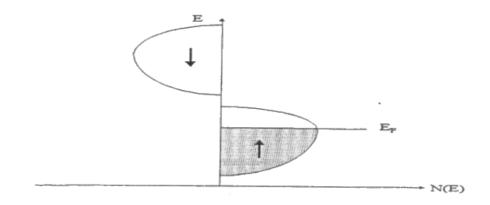

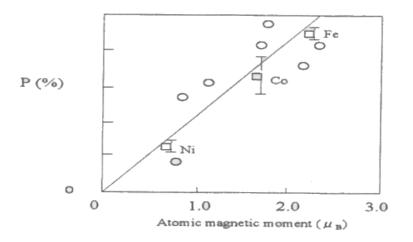

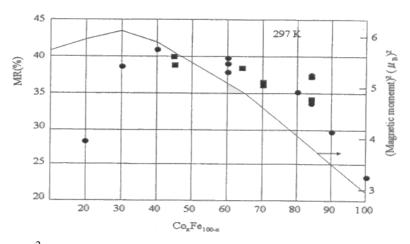

The values of P measured are shown in Table 2.1.1 for various ferromagnets except for the theoretically expected values for half metals with P=1, which have an energy gap in the minority spin (down spin) band as shown schematically in Fig. 2.5, thus only majority spin (up spin) electrons at the Fermi level. The spin polarization of tunneling electrons seems to be nearly proportional to the magnetic moment  $\mu$  of the electrode as shown for Ni-Fe alloys in Fig. 2.6 [8], while it is not always proportional to  $\mu$  of the ferromagnetic electrode as shown in Fig. 2.7 [10], which exhibits TMR and  $\mu^2$  as a function of the composition of Fe-Co alloy electrodes used for the junctions.

| Magnetic material                 | Spin polarization | Magnetic materials             | Spin polarization |

|-----------------------------------|-------------------|--------------------------------|-------------------|

| Fe                                | 0.44              | NiMnSb                         | 1,0.58            |

| Со                                | 0.35              | PtMnSb                         | 1                 |

| Ni                                | 0.23              | CrO2                           | 1                 |

| Ni <sub>80</sub> Fe <sub>20</sub> | 0.25,0.45         | Fe <sub>3</sub> O <sub>4</sub> | 1                 |

| Fe <sub>50</sub> Co <sub>50</sub> | 0.53              | (La-Sr)MnO <sub>3</sub>        | 1                 |

Table 2.1.1 Spin polarization of various magnetic materials

Equation (2.1.5) assumes that all electrons at the Fermi level have the same probability of tunneling and also neglects the influence of the barrier. In fact, however, TMR depends on tunneling barrier height for the MTJ using CoFe electrodes. The TMR is larger for the higher barrier height. The barrier height can be estimated by Simmons' expressions (2.1.7)-(2.1.10)

$$J = \beta (V + V^{3}), \qquad (2.1.7)$$

$$\beta = \left[ 3e^{2} (2m\phi)^{1/2} / 2h^{2}s \right] \exp \left( -A\phi^{1/2} \right) \left[ \Omega^{-1}cm^{2} \right], \qquad (2.1.8)$$

$$\gamma = (Ae)^{2} / 96\phi - Ae^{2} / 32\phi^{1/4}, \qquad (2.1.9)$$

$$A = 4\pi (2m)^{1/2} s / h = 1.02 \left[ A / (e^{V})^{1/2} \right], \qquad (2.1.10)$$

for lower bias voltage, where J,  $\phi$  and s are current density [A/cm<sup>2</sup>], barrier height [eV] and barrier thickness [cm], respectively.

Fig. 2.5. Schematic energy band structure for a half metal

Fig. 2.6. Spin polarization of tunneling electrons versus the magnetic moment  $\mu$  of the electrode.

Fig. 2.7. TMR and  $\mu^2$  as function of the composition of Fe-Co alloy electrodes used for the junctions.

#### 2.1.2 Magneto Impedance Theory

Magneto impedance,  $MI = M|Z|e^{i\theta} = MR + iMX$ , in which  $X = X_L - X_C$ , originates mainly from the inductance and capacitance of the magneto device. Z is the impedance,  $\theta$  is the phase angle, R is the real part of magneto impedance, and X is the imaginary part of magneto impedance.

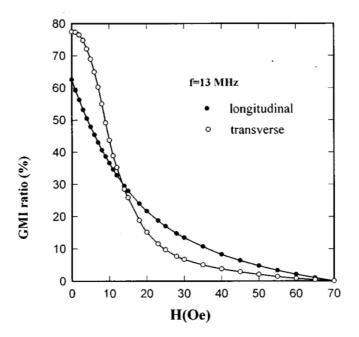

In 1999, X.Q. Xiao [11] shows giant magnetoimpedance (GMI) effect in films with a sandwiched structure [12]. As compared to single layered films, the sandwiched films have much higher GMI ratio at relatively low frequencies. This is because of the separation of the ac current path from the magnetic flux path. The inner highly conductive metal reduces the entire resistance of the sandwiched film, and the outer magnetic layers form a magnetic alloy closed-loop structure. Therefore, less power is dissipated in the films to generate the ac transverse field. In the FeNiCrSiB/Cu/FeNiCrSiB structure, GMI ratios of 63% and 77% have been obtained at 13 MHz in longitudinal and transverse fields, respectively as shown in Fig. 2.8. These values are almost twice as large as those obtained in single layered FeNiCrSiB films.

Fig. 2.8. Field dependence of  $\triangle |Z| / |Zs|$  at 13 MHz in longitudinal (filled symbols) and transverse (hollowed symbols) field.

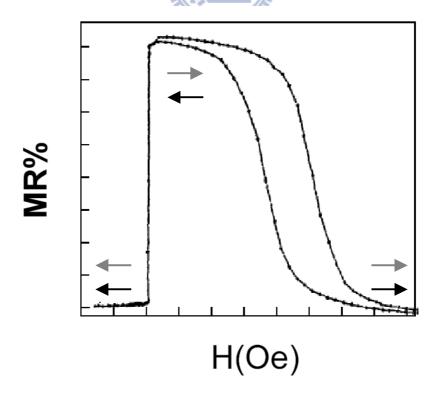

In 2000, M.F. Gillies [13] further proposed the magneto impedance effect for magneto tunneling junctions [14]. The structure is the Si/SiO2/Co/AlOx /Co. Due to differing conductivities charge collects at the interface between the dielectrics as well as on the capacitor plates (Maxwell Wagner capacitor model). This results in two contributions to the impedance. In the case of the magnetic tunnel junctions studied, they extend this simple analysis to more than two layers in order to provide a model with which the complicated results of the impedance measurements as shown in Fig. 2.9 (a) and (b). By this AC analysis, the oxide/Co multilayer proved a very useful way of determining the total oxide thickness as a function of oxidation time and allowed a rough check of what was determined from the impedance measurements. The strength of the impedance measurements is that they provide a "fingerprint" of the oxide, rather than definitive fit parameters, and in so doing help to characterize the oxide.

Fig. 2.9. (a) Real and (b) imaginary parts of impedance for junctions with different oxidation times (in seconds). In both figures the dots show the measured results and the solid lines are fits.

#### 2.1.3 Field Driven Magnetization Switching Designs

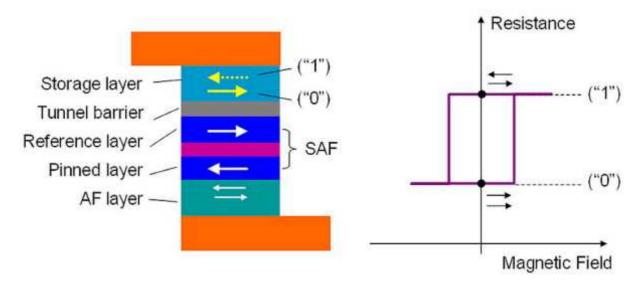

In most of today's MRAM designs, the memory element is a magnetic tunnel junction (MTJ) that consists of two magnetic electrodes sandwiching an insulative tunnel barrier, as shown in Fig. 2.10 [15-18]. The resistance of these magnetic tunnel junctions depends on the relative orientation of the magnetic moments in the two magnetic electrodes interfacing with the tunnel barrier [19-22]. When the magnetic moments of the two magnetic layers are antiparallel, the resistance of the tunnel junction is significantly higher than when they are in parallel. The magnetic electrodes are shaped like an ellipse to create a shape-defined magnetic anisotropy. The magnetic moment will always be resting along the long axis of the element, referred to as the magnetic easy axis, as shown in Fig. 2.11 [23]. Assuming we can "fix" or "pin" the direction of the magnetic moment of the bottom layer, referred to as the reference layer, along the easy axis, the magnetic moment orientation of the storage layer along the easy axis will give rise to two states with distinctively different resistance values, thereby, the two states in binary bit. The magnetization of the reference layer is "fixed" via a multilayer structure, which includes an antiferromagnetic layer at the bottom. The reference layer is part of a trilayer known as synthetic antiferromagnet (SAF) that is free of stray field. A good example is CoFe/Ru/CoFe with Ru of thickness around 8A°. The antiferromagnetic layer yields an interfacial exchange field that "pins" the magnetic moment of the bottom SAF layer (pinned layer).

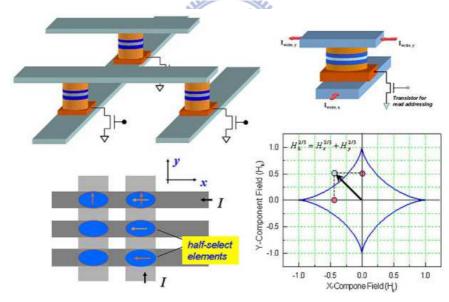

In a memory element array, each memory element is connected to a transistor, which performs the read addressing for reading back the memory state of an individual cell. The memory state writing of an individual memory element in the array is performed by a x-y grid of conducting wires, referred to as word lines and digital lines, placed over and below the memory elements with a memory element located at each cross, as shown in Fig. 2.12.

A current flowing through a selected word line (running in the y-direction in the figure) generates a magnetic field along the easy axis  $H_x$  while a current flowing through a selected

digital line (running in the x-direction) generates a field  $H_y$  in a direction transverse to the easy axis. A simple theoretical analysis shows that the field threshold for resulting in a magnetic switching is given by  $H_x^{2/3}+H_y^{2/3}=H_k^{2/3}$  often referred to as the Stoner–Wohlfarth switching astroid, where  $H_k$  is the anisotropy field of the element [24]. According to the above equation, the switching field threshold is the lowest when both field components are equal in magnitude: The memory state of the element at the cross of the activated word line and digital line can be changed. Whereas the rest of the elements along the selected word or digital lines, known as the half-selected elements, shall not be affected since they only experience one of the two fields, provided each field component is below  $H_k$ .

Fig. 2.10. Schematic drawing of a typical magnetic tunnel junction memory element and corresponding memory states that have two distinctive resistance values due to the magnetoresistive effect.

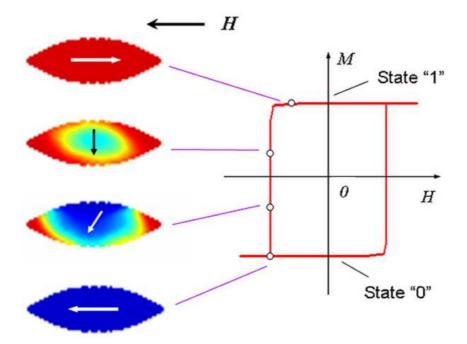

Fig. 2.11. Simulated magnetic switching of an eye-shaped magnetic element. The magnetization reversal starts at the center of the element with quasi-coherent magnetization rotation. The reversed region expands towards the ends as the reversal completes.

Fig. 2.12. Schematic drawing of the memory element array. Each memory element is connected to a field effect transistor for read addressing. A grid of x-y conducting wires, known as the digital lines (wires along the x-direction) and word lines (wires along the y-direction), is placed over and below the memory elements for providing the magnetic field for the write operation. Each memory element is located at a cross in the x-y wire grid. The lower bottom shows the switching field threshold contour, known as the Stoner–Wohlfarth switching astroid. The magnetization of the storage layer will remain unchanged if the field applied is located within the enclosed region of the astroid. Otherwise, the magnetic moment will irreversibly switch to the direction of the word line field.

#### 2.1.4 Spin Torque Transfer Driven Switching Designs