# 國立交通大學光電工程研究所

分散式控制混合型被動光纖網路 之設計成果

# Design and Implementation of Novel Distributed Control Hybrid Passive Optical Network

研究生:林文翔

指導教授:陳智弘 老師

中華民國九十七年六月

# 分散式控制混合型被動光纖網路 之設計成果

# Design and Implementation of Novel Distributed Control Hybrid Passive Optical Network

研究生:林文翔 Student: Wen-Hsiang Lin

指導教授: 陳智弘 老師 Advisor: Associate Prof. Jyehong Chen

A Thecis

Submitted to Institute of Electro-Optical Engineering

College of Electrical Engineering and Computer Science

National Chiao Tung University

In Partial Fulfillment of the Requirements

For the Degree of

Master

In

Institute of Electro-Optical Engineering

June 2008

Hsinchu, Taiwan, Republic of China

中華民國九十七年六月

# 分散式控制混合型被動光纖網路 之設計成果

學生:林文翔 指導教授:陳智弘 老師

國立交通大學

光電工程研究所碩士班

# 摘要

近年來,數位化資訊的蓬勃發展,網際網路的普及,以往以數據為導向的網路服務漸漸轉成以視頻、語音和數據整合為主,所以用戶需要的網路頻寬也越來越大。以前用的非對稱數位用戶迴路網路系統已不敷使用,然而被動式光纖網路系統可以提供很大的網路頻寬,而受到極大的重視,漸漸取代了非對稱數位用戶迴路網路系統。標準的分時多工、分頻多工被動式光纖網路系統中,時槽和波長的利用是很沒效率的,因為閒置中的時槽或波長無法被共用,而造成頻寬浪費。集中式動態頻寬分配由於封包訊息無法即時的更新,使封包延遲造成即時資料停頓。因此我們提出了一個全新架構的系統:分散式控制混合型被動光纖網路。

分散式控制混合型被動光纖網路結合了分時多工與分波多工技術,以增加網路 頻寬和降低成本,分散式動態頻寬分配可以將封包訊息即時的更新,使即時資料 不會延遲。我們用元件可程式邏輯閘陣列來實踐光路線終端以及光網路單元,實 際的架起一個分散式控制混合型被動光纖網路系統。 **Design and Implementation of Novel Distributed**

**Control Hybrid Passive Optical Network**

Student: Wen-Hsiang Lin

Advisor: Dr. Jyehong Chen

Institute of Electro-Optical Engineering

National Chiao Tung University

Recently due to digital information flourishing and internet penetrating, formerly

data-oriented network services changed into the integration of video, voice, and data.

Users need larger and larger bandwidth. ADSL cannot support with bandwidth now,

PON gradually replaces ADSL because of larger bandwidth. In the PON network

system, TDM-PON and WDM-PON, the use of slot and wavelength is not very

efficient since idle in the slot and wavelength cannot be shared. Then centralized

control dynamic bandwidth allocation (DBA) cannot update packets information

immediately, so it makes real-time data delay. For this reason, we propose a novel

system: Distributed Control Hybrid Passive Optical Network (DHPON)

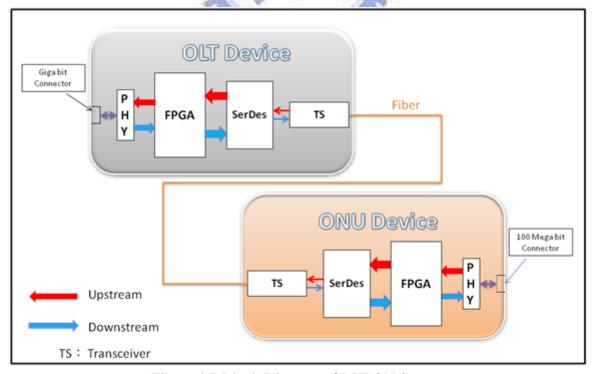

DHPON combines TDM-PON and WDM-PON to increase the network bandwidth

and reduce costs, distributed control DBA can update packets information immediately

avoiding real-time data delay. We use FPGA to set up optical line terminal (OLT) and

optical network unit (ONU) constructing a DHPON system.

ii

#### 致謝

# Acknowledgements

這篇論文得以完成,首先我要誠摯的感謝指導教授 陳 智弘 老師,在我研究所就讀期間悉心地教導與指點,得以一窺光通訊領域的深奥,使我在這兩年中獲益匪淺。在陳老師亦師亦友的教導下,得到的不只是學術上的心得,更重要的是待人處事的啟發,令我受益良多,將受用一輩子。

另外特別感謝清雲學長犧牲下班時間、不厭其煩的給予很多的教導以及幫忙, 每天一起實驗到晚上11、12點,指出我實驗中的缺失及問題,總能在我迷惘時為 我解惑。如果沒有清雲學長,相信這篇論文無法順利完成。

感謝實驗室成員,建和、曹正、晟峰、俊臻 學長,在課業、生活以及研究上不吝嗇地給我最大的關懷與指教,使我一路茁壯。還有陪伴我一同成長的同學, 偉哲、文智、盛鵬、易辰,以及碩一的學弟妹,因為有你們,讓我碩士生涯過得 很充實和愉快。

最後,感謝我的父親-林 木柱 先生、母親-蔡 淑邁 女士、姊姊 林君怡 、弟弟 林文傑,謝謝你們無怨無悔的付出、支持我、鼓勵我。

我由衷地感謝每一個幫助我的人,我沒有辜負您們的期盼,我的成就與驕傲全因您們而得,我將一切的榮耀都奉獻給您們,謝謝。

謹將此論文獻給所有愛我及我愛的人

西元2008年6月 於新竹交大

# **Contents**

| Chinese Al  | stract i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| English Ab  | <b>stract</b> ii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |

| Acknowled   | gements iii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

| Contents    | iv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

| List of Fig | ıres vii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |

| List of Tab | les x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |

| Chapter 1   | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1 |

|             | AND DESCRIPTION OF THE PARTY OF |   |

| Chapter 2   | Conventional and Novel Architecture of PON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |

| 2.1         | Passive Optical Network Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1 |

| 2.2         | Time Division Multiplexed PON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |

|             | 2.2.1 Broadband PON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5 |

|             | 2.2.2 Gigabit PON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7 |

|             | 2.2.3 Ethernet PON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3 |

| 2.3         | Wavelength Division Multiplexed PON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ) |

| 2.4         | Centralized Control Dynamic Bandwidth Allocation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ) |

|             | 2.4.1 Interleaved Polling with Adaptive Cycle Time (IPACT) 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | l |

|             | 2.4.2 Round Trip Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2 |

| 2.5         | Distributed Control Dynamic Bandwidth Allocation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3 |

| 2.6         | Distributed Control Hybrid Passive Optical Network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1 |

|             | 2.6.1 DHPON Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1 |

|             | 2.6.2 Concept of the Distributed Control DBA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5 |

|             | 2.6.3 An Example of the Distributed Control DBA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5 |

|           | 2.6.4  | The Data Traffic of DHPON                         | 17 |

|-----------|--------|---------------------------------------------------|----|

|           | 2.6.5  | Advantage of DHPON                                | 18 |

|           |        |                                                   |    |

| Chapter 3 | Distr  | ributed Control Hybrid Passive Optical Network    |    |

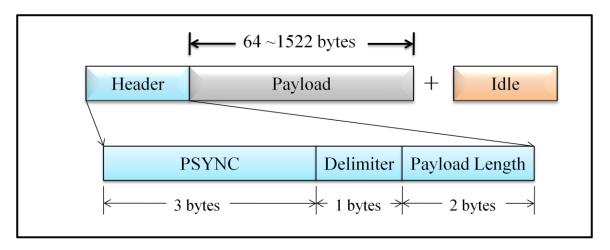

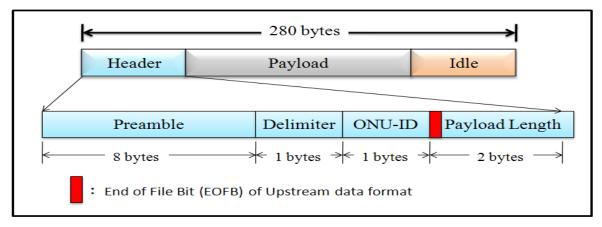

| 3.1       | The Da | ata Format of DHPON                               | 20 |

|           | 3.1.1  | Data Format in Downstream                         | 20 |

|           | 3.1.2  | Data Format in Upstream                           | 21 |

| 3.2       | Downs  | stream on DHPON                                   | 22 |

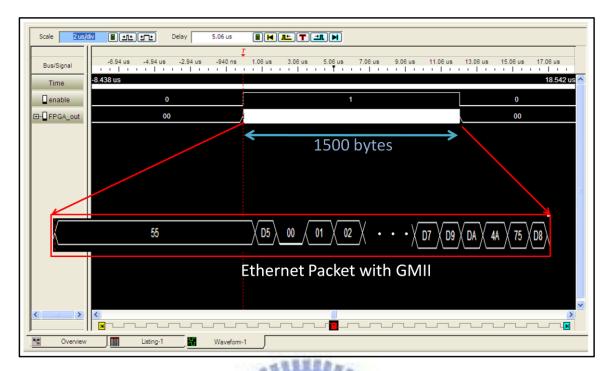

|           | 3.2.1  | Gigabit Media Independent Interface (GMII) on OLT | 23 |

|           | 3.2.2  | Downstream Data Buffer on OLT                     | 23 |

|           | 3.2.3  | Framer on OLT                                     | 24 |

|           | 3.2.4  | PON MAC on ONU                                    | 24 |

|           | 3.2.5  | Downstream Data Buffer on ONU                     | 25 |

|           | 3.2.6  | Media Independent Interface (MII) on ONU          | 25 |

| 3.3       | Upstre | am on DHPON                                       | 26 |

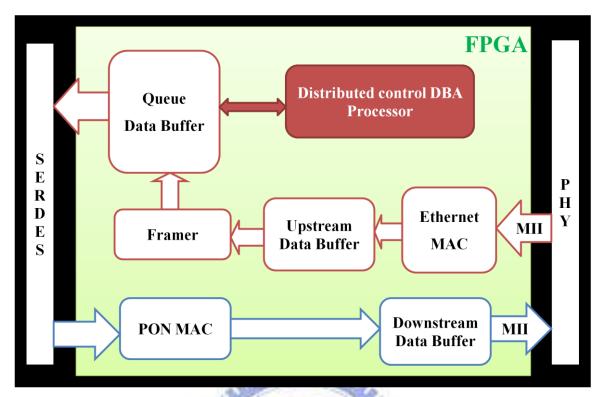

|           | 3.3.1  | Media Independent Interface (MII) on ONU          | 27 |

|           | 3.3.2  | Ethernet MAC on ONU                               | 27 |

|           | 3.3.3  | Upstream Data Buffer on ONU                       | 27 |

|           | 3.3.4  | Framer on ONU                                     | 28 |

|           | 3.3.5  | Queue Data Buffer on ONU                          | 29 |

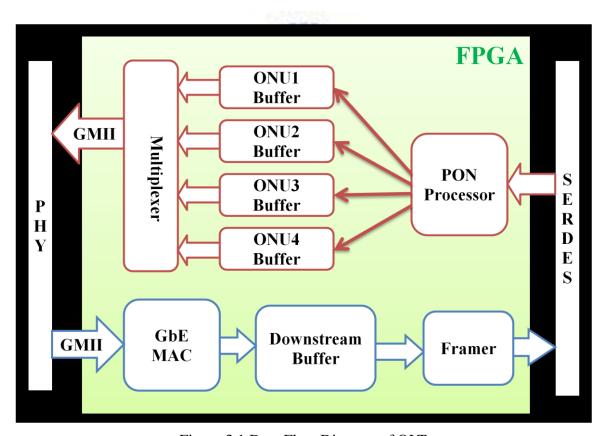

|           | 3.3.6  | PON Processor on OLT                              | 29 |

|           | 3.3.7  | ONU Buffer and Multiplexer                        | 30 |

|           | 3.3.8  | Gigabit Media Independent Interface (GMII) on OLT | 30 |

# **Chapter 4 Devices on Board of DHPON**

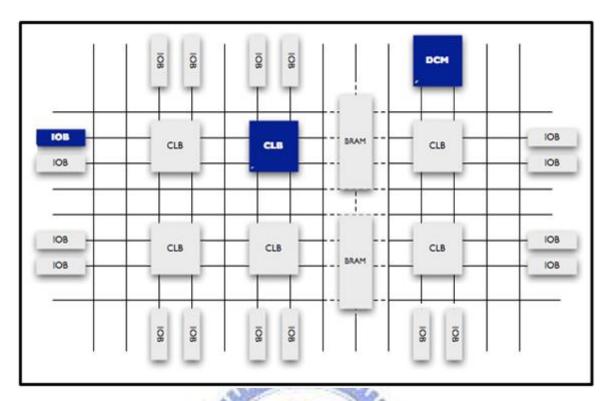

| 4.1                  | Field Programmable Gate Array (FPGA)          |                                                    |  |  |

|----------------------|-----------------------------------------------|----------------------------------------------------|--|--|

|                      | 4.1.1                                         | FPGA Features 33                                   |  |  |

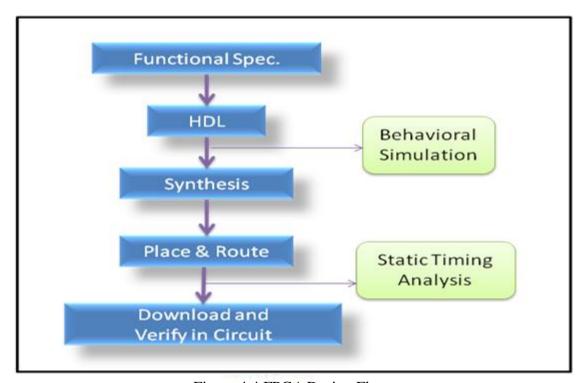

|                      | 4.1.2                                         | Design Flow of FPGA                                |  |  |

|                      | 4.1.3                                         | FPGA on ONU                                        |  |  |

| 4.2                  | Physica                                       | al Layer                                           |  |  |

|                      | 4.2.1                                         | OLT Physical Layer                                 |  |  |

|                      | 4.2.2                                         | ONU Physical Layer                                 |  |  |

| 4.3                  | Serializ                                      | zer/Deserializer (SerDes)                          |  |  |

| 4.4                  | Optical                                       | Transceiver of ONU                                 |  |  |

| 4.5                  | Optical                                       | Transceiver of OLT                                 |  |  |

| 4.6                  | Summa                                         | ary                                                |  |  |

|                      |                                               | ESBE                                               |  |  |

|                      |                                               |                                                    |  |  |

| Chapter 5            | Testi                                         | ng and Results on Hardware                         |  |  |

| <b>Chapter 5</b> 5.1 |                                               | ng and Results on Hardware Results of Data Traffic |  |  |

| •                    |                                               |                                                    |  |  |

| •                    | Testing                                       | Results of Data Traffic                            |  |  |

| •                    | Testing 5.1.1 5.1.2                           | Results of Data Traffic                            |  |  |

| 5.1                  | Testing 5.1.1 5.1.2                           | Results of Data Traffic                            |  |  |

| 5.1                  | Testing 5.1.1 5.1.2 Testing                   | Results of Data Traffic                            |  |  |

| 5.1                  | Testing 5.1.1 5.1.2 Testing 5.2.1             | Results of Data Traffic                            |  |  |

| 5.1                  | Testing 5.1.1 5.1.2 Testing 5.2.1 5.2.2       | Results of Data Traffic                            |  |  |

| 5.1                  | Testing 5.1.1 5.1.2 Testing 5.2.1 5.2.2 5.2.3 | Results of Data Traffic                            |  |  |

| 5.1                  | Testing 5.1.1 5.1.2 Testing 5.2.1 5.2.2 5.2.3 | Results of Data Traffic                            |  |  |

# LIST OF FIGURES

| Figure 2.1  | The Architecture of Passive Optical Network | 5  |

|-------------|---------------------------------------------|----|

| Figure 2.2  | The Architecture of TDM-PON                 | 6  |

| Figure 2.3  | Upstream and Downstream Formats of EPON     | 9  |

| Figure 2.4  | The Architecture of WDM-PON                 | 10 |

| Figure 2.5  | Concept of Centralized-Control DBA          | 11 |

| Figure 2.6  | Example of IPACT                            | 12 |

| Figure 2.7  | Round Trip Time of Centralized Control DBA  | 13 |

| Figure 2.8  | The Architecture Distributed Control DBA    | 14 |

| Figure 2.9  | The Architecture of DHPON                   | 15 |

| Figure 2.10 | Basic Concept of Distributed Control DBA    | 16 |

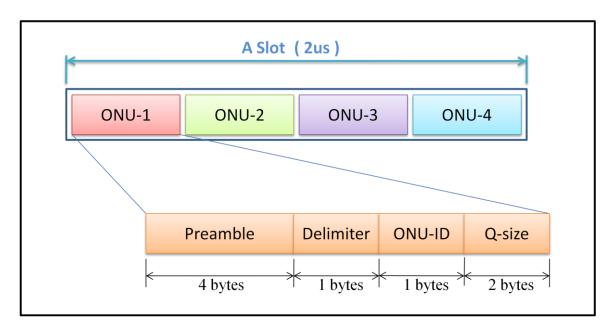

| Figure 2.11 | DBA Control Message of an ONU               | 17 |

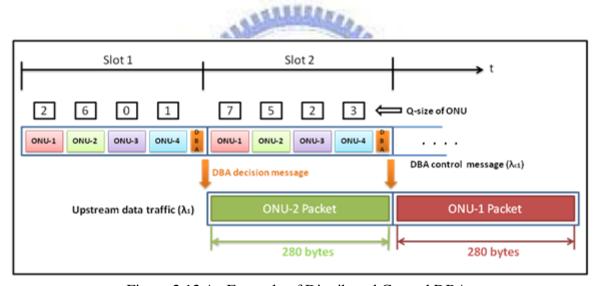

| Figure 2.12 | An Example of Distributed Control DBA       | 17 |

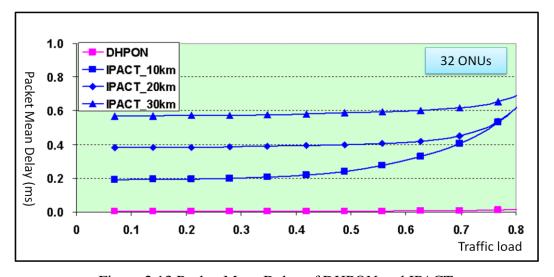

| Figure 2.13 | Packet Mean Delay of DHPON and IPACT        | 18 |

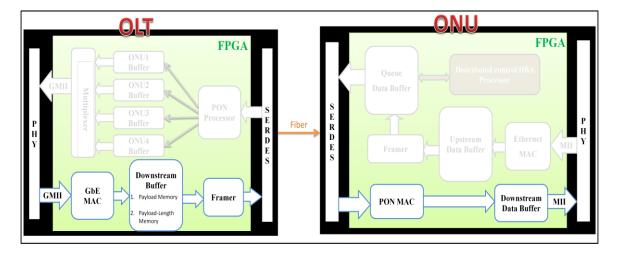

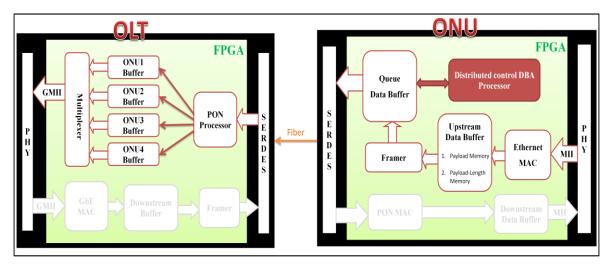

| Figure 3.1  | Data Flow Diagram of OLT                    | 19 |

| Figure 3.2  | Data Flow Diagram of ONU                    | 20 |

| Figure 3.3  | Data Format in Downstream                   | 21 |

| Figure 3.4  | Data Format in Upstream                     | 22 |

| Figure 3.5  | Data Flow Diagram of Downstream             | 22 |

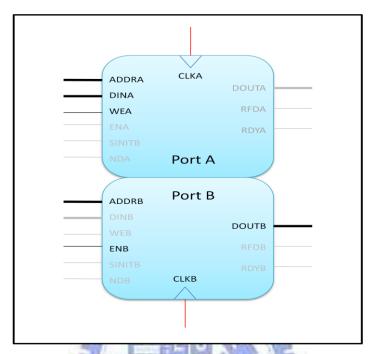

| Figure 3.6  | Dual Port Block Memory                      | 24 |

| Figure 3.7  | Data Flow Diagram of Upstream               | 27 |

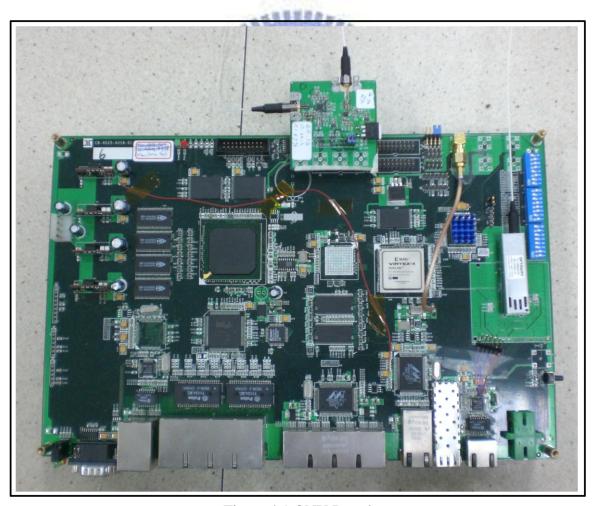

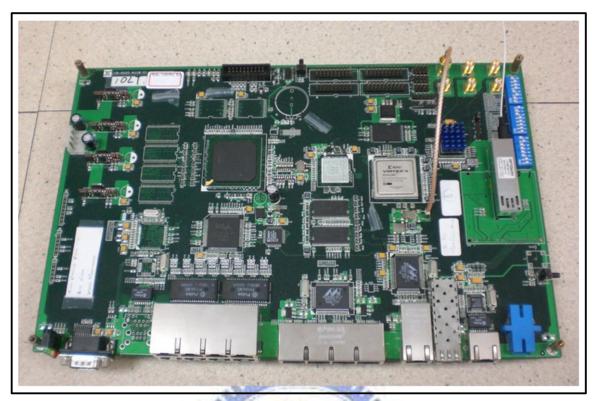

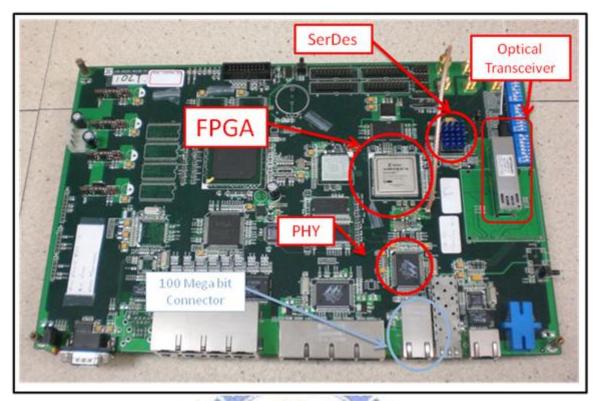

| Figure 4.1  | ONU Board                                   | 31 |

| Figure 4.2  | OLT Board                                   | 32 |

| Figure 4.3  | Block Structure of FPGA                     | 33 |

| Figure 4.4  | FPGA Design Flow                            | 35 |

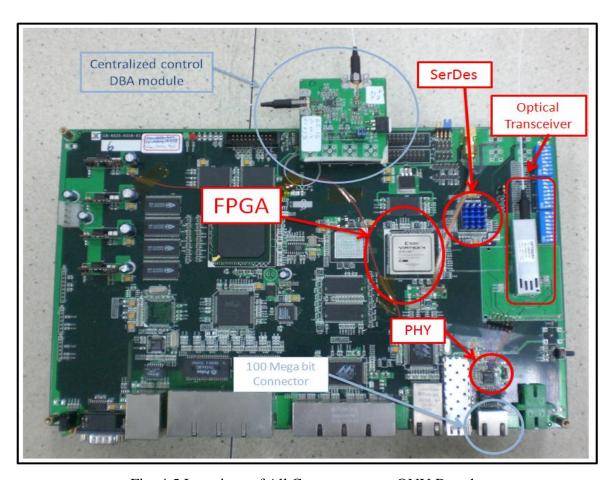

| Figure 4.5  | Locations of All Components on ONU Board     | 40 |

|-------------|----------------------------------------------|----|

| Figure 4.6  | Locations of All Components on OLT Board     | 41 |

| Figure 4.7  | Block Diagram of DHPON System                | 41 |

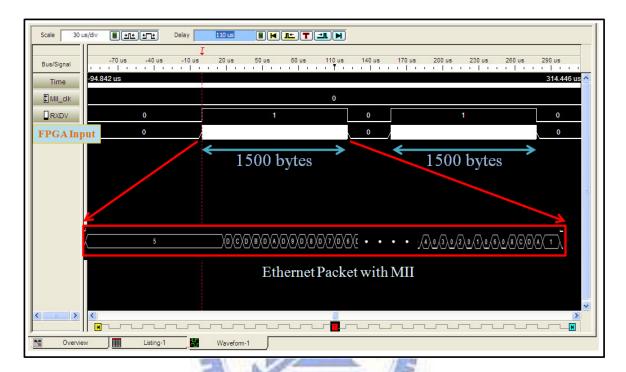

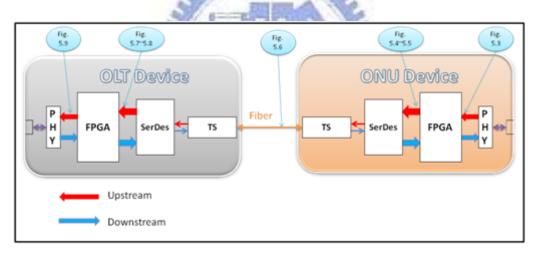

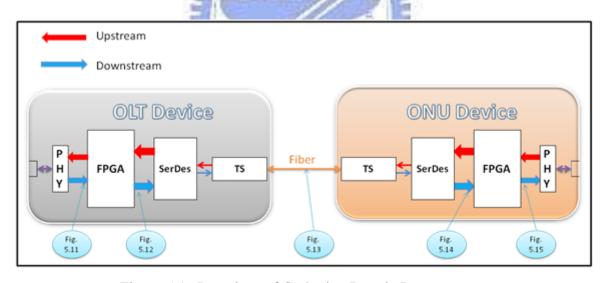

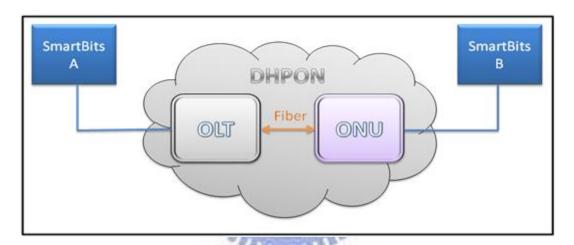

| Figure 5.1  | Testing Architecture of DHPON                | 43 |

| Figure 5.2  | Connect Logic-Analyzer with the Board        | 44 |

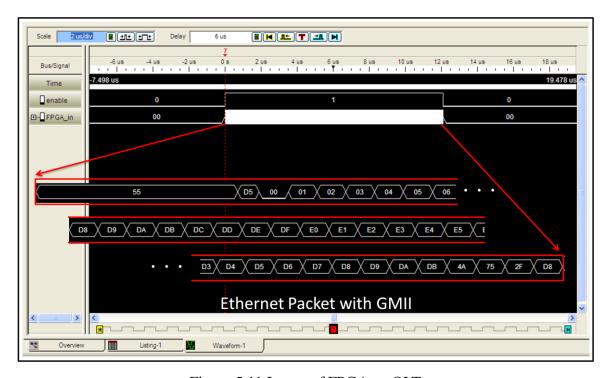

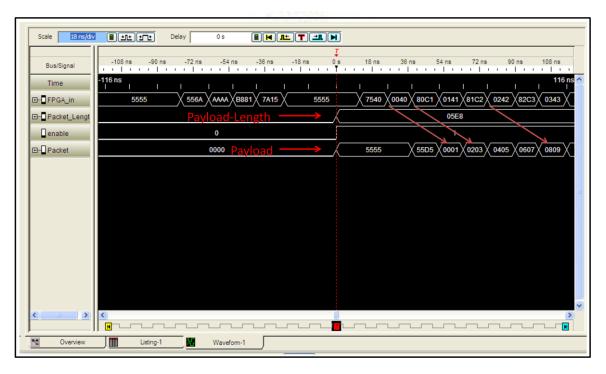

| Figure 5.3  | Inputs of FPGA on ONU Board                  | 45 |

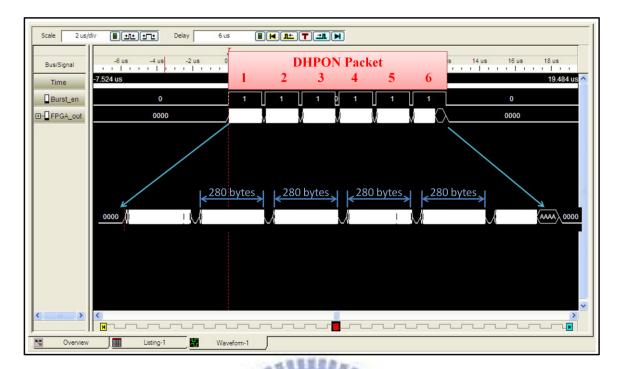

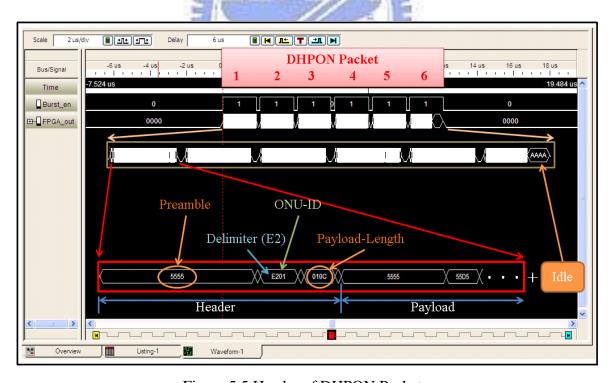

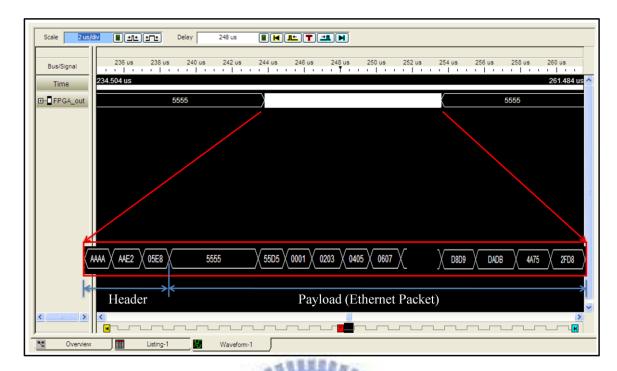

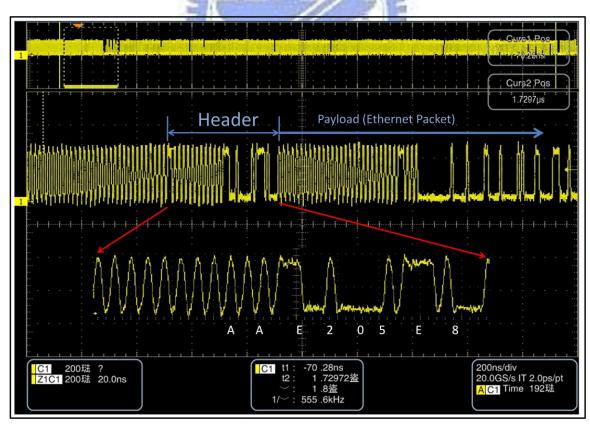

| Figure 5.4  | DHPON Packets                                | 46 |

| Figure 5.5  | Header of DHPON Packet                       | 46 |

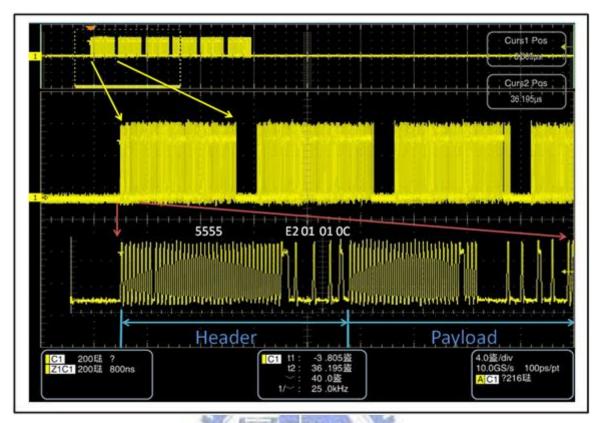

| Figure 5.6  | DHPON Packets with Optical Signal on Fiber   | 47 |

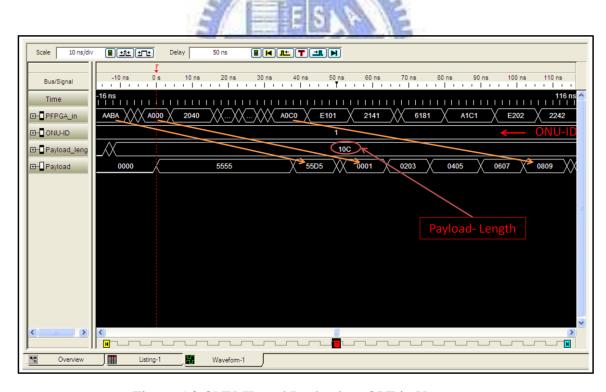

| Figure 5.7  | Input Data on OLT in Upstream                | 48 |

| Figure 5.8  | ONU-ID and Payload on OLT in Upstream        | 48 |

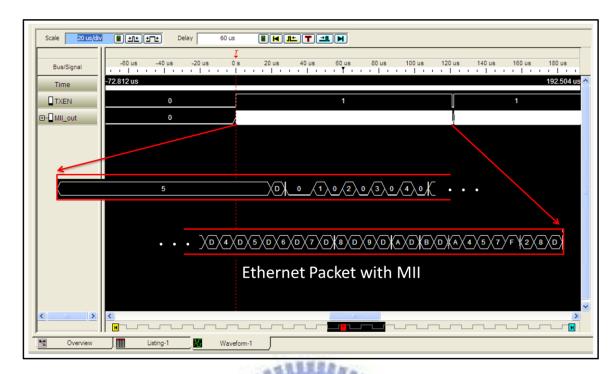

| Figure 5.9  | Output Packet on OLT in Upstream             | 49 |

| Figure 5.10 | Locations of Gathering Data in Upstream      | 49 |

| Figure 5.11 | Inputs of FPGA on OLT                        |    |

| Figure 5.12 | Packets of Downstream                        | 51 |

| Figure 5.13 | Packets of Downstream on Fiber               | 51 |

| Figure 5.14 | Input Data of FPGA on ONU                    | 52 |

| Figure 5.15 | Output Packet on ONU in Downstream           | 53 |

| Figure 5.16 | Locations of Gathering Data in Downstream    | 53 |

| Figure 5.17 | Testing Architecture by SmartBits            | 54 |

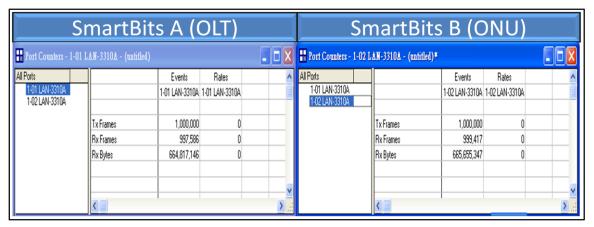

| Figure 5.18 | Results with Transmitting 1,000,000 packets  | 55 |

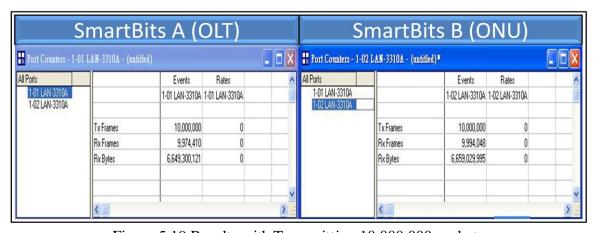

| Figure 5.19 | Results with Transmitting 10,000,000 packets | 55 |

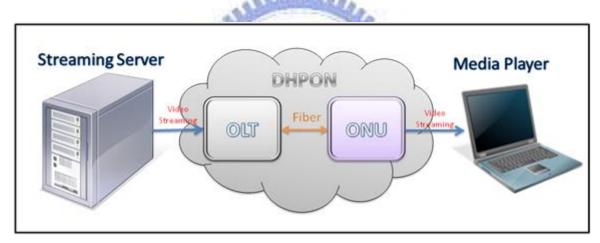

| Figure 5.20 | DHPON with VLC                               | 56 |

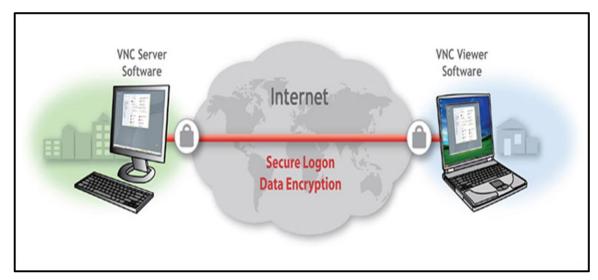

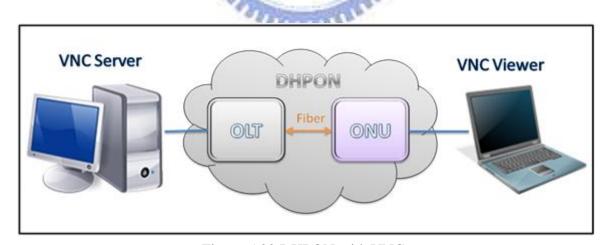

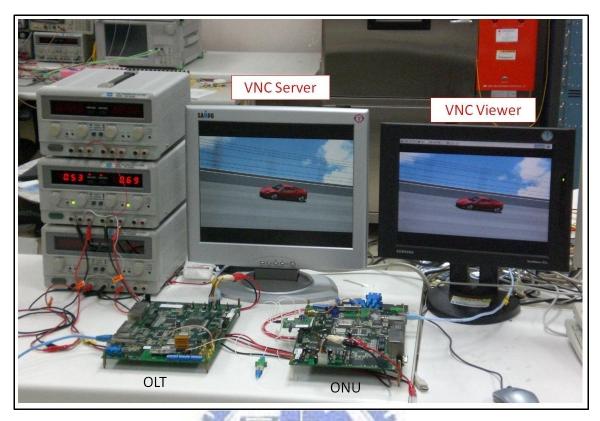

| Figure 5.21 | VNC System                                   | 57 |

| Figure 5.22 | DHPON with VNC                               | 57 |

| Figure 5.23 | Testing Results by VNC | 58 |

|-------------|------------------------|----|

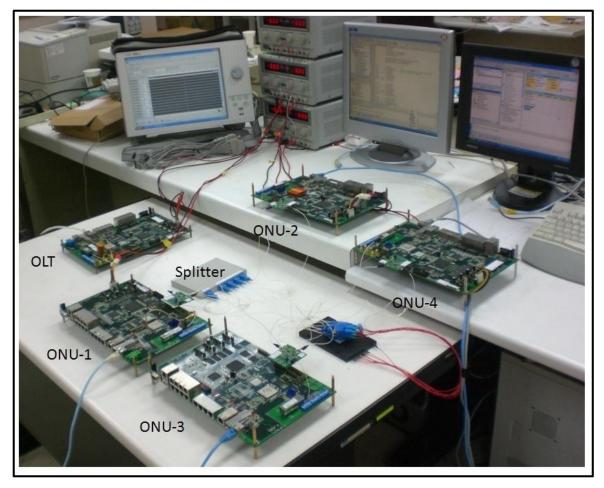

| Figure 6.1  | DHPON System           | 59 |

# LIST OF TABLES

| Table 1.1 | Bandwidth of per User    | 2  |

|-----------|--------------------------|----|

| Table 2.1 | Comparison of TDM-PON    | 9  |

| Table 4.1 | Virtex-4 LX60 Data Sheet | 36 |

#### CHAPTER 1

#### Introduction

There are several technologies of broadband access network: digital subscriber line (DSL), coaxial cable (Cable), passive optical network (PON), and wireless. In recent years, the access network technology is DSL, it includes asymmetric digital subscriber line (ADSL) and very high data rate DSL (VDSL).

The ADSL can operate in parallel with conventional analogue voice telephony over the same line. Asymmetric means that a higher speed is available from the exchange to the user (downstream) and a slower speed from the user to the exchange (upstream). Capability varies with distance - up to 8 Mbps downstream can be supported up to 2 km and 2 Mbps up to 5 km. 64 kbps is the usual speed in upstream. Then, VDSL is a new technology; it is expected to provide speed as high as 52 Mbps in downstream, but over shorter distances than ADSL - 20 Mbps in 1 km and 52 Mps in 0.3 km, and between 1.5 and 2.3 Mbps upstream [1].

In the meantime, at the user end, the drastic improvement of the performance of digital electronics and the computers has made possible expanding multimedia services such as video on demand, videoconferencing, high definition TV (HD-TV), e-learning, interactive games, voice over IP (VoIP), and others. The bandwidth of DSL cannot satisfy users. PON is considered an ultimate solution to meet higher bandwidth requirements in access network.

PON is a single, shared optical fiber that uses inexpensive optical splitters to divide the single fiber into separate strands feeding individual subscribers. PON is called "passive"

because, other than at the central office (CO) and subscriber endpoints, there are no active electronics within the access network.

The main advantage of PON is that it requires less wiring than point to point, that it mutualisms the service for several subscribers, and that it has no active element beyond the central exchange, in other words, only optical fibers and optical passive elements do not require any electrical power or active management. In addition, the lifetime of the outside passive plant should be greater than 25 years to justify the installation costs and maximize the savings in operational expenses.

There are several standard of PON to provide access network: APON (ATM PON), BPON (Broadband PON), GPON (gigabit PON), and EPON (Ethernet PON). BPON can provide 622Mbps in downstream to support 32 users, GPON can provide 2.488Gbps in downstream to support 64 users, and EPON can provide 1Gbps in downstream to support 16 users [2]. The bandwidth of per user of these competing technologies is shown as Table 1.1.

| Service | Users | Bandwidth/User | Range |

|---------|-------|----------------|-------|

| ADSL    | 1     | 2 Mb/s         | 5 Km  |

| VDSL    | 1     | 20 Mb/s        | 1 Km  |

| BPON    | 32    | 20 Mb/s        | 20 Km |

| GPON    | 64    | 40 Mb/s        | 20 Km |

| EPON    | 16    | 60 Mb/s        | 20 Km |

Table 1.1. Bandwidth of per User

Although there is high bandwidth in PON, it is a fatal disadvantage, which is that round trip time (RTT) is too long. It causes the data packet information doesn't update immediately, that induces data packet delay and the waste of bandwidth, so we provide a new network structure: Distributed Control Hybrid Passive Optical Network to solve the problem. I will introduce in detail in the chapter 2.

#### **CHAPTER 2**

#### Conventional and Novel Architecture of PON

I will introduce several types of HTTx and technologies about PON in this chapter.

#### 2.1 Passive Optical Network Overview

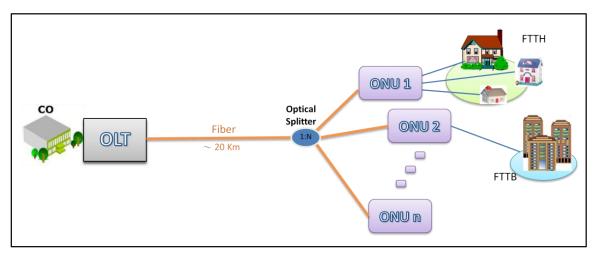

The architecture of Passive Optical Network is shown as Fig.2.1.

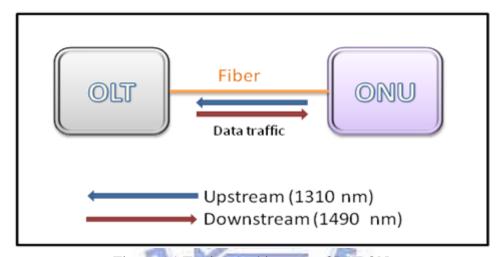

As Fig.2.1 show, passive optical network (PON) is a kind of tree topology. Optical Line Terminal (OLT) is the main element of the network, and it is usually placed in the local exchange. Optical Network Unit (ONU) serves as an interface to the network, and it is deployed on a customers' side. ONU connects to OLT by means of optical fiber, and there is no active element in PON. PON is a kind of a Point-to-Multiple-Points technology. A single OLT can serve several ONUs. An ONU can serve as a point of access for many customers, and be deployed at customers' houses (Fiber to the Home, FTTH), in buildings (Fiber to the Building, HTTB), or on the streets (Fiber to the Curb, HTTC) [3].

The data are sent to each ONU through the splitter by OLT. In downstream, although the structure and power are the same, the data signals are attenuated. In upstream, the data signals are from each ONU to OLT, the direction and condition are opposite to those of downstream. The data signals from each ONU at different time and arrive at the input of the splitter. After all data signals from each ONU traverse through the splitter, they are combined with each other. Then the mixture of all data signals is received by OLT. To avoid the interference of data from each ONU in upstream, we apply Time Division Multiple Access (TDMA) method or Wavelength Division Multiple (WDM) method.

Figure 2.1 The Architecture of Passive Optical Network

#### 2.2 Time Division Multiplexed PON

FTTX has been a long-cherished goal for carriers. The Time Division Multiplexed Passive Optical Network (TDM-PON) architecture as we know it today an economical method of sharing a single fiber and central office (CO) transceiver among many customers-was conceived in the late 1980s, when FTTX concepts were first developed.

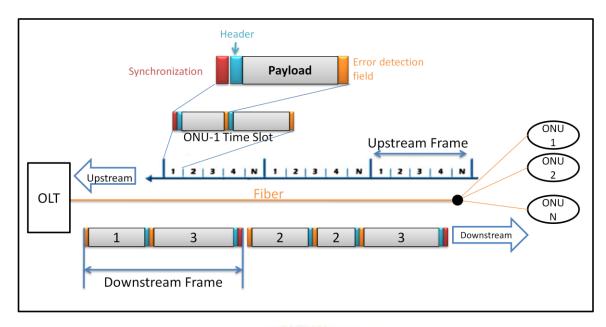

The architecture of TDM-PON is shown as Fig 2.2. The main concept behind the TDM approach is to use a single high-performance shared transceiver at the central office to communicate with the "n" remote ONU transceivers. This approach requires the use of a 1 x n optical splitter to divide the optical power equally between the multiple ONUs. Since each remote ONU uses the same upstream wavelength, they must all take turns using dedicated and variable time slots where only a single ONU is allowed to transmit. A relatively complex processor located at the OLT controls the management and assignment of these individual transmission time slots. In the downstream direction a single data wavelength is used to broadcast to all the users. The ONUs identify their specific data packets by address information located in the header bit streams.

This traditional single-wavelength PONs combine the high capacity provided by optical fiber with the low installation and maintenance cost of a passive infrastructure. The optical carrier is shared by means of a passive splitter among all the subscribers. As a consequence, the number of ONUs is limited because of the splitter attenuation and the working bit rate of the transceivers in the central office (CO) and in the ONUs. Current specifications allow for 32 ONUs at a maximum distance of 20 km from the OLT and 64 ONUs at a maximum distance of 10 km from the OLT.

Figure 2.2 The Architecture of TDM-PON

TDM-PON has been developed for a long time such as ATM-PON (A-PON), Broadband-PON (B-PON), Gigabit-PON (G-PON), and Ethernet-PON (E-PON).

#### 2.2.1 Broadband PON

The broadband PON (BPON) was first introduced, and it was accepted in 1996 by International Telecommunications Union (ITU). The standard was endorsed by a number of network providers and equipment vendors which cooperated together in the Full Service Network Access (FSAN) group. The FSAN group proposed the Asynchronous Transfer Mode (ATM) protocol should be used to carry users' data, and sometimes access

networks based on this standard are referred to as APONs.

The architecture of BPON is flexible and adapts well to different scenarios. The underlying ATM protocol provides support for different types of service by means of adaptation layers. The small size of ATM cells and the use of virtual channels and links allow allocating available bandwidth to the end users with a fine granularity. Moreover, the deployment of ATM in a backbone of metropolitan networks and easy mapping into SDH/SONET containers allows the use of only one protocol from one end user to another.

Yet, the advantages of ATM proved to be the main obstacle in deployment of BPON and despite many field trails BPON did not gain much popularity. The complexity of the ATM protocol was hard to implement and in many cases superfluous. Much simpler, data only oriented Ethernet protocols found a widespread use in local area networks and started to replace ATM in many metropolitan area and backbone networks [4].

#### 2.2.2 Gigabit PON

In May, 2001, almost at the same time as EDMA presenting the concept of EPON, FSAN organization also started to set the standard of GPON, the object is not only operating at higher speed (up to 2.4GB/s) but also there is much higher efficiency than other PON in multi-work, operation, administration, maintenance and provisioning, (OAM&P), and expander. Finally at the beginning of 2003, ITU-T approved the standard of GPON in G984.1, G984.2, and G984.3. According to the standard, GPON can provide the bandwidth for 1.244 Gb/s in upstream and 2.488 Gb/s in downstream. The distance of transmission covers at least 20 km, which is three times longer than 6km of ADSL. However as a whole, GPON is better than BPON and EPON in video, voice, and data.

Although GPON is high performance in transmission, GPON is too expensive to use widespread.

#### 2.2.3 Ethernet PON

At the beginning of 2001,IEEE set up 802.3 Ethernet in the First Mile to develop Ethernet network standard. EPON is the technology combine Ethernet with PON, it use standard format to load IP work without conversion, ONU can collect to a simple facility without adding extra exchange function. At the same time EPON doesn't require the expensive and complicated ATM and SONET, in order to simplify the network and share users with low-cost distribution of the bandwidth. Therefore, EPON is cheaper, wider bandwidth, and stronger in service than BPON and GPON.

EPON still use broadcasting method in downstream, by OLT sending Ethernet packet to ONT, every packet would record the address of destination, after receiving packet, ONU access packet of their own and throw others way; upstream is still in TDMA method, controlling slot signal is sent by OLT, the signal control ONUs packet of upstream in order. The length of EPON's upstream and downstream formats are both 2 ms, it is shown as Fig. 2.3, upstream format consists of a Header and many variable-length slots, every ONT has a corresponding slot, it contains the packet sending to OLT, some information about slots, and control bit. If ONU didn't send the data to slot which is allocated, it must be to fill the empty slot bytes, avoiding conflict at the compound. The downstream format also consists of many variable-length slots, in each slot in a byte contains the synchronization message signs, let ONU and OLT make a every 2 ms synchronal sending. EPON can provide 1Gb/s both in upstream and downstream [5]. Table 2.1 compares tree standardized TDM-PON: BPON, GPON, and EPON.

Figure 2.3 Upstream and Downstream Formats of EPON

| A. C. |           |            |              |

|-------------------------------------------|-----------|------------|--------------|

|                                           | BPON      | GPON       | EPON         |

| Stranded                                  | ITU G.983 | ITU G.984  | IEEE 802.3ah |

| Framing                                   | ATM       | GEM/ATM    | Ethernet     |

| Max Bandwidth                             | 622 Mb/s  | 2.488 Gb/s | 1 Gb/s       |

| Users/PON                                 | 32        | 64         | 16           |

| Avg. Bandwidth/User                       | 20Mb/s    | 40Mb/s     | 60Mb/s       |

| Video                                     | RF        | RF/IP      | RF/IP        |

| Estimated Cost                            | Medium    | high       | Low          |

Table 2.1 Comparison of TDM-PON

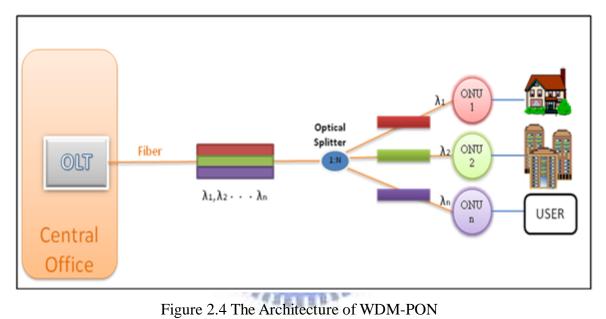

#### 2.3 Wavelength Division Multiplexed PON

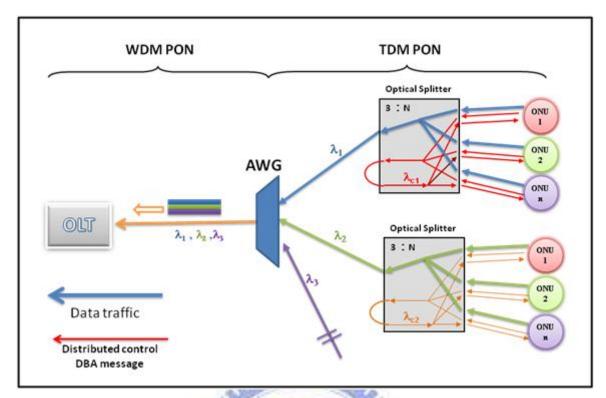

The architecture of WDM-PON is shown as Fig. 2.4. The straightforward approach to build a WDM-PON is to reserve a separate wavelength channel from the OLT to each

ONU, for each upstream and downstream direction. In other word, each ONU gets a dedicated point-to-point optical channel to the OLT, so data collision will not happen when OUNs send out data simultaneously. In downstream, the specific wavelength channel is divided to specific ONU by a passive arrayed wavelength grating (AWG). In upstream, the function of AWG is like an optical filter. Because there is a specific wavelength for each OUN, which cannot be shared, so the cost of WDM-PON is very expensive [6].

#### 2.4 **Centralized Control Dynamic Bandwidth Allocation**

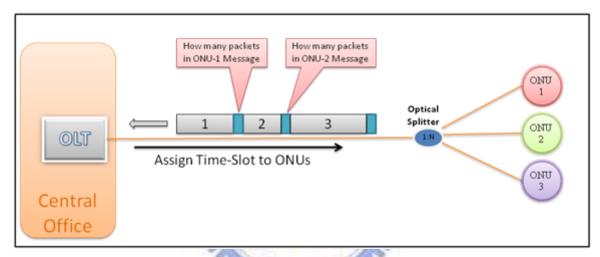

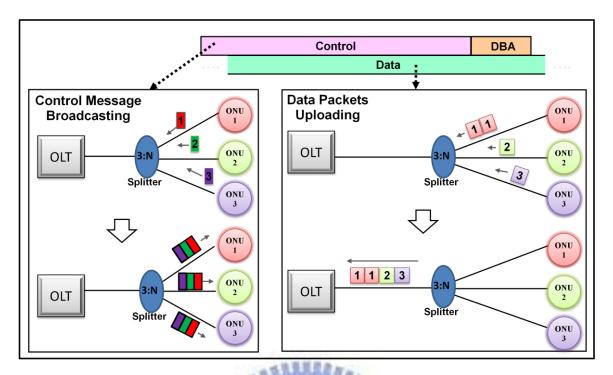

The centralized control Dynamic Bandwidth Allocation (DBA) is shown as Fig. 2.5. the 'centralized' means that DBA control signal is sent form ONUs to OLT with the same wavelength as the one of data channel. ONUs send the buffer information to the OLT, then the OLT send the acknowledgement character signal to each ONU, after OLT receive the the buffer information. The prevailing method of centralized control DBA scheme is Interleaved Polling with Adaptive Cycle Time (IPACT) [7].

#### 2.4.1 Interleaved Polling with Adaptive Cycle Time (IPACT)

In an IPACT scheme. ONU will send a message at the end of its data packets. The message is about that how many packets in its buffer want be sent at next time. As Fig. 2.5, the ONU that is scheduled next (say, in round-robin fashion) will monitor the transmission of the previous ONU and will time its transmission such that it arrives to the OLT right after the transmission from the previous ONU. Thus, theoretically, there will be no data collision and no bandwidth will be wasted [8].

Figure 2.5 Concept of Centralized-Control DBA

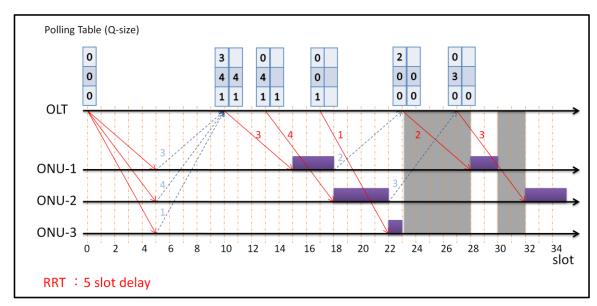

For example as Fig. 2.6, we suppose that there are three ONUs and round trip time (RTT) of each ONU is 5 slot time. At first, there is not packet in each ONU, in other words, the queue size (Q-size) of packet of each ONU is zero. The OLT ask each ONU that how many packets be stored in the buffer. Then each ONU send an abbreviation to OLT, the abbreviation is a message with Q-size of packet in the buffer. After OLT receiver the message of each ONU, it will assign the slot of transmission to each ONU. After ONU finish the data transmission, it send the new Q-size of packet to OLT. As Fig. 2.6, the shadow means the slots be not used, so the bandwidth will be waste. This is a disadvantage of IPACT.

Figure 2.6 Example of IPACT

#### 2.4.2 Round Trip Time

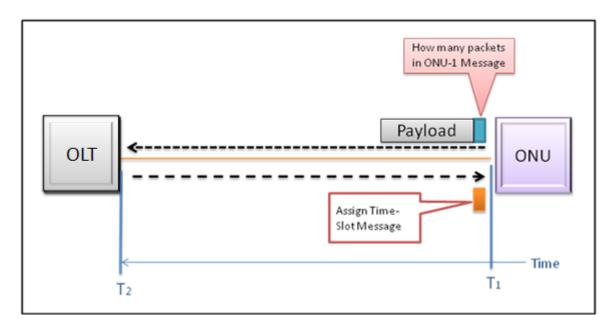

RTT is the key point of the PON structure, it means the required time for a signal from ONU to OLT. The calculation of RTT is shown as the Fig. 2.7. In the illustration, the signal is from ONU at T1, and the signal arrive OLT at T2, then the RTT is 2\*(T2-T1). The distance from OLT to ONU is usually larger than 20 kilometers, which is very far, so RTT would be long in result (usually about 0.2 ms). If RTT is long, the DBA Q-size signal will not be updated immediately and the packet of data packet will be delay. The situation is not good to DBA. It makes real- time data, such as online games and videoconferencing, lagged. This is the main shortcoming of centralized control DBA. Based on the problem, we provide a novel architecture of DBA, Distributed Control Dynamic Bandwidth Allocation, to reduce RTT. We hope the method will improve centralized control DBA.

Figure 2.7 Round Trip Time of Centralized Control DBA

STREET,

#### 2.5 Distributed Control Dynamic Bandwidth Allocation

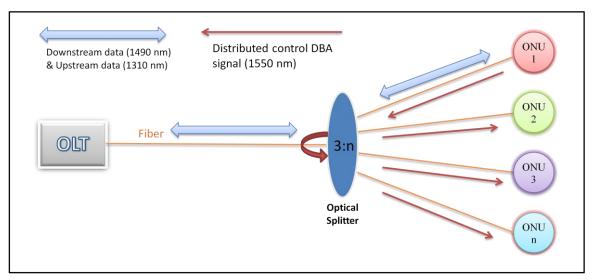

The architecture of distributed control DBA is shown as Fig. 2.8. Distributed control DBA means DBA control message isn't transmitted to OLT. In this method, DBA control message is transmitted to the splitter by each ONU with 1550nm- wavelength and goes back to each ONU directly, then DBA control signal of all ONUs could be received by each ONU. After gathering DBA control message of all ONUs, each ONU will determine to transmit the data or not by itself. Because the distance between ONU and the splitter (about 1 Km) is shorter than that between ONU and OLT, it will shorten RTT (about 0.01 ms) dramatically.

The main advantage of Distributed control DBA is that the DBA control signal will be updated immediately and the packet of data will not be delayed. The technology makes real-time data not lagged. It could be applied to online games and videoconferencing, and makes displays smooth.

Figure 2.8 The Architecture Distributed Control DBA

#### 2.6 Distributed Control Hybrid Passive Optical Network