# 國立交通大學

## 資訊科學與工程研究所

### 碩士論文

Design and Implementation of Power-Efficient Reconfigurable Fixed-Width Multipliers

研 究 生:涂晉豪

指導教授:范倫達 博士

#### 中華民國九十七年七月

#### 低功耗可重組固定寬度乘法器之設計與實作

#### Design and Implementation of Power-Efficient Reconfigurable

#### Fixed-Width Multipliers

研究生:涂晉豪 Student: Jin-Hao Tu

指導教授:范倫達博士 Advisor: Dr. Lan-Da Van

國 立 交 通 大 學 資訊科學與工程研究所 碩 士 論 文

Submitted to Institute of Computer Science and Engineering

A Thesis

College of Computer Science

National Chiao Tung University

in partial Fulfillment of the Requirements

for the Degree of

Master

in

**Computer Science**

July 2008

Hsinchu, Taiwan, Republic of China

中華民國九十七年七月

#### 低功耗可重組固定寬度乘法器之設計與實作

學生:涂晉豪

指導教授:范倫達 博士

國立交通大學 資訊科學與工程研究所

#### 摘 要

在本論文中,我們提出了具有四種運算模式的可重組固定寬度 Booth 乘法器 以及可重組固定寬度 Baugh-Wooley 乘法器。此四種運算模式提供了高精準度運 算、平行運算、全精準度運算等特性,可因應多種不同的運算需求。根據模擬結 果,對於一個 16x16 可重組固定寬度 Booth 乘法器,平均四種運算模式的功率消 耗可比 16x16 非重組固定寬度 Booth 乘法器節省 14.0%的功率消耗。而 16x16 可重 組固定寬度 Baugh-Wooley 乘法器亦可節省 12.56%的功率消耗。另外我們將可重組 固定寬度乘法器應用於 FIR 濾波器中,藉此說明可重組固定寬度乘法器具有功率 調節的能力,進而達到省電的目的。

## Design and Implementation of Power-Efficient Reconfigurable Fixed-Width Multipliers

Student : Jin-Hao Tu

Advisor : Dr. Lan-Da Van

Institute of Computer Science and Engineering College of Computer Science National Chiao Tung University

#### ABSTRACT

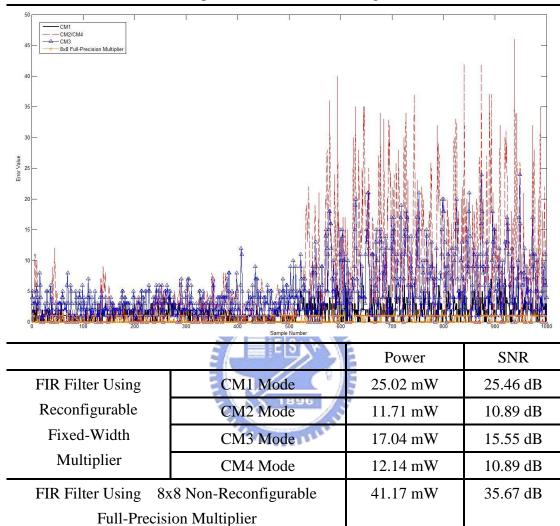

Willies.

In this thesis, we propose a reconfigurable fixed-width Booth multiplier and a reconfigurable fixed-width Baugh-Wooley multiplier design framework that provides four configuration modes (CMs). The presented four configuration modes of the reconfigurable fixed-width multiplier are capable of providing high resolution, parallel, and full-precision multiplications for different computation demands. From the simulation results, the proposed 16x16 reconfigurable fixed-width Booth multiplier can attain the power saving of 14.0% on average with respect to that of the 16x16 non-reconfigurable fixed-width Booth multiplier. On the other hand, the proposed 16x16 reconfigurable fixed-width Baugh-Wooley multiplier can save 12.56% power consumption on average in comparison with that of the 16x16 non-reconfigurable fixed-width Baugh-Wooley multiplier. Furthermore, we apply the proposed reconfigurable multiplier to FIR filter to show the power scalable capability under four different modes.

誌 謝

首先感謝指導教授 范倫達老師在這兩年多以來的悉心指導與建議,並提供我 各方面的協助,使我可以確立並完成我的論文研究。此外,亦要感謝王旭昇學長 無私地提供協助,讓我的研究得以順利地進行下去。其次是感謝 VIPLab 實驗室的 夥伴們,感謝你們在我的研究生生活中所帶來的溫馨與歡笑。

最後要感謝家人和親友們的關心、支持與鼓勵,尤其是親愛的爸爸媽媽,你 們讓我可以無後顧之憂的完成學業。再次感謝以上所有幫助過我的人,謹以此文 獻給你們。

# Contents

| 摘 要 I                                   |

|-----------------------------------------|

| ABSTRACT II                             |

| 誌 謝Ш                                    |

| CONTENTS                                |

| LIST OF TABLES                          |

| LIST OF FIGURES                         |

| Chapter 1 Introduction1                 |

| 1.1 Motivation                          |

| 1.2 Thesis Organization                 |

| Chapter 2 Fundemental Concepts          |

| 2.1 Array Multipliers4                  |

| 2.1.1 Booth Multiplier                  |

| 2.1.2 Baugh-Wooley Multliplier7         |

| 2.2 Subword Multiplication              |

| 2.3 Low-Error Fixed-Width Multipliers10 |

| Chapter 3 Design of Reconfigurable Fixed-width Multipliers              |

|-------------------------------------------------------------------------|

| 3.1 Reconfigurable Fixed-Width Booth Multiplier13                       |

| 3.1.1 CM1: <i>nxn</i> Fixed-Width Multiplier14                          |

| 3.1.2 CM2: Two $n/2xn/2$ Fixed-Width Multipliers                        |

| 3.1.3 CM3: <i>n</i> /2x <i>n</i> /2 Full-Precision Multiplier <b>19</b> |

| 3.1.4 CM4: Sum of Two $n/2xn/2$ Fixed-Width Multipliers                 |

| 3.1.5 Proposed Structure                                                |

| 3.2 Reconfigurable Fixed-Width Baugh-Wooley Multiplier                  |

| 3.2.1 CM1: <i>nxn</i> Fixed-Width Multiplier28                          |

| 3.2.2 CM2: Two $n/2xn/2$ Fixed-Width Multipliers                        |

| 3.2.3 CM3: <i>n</i> /2x <i>n</i> /2 Full-Precision Multiplier           |

| 3.2.4 CM4: Two <i>n</i> /4x <i>n</i> /4 Full-Precision Multipliers      |

| 3.2.5 Proposed Structure 34                                             |

| Chapter 4 Implenmentation and Comparison                                |

| 4.1 Simulation Results of Reconfigurable Fixed-Width Multiplier         |

| 4.1.1 Reconfigurable Fixed-Width Booth Multiplier                       |

| 4.1.2 Reconfigurable Fixed-Width Baugh-Wooley Multiplier                |

| 4.2 Application of Reconfigurable Fixed-Width Multiplier                |

| Chapter 5 Conclusion and Future Work                                    |

| Bibliography                                                            |

| Biography                                                               |

# **List of Tables**

| Chapte | r 2                                                                         |

|--------|-----------------------------------------------------------------------------|

| 2.1:   | Modified Booth recoding table                                               |

| Chapte | r 3                                                                         |

| 3.1:   | Proposed four configuration modes of the reconfigurable fixed-width Booth   |

|        | multiplier14                                                                |

| 3.2:   | Truth table of the decoder for the reconfigurable fixed-width Booth         |

|        | multiplier                                                                  |

| 3.3:   | Truth table of sub-calibration-circuit1 (SCC1) and sub-calibration-circuit2 |

|        | (SCC2)                                                                      |

| 3.4:   | Proposed four configuration modes of the reconfigurable fixed-width         |

|        | Baugh-Wooley multiplier                                                     |

| 3.5:   | Truth table of the decoder for the reconfigurable fixed-width Baugh-Wooley  |

|        | multiplier                                                                  |

| Chapte | r 4                                                                         |

- 4.1: Qualitative comparison between different reconfigurable architectures ...... 45

|      | multipliers and the 16x16 non-reconfigurable fixed-width Booth multipliers |

|------|----------------------------------------------------------------------------|

| 4.3: | Chip Characteristics of the 16x16 reconfigurable fixed-width Booth         |

# **List of Figures**

#### Chapter 2

| 2.1: | Block diagram of Booth recoding circuit                                           |  |  |  |

|------|-----------------------------------------------------------------------------------|--|--|--|

| 2.2: | Modified Booth partial-product diagram with sign-generate sign extension          |  |  |  |

|      | scheme for an <i>n</i> x <i>n</i> multiplier <b>7</b>                             |  |  |  |

| 2.3: | Partial-product array diagram for an <i>n</i> x <i>n</i> Baugh-Wooley multiplier  |  |  |  |

| 2.4: | Subword multiplication (a) two $n/2xn/2$ multiplications, (b) two $n/2xn/2$       |  |  |  |

|      | partial-product array distribution, (c) four $n/4xn/4$ multiplications, and (d)   |  |  |  |

|      | four $n/4xn/4$ partial-product array distribution                                 |  |  |  |

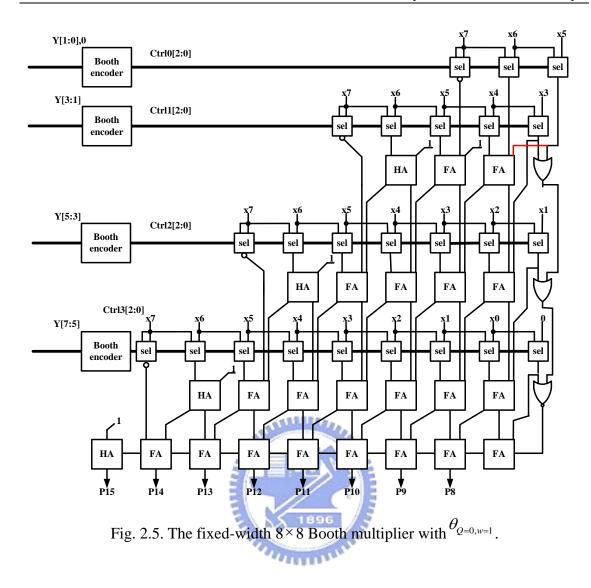

| 2.5: | The fixed-width 8×8 Booth multiplier with $\theta_{Q=0,w=1}$                      |  |  |  |

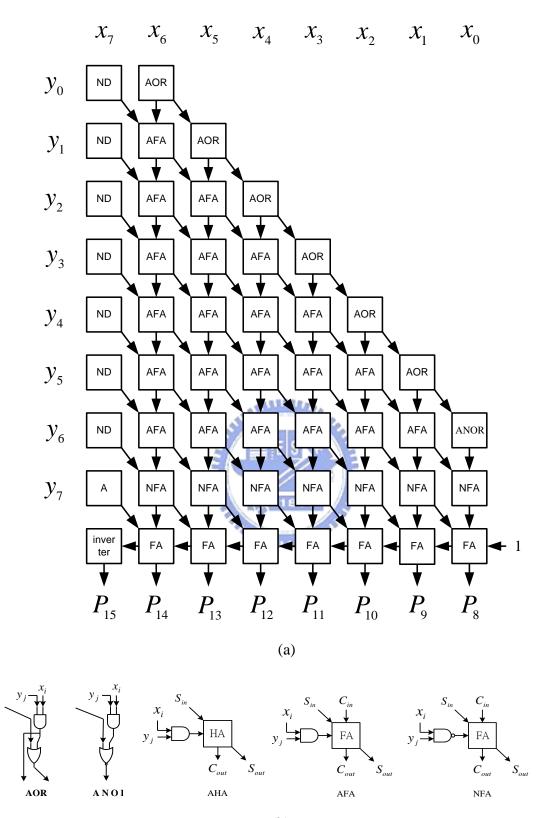

| 2.6: | (a) The fixed-width 8×8 Baugh-Wooley multiplier with $\theta_{Q=0,w=1}$ , and (b) |  |  |  |

|      | logic diagrams of AOR, ANOR, AHA, AFA, NFA12                                      |  |  |  |

|      |                                                                                   |  |  |  |

### Chapter 3

|      | multiplier involving MUL1, MUL2, and discarding truncated region of LSP |

|------|-------------------------------------------------------------------------|

| 3.1: | Prototype structure of the proposed reconfigurable fixed-width Booth    |

| 3.3:                                                | Subword operation for two $n/2xn/2$ fixed-width multiplications                                                                                                |

|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.4:                                                | (a) Partial-product array diagram for two $n/2xn/2$ fixed-width multipliers                                                                                    |

|                                                     | with $n=8$ , (b) configuration settings of S <sub>2,4</sub> and S <sub>3,4</sub> , (c) configuration                                                           |

|                                                     | parameter settings, and (d) configured Booth recoding circuit18                                                                                                |

| 3.5:                                                | Subword operation for one $n/2xn/2$ full-precision multiplication                                                                                              |

| 3.6:                                                | (a) Partial-product array diagram for $n/2xn/2$ full-precision multiplier with                                                                                 |

|                                                     | n=8, (b) configuration settings of S <sub>2,4</sub> and S <sub>3,4</sub> , (c) configuration parameter                                                         |

|                                                     | settings, and (d) configured Booth recoding circuit                                                                                                            |

| 3.7:                                                | Partial-product array diagram for sum of two $n/2xn/2$ fixed-width multipliers                                                                                 |

|                                                     | with <i>n</i> =8                                                                                                                                               |

| 3.8:                                                | Overall structure of the proposed reconfigured fixed-width Booth multiplier                                                                                    |

|                                                     | for <i>n</i> =8                                                                                                                                                |

|                                                     |                                                                                                                                                                |

| 3.9:                                                | Logical diagram of SCC1 and SCC2.26                                                                                                                            |

| 3.9:<br>3.10:                                       | The second s                                                 |

|                                                     | The state                                                                                                                                                      |

|                                                     | Prototype structure of the proposed reconfigurable fixed-width                                                                                                 |

|                                                     | Prototype structure of the proposed reconfigurable fixed-width<br>Baugh-Wooley multiplier involving MUL1, MUL2, MUL3 and discarding<br>truncated region of LSP |

| 3.10:                                               | Prototype structure of the proposed reconfigurable fixed-width<br>Baugh-Wooley multiplier involving MUL1, MUL2, MUL3 and discarding<br>truncated region of LSP |

| 3.10:                                               | Prototype structure of the proposed reconfigurable fixed-width<br>Baugh-Wooley multiplier involving MUL1, MUL2, MUL3 and discarding<br>truncated region of LSP |

| 3.10:                                               | Prototype structure of the proposed reconfigurable fixed-width<br>Baugh-Wooley multiplier involving MUL1, MUL2, MUL3 and discarding<br>truncated region of LSP |

| 3.10:                                               | Prototype structure of the proposed reconfigurable fixed-width<br>Baugh-Wooley multiplier involving MUL1, MUL2, MUL3 and discarding<br>truncated region of LSP |

| <ul><li>3.10:</li><li>3.11:</li><li>3.12:</li></ul> | Prototype structure of the proposed reconfigurable fixed-width<br>Baugh-Wooley multiplier involving MUL1, MUL2, MUL3 and discarding<br>truncated region of LSP |

|         | parameter settings                                                        | 32 |

|---------|---------------------------------------------------------------------------|----|

| 3.15:   | Subword operation for two $n/4xn/4$ full-precision multiplications        | 33 |

| 3.16:   | (a) Proposed partial-product array diagram for CM4, and (b) configuration | n  |

|         | parameter settings                                                        | 33 |

| 3.17:   | Proposed pipelined reconfigurable multiplier                              | 36 |

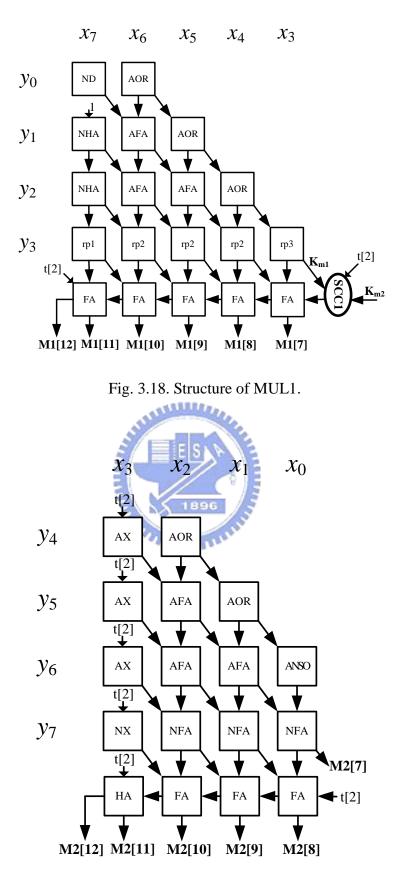

| 3.18:   | Structure of MUL1                                                         | 37 |

| 3.19:   | Structure of MUL2                                                         | 37 |

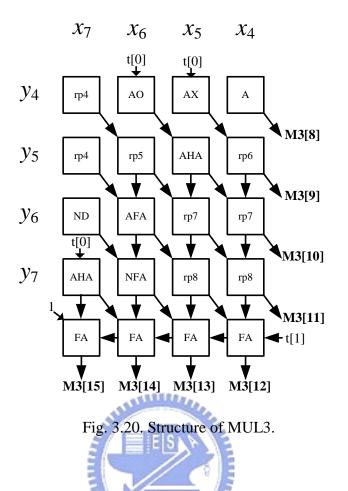

| 3.20:   | Structure of MUL3                                                         | 38 |

| 3.21:   | Logic diagrams of the other processing elements                           | 39 |

| 3.22:   | Proposed power-efficient pipelined reconfigurable fixed-width             |    |

|         | Baugh-Wooley multiplier                                                   | 42 |

| Chapter | r 4                                                                       |    |

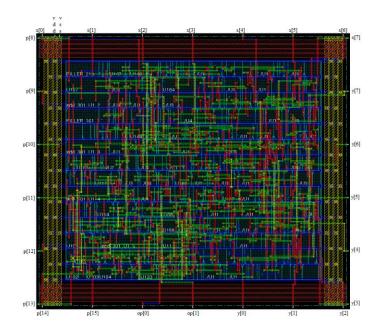

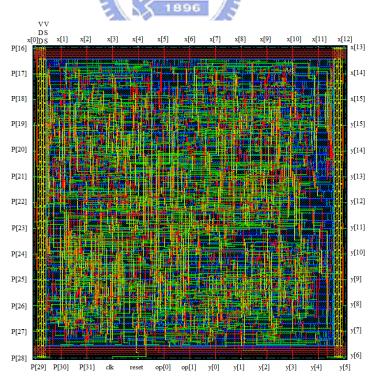

| 4.1:    | Proposed reconfigurable fixed-width Booth multiplier layout for $n=8$     | 47 |

| 4.2:    | Proposed pipelined reconfigurable fixed-width Baugh-Wooley multiplier     |    |

|         | layout for <i>n</i> =16                                                   | 49 |

# Chapter 1

## Introduction

During the past decade, the multipliers [1-32] in VLSI signal processing systems stand the test for multimedia-communication applications. Among these multipliers, the basic multiplication either follows Booth [1-3] or Baugh-Wooley algorithms [4]. In many digital signal processing (DSP) algorithms such as digital filters, discrete cosine transform (DCT), and wavelet transform, it is desirable to provide full-precision multiplication [5-8], and fixed-width multiplication [9-20] that produces *n*-bit output product with *n*-bit multiplier and *n*-bit multiplicand with low truncation error. A fixed-width multiplier (also referred to as single precision multiplier) with area and power saving can be achieved either by directly truncating n least significant columns and preserving n most significant columns or by other efficient methods [9-20]. By the former method, significant truncation errors will be introduced since no error compensation is considered. Thus, the latter schemes explore issues on low truncation error and small area. Lim [9] first utilized statistical techniques to estimate and simulate the error-compensation bias. However, in his analysis, the reduction and rounding errors are separately treated such that this scheme does not lead to an accurate enough error-compensation bias. Note that the sum of the reduction and rounding errors equals truncation error [10]. In [10-11], the presented work improved the the error-compensation bias to be more accurate and practical since the reduction and rounding errors are concurrently treated. Later, in [12-20], many researchers analyzed

an adaptive error-compensation bias under keeping n+w most significant columns and proposed various fixed-width multipliers. On the other hand, much work, recently, focuses on constructing reconfigurable full-precision multipliers [21-31]. In [21-26], one reconfigurable full-precision multiplier has been proposed by the subword partitioning technique, where one nxn, two n/2xn/2, or four n/4xn/4 full-precision multiplications can be performed. In [27-29], a reconfigurable full-precision multiplier consists of an array of 4x4 or 8x8 small multipliers, where the multiplier introduced in [28] has more configuration modes than that of [27, 29]. The complicated reconfigurable architecture can provide multiple 4x4, 8x8, 16x16, 32x32, and 64x64 operations and support unsigned, signed and 2's-complement multiplications. Nevertheless, the architecture [28] led to larger hardware area. The low-power multiplier designs are debated in [30-32]. In [30], a 2-D pipeline gating technique is employed to design a power-aware array multiplier that is adaptive to the high or low resolution operations. In [31], the power cut-off technique is employed to reduce power consumption when lower resolution multiplication is demanded. In [32], a Baugh-Wooley multiplier made use of the dynamic range detection unit and truncated multiplication technique to save power consumption. Nevertheless, the proposed multiplier provided only truncated output precisions under nxn truncated multiplication and didn't discuss how to generate the full-precision multipliers and other fixed-width type multiplier.

#### **1.1 Motivation**

As growing demands on portable computing and communication systems, the power-efficient multiplier plays an important role in very large-scale integration (VLSI) systems. As we know that the conventional reconfigurable multiplier designs [21-31] are based on the full-precision multiplier infrastructure to generate the full-precision multipliers. However, it can be seen that the full-precision multiplier is much more cost ineffective and

power-inefficient than the fixed-width multipliers [19-20]. The fixed-width multiplier and the reconfigurable multiplier are two feasible approaches for the design of power-efficient multipliers. To our best knowledge, we are the first one to explore the power-efficient reconfigurable fixed-width multiplier and discuss how to reconfigure the structure to generate a family of useful fixed-width and full-precision multipliers.

#### **1.2 Thesis Organization**

The rest of the paper is organized as follows. The Booth multiplier, Baugh-Wooley multiplier, subword multiplication and low-error fixed-width multiplier are briefly reviewed in Chapter 2. In Chapter 3, the proposed reconfigurable fixed-width multiplication engine with four configuration modes is presented. The comparison results in terms of area size and power saving are presented in Chapter 4. For FIR filter application, the error comparison and power scalable performance using various fixed-width and full-precision multipliers are illustrated in the same chapter. Last, brief statements conclude the presentation of this thesis.

# Chapter 2

### **Fundamental Concepts**

In this chapter, the fundamental concepts will be given, including the introduction to the Booth multiplier, Baugh-Wooley multiplier, subword multiplication, and low-error fixed-width multiplier.

#### **2.1 Array Multipliers**

In this thesis, we will introduce two kinds of reconfigurable fixed-width multipliers.

#### 2.1.1 Booth Multiplier

Considering two 2's-complement integer operands, we can respectively represent an *n*-bit multiplicand X and an *n*-bit multiplier Y as follows.

$$X = -x_{n-1}2^{n-1} + \sum_{i=0}^{n-2} x_i 2^i$$

(1)

$$Y = -y_{n-1}2^{n-1} + \sum_{i=0}^{n-2} y_i 2^i$$

(2)

where  $x_i, y_i \in \{0,1\}$ . The 2*n*-bit full-precision product  $P_{FP}$  can be written as

$$P_{FP} = X \cdot Y \tag{3}$$

If n is even, Y can be rewritten as

$$Y = \sum_{i=0}^{(n-2)/2} y_i' 2^{2i}$$

(4)

where  $y'_i = y_{2i-1} + y_{2i} - 2y_{2i+1}$  and  $y_{-1} = 0$ . The term  $y'_i$  has a value of {-2, -1, 0, 1, 2}. Each recoded value performs a certain operation on the multiplicand *x*; the multiple additions at each stage are required to generate the product. Substituting (4) into (3), we obtain

$$P_{FP} = \sum_{i=0}^{(n-2)/2} y_i' \cdot X \cdot 2^{2i} = \sum_{i=0}^{(n-2)/2} S_i$$

(5)

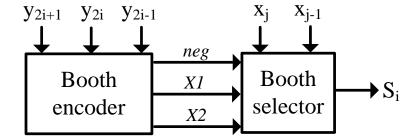

where  $S_i = y'_i \cdot X \cdot 2^{2i}$ . Triplet scanning takes place from  $y_{-1}$  to the most significant bit (MSB) with a one-bit overlap. Table 2.1 lists the recoding rule and Fig. 2.1 shows the block diagram of the Booth recoding circuit. In Fig. 2.1, the Booth encoder generates three Booth recoding bits *neg*, *X1*, and *X2* to the Booth selector and then the Booth selector selects input multiplicand  $\{x_j, x_{j-1}\}$  as output partial products. In order to simplify the representation of each partial product, we define the following notation.

$$S_i = S_{i,n-1} 2^{2i+n-1} + S_{i,n-2} 2^{2i+n-2} + S_{i,n-3} 2^{2i+n-3} + \dots + S_{i,0} 2^{2i}$$

(6)

where  $S_{i,j}$  represents the *j*-th bit product of the *i*-th row. In conventional 2's-complement Booth arithmetic operations, the partial product sign extensions are required for each stage, but these extended sign bits lead to large amount of area and power overhead. The sign *S* of an *n* by *n* multiplier can be expressed as

$$S = (S_{0,n} \sum_{j=n}^{2n-1} 2^j) 2^0 + (S_{1,n} \sum_{j=n}^{2n-3} 2^j) 2^2 + (S_{2,n} \sum_{j=n}^{2n-5} 2^j) 2^4 + \dots + (S_{n/2-1,n} \sum_{j=n}^{n+1} 2^j) 2^{2(n/2-1)}$$

$$=(2^{n+1} + \overline{S_{0,n}} \cdot 2^{n}) + (2^{n+3} + \overline{S_{1,n}} \cdot 2^{n+2}) + (2^{n+5} + \overline{S_{2,n}} \cdot 2^{n+4}) + \dots + (2^{2n-1} + \overline{S_{n/2-1,n}} \cdot 2^{2n-2}) + 2^{n}$$

(7)

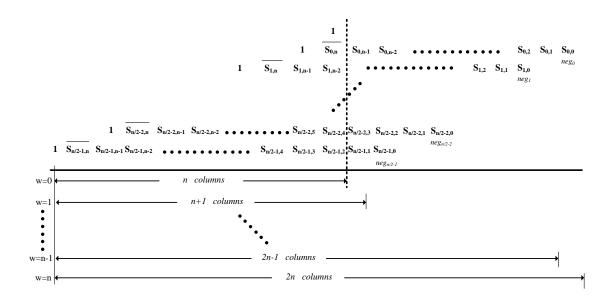

Substituting (6) and (7) into (5), we can obtain the partial-product array diagram for nxnBooth multiplier as depicted in Fig. 2.2, where notation w means to keep n+w most significant columns of the partial products for fixed-width multiplications. If w=n, the fixed-width multiplier becomes a full-precision multiplier. In this thesis, we would like to reconfigure the fixed-width multiplication engine to generate several useful multipliers under the limited hardware resource for DSP and image processing applications.

| <i>Y</i> 2i+1 | Y2i | <i>y</i> 2i-1 | $y'_i$ | neg | X1 | X2 |

|---------------|-----|---------------|--------|-----|----|----|

| 0             | 0   | 0             | EO     | 0   | 0  | 0  |

| 0             | 0   | 1             | X      | 0   | 1  | 0  |

| 0             | 1   | 0             | 189    | 0/  | 1  | 0  |

| 0             | 1   |               | 2      | 0   | 0  | 1  |

| 1             | 0   | 0             | -2     | 1   | 0  | 1  |

| 1             | 0   | 1             | -1     | 1   | 1  | 0  |

| 1             | 1   | 0             | -1     | 1   | 1  | 0  |

| 1             | 1   | 1             | 0      | 0   | 0  | 0  |

Table 2.1: Modified Booth recoding table

Fig. 2.1. Block diagram of Booth recoding circuit.

Fig. 2.2. Modified Booth partial-product diagram with sign-generate sign extension scheme for an  $n \times n$  multiplier.

#### 2.1.2 Baugh-Wooley Multiplier

Considering two 2's-complement integer operands, we can respectively represent an *n*-bit multiplicand *X* and an *n*-bit multiplier *Y* as (1) and (2). The 2*n*-bit full-precision product  $P_{FP}$  can be written as

$$P_{FP} = X \cdot Y$$

$$= x_{n-1}y_{n-1}2^{2n-2} + \sum_{i=0}^{n-2} \sum_{j=0}^{n-2} x_i y_j 2^{i+j}$$

$$+ 2^{n-1}(-2^{n-1} + \sum_{j=0}^{n-2} \overline{x_{n-1}y_j} 2^j + 1)$$

$$+ 2^{n-1}(-2^{n-1} + \sum_{i=0}^{n-2} \overline{y_{n-1}x_i} 2^i + 1)$$

(8)

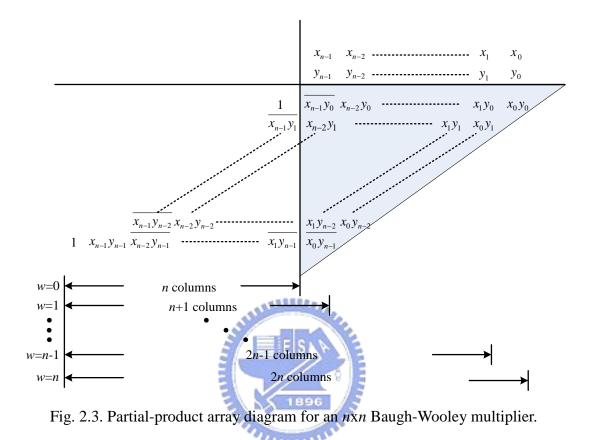

Eq. (8) represents the Baugh-Wooley algorithm [4-6] in which this array multiplier sums partial-product bits corresponding to each weighting. The partial-product array for  $n \ge n \ge n$  2's-complement multiplication are depicted in Fig. 2.3, where notation *w* means to keep n+w most significant columns of the partial products for fixed-width multiplications. If w=n, the fixed-width multiplier becomes a full-precision multiplier.

In this thesis, we would like to reconfigure the fixed-width multiplication engine to generate four useful multipliers under the limited hardware resource.

#### 2.2 Subword Multiplication

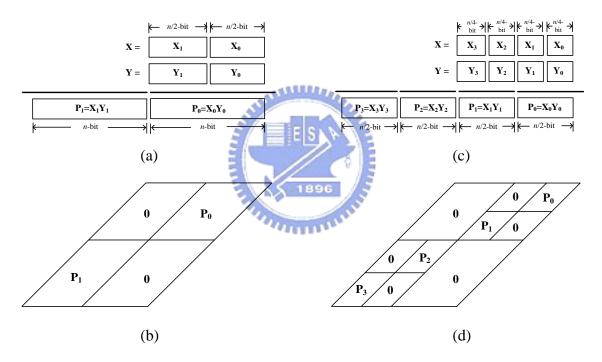

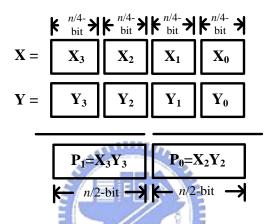

Many DSP and computer applications demand to operate at lower resolution, where the data can be expressed in a half-word length [21-26]. Generally, applying the subword multiplication scheme, we can partition an *n*-bit operand into two independent n/2-bit operands or four independent n/4-bit operands; hence, the subword multiplier can perform not only nxn full-precision multiplication but also two n/2xn/2 or four n/4xn/4 full-precision multiplications in parallel. Fig. 2.4 illustrates subword multiplication and the partial product array distribution [21-26]. In Fig. 2.4(a), two *n*-bit operands, *X* and *Y*, are partitioned into two independent pairs of n/2-bit subwords, and

then the two pairs of n/2-bit subwords are multiplied to produce two independent *n*-bit products:  $P_1=X_1Y_1$  and  $P_0=X_0Y_0$ , where the partial product array distribution is addressed in Fig. 2.4(b). On the other hand, n/4xn/4 subword multiplication and the partial product array distribution are illustrated in Fig. 2.4(c) and 2.4(d), respectively. To our best knowledge, the current subword scheme is applied only to full-precision multiplication based on the full-precision multiplier infrastructure. In the following section, we will extend this subword scheme to fixed-width and full-precision multiplication using the fixed-width prototype multiplier.

Fig. 2.4. Subword multiplication (a) two n/2xn/2 multiplications, (b) two n/2xn/2 partial-product array distribution, (c) four n/4xn/4 multiplications, and (d) four n/4xn/4 partial-product array distribution.

#### **2.3 Low-Error Fixed-Width Multipliers**

It is known that the various fixed-width multipliers with adaptive compensation biases have been widely discussed in [12-20]. Herein, regarding the tradeoffs of the truncation error and area cost in [19-20], we choose w=1 (i.e., keeping n+1 most significant columns) and Q=0 for the prototype multiplier structure, where Q has been clearly defined in [19-20]. The error-compensation bias can be summarized as

$$\sigma_{Type1,Q=0,w=1} = \begin{cases} \left\lfloor \frac{1}{2} (E_{main} + \theta_{Q=0,w=1}) + \frac{1}{2} \right\rfloor, \text{ if } \theta_{Q=0,w=1} = 0\\ \left\lfloor \frac{1}{2} (E_{main} + \theta_{Q=0,w=1}) + 0 \right\rfloor, \text{ if } \theta_{Q=0,w=1} > 0 \end{cases}$$

(9)

where  $E_{main} = S_{0,n-1} + S_{1,n-3} + S_{2,n-5} + \cdots + S_{n/2-2,3} + S_{n/2-1,1}$  (i.e., the (n+1)th column counted from left to right of Fig. 2.2) and  $\theta_{Q=0,w=1} = S_{0,n-2} + S_{1,n-4} + S_{2,n-6} + \cdots + S_{n/2-2,2} + S_{n/2-1,0}$  (i.e., the (n+2)th column counted from left to right of Fig. 2.2) for the Booth architecture. If the Baugh-Wooley architecture is the basic multiplier,  $E_{main} = \overline{x_{n-1}y_0} + x_{n-2}y_1 + x_{n-3}y_2$  $+ \cdots + x_1y_{n-2} + \overline{x_0y_{n-1}}$  (i.e., the (n+1)th column counted from left to right of Fig. 2.3) and  $\theta_{Q=0,w=1} = x_{n-2}y_0 + x_{n-3}y_1 + x_{n-4}y_2 + \cdots + x_1y_{n-3} + x_0y_{n-2}$  (i.e., the (n+2)th column counted from left to right of Fig. 2.3). Fig. 2.5 and Fig. 2.6(a) are the prototype Booth multiplier structure and the prototype Baugh-Wooley multiplier structure for n=8, respectively, where A, ND, HA, and FA denote AND gate, NAND gate, a half adder and a full adder, respectively, and the logic diagrams of the other processing elements are depicted in Fig. 2.6(b).

(b)

Fig. 2.6. (a) The fixed-width 8×8 Baugh-Wooley multiplier with  $\theta_{Q=0,w=1}$ , and (b) logic diagrams of AOR, ANOR, AHA, AFA, NFA.

# Chapter 3

# Design of Reconfigurable Fixed-Width Multipliers

In this chapter, we describe the design methodology of the reconfigurable fixed-width multipliers based on the Booth architecture and the Baugh-Wooley architecture, respectively.

#### 3.1 Reconfigurable Fixed-Width Booth Multiplier

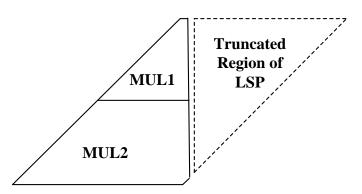

In this section, we begin to demonstrate how to generate four different multipliers under the limited hardware resource of the fixed-width Booth multiplier. In this thesis, we use the fixed-width multiplier in Fig. 3.1 as our reconfigurable Booth multiplier prototype instead of the full-precision multiplier structure, where the fixed-width multiplier truncates partial products of the least significant part (LSP) as shown in the dash-lined region of Fig. 3.1 and compensate the error with adaptive compensation bias. In Fig. 3.1, two modules denoted as MUL1 and MUL2 are used to reconfigure the following four different multipliers as listed in Table 3.1 through the corresponding four configuration modes (CMs). Thus, the proposed reconfigurable fixed-width Booth multiplier employing MUL1 and MUL2 is essentially different from the full-precision one [21-31]. Without loss of the generality, we use n=8 to investigate each CM case.

Fig. 3.1. Prototype structure of the proposed reconfigurable fixed-width Booth multiplier involving MUL1, MUL2, and discarding truncated region of LSP.

Table 3.1: Proposed four configuration modes of the reconfigurable fixed-width Booth multiplier

| Configuration | Function Descriptions             | Mode Applications                        |

|---------------|-----------------------------------|------------------------------------------|

| Mode (CM)     | 111                               |                                          |

| CM1           | <i>nxn</i> fixed-width multiplier | High resolution computations:            |

|               |                                   | Multiplication, matrix multiplication,   |

|               |                                   | square-root operation, filter, transform |

| CM2           | two n/2xn/2 fixed-width           | Parallel computations: Multiplication,   |

|               | multipliers                       | matrix multiplication, square-root       |

|               |                                   | operation, filter, transform             |

| CM3           | n/2xn/2 full-precision            | Full-precision computations:             |

|               | multiplier                        | Multiplication, matrix multiplication,   |

|               |                                   | square-root operation, filter, transform |

| CM4           | sum of two $n/2xn/2$              | Parallel multiplication and add          |

|               | fixed-width multipliers           | computations: Matrix multiplication,     |

|               |                                   | filter, transform                        |

#### 3.1.1 CM1: *nxn* Fixed-Width Multiplier

CM1 is in charge of operating  $n \ge n$  fixed-width multiplication that receives two *n*-bit numbers and produces an *n*-bit product. Since CM1 is confined to w=1, the partial-product array diagram as shown in Fig. 3.2(a) with n=8 can be easily obtained from Fig. 2.2. The partial products in the dash-lined region of Fig. 3.2(a) denoted as  $\sigma_{CM1}$

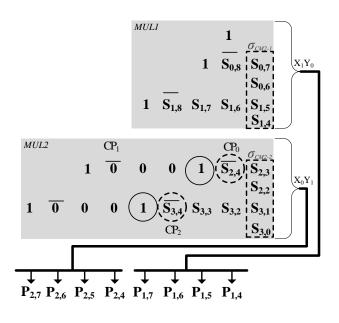

are used to compute the error compensation bias in (9). Note that the error performance results of the Booth-based CM1 are the same as those of [20] because we implement the same adaptive compensation bias circuits. Throughout the section 3.1, in order to completely achieve four configuration modes, we provide three configuration parameters  $CP_0$ ,  $CP_1$ , and  $CP_2$  combining with the partial product setting to generate four multipliers. For the fixed-width multiplier with *n*=8, the bit position of these parameters are shown in Fig. 3.2(a). In CM1,  $CP_0$ ,  $CP_1$ , and  $CP_2$  are set to 0 as shown in Fig. 3.2(b). Associated with  $CP_0$ ,  $CP_1$ , and  $CP_2$ , the product of CM1 can be generally expressed as

$$P_{CM1} = \{P_{2n-1}, P_{2n-2}, P_{2n-3}, \dots, P_n\}$$

$$= \sum_{i=0}^{(n-2)/2} \sum_{j=1}^{2i} S_{i,n-j} \cdot 2^{2i+n-j}$$

$$+ (2^{n+1} + \overline{S_{0,n}} \cdot 2^n) + (2^{n+3} + \overline{S_{1,n}} \cdot 2^{n+2})$$

$$+ (2^{n+5} + \overline{S_{2,n}} \cdot 2^{n+4}) + \cdots + (2^{2n-1} + \overline{S_{n/2-1,n}} \cdot 2^{2n-2}) + 2^n$$

$$+ \sigma_{CM1} + CP_0 \cdot 2^n + CP_1 \cdot 2^{\frac{3n}{2}} + CP_2 \cdot 2^{\frac{3n}{2}-2}$$

$$(10)$$

$$u_{i} \frac{1}{1} \frac{1}{S_{0,8}} \frac{\sigma_{Cu}}{S_{0,7}}$$

$$1 \overline{S_{1,8}} S_{1,7} S_{1,6} \frac{S_{1,4}}{S_{1,4}}$$

$$\frac{MU22}{1} \frac{CP_1}{1} \frac{CP_1}{S_{2,8}} S_{2,7} S_{2,6} S_{2,5} S_{2,4} \frac{S_{2,3}}{S_{2,4}}$$

$$(10)$$

$$\frac{1}{P_15} \frac{1}{P_{14}} \frac{1}{P_{13}} \frac{1}{P_{12}} \frac{1}{P_{11}} \frac{1}{P_{10}} \frac{1}{P_9} \frac{1}{P_8}$$

$$(a)$$

$$(b)$$

Fig. 3.2. (a) Partial-product array diagram for  $n \ge n$  fixed-width multiplier with n=8, and (b) configuration parameter settings.

#### 3.1.2 CM2: Two *n*/2x*n*/2 Fixed-Width Multipliers

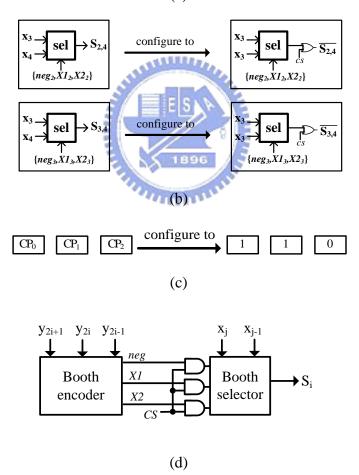

CM2 plays a role of concurrently performing two n/2xn/2 fixed-width multiplications. In this configuration mode, we need two copies of hardware resource to implement CM2. The corresponding fixed-width subword operation of CM2 is illustrated in Fig. 3.3, where two subword products are  $X_1Y_0$  and  $X_0Y_1$  because of the limited hardware resource and each fixed-width multiplication has n/2-bit wide output. Note that we can produce subword products  $X_0Y_0$  and  $X_1Y_1$  as the conventional subword multiplication by exchanging  $X_0$  and  $X_1$  before the Booth selector. However,  $X_0Y_0$  and  $X_1Y_1$  will lead to larger exchange hardware overhead. Thus, we adopt  $X_1Y_0$ and  $X_0Y_1$  subword operations. The partial-product array diagram is depicted in Fig. 3.4(a), where  $\sigma_{CM2-1}$  and  $\sigma_{CM2-2}$  denote the error compensation biases of  $X_1Y_0$  and  $X_0Y_1$ , respectively. In Fig. 3.4(a) with n=8, compared with CM1, MUL1 can be unchanged while MUL2 must configure {  $S_{3,4}, S_{2,4}$  } to {  $\overline{S_{3,4}, \overline{S_{2,4}}}$  }, and {  $S_{3,5}, S_{2,5}$  } to { 1,1 } circled by dash-line and solid-line, respectively. In the logic gate level, we OR the original partial-product with the control signal to generate 1 and use XOR gate to produce inverted sign-bit as shown in Fig. 3.4(b), where CS denotes the control signal and note that the input  $\{x_4, x_3\}$  are configured to  $\{x_3, x_3\}$ . In addition,  $S_{2,6}$ ,  $S_{2,7}$ ,  $S_{3,6}$ , and  $S_{3,7}$  are set to zero. The configuration parameter settings of CM2 are addressed in Fig. 3.4(c), where CP<sub>0</sub>, CP<sub>1</sub>, and CP<sub>2</sub> are set to 1, 1, and 0, respectively. Since other partial products are configured to 0, we do not need to AND these partial products with control signal. Our approach is to AND three Booth recoding bits with the control signal as shown in Fig. 3.4(d) to save the number of AND gates while n increases. Hence, no matter how many partial products needed to be configured to 0, we merely require three AND gates if these partial products are in the same row. In addition, due to permanent inverted MSB output of the partial products in MUL2, the bits denoted as  $\overline{0}$  represent one, but the summation result of the most significant half of MUL2 still produces zero. In summary, the two products of CM2 can be generally expressed in (11a) and (11b).

$$P_{CM2-1} = \{P_{1,n-1}, P_{1,n-2}, P_{1,n-3}, \dots, P_{1,n/2}\}$$

$$= \sum_{i=0}^{(n/2-2)/2} \sum_{j=1}^{2i} S_{i,n-j} \cdot 2^{2i+(n/2)-j}$$

$$+ (2^{n/2+1} + \overline{S_{0,n}} \cdot 2^{n/2}) + (2^{n/2+3} + \overline{S_{1,n}} \cdot 2^{n/2+2})$$

$$+ (2^{n/2+5} + \overline{S_{2,n}} \cdot 2^{n/2+4})$$

$$+ \dots + (2^{n-1} + \overline{S_{(n/2-2)/2,n}} \cdot 2^{n-2}) + 2^{n/2}$$

$$+ \sigma_{CM2-1}$$

(11a)

$$P_{CM2-2} = \{P_{2,n-1}, P_{2,n-2}, P_{2,n-3}, \dots, P_{2,n/2}\}$$

$$= \sum_{i=(n/2-2)/2}^{(n-2)/2} \sum_{j=(n/2)+1}^{2i} S_{i,n-j} \cdot 2^{2i+(n/2)-j}$$

$$+ (2^{n/2+1} + \overline{S_{(n/2-2)/2+1,n/2}} \cdot 2^{n/2})$$

$$+ (2^{n/2+3} + \overline{S_{(n/2-2)/2+2,n/2}} \cdot 2^{n/2+2})$$

$$+ (2^{n/2+5} + \overline{S_{(n/2-2)/2+3,n/2}} \cdot 2^{n/2+4})$$

$$+ \dots + (2^{n-1} + \overline{S_{(n-2)/2,n/2}} \cdot 2^{n-2})$$

$$+ \sigma_{CM2-2} + CP_0 \cdot 2^{n/2} + CP_2 \cdot 2^{n-2}$$

(11b)

where  $\{\overline{S_{(n/2-2)/2+1,n/2}}, \overline{S_{(n/2-2)/2+2,n/2}}, \overline{S_{(n/2-2)/2+3,n/2}}, \cdots, \overline{S_{(n-2)/2,n/2}}\}\$  are the reconfigured

partial products as similar to that in Fig. 3.4(b), rather than to complement these partial-products of CM1.

$$\mathbf{X} = \begin{bmatrix} \mathbf{X}_1 & \mathbf{X}_0 \\ \mathbf{X}_1 & \mathbf{X}_0 \end{bmatrix}$$

$$\mathbf{Y} = \begin{bmatrix} \mathbf{Y}_1 & \mathbf{Y}_0 \\ \mathbf{Y}_1 & \mathbf{Y}_0 \end{bmatrix}$$

$$\begin{bmatrix} \mathbf{P}_1 = \mathbf{X}_0 \mathbf{Y}_1 & \mathbf{P}_0 = \mathbf{X}_1 \mathbf{Y}_0 \\ \mathbf{F}_1 = \mathbf{X}_0 \mathbf{Y}_1 & \mathbf{F}_0 = \mathbf{X}_1 \mathbf{Y}_0 \end{bmatrix}$$

Fig. 3.3. Subword operation for two n/2xn/2 fixed-width multiplications.

(a)

Fig. 3.4. (a) Partial-product array diagram for two n/2xn/2 fixed-width multipliers with n=8, (b) configuration settings of S<sub>2,4</sub> and S<sub>3,4</sub>, (c) configuration parameter settings, and (d) configured Booth recoding circuit.

#### 3.1.3 CM3: *n*/2x*n*/2 Full-Precision Multiplier

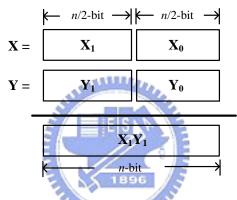

CM3 serves as performing an n/2xn/2 full-precision multiplication. The corresponding subword operation of CM3 is illustrated in Fig. 3.5, where the subword product is  $X_1Y_1$  with *n*-bit wide output. Since the proposed reconfigurable structure to implement full-precision multiplication is based on the fixed-width multiplier fabric, it can be seen that MUL2 is able to achieve this mode operation. Next, the partial-product array diagram is depicted in Fig. 3.6(a) with n=8, where the configuration of S<sub>2,4</sub> and  $S_{3,4}$  circled by dash-line are different from the ones of other modes because their multiplicand inputs of the Booth selector have to be configured from  $\{x_4, x_3\}$  to  $\{x_4, 0\}$ as shown in Fig. 3.6(b). The partial-product  $S_{3,2}$  is configured to  $neg_2$  circled by solid-line for 2's-complement computation. In addition,  $S_{2,2}$ ,  $S_{2,3}$ ,  $S_{3,0}$ ,  $S_{3,1}$ , and  $S_{3,3}$  are configured to 0 in MUL2. In this mode, the output of MUL1 needs to generate zero as shown in the upper diagram of Fig. 3.6(a). The configuration parameter settings of CM3 are addressed in Fig. 3.6(c), where CP<sub>0</sub>, CP<sub>1</sub>, and CP<sub>2</sub> are set to 0, 1, and  $neg_{n/2-1}$ , respectively. For n=8,  $neg_{n/2-1}$  is  $neg_3$ . On the other hand, we AND three Booth recoding bits with the control signals to generate 0 in MUL2 as mentioned in the above paragraph. However, in order to generate 0 in MUL1, we can use AND gates before the Booth encoder to AND the multiplier inputs with the control signal as shown in Fig. 3.6(d) such that the Booth encoder generates 0 before the Booth selector. In summary, the product of CM3 can be generally expressed in (12).

$$P_{CM3} = \{P_{n-1}, P_{n-2}, P_{n-3}, \dots, P_0\}$$

$$= \sum_{i=(n/2-2)/2}^{(n-2)/2} \sum_{j=1}^{n/2} S_{i,n-j} \cdot 2^{2i-j}$$

$$+ (2^{n/2+1} + \overline{S_{(n/2-2)/2+1,n}} \cdot 2^{n/2})$$

$$+ (2^{n/2+3} + \overline{S_{(n/2-2)/2+2,n}} \cdot 2^{n/2+2})$$

$$+ (2^{n/2+5} + \overline{S_{(n/2-2)/2+3,n}} \cdot 2^{n/2+4})$$

$$+ \dots + (2^{n-1} + \overline{S_{(n-2)/2,n}} \cdot 2^{n-2})$$

$$+ \sum_{k=(n/2-2)/2+1}^{(n-2)/2-1} e_{k} \cdot 2^{2(k-(n/2-2)/2-1)}$$

$$+ CP_0 \cdot 2^0 + CP_1 \cdot 2^{n/2} + CP_2 \cdot 2^{n/2-2}$$

(12)

where  $S_{i,n/2}$  are the reconfigured partial products as similar to that in Fig.3.6(b).

Fig. 3.5. Subword operation for one n/2xn/2 full-precision multiplication.

Fig. 3.6. (a) Partial-product array diagram for n/2xn/2 full-precision multiplier with n=8, (b) configuration settings of S<sub>2,4</sub> and S<sub>3,4</sub>, (c) configuration parameter settings, and (d) configured Booth recoding circuit.

#### 3.1.4 CM4: Sum of Two n/2xn/2 Fixed-Width Multipliers

The main function of CM4 is to add two n/2-bit wide fixed-width multiplication results. The partial product array diagram is sketched in Fig. 3.7. In Fig. 3.7, the configuration settings are the same as those of CM2; however, the output arrangement is different. The details will be explained in the next paragraph.

Fig. 3.7. Partial-product array diagram for sum of two n/2xn/2 fixed-width multipliers with n=8.

#### 3.1.5 Proposed Structure

According to the above partial-product array analysis of the four configuration modes, we observe the following architecture design viewpoints.

- Need to individually operate MUL1 and MUL2 for CM2. There exists a last-stage adder to sum the outputs of MUL1 and MUL2 to generate product for CM1, CM3, and CM4.

- 2) Need to reconfigure adaptive compensation circuit for nxn and n/2xn/2 fixed-width multiplication.

- 3) Need to reconfigure Booth encoder circuit for nxn and n/2xn/2 multiplication.

- 4) Need to control carryout signals according to different CMs.

- 5) Need to rearrange the output of the final product according to CMs.

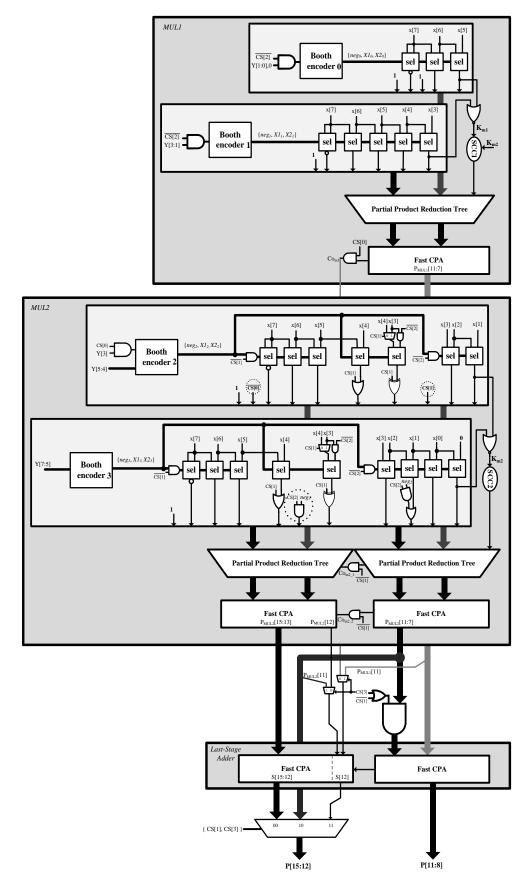

According to the above viewpoints, the proposed reconfigurable structure for n=8can be depicted in Fig. 3.8, where we separate the fixed-width multiplication array into two multiplier modules MUL1 and MUL2 and then their outputs are fed into the last-stage adder. First of all, there is one decoder which is charge of decoding OP code to generate control signals for two multiplier modules, where the truth table of this decoder is listed in Table 3.2. After observation, the parameters CP<sub>0</sub>, CP<sub>1</sub>, and CP<sub>2</sub> circled by dash-line in Fig. 3.8 can be easily realized by CS[1],  $\overline{CS[0]}$ , and  $\overline{CS[2]} \cdot neg_3$ , respectively. For last-stage adder, since we do not need to sum up MUL1 and MUL2 for CM2, the least significant half inputs of the last-stage adder must be switched from the least significant half products of MUL2 to zero. Thus, the least significant half products of the last-stage adder can directly output the products of MUL1. In Fig. 3.8, we use AND gates to switch the least significant half products of MUL2 to zero. Second, for CM4, sign extension is required before summing up MUL1 and MUL2 so that sign bits are generated after summation. In Fig. 3.8, there are two multiplexers to select sign bits of MUL1 and MUL2, which are denoted as P<sub>MUL1</sub>[11] and P<sub>MUL2</sub>[11], respectively. Thus, the most significant half products of the last-stage adder will generate the sign bit denoted as S[12].

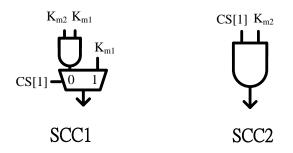

From viewpoint 2, since  $\sigma_{CM1}$  is composed of  $\sigma_{CM2-1}$  and  $\sigma_{CM2-2}$ , two adaptive compensation biases  $\sigma_{CM2-1}$  and  $\sigma_{CM2-2}$  are needed to carefully control. According to the binary thresholding mentioned in [20], if each adaptive compensation bias adds a constant K = 1/2 for  $\theta_{Q=0,w=1} = 0$ , the two adaptive compensation biases are not equivalent to the compensation design as shown in Fig. 7 of [20]. Thus, the design will lead to larger truncation error for CM1 than that of adding a constant K=1/2 one time. Herein, we propose sub-calibration-circuit 1 (SCC1) and sub-calibration-circuit 2 (SCC2) to keep away from double constant addition and to achieve this reconfiguration for nxnand n/2xn/2 fixed-width multiplications. The logic diagram of SCC1 and SCC2 as shown in Fig. 3.9 is little area overhead, where the truth table of SCC1 and SCC2 is tabulated in Table 3.3. For CM1, if  $K_{m1}=1$  and  $K_{m2}=1$  (i.e.  $\theta_{Q=0,w=1}=0$ ), then SCC1=1 and SCC2=0 to avoid double addition of constant K=1/2. Otherwise, SCC1=0 and SCC2=0 since  $\theta_{Q=0,w=1} \neq 0$ . For CM2 or CM4, two independent n/2xn/2 multipliers are operated in parallel. Thus, SCC1 and SCC2 follow the values of  $K_{m1}$  and  $K_{m2}$  (i.e., SCC1= $K_{m1}$  and SCC2=  $K_{m2}$ ).

From viewpoint 3, apart from the above mentioned configurations, the multiplier  $y_{n^{2}-1}$  has to be configured to 0 when CM2, CM3, or CM4 are performed. In Fig. 3.8, the input of the Booth encoder2 is {Y[5],Y[4],Y[3]} for CM1. On the other hand, while one of other three modes is selected, the input of the Booth encoder2 is {Y[5],Y[4],0}. In addition, three carryout signals denoted as  $Co_{m1}$ ,  $Co_{m2-1}$ , and  $Co_{m2-2}$  are also configured from viewpoint 4.  $Co_{m1}$  is propagated to the last-stage adder only if CM1 is performed.  $Co_{m2-1}$ , and  $Co_{m2-2}$  are propagated if either CM1 or CM3 is performed. From viewpoint 5, the output arrangement of the final product is different according to the different modes. As shown in Fig. 3.8, there exists a multiplexer to select the most significant half of the final product. If {CS[1], CS[3]}={0, 0}, that means either CM1 or CM3 is performed and then the output is switched to the least significant half of the last-stage adder (i.e. S[15:12]). If {CS[1], CS[3]}={1, 0}, that means CM2 is performed and then the output is switched to the least significant half of MUL2 (i.e.  $P_{MUL2}$ [11:8]). If {CS[1], CS[3]}={1, 1}, that means CM4 is performed and the output is extended to 8 bits with sign bit S[12].

Fig. 3.8. Overall structure of the proposed reconfigured fixed-width Booth multiplier for n=8.

Fig. 3.9. Logical diagram of SCC1 and SCC2.

Table 3.2: Truth table of the decoder for the reconfigurable fixed-width Booth multiplier

| OP[2:0] |    | CS  | [3:0] |   |

|---------|----|-----|-------|---|

| 00(CM1) | 0  | 0   | 0     | 1 |

| 01(CM2) | 0  | 0   | 1     | 0 |

| 10(CM3) | 0  | 11. | 0     | 0 |

| 11(CM4) | 10 | 0   | 1     | 0 |

|         |    |     |       |   |

Table 3.3: Truth table of sub-calibration-circuit1 (SCC1) and sub-calibration-circuit2 (SCC2)

| K <sub>m1</sub> | K <sub>m2</sub> | CM1    |        | CM2 c  | or CM4 |

|-----------------|-----------------|--------|--------|--------|--------|

|                 |                 | Output | Output | Output | Output |

|                 |                 | of     | of     | of     | of     |

|                 |                 | SCC1   | SCC2   | SCC1   | SCC2   |

| 0               | 0               | 0      | 0      | 0      | 0      |

| 0               | 1               | 0      | 0      | 0      | 1      |

| 1               | 0               | 0      | 0      | 1      | 0      |

| 1               | 1               | 1      | 0      | 1      | 1      |

#### 3.2 Reconfigurable Fixed-Width Baugh-Wooley Multiplier

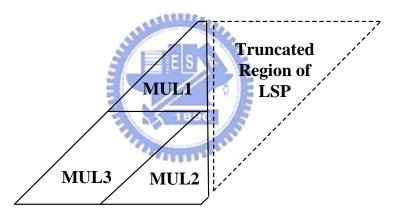

In this section, we begin to demonstrate how to generate four different multipliers under the limited hardware resource of the fixed-width Baugh-Wooley multiplier. In this thesis, we use the fixed-width multiplier in Fig. 3.10 as our reconfigurable Baugh-Wooley multiplier prototype instead of the full-precision multiplier structure, where the fixed-width multiplier truncates partial products of the least significant part (LSP) as shown in the dash-lined region of Fig. 3.10. In Fig. 3.10, three modules denoted as MUL1, MUL2, and MUL3 are used to reconfigure the following four different multipliers as listed in Table 3.4 through the corresponding four configuration modes (CMs). Thus, the proposed reconfigurable fixed-width Baugh-Wooley multiplier employing MUL1, MUL2, and MUL3 is essentially different from the full-precision one [21-31]. Without loss of the generality, we use n=8 to investigate each CM case in the following.

Fig. 3.10. Prototype structure of the proposed reconfigurable fixed-width Baugh-Wooley multiplier involving MUL1, MUL2, MUL3 and discarding truncated region of LSP.

| Configuration<br>Mode (CM) | Function Descriptions                                | Mode Applications                                                                                             |

|----------------------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| CM1                        | <i>nxn</i> fixed-width multiplier                    | High resolution computations: Multiplication, matrix multiplication, square-root operation, filter, transform |

| CM2                        | two <i>n</i> /2x <i>n</i> /2 fixed-width multipliers | Parallel computations: Multiplication, matrix multiplication, square-root operation, filter, transform        |

| CM3                        | n/2xn/2 full-precision<br>multiplier                 | Full-precision computations: Multiplication, matrix multiplication, square-root operation, filter, transform  |

| CM4                        | two <i>n</i> /4x <i>n</i> /4 fixed-width multipliers | Parallel computations: Multiplication, matrix<br>multiplication, square-root operation, filter, transform     |

Table 3.4: Proposed four configuration modes of the reconfigurable fixed-width Baugh-Wooley multiplier

#### 3.2.1 CM1: nxn Fixed-Width Multiplier

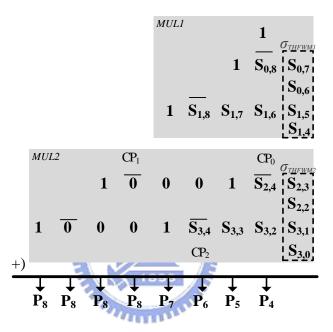

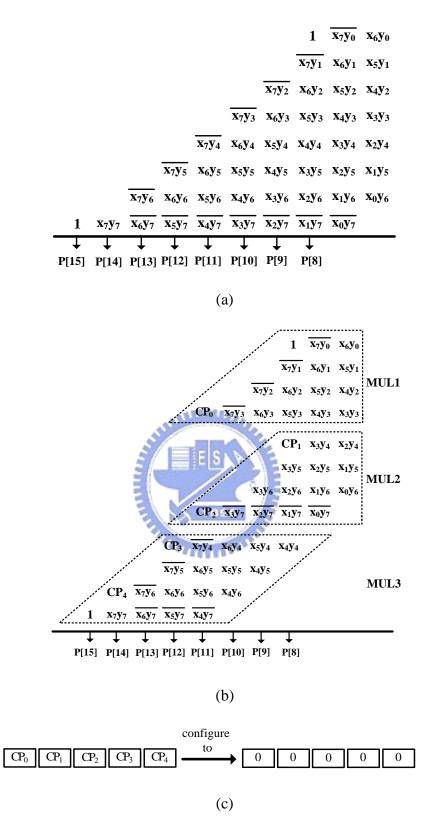

CM1 is in charge of operating *nxn* fixed-width multiplication that receives two n-bit numbers and produces an *n*-bit product. It is known that the various fixed-width multipliers with adaptive compensation biases have been widely discussed in [12-20]. Herein, regarding the tradeoffs of the truncation error and area cost in [19], we choose w=1 (i.e., keeping n+1 most significant columns) and Q=0 for the prototype multiplier structure in CM1, where Q has been clearly defined in [19]. Since CM1 is confined to w=1, the partial-product array diagram as shown in Fig. 3.11 (a) with n=8 can be easily obtained from Fig. 2.3. As mentioned above in this section, the rest partial products are decomposed into three multiplication modules MUL1, MUL2, and MUL3 as depicted in Fig. 3.11(b). The partial products of the three blocks are summed up independently and then the three summations are added together to produce final product. Throughout the section 3.2, in order to completely achieve four configuration modes, we provide five configuration parameters CP<sub>0</sub>, CP<sub>1</sub>, CP<sub>2</sub>, CP<sub>3</sub>, and CP<sub>4</sub> combining with the proper partial product setting to generate other multipliers. In CM1, CP<sub>0</sub>, CP<sub>1</sub>, CP<sub>2</sub>, CP<sub>3</sub>, and CP<sub>4</sub> are set to 0 as shown in Fig. 3.11(c).

Fig. 3.11. (a) Partial-product array diagram for *nxn* fixed-width multiplication, (b) proposed partial-product array diagram using MUL1, MUL2, and MUL3 for CM1, and (c) configuration parameter settings.

#### 3.2.2 CM2: Two *n*/2x*n*/2 Fixed-Width Multipliers

CM2 plays a role of concurrently performing two n/2xn/2 fixed-width multiplications. In this configuration mode, we need two copies of hardware resource to implement CM2. First, we have to determine which multiplier modules are suitable for two n/2xn/2 fixed-width multiplications under the constraint of the minimum number of modules and partial-product configuration settings. It is manifest that MUL1 and MUL2 are suitable for two n/2xn/2 fixed-width multiplications. Due to the use of MUL1 and MUL2, the corresponding fixed-width subword operation of CM2 is illustrated in Fig. 3.12, where two subword products are  $X_1Y_0$  and  $X_0Y_1$ , and each fixed-width multiplication has n/2-bit wide output. If we choose MUL3 for  $X_1Y_1$  and either MUL1 for  $X_I Y_0$  or MUL2 for  $X_0 Y_I$ , we can find that it is difficult to implement two input-independent fixed-width multipliers owing to the same  $X_1$  or  $Y_1$ . Even though we can carry out one n/2xn/2 fixed-width multiplier from partial products of  $X_1Y_1$ , larger number of configuration parameters is needed. That means lower flexibility and larger numbers of parameter settings are incurred. Once deciding the fixed-width subword product candidates, we can depict the partial-product array diagram using MUL1 and MUL2 in Fig. 3.13(a), where the partial products circled by dot-line are needed to be reconfigured in comparison with CM1. In Fig. 3.13(a), compared with partial products of MUL1 and MUL2 of CM1,  $x_4y_3$ ,  $x_5y_3$ ,  $x_6y_3$ ,  $\overline{x_7y_3}$ ,  $x_3y_4$ ,  $x_3y_5$ ,  $x_3y_6$ , and  $\overline{x_3y_7}$ are complemented,  $x_3y_3$  is configured to zero. The configuration parameters of CM2 can be set as addressed in Fig. 3.13(b), where  $CP_0$ ,  $CP_1$ , and  $CP_2$  are set to 1. The rest partial products are unchanged.

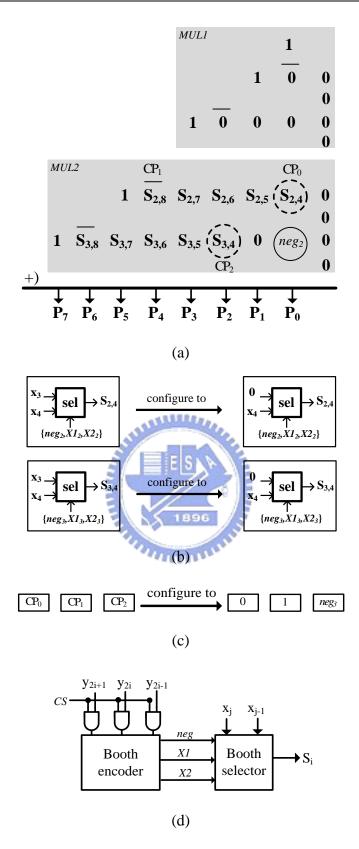

|            |                                                 | $\leftarrow$ n/2-bit $\rightarrow$            |

|------------|-------------------------------------------------|-----------------------------------------------|

| <b>X</b> = | <b>X</b> 1                                      | X <sub>0</sub>                                |

| <b>Y</b> = | Y <sub>1</sub>                                  | Y <sub>0</sub>                                |

| -          | P <sub>1</sub> =X <sub>0</sub> Y <sub>1</sub>   | P <sub>0</sub> =X <sub>1</sub> Y <sub>0</sub> |

|            | $\longleftarrow n/2\text{-bit} \longrightarrow$ | $\leftarrow$ n/2-bit $\rightarrow$            |

Fig. 3.12. Subword operation for two n/2xn/2 fixed-width multiplications.

Fig. 3.13. (a) Proposed partial-product array diagram for CM2, and (b) configuration parameter settings.

#### 3.2.3 CM3: n/2xn/2 Full-Precision Multiplier

CM3 serves as performing an n/2xn/2 full-precision multiplication. In behavior similar to that in CM2, the design procedures can be stated as follows. First, we have to

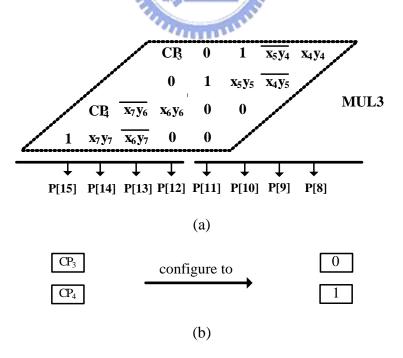

determine which modules are suitable for n/2xn/2 full-precision multiplications with the minimum number of modules and partial-product configuration settings. Under these constraints, since the proposed reconfigurable structure to implement full-precision multiplication is based on the fixed-width multiplier fabric, we can observe that just only one module, MUL3, can meet. Thus, the partial product array diagram of the MUL3 is depicted in Fig. 3.14, where CP<sub>3</sub> and CP<sub>4</sub> are set to 1 and 0, respectively.

Fig. 3.14. (a) Proposed partial-product array diagram for CM3, and (b) configuration parameter settings.

#### 3.2.4 CM4: Two n/4xn/4 Full-Precision Multipliers

CM4 widely used in lower resolution operation serves as performing two n/4xn/4 full-precision multiplications. Under the minimum number of modules and partial-product configuration setting constraints, we make use of the MUL3 to fulfill the CM4 operation. Due to the use of MUL3, the corresponding subword operation of CM4 is illustrated in Fig. 3.15, where two subword products are  $X_2Y_2$  and  $X_3Y_3$ , and each fixed-width multiplication has n/2-bit wide output. Then, the partial product array

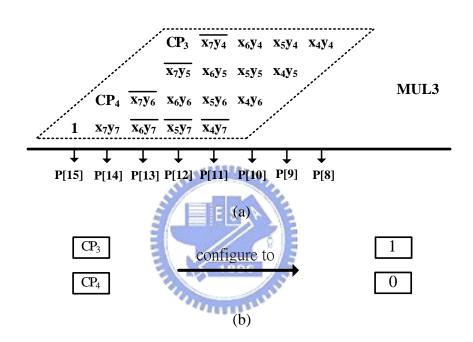

diagram of two n/4xn/4 full-precision multipliers can be obtained in Fig. 3.16(a). In Fig. 3.16(a), compared with partial products of the MUL3 of CM1,  $x_5y_4$  and  $x_4y_5$  are complemented,  $x_6y_4$  and  $x_6y_5$  are configured to one,  $\overline{x_7y_4}$ ,  $\overline{x_7y_5}$ ,  $x_4y_6$ ,  $x_5y_6$ ,  $\overline{x_4y_7}$ , and  $\overline{x_5y_7}$  are configured to zero. The configuration parameters of CM4 can be set as addressed in Fig. 3.16(b), where CP<sub>3</sub> and CP<sub>4</sub> are set to 0 and 1, respectively. The rest partial products are unchanged.

Fig. 3.15. Subword operation for two n/4xn/4 full-precision multiplications.

Fig. 3.16. (a) Proposed partial-product array diagram for CM4, and (b) configuration parameter settings.

#### **3.2.5 Proposed Structure**

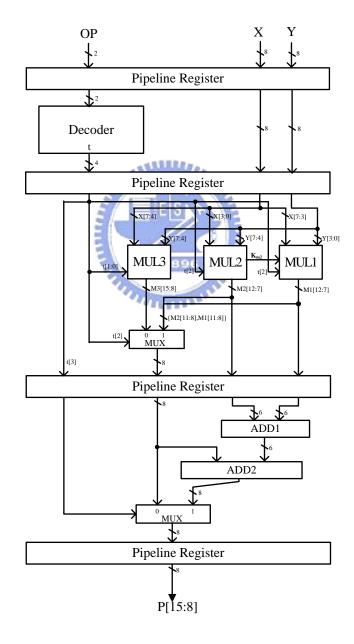

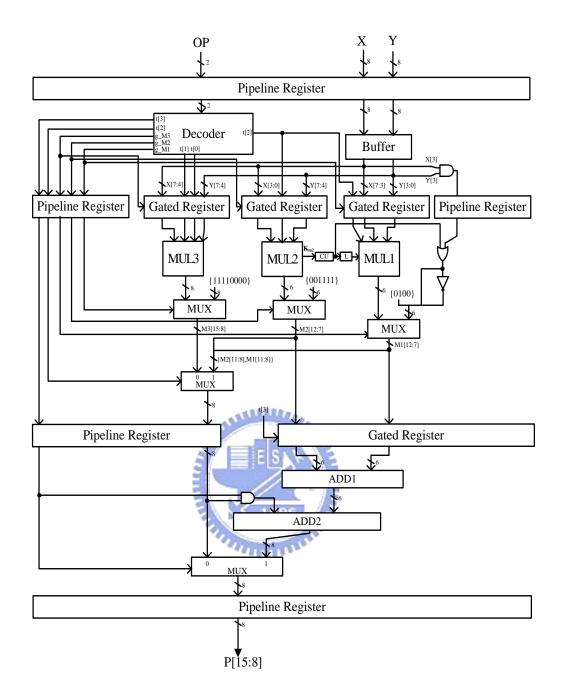

The proposed reconfigurable fixed-width Baugh-Wooley multiplier for n=8 is a pipelined structure as depicted in Fig. 3.17, where ADD and MUX denote an adder and a multiplexer, respectively. The detailed diagrams of the corresponding MUL1, MUL2, MUL3 are exposed in Fig. 3.18, 3.19, and 3.20, respectively, where A, ND, HA, and FA denote an AND gate, a NAND gate, a half adder and a full adder, respectively, and the logic diagrams of the other processing elements are depicted in Fig. 3.21. The overall structure in Fig. 3.17 is partitioned into three stages. The first stage is responsible for decoding the operation (OP) code to generate control signals for the next stage, where the truth table of this decoder is listed in Table 3.5. According to the control signals, we can manipulate three multiplication modules involving MUL1, MUL2, and MUL3 are manipulated at the second stage. As shown in Fig. 3.18, 3.19 and 3.20, since CM1 and CM2 enable MUL1 and MUL2 to compute at the same time, t[2] are used to configure MUL1 and MUL2 for correct function. Similarly, since CM1, CM3 and CM4 need to enable MUL3, t[1] and t[0] with the values of {00, 10, 01} are used to configure the MUL3 in accordance with three different modes. As a consequence,  $CP_0$ ,  $CP_1$ , and  $CP_2$ can be implemented by t[2], CP<sub>3</sub> and CP<sub>4</sub> can be realized by t[1] and t[0], respectively. In another viewpoint, from configuration parameter settings as shown in Fig. 3.11(c), 3.13(b), 3.14(b), 3.16(b), we can easily follow the above CP implementation.

A multiplexer at the second stage selects the output of MUL3 or the concatenation output of MUL1 and MUL2, and this design will be beneficial for power saving discussed in the next section. For CM1, since we have three multiplier modules MUL1, MUL2, and MUL3 to implement nxn fixed-width multiplication for Type 1 with  $\theta_{Q=0,w=1}$  [19], two adaptive compensation biases of MUL1 and MUL2 are needed to carefully control. According to the binary thresholding mentioned in [19], if each adaptive compensation bias adds a constant K = 1/2 for  $\theta_{Q=0,w=1} = 0$ , the two adaptive compensation biases are not equivalent to the compensation design as shown in Fig. 5 of [19]. Thus, the design will lead to larger truncation error for CM1 than that of adding a constant K=1/2 one time. As mentioned in chapter 3.1.5, we propose sub-calibration-circuit 1 (SCC1) and sub-calibration-circuit 2 (SCC2) to keep away from double constant addition and to achieve this reconfiguration for nxn and n/2xn/2fixed-width multiplications. The logic diagram of SCC1 and SCC2 as shown in Fig. 3.21 is little area overhead, where the truth table of SCC1 and SCC2 is the same as Table 3.3.

The third stage is in charge of accumulating the output values of MUL1, MUL2, and MUL3 for CM1 and selecting output of final product according to four CMs. In Fig. 3.17, ADD1 adds the output of MUL1 and MUL2; however, the output bits of ADD1 only include carryout and ignore least significant bit due to the fixed-width output. For example, originally, A[3:0]+B[3:0] will produce {carry- out, C[3:0]}, but we only need {carryout, C[3:1]}. ADD2 adds the output of ADD1 and the output of the multiplexer at the second stage to achieve CM1. We make use of the control signal t[3] to determine the final correct product among different CMs. Note that the proposed reconfigurable methodology and concept can be applied to the larger bit width and used to increase configuration modes such as n/8xn/8 and n/16xn/16 multipliers while the larger world length is given. For example, from the above analysis, the conventional full-precision subword multiplication schemes [21-26] can be applied to MUL3 to increase configuration modes including four n/8xn/8, eight n/16xn/16 full-precision multipliers, and so forth according to the larger input word length n. On the other hand, although we discuss only 2's-complement multiplication in this thesis, this reconfigurable concept can be easily extended to un-signed array multiplication.

| OP[2:0] | t[3] | t[2] | t[1] | t[0] |

|---------|------|------|------|------|

| 00(CM1) | 1    | 0    | 0    | 0    |

| 01(CM2) | 0    | 1    | 0    | 0    |

| 10(CM3) | 0    | 0    | 1    | 0    |

| 11(CM4) | 0    | 0    | 0    | 1    |

Table 3.5: Truth table of the decoder for the reconfigurable fixed-width Baugh-Wooley multiplier

Fig. 3.17. Proposed pipelined reconfigurable multiplier.

Fig. 3.19. Structure of MUL2.

In the following, we further discuss how to design power efficient pipelined reconfigurable multiplier. As mentioned in the above, the multiplications of CM2, CM3, and CM4 are of power-inefficient because they invoke all hardware resource to compute. It is desirable to apply low-power schemes such that the proposed reconfigurable fixed-width Baugh-Wooley multiplier possesses power-efficient capability. We apply low-power schemes including clock gating and zero input techniques to achieve power saving.

| Name             | rp1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | rp6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | AOR                                 | AFA                                                                                                                              |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Logic<br>Diagram | $x_{i}$ $y_{j}$ $y_{i}$ $y_{i$ | $x_i$<br>$y_j$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$<br>$y_i$ |                                     | $x_{i} \xrightarrow{S_{in}} C_{in}$ $y_{j} \xrightarrow{FA} C_{out} \xrightarrow{S_{out}} S_{out}$                               |