國立交通大學

電機學院 電信學程

碩士論文

寬頻低雜訊放大器與濾波器於CMOS製程實現

Implementation integration of Wideband Low-noise Amplifier

and Filter in CMOS Processes

研究 生：杜岳昌

指 導 教 授：周復芳 博 士

中華民國九十八年六月

# 寬頻低雜訊放大器與濾波器於 CMOS 製程實現

## Implementation integration of Wideband Low-noise Amplifier and Filter in CMOS Processes

研究 生：杜岳昌

Student : Yueh-Chang Du

指導 教授：周復芳 博士

Advisor : Dr. Christina F. Jou

Submitted to College of Electrical and Computer Engineering

National Chiao Tung University

in partial Fulfillment of the Requirements

for the Degree of

Master of Science

in

Communication Engineering

June 2009

Hsinchu, Taiwan, Republic of China

中華民國九十八年六月

# 寬頻低雜訊放大器與濾波器於CMOS製程實現

研 究 生：杜岳昌

指 導 教 授：周復芳 博 士

國 立 交 通 大 學 電 機 學 院 電 信 學 程 碩 士 班

## 中文摘要

本篇論文主要是探討寬頻低雜訊放大器結合寬頻濾波器之設計與分析。在寬頻低雜訊放大器的設計中，使用了兩級的放大器架構，以達到寬頻的特性。其中第二級放大器中使用中間級共振電路架構 (Inter-Stage Resonance)，達到寬頻的增益，並使用並聯尖峰(Shunt-Peaking)的頻寬延伸技術來完成寬頻特性。而在寬頻濾波器設計上，使用了雙 $\pi$ 型 (Double- $\pi$ ) 濾波器架構，以實現在頻寬中有平坦增益，而在頻寬外有快速衰減的效果。所設計的寬頻低雜訊放大器的模擬結果如下：頻寬為 3 ~ 8 GHz，平均增益為 16 dB，雜訊指為 4.6 ~ 5.4 dB，輸入反射係數為  $< 12$  dB，input  $P_{1dB}$  最小值為 -23.4 dBm，IIP3 最小值為 -11 dBm，功率消耗為 14.25 mW。

# Implementation integration of Wideband Low-noise Amplifier and Filter in CMOS Processes

Student: Yueh-Chang Du

Advisor: Dr. Christina F. Jou

Degree Program of Electrical and Computer Engineering

National Chiao Tung University

This thesis discusses the design and analysis integration of an ultra wideband low-noise amplifier and a wideband filter. In order to obtain the wide-band performance, the 2<sup>nd</sup> stage amplifier structures be used in the design of the wideband low-noise amplifier. The 2<sup>nd</sup> stage amplifier used the inter-stage resonance structure to achieves the wideband gain, the shunt-peaking technique is used to extend the bandwidth. The double- $\pi$  filter structure is used in the wideband filter design to achieves the gain flatness and the sharp attenuation out of the desired band. The simulation results of the amplifier are as follows: : The bandwidth is 3 ~ 8 GHz. The average gain is 16 dB. The noise figure is 4.6 ~ 5.4 dB. The input return loss is <12 dB. The input  $P_{1dB(min.)}$  is -23.4dBm. The  $IIP3_{(min.)}$  is -11dBm. The power consumption is 14.25 mW.

# 致謝

在職進修為一條漫長而辛苦的道路，能夠順利達到終點絕非個人之力量所能完成，除了本身之意志與堅持外，另外要感謝的人真的很多，這一路上其他貴人的幫助絕不可忘記。首先要感謝指導教授周復芳博士，我在交通大學進修的這三年中的成長，都是老師一點一滴的栽培，老師對學術研究的堅持與執著，讓我隨時戰戰兢兢的面對研究而不敢有任何鬆懈。也要感謝口試委員胡樹一教授及李信宏教授，給予本論文甚多的建議與指導，使本論文得以更加完善。

而實驗室博士班學長的指導更是讓我銘記在心，感謝吳匯儀學長、吳俊緯學長、林志鵬學長的指導與提攜，讓我這個原本對於射頻電路與天線懵懂的學生，到現在也具備了相當的專業知識。而實驗室同學奕霖、玠皇、昭維、子哲及宗廷的幫忙讓我這個在職生可以順利完成學業上的要求。

如果沒有公司的體諒與支持，也不可能順利完成學業。首先要謝謝目前所服務的宏暘科技總經理王明宗博士，讓我可以工作與學校兩者兼顧。另外，特別感謝公司射頻研發部的黃益地協理、黃士哲經理及楊啟明經理對我的鼓勵與提攜後進的胸襟，讓我在競爭激烈的職場中擁有繼續堅持下去的動力。

也要感謝的還有我的父母及家人，有他們的支持得以讓我專心於繁忙的工作及學術研究中。在這段時間中有許多難關，如果沒有家人的支持，我可能也無法克服這些困難。

最後僅以此論文獻給在這段時間所有支持與鼓勵我的家人及朋友，請與我分享獲得學位的喜悅。

# 目 錄

|                                                                                                 |     |

|-------------------------------------------------------------------------------------------------|-----|

| 中文摘要.....                                                                                       | i   |

| 英文摘要.....                                                                                       | ii  |

| 致謝.....                                                                                         | iii |

| 目錄.....                                                                                         | iv  |

| 表目錄.....                                                                                        | vi  |

| 圖目錄.....                                                                                        | vii |

|  第一章 緒論..... | 1   |

| 1.1 動機.....                                                                                     | 1   |

| 1.2 論文組織.....                                                                                   | 2   |

| 第二章 寬頻低雜訊放大器與寬頻濾波器設計.....                                                                       | 4   |

| 2.1 寬頻低雜訊放大器之輸入阻抗分析.....                                                                        | 5   |

| 2.2 寬頻濾波器之工作原理及設計.....                                                                          | 10  |

| 2.2.1 平面螺旋電感.....                                                                               | 11  |

| 2.2.2 電容.....                                                                                   | 12  |

| 2.2.3 寬頻濾波器設計.....                                                                              | 12  |

| 2.3 寬頻放大器之增益分析.....                                                                             | 16  |

| 第三章 寬頻低雜訊放大器結合寬頻濾波器模擬.....                                                                      | 20  |

| 3.1 佈局考量.....                                                                                   | 20  |

| 3.2 模擬結果.....                                                                                   | 21  |

|             |    |

|-------------|----|

| 第四章 結論..... | 31 |

| 參考文獻.....   | 32 |

# 表 目 錄

|                                     |    |

|-------------------------------------|----|

| 表 1.1.1 無線通訊標準之相關規格.....            | 2  |

| 表 3.2.1 以 TT、FF 及 SS 模式所模擬之參數值..... | 29 |

| 表 3.2.2 WB LNA 模擬之參數值比較表.....       | 30 |

# 圖 目 錄

|                                                                        |    |

|------------------------------------------------------------------------|----|

| 圖 2.1 寬頻低雜訊放大器結合寬頻濾波器之電路設計圖.....                                       | 5  |

| 圖 2.1.1 第一級放大器電路架構.....                                                | 6  |

| 圖 2.1.2 第一級放大器 $M_1$ 連接負載時之小訊號模型.....                                  | 6  |

| 圖 2.1.3 分析電阻性負載時之輸入阻抗所形成之小訊號模型等效電路<br>圖.....                           | 7  |

| 圖 2.1.4 分析電容性負載時之輸入阻抗所形成之小訊號模型等效電路<br>圖.....                           | 8  |

| 圖 2.1.5 將相依電流源 $g_m V_{gs}$ 轉變成相依電壓源 $g_m r_o V_{gs}$ 後之等效電路<br>圖..... | 9  |

| 圖 2.2.1.1 常見的平面螺旋電感形式.....                                             | 11 |

| 圖 2.2.2.1 平行金屬板結構電容.....                                               | 12 |

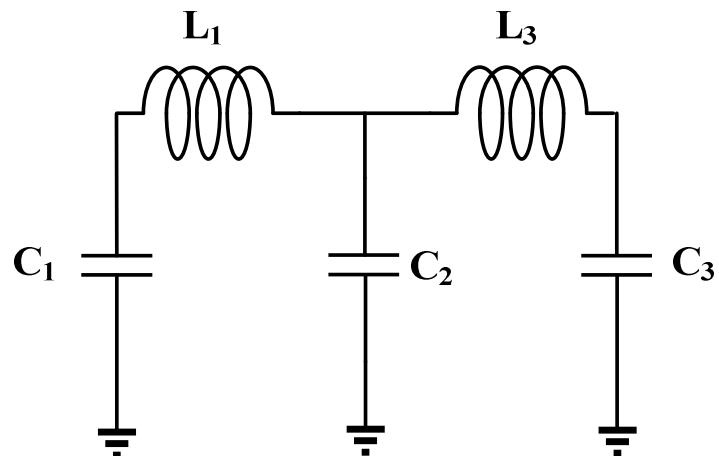

| 圖 2.2.3.1 本文所提出之雙 $\pi$ 型寬頻濾波器架構.....                                  | 13 |

| 圖 2.2.3.2 分別考慮寬頻低雜訊放大器之輸入阻抗及加上寬頻濾波器<br>之輸入阻抗示意圖.....                   | 14 |

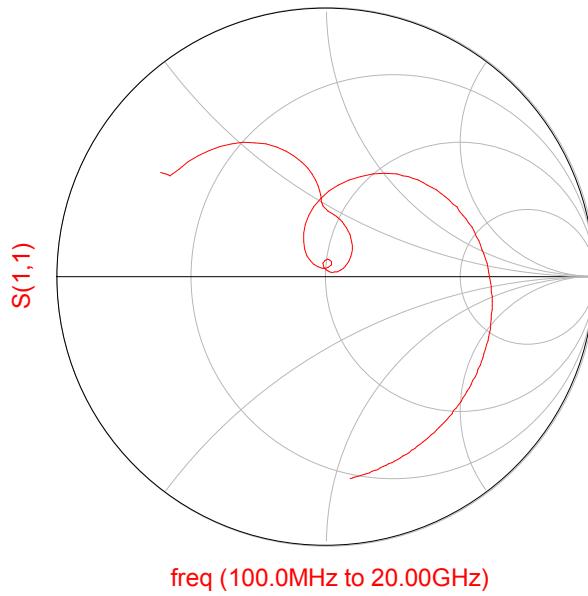

| 圖 2.2.3.3 寬頻低雜訊放大器之輸入阻抗.....                                           | 14 |

| 圖 2.2.3.4 寬頻濾波器結合寬頻低雜訊放大器後之輸入阻抗.....                                   | 15 |

| 圖 2.2.3.5 寬頻濾波器在高頻響應時之等效電路.....                                        | 16 |

|                                                |    |

|------------------------------------------------|----|

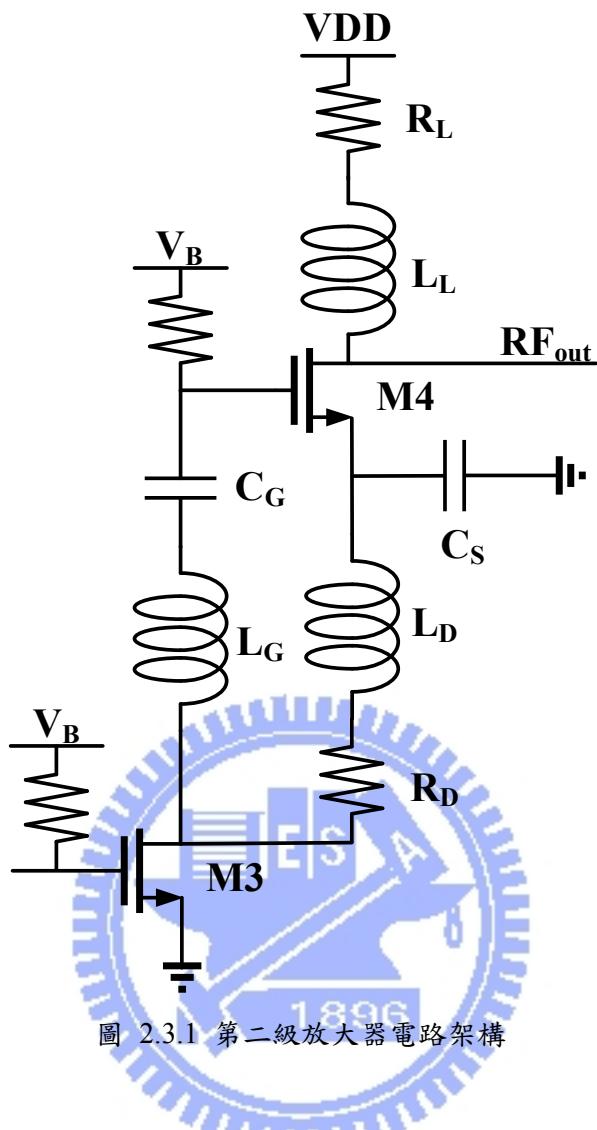

| 圖 2.3.1 第二級放大器電路架構.....                        | 17 |

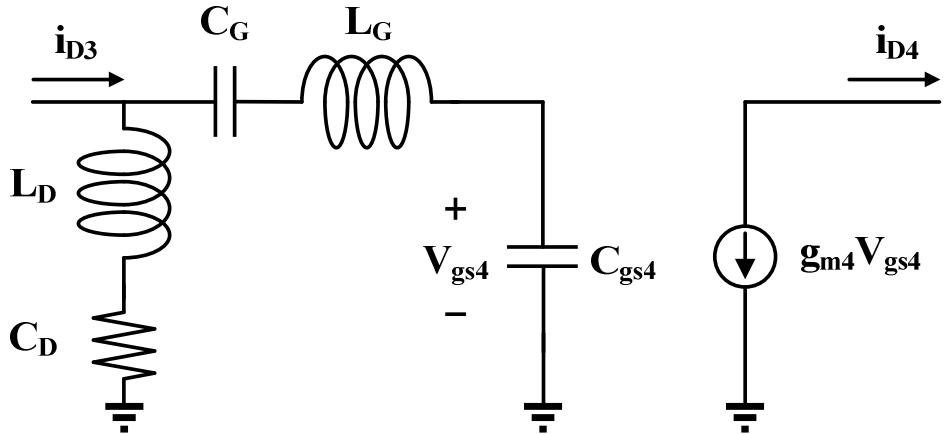

| 圖 2.3.2 第二級放大器電路之小訊號模型.....                    | 18 |

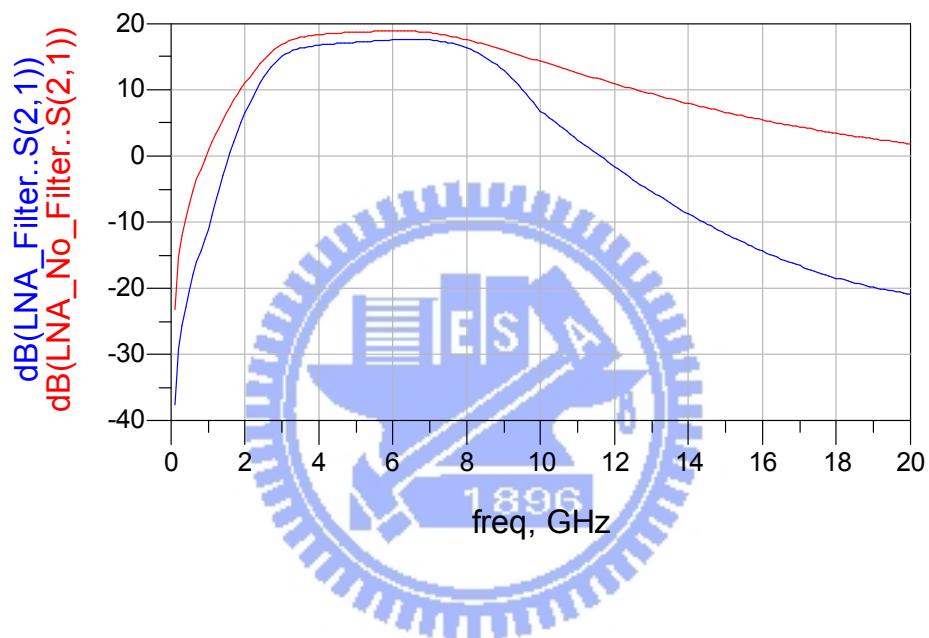

| 圖 2.3.3 本文所設計之寬頻低雜訊放大器結合寬頻濾波器與否之增益<br>比較圖..... | 19 |

| 圖 3.1.1 寬頻低雜訊放大器與寬頻濾波器佈局圖(1.0 × 0.8 mm)....    | 21 |

| 圖 3.2.1 以 TT 模式所模擬之輸入阻抗.....                   | 22 |

| 圖 3.2.2 以 FF 模式所模擬之輸入阻抗.....                   | 22 |

| 圖 3.2.3 以 SS 模式所模擬之輸入阻抗.....                   | 23 |

| 圖 3.2.4 以 TT 模式所模擬之 S 參數.....                  | 23 |

| 圖 3.2.5 以 FF 模式所模擬之 S 參數.....                  | 24 |

| 圖 3.2.6 以 SS 模式所模擬之 S 參數.....                  | 24 |

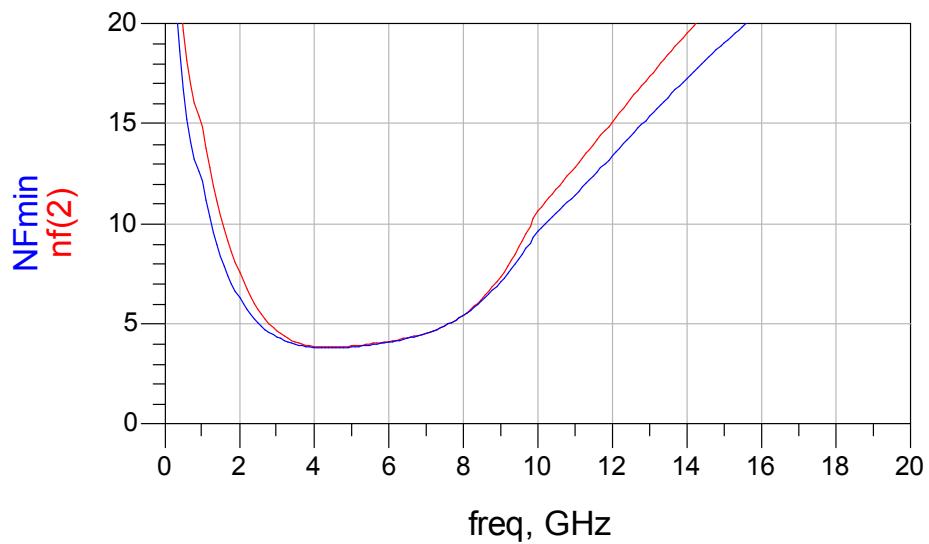

| 圖 3.2.7 以 TT 模式所模擬之雜訊指數.....                   | 25 |

| 圖 3.2.8 以 FF 模式所模擬之雜訊指數.....                   | 25 |

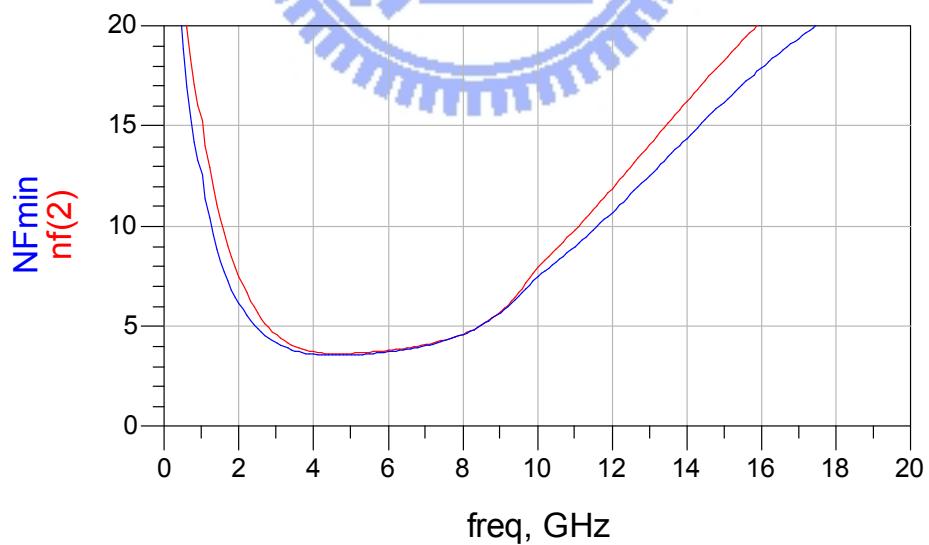

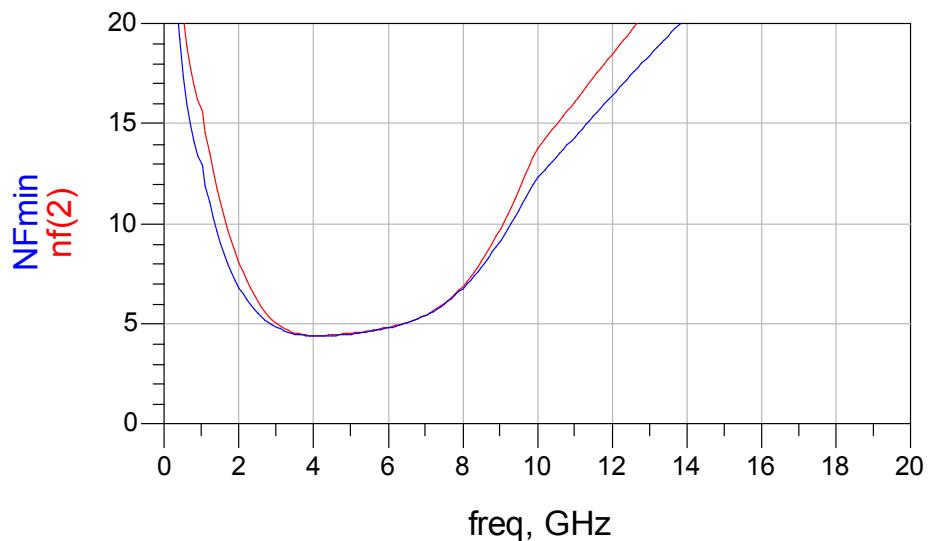

| 圖 3.2.9 以 SS 模式所模擬之雜訊指數.....                   | 26 |

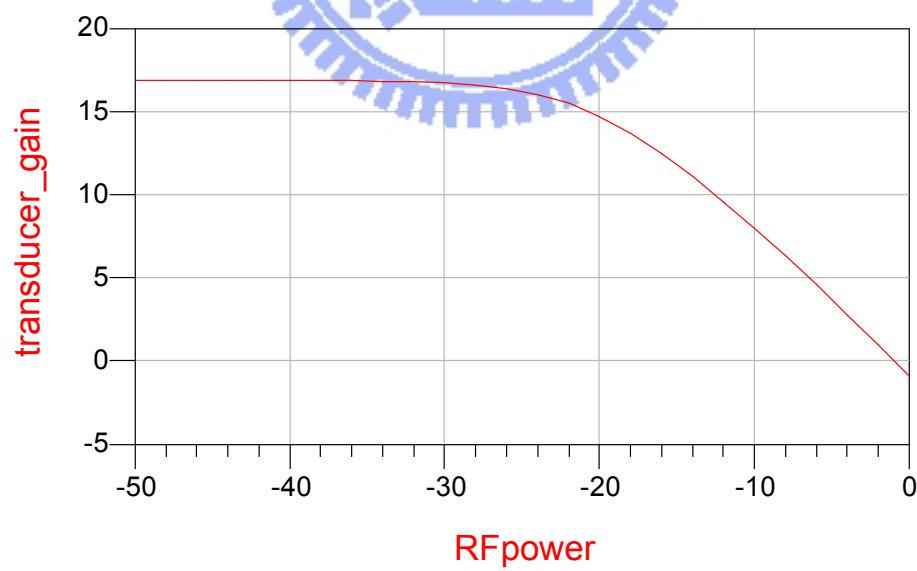

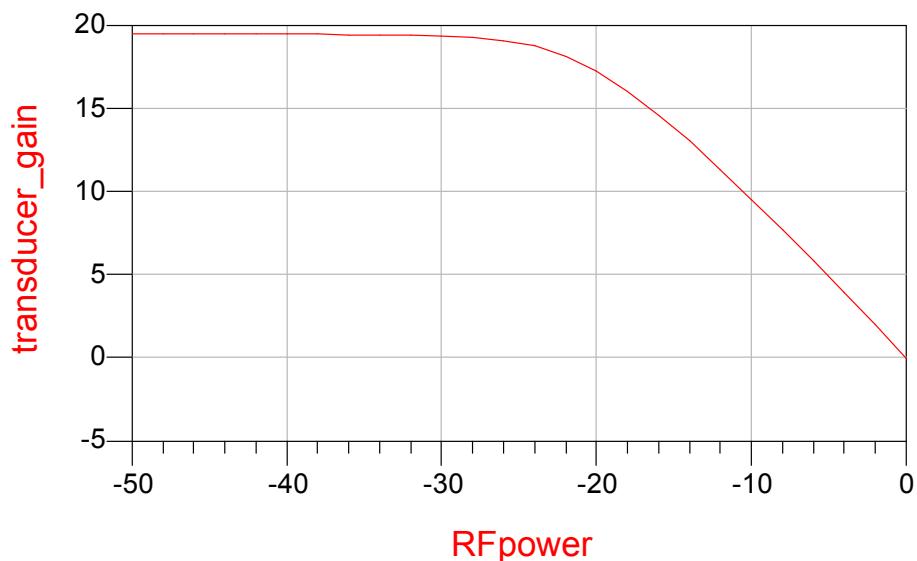

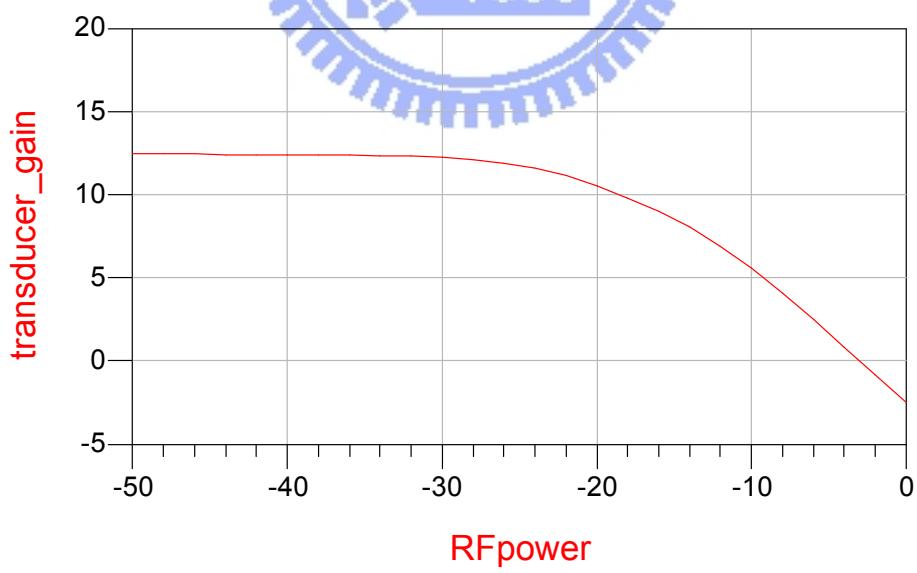

| 圖 3.2.10 以 TT 模式在 5GHz 所模擬之 P1dB.....          | 26 |

| 圖 3.2.11 以 FF 模式在 5GHz 所模擬之 P1dB.....          | 27 |

| 圖 3.2.12 以 SS 模式在 5GHz 所模擬之 P1dB.....          | 27 |

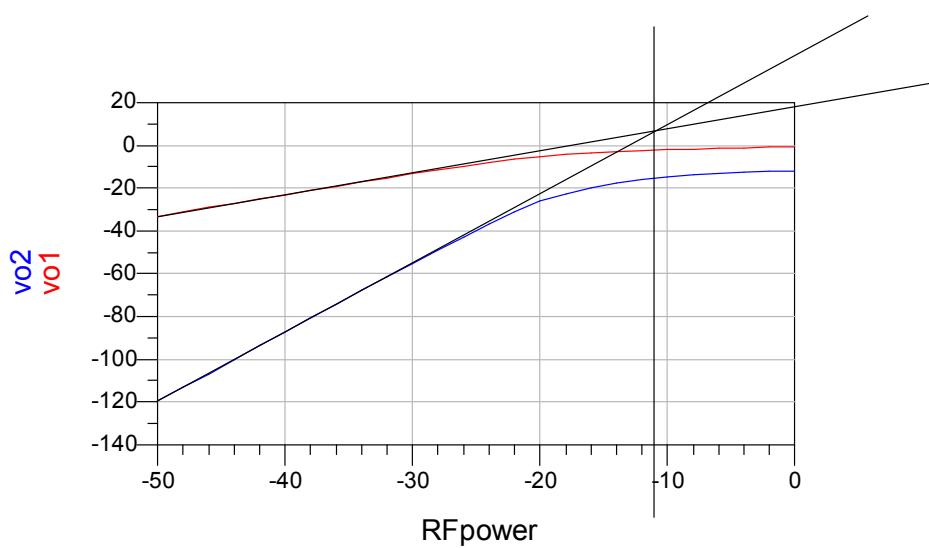

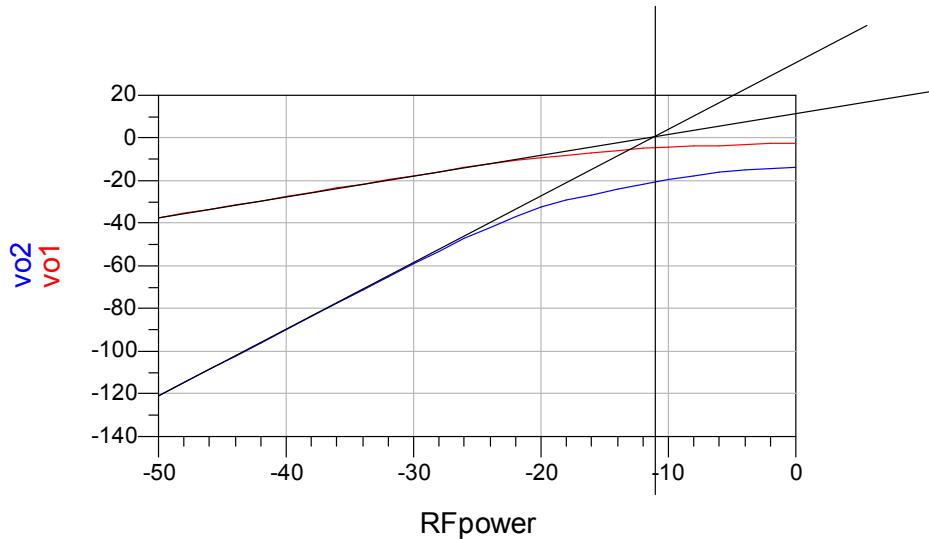

| 圖 3.2.13 以 TT 模式在 5GHz 所模擬之 IIP3.....          | 28 |

| 圖 3.2.14 以 FF 模式在 5GHz 所模擬之 IIP3.....          | 28 |

# 第一章

## 緒論

### 1.1. 動機

近年來因半導體製程的進步，使得無線通訊電路可得以朝向手持式裝置（Hand-Held）的方向發展，進而帶動各式無線通訊規格的蓬勃發展。然而在無線通訊中，並不像有線通訊一樣，可以利用傳輸線來傳輸資料，任何無線通訊都必須利用頻譜（Spectrum）做為通道以傳輸資料。而頻譜是自然界中做重要的資產，它無法像有線通訊一樣可以任意擴充，所以目前無線通訊的頻率均需往高頻發展，以得到更多的頻段以供利用。

目前較為熱門的消費性無線通訊產品從早期全球移動通信系統（Global System for Mobile Communications；GSM），到近年來無線區域網路（Wireless Local Area Networks；WLAN）、全球定位系統（Global Positioning System；GPS）、數位廣播（Digital Video Broadcasting；DVB），甚至是超寬頻（Ultra-Wideband；UWB）無不就是希望在有限的頻譜中，利用最小的頻寬下，傳送最大的資料。

表 1.1.1 為 GSM、WLAN 及 UWB 之相關規格。

表 1.1.1 無線通訊標準之相關規格

| Standards         | GSM                                                                                                          | WLAN<br>IEEE 802.11 a, b, g<br>IEEE 802.11n                                                                               | UWB            |

|-------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------------|

| Frequency Range   | GSM 850：<br>UL : 824 ~ 849 MHz<br>DL : 869 ~ 894 MHz<br>GSM 900：<br>UL : 890 ~ 915 MHz<br>DL : 935 ~ 960 MHz | IEEE 802.11 b, g, n：<br>2.4 ~ 2.497 GHz<br>IEEE 802.11 a, n：<br>5.15 ~ 5.35 GHz<br>IEEE 802.11 a, n：<br>5.725 ~ 5.825 GHz | 3.1 ~ 10.6 GHz |

| Modulation        | GMSK<br>8PSK<br>QPSK<br>16QAM<br>32QAM                                                                       | BPSK<br>QPSK<br>16QAM<br>64QAM                                                                                            | QPSK           |

| Multiple Access   | TDMA/FDMA                                                                                                    | OFDM<br>CSMA/CA                                                                                                           | OFDM           |

| Channel Bandwidth | 200 kHz                                                                                                      | 20 MHz                                                                                                                    | 528 MHz        |

| Peak Data Rate    | 14.4 kbits/s                                                                                                 | 54 Mbits/s                                                                                                                | 480 Mbits/s    |

本文將以台灣積體電路製造股份有限公司 (TSMC) 製程中的 0.18um CMOS 模型設計超寬頻 (Ultra-Wideband) 放大器。在實現超寬頻放大器電路設計後，將放大器前級加入以被動元件 (Passive Component) 所設計的寬頻濾波器，以探討此電路架構在 CMOS 製程中實現。

## 1.2. 論文組織

本論文內容分為四個章節；第一章為緒論，說明本文之動機及論文結構，第二章將詳述此寬頻低雜訊放大器與寬頻濾波器的設計原理與概念，第三章將說明

寬頻低雜訊放大器結合寬頻濾波器模擬的結果，最後一章為此論文的總結。

# 第二章

## 寬頻低雜訊放大器與寬頻濾波器

### 設計

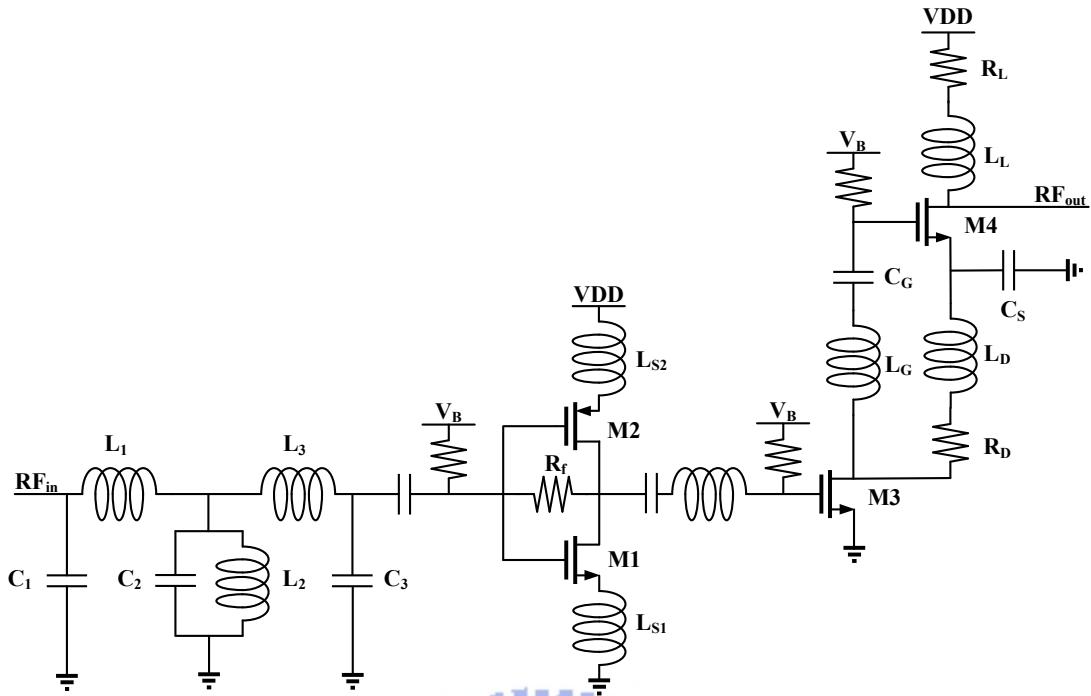

在設計寬頻低雜訊放大器時，首先要考慮到要求頻率範圍內的增益平坦（Gain Flatness）的要求，即希望能夠在設計頻寬中的增益皆有共同的大小。而且功率損耗（Power Consumption）、雜訊指數（Noise Figure）、P1dB（1 dB Compression Point）及 IIP3（3rd-order intercept point）的特性也必須列入設計的考量之中。

為實現寬頻低雜訊放大器的設計，在電路設計上採用兩級放大器架構，如圖 2.1 所示。第一級放大器為由 CMOS 反向器（Inverter）放大器，回授電阻（Resistive feedback）與源級衰退電感（Source Degenerated Inductor）所組成的放大器架構。第二級放大器為兩個 NMOS 疊接（Cascode）的共源級（Common Source）放大器架構。此兩級放大器均各別採用共用電流（Current-Reused）方式以降低電路的功率損耗。並在放大器電路前級加入寬頻濾波器以達成快速衰減頻寬以外之信號功能。

圖 2.1 寬頻低雜訊放大器結合寬頻濾波器之電路設計圖

## 2.1. 寬頻低雜訊放大器之輸入阻抗分析[13]

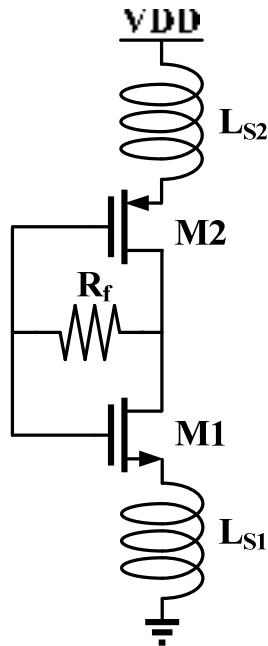

第一級放大器為由 CMOS 反向器 (Inverter) 放大器、回授電阻 (Feedback Resistor) 以及源級衰退電感 (Source Degenerated Inductor) 所組成的放大器架構，如圖 2.1.1 所示， $R_f$  即為回授電阻。在直流分析時， $R_f$  可形成汲極迴授 (Drain feedback) 電路，可使得  $M_1$  及  $M_2$  均工作於飽和區 (Saturation Region)，以形成放大器架構；在交流分析時， $R_f$  可匹配輸入電阻及電壓增益。當此放大器在飽和區工作時，其流經  $M_1$  及  $M_2$  之電流為同一組電流，即為共用電流方式 (Current-Reused)，可降低電路的功率損耗。

圖 2.1.1 第一級放大器電路架構

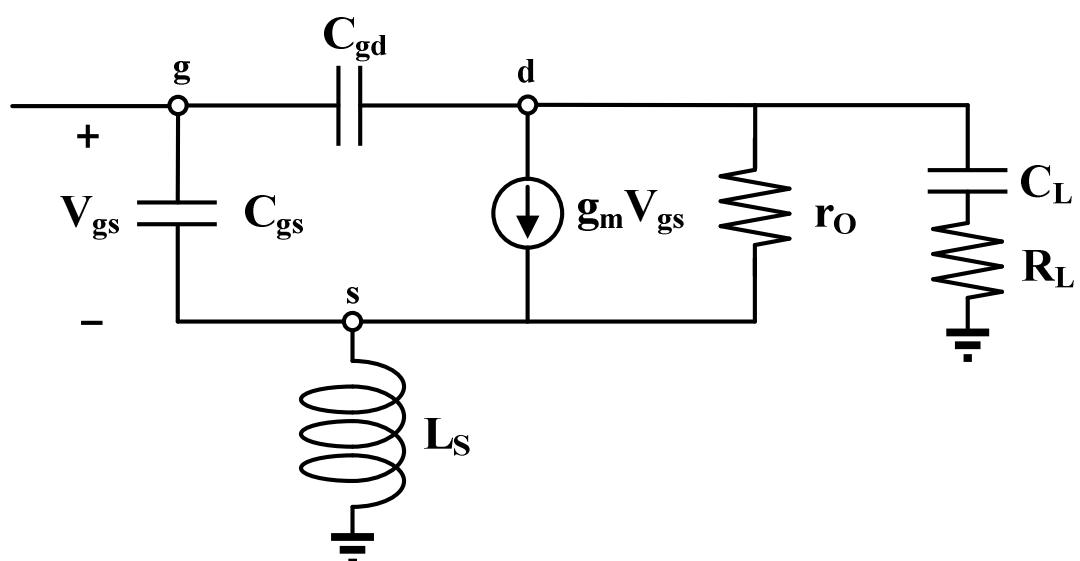

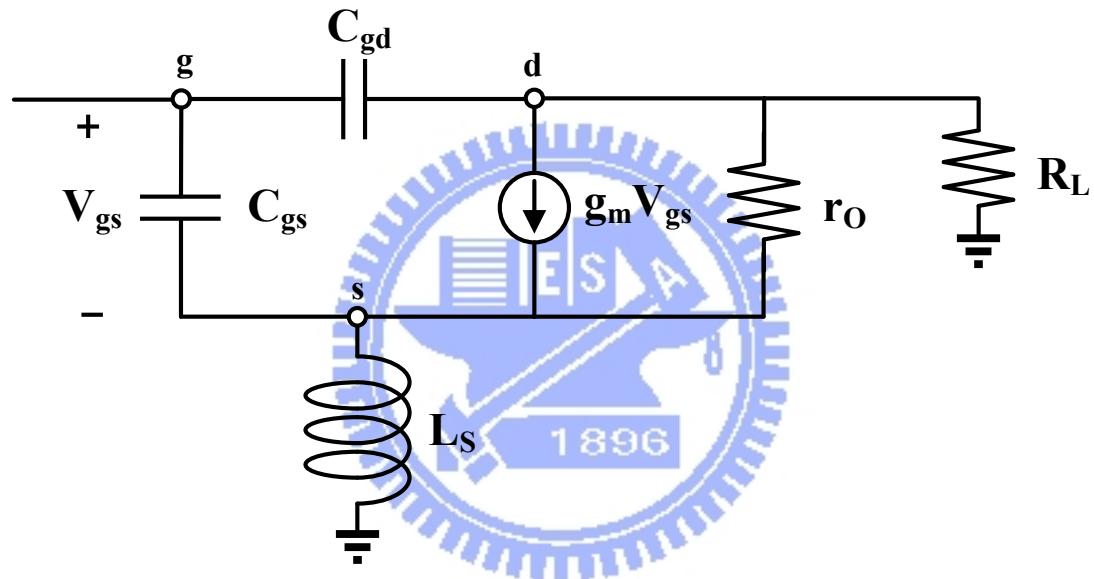

為說明第一級放大器可達成寬頻的輸入匹配特性，在此以第一級放大器中  $M_1$  的完整小訊號模型加上負載說明，如圖 2.1.2 所示。其中  $R_L$  及  $C_L$  即為第二級放大器之寄生電容及寄生電阻，在此當作第一級放大器的負載。

圖 2.1.2 第一級放大器  $M_1$  連接負載時之小訊號模型

首先說明高頻響應時之輸入阻抗分析，如圖 2.1.3 所示。此時負載僅為  $R_L$  之效應。若將  $C_{gd}$  及  $r_o$  忽略，且假設  $C_{gs}$  之阻抗遠大於  $L_S$  之阻抗的條件之下，則圖 2.1.3 所形成的輸入阻抗可近似為：

$$Z_{in} = \frac{1}{j\omega C_{gs}} + \frac{L_s(g_m + j\omega C_{gs})}{C_{gs}} \approx \frac{1}{j\omega C_{gs}} + \frac{L_s g_m}{C_{gs}} \quad (2.1)$$

圖 2.1.3 分析電阻性負載時之輸入阻抗所形成之小訊號模型等效電路圖

由 (2.1) 式可得知當相依電流  $g_m V_{gs}$  流經電感  $L_S$  時將產生與輸入電流同相位 (In Phase) 之電壓，此時可產生其值為  $L_S g_m / C_{gs}$  之輸入電阻。當較小之  $C_{gd}$  將會增加有效輸入電容，且當一有限值  $r_0$  將會衰退  $g_m$ ，並且會降低由  $L_S$  所產生之輸入阻抗的實部。因此，(2.1) 式之較為理想的表示式為：

$$Z_{in} \approx \left( \frac{1}{j\omega C_{gs}} + \frac{L_S \gamma g_m}{C_{gs}} \right) \left[ 1 + \frac{C_{gd}}{C_{gs}} (1 + \gamma g_m R_L) \right]^{-1} \quad (2.2)$$

上式之假設條件為  $\omega L_s \ll \frac{1}{\omega C_{gs}}$  、  $\omega L_s \ll R_L$  且流經  $C_{gd}$  之洩漏電流

(Leakage Current) 遠小於汲級電流時。

其中  $\gamma$  在此定義為衰退因子 (Degradation Factor)，如 (2.3) 式。

$$\gamma = \frac{r_o}{r_o + R_L + j\omega L_s} \quad (2.3)$$

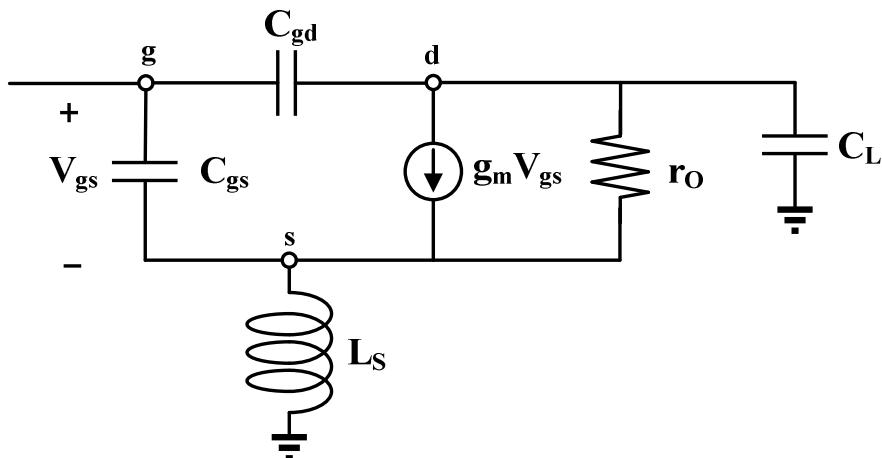

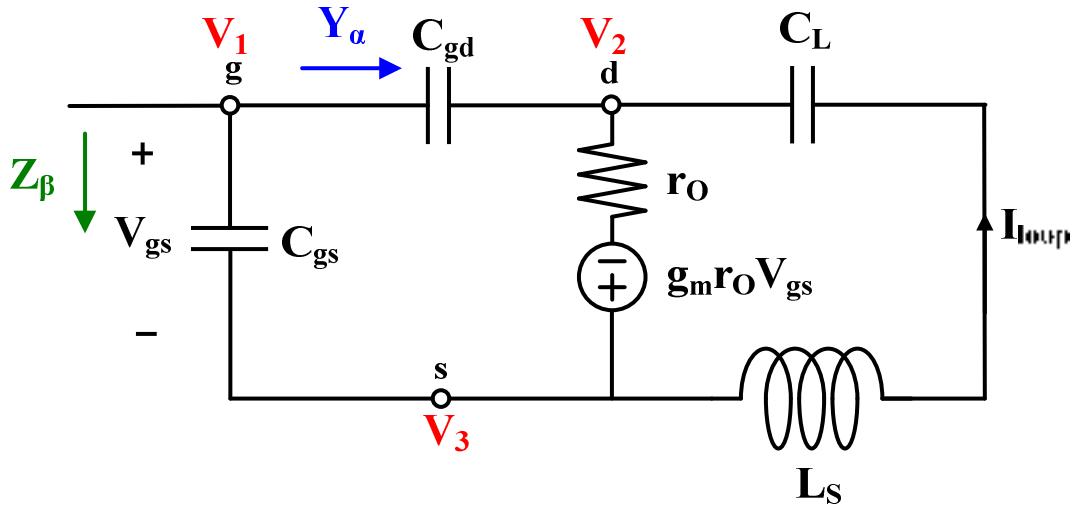

接下來說明低頻響應時之輸入阻抗分析，如圖 2.1.4 所示。此時負載僅為  $C_L$  之效應。在此先將相依電流源  $g_m V_{gs}$  轉變成相依電壓源  $g_m r_o V_{gs}$ ，如圖 2.1.5 所示。其中  $Y_\alpha$  為從  $C_{gd}$  分支看入所形成的導納，而  $Z_\beta$  為從  $C_{gs}$  分支看入後所形成的阻抗， $V_1$ 、 $V_2$  及  $V_3$  分別為 MOS 之 G、D 及 S 端點之電壓。若相依電流  $g_m V_{gs}$  遠大於流經  $C_{gd}$  或  $C_{gs}$  之電流時，則迴路電流  $I_{loop}$  可被近似為：

$$I_{loop} = g_m r_o V_{gs} \left[ r_o + \frac{1}{j\omega C_L} + j\omega L_s \right]^{-1} \quad (2.4)$$

圖 2.1.4 分析電容性負載時之輸入阻抗所形成之小訊號模型等效電路圖

圖 2.1.5 將相依電流源  $g_m V_{gs}$  轉變成相依電壓源  $g_m r_o V_{gs}$  後之等效電路圖

因此，從  $C_{gd}$  分支看入時所形成的導納  $Y_\alpha$  為：

$$Y_\alpha = j\omega C_{gd} \frac{V_1 - V_2}{V_1} = j\omega C_{gd} + \left( R_\alpha + \frac{1}{j\omega C_\alpha} + j\omega L_\alpha \right)^{-1} \quad (2.5)$$

其中：

$$R_\alpha = \frac{C_L}{g_m C_{gd}}$$

$$C_\alpha = g_m r_o C_{gd}$$

$$L_\alpha = \frac{L_s C_L}{g_m r_o C_{gd}} (1 + g_m r_o) \quad (2.6)$$

而從  $C_{gs}$  分支看入時所形成的阻抗  $Z_\beta$  為：

$$Z_\beta = \frac{1}{j\omega C_{gs}} \frac{V_1}{V_1 - V_3} = \frac{1}{j\omega C_{gs}} + \left( \frac{1}{R_\beta} + j\omega C_\beta + \frac{1}{j\omega L_\beta} \right)^{-1} \quad (2.7)$$

其中：

$$\begin{aligned} R_\beta &= \frac{g_m L_s}{C_{gs}} \\ C_\beta &= \frac{C_{gs}}{g_m r_o} \\ L_\beta &= \frac{L_s g_m r_o C_L}{C_{gs}} \end{aligned} \quad (2.8)$$

因此，可由  $Y_\alpha$  及  $Z_\beta$  的關係中得知電容性負載時所形成之輸入阻抗為：

$$Z_{in} = \left( Y_\alpha + \frac{1}{Z_\beta} \right)^{-1} \quad (2.9)$$

## 2.2. 寬頻濾波器之工作原理及設計

在高頻濾波器之設計與製作上，常見的濾波器設計為巴特渥斯 (Butterworth) 以及柴比雪夫 (Chebyshev) 二種架構。選用巴特渥斯架構的優點是在通過頻帶 (Pass Band) 內有較佳的平坦度，而缺點則為在截止頻帶 (Stop Band) 具有漣波 (Ripple) 現象且轉態帶 (Transition Band) 的衰減變化並不陡峭。柴比雪夫架構的優點是在轉態帶的衰減變化比巴特渥斯陡峭快速，而且截止頻帶內不會有漣波現象產生，缺點則為通過頻帶內較不平坦，且具有大小相同的漣波現象產生，所以柴比雪夫濾波器亦稱為同漣波 (Equal ripple) 濾波器。兩者濾波器架構皆利用電感及電容元件以實現濾波器的設計。

在下列各節中將詳述在 COMS 製程中平面螺旋電感及電容的原理並將其應用於寬頻濾波器設計之實現

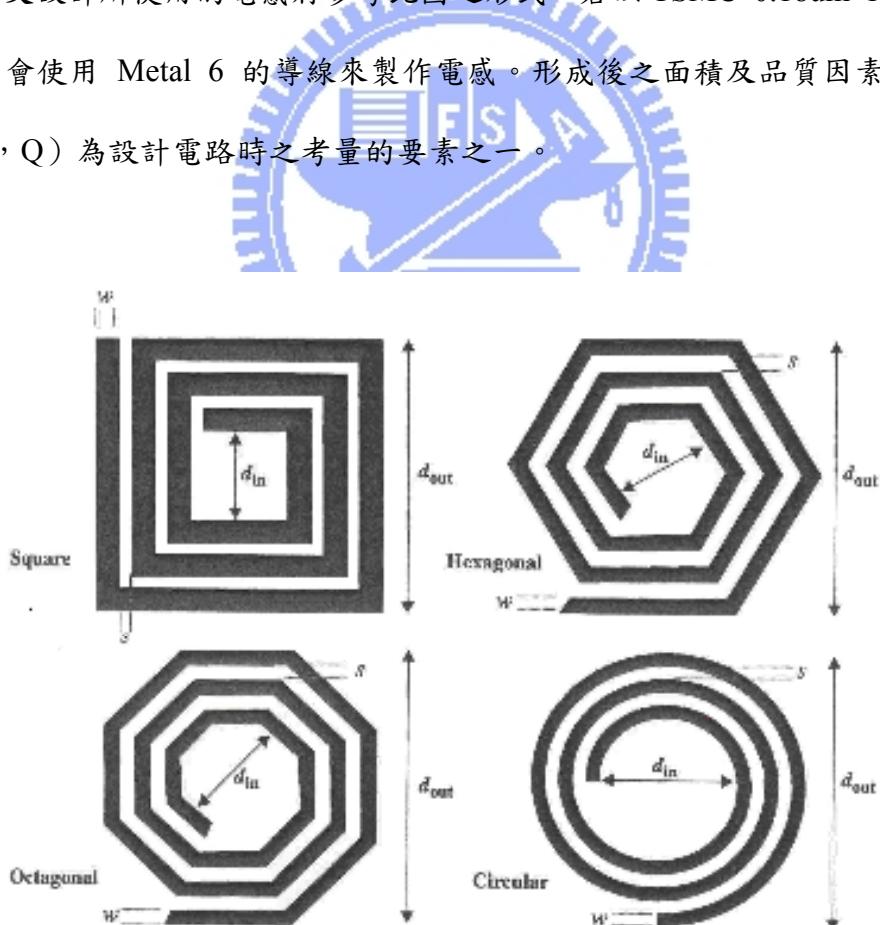

### 2.2.1. 平面螺旋電感 [2]

電感由早期的含鐵心的繞線式電感，到目前的晶片型電感（Chip Inductor），其演進的目的亦為縮小面積的目標而努力。而拜半導體製程的進步之賜，現今電感也可在積體電路中實現。其方式為亦為以基底（Substrate）為介質，利用金屬線形成平面螺旋（Spiral）方式實現，其平面螺旋電感常見的形式如圖 2.2.1.1 所示，本文設計所使用的電感將參考此圖之形式。若以 TSMC 0.18um 1P6M 製程為例，會使用 Metal 6 的導線來製作電感。形成後之面積及品質因素（Quality Factor, Q）為設計電路時之考量的要素之一。

圖 2.2.1.1 常見的平面螺旋電感形式

## 2.2.2. 電容

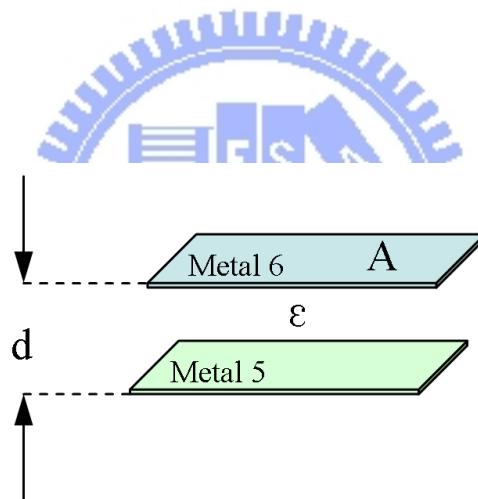

電容器的基本原理為利用兩個平行金屬板結構並且在平行金屬板中加上適當介質後即可形成一個電容器，如圖 2.2.2.1。利用此原理，同樣可在 CMOS 製程中製造出電容。而在實現上通常以 Metal 6 以及 Metal 5 兩層金屬層作為平行金屬板，而平行板中以高介電常數之絕緣材料之結構，此結構產生之電容亦稱為 MIM 電容（Metal-Insulator-Metal）。而按照平行結構電容基本公式，如 (2.10) 式，改變平行板之面積後即可改變電容值。

$$C = \varepsilon \frac{A}{d}$$

圖 2.2.2.1 平行金屬板結構電容

## 2.2.3. 寬頻濾波器設計

在 [6] [7] 中，同樣使用電感及電容元件在放大器前級以形成匹配電路，但卻不具有濾波器之功能。本文提出一雙  $\pi$  型（Double- $\pi$ ）濾波器架構，不僅將電感及電容元件置於放大器前級用以匹配輸入阻抗外，還實現了寬頻濾波器的設計。

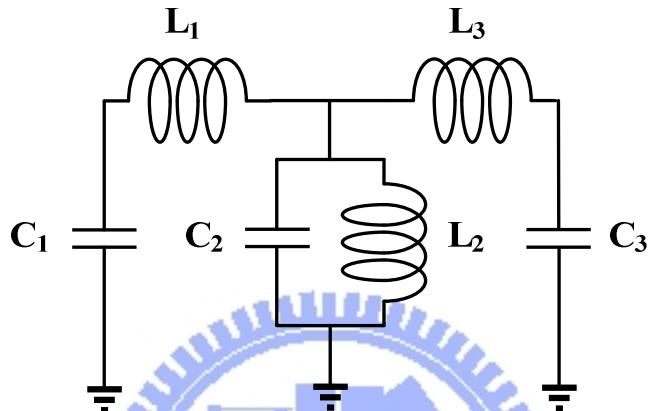

此雙  $\pi$  型濾波器即為一種帶通濾波器（Band-pass filter）的設計，其頻率範圍設計在 3-8 GHz，在設計上使用三階共振電路設計。在通過頻帶內具有良好的平坦度，沒有漣波現象的產生，而且轉態帶的衰減變化也具快速陡峭的變化。本寬頻濾波器架構如圖 2.2.3.1 所示。

圖 2.2.3.1 本文所提出之雙  $\pi$  型寬頻濾波器架構

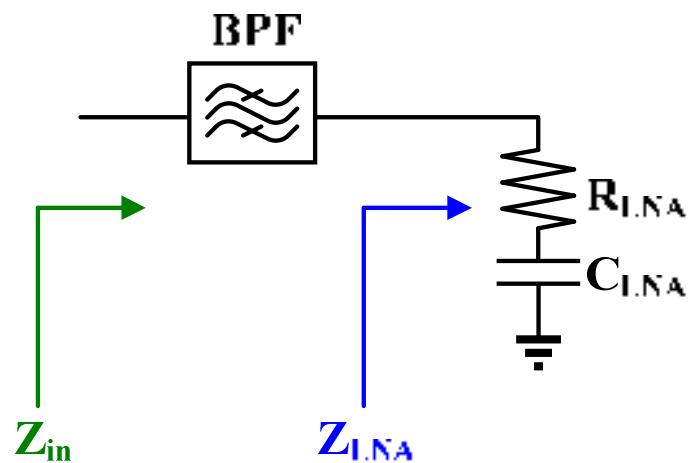

而在分析完整放大器之輸入阻抗時，需考慮由寬頻放大器電路之輸入阻抗 ( $Z_{LNA}$ ) 加上濾波器之輸入阻抗產生之匹配特性 ( $Z_{in}$ )，如圖 2.2.3.2 所示。而在分析寬頻放大器之輸入阻抗後，其為一 RC 等效電路架構，如圖 2.2.3.3 所示。而將寬頻濾波器電路加入寬頻低雜訊放大器電路前級後，可將寬頻低雜訊放大器之輸入阻抗匹配至特性阻抗，如圖 2.2.3.4 所示。

圖 2.2.3.2 分別考慮寬頻低雜訊放大器之輸入阻抗及加上寬頻濾波器之輸入阻抗示意圖

圖 2.2.3.3 寬頻低雜訊放大器之輸入阻抗

圖 2.2.3.4 寬頻濾波器結合寬頻低雜訊放大器後之輸入阻抗

而利用寬頻濾波器完成輸入阻抗匹配之後，考慮在高頻響應時須產生濾波器特性之電路，如圖 2.2.3.5 所示。其中原寬頻濾波器中之  $L_2$  在高頻時已產生開路效應，此時利用  $C_1$ 、 $C_2$  及  $C_3$  在高頻時可與  $L_1$  及  $L_2$  產生共振，結合寬頻低雜訊放大器之輸入阻抗時，可產生 LC 低通濾波器之效果，進而使放大器之增益在高頻時能有明顯之轉折頻率（Corner frequency）產生。

圖 2.2.3.5 寬頻濾波器在高頻響應時之等效電路

### 2.3. 寬頻放大器之增益分析[6, 12]

第二級放大器為兩個 NMOS 皆以共源級放大器組態疊接 (Cascode) 而成的放大器架構，如圖 2.3.1 所示。 $L_D$  與  $R_D$  為共源級放大器  $M_3$  的負載， $R_L$  與  $Z_L$  則為共源級放大器  $M_4$  的負載。 $C_G$  為耦合 (Coupling) 電容， $C_S$  為旁路 (Bypass) 電容。

圖 2.3.1 第二級放大器電路架構

此放大器為兩級 CS 組態放大器利用  $L_G$  以形成中間級耦合 (Inter-Stage Coupling) 以及共用電流 (Current-Reused) 的放大器架構。 $L_G$  用以被調整與  $M_4$  之  $C_{gs}$  形成串聯諧振 (Series Resonance) 電路，達成兩組放大器間訊號之偶合，以將信號傳遞至輸出端。其中  $L_G$  及  $C_G$  會在在共振頻率下且在所需頻寬內使共用電流 (Current Reuse) 形成最大值。 $R_L$  及  $L_L$  為並聯尖峰 (Shunt Peaking) 之設計方式，其可提供延伸所設計之高頻頻寬。

若忽略  $M_4$  之  $C_{gs}$  下，以  $M_3$  之 Drain 為輸入端，到  $M_4$  之 Drain 為輸出端所形成的小信號模型則為圖 2.3.2 所示。

圖 2.3.2 第二級放大器電路之小訊號模型

其電流增益如 (2.11) 式所示：

$$\frac{i_{d4}}{i_{d3}} = \frac{g_{m4}}{sC_{gs4}} \frac{sL_D + \frac{1}{sC_D}}{sL_D + sL_G + \frac{1}{sC_D} + \frac{1}{sC_G} + \frac{1}{sC_{gs4}}} \quad (2.11)$$

從 (2.11) 式可得知，當  $L_D$  與  $C_D$  形成高阻抗且  $L_G$  與  $C_{gs4}$  形成共振時，則可近似為 (2.12) 式。其中  $\omega_T$  為  $M_4$  的截止頻率 (Cutoff Frequency)，而  $\omega$  則為輸入操作頻率。在此可發現 (2.12) 式中與  $M_4$  之尺寸大小無關，換言之，可利用較小尺寸  $M_4$  以得到較高頻之截止頻率，進而得到較高之線性度 (Linearity)。

$$\frac{i_{d4}}{i_{d3}} \cong \frac{g_{m4}}{sC_{gs4}} \cong \frac{\omega_T}{\omega} \quad (2.12)$$

在完成電路設計後，在此說明本文加入寬頻濾波器設計之優點。在此以圖 2.3.3 說明。為使無線通訊接收機接收所需頻帶內的訊號，並隔絕頻帶以外的信號，濾波器的設計顯得格外重要，在寬頻低雜訊放大器中，雖然在 3-12 GHz 內

具有較大的增益，但在頻帶以外的訊號（含雜訊）也會經過放大器電路跟著放大，此時勢必會影響操作頻段中待放大訊號的品質。若將濾波器加入低雜訊放大器的前級，則在所設計的操作頻率（3-8 GHz）以外的訊號已呈現衰減現象。換言之，頻帶以外的信號及雜訊也被衰減，因此可提升頻帶內待放大訊號的品質。

圖 2.3.3 本文所設計之寬頻低雜訊放大器結合寬頻濾波器與否之增益比較圖

# 第三章

## 寬頻低雜訊放大器結合寬頻濾波 器模擬

### 3.1. 佈局考量

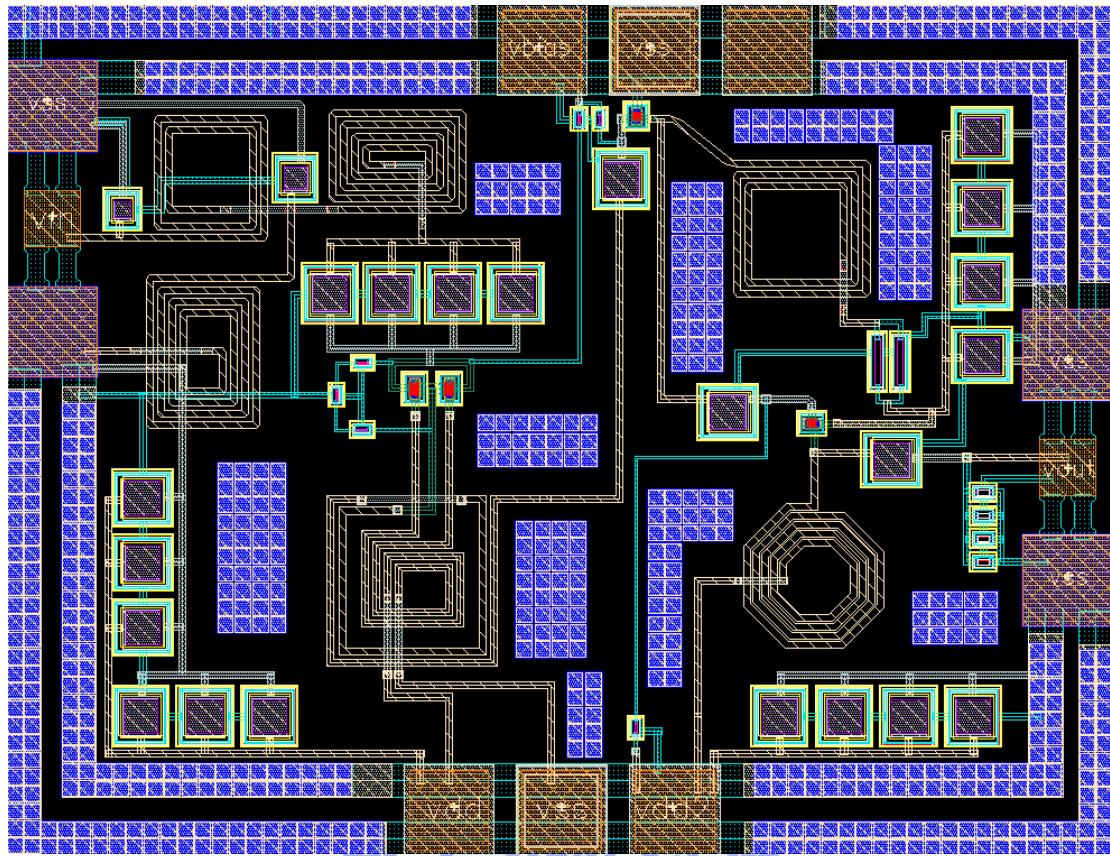

在完成寬頻放大器及寬頻濾波器之電路設計後，即可進行電路佈局（Layout）。導線（Trace）之長度需越短越好，以避免產生過大之損耗及產生過大的寄生的電感及電容效應。若導線過長時，將將導線之效應代入電磁模擬軟體模擬後，再帶回電路中與設計電路一併考量，以確保電路的準確性。直流導線上需加上旁路電容，避免導線產生的電感效應。在完成佈局及電路模擬後，需執行設計規則檢查（Design Rule Check；DRC）和佈局對線路（Layout versus Schematic；LVS）驗證無誤後即完成佈局。在完成佈局後晶片尺寸為  $1.0 \times 0.8$  mm，如圖 3.1.1 所示。

圖 3.1.1 寬頻低雜訊放大器與寬頻濾波器佈局圖 (1.0 × 0.8 mm)

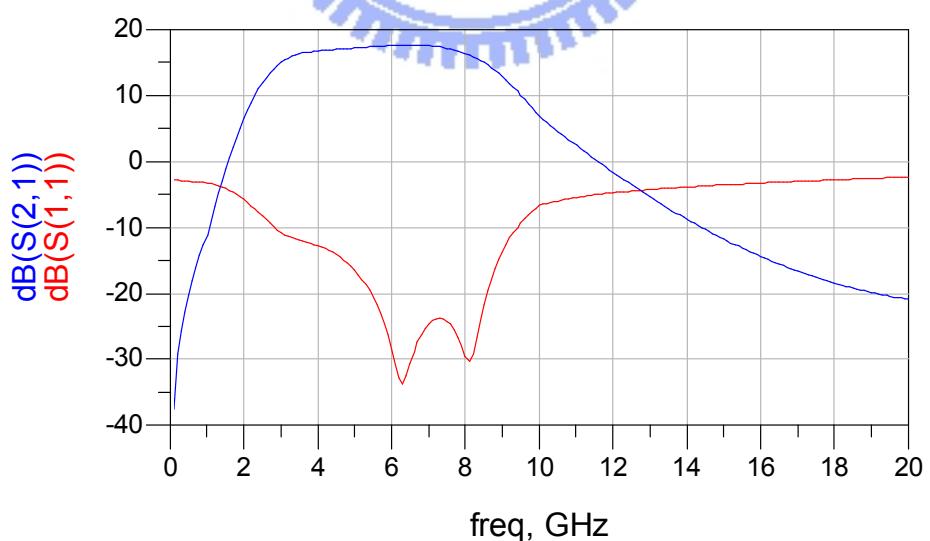

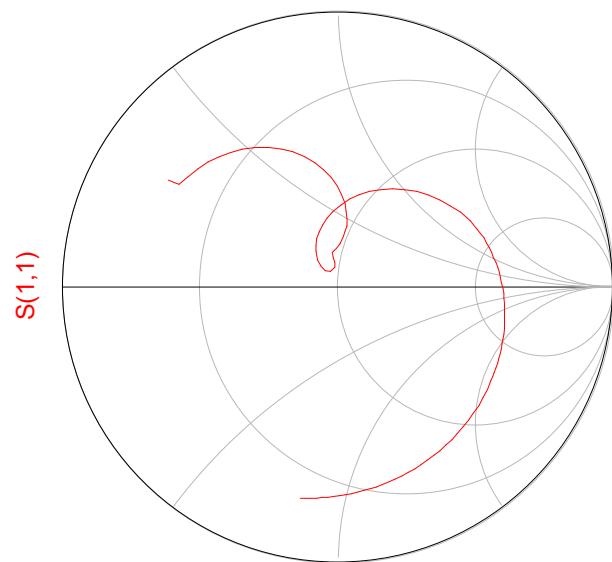

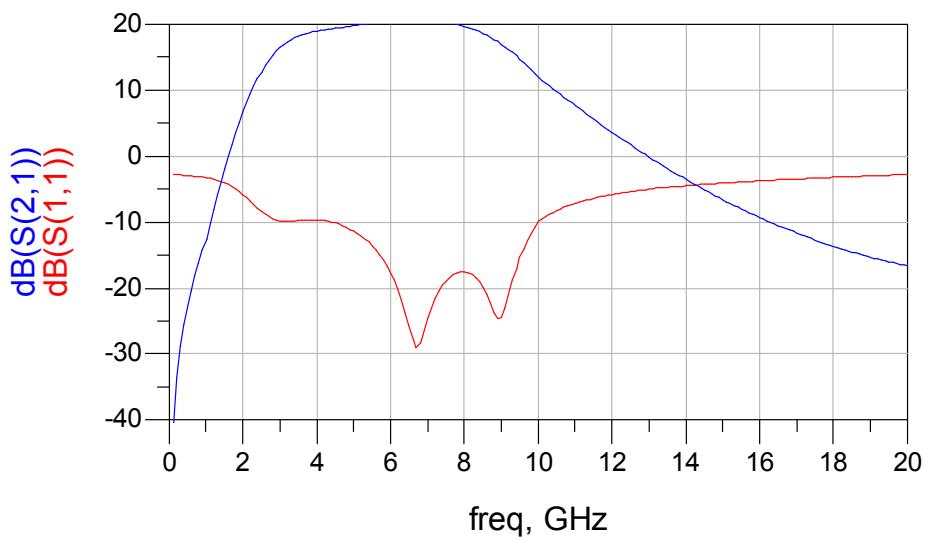

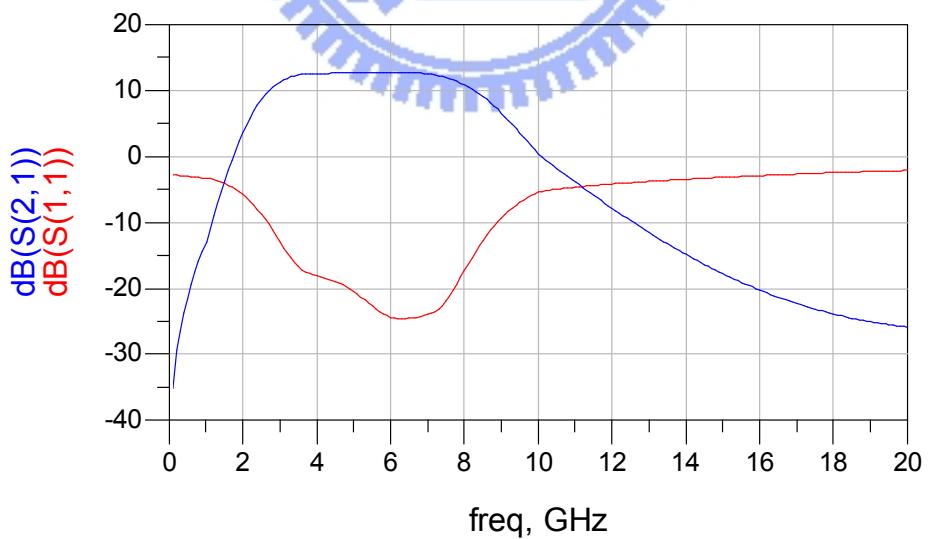

## 3.2. 模擬結果

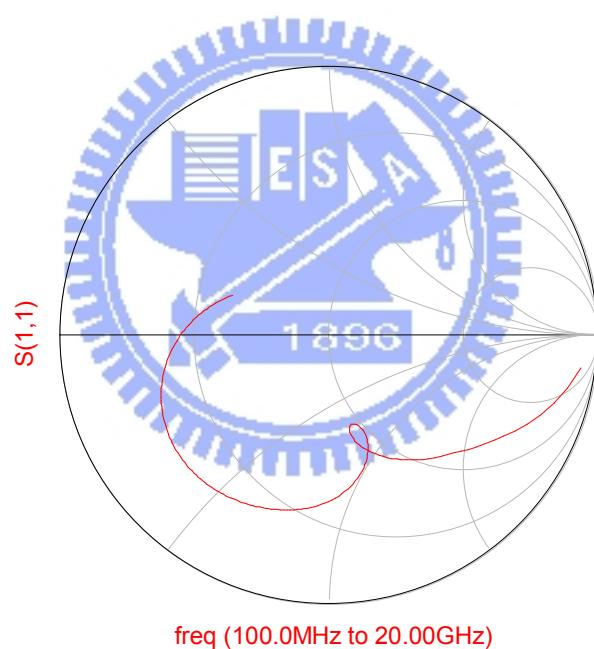

在電路設計階段中之模擬須考慮到製程變異 (Process Corner) 的因素，TSMC 提供三種製程變異模型以供模擬結果參考，分別為快速-快速 (Fast-Fast)，典型-典型 (Typical-Typical) 以及慢速-慢速 (Slow-Slow)，其模擬結果分別如下列各圖所示，並將各製程變異模式所模擬之參數值列於表 3.2.1。

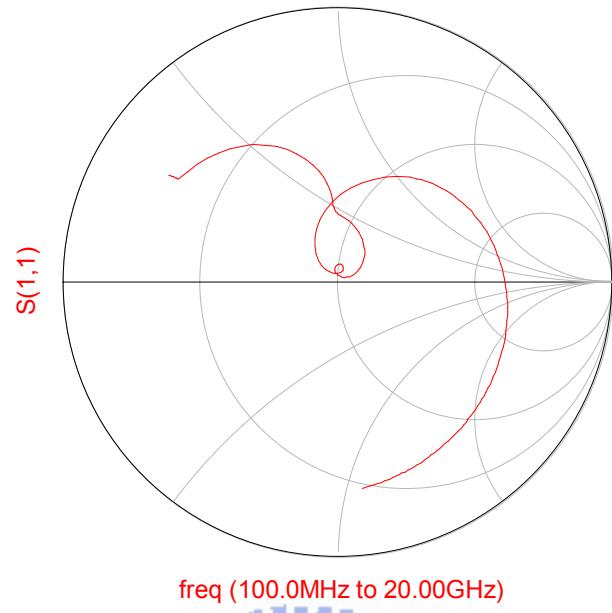

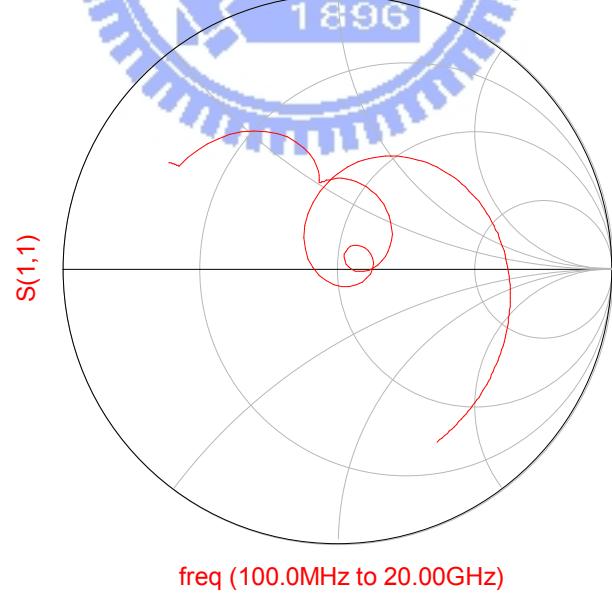

圖 3.2.1 以 TT 模式所模擬之輸入阻抗

圖 3.2.2 以 FF 模式所模擬之輸入阻抗

圖 3.2.4 以 TT 模式所模擬之 S 參數

圖 3.2.5 以 FF 模式所模擬之 S 參數

圖 3.2.6 以 SS 模式所模擬之 S 參數

圖 3.2.7 以 TT 模式所模擬之雜訊指數

圖 3.2.8 以 FF 模式所模擬之雜訊指數

圖 3.2.9 以 SS 模式所模擬之雜訊指數

圖 3.2.10 以 TT 模式在 5GHz 所模擬之 P1dB

圖 3.2.11 以 FF 模式在 5GHz 所模擬之 P1dB

圖 3.2.12 以 SS 模式在 5GHz 所模擬之 P1dB

圖 3.2.13 以 TT 模式在 5GHz 所模擬之 IIP3

圖 3.2.14 以 FF 模式在 5GHz 所模擬之 IIP3

圖 3.2.15 以 SS 模式在 5GHz 所模擬之 IIP3

表 3.2.1 以 TT、FF 及 SS 模式所模擬之參數值

| Mode                | TT      | FF      | SS      |

|---------------------|---------|---------|---------|

| Frequency (GHz)     | 3-8     | 3-8     | 3-8     |

| S11(dB)             | < -10   | < -10   | < -13   |

| S22(dB)             | < -4    | < -4    | < -4    |

| S21(dB)             | > 15    | > 18    | > 10    |

| S12(dB)             | < -50   | < -50   | < -50   |

| NF(dB)              | 4.3-5.4 | 4.1-4.5 | 4.8-6.7 |

| Power (mW)          | 14.25   | 23.26   | 8.39    |

| P1dB(dB)<br>(5 GHz) | -23     | -23     | -23     |

| IIP3(dB)<br>(5 GHz) | -11     | -9.8    | -11     |

表 3.2.2 WB LNA 模擬之參數值比較表

|       | Tech.              | S <sub>11</sub><br>( dB ) | S <sub>21</sub><br>( dB ) | BW<br>( GHz ) | NF <sub>min</sub><br>( dB ) | IIP3<br>( dB )    | P <sub>1dB</sub><br>( dB ) | P <sub>diss</sub><br>( mW ) |

|-------|--------------------|---------------------------|---------------------------|---------------|-----------------------------|-------------------|----------------------------|-----------------------------|

| TT    | 0.18<br>um         | < -10                     | > 15                      | 3-8           | 4.6                         | -11               | -23.4                      | 14.25                       |

| FF    |                    | < -9                      | > 15                      |               | 4.6                         | -9.8              | -23                        | 23.26                       |

| SS    |                    | < -13                     | > 10                      |               | 5.02                        | -11               | -23                        | 8.39                        |

| [ 6 ] | 0.18<br>um<br>CMOS | < -8                      | > 13.5                    | 3.1-10.6      | 3.1                         | -7 <sup>*</sup>   | N/A                        | 11.9                        |

| [ 7 ] | 0.18<br>um<br>CMOS | < -9.9                    | > 9.3                     | 2.3-9.2       | 4.0                         | -6.7 <sup>*</sup> | -15                        | 9                           |

\* at 6 GHz

# 第四章

## 結論

本論文提出了頻寬在 3-8 GHz 之寬頻低雜訊放大器結合寬頻濾波器的電路設計，此設計使用了 TSMC 0.18um CMOS 模型，並且使用高頻模擬軟體 ADS 與 MOMENTUM 模擬其設計，此電路設計完成後已進行電路佈局。其電路佈局已送交國家晶片系統設計中心（CIC）審查以實現晶片設計並進行量測。

在寬頻低雜訊放大器的設計中，使用了兩級的放大器架構，以達到寬頻之特性。在第二級放大器中使用了中間級共振電路架構（Inter-Stage Resonance），以達到寬頻的增益，並使用並聯尖峰(shunt-Peaking)的頻寬延伸技術來完成寬頻特性。而在寬頻濾波器設計上，使用了雙 $\pi$ 型（Double- $\pi$ ）濾波器架構，以實現在頻寬中有平坦增益，而在頻寬外有快速衰減的效果。所設計的寬頻低雜訊放大器的模擬結果如下：頻寬為 3 ~ 8 GHz，平均增益為 16 dB，雜訊指為 4.6 ~ 5.4 dB，輸入反射係數為  $< 12$  dB，input  $P_{1dB}$  最小值為 -23.4 dBm，IIP3 最小值為 -11 dBm，功率消耗為 14.25 mW。

未來本文改善的方向為將此寬頻低雜訊放大器結合寬頻濾波器的電路操作頻率設計在超寬頻（Ultra-Wideband；UWB）的規格中，即為 3.1~10.6 GHz。而輸出反射係數（ $S_{22}$ ）未盡理想，也需將輸出阻抗匹配至特性阻抗以改善其特性。

# 參 考 文 獻

- [1] B. Razavi, RF Microelectronics, Upper Saddle River, NJ: Prentice Hall, 1998

- [2] T. H. Lee, The Design of CMOS Radio Frequency Integrated Circuits. Cambridge University Press, 1998

- [3] David M.Pozar, Microwave Engineering, 2nd ed, John Wiley & SONS, INC., New York, 1998

- [4] Guillermo Gonzaley, "Microwave Transistor Amplifiers analysis and Design second edition", Prentice Hall, 1997

- [5] B. Razavi, Design of analog CMOS Integrated Circuits, McGraw-Hill Education, 2000

- [6] Yi-Jing Lin, Shawn S. H. Hsu, Member, IEEE, Jun-De Jin, and C. Y. Chan, "A 3.1–10.6 GHz Ultra-Wideband CMOS Low Noise Amplifier With Current-Reused Technique" in IEEE MWCL, March 2007

- [7] A. Bevilacqua and A. M. Niknejad, "An ultra-wideband CMOS LNA for 3.1 to 10.6 GHz wireless receiver," in IEEE ISSCC Tech. Dig., 2004, pp. 382–383.

- [8] D. K. Shaeffer and T. H. Lee, "A 1.5-V, 1.5-GHz CMOS Low Noise Amplifier", IEEE Journal of Solid-State Circuits, vol. 32, NO. 5, p745~p759, May 1997

- [9] Friis, H.T. "Noise Figures of Radio Receiver", Proc. of the IRE, July, 1944, pp. 419-422

[10] 張志揚教授, *Microwave Measurement*, 國立交通大學電信工程研究所, 2005

[11] R. G. Arnold, C. C. Faulkner and D. J. Pedder, “Silicon MCM-D Technology for RF Integration”, IEEE Multichip Module Conference, p340~p344, 1997.

[12] Choong-Yul Cha and Sang-Gug Lee, “A 5.2-GHz LNA in 0.35 um CMOS Utilizing Inter-Stage Series Resonance and optimizing the Substrate Resistance”, IEEE Journal of Solid-State Circuits, vol. 38, NO. 4, p669~p672, April 2003

[13] Robert Hu , “Wide-Band Matched LNA Design Using Transistor’s Intrinsic Gate–Drain Capacitor”, IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES, VOL. 54, NO. 3, MARCH 2006.