# Two-Dimensional Simulation of Orientation Effects in Self-Aligned GaAs MESFET's

SHIH-HSIEN LO, STUDENT MEMBER, IEEE, AND CHIEN-PING LEE, MEMBER, IEEE

Abstract—The stress-induced orientation effects in self-aligned GaAs MESFET's have been studied using a two-dimensional analysis. Devices oriented along different crystal directions, with different gate lengths, and under different stress conditions were studied. It was found that the piezoelectric effect caused by the surface stress plays a very important role in the device characteristics of short-channel self-aligned MESFET's. Structure parameters such as lateral spreading of N<sup>+</sup> ions and p-type impurity concentration in the substrate were found to have great influence on the short-channel effect as well as the orientation effect. The short-channel effects can be suppressed and the device performance improved if the devices are oriented in the right direction and the structure of the devices and the thickness of the surface dielectric layer are properly chosen.

#### Nomenclature

- Distance between the edge of N<sup>+</sup> implant to the  $a_0$ center of the gate.

- Electron diffusion coefficient.

- Dielectric film thickness.

- $= 2.69 \times 10^{-17} \text{ C/dyn}.$

- $E_c$   $E_0$   $E_t$   $I_{ds}$   $J_n$  k  $L_g$   $L_{gd}$   $L_{sg}$   $N_c$   $N_d$ Energy of the bottom of conduction band.

- Critical field.

- Energy level of the deep donor "EL-2."

- Drain-source current.

- Electron current density.

- Boltzmann's constant.

- Gate length.

- Distance between the gate and the drain.

- Distance between the gate and the N<sup>+</sup> region.

- Distance between the source and the gate.

- Acceptor concentration.

- Effective density of states of conduction band.

- Donor concentration.

- Piezoelectric charge density.

- Peak density of implanted profile.

- Deep-donor EL-2 density.

- Ionized deep-donor EL-2 density.

- Electron density.

- $\frac{q}{R_p}$ Electron charge.

- Projected range.

- Ŕ, Lateral straggle parameter.

- T Absolute temperature.

- Drain-source voltage.

Manuscript received June 1, 1989; revised January 1, 1990. The review of this paper was arranged by Associate Editor S. S. Pei.

The authors are with the Institute of Electronics, National Chiao Tung University, Hsin Chu, Taiwan, ROC.

IEEE Log Number 9037520

Gate-source voltage.

Threshold voltage.

Electron saturation velocity.  $v_{ns}$

Electrostatic potential.

Dielectric permittivity.

= 390 electrons / dyn.  $\gamma_b$

Stress induced by the dielectric overlayer.

β = 0.59.

Low-field electron mobility.  $\mu_{n0}$

Electron mobility.

Straggle parameter.  $\Delta R_n$

#### I. Introduction

T HAS BEEN known for some time that the electrical Lectural characteristics of GaAs MESFET's depend on the orientation of the gate with respect to the substrate [1]. The threshold voltage, the drain current, and even the device uniformity depend on the gate orientation. The threshold voltage shift at small gate lengths, commonly known as the short-channel effect, is also orientation-dependent. These interesting phenomena, which do not exist for Si FET's, are due to the nature of the zinc-blende crystal structure of GaAs. Because this orientation effect has a large impact on device performance and circuit yield, a lot of work have been done in trying to understand and control this effect [2]-[7]. Initially, it was attributed to an anisotropic stress-enhanced lateral diffusion of N<sup>+</sup> impurities from the source and the drain regions into the channel [2]-[4]. In 1984, Asbeck et al. proposed a different explanation which attributed the orientation dependence to the surface stress induced piezoelectric effect [8]. They found that the stress caused by the dielectric overlayer on GaAs MESFET's produces a considerable amount of piezoelectric polarization charges that can effectively vary the doping profile in the FET's channel and therefore shift the threshold voltage and the drain current. This explanation has since been verified experimentally by several authors [6], [7].

In the past the influence of the stress on the FET characteristics was studied mostly with one-dimensional analysis. The threshold voltage shift caused by the piezoelectric effect was estimated by integrating the contributions of the piezoelectric charges in the FET's channel under the midpoint of the gate [8]-[10]. However, the strain field, the piezoelectric charge distributions, as well as the carrier transport in the channel of the FET are two-dimensional problems. This is especially true for selfaligned MESFET's and short-gate devices, in which the stress is strong and the short-channel problem is severe. So, for a better understanding of the influence of the stress on FET characteristics, a full two-dimensional analysis is needed. Onodera *et al.* have implemented the Asbeck's piezoelectric model into a two-dimensional simulator for GaAs MESFET to study the orientation effect in GaAs MESFET's and their results were in fair agreement with experimental results [11].

In self-aligned GaAs MESFET's, especially those with short gates, the device characteristics depend very much on the device structure and substrate properties. In order to obtain a clear understanding of the short-channel behavior of these devices, one has to take all the structure parameters as well as the piezoelectric effect into consideration. In self-aligned MESFET's, one of the most important structure parameters is the amount of lateral spreading of N<sup>+</sup> implant into the n channel. This amount, however, depends on the self-aligned structure used. The refractory metal gate structure normally has the N<sup>+</sup> implant right next to the gate and therefore has a stronger lateral spreading than the structures with a spacing between the N<sup>+</sup> implant and the gate. Chen et al. have studied the effect of N<sup>+</sup> lateral spreading and the piezoelectric effect using a one-dimensional method [9]. The two-dimensional behavior of the N<sup>+</sup> carrier distribution, however, was not considered. Other important factors influencing the characteristics of the FET's are the amount of EL-2's and the residual shallow acceptor concentration in the semi-insulating substrate. Horio et al. have numerically calculated these effects on the characteristics of the FET's [12]. But, piezoelectric effect was not considered in their calculation.

In this paper, we report results from a two-dimensional simulation of self-aligned GaAs MESFET's. The impacts on the device performance due to the piezoelectric effect and the structure and material parameters have all been taken into consideration. Device parameters such as lateral spreading of N<sup>+</sup> ions and residual carbon concentration in the substrate have been taken into account to study the correlation between the short-channel effect and the piezoelectric effect. Devices with different gate lengths, different dielectric thickness, and oriented in different directions were also studied.

#### II. DEVICE STRUCTURE AND PHYSICAL MODEL

#### A. Device Structure and Implantation Profile

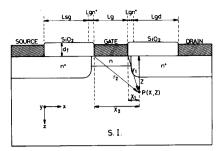

A cross-sectional view of the device of the self-aligned MESFET structure used in this study is shown in Fig. 1. This is one of the most popular self-aligned structures used today. The  $N^+$  region next to the gate is implanted in a self-aligned fashion using either the gate metal [6], [7] or the dummy gate [13] as the implantation mask. A 0.1- $\mu$ m spacing is left between the  $N^+$  region and the gate to resemble some of the more advanced structures for reduced gate capacitance, gate leakage, and short-channel effects

Fig. 1. One of the self-aligned MESFET structure used in the study.

[14]. To compare devices with different lateral spreading of  $N^+$  ions, we have also simulated devices without  $N^+$ gate spacing. Structure parameters of the MESFET used in the calculation are listed in Table I. Different implantation profiles were chosen for the n channel and the  $N^+$  region. In the vertical direction, they are represented by the Gaussian function

$$N(z) = N_p \cdot \exp\left[-\frac{(z - R_p)^2}{2\Delta R_p^2}\right]. \tag{1}$$

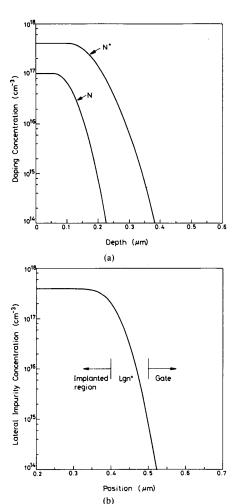

The projected range,  $R_p$ , is 600 Å for the n channel and 1000 Å for the N<sup>+</sup> region. Two straggle parameters [15] are used for each Gaussian profile. For  $z \le R_p$ ,  $\Delta R_p$  is 5  $\mu$ m. For  $z \ge R_p$ ,  $\Delta R_p$  is 450 Å for the n channel and 700 Å for the N<sup>+</sup> region. The peak concentration,  $N_p$  for the channel is  $1 \times 10^{17}$  cm<sup>-3</sup> and  $4 \times 10^{17}$  cm<sup>-3</sup> for the N<sup>+</sup> region. The lateral spreading of N<sup>+</sup> ions beyond the edge of the implantation mask has also been considered. This is very important for the self-aligned structure considered here because it can change the source resistance and cause short-channel effect. The expression for the lateral distribution of implanted ions has been derived by Furukawa et al. [16]. Following their derivation, the contribution of the lateral distribution of implanted ions to the channel doping is described by

$$N(x, z) = \frac{N(z)}{2} \left[ \operatorname{erfc} \left( \frac{a_0 - x}{\sqrt{2} \Delta R_t} \right) + \operatorname{erfc} \left( \frac{a_0 + x}{\sqrt{2} \Delta R_t} \right) \right]$$

(2)

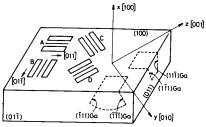

where N(z) is the Gaussian profile discussed before. The x dependent terms are the complementary error functions, describing the lateral spreading.  $a_0$  is the distance between the edge of  $N^+$  implant to the center of the gate, i.e.,  $a_0 = L_{ph}^+ + 1/2 L_p$ . The doping profiles for the n channel and the  $N^+$  region are shown in Fig. 2(a) and the lateral spreading with  $\Delta R_t = 350$  Å are shown in Fig. 2(b). The devices are assumed to be fabricated on (100) substrates. Their orientation relative to the substrates are shown in Fig. 3. The surface dielectric layer on the device (see Fig. 1) is used either as an annealing cap or as a passivation layer. Depending on the dielectric material and the process technique, the dielectric film may be under significant stress. Because the film is not continuous and because the stress in the gate metal is usually negli-

TABLE I STRUCTURE PARAMETERS

| Parameter Value                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                              |

| L <sub>g</sub> 0.5, 0.75, 1, 2, 3, 4 and 5 μm                                                                                |

| $L_{sg}$ 0.75 $\mu m$                                                                                                        |

| $L_{\sf gd}$ 0.75 $\mu{ m m}$                                                                                                |

| $L_{gn}^+$ 0.1 $\mu m$ or 0 $\mu m$                                                                                          |

| d <sub>f</sub> 600 nm or 1200 nm                                                                                             |

| $N_a$ 1 × 10 <sup>15</sup> cm <sup>-3</sup> , 2 × 10 <sup>15</sup> cm <sup>-3</sup> or 3 × 10 <sup>15</sup> cm <sup>-3</sup> |

#### Ion implantation for N channel

| $1 \times 10^{17} \text{ cm}^{-3}$ |

|------------------------------------|

| $0.06~\mu\mathrm{m}$               |

| 5 μm                               |

| $0.045~\mu\mathrm{m}$              |

|                                    |

Ion implantation for N<sup>+</sup> layer

$N_P$ 4 × 10<sup>17</sup> cm<sup>-3</sup> 0.10 μm  $R_{p}$  $\Delta R_{\text{P1}}$ 5 μm  $\Delta R_{\text{P2}}$  $0.07 \mu m$ 350 Å or 700 Å  $\Delta R_{\text{t}}$

gible [8], the strain field and the induced piezoelectric charge distribution in the channel of the FET is not uniform and is greatly intensified along the edges of the gate. Following the derivation of Kirby et al. [17] and Asbeck et al. [8], we can express the piezoelectric charge density in the channel as (see Fig. 1 for coordinate system)

$$N_{pz} = \gamma_b \sigma_f d_f \left( \frac{x_1 z (x_1^2 - \beta z^2)}{r_1^6} - \frac{x_2 z (x_2^2 - \beta z^2)}{r_2^6} \right) \quad (3)$$

where

$\gamma_b = 2d_{14}(4 - \nu)/\pi = 390 \text{ electrons/dyn}$

$\nu = 0.23$ , Poisson ratio of GaAs  $d_{14} = 2.69 \times 10^{-17}$  C/dyn, the orientation-dependent strain constant, which is positive for [0 1 1] FET's and negative for [0 1 1] FET's

dielectric thickness

$\vec{\beta} = (2 + \nu)/(4 - \nu) = 0.59$   $\sigma_f$  stress in the dielectric film.

These piezoelectric charges can be considered as additional dopants for the FET's channel. Since  $d_{14}$  is orientation-dependent, the characteristics of the FET depend on the gate orientation. In this study, the surface dielectric layer is assumed to be SiO<sub>2</sub>, which is under compressive stress on GaAs. The magnitude of the stress depends on the techniques of deposition. Here we assume the value being  $1 \times 10^9$  dyne/cm<sup>-2</sup> [6].

Fig. 2. (a) Doping profiles for the n channel and the N<sup>+</sup> layer. (b) Lateral spreading of implanted N+ impurities.

Fig. 3. Schematic drawing of the orientations of the FET's with respect to the GaAs substrate. A in the  $(0\ 1\ 1)$  direction, B in the  $(0\ 1\ T)$  direction, C in the (0 1 0) direction, and D in the (0 0 1) direction.

The deep levels in semi-insulating substrates are also considered in our simulation. In LEC (Liquid Encapsulated Czochralski) grown GaAs, it is well known that EL-2's, the mid-gap donor states, compensate shallow carbon acceptors to cause the semi-insulating properties. We assume the concentrations for the EL-2 being 1  $\times$  $10^{16} \text{ cm}^{-3}$  and carbon being  $1 \times 10^{15} \text{ cm}^{-3}$ ,  $2 \times 10^{15}$  cm $^{-3}$ , or 3  $\times$  10 $^{15}$  cm $^{-3}$ . These are typical values for commercially available undoped LEC substrates [18].

In the simulated devices, the gate is symmetrically placed between the source and the drain contacts. The spacing between the gate and the source is  $0.75~\mu m$ . The gate length is varied from 0.5 to  $5~\mu m$ .

### B. Basic Equations and 2-D Simulation

The basic equations used in our calculation are as follows:

#### 1) Poisson's equation

$$\nabla^2 \Psi = -\frac{q}{\epsilon} \left( -n + N_d - N_a + N_i^+ + N_{pz} \right) \quad (4)$$

where  $N_{pz}$  is the piezoelectric charge density shown in (3) and  $N_t^+$  is the ionized EL-2 concentration. From the relations

$$n = N_c \exp\left[-(E_c - E_f)/kT\right]$$

(5)

$$N_t^+ = N_t \cdot \left[ 1 - \frac{1}{1 + \exp\left[ (E_t - E_f)/kT \right]} \right]$$

(6)

$N_t^+$  can be expressed as

$$N_t^+ = \frac{N_c \cdot \exp\left[-\left(E_c - E_t\right)/kT\right]}{n + N_c \exp\left[-\left(E_c - E_t\right)/kT\right]} \cdot N_t \quad (7)$$

where the EL-2 level,  $E_t$ , is taken to be 0.69 eV below the conduction band [12].

2) Current continuity equation

$$\nabla \cdot \vec{J}_n = 0. \tag{8}$$

The hole current is neglected.

3) Drift and diffusion equation

$$\vec{J}_n = -q \mu_n n \nabla \psi + q D_n \nabla n. \tag{9}$$

The field-dependent mobility is given as [19]

$$\mu_n = \frac{\mu_{n0} + (\nu_{ns}/E)(E/E_0)^4}{1 + (E/E_0)^4} \tag{10}$$

where the critical field  $E_0 = 4300 \text{ V/cm}$ , the saturation velocity  $v_{ns} = 0.8 \times 10^7 \text{ cm/s}$ , and the low-field mobility  $\mu_{n0} = 6000 \text{ cm}^2/\text{V} \cdot \text{s}$ .

The equations described above were discretized by finite difference method. The spacings between mesh points were varied with the highest mesh density under the gate near the drain end to ensure enough spatial resolution and calculation accuracy. The lower boundary of the devices simulated was set at 3  $\mu$ m below surface to make sure that all physical phenomena studied occur well within this boundary. The Gummel scheme was adopted to solve the discretized equations [20]. The convergence criteria in our calculation are that the relative changes in the magnitude of terminal currents are less than  $10^{-4}$ .

#### III. RESULTS AND DISCUSSIONS

## A. Orientational-Dependent Short-Channel Effects

For short-gate MESFET's, short-channel effects are very important in determining the device characteristics and eventually set the ultimate limit for the smallest dimension that can be used for usable devices. This is especially true for self-aligned structures where the proximity of N<sup>+</sup>-implanted regions further enhances the short-channel effects. The piezoelectric effect is also stronger for short-channel devices because the piezoelectric charge density, as indicated in (3), is higher when the gate is smaller.

According to (3), the piezoelectric charges have opposite polarities for FET's oriented along [0 1 1] and  $[0\ 1\ \overline{1}]$  directions. The threshold voltage shifts caused by the piezoelectric effects, therefore, should be in opposite directions for the FET's in these two orientations. The amount of shift has been calculated using a simple onedimensional analysis [8]. However, experimentally, the phenomenon discussed here is usually not observed. The threshold voltage of the FET's in one of the directions does not suffer as much shift than that of the FET's in the other direction [1]-[3]. For devices with very short gates  $(\leq 1 \mu m)$ , the threshold voltage shift can be even in the same direction. This, of course, cannot be explained by the piezoelectric effect alone. One has to consider the short-channel effects, which are independent of gate orientation, and the piezoelectric effect together in order to satisfactorily explain the observed phenomena.

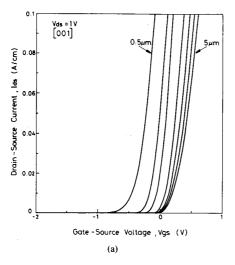

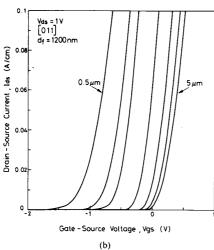

Before we discuss the influence of piezoelectric effect on the short-channel effect, it is worthwhile to look at the short-channel effect by itself. This actually is the case for devices oriented along [0 0 1] direction on (1 0 0) substrates. Because of crystal symmetry, the piezoelectric charges vanish in this orientation. I-V characteristics were calculated for devices with  $L_g = 0.5$ , 0.75, 1, 2, 3, 4, and 5  $\mu$ m. The N<sup>+</sup>-gate spacing,  $L_{gn}^+$ , the lateral spreading,  $\Delta R_t$ , and the carbon concentration,  $N_a$ , used in the calculation are 0.1  $\mu$ m, 350 Å, and 1  $\times$  10<sup>15</sup> cm<sup>-3</sup>, respectively. Fig. 4(a) shows the calculated  $I_{ds}$  versus  $V_{gs}$ curves at  $V_{ds} = 1 \text{ V}$  for different  $L_g$ 's. (The gate width is assumed to be 10  $\mu$ m.) Short-channel effects can be clearly seen in these figures. For the FET's with gate lengths longer than 2  $\mu$ m, the threshold voltage is nearly constant. But when the gate length is smaller than 2  $\mu$ m, the threshold voltage shifts toward negative values as the gate length is reduced. For devices oriented along [0 1 1] and [0 1 1] directions, because of piezoelectric effect, the results are very different. If the dielectric overlayer thickness is 1200 nm, the calculated  $I_{ds}$  versus  $V_{gs}$  curves are shown in Fig. 4(b) and (c) for  $[0\ 1\ 1]$  and  $[0\ 1\ \overline{1}]$  FET's, respectively. In the [0 1 1] direction, the short-channel effects are greatly enhanced. There is a wider spread in threshold voltage between devices with different gate length. In the [0 1 1] direction, however, the threshold voltages of different devices have nearly the same value. In other words, the short-channel effects seem to be compensated by the piezoelectric effect.

Fig. 4. The drain-source current  $I_{ds}$  versus gate-source voltage  $V_{gs}$ . Curves for (a) [0 0 1]-oriented MESFET's, (b) [0 1 1]-oriented MESFET's, (c) [0 1 T]-oriented MESFET's at  $V_{ds} = 1$  V. The gate lengths are 0.5, 0.75, 1, 2, 3, 4, and 5  $\mu$ m.

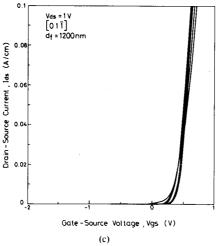

The subthreshold behavior of FET's is also greatly influenced by the short-channel effects. When the gate length shrinks down to the submicrometer regime, the subthreshold leakage often causes poor cutoff characteristics. The calculated subthreshold currents versus gate voltage for devices with the same structures of those used in Fig. 4 are shown in Fig. 5. Fig. 5(a) is for [0 0 1] oriented devices while Fig. 5(b) and (c) presents [0 1 1] and  $[0 \ 1 \ \overline{1}]$  oriented devices, respectively. In the [0 0 1] direction, in which the devices are immune from the piezoelectric effect, one can see clearly as the gate length becomes smaller, not only the threshold voltage shifts, the subthreshold conduction also becomes worse. In the [0 1 1] direction, the effect is much worse. The slope of the subthreshold conduction curves (log  $(I_{ds})$ versus  $V_{gs}$ ) degrade badly at small gate lengths. The best subthreshold behavior is observed for devices oriented in the  $\begin{bmatrix} 0 & 1 & \overline{1} \end{bmatrix}$  direction. The slopes remain the same except for the FET with 0.5-μm gate length. The improvement in subthreshold conduction for the  $[0\ 1\ \overline{1}]$  FET's caused by piezoelectric effect has been observed experimentally and agrees well with our calculated results [7].

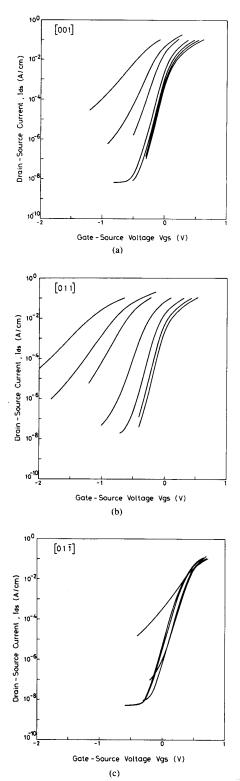

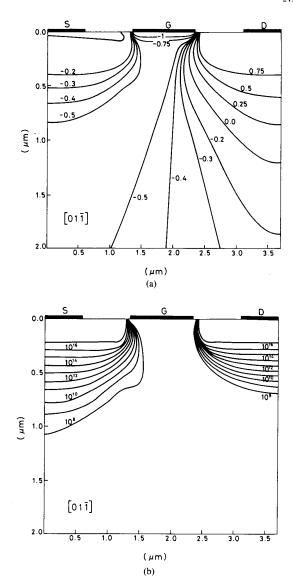

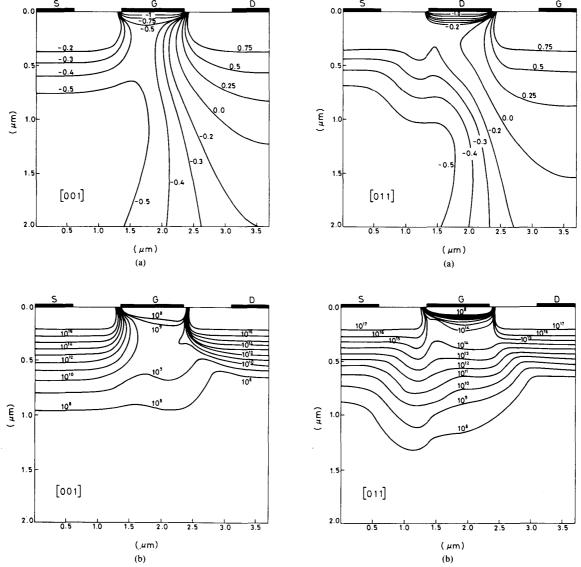

The orientation-dependent FET behavior can be best illustrated by the two-dimensional contour plots of the potential distribution and the carrier density distribution shown in Figs. 6-8. In these figures the contour plots of self-aligned MESFET's with a 1-µm gate length and a 1200-nm-thick SiO<sub>2</sub> overlayer oriented in  $[0 \ 1 \ \overline{1}]$ , [0 0 1], and [0 1 1] directions are shown. The devices are biased with  $V_{ds} = 1 \text{ V}$  and  $V_{gs} = -0.6 \text{ V}$ . Based on Fig. 4, we know, under this bias condition, the  $[0\ 1\ \overline{1}]$ FET and the [0 0 1] FET are below threshold and the [0 1 1] FET is above threshold. From Fig. 6(a) and (b), it can be seen that in the  $[0 \ 1 \ \overline{1}]$  FET there is a wide potential barrier in the substrate between the source and the drain and the channel is totally cut off (see Fig. 6(a)). For the [0 0 1] FET, where there is no piezoelectric effect. Fig. 7(a) shows that the width of the potential barrier is narrower and there is some subthreshold current in this case. The carrier density distribution in Fig. 7(b) shows that the current path is deep into the substrate. For the [0 1 1] FET the situation is totally different from those of the other two FET's. Fig. 8(a) shows there is no potential barrier existing between the source and the drain in the substrate. The channel is open and there is plenty of current flowing between the source and the drain contacts. The carrier density distribution shown in Fig. 8(b) indicates again there is a current leakage path in the substrate. Comparing Figs. 6(b), 7(b), and 8(b), we can clearly see the effect of piezoelectric charges on the current conduction in the FET's. In the [0 1 1] FET the carriers are depleted in the region under the gate, while in the [0 1 1] FET the carrier density increases due to the piezoelectric charges. From Fig. 8(b), one can see that the piezoelectric charge distribution is very deep.

Subthreshold conduction and short-channel effects are closely related problems for the FET devices. When the channel length is small, because of the proximity of the

Fig. 5. Subthreshold conduction behavior ( $I_{ds}$  versus  $V_{gs}$  curves shown in logarithm scale) for (a) [0 0 1]-oriented, (b) [0 1 1]-oriented, and (c) [0 1 T]-oriented devices with various gate lengths. Devices and the biased conditions are the same as those described in Fig. 4.

Fig. 6. Two-dimensional contour plots of (a) the potential distribution and (b) the carrier distribution for [0 1 T]-oriented FET's. The FET's have 1- $\mu$ m gate and 1200-nm SiO<sub>2</sub> overlayer. The sources are grounded; the drain voltage is V and the gate voltage is -0.6 V.

source and drain regions, the potential along the channel of the FET varies with the channel length and the drain voltage. In the subthreshold regime, increasing drain voltage and/or decreasing channel length will lower the potential barrier between the source and the drain and therefore increase the subthreshold current and decrease the threshold voltage. Fig. 9(a) and (b) presents the calculated potential distribution along the potential valley under the gate of the 0.5-, 0.75-, and 1- $\mu$ m gate MESFET's in the [0 0 1] and [0 1  $\bar{1}$ ] directions, respectively, at  $V_{ds}=1$  V and  $V_{gs}=-0.6$  V, the valley being the lowest potential channel where electrons travel. For the [0 0 1] oriented FET's the barrier heights for the MESFET's with

Fig. 7. Two-dimensional contour plots of (a) the potential distribution and (b) the carrier distribution for [0 0 1]-oriented FET's. The FET's have 1- $\mu$ m gate and 1200-nm SiO<sub>2</sub> overlayer. The sources are grounded; the drain voltage is 1 V and the gate voltage is -0.6 V.

Fig. 8. Two-dimensional contour plots of (a) the potential distribution and (b) the carrier distribution for  $[0\ 1\ 1]$ -oriented FET's. The FET's have 1- $\mu$ m gate and 1200-nm SiO $_2$  overlayer. The sources are grounded; the drain voltage is 1 V and the gate voltage is  $-0.6\ V$ .

gate lengths equal to 0.5, 0.75, and 1  $\mu$ m are 0.203, 0.349, and 0.445 eV, respectively. A 0.24-eV difference in barrier height between the 0.5- and 1- $\mu$ m gate MESFET's is observed. So the amount of carriers that can surmount the barrier to reach the drain is higher for the 0.5-  $\mu$ m gate MESFET. The cause of the difference in the barrier height between devices with different gate lengths is believed to be similar to the drain-induced barrier-lowering effect in the short-channel Si MOSFET's [21]. In the [0 1  $\overline{1}$ ] direction, the potential barriers in the 1- and 0.75-  $\mu$ m devices, the barriers have nearly flat top, indicating

the channel under the gates is totally depleted. For the [0 1 1] oriented FET's (potential distributions not shown in the figure), because the devices are above threshold, the channels are open and no potential barrier exist.

From the potential distribution described above, one can clearly see the relationship between the barrier height and subthreshold conduction. The lower the barrier height, the higher is the subthreshold conduction. The piezoelectric charges in the channels modify the doping profiles and effectively change the potential distributions and, therefore, the subthreshold conduction.

Fig. 9. The channel voltage along the potential valley under the gate for 0.5-, 0.75-, and 1- $\mu$ m gate MESFET's in (a) the [0 0 1] direction and (b) the [0 1 T] direction at  $V_{ds}=1$  V and  $V_{vs}=-0.6$  V.

### B. Piezoelectric Effects and Device Structures

1) Dielectric Layer Thickness: Since the stress induced in a device is proportional to the thickness of the surface dielectric layer, devices with different dielectric overlayer thickness are affected differently. In this subsection, results from devices with 1200- and 600-nm SiO<sub>2</sub> layers are presented. Other device parameters are the same as described before.

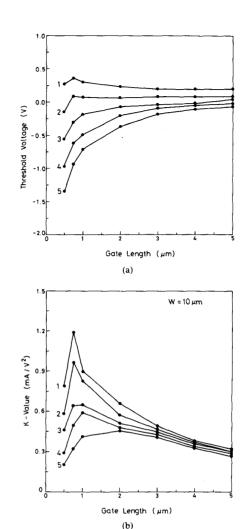

By fitting the I-V characteristics with the relation  $I_{ds} = K \times (V_{gs} - V_t)^2$ , we have calculated the threshold voltage and the K factors of the devices. Fig. 10(a) and (b), respectively, shows the calculated threshold voltage and K value versus gate length  $L_g$  for devices with two different dielectric overlayer thicknesses,  $d_f = 1200$  and 600 nm, and along three different orientations ([0 1 1], [0 0 1], and [0 1 1]). Curves 1 and 2 are for devices oriented in the [0 1 1] direction, while curves 4 and 5 are for those in the [0 1 1] direction. Curves 1 and 5 are those with  $d_f$

Fig. 10. (a) Threshold voltage and (b) K value versus gate length for three different orientations and two different dielectric thicknesses. Curve 1 for the  $[0\ 1\ T]$  orientation and  $d_f=1200$  nm; curve 2 for the  $[0\ 1\ T]$  orientation and  $d_f=600$  nm; curve 3 for the  $[0\ 0\ 1]$  orientation; curve 4 for the  $[0\ 1\ 1]$  orientation and  $d_f=600$  nm; curve 5 for the  $[0\ 1\ 1]$  orientation and  $d_f=1200$  nm. The  $N_a$ ,  $L_{gn}^+$  and  $\Delta R_i$  are  $1\times 10^{15}$ , 0.1  $\mu$ m, and 350 Å, respectively.

= 1200 nm while curves 2 and 4 are with  $d_f = 600$  nm. Curve 3 represents devices oriented in the [0 0 1] direction, which is immune from the piezoelectric effects. Since the piezoelectric effect is proportional to the thickness of the dielectric overlayer (see (3)), curves 1 and 5 correspond to devices with twice the effect as the devices of curves 2 and 4. This is the reason why curve 5 has the lowest threshold voltages, and curve 1 has the highest threshold voltages. Comparing curves 1, 2, 4, and 5 with curve 3 in Fig. 10(a), one can see that the piezoelectric effect has a strong influences on the short-channel effects. In the [0 1 1] direction, the piezoelectric effect enhances the threshold-voltage shift, but suppresses it in the [0 1  $\overline{1}$ ] direction. The threshold voltage is nearly constant with gate length for curves 1 and 2. The slight increase

in threshold voltage for  $L_{\rm g} < 2~\mu{\rm m}$  of curve 1 indicates that for these devices the piezoelectric effect is stronger than the short-channel effect, which would otherwise bend the curve downward. When  $d_f = 600~{\rm nm}$  (curve 2), the threshold voltage is constant except for  $L_{\rm g} = 0.5~\mu{\rm m}$ , where it shifts to a slightly lower value. This is because the piezoelectric effect is not strong enough to totally overcome the short-channel effects.

The K value shown in Fig. 10(b) also has a strong dependence on piezoelectric effect. In the  $[0 \ 1 \ \overline{1}]$  direction, the K values of the devices are enhanced by the stress, while in the [0 1 1] direction they are depressed by the stress. This can be explained by the modulation of channel depth by piezoelectric charges. In  $[0 \ 1 \ \overline{1}]$  direction, the channel doping profile is sharpened by the piezoelectric charge distribution, while in the [0 1 1] direction, the opposite situation takes place, i.e., the effective doping profile becomes broadened. Since the K value is inversely proportional to the channel depth, devices oriented in the  $[0, 1, \overline{1}]$  direction have a higher K value than those oriented in the  $[0 \ 1 \ 1]$  direction. The degradation of the Kvalue at very small gate lengths is due to short-channel effects. It should be pointed out that the position of the peak varies for different device orientations and different stress conditions. If we use the peak position of the [0 0 1] devices (curve 3) as a reference, where the peak occurs at a gate length around 1  $\mu$ m, the gate length where maximum K occurs for the  $[0\ 1\ 1]$  oriented devices is longer but it is shorter for the [0 1 1] oriented devices. The difference in the peak position is larger when the SiO<sub>2</sub> layer is thicker or the stress is stronger. This phenomenon has been observed experimentally by Onodera et al., and their results agree with our calculation [6], [7].

2) Effect of Lateral Spreading of the  $N^+$  Ions: The lateral spreading of the  $N^+$  layer can significantly affect the device behavior [13]. We have simulated devices with three different lateral spreading conditions. The results presented in the previous sections are for structures with 0.1- $\mu$ m spacing ( $L_{gn^+}$ ) between the  $N^+$  implant and the gate, and a 350-Å standard deviation ( $\Delta R_I$ ) for the lateral spreading of the  $N^+$  ions. To investigate the effects of stronger lateral spreading, we have also stimulated devices with 700 Å and devices with  $L_{gn^+} = 0 \ \mu$ m.

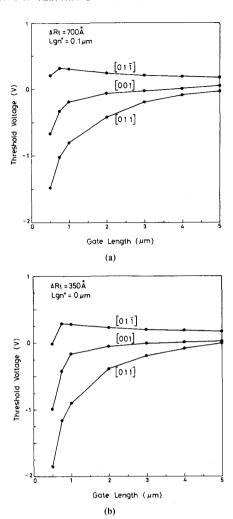

Fig. 11(a) and (b) presents the calculated threshold voltage versus the gate length plots for devices with different condition of lateral spreading. Fig. 11(a) is for  $L_{gn^+}=0.1~\mu m$  and  $\Delta R_t=700~\text{Å}$ . Fig. 11(b) is for  $L_{gn^+}=0~\mu m$  and  $\Delta R_t=350~\text{Å}$ . These figures should be compared with Fig. 10(a), where the threshold voltage for devices with  $L_{gn^+}=0.1~\mu m$  and  $\Delta R_t=350~\text{Å}$  are shown. It is clear from these figures that the short-channel effect and the piezoelectric effect are stronger for devices with larger N<sup>+</sup> lateral spreading. When  $L_{gn^+}=0~\mu m$ , the threshold voltage shift for the [0~1~1] FET with a 0.5- $\mu m$  gate length is almost 2 V, which is about 0.5 V larger than for the FET with  $L_{gn^+}=0.1~\mu m$ . In the [0~1~1] direction, the threshold-voltage shift is relatively small except at very small gate lengths. When  $L_g$  is less than

Fig. 11. Threshold voltage  $V_r$  versus gate length  $L_g$  for (a)  $L_{gn^+} = 0.1~\mu m$  and  $\Delta R_t = 700$  Å and (b)  $L_{gn^+} = 0~\mu m$  and  $\Delta R_t = 350$  Å. The curves for  $L_{gn^+} = 0.1~\mu m$  and  $\Delta R_t = 350$  Å have been shown in Fig. 10(a).

$0.75~\mu m$ , the threshold voltage curves bend downward as the short-channel effect overcomes the piezoelectric effect. The downward bending is stronger for devices with larger N<sup>+</sup> lateral spreading due to stronger short-channel effect. From the results presented here, one can see it is very beneficial to have a 0.1- $\mu m$  spacing between the N<sup>+</sup> implant and the gate for suppressing the short-channel effects

The relationship between the  $N^+$  lateral spreading and the threshold voltage shift has been studied by Chen *et al.* [9] using a one-dimensional analysis. They attributed the threshold voltage shift to the additional channel dopants under the gate from the lateral spreading of the  $N^+$  ions. The threshold-voltage shift was calculated by integrating the contribution from these additional charges under the midpoint of the gate. In the structure described in this paper, however, we found the threshold-voltage shift cannot be simply explained by the additional charges under

Fig. 12. Threshold voltage  $V_1$  versus gate length  $L_{\kappa}$  for (a)  $N_a = 2 \times 10^{15}$  cm<sup>-3</sup> and (b)  $N_a = 3 \times 10^{15}$  cm<sup>-3</sup>. The curve for  $N_a = 1 \times 10^{15}$  cm<sup>-3</sup> has been shown in Fig. 10(a).

the midpoint of the gate. With the parameters chosen in this study, the number of additional charges caused by  $N^+$  lateral spreading under the middle of the gate is too small to cause any significant changes in the threshold voltage. Accurate determination of the threshold voltages is a two-dimensional problem which takes into account of the actual charge distribution in the device channel. This is especially true for devices with small gate lengths and under strong influence of the piezoelectric effect.

3) Impurity Concentration  $N_a$ : In LEC semi-insulating GaAs substrates, the shallow carbon acceptors are compensated by deep EL-2 donors. The empty EL-2 concentration is equal to the carbon concentration. At the channel-substrate interface of a MESFET, the empty EL-2's are filled due to the interface band bending creating a negative space-charge region. On the channel side, a positive space-charge region is formed to balance the negative space-charge region on the substrate side. The width of the positive space-charge region depends on the concentration  $N_a$ :

tration of the shallow acceptors (in the case carbon) in the substrate. As the carbon concentration increases, the positive space-charge region widens leaving a narrower conduction channel for the FET.

In our study, we have simulated devices with three different carbon concentrations in the substrates. They are  $1\times10^{15}~{\rm cm}^{-3}$ ,  $2\times10^{15}~{\rm cm}^{-3}$ , and  $3\times10^{15}~{\rm cm}^{-3}$ . The EL-2 concentration is left to be  $1\times10^{16}~{\rm cm}^{-3}$ . Other device parameters are the same as those used for Fig. 10. The surface SiO<sub>2</sub> overlayer is taken to be 1200 nm.

The calculated threshold voltage versus gate length plots for devices with  $N_a = 2 \times 10^{15}$  cm<sup>-3</sup> and  $N_a = 3 \times 10^{15}$  cm<sup>-3</sup> are shown in Fig. 12(a) and (b), respectively. These figures should be compared with Fig. 10(a), where  $N_a = 1 \times 10^{15}$  cm<sup>-3</sup> is used. As  $N_a$  increases, the threshold voltage shifts toward the positive direction as expected. The short-channel effect is also reduced when  $N_a$  increases. This agrees with the results from studies on MESFET's with a buried p-layer under the channel [22], [23]. From Fig. 12(a) and (b), one can see that for the  $[0\ 1\ 1]$  FET's, the short-channel effect has been reduced to such a degree that it can no longer compensate for the piezoelectric effect. So the threshold voltage at small gate lengths does not bend downward as that shown in Fig. 10(a).

It is interesting to see that as  $N_a$  is increased the orientation effect is also reduced. The threshold voltage difference between the  $[0\ 1\ \bar{1}]$  FET's and the  $[0\ 1\ 1]$  FET's is smaller when  $N_a$  is higher. This can be qualitatively explained as follows: When  $N_a$  is higher, the conduction channel becomes narrower. So less piezoelectric charges reside in the channel and the piezoelectric effect becomes weaker. This phenomenon has been recently observed experimentally on a self-aligned MESFET structure with a buried p-layer [24].

# IV. Conclusions

A two-dimensional simulation has been performed on self-aligned GaAs MESFET's with surface stress. The stress-induced piezoelectric effect causes the orientation dependence of the electric characteristics of the FET. The short-channel effects were found to be strongly dependent on the piezoelectric effect. With proper device orientation the piezoelectric effect can compensate for the short-channel effect. Self-aligned MESFET's with different structure parameters such as the lateral spreading of N<sup>+</sup> impurities, the N<sup>+</sup>-gate spacing, and the shallow acceptor concentration have been simulated. It was found that lateral spreading of N<sup>+</sup> ions enhances the short-channel effect and the orientation effect. Higher carbon concentration in the substrate, however, reduces both effects. By choosing proper device structure with proper stress in the dielectric overlayer and aligning the devices in the right orientation, the short-channel effect can be effectively suppressed. Constant threshold voltage without gate length dependence can be achieved and the K value of the devices can also be improved. The compensation of the

short-channel effect by the piezoelectric effect, which does not exist for Si devices, may prove to be advantageous for GaAs MESFET's with scaled down dimensions for future semiconductor technologies.

#### REFERENCES

- [1] C. P. Lee, R. Zucca, and B. M. Welch, "Orientation effect on planar GaAs Schotty barrier field effect transistor," *Appl. Phys. Lett.*, vol. 37, no. 3, p. 311, 1980.

- [2] N. Yokoyama, H. Onodera, T. Ohnishi, and A. Shibatomi, "Orientation effect of self-aligned source/drain GaAs Schottky barrier field-effect transistors," Appl. Phys. Lett., vol. 42, no. 3, p. 270, 1983.

- [3] R. A. Sadler and L. F. Eastman, "Orientation effect reduction through capless annealing of self-aligned planar GaAs Schottky barrier fieldeffect transistors," Appl. Phys. Lett., vol. 43, no. 9, p. 865, 1983.

- [4] K. L. Mclaughlin and M. S. Birrittella, "Preferential diffusion and orientation effects of Schottky barrier GaAs field-effect transistors," *Appl. Phys. Lett.*, vol. 44, no. 2, p. 252, 1984.

- [5] M. F. Chang, C. P. Lee, P. M. Asbeck, R. P. Vahrenkamp, and C. G. Kirkpatrick, "Role of the piezoelectric effect in device uniformity of GaAs integrated circuits," *Appl. Phys. Lett.*, vol. 45, no. 3, p. 279, 1984.

- [6] T. Ohnishi, T. Onodera, N. Yokoyama, and H. Nishi, "Comparison of the orientation effect of SiO<sub>2</sub>- and Si<sub>3</sub>N<sub>4</sub>-encapsulated GaAs MESFET's," *IEEE Electron Device Lett.*, vol. EDL-6, p. 172, 1985.

- [7] T. Onodera, T. Ohnishi, N. Yokoyama, and H. Nishi, "Improvement in GaAs MESFET performance due to piezoelectric effect," *IEEE Trans. Electron Devices*, vol. ED-32, p. 2314, 1985.

- [8] P. M. Asbeck, C. P. Lee, and M. C. Chang, "Piezoelectric effects in GaAs FET's and their role in orientation-dependent device characteristics," *IEEE Trans. Electron Devices*, vol. ED-31, no. 10, p. 1377, 1984.

- [9] C. H. Chen, A. Peczalski, M. S. Shur, and H. K. Chung, "Orientation and ion-implanted effects in self-aligned GaAs MESFET's," *IEEE Trans. Electron Devices*, vol. ED-34, no. 7, p. 1470, 1987.

- [10] J. C. Ramirez, P. J. McNally, L. S. Cooper, J. J. Rosenberg, L. B. Freeund, and T. N. Jackson, "Development and experimental verification of a two-dimensional numerical method of piezoelectric induced threshold voltage shifts in GaAs MESFET's," *IEEE Trans. Electron Devices*, vol. 35, no. 8, p. 1232-1240, 1988.

- Electron Devices, vol. 35, no. 8, p. 1232-1240, 1988.

[11] T. Onodera, T. Ohnishi, and H. Nishi, "The role of piezoelectric in GaAs MESFET's ICs," Gallium Arsenide and Related Compounds, pp. 517-522, 1985.

- pp. 517-522, 1985.

[12] K. Horio, H. Yanai, and T. Ikoma, "Numerical simulation of GaAs MESFET's on the semi-insulated substrate compensated by deep traps," *IEEE Trans. Electron Devices*, vol. 35, no. 11, pp. 1778-1785, 1988.

- [13] K. Yamasaki, K. Asai, T. Mizutani, and K. Kurumada, "Self-aligned implantation for n<sup>+</sup>-layer technology (SAINT) for high-speed GaAs ICs," *Electron. Lett.*, vol. 18, no. 3, pp. 119-121, 1982.

- [14] N. Kato, Y. Matsuoka, K. Ohwada, and S. Moriya, "Influence of n<sup>+</sup>-layer-gate gap on short-channel effects of GaAs self-aligned MESFET's (SAINT)," *IEEE Electron Device Lett.*, vol. EDL-4, no. 11, p. 417, 1983.

- [15] S. M. Sze, VLSI Technology. New York: McGraw-Hill, 1983, p. 225.

- [16] S. Furukawa, H. Matsumura, and H. Ishiwara, "Theoretical considerations of lateral spread of implanted ions," *Japan. J. Appl. Phys.*, vol. 11, no. 2, pp. 134–142, 1972.

- [17] P. A. Kirby and P. R. Selway, "Photoelastic waveguides and their effect on stripe-geometry GaAs/Ga<sub>1-x</sub>Al<sub>x</sub>As lasers," *J. Appl. Phys.*, vol. 50, no. 7, pp. 4567-4579, 1979.

- [18] D. E. Holmes, R. T. Chen, K. R. Elliott, C. G. Kirkpatrick, and P. W. Yu, "Compensation mechanism in liquid encapsulated Czochralski GaAs: Importance of melt stoichiometry," *IEEE Trans. Electron Devices*, vol. ED-29, no. 7, p. 1045, 1982.

- [19] W. R. Curtice, "Direct comparison on the electron-temperature model with the particle-mesh (Monte Carlo) model for the GaAs MESFET," *IEEE Trans. Electron Devices*, vol. ED-29, no. 12, pp. 1942-1943, 1987

- [20] H. K. Gummel, "A self-consistent iterative scheme for one-dimensional steady state transistor calculations," *IEEE Trans. Electron Devices*, ED-11, pp. 455-465, 1964.

- [21] R. R. Troutman, "VLSI limitations from drain-induced barrier low-ering," *IEEE Trans. Electron Devices*, vol. ED-26, no. 4, pp. 461-469, 1979.

- [22] K. Yamasaki, N. Kato, and M. Hirayama, "Below 10 ps/gate operation with buried p-layer SAINT FET's," Electron. Lett., vol. 20, pp. 1029-1031, 1984.

- [23] \_\_\_\_, "Buried p-layer SAINT for very high speed GaAs LSI's with submicrometer gate length," *IEEE Trans. Electron Devices*, vol. ED-32, pp. 2420-2425, 1985.

- [24] R. A. Sadler, G. D. Studtmann, A. E. Geissberger, H. P. Singh, and R. A. Burrier, "A buried p-layer self-aligned process for high-yield LSI circuits," in *GaAs IC Symp. Tech. Dig.*, pp. 219–222, 1989.

Shih-Hsien Lo (S'90) was born in Taiwan, Republic of China, in 1964. He received the B.S. degree in electrical engineering from National Cheng-Kung University in 1986 and the M.S. degree in electronics engineering from National Chiao-Tung University in 1988. Currently he is working toward the Ph.D. degree in National Chiao-Tung University.

His research interests are in the areas of numerical modeling and electrical characterization of GaAs MESFET devices.

Chien-Ping Lee (M'80) received the B.S. degree in physics from National Taiwan University in 1971 and the Ph.D. degree in applied physics from the California Institute of Technology in 1978. While at Caltech, he worked on GaAs-based integrated optics.

He was credited with the design and fabrication of several important optoelectronic components, including the first integrated optoelectronic circuit, which consists of a laser and a Gunn device fabricated on a same substrate. After graduation,

he joined Bell Laboratories, where he worked on integrated optics and semiconductor lasers. He joined Rockwell International in 1979 and worked on GaAs integrated integrated circuits. He did extensive work on substrate-related effects such as the orientation effect and the backgating effect. In 1982 he was promoted to be a project leader and later a manager with responsibility for the development of ultra-high-speed integrated circuits using high electron mobility transistors. In 1987 he joined National Chiao Tung University, where he is now a professor and the director of the semi-conductor research center. He is also the director of the National Sub-micron Device Laboratory in charge of the construction of the first submicrometer device research center in the country. His current research interests are in the areas of III-V optoelectronic devices, MBE technology, heterostructure devices and physics, and device simulation.