# 國立交通大學

電機學院IC設計產業研發碩士班

#### 碩士論文

低功率正反器之設計應用於晶片網路以及 維特比解碼器

1896

Ultra Low Power Flip Flop Design for Network-on-chip and Viterbi Decoder Application

研究生:王尹伶

指導教授:黃威 教授

中華民國九十七年九月

#### 低功率正反器之設計應用於晶片網路以及維特比解碼器

# Ultra Low Power Flip Flop Design for Network-on-chip and Viterbi Decoder Application

研究生: 王尹伶 Student: Yin-Ling Wang

指導教授:黃威 Advisor:Wei Huang

#### A Thesis

Submitted to College of Electrical and Computer Engineering

National Chiao Tung University

in partial Fulfillment of the Requirements

for the Degree of

Master

in

Industrial Technology R & D Master Program on IC Design

August 2008

Hsinchu, Taiwan, Republic of China

中華民國九十七年九月

# 低功率正反器之設計應用於晶片網路以及 維特比解碼器

學生: 王尹伶 指導教授: 黃威

#### 國立交通大學電機學院產業研發碩士班

本論文使用低功耗電路設計的技術,來實現時脈驅動儲存元件之設計。一個適合應用在低震盪電壓時脈的邊緣觸發正反器 (LCSFF) 被提出,且使用 UMC 90nm 標準元件的技術來設計以及佈局。此單緣觸發正反器使用了低電壓的時脈震盪延遲電路,來產生操作的觸發波形和電晶體疊加技術,來達到減低漏電流的低功耗設計。

此一低震盪電壓時脈正反器,非常適用應用於需要大量儲存單元的系統。本論文中將把此正反器應用在晶片網路裏的串列器以及解串列器,還有維特比解碼器裏的記憶殘存單元。根據模擬結果顯示,這樣的應用可以減少至少 27.5 %的功率消耗。

# Ultra Low Power Flip Flop Design for Network-on-chip and Viterbi Decoder Application

Student: Yin-Ling Wang Advisors: Dr. Wei Hwang

Industrial Technology R & D Master Program of Electrical and Computer Engineering College National Chiao Tung University

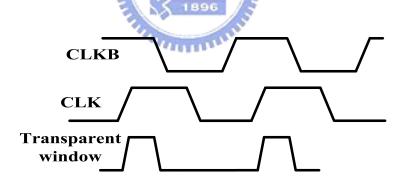

The clocked storage elements using the low power technique are realized in this paper. The low clock swing edge-triggered flip-flop (LCSFF) suitable for the low switching activity applications is proposed and simulated in UMC 90nm technology, and layout in UMC 90nm standard cell. The single edge-triggered flip-flop uses low swing voltage delay chain generating the operation transparency window for reduces the power consumption. The flip-flop uses the power gating technique to reduce the leakage current.

The low clock swing flip-flop (LCSFF) suitable for the system which used a great quantity of memory. In this thesis it applies to the serializer and deserailizer in network on chip and the survivor memory unit in viterbi decoder. The simulation result shows the applications could save more than 27.5% power.

### 致謝

首先我要感謝我的指導教授黃威老師,不論是在基礎課程或是研究方向 上面,老師都竭盡所能的教導我。不僅提供觀念上的協助,還有許多研究 資源的提供。使得我不僅在專業知識上獲益良多,也學到很多做人處事的 態度。

再來,我要感謝實驗室的學長以及同學們,不論是一起討論作業專題還是研究方向,同學們都不吝給予最大的協助以及鼓舞。特別要感謝Si2lab的李鎮宜老師以及同學,在研究資源方面提供的協助及幫忙。

最後,我要感謝我的父母以及家人好友,不僅在生活方面提供後盾, 讓我無後顧之憂的全力完成論文,也在我失落徬徨時,不吝給予最大的愛 與關懷。

最後,我要把這份論文的成果分享給每一個幫助過我的人。

## **Contents**

| Chapter 1                                                  |           |

|------------------------------------------------------------|-----------|

| Introduction                                               | 1         |

|                                                            |           |

| Chapter 2                                                  |           |

| Low Power Digital Circuit Design Concepts and Ove          | erview of |

| Network on Chip and Channel Coding                         | 3         |

| 2.1 Introduction                                           | 3         |

| 2.2 Device Characteristic                                  | 4         |

| 2.2.1 Size Issue                                           | 4         |

| 2.2.2 Power Issue                                          | 5         |

| 2.3 Introduction The Abstraction Levels of Network on Chip | 7         |

| 2.4 Introduction of Channel Coding                         | 10        |

| Chapter 3                                                  |           |

| Low Power Pulse- based Flip-Flop Design                    | 13        |

| 3.1 Introduction                                           | 13        |

| 3.2 Flip-Flop Characterization Events                      | 15        |

| 3.2.1 Timing Factors                                       | 15        |

| 3.2.2 Energy Factors                                       | 17        |

| 3.3 Low Power Techniques of Flip-Flop                      | 18        |

| 3.3.1 Clock Gating Technique                               | 19        |

| 3.3.2 Data Gating Technique                                | 21        |

| 3.3.3 Power Gating Technique                               | 23        |

| 3.4 Conventional Edge-Triggered Flip-Flop                                                                                                                                                                                                                                                                                                                 | 26                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| 3.4.1 Master Slave Flip- Flop                                                                                                                                                                                                                                                                                                                             | .27                                  |

| 3.4.2 Pulse Triggered Flip- Flop                                                                                                                                                                                                                                                                                                                          | .29                                  |

| 3.4.2.1 Explicit-Pulsed Flip-Flop                                                                                                                                                                                                                                                                                                                         | .30                                  |

| 3.4.2.2 Implicit Pulsed Flip-Flop                                                                                                                                                                                                                                                                                                                         | 34                                   |

| 3.5 Proposed Edge-Triggered Flip-Flop Design and Simulation Result                                                                                                                                                                                                                                                                                        | 39                                   |

| 3.5.1 The Motivation of Proposed The New Flip- Flop                                                                                                                                                                                                                                                                                                       | 39                                   |

| 3.5.2 Proposed Pulse Generator of Flip- Flop                                                                                                                                                                                                                                                                                                              | 40                                   |

| 3.5.3 Proposed Low Clock Swing Flip- Flop                                                                                                                                                                                                                                                                                                                 | 42                                   |

| 3.5.4 Simulation Result and Comparisons                                                                                                                                                                                                                                                                                                                   | 45                                   |

| 3.5.5 Layout and Post Simulation Result                                                                                                                                                                                                                                                                                                                   | 46                                   |

| Chapter 4  Low Clock Swing Flip-Flop Design for Serializer/Deserializer in                                                                                                                                                                                                                                                                                | 1                                    |

| Low Clock Swing Flip-Flop Design for Serializer/Deserializer in                                                                                                                                                                                                                                                                                           |                                      |

| Low Clock Swing Flip-Flop Design for Serializer/Deserializer in                                                                                                                                                                                                                                                                                           | 49                                   |

| Low Clock Swing Flip-Flop Design for Serializer/Deserializer in Network on Chip                                                                                                                                                                                                                                                                           | <b>49</b><br>.49                     |

| Low Clock Swing Flip-Flop Design for Serializer/Deserializer in Network on Chip                                                                                                                                                                                                                                                                           | <b>49</b><br>.49<br>.54              |

| Low Clock Swing Flip-Flop Design for Serializer/Deserializer in Network on Chip                                                                                                                                                                                                                                                                           | <b>49</b><br>.49<br>.54<br>.56       |

| Low Clock Swing Flip-Flop Design for Serializer/Deserializer in Network on Chip                                                                                                                                                                                                                                                                           | .49<br>.54<br>.56<br>.57             |

| Low Clock Swing Flip-Flop Design for Serializer/Deserializer in Network on Chip                                                                                                                                                                                                                                                                           | 49<br>.49<br>.54<br>.56<br>.57       |

| Low Clock Swing Flip-Flop Design for Serializer/Deserializer in Network on Chip                                                                                                                                                                                                                                                                           | .49<br>.54<br>.56<br>.57<br>60       |

| Low Clock Swing Flip-Flop Design for Serializer/Deserializer in Network on Chip.  4.1 Introduction  4.2 Practical Application in NoC Framework  4.2.1 Triplication Error Correction Coding Stage  4.2.2 Green Bus Coding Stage for Crosstalk Avoidance  4.3 Serializer and Deserializer Design for NoC  4.3.1 Introduction of Serializer and Deserializer | .49<br>.54<br>.56<br>.57<br>60<br>60 |

#### Chapter 5

| Low Clock Swing Flip-Flop Application of Viterbi Decod | ler70 |

|--------------------------------------------------------|-------|

| 5.1 Introduction                                       | 70    |

| 5.2 The Design of Proposed Viterbi Decoder             | 73    |

| 5.2.1 Implementation of SST                            | 75    |

| 5.2.2 Radix-2x2 ACS Structure                          | 76    |

| 5.2.3 Implementation of Path Merging Detection Unit    | 78    |

| 5.3 Simulation and Implementation Results              | 81    |

|                                                        |       |

| Chapter 6                                              |       |

| Conclusion and Future Work                             | 84    |

| Bibliography                                           | 87    |

| 1896                                                   |       |

## **List of Figures**

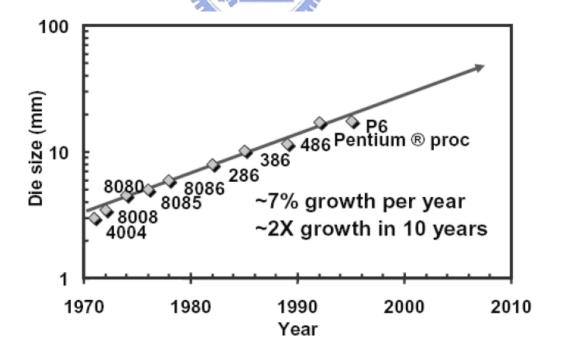

| Fig 2.1 The predict die size by S. Brokar4                                |

|---------------------------------------------------------------------------|

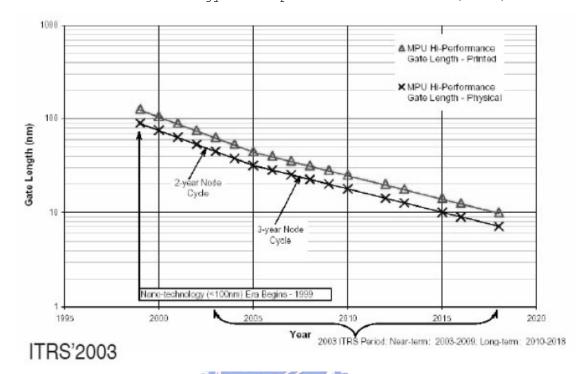

| Fig 2.2 The gate length predict by ITRS5                                  |

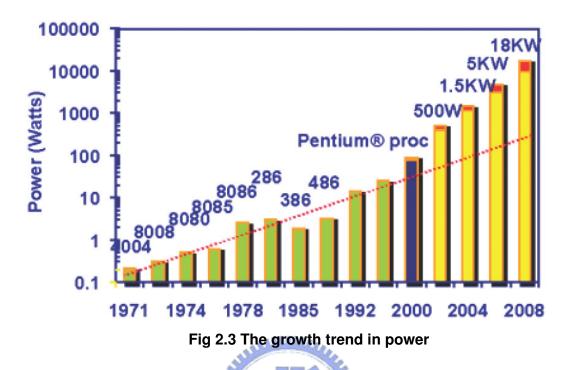

| Fig 2.3 The growth trend in power6                                        |

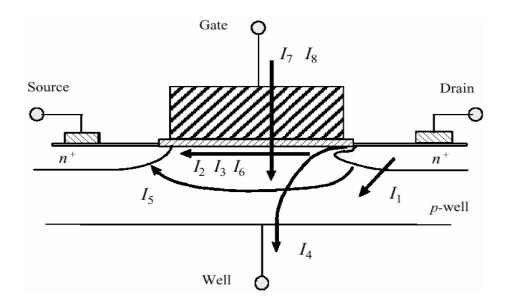

| Fig 2.4 The leakage sources for the static CMOS transistor7               |

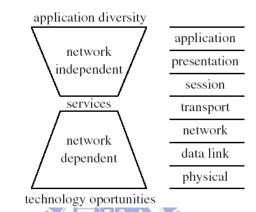

| Fig 2.5 The abstraction levels of NoC8                                    |

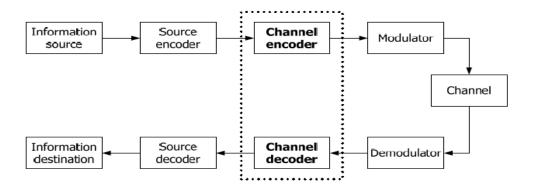

| Fig 2.6 Block diagram of a digital communication system11                 |

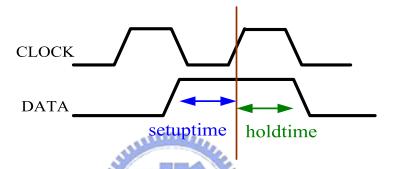

| Fig 3.1 Waveform diagram of setup time and hold time16                    |

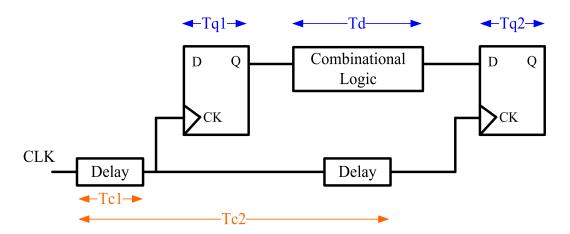

| Fig 3.2 The diagram of setup time and hold time17                         |

| Fig 3.3 The diagram of clock gating technique19                           |

| Fig 3.4 The condition captured flip-flop (CCFF)20                         |

| Fig 3.5 The diagram of data gating technique21                            |

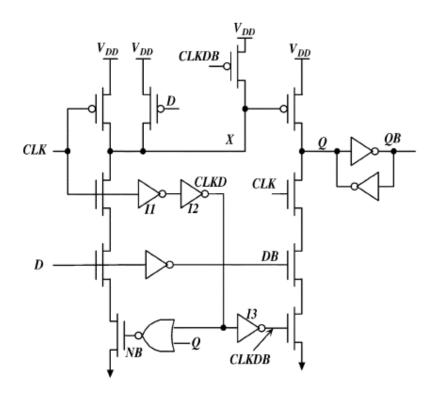

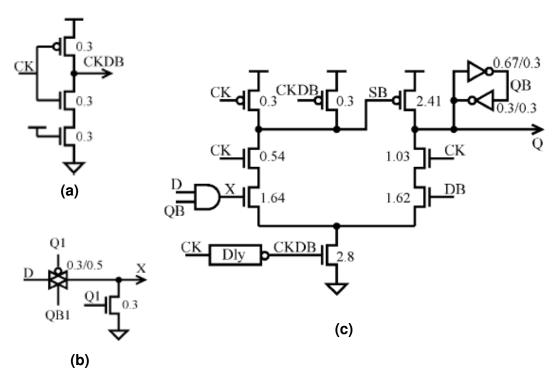

| Fig 3.6 (a) Delay cell (Dly) for producing CKDB from CK22                 |

| (b) AND gate for producing mapped input X from AND operation of D         |

| and QB1                                                                   |

| (c) Conditional Data Mapping Flip-Flop (CDMFF)                            |

| Fig 3.7 (a) Conditional precharge technique24                             |

| (b) Conditional discharge technique                                       |

| Fig 3.8 Conditional discharge double-edge triggered flip-flop (CDFF)25    |

| Fig 3.9 The Transmission-Gate Flip-Flop (TGFF)2                           |

| Fig 3.10 The race condition in TGFF28                                     |

| Fig 3.11 The C2MOS Flip-Flop29                                            |

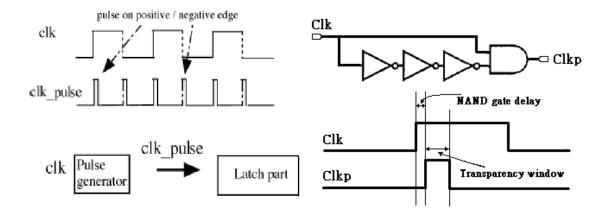

| Fig 3.12 The diagram of explicit-pulsed flip-flop and the prevalent pulse |

| generator circuit31                                                         |

|-----------------------------------------------------------------------------|

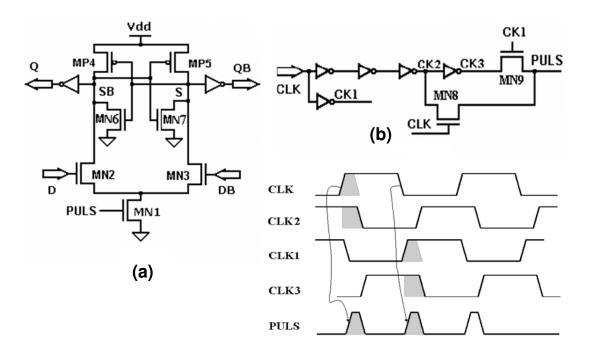

| Fig 3.13 Dual-edge triggered static pulsed flip-flop32                      |

| (a) DESPFF                                                                  |

| (b) Pulse generator and waveform                                            |

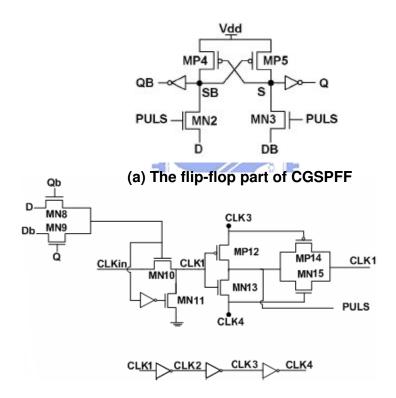

| Fig 3.14 The Clock Gated Static Pulsed Flip-Flop (CGSPFF)33                 |

| (a) The flip-flop part of CGSPFF                                            |

| (b) The pulse generator part of CGSPFF                                      |

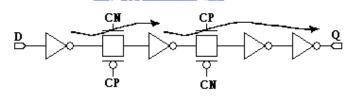

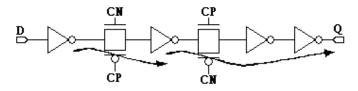

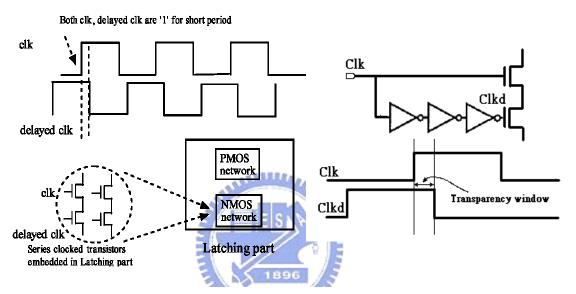

| Fig 3.15 The diagram of implicit-pulsed flip-flop and the prevalent pulse   |

| generator circuit35                                                         |

| Fig 3.16 The Hybrid Latch Flip-Flop (HLFF)36                                |

| Fig 3.17 Clock Branch Sharing Implicit Pulse Flip-Flop and(CBS_IP) and      |

| waveform38                                                                  |

| Fig 3.18 Proposed Low Swing Inverter Chain41                                |

| Fig 3.19 Proposed Low Clock Swing Flip-Flop (LCSFF)43                       |

| Fig 3.20 The Waveform of Transparent Window43                               |

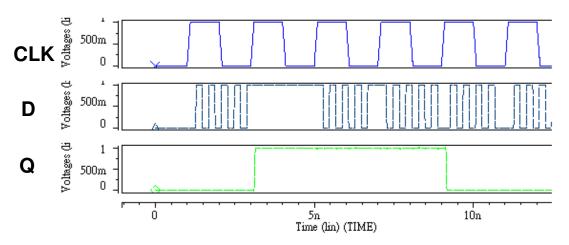

| Fig 3.21 The Data Tolerance Simulation Result44                             |

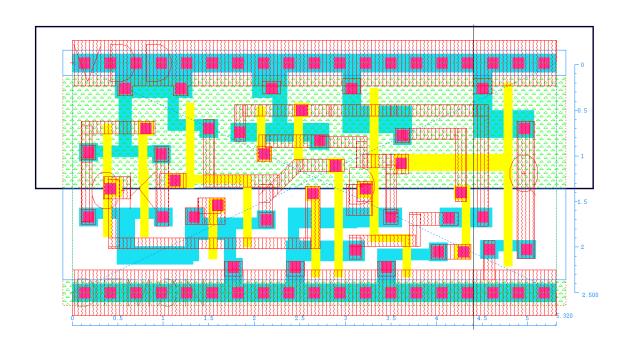

| Fig 3.22 The layout view of LCSFF in UMC90nm standard cell47                |

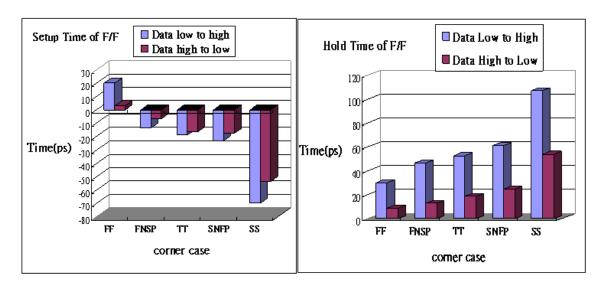

| Fig 3.23 The post simulation of setup time and hold time48                  |

|                                                                             |

| Fig 4.1 Traditional Synchronous Bus49                                       |

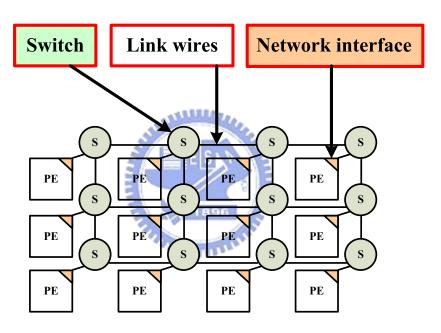

| Fig 4.2 Network-on-Chip Architecture51                                      |

| Fig 4.3 A simple architecture of Network on Chip52                          |

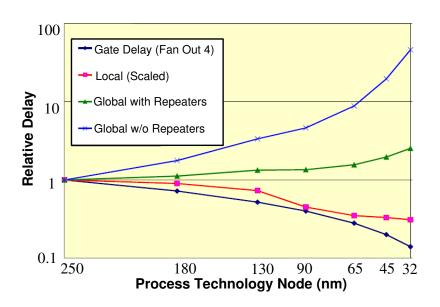

| Fig 4.4 Interconnect delay and gate delay under different53                 |

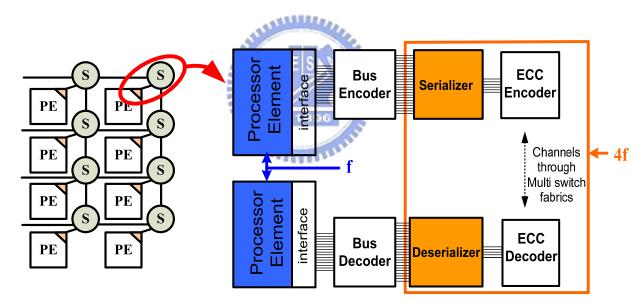

| Fig 4.5 A joint bus and error correction coding scheme with serializers and |

| deserializer in network-on-chip55                                           |

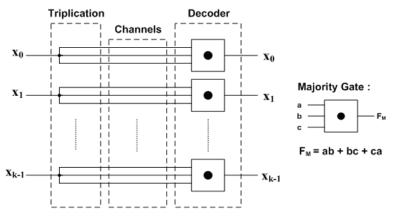

| Fig 4.6 Triplication error correction coding scheme57                       |

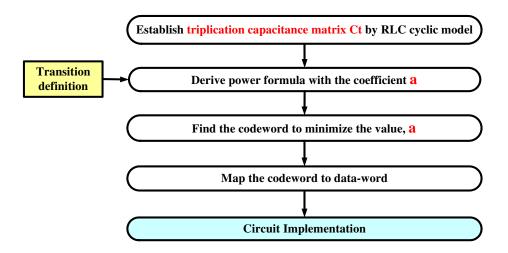

| Fig 4.7 Design flow of green bus coding57                                      |

|--------------------------------------------------------------------------------|

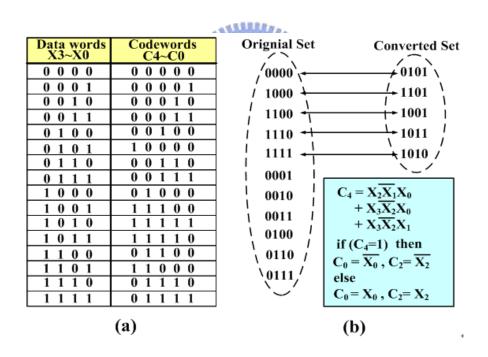

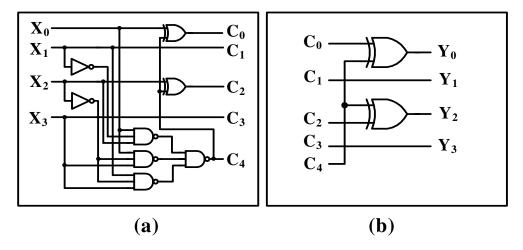

| Fig 4.8 (a) 4-to-5 Green bus coding scheme58                                   |

| (b) Original set and converted set of Green bus code                           |

| Fig 4.9 Circuit implementation of green bus coding                             |

| (a) Encoder (b) Decoder59                                                      |

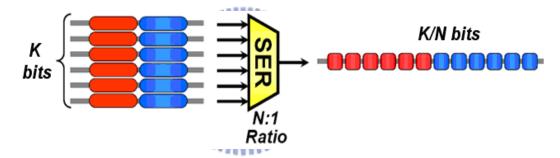

| Fig 4.10 K bit -to- (K/N) bit serialization with N:1 ratio61                   |

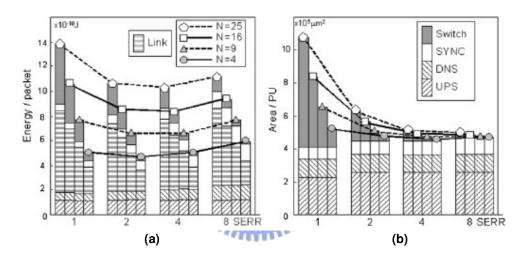

| Fig 4.11 (a) Energy and (b) area of an NoC according to Serialization ratio.62 |

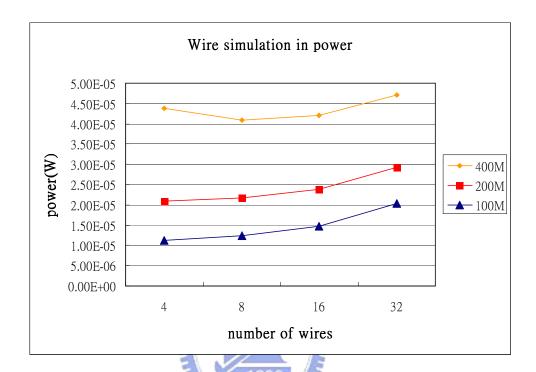

| Fig 4.12 Power Simulation Result of Different Numbers of Wire63                |

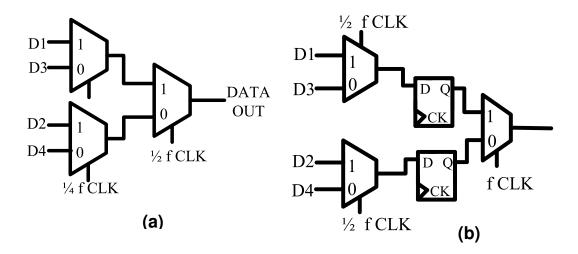

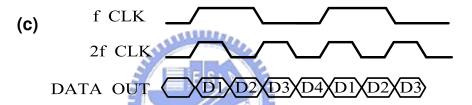

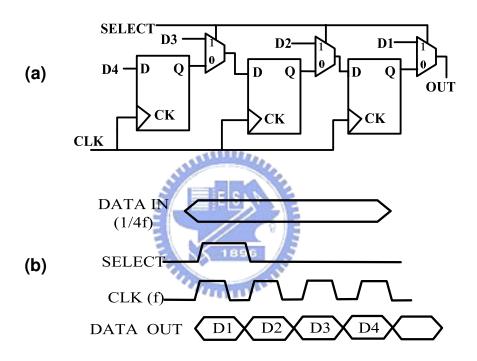

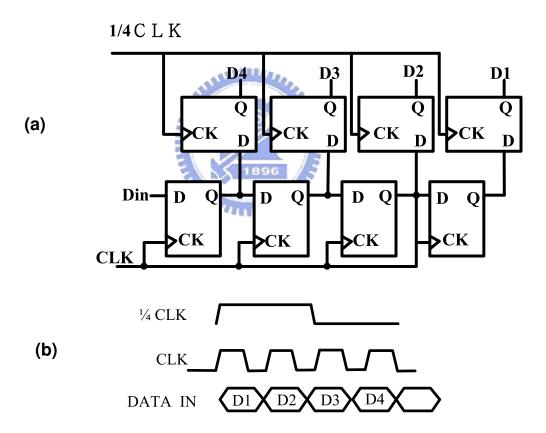

| Fig 4.13 The tree-based serializer and waveform64                              |

| Fig 4.14 The shift-register serializer and operation waveform65                |

| Fig 4.15 The mixed structure serializer and operation waveform66               |

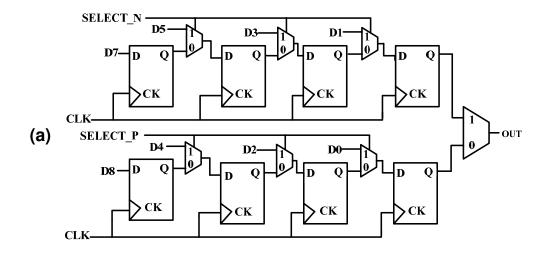

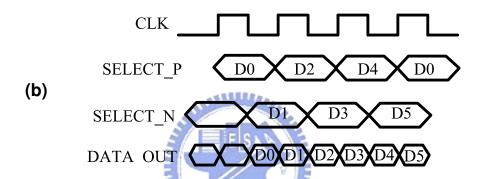

| Fig 4.16 The shift-register description and operation waveform67               |

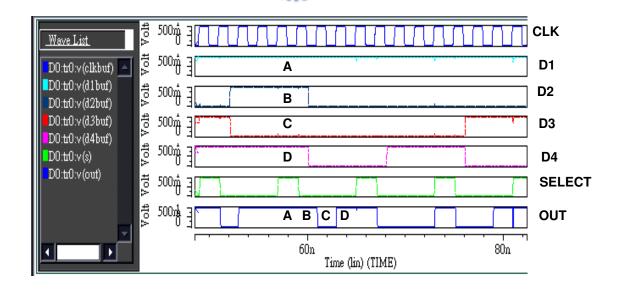

| Fig 4.17 SPICE simulation waveform of 4-1 serializer68                         |

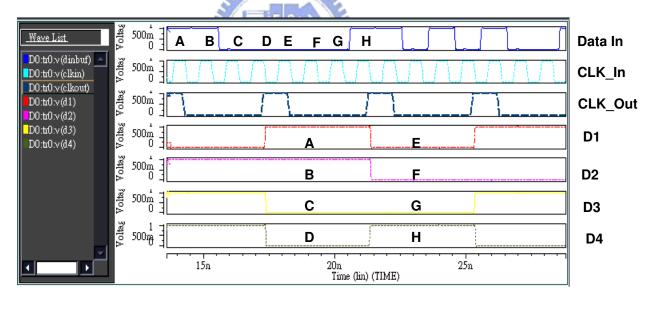

| Fig 4.18 SPICE simulation waveform of 1- 4 deserializer69                      |

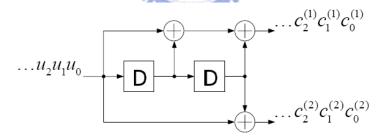

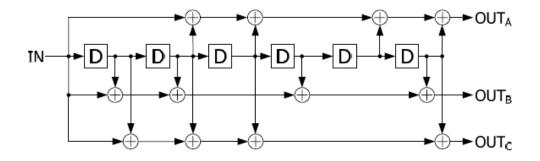

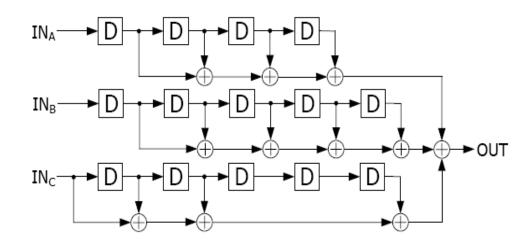

| Fig 5.1 The (2, 1, 2) convolutional encoder70                                  |

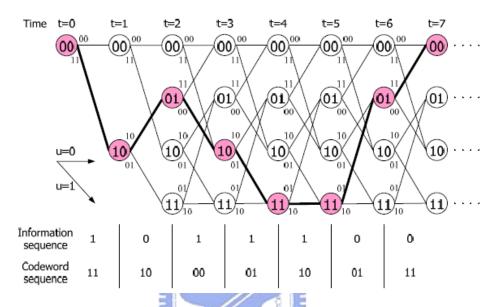

| Fig 5.2 The trellis diagram of the convolutional encoder in Fig 5.171          |

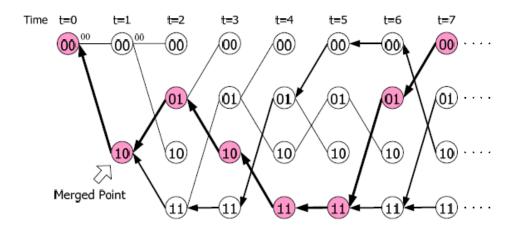

| Fig 5.3 Path merging phenomenon in Viterbi decoding over a noisy channel.72    |

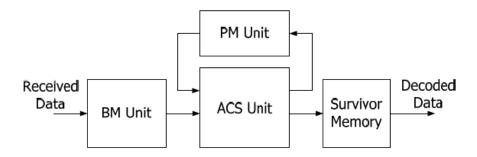

| Fig 5.4 The conventional block diagram of Viterbi decoder73                    |

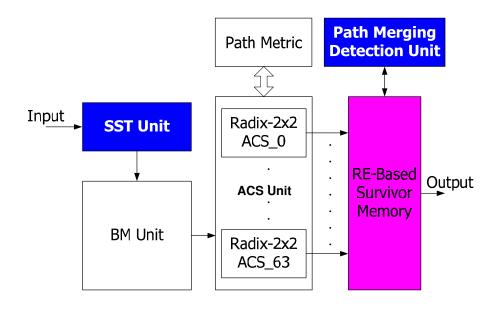

| Fig 5.5 The block diagram of proposed Viterbi decoder74                        |

| Fig 5.6 The convolutional encoder of MB-OFDM UWB system75                      |

| Fig 5.7 The pre-decoder for the convolutional encoder75                        |

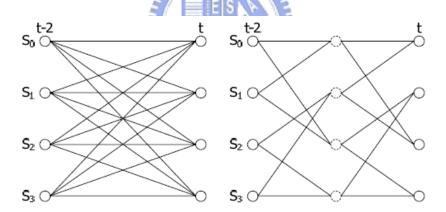

| Fig 5.8 The 4-state radix-4 and radix-2x2 trellis diagrams76                   |

| (a) 4-state radix-4 trellis diagram                                            |

| (b) 4-state radix-2x2 trellis diagram                                          |

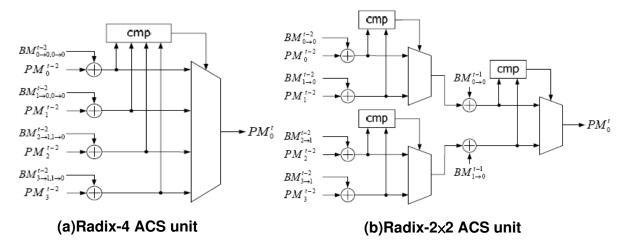

| Fig 5.9 The radix-4 and radix-2x2 ACS units77                                  |

- (a) Radix-4 ACS unit

- (b) Radix-2×2 ACS unit

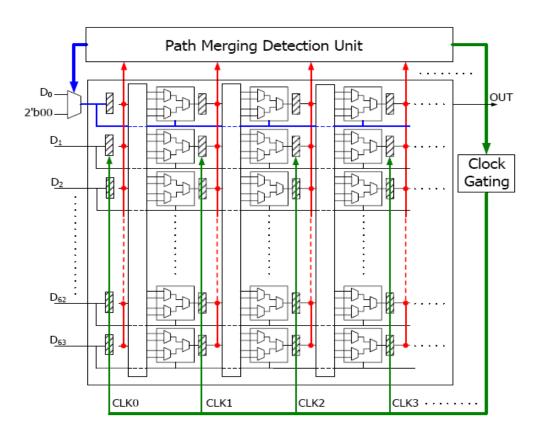

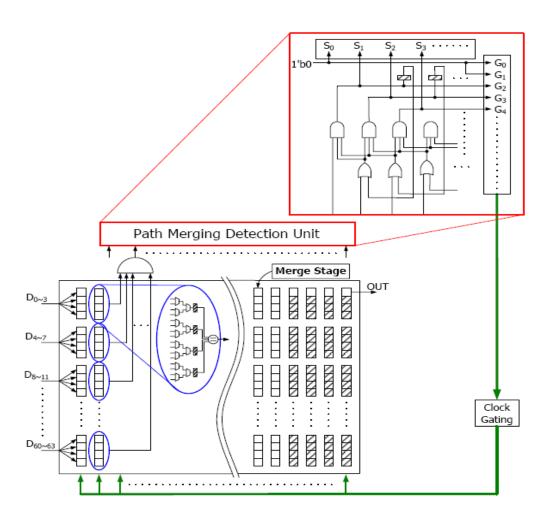

| Fig 5.10 | O A RE-based survivor memory with variable truncation length   | 78 |

|----------|----------------------------------------------------------------|----|

| Fig 5.11 | 1 The implementation of variable truncation length             | 80 |

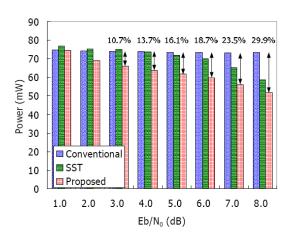

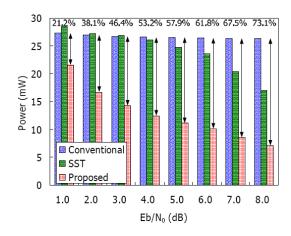

| Fig 5.12 | 2 The power simulation results in different channel conditions | 83 |

|          | (a) The power of whole Viterbi decoder                         |    |

|          | (b) The power of the survivor memory                           |    |

## **List of Table**

| Table 3.1 The simulation result compare with typical inverter chain40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 3.2 The comparisons of proposed LCSFF with other flip-flop45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Table 3.3 The presimulation of setup time and hold time of LCSFF46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Table 3.4 The simulation result of LCSFF47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Table 3.5 The post simulation of setup time and hold time of LCSFF48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Table 4.1 Design background of simulation of serializer68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Table 4.2 Design background of simulation of deserializer69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ALLE CONTRACTOR OF THE PARTY OF |

| Table 5.1 Comparison of complexity between radix-4 and radix-2×2 ACS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| units77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Table 5.2 The gate counts of different comparators and multiplexers77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Table 5.3 The gate counts of different implementations81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Table 5.4 Design parameters of the proposed Viterbi decoder82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Table 5.5 Simulation result compares with other Viterbi decoder83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

#### **Chapter 1**

#### Introduction

In the deep-submicron or nanometer era, the power dissipation is becoming a major design requirement, not only in portable application, but also in high performance VLSI systems. In a highly synchronous system, the power consumption of the clock network contributes is up to 45% of overall system power dissipation. And the clocked storage elements consume 90% power dissipation of the clock network. If we can design a low power clocked storage element, then the total power of the system will reduced great quantity power consumption.

A low power clocked storage element is the important concept in the digital circuit design. In this thesis, I will focus on the low power clocked storage elements design, by means of reduce clock loading and low swing technique.

In chapter 2, the low power digital circuit design concepts are discussed. It is emphasized on the device characteristic and the circuit design concepts. The evolution of modern flip flops are discussed and designed in chapter 3. A low clock swing flip flop (LCSFF) is proposed. This flip-flop uses low swing voltage technique, conditional capture technique, and stacked technique to reduce the leakage current in the flip-flop. It could reduce both the dynamic power and static power efficiently. In chapter 4, propose the

serializer and deserializer with self corrected green coding scheme for Network-on-Chip. In chapter 5, the application of low clock swing flip-flop in survivor memory unit, which proposed in a low power Viterbi decoder for wireless communication systems. In chapter 6 is the conclusions and future works.

#### **Chapter 2**

# Low Power Digital Circuit Design Concepts and Overview of Network on Chip and Channel Coding

#### 2.1 Introduction

The power consumption of circuits and systems is critically important in modern VLSI especially for low power applications and, hence, the power optimization techniques are applied at different levels of the digital design. The design of low power logic is one of the most important tasks to minimize the power consumption of digital circuits. Even the analog TC, RF IC, and wireless applications, have become the hot research topics in the recent year. But the digital circuit is still contributed the major part of a chip. In a conventional IC, 90% area of that is contributed by the digital circuit. To be a good IC designer, the basic digital circuit design concepts have to be studied in the beginning.

In the section 2.2, some device characteristic will be presented. The basic concepts in size, power, and performance of the device will be discussed [1]. In rest section will introduce Network on Chip and Channel Coding.

#### 2.2 Device Characteristic

#### 2.2.1 Size Issue

As the technology scaling in modern VLSI design, more and more transistors are integrated into a chip. It is possible to embed more and more function blocks in a system. The Moore's Law made a prediction that the semiconductor technologies will double its effectiveness every 18 months and it still comes into effect.

The Fig 2.1 shows the transistor counts of Intel Pentium series. It gets a exponential growth in the die size and proves the Moore's law indirectly.

Fig 2.1 the predict die size by S. Brokar.

Fig 2.2 shows the technology trends of gate length by International Technology Roadmap for Semiconductors (ITRS) in 2003.

Fig 2.2 The gate length predict by ITRS

#### 2.2.2 Power Issue

In the deep-submicron or nanometer era, it brings out the power problem when the more and more transistors are integrated into one chip. The Fig 2.3 shows the trends in power consumption of each processor. The power consumption is increasing exponentially and may be achieved to 18KW in 2008. The high power consumption will reduce the life of the battery in a portable application and cause the problem to cool down the system. In order to resolve the thermal problem, more and more low power techniques and technologies are

proposed. Some of which will be introduced in the chapter 3.

The power consumption includes both a dynamic and static parts. The dynamic part is mainly attributed to charging and discharging of the capacitances. The other part is associated with the leakage current of the transistors. In addition to the dynamic power consumption, the high leakage current in deep sub-micron regimes has become a significant contributor to the power dissipation of CMOS circuits as the CMOS technology scales down [1]. The subthreshold leakage power is expected to become a significant fraction of the total power in the sub-100 nm CMOS technology where reducing the subthreshold leakage power of the circuit is crucial.

Fig 2.4 shows the cross sectional view of FETMOS, which illustrate leakage current.

Fig 2.4 The leakage sources for the static CMOS transistor

- I1: PN junction reverse bias current

- I2: Weak inversion

- I3: Drain-induced barrier lowering (DIBL)

- I4: Gate-induced drain leakage (GIDL)

- I5: Punchthrough

- I6: Narrow width effect

- I7: Gate oxide tunneling

- I8: Hot carrier injection

The more ditails in low power design will present in rest chapters.

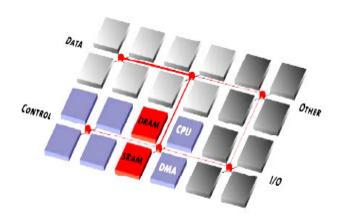

# 2.3 Introduction The Abstraction Levels of Network on Chip

For a micro-network, the protocol stack will be reduced to

physical layer, data-link layer, network and transport layer and software layer [35] which showed in Fig 2.5. The characteristics of each layer will be described in this section. The NoC protocols are described bottom-up, starting from the physical up to the software layer.

Fig 2.5 The abstraction levels of NoC

In the physical layer, global wires are the physical implementation of the communication channels. Traditional rail-to-rail voltage signaling with capacitive termination is definitely not well-suited for high-speed, low-energy communications for future global interconnect. Reduced swing can significantly reduce communication power dissipation which preserves the speed of data communication. Nevertheless, as the technology trends lead us to use smaller voltage swings and capacitances, the upset probabilities will rise. It is important to realize that a well-balanced design, because the overhead in performance, energy-efficiency and modularity may be too high. Physical layer design should find a compromise between competing

quality metrics and provide a clean and complete abstraction of channel characteristics to micro-network layers above.

In the data-link layer abstracts the physical layer as an unreliable digital link, where the probability of bit upsets is non null. Furthermore, reliability can be traded off for energy. The main purpose of data-link protocols is to increase the reliability of the link up to a minimum required level, under the assumption that the physical layer by itself is not sufficiently reliable. At the data link layer, error correction can be complemented by several packet-based error detection and correction protocols. Several parameters in the protocols can be adjusted depending on the goal to achieve maximum performance at a specified residual error probability within given energy consumption bounds.

At the network layer, packet data transmission can be customized by the choice of switching and routing algorithms. The NoC designers establish path of connection to its destination. Switching and routing affect heavily performance and energy consumption.

Robustness and fault tolerance will also be highly desirable. At the transport layer, algorithms deal with the decomposition of messages into packets at the source and their assembly at destination. Packetization granularity is a critical design decision because the behavior of most network control algorithm is very sensitive to packet size. Packet size can be application specific in SoCs, as opposed to general network.

Software layers comprise system and application software which includes processing element and network operating systems. The system software provides us with an abstraction of the underlying hardware platform. Moreover, policies implemented at the system software layer request either specific protocols or parameters at the lower layers to achieve the appropriate information flow. The hardware abstraction is coupled to the design of wrappers for processor cores which perform as network interfaces between cores and NoC architecture.

#### 2.4 Introduction of Channel Coding

A communication system connects an information source to a destination through a channel. The physical channel may be wireline cables, microwave links, and even storage media. Fig 2.6 shows a typical digital communication system. The transmission end is composed of source encoder, channel encoder, and modulator. The receiving end is composed of demodulator, channel decoder, and source decoder.

Fig 2.6 Block diagram of a digital communication system

A signal will be distorted by some effects such as noise, interference, and fading as it passes through the channel. To overcome the channel effects, the channel encoder introduces some redundancy in the output of the source encoder, called the information sequence. Next, the modulator converts the new sequence with redundancy, called the codeword sequence, into analog signals transmitted through the channel. In the receiver, the demodulator estimates the transmitted signal and makes some error because of channel noise. The demodulated sequence is called received sequence, which may not match the codeword sequence due to the errors.

The channel decoder uses the redundancy in the codeword to correct the errors in the received sequence and produces an estimate of the information sequence. A subject dealing with the design of channel encoder and channel decoder, referred to channel coding or error control coding, are developed to improve the performance of the overall system.

There are two main types of channel coding, the block code and the convolutional code. For the block codes, the encoder transforms a block of k information symbols into a block of n symbols called a codeword. These codes are usually referred as (n, k) block codes. The (n-k) redundancy symbols, also termed as parity symbols, depend only on the corresponding k information symbols and not on other information symbols. This means the block code is memoryless. Some of the commonly used block codes are Hamming code, BCH code, Reed-Solomon (RS) code, and low-density parity-check (LDPC) code.

For the Convolutional code, the encoder contains memory elements. The (n, k, m) Convolutional encoder has k inputs, n outputs, and m memory elements. Convolutional code converts the entire data stream into one single codeword by a linear shift-register circuit that performs a convolutional operation on the information sequence. The encoded bits depend not only on the current k input bits but also on the previous bits.

The Viterbi algorithm [1] proposed by A.J. Viterbi in 1967 is used to decode convolutional code. Forney [2] later proves that the Viterbi algorithm provides a maximum likelihood (ML) decoding algorithm. Until now, Viterbi algorithm is still the optimal solution for convolutional code and has become an important algorithm in communication systems.

#### **Chapter 3**

#### Low Power Pulse- based Flip-Flop Design

#### 3.1 Introduction

As the technology scaling down in VLSI design, it is possible to build chips consisting of millions of transistors. It accompanies both higher speed and larger power consumption, especially in deep-submicron technologies. Recently, the portable applications such as notebook PC, personal digital assistant (PDA), mobile phones and portable media players (PMP), are widely used in modern society. The public are look forward to longer battery lifetime. Furthermore, modern high technology products configure multi -cores, it stands for that the most important issue in deep submicron will be "power". Power dissipation is becoming a limiting factor in both high performance and mobile applications [1][2].

The power consumption in CMOS circuits comes from static and dynamic parts:

- Static dissipation due to

- > Subthreshold condition through OFF transistors

- > Tunneling current through gate oxide

- > Leakage through reverse-biased diodes

- Contention current in ratioed circuit

- Dynamic dissipation due to

- Charging and discharging of load capacitance

- "short-circuit" current while both pMOS and nMOS networks

are partially ON

$$P_{total} = P_{static} + P_{dynamic} \tag{3.1}$$

$$P_{static} = I_{static} * V_{DD} = (I_{dc} + I_{leakage}) * V_{DD}$$

(3.2)

$$P_{dynamic} = \alpha * C * V_{DD}^2 * f$$

(3.3)

-  $\alpha$  : Switching probability of one clock cycle

- f : the clock frequency

- C : the load capacitance

We take notice of the power formula (3.3), it shows dynamic power dissipation is proportional to the square of the supply voltage. Therefore reducing supply voltage (VDD) can save the power consumption efficient. Furthermore, the dynamic part is mainly attributed to charging and discharging of the capacitances. By means of cut down the loading capacitance will be the most significant improvement of the subject.

The principal source of the power consumption in digital systems is the clock tree which may consume up to 45% of the system power [3] [4]. The clock system consists of the clock distribution network and timing elements (flip-flops and latches), which is one of the most power consuming components in a VLSI system [5]. It accounts

for 30% to 60% of the total power dissipation in a system [6]. Latches and flip-flops have all pervasive applications in sequential circuit design, especially in pipelined circuit, signal processing and communication system.

To summarize the above-mentions, curtailing the power by reducing clock loading capacitance in flip-flops will have a deep impact on the total power consumed.

The rest of this chapter is organized as follows. Section 3.2 describes Flip-Flop characterization events. Section 3.3 describes the low power design techniques of Flip-Flop. Section 3.4 describes conventional edge-triggered Flip-Flops. Section 3.5 proposed a Low power pulse-based Flip-Flop. Section 3.6 showed the compared simulation results.

#### 3.2 Flip-Flop Characterization Events

#### 3.2.1 Timing Factors

Flip-Flops and latches are crucial elements of the design which attach great importance to delay and energy. The basic Flip-Flop timing parameters are setup time, hold time, and clock to Q delay. These are the indexes to judge the performance of the Flip-Flop.

Setup time is the stable required time (before the clock edge) for data input correctly latched by the Flip-Flop. Hold time is the stable required time (after the clock edge) for data input correctly latched by the Flip-Flop. The clock to Q delay is the delay time from the active clock edge to the output. The simple diagram is showed in Fig 3.1.

Fig 3.1 Waveform diagram of setup time and hold time

In a digital system, it has to satisfy the equation (3.4) and (3.5) to avoid timing violation. The equation (3.4) shows the hold time margin, the sum of clock to Q delay and logic delay must be greater or equal to the sum of hold time and relative clock skew. The equation (3.5) shows the setup time margin, the sum of clock cycle time and relative clock skew must be greater or equal to the sum of setup time and clock to Q delay and logic delay. I use a simple example to explain the hold time and setup time margin in the Fig 3.2.

$$(Tq1 + Td) \ge T_{hold} + (Tc2 - Tc1) \tag{3.4}$$

$$(T_{cycle} + Tc2 - Tc1) \ge T_{setup} + (Tq1 + Td)$$

(3.5)

Fig 3.2 The diagram of setup time and hold time

- Tq : clock to Q delay time in Flip-Flop

- Td : combinational logic delay time

- Tc : clock delay time

- Thold: hold time

- Tsetup : setup time

- Tcycle : cycle period time

#### 3.2.2 Energy Factors

Another crucial point for Flip-Flop design is the power consumption, which include dynamic and static parts. When input data maintained, the power consuming called static power consumption. If the next data inverse of former data, it called dynamic power consumption. As the equation (3.3).So I define the Flip-Flop switching probability as "switching activity  $\alpha$ ". I have applied some different input pattern to test the power efficiency of Flip-Flop. The pattern, "0101010101" (  $\alpha$ =1 ) , means the input data is always switching, reflects the maximum active power

consumption. The pattern "0000000000" or "11111111111" (  $\alpha\!=\!0$  ), means the static power consumption, reflects the leakage power consumption.

The dynamic power consumption is always larger than static power consumption, and switch activity of Flip-Flop is different in various applications. We employ low power techniques could reduce switch activity considerably. In addition use an applicable Flip-Flop to conform to the application is one way to meet low power target.

#### 3.3 Low Power Techniques of Flip-Flop

Most of the Flip-Flops presented here are dynamic in nature, and some internal nodes are precharged in each cycle without producing any useful activity at the output when the input is stable. Reducing this redundant switching activity has a profound effect in reducing the power dissipation, and in the literature many techniques were presented for this purpose [5]-[8].

A brief survey of such techniques is conducted in this work, and the main techniques were classified into: clock gating; data gating and power gating.

#### 3.3.1 Clock Gating Technique

It shows the general scheme for clock gating technique in Fig.3.3.

This technique is mainly applied for implicit pulse-triggered

Flip-Flops such as CCFF [7], which is shown in Fig.3.4. This

Flip-Flop employs the internal clock-gating method.

Briefly, in this technique, an output signal controlled gate (Q-controlled gate) is inserted on the path of the delayed clock to the first stage, Fig.3.3.

Fig. 3.3 The diagram of clock gating technique

Flip-Flops in this category feature a transparent window period that is used to sample the input. This transparent window, created by an implicit pulse generator, is determined by the time when both clocked transistors in the first stage are simultaneously on. In

Fig 3.4, after sampling a HIGH state at the input, the output  $\boldsymbol{\varrho}$  will be HIGH. To take notice of the NOR gate, this output state could be used to shut the transparent window as long as it is HIGH, preventing the redundant activities of the internal node  $\boldsymbol{x}$ .

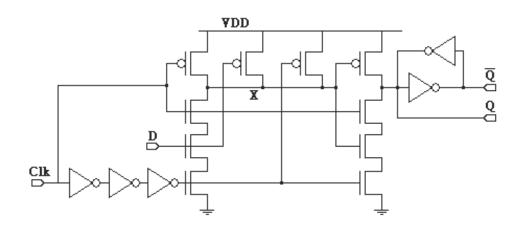

Fig 3.4 The condition captured flip-flop (CCFF)

In Fig 3.4, the condition captured Flip-Flop (CCFF) is introduced to reduce redundant power at the internal node X. This Flip-Flop employs a scheme much like the JK-type-Flip-Flop, but it adds one more gate that is switching with the clock compared to HLFF [8]. This addition leads to an increase in the power consumed by the clock system, and it may offset the savings gained from reducing the internal redundant switching power.

#### 3.3.2 Data Gating Technique

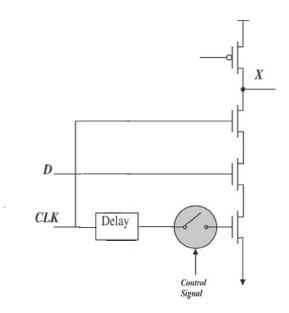

It shows the general scheme for data gating technique in Fig.3.5.

This technique is mainly applied for implicit pulse-triggered

Flip-Flop such as SDMFF [9], which is shown in Fig.3.6. This

Flip-Flop employs the internal data-gating method.

Briefly, in this technique, an output signal controlled gate (Q-controlled gate) is inserted on the path of the input data to the first stage, Fig.3.5.

Fig 3.5 The diagram of data gating technique

In Fig.3.6, I take Conditional Data Mapping Flip-Flop (CDMFF) to stand for data gating technique. Fig.3.6(a) illustrates a delay cell "Dly", which is used for producing **CKDB** from **CK**(clock signal).

The cell consumes less power than the conventional one, comprised of three inverters connected in series. Fig. 3.6(b) illustrates a pass-gate version of AND gates used to construct the data mapping, for decreasing the latency of the data path. Note that the state-of-the-art cell libraries [10] [11] allow the use of pass-gate inputs for high performance and design flexibility. The inputs can be driven by wide choices of logic gates.

Fig 3.6 (a) Delay cell (Dly) for producing CKDB from CK. (b) AND gate for producing mapped input X from AND operation of D and QB1. (c)

Conditional Data Mapping Flip-Flop (CDMFF)

In Fig.3.6(c), the circuit illustrates the schematic diagram of the CDMFF with a single-ended structure (s-CDMFF). The flip-flop consists of three stages, where an AND gate generates a mapped input

$m{X}$  from  $m{D}$  and  $m{QB}$  in the first stage, and a single-ended pulse generator produces a reverse pulse  $m{SB}$  from  $m{X}$  in the second stage. In the third stage, a latch generates the output  $m{Q}$  from  $m{SB}$  and  $m{DB}$ .

#### 3.3.3 Power Gating Technique

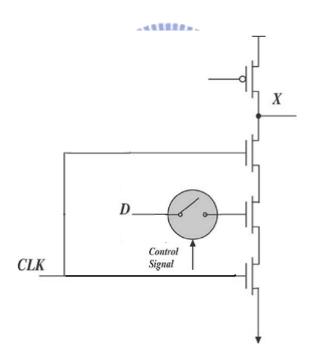

This power gating technique is utilized by mostly low power Flip-Flops. So I subdivide them into two parts, the conditional precharge technique and conditional discharge technique. There shows the general scheme for power gating techniques which include the conditional precharge technique and conditional discharge technique in Fig.3.7 (a) and (b), respectively.

Fig. 3.7 (a) shows the general scheme of the conditional precharge technique. The general idea of this technique is that the precharging path is controlled to avoid precharging the internal node when D stays HIGH. In the absence of the pMOS precharge control and when D stays HIGH for a long time, the discharge path will be on during the evaluation periods, causing node X to discharge after each precharging phase. To eliminate these charging/discharging activities, a PMOS transistor is inserted in the precharging path, which will prevent the precharging of node X in case the data input is stable HIGH.

Fig 3.7 (a) Conditional precharge technique (b) Conditional discharge technique

The clock-gating technique results in redundant power consumed by the gate controlling the delivery of the delayed clock to the flip-flop. As a result, conditional precharge technique outperformed the conditional capture technique in reducing the flip-flop's energy-delay-product (EDP) [12]. The conditional precharge technique is difficult to use a double-edge triggering structure for these flip-flops, as it will require a lot of transistors.

In conditional discharge technique, the extra switching activity is eliminated by controlling the discharge path when the input is stable HIGH. In this scheme, an NMOS transistor controlled by output *Qb* is inserted in the discharge path of the stage with

the high-switching activity. When the input undergoes a LOW to HIGH transition; the output  $\mathbf{Q}$  changes to HIGH and  $\mathbf{Qb}$  to LOW. This transition at the output switches off the discharge path of the first stage to prevent it from discharging or doing evaluation in succeeding cycles as long as the input is stable HIGH.

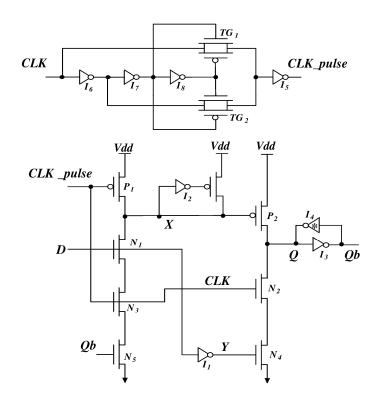

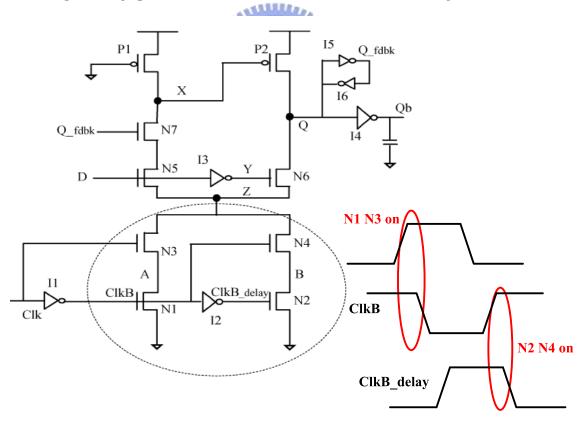

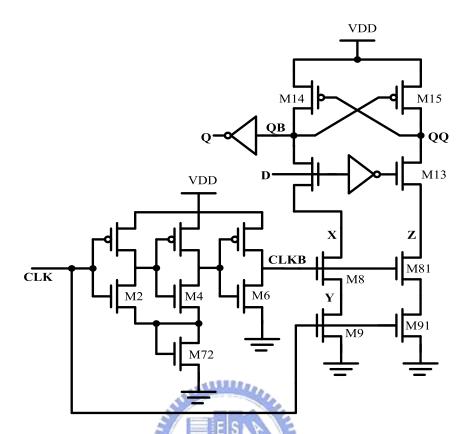

Fig 3.8 Conditional discharge double-edge triggered flip-flop (CDFF)

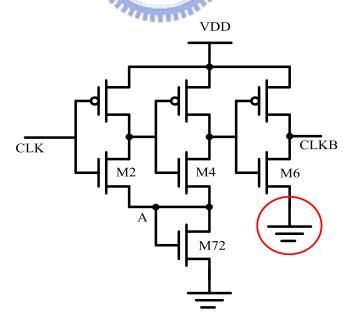

Fig 3.8 shows the conditional discharge flip-flop (CDFF). It uses a pulse generator as in [13], which is suitable for double-edge sampling. The flip-flop is made up of two stages. The conditional discharging scheme is employed in the CDFF as follows:

Stage one is responsible for capturing the LOW to HIGH transition. In order to reduce the redundant switch power, we employ a discharge control transistor  $\it N5$  at the discharge path of the first stage.

When  $\mathbf{Qb}$ =HIGH, which means  $\mathbf{Q}$ =LOW and  $\mathbf{X}$ =HIGH, N5 turns on, and the discharge path is enabled. If the input  $\mathbf{D}$  makes a LOW to HIGH transition, and  $\mathbf{CLK}$ \_pulse is HIGH,  $\mathbf{N1}$ ,  $\mathbf{N5}$ , and  $\mathbf{N3}$  switch on, the internal node  $\mathbf{X}$  is discharged to LOW, and  $\mathbf{Q}$  is pulled up to HIGH with  $\mathbf{Qb}$  pulled down to LOW, which shuts off the NMOS stack in first stage. For this  $\mathbf{D}$  transition (LOW to HIGH),  $\mathbf{X}$  is discharged only once; i.e., consecutive HIGH level at will not be sampled because the discharging path is inhibited by  $\mathbf{N5}$  which controlled by  $\mathbf{Qb}$ .

D was LOW during the sampling period, then the first stage is disabled, and node X retains its precharge state. Whereas, node Y will be HIGH, and the discharge path in the second stage will be enabled in the sampling period, allowing the output node to discharge and to correctly capture the input data.

## 3.4 Conventional Edge-Triggered Flip-Flop

The flip-flops are widely used not only in the synchronous and high performance system but also in system on chip (SOC) design. There are many kinds of flip-flop had proposed to satisfied the different system requirements. I will give an overview about each conventional flip-flop and illustrate the advantage and disadvantage of the flip-flop in this chapter. This section is organized with a sequence of develop.

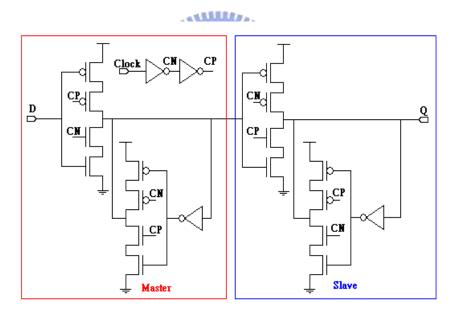

## 3.4.1 Master Slave Flip- Flop

Master-slave flip-flop is the typical edge triggered flip-flop that is designed to immune the race condition. The master-slave flip-flop is composed of two latches, the master one is sensitive to the logic level 0, and the slave one is sensitive to the logic level 1. When the clock is low, the master one is active and restores the input data, and the slave one keeps the previous data in the feedback loop circuit. When the clock is high, the master one is frozen the state by clock, and the slave one is active and sensitive the data from the master latch in a short time. Due to the cascaded structure, the flip-flop works as the edge-triggered flip-flop.

Fig 3.9 The Transmission-Gate Flip-Flop (TGFF)

The figure 3.9 shows the transmission-gate type master-slave flip-flop (TGFF), the flip-flop is used in PowerPC 603[14]. The

TGFF uses the transmission gates to isolate the master part and slave part, and the transmission gates are driven by opposite clock level. And it also speeds up the data pass-through time and reduces the power consumption by using the transmission gates. The other feature is that the TGFF adds the input gate isolation, and it can get better noise immunity. The advantages of the TGFF are short direct path and a low power feedback, but it has a big clock load which effects the power consumption of the clock tree.

Using the transmission gates as the isolation circuit has several merits, but it also causes some problem. The TGFF flip-flop may cause the race condition when the true clock and inverse clock have the overlapping range, and it is illustrated in the fig 3.10.

(a) The clock with 1 - 1 overlap

(b) The clock with 0 - 0 overlap

Fig 3.10 The race condition in TGFF

If these two control clocks have a 1-1 overlapping condition, the data may pass through the NMOS gates from input to output.

Similarly the data may pass through the PMOS gates from input to output when the  $0\,-\,0$  overlapping condition.