國 立 交 通 大 學

電機學院 IC 設計產業研發碩士班

碩士論文

溫度感測與體溫開關整合晶片設計

Integrated Chip Design for Temperature Sensor and Body

研究生：王建昇

指導教授：林進燈 博士

中華民國 九十八 年 一 月

# 溫度感測與體溫開關整合晶片設計

## Integrated chip design for temperature sensor and body temperature switch

研究生：王建昇

Student: Chien-Sheng Wang

指導教授：林進燈 博士

Advisor: Dr. Chin-Teng Lin

國立交通大學

電機學院 IC 設計產業研發碩士班

碩士論文

A Thesis

Submitted to College of Electrical and Computer Engineering

National Chiao Tung University

in partial Fulfillment of the Requirements

for the Degree of

Master

in

Industrial Technology R & D Master Program on

IC Design

January 2009

Hsinchu, Taiwan, Republic of China

中華民國 九十八 年 一月

# 溫度感測與體溫開關整合晶片設計

學生：王建昇

指導教授：林進燈 博士

國立交通大學電機學院產業研發碩士班

## 中文摘要

近年來，生醫訊號擷取與分析系統大多朝向可攜式研究為目標。採用電池安裝啟動之方式，目的是增加使用之可攜性與便利性。由於人體體溫相對於腦波與心跳是相當明顯的生理訊號，為了讓可攜式裝置能達到自動啟動及停止之動作，本論文將利用溫度晶片整合於可攜式生醫系統控制電源開關動作，更能達到系統晶片與可攜式生醫系統整合。

一般數位溫度感測系統包括前端的溫度感測電路及能帶隙參考電壓源，與後端的類比數位轉換電路，本論文基於基體推動 (bulk driven) 技術設計，達到低輸入電壓、低消耗功率之效果，並整合了溫度顯示及溫度開關電路。(1) 溫度開關是利用 PMOS 當主動負載將能帶隙參考電壓分壓，與溫度感測電路產生的電壓在 30°C 時經過比較電路控制 MOSFET 開關，MOSFET 與後端偏壓電路連接，以控制 MOSFET 開與關，即控制後端電路動作與不動作之切換。(2) 溫度顯示是將溫度感測電路利用反相放大器調整電壓及線性度，達到足夠的解析度，以供外接的 ADC 使用。(3) 能帶隙參考電壓設計為 0.75V，是為了之後將 ADC 整合在晶片內所預留，在此範圍主要是能得到較佳的感測準確度。

本論文的晶片設計使用台積電 0.18um 1P6M CMOS 的標準製程參數，模擬 -10°C ~ 80°C 溫度範圍內，所設計的電路正比於溫度變化的電壓值，電壓隨溫度變化率為 2.25 mV/°C，能帶隙參考電壓為 0.75V。

# Integrated Chip Design for Temperature Sensor and Body Temperature Switch

Student: Chien-Sheng Wang

Advisor: Dr. Chin-Teng Lin

Industrial Technology R & D Master Program of

Electrical and Computer Engineering College

National Chiao Tung University

## ABSTRACT

Most of the portable devices for biomedical are starting by the installation of battery. In recent years, with the evolution of manufacturing process and microelectronic technology, the chip is easier to integrate with the portable biomedical system. For the convenience, we want to switch the system by temperature. Because the human body temperature is a very clear physiological signal compared with the brain waves and heart rate, this thesis integrate the temperature circuit into the biomediacal system used for a switch.

A traditional digital temperature sensor system is composed of a temperature sensor in the front-end design and an analog to digital converter (ADC) in the back-end design. To reach the effect of low input voltage and low power consumption, this thesis uses the bulk driven technology. Moreover, the functions of temperature display and the temperature switch are also integrated into the design. The proposed design has three features as follows. (1) The temperature switch uses PMOS as active load to divide the bandgap voltage. The divided voltage will compare with the voltage of temperature sensor at  $30^{\circ}\text{C}$  to control MOSFET connected with the bias circuit in the back-end design. (2) Temperature display is that the temperature sensor uses the inverting amplifier to adjust the voltage and linearity and to achieve sufficient resolution for the external ADC. (3) The bandgap reference voltage is designed as 0.75V. This can be integrated with ADC in the future and can get better sensor

accuracy.

In this thesis, the proposed chip design is implemented by TSMC 0.18um 1P6M CMOS standard process parameters and is simulated in the temperature range from -10°C to 80°C. Especially, the circuit voltage is proportional to temperature. This means that the voltage increases 2.25mV when temperature rises by 1°C. The bandgap reference voltage is designed as 0.75V.

## 誌 謝

本論文的完成，首先要感謝指導教授林進燈博士這兩年來的悉心指導，讓我學習到許多寶貴的知識，在學業及研究方法上也受益良多。另外也要感謝口試委員們的建議與指教，使得本論文更為完整。

其次，感謝協助指導資訊媒體實驗室的鍾仁峯博士、范倫達博士，在理論及實作技巧上給予我相當多的幫助與建意，讓我獲益良多。此外，也衷心感謝學長姐紹航、俊傑、德瑋、智文、吉隆及靜瑩，同學煒忠、寓鈞、舒愷、孟哲、依伶、孟修、毓婷及儀晨的相互砥礪，以及學弟妹昕展、哲睿、介恩、有德及家欣在研究過程中所給我的鼓勵與協助。

感謝我的父母親王高淵先生和陳瓊姿女士對我的教育與栽培，並給予我精神及物質上的一切支援，使我能安心地致力於學業。

謹以本論文獻給我的家人及所有關心我的師長與朋友們。

# 目錄

|                                              |      |

|----------------------------------------------|------|

| 中文摘要.....                                    | ii   |

| ABSTRACT.....                                | iii  |

| 誌 謝.....                                     | v    |

| 目錄.....                                      | vi   |

| 圖目錄.....                                     | viii |

| 表目錄.....                                     | xi   |

| 第一章 緒論.....                                  | 1    |

| 1-1    溫度感測簡介.....                           | 1    |

| 1-2    論文架構.....                             | 4    |

| 第二章 溫度感測相關研究.....                            | 5    |

| 2-1    CMOS 製程溫度感測相關研究 .....                 | 5    |

| 2-1-1    弱反轉區（weak inversion）之溫度感測器設計 .....  | 6    |

| 2-1-2    橫向式雙載子接面電晶體與縱向式雙載子接面電晶體 .....       | 7    |

| 2-2    低電壓電路設計相關研究.....                      | 9    |

| 2-2-1    浮動閘極（Floating Gate）MOSFET .....     | 9    |

| 2-2-2    基體推動（Bulk-Driven）MOSFET .....       | 12   |

| 2-2-3    基體推動 MOSFET 之原理 .....               | 20   |

| 2-3    研究動機.....                             | 21   |

| 第三章 溫度感測器電路.....                             | 24   |

| 3-1    系統架構.....                             | 24   |

| 3-2    CMOS 溫度感測器 .....                      | 25   |

| 3-2-1    正比於絕對溫度電路.....                      | 26   |

| 3-2-2    能帶隙參考電壓源（Bandgap Reference）電路 ..... | 29   |

| 3-3    基體推動 MOSFET 電路之特性.....                | 33   |

| 3-3-1    基體推動 MOSFET 之頻率特性.....              | 33   |

| 3-3-2    基體推動 MOSFET 之雜訊（Noise） .....        | 34   |

| 3-3-3    基體推動 MOSFET 差動對.....                | 39   |

|                                       |           |

|---------------------------------------|-----------|

| <b>第四章 電路設計及模擬結果 .....</b>            | <b>41</b> |

| 4-1    模擬環境與設計流程 .....                | 41        |

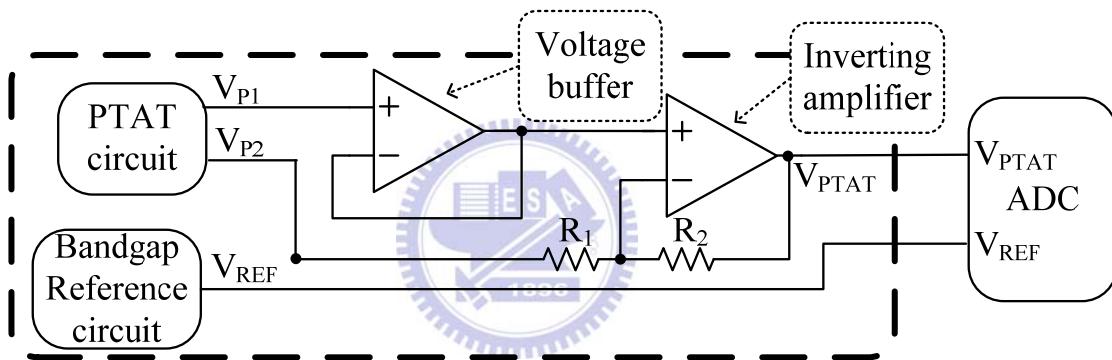

| 4-2    溫度開關及感測之整體電路架構 .....           | 41        |

| 4-3    基體推動之正比於絕對溫度電路架構 .....         | 43        |

| 4-4    基體推動之能帶隙參考電壓電路架構 .....         | 46        |

| 4-5    電壓緩衝器 (voltage buffer) .....   | 48        |

| 4-6    全電路模擬結果 .....                  | 54        |

| 4-6-1    溫度感測顯示 .....                 | 54        |

| 4-6-2    溫度開關 .....                   | 55        |

| <b>第五章 晶片實現與量測 .....</b>              | <b>59</b> |

| 5-1    晶片佈局 .....                     | 59        |

| 5-2    晶片佈局後模擬 .....                  | 61        |

| 5-3    佈局驗證結果錯誤說明 .....               | 67        |

| 5-4    測試考量及預計規格列表 .....              | 69        |

| <b>第六章 結論與未來展望 .....</b>              | <b>71</b> |

| 6-1    結論 .....                       | 71        |

| 6-2    未來展望 .....                     | 71        |

| <b>參考文獻 .....</b>                     | <b>73</b> |

| <b>附錄 :</b>                           | <b>77</b> |

| A. 打線圖(SB18) .....                    | 77        |

| B. Tapeout Review Form .....          | 78        |

| C. CIC Tapeout Question & Reply ..... | 83        |

# 圖 目 錄

|        |                                                                                                              |    |

|--------|--------------------------------------------------------------------------------------------------------------|----|

| 圖 1-1  | 一般常見的電子式溫度感測器 .....                                                                                          | 2  |

| 圖 2-1  | 弱反轉區參考電壓電路 .....                                                                                             | 7  |

| 圖 2-2  | (a) 採用 p-well CMOS 製程 n 通道電晶體之截面圖；(b) 橫向式雙載子電晶體之載子流向圖.....                                                   | 8  |

| 圖 2-3  | CMOS 製程所產生之寄生縱向式雙載子接面電晶體 (a) pnp (b) npn                                                                     | 8  |

| 圖 2-4  | 多輸入浮動閘極 (Multi-Input Floating Gate) MOSFET 電路圖 .....                                                         | 10 |

| 圖 2-5  | 浮動閘極技術之差動對電路圖 .....                                                                                          | 11 |

| 圖 2-6  | 利用浮動閘極技術所設計之基本電流鏡電路圖 .....                                                                                   | 12 |

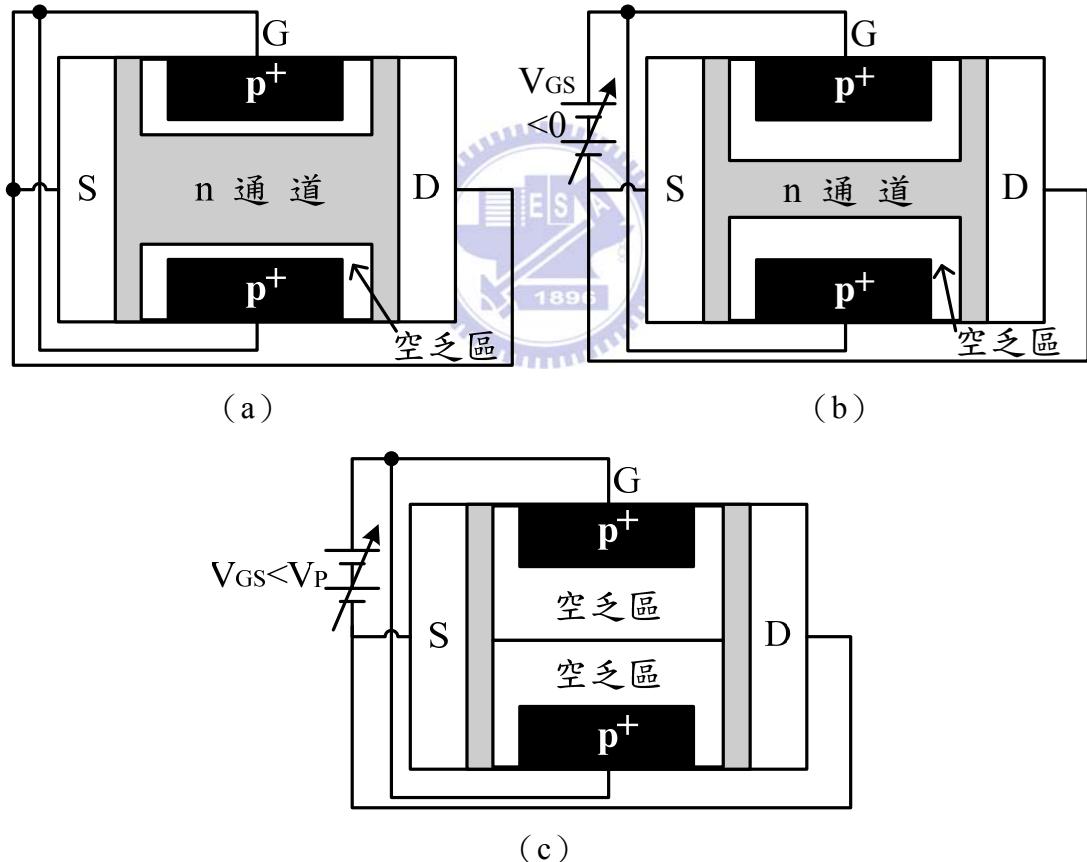

| 圖 2-7  | 分別為結構及電路符號；(a) 為 p 通道 JFET , (b) 為 n 通道 JFET ..                                                              | 13 |

| 圖 2-8  | n 通道 JFET 結構示意圖 .....                                                                                        | 14 |

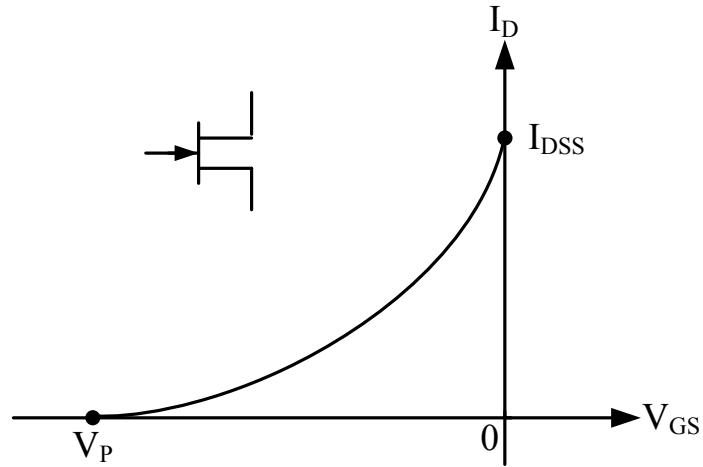

| 圖 2-9  | p 通道 JFET 偏壓 .....                                                                                           | 14 |

| 圖 2-10 | n 通道 JFET 接上所需偏壓 .....                                                                                       | 15 |

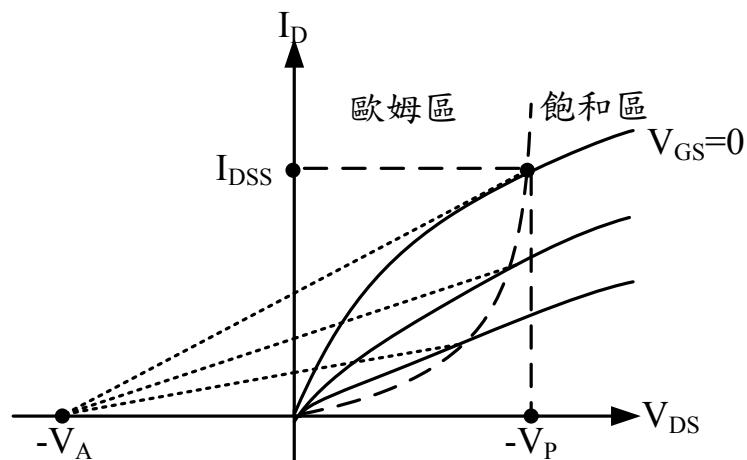

| 圖 2-11 | 電壓 $V_{DS}$ 很小時，不同 $V_{GS}$ 對 $I_D$ 的變化 .....                                                                | 16 |

| 圖 2-12 | $V_{GS}$ 對通道電阻的變化；(a) $V_{GS}=0$ 時的情況，(b) $V_{GS}$ 反偏時，空乏區增大，通道寬度減少，通道電阻增加，(c) $V_{GS} < V_p$ ，通道全部被夾止 ..... | 16 |

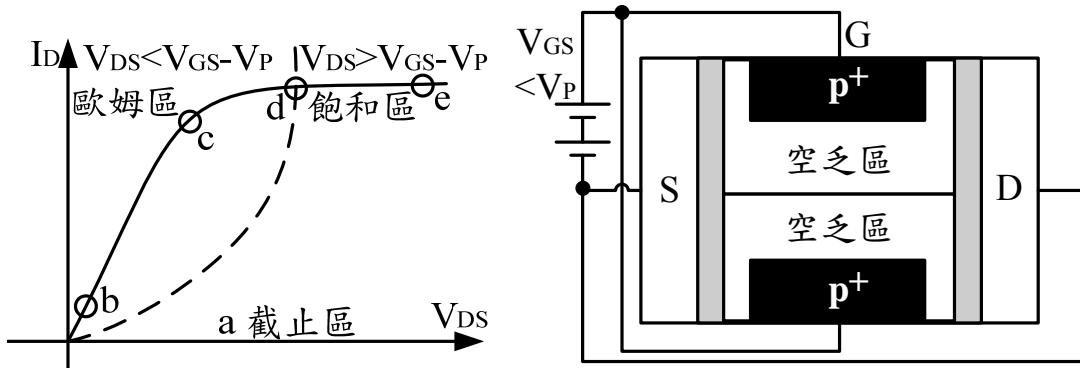

| 圖 2-13 | $V_{GS}$ 為定值且 $V_p < V_{GS} < 0$ 時，電流 $I_D$ 對電壓 $V_{DS}$ 變化過程，與相對應之特性曲線 .....                                | 18 |

| 圖 2-14 | 飽和轉換曲線 .....                                                                                                 | 19 |

| 圖 2-15 | 通道長度調變效應 .....                                                                                               | 19 |

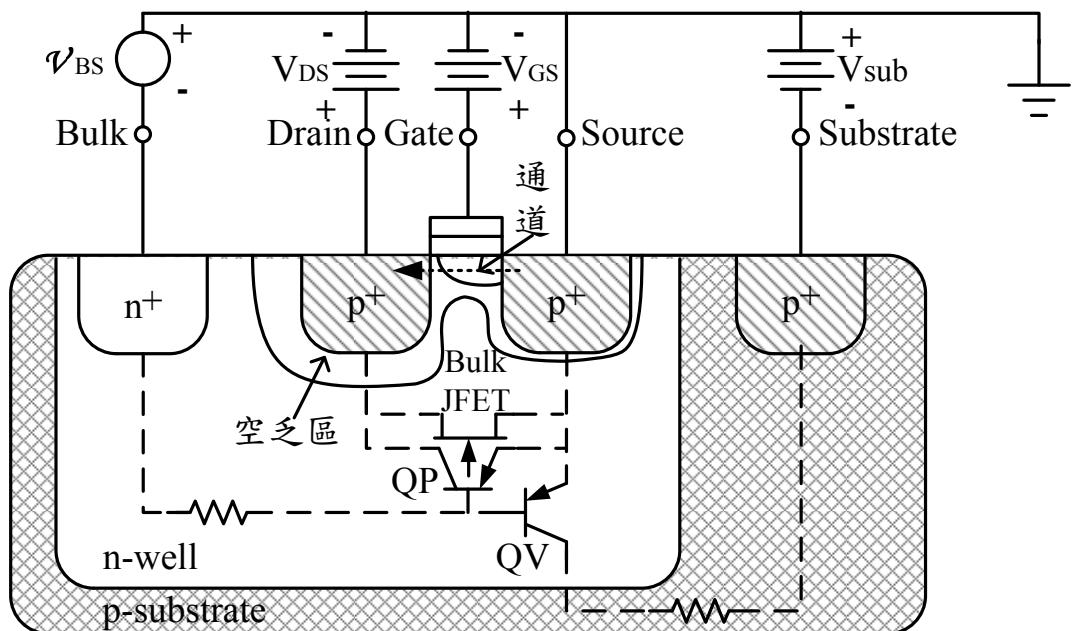

| 圖 2-16 | 基體推動 PMOS 電晶體截面圖 .....                                                                                       | 20 |

| 圖 2-17 | 可攜之無線嵌入式即時生理訊號分析系統 .....                                                                                     | 22 |

| 圖 2-18 | 入睡前體溫下降率最大值 [Murphy,1997] .....                                                                              | 23 |

| 圖 3-1  | 利用溫度開關控制偏壓電路，溫度感測經 ADC、DSP 顯示 .....                                                                          | 24 |

| 圖 3-2  | CMOS 製程中寄生縱向式 pnp 雙載子電晶體 .....                                                                               | 26 |

| 圖 3-3  | 兩個雙載子電晶體之 $I_C$ 與 $V_{BE}$ 差異產生 PTAT 電壓曲線 .....                                                              | 28 |

| 圖 3-4  | 產生 PTAT 電壓概念生成圖 .....                                                                                        | 28 |

|                                                        |    |

|--------------------------------------------------------|----|

| 圖 3-5 (a) 基本 PTAT 電流電路 ;(b) 經電流鏡之 PTAT 電流 .....        | 29 |

| 圖 3-6 能帶隙參考電壓基本原理 .....                                | 30 |

| 圖 3-7 一般能帶隙參考電壓電路 .....                                | 33 |

| 圖 3-8 (a) 基體推動相似於一 JFET ;(b) 基體推動之等效 JFET 截面圖與符號 ..... | 36 |

| 圖 3-9 基體驅動 MOSFET 小訊號模型 .....                          | 37 |

| 圖 3-10 NMOSFET 之 I-V 特性曲線 (a) 為閘極輸入 (b) 基體推動 .....     | 38 |

| 圖 3-11 不同輸入方式之差動對 (a) 閘極輸入 ;(b) 基體推動 .....             | 40 |

| 圖 4-1 溫度開關及感測之整體架構圖 .....                              | 42 |

| 圖 4-2 PTAT 電壓參考電路圖 .....                               | 44 |

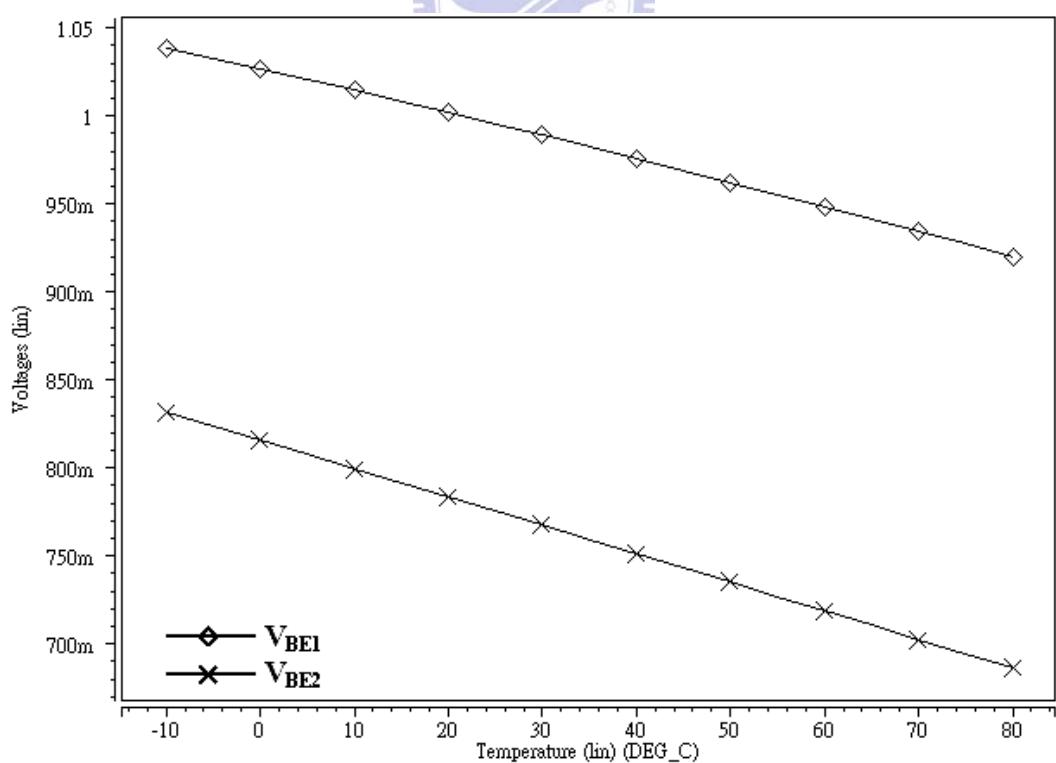

| 圖 4-3 雙載子電晶體之 $V_{BE}$ 對溫度之變化 .....                    | 44 |

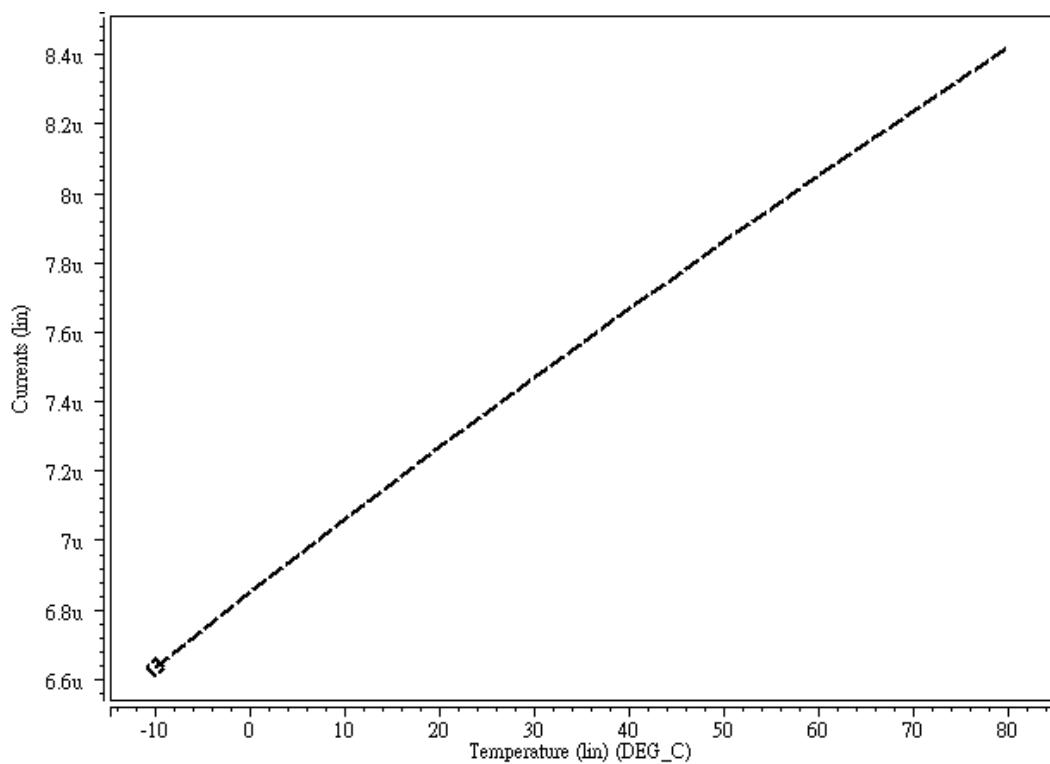

| 圖 4-4 PTAT 電流 $I_3$ 之結果 .....                          | 45 |

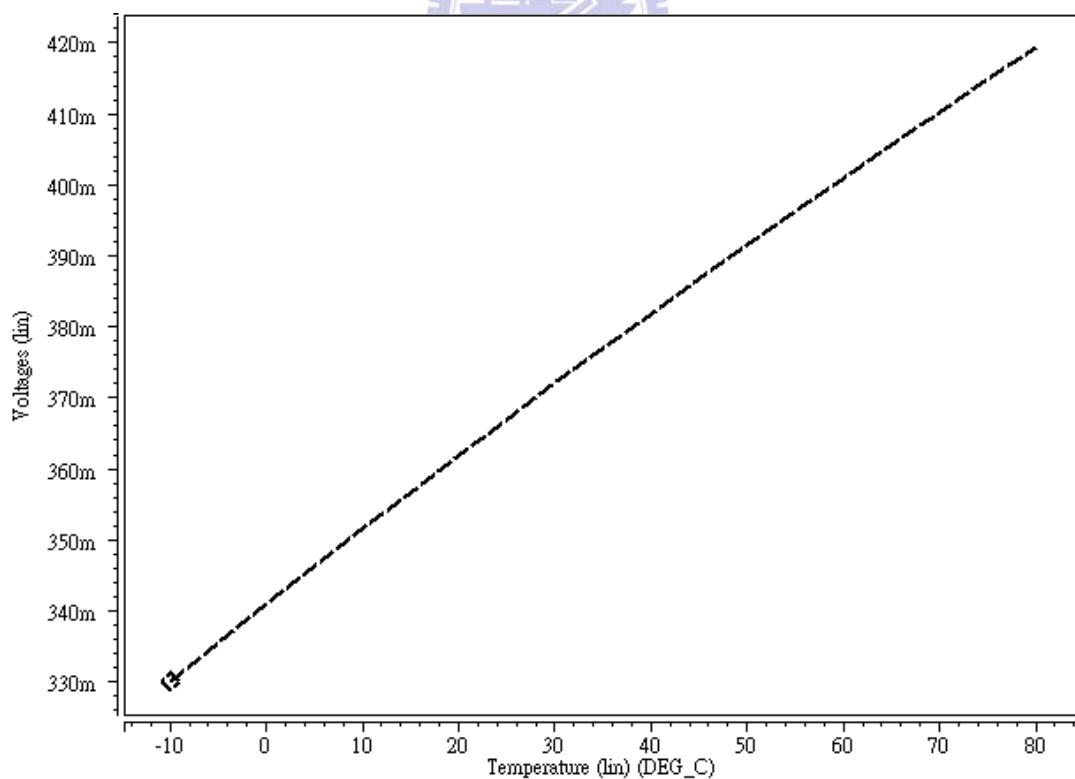

| 圖 4-5 $\Delta V_{BE}$ 之 PTAT 電壓 .....                  | 45 |

| 圖 4-6 基體推動之能帶隙參考電壓電路 .....                             | 46 |

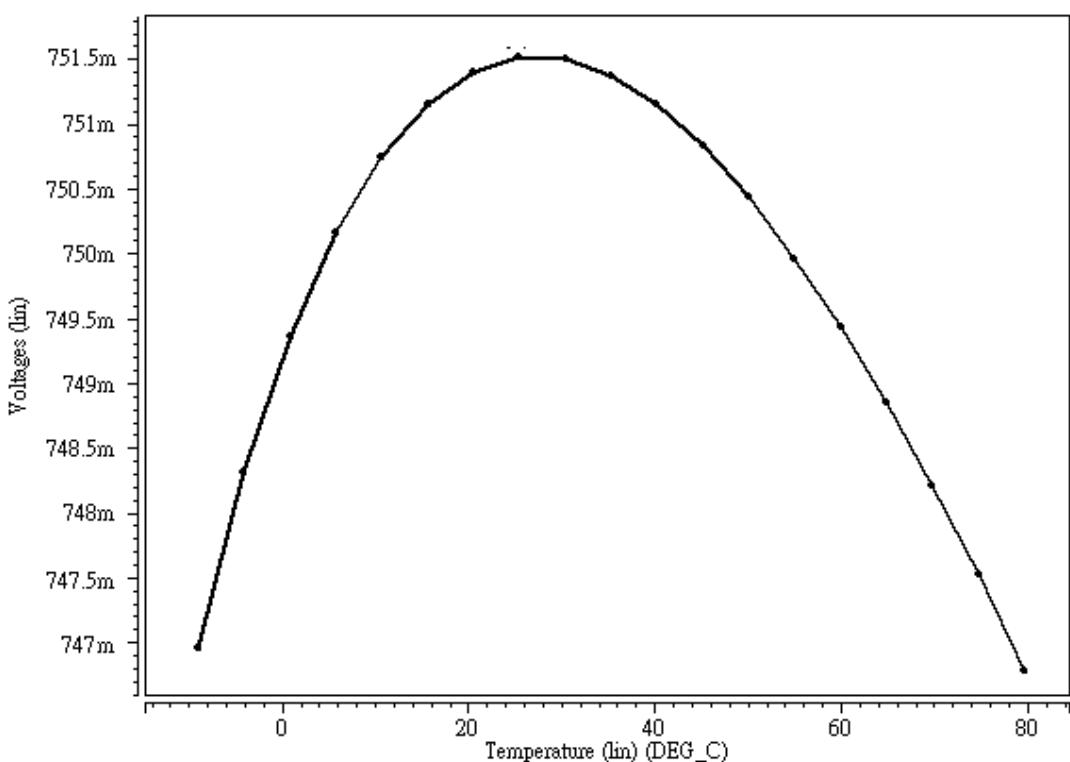

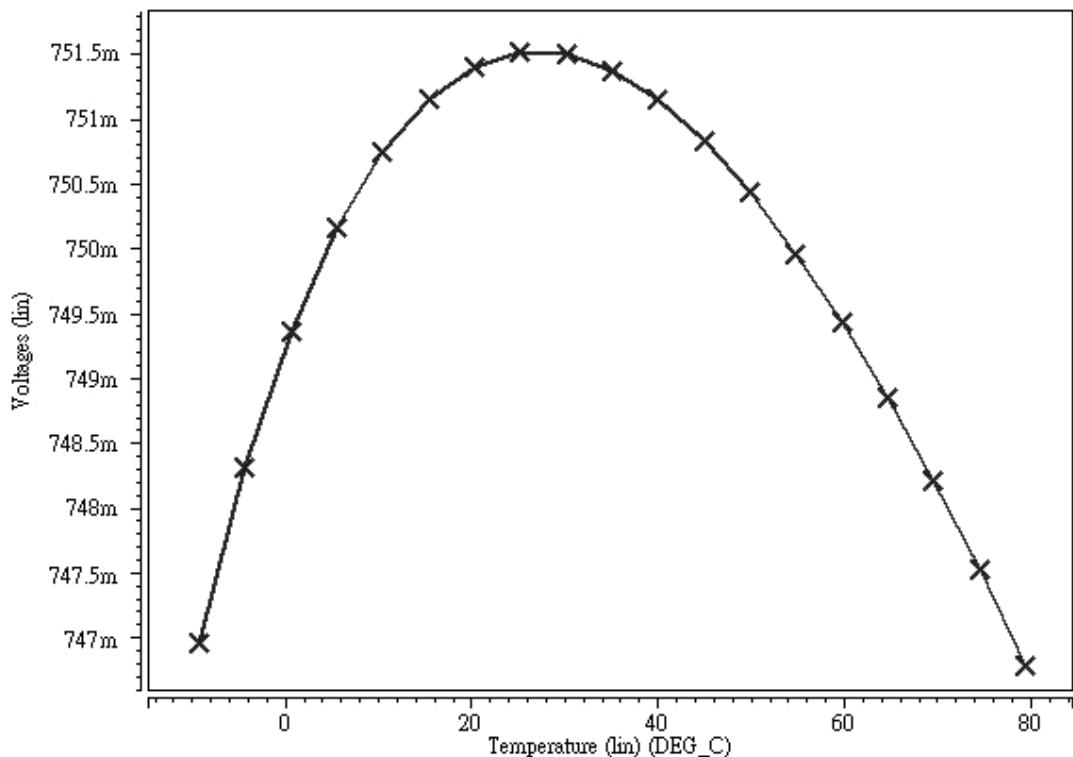

| 圖 4-7 能帶隙參考電壓電路輸出曲線 .....                              | 48 |

| 圖 4-8 雙級組態運算放大器電路圖 .....                               | 49 |

| 圖 4-9 寬擺幅定轉導偏壓電路 .....                                 | 50 |

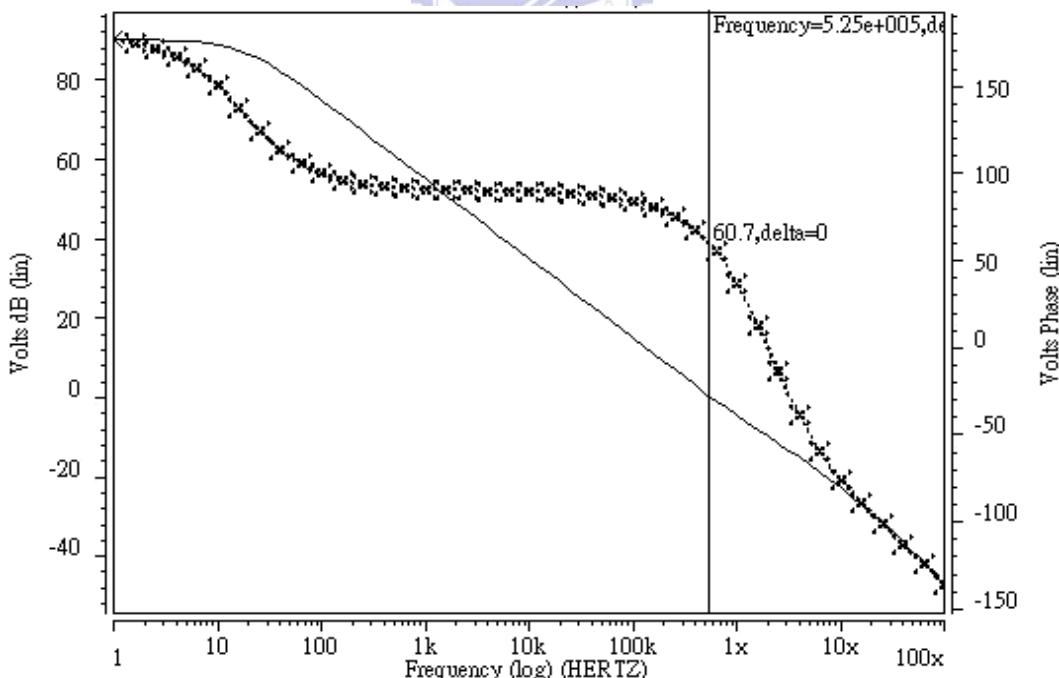

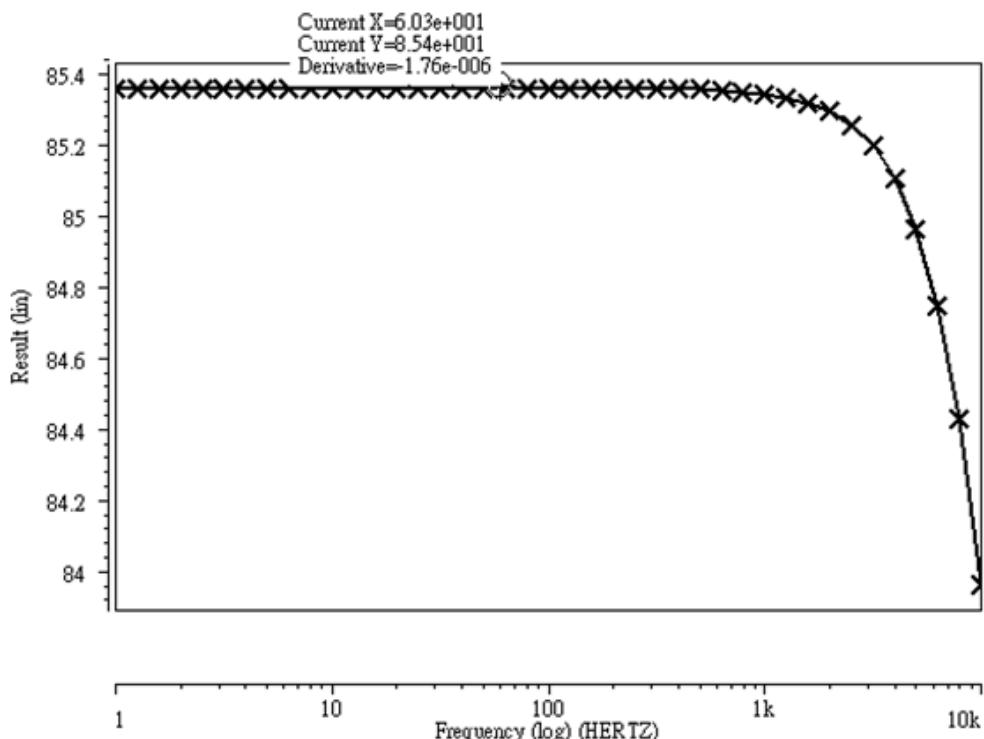

| 圖 4-10 增益-頻率響應圖 .....                                  | 51 |

| 圖 4-11 頻率響應與相位邊際值 .....                                | 51 |

| 圖 4-12 slew rate 之暫態分析 .....                           | 52 |

| 圖 4-13 共模拒斥比(CMRR) 頻率響應圖 .....                         | 52 |

| 圖 4-14 PSRR+之頻率響應 .....                                | 53 |

| 圖 4-15 PSRR-之頻率響應 .....                                | 53 |

| 圖 4-16 溫度感測顯示之架構 .....                                 | 54 |

| 圖 4-17 溫度感測電路模擬結果 .....                                | 55 |

| 圖 4-18 溫度開關架構圖 .....                                   | 55 |

| 圖 4-19 $V_{REF1}$ 模擬結果 .....                           | 56 |

| 圖 4-20 $V_{REF2}$ 模擬結果 .....                           | 57 |

| 圖 4-21 比較器輸入端之電壓模擬圖 .....                              | 57 |

| 圖 4-22 經比較器後 $V_{COMP}$ 之輸出結果 .....                    | 58 |

|                                          |    |

|------------------------------------------|----|

| 圖 4-23 模擬後端電路需 1V 之輸出 .....              | 58 |

| 圖 5-1 PNP 電晶體之佈局 .....                   | 60 |

| 圖 5-2 完整前端電路佈局(含 ESD PAD) 及電路佈局示意圖 ..... | 60 |

| 圖 5-4 溫度顯示之 pre-simulation .....         | 61 |

| 圖 5-5 溫度顯示之 post-simulation .....        | 62 |

| 圖 5-6 比較器輸入端之 pre-simulation .....       | 63 |

| 圖 5-7 比較器輸入端之 post-simulation .....      | 64 |

| 圖 5-8 比較器輸出端之 pre-simulation .....       | 65 |

| 圖 5-9 比較器輸出端之 post-simulation .....      | 66 |

| 圖 5-10 有 6 個 DRC ERROR .....             | 67 |

| 圖 5-11 可允許 DRC 之錯誤 .....                 | 67 |

| 圖 5-12 LVS 驗證正確 .....                    | 68 |

| 圖 5-13 晶片的測試架構 .....                     | 69 |

# 表目錄

|                                                   |    |

|---------------------------------------------------|----|

| 表 1-1 接觸式及非接觸式兩種溫度感測器之比較：                         | 2  |

| 表 2-1 浮動閘極 MOSFET 及基體推動 MOSFET 兩種主要方式比較表：         | 21 |

| 表 4-1 各種運算放大器( operational amplifier; OP )組態之效能比較 | 48 |

| 表 5-1 預計規格表：                                      | 70 |

# 第一章

## 緒論

### 1-1 溫度感測簡介

溫度之定義是指一物體或環境冷熱程度的數值表示，而溫標（Temperature Scale）表示法有很多，但皆是以在一大氣壓下純水之冰點（Ice Point）及沸點（Boiling Point）的溫度做為基準而訂定，常用的溫標如下：

(1) 華氏（Fahrenheit，°F）：

此表示法中，若定義水在一大氣壓其冰點為 32°F 而沸點為 212°F，兩者間差 180°F。

(2) 摄氏（Celsius，°C）：

此為公制系統的溫度單位，若定義水在一大氣壓其冰點為 0°C，沸點為 100°C，是目前最常使用的溫標。

(3) 絶對熱力學溫標（Absolute Thermodynamic Temperature Scale）：

此溫標之零點為絕對零度（絕對零度是指所有物質之熱含量為零的最高溫度）。可分為兩種：雷氏（Rankine，°F；又稱華氏絕對溫標），其冰點為 491.69°F，沸點為 671.69°F 及凱氏（Kelvin，K；又稱攝氏絕對溫標），其冰點為 273.16K，沸點為 373.16K。

在市面上能做溫度量測的材料和元件相當的多，而溫度感測器依物理量有以下型式：

1. 液體：液體因溫度上升而膨脹。

2. 氣體：氣體之體積或壓力因溫度而改變。

3. 金屬：金屬熱脹冷縮的性質。

4. 電阻特性：利用電阻熱變化之原理。

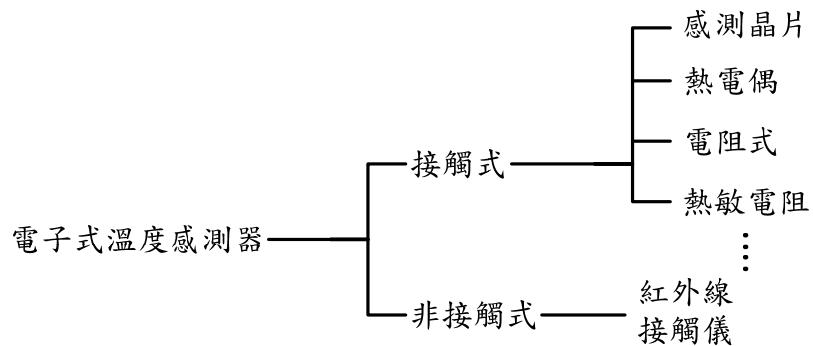

依感測方式可以分為接觸式及非接觸式，如圖 1-1 所示，表 1-1 為兩種方式之比較：

圖 1-1 一般常見的電子式溫度感測器

表 1-1 接觸式及非接觸式兩種溫度感測器之比較[1]：

|      | 接觸式                                                       | 非接觸式                                             |

|------|-----------------------------------------------------------|--------------------------------------------------|

| 量測條件 | 1. 直接接觸受測物<br>2. 受測物溫度不會因與感測器接觸而損失<br>3. 感測器溫感特性不會受直接接觸影響 | 1. 需能感測受測物之熱輻射<br>2. 受測物發散之熱輻射需明確並具再現性           |

| 工作特徵 | 1. 热容量小待測物易因直接接觸造成熱能損失<br>2. 不易量測運動中的物體<br>3. 感測位置不受限制    | 1. 不會影響受測物體之溫度<br>2. 可量測運動中之物體<br>3. 通常僅能對物體表面量測 |

| 溫度範圍 | 一般而言不適合用於過高溫情況                                            | 適用於高溫                                            |

| 感測延遲 | 需等待感測物與感測器間溫度平衡方能得到正確溫度，故延遲較久                             | 僅需量測受測物之熱輻射，故延遲較小                                |

業界因成本、體積、穩定性的考量，而常使用熱電偶感測器(Thermocouples)；熱電偶的原理是將兩種不同的金屬線焊接或絞合在一起，構成一環路，在不同的溫度金屬間會產生不同的電壓差（稱 Seebeck 效應），電壓值和環路兩接點溫度差成正比，同時滿足下列關係式：

$$V = \int_{T1}^{T2} (Q_A - Q_B) dT \quad (1.1)$$

其中  $Q$  為金屬之熱傳導係數。

實際上，金屬之熱傳導係數  $Q_A, Q_B$  與溫度幾乎無關，因此式(1.1)可以簡化成如式(1.2)趨近線性的關係式，此也是一般較常使用的關係式。

$$V = \alpha(T2 - T1) \quad (1.2)$$

熱電偶的感測範圍雖然相當廣，但卻無法整合到 IC 中使用。

電阻式溫度感測器 (RTD；Resistance Temperature Detector) 為一具有正溫度係數之導線，是利用材料的電阻隨溫度變化而改變之特性且特性曲線接近直線、線性範圍廣。一般常見有白金 (Pt)、鎳 (Ni) 和銅 (Cu) 等金屬材質，其結構主要有兩種：浸入探針 (immersion probe) 型和表面溫度感測 (surface probe) 型。RTD 量測範圍約在-200°C 到 500°C 之間。由於元件體積大，溫度傳導比較慢，不適合用於需快速的溫度量測。

熱敏電阻(thermally sensitive resistance)為陶瓷半導體材料，是利用溫度改變時內部電阻值會隨著大幅變化的特性，但熱敏電阻的電阻與溫度曲線為非線性。大部分熱敏電阻具有負溫度係數 (NTC，Negative Temperature Coefficient)，量測範圍一般在-40°C 到 150°C。因為熱敏電阻屬於電阻性質，當電流流過會產生熱量，所以要防止熱敏電阻過度自熱，否則所量測的是熱敏電阻因電流產生的溫度，而不是周圍環境要量測的溫度。

IC 式溫度感測器具備精確度高、成本低、尺寸小的優勢，且其運作溫度範圍和穩定可靠度都有良好效果，和熱電偶感測器 (Thermocouples)、熱敏電阻 (Thermistors)、電阻式溫度偵測器 (resistance temperature detectors，RTDs) 等常見的熱感測元件相比，更適合用於可攜式消費性電子產品。IC 式溫度感測器，主要可分為數位式與類比式，數位式溫度感測器則可用以偵測遠端或本地的溫

度，且能提供溫度監測、風扇控制等功能，而類比式溫度感測器能依溫度來改變輸出的電壓或電流。類比式普遍存在於不需要以數位方式來輸出或處理溫度數據的場合。

隨著 CMOS 製程的演進，積體電路也朝著將許多電路整合在同一晶片發展，此則會導致晶片中的功耗不斷增加，而解決方法是將積體電路電源電壓朝著低操作電壓來設計，但直接降低操作電壓可能導致電路無法正常動作，所以解決方法可以由製程去降低電晶體的臨界電壓 (V<sub>th</sub>)，但需要較高的製作成本，也可以利用電路設計技巧，使用基體推動(Bulk-Driven)的方法，來達到低輸入電壓、低消耗功率的效果，此方法為本論文所採用之技巧。

## 1-2 論文架構

本論文可分六個部分，各章節提要如下：

- 第一章 緒論

- 第二章 溫度感測相關研究。說明一般溫度感測設計原理，電路架構介紹，主要說明整體系統架構。本電路採用 1.5V 的供應電壓，而電路設計將受限於此電壓，所以說明何種電路適用於低電壓電路。

- 第三章 溫度感測器電路。利用 CMOS 製程中寄生 BJT 對溫度的特性，設計出正比於溫度係數電壓電路及產生與溫度無關之參考電路。

- 第四章 電路設計及模擬結果。利用基體推動架構設計溫度感測電路，並使用 HSpice 模擬電路結果。

- 第五章 晶片實現與量測。將 layout 後的 post-simulation 與 pre-simulation 結果做比較，並考慮晶片量測方式。

- 第六章 結論與未來展望。

## 第二章

### 溫度感測相關研究

本章節在說明目前有三種溫度感測器設計技巧可以適用於 CMOS 製程，在此將討論三種技巧中何種適合整合於溫度感測器。然而傳統能帶隙參考電壓源電路至少需要一個最小 1.4V 的供應電壓，但本實驗電路所用之電壓為 1.5V，此電壓用於傳統能帶隙參考電壓源電路將可能導致電路無法正常運作，所以也將探討符合溫度感測之低電壓電路。

#### 2-1 CMOS 製程溫度感測相關研究

可相容於 IC 電路中的溫度感測元件主要有二極體 (diode)、雙載子電晶體 (Bipolar Junction Transistor ; BJT)、MOS (Metal Oxide Semiconductor) 電晶體。在 CMOS 製程方面，有三種技巧可以設計溫度感測器[2]：

- (1) CMOS 電晶體操作於弱反轉區 (weak inversion)：主要是運用 MOS 操作於弱反相區之閘-源極電壓( $V_{gs}$ )，此電壓具有溫度係數的特性。

- (2) 橫向雙載子接面 (lateral bipolar) 電晶體。

- (3) 縱向雙載子接面 (vertical bipolar) 電晶體。

以下針對 CMOS 電晶體操作於弱反轉區、橫向雙載子接面及縱向雙載子接面三種設計技巧討論其特性：

## 2-1-1 弱反轉區 (weak inversion) 之溫度感測器設計

Vittoz 於[3]表示當 CMOS 電晶體操作於弱反轉區時，可以產生感溫電壓，如圖 2-1 所示，假設 Q1 及 Q2 電晶體操作於弱反轉區，則汲極電流  $I_D$  可以表示成式(2.1)[4][5][6]：

$$I_{D(1,2)} = \left( \frac{W}{L} \right)_{1,2} I_{DO} \exp \left( \frac{V_{gs(1,2)}}{n V_t} \right) \quad (2.1)$$

輸出電壓為式(2.2)：

$$V_O = V_{gs3} + n V_t \frac{R_2}{R_3} \ln \left[ \frac{I_1 I_{DO2} \left( \frac{W}{L} \right)_2}{I_2 I_{DO1} \left( \frac{W}{L} \right)_1} \right] \quad (2.2)$$

弱反轉區與強反轉區間於  $V_{GS} = V_T + 2nV_t$  產生轉變[7][8]且  $I_{DO}$  為式(2.3)[9]：

$$I_{DO} = \frac{2 K' (n V_t)^2}{e^2} \quad (2.3)$$

根據上述(2.2)與(2.3)兩個關係式、移動率 ( $\mu n$ ) 和溫度之變化為  $\mu n(T) \sim T^2$  之關係可得式(2.4)、(2.5)：

$$V_O = V_{gs3} + n V_t \frac{R_2}{R_3} \ln \left[ \frac{I_1 \left( \frac{W}{L} \right)_2}{I_2 \left( \frac{W}{L} \right)_1} \right] \quad (2.4)$$

$$V_O = V_{gs2} + A T \quad (2.5)$$

上式中若  $I_1$ 、 $I_2$  與溫度無關，則  $A$  為定值。若電晶體 Q3 為飽和區，則溫度係數為式(2.6)：

$$\frac{dV_{gs}}{dT} = \frac{V_{gs} - V_T}{T} - \left( 2 + \frac{k}{\sqrt{2\Phi_F}} \right) \left( \frac{E_G}{2q} - \Phi_F \right) \frac{1}{T} \quad (2.6)$$

當  $k = 0$ ，則近似為式(2.7)：

$$V_{gs} > V_T + \frac{E_G}{q} - 2\Phi_F = V_T \quad (2.7)$$

由式(2.5)可知  $I_1$ 、 $I_2$  可以與溫度無關，但因製程影響導致導通電壓變化大，無法取消參考電壓的溫度係數[10][11]，所以效果有限。

圖 2-1 弱反轉區參考電壓電路

## 2-1-2 橫向式雙載子接面電晶體與縱向式雙載子接面電晶體

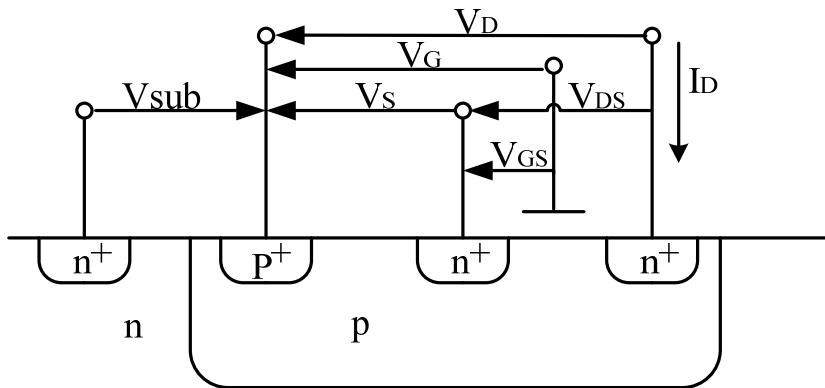

圖 2-2 (a) 為採用 p-well CMOS 製程 n 通道電晶體之截面圖。圖 2-2 (b) 表示橫向式雙載子電晶體操作時的載子流向，因為缺少了 p+埋入層，導致通道之載子遷移率不平均，基底會有漏電流產生。射極 (emitter) 電流  $I_E$  分別流向基極 (base) 電流  $I_B$ 、橫向集極 (lateral collector) 電流  $I_C$  及基底 (substrate) 電流  $I_S$ ，因此共基極電流增益 (common base current gain ;  $\alpha$ )  $\alpha = -I_C/I_E$  及  $\alpha_S = -I_S/I_E$  無法趨近 1，且基極雜質濃度低，在共射極電流增益 (common emitter current gain ;  $\beta$ )  $\beta = I_C/I_B$  及  $\beta_S = I_S/I_B$  將需較大的值，所以電流增益過低、臨界電流小及基底產生的漏電流難以精確控制，使得橫向式雙載子電晶體不適用於溫度感測。

(a)

(b)

圖 2-2 (a) 採用 p-well CMOS 製程 n 通道電晶體之截面圖；(b) 橫向式雙載子電晶體之載子流向圖

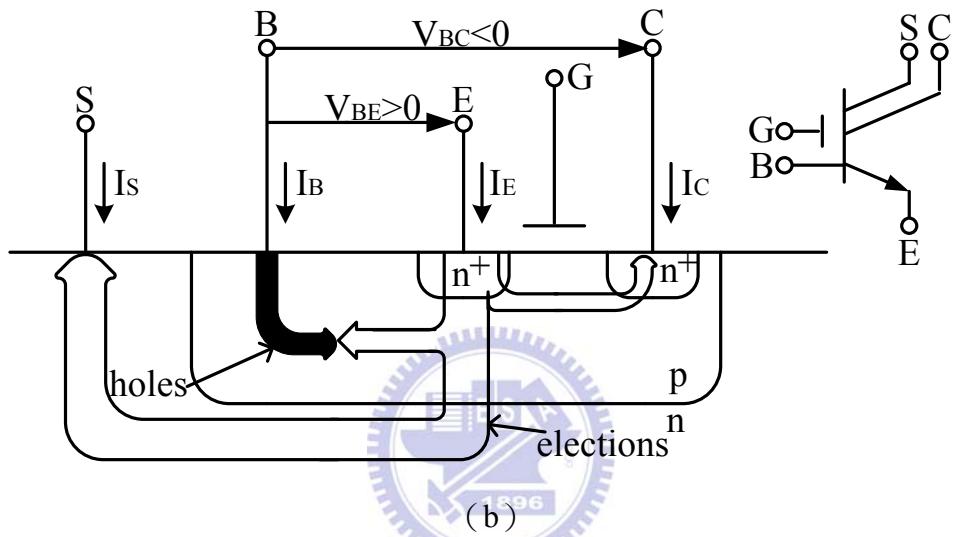

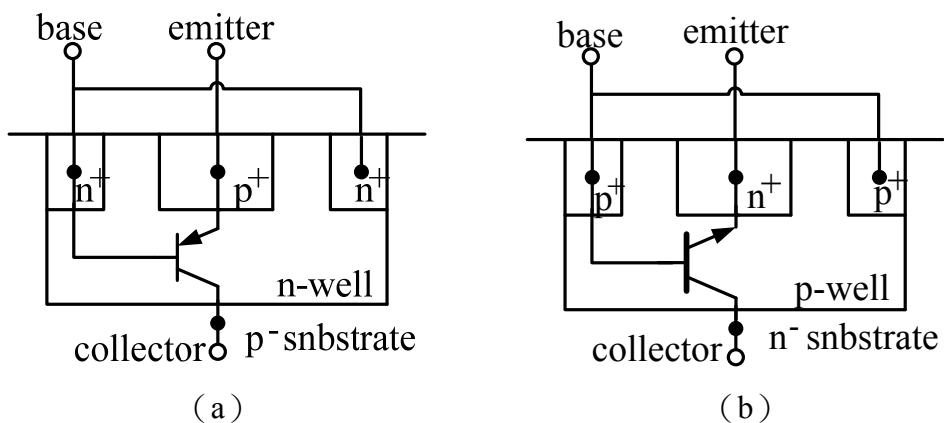

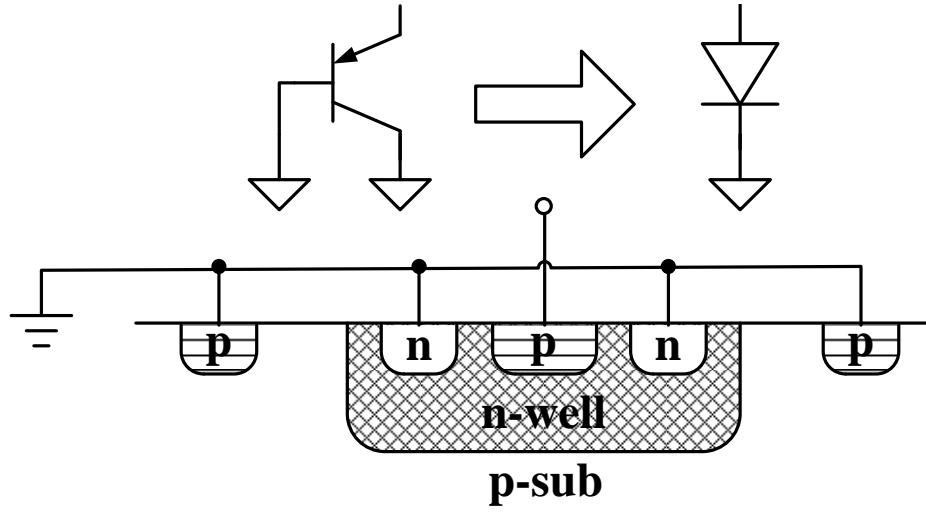

CMOS 製程中在 n-well 會產生 pnp 寄生縱向(vertical) 式雙載子接面電晶體如圖 2-3 (a)，在 p-well 會產生 npn 寄生縱向式雙載子接面電晶體圖 2-3 (b)。

圖 2-3 CMOS 製程所產生之寄生縱向式雙載子接面電晶體 (a) pnp (b) npn

根據[2]及之前的討論，縱向式雙載子接面電晶體比較適合整合於溫度感測器，且可以利用 CMOS 製程中寄生的 pnp 縱向式雙載子接面電晶體。目前也有採用 CMOS 架構的溫度感測器，但和寄生縱向式雙載子電晶體溫度感測器相比，寄生縱向式雙載子電晶體溫度感測器還是目前普遍使用的技術，原因是因為寄生縱向式雙載子電晶體受封裝影響小、所需的晶片面積小、基底漏電流較小及受製程影響較小。

## 2-2 低電壓電路設計相關研究

因為CMOS製程不斷的演進，電晶體的尺寸也不斷縮小，使得電晶體的臨界電壓（Threshold Voltage； $V_T$ ）和可靠性降低，功耗增加，而解決功耗增加方法可利用降低操作電壓來達成，操作電壓降低對數位電路則能有效降低功耗，但對於類比電路，若直接將操作電壓降低有可能會影響類比電路的正常操作，所以要達到在低電壓設計類比電路的方法有：

- (1) 採用較新製程以降低電晶體之臨界電壓值。但由於次臨界導通之影響，在深次微米（0.5到1微米）製程的臨界電壓不會比標準CMOS製程的臨界電壓有較明顯的減少[12]，所以降低操作電壓將受到臨界電壓的限制。採用電位平移（Level Shift）將所需的工作電壓低於臨界電壓，根據[13]可知，電位平移的缺點是當無輸入電流時，輸出會產生偏移電流，且偏移電流大於輸入電流時，偏移電流將影響電路之操作。

- (2) 利用浮動閘極（Floating Gate；FG）MOSFET及基體推動（Bulk-Driven）MOSFET，此兩種為主要方式[14]，以下將分別討論之。

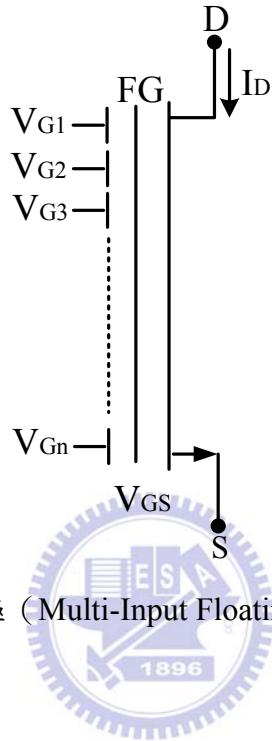

### 2-2-1 浮動閘極（Floating Gate）MOSFET

浮動閘極（FG）已經廣泛的運用在數位記憶體中，因為浮動閘極是利用多閘極的觀念，臨界電壓 $V_T$ 為可調，所以也有應用在低工作電壓環境的類比電路。浮動閘極MOSFET有浮動閘極及控制閘極兩層閘極，而浮動閘極漂浮在兩層介質之

間且有電荷儲存，因為 $\text{SiO}_2$ 有著良好的絕緣性，所以電荷放電極為緩慢，當浮動閘極MOSFET經紫外線光照射一段時間，在浮動閘極上的電荷將會消失[13]。控制浮動閘極的電壓是利用控制閘極經電容耦合方式進行，經由改變控制閘極之電壓便能調整臨界電壓大小。圖2-4為多輸入浮動閘極（Multi-Input Floating Gate；MIFG）MOSFET，使用於類比電路設計。

圖 2-4 多輸入浮動閘極（Multi-Input Floating Gate）MOSFET 電路圖

以兩輸入浮動閘極為例，將直流電壓（ $V_b$ ）加在一閘極當偏壓閘極，另加在一閘極當訊號閘極，則MOSFET的 $V_T$ 可調整成一新的值 $V_T(\text{equivalent})$ 如式(2.8) [15]：

$$V_{T(\text{equivalent})} = \frac{V_T - V_b k_1}{k_2} \quad (2.8)$$

其中  $k_1 = C_{G1}/C_{\text{TOTAL}}$ ， $k_2 = C_{G2}/C_{\text{TOTAL}}$ ，而  $C_{G1}$  及  $C_{G2}$  為浮動閘極與控制閘極之間的電容， $C_{\text{TOTAL}}$  為控制閘極與浮動閘極、浮動閘極與汲極、浮動閘極與源極、浮動閘極與基體以上之間電容的總和[16][17][18]。由式(2.8)可知，適當的選擇  $V_b$ 、 $k_1$  及  $k_2$  便能得到比  $V_T$  更低的  $V_T$  (equivalent)。假設  $gm(\text{FG})$  是從浮動閘極看入的轉導（trans-conductance），則等效轉導  $gm(\text{effective})$  如式 (2.9) [16][17][18]：

$$g_m(\text{effective}) = k_2 g_m(\text{FG}) \quad (2.9)$$

式中  $gm(\text{effective})$  比  $gm(\text{FG})$  少了  $k_2$  因子，是因為迴授是透過  $C_{gd}$  由汲極到浮動閘極，且操作在相同的偏壓條件下比 MOSFET 少了輸出阻抗。而浮動閘極的等效輸出電導  $go(\text{effective})$  為式(2.10)[13]：

$$g_o(\text{effective}) = (g_o + \left( \frac{C_{gd} g_m}{C_{TOTAL}} \right)) \quad (2.10)$$

其中 $C_{gd}$ 為閘極與汲極之電容、 $g_o$ 為MOSFET的輸出電導。圖2-5為使用浮動閘極技術的差動對(differential pair)。圖2-6利用浮動閘極所設計的基本電流鏡(current mirror)， $V_b$ 為調整MOSFET的臨界電壓。雖然浮動閘極可以在低電壓下工作，但仍有以下缺點[13]限制了浮動閘極在低壓設計的應用：

- (1) 由式(2.9)可知，浮動閘極 MOSFET 的輸出阻抗小，故只能實現於低電壓增益之架構。

- (2) 浮動閘極 MOSFET 不能使用傳統的製程，需要另外的特殊製程製作浮動閘極，製程的複雜性會增加製作成本。

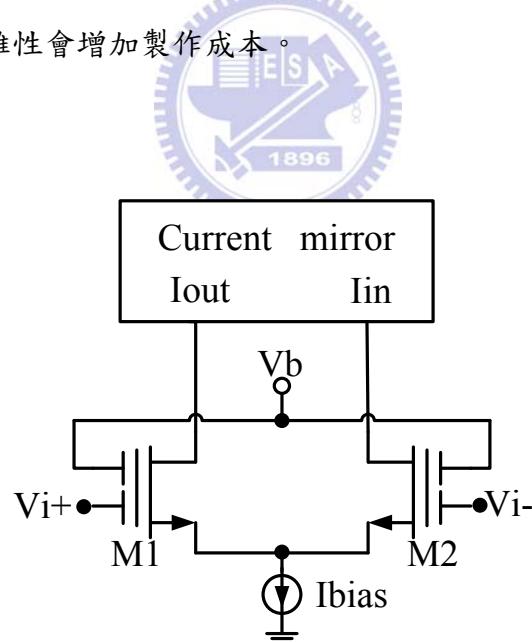

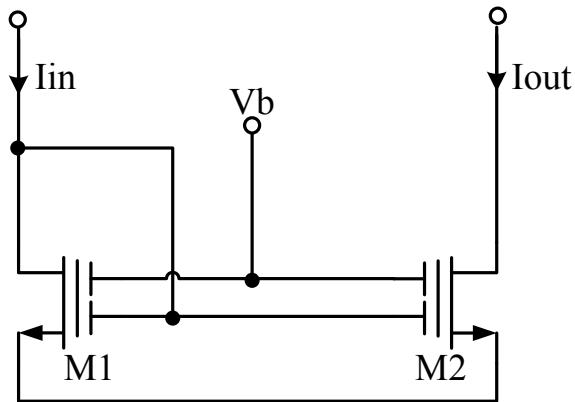

圖 2-5 浮動閘極技術之差動對電路圖

圖 2-6 利用浮動閘極技術所設計之基本電流鏡電路圖

## 2-2-2 基體推動 (Bulk-Driven) MOSFET

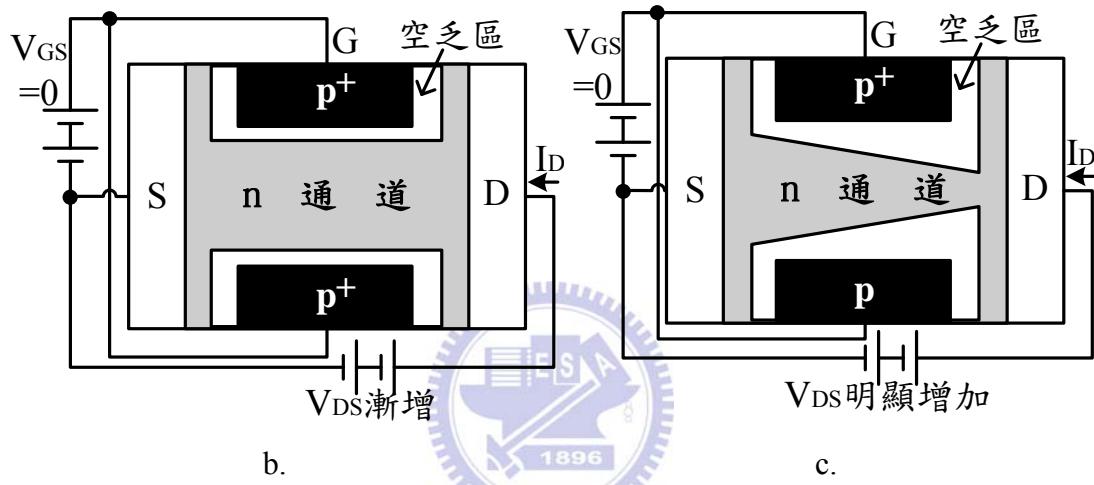

因為基體推動 (Bulk-Driven) MOSFET 與接面場效電晶體 (Junction Field Effect Transistor, JFET) 有著類似的特性與結構[19]，所以先探討接面場效電晶體的部份，以便於瞭解基體推動 MOSFET 之原理。

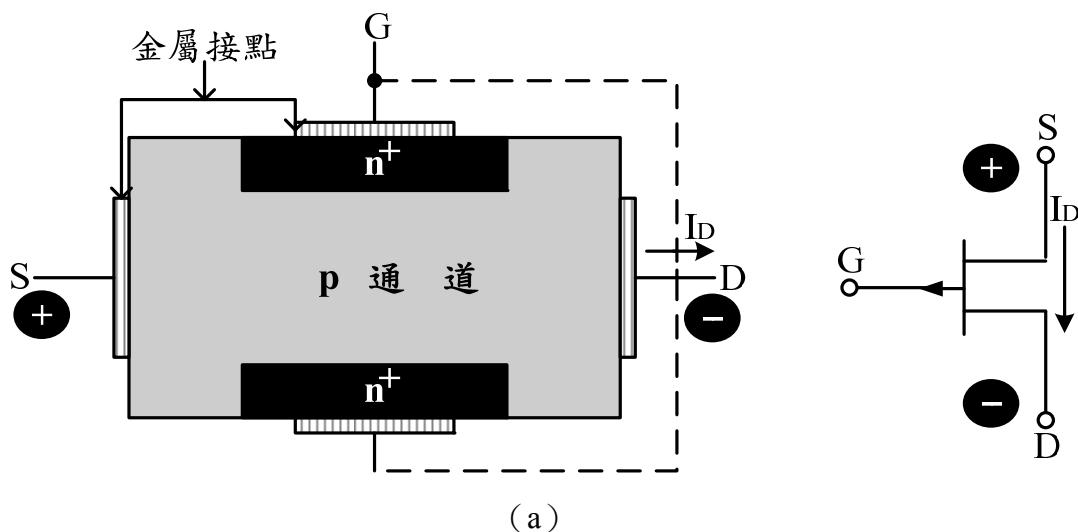

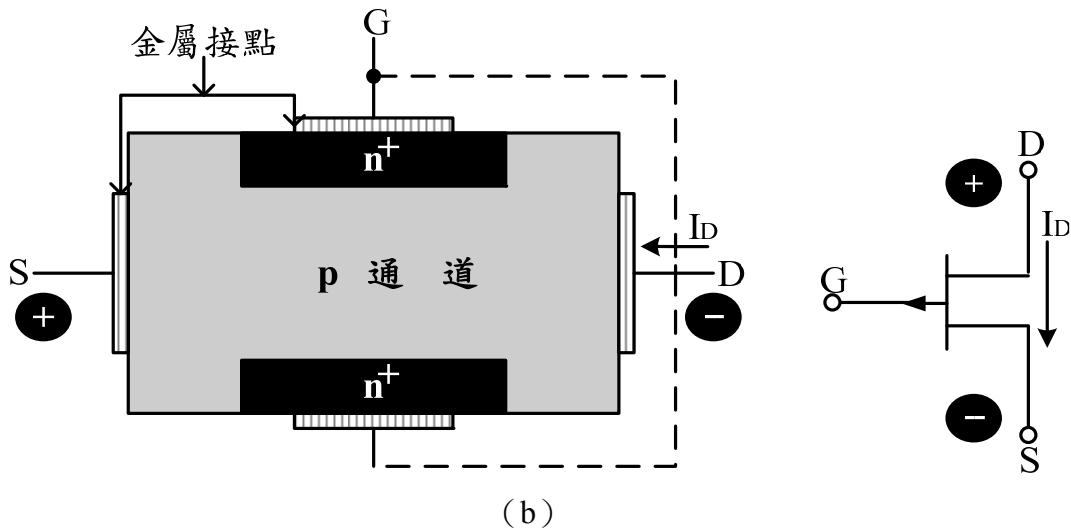

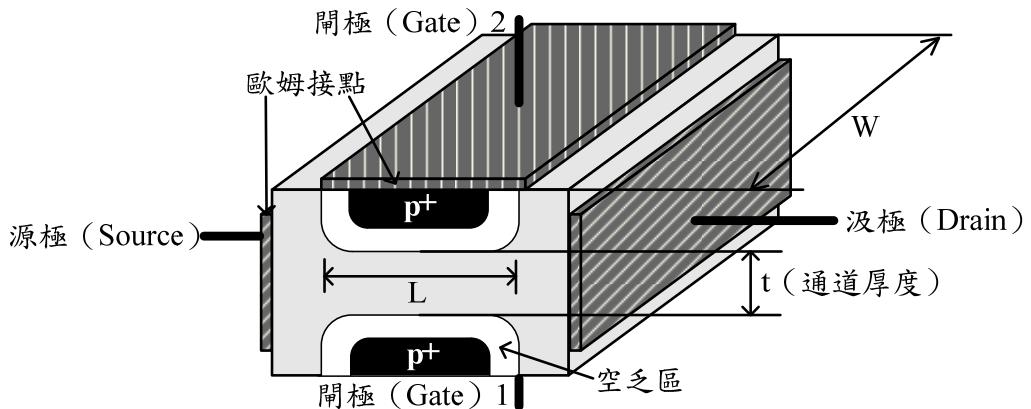

接面場效電晶體架構為三端點元件，其三端點分別為汲極 (Drain, D 極)、閘極 (Gate, G 極)、源極 (Source, S 極)，是一種具有內建通道的電晶體，而依內建通道的摻雜可分為 p 通道及 n 通道，如圖 2-7。因 JFET 中沒有氧化層，閘極只靠 pn 接面反偏來阻隔閘極電流，其阻隔效果比 MOS 之氧化層絕緣差，且 JFET 閘極電流在每升高  $10^{\circ}\text{C}$ ，電流大小就會倍增，對於溫度相當敏感。

圖 2-7 分別為結構及電路符號；(a) 為 p 通道 JFET，(b) 為 n 通道 JFET

就 n 通道 JFET 而言，n 是指通道上的半導體型態為 n 型，多數載子為電子。圖 2-8 通道 JFET 的結構示意圖，閘極是以 p+型半導體而源極與汲極是以 n 型半導體通道連結，個別再經由歐姆接點接到外界電路。閘極為控制電子之流動，若將閘極 1 及閘極 2 連結到同一電位如圖 2-7 (b)，在閘極與通道之間的 pn 接面加上逆向偏壓，會產生一個與電子運動方向垂直的內建電場即空乏區。因為摻雜濃度的關係，通道的摻雜濃度低於閘極，所以空乏區主要會落在通道上。若在源極和汲極間形成電位差，則可驅動通道上多數載子（電子）之流動。當逆向偏壓改變，可以增大或縮小 pn 接面在通道間空乏區的寬度，藉以改變源極與汲極間的通道電阻  $R_{DS}$ ，進而達到控制電流之目的，而  $R_{DS} = \rho(L/(t \times W))$  或  $R_{DS} = \rho(L/A)$ ，其中  $\rho$  為材料的電阻率，L 為通道長度，W 為通道寬度，t 為半導體通道的厚度，A 為通道的等效截面積，故通道厚度 t 變小，通道電阻  $R_{DS}$  則越大。若閘極逆向偏壓持續增加到一定值，n 通道將會整個被空乏區寬度佔滿而消失，此通道的情況稱之為夾止（pinch off），因通道厚度 t 消失，所以通道電阻  $R_{DS}$  變成很大，此時的閘極電壓差為夾止電壓(pinch-off voltage) $V_p$ 。

圖 2-8 n 通道 JFET 結構示意圖

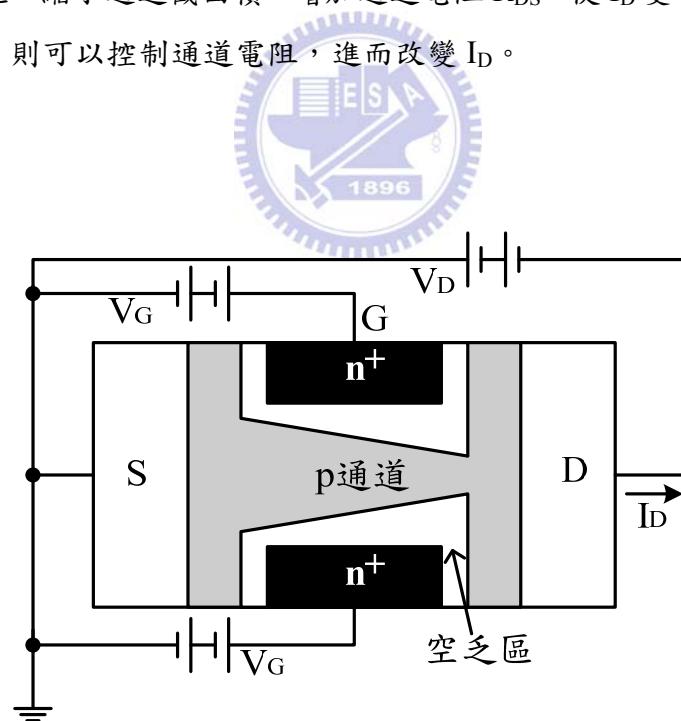

而 p 通道 JFET 之偏壓可如圖 2-9：(1) 源極與汲極間加上順向偏壓  $V_D$ ，驅使通道中的電洞形成電流  $I_D$ 。(2) 源極與閘極、汲極與閘極產生逆向偏壓  $V_G$ ，增加 pn 空乏區，縮小通道截面積，增加通道電阻  $R_{DS}$ ，使  $I_D$  變小。若  $V_D$  為一定值而改變  $V_G$ ，則可以控制通道電阻，進而改變  $I_D$ 。

圖 2-9 p 通道 JFET 偏壓

p 通道 JFET 和 n 通道 JFET 差異是在於 p 通道是由 p 型半導體形成，導通時驅動電洞由源極經通道流入汲極，源極電位必須高於汲極，且閘極是由 n+型半

導體所形成，在閘極必須加上一定的正電壓才能將通道夾止，也就是正值的夾止電壓  $V_p$ 。所以 p 通道 JFET 和 n 通道 JFET 差異為電流和偏壓的極性相反，其他特性均類似，以下將以 n 通道 JFET 進行討論之。

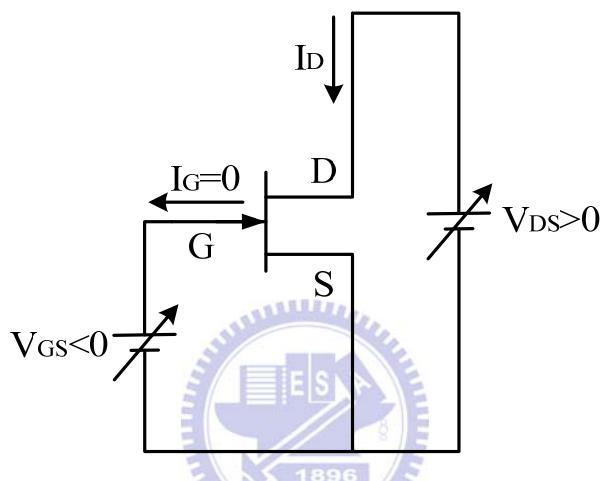

n 通道 JFET 的閘極為 p 型半導體，所以需要較低電位 ( $V_{GS}$ ) 才有反偏效果，且汲極的電位需大於源極電位產生電位差 ( $V_{DS}$ )，才能形成電流，如圖 2-10。因此，依反偏情況而言，源極與閘極之間較弱，汲極與源極之間較明顯，通道形成情況在源極最大，汲極處最小。所以  $V_{GS}$  決定通道之有無， $V_{DS}$  決定通道之夾止。

圖 2-10 n 通道 JFET 接上所需偏壓

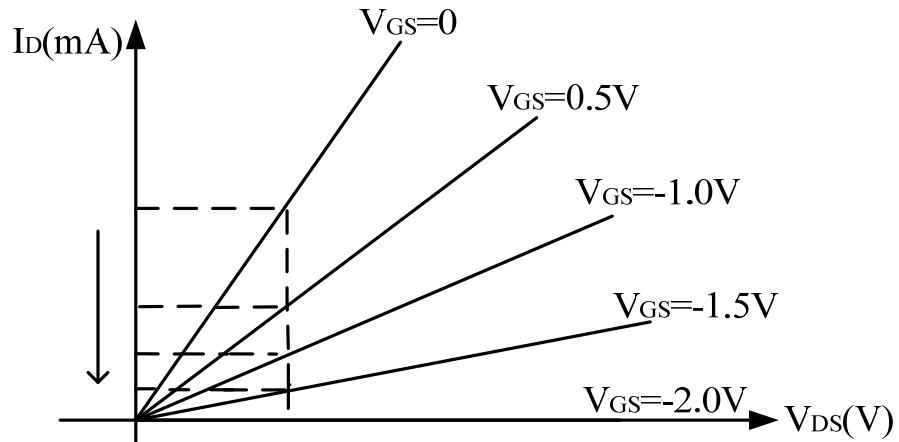

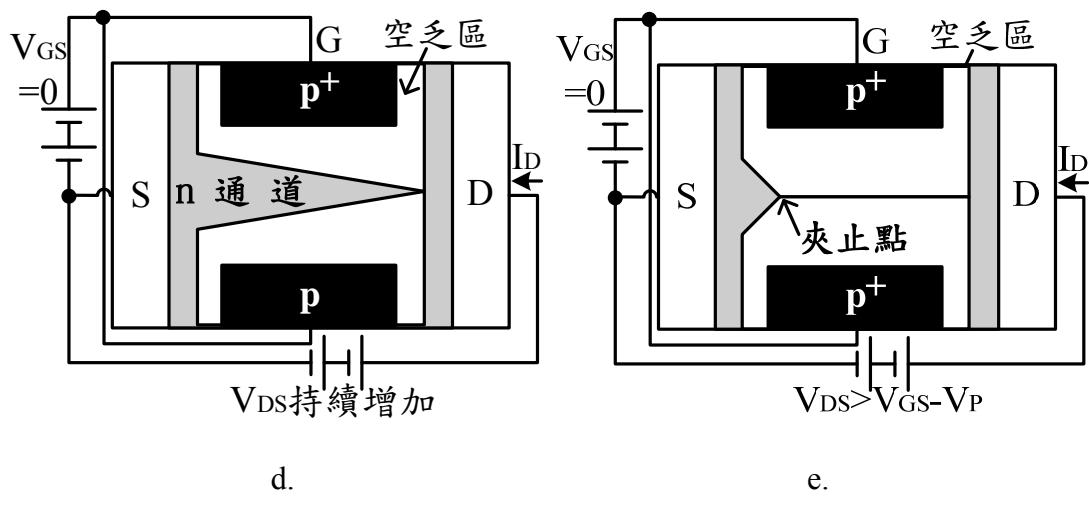

當汲、源間所加電壓  $V_{DS}$  很小時，可以觀察不同的  $V_{GS}$  對  $I_D$  控制變化如圖 2-11。假設汲、源間所加電壓  $V_{DS}=0$  時：(1)  $V_{GS}=0$  時，通道最寬，電阻最小如圖 2-12 (a)。(2) 當  $V_{GS}<0$  時，如圖 2-12 (b)，因通道的摻雜濃度小於閘極，導致空乏區往通道變寬而使通道變薄及通道電阻  $R_{DS}$  增加。圖 2-11 虛線為  $V_{GS}$  越往負變化，在相同的  $V_{DS}$ ， $I_D$  則會變小。(3) 當  $V_{GS}$  小於  $V_p$ ，兩側之空乏區將在通道中央閉合，通道全部被夾止，如圖 2-11 (c)。因空乏區中沒有了電子，汲-源間的電阻將會無窮大，所以  $I_D=0$ ，此操作區稱為截止區，而  $V_{GS}$  稱為夾止電壓 ( $V_p$ )。

圖 2-11 電壓  $V_{DS}$  很小時，不同  $V_{GS}$  對  $I_D$  的變化

圖 2-12  $V_{GS}$  對通道電阻的變化；(a)  $V_{GS}=0$  時的情況，(b)  $V_{GS}$  反偏時，空乏區增大，通道寬度減少，通道電阻增加，(c)  $V_{GS} < V_p$ ，通道全部被夾止

上述主要是假設  $V_{DS}$  為定值的情況，閘源極電壓 ( $V_{GS}$ ) 決定了空乏區的寬度

[20]，以下則假設  $V_{GS}$  為定值且  $V_p < V_{GS} < 0$ ，改變  $V_{DS}$ ，能影響  $I_D$  操作的情況，圖 2-13 為 n 通道 JFET 電流  $I_D$  對電壓  $V_{DS}$  變化過程，與相對應之特性曲線，如下說明。

- (a) 當  $V_{GS} < 0$  反偏至某一程度，空乏區擴展到將源極通道完全消失，且無電流形成，此臨界狀態稱為夾止，而  $V_{GS}$  為夾止電壓，即為  $V_p$ ，其大小與通道摻雜濃度及通道寬度平方正比。因此， $V_{GS} < V_p$  時源極的通道呈現夾止為截止的情況，所以必須滿足  $V_{GS} \geq V_p$  通道才能存在。

- (b) 當  $V_{GS} = 0$ ， $V_{DS}$  微幅增加，則通道兩邊的反偏電壓相近，所以空乏區與通道深淺均勻，此時  $I_D$  與  $V_{DS}$  成線性關係，通道電阻保持定值。

- (c)  $V_{DS}$  明顯上升， $V_{GD}$  反偏效果大於  $V_{GS}$ ，空乏區沿源極往汲極方向寬度漸增，通道呈現不均勻分佈且寬度隨  $V_{DS}$  上升而下降，通道電阻已非線性，故  $I_D = I_{DSS} / V_p^2 (V_{GS} - V_p)^2 = I_{DSS} (1 - V_{GS} / V_p)^2$ ， $I_D$  變化減緩，此時汲極尚未夾止，所以滿足  $V_{GD} > V_p$ ，即  $V_{DS} < V_{GS} - V_p$ 。

- (d)  $V_{DS}$  持續增加到  $V_{DS} = V_{GS} - V_p$  即  $V_{GD} = V_{GS} - V_{DS} = V_p$  (夾止電壓)時，恰可夾止通道在汲極處，因為此時通道仍然存在，通道內電場仍能使多數載子移動，所以汲極電流  $I_D \neq 0$ 。

- (e) 當  $V_{GD} < V_p$  時，即是  $V_{DS} > V_{GS} - V_p$ ，夾止區由汲極端往源極端延伸，通道的有效長度變小，便產生通道長度調變效應，導電通道電阻與  $V_{DS}$  變化不大，但會與  $V_{DS}$  所形成之電場強度大小有關，此區域稱恆流區 (constant-current) 或是稱之為飽和區 (saturation region)。飽和區之特點為  $I_D$  幾乎不隨  $V_{DS}$  變化，故曲線近似水平， $I_D$  已趨近飽和，因為  $I_D$  大小僅受控制於  $V_{GS}$ ，若  $|V_{GS}|$  增加，通道電阻將增加， $I_D$  減少，此時  $I_D$  可由方程式 (2.11) 表示：

$$I_D = \frac{I_{DSS}}{V_p^2} (V_{GS} - V_p)^2 = I_{DSS} \left(1 - \frac{V_{GS}}{V_p}\right)^2 \quad .(2.11)$$

其中第二等式為 Shockley's 方程式， $I_{DSS}$  為  $V_{GS} = 0$  之飽和電流。

特性曲線

a.

b.

c.

d.

e.

圖 2-13  $V_{GS}$  為定值且  $V_P < V_{GS} < 0$  時，電流  $I_D$  對電壓  $V_{DS}$  變化過程，與相對應之特性曲線

根據式(2.11)可以繪出圖2-14飽和轉換曲線，曲線為拋物線是因 $V_{GS}$ 變化在 $V_P$ 和0之間時， $I_D$ 和 $(V_{GS}-V_P)^2$ 為正比[20]。JFET因具有雜訊低的特點[21]，所以適合用於低電壓及低電流之電路。

圖 2-14 飽和轉換曲線

當達到飽和區時，若持續增加 $V_{DS}$ ，則夾止點將會往源極移動，將會使 $I_D$ 略隨 $V_{DS}$ 增加，所以飽和區曲線會呈現斜線，如圖 2-15，即為通道長度調變效應，所以可以將式(2.11) $I_D$ 特性方程式修正為式(2.12)：

$$I_D = \frac{I_{DSS}}{V_p^2} (V_{GS} - V_p)^2 (1 + \lambda V_{DS}) \quad (2.12)$$

其中通道調變效應係數  $\lambda = V_A^{-1}$ ， $V_A$  為 Early 電壓。

圖 2-15 通道長度調變效應

### 2-2-3 基體推動MOSFET之原理

類比電路設計於低壓時受到臨界電壓 ( $V_T$ ) 的限制，所以在 CMOS 技術中 MOSFET 要操作在強反轉 (Strong Inversion) 當作放大器使用，其所需電源需滿足式(2.13)[22]：

$$V_{DD} + |V_{SS}| \geq V_{GS} = V_{DSsat} + |V_T| \quad (2.13)$$

其中  $V_{DD}$  為正電源， $V_{SS}$  為負電源， $V_T$  為PMOS或NMOS電晶體最大臨界電壓值。

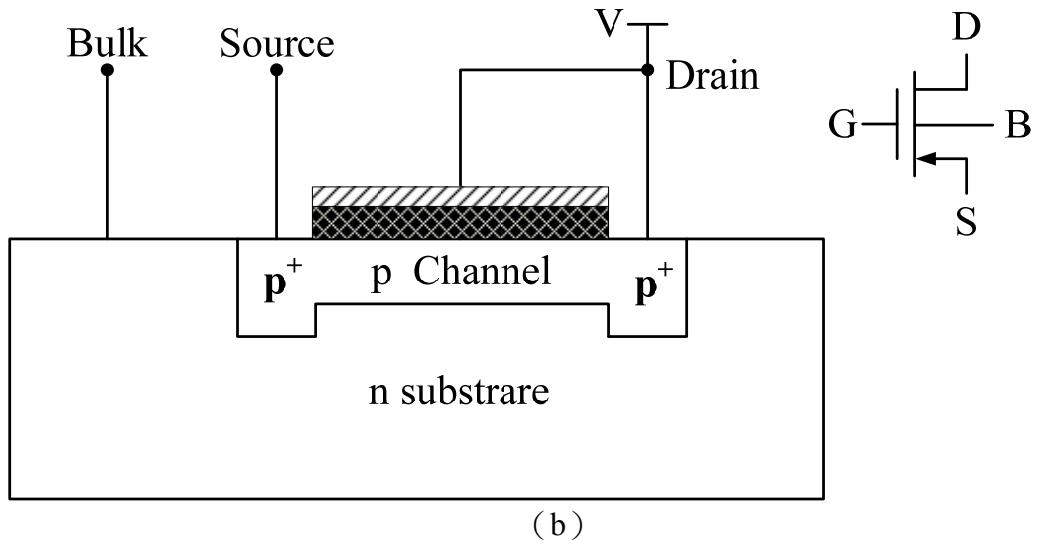

若使用閘極推動 (gate-driven) 之MOSFET，則電源需改成式(2.14)[22]：

$$V_{DD} + |V_{SS}| \geq V_{GS} = V_{DSsat} + |V_T| + V_{signal} \quad (2.14)$$

上式中需要比式(2.13)多考慮輸入訊號之電壓值( $V_{signal}$ )。若 MOSFET 改為基體推動技術，則式(2.14)的臨界電壓值  $V_T$  則可以在輸入電壓訊號  $V_{signal}$  中消除，便能增加電壓訊號的擺幅。基體推動技術只能用於獨立阱 (independent well) 之 MOSFET，主要是避免其他阱 (well) 的訊號干擾到輸入訊號，而因為需要獨立阱，就目前的製程僅 PMOS 符合使用基體推動技術，圖 2-16 為 n-well 基體推動技術 PMOS 電晶體之截面圖，圖中標示了寄生的橫向 pnp (QP)、直向 pnp (QV) 電晶體與 bulk JFET 來表示此 MOSFET[23]。

圖 2-16 基體推動 PMOS 電晶體截面圖

雖然基體推動 MOSFET 適用於低電壓之類比電路，但仍有以下缺點[13]：

- (1) 基體推動 MOSFET 之  $g_m$  比閘極推動 MOSFET 之  $g_m$  小。

- (2) 基底輸入 MOSFET 若設計不良可能會使寄生之雙極性電晶體（Bipolar Junction Transistors, BJT）導通，進而發生門鎖（latch up）現象。

- (3) 基體推動 MOSFET 受限於製程技術。當使用單一 n-well 製程，此時 NMOSFET 並不具有 p-well，則只能使用基體推動 PMOS 電晶體，NMOS 電晶體無法採用基體推動的方式，反之，若使用單一 p-well 製程，此時 PMOSFET 並不具有 n-well，則只能使用基體推動 NMOS 電晶體，PMOS 電晶體無法採用基體推動的方式。

- (4) 因為不同的基體推動 MOSFET，其輸入需在獨立的 well，如此輸入端才能避免其他 well 訊號干擾，此會造成佈局面積增加。在設計時若需要相互匹配的電晶體，在佈局時需將相互匹配的 MOS 電晶體盡量靠近，無法用一般 MOS 電晶體匹配的畫法。

表 2-1 為浮動閘極與基體推動技術的比較表[13]：

表 2-1 浮動閘極 MOSFET 及基體推動 MOSFET 兩種主要方式比較表：

| 技術   | 有效頻寬 | 電壓要求          | 功耗 | 製程要求 |

|------|------|---------------|----|------|

| 浮動閘極 | 中    | $<2VT$        | 中  | 特殊   |

| 基體推動 | 低    | $\approx 2VT$ | 高  | 特殊   |

### 2-3 研究動機

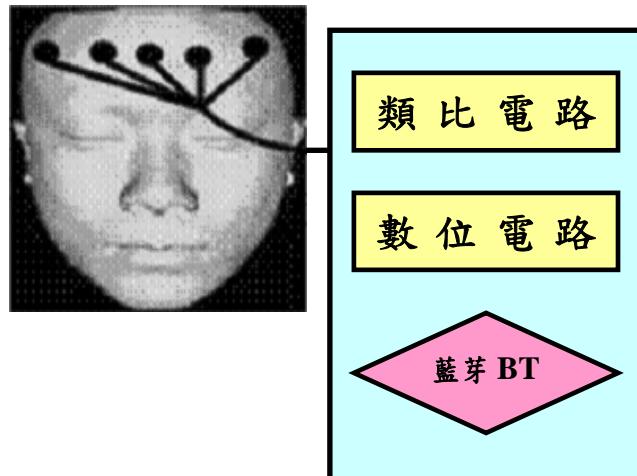

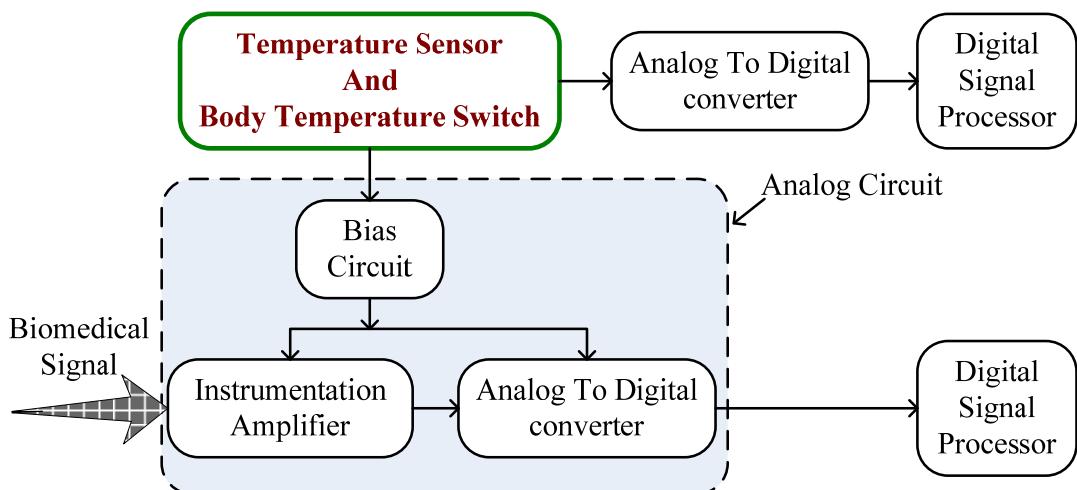

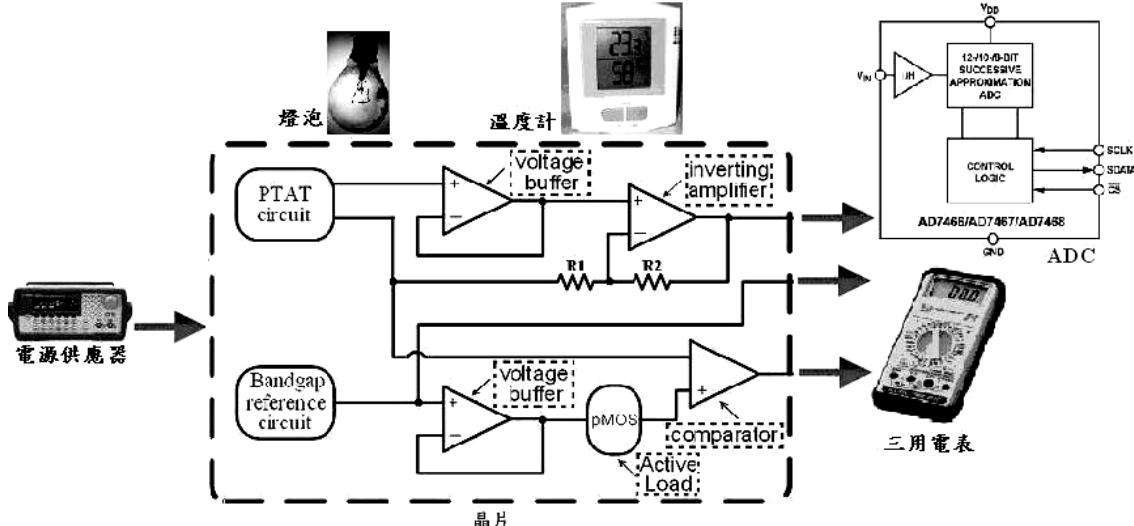

為了配合本實驗室所研發的「可攜之無線嵌入式即時生理訊號分析系統」如圖 2-17，讓此系統達到與人接觸時，能自動開啟及顯示其溫度的功能，此系統的前端分為兩部分：(1) 類比電路和 (2) 數位控制電路部份。類比電路主要就是為了要將擷取進來的訊號做到放大的功能和濾波等功能，等到前置處理完畢之後，將會經過 ADC(Analog to Digital Converter)的轉換，再經由數位電路來控制

每一個通道(Channel)所抓取到的 Data，最後利用 SPI(Serial Peripheral Interface) 傳輸介面來與後端藍芽輸出做個做特定輸出頻率上的溝通。

圖 2-17 可攜之無線嵌入式即時生理訊號分析系統

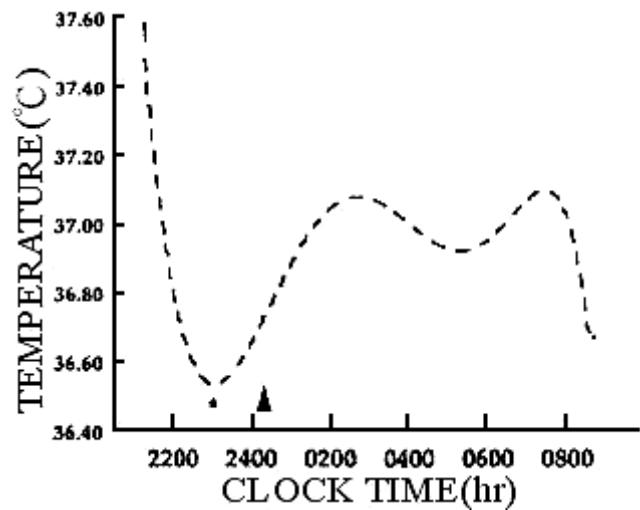

利用體溫當啟動的訊號，是因為體溫相對於心跳或腦波是人體中較明顯的生理訊號，且一般在擷取生理訊號時，環境溫度為受測者最能接受的溫度，大部分為室溫  $25^{\circ}\text{C}$ ，而人體額頭溫度比實際體溫略低約為  $36^{\circ}\text{C}$ ，故運用室溫及額溫的溫差來判斷是否啟動電路，但為了縮短溫度上升等待的時間，將設計在  $30^{\circ}\text{C}$  時就能準備啟動系統，且  $30\text{--}35^{\circ}\text{C}$  之間作為緩衝之用，不會立即讓後端電路動作，如此可以避免誤動作的產生。因為一開始由類比電路擷取訊號，類比電路皆有偏壓 (bias) 部份，所以為了達到自動啟動，最佳的方式是控制最前置的類比偏壓電路部分，決定是否開始擷取訊號。本實驗室之分析系統主要是觀察人體睡意前的  $\alpha$  波，而溫度顯示可以觀察人體在進入睡眠狀態時的體溫變化，如圖 2-18，根據 Murphy[1997] 在該研究中發現，將近 90% 的受測者體溫下降率最大值會在睡前的一段時間內，圖 2-18 中圓點記號代表體溫下降率最大的時候 (以每分鐘體溫變化為單位)，而三角形記號為受測者實際入睡時間[24]，由此可以研究受測者體溫之變化。本系統是運用在可攜式型態，電壓來源將採用電池，市面上電池之電壓約為  $1.5\text{V}$ ，所以相關整合電路設計電壓源皆為  $1.5\text{V}$ 。採用半導體的方式來感測溫度，是因為雙載子接面電晶體對於溫度敏感的特性、成本低、高敏感度及便整合於類比電路中。

圖 2-18 入睡前體溫下降率最大值 [24]

## 第三章

### 溫度感測器電路

在「可攜之無線嵌入式即時生理訊號分析系統」的類比電路部份有儀表放大器 (Instrumentation Amplifier, IA) 及數位類比轉換 (Analog to Digital Converter, ADC) , 而以上電路皆有偏壓 (bias) 電路，則可以利用開關去控制 IA 及 ADC 的偏壓電路，即能控制 IA 及 ADC 電路之運作，而人體體溫為相當明顯的生理訊號，因此可以利用人體溫度去控制分析系統之運作，又因為與人體有所接觸，所以也能測得人體溫度，偵測受測者當時的情況。所以本章將討論在 CMOS 製程中感測溫度之電路。

#### 3-1 系統架構

如圖 3-1 為整體系統的架構圖，圖中溫度開關控制 IA 及 ADC 的偏壓電路，溫度感測則由外接 ADC 顯示溫度效果。

圖 3-1 利用溫度開關控制偏壓電路，溫度感測經 ADC、DSP 顯示

溫度開關方面是利用 CMOS 製程中的縱向雙載子 (vertical bipolar) 電晶體感測體溫，此電路會產生正比於絕對溫度 (Proportional To Absolute Temperature) 電壓的特性，另一電路為能帶隙參考 (bandgap reference) 電壓電路，此電路能產生不受製程與溫度影響的電壓，將此電壓當作比較器的參考位準，與正比於絕對溫度電壓比較，比較器後端連接一 MOSFET 當開關，控制 IA 及 ADC 之偏壓電路，而之後整合時，IA 及 ADC 將使用同一偏壓電路，以有效控制分析系統整體電路。

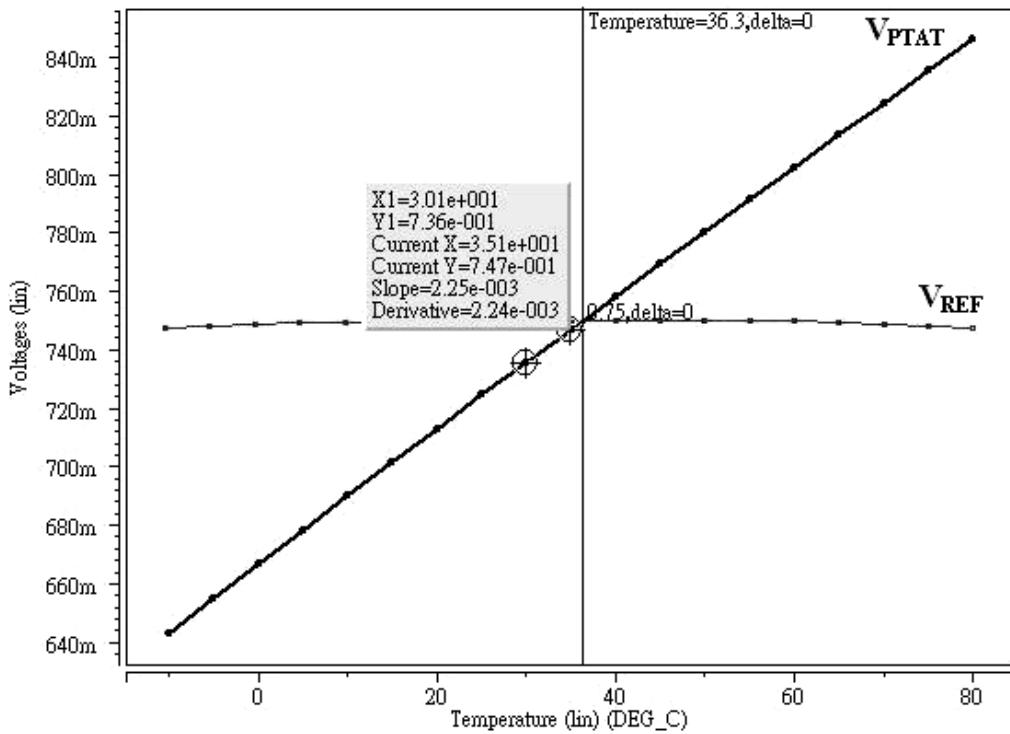

溫度顯示方面是將縱向雙載子電晶體感測的正比於絕對溫度電壓，經反相放大器調整線性度及解析度，以便於符合外接 10-bit 類比數位轉換器 (型號 AD7466) 使用，而為了之後能將類比數位轉換器整合於積體電路之內，所以將預留能帶隙參考電壓，電壓值為 0.75V，此 0.75V 電壓將會與正比於絕對溫度電壓交叉於 36°C，如此在此工作範圍可以得到較佳的感測準確度。

溫度開關與溫度感測皆是利用同一個正比於絕對溫度電壓電路及同一個能帶隙參考電壓電路，運用電壓緩衝器、反相放大器、主動負載及比較器達到開關及溫度顯示的功能，而不需利用兩組正比於絕對溫度電壓電路與能帶隙參考電壓電路，才能完成開關及溫度顯示的功能。

本論文提出一個用於可攜式裝置的溫度整合開關設計，低功率將是重要考量之一，最直接的方法是利用降低操作電壓解決此考量，而在數位電路中降低操作電壓，確實能有效的降低功耗，但對於類比電路降低操作電壓將可能電路無法正常動作，且一般傳統溫度感測電路的運算放大器也影響了最低供應電壓的範圍，所以為了符合在低電壓的情況，溫度感測電路將採用基體推動 (Bulk-Driven) MOSFET 之架構，此架構有別於一般利用閘極 (Gate) 輸入的方式，是利用基體當輸入端，解決了閘極輸入受限於臨界電壓 (threshold voltage) 的限制，而且可以增加輸入擺幅範圍。

### 3-2 CMOS 溫度感測器

本論文所使用的架構為第二章所提的 pnp 寄生縱向式雙載子接面電晶體，而接線方式類似於二極體 (diode) 如圖 3-2，由於是屬於寄生的 pnp 寄生縱向式雙載子

接面電晶體，所以 $\beta$ 值很低，易造成電路的失真及準確度不夠，所以皆會使用一放大器架構改善其缺點。

圖 3-2 CMOS 製程中寄生縱向式 pnp 雙載子電晶體

### 3-2-1 正比於絕對溫度電路

大多數 CMOS 製程溫度感測器整合，皆採用基底雙載子電晶體感測溫度。對於單一個雙載子元件而言，集極電流與基極-射極電壓關係如式(3.1)：

$$I_C(T) = I_S(T) \exp\left(\frac{-V_{BE}}{V_T}\right) \quad (3.1)$$

上式中  $I_S$  為飽和電流和  $\mu kTni^2$  成比例， $\mu$  為遷移率、 $ni$  為載子濃度， $T$  為凱式 (Kelvin) 絕對溫度。 $V_T$  為臨界電壓  $V_T = kT/q$ ， $k$  為波茲曼 (Boltzmann) 常數  $(1.38066 \times 10^{-23} J/K)$ ， $q$  為單位電荷帶電量  $(1.60218 \times 10^{-19} C)$ 。飽和電流  $I_S$  可以表示成式(3.2)[25]：

$$I_S(T) = A_E q \left( \frac{D_p n_{po}}{L_p} + \frac{D_n p_{no}}{L_n} \right) \quad (3.2)$$

其中  $A_E$  為射極面積， $D_p$  為電洞在 n 型半導體內的擴散常數， $D_n$  為電子在 p 型半導體內的擴散常數， $n_{po}$  與  $p_{no}$  分別為 p 型半導體及 n 型半導體內之少數載子之

平衡濃度， $L_p$  為電洞在 n 型半導體內之擴散常數， $L_n$  為電子在 p 型半導體內之擴散常數。將上式整理可得式(3.3)集極電流密度之方程式：

$$I_C(T) = A_E C T^\eta \exp\left(\frac{V_{BE} - V_{g0}}{V_T}\right) \quad (3.3)$$

式中 C 及  $\eta$  皆為製程相關常數， $V_{g0}$  為在 0K 時的能隙電壓。

由式(3.3)可導出  $V_{BE}$  之關係式式(3.4)：

$$V_{BE} = V_T \ln\left(\frac{I_C(T)}{A_E C T^\eta}\right) + V_{g0} \quad (3.4)$$

現在考慮假設某溫度  $T_\gamma$  時的  $I_C$  值式(3.5)：

$$I_C(T_\gamma) = A_E C T_\gamma^\eta \exp\left(\frac{V_{BE}(T_\gamma) - V_{g0}}{V_T}\right) \quad (3.5)$$

由上式可以導出  $V_{BE}(T_\gamma)$  式(3.6)：

$$V_{BE}(T_\gamma) = V_{g0} + V_{T_\gamma} \ln\left(\frac{I_C(T_\gamma)}{A_E C T_\gamma^\eta}\right) \quad (3.6)$$

將以上重新整理可得式(3.7)：

$$V_{BE}(T) = V_{g0} \left(1 - \frac{T}{T_\gamma}\right) + \frac{T}{T_\gamma} V_{BE}(T_\gamma) - \eta V_T \ln \frac{T}{T_\gamma} + V_T \ln \left(\frac{I_C(T)}{I_C(T_\gamma)}\right) \quad (3.7)$$

從上式可以發現  $V_{BE}$  幾乎與溫度呈線性。

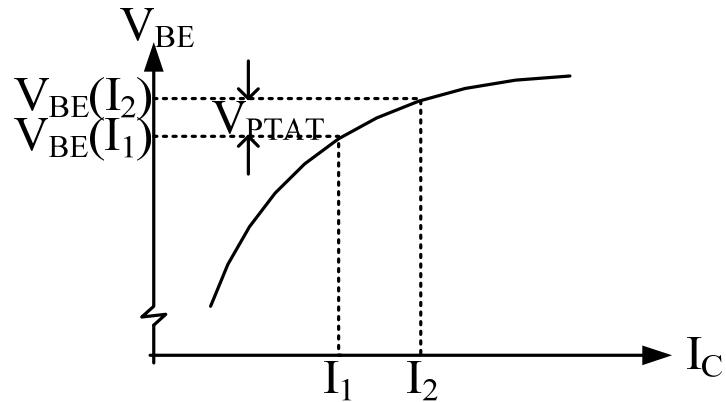

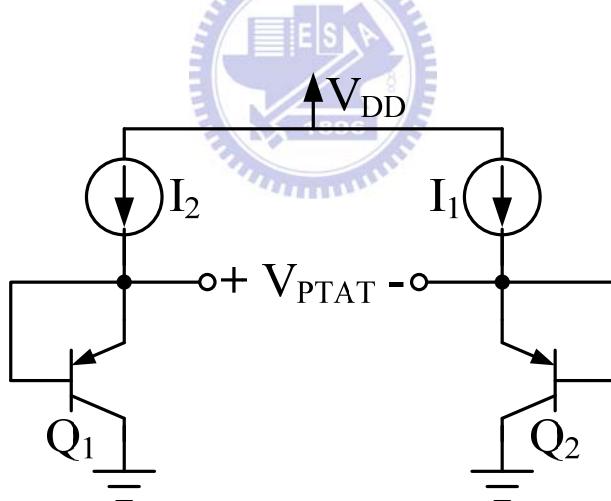

當有兩個雙載子電晶體操作於不同的射極電流密度，則基極-射極電壓差將正比於絕對溫度(Proportional To Absolute Temperature ; PTAT)，如圖3-3所示[26]。在圖3-4中假設電晶體規格一致 ( $I_S$  飽和電流相同) 而  $I_1$  為集極電流，則  $V_{BE}(I_1) = (kT/q) \ln(I_1/I_S)$ 。兩  $V_{BE}$  之電壓差可以得 PTAT 電壓 ( $V_{PTAT}$ ) 為式(3.8)：

$$V_{PTAT} = V_{BE}(I_2) - V_{BE}(I_1) = \frac{kT}{q} \ln \left( \frac{I_2}{I_1} \right) \quad (3.8)$$

若  $I_2 = nI_1$ ， $n$  為  $Q_1$  與  $Q_2$  的比值，則  $V_{PTAT} = (kT/q) \ln n$ ，因此  $V_{PTAT}$  為一正溫度係數電壓。若在相同集極電流 ( $I_1 = I_2$ ) 流入兩個不同尺寸的電晶體，而形成電流密度不同，其結果也得到一正溫度係數電壓，同(3.8)式。

圖 3-3 兩個雙載子電晶體之  $I_C$  與  $V_{BE}$  差異產生 PTAT 電壓曲線

圖 3-4 產生 PTAT 電壓概念生成圖

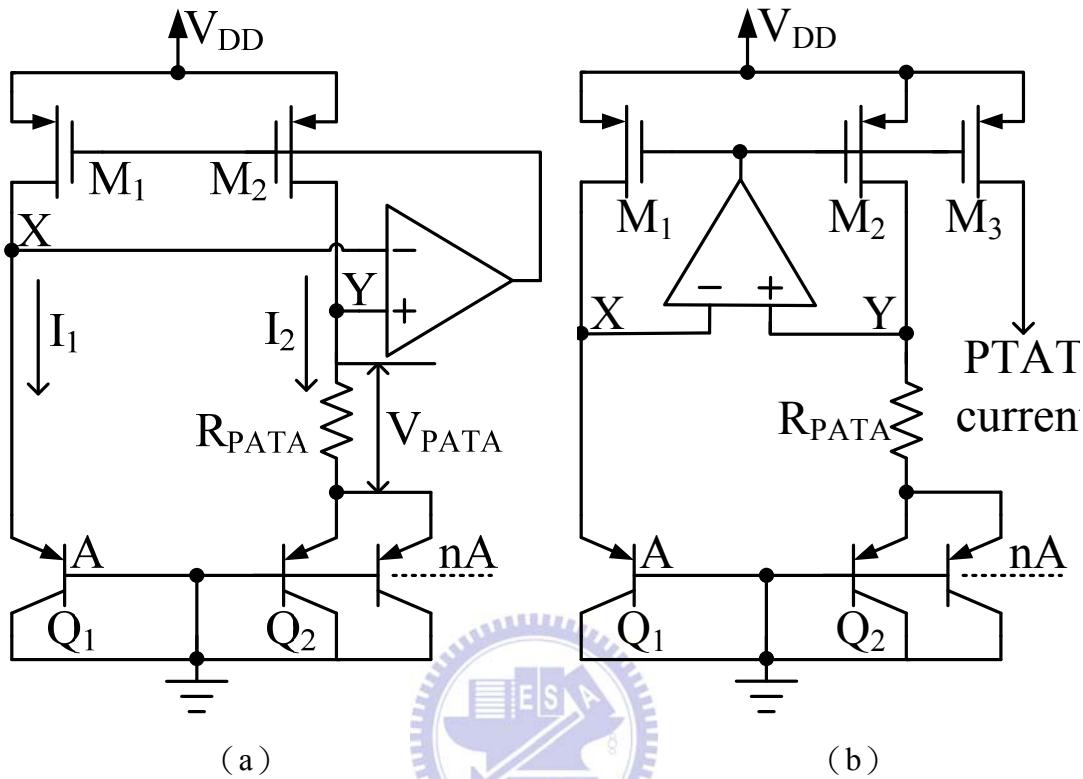

圖3-5 (a) 為產生PTAT電流的基本電路，是由 $Q_1$ 、 $Q_2$ 兩個pnp BJT電晶體及 $R_{PTAT}$ 電阻產生PTAT電流，運算放大器主要因為開路電壓增益大，透過負迴授(negative feedback)機制確保虛短路(virtual short)的性質，將輸出、入端關係限定住，使得X、Y兩點之電位相同。在操作時可以分為流經 $Q_1$ 的集極電流( $I_1$ )、流經 $Q_2$ 的集極電流( $I_2$ )與運算放大器的工作電流，當 $I_1 = I_2$ 時，電路需確保 $X =$

$Y$ ，所以  $I_1 = I_2 = (V_T \ln n) / R_{PTAT}$ ， $n$  通常為 8，經電流鏡後取得 PATA 電流，如圖 3-5 (b)。而此架構需運算放大器與若干電阻，所以面積相對比較大。

圖 3-5 (a) 基本 PTAT 電流電路；(b) 經電流鏡之 PTAT 電流

### 3-2-2 能帶隙參考電壓源 (Bandgap Reference) 電路

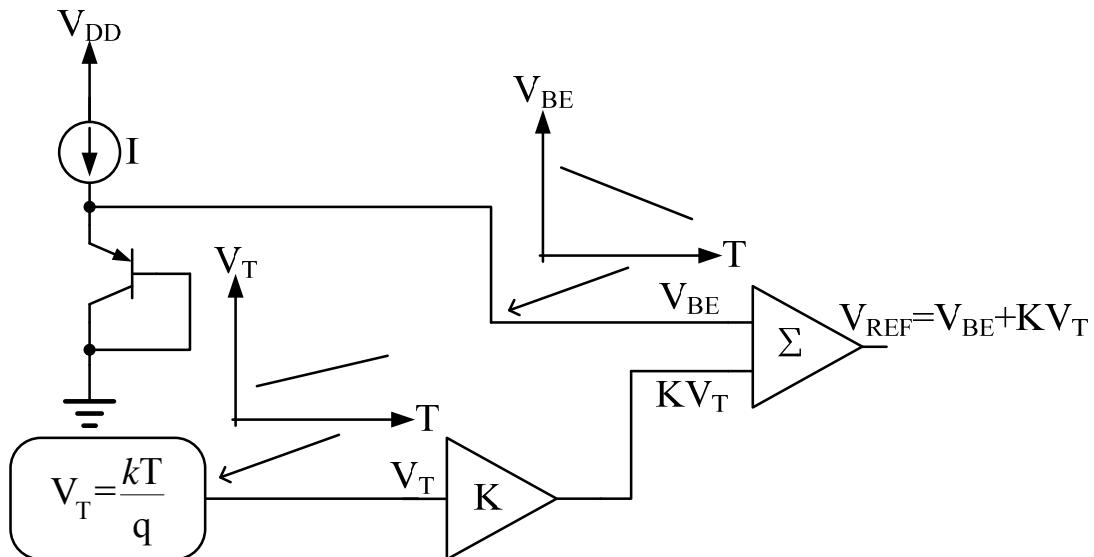

參考電壓源 (Voltage reference) 的目的為了產生和製程無關、具溫度特性的電源，而所要求之溫度特性有：(1) 常數轉導 ( $G_m$ ) 偏壓，轉導為決定雜訊、小訊號增益之參數，理想情況是使其轉導和溫度、製程無關。(2) 與絕對溫度成正比 (Proportional To Absolute Temperature；PTAT)。(3) 與溫度無關，大部分製程參數和溫度互有關係，若能產生與溫度無關之參考電路，此電路通常應與製程無關。能帶隙參考電壓之額定溫度係數 (Temperature Coefficients, TCs) 為零，是利用兩個正、負相反的 TC，經適當的加權相加，即能得到一個零 TC 值。

傳統的能帶隙參考電壓原理如圖 3-6 所示，首先以  $pn$  接面順向導通產生  $V_{BE}$ ，此值為負溫度係數，此外  $pn$  接面也產生一正比於絕對溫度之熱電壓  $V_T (= kT/q)$ ，

先將  $V_T$  乘上常數  $K$  再與  $V_{BE}$  電壓相加，完成零溫度係數的電壓輸出特性式(3.9)。

$$V_{REF} = V_{BE} + KV_T \quad (3.9)$$

圖 3-6 能帶隙參考電壓基本原理

根據圖3-6可知，能帶隙參考電壓需先有一組負溫度係數電壓，由式(3.1)可知  $I_S$  和  $\mu kT n_i^2$  之關係，而這些數值可以用  $\mu \propto \mu_0 T^m$ ， $m \approx -3/2$  來表示與溫度之相關性及  $n_i^2 \propto T^3 \exp[-E_g/(kT)]$ ， $E_g$  為 Si 的能帶隙約 1.12eV，因此  $I_S$  為式(3.10)：

$$I_S = b T^{4+m} \exp \frac{-E_g}{kT} \quad (3.10)$$

式中  $b$  為比例因子。依式(3.1)可得  $V_{BE} = V_T \ln(I_C/I_S)$ ，此將基極-射極電壓對溫度微分，可以計算基極-射極電壓之溫度係數，而  $I_C$  電流特性為溫度之函數，但為簡化分析，將  $I_C$  假設成常數，可得式(3.11)：

$$\frac{\partial V_{BE}}{\partial T} = \frac{\partial V_T}{\partial T} \ln \frac{I_C}{I_S} - \frac{V_T}{I_S} \frac{\partial I_S}{\partial T} \quad (3.11)$$

式(3.11)中的  $\partial I_S / \partial T$  可由式(3.10)將  $I_S$  對  $T$  取微分得式(3.12)：

$$\frac{\partial I_S}{\partial T} = b(4+m)T^{3+m} \exp \frac{-E_g}{kT} + bT^{4+m} \left( \exp \frac{-E_g}{kT} \right) \left( \frac{E_g}{kT^2} \right) \quad (3.12)$$

所以  $(V_T \partial I_S) / (I_S \partial T)$  為式(3.13)：

$$\frac{V_T}{I_S} \frac{\partial I_S}{\partial T} = (4+m) \frac{V_T}{T} + \frac{E_g}{kT^2} V_T \quad (3.13)$$

將上式代入式(3.11)中，整理為式(3.15)：

$$\frac{\partial V_{BE}}{\partial T} = \frac{V_T}{T} \ln \frac{I_C}{I_S} - (4+m) \frac{V_T}{T} - \frac{E_g}{kT_2} V_T \quad (3.14)$$

$$= \frac{V_{BE} - (4+m)V_T - E_g/q}{T} \quad (3.15)$$

由上式可以得知  $V_{BE}$  本身之溫度係數與溫度相關性。

如式(3.8)所提，若  $I_2 = nI_1$ ， $n$  為  $Q1$  與  $Q2$  的比值，則  $V_{PTAT} = V_{BE} = (kT/q) \ln n$ ，因此， $V_{BE}$  之微分表示為一個正溫度係數式 (3.16)：

$$\frac{\partial V_{PTAT}}{\partial T} = \left( \frac{k}{q} \right) \ln n \quad (3.16)$$

由式(3.15)及式(3.16)相加整理，可得式(3.17)，式中  $V_T \ln n$  為在兩個不同集極電流密度時，雙載子電晶體之  $V_{BE}$  電壓差。將式(3.17)適當的調整  $a1$  及  $a2$  即可以得到與溫度無關之參考電路。

$$V_{REF} = a1V_{BE} + a2(V_T \ln n) \quad (3.17)$$

若將式(3.9)  $V_{REF}$  對  $T$  取微分為式(3.18)：

$$\frac{\partial V_{REF}}{\partial T} = \frac{\partial V_{BE}}{\partial T} + \frac{V_T}{T} \ln n \quad (3.18)$$

再將式(3.18)設為零且  $\partial V_{BE} / \partial T$  利用式(3.15)取代之，可得式(3.19)，整理後為式(3.20)：

$$\frac{V_{BE} - (4+m)V_T - E_g/q}{T} + \frac{V_T}{T} \ln n = 0 \quad (3.19)$$

$$V_{BE} - (4+m)V_T - E_g/q = -V_T \ln n \quad (3.20)$$

將式(3.20)代入式(3.9)可以得式(3.21)：

$$V_{REF} = \frac{E_g}{q} + (4+m)V_T \quad (3.21)$$

式中  $E_g/q$  為 Si 之能帶隙， $m$  為溫度指數之遷移率， $V_T$  為熱電壓。所以當  $T \rightarrow 0$  則  $V_{REF} \rightarrow E_g/q$ ，此即稱為能帶隙參考電壓 (bandgap reference)。

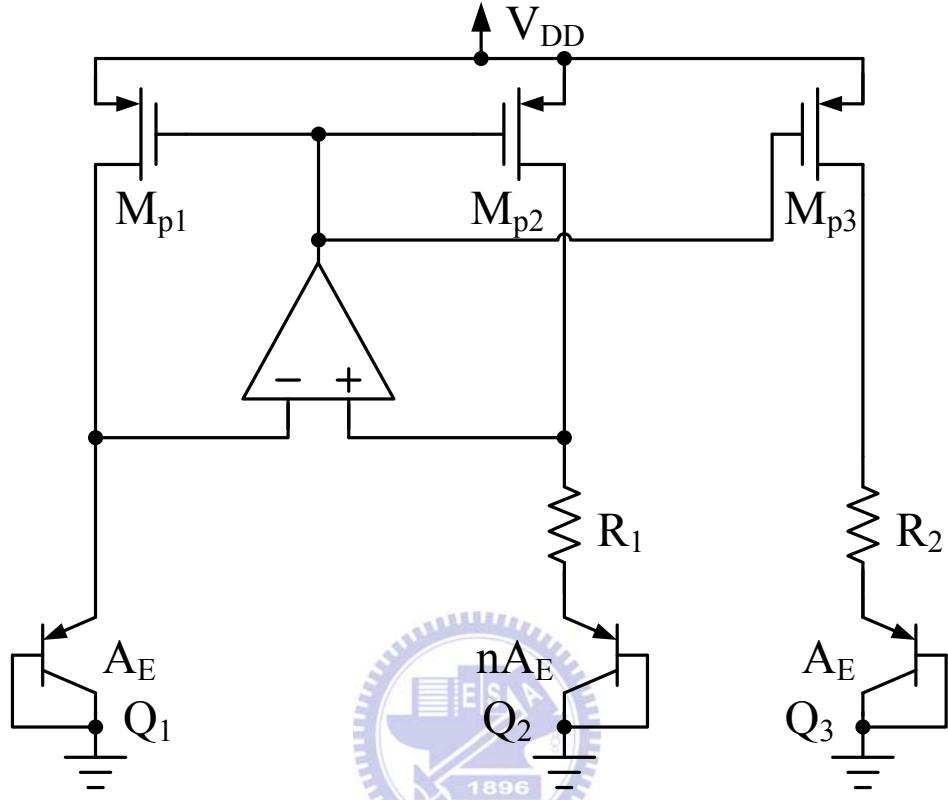

一般的能帶隙參考電壓電路如圖 3-7 所示，利用 pnp 雙載子電晶體取代 npn 雙載子電晶體達成能帶隙參考電壓是為了符合 CMOS 製程的相容性，且採用 PMOS 電流源取代電阻提供偏壓電流給雙載子電晶體，以確保兩個雙載子電晶體具有相同的溫度特性，運算放大器 (Operational Amplifier; OP) 迴授機制主要是為了流經  $M_{p1}$  及  $M_{p2}$  有相同之電流值。圖 3-7 中的能帶隙參考電壓  $V_{REF} = V_{BE3} + V_{R2}$ ， $Q_1$ 、 $Q_2$  及  $R_1$  可以提供一 PTAT 電流  $I_{R1}$  式(3.22)：

$$I_{R1} = \frac{(V_{BE1} - V_{BE2})}{R_1} = \frac{\ln n}{R_1} V_T \quad (3.22)$$

將式(3.22)代入  $V_{REF}$  可得式(3.23)：

$$V_{REF} = V_{BE3} + \frac{R_2}{R_1} V_T \ln n \quad (3.23)$$

適當選擇  $M_{p3}$  尺寸、 $R_1$  及  $R_2$  的比率，以便 PTAT 電流轉成一個和在  $Q_3$  上相反於絕對溫度 (Complementary to Absolute Temperature Voltage; CTAT) 電壓相等之 PTAT 電壓，如此可以得到一不隨溫度改變之能帶隙參考電壓。

$V_{REF}$  之完整方程式應為式(3.24)[27]：

$$V_{REF} = V_{G0} - \frac{T}{T_0} (V_{G0} - V_{BE0}) + (m + \eta - 1) \frac{kT_0}{q} + KV_T \ln n \quad (3.24)$$

其中  $V_{G0}$  為在  $0^{\circ}\text{K}$  時矽的參考電壓， $m$  是溫度常數約為 2.3，由於擴散層電阻（diffusion resistors）與溫度有關，故  $\eta$  為校正項， $T_0$  為參考溫度， $V_{BE0}$  為在參考溫度時的基極-射極接面電壓。

圖 3-7 一般能帶隙參考電壓電路

### 3-3 基體推動 MOSFET 電路之特性

根據第二章之討論，可知基體推動技術需要獨立阱，適合用於目前CMOS製程中之PMOS，以下將討論基體推動MOSFET之頻率特性、雜訊。

#### 3-3-1 基體推動MOSFET之頻率特性

閘極推動的特徵頻率 ( $f_T$ ) 為式(3.25)：

$$f_{T, \text{gate-driven}} \approx \frac{g_m}{2\pi C_{gs}} \quad (3.25)$$

式中  $C_{gs}$  為閘極-源極間電容[28]。

基體推動的特徵頻率為式(3.26)：

$$f_{T,\text{bulk-driven}} \approx \frac{g_{mb}}{2\pi(C_{bs} + C_{bsub})} = \frac{\eta g_m}{2\pi(C_{bs} + C_{bsub})} \quad (3.26)$$

其中  $C_{bs}$  是指 n 隅-源極間電容， $C_{bsub}$  為 n 隅-基體間電容。若在  $3\mu\text{m}$  CMOS 製程，根據[29]，在 NMOS 採用指叉佈局 (Interdigitated Layout) 時， $C_{bs} \approx 0.18C_{gs}$ 。

當基體推動 MOSFET 操作在飽和區且根據[30]可得式(3.27)：

$$f_{T,\text{bulk-driven}} \approx \frac{\eta}{3.8} f_{T,\text{gate-driven}} \quad (3.27)$$

隨著 CMOS 製程的進步，如果隅和基體增加摻雜密度為  $S$  倍，則  $C_{ox}$  增加的比例因數 (scaling factor) 為  $S > 1$ ，而  $C_{bsub}$  只增加  $\sqrt{S}$  倍[31]，可將式(3.27)改為式(3.28)：

$$f_{T,\text{bulk-driven}} \approx \frac{\eta\sqrt{S}}{3.8} f_{T,\text{gate-driven}} \quad (3.28)$$

在將來標準的 CMOS 製程， $f_{T,\text{bulk-driven}}$  與  $f_{T,\text{gate-driven}}$  仍然不會相等，但是應用在基體推動技術也不會犧牲太多之頻率響應[22]。

### 3-3-2 基體推動MOSFET之雜訊 (Noise)

閘極推動與基體推動之通道雜訊電流完全相似的，然而，若汲極推動與閘極推動之增益因子 (gain factor) 不同，是因為將通道雜訊電流歸於輸入，同時，基體驅動MOSFET的基體 (或隅) 也會造成附加的熱雜訊 (Thermal Noise)，特別注意若使用非矽製程，則也會有閘極電阻。基體推動MOSFET雜訊可由均方根雜訊電壓表示如下式(3.29)[30]：

$$V_{nibulk}^{-2} = \left( \frac{8kT(1+\eta)}{3\eta^2 g_m} + \frac{KF}{2fC_{ox}WLK} \frac{1}{\eta^2} + 4kT \left( \frac{1}{N} \right)^2 \times \left( \sum_{i=1}^N R_{bi} + \frac{1}{\eta^2} \sum_{i=1}^N R_{gi} \right) \Delta f \right) \quad (3.29)$$

其中  $N$  為指叉 MOSFET 架構中交叉 CMOS 閘極的個數， $R_{bi}$  為第  $i$  個閘極通道之有效串聯基體電阻， $R_{gi}$  為第  $i$  個閘極之有效串聯閘極與金屬間電阻。在式(3.29)中，前兩項分別為基體推動所產生的白雜訊（white noise）與閃爍雜訊（flicker noise），後兩者為阱與金屬間、閘極與金屬間電阻所產生的白雜訊， $N^{-2}$  係數是由閘極電阻所產生，而後兩組由閘極電阻產生的雜訊，可以利用指叉 MOSFET（即 MOSFET 會有多個閘極）之架構降低其影響力，為了將基體推動 MOSFET 產生的雜訊降至最小，整個佈局應多利用基體接觸。

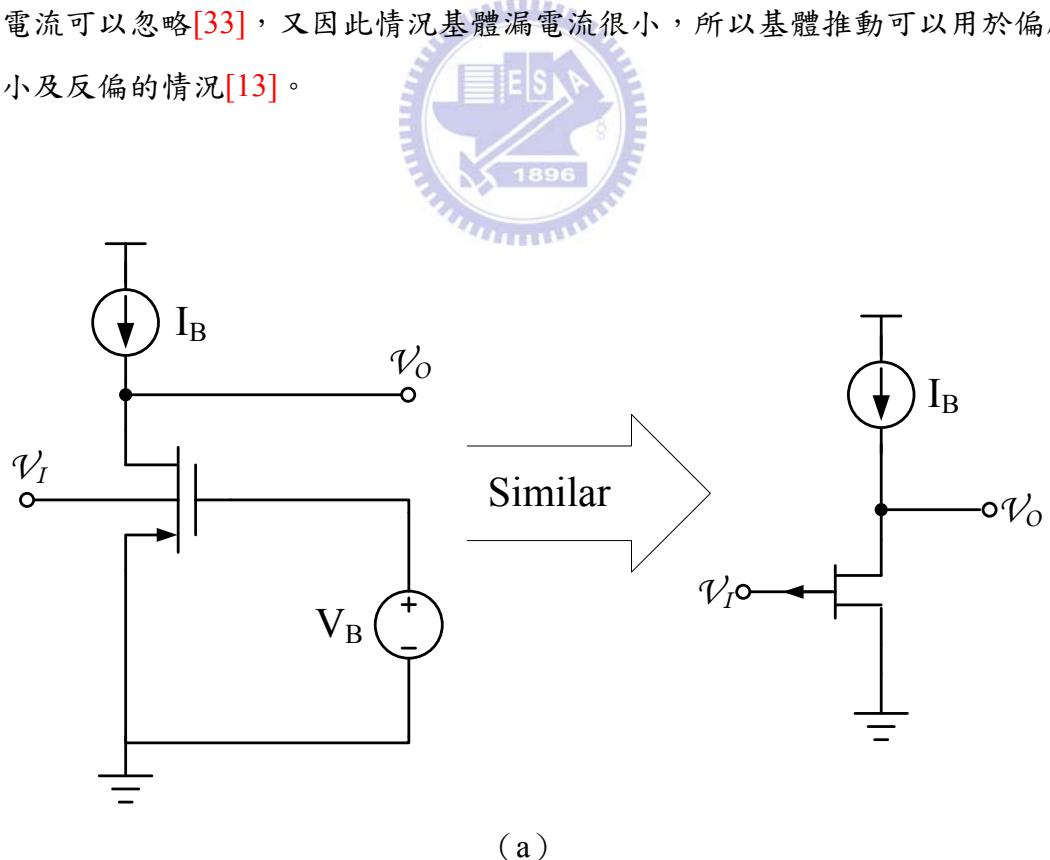

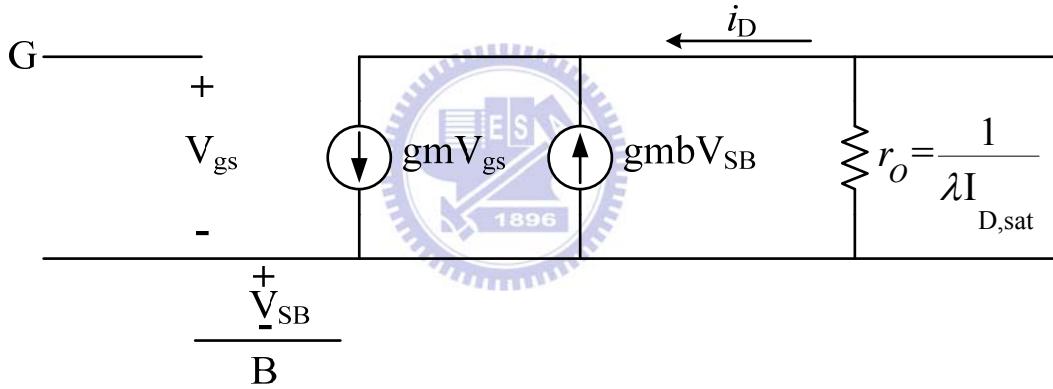

基體推動的操作需有通道形成，即在閘極之間加入一偏壓，使汲極與源極間產生通道，汲極依一般之方式連接，在基體端與源極間輸入電壓，若電壓發生變化時，空乏區厚度也將變化，進而改變汲極與源極間所產生的通道，如此，基體端與源極間輸入電壓可以控制源極流向汲極的電流，所以基體推動其動作原理類似JFET電晶體[32]如圖3-8 (a)，圖3-8 (b) 為基體推動由基體端輸入之等效JFET截面圖。因為基體-源極接面間電壓很小，流經寄生雙載子電晶體（即QP及QV）之電流可以忽略[33]，又因此情況基體漏電流很小，所以基體推動可以用於偏壓很小及反偏的情況[13]。

圖 3-8 (a) 基體推動相似於一 JFET ;(b) 基體推動之等效 JFET 截面圖與符號

根據[34]可得汲極電流方程式  $i_D$  為式(3.30)與式(3.31)：

$$i_D = \frac{k' W}{L} \left( V_{GS} - V_T - \frac{n}{2} V_{DS} \right) V_{DS} \quad , \quad V_{DS} \leq V_{DS}(\text{sat}) \quad (3.30)$$

$$i_D = \frac{k' W}{2n L} (V_{GS} - V_T)^2 (1 + \lambda V_{DS}) \quad , \quad V_{DS} \geq V_{DS}(\text{sat}) \quad (3.31)$$

其中  $n = 1 + C_{BC}/C_{OX} + qNFS/C_{OX} = 1 + \gamma/2\sqrt{\phi_F - V_{BS}}$  ，  $V_{DS}(\text{sat}) = (V_{GS} - V_T)/n$  ，

$\gamma$  為基底效應 (body-effect) 係數。在基體推動時由閘極到源極的電壓 ( $V_{GS}$ ) 變成一個常數，可將式(3.30)、(3.31)汲極電流方程式表示成式(3.32)、(3.33)[35]：

$$i_D = \frac{k' W}{L} \left( V_{GS} - V_{T0} - \gamma \sqrt{2\phi_F - V_{BS}} + \gamma \sqrt{2\phi_F} - \frac{n}{2} V_{DS} \right) \times V_{DS} \quad , \quad V_{DS} \leq V_{DS}(\text{sat}) \quad (3.32)$$

$$i_D = \frac{k' W}{2nL} \left( V_{GS} - V_{T0} - \gamma \sqrt{2\phi_F - V_{BS}} + \gamma \sqrt{2\phi_F} \right)^2 \times (1 + \lambda V_{DS}) \quad , \quad V_{DS} \geq V_{DS}(\text{sat}) \quad (3.33)$$

因此  $V_{GS}$  為常數時，飽和汲極電流 ( $i_D$ ) 將受控於基體-源極電壓 ( $V_{BS}$ ) 及得到

低的臨界電壓。飽和時的小訊號轉導為式(3.34)：

$$g_{mbs} = \frac{di_D}{dV_{BS}} \Big|_{V_{BSQ}} = \left( \frac{di_D}{dV_{TH}} \right) \left( \frac{dV_{TH}}{dV_{BS}} \right) = \frac{\gamma g_m}{2\sqrt{2\phi_F - V_{BS}}} = \eta g_m \quad (3.34)$$

其中  $g_m$  為閘極對通道的小訊號轉導值， $\eta = g_{mbs}/g_m$  約  $0.2 \sim 0.4$ ， $\phi_F$  為強反轉時的表面電位。當操作在基體-源極接面順偏  $V_{BS} \geq 2\phi_F - 0.25\gamma^2 \approx 0.5V$  [22] 時，基體推動轉導將大於或等於正常閘極之轉導值 ( $g_m$ )。圖 3-9 為基體驅動 MOSFET 小訊號模型。

由於基體推動MOSFET可以不受臨界電壓的限制，且在基體-源極輸入微小電壓即可調整汲極電流，所以能適用於低壓應用。

圖 3-9 基體驅動 MOSFET 小訊號模型

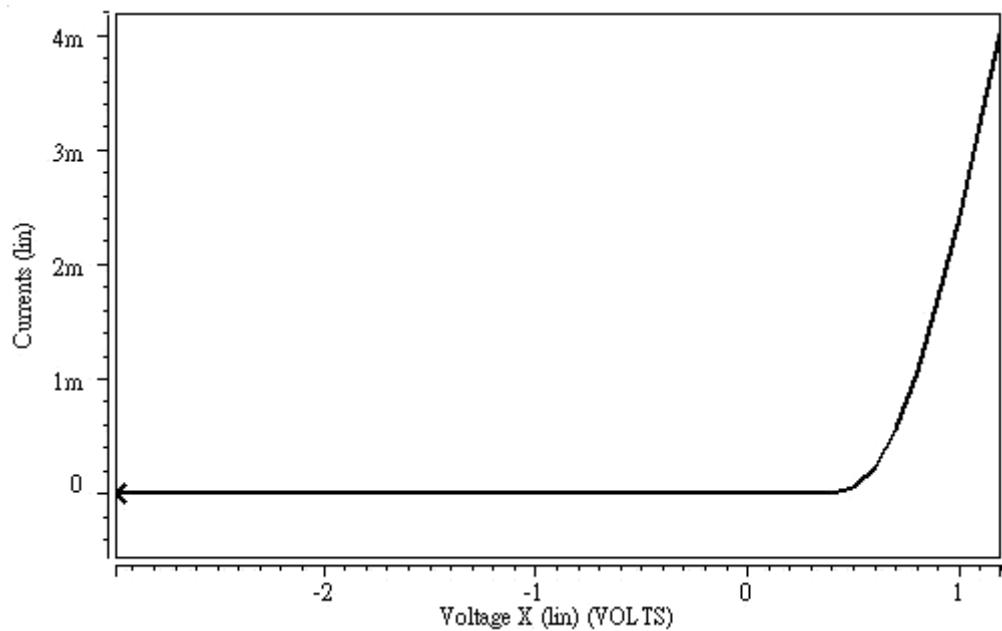

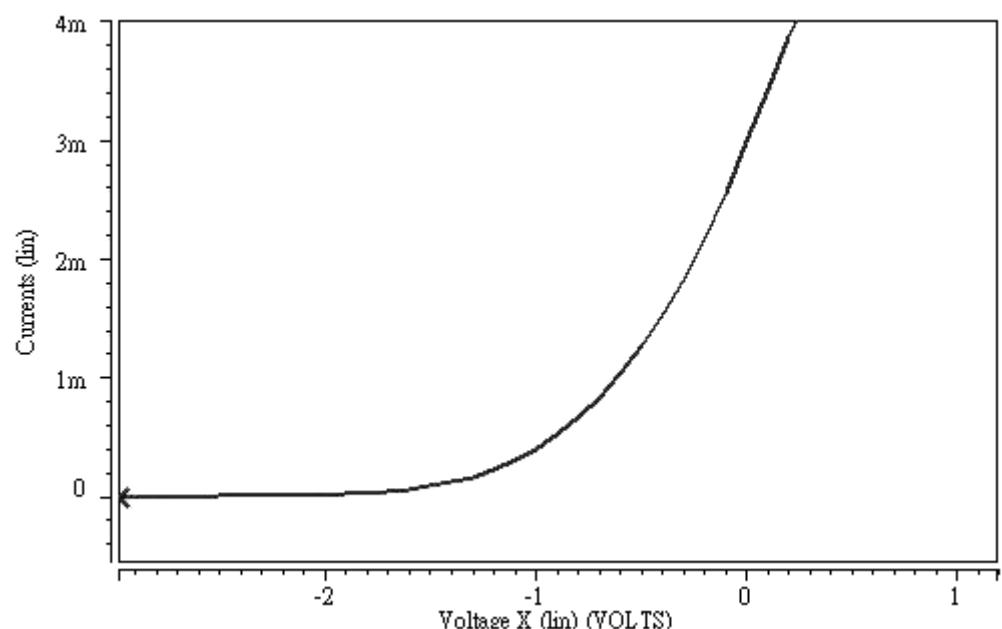

圖 3-10 分別為(a)NMOSFET 的汲極電流對閘-源極( $V_{GS}$ )電壓，(b)NMOSFET 的汲極電流對基-源極電壓( $V_{BS}$ )曲線圖：

由圖 3-10 結果可以觀察出閘極輸入電晶體動作需要  $V_{GS}$  大於臨界電壓，而基體推動電晶體，當輸入負電壓時也可以產生汲極電流。

( a )

( b )

圖 3-10 NMOSFET 之 I-V 特性曲線 (a) 為閘極輸入 (b) 基體推動

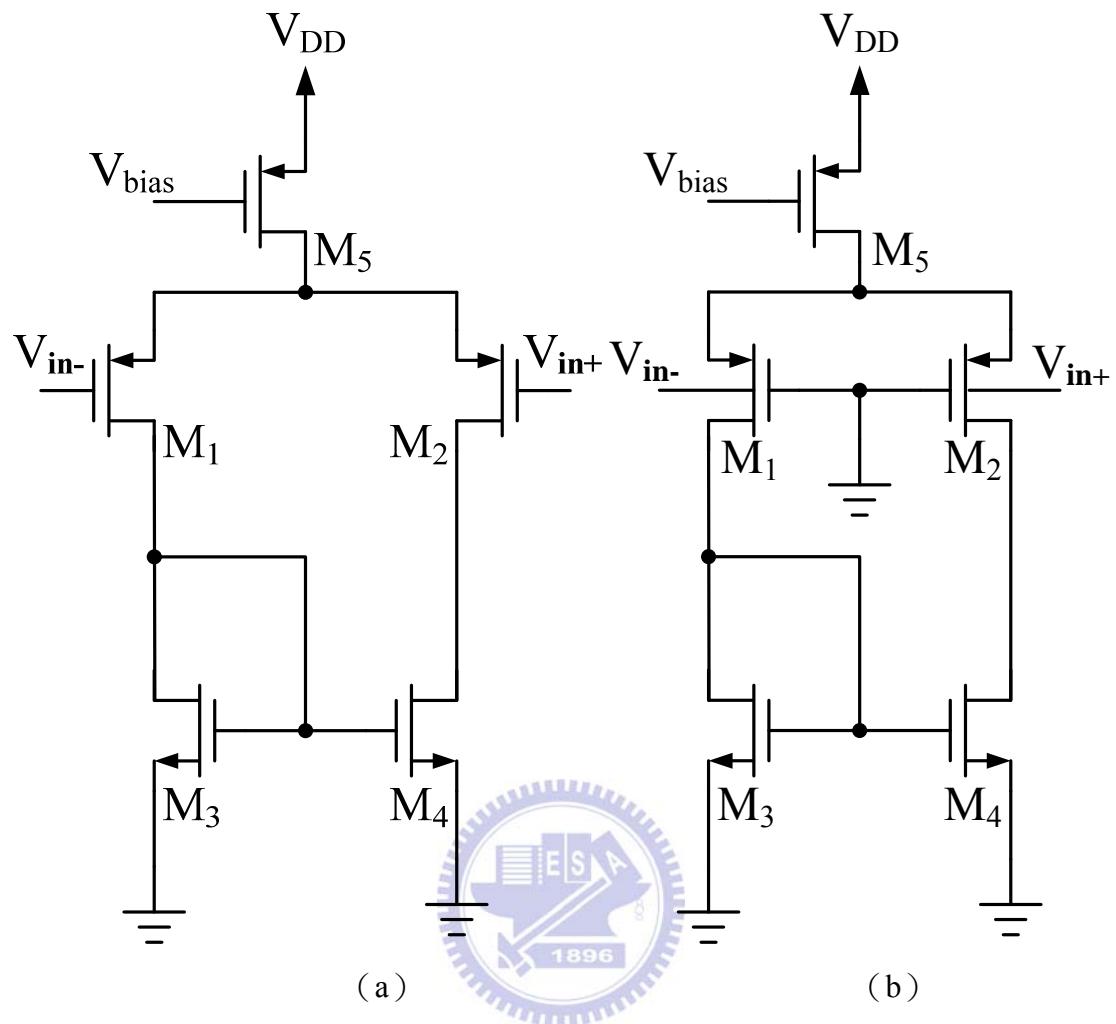

### 3-3-3 基體推動MOSFET差動對

圖 3-11 (a) 為一般閘極推動之差動輸入對 (differential input pair)，其輸入共模範圍 (Input Common Mode Range ; ICMR) 最低為 ( $V_{DS3,sat} - |V_{Tp}|$ ) 至最高為 ( $V_{DD} - |V_{DS5,sat}| - |V_{GS1}|$ )，若在  $V_{DD} = 0.9V$ ,  $V_{DS,sat} = 0.1V$ ,  $V_{Tp} = 0.7V$  的情況，閘極推動之 ICMR 為 -0.6V 至 0V，此範圍無法操作在低壓情況。若改成基體推動方式，如圖 3-11 (b)，此電路的 ICMR 只受限於汲極與基體、源極與基體間二極體的漏電流 (leakage current)，所以 ICMR 為 0.3V 至 0.9V，最小輸入級電源為  $V_{DS5,sat} + V_{GS1}$ ，如此可以操作在 0.9V 的電源[36]。針對基體推動之共模互斥比 (Common-Mode Rejection Ratio, CMRR)，則考慮由一差動輸入訊號且單端輸出的情況，由圖 3-11 (b) 可得電壓增益為式(3.35)：

$$A_{Vd} = \frac{g_{mb}}{2(g_{ds1} + g_{ds3} + g_L)} \quad (3.35)$$

式中  $g_L$  為輸出負載電導。若為共模輸入訊號，對應單端電壓增益為式(3.36)：

$$A_{Vc} = \frac{g_{mb} \cdot \frac{g_{ds5}}{2}}{g_m(g_L + g_{ds1})} \quad (3.36)$$

由式(3.35)、(3.36)可整理出基體推動 MOSFET 差動對之 CMRR 式(3.37)：

$$\text{CMRR} = \frac{A_{Vd}}{A_{Vc}} = \frac{g_m(g_L + g_{ds1})}{2(g_{ds3} + g_{ds1} + g_L) \left( \frac{g_{ds5}}{2} \right)} \quad (3.37)$$

依式(3.37)可以觀察到基體推動比一般閘極輸入差動對有較高的 CMRR 值。

由以上結論可知道基體推動差動對有優於閘極推動差動對之 ICMR、CMRR 及雜訊抑制的能力。

圖 3-11 不同輸入方式之差動對 (a) 閘極輸入；(b) 基體推動

## 第四章

# 電路設計及模擬結果

本章節將討論及模擬利用基體推動的技巧設計正比於絕對溫度電路、能帶隙參考電壓電路及系統所需之電壓緩衝器，最後將模擬所設計之溫度顯示與溫度開關結果。

### 4-1 模擬環境與設計流程

本晶片模擬環境使用台積電 0.18um 1P6M CMOS 的標準製程參數，利用 HSpice 模擬-10~80°C 溫度範圍內，所設計的電路正比於溫度變化的電壓值，電壓隨溫度變化率為 2.25 mV/°C，能帶隙參考電壓為 0.75V。

電路之設計流程為：

- (1) 首先了解目前正比於絕對溫度及能隙參考電壓電路的基本電路架構。

- (2) 訂出所需的SPEC。

- (3) 設計正比於絕對溫度及能隙參考電壓電路；以HSpice做Pre-sim模擬來驗證是否達到SPEC。

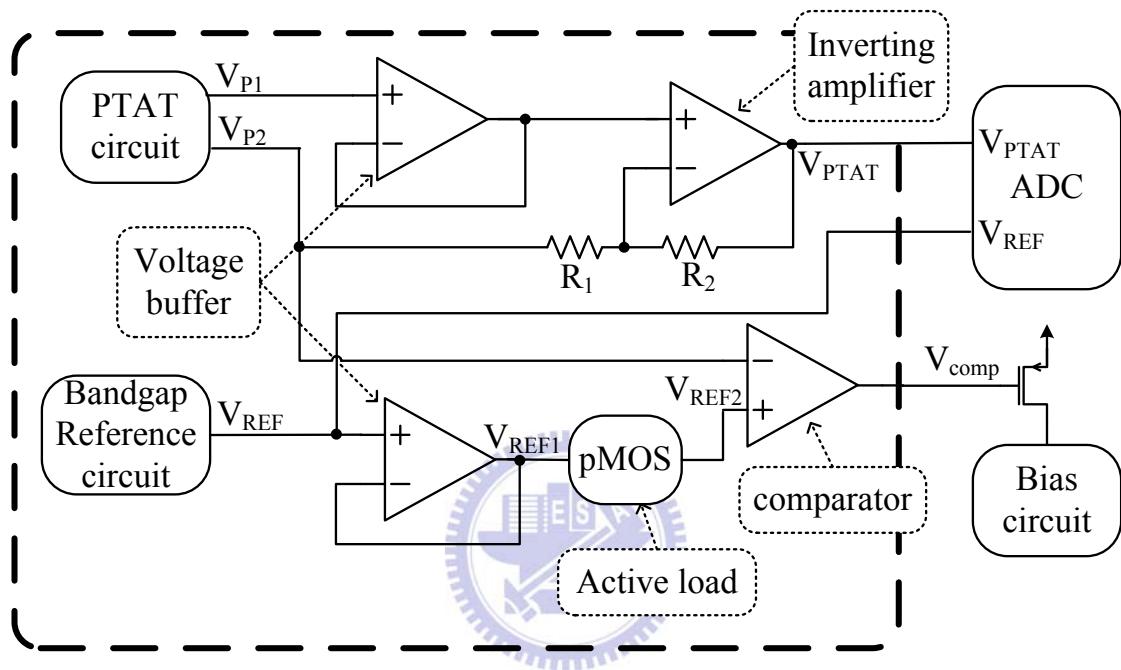

### 4-2 溫度開關及感測之整體電路架構

本電路所設計之溫度開關及感測，主要由正比於絕對溫度（Proportional to

absolute temperature, PTAT) 電路、能階隙參考電壓產生電路 (Bandgap Reference Voltage Generator)、運算放大器 (Operational Amplifier, OP) 接成電壓緩衝器使用 (voltage buffer) 及比較器 (Comparator) 等元件所組成，整體架構如圖4-1所示，虛線為本晶片所設計部分：

圖 4-1 溫度開關及感測之整體架構圖

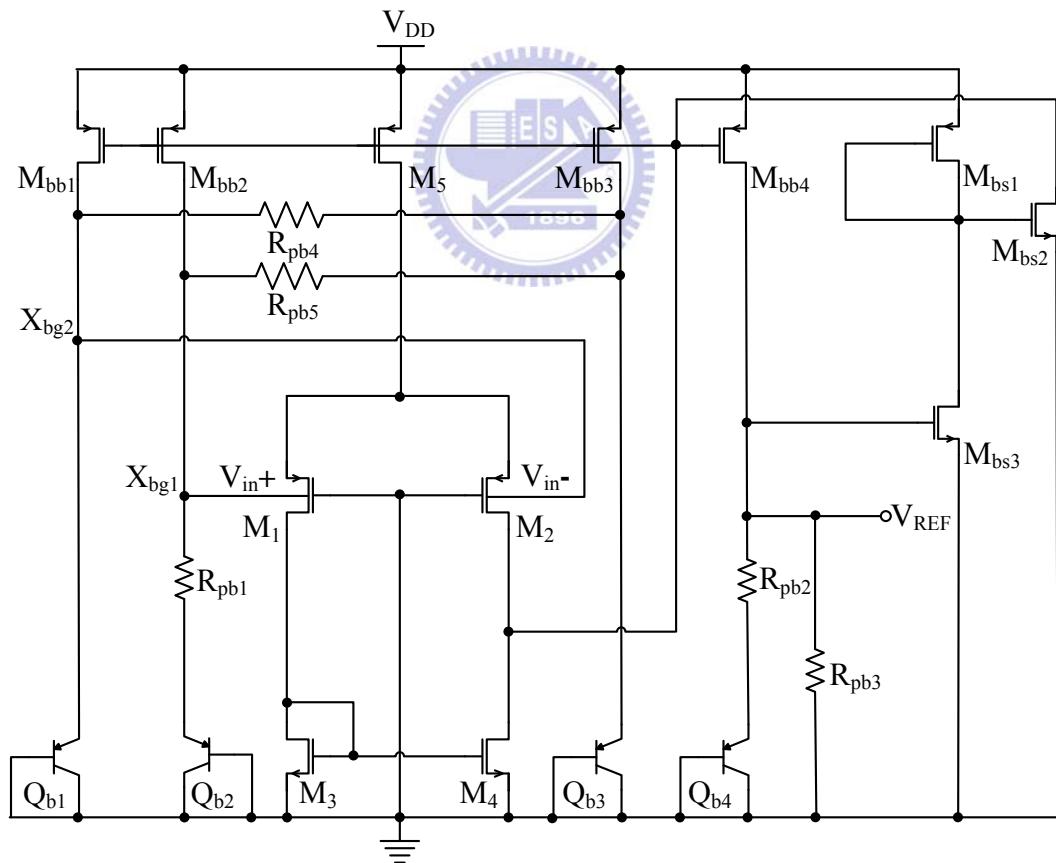

圖 4-1 中的正比於絕對溫度 (Proportional to absolute temperature, PTAT) 電路及能階隙參考電壓產生 (Bandgap Reference Voltage Generator) 電路是採用同一個電路。因為本電路所用電壓為 1.5V，此低電壓將可能導致溫度感測電路無法動作，所以正比於絕對溫度電路架構及基體推動之能帶隙參考電壓電路架構將採用基體推動方式實現。因為不需用在高頻，速度也不用太快，所以運算放大器電路是採用雙級 (two-stage) 架構，以下將對電路詳細討論之。

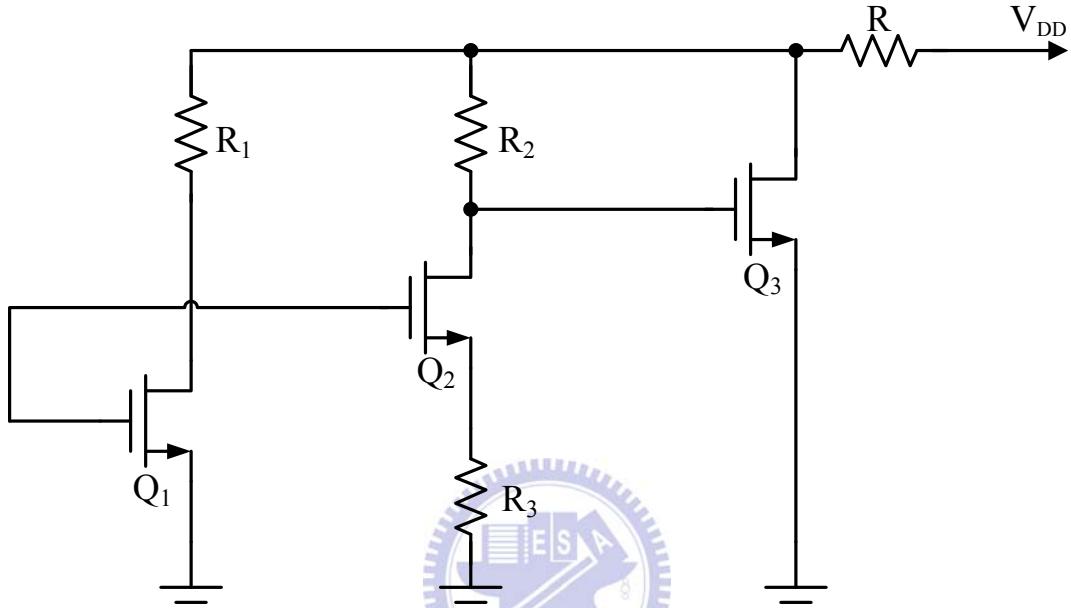

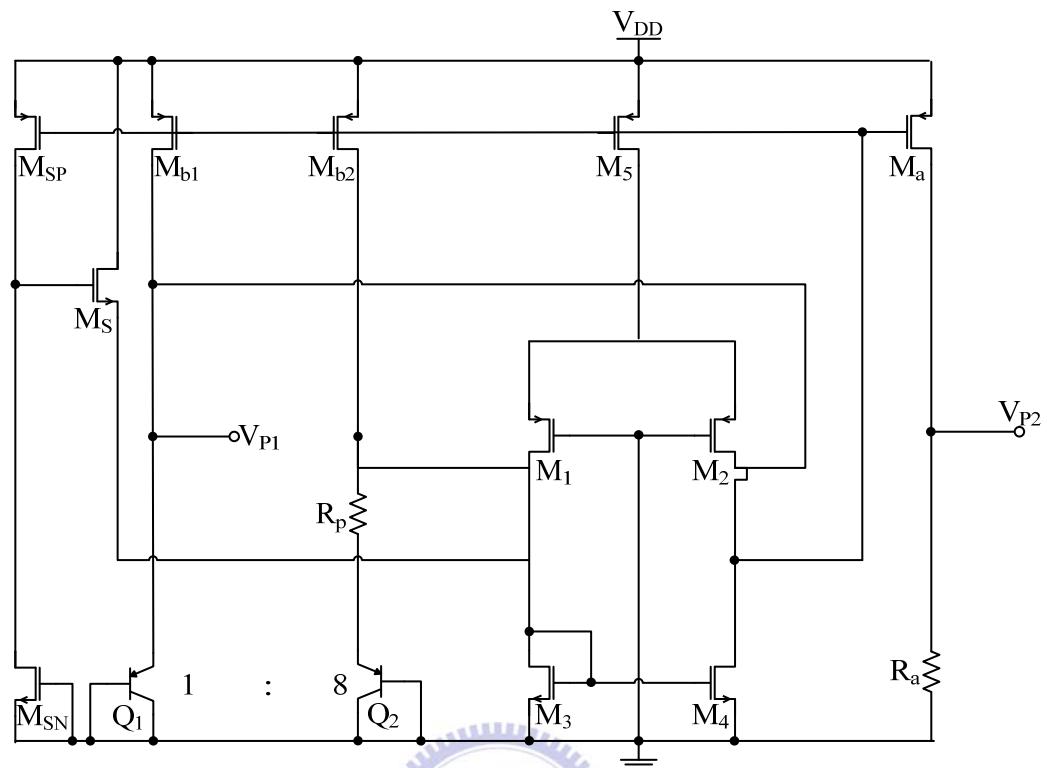

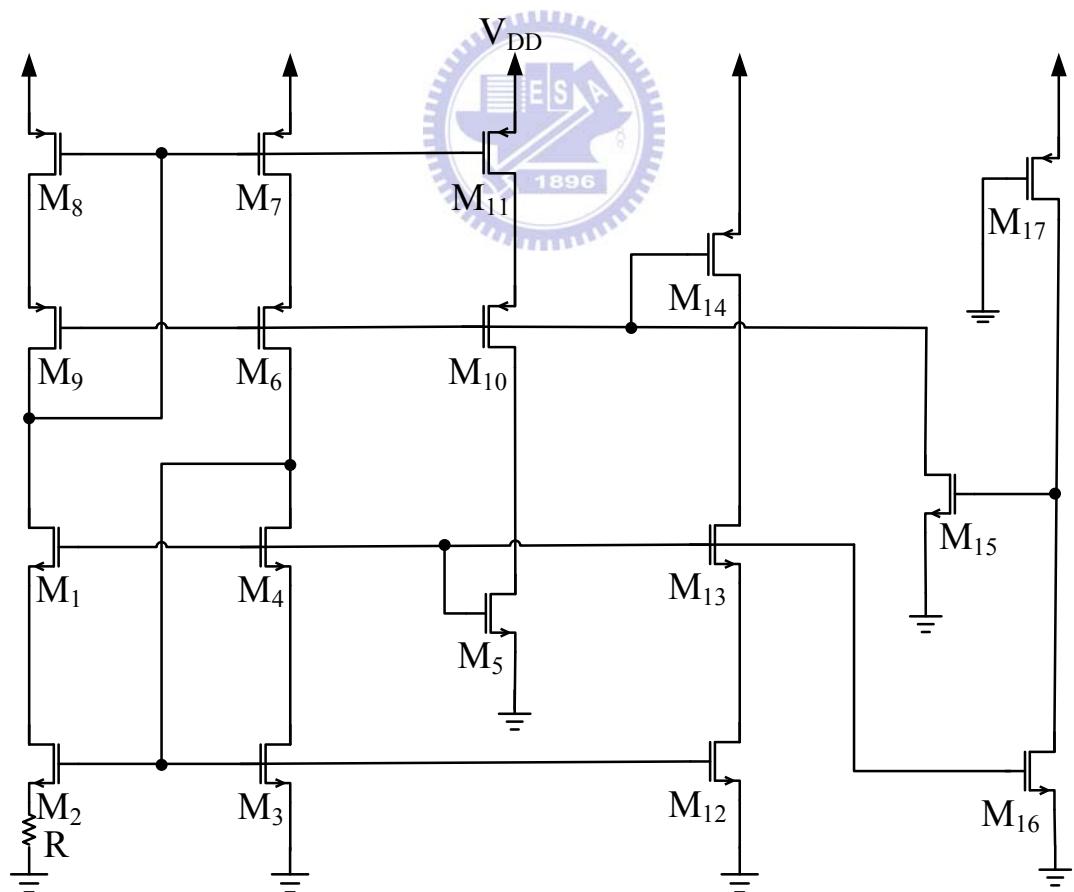

### 4-3 基體推動之正比於絕對溫度電路架構

隨著 CMOS 製程的進步，電源也隨著變小，此造成如運算放大器 (operational amplifier；OP) 之類比電路設計上的難度，其中包含了差動放大器 (differential amplifier)，為了符合低電壓、高輸入共模範圍 (ICMR) 及高共模互斥比 (CMRR)，根據第二、三章所討論的結果，將採用具有基體推動 PMOSFET 架構及電流迴授方式的正比於絕對溫度 (PTAT) 電路[37]，如圖 4-2 所示，該圖中誤差放大器 (error amplifier) (圖 3-5 中的 OP 部份) 利用由 M1~M5 構成的基體推動 PMOSFET 架構，使  $X_1$  與  $X_2$  具有產生及固定電位，讓  $X_1=X_2$ ， $Q_1$ 、 $Q_2$  與  $R_p$  形成 PTAT 電流  $I$  為式(4.1)：

$$I = I_1 = I_2 = \frac{V_T \ln(n)}{R_p} \quad (4.1)$$

其中  $n$  為  $Q_1$  與  $Q_2$  之間射極面積 ( $A_E$ ) 之比， $V_T$  為臨界電壓。若  $(W/L)_{Ma} = 2(W/L)_{Mb1}$ ，則 PTAT 電流  $I_3$  為式(4.2)：

$$I_3 = 2I_1 = 2I_2 = 2 \frac{V_T \ln(n)}{R_p} \quad (4.2)$$

所以輸出 PTAT 輸出電壓  $V_{P2}$  為式(4.3)：

$$V_{P2} = I_3 R_a = \frac{2R_a V_T \ln(I_{S1}/I_{S2})}{R_p} \quad (4.3)$$

正比於絕對溫度電路模擬：圖 4-2 之  $X_1$  及  $X_2$  的 PTAT 電壓變化為圖 4-3，圖 4-4 為 PTAT 電流  $I_3$  之結果， $V_{P2}$  之結果為圖 4-5。

圖 4-2 PTAT 電壓參考電路圖

圖 4-3 雙載子電晶體之  $V_{BE}$  對溫度之變化

圖 4-4 PTAT 電流  $I_3$  之結果

圖 4-5  $\Delta V_{BE}$  之 PTAT 電壓

#### 4-4 基體推動之能帶隙參考電壓電路架構

能帶隙參考電壓電路主要是根據[38]修改，一般能帶隙參考電壓電路最小供應電壓通常為 1.8V，此也將限制能帶隙參考電壓電路所使用之運算放大器的輸入共模範圍 (ICMR)，且傳統的能帶隙參考電壓為式(3.23)，其電路操作的最小供應電壓  $V_{DD(MIN)} = V_{ref} + V_{DSAT(PMOS)}$ ，在室溫時能提供一個 1.26V 的參考電壓 ( $V_{ref}$ )， $V_{DSAT(PMOS)}$  受製程影響，電壓變化範圍為 0.1V 至 0.3V，所以至少需要一個最小 1.4V 的供應電壓[39]，而本論文所使用的供應電壓只有 1.5V，將可能會導致電路無法正常運作，所以將運算放大器部分利用之前所提的基體推動技術設計之，如圖 4-6 所示，M1~M5 為上一節所使用之基體推動架構，Mbb3、Qb3、Rpb4 及 Rpb5 為曲線補償之電路。

圖 4-6 基體推動之能帶隙參考電壓電路

圖 4-6 之 PTAT 電壓由 Qb1 及 Qb2 的射極面積比所產生其值  $\Delta V_{BE}$  為  $\Delta V_{BE} = V_{BE1} - V_{BE2} = V_T \ln(I_c/I_s) - V_T \ln(I_c/nI_s) = V_T \ln n$ ， $n$  為電流密度。若考慮經由 Rpb2 及 Qb4 輸出的參考電壓為  $V_{REF} = V_{BE4} + K \Delta V_{BE}$ ，同式(3.23)， $K$  為  $R_{pb2}$  與  $R_{pb1}$  之比值。接上  $R_{pb3}$  進而調整參考電壓值，如式(4.4)：

$$V_{REF} = K' (V_{BE4} + I_{M4} R_2) \quad (4.4)$$

其中  $K' = R_3 / (R_2 + R_3)$ 。所以  $V_{REF}$  是由電阻  $R_{pb1}$ 、 $Qb1$  及  $Qb2$  產生 PTAT 電壓，經電流鏡複製到  $Qb4$ ，形成可以由  $R_{pb2}$  及  $R_{pb3}$  調整比例之與溫度無關參考電壓。

根據物理特性， $V_{BE}$  與溫度之關係為式(4.5) [40]：

$$V_{BE}(T) = V_G - (V_G - V_{BE0}) \frac{T}{T_0} - (\eta - \alpha) V_T \ln \frac{T}{T_0} \quad (4.5)$$

其中  $V_G$  為矽的參考電壓， $\eta$  為製程參數， $\alpha$  是跟流經 BJT 的電流特性之相關值，當其電流為 RTAT 電流時， $\alpha$  為 1；若電流與溫度無關的時， $\alpha$  為 0， $T_0$  為參考溫度， $V_{BE0}$  為在參考溫度時的基極-射極接面電壓，由式(4.5)可以得知  $V_{BE}$  具有負溫度係數。此電路為了具有曲率補償 (curvature compensation) 之特性，將對式(4.5)的第三部分  $V_T$  進行補償，利用圖 4-6 中之 Mbb3、Qb3、Rbp4 及 Rbp5 達到曲率補償的效果，所以式(4.4)可以修改為式(4.6)

$$V_{REF} = K' (V_{BE4} + I_{M4} R_2) + \frac{R_1}{R_{4,5}} V_{NL} \quad (4.6)$$

式中  $V_{NL} \equiv V_{BE3}(T) - V_{BE1,2}(T) = V_T \ln(T/T_0)$

圖 4-7 為基體推動之能帶隙參考電壓電路輸出之結果， $Qb1$ 、 $Qb2$  及  $Qb3$ 、 $Qb4$  之射極面積皆為 1 : 8，曲線為已經由 HSpice 模擬曲線補償電路後之輸出。

圖 4-7 能帶隙參考電壓電路輸出曲線

#### 4-5 電壓緩衝器 (voltage buffer)

一般運算放大器各種架構及效能比較如表 4-1[41]所示。

表 4-1 各種運算放大器 (operational amplifier ; OP) 組態之效能比較

|                | Gain   | Output Swing | Speed   | Power Dissipation | Noise  |

|----------------|--------|--------------|---------|-------------------|--------|

| Telescopic     | Medium | Medium       | Highest | Low               | Low    |

| Folded-Cascode | Medium | Medium       | High    | Medium            | Medium |

| Gain-Boosted   | High   | Medium       | Medium  | High              | Medium |

| Two-Stage      | High   | Highest      | Low     | Medium            | Low    |

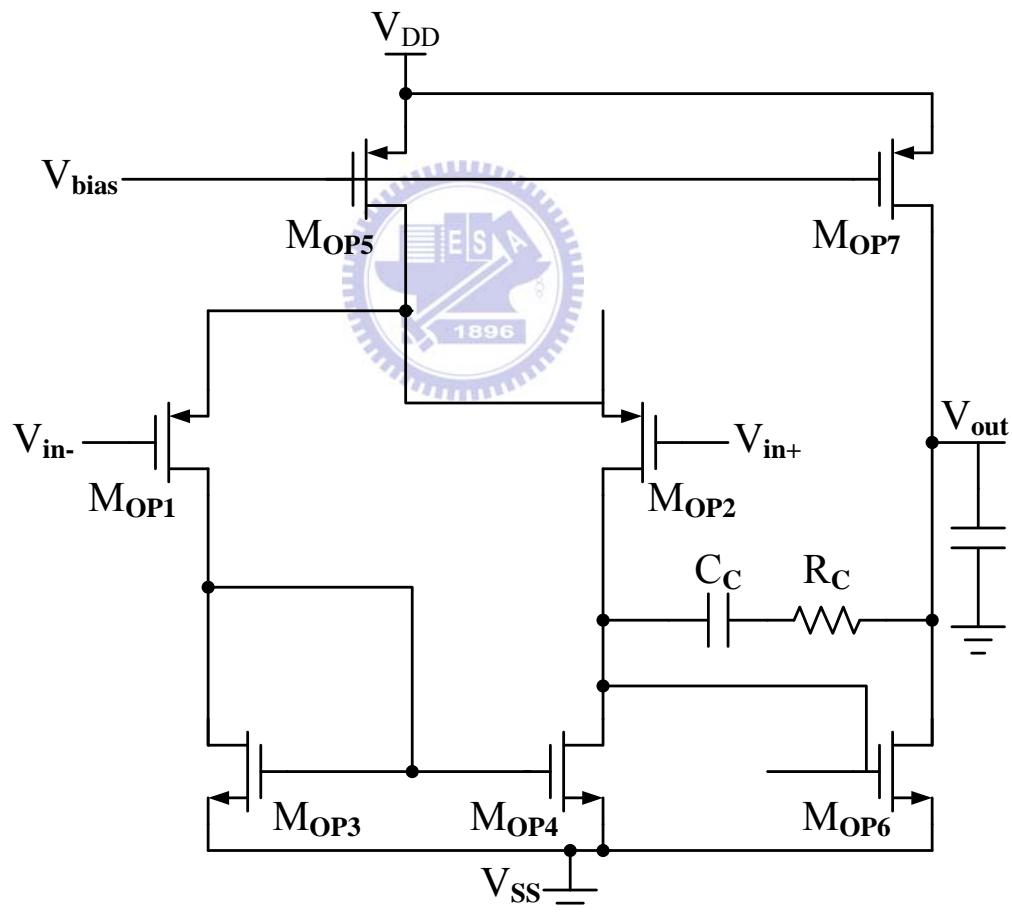

因為要當電壓緩衝器使用，所以要求有較佳的增益、較低的雜訊及高的輸出擺幅，以免失真，電路之操作非高頻，只考慮直流狀態與低頻，對速度之要求不高，所以選用雙級 (two-stage) 運算放大器，如圖 4-8。第一級由  $M_{OP1}$  到  $M_{OP5}$  所組成，主要為得到高的增益，第二級由  $M_{OP6}$  及  $M_{OP7}$  構成共源極 (common source) 組態，以達到最大輸出振幅，補償電容 ( $C_C$ ) 及補償電阻 ( $R_C$ ) 是為電路達到穩定度。

使用電壓緩衝器之原因為其具有高輸入阻抗和低輸出阻抗，由於具有高輸入阻抗，如此可以不必考慮負載效應及避免準確度不夠問題，主要讓感溫部份不受後端電路影響，產生隔離效果，也能產生足夠的電流驅動能力。

圖 4-8 雙級組態運算放大器電路圖

OP 所使用的偏壓電路為寬擺幅定轉導偏壓電路 (Wide-Swing Constant-Gm Cascod Biasing Circuit)，如圖 4-9 所示，其中可以分成三部份：第一部份為偏壓迴路，主要是由寬擺幅疊接式電流鏡(High-Swing Cascode Current Mirror)架構[42]由 M1~M4、M6~M9 及 Rb 所構成，用以提供穩定的電流源。第二部份為 M5、M10~M14 構成的疊接偏壓(Cascode Bias)，利用電流鏡架構去複製偏壓迴路的電流，加上疊接結構去偏壓；第三部份為 M15~M17 構成的啟動電路(Start-Up Circuit)，因為此架構採用寬擺幅與定轉導架構去實現，所以必須加上啟動電路去維持偏壓電路隨時都能正常操作，啟動電路的設計，主要以低功耗與不影響原先偏壓電路。當只有在偏壓電路操作不正常時，啟動電路會根據與偏壓電路的之間的回授機制，將電壓拉回修正，維持偏壓電路的正常操作狀態。

圖 4-9 寬擺幅定轉導偏壓電路

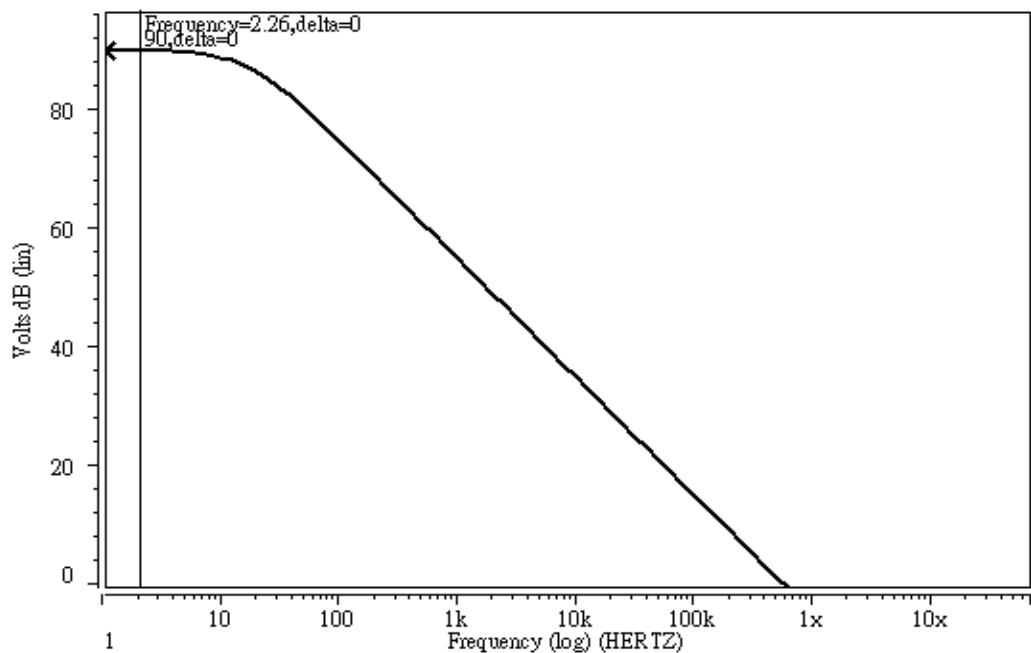

OP 經 HSpice 模擬之結果，如圖 4-10 為增益與頻率響應圖，圖 4-11 頻率響應與相位邊際值圖。

圖 4-10 增益-頻率響應圖

圖 4-11 頻率響應與相位邊際值

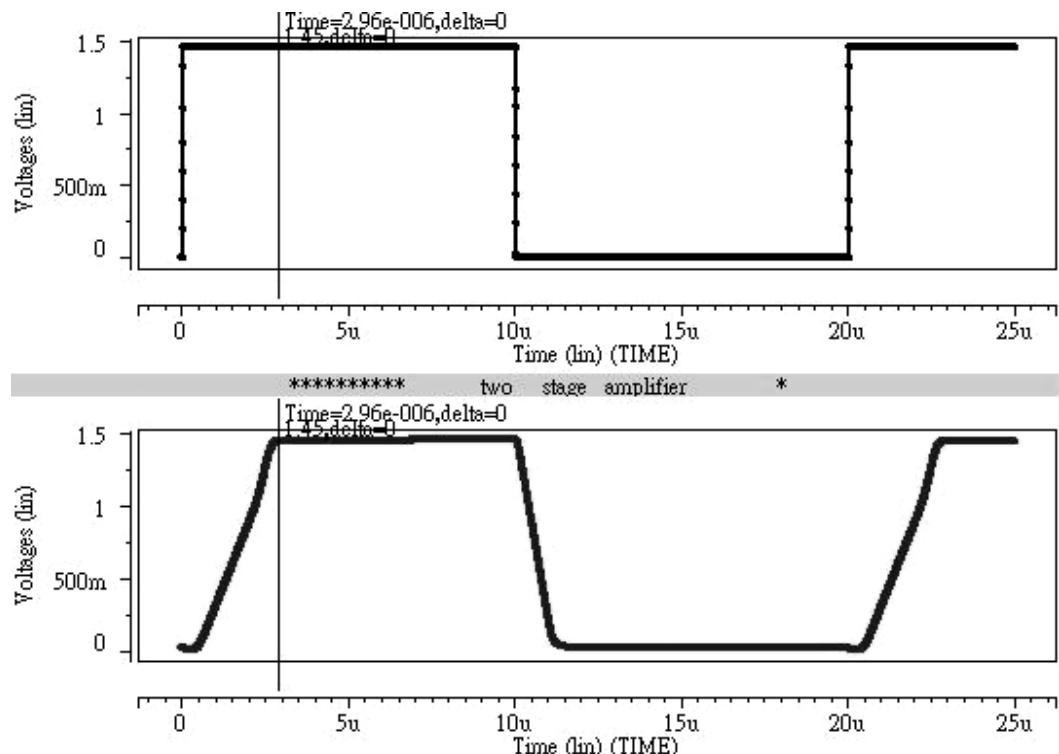

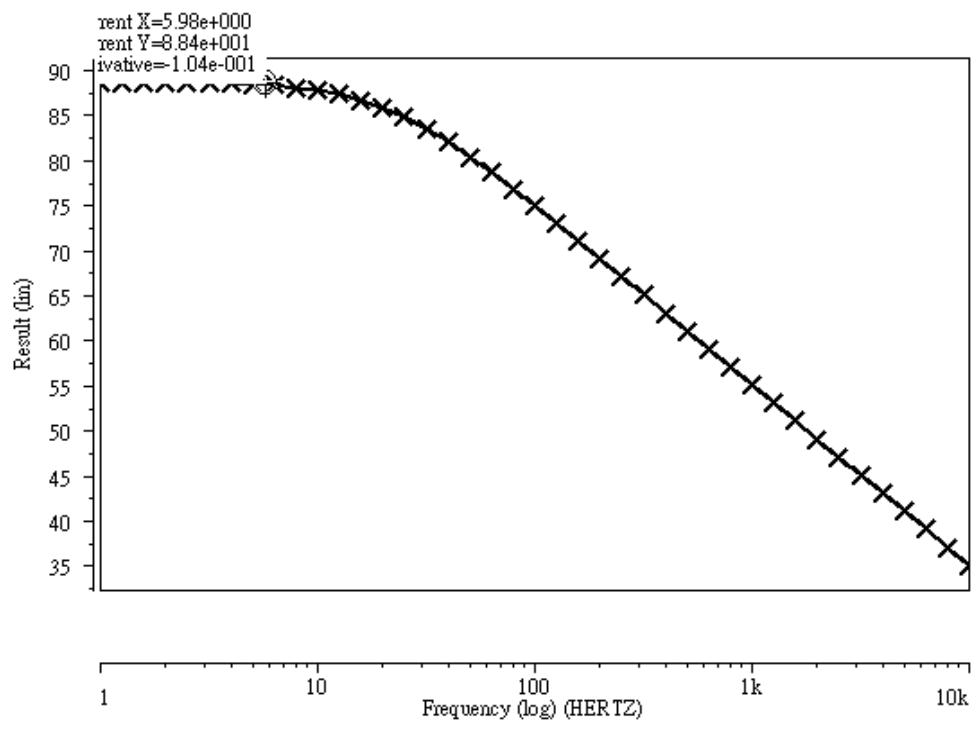

圖 4-12 為 OP 輸出（下標）的延遲率，圖 4-13 為共模互斥比（Common-Mode

Rejection Ratio , CMRR ) 約為 83.2dB@60Hz 。

圖 4-12 slew rate 之暫態分析

圖 4-13 共模拒斥比(CMRR) 頻率響應圖

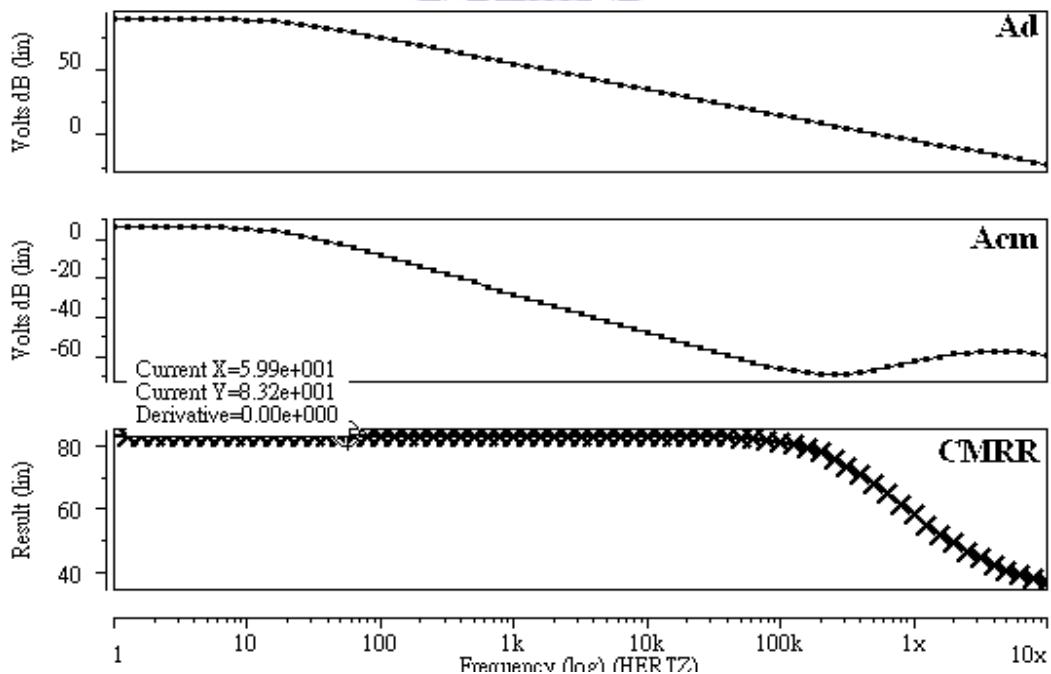

圖 4-14 為 PSRR+ 約 85.4dB@60Hz，圖 4-15 為 PSRR- 約 88.4dB@60Hz。

## 4-6 全電路模擬結果

整體電路大致上可以分成兩小部分：圖4-16為溫度感測顯示部分，圖4-18為溫度開關部分。

### 4-6-1 溫度感測顯示

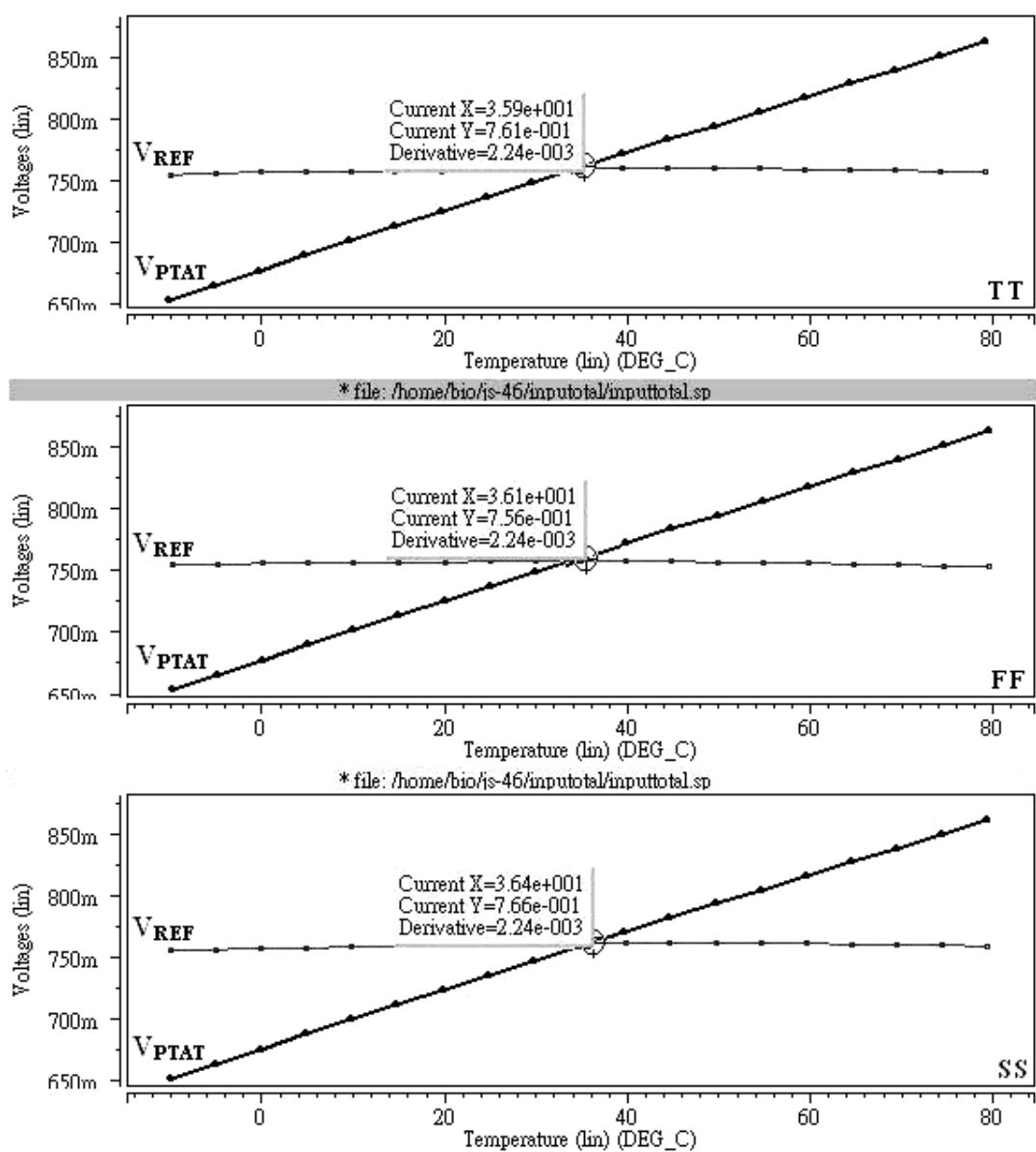

先模擬圖4-16，PTAT電路中  $V_{P1}$  經過電壓緩衝器後接在反相放大器之  $V_{in+}$  當輸入， $V_{P2}$  結果為圖4-5，經過反相放大器調整線性度及解析度，可以得圖4-17。

圖 4-16 溫度感測顯示之架構

$V_{REF}$  是為之後整合 ADC 所預留，其值為 0.75V。 $V_{PTAT}$  的溫度模擬範圍為  $-10 \sim 80^\circ\text{C}$ ，變化量約為  $2.25 \text{ mV/}^\circ\text{C}$ ，電路之供應電壓為 1.5V，假設 ADC 為  $n$  bit，則需滿足式(4.7)，才能顯示  $1^\circ\text{C}$  的變化。

$$\frac{1.5\text{V}}{2.25 \text{ mV/}^\circ\text{C}} \leq 2^n \quad (4.7)$$

根據式(4.7)可以得到  $n$  需要 10bit 才能滿足，所以 ADC 需要 10bit。

$V_{REF}$  與  $V_{PTAT}$  在  $36^\circ\text{C}$  交叉，是因為  $36^\circ\text{C}$  為人體體溫，且之後 ADC 整合時在此範圍能得到較佳的感測準確度。

圖 4-17 溫度感測電路模擬結果

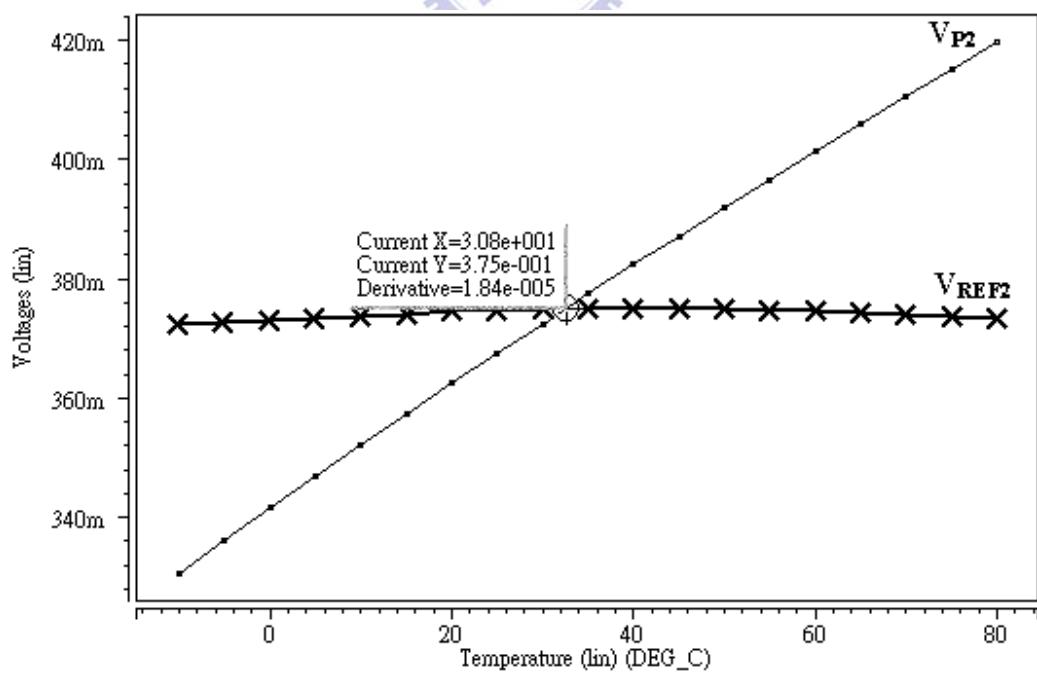

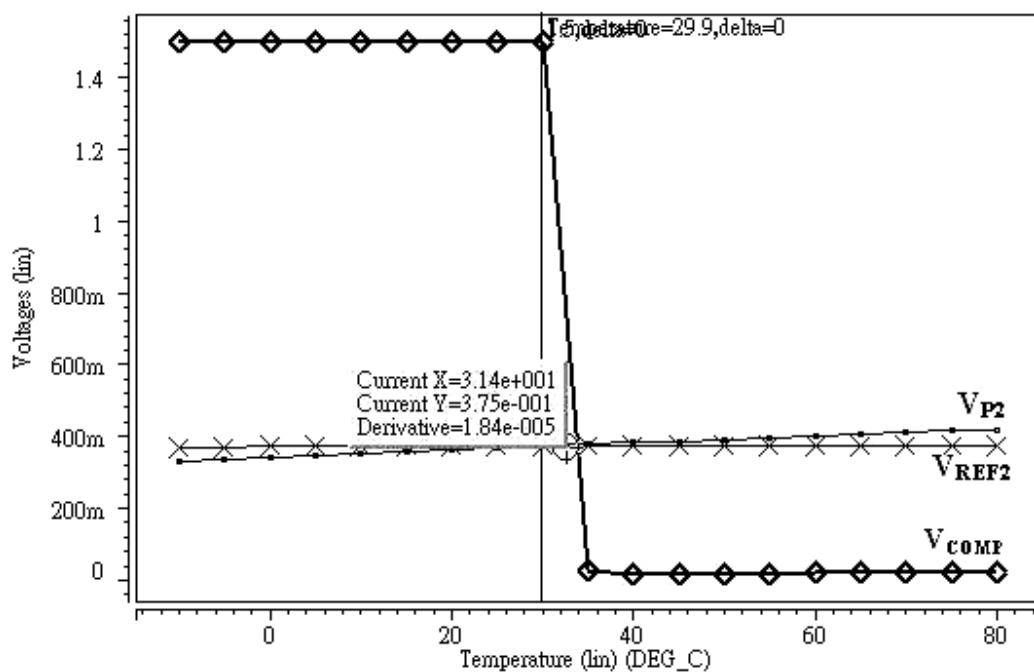

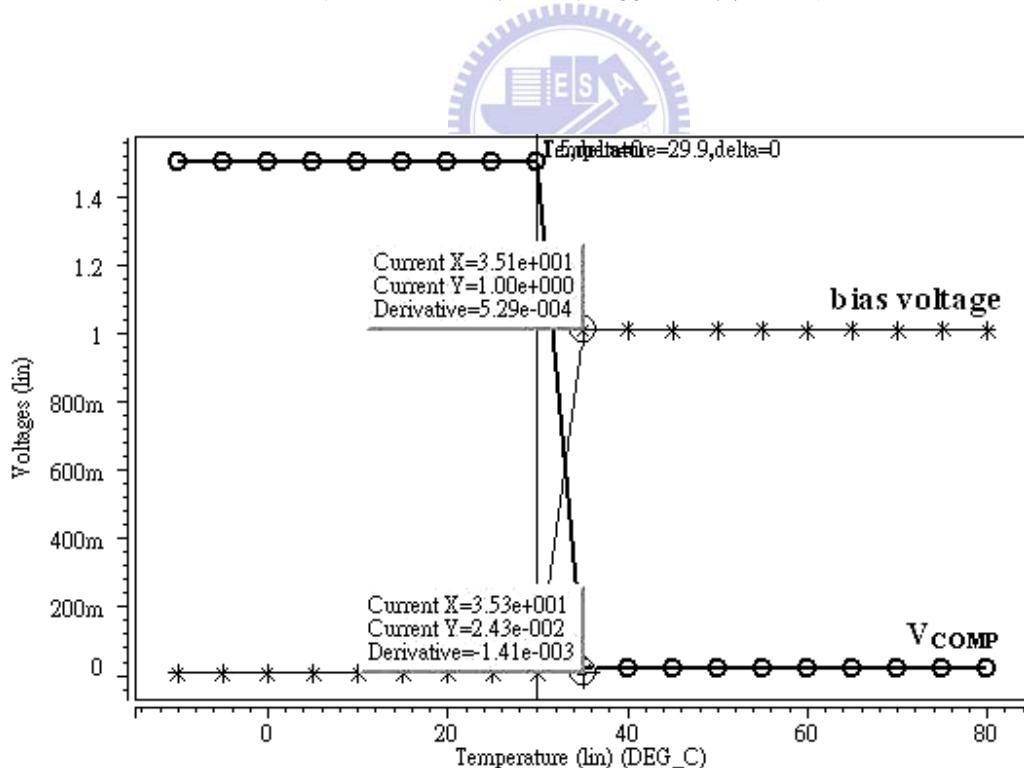

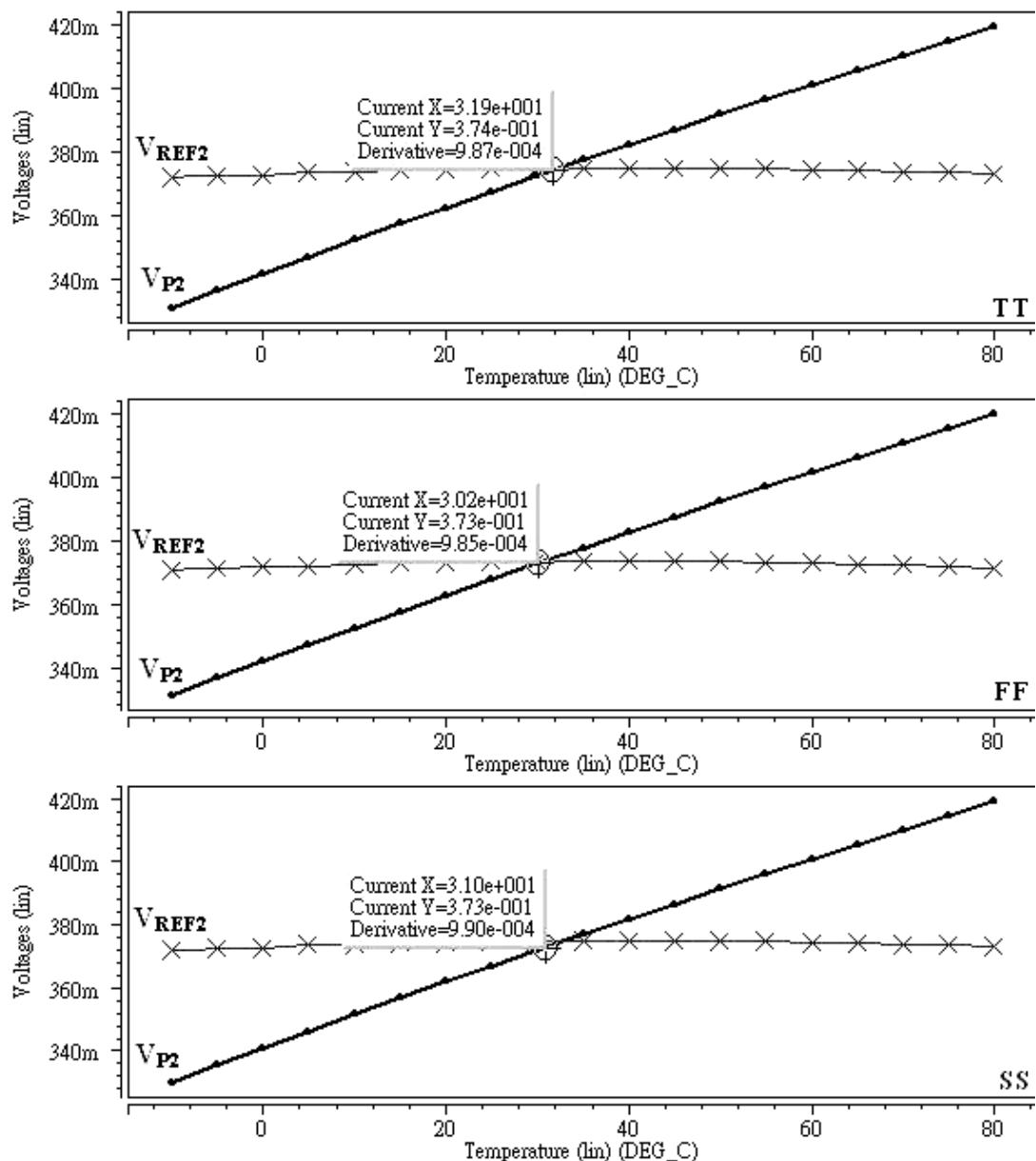

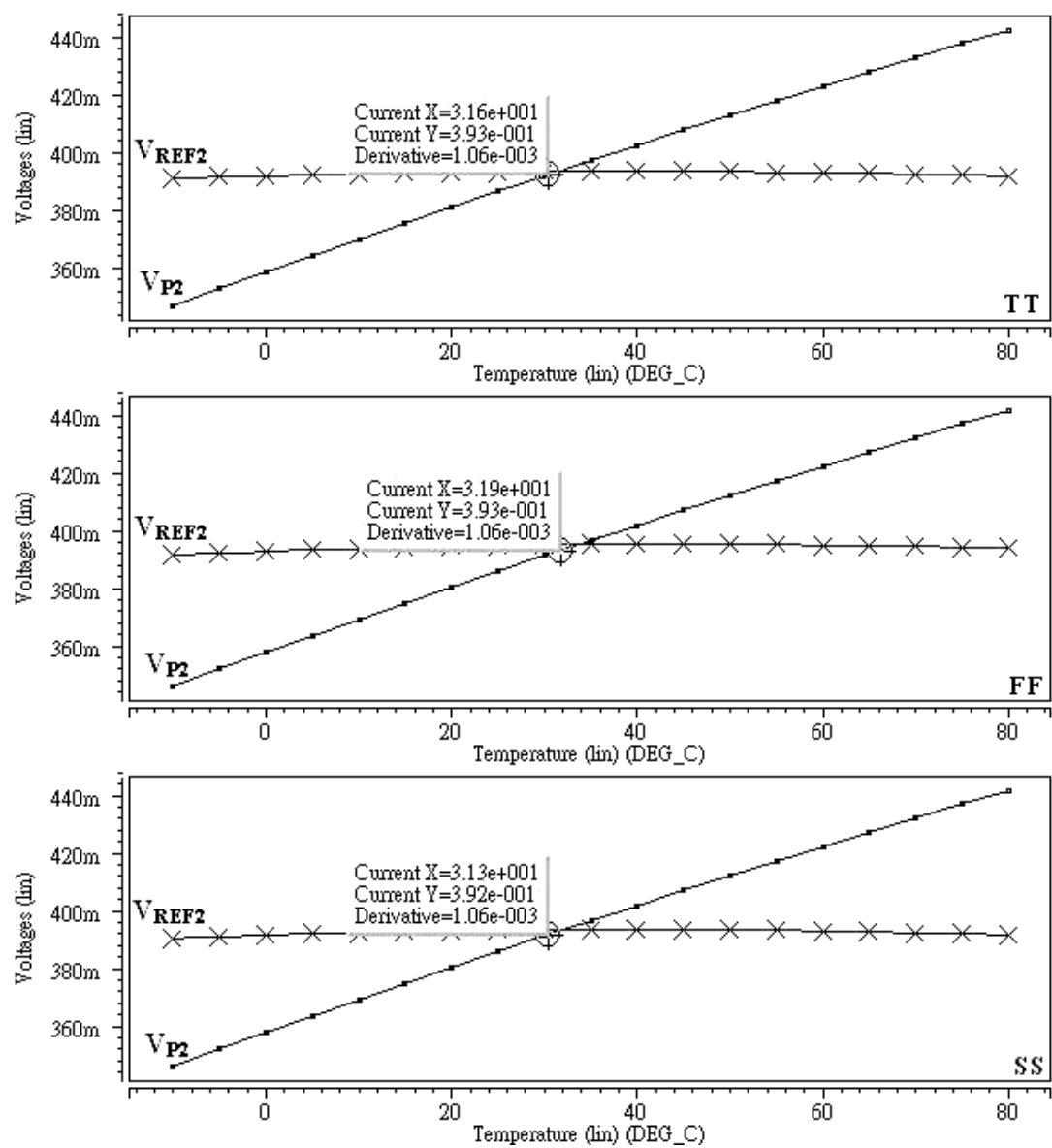

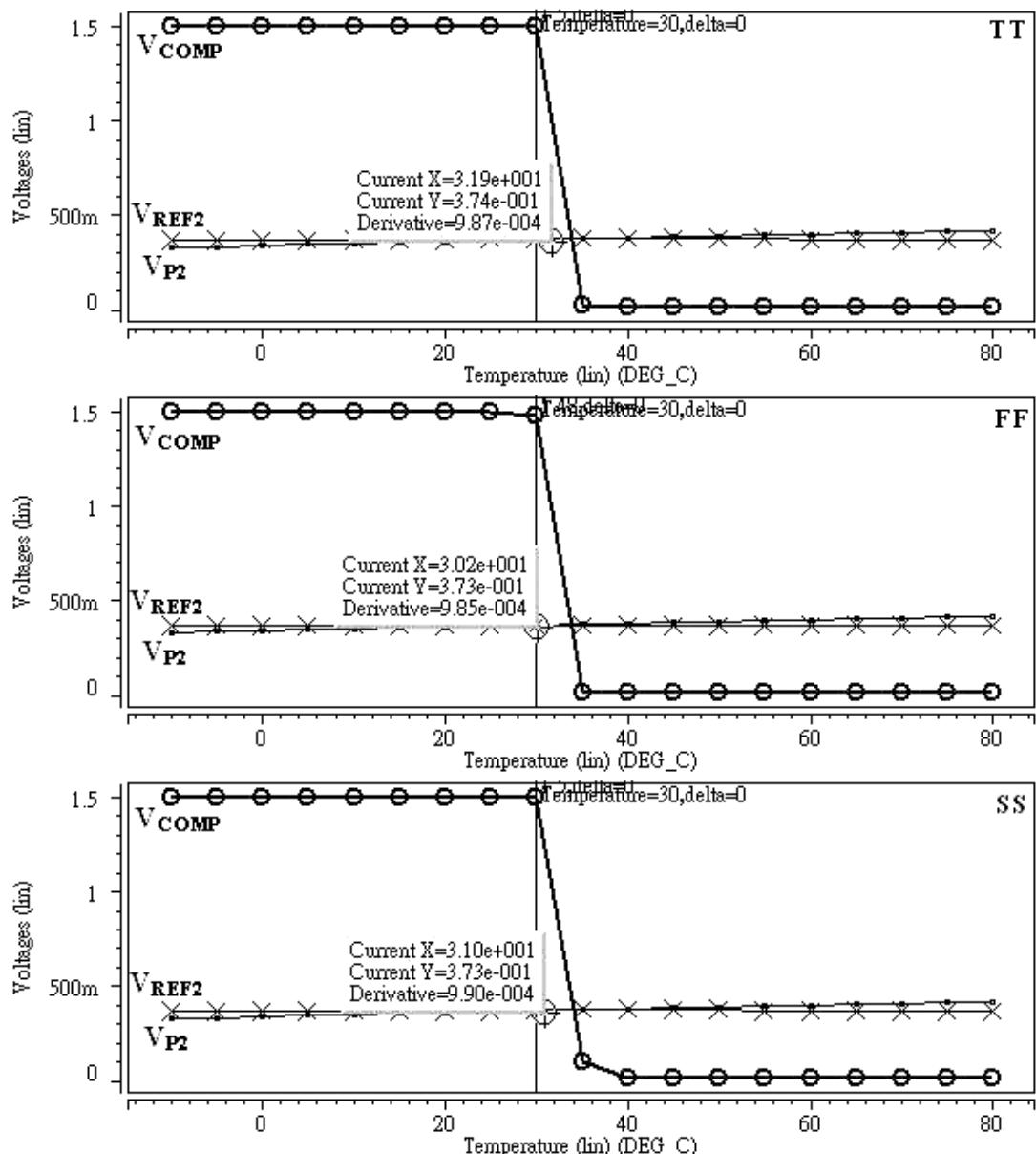

#### 4-6-2 溫度開關

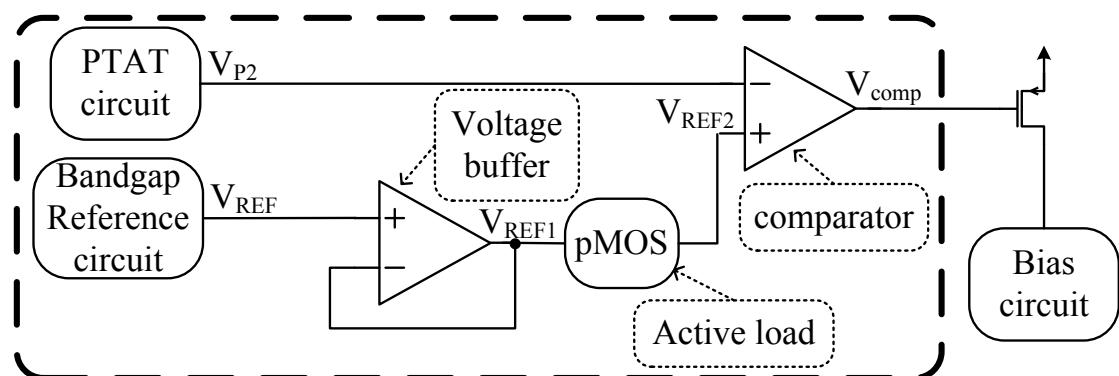

將感溫的 PTAT 電壓和經降壓後的能帶隙參考電壓透過比較器控制後端 PMOSFET，即能控制類比之偏壓電路，如圖 4-18。

圖 4-18 溫度開關架構圖

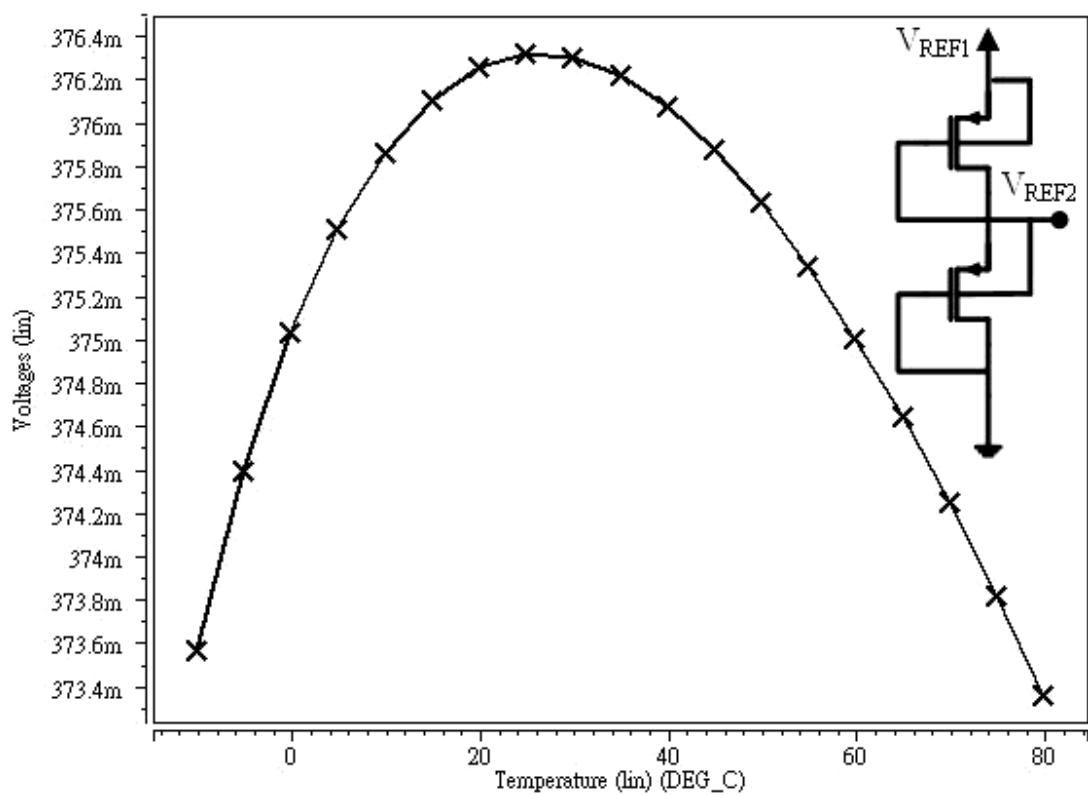

圖 4-18 中  $V_{P2}$  模擬結果為圖 4-5， $V_{REF}$  模擬為圖 4-7，圖 4-19 為  $V_{REF}$  經過電壓緩衝器後的  $V_{REF1}$ ，將此電壓經由 PMOS 組成的主動負載分壓後之模擬結果，如圖 4-20，使用 PMOS 主動負載當分壓，主要是因為主動負載在積體電路中容易製造，相對於被動負載如電阻，圖 4-21 中  $V_{P2}$  為比較器負端， $V_{REF2}$  為比較器正端之電壓準位。圖 4-22 為經比較器後之結果，因為只用 PMOS 當控制偏壓電路之開關，所以比較器輸出是在低電位的時候，才讓所控制的後端電路開始動作。圖 4-23 為假設後端類比電路動作需要 1V 之偏壓，當到達 30°C 比較器後端之 PMOS 動作後，偏壓電路輸出 1V 電壓，供應給所需之電路。

圖 4-19  $V_{REF1}$  模擬結果

圖 4-20 V<sub>REF2</sub> 模擬結果

圖 4-21 比較器輸入端之電壓模擬圖

圖 4-22 經比較器後  $V_{COMP}$  之輸出結果

圖 4-23 模擬後端電路需 1V 之輸出

## 第五章

### 晶片實現與量測

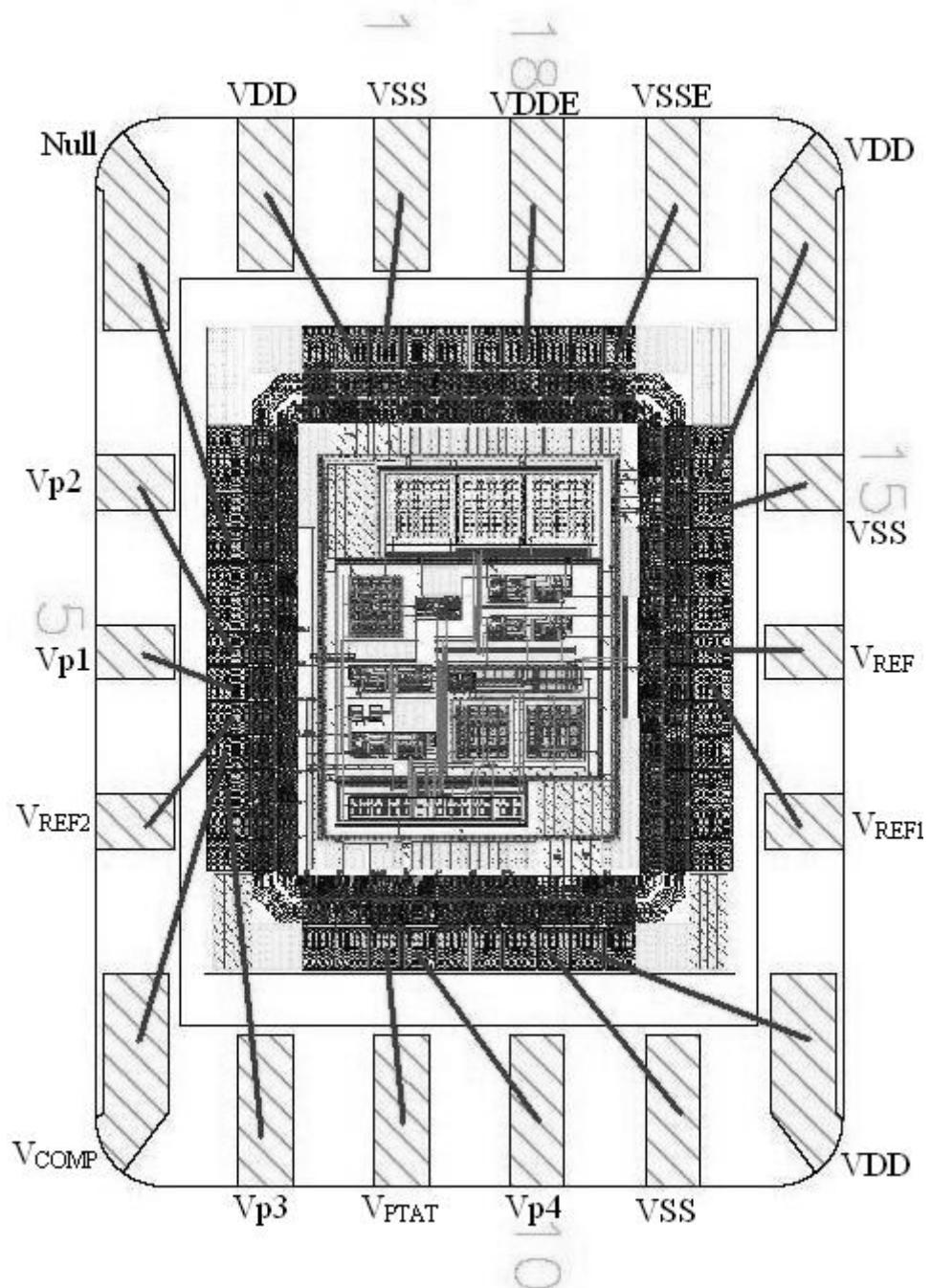

本晶片是利用Laker Tools佈局，並且測試佈局後驗證 (Calibre DRC 和 LVS) ，然後做完整佈局後驗證(Post-simulation) ，再由CIC下線製作晶片，待晶片製作完成進行量測。

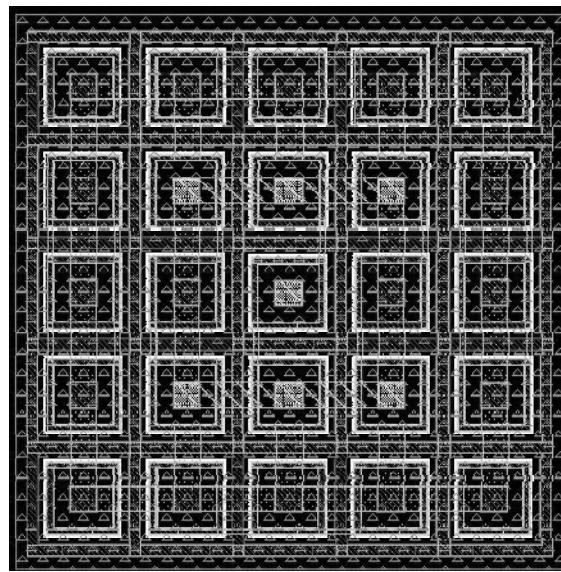

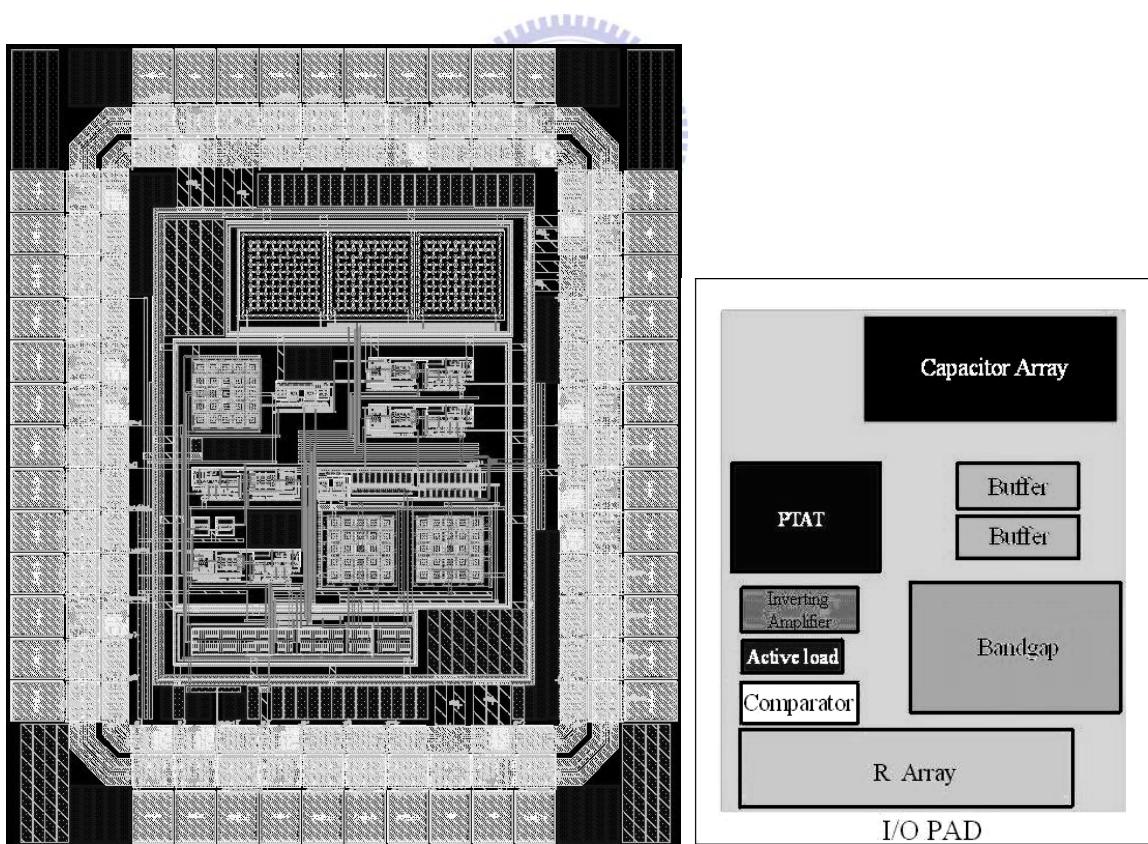

5-1 晶片佈局

圖5-1為面積呈現1:8的PNP電晶體，佈局成九宮格的型式形成一個工整PNP電晶體，如此可以減少面積且避免不協調 (mismatch) 的現象。圖5-2為完整前端電路佈局(含ESD PAD)及電路佈局示意圖。

圖 5-1 PNP 電晶體之佈局

圖 5-2 完整前端電路佈局(含 ESD PAD) 及電路佈局示意圖

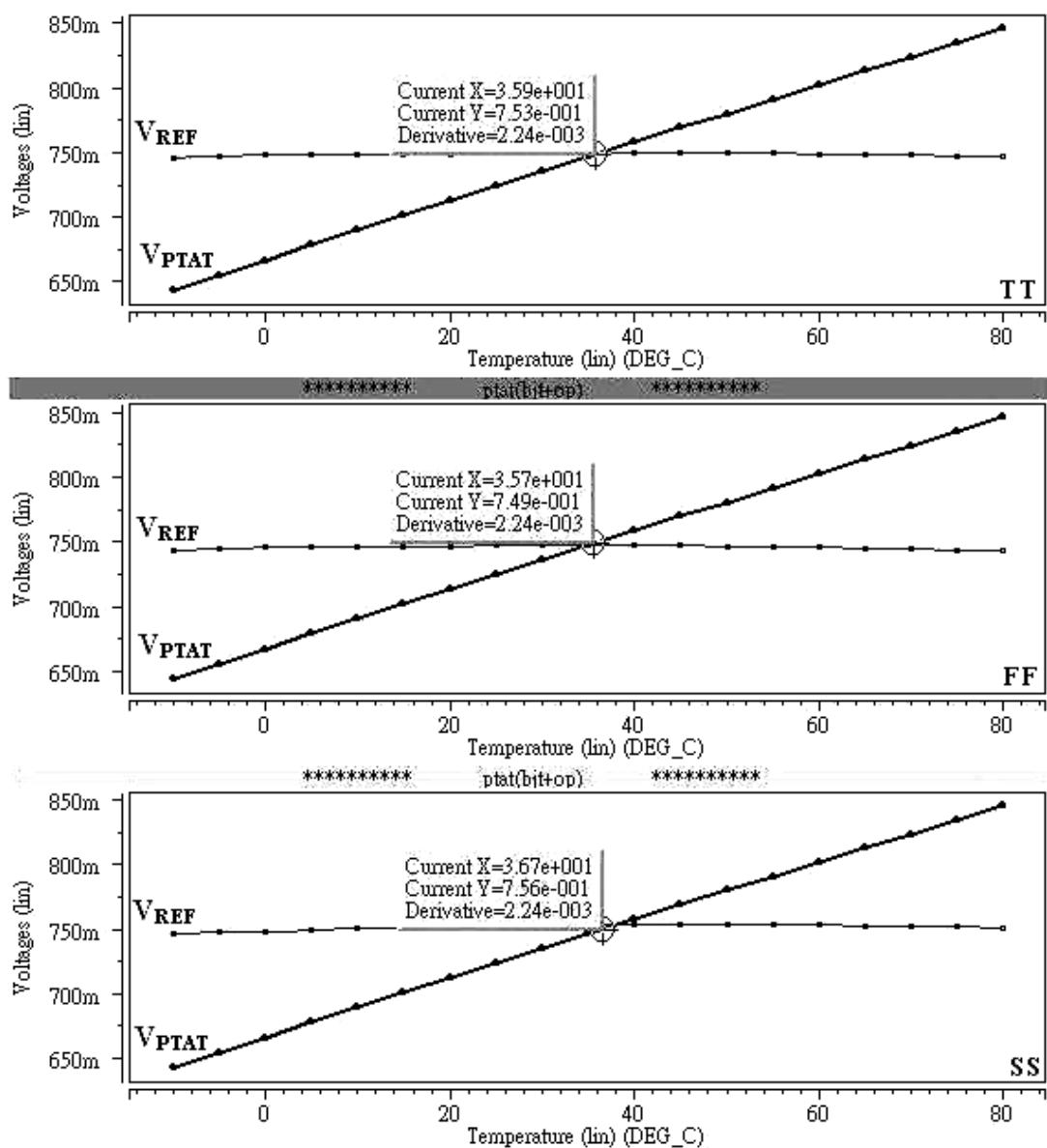

## 5-2 晶片佈局後模擬

圖5-3及圖5-4顯示的是經由反相放大器的輸出電壓，在電源電壓1.5V之下對溫度變化-10~80°C，分別為TT、FF、SS的輸出情形。X軸為溫度變化範圍，Y軸為電壓範圍，斜直線（圖4-16之 $V_{PTAT}$ ）為經反相放大器供給ADC的訊號及橫線（圖4-16之 $V_{REF}$ ）為能帶隙參考電壓，是為之後整合ADC所預留的電壓，其中圖5-3為pre-simulation、圖5-4為post-simulation的結果。

圖 5-3 溫度顯示之 pre-simulation

圖 5-4 溫度顯示之 post-simulation

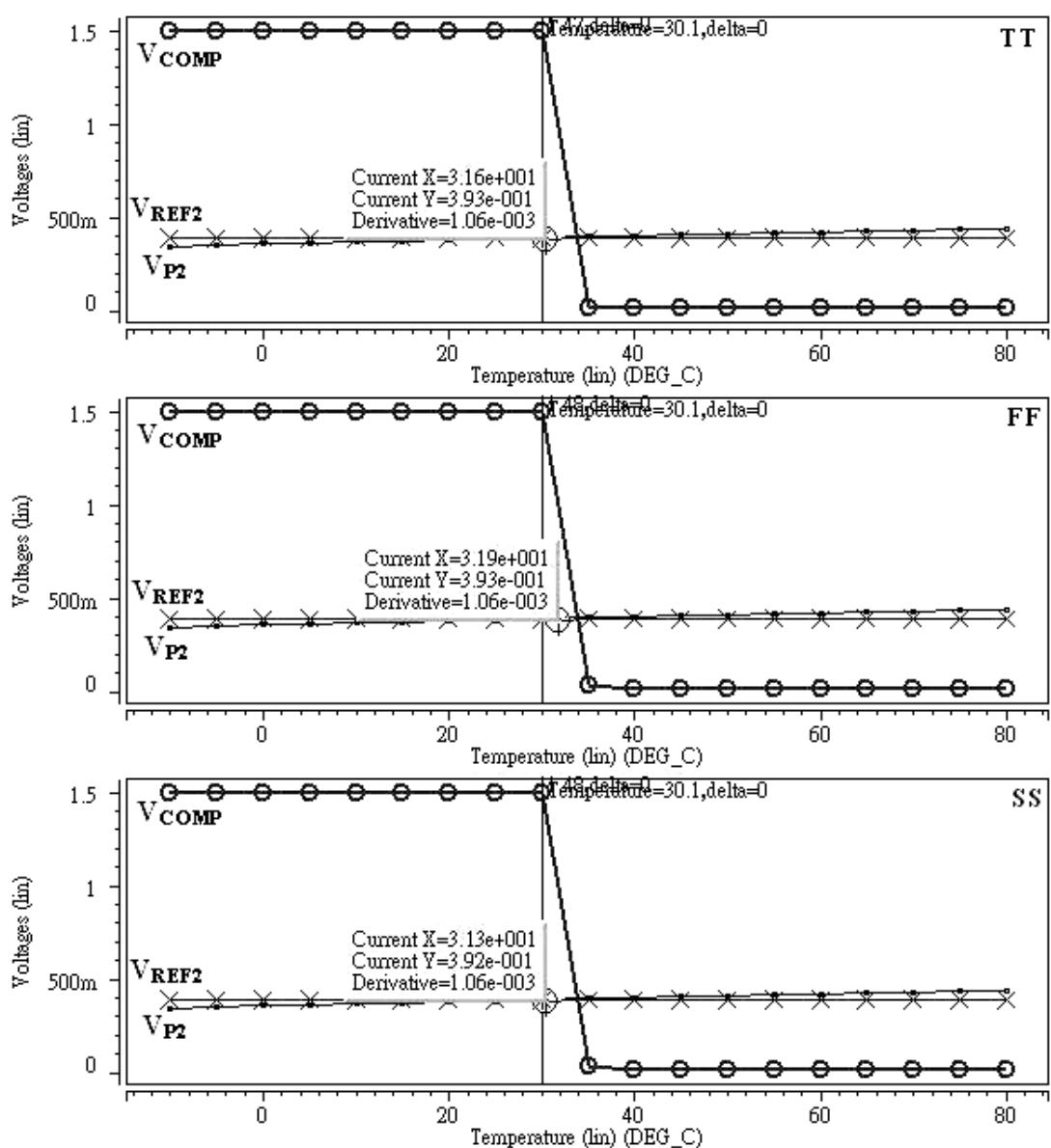

圖 5-5 與圖 5-6 分別顯示比較器輸入電壓的 pre-simulation 與 post-simulation 模擬結果，在電源電壓 1.5V 之下對溫度變化 -10~80°C，分別為 TT、FF、SS 的輸入情形。X 軸為溫度變化範圍，Y 軸為比較器電路的輸入電壓。下兩圖中斜直線為圖 4-18 之  $V_{P2}$ ，橫線為圖 4-18 之  $V_{REF2}$ 。

圖 5-5 比較器輸入端之 pre-simulation

圖 5-6 比較器輸入端之 post-simulation

圖 5-7 與圖 5-8 分別為比較器輸出端之 pre-simulation 及 post-simulation 之模擬結果。在電源電壓 1.5V 之下對溫度變化 -10~80°C，分別為 TT、FF、SS 的輸入情形。X 軸為溫度變化範圍，Y 軸為比較器電路之電壓。當比較器輸入電壓比較後，輸出為圖 5-7 與圖 5-8 中的  $V_{COMP}$  曲線。

圖 5-7 比較器輸出端之 pre-simulation

圖 5-8 比較器輸出端之 post-simulation

### 5-3 佈局驗證結果錯誤說明

- DRC驗証結果：

| Topcell total : 320 Results (in 6 of 323 Checks)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Topcell total : 320 Results (in 6 of 323 Checks)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul style="list-style-type: none"><li>↳ <input checked="" type="checkbox"/> Check NWR.E.3</li><li>↳ <input checked="" type="checkbox"/> Check OD.R.1.WARN</li><li>↳ <input checked="" type="checkbox"/> Check OD.W.1_OD.W.2</li><li>↳ <input checked="" type="checkbox"/> Check OD.S.1</li><li>☒ <input checked="" type="checkbox"/> Check OD.C.1 - 25 Results</li><li>☒ <input checked="" type="checkbox"/> Check OD.C.2_OD.C.3 - 5 Results</li><li>↳ <input checked="" type="checkbox"/> Check OD.C.4</li><li>☒ <input checked="" type="checkbox"/> Check OD.C.5 - 4 Results</li><li>↳ <input checked="" type="checkbox"/> Check OD.W.3</li><li>↳ <input checked="" type="checkbox"/> Check OD.A.1</li><li>↳ <input checked="" type="checkbox"/> Check OD2.E.1</li><li>↳ <input checked="" type="checkbox"/> Check OD2.S.1</li></ul> | <ul style="list-style-type: none"><li>↳ <input checked="" type="checkbox"/> Check NP.A.1</li><li>↳ <input checked="" type="checkbox"/> Check RPO.W.1</li><li>☒ <input checked="" type="checkbox"/> Check RPO.S.1 - 12 Results</li><li>↳ <input checked="" type="checkbox"/> Check RPO.C.1</li><li>↳ <input checked="" type="checkbox"/> Check RPO.C.2</li><li>☒ <input checked="" type="checkbox"/> Check RPO.C.3 - 34 Results</li><li>↳ <input checked="" type="checkbox"/> Check RPO.C.4</li><li>↳ <input checked="" type="checkbox"/> Check RPO.E.1</li><li>↳ <input checked="" type="checkbox"/> Check RPO.C.5</li><li>☒ <input checked="" type="checkbox"/> Check RPO.C.6 - 240 Results</li><li>↳ <input checked="" type="checkbox"/> Check RPO.A.1</li><li>↳ <input checked="" type="checkbox"/> Check CO.W.1</li></ul> |

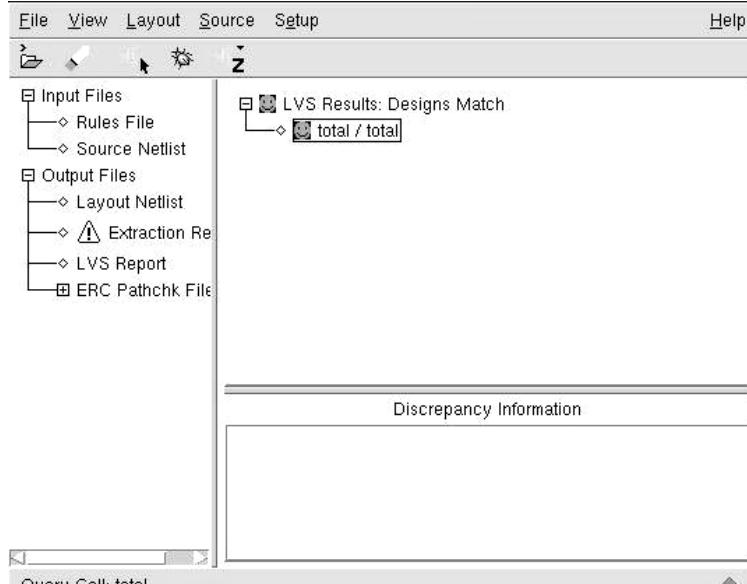

圖 5-9 有 6 個 DRC ERROR

圖 5-9 共 6 個 DRC ERROR 為 I/O PAD 的內部錯誤，如圖 5-10 所示，為可忽略的錯。

#### 常見command file判斷錯誤

| 原因                       | 適用          | 座標標示 |

|--------------------------|-------------|------|

| <b>STC I/O PAD ERROR</b> | STC18io_18T | N/A  |

| 批註用編號                    |             |      |

| OD.C.1                   |             |      |

| OD.C.2_OD.C.3            |             |      |

| OD.C.5                   |             |      |

| RPO.S.1                  |             |      |

| RPO.C.3                  |             |      |

| RPO.C.6                  |             |      |

圖 5-10 可允許 DRC 之錯誤

● LVS驗証結果：

圖5-11為佈局後（含ESD及PAD）之LVS驗證結果。

```

#####

##      C A L I B R E      S Y S T E M      ##

##      L V S      R E P O R T      ##

#####

REPORT FILE NAME:      total.lvs.report

LAYOUT NAME:          /home/bio/js-46/total_lay.sp ('total')

SOURCE NAME:          /home/bio/js-46/total.sp ('total')

RULE FILE:            /home/bio/js-46/_calibre.lvs_

CREATION TIME:        Tue Dec 16 20:40:35 2008

CURRENT DIRECTORY:   /home/bio/js-46

USER NAME:            js-46

CALIBRE VERSION:     v2007.1_31.29   Wed Apr  4 12:34:34 PDT 2007

OVERALL COMPARISON RESULTS

#      #####      #      #

#      #      CORRECT      #      #

#      #      #      #      #

#      #####      #      #

Warning: Ambiguity points were found and resolved arbitrarily.

*****

CELL SUMMARY

*****

Result      Layout      Source

-----      -----      -----

CORRECT     total       total

```

圖 5-11 LVS 驗證正確

## 5-4 測試考量及預計規格列表

晶片的測試架構如圖5-12所示，其目的在於確認此晶片是否能夠正常運作，有效的感測溫度訊號，達到溫度感測及開關之效果。量測晶片時所須用到的器材包括：恆溫箱、邏輯分析儀、電源供應器、三用電表等。而測試步驟如下：

- (1) 將晶片放置恆溫箱中，箱中將放置燈泡與溫度計。

- (2) 將電源供應器調整適當供應電壓，並接上其電源(0/1.5V)。

- (3) 燈泡未開啟時，將晶片溫度感測端接至外部 ADC，將 ADC 輸出接至邏輯分析儀觀察其變化。將晶片內部比較器輸出至三用電表觀察電壓之變化，也利用三用電表測量能帶隙參考電路之電壓值，並記錄當時溫度。

- (4) 開啟燈泡，重複步驟 (3)。此時注意溫度計達  $30^{\circ}\text{C}$  時，三用電表電壓之變化，是否如模擬之結果。

- (5) 若 PTAT 電路、能帶隙參考電壓電路、電壓緩衝器、比較器未達到所需結果或有問題，已由其輸出端拉出 pin 腳，可由此測試腳輸入所須的訊號，不會因部分電路的問題影響到整個電路的測試。

圖 5-12 晶片的測試架構

表5-1為Pre-Simulation與Post-Simulation的預計規格表。

表 5-1 預計規格表：

| Process Technology           | TSMC 0.18um 1P6M |                 |

|------------------------------|------------------|-----------------|

|                              | Pre-Simulation   | Post-Simulation |

| Supply voltage               | 1.5V             | 1.5V            |

| Temperature range            | -10~80°C         | -10~80°C        |

| PTAT voltage                 | 2.25 mV/°C       | 2.25 mV/°C      |

| Chip size (mm <sup>2</sup> ) | 1.019×1.214      |                 |

## 第六章

### 結論與未來展望

#### 6-1 結論

在本論文中，採用了具有低電壓、高輸入共模範圍（ICMR）及高共模互斥比（CMRR）的基體推動架構，實現了在低電壓時的溫度感測電路，將一般傳統使用運算放大器迴授方式，由閘極輸入架構使BJT兩端有相同的電壓值，改由基體推動的架構去獲得BJT兩端具有相同之電壓值，如此可以減少臨界電壓之影響。

將感測的正比於絕對溫度電壓利用放大器調整線性度及解析度，經調整過後的正比於絕對溫度電壓外接10bitADC以便溫度顯示。將正比於絕對溫度電壓與能帶隙參考電壓經比較器，方能控制後端電路之開或關，而能帶隙參考電壓當作比較器的比較電壓，當溫度達到30°C所產生的正比於絕對溫度電壓高於能帶隙參考電壓，則使後端電路動作。本論文也模擬了後端電路若需要1V偏壓的情況，也就是當溫度達到30°C之後，便能使後端需要1V偏壓之電路開始動作。

#### 6-2 未來展望

本論文完成了溫度感測電路、能帶隙參考電壓電路及比較器，溫度開關部分已經完成模擬，之後可以朝向依所需溫度讓後端電路動作之設計，即依所需溫度則能控制後端電路開、關，而溫度顯示方面尚缺類比數位轉換電路，根據模擬結果需要

一個10-bit的類比數位轉換電路，以完成一個數位輸出的溫度感測系統。未來仍須國家晶片中心，證實本論文之理論及模擬結果。

目前因製程的進步及電晶體密度的提高，造成因系統晶片功耗所產生的溫度問題，而本論文除了應用於生醫方面，也盼能應用於晶片溫度之監控與溫度對晶片造成傷害之避免。

## 參考文獻

- [1] 吳朗, 溫度感測器理論與應用, 全華科技圖書股份有限公司, 1986

- [2] A. Bakker, J.H. Huijsing, "Micropower CMOS temperature sensor with digital output," *IEEE Journal of Solid-State Circuits*, vol. 31, Issue: 7, pp. 933-937, July 1996.

- [3] E. A. Vittoz, "A low-voltage CMOS bandgap reference," *IEEE J. Solid-State Circuits*, vol. SC-14, pp. 573-577, 1979.

- [4] R. L. Geiger, P. E. Allen, N. R. Strader, *VLSI Design Techniques for Analog and Digital Circuits*, McGraw-Hill, 1990.

- [5] A. RUSU, *Modelarea componentelor microelectronice active* Ed, Academiei, 1990.

- [6] M. Sudha, W.T. Holman, A bw noise sub-bandgap voltage reference, *Circuits and Systems. Proceedings of the 40<sup>th</sup> Midwest Symposium*, Vol. 1, pp. 193 -196, 1997.

- [7] L.L.G. Vermaas, C.R.T. De Mori, R.L. Moreno, A.M. Pereira. E. Chany R., "A bandgap voltage reference using digital CMOS process," *Electronics, Circuits and Systems, IEEE International Conference*, Vol. 2 , pp. 303 -306, 1998.

- [8] M.A.T. Sanduleanu, A.J.M. Van Tuijl, R.F. Wassenaar, "Accurate low power bandgap voltage reference in 0.5um CMOS technology," *Electronics Letters*, Vol. 3410, pp. 1025 -1026, 1998.

- [9] C. Popa, O. Mitrea, "Micropower CMOS bandgap voltage reference," *Proceedings of the 2nd International Symposium*, pp. 502 - 506, 19-21, June 2001.

- [10] C. Popa, *Circuite integrate analogice. Surse de curent. Surse de fensiune*, Editura MATRIX ROM, Bucureati, 1999

- [11] A. Buck, C. McDonald, S. Lewis, T.R. Viswanathan, "A CMOS bandgap reference without resistors," *Digest of Technical Papers. ISSCC*, pp. 442 475, 2000.

- [12] B.J Blalock, P.E. Allen, "Designing 12V op amps using standard digital CMOS technology," *IEEE Trans Circuits and System II: Analog and Digital Signal Processing*, 1998.

- [13] S. S. Rajput, S. S. Jamuar, "Low voltage analog circuit design techniques," *IEEE Circuits and Systems Magazine*, 2002.

- [14] K Lasanen, E R Ruotsalainen, J. Kostamovaara, "A 1-V 5 $\mu$ W CMOS-opamp with

- bulk-driven input transistors," *Proceedings of the 43<sup>rd</sup> IEEE Midwest Symposium on Circuits and Systems*, 2000.

- [15] Y. Ber2. T. S. Lande. O. Naess. And H. Gundersen. "Ultra low voltage floating gate transconductance amplifiers," *IEEE Trans. Circuits Svst. II*, vol. 48, pp. 32-44. Jan 2001.

- [16] E. Sanchez-Sinencio, "Low Voltage Analog Circuit Design Techniques," *IEEE Dallas CAS Workshop*, 2000.

- [17] S. Yan and E. Sanchez-Sinencio, "Low Voltage Analog Circuit Design Techniques: A Tutorial," *IEICE Transactions on Fundamentals*, vol. E83-A, Febr 2000.

- [18] E. Sanchez-Sinencio and A. G. Andreou, ed., "Low Voltage/Low Power Integrated Circuits and Systems," *IEEE Press*, 1999.

- [19] Y. Haga, H. Z. Hoseini, L. Berkovi, and I. Kale, "Design of A 0.8VoltFully Differential CMOS OTA Using the Bulk-Driven Technique," *IEEE Circuits and Systems*, vol. 1, pp. 220-223, 2005.

- [20] D. A. Neamen, *Semiconductor Physics and Device*, Third Edition, McGraw Hill, 2003.

- [21] F.A. Levinzon, "Noise of the JFET Amplifier," *IEEE Transactions on Circuits and System*, vol. 47, NO. 7, pp. 981-985, July 2000.

- [22] B.J. Blalock, P.E Allen, and G.A Rincon-Mora, "Designing 1-V op amps using standard digital CMOS technology," *IEEE Trans. Circuits Syst. II*, Vol. 45, pp. 769 – 780, July 1998.

- [23] J. Blalock, E. Allen and A. Rincon-Mora, "A 1 V CMOS Op Amp Using Bulk-Driven MOSFET's," *ISSCC*, pp. 192-193, Feb 1995.

- [24] [http://designer.mech.yzu.edu.tw/article/articles/technical/\(2002-07-20\)%20%E7%9D%A1%E7%9C%A0%E7%9B%A3%E6%B8%AC%E7%9B%B8%E9%97%9C%E7%A0%94%E7%A9%B6%E7%B0%A1%E4%BB%8B.htm](http://designer.mech.yzu.edu.tw/article/articles/technical/(2002-07-20)%20%E7%9D%A1%E7%9C%A0%E7%9B%A3%E6%B8%AC%E7%9B%B8%E9%97%9C%E7%A0%94%E7%A9%B6%E7%B0%A1%E4%BB%8B.htm)

- [25] Trond Ytterdal, Yuhua Cheng, Tor A. Fjeldly, *Device Modeling for Analog and RF CMOS Circuit Design*, John Wiley & Sons Ltd, 2003.

- [26] Bakker, A.; "CMOS smart temperature sensors - an overview," *Proceedings of IEEE*, vol. 2, pp. 1423 –1427, 12-14 June 2002.

- [27] David A. Johns and Ken Martin, *Analog Integrated Circuit Design*, John Wiley and

Sons, pp.354 – 364, 1997.

- [28] K. Laker and W. Sansen, Design of Analog Integrated Circuits and Systems, New York: McGraw-Hill, pp. 20–22, 1994.

- [29] F. O. Eyned and W. Sansen, Analog Interfaces for Digital Signal Processing Systems, Boston, MA: Kluwer Academic, 1993.

- [30] B. J. Blalock, A 1-volt CMOS wide dynamic range operational amplifier, Ph.D. dissertation, School Elect. Comput. Eng., Georgia Inst. Technol., Atlanta, GA, 1996.

- [31] J. P. Uyemura, Fundamentals of MOS Digital Integrated Circuits, Reading, MA: Addison-Wesley, 1988.

- [32] B.J Blalock, O.E Allen, "Low-voltage, bulk-driven MOSFET current mirror for CMOS technology," *IEEE International Symposium on Circuits and Systems*, 1995.

- [33] P.E Allen, B.J Blalock, G.A Rincon, "A 1V CMOS opamp using bulk-driven MOSFETs. Digest of Technicl," *IEEE International Solid2 State Circuit Conference*, 1995.

- [34] K. R. Laker and W. M.C. Sansen, Design of Analog Integrated Circuits and Systems, McGraw-Hill, Inc., NY, pp. 20-22, 1994.

- [35] B.J. Blalock, P.E. Allen, "A low-voltage, bulk-driven MOSFET current mirror for CMOS technology," *IEEE International Symposium*, Vol. 3, pp.1972 – 1975, 28 April-3 May 1995.

- [36] I. Grech; J. Micallef, G. Azzopardi, C.J. Debono, "A 0.9 V wide-input-range bulk-input CMOS OTA for G/sub m/-C filters," *IEEE International Conference*, Vol. 2, pp. 818 - 821, 14-17, Dec. 2003.

- [37] Zhangming Zhu; Yintang Yang; "A 0.8 V low-power CMOS PTAT voltage," *IEEE International Workshop*, pp. 1 – 5, May 28-30, 2005.

- [38] K. Tom, A. Alvandpour, "Curvature compensated CMOS bandgap with sub 1V supply," *IEEE International Workshop on Electronic Design*, pp. 17-19 Jan 2006.

- [39] Y. Jiang, Edward K.F. Lee, "Design of Low-Voltage Bandgap Reference Using Transimpedance Amplifier," *IEEE Transactions on Circuits and Systems*, vol. 34, pp. 552- 555, July 2000.

- [40] K.Lasanen, V. Korkala, E. Raisanen-Ruotsalainen, J. Kostamovaara, "Design of a Low Power 1V CMOS Bandgap Reference Based on Resistive Subdivision," *IEEE*

*Circuits and Systems*, vol. 4, pp. 564-567, May 2002.

- [41] Behzad Razavi, Design of Analog CMOS Integrated Circuits, McGraw-Hill, 2001.

- [42] D.A. Johns and K. Martin, Analog Integrated Circuit Design, John Wiley & Sons, New York, 1997.

## 附錄：

### A. 打線圖(SB18)

圖 A. 電路接腳註明及修改後之打線圖

## B. Tapeout Review Form

Tapeout review form 的用意在提醒設計者在設計、模擬、佈局、佈局驗證及 tapeout 時具備設計理念及了解應注意事項,希望能藉此提昇晶片設計的成功率及達到完整的學習效果。因此,請指導教授及設計者確實檢查該晶片設計過程是否已注意本表格之要求,並在填寫確定後簽名,若審查時發現設計內容與 Tapeout Review Form 之填寫不符,很可能遭取消該晶片下線製作資格。可參考本表後所附範例確實填寫。

專題名稱: 溫度感測與體溫開關整合晶片設計

Top Cell 名稱:total

製程名稱:TSMC .18 1P6M

### 1 電路概述

1-1. 工作電壓:1.5V

1-2. 工作頻率:60mHz

1-3. 功率消耗: 601.9852u

1-4. 是否使用 CIC 提供之 ARM CPU IP? 否

使用 CPU 之種類為何? (ARM7TDMI or ARM926EJ)

1-5. 此電路架構於貴實驗室是否第一次設計?是(接 2-1)V 否(接 1-5-1)

1-5-1. 此電路之前不 work 或 performance 不好的原因為何?

1-5-2. 對之前的錯誤作何種修改?

### 2 電路模擬考量

2-1. 已用 SS,SF,TT,FS,FF 中哪些不同狀態之 spice model 模擬?SS,TT,FF

2-2. 已模擬過電壓變動+/-10%中哪些情況對電路工作之影響? 是

2-3. 如何考量溫度變異之影響?模擬-10~80°C溫度的變化

2-4. 如何考量電阻、電容製程變異之影響?加入 Dummy

2-5 模擬時是否加入 IO PAD、Bonding wire 的效應及考量測試儀器之負載等影響? 是\_\_\_\_\_

2-6 是否作 LPE 及 post layout simulation? 是\_\_\_\_\_使用的軟體為 Laker、Caliber、Hspice

### 3 Power Line 佈局考量

3-1. Power Line 畫多寬? >4.7um

3-2. 是否考量 power line current density? 是\_\_\_\_\_

3-3. 是否考量 Metal Line 之寄生電阻、電容? 是\_\_\_\_\_

### 4 DRC,LVS

4-1. 是否有作 whole chip 的 DRC 及 LVS? 是\_\_\_\_\_

4-2. 除了 PAD 上 DRC 的錯誤之外,內部電路及與 PAD 連接的線路是否有錯? 否\_\_\_\_\_

錯誤原因为何? \_\_\_\_\_

4-3. 在作 LVS 的過程中,PIN 腳及元件是否 match? 是\_\_\_\_\_ 不 match 的原因为何? \_\_\_\_\_

4-4. 檢查 PAD 與 PAD 間是否有移位、短路或斷路的現象? 否\_\_\_\_\_

### 5 類比-混合訊號電路佈局考量(類比-混合訊號電路設計者填寫)

#### 5-1 佈局對稱性及一致性考量

5-1-1 OP(Comparator) Input Stage 是否對稱? 是\_\_\_\_\_

5-1-2 OP(Comparator) Input Stage 是否對稱? 是\_\_\_\_\_

5-1-3 佈局中對稱元件是否使用 dummy cell 技巧? 是\_\_\_\_\_

5-1-4 對稱電容是否採用同心圓佈局? 是\_\_\_\_\_

5-1-5 對稱單位電容四周是否切成 45 度斜角? 是\_\_\_\_\_

5-1-6 對稱電容的單位面積是否一致? 是\_\_\_\_\_

單位電容面積多大? 7.399 um x 7.399 um

單位電容值多大? 0.05 pF

5-1-7 電阻採用哪一材質製作? P+ poly resistor with RPO \_\_\_\_\_

單位電阻值多大? 5K ohm \_\_\_\_\_

5-2 電路雜訊佈局考量

5-2-1 是否將 Analog 及 Digital 的 power line 分開? 是 \_\_\_\_\_

5-2-2 Analog area 是否用 guard ring 隔絕? 是 \_\_\_\_\_

5-2-3 Digital area 是否用 guard ring 隔絕? 是 \_\_\_\_\_

5-2-4 對於 sensitive line 是否使用 shield 的技巧? 是 \_\_\_\_\_

5-2-5 Analog guard ring 及 shield 是否接至乾淨之電位? 是 \_\_\_\_\_

5-2-6 是否將 sensitive line 儘量縮短及避免跨越 noise(clock)line? 是 \_\_\_\_\_

5-2-7 電容的上下極板是否接對? 是 \_\_\_\_\_

6 MEMS 設計考量(MEMS 設計者填寫)

6-1 請簡述所進行之後製程: \_\_\_\_\_

6-2 後製程操作地點: \_\_\_\_\_

6-3 下線者目前是否有操作該製程設備之合法授權? \_\_\_\_\_ 若目前無操作該製程設備之合法授權，是否可在晶片取回前得到合法授權? \_\_\_\_\_

6-4 下線者是否有使用該製程設備之經驗? \_\_\_\_\_

6-5 是否有該後製程之製程參數（壓力、溫度、流量、……）? \_\_\_\_\_

6-6 之前是否有成功實現過該後製程? \_\_\_\_\_

6-7 Layout 違反 design rule 的部分是否會影響微結構本身或元件操作? \_\_\_\_\_

6-8 Layout 之蝕刻孔尺寸是否足以讓結構懸浮? \_\_\_\_\_

6-9 元件驅動電壓範圍? \_\_\_\_\_

7 RF Circuit 電路佈局考量 (RF 操作頻段設計者填寫):

7-1 電路規格適用何種系統? \_\_\_\_\_

7-2 說明被動元件模型的來源 \_\_\_\_\_

7-3 模擬軟體 (可不只一種)? \_\_\_\_\_

7-4 系統整合 chip 裡之各個 block 是否曾下過線且量測符合預期規格 (chip 為系統整合者)

回答,並說明製程梯次代號)? \_\_\_\_\_

7-5 佈局考量：

7-5-1 元件佈局方式是否與模型提供者所提供的佈局一致? 是\_\_\_\_\_

7-5-2 接地與電壓源是否均勻? 是\_\_\_\_\_

7-5-3 元件與拉線的電流承載能力考量? 是\_\_\_\_\_

7-5-4 拉線是否過長過細? 否\_\_\_\_\_

7-5-5 PAD 的佈局是否配合量測上之考量? 是\_\_\_\_\_

7-5-6 PAD 與 Bond-wire 的效應是否考量? 是\_\_\_\_\_

7-6 DRC 驗證過程中, 部分錯誤若為特殊考量, 請說明 是\_\_\_\_\_

OD.C.1、OD.C.2、OD.C.3、OD.C.5、RPO.S.1、RPO.C.3、RPO.C.6 等 DRC 錯誤皆發生 TSMC PAD 處, 為可忽略之錯

7-7 LVS 驗證過程中, 電感電容或其他特殊元件的比對是否做過處理, 請說明 是\_\_\_\_\_

加入 DUMMY 減少製程上的飄移與 shadow 現象

7-8 量測方式為 on wafer, on PCB or in package? 並說明量測時應該注意事項與量測地點

on PCB, 初步先電性量測, 次為溫度量測, 測試平台分為常溫及人體體溫, 以測試電路是否常溫下正常工作

8 PAD Replacement 考量(使用 TSMC I/O PAD 設計者填寫)

8-1 個人設計的 Cell 名稱(cell-name)未與 TSMC 所提供之任一 Pad Cell 名稱相同 是\_\_\_\_\_

8-2 採用 Create Instance 方式加入 I/O Pad, 未用 Copy 或 Flatten 破壞 Instance 的結構 是\_\_\_\_\_

8-3 由 IC Core 部份拉線到 Pad 只拉到最邊緣部分, 未過於覆蓋 Pad 是\_\_\_\_\_

9. 使用 ARM926EJ or ARM7TDMI CPU IP

9-1. 若有使用 ARM926EJ /ARM7TDMI CPU IP, 請提供以下訊息以便向 ARM 原廠申

請 Design ID 。

使用的 CPU 種類 (ARM926EJ or ARM7TDMI) : \_\_\_\_\_

使用的 metal layers 的層數: \_\_\_\_\_

佈局中 ARM926EJ /ARM7TDMI Macro 的 cell name: \_\_\_\_\_

這個晶片是否為修訂版本(revision,也就是之前曾下線過相同晶片) ? \_\_\_\_\_

若是修訂版本，前一次下線的晶片編號: \_\_\_\_\_

修訂版本的原因是 ? (例如修正 bug) \_\_\_\_\_

## 10 其他考量

10-1 是否考量測試時的輸出量測點? 是

10-2 是否考量電路之可修改性(如用 laser cut 設備) 是

設計者簽名: 王建昇 指導教授簽名: 林進燈

## C. CIC Tapeout Question & Reply

編號 114b

計畫名稱：溫度感測與體溫開關整合晶片設計

包裝材料：18 S/B:8Pcs, DieSort:10EA, 製作經費預估\$71,516

評比 B

建議/修改

1. 後模擬是否考慮封裝之鎊線影響？

Ans：在模擬時已列入考慮，寄生效應的影響會在數GHz頻率以上，而我們的應用頻率範圍在60Hz屬於低頻，所以鎊線的寄生效應對電路本身影響並不大。

2. 提供Core的I/O pad不足。

Ans：本設計採用18 PIN的封裝，並將有剩下的I/O PAD加入電源輸入腳位，以提供核心和PAD足夠的電源，PIN腳訊號對應如下題的表格說明。新加入PAD，已經重新layout補上，並做完DRC與LVS的驗證。

3. PDA的擺置說明不清。

Ans：

| Pin NO. | Signal name | I/O durection | Signal explanation |

|---------|-------------|---------------|--------------------|

| 1       | VSS         | I             | Core電源             |

| 2       | VDD         | I             | Core電源             |

| 3       | Null        | O             | 散熱用                |

| 4       | Vp2         | O             | PTAT感溫電壓輸出         |

|    |                   |   |              |

|----|-------------------|---|--------------|

| 5  | V <sub>p1</sub>   | O | PTAT電壓輸出     |

| 6  | V <sub>REF2</sub> | O | PMOS主動負載訊號輸出 |

| 7  | V <sub>COMP</sub> | O | 比較器結果輸出      |

| 8  | V <sub>p3</sub>   | I | 反向放大器訊號輸入    |

| 9  | V <sub>PTAT</sub> | O | 反向放大器結果輸出    |

| 10 | V <sub>p4</sub>   | I | 反向放大器訊號輸入    |

| 11 | V <sub>SS</sub>   | I | Core電源       |

| 12 | V <sub>D</sub>    | I | Core電源       |

| 13 | V <sub>REF1</sub> | I | PMOS主動負載訊號輸入 |

| 14 | V <sub>REF</sub>  | O | Bandgap電壓輸出  |

| 15 | V <sub>SS</sub>   | I | Core電源       |

| 16 | V <sub>D</sub>    | I | Core電源       |

| 17 | V <sub>SSE</sub>  | I | ESD電源        |

| 18 | V <sub>DDE</sub>  | I | ESD電源        |

4. 無offset voltage的分析，此設計參數會影響此電路準確性。

Ans：offset voltage只影響線性區斜率，並不影響電路之應用且溫度顯示及溫度開關皆能在所接受的範圍正常動作，所以未特別針對offset voltage去模擬影響情況。

5. 電路架構改良說明不清楚。

Ans：一般傳統溫度感測電路與帶隙參考電壓電路的運算放大器影響了最低供應電壓的範圍，所以為了符合在低電壓的情況，溫度感測電路將採用基體推動(Bulk-Driven) MOSFET之架構，此架構有別於一般利用閘極(Gate)輸入的方式，是利用基體當輸入端，解決了閘極輸入受限於臨界電壓(threshold voltage)

的限制，而且可以增加輸入擺幅範圍。

6. 設計結果完整，有良好實用性。

Ans：謝謝評審委員的指教。

7. bulk-driven方式應考慮latch-up問題。

Ans：在layout上已各自用雙層Gard Rings分隔且隔開40um以上，以避免latch up效應產生。

8. 晶片面積很大，但PAD使用很少，應增加VDD/VSS等。

Ans：描述如同問題2，已經重新layout補上，圖5-2為修改後之layout圖，圖5-9與圖5-11分別為修改後之DRC與LVS驗證，圖A為修改後之打線圖。

佈局是否需修改？

Yes