# **Short Papers**

# Efficient Physical Timing Models for CMOS AND-OR-Inverter and OR-AND-Inverter Gates and Their Applications

CHUNG-YU WU AND MING-CHUEN SHIAU

Abstract—Efficient physical timing models for complex CMOS AND-OR-Inverter (AOI) and OR-AND-Inverter (OAI) gates have been successfully developed. Through extensive comparisons with SPICE simulation results, the developed models have shown a maximum error of 30% for long-channel and small-geometry CMOS AOI/OAI gates with wide ranges of channel dimensions, capacitive loads, logic input patterns, circuit configurations, device parameter variations, and non-characteristic waveform input excitations. The error can be further reduced to 16% with commonly used device dimensions. The developed timing models are successfully applied to the autosizing of CMOS AOI/OAI gates. The results show a good accuracy and a reasonable CPU time consumption.

### Nomenclature

| В                     | Mobility correction factor (SPICE device parameter).                                                                                      |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| $C_{\mathrm{bdn(p)}}$ | Bulk-drain p-n junction capacitance of an n-channel (p-channel) MOSFET.                                                                   |

| $C_{bsn(p)}$          | Bulk-source p-n junction capacitance of an n-channel (p-channel) MOSFET.                                                                  |

| $C_{\mathrm{gbn(p)}}$ | Gate-bulk capacitance of an n-channel (p-channel) MOSFET.                                                                                 |

| $C_{\mathrm{gdn}(p)}$ | Gate-drain capacitance of an n-channel (p-channel) MOSFET.                                                                                |

| $C_{gsn(p)}$          | Gate-source capacitance of an n-channel (p-channel) MOSFET.                                                                               |

| DELTA                 | Narrow-channel width factor (SPICE device parameter).                                                                                     |

| GAMMA                 | Bulk threshold parameter in SPICE, which represents the proportionality factor relating the change in threshold voltage to backgate bias. |

| $I_{dn(p)}$           | Linearized drain current of an n-channel (p-channel) MOSFET in the large-signal equivalent circuit.                                       |

| $I_{\mathrm{DS}}$     | DC drain current of a MOSFET.                                                                                                             |

| $L^{-}$               | Effective channel length of a MOSFET.                                                                                                     |

| $L_{mask}$            | Mask channel length of a MOSFET.                                                                                                          |

| N                     | Fan-out number of a gate.                                                                                                                 |

| NSUB                  | Substrate doping concentration (SPICE device parameter).                                                                                  |

| $T_{\text{OX}}$       | Oxide thickness (SPICE device parameter).                                                                                                 |

| <i>U</i> CRIT         | Critical field for mobility degradation due to normal                                                                                     |

|                       | field (SPICE device parameter).                                                                                                           |

| UEXP                  | Critical field exponent for mobility degradation due                                                                                      |

Manuscript received February 13, 1987; revised September 4, 1987, February 15, 1988, and August 17, 1989. This paper was recommended by Editor M. R. Lightner.

to normal field (SPICE device parameter).

The authors are with the Institute of Electronics and the Department of Electronics Engineering, National Chiao Tung University, Hsinchu, Taiwan, China.

IEEE Log Number 9035468.

| UO                         | Surface mobility at low gate voltage and large de-                         |

|----------------------------|----------------------------------------------------------------------------|

|                            | vice size (SPICE device parameters).                                       |

| <i>U</i> TRA               | Mobility degradation factor due to lateral field (SPICE device parameter). |

| $V_{oj}$                   | Large-signal voltage at the internal node j of a logic                     |

|                            | gate.                                                                      |

| $V_{\rm BS(D)}$            | Bulk-source (drain) voltage of a MOSFET.                                   |

| $V_{ m DD}$                | Power supply voltage.                                                      |

| $V_{\rm DS(GS)}$           | Drain-source (gate-source) voltage of a MOSFET.                            |

| $V_T$                      | Threshold voltage of a MOSFET under substrate bias.                        |

| $V_{\mathrm{TO}}$          | Zero-bias threshold voltage of a MOSFET.                                   |

| $\mathbf{w}^{\mathrm{IO}}$ | Effective channel width of a MOSFET.                                       |

| XJ                         | Metallurgical junction depth (SPICE device parameter).                     |

| $\epsilon_{SI(SIO_2)}$     | Permittivity of $S_i$ semiconductor (silicon dioxide).                     |

| $\mu_{n(p)}$               | Electron (hole) surface mobility.                                          |

| $\phi_F$                   | Fermi potential.                                                           |

|                            |                                                                            |

### I. Introduction

Efficient timing models or macromodels of MOS logic gates [1]–[22] have shown many advantageous features in the design of MOS digital IC's. They can be applied to timing analysis and verification of MOS circuits [4]–[11], [18]–[20] as well as circuit optimization and autosizing [12]–[17], [21], [22]. Furthermore, all these models have reasonable accuracy and consume little computer memory and CPU time. They can also provide a deep insight into the speed nature of digital MOS IC's.

Although CMOS has become a dominant technology in digital VLSI/ULSI [23], only a few timing models have so far been proposed [5]-[7], [14]-[17], [19]-[22]. Among them, the use of the step-response models [14] does not guarantee the required accuracy due to the neglect of the strong influence of input signals on delay times [16].

There are two approaches to cope with the input waveshape effects [17]. One is table driven techniques like Crystal [5]. Crystal is a timing simulator in which transistor resistances can be adjusted according to the input waveforms and device operating regions to obtain a higher accuracy. This approach, however, has been proven to have some limitations [17]. These limitations are, for example, the accuracy problem due to resistance extractions for the gates with different beta ratios, sizes, etc., the problem due to the table interpolations, and the difficulties in optimizations. The other approach is entirely based on device equations. In this approach, the resistance extractions are not required and the table interpolation problem can be avoided. Moreover, this approach is quite suitable for optimization and autosizing. For efficient design automation and optimization, good analytical delay macromodels [6], [7], [16]–[22] entirely based on device equations are required [17].

Generally, accurate and efficient timing models entirely based on device equations are very useful in various CAD applications in VLSI, such as timing verification, optimization, logic simulation, and autosizing [17].

So far, the timing models for inverters, NAND and NOR gates [5]-[7], [14]-[16], [19]-[22] have been developed. However, the timing models for AND-OR-Inverter (AOI) and OR-AND-Inverter (OAI) gates, which are commonly used in the design of CMOS digital IC's, have not yet been reported. Due to their complicated structures, the computer time consumed in the simulation of the circuits containing those gates is very long. The efficient timing models of those CMOS gates, therefore, are more urgently required than those of other simple combinational logic gates.

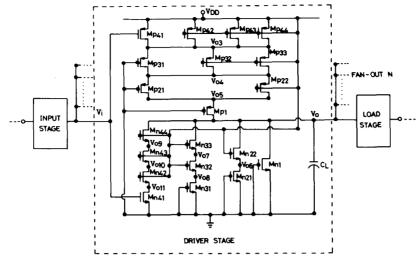

Fig. 1. A chain of identical CMOS 4-3-2-1-input AOI gates under the worst-case timing condition.

It is the aim of this paper to develop efficient physical timing models for CMOS AOI/OAI gates with wide ranges of channel dimensions, capacitive loads, circuit configurations, input excitations, and device parameters. As compared to the SPICE [24] simulation results, the maximum error of model calculation results is 30% within a large applicable range. Fine tuning within a special range can reduce the error to 16%. By using the developed models, the signal timing of the commonly used CMOS AOI/OAI gates with less than 4 PMOSFET's or 4 NMOSFET's in series can be quickly computed. Moreover, autosizing of CMOS AOI/OAI gates can be performed through the use of the timing models.

The model formulations are described in Section II. Comparisons between model calculations and SPICE simulations are given in Section III. An application example of the developed models in autosizing is given in Section IV. Finally, conclusions are made.

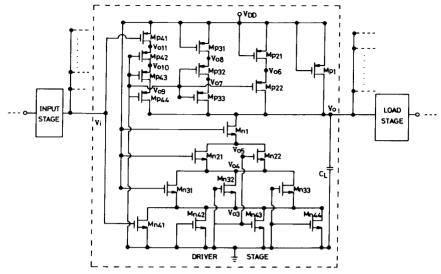

### II. TIMING MODELS

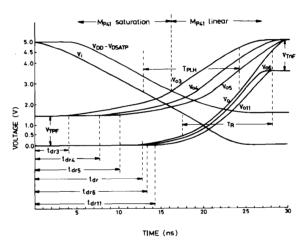

As an illustrative example for model formulations, a 3.5-um CMOS 4-3-2-1-input AOI gate under a worst-case timing condition is considered. The AOI gate circuit is shown in Fig. 1 where the input voltage  $V_i$  drives the MOSFET's  $M_{p41}$  and  $M_{n41}$ . It is known that after the signal passes through several stages, the rising or the falling waveforms at the output node of a stage gradually become the same, being independent of input excitations. Such waveforms are named characteristic waveforms [16]. The typical characteristic waveforms obtained from the SPICE simulations for the falling input voltage  $V_i$  are plotted in Fig. 2. As the name of characteristic waveforms implies [16], the waveforms of the AOI gate in 1.5-μm CMOS technology are very similar to those of Fig. 2. As shown in the figure, the output voltage  $V_o$  has a rising waveform with the characteristic rise time  $T_R$  defined as the time interval between  $V_o$ =  $0.1 V_{\rm DD}$  and  $V_o = 0.9 V_{\rm DD}$ . The rise delay time  $T_{\rm PLH}$  for the output voltage  $V_o$  and the initial delay time  $t_{dri}$  for any output voltage  $V_{oj}$ are also indicated in Fig. 2.

During the rise time period  $T_R$ , the operating region of each MOSFET can be determined from its drain-source voltage  $V_{\rm DS}$  and drain-source saturation voltage  $V_{\rm DSAT}$  generated from its corresponding gate-source voltage  $V_{\rm GS}$  and drain-source voltage  $V_{\rm DS}$ . From the simulated curves in Fig. 2, it is found that the MOSFET's  $M_{\rm p31},\ M_{\rm p21},\ M_{\rm p1},\ M_{\rm n44},\ M_{\rm n43},\ M_{\rm n42},\ M_{\rm n33},\ M_{\rm n32},\ {\rm and}\ M_{\rm n22}$  in the series branches of the driver stage are mostly operated in the linear region during  $T_R$ . This is because they all have a smaller  $V_{\rm DS}$  during  $T_R$ . The driven PMOSFET  $M_{\rm p41}$  has a gate-source voltage  $V_i$

Fig. 2. Typical rise characteristic waveforms of a CMOS 4-3-2-1-input AOI gate.

$V_{\rm DD}$  and a drain-source voltage  $V_{\rm o3}-V_{\rm DD}$ . The trajectory of  $V_{\rm DD}-V_{\rm DSATP}$  has an intersection point with the curve of  $V_{\rm o3}$  as shown in Fig. 2. According to our observations, this intersection point is located outside the rise time region for typical AOI gates even when the device channel length is down to 1.5  $\mu$ m. This means that during  $T_R$  the drain-source voltage  $|V_{\rm DD}-V_{\rm o3}|=|V_{\rm DS}|$  is always smaller than  $V_{\rm DSATP}$  in the PMOSFET  $M_{\rm p41}$ . Thus it is operated in the linear region during  $T_R$  and in those complex AOI gates only the linear-region current is involved in deriving the formula of  $T_R$ . This is true for AOI/OAI gates with long-channel and small-geometry MOSFET's.

Under the similar considerations, the PMOSFET  $M_{p41}$  of the load stage is mostly in the linear region during  $T_R$  whereas the NMOSFET  $M_{n41}$  of the load stage is mostly in the saturation region. Both devices in the load stage are treated as a capacitive load and their capacitances are calculated according to their operating regions.

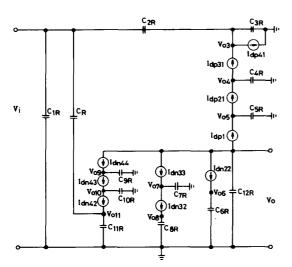

From the determined operating region and the large-signal equivalent circuit of each MOSFET, the overall large-signal equivalent circuit of the 4-3-2-1-input AOI gate during the characteristic rise time  $T_R$  can be built as shown in Fig. 3 where the load stage

Fig. 3. Large-signal equivalent circuit of a CMOS 4-3-2-1-input AOI gate during the rise time period.

is effectively represented by a capacitive load to the driver stage. Both the capacitive load and the fixed capacitor  $C_L$  are included in the capacitance  $C_{12R}$ .

The expressions of all the capacitances in the equivalent circuit are listed in Table I where the device capacitances  $C_{\rm gd}$ ,  $C_{\rm gs}$ , and  $C_{\rm gb}$  can be approximated by appropriate constant values [25] according to the operating region of the associated MOSFET. The voltage-dependent p-n junction reverse-bias capacitances  $C_{\rm bd}$  and  $C_{\rm bs}$  can also be approximated by their constant values calculated from the same formulas in SPICE [24] at the linearization point. The linearization point in this case is optimally determined at the center point with  $t=t_e$  where  $V_o(t_e)=V_{\rm DD}/2$ . All the other node voltages at the point can be found from the characteristic waveforms. After the above cited linearization procedure, all the capacitances listed in Table I become linear and have fixed values. Since the p-n junction reverse-bias capacitance is not a strong function (e.g., exponential function) of voltage, the linearization leads to a limited error.

The linear-region drain current used in the modified SPICE program is expressed in Table II. By applying the same technique [6], the voltage-dependent mobility and the nonlinear terms in the current expression can be linearized. The resultant expressions of the linearized drain currents in the equivalent circuit of Fig. 3 are listed in Table III. Note that the drain currents in the equivalent circuit are those of the linear region, the linearization thus does not lead to an unbearable error. With the linearized capacitances and drain currents, the equivalent circuit of Fig. 3 becomes a linear circuit.

Since the internal characteristic waveform in a digital circuit strongly depends upon the circuit structure rather than the input excitation, it can be well characterized by the poles and zeros of the corresponding equivalent circuit. In complicated circuits like CMOS AOI/OAI gates, they tend to have a dominant pole. Thus the signal timing can be analytically modeled from the dominant pole only. Dominant-pole calculation in the S domain, however, is too tedious in a complex logic gate. In this paper, the zero value time constant method [26] will be applied to simplify the dominant-pole calculation while obtaining a satisfactory result.

To compute the dominant pole of the equivalent circuit in Fig. 3, the input port is short circuited. Thus the output resistance looking into each capacitor with all others taken away can be found. The expressions of all the output resistances are given in Table IV. From these expressions, it can be seen that the effective resistances of each MOSFET, for example,  $M_{\rm p31}$ , in the associated output resistance expressions, for example,  $R_{4R}$ ,  $R_{5R}$ , and  $R_{12R}$ , are different.

TABLE I

THE EXPRESSIONS OF THE CAPACITANCES IN THE EQUIVALENT CIRCUIT USED FOR THE CHARACTERISTIC RISE TIME CALCULATION OF A CMOS 4-3-2-1-INPUT AOI GATE

TABLE II

DRAIN CURRENT EQUATION USED IN THE MODIFIED SPICE PROGRAM FOR A

MOSFET IN THE LINEAR REGION

$$\begin{split} &I_{DS} = \beta \{ (V_{GS} - V_{BIN} - \frac{\eta}{2} - V_{DS}) \cdot V_{DS} - \frac{2}{3} \gamma_s [ (2\phi_F + V_{DS} - V_{BS})^{3/2} - (2\phi_F - V_{BS})^{3/2} ] \} \\ &\rho = \frac{W}{L} \cdot \psi_s \cdot C_{OX} \\ &C_{OX} = \frac{{}^c \cdot S \cdot IO_2}{TOX} - \frac{UCR \cdot IT \cdot {}^c \cdot S_1}{UCR \cdot IT \cdot {}^c \cdot S_1} \\ &\mu_s = UO(\frac{UCR \cdot IT \cdot {}^c \cdot S_1}{C_{OX} | V_{GS} - V_{TH} - UTRA \cdot \min(V_{DS} \cdot 2\phi_F)|})^{UEXP} \\ &V_{TH} = V_{BIN} + \gamma_s \cdot (2\phi_F - V_{BS})^{1/2} \\ &V_{BIN} = V_{BI} + (\eta - 1) \cdot (2\phi_F - V_{BS}) \\ &V_{BI} = V_{TO} - GAMMA \cdot (2\phi_F)^{1/2} \\ &\eta = 1 + \frac{\pi \cdot DELTA \cdot \cdot \cdot S_1}{4 \cdot C_{OX} \cdot W} \\ &\gamma_s = GAMMA \cdot (1 - \alpha_S - \alpha_D) \\ &\alpha_S = \frac{1}{2} \cdot \frac{XJ}{L} \cdot [(1 + \frac{2 \cdot W}{XJ})^{1/2} - 1] \\ &\alpha_D = -\frac{1}{2} \cdot \frac{XJ}{L} \cdot [(1 + \frac{2 \cdot W}{XJ})^{1/2} - 1] \\ &W_S = XD \cdot (2\phi_F - V_{BS})^{1/2} \\ &W_D = XD \cdot (2\phi_F - V_{BS} + V_{DS})^{1/2} \\ &XD = (\frac{2 \cdot \cdot \cdot S_1}{4 \cdot VSUB})^{1/2} \end{split}$$

It is not adequate, therefore, to use a fixed resistance to represent an MOSFET in a logic gate.

According to the zero value time constant method, the characteristic rise pole  $P_r$  can be expressed as

$$P_{r} = \left[ R_{23R} (C_{2R} + C_{3R}) + R_{4R} C_{4R} + R_{5R} C_{5R} + R_{6R} C_{6R} + R_{7R} C_{7R} + R_{8R} C_{8R} + R_{9R} C_{9R} + R_{10R} C_{10R} + R_{11R} (C_{11R} + C_{R}) + R_{12R} C_{12R} \right]^{-1}.$$

(1)

#### TABLE III

THE EXPRESSIONS OF THE LINEARIZED DRAIN CURRENTS IN THE EQUIVALENT CIRCUIT USED FOR THE CHARACTERISTIC RISE TIME CALCULATION OF A CMOS 4-3-2-1-INPUT AOI GATE

$X_{kD} = \left[ -V_{Gk} + V_{BINk} - \frac{2}{3} Y_{Sk} (|2\phi_{Fk}| + V_{Bk} - V_{Dk})^{1/2} + \frac{n_k}{3} Y_{Dk} \right]_{k=10}$

THE EXPRESSIONS OF THE OUTPUT RESISTANCES LOOKING INTO THE CAPACITOR PORTS IN THE EQUIVALENT CIRCUIT OF A CMOS 4-3-2-1-INPUT AOI GATE

$$\begin{split} R_{23R} &= \frac{1}{\beta_{p41} X_{p41D}} \\ R_{4R} &= \frac{1}{\beta_{p31} X_{p31D}} + \frac{X_{p31S}}{X_{p31D}} \frac{1}{\beta_{p41} X_{p41D}} \\ R_{5R} &= \frac{1}{\beta_{p21} X_{p21D}} + \frac{X_{p21S}}{X_{p21D}} \frac{1}{\beta_{p31} X_{p31D}} + \frac{X_{p21S} X_{p31S}}{X_{p21D} X_{p31D}} \frac{1}{\beta_{p11} X_{p41D}} \\ R_{12R} &= \frac{1}{\beta_{p1} X_{p1D}} + \frac{X_{p1S}}{X_{p1D}} \frac{1}{\beta_{p21} X_{p21D}} + \frac{X_{p1S} X_{p21D} X_{p31D}}{X_{p1D} X_{p21D}} + \frac{X_{p1S} X_{p21D} X_{p31D}}{X_{p1D} X_{p21D} X_{p31D}} \\ &+ \frac{X_{p1S} X_{p21S} X_{p31S}}{X_{p1D} X_{p21D} X_{p31D}} \frac{1}{\beta_{p41} X_{p41D}} \\ R_{6R} &= \frac{1}{\beta_{n32} X_{n32S}} + \frac{X_{n32D}}{X_{n32S}} R_{12R} \\ R_{7R} &= \frac{1}{\beta_{n33} X_{n33S}} + \frac{X_{n33D}}{X_{n33S}} \frac{1}{\beta_{n33} X_{n33S}} + \frac{X_{n32D} X_{n33D}}{X_{n32S} X_{n33S}} R_{12R} \\ R_{9R} &= \frac{1}{\beta_{n44} X_{n44S}} + \frac{X_{n44D}}{X_{n44S}} R_{12R} \\ R_{10R} &= \frac{1}{\beta_{n42} X_{n42S}} + \frac{X_{n43D}}{X_{n43S}} \frac{1}{\beta_{n44} X_{n44S}} + \frac{X_{n43D} X_{n44D}}{X_{n44S} X_{n43S}} R_{12R} \\ R_{11R} &= \frac{1}{\beta_{n42} X_{n42S}} + \frac{X_{n42D}}{X_{n42S}} \frac{1}{\beta_{n43} X_{n43S}} + \frac{X_{n42D} X_{n43D}}{X_{n42S} X_{n43S}} \frac{1}{\beta_{n44} X_{n44S}} \\ &+ \frac{X_{n42D} X_{n43D} X_{n44D}}{X_{n42S} X_{n43S} X_{n44S}} R_{12R} \\ &+ \frac{X_{n42D} X_{n43D} X_{n44D}}{X_{n42S} X_{n43S} X_{n44S}} R_{12R} \end{aligned}$$

Because the output voltage is assumed to have a single-pole response, the characteristic rise time  $T_R$  can be written as

$$T_R = \ln 9/P_r. \tag{2}$$

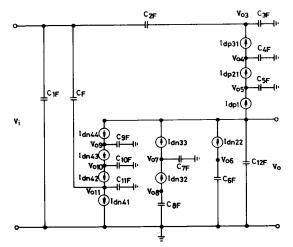

Similarly, the large-signal equivalent circuit for the characteristic fall time calculation can be obtained as shown in Fig. 4. The characteristic fall pole  $P_f$  and fall time  $T_F$  can be written as

$$P_{f} = \left[ R_{23F} (C_{2F} + C_{3F}) + R_{4F} C_{4F} + R_{5F} C_{5F} + R_{6F} C_{6F} + R_{7F} C_{7F} + R_{8F} C_{8F} + R_{9F} C_{9F} + R_{10F} C_{10F} + R_{11F} (C_{11F} + C_{F}) + R_{12F} C_{12R} \right]^{-1}$$

$$(3)$$

$$T_{f} = \ln 9 / P_{f}.$$

Both  $P_r$  and  $P_f$  are nonlinear equations of  $P_r/P_f$ . However, they can be easily solved by using numerical iterations.

The rise propagation delay  $T_{\rm PLH}$  as defined in Fig. 2 can be expressed as

$$T_{\text{PLH}} = t_{\text{dr}} + \frac{\ln 2}{\ln 9} T_R - \frac{\ln 2}{\ln 9} T_F.$$

(5)

For simplicity, empirical laws for the initial delay times  $t_{\rm dr}$  and  $t_{\rm df}$  were found. As a result, the rise propagation delay  $T_{\rm PLH}$  and the pair delay  $T_{\rm P}$  can be reformulated by the simple relations

$$T_{\rm PLH} = 0.8T_R - 0.15T_F \tag{6}$$

$$T_P = T_{PLH} + T_{PHL} = 0.3T_R + 0.7T_F.$$

(7)

Note that the above equations are universal and can be used to calculate the delay times for various AOI gates with satisfactory

Fig. 4. Large-signal equivalent circuit of a CMOS 4-3-2-1-input AOI gate during the fall time period.

accuracy, as will be verified in the following section. It can be realized that the delay equations (6) and (7) are universal only when  $T_R$  and  $T_F$  are calculated from the derived formulas.

For the 4-3-2-1-input AOI gate under nonworst-case timing condition, the input voltage  $V_i$  drives an NMOSFET and a PMOSFET other than  $M_{\rm n41}$  and  $M_{\rm p41}$ , respectively. The delay times can be similarly modeled but with different capacitances and currents.

In the PMOSFET part of the 4-3-2-1-input AOI gate, there are four different branches each with 1, 2, 3, or 4 PMOSFET's in parallel. The four branches can be connected in series to form 24 different configurations. The delay times of these different AOI gates can be characterized by using the developed modeling technique. Besides the 4-3-2-1-input AOI gate with 24 different configurations, the modeling technique can also be applied to other AOI gates with less than 4 NMOSFET's or 4 PMOSFET's in series. The timing models for all these AOI gates have been built with the delay time equations of (6) and (7).

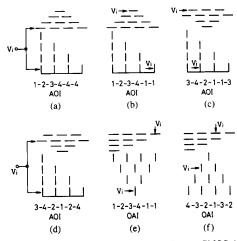

A six-digit code is designed to represent various AOI gates for easy identification. Each of the first four most significant digits (MSD's) represents the number of parallel PMOSFET's in a branch. The branch farthest to the output node corresponds to the first MSD and so on. The fifth digit is used to denote the position of the PMOSFET branch driven by the input voltage. The driven PMOSFET branch farthest to the output node is denoted as 1 whereas that nearest to the output node as 4. The sixth digit denotes the position of the driven NMOSFET in a series NMOSFET branch. Starting with 1 for the top MOSFET, each of the lower MOSFET's is assigned to a successively larger number. According to the above description, the AOI gate in Fig. 1 can be represented by 4-3-2-1-1-4. More examples are given in Fig. 5(a)-(d) where the AOI gates are shown by the symbolic diagrams. A similar code system is used to represent OAI gates. Two examples are given in Fig. 5(e) and (f)

A 4-3-2-1-input OAI gate under the worst-case timing condition is shown in Fig. 6 where the input voltage drives the MOSFET's  $M_{\rm n41}$  and  $M_{\rm p41}$ . Similar to the AOI gates, the NMOSFET branches in series can be arranged to form 24 different configurations. For all these different configurations of OAI gates and other simpler OAI gates with less than 4 PMOSFET's or 4 NMOSFET's in series, the worst-case and the nonworst-case timing can be characterized by applying the same modeling technique. The timing models for all these OAI gates have been built. The universal delay time equations for the OAI gates are

$$T_{\rm PLH} = 0.8T_{R} - 0.25T_{F} \tag{8}$$

$$T_P = 0.4T_R + 0.6T_F \tag{9}$$

Fig. 5. Symbolic diagrams and six-digit codes of some CMOS AOI/OAI gates.

where  $T_R$  and  $T_F$  are the calculated characteristic rise and fall times of OAI gates, respectively.

Note that the developed timing modes can be applied to CMOS AOI/OAI gates with both long-channel and small-geometry devices, because a small-geometry AOI/OAI gate has an inherent output voltage waveform nearly independent of the device channel lengths and its timing can be characterized similarly as in the long-channel case. However, this similarity does not exist in simple CMOS inverters, and NAND/NOR gates [6], [22].

# III. COMPARISONS WITH SPICE SIMULATIONS

To verify the accuracy of the developed analytical timing models, extensive comparisons between theoretical calculations and SPICE simulations were made for the AOI/OAI gates with different configurations, device sizes, device parameters, capacitive loads, and input excitations. Fig. 7(a) shows the 3.5- $\mu$ m CMOS 3-2-1-0-1-3 AOI gates with  $C_L = 5.0$  pF and normal device parameters, whereas Fig. 7(b) shows the 4-3-2-1-1-4 OAI gates with  $C_L = 0$  pF and  $V_{TON}$  reduced to 0.3 V. It is found that the maximum error is 30% in the calculated delay times for the AOI/OAI gates with fixed load capacitors.

The input waveform effect on the output signal timing is incorporated into our model through the term  $V_{\rm GS} \cdot V_{\rm DS}$  in the drain-current expression of the driven MOSFET's. For example, the rise time calculation of the AOI gate as shown in Fig. 1, the drain current  $I_{\rm dp41}$  of the driven PMOSFET  $M_{\rm p41}$  has a term  $V_{\rm GS} \cdot V_{\rm DS}$  which is related to  $V_i \cdot V_{\rm o3}$  and then is linearized as  $V_i \cdot (t_e) \cdot V_{\rm o3} \cdot (t)$ . Since  $t_e$  is related to the output rise pole  $P_r$  and  $V_i$  to the input fall pole  $P_f$ , the term  $V_i \cdot (t_e)$  in  $X_{\rm p41D}$  of the resultant linearized drain current  $I_{\rm p41}$  and all the resistances is a function of  $P_f/P_r$  as may be seen from Tables III and IV. Finally, the output rise pole  $P_r$  becomes a function of the input fall pole  $P_f$  and the input waveform effect is included. Thus the developed model can predict the output responses under noncharacteristic input waveform excitations.

Table V shows the  $3.5 \mu m$  CMOS 1-2-3-4-4-2 AOI gates driven by the step input and the input waveforms with rise and fall times two times as large as those in the characteristic waveform case. The ability to calculate the noncharacteristic waveform timing makes the developed models more practical and versatile in computing the timing of CMOS AOI/OAI gates.

There is a compromise between the model accuracy and the applicable ranges of the models. Thus the maximum error of 30% can be reduced if the model applicable range is slightly confined to those gates with commonly used device dimensions. For example, the maximum error of delay times for the CMOS AOI gates with

Fig. 6. A chain of identical CMOS 4-3-2-1-input OAI gates under the worst-case timing condition.

Fig. 7. Calculated and simulated rise/pair delay of (a) the 3.5- $\mu$ m CMOS 3-2-1-0-1-3 AOI gates with normal parameters; (b) the 3.5- $\mu$ m CMOS 4-3-2-1-1-4 OAI gates with a reduced  $V_{\rm TON}$  to 0.3 V.

commonly used device dimensions can be reduced to 16% by properly tuning the universal constants in (6) and (7). The tuned results are

$$T_{\rm PLH} = 0.9T_R - 0.11T_F \tag{10}$$

TABLE V CALCULATED AND SIMULATED TIMING DATA OF CMOS 1-2-3-4-4-2 AOI GATES WITH  $W_P/W_N=4~\mu {\rm m}/3.5~\mu {\rm m}$  and  $L_{\rm mask}=3.5~\mu {\rm m}$

| Input<br>Excitation               | C <sub>L</sub><br>(pf) | Data Type   | T <sub>R</sub> | TPLH   | $	au_{	ext{F}}$ | T <sub>PHL</sub> |

|-----------------------------------|------------------------|-------------|----------------|--------|-----------------|------------------|

|                                   |                        | THEORY (ns) | 26,28          | 21.02  | 4.86            | 4.13             |

| Step                              | 0                      | SPICE (ns)  | 28.80          | 25.30  | 6.45            | 4.52             |

|                                   |                        | ERROR (%)   | -8.75          | -16.90 | -24.60          | -8.63            |

|                                   | 5                      | THEORY (ns) | 666            | 532.8  | 141             | 133.95           |

|                                   |                        | SPICE (ns)  | 830            | 581    | 198             | 138.6            |

|                                   |                        | ERROR (%)   | -19.7          | -8.30  | -28.80          | -3.35            |

| Rise Time                         | 0                      | THEORY (ns) | 30.35          | 20.88  | 22.80           | -8.80            |

| =56.3 ns<br>Fall Time<br>=25.32ns |                        | SPICE (ns)  | 28.10          | 29.40  | 18              | -7.20            |

|                                   |                        | ERROR (%)   | +8.00          | -29    | +26.60          | -22              |

| Rise Time<br>=1660ns              |                        | THEORY(ns)  | 856.6          | 575    | 602             | -318.3           |

|                                   | 5                      | SPICE (ns)  | 855            | 640.5  | 465             | -248             |

| Fall Time<br>=736 ns              |                        | ERROR (%)   | +0.19          | -10.2  | +29.4           | -29.7            |

$$T_P = 0.46T_R + 0.66T_F. (11)$$

Similarly, the tuned equations for the CMOS OAI gates are

$$T_{\rm PLH} = 0.67T_R - 0.33T_F \tag{12}$$

$$T_P = 0.45T_R + 0.72T_F. (13)$$

As expected, the developed timing models can also be applied to complex small-geometry CMOS AOI/OAI gates. It is found that the maximum error is still 16% for various 1.5- $\mu$ m CMOS AOI/OAI gates with commonly used device dimensions. Part of comparisons are shown in Fig. 8(a) and (b) for 1.5- $\mu$ m CMOS AOI and OAI gates with  $C_L=0.0$  pF, respectively.

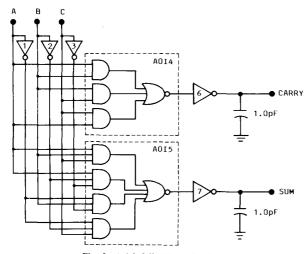

# IV. Applications of the Timing Models in Autosizing

To demonstrate the application of the developed timing models in autosizing, the timing models are implemented in an experimental autosizing program called the TIming Synthesis and Analysis

Fig. 8. Calculated and simulated rise/pair delay of (a) the 3.5-μm CMOS 4-3-2-1-1-4 AOI gates; (b) the 1.5-μm CMOS 4-3-2-1-1-4 OAI gates.

Fig. 9. A 1-b full adder to be sized.

(TISA) Program [6]. In the TISA, two popular CMOS design strategies are adopted in synthesizing the device sizes. One strategy is that all the same type of MOSFET's in series in a logic gate are designed with equal channel widths and so are all MOSFET's in parallel [10]. The other is that only the input excitation pattern which leads to the worst-case timing of a logic gate is considered in sizing. This results in a save design so that the actual chip delay is always smaller than that synthesized. Under these two strategies, the optimal device sizes which lead to the minimum total delay time can be obtained by solving the developed timing equations through the numerical optimization algorithm [27].

As shown in Fig. 9, a 1-b full adder is designed. The synthesized device sizes are listed in Table VI. Table VII lists the comparisons between SPICE simulations and model calculations under

TABLE VI

THE DEVICE SIZES OF THE FULL ADDER IN FIG. 9 SYNTHESIZED BY USING

THE TISA PROGRAM WITH THE MINIMUM TOTAL DELAY TIME

| a .   | Dimension                        |                |  |  |

|-------|----------------------------------|----------------|--|--|

| Gates | $W_{\mathbf{P}}(\mu \mathbf{m})$ | $W_{N}(\mu m)$ |  |  |

| INV1  | 10.5                             | 3.5            |  |  |

| INV2  | 10.5                             | 3.5            |  |  |

| INV3  | 10.5                             | 3.5            |  |  |

| A014  | 11.5                             | 3.5            |  |  |

| A015  | 100                              | 35             |  |  |

| INV6  | 19.5                             | 6.0            |  |  |

| INV7  | 268                              | 84             |  |  |

$TABLE\ VII$  Comparisons of Timing Data for the Full Adder in Fig. 9 with the Device Sizes in Table VI

| Total Delay Time (ns) |       |          |        |       |          |  |  |

|-----------------------|-------|----------|--------|-------|----------|--|--|

| CARRY                 |       |          | SUM    |       |          |  |  |

| THEORY                | SPICE | ERROR(%) | THEORY | SPICE | ERROR(%) |  |  |

| 4.60                  | 4.15  | 10.8     | 6.22   | 5.80  | 7.2      |  |  |

the consideration that the input pattern ABC changes from 100 to 110. It is found that the error is 10.8 and 7.2% for the outputs CARRY and SUM.

### V. Conclusion

Efficient physical timing models for complex 1.5- and 3.5- $\mu$ m CMOS AOI/OAI gates have been successfully developed to calculate the signal timing without performing troublesome SPICE transient simulations. Under the characteristic waveform consideration, the rise time and fall time equations in the developed models are first derived from the dominant pole of the linearized large signal equivalent circuit of the gate. To efficiently find the dominant pole, the zero value time constant method [26] is adopted. Universal laws are then found to calculate the delay times from the calculated rise and fall times.

Extensive comparisons between theoretical computations and SPICE simulations were made. It is found that the developed timing models have a maximum error of 30% in calculating the signal timing of the CMOS AOI/OAI gates with wide ranges of device dimensions, capacitive loads, device parameter variations, logic input patterns, and input excitation waveforms not deviating much from the characteristic. The same maximum error is found in the timing calculations of all different configurations of the CMOS AOI/OAI gates with less than 4 NMOSFET's or 4 PMOSFET's in series. However, the model error can be further tuned to 16% for 1.5 and 3.5-µm CMOS AOI/OAI gates with commonly used device dimensions

The application of the developed timing models in autosizing has also been demonstrated successfully. With the aid of the developed timing models, the sized gates can have a much less deviation in delay times from the simulated values. This gives a more correct design than the case of using a rough timing model. The consumed CPU time is still in the reasonable range.

### ACKNOWLEDGMENT

The authors would like to thank reviewers for their critical reading of the manuscript and helpful suggestions.

#### REFERENCES

- [1] E. Seewann, "Switching speed of MOS inverters," *IEEE J. Solid-State Circuits*, vol. SC-15, pp. 246-252, Apr. 1980.

- State Circuits, vol. SC-15, pp. 246-252, Apr. 1980.

[2] L. A. Glasser, "The analog behavior of digital integrated circuits," in Proc. 18th Design Automation Conf., 1981, pp. 603-612.

- [3] J. G. Simmons and G. W. Taylor, "An analytical treatment of the performance of submicrometer FET logic," *IEEE J. Solid-State Cir*cuits, vol. SC-20, pp. 1242-1251, Dec. 1985.

- [4] P. Subramaniam, "Modeling MOS VLSI circuits for transient analysis," *IEEE J. Solid-State Circuits*, vol. SC-21, pp. 276-285, Apr. 1986.

- [5] J. K. Ousterhout, "A switch-level timing verifier for digital MOS VLSI," *IEEE Trans. Computer-Aided Design*, vol. CAD-4, pp. 336–349, July 1985.

- [6] C.-Y. Wu, J.-S. Hwang, C. Chang, and C.-C. Chang, "An efficient timing model for CMOS combinational logic gates," *IEEE Trans. Computer-Aided Design*, vol. CAD-4, pp. 636-650, Oct. 1985.

[7] C.-Y. Wu and J.-S. Hwang, "Efficient timing models for character-

- [7] C.-Y. Wu and J.-S. Hwang, "Efficient timing models for characteristic waveforms of CMOS logic gates," in *Proc. 27th Midwest Symp.* on *Circuits and Systems*, June 1984, pp. 574-578.

- [8] N. Jouppi, "TV: An NMOS timing analyzer," in Proc. 3rd Callech, Conf. on VLSI, Mar. 1983, pp. 71-86.

- [9] T. Tokuda, K. Okazaki, K. Sakashita, I. Ohkura, and T. Enomoto, "Delay-time modeling for ED MOS logic LSI," *IEEE Trans. Computer-Aided Design*, vol. CAD-2, pp. 129-134, July 1983.

[10] J. A. Pretorius, A. S. Shubat, and C. A. T. Salama, "Analysis and

- [10] J. A. Pretorius, A. S. Shubat, and C. A. T. Salama, "Analysis and design optimization of domino CMOS logic with application to standard cells," *IEEE J. Solid-State Circuits*, vol. SC-20, pp. 523-530, Apr. 1985.

- [11] R. J. Bayruns, R. L. Johnston, D. L. Fraser, Jr., and S. C. Fang, "Delay analysis of Si NMOS bit/s logic circuits," *IEEE J. Solid-State Circuits*, vol. SC-19, pp. 755-764, Oct. 1984.

- [12] D. Auvergne, G. Cambon, D. Deschacht, M. Robert, G. Sagnes, and V. Tempier, "Delay-time evaluation in ED MOS logic LSI," *IEEE J. Solid-State Circuits*, vol. SC-21, pp. 337-342, Apr. 1986.

- [13] E. Tamura, K. Ogawa, and T. Nakano, "Path delay analysis for hierarchical building block layout system," in *Proc. 20th Design Automation Conf.*, pp. 403-410, June 1983.

- [14] A. Kanuma, "CMOS circuit optimization," Solid-State Electron., vol. 26, pp. 47-58, Jan. 1983.

- [15] D. Etiemble, V. Adeline, N. H. Duyet, and J. C. Ballegeer, "Microcomputer oriented algorithms for delay evaluation of MOS gates," in *Proc. 21st Design Automation Conf.*, 1984, pp. 358-364.

- [16] N. Hedenstierna and K. O. Jeppson, "CMOS circuit speed and buffer optimization," *IEEE Trans. Computer-Aided Design*, vol. CAD-6, pp. 270-281, 1987.

- [17] M. D. Matson and L. A. Glasser, "Macromodeling and optimization of digital MOS VLSI circuits," *IEEE Trans. Computer-Aided De*sign, vol. CAD-5, pp. 659-678, Oct. 1986.

- [18] C. Y. Wu and Y. T. Lin, "A new general method to model signal timing of E/D NMOS logic," Int. J. Circuit Theory Appl., vol. 17, pp. 447-464, Oct. 1988.

- [19] C. Y. Wu and M. C. Shiau, "A new interconnection delay model considering the effects of short-channel logic gates," in *Proc. IEEE Int. Symp. on Circuits and Systems*, June 1988, pp. 2847-2850.

- [20] M. C. Shiau and C. Y. Wu, "The signal delay in interconnection lines considering the effects of small-geometry CMOS inverters," to be published in *IEEE Trans. Circuits Syst.*, 1990.

- [21] C. Y. Wu and J. S. Hwang, "A new autosizing algorithm for CMOS combinational logic circuits," in Proc. Int. Symp. on VLSI Technology, Systems and Applications, May 1989, pp. 242-246.

- [22] —, "Physical timing models of small-geometry CMOS inverters and multi-input NAND/NOR gates and their applications," Solid-State Electron., vol. 32, pp. 449-467, 1989.

- [23] J. R. Pfiester, J. D. Shott, and J. D. Meindl, "Performance limits of CMOS ULSI," *IEEE J. Solid-State Circuits*, vol. SC-20, pp. 253-263. Feb. 1985.

- [24] A. Vladimirescu and S. Liu, "The simulation of MOS integrated circuits using SPICE2," Electronic Res. Lab. Memo. VCB/ERL-M80/70, Univ. California, Berkeley, Oct. 1980.

- [25] M. I. Emasry, "Digital MOS integrated circuits: A tutorial," in Digital MOS Integrated Circuits. New York: IEEE Press, pp. 4-27, Mar. 1981.

- [26] P. R. Gray and R. G. Meyer, Analysis and Design of Analog Integrated Circuits. New York: Wiley, 1977.

- [27] P. E. Gill, W. Murray, and M. H. Wright, Practical Optimization. New York: Academic, 1981, pp. 99.

# **Detection of Multiple Faults in MOS Circuits**

### F. JOEL FERGUSON

Abstract—This paper characterizes test sets that detect multiple faults in MOS circuits guided by the observation that such circuits are implemented as networks of switches. This leads to a conceptually simple technique for generating multiple fault test sets. Sufficient conditions for the detection of all multiple faults are given for switch networks, and it is shown that a test set exists meeting these conditions for any irredundant circuit with certain restrictions on fan out. In the cases where these conditions cannot be met, a class of "robust" test sets is presented. Test sets are presented that generate complete multiple fault test sets with fewer vectors for many MOS complex gates than is possible using a gate-level description of the circuit.

### I. Introduction

Recently, there has been much interest in modeling faults in MOS circuits at the circuit level due to the inability of logic-level fault models to adequately characterize their faulty behavior [1]-[3]. Wadsack [1] showed that transistor-stuck faults in MOS, especially CMOS, circuits can cause sequential behavior in a combinational circuit. Galiay et al. [2] showed that many faults in MOS circuits cannot be modeled by the gate-level single-line stuck-at-0/1 fault (SSF) model, implying that many actual faults may not be detected by SSF test sets.

Multiple faults are possible and probable due to a single fabrication defect [3]-[5]. Three percent of all single defects that were simulated in [5] caused multiple faults. The distribution of defect sizes in that study was inversely proportional to the cube of the defect radius and only defects of a radius less than 4  $\mu$ m were considered. Since defects often appear in clusters [6] and are often more than 4  $\mu$ m in radius, the likelihood of multiple faults in physical circuits is even greater than indicated in [5].

There has been considerable research in detecting multiple-line stuck-at faults (MSFS) in gate-level circuits. Gault et al. [7] detailed several circuit structures in which any complete SSF test set is a complete MSF test set, characterized conditions that one component of a multiple fault can mask another, and set limits on the number of tests necessary for a complete MSF test set for some classes of circuits. Schertz and Metze [8] developed equivalence classes to determine possible masking relationships among faults. Agarwal and Fung [9] set bounds on the percentage of multiple faults detected by SSF test sets, and Hughes [10] presented experimental data concerning the percentage of multiple faults detected by SSF test sets. Other gate-level research focused on algebraic techniques for generating MSF test sets [11], [12].

El-ziq and Su [13] developed test procedures for the detection of all multiple transistor stuck faults for a specific class of complex gates with fan-out free inputs. Jha developed a procedure based

Manuscript received September 12, 1988; revised May 8, 1989 and September 6, 1989. This work was supported in part by the Semiconductor Research Corporation under Contracts SRC-83-01-022 and 89-DJ-141. This paper was recommended by Associate Editor V. K. Agarwal.

The author is with the Computer Engineering Department, University of California at Santa Cruz, Santa Cruz, CA 95064.

IEEE Log Number 9036171.