# 國 立 交 通 大 學 電控工程研究所 博 士 論 文

# 單級並聯型升壓返馳式轉換器

- 研究生:李恆毅

- 指導教授:張隆國 博士

- 陳鴻祺 博士

中華民國九十九年五月

單級並聯型升壓返馳式轉換器

Single-Stage Parallel Boost-Flyback Converter

| 研 | 究 | 生  | : | 李 | 恆 | 毅 |    | Student: | Heng-Yi Li        |

|---|---|----|---|---|---|---|----|----------|-------------------|

| 指 | 導 | 教授 | : | 張 | 隆 | 國 | 博士 | Advisor: | Dr. Lon-Kou Chang |

|   |   |    |   | 陳 | 鴻 | 褀 | 博士 |          | Dr. Hung-Chi Chen |

Submitted to Institute of Electrical Control Engineering

College of Electrical Engineering

National Chiao Tung University

in Partial Fulfillment of the Requirements

for the Degree of

Doctor of Philosophy

in

**Electrical Engineering**

May 2010

Hsinchu, Taiwan, Republic of China.

中華民國九十九年五月

# 單級並聯型升壓返馳式轉換器

研究生:李恆毅 指導教授:張隆國 博士/ 陳鴻祺 博士

國立交通大學電控工程研究所

#### 摘要

無論單級式或兩級式交直流轉換器,均有部份電能會重覆處理或循 環。因此,本論文應用了並聯式功因校正的概念,提出了一種嶄新的單級 並聯式功率因數校正設計。此設計係利用升壓-返馳半級(包括升壓單元和 返馳單元)產生兩條並聯電能處理路徑。主要的輸入功率經反馳單元轉換 後即輸出至負載,而剩餘的功率經升壓單元處理,再儲入大型電容,然後 被直流-直流半級取出作為輸出功率調節。理論分析證實,只要升壓單元和 反馳單元運轉於非連續模式,且工作週期和切換頻率維持固定,減少升壓 電感可提昇功率因數。因大部份功率僅經一次處理,故轉換效率提高和開 關電流應力降低。在此架構中,可將返馳單元和直流-直流半級作不同電路 的替換,而衍生其它不同的轉換電路。

本論文以單級並聯式升壓-反馳-反馳轉換器為對象,分析電路的運轉模 式和各元件的平均切換週期信號,提出功率分配和大型電容電壓之影響參 數、設計方程式和設計程序。藉著遵循設計程序,一個 80 瓦泛用電壓的原 型被建置。實驗結果顯示,在使用範圍的最壞條件下,測得的諧波電流仍 符合 IEC61000-3-2 class D 限制,最高大型電容電壓為 415.4 伏特,最大轉 換效率達 85.8%。

從上述電路分析得知,轉換器在半個線週期也會有兩個操作模式,其 中之一模式,工作週期需隨著線電壓相位改變而改變以維持輸出恆定。這 種工作週期可變之轉換器的小信號轉移函數無法以傳統頻率響應量測證 實。因此,藉著建立各模式的小信號模型和提出模式分界點補償器的設計 方法,使轉換器的動態響應在操作範圍內具有較小的穩態誤差、快速上升 時間和大量阻尼。最後,並聯式轉換器的動態模型和所設計的補償器,以 模擬和實驗在時域內得以證實。

關鍵字:交直流轉換器,並聯式功因校正、返馳式轉換器。

i

# Single-Stage Parallel Boost-Flyback Converter

Student: Heng-Yi Li

Advisor: Dr. Lon-Kou Chang/ Dr. Hung-Chi Chen

### Institute of Electrical Control Engineering National Chaio Tung University

#### Abstract

It is known that part of the power is repeatedly processed or recycled in the conventional single-stage ( $S^2$ ) and two-stage AC/DC converters. Therefore, a novel  $S^2$  scheme is presented based on the parallel power factor correction (PPFC). In the scheme, the boost-flyback semi-stage containing boost cell and flyback cell is used to generate two energy processing path. The main input power flow stream is processed only by flyback cell and output to load directly. And the remaining input power stream is stored in bulk capacitor by boost cell and then transferred by DC/DC semi-stage to output for regulating output power. Theoretical analysis shows that as the boost cell and flyback cell operate in DCM and duty ratio and switching frequency are kept constant, using smaller boost inductor can result in higher power factor. Since most power is processed only once, the power conversion efficiency is improved and the current stress of control switch is reduced. The scheme can also be applied to other conversion circuits by replacing flyback cell and DC/DC semi-stage with other topology.

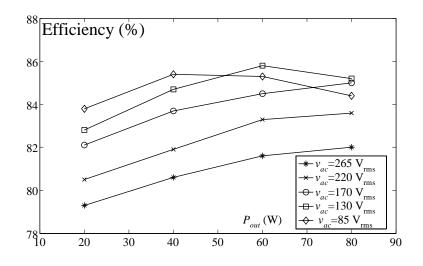

Taking the parallel boost-flyback-flyback converter as an example, the operation modes and average switching period signals are analyzed, the key parameters of power distribution and bulk capacitor voltage, design equations, and design procedure are also presented. By following the procedure, an 80 W universal prototype has been built and tested. The experimental results show that at the worst condition of operation range the measured line harmonic current complies with the IEC61000-3-2 class D limits, the maximum bulk capacitor voltage is about 415.4 V, and the maximum efficiency is about 85.8%.

It can be seen from the converter analysis, there are two operation modes in half line cycle and the duty ratio varied with line phase to keep output constant in one mode. The small signal transfer function of the converter with variable duty ratio cannot be validated with conventional frequency response measurement. Hence, the small-signal models of operation modes are built and the compensator design at the boundary of modes is presented, the dynamic response has small steady state error, fast rise time, and heavily damping within operation range. Finally, the dynamic model and designed compensator of parallel converter are verified in time domain by simulation and experiment.

Keywords: AC to DC converter, parallel power factor correction, flyback converter.

#### 誌 謝

本論文完成,使我有『黑夜將盡,黎明破曉』的感覺。感謝神在黑夜中的引導,以 及師長和同學的幫助。首先,要感謝我的指導教授張隆國博士,在前六年的研究生涯裡, 由於他的啟蒙和教導,並在邏輯思考與論文寫作方面下了不少苦心,使我能完成論文, 在此謹致最深忱的謝意與敬意。然後,還要感謝另一位指導教授陳鴻祺教授,在最後兩 年給予後續的指正及幫助,使我能順利畢業。另外,要感謝廖德誠教授的經驗傳授和精 神鼓勵,他的系統系性思考原則,幫助我化繁為簡,快速找到問題關鍵。感謝林君明教 授的鼓勵,他的引導式的發問,使我能澄清重要的基本觀念。感謝潘晴財教授和廖聰明 教授,也是令我景仰的學者,他們發表電源控制方面的著作對本研究極有幫助,而後續 的指正以及寶貴的建議,也使得本論文更加地完整。

在這八年的博士生涯裡,要特別感謝晏銘,在我研究初期,給予許多資料、建議和協助,使我得以快速地步上研究軌道。感謝基漳所提供的實務經驗與協助。感謝 815 實驗室的歷屆學長、同學及學弟,以及阿暉,在研究上所提供的建議與協助,還有許多生活上的幫忙。感謝如璇,與我一同奮戰,從 815 實驗室經 740 室到 613A 室,並給我許多寶貴的訊息。感謝 613A 室的廖振宇和其他同學。感謝世澤,常常幫我下載資料及提供信息。感謝田叔叔、寶珠阿姨、板橋市召會的治平、俊宏等,感謝你們在精神上的鼓勵。感謝推薦我來進修的核研所曾錦清博士和關心我的同事。

最後要感謝我的家人,尤其是我所敬愛的雙親,平常幫忙照顧小孩,由於他們的支 持與鼓勵,使我能全心全意的專注於功課與研究工作上。特別要感謝內人明珠對欣安、 欣柔和興仁的照顧,讓我無後顧之憂地在交大完成博士學位。謹將此研究成果與榮耀獻 給我的家人以及所有關心我的親朋好友!

李恆毅 2010 年初春

#### 于新竹交大

| Abstract (Chinese)                                              | i   |

|-----------------------------------------------------------------|-----|

| Abstract (English)                                              | ii  |

| Acknowledgements (Chinese)                                      | iii |

| Contents                                                        | iv  |

| List of Tables                                                  | vi  |

| List of Figures                                                 | vii |

| Notation                                                        | ix  |

| CHAPTER 1. INTRODUCTION                                         | 1   |

| 1.1 Background                                                  | 1   |

| 1.2 Motivation                                                  | 4   |

| 1.3 Contributions of the Dissertation                           | 5   |

| 1.4 Dissertation Outline                                        | 7   |

| CHAPTER 2. Synthesis of Single-Stage Parallel Converters        | 8   |

| 2.1 Review of Conventional Parallel AC-to-DC Converters         |     |

| 2.2 S <sup>2</sup> Parallel Boost-Flyback Converter             | 13  |

| 2.2.1 Principle                                                 | 13  |

| 2.2.2 SSTO Boost-Flyback Circuit                                | 16  |

| 2.3 New Family of Parallel Boost-Flyback Converter              | 19  |

| CHAPTER 3. ANALYSIS AND DESIGN OF A SINGLE-STAGE-SINGLE-SWITCH  |     |

| PARALLEL Boost-Flyback-Flyback CONVERTER                        | 21  |

| 3.1 Analysis of the Proposed Converter                          | 21  |

| 3.2 Power Distribution and Bulk Capacitor Voltage               | 32  |

| 3.3 Design Equations                                            |     |

| 3.4 Example and Design Procedure                                |     |

| 3.5 Experimental Results                                        | 42  |

| CHAPTER 4. MODELING AND CONTROL OF A SINGLE-STAGE-SINGLE-SWITCH |     |

| PARALLEL Boost-Flyback-Flyback CONVERTER                        |     |

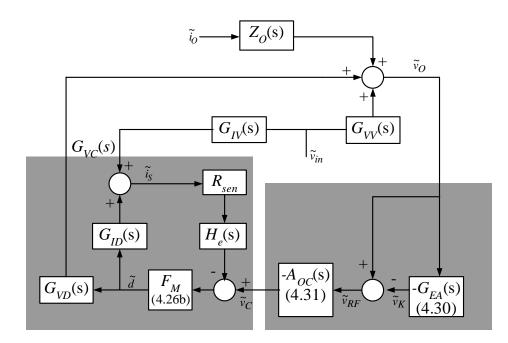

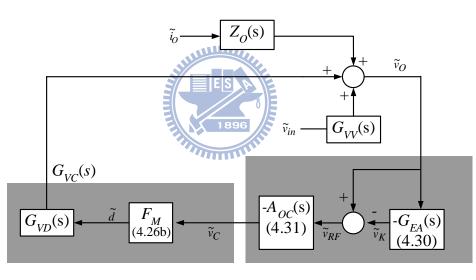

| 4.1 Small Signal Modeling                                       | 53  |

| 4.1.1 M <sub>1</sub> Mode                                       | 53  |

| 4.1.2 M <sub>2</sub> Mode                                       | 56  |

| 4.1.3 Current Mode Controller and Optocoupler Feedback          | 57  |

| 4.2 Controller Design                                           | 60  |

| 4.2.1 Model Uncertainty                                         | 60  |

# Contents

| 4.2.2 Controller Design                                 |    |

|---------------------------------------------------------|----|

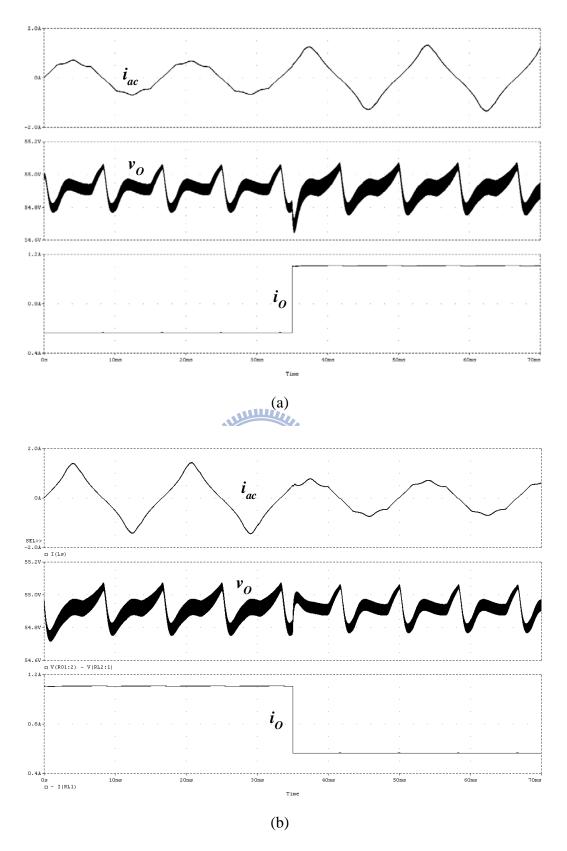

| 4.3 Simulation and Experimental Results                 | 64 |

| CHAPTER 5. CONCLUSIONS AND SUGGESTIONS FOR FURTHER WORK | 71 |

| 5.1 Conclusions                                         | 71 |

| 5.2 Suggestions for Further Work                        | 73 |

| REFERENCES                                              | 74 |

# List of Tables

| Table 1.1 | Limits for Class D equipment in standard IEC 61000-3-2           | 3  |

|-----------|------------------------------------------------------------------|----|

| Table 1.2 | Recently published S <sup>2</sup> approaches                     | 6  |

| Table 3.1 | Various operation modes in the proposed circuit                  |    |

| Table 3.2 | Various cases in the proposed circuit                            | 29 |

| Table 3.3 | The corresponding parameters of cases I-III illustration example |    |

| Table 3.4 | Indirect power ratio <i>K</i> <sub><i>IDP</i></sub>              | 35 |

| Table 3.5 | Parameters of critical components                                | 43 |

| Table 4.1 | Converter specifications and parameters of components            | 61 |

| Table 4.2 | Open loop poles and zero for various phases                      | 62 |

| Table 4.3 | Parameters of controller and optocoupler circuit                 | 64 |

| Table 4.4 | Gain crossover frequency and phase margin for various conditions | 64 |

| Table 4.5 | Measured power factor, load regulation, and ripple voltage       | 68 |

# List of Figures

| Fig. 1.1 | Two-stage AC/DC converter scheme                                                                                          |

|----------|---------------------------------------------------------------------------------------------------------------------------|

| Fig. 1.2 | Typical single-stage AC/DC converter scheme                                                                               |

| Fig. 1.3 | Parallel power factor correction converter scheme                                                                         |

| Fig. 1.4 | Power relationship of ideal PFC converter5                                                                                |

| Fig. 2.1 | Full bridge boost PPFC circuit [9-10]9                                                                                    |

| Fig. 2.2 | The parallel method with TIBuck converter: (a) Two-output flyback converter                                               |

|          | with TIBuck postregulator [12] and (b) equivalent circuit of TIBuck postregu-                                             |

|          | lator                                                                                                                     |

| Fig. 2.3 | Single switch parallel power factor correction AC/DC converter with inherent                                              |

|          | load current feedback11                                                                                                   |

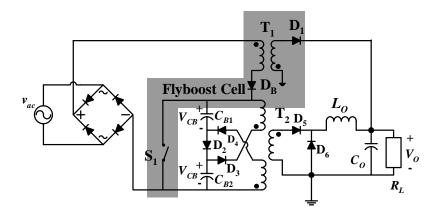

| Fig. 2.4 | Single-stage AC/DC converters with flyboost cell                                                                          |

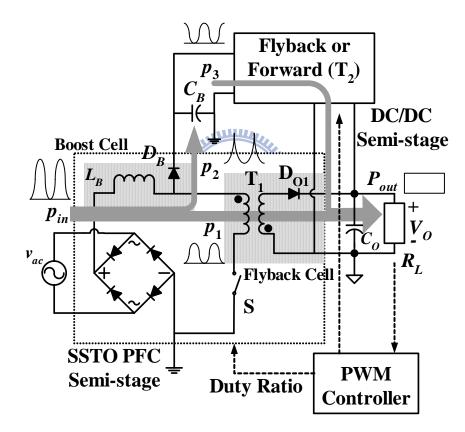

| Fig. 2.5 | Proposed S <sup>2</sup> PPFC scheme                                                                                       |

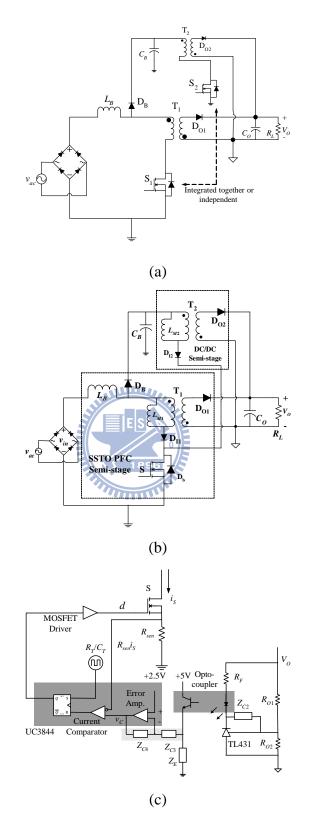

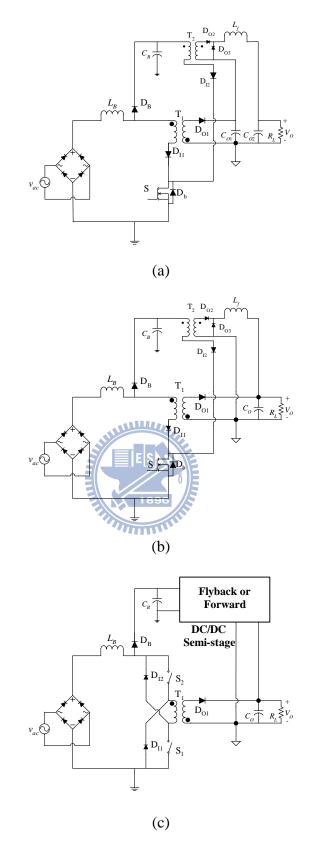

| Fig. 2.6 | S <sup>2</sup> Implementation circuit of parallel boost-flyback-flyback converter: (a)                                    |

|          | two-switch circuit, (b) single-switch circuit, and (c) feedback controller circuit.                                       |

|          |                                                                                                                           |

| Fig. 2.7 | SSTO boost-flyback converter: (a) circuit and (b) main waveforms                                                          |

| Fig. 2.8 | Derived topologies from proposed parallel scheme: (a) with forward semi-stage,                                            |

|          | (b) with TIBuck semi-stage, (c) $S^2$ boost-two-switch-flyback parallel con-                                              |

|          | verter scheme                                                                                                             |

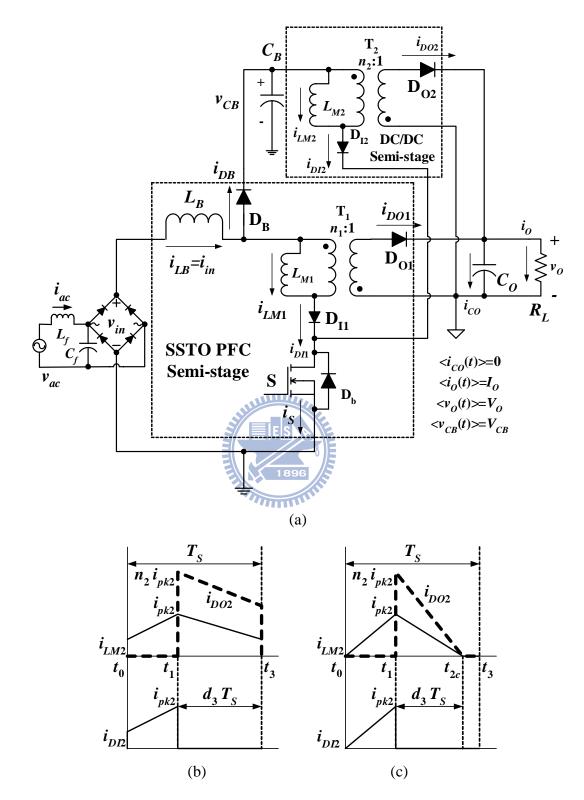

| Fig. 3.1 | Parallel boost-flyback-flyback converter: (a) Implementation circuit, (a)                                                 |

|          | DC/DC semi-stage waveform in $M_1$ mode, and (b) DC/DC semi-stage wave-                                                   |

|          | form in M <sub>2</sub> mode                                                                                               |

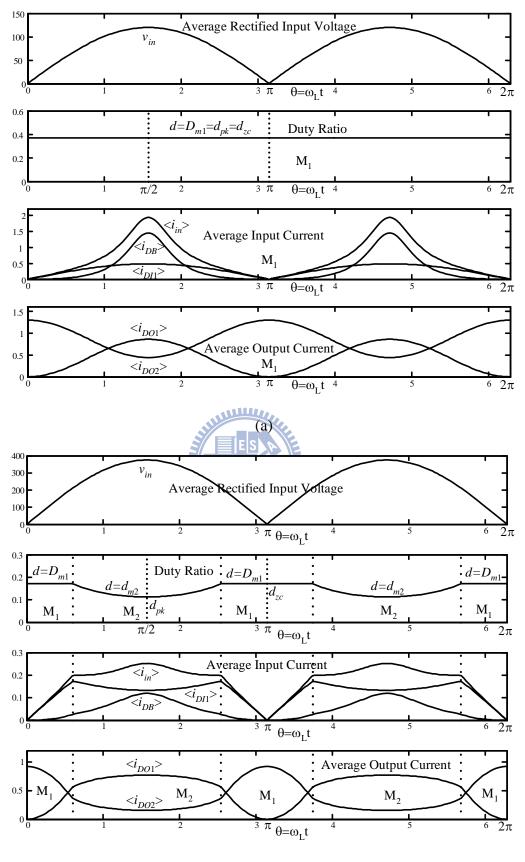

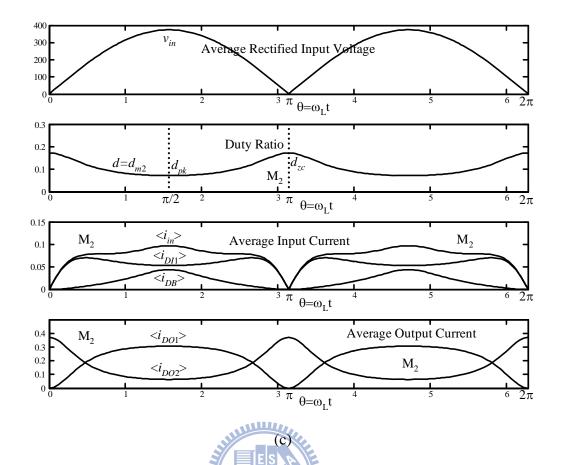

| Fig. 3.2 | Main waveforms of parallel boost-flyback-flyback converter in a line cycle: (a)                                           |

|          | case I ( $M_1$ mode only), (b) case II (both $M_1$ and $M_2$ modes), and (c) case III                                     |

|          | (M <sub>2</sub> mode only)                                                                                                |

| Fig. 3.3 | Average switch current for case I                                                                                         |

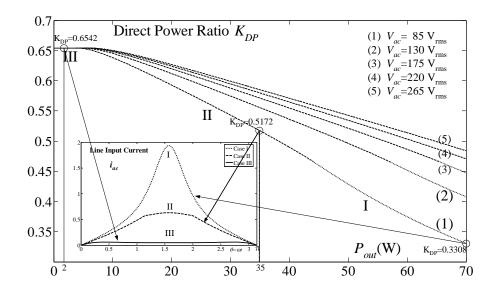

| Fig. 3.4 | $K_{DP}$ versus output power for different $V_{ac}$ and cases at the condition of Table                                   |

|          | 3.3-case I                                                                                                                |

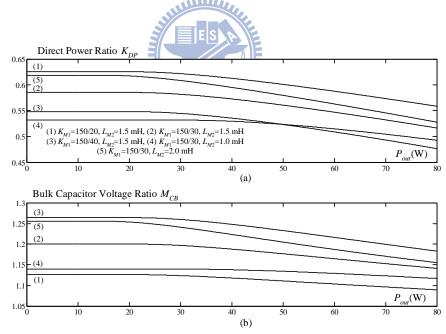

| Fig. 3.5 | (a) $K_{DP}$ and (b) $M_{CB}$ versus output power for different $K_{M1}$ and $L_{M2}$ , at                                |

|          | $L_{M1}=150 \mu\mathrm{H},  n_2=1.7,  V_{ac}=265 \mathrm{V_{rms}},  V_O=54 \mathrm{V}.$ 36                                |

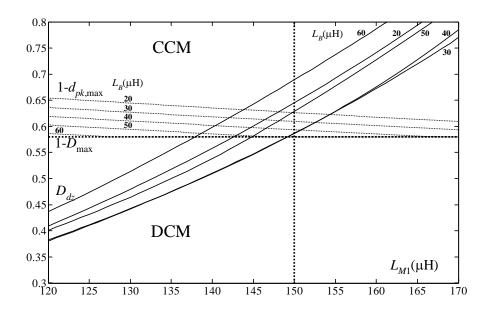

| Fig. 3.6 | $D_{dz}$ and $(1-d_{pk,max})$ versus $L_{M1}$ for different $L_B$ , $L_{M2} = 1.5$ mH, at $D_{max} = 0.42$ ,              |

|          | $V_{ac} = 85 \text{ V}_{\text{rms}}, V_O = 54 \text{ V}, \text{ and } P_{out} = 60 \text{ W}$                             |

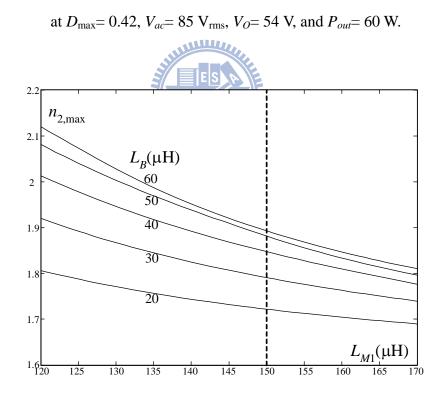

| Fig. 3.7 | $M_{CB,\min}$ and $n_{2,\max}$ versus $L_{M1}$ for different $L_B$ , $L_{M2} = 1.5$ mH, at $D_{\max} = 0.42$ , $V_{ac} =$ |

| 85 $V_{rms}$ , $V_O = 54$ V, and $P_{out} = 60$ W                                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

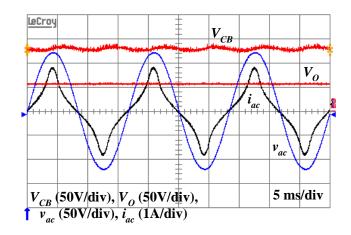

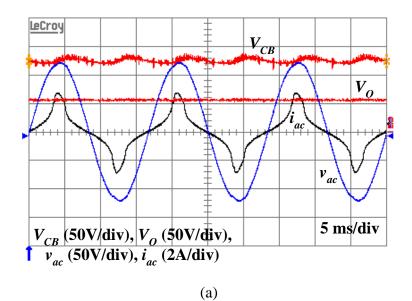

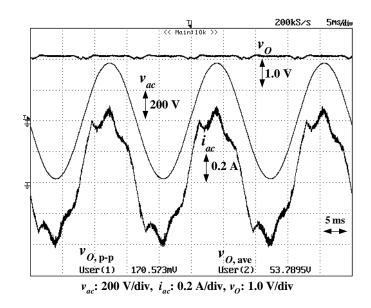

| Fig. 3.8 Measured line voltage, bulk capacitor voltage, line current, output voltage: (a)                                                                   |

| $V_{ac}$ =85 V <sub>rms</sub> , $P_{out}$ =60 W, (b) $V_{ac}$ =265 V <sub>rms</sub> , $P_{out}$ =60 W, and (c) $V_{ac}$ =265 V <sub>rms</sub> ,             |

| $P_{out}=20 \text{ W}$                                                                                                                                      |

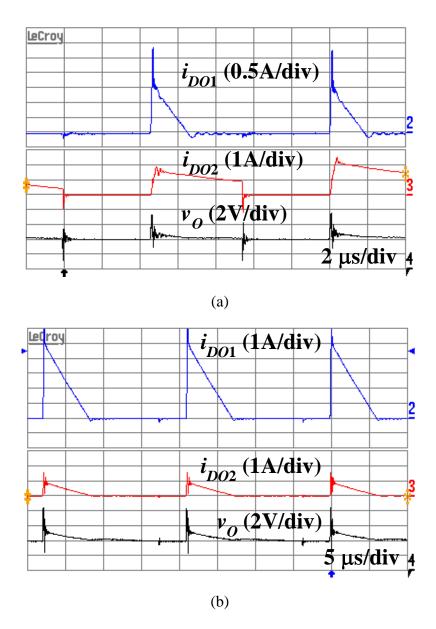

| Fig. 3.9 Measured switching current waveforms: (a) $M_1$ mode and (b) $M_2$ mode at                                                                         |

| $V_{ac} = 130 \text{ V}_{\text{rms}}, R_L = 60.24 \Omega$                                                                                                   |

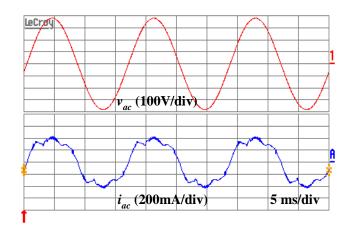

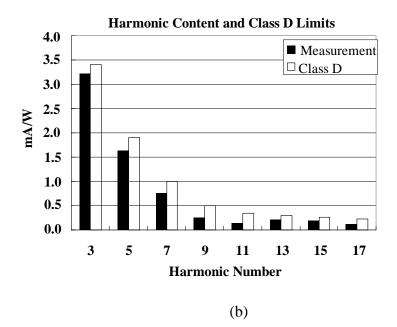

| Fig.3.10 (a) Line voltage and line current measured at the worst condition ( $V_{ac}$ =85 V <sub>rms</sub>                                                  |

| and $P_{out}$ =80 W) and (b) harmonic content and class D limits46                                                                                          |

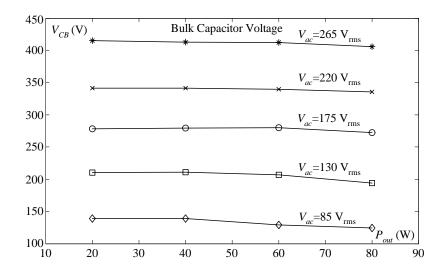

| Fig. 3.11 Measured bulk capacitor voltage versus load under line variations47                                                                               |

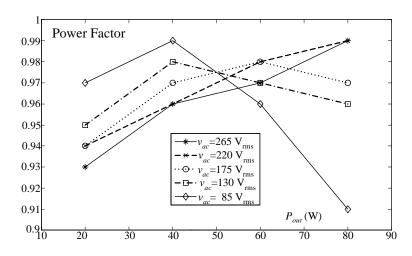

| Fig. 3.12 Measured power factor versus load under line variations                                                                                           |

| Fig. 3.13 Measured efficiency versus load under line variations                                                                                             |

| Fig. 4.1 Schematic diagram of $S^4$ parallel boost-flyback-flyback converter with opto-                                                                     |

| coupler feedback current mode controller                                                                                                                    |

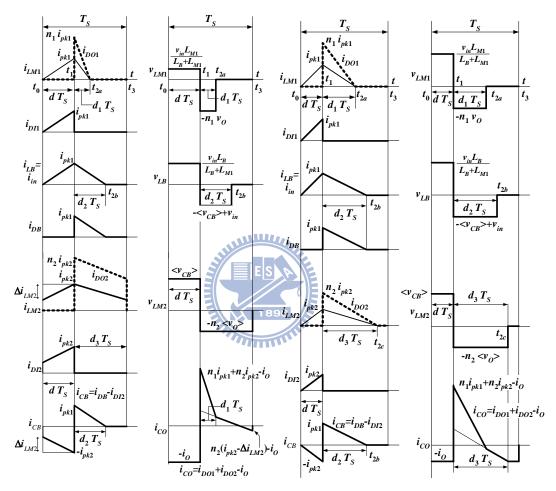

| Fig. 4.2 Illustrated waveforms within one switching period: (a) for DCM-DCM                                                                                 |

| boost-flyback semi-stage + CCM flyback DC/DC semi-stage ( $M_1$ mode); (b)                                                                                  |

| for DCM-DCM boost-flyback semi-stage + DCM flyback DC/DC semi-stage                                                                                         |

| DCM ( $M_2$ mode)                                                                                                                                           |

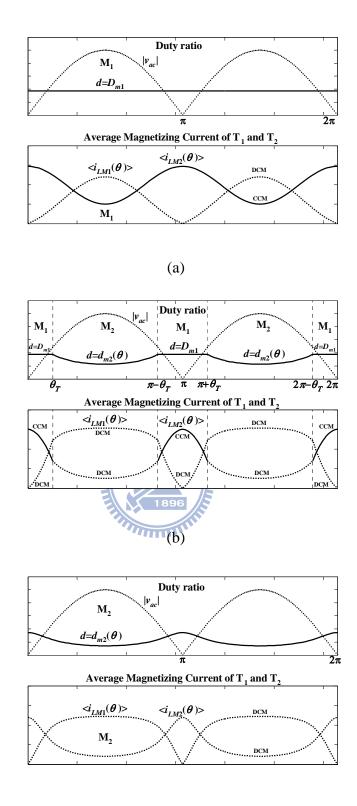

| Fig. 4.3 Operation waveforms in a line cycle: (a) case I ( $M_1$ mode only), (b) case II                                                                    |

| (both $M_1$ and $M_2$ modes), and (c) case III ( $M_2$ mode only)                                                                                           |

| Fig. 4.4 Small signal block diagram: (a) $M_1$ mode and (b) $M_2$ mode60                                                                                    |

| Fig. 4.5 Theoretical waveforms of the parallel boost-flyback-flyback converter at $V_{ac}$ =                                                                |

| 265 $V_{\rm rms}$ and $P_{out}$ =60 W                                                                                                                       |

|                                                                                                                                                             |

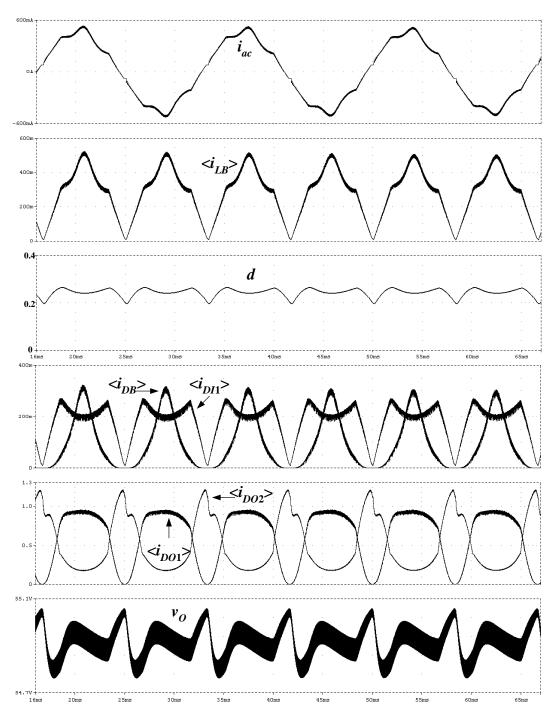

| Fig. 4.6 PSPICE simulation waveforms of the parallel boost-flyback-flyback converter                                                                        |

| Fig. 4.6 PSPICE simulation waveforms of the parallel boost-flyback-flyback converter<br>at $V_{ac} = 265 \text{ V}_{\text{rms}}$ and $P_{out}=60 \text{ W}$ |

|                                                                                                                                                             |

| at $V_{ac} = 265 \text{ V}_{\text{rms}}$ and $P_{out} = 60 \text{ W}$                                                                                       |

| at $V_{ac} = 265 \text{ V}_{\text{rms}}$ and $P_{out} = 60 \text{ W}$                                                                                       |

| at $V_{ac} = 265 \text{ V}_{rms}$ and $P_{out}=60 \text{ W}$                                                                                                |

| at $V_{ac} = 265  V_{rms}$ and $P_{out}=60  W$                                                                                                              |

# Notation

The follow notations are adopted throughout this work.

AC/DC: ac-to-dc

BIFRED: boost integrated/flyback rectifier/energy storage/dc-to-dc converter

DC/DC: dc-to-dc

ICS: input current shaper

$K_{DP}$ : direct power ratio

*K*<sub>*IDP*</sub>: indirect power ratio

$K_{M1}$ : inductance ratio

$M_{CB}$ : voltage gain of boost cell

$M_O$ : voltage gain of flyback cell

PF: power factor

PFC: power factor correction

PPFC: parallel power factor correction

SSTO: single-switch two-output

S<sup>2</sup>: single-stage

S<sup>4</sup>: single-stage-single-switch

TIBuck: two-input-buck

$T_{HL}$ : half line period

$T_L$ : line period

*T<sub>S</sub>*: switching period

$\langle x(t) \rangle$ : moving average of x(t) over  $T_S$

- X(t): the dc part of  $\langle x(t) \rangle$  or x(t)

- $\tilde{x}(t)$ : the ac part of  $\langle x(t) \rangle$  or x(t)

### **CHAPTER 1**

#### INTRODUCTION

#### 1.1 Background

Most electronic equipment is supplied by 60 Hz utility power by using the ac-to-dc (AC/DC) converter which is a diode rectifier followed by a bulk capacitor. Since these power converters absorb energy from the AC line only when the line voltage is higher than the DC bus voltage, the input line current contains rich harmonics, which pollute the power system and interfere with other electric equipment.

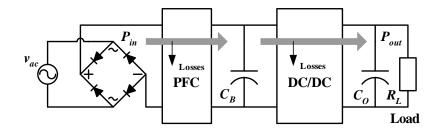

Hence, the power factor correction (PFC) has been widely employed for improving the power quality of the power converters. In conventional converters design, a two-stage structure as shown in Fig. 1.1 was usually employed for performing PFC and output regulation simultaneously, where the bulk capacitor  $C_B$  is in the power transfer path between the PFC stage and dc-to-dc (DC/DC) stage. This structure can give high power factor and high regulation simultaneously by using two independent controllers and power stages, but the cost of switching devices and the control circuitry is not easy to cut down especially in low power application. Although unity power factor is the ideal objective, it is no longer an essential requirement. According to the regulation IEC61000-3-2 [1], the power supplies of low power products such as computers, PC monitors and television sets have to comply with Class D limits as shown in Table 1.1. This fact promotes the development of the single-stage  $(S^2)$ AC/DC converter as shown in Fig. 1.2, such as boost integrated/flyback rectifier/energy storage/dc-to-dc converter (BIFRED) [2] and boost input current shaper (ICS) [3]-[8], which comply with the regulations without achieving unity power factor. In those designs two power stages were integrated into one stage by using only one controller and sharing the control switch so that the component count and cost could be reduced. However, these converters have the problems of high bulk capacitor voltage at high line and light load when PFC

semi-stage is operated in DCM and DC/DC semi-stage in CCM. Some alternative designs [5]-[8] using additional coupled feedback windings could reduce the bulk capacitor voltage, but they also result in dead angle in the input current so the input current distortion is increasing. Furthermore, it can be seen that part of the power is repeatedly processed or recycled in both the conventional two-stage and single-stage AC/DC converters.

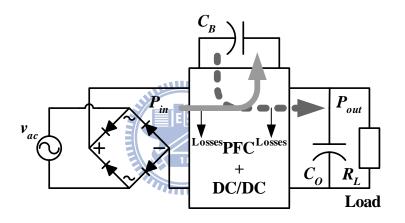

To improve the power processing, the parallel power factor correction (PPFC) scheme as shown in Fig. 1.3 has been proposed in [9] and [10]. In those schemes, two parallel power flow paths are used and part of the input power is processed only once. Therefore, the converters could transfer power with higher efficiency. Since each path only transmits part of the whole conversion power, the components can be replaced with smaller ones. However, the PPFC design has complex circuit with special control scheme as mentioned in [11]. Another scheme of parallel power processing approach was presented on the base of two-output pre-regulator cascaded with two-input post-regulator [12]. Although the output capacitor is smaller and the power conversion efficiency is high, some extra implementation prices exist, such as, multiple switching devices and floating MOSFET driver. In addition, the output voltage range of the post-regulator is limited so it is not suitable for universal input, and it is a two-stage structure so it needs two controllers. The universal boost/forward converter presented in [14]-[15] makes use of an auxiliary transformer to reduce link voltage stress without inducing the dead angle of the line current. Hence, it inspires the parallel idea for the universal S<sup>2</sup> converter in this dissertation.

Fig. 1.1 Two-stage AC/DC converter scheme.

| Harmonic wave       | Maximum permissible har-      | Maximum permissible har- |  |  |  |

|---------------------|-------------------------------|--------------------------|--|--|--|

| Order n             | monic current per watt (mA/W) | monic current (A)        |  |  |  |

| 3                   | 3.4                           | 2.30                     |  |  |  |

| 5                   | 1.9                           | 1.14                     |  |  |  |

| 7                   | 1.0                           | 0.77                     |  |  |  |

| 9                   | 0.5                           | 0.40                     |  |  |  |

| 11                  | 0.35                          | 0.33                     |  |  |  |

| 13                  | 3.85/n                        | 0.21                     |  |  |  |

| $15 \leq n \leq 39$ | 5.03/11                       | 0.15×(15/n)              |  |  |  |

Table 1.1 Limits for class D equipment in standard IEC 61000-3-2

Fig. 1.2 Typical single-stage AC/DC converter scheme.

Fig. 1.3 Parallel power factor correction converter scheme.

#### **1.2 Motivation**

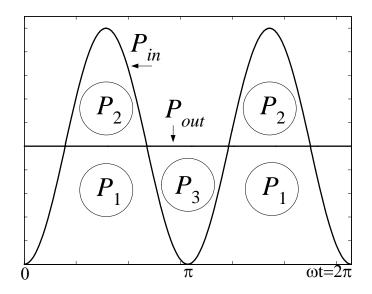

For the power relationship of an ideal PFC AC/DC converter as shown in Fig. 1.4, the ac input power  $(P_{in})$  is a sine square function biased by constant output power  $(P_{out})$ . It is clear that 68% of line average input power  $(P_1)$  can be transferred to output directly through PFC stage, which is called the direct power. Only the remaining 32% of line average input power  $(P_2/P_3)$  needs to be stored in  $C_B$  temporarily through PFC stage and taken off from the  $C_B$ through DC/DC stage. Since the processed powers are not directly transferred from ac input to dc output, they are called indirect powers. However, for conventional scheme, no matter whether it is a two-stage or a single-stage configuration as shown in Fig. 1.1 and 1.2,  $P_{in}$  is first transferred into somewhat pulsating dc power stored on  $C_B$  by the PFC stage. The power stored on  $C_B$  is processed again by the DC/DC stage to reach final  $P_{out}$  for load ( $C_O$  and  $R_L$ ). The conversion efficiency of the double power processing is low, which is the product of the efficiency of each power conversion. In addition, these two processing stages are in cascade, they both have to handle whole input power. Fortunately the parallel scheme can transfer partial input power to output directly without going through DC/DC stage as shown in Fig. 1.3. Therefore, based on the aforementioned concept, a new family of  $S^2$  parallel AC/DC converter is proposed in this dissertation to increase the direct power content percentage on the input power. The parallel converters are expected to have advantages of high efficiency and small rating components.

Fig. 1.4 Power relationship of ideal PFC converter.

#### **1.3 Contributions of the Dissertation**

This study proposes a new family of  $S^2$  parallel AC/DC converter. In the circuits, the front semi-stage is of single-switch two-output (SSTO) boost-flyback configuration that works as a power factor corrector. Part of input power is processed only with the front flyback cell, and the remainder of input power is processed through the path along boost cell-*C*<sub>B</sub>-DC/DC semi-stage. To illustrate the circuit and control of the proposed converter, several recently published low-power single-stage approaches are tabulated in Table 1.2. Only the proposed converter and those in [20-21] are implemented with single switch and single-loop controller. However, the efficiency of [20] is significantly lower than the proposed one and the component count of [21] is more than the proposed one. It can be seen from Table 1.2 that the circuits in [20], [21], and [13] have relatively small capacitor voltages. However, the circuit of [20] has the shortcoming of low efficiency. The circuit of [21] employs two bulk capacitors and multi-winding transformer to get low voltage. The circuit in [13] puts bulk capacitor on the secondary side of flyback transformer, which results in the low capacitor voltage. However, it also has the shortcomings of extra control switch and that the efficiency would decrease when universal voltage is applied. Though the bulk capacitor voltage in proposed converter is higher than those in [13], [20], and [21], it is not higher than 450 V, the voltage limitation of commercial capacitors. Additionally, the use of single switch with small current stress, two parallel power streams with small components, and single-loop controller is a competitive advantage in the low-power universal applications. The modeling and control of the parallel converter is also presented. The technique can solve the model uncertainty problem and be generalized to other parallel converter.

|          | Diode | Control | Magnetic     | Control    | $V_{CB}\left(\mathbf{V}\right)$ | Switching | Input               | Output  | Output | Maximum    | PF (%) or  |

|----------|-------|---------|--------------|------------|---------------------------------|-----------|---------------------|---------|--------|------------|------------|

|          |       | switch  | components   |            |                                 | frequency | voltage             | voltage | power  | efficiency | compliance |

|          |       |         |              |            |                                 | (kHz)     | (V <sub>rms</sub> ) | (V)     | (W)    | (%)        |            |

| [20]     | 4     | 1       | 1 T with 3   | Single     | <375                            | 96        | 90-264              | 5       | 60     | 73.2       | IEC        |

| 2004     |       |         | windings + 1 | controller |                                 |           |                     |         |        |            | 1000-3-2   |

|          |       |         | L            |            |                                 | U.,       |                     |         |        |            | Class D    |

| [21]     | 7     | 1       | 1 T with 3   | Single     | <260                            | 100       | 85-265              | 28      | 150    | 83.2       | >0.97      |

| 2005     |       |         | windings + 1 | controller |                                 | H E       |                     |         |        |            |            |

|          |       |         | T + 1 L      | UC3844     | 18                              |           |                     |         |        |            |            |

| [13]     | 2     | 2       | 1 T + 1 L    | Single     | <35                             | 2 11      | 187-265             | 56      | 100    | 85.4       | IEC        |

| 2007     |       |         |              | controller |                                 | <b>P</b>  |                     |         |        |            | 61000-3-2  |

|          |       |         |              |            |                                 |           |                     |         |        |            | Class D    |

| [22]     | 4     | 2       | 1 T + 1 L    | Two con-   | 400                             | 50        | 100-240             | 24      | 100    | 87         | 0.93-0.96  |

| 2008     |       |         |              | trollers   |                                 |           |                     |         |        |            | IEC        |

|          |       |         |              | and logic  |                                 |           |                     |         |        |            | 61000-3-2  |

|          |       |         |              |            |                                 |           |                     |         |        |            | Class D    |

| [23]     | 2     | 2       | 1 T with 6   | Single     | ?                               | 140       | 110-120             | ?       | 150    | 92         | IEC        |

| 2008     |       |         | windings     | controller |                                 |           |                     |         |        |            | 1000-3-2   |

|          |       |         |              | and logic  |                                 |           |                     |         |        |            | Class D    |

| Proposed | 5     | 1       | 2 T + 1 L    | Single     | <415.4                          | 100       | 85-265              | 54      | 80     | 85.8       | 0.91-0.99  |

|          |       |         |              | controller |                                 |           |                     |         |        |            | IEC        |

|          |       |         |              | UC3844     |                                 |           |                     |         |        |            | 61000-3-2  |

|          |       |         |              |            |                                 |           |                     |         |        |            | Class D    |

Table 1.2 Recently published S<sup>2</sup> approaches

Letter T denotes transformer, letter L denotes inductor,  $V_{CB}$  denotes bulk capacitor voltage, mark '?' denotes that the item was not mentioned in the literature.

#### **1.4 Dissertation Outline**

This dissertation is composed of five chapters. The content of each chapter is briefly described as follows:

Chapter 1 introduces the background regarding the present power factor correction techniques and parallel converter concept. It then lists the research motivations and contributions.

Chapter 2 offers a review of conventional parallel AC/DC converters and introduces proposed parallel boost-flyback converter.

Chapter 3 analyzes the parallel boost-flyback-flyback converter by averaging method at first. Then, the power distribution and bulk capacitor voltage of the converter are studied. The design equations and procedure for universal application are also derived. In addition, the experiment results of 80 W prototype are presented.

Chapter 4 depicts the modeling and control of the parallel boost-flyback-flyback converter. The text contains the large signal model, small signal model, compensator design, simulation and experimental results.

Chapter 5 summarizes the conclusions of this work and presents suggestions for further work in related research directions.

### **CHAPTER 2**

### SYNTHESIS OF SINGLE-STAGE PARALLEL CONVERTERS

In the last decade, many efforts were made to implement the PPFC scheme for reducing power processing. However, besides efficiency, there are several aspects must be considered from the viewpoint of AC/DC converter, such as component count, circuit complexity, component voltage and current stresses, input current quality, etc. Thus, the main objective of this chapter is to present a topological study of the representative parallel converters and then propose a new family of parallel boost-flyback converters.

#### 2.1 Review of Conventional Parallel AC-to-DC Converters

The concept and scheme of PPFC are first proposed by Y. Jiang *et al.* [9-10] and implemented with full bridge boost PPFC circuit as shown in Fig. 2.1. The circuit operates in two cases. For the case  $P_{in} > P_{out}$ , all switches act so that the partial input energy is transferred to load through T<sub>1</sub> directly and excess energy is put into  $C_B$ . Whereas, for the case  $P_{in} < P_{out}$ , all switches act so that the input energy is transferred to  $C_B$  and the stored energy in  $C_B$  is transferred to load through T<sub>2</sub>.

The PPFC circuit shown in Fig. 2.1 clearly demonstrates that the power is through two parallel processing paths and partial input power is processed only once. However, the circuit contains two isolation transformers, fives switches and multi-loop control together with logic circuits. Complicated circuit structure may cause practical issues such as sophisticated operation mechanism, complex control, and thus difficult design and poor reliability. Thus, this converter would be good for those applications where the power level is high. For below a certain power level, it seems too complex and expensive.

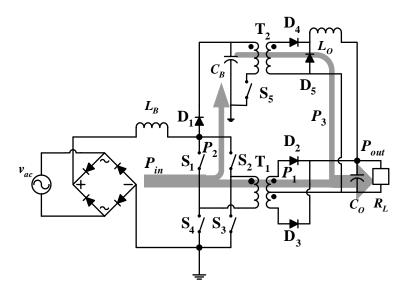

Fig. 2.1 Full bridge boost PPFC circuit [9-10].

To simplify the circuit, another parallel method [12] that could improve the dynamic response of PFC stage with almost no efficiency penalty is shown in Fig. 2.2(a). In the circuit, the first stage is a two-output flyback converter, which supplies two "poorly regulated" (from the dynamic point of view) outputs instead of one, both at relatively close voltages. The second stage is a Two-Input-Buck (TIBuck) postregulator, which is highly efficient. From the static characteristic of view, the TIBuck postregulator is equivalent to two half converters in series as shown in Fig. 2.2(b). For the half converter at the top, it is a standard buck converter, whose input and output voltages are  $v_1-v_2$  and  $v_0-v_2$ , respectively, and whose output load is  $R_L$  $(v_0-v_2)/v_0$ . Besides, for the converter at the bottom, it works as a lossless converter, whose input and output voltages are  $v_2$ , and the load is  $R_L v_2/v_0$ . Therefore, the total output power comes up to the load following two different paths. A considerable fraction of the input power (typically 85%–90%) comes up to the load with no power processing, whereas the remaining power undergoes a power processing based on a buck topology, therefore, with a typical efficiency of 80%–95%.

Although the parallel method with TIBuck converter has the advantages of small output capacitor and high power conversion efficiency, some extra implementation prices exist, such as, multiple switching devices and floating MOSFET driver. In addition, the output voltage range of the post-regulator is limited so as not suitable for universal input, and each stage needs individual controller.

TIBuck postregulator [12] and (b) equivalent circuit of TIBuck postregulator.

To realize the PPFC concept with a single stage topology, a single-switch PPFC AC/DC converter with flyback converter [20] is proposed as shown in Fig. 2.3. The concept is to create a voltage source that is parallel to the rectified input voltage source. When the line voltage is near the zero crossing area, the paralleled voltage source that is approximate to  $V_{CB} \cdot N_1/(N_1 + N_2)$  provides the output power as  $P_3$ . When the line voltage is near the peak area, it is the rectified input voltage source that provides main power  $P_1$  to the output directly and

also stores some extra power  $P_2$  in the bulk capacitor. Furthermore, during peak line voltage both  $L_B$  and  $T_1$  operate in CCM, and the boost inductor current is strongly dependent on the reflected load current. This inherent load current feedback mechanism can reduce the input power at light load without reducing the duty ratio. All the current processed by the switch is the primary side current of the feedback converter. Hence, the load current feedback can effectively reduce both the voltage stress of the bulk capacitor and the current stress of the active stress. The proposed converters combine the advantages of simple topology, low bulk capacitor voltage and low switch current stress. However, the efficiency and power factor are not better compared to other methods as can be seen in Table 1.2.

Fig. 2.3 Single switch parallel power factor correction AC/DC converter with inherent load current feedback.

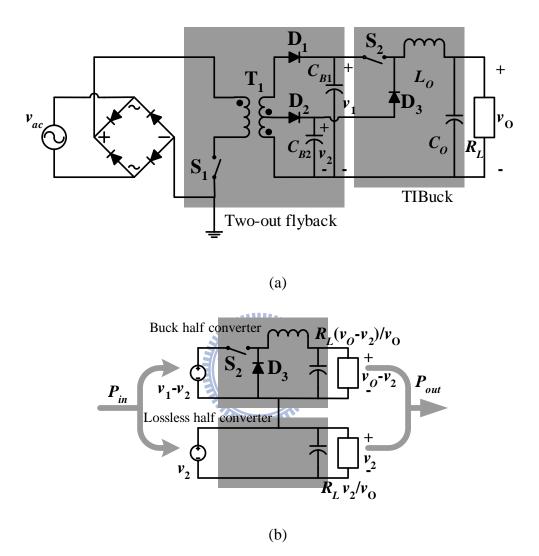

To improve the efficiency and power factor, an alternative method based on a novel PFC cell called "flyboost" to reduce redundant power processing is presented [21]. The method contains a new family of  $S^2$  converters derived from the direct power transfer concept and is intended for use in low to medium power level AC/DC converters such as adapters of personal computers.

The representative flyboost circuit shown in Fig. 2.4 has two operation modes. When recti-

fied line voltage  $|v_{ac}(t)|$  is less than  $2V_{CB}$ - $n_1V_O$  ( $n_1$ : the turn ratio of T<sub>1</sub>;  $V_O$ : output voltage), Transformer T<sub>1</sub> works like a flyback transformer to discharge all stored input power directly to the load. The portion of power is processed by active switch S<sub>1</sub> only once. Meanwhile, DC/DC cell will deliver some power from bus capacitors to the load to keep tight output voltage regulation. When instantaneous input voltage goes higher, and  $|v_{ac}(t)|$  is higher than  $2V_{CB}$ - $n_1V_O$ , the voltage across transformer T<sub>1</sub> primary winding is clamped to  $2V_{CB}$ - $|v_{ac}(t)|$ during S<sub>1</sub> OFF interval, which will be less than  $n_1V_O$ . It means that diode D<sub>1</sub> in T<sub>1</sub> secondary discharging path will not conduct. T<sub>1</sub> works like a boost inductor and discharges its magnetizing energy to both bus capacitors via D<sub>2</sub>. And DC/DC cell will deliver all output power from bus capacitors to the load. Under this mode, the input power is stored in bus capacitors, and then transferred to the load by DC/DC cell, resulting in this portion of power being processed twice by switch S<sub>1</sub>.

It can be seen that the derived  $S^2$  flyboost converters are of simplified circuit configuration and control, and typically, only one simple voltage control and one power switch are needed in circuit implementation. Experimental results demonstrate that the flyboost cell significantly improves the efficiency over the conventional converter. Moreover, experiments also verify that a newly derived  $S^2$  converter can operate in discontinuous current mode + continuous current mode (DCM+CCM) operation due to the clamped bulk capacitor voltage characteristic of flyboost PFC cell. However, the components of the circuit of seem excessive because two bulk capacitors and multi-winding transformer are employed to get low voltage.

Fig. 2.4 Single-stage AC/DC converters with flyboost cell.

# 2.2 S<sup>2</sup> Parallel Boost-Flyback Converter

#### 2.2.1 Principle

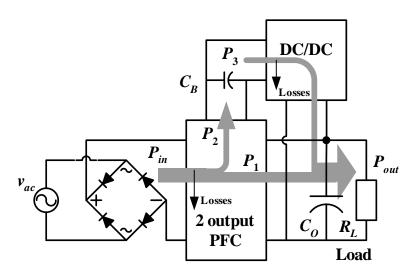

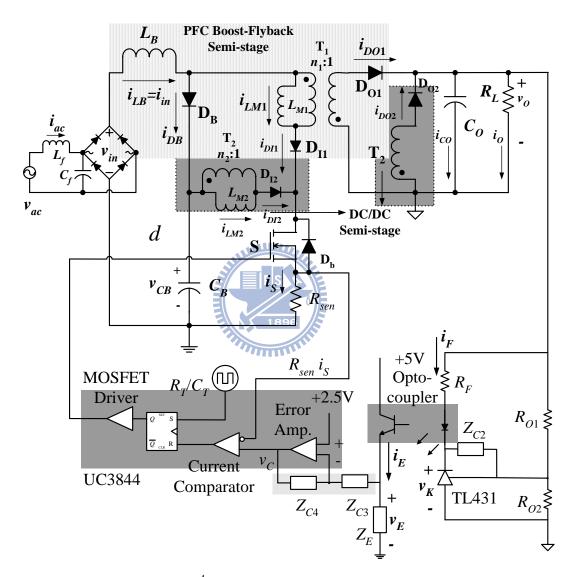

The new design power flow scheme of a single-stage ( $S^2$ ) PPFC is shown in Fig. 2.5. In Fig. 2.5, the line power,  $p_{in}$  is fed to SSTO boost-flyback semi-stage and split to two power flow streams,  $p_1$  and  $p_2$ . The power flow stream  $p_1$  is processed only by flyback cell and transferred to output directly, and hence it is direct power. Since the instantaneous  $p_{in}$  is always different from output power  $P_{out}$ , the remaining input power,  $p_2$ , is buffered to bulk capacitor  $C_B$  through the boost function of boost cell to regulate power flow. To fulfill a better output power regulation, a DC/DC semi-stage is employed to transfer the power, denoted by  $p_3$ , from  $C_B$  to the output when  $p_{in}$  is low, especially smaller than  $P_{out}$ . The power series  $p_2$  and  $p_3$  are processed twice from ac input to dc output, and hence they are indirect powers. Furthermore, to obtain high power factor, the boost and flyback cells both had better operate in discontinuous conduction mode (DCM), whereas the DC/DC semi-stage can be implemented with forward or flyback configuration and operate either in continuous conduction mode (CCM) or DCM. A S<sup>2</sup> implemented circuit of Fig. 2.5 is shown in Fig. 2.6(a). The circuit has been simplified so as to use only one common power control switch for SSTO boost-flyback and DC/DC semi-stages as shown in Fig. 2.6(b). In Fig. 2.6(b), PFC and output regulation are

performed with one feedback controller as shown in Fig. 2.6(c). The practical realization circuit in Fig. 2.6(b) is composed of a SSTO boost-flyback semi-stage, which is constructed by  $L_B$ , D<sub>B</sub>, T<sub>1</sub>, D<sub>O1</sub>, D<sub>I1</sub>, S, D<sub>b</sub>, and a bulk capacitor  $C_B$ , and a DC/DC semi-stage, which is implemented by a flyback circuit and constructed by T<sub>2</sub>, D<sub>O2</sub>, D<sub>I2</sub>, S, and D<sub>b</sub>. In Fig. 2.6(a) and (b), the two transformers T<sub>1</sub> and T<sub>2</sub> share the load current, so their size could be small. Furthermore, the boost inductor  $L_B$  and transformers T<sub>1</sub> process the input power together when switch S is on, so the size of  $L_B$  could be of smaller one. Therefore, the sizes of  $L_B$ , T<sub>1</sub> and T<sub>2</sub>, can be chosen smaller ones in this design.

Fig. 2.5 Proposed  $S^2$  PPFC scheme.

Fig. 2.6 S<sup>2</sup> Implementation circuit of parallel boost-flyback-flyback converter: (a) two-switch circuit, (b) single-switch circuit, and (c) feedback controller circuit.

#### 2.2.2 SSTO Boost-Flyback Circuit

In order to clearly build the primary operation concepts and theories of the proposed S<sup>2</sup> parallel AC/DC converter depicted in Fig. 2.5 and 2.6, the operation of a SSTO boost-flyback converter depicted in Fig. 2.7(a) will be introduced in advance. In SSTO boost-flyback converter,  $T_1$ - $D_{01}$ - $D_{11}$ - $C_0$ - $R_0$ -S is the flyback cell and  $L_B$ - $D_B$ - $C_B$ - $R_B$ -S is the boost cell. This converter has power factor correction function that will be demonstrated later. In the converter, the boost inductance  $L_B$  and the flyback transformer  $T_1$  both operate in DCM. When control switch S is turned on,  $T_1$  and  $L_B$  are charged serially. When S is turned off,  $T_1$  and  $L_B$  are discharged to  $R_0$ - $C_0$  and  $R_B$ - $C_B$  respectively. The main current waveforms of SSTO boost-flyback converter operating in one switching period are shown in Fig. 2.7(b). To demonstrate the operation theory of the converter, the moving average notation  $\langle x(t) \rangle$  of a waveform x(t) over a switching period  $T_5$  is employed and defined as follows [16],

$$\langle x(t)\rangle = \langle x(t)\rangle_{T_S} = \frac{1}{T_S} \int_{t}^{t+T_S} x(\tau)d\tau .$$

(2.1)

To focus on the primary analyses, some assumptions are made as follows:

- 1) All components are ideal.

- 2) Since switching frequency  $f_S$  is far greater than line frequency  $f_L=1/T_L$ , where  $T_L$  is line period. The input voltage  $v_{in}(t)$ , regarded as the rectified line voltage  $V_{inpk}|\sin(\omega_L \cdot t)|$ , is approximated to a constant over one switching period, where  $V_{inpk}$  is the ac voltage amplitude, and  $\omega_L = 2 \cdot \pi/T_L$ .

- 3) Since bulk capacitor  $C_B$  and output capacitor  $C_O$  are sufficiently large, flyback output voltage  $V_O$  and boost output voltage  $V_{CB}$  are regarded as constants within one half line cycle.

From Fig. 2.7(a), it can be seen that the average input current  $\langle i_{in}(t) \rangle$  is equal to the sum of average flyback input diode current  $\langle i_{DI1}(t) \rangle$  and average boost output diode current  $\langle i_{DB}(t) \rangle$ . Therefore, by summing the current waveforms of  $\langle i_{DI1}(t) \rangle$  and  $\langle i_{DB}(t) \rangle$  shown in Fig. 2.7(b),  $\langle i_{in}(t) \rangle$  can be obtained as

$$\left\langle i_{in}(t)\right\rangle = \left\langle i_{DI1}(t)\right\rangle + \left\langle i_{DB}(t)\right\rangle = \frac{i_{pk1} \times (d+d_2)}{2}, \qquad (2.2)$$

where *d* is the duty ratio of S,  $d_2$  is the boost cell diode conduction time ratio, and the current peak value can be obtained from

$$i_{pk1} = \frac{d \cdot v_{in}(t)}{f_s(L_B + L_{M1})} = \frac{d_2 \cdot (V_{CB} - v_{in}(t))}{f_s L_B} = \frac{d_1 \cdot n_1 \cdot V_O}{f_s L_{M1}},$$

(2.3)

where  $L_{M1}$  is the primary magnetizing inductance of T<sub>1</sub>,  $n_1$  is the primary turns ratio of T<sub>1</sub>, and  $d_1$  is the flyback cell output diode conduction time ratio. From (2.3),  $d_2$  can be obtained as

$$d_{2} = \frac{d \cdot v_{in}(t)}{(V_{CB} - v_{in}(t))} \left(\frac{L_{B}}{L_{B} + L_{M1}}\right).$$

(2.4)

With substituting (2.3) and (2.4) into (2.2),  $\langle i_m(t) \rangle$  can be found as

$$\langle i_{in}(t) \rangle = \frac{d^2 v_{in}(t)}{2 f_s (L_B + L_{M1})} \left( 1 + \frac{v_{in}(t)}{(V_{CB} - v_{in}(t))} \left( \frac{L_B}{L_B + L_{M1}} \right) \right).$$

(2.5)

Since the average current of  $C_O$  over a half line cycle is zero at steady state, the half line average current of  $i_{DO1}$  is equal to the average output current. Thus,

$$\frac{2}{T_L} \int_0^{\frac{\pi}{OL}} \langle i_{DO1}(t) \rangle dt = \frac{V_O}{R_O} \,.$$

(2.6)

From Fig. 2.7(b), average current over one switching period  $\langle i_{DO1}(t) \rangle$  in (2.6) can be obtained as follows

$$\langle i_{DO1}(t) \rangle = \frac{n_1 \cdot i_{pk1} \cdot d_1}{2},$$

(2.7)

where the magnetism discharging time ratio of  $T_1$  transformer,  $d_1$ , can be found from (2.3) as

$$d_{1} = \frac{d \cdot v_{in}(t)}{n_{1} \cdot V_{O}} \left( \frac{L_{M1}}{L_{B} + L_{M1}} \right).$$

(2.8)

With substituting (2.3) and (2.8) into (2.7),  $\langle i_{DOI}(t) \rangle$  can be obtained as

$$\langle i_{DO1}(t) \rangle = \frac{L_{M1} d^2 v_{in}^2(t)}{2 f_s (L_B + L_{M1})^2 V_o} .$$

(2.9)

Substituting (2.9) into (2.6), the voltage gain of flyback cell  $M_0$  can be obtained as

$$M_{O} = \frac{V_{O}}{V_{inpk}} = d \cdot \sqrt{\frac{L_{M1} \cdot R_{O}}{4f_{S}(L_{B} + L_{M1})^{2}}},$$

(2.10)

where  $R_0$  is the load resistance of flyback cell.

Similarly, since  $C_B$  has zero average current over a half line cycle in steady state, the average current relation can be obtained as

$$\frac{2}{T_L} \int_0^{\frac{\pi}{\omega_L}} \langle i_{DB}(t) \rangle dt = \frac{V_{CB}}{R_B}, \qquad (2.11)$$

where  $\langle i_{DB}(t) \rangle$  can be obtained from Fig. 2.7(b) as

$$\langle i_{DB}(t) \rangle = \frac{i_{pk1} \cdot d_2}{2} = \frac{L_B d^2 v_{in}^2(t)}{2 f_S (L_B + L_{M1})^2 (V_{CB} - v_{in}(t))}.$$

(2.12)

The voltage gain of boost cell  $M_{CB}$  is defined and obtained with substituting (2.12) into (2.11) as

$$M_{CB} = \frac{V_{CB}}{V_{inpk}} = \frac{d^2 \cdot R_B \cdot L_B}{2\pi \cdot f_s (L_B + L_{M1})^2} \int_0^{\pi} \frac{\sin^2 \theta}{M_{CB} - |\sin \theta|} d\theta , \qquad (2.13)$$

where  $R_B$  is the load resistance of boost semi-stage.

It can be seen from (2.5) that while *d* and  $f_S$  are regarded as constants, the arrangement of smaller ratio of  $L_B/(L_B + L_{M1})$  can result in higher linear relation between  $\langle i_{in}(t) \rangle$  and  $v_{in}(t)$ , in other words, lower input harmonic distortion. Furthermore, (2.10) and (2.13) show that voltage gain rises as load resistance increases. In particular,  $V_{CB}$  in (2.13) can be very high at light load and high line. Therefore, the method to keep it under commonly accepted limit would be presented in Chapter 3.

Fig. 2.7 SSTO boost-flyback converter: (a) circuit and (b) main waveforms.

## 2.3 New Family of Parallel Boost-Flyback Converter

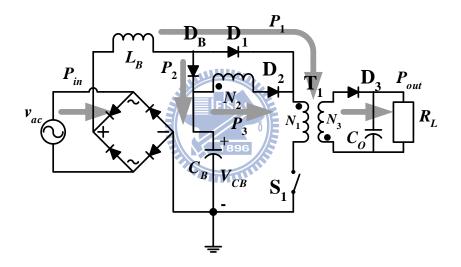

Based on the proposed S<sup>2</sup> PPFC scheme shown in Fig. 2.5, more circuits of the proposed S<sup>4</sup> boost-flyback converters can be formed by modifying the DC/DC semi-stage or flyback cell. By replacing the flyback DC/DC semi-stage in Fig. 2.6 with another DC/DC circuit such as forward circuit, a new single-stage-single-switch parallel AC/DC converter is obtained in Fig. 2.8(a). Moreover, the SSTO boost-flyback converter can be incorporated with the two-input Buck (TIBuck) post-regulator [12] to form another new single stage single switch parallel AC/DC converter as shown in Fig. 2.8(b). This converter can decrease the size of the bulk capacitor and improve the dynamic response with almost no efficiency penalty in either. Alternatively, the flyback cell of SSTO boost-flyback semi-stage can be replaced with a two-switch-flyback circuit to form another parallel scheme shown in Fig. 2.8(c), which has the merits of low switch voltage stress and leakage inductance clamping.

Fig. 2.8 Derived topologies from proposed parallel scheme: (a) with forward semi-stage, (b) with TIBuck semi-stage, (c)  $S^2$  boost-two-switch-flyback parallel converter scheme.

### **CHAPTER 3**

# Analysis and Design of a Single-Stage-Single-Switch Parallel

# **Boost-Flyback-Flyback Converter**

The practical realization circuit of proposed  $S^2$  PPFC scheme is composed of a SSTO boost-flyback semi-stage,  $C_B$ , and a DC/DC semi-stage. The SSTO boost-flyback semi-stage splits input power into two power flow streams including direct power stream and indirect stream. The direct power stream is processed only by flyback cell and transferred to output directly. The indirect power stream is buffered to  $C_B$  through the boost function of boost cell to regulate power flow through DC/DC semi-stage. As the boost cell and flyback cell operate in DCM, and duty ratio and switching frequency are constants, the arrangement of smaller ratio of boost inductor can result in higher power factor. The  $V_{CB}$  can be very high at light load and high line. Therefore, the method to keep input current harmonics and  $V_{CB}$  under commonly accepted limit would be presented later.

#### 3.1 Analysis of the Proposed Converter

The proposed  $S^2$  boost-flyback-flyback PPFC that has two semi-stages is shown in Fig. 2.5 and Fig. 2.6. The  $S^2$  implementation circuit in Fig. 2.6(b) is redrawn as Fig. 3.1(a). The boost-flyback semi-stage has power factor correction function and simultaneously gives two energy-processing paths. Being the remaining semi-stage, the flyback DC/DC converter circuit has fast output regulation ability. The proposed circuit has three magnetic elements, and each element has two operation modes (i.e. CCM and DCM). Hence, there are eight modes may happen in the circuit as shown Table 3.1. In order to obtain good power factor, the boost and flyback cells are designed to operate in DCM, whereas the flyback DC/DC semi-stage operates in either CCM or DCM in a line cycle. Thus, the converter has two operating states. The operation state while the flyback DC/DC semi-stage operates in CCM is defined as the  $M_1$  state. Contrarily, the operation state while the flyback DC/DC semi-stage operates in DCM is defined as the  $M_2$  state. However, making  $L_B$  operate in DCM in universal application is not easy, and CCM offers higher efficiency and lower current stress than DCM.  $M_3$  and  $M_4$  modes are allowed under harmonic limitation of IEC 61000-3-2 Class D, and not discussed in this dissertation. With properly selected  $n_1$ , it is easy to control  $T_1$  in DCM, so  $M_5$ - $M_8$  modes would not happen. The main current waveforms of the boost-flyback semi-stage in a switching period are the same as Fig. 2.7(b), and the waveforms of flyback DC/DC semi-stage in both two modes are shown in Fig. 3.1 (b) and (c). The circuit operations of the single-switch implemented circuit shown in Fig. 2.6(b) are demonstrated as follows:

In  $t_0 \le t \le t_1$  control switch S is switched on, flyback input diode D<sub>I1</sub> conducts, and D<sub>B</sub>, D<sub>O1</sub> and D<sub>O2</sub> are cut-off. Because the boost inductor  $L_B$  and the flyback transformer primary inductance  $L_{M1}$  both are connected in series, they are charged by the input power at the same time. The current  $i_{LB}$ , which is equal to  $i_{D1}$  and also the magnetizing current of T<sub>1</sub>,  $i_{LM1}$ , increases linearly from zero. Meanwhile, the currents  $i_{D12}$ , which is equal to the magnetizing current of T<sub>2</sub>,  $i_{LM2}$ , also increases linearly from its initial value while in M<sub>1</sub> mode and from zero while in M<sub>2</sub> mode. At the moment  $t_1$ , S is turned off. The currents  $i_{LB}$ ,  $i_{D11}$ , and  $i_{LM1}$  reach the same peak value  $i_{pk1}$  and the currents,  $i_{D12}$  and  $i_{LM2}$  reach another peak value  $i_{pk2}$ .

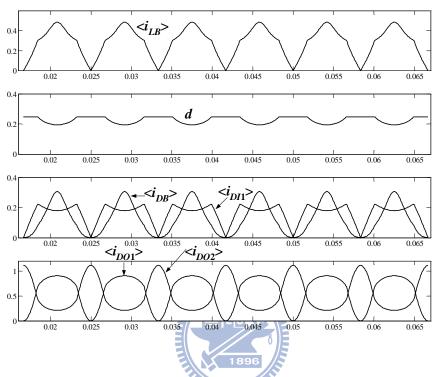

In  $t_1 \le t \le t_3$ , the main switch S is off, the diode  $D_{I1}$  and  $D_{I2}$  are off, and  $D_B$ ,  $D_{O1}$  and  $D_{O2}$  are on. The magnetic energy of inductor  $L_B$  is transferred to  $C_B$  and the magnetic energies of the transformers  $T_1$  and  $T_2$  are transferred to the same output load  $R_L$  simultaneously. Consequently, the energy discharging in  $T_1$  produces the result that  $i_{LM1}$  and  $i_{DO1} (=n_1 \cdot i_{LM1})$  both decrease linearly to zero at  $t_{2a}$  and keep zero until  $t_3$ , and  $i_{LB}$  and  $i_{DB}$  decrease linearly to zero at  $t_{2b}$ . The energy discharging in  $T_2$  gives the result that both  $i_{LM2}$  and  $i_{DO2} (=n_2 \cdot i_{LM2})$  decrease linearly to none zero final values at  $t_3$  for  $M_1$  mode and to zero at  $t_{2c}$  for  $M_2$  mode. Since  $M_1$  and  $M_2$  modes are to be discussed, three kinds of the combination of operation modes may be yielded within a half line cycle as shown in Table 3.2. The major currents waveforms and the corresponding duty ratios waveforms are depicted and shown in Fig. 3.2. Case I normally happens in low input voltage and high output power condition, whereas Case III normally happens at high input voltage and low output power.

For transient current balance of  $C_0$ , the transient load current can be expressed as

$$i_{O}(t) = i_{DO1}(t) + i_{DO2}(t) - i_{CO}(t), \qquad (3.1a)$$

where  $i_{DO1}(t)$ ,  $i_{DO2}(t)$ , and  $i_{CO}(t)$  represent the transient current of D<sub>O1</sub>, D<sub>O2</sub>, and C<sub>O</sub>. By an ideal output voltage feedback control, the duty-cycle of control switch is varied in order to set output voltage on reference value. As shown in Fig. 3.1, the input current  $(i_{DO1}(t)+i_{DO2}(t))$  of C<sub>O</sub> is regulated to balance with output current  $(i_O)$  in T<sub>S</sub> so that  $\langle i_O(t) \rangle = I_O$ ,  $\langle i_{CO}(t) \rangle = 0$ ,  $\langle v_O(t) \rangle = V_O$ , and

ALLIN.

(3.1a) can be expressed as

$$I_{o} = \frac{V_{o}}{R_{L}} = \frac{P_{out}}{V_{o}} = \langle i_{DO1}(t) \rangle + \langle i_{DO2}(t) \rangle, \qquad (3.1b)$$

1896

where  $V_0$  is the average output voltage,  $R_L$  is the load resistance,  $\langle i_{D01}(t) \rangle$  represents the averaging current of D<sub>01</sub> as expressed in (2.9), and  $\langle i_{D02}(t) \rangle$  represents the averaging current of D<sub>02</sub>. Although the input voltage varies in a half line cycle, the output power will be kept constant through the output feedback control. To make (3.1b) come true, the ideal output voltage feedback controller should have superior transient response and robust stability. The structure of controller is implemented with current mode controller with optically isolated feedback as shown in Fig. 2.6(c). In the circuit of Fig. 2.6(c), output voltage signal  $V_0$  is transferred to UC3844 via TL431 and opt-coupler, the switch current  $i_S$  is sensed and fed back to comparator, then the duty ratio d of control switch S is well controlled.

For the  $M_1$  mode, consider the bulk capacitance is a large one. Then the duty ratio d in  $M_1$  mode will be kept nearly constant  $D_{m_1}$  and yield a high regulation output, which is given by

$$V_{O} = \frac{V_{CB} \cdot d}{n_{2}(1-d)} \bigg|_{d=D_{m1}},$$

(3.2)

where  $n_2$  is the turns ratio of T<sub>2</sub>. From (3.2),  $D_{m1}$  can be found as

$$d = D_{m1} = \frac{n_2 V_O}{n_2 V_O + V_{CB}} \,. \tag{3.3}$$

From (3.1b),  $\langle i_{DO2}(t) \rangle$  can be obtained as

$$\left\langle i_{DO2}(t)\right\rangle = I_O - \left\langle i_{DO1}(t)\right\rangle \Big|_{d=D_{m1}}.$$

(3.4)

While in M<sub>2</sub> mode, T<sub>2</sub> operates in DCM. From Fig. 3.1(b) by following the similar deriving procedure of (2.9),  $\langle i_{DO2}(t) \rangle$  can be obtained as

$$\langle i_{DO2}(t) \rangle = \frac{n_2 \cdot i_{pk2} \cdot d_3}{2} = \frac{d^2 \cdot V_{CB}^2}{2f_S L_{M2} V_O} \Big|_{d=d_{m2}},$$

(3.5)

where  $d_{m2}$  is the instant duty ratio in M<sub>2</sub> mode. Substituting (2.9) and (3.5) into (3.1b), it can be obtained as

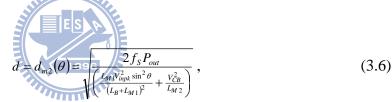

where  $\theta = \omega_L \cdot t$  is the phase of sinusoidal line voltage, and  $P_{out}$  is the output power. In order to generate the complex duty  $d_{m2}$ , the compensator in the current mode control had been optimized to possess superior transient responses such as small rising time, low overshoot, and zero steady state error. Addition, the compensator also can generate the correct duty  $d_{m2}$  with different operation modes due to its superior performances.

From (2.9) and (3.1b),  $\langle i_{DO1}(t) \rangle$  reaches maximum and  $\langle i_{DO2}(t) \rangle$  reaches minimum at  $\theta = \pi/2$ . For case I, the converter operates only in M<sub>1</sub> mode (T<sub>2</sub> operates in CCM),  $I_O$  must be greater than the boundary value  $I_{DO1PK} + I_{DO2B}$ ,

$$I_o \ge I_{DO1PK} + I_{DO2B}, \qquad (3.7)$$

where  $I_{DO1PK}$  is the peak value of  $\langle i_{DO1}(t) \rangle$  and  $I_{DO2B}$  is the boundary value of  $i_{DO2}$  between

CCM and DCM. The former can be obtained by replacing *d* with  $D_{m1}$  and  $v_{in}(t)$  with  $V_{inpk} \sin(\pi/2)$  in (2.9), and expressed as

$$I_{DO1PK} = \frac{L_{M1} D_{m1}^2 V_{inpk}^2}{2f_s (L_B + L_{M1})^2 V_o},$$

(3.8)

and the latter can be obtained by replacing d with  $D_{m1}$  in (3.5) and expressed as

$$I_{DO2B} = \frac{D_{m1}^2 \cdot V_{CB}^2}{2f_S L_{M2} V_O} \,. \tag{3.9}$$

Furthermore, as  $I_O$  is smaller than the boundary value in (3.7),  $M_2$  mode shows in the operation of the proposed converter as plotted in Fig. 3.2(b). From the equality  $I_{DO2} = I_{DO2B}$  and (3.1b), the transition angle  $\theta_T$  from  $M_1$  to  $M_2$  mode can be expressed as

$$\theta_T = \omega_L \cdot t_T = \sin^{-1} \left[ \sqrt{\frac{2f_s (L_B + L_{M1})^2 V_O}{L_{M1} D_{m1}^2 V_{inpk}^2} (I_O - I_{DO2B})} \right].$$

(3.10)

As  $I_O$  gets smaller, the interval of M<sub>2</sub> becomes wider and M<sub>1</sub> becomes narrower. It can also be seen from (2.9) that  $\langle i_{DO1}(t) \rangle$  reaches zero at line voltage phase being 0 and  $\pi$  and from (3.1b) that  $\langle i_{DO2}(t) \rangle$  reaches maximum at the same time. Thus, as  $I_O$  gets smaller than the boundary value of (3.9), the converter would work in M<sub>2</sub> mode only during a half line cycle. Consequently, for case II operation that the converter works in both M<sub>1</sub> and M<sub>2</sub> modes in a half line cycle,  $I_O$  will be in the range of

$$I_{D01PK} + I_{D02B} \ge I_0 \ge I_{D02B}.$$

(3.11)

Besides, for case III operation that the converter works only in  $M_2$  mode in a half of a line cycle,  $I_0$  is smaller than the boundary value

$$I_{DO2B} \ge I_o. \tag{3.12}$$

Based on above discussion, the theoretical currents and voltages waveforms for the cases I to III examples are illustrated in Fig. 3.2(a)-(c) and the corresponding parameters used are shown in Table 3.3. For the case I operation, the value of  $L_{M2}$  in (3.9) is intentionally selected a large one so that (3.7) can be satisfied and case I operation can present. For the other parameters,  $L_B$ ,  $L_{M1}$ ,  $n_1$ , and  $n_2$ , they are selected according to the procedure described in Section

3.4 so that cases II and III can be activated.

From Fig. 2.6 and Fig. 3.2(a)-(c), it can be seen that the average input current  $\langle i_{in}(t) \rangle$  is divided into  $\langle i_{DI1}(t) \rangle$  and  $\langle i_{DB}(t) \rangle$  through the operation of boost-flyback semi-stage. Among these two currents,  $\langle i_{DI1}(t) \rangle$  is transformed to  $\langle i_{DO1}(t) \rangle$  by the flyback cell, and then transferred to  $R_L$  directly. Alternatively,  $\langle i_{DB}(t) \rangle$  is mainly buffered in C<sub>B</sub> during  $v_{in}$  peak, then transformed to  $\langle i_{DO2}(t) \rangle$  by the flyback DC/DC semi-stage, and then transferred to  $R_L$  for output regulation. The output current  $I_O$  is primarily supplied by  $\langle i_{DO2}(t) \rangle$  in low line voltage duration.

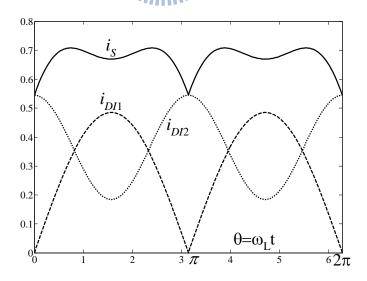

The switch current of conventional cascade S<sup>4</sup> converter like [3] mainly composed of inductor current of the boost-ICS semi-stage and the transformer primary current of the flyback semi-stage. Both semi-stages have to handle the whole input power. Hence, the peak switch current is doubled and reaches peak value when input power is the maximum and occurs at  $\theta = \omega_L \cdot t = \pi/2$ . In Fig. 2.6, the average switch current  $\langle i_S(t) \rangle$  of the proposed converter is the sum of  $\langle i_{Dl1}(t) \rangle$  and  $\langle i_{Dl2}(t) \rangle$ , and can be expressed as

$$\langle i_{s}(t)\rangle = \langle i_{D11}(t)\rangle + \langle i_{D12}(t)\rangle, \qquad (3.13)$$

where both  $\langle i_{DI1}(t) \rangle$  and  $\langle i_{DI2}(t) \rangle$  represent the charged current of the first semi-stage from line input and the transformer primary current of second semi-stage from bulk capacitor, and can be obtained from Fig. 2.7(b) as

$$\langle i_{DI1}(t) \rangle = \langle i_{LB}(t) \rangle - \langle i_{DB}(t) \rangle, \qquad (3.14)$$

and

$$\langle i_{DI2}(t) \rangle = \frac{V_O}{V_{CB}} \langle i_{DO2}(t) \rangle = \frac{V_O}{V_{CB}} (I_O - \langle i_{DO1}(t) \rangle).$$

(3.15)

It can be seen from (3.13) and (3.15) that if  $\langle i_{DO1}(t) \rangle$  increases, more output current will be provided by flyback cell, and  $\langle i_S(t) \rangle$  will be reduced. Contrarily, if flyback cell is absent (i.e.  $\langle i_{DO1}(t) \rangle = 0$ ), the circuit in Fig. 2.6(b) will be reduced to a conventional S<sup>2</sup> converter [3]. Furthermore, from Fig. 2.7(b),  $\langle i_{DI1}(t) \rangle$  can be further obtained as

$$\langle i_{DI1}(t) \rangle = \frac{i_{pk1} \cdot d}{2} = \frac{d^2 V_{inpk} \sin(\omega_L \cdot t)}{2f_s(L_B + L_{M1})}.$$

(3.16)

Substituting (2.9) into (3.4) and the result is substituted into (3.15),  $\langle i_{DI2}(t) \rangle$  for M<sub>1</sub> mode can be further expressed as

$$\langle i_{DI2}(t) \rangle = \frac{V_O}{V_{CB}} \left( I_O - \frac{L_{M1} D_{m1}^2 V_{inpk}^2 \sin^2(\omega_L t)}{2f_S (L_B + L_{M1})^2 V_O} \right).$$

(3.17)

Substituting (3.5) into (3.15),  $\langle i_{DI2}(t) \rangle$  for M<sub>2</sub> mode can be further obtained as

$$\langle i_{DI2}(t) \rangle = \frac{d^2 \cdot V_{CB}}{2f_S L_{M2}} \Big|_{d=d_{m2}},$$

(3.18)

where  $d_{m2}$  can be obtained from (3.6). It can be seen from (3.16)-(3.18) and Fig. 3.3 that  $\langle i_{DI1}(t) \rangle$  reaches local maximum at  $\theta = \omega_L \cdot t = \pi/2$  while  $\langle i_{DI2}(t) \rangle$  is minimum, and  $\langle i_{DI2}(t) \rangle$  reaches local maximum at  $\theta = \omega_L \cdot t = 0$  or  $\pi$  while  $\langle i_{DI1}(t) \rangle$  is zero. Therefore, the power processed by flyback cell is transferred to load directly and would not be processed by the switch again, the local maximum current stresses due to direct and indirect power do not appear at the same time during half line cycle, so the overall current stress of main switch compared small with that of conventional S<sup>4</sup> converter.

Fig. 3.1 Parallel boost-flyback-flyback converter: (a) Implementation circuit, (b) DC/DC semi-stage waveform in M<sub>1</sub> mode, and (c) DC/DC semi-stage waveform in M<sub>2</sub> mode.

| Mode           | $M_1$    | $M_2$    | <b>M</b> <sub>3</sub> | $M_4$               | $M_5 \ldots M_8$ |

|----------------|----------|----------|-----------------------|---------------------|------------------|

| $L_B$          | DCM      | DCM      | ССМ                   | CCM                 | CCM/DCM          |

| <b>T</b> 1     | DCM      | DCM      | DCM                   | DCM                 | ССМ              |

| T <sub>2</sub> | ССМ      | DCM      | ССМ                   | DCM                 | CCM/DCM          |

|                | Self PFC | Self PFC | Allowed under CL. D   | Allowed under CL. D | Not happen       |

Table 3.1 Various operation modes in the proposed circuit

Table 3.2 Various cases in the proposed circuit

| Case | Mode                            | $V_{ac}$ | $P_{out}$ |  |

|------|---------------------------------|----------|-----------|--|

| Ι    | $M_1$                           | Low      | High      |  |

| Ш    | M <sub>1</sub> + M <sub>2</sub> | Medium   | Medium    |  |

| III  | M <sub>2</sub> ES               | High     | Low       |  |

|      |                                 |          |           |  |

Table 3.3 The corresponding parameters of cases I-III illustration example

| Case | $L_B$         | $L_{M1}$       | $n_1$ | $L_{M2}$ | <i>n</i> <sub>2</sub> | $V_{ac}$             | $V_O$ | Pout | $f_{S}$ | $f_L$ | V <sub>CB</sub> |

|------|---------------|----------------|-------|----------|-----------------------|----------------------|-------|------|---------|-------|-----------------|

| Ι    | 35 <i>µ</i> H | 135 <i>µ</i> H | 1.2   | 4 mH     | 1.4                   | 85 V <sub>rms</sub>  | 54 V  | 70 W | 100 kHz | 60 Hz | 128.5 V         |

| II   | 30 <i>µ</i> H | 150 <i>μ</i> Η | 1.6   | 1.5 mH   | 1.9                   | 265 V <sub>rms</sub> | 54 V  | 50 W | 100 kHz | 60 Hz | 444.5 V         |

| III  | 30 µ H        | 150 μ H        | 1.6   | 1.5 mH   | 1.9                   | $265 \ V_{rms}$      | 54 V  | 20 W | 100 kHz | 60 Hz | 449.9 V         |

(b)

(Continued on next page)

Fig. 3.2 Main waveforms of parallel boost-flyback-flyback converter in a line cycle: (a) case I ( $M_1$  mode only), (b) case II (both  $M_1$  and  $M_2$  modes), and (c) case III ( $M_2$  mode only).

Fig. 3.3 Average switch current for case I.

## 3.2 Power Distribution and Bulk Capacitor Voltage

In the proposed S<sup>2</sup> PPFC scheme shown in Fig. 2.5, the power distribution between the direct ( $p_1$ ) and indirect power ( $p_2$  or  $p_3$ ) processing paths is one of the important design considerations since it affects not only the converter efficiency but also the power ratings required to the components in each processing power path. Besides, in the indirect power path, the energy balance between the power flow into ( $p_2$ ) and out ( $p_3$ ) of bulk capacitor determines the bulk capacitor voltage, which can be very high if not properly design. Based on the above design considerations, the power distribution will be analyzed according to the implementation circuit shown in Fig. 2.6(b), and hence the formula related to power distribution and bulk capacitance voltage can be derived. They are formulated as follows:

The input power  $p_{in}$  is composed of  $p_1$  and  $p_2$ ,

$$p_{in}(\theta) = v_{in}(t) \langle i_{LB}(t) \rangle = p_1(\theta) + p_2(\theta).$$

(3.19)

The direct power processed by flyback semi-stage is given by

$$p_{1}(\theta) = v_{in}(t) \frac{L_{M1}}{L_{B} + L_{M1}} \langle i_{DI1}(t) \rangle = V_{O} \langle i_{DO1}(t) \rangle .$$

(3.20a)

Substitution of  $\langle i_{DO1}(t) \rangle$  given by (2.9) to (3.20a) gives

$$p_1(\theta) = 2k_p P_{out} \sin^2 \theta , \qquad (3.20b)$$

where

$$k_{p} = \frac{P_{1,pk}(d)}{P_{out}} = \frac{L_{M1}d^{2}V_{inpk}^{2}}{4f_{s}(L_{B} + L_{M1})^{2}P_{out}},$$

(3.21)

and

$$P_{1,pk}(d) = \frac{L_{M1}d^2 V_{inpk}^2}{4f_s (L_B + L_{M1})^2}.$$

(3.22)

In  $M_1$  mode,  $k_p$  is a constant and can be found by

$$k_{p} = k_{p} \Big|_{d = D_{m1}} = K_{P1}.$$

(3.23)

In M<sub>2</sub> mode,  $k_p$  is a function of  $\theta$  and obtained by

$$k_{p} = k_{p} \Big|_{d = d_{m2}(\theta)} = k_{p2}(\theta) = \frac{L_{M1} \cdot V_{inpk}^{2}}{2 \Big[ L_{M1} V_{inpk}^{2} \sin^{2} \theta + \frac{V_{CB}^{2}}{L_{M2}} (L_{B} + L_{M1})^{2} \Big]}.$$

(3.24)

It can be seen from (3.24) that  $k_{p2}$  is independent of  $P_{out}$ . The values of  $D_{m1}$  and  $d_{m2}$  can be obtained from (3.3) and (3.6).

The indirect power processed by boost semi-stage from  $L_B$  to  $C_B$  is given by:

$$p_2(\theta) = V_{CB} \langle i_{DB}(t) \rangle. \tag{3.25a}$$

Substitution of  $\langle i_{DB}(t) \rangle$  given by (2.12) into (3.25a) gives

$$p_{2}(\theta) = \frac{M_{CB} \sin^{2} \theta}{M_{CB} - |\sin \theta|} \frac{2k_{p} P_{out}}{K_{M1}},$$

(3.25b)

where  $K_{M1}$  is called inductance ratio and expressed as

$$K_{M1} = \frac{L_{M1}}{L_B} \,. \tag{3.26}$$

The dimensionless variable  $M_{CB}$  in (2.13) in (3.25b) can be regarded as the normalized  $V_{CB}$  with respect to  $V_{inpk}$ . In practice, the true value of  $V_{CB}$  is lower than the theoretical value because of presence of the equivalent series resistance (ESR) of inductance and capacitor. Thus, in order to avoid the bulk capacitor voltage  $V_{CB}$  from exceeding the limitation voltage, 450 V, of the commercial capacitor, it is suggested that  $M_{CB}$  had better been controlled below or just equal to 1.2 for  $V_{ac}$ =265 V<sub>rms</sub>. Furthermore, the indirect power processed by flyback DC/DC semi-stage from  $C_B$  can be expressed as

$$p_{3}(\theta) = V_{o} \langle i_{DO2}(t) \rangle = P_{out} - p_{1}(\theta) = P_{out} (1 - 2k_{p} \sin^{2} \theta).$$

(3.27a)

Substituting (3.5) into (3.27a),  $p_3$  for M<sub>2</sub> mode can be expressed as

$$p_{3}(\theta) = \frac{d^{2} \cdot V_{CB}^{2}}{2f_{S}L_{M2}}\Big|_{d=d_{m2}} = \frac{d^{2} \cdot \left(M_{CB} \cdot V_{inpk}\right)^{2}}{2f_{S}L_{M2}}\Big|_{d=d_{m2}}.$$

(3.27b)

Since  $p_1$  and  $p_2$  (or  $p_3$ ) vary with  $\theta = \omega_L \cdot t$ , they would be expressed as

$$P_{x,ave}\Big|_{x=1,2,3} = \frac{1}{\pi} \int_0^{\pi} p_x(\theta) d\theta \Big|_{x=1,2,3}.$$

(3.28)

Therefore, direct power ratio  $K_{DP}$  is defined as

$$K_{DP} = \frac{P_{1,ave}}{P_{out}} \,. \tag{3.29}$$

In this equation, high  $K_{DP}$  implies high efficiency and large utilization performance of T<sub>1</sub>. Because the average power sent to and out from  $C_B$  are equal for a half line cycle, the indirect power ratio  $K_{IDP}$  can be defined as

$$K_{IDP} = \frac{P_{2,ave}}{P_{out}} = \frac{P_{3,ave}}{P_{out}} = 1 - K_{DP}.$$

(3.30)

The more detailed indirect power ratio expressions defined in (3.30) for three cases can be derived as shown in Table 3.4 by substituting (3.25b) and (3.27a) into (3.28) and normalizing with  $P_{out}$ . By using iterative approaching methodology for obtaining accurate  $M_{CB}$ , the detailed expressions in Table 3.4 are calculated repeatedly until (3.30) is satisfied, and  $K_{DP}$ ,  $K_{IDP}$ , and  $M_{CB}$  can be solved consequently. Following the iterative calculation process, the curves of direct power ratio  $K_{DP}$  versus output power  $P_{out}$  for different line input voltage  $V_{ac}$  and operation cases are obtained and shown in Fig. 3.4, and the curves are obtained by taking the converter parameters in Table 3.3-case I as an example. It can be seen from Fig. 3.4 that the relation between  $K_{DP}$  and case is  $(K_{DP})_{II} \times (K_{DP})_{II} \cdot (K_{DP})_{II}$ .  $K_{DP}$  increases as  $P_{out}$  is low or  $V_{ac}$  is high.

The curves of  $K_{DP}$  and  $M_{CB}$  versus  $P_{out}$  for different  $K_{M1}$  and  $L_{M2}$  at the assigned conditions of the converter,  $L_{M1}$ =150  $\mu$  H,  $n_2$ =1.7,  $V_{ac}$ =265  $V_{rms}$ , and  $V_O$ =54 V, are shown in Fig. 3.5. Substituting (3.19) into case III of Table 3.4,  $M_{CB}$  obtained from (3.30) is independent of  $P_{out}$ . Hence, each  $M_{CB}$  curve in Fig. 3.5(b) is horizontal when converter operates in case III. From Fig. 3.5(a), it can be seen that  $K_{DP}$  is greater at low output power. That is to say,  $K_{IDP}$  rises as output power increases. This implies that the direct power is the main portion providing the load and the indirect power is regarded as energy reservoir used for regulating the power flow to load. Besides, it can be seen from Fig. 3.5(b) that  $M_{CB}$  increases as  $P_{out}$  decreases, and approaches and holds to the maximum value at lighter load. This phenomenon shows that high bulk capacitor voltage will be resulted at high line and case III. However, from Fig. 3.5, it also can be seen that  $K_{DP}$  goes up and  $M_{CB}$  slides down as  $K_{M1}$  increases. This is because more input power goes through flyback cell without being buffered by  $C_B$ . Hence, for the purpose of obtaining high efficiency and low  $V_{CB}$  it is better to select  $K_{M1}$  as large as possible. Furthermore, the decrease of  $L_{M2}$  can lower both  $K_{DP}$  and  $M_{CB}$  since it can be seen from (3.5) that low  $L_{M2}$  will result in large current  $i_{DO2}$  for M<sub>2</sub> mode, or equivalently to say that the output power ratio provided by  $C_B$  will be increased. In other words, more output power comes from buffered energy and less input power passes through flyback cell, so this will result in lower efficiency. However, it is good for reducing the maximum value of  $M_{CB}$  since more power is continuously sent out from  $C_B$ . Therefore,  $M_{CB}$  has to be lower to achieve half line cycle average indirect power balance in (3.30) as can be seen from (3.25b) and (3.27b). Besides, decreasing  $L_{M2}$  would cause flyback DC/DC semi-stage closer to DCM but make worse output voltage regulation. A compromise is suggested for selecting proper value of  $L_{M2}$  in considering of the proper values of  $V_{CB}$ ,  $K_{DP}$ , and output voltage regulation. It can be seen from Fig. 3.5 that curves (1) and (2) have high  $K_{DP}$  and the maximum values of  $M_{CB}$  are below or close to 1.2 among all curves. Thus, with the consideration of obtaining high efficiency and low  $V_{CB}$ , curves (1) and (2) are better choices.

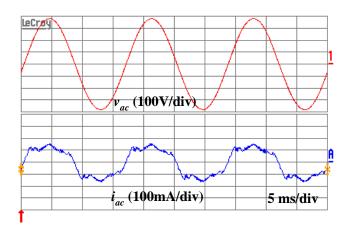

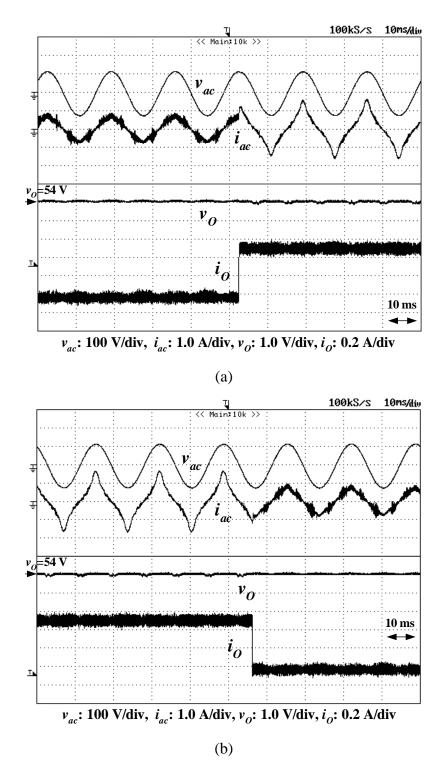

| Case | P2,ave/Pout                                                                                                                                                                                                                                                                                   | P <sub>3,ave</sub> /P <sub>out</sub>                                                                                                                                                           |