# 國立交通大學電子工程學系電子研究所

博士論文

運用於射頻系統封裝應用之異質整合技術開發 Development of Heterogeneous Integration Technology for RF System-on-Package Applications

研究生: 趙子元

指導教授:鄭裕庭 教授

中華民國 一〇一 年 二 月

### 運用於射頻系統封裝應用之異質整合技術開發

Development of Heterogeneous Integration Technology for RF System-on-Package Applications

研究生:趙子元 Student:Tzu-Yuan Chao

指導教授: 鄭裕庭教授 Advisor: Prof. Yu-Ting Cheng

Submitted to Department of Electronics Engineering and

Institute of Electronics

College of Electrical and Computer Engineering

National Chiao Tung University

in Partial Fulfillment of the Requirements

for the Degree of Doctor of Philosophy

in Electronics Engineering

February 2012

Hsinchu, Taiwan, Republic of China

中華民國 一〇一 年 二 月

# 運用於射頻系統封裝應用 之異質整合技術開發

學生: 趙子元 指導教授: 鄭裕庭教授

國立交通大學電子工程學系 電子研究所 博士班

摘 要

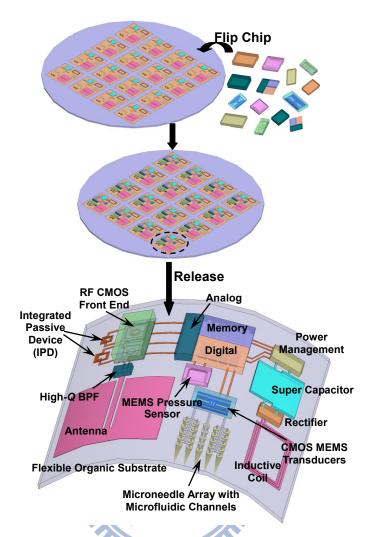

在不久後的將來,由於材料特性與元件結構的自然限制,矽基互補式金屬氧化物半 導體(CMOS)技術的持續微小化將不再遵守摩爾定律(Moore's Law)之預測而達到其終 點。例如,當通道長度低於 9 奈米時,金氧半場效電晶體(MOSFET)將表現出較大的漏電 流從而導致功率消耗之增加。相較於 CMOS 技術的微小化,在微電子系統的發展中,一 個新興的技術趨勢在於實現超越摩爾定律(More than Moore)之目標,對於未來微電子 系統的效能提升,主要將集中於系統整合之技術發展而非電晶體密度之增加來創造高附 加價值與功能多樣化之微電子系統。因此,系統封裝(SOP)將成為一個非常重要的技術 發展方向來整合 CMOS 與 non-CMOS 元件,例如無線被動元件、感測器與制動器、微流道... 等,於一個單一封裝體之中。此篇博士論文之目標即為開發應用於下一世代高效能、低 成本智慧型系統製造的射頻系統封裝(RF SOP)之關鍵技術發展。憑藉著系統封裝的優點 可進一步將現有組裝了大量元件的龐大電路板縮小在一個微型封裝基板中,此優點伴隨 著一個技術挑戰,其技術難度在於如何整合所有的 CMOS 晶片於封裝基板之上並且具有 低損耗與低寄生效應的連接特性,特別是在射頻系統整合方面,為了克服這個困境,在 此論文中首先提出用於異質晶片整合(Heterogeneous chip integration)之金-金熱壓 接合(Au-Au thermocompressive bonding)技術,此技術可以提供一個低損耗的連接而不 需要在電性轉接結構上採用複雜的結構設計或額外的阻抗匹配,從 DC 到 50GHz 頻率範 圍可具有低於-15dB 的返回損失及-1.8dB 的插入損失。為了展現此連接技術在射頻微機 電異質晶片整合的可行性,一個低功率射頻低雜訊放大器(Low noise amplifier)藉由

整合 TSMC 0.18-µm RF CMOS 晶片與製作有高品質因子微機電式電感(high-Q MEMS Inductor)的矽載具(Si carrier)被提出來,此連接技術與矽載具系統封裝應用方案也可以使用在其他微電子封裝應用,例如:軟性電子,光電,微機電系統…等。

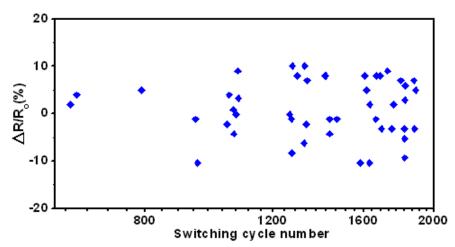

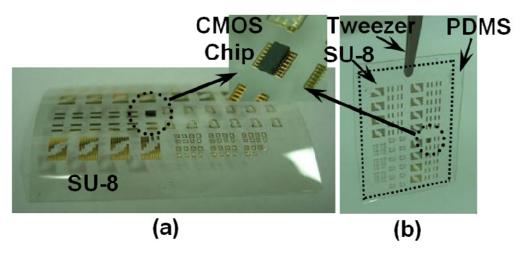

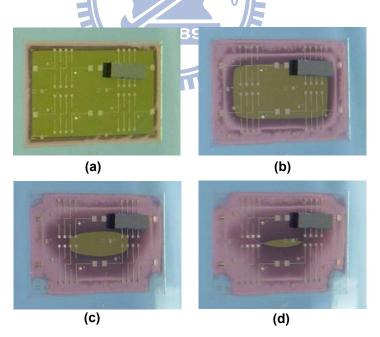

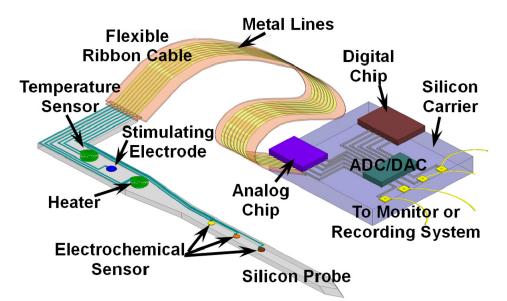

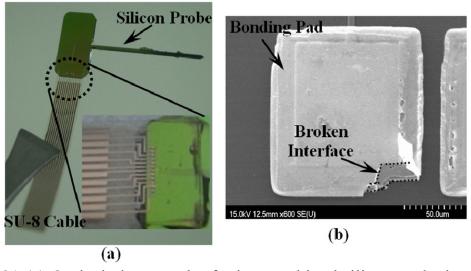

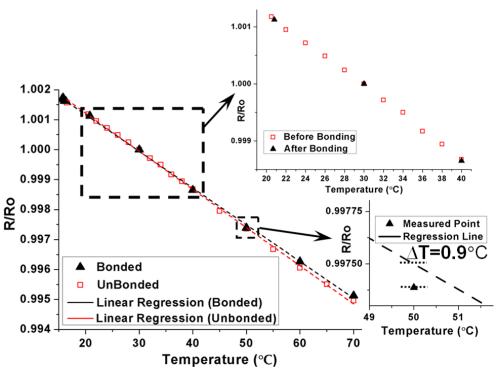

在此論文中,軟性電子應用(Flexible electronics)是另一個研究主題之概念展示。以軟性微電子整合為例,首先提出了先進 SU-8 微加工製程來展現嵌入元件在軟性基板的可行性,利用此製程可使製作微機電串聯式切換器(MEMS serial switch)之製程溫度低於 135°C。提出之 SU-8 微機電切換器為靜電力驅動之兩端固定 SU-8 樑結構,高頻特性方面在 12GHz 可提供-28. 2dB 之高隔離度,若製作於 100公·cm 之矽晶圓之上由於降低了基板損失則預期具有低於-0. 75dB 之插入損失。此外,與先前矽基射頻系統封裝概念相同,吾人發展並提出一個低成本晶圓級軟性微系統整合技術來實現軟性射頻系統封裝,此技術合併先前開發之無凸塊射頻系統封裝連接方案與特殊的表面清潔製程來達成接合溫度低於 200°C 之 CMOS 晶片組裝於 SU-8/PDMS 有機基板之上。射頻轉接結構在有機基板上同樣展現低損耗的特性,在 40GHz 有大約-15dB 返回損失與-0. 8dB 插入損失。此外,相同的整合製程被利用來整合生醫矽探針與 SU-8 軟性帶狀排線以提供可靠的信號傳輸至人體外部之讀取設備。同時,利用金化學惰性的優點,晶圓級犧牲層釋放製程也被提出來實現未來低成本批次製造之軟性微系統。

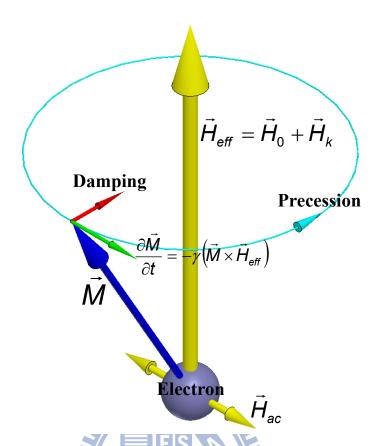

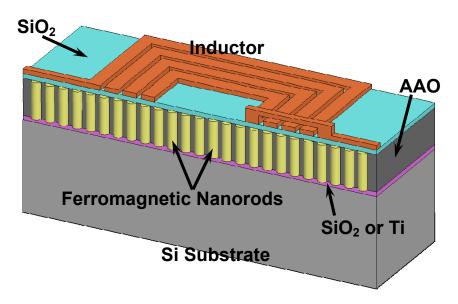

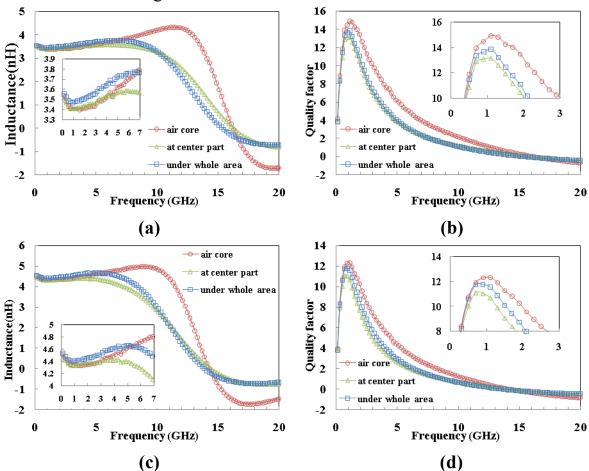

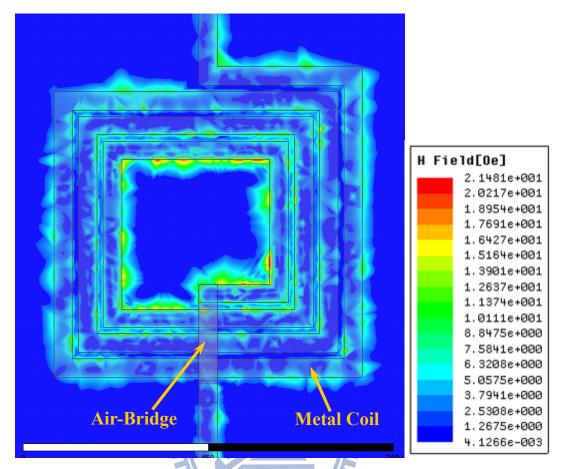

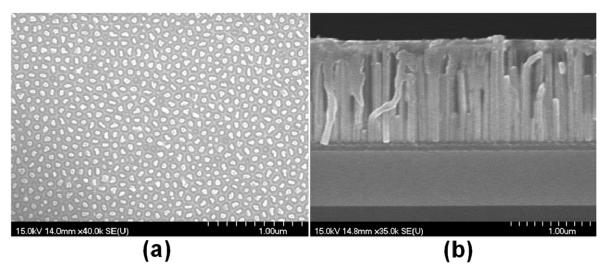

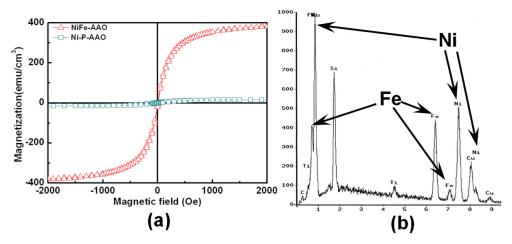

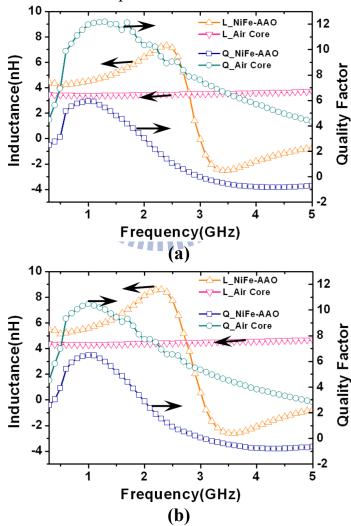

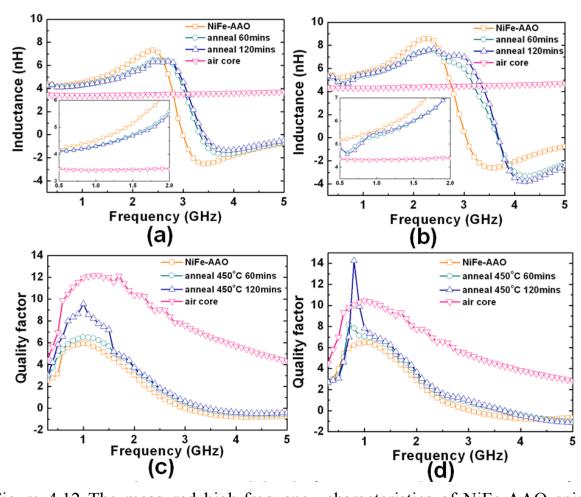

除了組裝晶片於封裝基材之上,在射頻系統封裝的進展上,發展高效能嵌入式被動元件是非常關鍵的,因此,在論文的最後部分,吾人研究並提出整合鐵磁性鐵芯之晶片式螺旋電感,晶片式電感被大量使用於射頻積體電路(RFIC)的設計上,然而,電感通常佔據大部分矽晶片之面積且無法隨著 CMOS 技術的進步而縮小,同時,電感的性能會受到如導體結構的電阻損耗(resistive loss)與矽基板損耗(substrate loss)等自然限制,因此吾人提出合併磁性奈米複合材料,包括鎮-磷-陽極氧化鋁(Ni-P-AAO)與鎳鐵-陽極氧化鋁(NiFe-AAO)材料,來作為晶片式電感之感應鐵芯以提升電感值,使用NiFe-AAO 奈米複合磁性鐵芯之螺旋電感在 GHz 頻率可提升約 25%之電感值並且沒有大幅的品質因子降低,本論文將提出相關磁性奈米複合薄膜之詳細實驗流程與奈米複合電感之整合製程與量測討論。

# Development of Heterogeneous Integration Technology for RF System-on-Package Applications

Student: Tzu-Yuan Chao Advisors: Prof. Yu-Ting Cheng

Department of Electronics Engineering and Institute of Electronics National Chiao Tung University

#### **ABSTRACT**

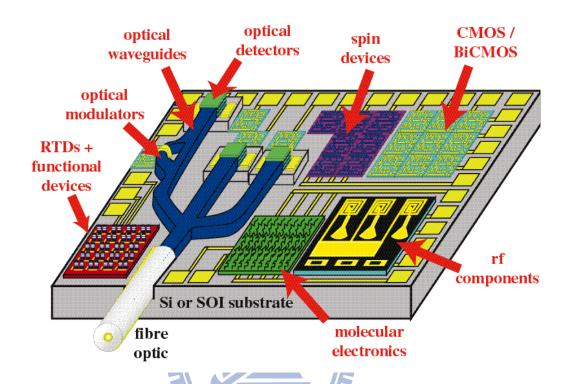

THE PARTY OF THE P

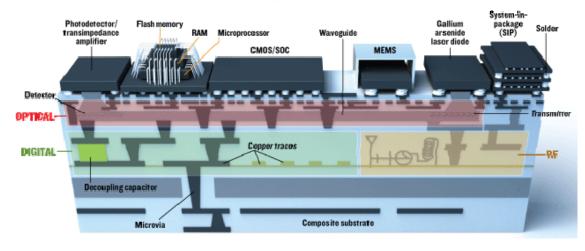

In the near future, the continuous downscaling of Si-based CMOS technology will not follow the Moore's Law and would reach its endpoint owing to the nature limitation of the material property and device structure. For instance, MOSFET channel lengths below 9 nm will exhibit higher leakage currents leading to increased power consumption. Instead of the CMOS scaling, an emerging technology trend in the development of microelectronics system is aimed to realize the goal of "More than Moore", indicating the future performance improvement of an microelectronic system would mainly focus on the technology of system integration rather than transistor density increase for creating high value and functional diversification of microelectronics systems. Thus, the integration of CMOS and non-CMOS based components, such as wireless passive components, sensors and actuators and microfluidic channel and so on, within a single package, i.e. system-on-package (SOP), would

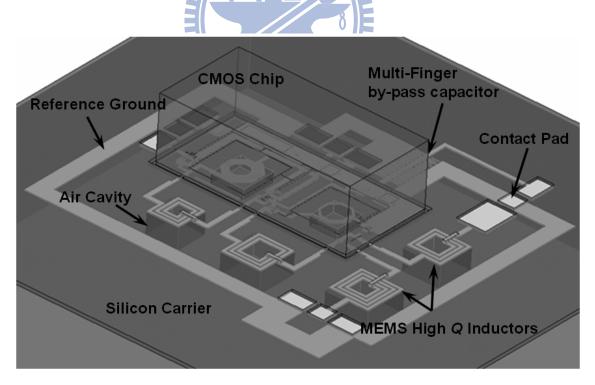

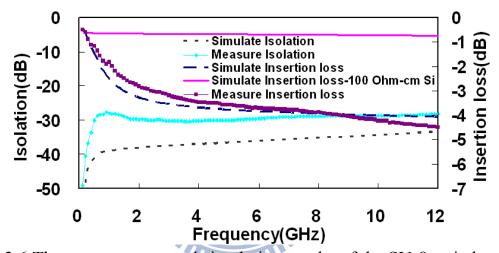

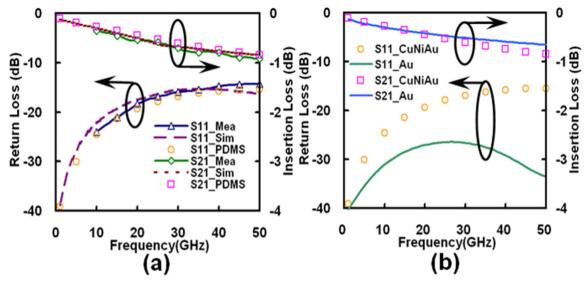

become an important technology development direction. The objective of the dissertation is to develop the key technologies of radio frequency SOP for the next generation high performance and low cost smart system fabrication. The virtue of SOP is aimed to further shrink a bulky circuit board assembled with components into a miniature packaging substrate. The virtue would come with a technical challenge which is the difficulty in the integration of a packaging substrate with all CMOS chips with low loss and low parasitic of interconnections, especially in RF system integration. To overcome this predicament, interconnecting technology using Au-Au an an thermocompressive bond is presented first in the dissertation for the heterogeneous chip integration. This technology can provide a low loss interconnection which is less than -15 dB return loss and -1.8 dB insertion loss up to 50 GHz without implementing complex structure designs and extra impedance matching networks in the electrical transition. A low-power RF low-noise amplifier by integrating a TSMC 0.18-µm RF CMOS chip with a silicon carrier substrate, where high Q MEMS inductors are fabricated, is proposed to demonstrate the feasibility of the interconnecting technology for RF MEMS heterogeneous chip integration. Such an interconnecting and the Si carrier SOP application schemes can be also applied to the other microsystem packaging applications like flexible electronics, optoelectronics, MEMS and so In the dissertation, flexible electronic application is another subject for the concept demonstration. For the case of flexible microsystem integration, a novel SU-8 micromachining process for MEMS series switch fabrication with processing temperature lower than 135°C is presented first to show the feasibility to embed devices in a flexible substrate. The proposed SU-8 MEMS switch is designed with a clamped-clamped SU-8 beam structure driven by

electrostatic force. The switch can exhibit better than -28.2 dB isolation up to 12 GHz and expect to have -0.75 dB insertion loss as long as the substrate resistivity is increased up to 100  $\Omega$ ·cm resulting in lower substrate loss. a low-cost wafer-level flexible microsystem integration technology is developed and presented for the ultimate realization of flexible RF SOP same concept as the prior Si-based RF SOP. The technology combines the previously developed bumpless RFSOP interconnection scheme with a special surface cleaning process to assemble a CMOS chip with an organic substrate (SU-8/PDMS) that the bonding temperature less than 200°C. The RF transition on the organic substrate also provides a low loss performance about -15dB return loss and -0.8dB insertion loss at 40GHz. In addition, the same integration process is utilized to integrate the biomedical Si probe with an SU-8 flexible ribbon cable for providing a reliable signal transmission to the instrument reader outside human body. Meanwhile, by taking advantage of chemical inertia of Au, a wafer-level sacrificial release process is also proposed and performed for future low-cost batch fabrication of flexible microsystem. In addition to the assembly of chips onto a packaging substrate, developing high performance embedded passive components is very critical in the advancement of RF SOP technology. Thus, in the last part of the dissertation, on-chip spiral inductor with ferromagnetic core is developed, investigated, and presented. On-chip inductors have been extensively used in the design of Radio Frequency Integrated Circuits (RFICs). It, however, occupies a large silicon chip area which cannot be scaled with the advancement of CMOS technology. Meanwhile, the performance of the inductor suffers with its nature limitation owing to resistive loss of its conducting structure and silicon substrate loss. inductance enhancement scheme is then proposed to incorporate magnetic

nanocomposite materials including Ni-P-AAO and NiFe-AAO with on-chip inductors as the inductive cores. The spiral inductor using a NiFe-AAO nanocomposite magnetic core can have more than 25% inductance enhancement without tremendous Q degradation to GHz range. The detail experimental procedures of synthesis and characterization of magnetic nanocomposite films, the integration process of nanocomposite inductors, and the related measurements and discussions are all presented in this dissertation.

#### 誌謝

在交大待了許多年,感謝許多人的幫助,讓我可以順利完成我的博士學業。首先我要感謝我的父母、姐姐、妹妹的支持與包容,讓我沒有後顧之憂得以專心進行博士論文的研究。謝謝吳媽媽、阿弼、弟弟的關心,以及禹夢的陪伴與照顧,這些都是我最後終能完成博士生涯的主要原因。

在論文的研究方面,感謝指導老師鄭裕庭教授不論在研究、論文寫作、生涯規劃、待人處世…等各方面的協助與建言。郭建男教授、CIC張大強博士在合作計畫中的幫忙與指導。以及各位口試委員願意在百忙之中替我口試,讓我的口試可以順利進行並給予不少有用的建議。此外,徐文祥教授研究群、郭建男教授研究群、張翼教授研究群、陳智教授研究群、CIC、NDL、交大奈米中心的技術員阿姨、清大奈科中心、自強基金會…等不論在實驗儀器或是量測設備上的提供與支持,讓我能夠在有限的資源中完成我的研究。

最後感謝所有待過 MIL 的學長、同學、學弟、學妹, 所有在交大這幾年裡認識的人, 由於人數眾多請恕我沒有一一列出, 因為你們的存在讓我的博士生涯變的沒有那麼苦悶, 十分感謝!

## Table of Contents

| Chinese Abstract  |                                                                                     | i    |

|-------------------|-------------------------------------------------------------------------------------|------|

| English Abstract  |                                                                                     | iii  |

| Acknowledgement   |                                                                                     | vii  |

| Table of Contents |                                                                                     | viii |

| List of Tables    |                                                                                     | X    |

| List of Figures   |                                                                                     | xi   |

| Chapter 1         | Introduction                                                                        |      |

| 1.1               | Overview                                                                            | 1    |

| 1.2               | Organization of the Dissertation                                                    | 7    |

| Chapter 2         | An Interconnecting Technology for RF MEMS Heterogeneous Chip Integration            |      |

| 2.1               | Introduction                                                                        | 10   |

| 2.2               | Bumpless Interconnect Scheme·····                                                   | 14   |

| 2.3               | Test Structure Design                                                               |      |

| 2.3.1             | DC Contact and RF Transition Structure                                              | 17   |

| 2.3.2             | Ultrawideband Low-Noise Amplifier (UWB LNA) and Si Carrier Design                   | 18   |

| 2.4               | Fabrication Process 6                                                               |      |

| 2.4.1             | Bonding Metallization                                                               | 20   |

| 2.4.2             | Si Carrier Fabrication ·····                                                        | 21   |

| 2.5               | Results and Discussions                                                             |      |

| 2.5.1             | Bumpless Interconnect Bonding                                                       | 22   |

| 2.5.2             | Electrical Characterizations of the DC Contact and the RF Transition Structure      | 23   |

| 2.5.3             | UWB LNA with MEMS Inductors                                                         | 24   |

| 2.5.4             | Discussions                                                                         | 25   |

| 2.6               | Summary·····                                                                        | 26   |

| Chapter 3         | SU-8-Based Low-temperature Fabrication Process for Flexible Microsystem Fabrication |      |

| 3.1               | Introduction·····                                                                   | 39   |

| 3.2               | An SU-8 Serial MEMS Switch                                                          |      |

| 3.2.1             | Switch Design and Fabrication Process                                               | 41   |

| 3.2.2             | Experimental Results and Discussions·····                                           | 44   |

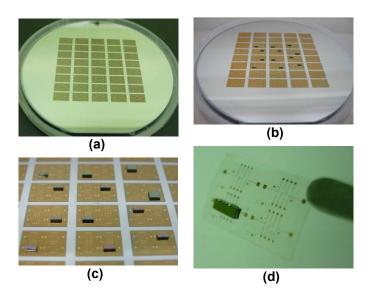

| 3.3               | Heterogeneous Chip Integration Process                                              | 47   |

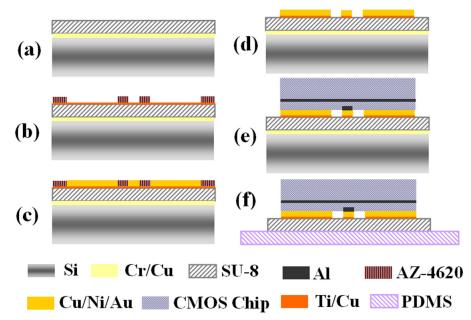

| 3.3.1             | Integration Process ······                                                          | 49   |

| 3.3.2            | Results and Discussions                             | 51  |  |  |  |  |

|------------------|-----------------------------------------------------|-----|--|--|--|--|

| 3.4              | An SU-8 Flexible Ribbon Cable 5                     |     |  |  |  |  |

| 3.4.1            | Flexible Interconnection Design and Fabrication 5   |     |  |  |  |  |

| 3.4.2            | Results and Discussions 5                           |     |  |  |  |  |

| 3.5              | Summary                                             | 60  |  |  |  |  |

| Chapter 4        | Ferromagnetic-AAO Nanocomposite for                 |     |  |  |  |  |

|                  | Performance Enhancement of On-Chip Spiral Inductors |     |  |  |  |  |

| 4.1              | Introduction ·····                                  | 74  |  |  |  |  |

| 4.2              | Ni-P-AAO Nanocomposite                              |     |  |  |  |  |

| 4.2.1            | Synthesis and Characterization·····                 | 79  |  |  |  |  |

| 4.2.2            | Inductor Fabrication·····                           | 81  |  |  |  |  |

| 4.2.3            | Measurement and Discussion                          | 82  |  |  |  |  |

| 4.3              | NiFe-AAO Nanocomposite                              |     |  |  |  |  |

| 4.3.1            | Synthesis and Characterization                      | 84  |  |  |  |  |

| 4.3.2            | Measurement and Discussion                          | 85  |  |  |  |  |

| 4.4              | Summary                                             | 87  |  |  |  |  |

| Chapter 5        | Conclusion and Future Research Direction            |     |  |  |  |  |

| 5.1              | Conclusion                                          | 97  |  |  |  |  |

| 5.2              | Future Research Direction                           | 99  |  |  |  |  |

| Reference        |                                                     | 101 |  |  |  |  |

| Curriculum Vitae |                                                     | 110 |  |  |  |  |

| Publication List |                                                     | 111 |  |  |  |  |

## List of Tables

| Chapter 2        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 2.1        | Comparison of Au Bump, Au Stud Bump, and Ni/Au Bumpless Processes [49,50]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 38 |

| Chapter 3        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| Table 3.1        | Surface element content analysis by XPS before and after acidic surface cleaning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 69 |

| Table 3.2        | Specific contact resistance vs. bonding temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 69 |

| Table 3.3        | Comparisons between previously developed technologies and this work.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 69 |

| Chapter 4        | The state of the s |    |

| Table 4.1        | Comparisons of performance variation between developed Ni-Based-AAO nanocomposite inductors with relative to air-core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|                  | inductor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 96 |

| <b>Table 4.2</b> | Comparisons between previously developed technologies [94-97] and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|                  | this work.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 96 |

## List of Figures

| Chapter 1  |                                                                         |    |

|------------|-------------------------------------------------------------------------|----|

| Figure 1.1 | The illustration of System-on-Chip (SOC). [3]                           | 9  |

| Figure 1.2 | The illustration of System-on-Package (SOP). [4]                        | 9  |

|            |                                                                         |    |

| Chapter 2  |                                                                         |    |

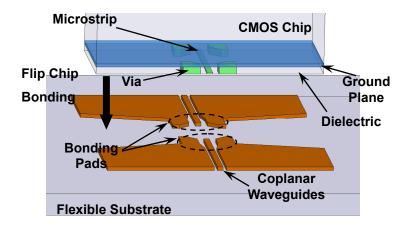

| Figure 2.1 | MEMS heterogeneous chip integration.                                    | 27 |

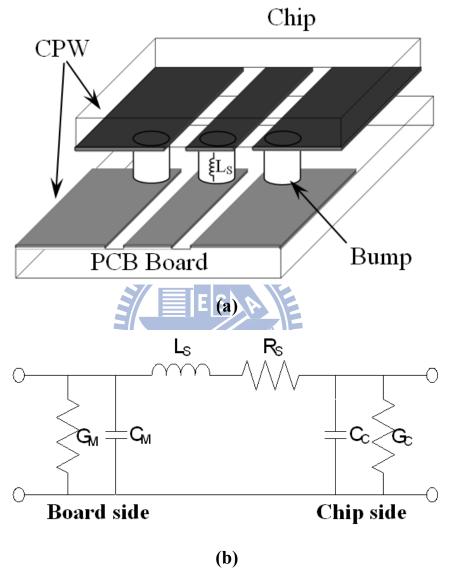

| Figure 2.2 | (a) Typical FC transition structure and (b) corresponding equivalent    | 28 |

|            | circuit model.                                                          |    |

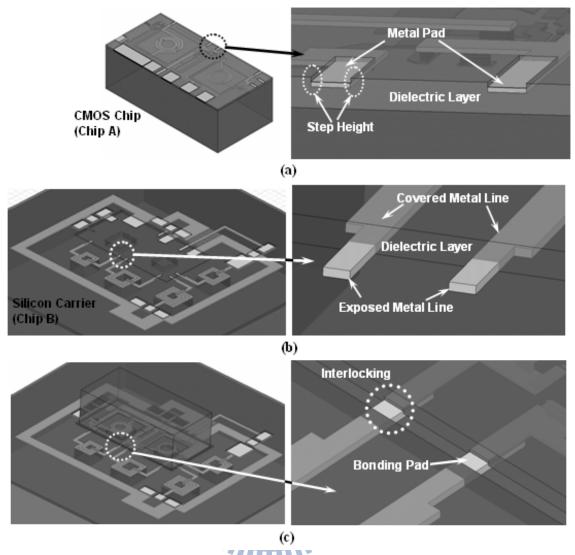

| Figure 2.3 | Self-interlocking bumpless interconnecting technology proposed for      | 29 |

|            | heterogeneous chip integration. (a) CMOS chip after blade dicing.       |    |

|            | The enlarged view of a diced CMOS chip near bonding pads shows a        |    |

|            | step height between the top surface of the bonding pad and the          |    |

|            | passivation. (b) Silicon carrier is fabricated using a standard CMOS    |    |

|            | backend process and a MEMS process. The backend process is              |    |

|            | utilized to fabricate interconnect lines and bonding pads for the CMOS  |    |

|            | chip assembly, and a MEMS process is utilized to etch silicon, which is |    |

|            | underneath the inductors for the purpose of substrate loss reduction.   |    |

|            | The thickness of the exposed metal line should be thicker than the step |    |

|            | height on the CMOS chip. (c) CMOS chip is integrated with the           |    |

|            | carrier using the bumpless interconnecting technology. The inset        |    |

|            | shows that the concave pad on the chip will be self-interlocked with    |    |

|            | the metal line on the carrier during the chip integration.              |    |

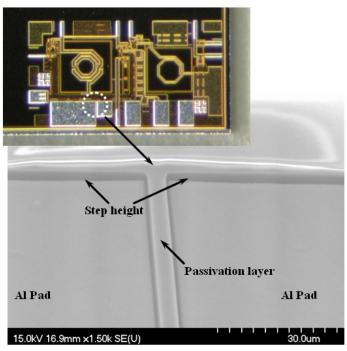

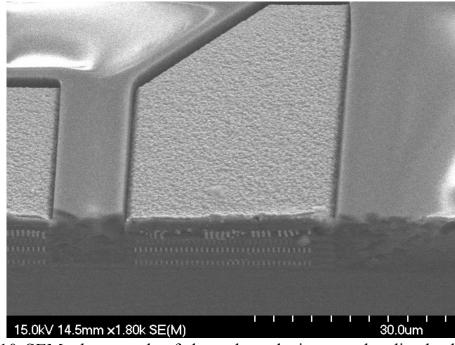

| Figure 2.4 | SEM photograph of the enlarged view on the corner of an Al pad          | 30 |

|            | shows a step height between the top surfaces of the Al contact pad and  |    |

| of the TSMC 0.18 μm mixed signal CMOS chip.                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

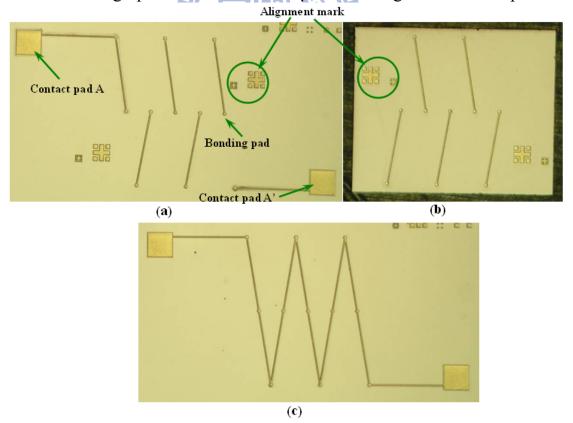

| Optical micrographs of dc contact resistance test structures, i.e., the                                                | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Daisy chain, including two separate chips (a, b), and a line pattern (c)                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| for de-embedding.                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

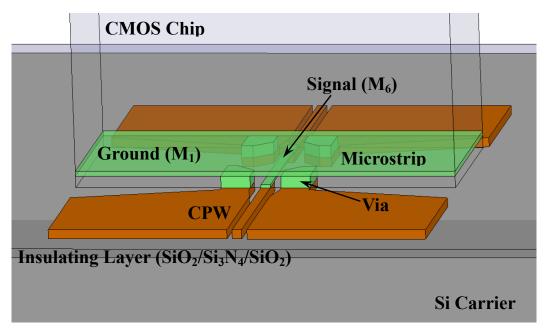

| The RF transition structure for characterization of the proposed                                                       | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| bumpless interconnecting technology from CPW on the Si carrier to                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| microstrip line on the CMOS chip fabricated in a standard 0.18μm                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CMOS process.                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

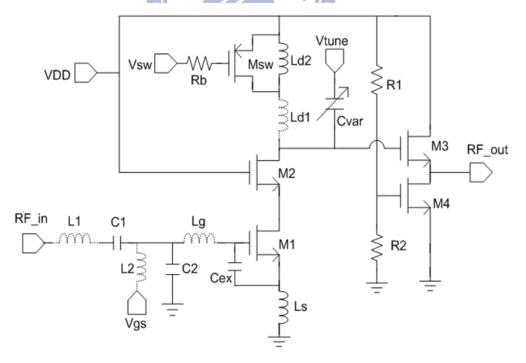

| Tunable LNA circuit. Four high $Q$ MEMS inductors (as shown in                                                         | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| dashed lines) are utilized to improve the circuit performance.                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

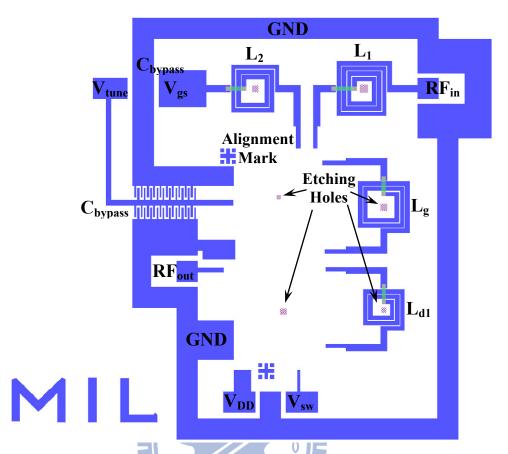

| The layout of Si carrier for UWB tunable LNA integration.                                                              | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

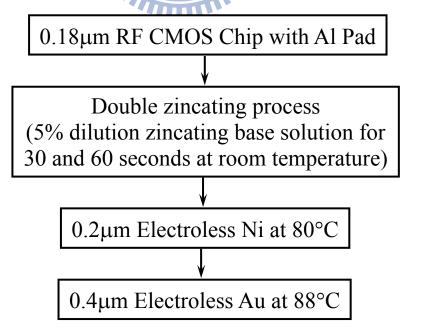

| Process flow of maskless metallization to the CMOS chip.                                                               | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SEM photograph of the enlarged view on the diced edges of the CMOS chip.                                               | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

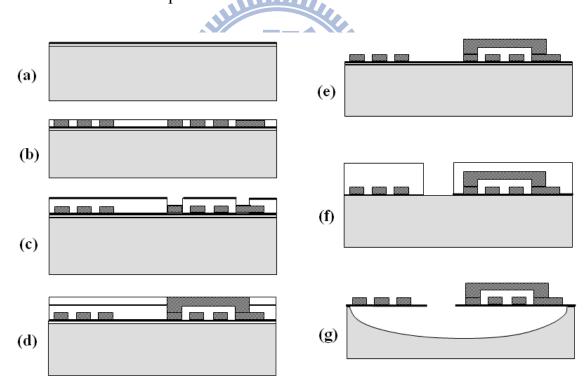

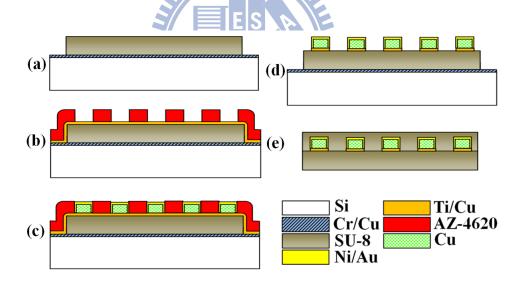

| Silicon carrier fabrication processes: (a) SiO <sub>2</sub> /Si <sub>3</sub> N <sub>4</sub> /SiO <sub>2</sub> membrane | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| and Ti/Cu seeding layer deposition, (b) first Cu plating, (c) via                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| patterning and air-bridge seeding layer deposition, (d) air bridge and                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| via plating, (e) photoresist and seeding layer removal, (f) membrane                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| patterning by reactive ion etching, and (g) silicon substrate removal                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| using XeF <sub>2</sub> gas followed by a photoresist strip.                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

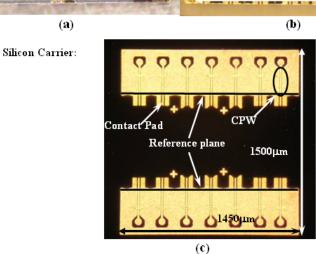

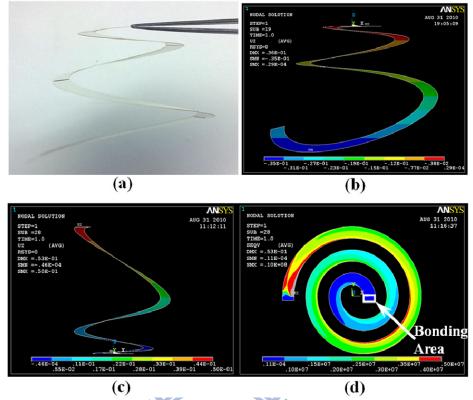

| Optical micrographs of (a) before, (b) after a blade dicing the CMOS                                                   | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| chip, and (c) as-fabricated silicon carrier.                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

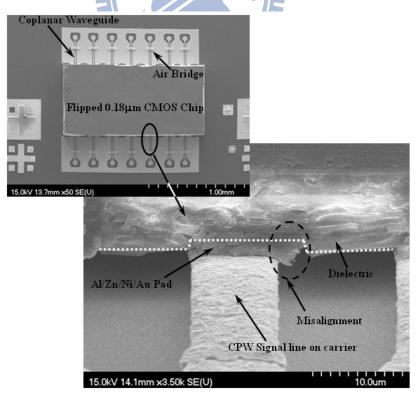

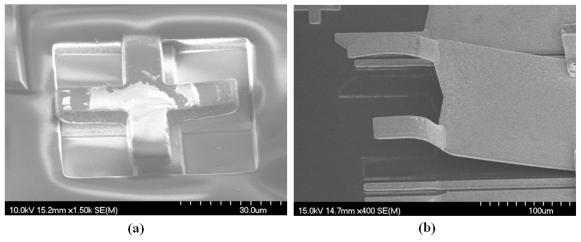

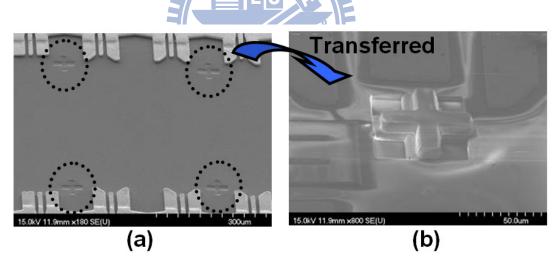

| SEM photographs of (Top) the chip-assembly result and (bottom) an                                                      | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| enlarged view at the bonding area.                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                        | Optical micrographs of dc contact resistance test structures, i.e., the Daisy chain, including two separate chips (a, b), and a line pattern (c) for de-embedding.  The RF transition structure for characterization of the proposed bumpless interconnecting technology from CPW on the Si carrier to microstrip line on the CMOS chip fabricated in a standard 0.18µm CMOS process.  Tunable LNA circuit. Four high <i>Q</i> MEMS inductors (as shown in dashed lines) are utilized to improve the circuit performance.  The layout of Si carrier for UWB tunable LNA integration.  Process flow of maskless metallization to the CMOS chip.  SEM photograph of the enlarged view on the diced edges of the CMOS chip.  Silicon carrier fabrication processes: (a) SiO <sub>2</sub> /Si <sub>3</sub> N <sub>4</sub> /SiO <sub>2</sub> membrane and Ti/Cu seeding layer deposition, (b) first Cu plating, (c) via patterning and air-bridge seeding layer deposition, (d) air bridge and via plating, (e) photoresist and seeding layer removal, (f) membrane patterning by reactive ion etching, and (g) silicon substrate removal using XeF <sub>2</sub> gas followed by a photoresist strip.  Optical micrographs of (a) before, (b) after a blade dicing the CMOS chip, and (c) as-fabricated silicon carrier.  SEM photographs of (Top) the chip-assembly result and (bottom) an |

the passivation in a standard CMOS chip. (Inset) Optical micrograph

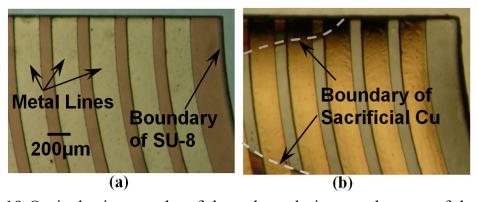

| Figure 2.14 | Enlarged SEW photographs of (a) alignment mark on the silicon carrier     | 33 |

|-------------|---------------------------------------------------------------------------|----|

|             | transferred onto the CMOS chip and (b) lifted Cu line on the silicon      |    |

|             | carrier after forcefully separating the bonded transition structure.      |    |

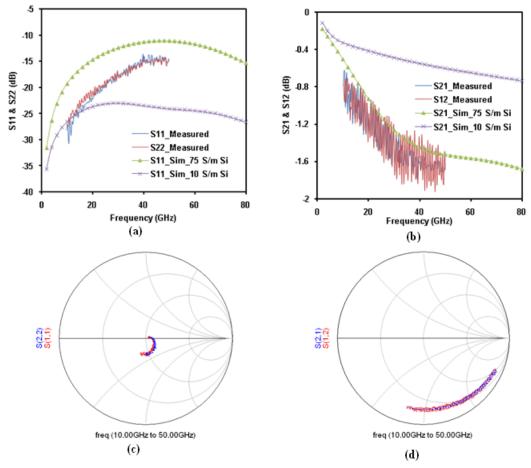

| Figure 2.15 | Simulation and measurement results of (a) return loss and (b) insertion   | 35 |

|             | loss of the EM signal propagating through the transition design with      |    |

|             | the transmission lines, a CPW, and a microstrip line, and corresponding   |    |

|             | measurement results of (c) return loss and (d) insertion loss shown in    |    |

|             | Smith charts.                                                             |    |

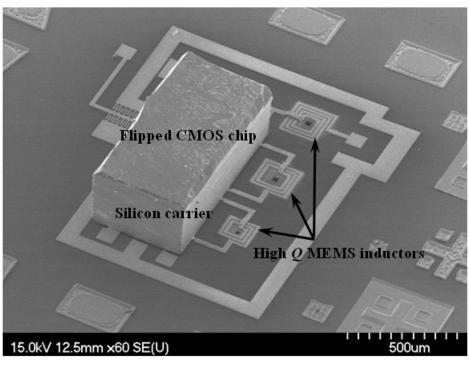

| Figure 2.16 | SEM photograph of the UWB tunable LNA with high $Q$ MEMS                  | 36 |

|             | inductors. The rectangular holes located in the center of inductors       |    |

|             | provide a path for XeF <sub>2</sub> vapor isotropic etching.              |    |

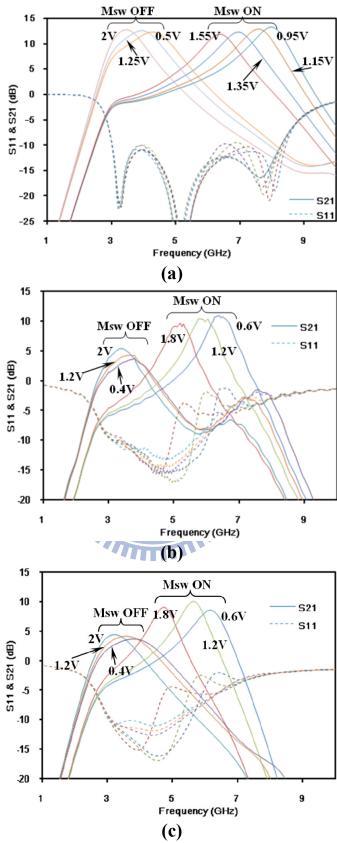

| Figure 2.17 | (a) Schematic simulation, (b) measurement results, and (c) full layout    | 37 |

|             | simulation of the return loss and gain with a different tuning voltage of |    |

|             | the UWB LNA circuit.                                                      |    |

|             |                                                                           |    |

| Chapter 3   |                                                                           |    |

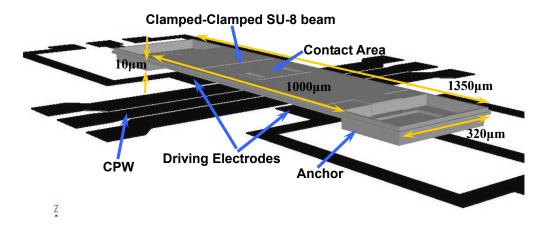

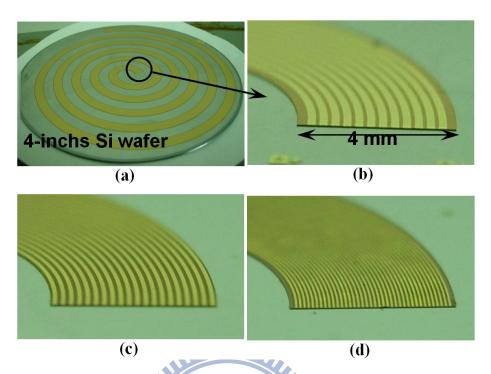

| Figure 3.1  | The scheme of clamped-clamped SU-8 beam MEMS series switch.               | 62 |

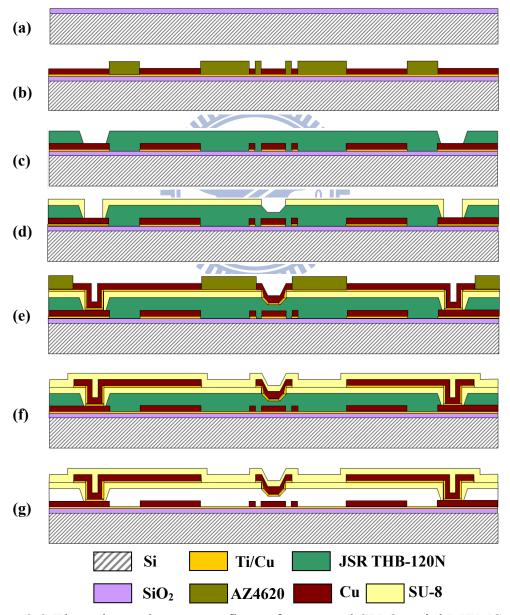

| Figure 3.2  | The schematic process flow of proposed SU-8 serial MEMS switch.           | 62 |

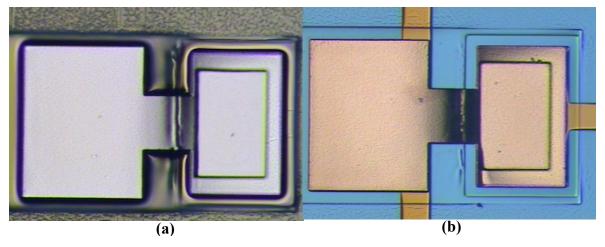

| Figure 3.3  | Optical micrographs of the enlarged view on the area of driving           | 63 |

|             | electrode of the switch (a) before and (b) after sacrificial JSR layer    |    |

|             | removal.                                                                  |    |

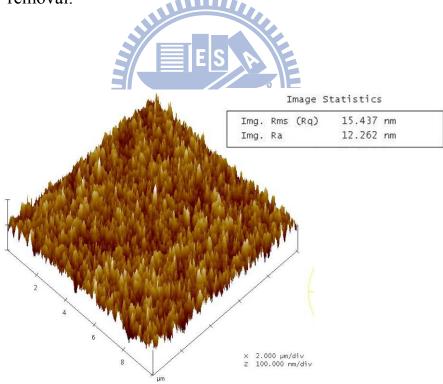

| Figure 3.4  | The AFM 3D profile image and average roughness of electroplating          | 63 |

|             | Cu surface.                                                               |    |

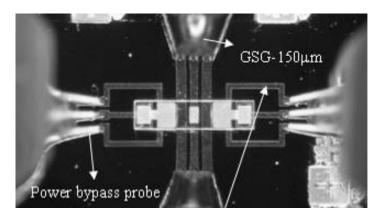

| Figure 3.5  | High frequency measurement setup for the MEMS switch.                     | 64 |

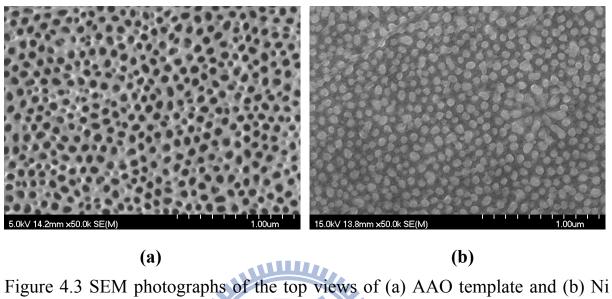

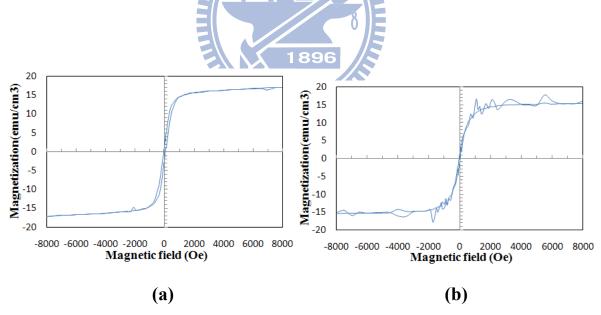

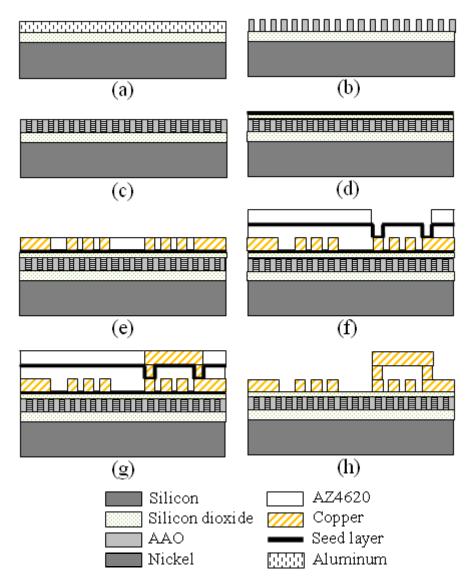

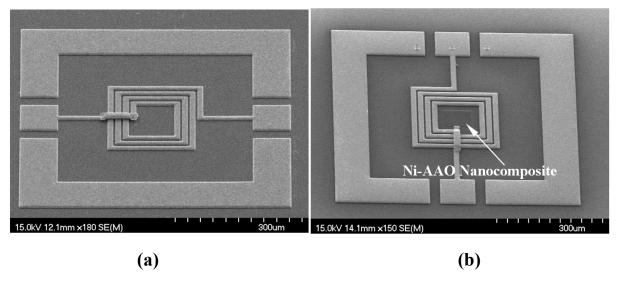

| Figure 3.6  | The measurement and simulation results of the SU-8 switch while the       | 64 |