# 國立交通大學

電信工程研究所

博士論文

ES

超大型積體電路的熱分析技術 Thermal Simulation Techniques for Very Large Scale Integration (VLSI) Circuits

研究生: 黄培育

指導教授:李育民

中華民國一百年十月

# 超大型積體電路的熱傳分析技術 Thermal Simulation Techniques for Very Large Scale Integration (VLSI) Circuits

研究生:黄培育 Student: Pei-Yu Huang

指導教授:李育民 博士 Advisor: Dr. Yu-Min Lee

國立交通大學

電信工程研究所

Submitted to Institute of Communication Engineering

College of Electrical and Computer Engineering

National Chiao Tung University

in Partial Fulfillment of the Requirements

for the Degree of Doctor of Philosophy

in Communication Engineering Hsinchu, Taiwan

中華民國100年10月

### 超大型積體電路的熱傳分析技術

學生: 黃培育 指導教授:李育民

國立交通大學電信工程所博士班

摘 要

持續縮小元件大小的互補式金氧半導體製程技術造成了在晶片上的高功率密度。這個事實導致在超大型積體電路上有很高的晶片溫度。晶片溫度將會影響到電路效能以及可靠度。此外,亦會增加電路的消耗功率。因此,許多研究者已致力於發展將溫度視為導向之一的電路最佳化以及效能分析技術。由於將熱傳視為導向的最佳化引擎需要在最佳化過程中執行許多次的熱傳分析,因此在以熱傳為導向之一的設計流程中需要一個準確且快速的熱分析器。為了提供前端設計流程的熱傳分析,此博士論文中發展了三個準確且快速的熱傳分析器。

給定了晶片上的功率分布之後,第一個分析器首先利用一組基底來表示晶片上的溫度。得到晶片溫度的表示式之後,我們發展了一個基於快速傅立葉轉換的演算法來計算出晶片的溫度分佈。基於以上的分析架構,第一個分析器也提供了堆疊晶片(stacked package)以及無接觸連線(contactless interconnection)架構的三維度積體電路之熱傳分析功能。

為了考慮製程變異以及溫度對於漏電功率的影響,第二個分析器提供了兩種熱電分析架構以快速且準確地估計晶片溫度的擾動。此外,為了提供更有意義的熱傳丈量尺度給前端設計之最佳化引擎,第二個分析器也準確且快速地提供了晶片上熱傳可靠度分布圖(thermal yield profile)。在此,熱傳可靠度分布圖為晶片溫度小於一個使用者給定之臨界溫度的機率分布圖。

為了提供以矽穿孔(through silicon via)技術為架構的三維度積體電路之熱傳分析,第三個分析器提供了一個基於查表法的分析架構。利用此查表法的分析架構,耗時的熱傳電導矩陣處理過程將可以被避免。

我們的實驗已驗證了以上三個熱傳分析器具有高度的估計準確率以及分析效能。

# Thermal Simulation Techniques for Very Large Scale Integration (VLSI) Circuits

Student: Pei-Yu Huang Advisor: Yu-Min Lee

Institute of Communication Engineering National Chiao Tung University

#### **ABSTRACT**

The continuously scaling down of the CMOS technology results in high on-chip power density, and this fact leads to high on-chip temperature in modern very large scale Integration (VLSI) circuits. On-chip temperature influences the performance and the reliability, and it also increases the power consumption of the circuits. Therefore, researchers have devoted to thermal-aware optimization techniques. Since the thermal-aware optimization engines require performing numerous thermal simulations in their optimization loops, an efficient and accurate thermal analyzer is essential for thermal-aware design flow. In this dissertation, three accurate and efficient thermal simulators for early stage thermal-aware design engines are proposed.

Given the deterministic on-chip power profile, the first simulator represents the on-chip temperature profile by a set of bases. Then, a fast Fourier transform based algorithm is developed to obtain the on-chip temperature profile. Based on the above simulation framework, the first proposed simulator also provides the thermal simulation for the stacked-chip or the contactless interconnection based three-dimensional integrated circuits (3-D ICs).

To take into account the impacts of the process variation and the temperature to leakage powers, the second simulator provides two electro-thermal simulation frameworks to accurately and efficiently predict the fluctuation of on-chip temperature profile. Moreover, to ensure the on-chip thermal reliability and provide more meaningful thermal costs for thermal-aware design engines, the second simulator can efficiently deliver the thermal yield profile, which is the probability profile of the temperature being less or equal to a user specified threshold temperature.

To provide the thermal estimation for early stage thermal-aware design engines for the through silicon via based 3-D ICs, the third proposed simulator provides a look-up table based thermal simulation framework. With the look-up table based framework, the time consumed dealing processes for the thermal conductance matrix of the equivalent thermal circuit can be avoided.

The experimental results have demonstrated the high-accuracy and high-efficiency of all the three proposed thermal simulators.

### 誌 謝

這篇論文能夠順利地完成,首先要感謝我的指導教授 李育民博士,當我遭遇困難時,老師總會適時指引我方向,讓我能夠繼續前進。 在攻讀博士期間,老師給我對於專業上的訓練指導以及在論文寫作方 面夙夜匪懈的幫助,讓我確實感受到老師對於自己的用心。我在此對你致上最高的謝意。

論文中實驗的部份,特別感謝李義明老師提供我們台積電 65 奈米 製程的製程參數,標準元件檔以及標準元件的電路檔。除了李義明老 師,在此特別感謝工業技術研究院蒯定明技術組長以及林昌賜技術副 理。兩位所提供的測試電路以及三維度晶片相關的工業規格,讓此論 文中對於三維度晶片相關的實驗能夠更符合工業標準。沒有你們的幫 助,要完成論文中實驗的部分是相當困難的。

在實驗室成員裡,感謝麒文、佳鴻、懷中、以及啟平對於部分實 驗的幫助。沒有你們,要獨力完成整個實驗是相當困難的。

特別感謝好友羿辰,給予我許多支持與鼓勵,陪伴我度過最低潮的日子。最後要深深地感謝我的父母,你們對於我在學業上衝刺的全力支持,讓我能夠順利完成博士學業。僅在此將本論文獻給你們,共享這份喜悅與榮耀。

## **Contents**

| 1 | Intr                                                                              | oduction | 1                                                                    | 1  |  |

|---|-----------------------------------------------------------------------------------|----------|----------------------------------------------------------------------|----|--|

|   | 1.1                                                                               | Therma   | al Related Issues of Modern VLSI Design                              | 1  |  |

|   |                                                                                   | 1.1.1    | Timing and Reliability Issues                                        | 1  |  |

|   | 1.2                                                                               | The Ef   | fects of Temperature and Process Variations on the Leakage Powers    | 4  |  |

|   |                                                                                   | 1.2.1    | Subthreshold Leakage Current                                         | 4  |  |

|   |                                                                                   | 1.2.2    | Gate Tunneling Leakage Current                                       | 6  |  |

|   |                                                                                   | 1.2.3    | Leakage Powers Inducing Electro-Thermal (Temperature-Power) Cou-     |    |  |

|   |                                                                                   |          | pling Effect                                                         | 7  |  |

|   |                                                                                   | 1.2.4    | Variations of Physical Device Parameters                             | 8  |  |

|   | 1.3                                                                               | Three-   | Dimensional Integrated Circuit and Its Thermal Issues                | 9  |  |

|   | 1.4                                                                               |          | al-Aware Design Flow                                                 | 12 |  |

|   | 1.5                                                                               |          | of On-Chip Thermal Simulation Methods                                | 14 |  |

|   |                                                                                   | 1.5.1    | Simulation Methods of Deterministic On-Chip Temperature Profile      | 14 |  |

|   |                                                                                   | 1.5.2    | Simulation Methods of Statistical On-Chip Temperature Profile        | 16 |  |

|   |                                                                                   | 1.5.3    | Simulation Methods of the Temperature Profile for 3-D ICs            | 18 |  |

|   | 1.6                                                                               | Contrib  |                                                                      | 19 |  |

|   | 1.7                                                                               | Organi   | outions of this Dissertation                                         | 21 |  |

|   |                                                                                   |          |                                                                      |    |  |

| 2 | Simulation Method I – Full-Chip Thermal Analysis for Early Design Stages via Gen- |          |                                                                      |    |  |

|   | erali                                                                             |          | gral Transforms                                                      | 22 |  |

|   | 2.1                                                                               |          | al Modeling for Early Design Stages                                  | 22 |  |

|   | 2.2                                                                               |          | hip Thermal Simulation                                               | 28 |  |

|   |                                                                                   | 2.2.1    |                                                                      | 29 |  |

|   |                                                                                   | 2.2.2    | System Transformation for Time-Varying Coefficients                  | 30 |  |

|   |                                                                                   | 2.2.3    | Average Rising Temperature Evaluation of Grid Cells                  | 31 |  |

|   | 2.3                                                                               |          | al Simulation for Stacked-Layer 3-D ICs                              | 41 |  |

|   | 2.4                                                                               |          | ach to Handle the Temperature Dependent Issue of Leakage Powers      | 44 |  |

|   | 2.5                                                                               | -        | mental Results                                                       | 45 |  |

|   |                                                                                   | 2.5.1    | Accuracy and Fast Convergence of the GIT Based Thermal Simulator .   | 45 |  |

|   |                                                                                   | 2.5.2    | Thermal Simulation for the Full-Chip Containing Lots of Functional   |    |  |

|   |                                                                                   |          | Blocks                                                               | 46 |  |

|   |                                                                                   | 2.5.3    | Accuracy and Efficiency of the GIT Based Thermal Simulator for the   |    |  |

|   |                                                                                   |          | 3-D IC Thermal Analysis                                              | 48 |  |

| 3 | Sim                                                                               | ulation  | Method II – An Efficient Method for Analyzing the Process Variations |    |  |

| J |                                                                                   |          | On-Chip Thermal Reliability                                          | 52 |  |

|   | 3.1                                                                               |          | tion Illustrations                                                   | 52 |  |

|   | 5.1                                                                               | 3.1.1    | Electro-Thermal Coupling Issue under Process Variations              | 52 |  |

|   |                                                                                   |          | Concept of On Chin Thermal Viold Profile                             | 54 |  |

|   | 3.2         | Prelim   | inaries                                                                 | 55              |

|---|-------------|----------|-------------------------------------------------------------------------|-----------------|

|   |             | 3.2.1    | Leakage Power Modeling                                                  | 55              |

|   |             | 3.2.2    | Modeling of Variations for Physical Device Parameters                   | 59              |

|   |             | 3.2.3    | Problem Formulation                                                     | 61              |

|   | 3.3         | Statisti | cal Electro-Thermal Analyzer                                            | 64              |

|   |             | 3.3.1    | Stochastic Projection Based Statistical Expression Generator            | 67              |

|   |             | 3.3.2    | Stochastic Collocation Based Statistical Expression Generator           | 78              |

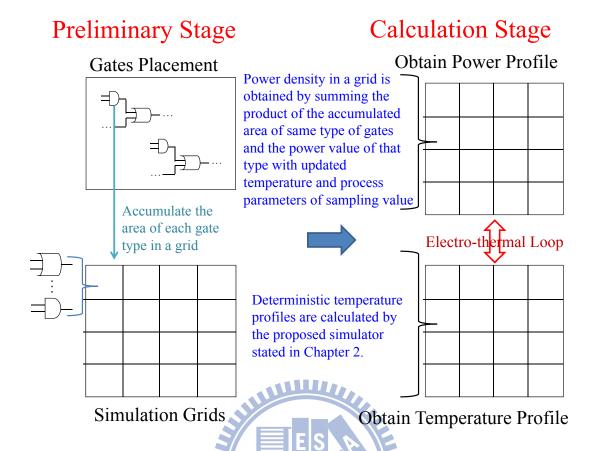

|   |             | 3.3.3    | Implementation of the Deterministic Electro-Thermal Simulation          | 84              |

|   |             | 3.3.4    | On-Chip Thermal Yield Computation                                       | 85              |

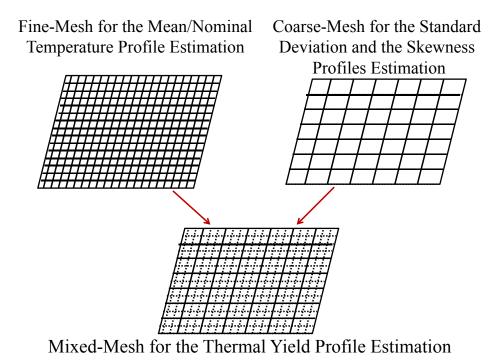

|   |             | 3.3.5    | Mixed-Mesh Thermal Yield Estimation                                     | 89              |

|   | 3.4         | Experi   | mental Results                                                          | 91              |

|   |             | 3.4.1    | Statistical Thermal Simulations With/Without Considering Electro-Thern  | nal             |

|   |             |          | Effects                                                                 | 93              |

|   |             | 3.4.2    | Accuracy and Efficiency                                                 | 93              |

| 4 | C:          | la4:a    | Mothed III IIITCim. A Leak III Takle Dugod Theman I Cimalaten fo        |                 |

| 4 | 3-D         |          | Method III – LUTSim: A Look-Up Table Based Thermal Simulator for        | <i>r</i><br>103 |

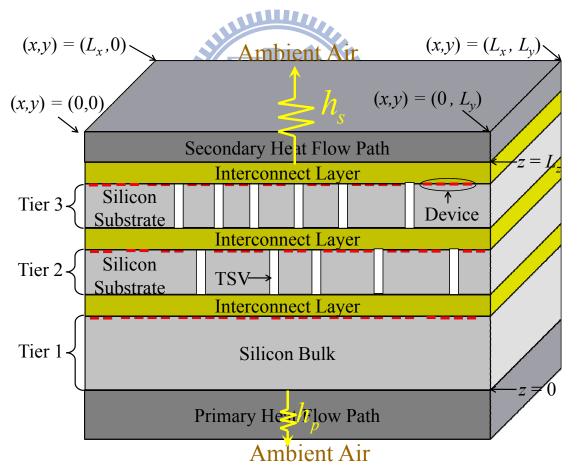

|   | 4.1         |          | al Model for Early Design Stages of TSVs based 3-D IC Structures        |                 |

|   | 4.2         |          |                                                                         |                 |

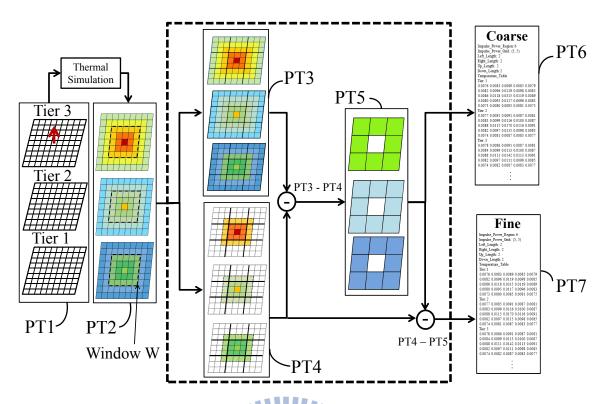

|   |             | 4.2.1    | Overview of LUTSim                                                      |                 |

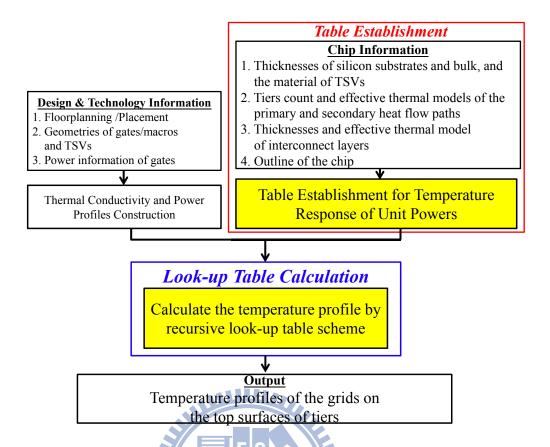

|   |             | 4.2.2    | Recursive Look-Up Table based Full-Chip Thermal Simulation              | 10,             |

|   |             |          | Framework                                                               | 109             |

|   |             | 4.2.3    | Fine Mesh Toble Establishment                                           | 111             |

|   |             | 4.2.4    | Double-Mesh Table Establishment                                         | 116             |

|   | 4.3         | Experi   | mental Results                                                          | 118             |

|   |             | 4.3.1    | Experimental Settings                                                   | 118             |

|   |             | 4.3.2    | Validation 1996                                                         | 110             |

|   |             | 4.3.3    | Robustness Verification                                                 | 119             |

| _ |             |          | Robustness Verification                                                 |                 |

| 5 |             | clusion  |                                                                         |                 |

|   | 5.1         |          | ary of Current Research Results                                         | 123             |

|   | 5.2         |          | Research Directions                                                     |                 |

|   |             | 5.2.1    | Statistical Thermal Simulation of 3-D ICs                               |                 |

|   |             | 5.2.2    | Thermal-aware Timing Analysis                                           |                 |

|   |             | 5.2.3    | Thermal-aware Design Engines                                            | 125             |

| A | Deri        | vation o | of the time-varying coefficients for GIT based thermal simulation metho | od              |

|   | and         | error b  | ound analysis of GIT based steady state temperature formulae            | 126             |

|   | <b>A.</b> 1 | Deriva   | tion of the Analytical Expression of Time-Varying Coefficients for the  |                 |

|   |             | Approx   | ximated Temperature                                                     | 126             |

|   | A.2         | Error E  | Bound Analysis of GIT Based Steady State Temperature Formulation        | 127             |

| В | Deri        | vation o | of the Projection Coefficients of Subthreshold and Gate Tunneling Leak  | <b>(-</b>       |

|   |             | Powers   |                                                                         | 130             |

|   | B.1         | Deriva   | tion of the Evaluating Algorithm for the Projection Coefficient of Gate |                 |

|   |             |          | ling Leakage Power                                                      | 130             |

|   |             | B.1.1    | Derivation of Evaluating Algorithm for the Projection Coefficient of    |                 |

|   |             |          | Subthreshold Leakage Power                                              | 133             |

# **List of Figures**

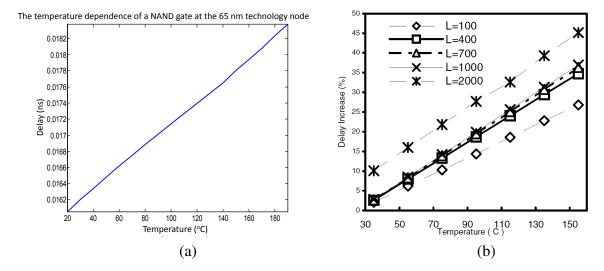

| 1.1         | The temperature dependences for the delays of gates and interconnects. (a) The temperature dependency of a NAND gate at the 65nm technology node. (b)                                                                                                                                                                                                                                                         |     |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|             | The temperature dependences for the delay of interconnect corresponding to                                                                                                                                                                                                                                                                                                                                    |     |

|             | different wire length L (reprinted from [1])                                                                                                                                                                                                                                                                                                                                                                  | 3   |

| 1.2         | An example for illustrating the non-uniform on-chip temperature profile induc-                                                                                                                                                                                                                                                                                                                                |     |

|             | ing clock skew.                                                                                                                                                                                                                                                                                                                                                                                               | 4   |

| 1.3         | The temperature and process variation dependencies of subthreshold and gate tunneling leakage currents of a NAND gate at $65nm$ technology node. (a) The temperature and process variation dependencies of subthreshold leakage current. (b) The temperature and process variation dependencies of gate tunneling leakage current. Here, $L$ is the device channel length, and its unit is $nm$ . $t_{ox}$ is |     |

|             | the oxide thickness, and its unit is $Am$                                                                                                                                                                                                                                                                                                                                                                     | 5   |

| 1.4         | The mechanism of electro-thermal coupling                                                                                                                                                                                                                                                                                                                                                                     | 8   |

| 1.5         | Parameter variations impacts on the leakage currents (reprinted from [2]). Here, the y-coordinate indicates the normalized occurrence frequency of the value of the device channel length, and the x-coordinate indicates the normalize value                                                                                                                                                                 |     |

|             | for the subthreshold leakage currents $(I_{sb})$                                                                                                                                                                                                                                                                                                                                                              | 9   |

| 1.6         | Implementation categories of 3-D ICs (reprinted from [3]). (a) Wire-bonded                                                                                                                                                                                                                                                                                                                                    |     |

|             | structure. (b) Microbump-3D package structure. (c) Face-to-face structure. (e) Contactless-capacitive with buried bumps structure. (f) Contactless-inductive structure. (f) Through silicon vias (TSVs) based structure with silicon substrates                                                                                                                                                               |     |

|             | on bulk. (g) TSVs based structure with silicon substrates on insulator (SOI).                                                                                                                                                                                                                                                                                                                                 | 10  |

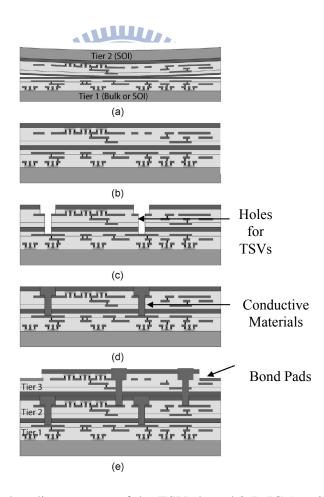

| 1.7         | The wafer bonding process of the TSVs based 3-D IC (reprinted from [4])                                                                                                                                                                                                                                                                                                                                       | 11  |

| 1.8         | Temperature-Aware Design Flow                                                                                                                                                                                                                                                                                                                                                                                 | 13  |

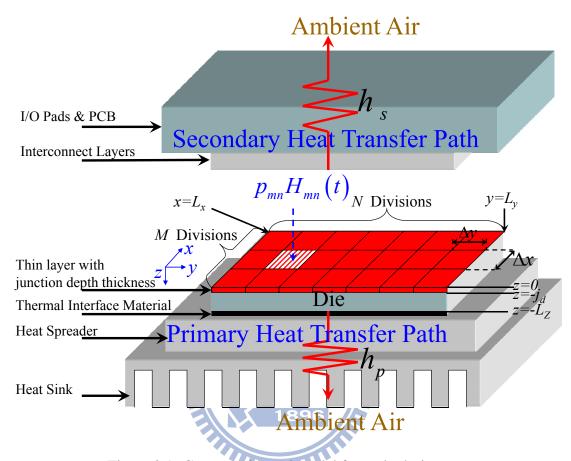

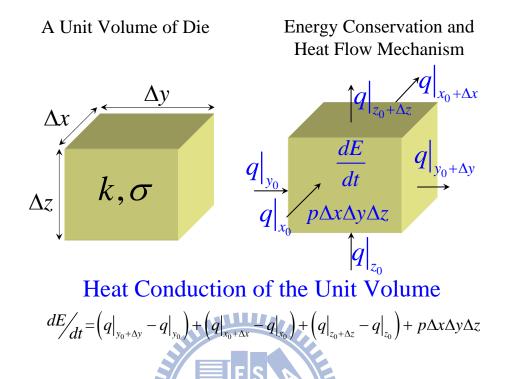

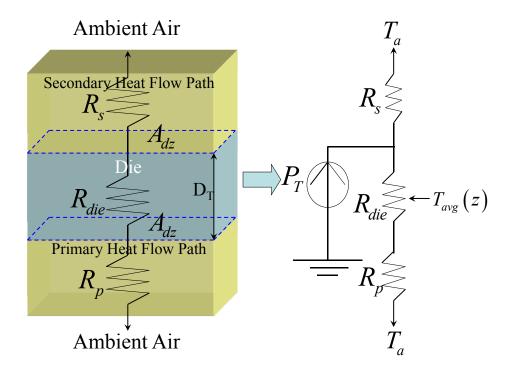

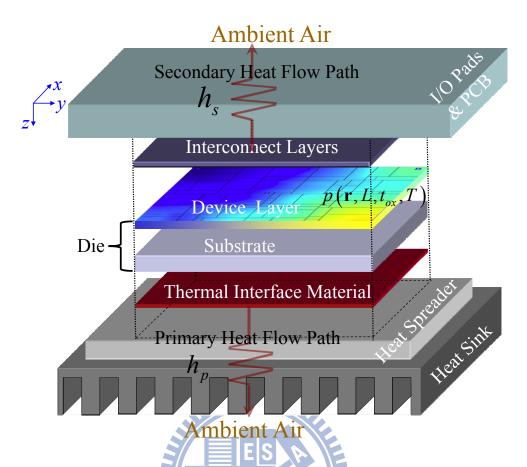

| 2.1         | Compact thermal model for early design stages                                                                                                                                                                                                                                                                                                                                                                 | 23  |

| 2.2         | Energy conservation law and the heat conduction equation                                                                                                                                                                                                                                                                                                                                                      | 24  |

| 2.3         | The 1-D thermal model for estimating the roughly steady state average temperature of die. The modeled thermal resistance network is shown in the right hand                                                                                                                                                                                                                                                   |     |

|             | side                                                                                                                                                                                                                                                                                                                                                                                                          | 26  |

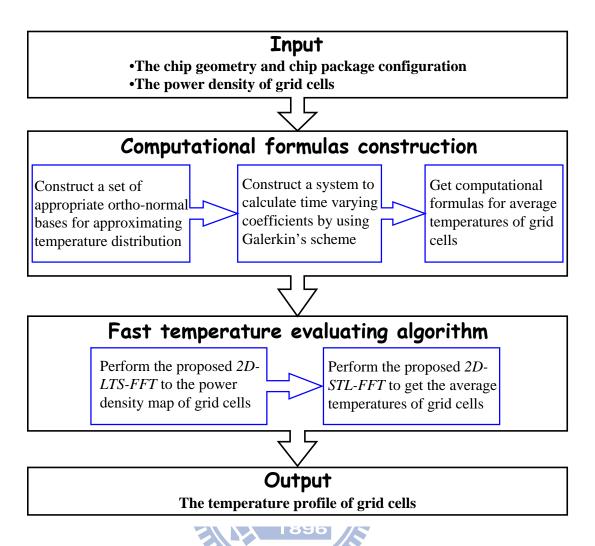

| 2.4         | The executing flow of the proposed GIT based thermal simulation method                                                                                                                                                                                                                                                                                                                                        | 28  |

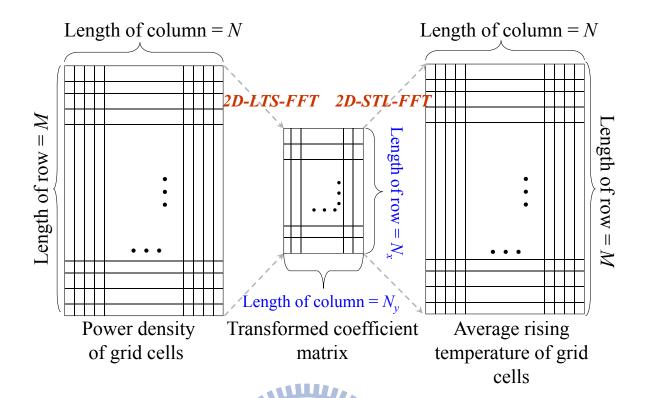

| 2.5         | The overview of using 2D-SLT-FFT and 2D-LTS-FFT to evaluate the average                                                                                                                                                                                                                                                                                                                                       | 2.4 |

| 2.6         | rising temperature of grid cells                                                                                                                                                                                                                                                                                                                                                                              | 34  |

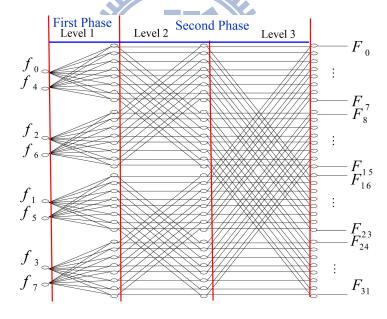

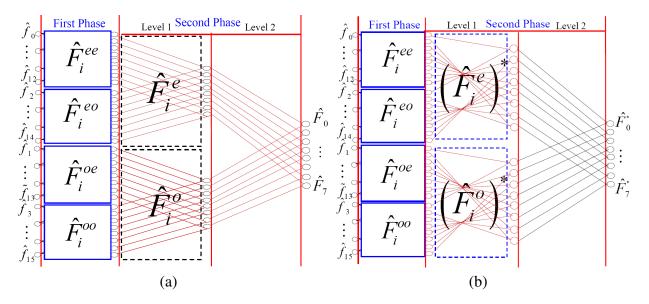

| 2.6         | Procedure of 1D-STL-FFT                                                                                                                                                                                                                                                                                                                                                                                       | 35  |

| 2.7         | The sketch of the computational flow for $ID$ -STL-FFT with $M=8$ and $M=16$ .                                                                                                                                                                                                                                                                                                                                | 35  |

| 2.8<br>2.9  | Procedure of <i>1D-LTS-FFT</i>                                                                                                                                                                                                                                                                                                                                                                                | 36  |

| <b>∠.</b> 9 | (a) The $ID$ - $LTS$ - $FFT$ (b) The $ID$ - $LTS$ - $FFT$ for negative frequencies                                                                                                                                                                                                                                                                                                                            | 37  |

| 2.10        | Procedure of 2D-STL-FFT                                                                                                                                                                                                                                                                                                                                                                                       | 38  |

|             |                                                                                                                                                                                                                                                                                                                                                                                                               | 20  |

|      | Simulating algorithm of the proposed steady state thermal simulator                        | 40 |

|------|--------------------------------------------------------------------------------------------|----|

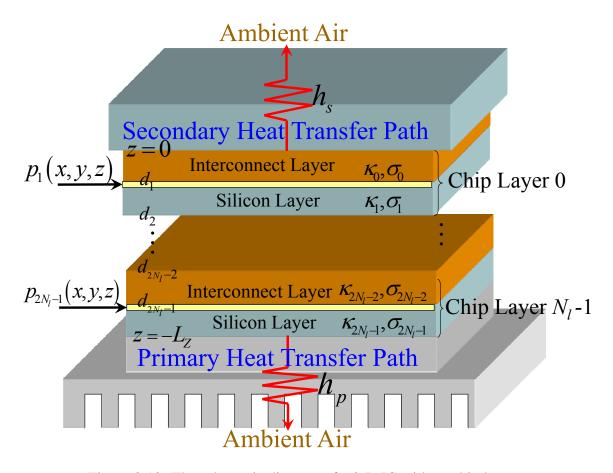

| 2.12 | The schematic diagram of a 3-D IC with $N_l$ chip layers                                   | 41 |

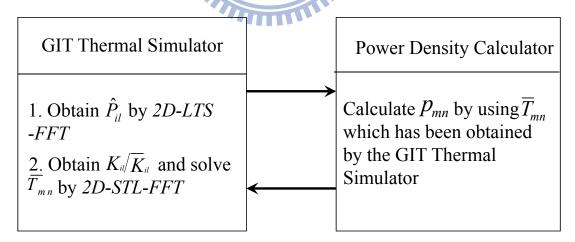

| 2.13 | Temperature-power iterative framework for dealing with the temperature de-                 |    |

|      | pendence issue of leakage power                                                            | 44 |

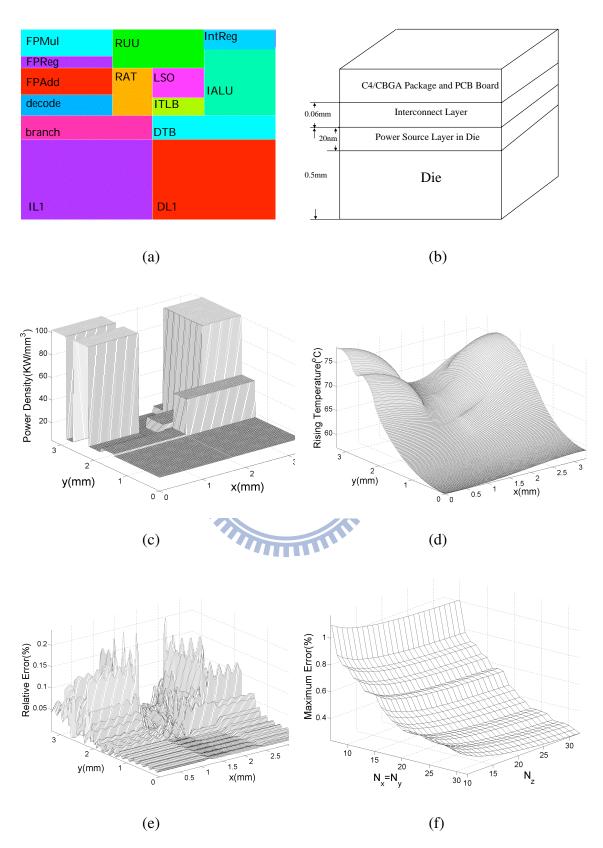

| 2.14 | Accuracy and the maximum error trend of a test chip. (a) Floorplan, (b) geome-             |    |

|      | tries of the test chip, (c) power distribution, (d) the rising temperature distribu-       |    |

|      | tion of the top surface of the die, (e) the relative error distribution, and (f) the       |    |

|      | maximum relative error versus truncation point                                             | 47 |

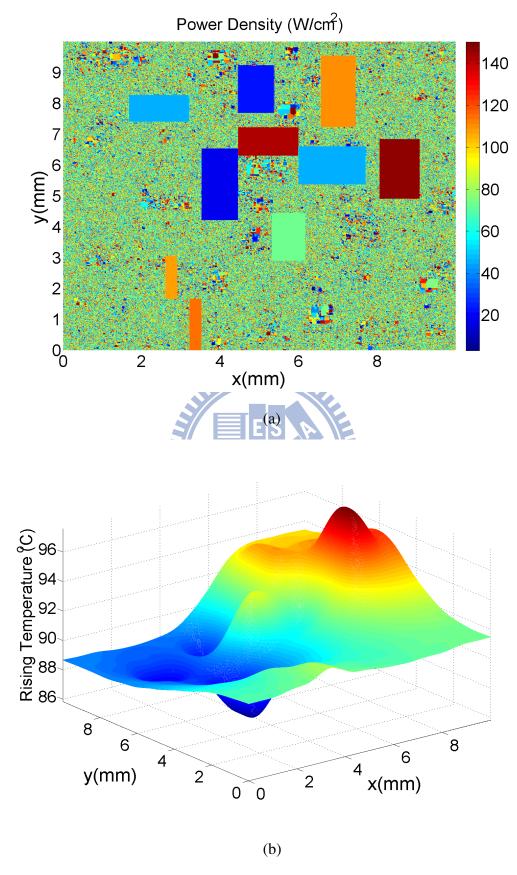

| 2.15 |                                                                                            |    |

|      | million functional blocks. (a) The power density distribution, and (b) the rising          |    |

|      | temperature distribution                                                                   | 49 |

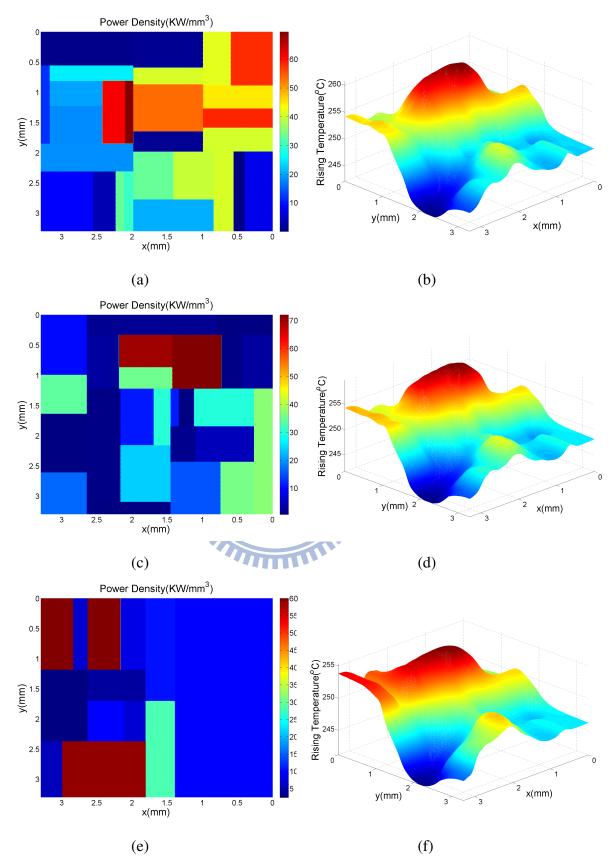

| 2.16 | Power density and temperature distribution of a test 3-D chip. Figures (a), (c)            |    |

|      | and (e) are the power density profiles on the top surface of the top, middle and           |    |

|      | bottom silicon layers, respectively. Figures (b), (d) and (f) are the temperature          |    |

|      | distribution on the top surface of the top, middle and bottom silicon layers,              |    |

|      | respectively                                                                               | 51 |

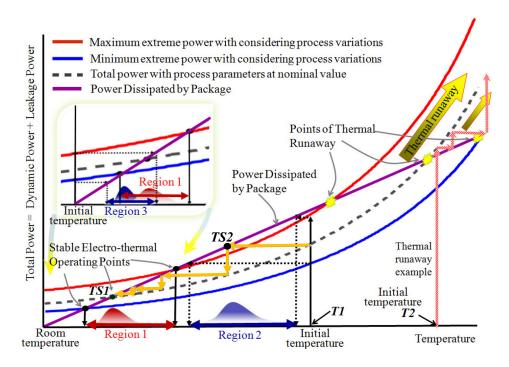

| 3.1  | An example for the electro-thermal coupling mechanism under process variations.            | 53 |

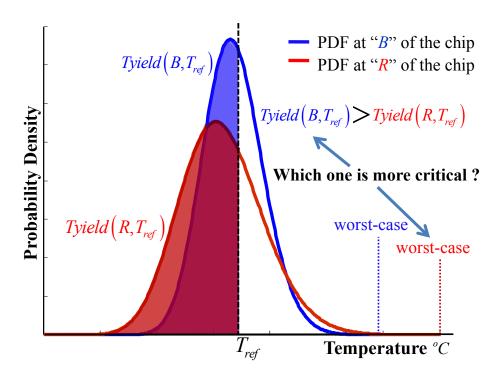

| 3.2  | PDFs of on-chip temperature values at two different positions ( $B$ and $R$ ) of a die     |    |

|      | for indicating which one is the <i>statistically hot-spot</i> location                     | 54 |

| 3.3  | Compact thermal model of physical design stages under process variations                   | 62 |

| 3.4  | An iterative scheme for computing the appropriate thermal conductivity of die.             |    |

|      | $\mu_T$ is a roughly average mean temperature of die, and $\mu_P$ is the mean of total     |    |

|      | on-chip power consumption after executing an iteration. $\mu_P$ can be obtained by         |    |

|      | the zeroth order of H-PC projected power of gates proposed in Figure 3.7 and               |    |

|      | Figure 3.9 of section 3.3.1                                                                | 63 |

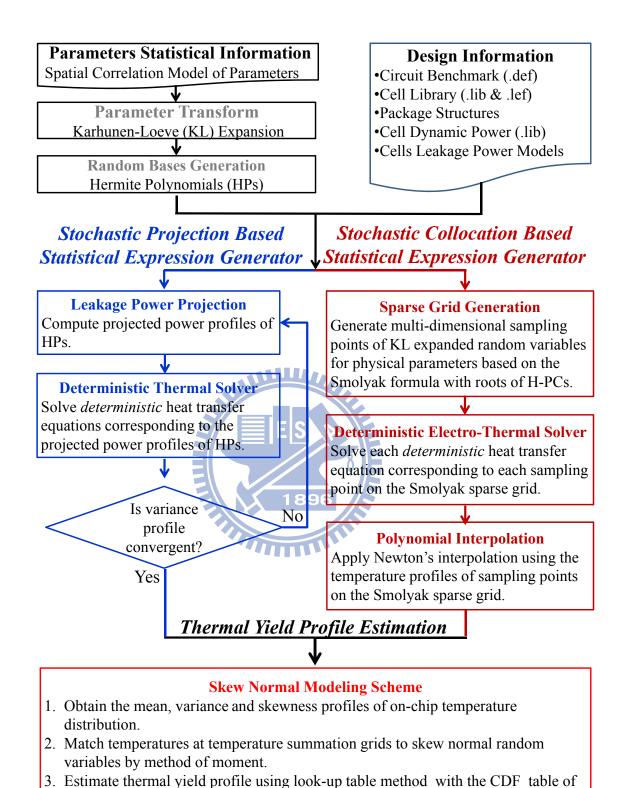

| 3.5  | Overview of the developed statistical electro-thermal analyzer                             | 65 |

| 3.6  | The electro-thermal updating scheme of the stochastic projection based statisti-           |    |

|      | cal expression generator                                                                   | 70 |

| 3.7  | The evaluating algorithm of projection coefficients of gate tunneling leakage              |    |

|      | power up to second order of HPs                                                            | 73 |

| 3.8  | The function that evaluates the related vectors for calculating the leakage powers.        | 74 |

| 3.9  | Subthreshold leakage power projection algorithm                                            | 75 |

| 3.10 | Stochastic projection based electro-thermal analysis algorithm. <i>NumGateType</i>         |    |

|      | in <i>Line</i> 13 is the number of gate types given from the industrial library file       | 77 |

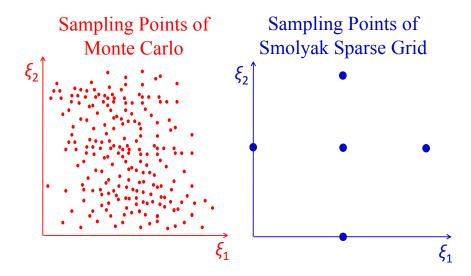

| 3.11 | The number of sampling random variables comparison between the Monte Carlo                 |    |

|      | method and the Smolyak sparse grid formulation. Here, the samples of Smolyak               |    |

|      | sparse grid are adopted for achieving a level two approximation                            | 79 |

| 3.12 | Deterministic electro-thermal analysis for each sampling point, $\xi^{j}$ , in sparse      |    |

|      | grid. $p_{leak}$ , $p_d$ and $p$ are the leakage, dynamic and total power density profiles |    |

|      | for each sampling point, respectively                                                      | 81 |

| 3.13 | Stochastic Collocation Based Statistical Expression Generating Algorithm                   | 83 |

|      | Implementation of solving the deterministic heat transfer equations                        | 84 |

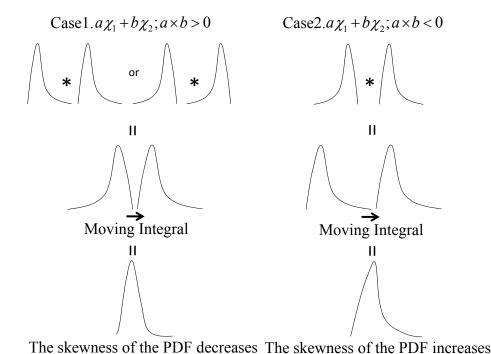

|      | Weighted sum of two independent non-central chi-square random variables.                   |    |

|      | Case1: the skewness of the PDF decreases because a left-skewed distribution                |    |

|      | and a right-skewed distribution are moving integrated. Case2: the skewness of              |    |

|      | the PDF increases because two right-skewed distributions are moving integrated.            | 87 |

| 3.16 | The executing sketch of the mixed-mesh thermal yield estimation                            | 89 |

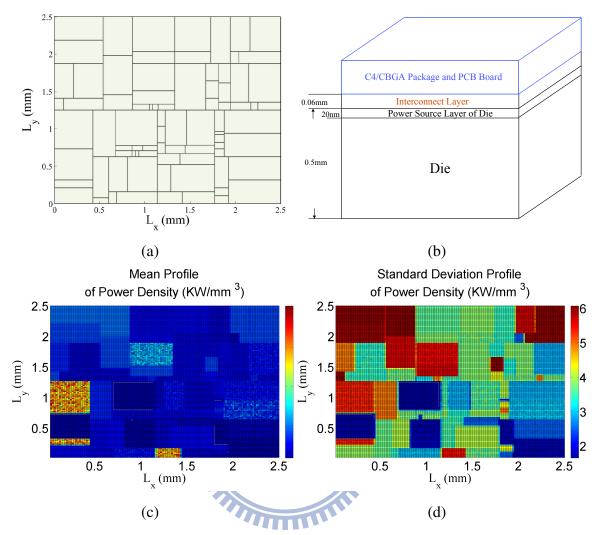

| 3.17 | Floorplan of the test die, geometries of the test chip and package, and mean and            |     |

|------|---------------------------------------------------------------------------------------------|-----|

|      | standard deviation profiles of the power density on the test chip. (a) Floorplan            |     |

|      | of the test die. (b) Geometries of the test chip and package. (c) The mean profile          |     |

|      | of power density. (d) The standard deviation profile of power density. Here, L <sub>x</sub> |     |

|      | and $L_v$ are the width and length of the test chip, respectively                           | 92  |

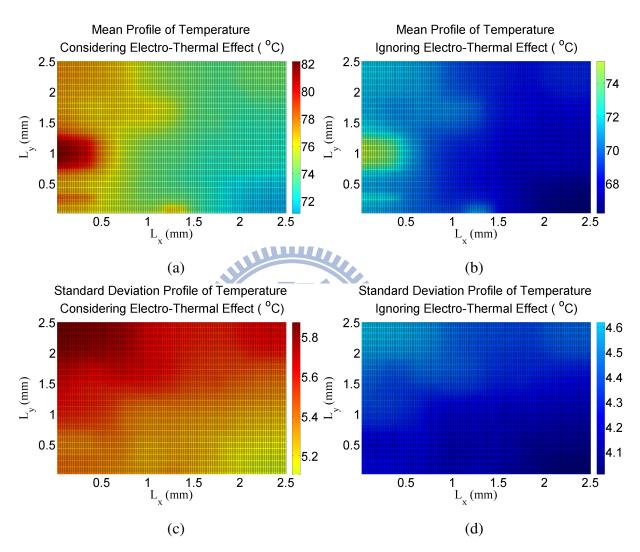

| 3.18 | Results of the Monte Carlo method with or without considering electro-thermal               | -   |

| 2.10 | effects. (a) The mean temperature profile with considering the electro-thermal              |     |

|      | effect. (b) The mean temperature profile without considering the electro-thermal            |     |

|      | effect. (c) The standard deviation profile of temperature distribution with con-            |     |

|      | • • •                                                                                       |     |

|      | sidering the electro-thermal effect. (d) The standard deviation profile of tem-             | 0.4 |

| 2.10 | perature distribution without considering the electro-thermal effect                        | 94  |

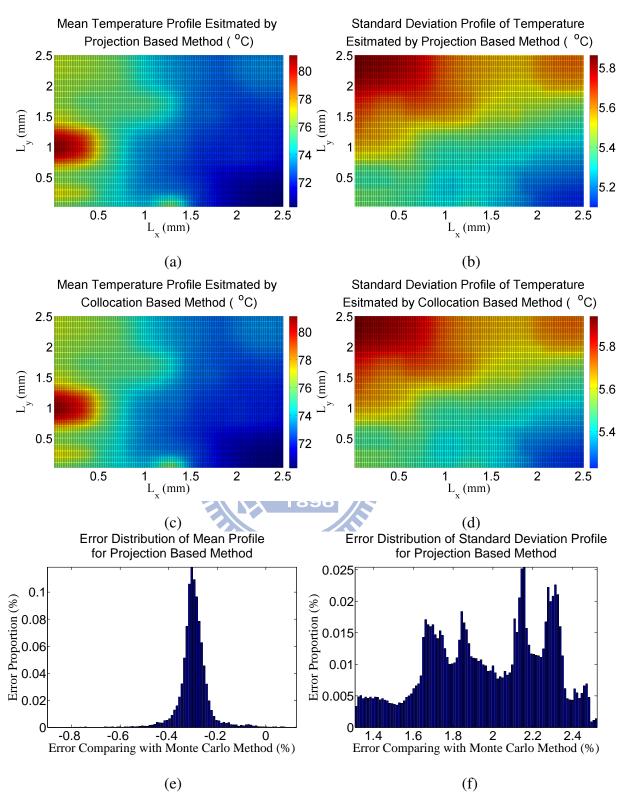

| 3.19 | Simulation results of the developed methods. (a) and (b) the mean and standard              |     |

|      | deviation profiles of the estimated temperature distribution got by the stochas-            |     |

|      | tic projection method, respectively. (c) and (d) the mean and standard deviation            |     |

|      | profiles of the estimated temperature distribution obtained by the stochastic col-          |     |

|      | location method, respectively. (e) and (f) the error distributions of the mean and          |     |

|      | standard deviation of the estimated temperature distribution got by the stochas-            |     |

|      | tic projection method, respectively                                                         | 96  |

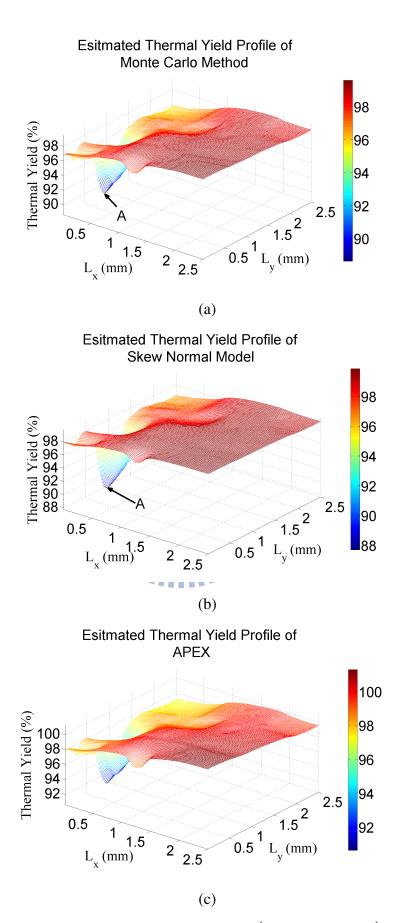

| 3.20 | tic projection method, respectively                                                         |     |

|      | (a) Profile obtained by the Monte Carlo method. (b) Profile obtained by the                 |     |

|      | proposed skew-normal based method. (c) Profile obtained by APEX                             | 99  |

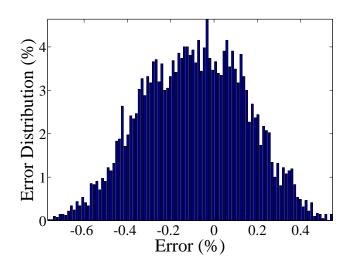

| 3.21 | The error distributions of the skew-normal based method and APEX. (a) Dis-                  |     |

|      | tribution of the skew-normal based method comparing with the Monte Carlo                    |     |

|      | method. (b) Distribution of APEX comparing with the Monte Carlo method                      | 100 |

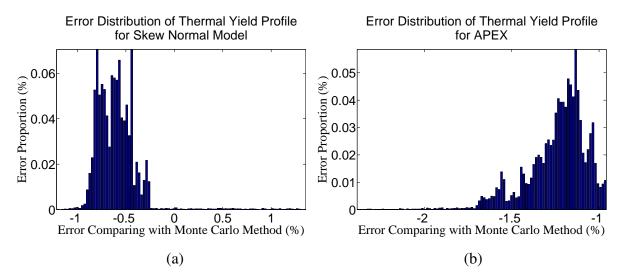

| 3.22 | The temperature CDF curve at position A in Figure 3.20(a) got by the Monte                  |     |

|      | Carlo method, and its estimated CDF curves obtained by the skew-normal model                |     |

|      | based method, APEX with the 4-th oredr and the 9-th order for the PDF/CDF                   |     |

|      | shifting process                                                                            | 100 |

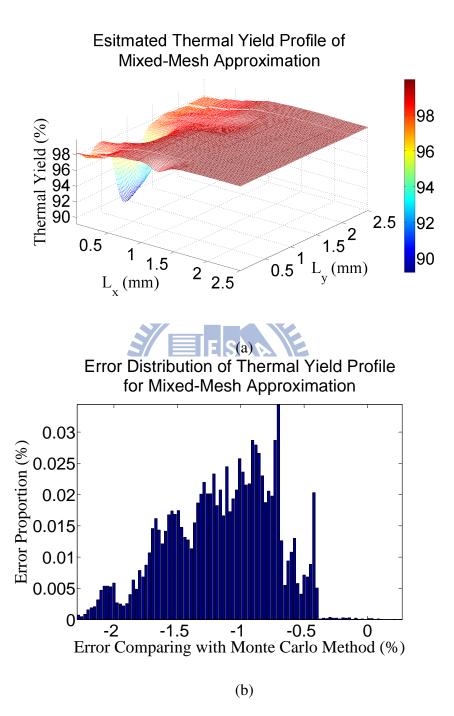

| 3 23 | The estimated thermal yield profile and the error distribution of the mixed-grid            | 100 |

| 3.23 | thermal estimation strategy.                                                                | 102 |

|      | thermal estimation strategy.                                                                | 102 |

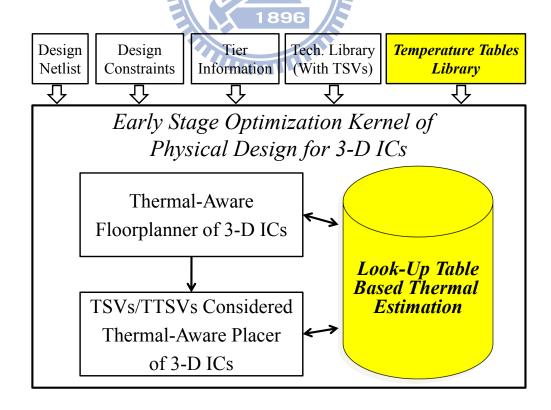

| 4.1  | Key points of LUTSim for the early physical design stages in 3-D ICs                        | 103 |

| 4.2  | Thermal model for the early design stage of a 3-D IC with three tiers                       |     |

| 4.3  | The flowchart of LUTSim                                                                     |     |

| 4.4  | Examples for the <i>lateral locality</i> and <i>local similarity</i> of the temperature re- |     |

|      | sponse induced by a unit power source. Each unit power source is inserted to a              |     |

|      | grid on the top-surface of the tier adjacent to the secondary heat flow path. (a)—          |     |

|      | (f) are the temperature responses with inserting a unit power source on grids               |     |

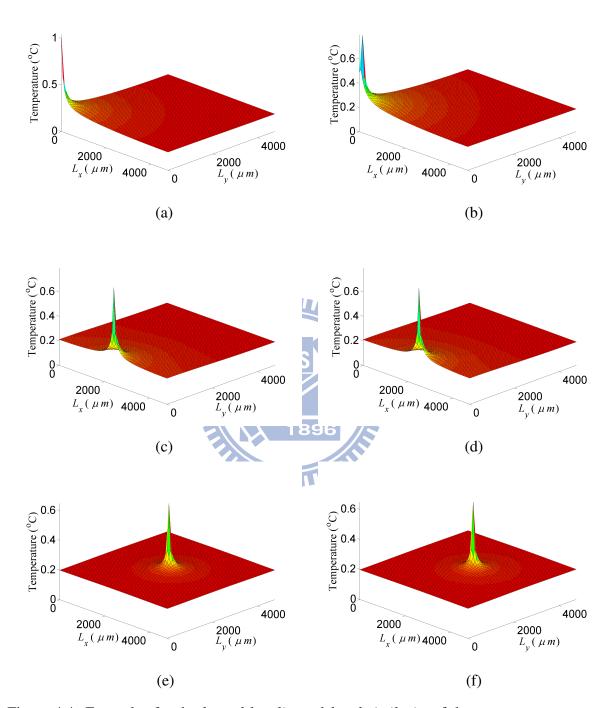

|      | (0,0), (1,1), (32,0), (33,0), (32,32) and $(33,33)$ , respectively                          | 112 |

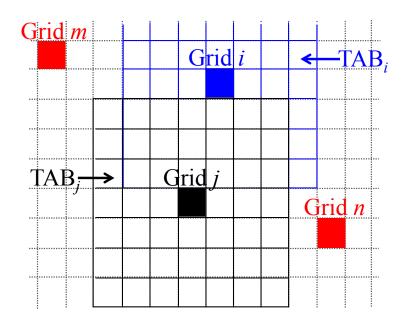

| 4.5  |                                                                                             | 113 |

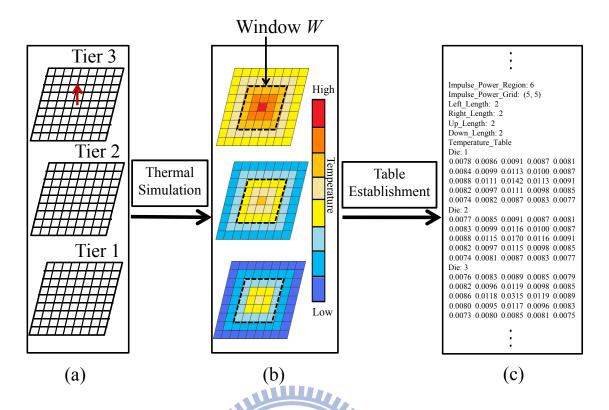

|      | The table establishing process of TR-UPS of a specific grid in $S_g$                        | 113 |

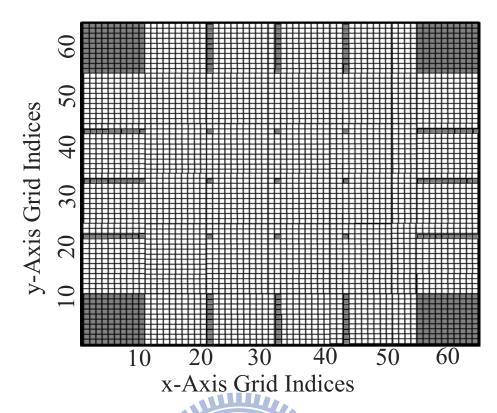

| 4.6  | An example of the selected representative grids in $S_g$ of a specific tier. Gray           | 111 |

| 4.7  | color grids are the representative grids                                                    | 114 |

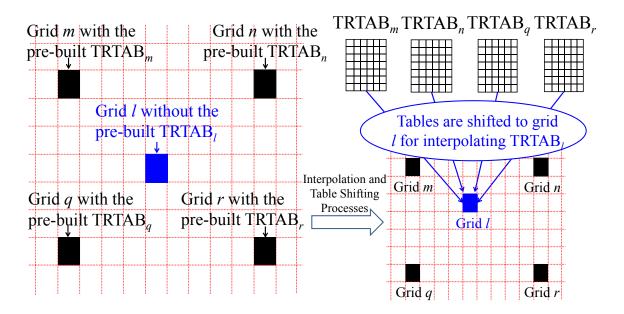

| 4.7  | The table shifting and interpolation processes for the grid having no pre-built             | 115 |

| 4.0  | unit power temperature response table                                                       | 115 |

| 4.8  | The error accumulation phenomenon of the fine-mesh look-up table strategy                   | 116 |

| 4.9  | The double-mesh table establishment of the unit power temperature response.                 |     |

| 4.10 | The calculating process of double-mesh look-up table technique                              | 118 |

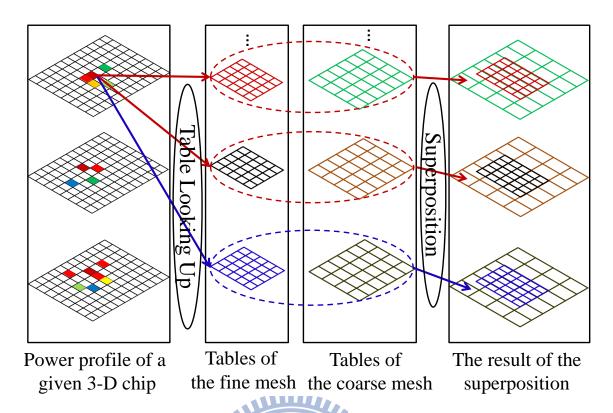

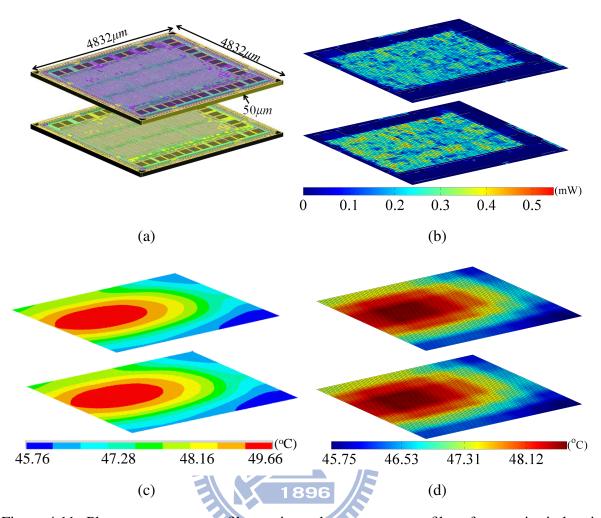

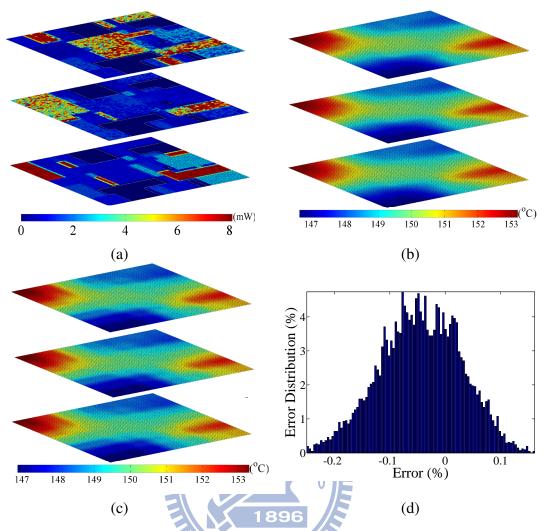

| 4.11 | Placement, power profiles, estimated temperature profiles of a two-tier indus- |     |

|------|--------------------------------------------------------------------------------|-----|

|      | trial chip by ANSYS and R-LUTSim. (a) Placement. (b) Power profiles. (c)       |     |

|      | Estimated temperature profiles by ANSYS. (d) Estimated temperature profiles    |     |

|      | by LUTSim                                                                      | 120 |

| 4.12 | Error distribution of LUTSim compared with ANSYS                               | 120 |

| 4.13 | The distribution of insertion numbers of TSVs for the test chip, "g-chip3",    |     |

|      | stated in Table 4.1                                                            | 121 |

| 4.14 | Power profiles, estimated temperature profile of fast MNA solver, estimated    |     |

|      | temperature profile of LUTSim and the error distribution between fast MNA      |     |

|      | solver and LUTSim of the test chip "g-Chip3". a two-tier industrial chip by    |     |

|      | ANSYS and R-LUTSim. (a) Power profiles. (b) Estimated temperature profile      |     |

|      | of fast MNA solver. (c) Estimated temperature profile of LUTSim (d) Error      |     |

|      | distribution between fast MNA solver and LUTSim                                | 122 |

### **List of Tables**

| 2.1 | Accuracy and Runtime Comparison of the proposed GIT based method and the Algorithm II of [5]                                                                                                                                                                                                                                  | 48         |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 3.1 | Accuracy comparison of leakage power models for an NAND gate under $65nm$ technology node. The results of HSPICE simulation with TSMC model card are employed to be the reference solution. The second column represents the fitting components of $f_g(L, t_{ox}, T)$ and $f_s(L, t_{ox}, T)$ adopted by the models proposed | 5.0        |

| 2.2 | by [6–8] and our proposed models                                                                                                                                                                                                                                                                                              | 56         |

| 3.2 | Accuracy comparison of leakage current models in [9] for an NAND gate under                                                                                                                                                                                                                                                   | <b>~</b> 0 |

|     | 65 <i>nm</i> technology node                                                                                                                                                                                                                                                                                                  | 58         |

| 3.3 | Parameters and Truncation Points for the Channel Length and the Oxide Thickness.                                                                                                                                                                                                                                              | 91         |

| 3.4 | Equivalent Thermal Parameters                                                                                                                                                                                                                                                                                                 | 92         |

| 3.5 | Accuracy and Efficiency of the Developed Statistical Expression Generators                                                                                                                                                                                                                                                    | 93         |

| 3.6 | Accuracy and Efficiency Comparison of the Skew Normal Model and APEX for                                                                                                                                                                                                                                                      |            |

|     | Estimating Thermal Yield Profiles. The results are compared with the Monte                                                                                                                                                                                                                                                    |            |

|     | Carlo method with $2 \times 10^5$ samples                                                                                                                                                                                                                                                                                     | 97         |

| 4.1 | Comparison between LUTSim and the fast MNA solver [10]                                                                                                                                                                                                                                                                        | 121        |

### Chapter 1

### Introduction

In this chapter, several major thermal related issues of modern VLSI design will be summarized in sections 1.1–1.3. Then, the description of thermal-aware design flow, the essentiality of the thermal simulation and the review of existing thermal simulation methods are given in sections 1.4 and 1.5. Finally, the contribution and organization of this dissertation are summarized in sections 1.6 and 1.7.

### 1.1 Thermal Related Issues of Modern VLSI Design

### 1.1.1 Timing and Reliability Issues

Since the threshold voltage and carrier mobility are temperature-dependent, the drain current is affected by temperature fluctuations. Therefore, the propagation delay of gate will drift while the gate operating at different temperature. The propagation delay of a metal-oxide-semiconductor field-effect transistor (MOSFET) can be approximated as follow [11, 12].

$$t_d(T) = \frac{C_L V_{\text{dd}}}{I_d(T)} = \frac{\beta \times \mu_{\text{eff}}(T)}{\left(V_g - V_{\text{th}}(T)\right)^{\alpha}},\tag{1.1}$$

where

$$\beta = \frac{L_{\text{eff}} C_L V_{\text{dd}}}{W C_{\text{ox}}},\tag{1.2}$$

and  $C_L$  is the load capacitance,  $V_{\rm dd}$  is the supply voltage,  $I_d$  is the drain current in the saturation region,  $C_{\rm ox}$  is the gate oxide capacitance,  $L_{\rm eff}$  is the effective channel length, W is the channel width,  $V_g$  is the gate voltage,  $\alpha$  is the velocity saturation index, T is the operating temperature,  $\mu_{\rm eff}(T)$  is the effective carrier mobility and  $V_{\rm th}(T)$  is the threshold voltage. The temperature

dependences of  $\mu_{\text{eff}}(T)$  and  $V_{\text{th}}(T)$  can be illustrated by following equations [13].

nMOS:

$$V_{\text{th}}(T) = V_{\text{th}}(T_0) + \left(KT1 + \frac{KT1L}{L_{\text{eff}}} + V_{\text{bseff}}KT2\right) \left(\frac{T}{T_0} - 1\right),$$

(1.3)

pMOS:

$$V_{\text{th}}(T) = V_{\text{th}}(T_0) - \left(KT1 + \frac{KT1L}{L_{\text{eff}}} + V_{\text{bseff}}KT2\right) \left(\frac{T}{T_0} - 1\right),$$

(1.4)

$$\mu_{\text{eff}}(T) = U_0 \left( \frac{T}{T_0} \right)^{U_{\text{te}}} \left\{ 1 + (U_c(T) V_{\text{bseff}} + U_a(T)) \theta(T) + U_b(T) \theta^2(T) \right\}^{-1}, \quad (1.5)$$

where

$$\theta(T) = \left(\frac{V_{\text{gst}} + 2V_{\text{th}}(T)}{T_{\text{OXE}}}\right),\tag{1.6}$$

and  $T_0$  is the reference temperature, KT1 is the temperature coefficient of threshold voltage, KT1L is the channel length corresponding temperature coefficient of threshold voltage, KT2 is the temperature inducing body-bias coefficient of the threshold voltage,  $V_{\text{bseff}}$  is the effective substrate to bias voltage,  $U_0$  is the mobility at the reference temperature,  $U_{\text{te}}$  is a fitting coefficient,  $T_{\text{OXE}}$  is the electrical gate-oxide thickness,  $U_a$  is the first-order mobility degradation coefficient,  $U_b$  is the second-order mobility degradation coefficient and  $U_c$  is the coefficient of the mobility degradation inducing body effect.

According to equations (1.1)–(1.6), the temperature fluctuation drifts the propagation delay of a MOSFET. The above phenomenon is illustrated in Figure 1.1(a). As shown in Figure 1.1(a), the gate delay is increased by the operating temperature. Besides the above phenomenon of a MOSFET/gate, Khan et. al. [12] have addressed that the on-chip temperature profile induces considerable variations of the full-chip circuit performance beyond the 90*nm* technology nodes.

In addition to the effect of the gate delay, the temperature dependence of the wire resistance r can be written as

$$r = \rho_0 \left( 1 + \alpha T \right),\tag{1.7}$$

where  $\rho_0$  is the resistance per unit length at 0 °C and  $\alpha$  is the temperature coefficient of the resistance per unit length (1/°C). Since the delay of wire is proportion to the resistance, it will be impacted by the temperature. To illustrate the above phenomenon, the temperature dependences of the wire delay corresponding to different lengths are shown in Figure 1.1(b).

Figure 1.1: The temperature dependences for the delays of gates and interconnects. (a) The temperature dependency of a NAND gate at the 65nm technology node. (b) The temperature dependences for the delay of interconnect corresponding to different wire length L (reprinted from [1]).

As shown in Figure 1.1(b), the wire delay will be increased by the operating temperature. And the longer the wire length is, the larger the temperature inducing wire delay is.

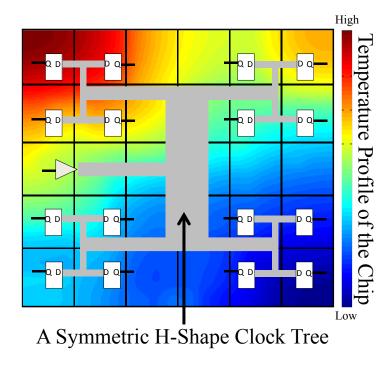

The temperature dependences of gates and wires result in several design issues. For example, the non-uniform on-chip temperature profile may induce the timing fault of the design [14]. As shown in Figure 1.2, the non-uniform on-chip temperature profile results in different delays of the wires and the registers/gates at different positions of the chip. Therefore, the clock skew occurs even though the clock tree is designed as a symmetric H-shape topology with equal distances to the registers. Moreover, based on Black's equation [15], the median-time-to-failure (MTF) of wire can be written as

$$MTF = Aj^{-n} \exp\left(\frac{Q}{k_B T_m}\right),\tag{1.8}$$

where A is a geometry-dependent constant, j is the average current density, n is an empirical constant with its value being 2 for the normal condition,  $k_B$  is the Boltzmann's constant and  $T_m$  is the temperature of the wire. As shown in equation 1.8, the MTF of wire negatively and exponentially depends on the operating temperature. Therefore, high on-chip temperature degrades the lifetime reliability of the circuit.

Figure 1.2: An example for illustrating the non-uniform on-chip temperature profile inducing clock skew.

# 1.2 The Effects of Temperature and Process Variations on the Leakage Powers

Due to the shrinking of device geometries, it is more difficult to control the physical device parameters. The growing variability of physical device parameters, such as the effective channel length and the gate oxide thickness, can induce considerable leakage power fluctuations. Since the on-chip temperature is transformed from the on-chip power, the fluctuations of on-chip leakage powers lead to the thermal simulation with nominal leakage powers is no longer effective to predict the on-chip temperature. In addition, since the leakage powers depend on the operating temperature, the temperature-power coupling effect occurs. This leads the electro-thermal analysis to be more concerned for ensuring the thermal reliability. In this chapter, we will introduce the temperature and process variations issues of two major leakage powers, gate tunneling and subthreshold leakage powers, and highlight its impacts on the on-chip temperature.

### 1.2.1 Subthreshold Leakage Current

The subthreshold leakage current of a MOSFET is defined as the conduction current between source and drain in "OFF" state. The subthreshold leakage current of the MOSFET can be

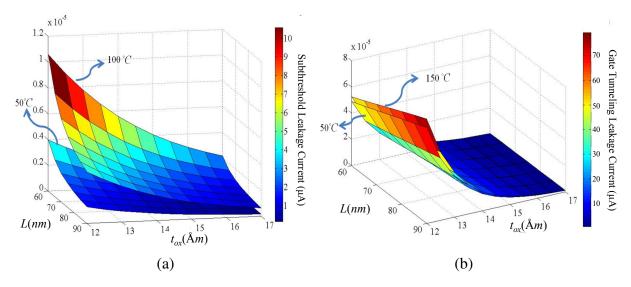

Figure 1.3: The temperature and process variation dependencies of subthreshold and gate tunneling leakage currents of a NAND gate at 65nm technology node. (a) The temperature and process variation dependencies of subthreshold leakage current. (b) The temperature and process variation dependencies of gate tunneling leakage current. Here, L is the device channel length, and its unit is nm.  $t_{ox}$  is the oxide thickness, and its unit is  $\stackrel{\circ}{A}m$ .

written as [16, 17]

$$I_{s} = I_{0} \exp\left(\frac{V_{gs} - V_{th}}{nkT/q}\right) \left(1 - \exp\left(\frac{V_{ds}}{kT/q}\right)\right), \tag{1.9}$$

where

$$I_{0} = \mu_{0}C_{ox}\left(\frac{W}{L}\right) \left(\frac{kT}{q}\right)^{2} e^{1.8}, \tag{1.10}$$

and  $V_{gs}$  is the gate-to-source voltage,  $V_{th}$  is the threshold voltage, n is the subthreshold swing factor, k is the Boltzmann's constant, T is the operating temperature, q is the charge of an electron,  $V_{ds}$  is the drain-to-source voltage,  $\mu_0$  is the low field carrier mobility,  $C_{ox}$  is the gate oxide capacitance, W is the channel width and L is the channel length.

According to the above model, the subthreshold leakage current exponentially depends on the operating temperature. Although the exponential dependencies for channel length L and oxide thickness  $t_{ox}$  are not shown in equation (1.10), the subthreshold leakage current exponentially depends on L and  $t_{ox}$  because  $V_{th}$  is a function of these physical device parameters [18]. To illustrate the dependencies of the temperature, the channel length and the oxide thickness for the subthreshold leakage current, the HSPICE simulation result for a NAND gate at 65nm technology node is shown in Figure 1.3(a).

### 1.2.2 Gate Tunneling Leakage Current

According to quantum mechanics, carriers have a finite probability to tunnel through the gate oxide. The current generated by these carriers is so-called the gate tunneling leakage current and have been characterized by BSIM4 gate tunneling model [19]. For describing the major parameters that affect the gate tunneling leakage current, BSIM4 model for the gate tunneling leakage current is simplified as [16, 20]

$$I_g = (A \cdot C)(W \cdot L) \exp\left(-B \cdot \frac{t_{ox}}{V_{gs}}\alpha\right),\tag{1.11}$$

where  $A = q^3/8\pi h\phi_b$ ,  $C = (V_{gs}/t_{ox})^2$ , W is the channel width, L is the channel length,  $B = 8\pi\sqrt{2m_{ox}}\phi_b^{3/2}/3hq$ ,  $t_{ox}$  is the oxide thickness,  $V_{gs}$  is the gate-to-source voltage,  $\alpha$  is a parameter with range from 0.1 to 1 depending on the voltage drop across the oxide (a typical value is 0.22867), h is the Planck's constant,  $m_{ox}$  is the effective mass of electron/hole, q is the charge of an electron, and  $\phi_b$  is the barrier height for electrons/holes in the conduction/valance band. The value of  $\phi_b$  is 3.1eV for electron and 4.5eV for hole.

According to the above empirical model, the gate tunneling leakage current negatively and exponentially depends on the oxide thickness. When the value of the oxide thickness is larger than 20Åm, the gate tunneling leakage current is relatively small comparing with other leakage currents, such as the subthreshold leakage current. However, the gate tunneling leakage current increases 2.5× for 1Åm decrease of oxide thickness. This results in over 30× increase of the gate tunneling leakage current per technology generation [21]. Therefore, the gate tunneling leakage current becomes an important factor in the advanced technology node, e.g the sub-100nm technology node [22]. Furthermore, although the dependencies of the temperature are not explicitly shown in equation (1.11), based on the SPICE simulation with BSIM4 model [23], the gate tunneling leakage current weakly depends on the temperature. To illustrate dependencies of the temperature, the channel length and the oxide thickness for the gate tunneling leakage current, the HSPICE simulation result for a NAND gate at 65nm technology node is shown in Figure 1.3(b).

# 1.2.3 Leakage Powers Inducing Electro-Thermal (Temperature-Power) Coupling Effect

Generally, the on-chip power consumption  $P_{\text{chip}}$  consists of dynamic power and leakage power, and it can be calculated by [24]

$$P_{\text{chip}} = S_{\text{act}} C_{\text{total}} V_{\text{dd}}^2 f + V_{\text{dd}} I_{\text{leak}}, \tag{1.12}$$

where  $S_{\text{act}}$  is the average switching activity of gates,  $C_{\text{total}}$  is the total load capacitance of gates,  $V_{\text{dd}}$  is the supply voltage, f is the operating frequency and  $I_{\text{leak}}$  is the total leakage current of gates.

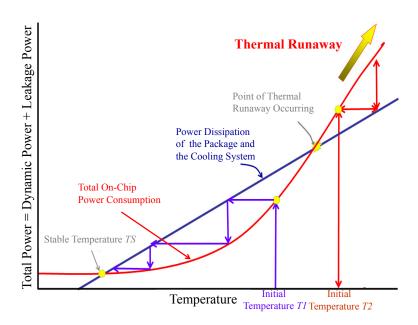

In the right hand side of equation (1.12), the first term is the dynamic power induced by the charging and discharging currents to the load capacitance of gates, and the second term is the leakage power induced by the leakage currents of gates. As mentioned in sections 1.2.1 and 1.2.2, the leakage powers exponentially depend on the operating temperature, and the on-chip leakage power will catch up with the on-chip dynamic power beyond the 90nm technology node [24,25]. On the other hand, the on-chip temperature is transformed from the on-chip power consumption. Therefore, electro-thermal (temperature-power) coupling occurs, and it induces the thermal reliability issues in the modern VLSI designs. For example, thermal runaway [26] may happen if the elector-thermal coupling is not well concerned during the package and the cooling system design.

The mechanism of electro-thermal coupling is exhibited in Figure 1.4. First, with an initial on-chip temperature, the initial on-chip power consumption is obtained. Based on the zeroth law of thermodynamics [27], surplus powers, which can not be dissipated by the package and the cooling system, will transform into heat for achieving the equilibrium of the generating and dissipated powers; therefore, the on-chip temperature increases. On the contrary, as the power dissipation capacity of the package and the cooling system is larger than the generating power of the chip, the on-chip temperature decreases. Because the leakage power consumption depends on the temperature, the total power consumption will change after the temperature is updated. With repeating the above mechanism, if the equilibrium of the generating and dissipated powers of the chip can be achieved, stable on-chip temperature and power consumption

Figure 1.4: The mechanism of electro-thermal coupling.

are accomplished. On the contrary, if the *thermal equilibrium* can not be achieved<sup>1</sup>, the chip thermally runs away. For example, as shown in Fig 1.4, the red curve indicates the generating power of the chip operating at different temperatures. The straight line indicates the maximum power that can be dissipated by the package and cooling system at different operating temperatures. Given an initial temperature T1, the stable operating temperature TS can be achieved after electro-thermal coupling is proceeded. On the other hand, if the initial temperature is T2, the thermal runaway occurs.

As the example illustrating, it is important to consider the electro-thermal coupling to ensure the thermal reliability of the circuit.

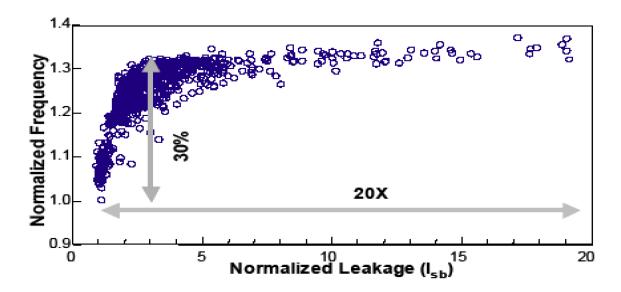

### 1.2.4 Variations of Physical Device Parameters

The shrinking of device geometries has leaded to considerable variations of physical device parameters. As mentioned in sections 1.2.1 and 1.2.2, leakage powers are sensitive to the physical device parameters, such as the channel length and the oxide thickness. Therefore, the variations of physical device parameters will induce considerable fluctuations of the leakage powers. As shown in Figure 1.5, Borkar et. al. [2] have pointed out that 30% process variations can cause about 20× leakage power fluctuations. Because of the electro-thermal coupling, this will result

<sup>&</sup>lt;sup>1</sup>The curves of the generating power of the chip and dissipated power of the package and the cooling system do not have intersection points, or the initial operating temperature is not well chosen [26]

Figure 1.5: Parameter variations impacts on the leakage currents (reprinted from [2]). Here, the y-coordinate indicates the normalized occurrence frequency of the value of the device channel length, and the x-coordinate indicates the normalize value for the subthreshold leakage currents  $(I_{sb})$ .

in considerable fluctuations of the on-chip temperature and the temperature inducing leakage power fluctuations. Therefore, under process variations, the on-chip temperature and leakage power should be treated statistically, especially for the leakage power dominated technology.

# 1.3 Three-Dimensional Integrated Circuit and Its Thermal Issues

The rapid growth of the functionalities and performance requirements of the computer and information technology industry leads to the continually scaling down of the technology. This fact degrades the routability and induces longer interconnects, and limits the performance of planar (two-dimensional) integrated circuits (2-D ICs). For example, the longer interconnect increases the delay of the signal transmission, raises the on-chip power consumption [28], and results in the issues such as signal integrity and routing congestion. With the vertical interconnect strategy, three-dimensional integrated circuit (3-D IC) can reduce the wire length, the transmission delay, the interconnect power and the chip area. Therefore, in recent years, 3-D IC has been regarded as an effective design strategy to overcome the performance bottlenecks of 2-D ICs [3, 29–33].

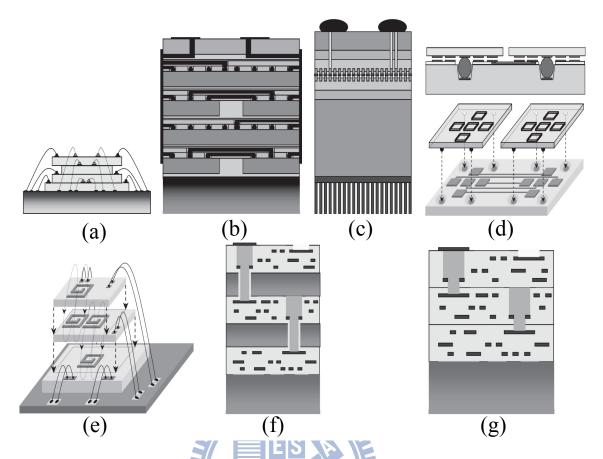

As shown in Figure 1.6, there are several implementation categories of 3-D IC [3]. The

Figure 1.6: Implementation categories of 3-D ICs (reprinted from [3]). (a) Wire-bonded structure. (b) Microbump-3D package structure. (c) Face-to-face structure. (e) Contactless-capacitive with buried bumps structure. (f) Contactless-inductive structure. (f) Through silicon vias (TSVs) based structure with silicon substrates on bulk. (g) TSVs based structure with silicon substrates on insulator (SOI).

wire-bonded structure stacks tiers, and transmits the signal between tiers by using the wires connecting to the board. This category suffers from the limitation on the resolution (for example,  $35\mu m$  pitch between  $15\mu m$  wires) of wire bonders on the board. Therefore, it is only practical for the design with small amount of inputs/outputs (I/Os) between stacked dies.

With the package technology, which can assemble fabricated tiers into a set of carrier wafers with a fixed size, the microbump-3D package structure connects signals between tiers by employing the solder bumps on top surfaces of tiers and the interconnects connecting to peripheries of tiers. This structure offers a much greater vertical interconnect density than that of the wirebonded structure. However, because it still requires routing signals to the tier periphery before sending them back to the destination inside the tiers, this structure does not significantly reduce the transmission delay.

The face-to-face structure flips the top tier, and connects top and bottom tiers by using the

interconnects of the metal layers or the through-via approach. With this structure, the interconnect length can be reduced. However, this structure is restricted to two tiers.

Different from the wire bonded, the microbump-3D package and face-to-face structures, as shown in Figure 1.6 (e) and (f), the contactless-capacitive or the contactless-inductive structure employs the capacitive or inductive coupling to communicate signals between tiers. However, this structure suffers from the challenge for supplying DC power to tiers. Typically, engineers use solder bumping to provide the DC power connectivity between tiers or between a tier and a substrate. Since the distance between the two tiers will be resulted by solder bumps, there are implementation difficulties to combine solder bumping DC connectivity and AC-coupled interconnection. For example, for ensuring the functionality of the capacitive coupling interconnection, the distance between tiers must be small enough to allow sufficient capacitive coupling.

Figure 1.7: The wafer bonding process of the TSVs based 3-D IC (reprinted from [4]).

Finally, as shown in Figure 1.6 (g) and (h), the structures of TSVs based 3-D ICs with silicon on bulk and on insulator etch holes passing through silicon substrates and fill the holes

with conducting materials to provide connectivity between tiers. Typically, these categories can be implemented by the wafer bonding process [4]. The wafer bonding process of a 3-D ICs consisting of three tiers are illustrated in Figure 1.7. First, as shown in Figure 1.7 (a) and (b), the two tiers with completed circuits are planarized, aligned, and bonded face to face. Then, the top handle substrate is removed. After that, as show in Figure 1.7 (c)–(d), holes for TSVs are etched through the top tier. Then, the conducing material are formed to generate TSVs. Finally, as shown in Figure 1.7 (d), the same process is repeated to generate the third stacked tier, and bond pads are etched to generate the I/Os. Due to the ability of current technology, the physical size of TSVs can be small (less than  $50\mu m$ ). Thereby, the TSVs based structures of 3-D IC have the potential to offer the greatest interconnect density; currently, they are the most popular implementation categories of 3-D ICs.

With the stacked tiers structure, 3-D ICs can also provide the flexibility for the mixed signal design, the suitability for the circuit operating on different supply voltages, and the capability for the heterogeneous integration. However, due to the higher power density and the ill of heat dissipation capability, the operating temperature of 3-D ICs will be higher than that of 2-D ICs. The tradeoff between the circuit performance and the thermal issue of 3-D ICs has been studied. As indicated by [3, 32, 33], the expected performance and design reliability of 3-D ICs are degraded because of the high temperature of 3-D ICs. Therefore, researchers have devoted to deal with the thermal issues in different stages of 3-D IC design flow [34–38].

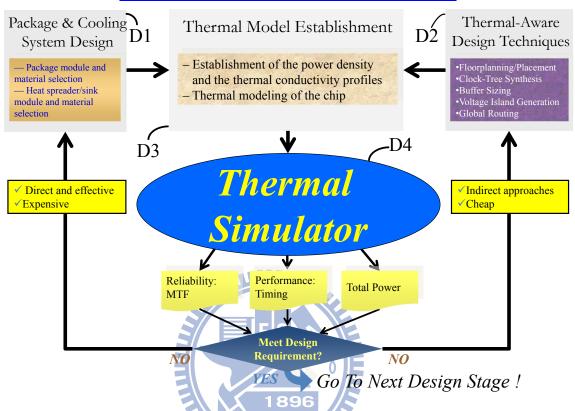

### 1.4 Thermal-Aware Design Flow

To ensure design qualities such as performance, power consumption and thermal reliability, researchers have devoted to thermal-aware design techniques for dealing with the thermal issues. The execution flow of thermal-aware design is shown in Figure 1.8. With the initial package/cooling system and the designed circuit, the power density profile, the thermal conductivity profiles, and the thermal model of the chip are established by the thermal model establishment process shown in D3 of 1.8. Then, the on-chip temperature profile is obtained by the thermal simulator shown in D4 of Figure 1.8. After the on-chip temperature profile is obtained, the circuit performances, such as the timing of the circuit, MTF of the interconnect and the power

consumption, can be evaluated. Then, the circuit performances are checked if they meet the design requirement.

### Thermal-Aware Design Flow

Figure 1.8: Temperature-Aware Design Flow

If the design requirement is not satisfied, one branch for reducing the on-chip temperature is to re-design the package and cooling system, and re-perform the processes shown in D3 and D4 of Figure 1.8 until the circuit performances meet the design requirement. Although the above thermal-aware design strategy is direct and effective, advanced package and cooling systems are expensive for reducing on-chip temperature [39].

Another design branch is to utilize circuit design techniques, such as thermal-aware floor-planning and placement [34–38,40–42], thermal-aware clock-tree synthesis [43], thermal-aware buffer sizing [44], thermal-aware voltage island generation [45,46] and thermal-aware global routing [47,48]. In this branch, the adjustment of the circuit, the thermal model establishment and the thermal simulation are performed until the circuit performances meet the design requirement. The above strategy is prevalent in modern VLSI design because it can meet the design requirement with cheaper package and cooling systems.

### 1.5 Review of On-Chip Thermal Simulation Methods

### 1.5.1 Simulation Methods of Deterministic On-Chip Temperature Profile

As mentioned in section 1.4, a thermal simulator is essential to obtain the temperature profile for providing the thermal cost to different design techniques. In general, after the power and the thermal conductivity profiles of the chip have been obtained, the temperature profile of the 2-D or 3-D chip can be accurately obtained by solving the equivalent SPICE-compatible thermal circuit generated by the finite difference method (FDM) [49, 50]. However, there are numerous nodes in the equivalent SPICE-compatible thermal circuit. This leads to a highly computational complexity for solving the on-chip temperature profile by employing the direct methods, such as HSPICE simulation or the LU decomposition based solver of the modified nodal analysis (MNA) system. Therefore, researchers have devoted to develop efficient yet accurate methods to speed up the runtime of the thermal analysis [5,51–59].

These advanced thermal simulators can be categorized into two classes, numerical and analytical methods. The numerical methods [51–59] firstly apply the FDM to generate the equivalent SPICE-compatible thermal circuit, and then developed advanced numerical techniques to solve the large scale MNA system. Wang et. al. [51] utilized the alternating-direction-implicit (ADI) method to split the equivalent thermal circuit into different alternating directions, and alternately performed the line smooth scheme in each direction. In [52,53], based on the moment matching and the Krylov subspace projection techniques, the model order reduction techniques were employed to improve the efficiency of transient simulation for the on-chip temperature profile. Li et. al. [54] applied the multi-grid method to speed up the convergence rate of basic iterative methods, and proposed a model order reduction scheme to further save the runtime of the transient simulation. Based on the framework of the multi-grid method, Yong et. al. [55] proposed the adaptive volume meshing and time-step selecting approaches to further reduce the complexity of the thermal analysis. Due to the flexibility of dealing with the complex structure, the numerical methods are the main stream in back-end design stages, such as the post layout thermal verification.

As pointed out in [40–42, 57–59], temperature-aware design should be brought to early design stages, such as floorplanning and placement stages. Since the detail layout of inter-

connects is not available in early design stages, an appropriate thermal model is required for the pre-layout interconnect layers. Therefore, Huang and Skadron el. al. [56–59] proposed compact thermal modeling techniques for the package, the cooling system and the pre-layout interconnect layers. With the compact thermal model, they proposed macro and grid based thermal circuit modeling techniques for coarse and fine granularities thermal simulation of the micro-architecture level design, respectively. Since their proposed thermal analysis method also requires solving a SPICE-compatible thermal circuit, the advanced numerical methods stated in [51–55] can also be adopted to further reduce the complexity.

The other category of thermal simulators, which is suitable for early design stages, is the analytical method. The primary advantage of analytical approaches is that they avoid the volume meshing procedure of entire substrate, and have closed-form representations of the on-chip temperature profile. Hence, they are flexible to obtain the temperature profile of certain user-specified regions without performing the full-chip thermal simulation. Furthermore, based on the closed-form representations, the on-chip temperature profile can be fast evaluated without solving the equivalent MNA system of the thermal circuit.

One existing analytical based full-chip thermal simulation technique is the Green's function based method [5]. The simulation framework proposed in [5] is executed as follows. First, the closed-form of the steady state Green's function corresponding to an impulse power source locating at any arbitrary location of die is firstly obtained. After that, the steady state on-chip temperature profile can be got by performing a table look-up method for obtaining the convolution of Green's function and the on-chip power density profile. To deal with the low efficiency of the look-up table method for the huge number of power sources, they approximated the on-chip power density profile by cosine waveforms. After that, they casted the on-chip temperature profile into the form of discrete cosine transform (DCT). With the fast Fourier transform (FFT), their complexity for obtaining the on-chip temperature profile can be in  $O(MN \log_2 MN)$ . Here, M and N are numbers of divisions for representing the on-chip power density and temperature profiles along x- and y-directions of die, respectively.

However, as their results exhibiting, a large truncation number of their basis functions is required to achieve an accurate estimation of the on-chip temperature profile. Moreover, the

numbers M and N are restricted to be the same with the truncation numbers of their basis functions along x-, and y-directions of die, respectively. This results in the restriction of the mesh size in their framework. Further, their formulation can only provide the steady state on-chip temperature profile. Although the steady state on-chip temperature profile is more concerned in thermal-aware physical design engines [34–38,42], as indicated by [56], the temporary characteristics of the on-chip temperature are also important for the real-time dynamic thermal management with transient workloads. Therefore, although the existing analytical based on-chip thermal analyzer [5] takes the advantage of their closed-form representation for the on-chip temperature profile, it still requires improving strategies to extend their application scopes.

### 1.5.2 Simulation Methods of Statistical On-Chip Temperature Profile

As mentioned in section 1.2.4, the process variations induce leakage power fluctuations. For the same designed circuit, this fact will lead to different temperature profile of different fabricated chip. However, the thermal simulation methods mentioned in section 1.5.1 did not take into account the process variations issues in their leakage power models. Thus, under the process variations being considered, they are inadequate to precisely provide the on-chip temperature profile, the hot-spot locations and the thermal related costs of thermal-aware design engines. To provide the statistical characteristics of the on-chip temperature profile, one direct strategy is to apply the Monte Carlo (MC) method. However, the MC method requires performing a large amount of thermal simulations corresponding to the sampling points for the device parameters. This leads the MC method to be inefficient for the practical application.

Instead of the MC method, Jaffari et. al. [9] proposed a recursive log-normal approximation algorithm to obtain the mean and standard deviation profiles of the statistical on-chip temperature distribution. Compared with the MC method, they have successfully demonstrated its efficiency and accuracy for estimating the mean and standard deviation profiles of the on-chip temperature distribution in the macro-architectural level. However, instead of constructing the leakage power models for each type of macro/gate, their proposed leakage power models were built for each bin (grid) of die. Hence, their bin based leakage power models need to be rebuilt after the macros/gates are exchanged by the optimization engines such as floorplanners or placers. Since the establishment of their leakage power models require time-consuming HSPICE

simulation and curve fitting, the re-establishing of the bin based leakage power models will degrade their efficiency for providing the thermal simulation in thermal-aware design flow. Moreover, their recursive log-normal approximation algorithm is restricted to their proposed leakage power models. As a matter of fact, the leakage power model is going to be more complicated for maintaining an acceptable accuracy level while the technology continuously scales down. Thus, their simulation framework still requires to be reformed for dealing with more complex leakage power models, which is required for more advanced technology generations.