## 國立交通大學

# 電信工程研究所

## 博士論文

應用於多頻段與超寬頻通訊之射頻接收 電路設計與分析

Design and Analysis of RF Receiver Circuits for Multiband and Ultra-Wideband Communication Applications

研究生:梁清標 Ching-Piao Liang

指導教授 : 鍾世忠 Shyh-Jong Chung

中華民國九十九年三月

## 應用於多頻段與超寬頻通訊之射頻接收 電路設計與分析

# Design and Analysis of RF Receiver Circuits for Multiband and Ultra-Wideband Communication Applications

研究生:梁清標 指導教授:鍾世忠 博士 Student: Ching-Piao Liang Advisor: Dr. Shyh-Jong Chung

A Dissertation

Submitted to Institute of Communication Engineering College of Electrical and Computer Engineering National Chiao Tung University in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in Communication Engineering Hsinchu, Taiwan

2010年3月

## 應用於多頻段與超寬頻通訊之射頻接收電 路設計與分析

研究生:梁清標 指導教授:鍾世忠 博士

#### 國立交通大學

#### 電信工程研究所

#### 摘要

本篇論文提出了數種適用於多頻段與超寬頻通訊系統的 0.18 微米互補式金 氧半製程射頻積體電路元件之架構、分析與設計。其中包含了 (1) 兩個使用諧 振切換與雜訊消除電路的多頻帶低雜訊放大器;(2) 具鏡像頻率抑制混頻器的設計; (3) 三個低功率超寬頻低雜訊放大器的分析與設計;(4) 採用降低相位雜訊技術的壓 控振盪器電路。

多頻帶低雜訊放大器藉由切換的概念來實現多頻帶操作,其能有效地減少系統面積來降低製作的成本,並且於第二個多頻帶低雜訊放大器設計中,利用回授 式雜訊相消電路能同時達到輸入匹配以及改善雜訊指數的效果。另外在所設計電 路的主動元件中額外引入一阻值較大的基極電阻,以避免雜訊從電晶體的基極端 交互流竄而惡化電路本身的雜訊指數特性。在不額外增加晶片面積、製程步驟、 以及直流功率損耗的前提之下,採用此雜訊降低電阻於 2.5 GHz 操作頻帶時,能 達到 32%的雜訊指數改善效果,可廣泛地應用在現今低雜訊放大器的設計。

其次,本論文提出了一個具鏡像頻率抑制的吉伯特降頻混頻器。相對於傳統的 Hartley 或 Weaver 鏡像頻率抑制電路架構,此混頻器能大幅地降低直流功率損 耗與電路設計的複雜度。並且搭配一負阻抗產生主動電路,藉由合適的負阻抗來 消除濾波器的正電阻以提升其品質因數 Q,進而增進鏡像訊號抑制的效果。此混 頻器於 2.4/5.2 GHz 使用頻段的量測結果如下:轉換增益 (conversion gain) 為 10.5/11 dB、一階與三階交叉點的輸入功率 (IIP<sub>3</sub>) 為 4.9/-5.2 dBm、單邊雜訊指 數 (SSB NF) 為 10/13 dB、鏡像頻率抑制效果可達 36/45 dB。

再其次,由於超寬頻系統的訊號強度遠低於 IEEE 802.11 a/b/g 以及 1.8 GHz DCS/GSM 系統,因此首先我們在第一個超寬頻低雜訊放大器中提出具頻帶外訊 號抑制能力的輸入匹配網路去壓制其他系統所造成的干擾。另外我們在第二個低 雜訊放大器電路中,藉由使用一個回授結構以及雙頻帶主動式低功率帶拒濾波電 路進一步地提升抑制干擾訊號的效果。經改良所設計出的低雜訊放大器在 1.8/2.4/5.2 GHz 能夠達到最大抑制效果為 55/48/45 dB。另一方面,由於減少輸入 端損耗元件的使用能有效地改善電路的雜訊指數,在此引入了電晶體的寄生電容 來達到超寬頻輸入匹配特性,當輸入回返損耗 (input return loss) 大於 10 dB 以上 時,其頻帶內最大增益為 16.2 dB,最小雜訊指數為 2.3 dB,且總直流功率損耗 僅為 6.8 mW。

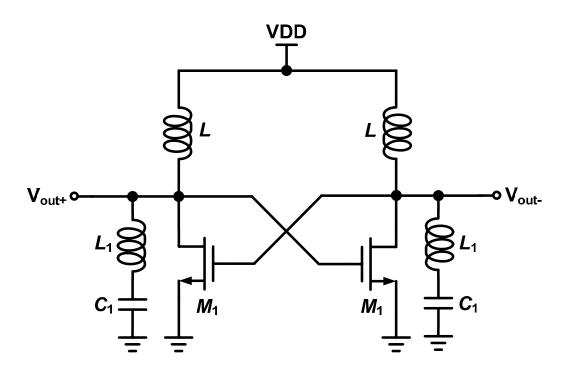

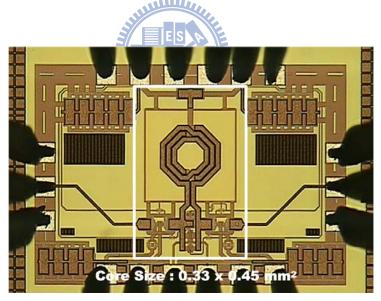

最後提出的是具降低相位雜訊參數之壓控振盪器電路,藉由最佳化被動元件 尺寸以及額外設計的二次諧波抑制電容與基極偏壓,整體電路性能參數 FOM (figure of merit) 能達到-190 dBc/Hz。此壓控振盪器晶片所使用的面積為 0.15 微 米平方,且由實驗的結果分析得知,總功率耗損僅為 1.9 mW,而在 1 MHz offset 時其相位雜訊約為-119 dBc/Hz。

ii

# Design and Analysis of RF Receiver Circuits for Multiband and Ultra-Wideband Communication Applications

Student : Ching-Piao Liang Advisor : Dr. Shyh-Jong Chung

## Department of Communication Engineering National Chiao Tung University

In this dissertation, the design methodologies and implementations of RF receiver circuits for multiband and ultra-wideband communication applications are proposed. There are four parts in this thesis, including: (1) the design of two triple-band low-noise amplifiers (LNAs) using switched resonators and a noise cancelation technique, (2) the design of dual-band image rejection mixer, (3) the analysis and design of three low-power UWB LNAs, and (4) the design of voltage-controlled oscillator (VCO) with phase-noise improvement.

First of all, the design of two triple-band LNAs with switched resonators is presented and fabricated in the TSMC 0.18-µm CMOS process. The proposed triple-band LNAs are demonstrated the feasibility to effectively decrease the size of multi-band RF systems by using a switched component. In addition, a considerable noise power diminution in MOS devices with an additional larger substrate resistor is presented in the second approach of the triple-band LNA. A 32% noise reduction of MOS devices can be achieved at 2.5 GHz without extra chip area, CMOS process steps and dc power. This noise reduction technique in MOS device is very promising in the nowadays LNA designs.

Secondly, this thesis presents a 2.45/5.2 GHz dual-band Gilbert downconversion mixer with image rejection function is presented, which is implemented in the 0.18-µm CMOS technology. The proposed differential dual-band image rejection circuitry is employed for the 2.45/5.2 GHz WLAN application to effectively diminish the dc power consumption and complexity of circuit design compared to the traditional Hartley or Weaver architectures. Moreover, the cross-connected pair consisted of NMOS and PMOS transistors in the proposed notch filter will further ameliorate the image rejection capability. The IC prototype attains conversion gain of 10.5/11 dB, IIP3 of -4.9/-5.2 dBm for RF= 2.45/5.2 GHz and IF=500 MHz while the image rejection ratio is better than 36/45 dB in the whole operation bandwidth.

Thirdly, three low-power UWB LNAs using 0.18-µm CMOS technology are presented. Due to the FCC's stringent power-emission limitation at the transmitter, the received signal power in the UWB system is smaller than those of the close narrow-band interferers such as the IEEE 802.11 a/b/g WLAN, and the 1.8 GHz DCS/ GSM. Therefore, we proposed a wideband input network with out-band rejection capability to suppress the out-band interference for our first UWB LNA. Moreover, a feedback structure and dual-band notch filter with low power active inductors will further attenuate the outband interferers without deteriorating the input matching bandwidth in the second UWB LNA. The 55/48/45 dB maximum rejections at 1.8/2.4/5.2 GHz, 15 dB power gain, and 3.5 dB minimum noise figure can be measured while consuming dc power of only 5 mW. On the other hand, to further improve the noise figure performance of the above out-band rejection LNAs, a new matching technique is presented in the third UWB LNA. The proposed broad-band

input match network can be obtained easily by selecting an appropriate width of the transistor, which could effectively avoid the usage of the low-*Q* on-chip inductors in the input network. The IC prototype achieves good performances: 16.2 dB maximum power gain, better than 10 dB input return loss, and 2.3 dB minimum noise figure while consuming dc power of only 6.8 mW.

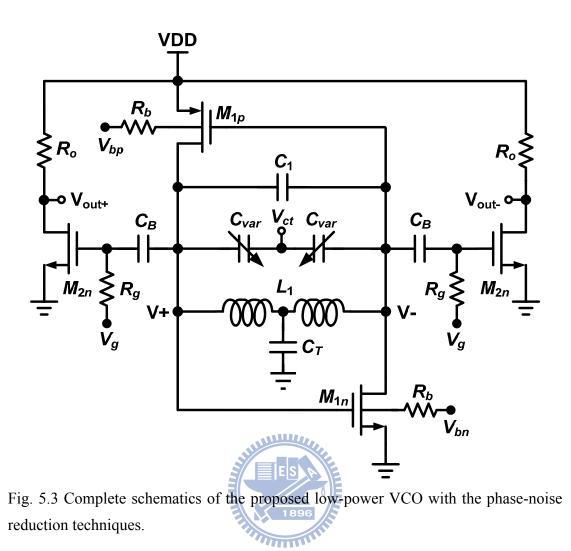

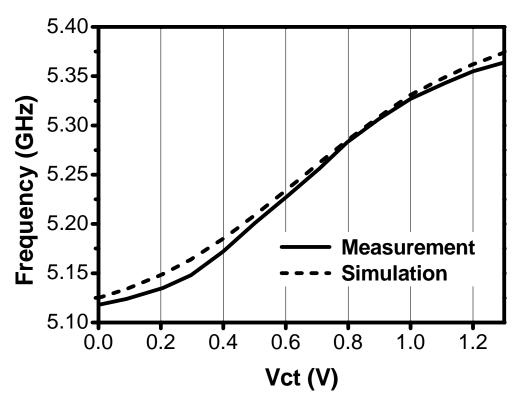

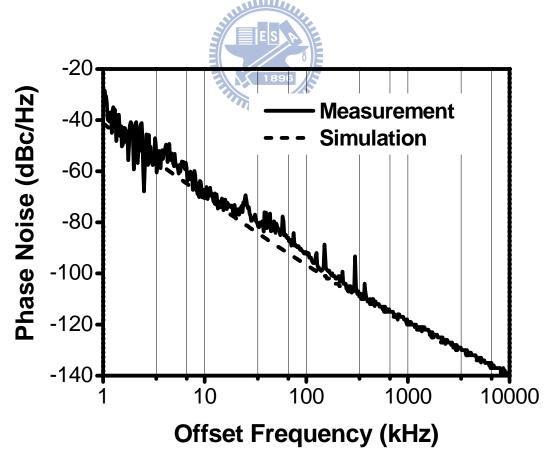

Finally, a low-power 5.25 GHz VCO with phase-noise improvement is designed in a 0.18- $\mu$ m CMOS 1P6M process. Due to the usage of a larger value of parallel capacitor, an additional harmonic-suppressed capacitor, and an appropriate bulk bias voltage of the transistor, a good figure of merit (FOM) of -190 dBc/Hz can be achieved without extra chip area and CMOS process steps. The fabricated VCO operates from 5.12 to 5.36 GHz with a power consumption of 1.9 mW and active chip area of 0.15 mm<sup>2</sup>. The measured phase noise at 1 MHz offset is about -119 dBc/Hz.

### 誌謝

本論文的完成,有賴許多貴人的協助、支持、鼓勵與相伴,在此衷心的感謝 您們!首先,我要感謝我的指導教授鍾世忠博士,在這四年半的博士班生涯中, 對於研究方面給予細心的指導,不厭其煩的叮嚀以及對我的包容與關懷,無論是 學術研究或待人處世,使學生在學業上獲得許多的知識並找到屬於自己的方向與 目標。此外也要特別感謝碩士班指導教授黃建彰博士,因為老師的栽培提攜,在 研究上給予學生滿滿的熱誠與信心,讓學生能順利的進入交通大學就讀博士班, 並以樂觀的思維來面對博士班的各種挫折與挑戰。

在此感謝口試老師:陳俊雄教授、黃天偉教授、張志揚教授、孟慶宗教授、 郭建男教授、邱煥凱教授,能在百忙之中抽空前來,給予論文上的指導與建議, 讓學生受益良多,也使得論文更為完備。感謝大學時期電子學啟蒙老師林螢光教 授在學生追求學問最無助的時候適時的拉我一把,讓學生能把電子學相關課程的 基礎扎穩,這份恩情學生永遠謹記在心,感謝學長佩宗、侑信與學姐菁偉,在研 究上給予的指導和建議;助理珮華姐姐的關心與協助;助理柯柯老人家所帶來的 歡笑;學弟妹顯鴻、郁娟、敦智、煥能、源哥、竣義、孝聰、泓偉、淑君、天建、 威璁、智偉、明緯、郁凱,在課業上互相的砥礪與生活上的陪伴,慶幸我們能共 同擁有酸苦甘甜的回憶;同時也感謝好友楊翎、鴻依給予的關心與包容,並且總 是能適時的替我分憂解勞;碩班同窗好友德棻、韋廷、煥哲、威弦、菘茂在實作 上提供的寶貴經驗;另外,要特別感謝伯父(曾世忠)與伯母(張素華)在日常生活 上給予實質與心靈上幫忙與鼓勵。

最重要的是感謝我的家人,特別是我的父母,因為有你們無私的奉獻與支持,讓我無後顧之憂地完成學業與研究,才能成就今日的我。謹以此論文獻給所 有幫助過我與關心我的人。

梁清標 于新竹交大

#### 2010年4月

### CONTENTS

| <b>ABSTRACT</b> (  | Chinese)                                             | i   |

|--------------------|------------------------------------------------------|-----|

| ABSTRACT (English) |                                                      | iii |

| ACHNOWLEDGEMENT    |                                                      |     |

| CONTENTS           |                                                      | vii |

| TABLE CAPT         | <b>FIONS</b>                                         | ix  |

| FIGURE CAP         | TIONS                                                | X   |

| CHAPTER 1          | INTRODUCTION                                         | 1   |

| 1.1                | BACKGROUND                                           | 1   |

| 1.2                | <b>RESEARCH MOTIVATION</b>                           | 2   |

| 1.3                | THESIS ORGANIZATION                                  | 4   |

| CHAPTER 2          | TRIPLE-BAND LOW NOISE AMPLIFIER                      | 7   |

| 2.1                | INTRODUCTION                                         | 7   |

| 2.2                | TRIPLE-BAND LOW NOISE AMPLIFIER WITH                 | 10  |

|                    | INPUT MATCHING DESIGN                                |     |

|                    | 2.2.1 Circuit Design and Analysis                    | 10  |

|                    | 2.2.2 Simulation and Experimental Results            | 14  |

| 2.3                | TRIPLE-BAND LOW NOISE AMPLIFIER WITH                 | 17  |

|                    | NOISE REDUCTION                                      |     |

|                    | 2.3.1 Triple-Band Load Network                       | 17  |

|                    | 2.3.2 Input Matching with Partial Noise Cancellation | 19  |

|                    | 2.3.3 Noise Reduction with Larger Substrate Resistor | 22  |

|                    | 2.3.4 Simulation and Experimental Results            | 25  |

| 2.4                | SUMMARY                                              | 29  |

| CHAPTER 3          | <b>IMAGE-REJECTION MIXER FOR</b>                     | 31  |

|                    | DUAL-BAND OPERATION                                  |     |

| 3.1                | INTRODUCTION                                         | 31  |

| 3.2                | CIRCUIT DESIGN                                       | 33  |

|                    | 3.2.1 Effect of Nonlinearity                         | 34  |

|                    | 3.2.2 Filter Design with Negative-Resistance Cells   | 35  |

| 3.3                | EXPERIMENTAL RESULTS                                 | 39  |

| 3.4                | SUMMARY                                              | 42  |

| CHAPTER 4        | WIDE       | E-BAND LOW NOISE AMPLIFIER          | 44  |

|------------------|------------|-------------------------------------|-----|

|                  | WITH       | HOUT-BAND REJECTION                 |     |

| 4.1              | INTRO      | DUCTION                             | 44  |

| 4.2              | WIDE       | -BAND LOW NOISE AMPLIFIER WITH      | 47  |

|                  | OUT-       | BAND REJECTION INPUT NETWORK        |     |

|                  | 4.2.1      | Circuit Design and Analysis         | 48  |

|                  | 4.2.2      | Optimum Out-Band Rejection          | 54  |

|                  | 4.2.3      | Simulation and Experimental Results | 59  |

| 4.3              | WIDE       | -BAND LOW NOISE AMPLIFIER WITH      | 63  |

|                  | FEED       | BACK STRUCTURE AND NOTCH FILTER     |     |

|                  | 4.3.1      | Effect of Feedback Structure        | 63  |

|                  | 4.3.2      | Analysis of Dual-Band Notch Filter  | 65  |

|                  | 4.3.3      | Design of Low Power Active Inductor | 68  |

|                  | 4.3.4      | Simulation and Experimental Results | 74  |

| 4.4              | WIDE       | -BAND LOW NOISE AMPLIFIER WITH      | 77  |

|                  | A NEV      | W MATCHING TECHNIQUE                |     |

|                  | 4.4.1      | Circuit Design and Analysis         | 77  |

|                  | 4.4.2      | Simulation and Experimental Results | 84  |

| 4.5              | SUMM       | IARY                                | 86  |

| CHAPTER 5        | VOL        | TAGE-CONTROLLED OSCILLATOR          | 88  |

|                  |            | I PHASE-NOISE IMPROVEMENT           |     |

| 5.1              |            | DUCTION                             | 88  |

| 5.2              | CIRCU      | U <b>IT DESIGN</b>                  | 90  |

| 5.3              | EXPE       | RIMENTAL RESULTS                    | 94  |

| 5.4              | SUMM       | IARY                                | 97  |

| CHAPTER 6        | CON        | CLUSIONS                            | 99  |

| APPENDIX         |            |                                     | 101 |

| REFERENCE        | REFERENCES |                                     |     |

| VITA             |            |                                     | 109 |

| PUBLICATION LIST |            |                                     | 110 |

### **TABLE CAPTIONS**

| Table 2.1 | Performance summary of previously published LNAs | 30 |

|-----------|--------------------------------------------------|----|

| Table 3.1 | Comparison with previously published mixers      | 43 |

| Table 4.1 | UWB LNA Performance summary                      | 87 |

| Table 5.1 | Performance summary of the low phase-noise VCOs. | 98 |

### FIGURE CAPTIONS

| Fig. 1.1<br>Fig. 2.1 | Several different applications merged into a system.<br>(a) Triple-band LNA reported in [8], [9]. (b) A noise-canceling amplifier in [15]-[17].                                                                                         | 3<br>8 |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Fig. 2.2             | <ul> <li>(a) Schematic of a dual-band input matching. (b)</li> <li>Schematic of a single-band input matching. (c) A</li> <li>proposed triple-band input matching with an additional</li> <li>switched component.</li> </ul>             | 11     |

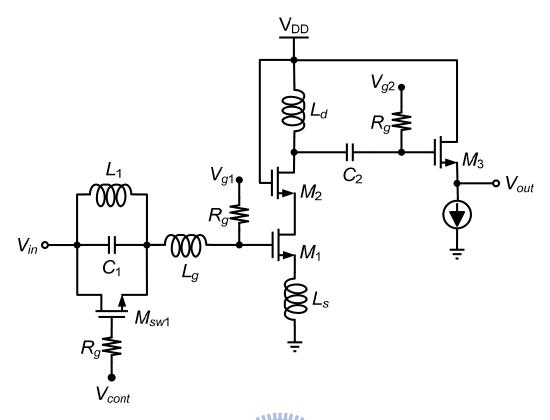

| Fig. 2.3             | Complete schematic of the proposed first triple-band LNA with input matching design.                                                                                                                                                    | 13     |

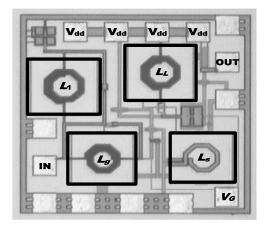

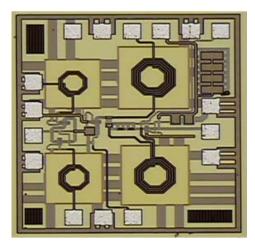

| Fig. 2.4             | Microphotograph of the first triple-band LNA with $0.98 \times 0.94 \text{ mm}^2$ die area.                                                                                                                                             | 14     |

| Fig. 2.5             | Measured and simulated S-parameters of proposed first triple-band LNA.                                                                                                                                                                  | 15     |

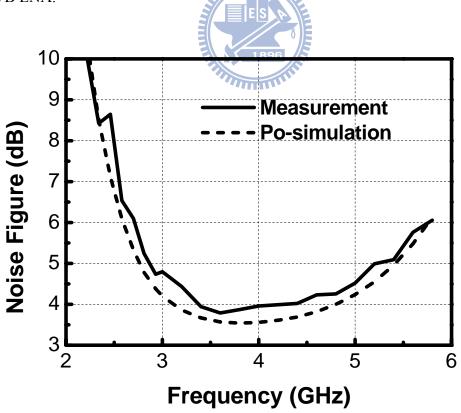

| Fig. 2.6             | Measured and simulated noise figure of proposed first triple-band LNA.                                                                                                                                                                  | 16     |

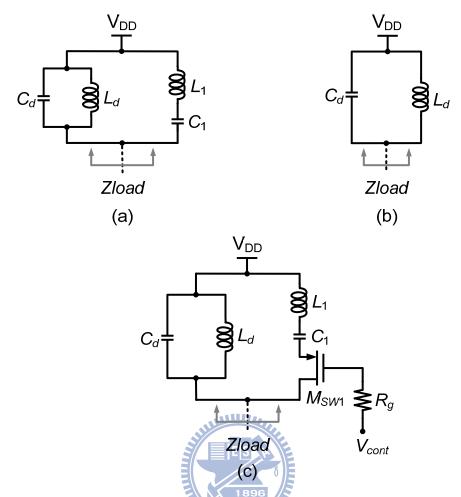

| Fig. 2.7             | (a) Schematic of a dual-band load network. (b) Schematic of a single-band load network. (c) A proposed triple-band load network with an additional switched component.                                                                  | 18     |

| Fig. 2.8             | The load impedance versus frequency with different $C$ parameters. (a) A dual-band load network when the switch is on. (b) A single-band load network when the switch is off.                                                           | 20     |

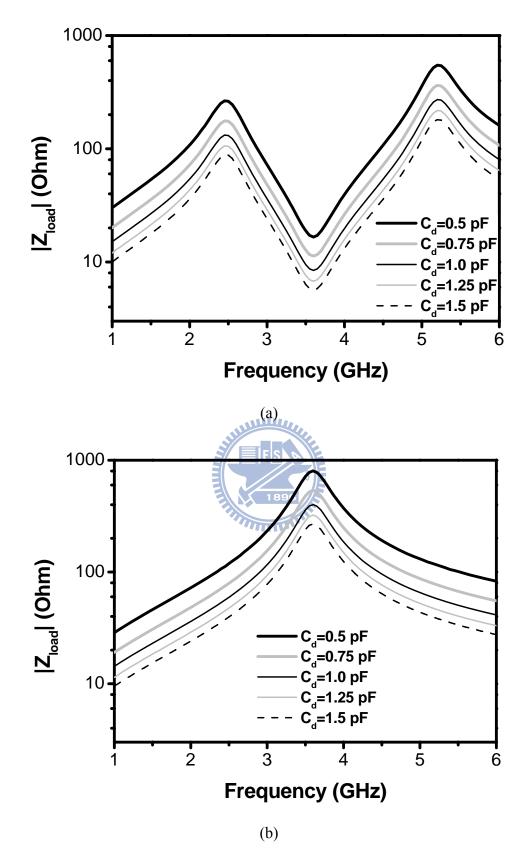

| Fig. 2.9             | Principle of the noise-canceling technique.                                                                                                                                                                                             | 21     |

| Fig. 2.10            | Simulated noise figures with and without the noise-canceling technique.                                                                                                                                                                 | 21     |

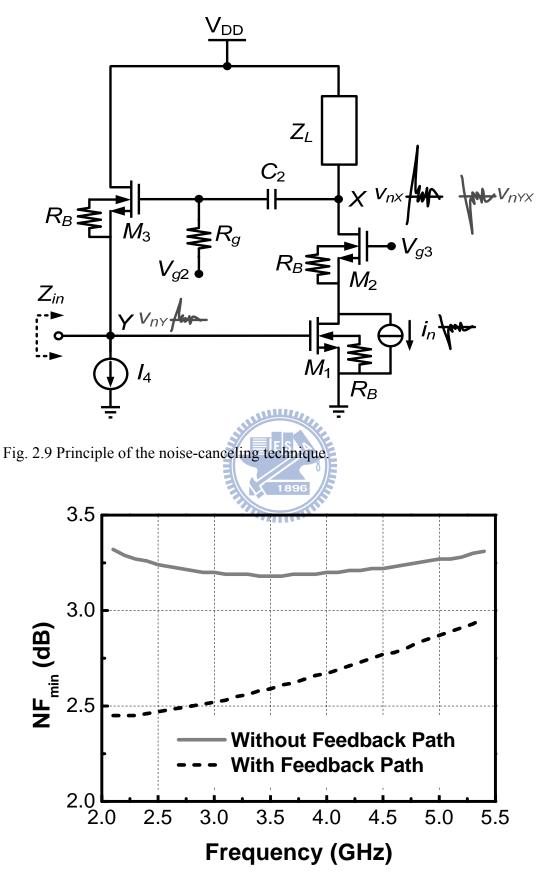

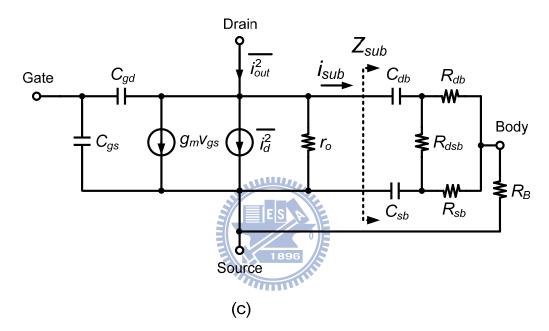

| Fig. 2.11            | (a) A NMOS device with a larger substrate resistance $R_B=8$ k $\Omega$ . (b) Structure of a NMOS with a larger substrate resistance $R_B$ . (c) The noise equivalent circuit of NMOS device with a larger substrate resistance $R_B$ . | 23     |

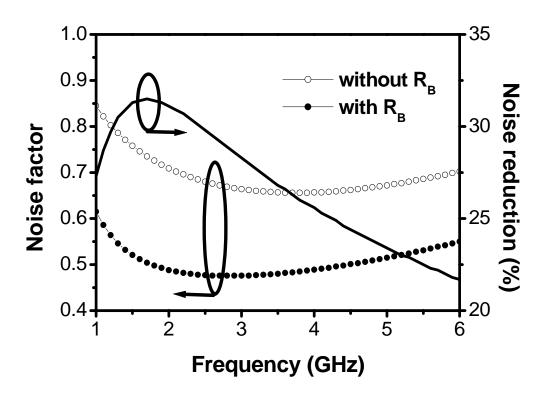

| Fig. 2.12            | Simulated the total MOS device noise factor $F$ (NF=10log <sub>10</sub> $F$ ) with and without the additional resistance $R_B$ =8 k $\Omega$ and the noise reduction when resistance $R_B$ is used.                                     | 24     |

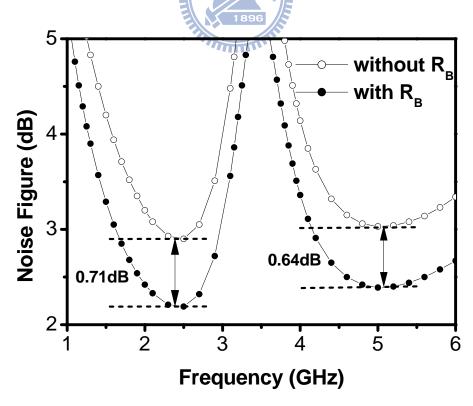

| Fig. 2.13            | Simulated noise figure with and without the additional resistor $R_B=8$ k $\Omega$ . (a) Dual-band status when the                                                                                                                      | 25     |

switch is on. (b) Single-band status when the switch is off.

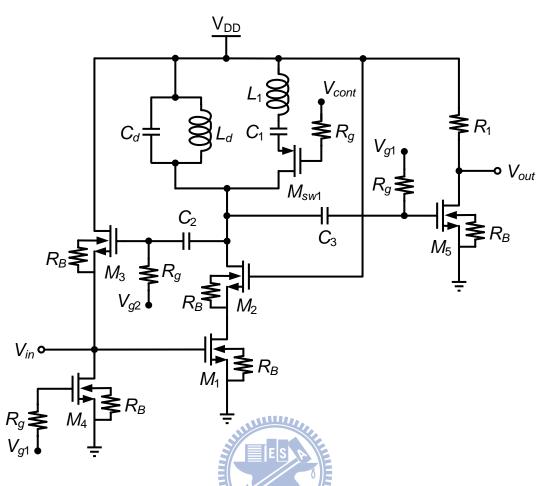

- Fig. 2.14 Complete schematic of the proposed second 26 triple-band LNA with the load network design and the noise reduction resistance  $R_B$ .

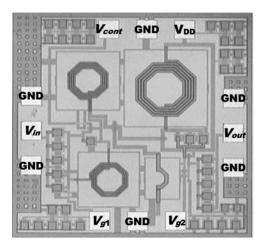

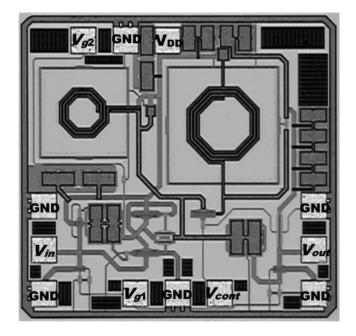

- Fig. 2.15 Microphotograph of the second triple-band LNA with 27  $0.75 \times 0.69 \text{ mm}^2$  die area.

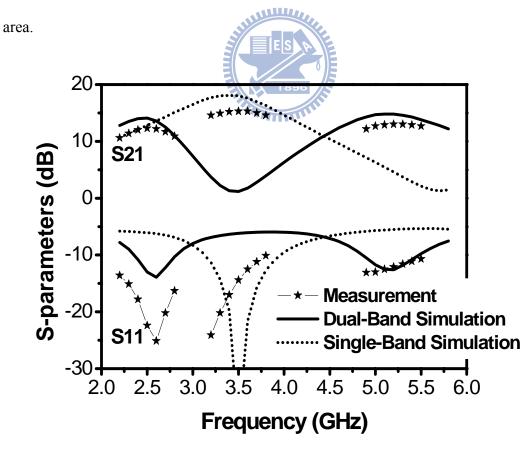

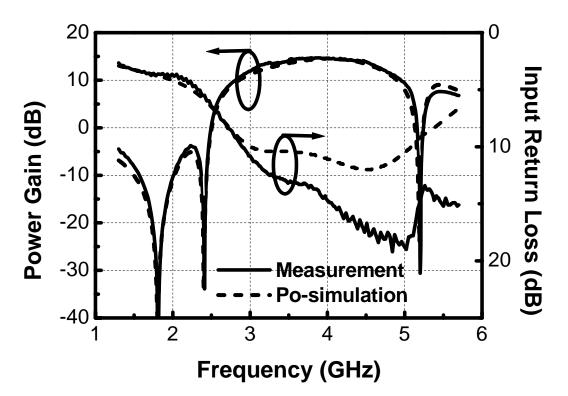

- Fig. 2.16 Measured and simulated S-parameters of the second 28 triple-band LNA.

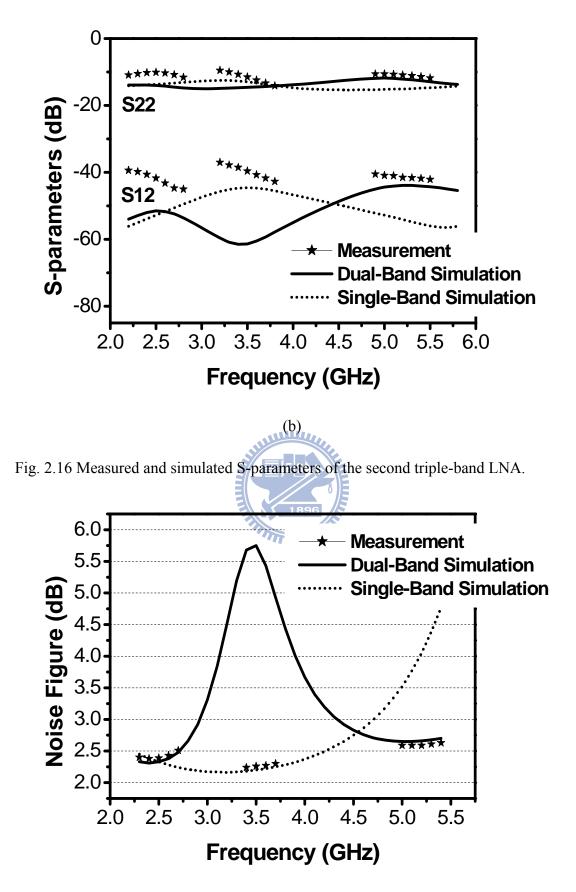

- Fig. 2.17 Measured and simulated noise figure of the second 28 triple-band LNA.

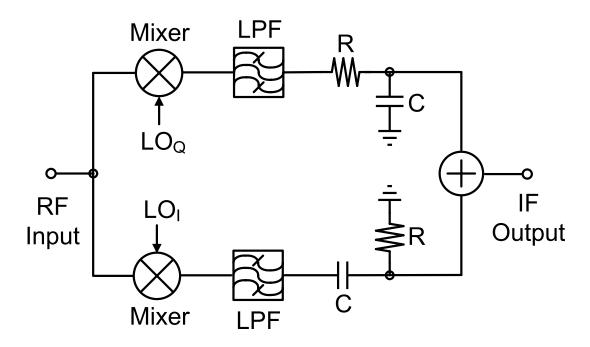

- Fig. 3.1Block diagram of the Hartley down-converter.32

- Fig. 3.2Block diagram of the Weaver down-converter.32

- Fig. 3.3 Complete schematics of the proposed dual-band image 33 rejection mixer.

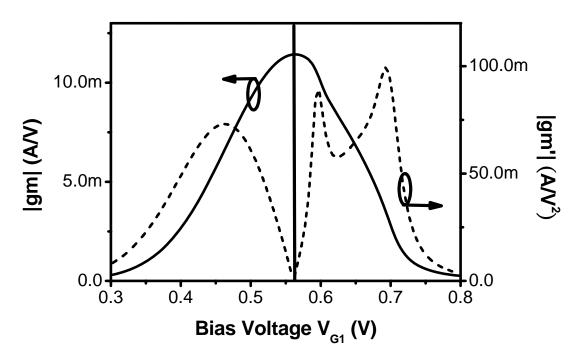

- Fig. 3.4 The nonlinear effect of a transistor with the bias 34 voltage  $V_{G1}$ .

- Fig. 3.5A third-order notch filter reported in [37].35

- Fig. 3.6 (a) The proposed differential dual-band third-order 36 notch filter. (b) The half circuit of (a). (c) Equivalent circuit at low frequency. (d) Equivalent circuit at high frequency.

- Fig. 3.7 The proposed differential dual-band notch filter with 38 the negative-resistance cells consisted of NMOS and PMOS transistors.

- Fig. 3.8 The proposed notch filter in the dual-band operation 39 frequencies has no influence on the impedance between nodes *X* and *Y*.

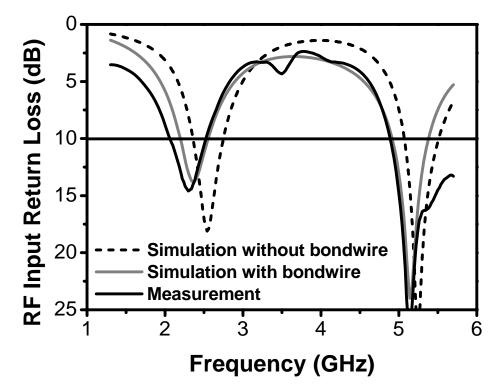

- Fig. 3.9 Measured and simulated RF return loss of the 40 proposed mixer.

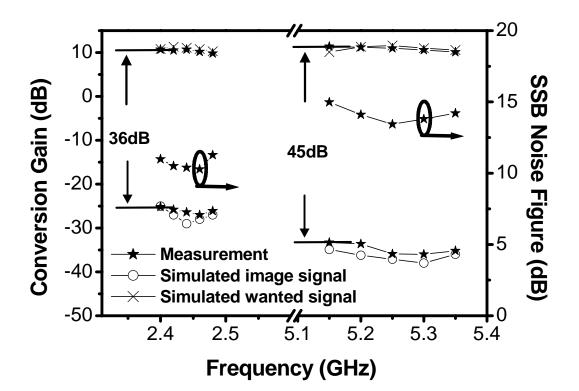

- Fig. 3.10 Conversion gain and noise figure of the proposed 41 mixer.

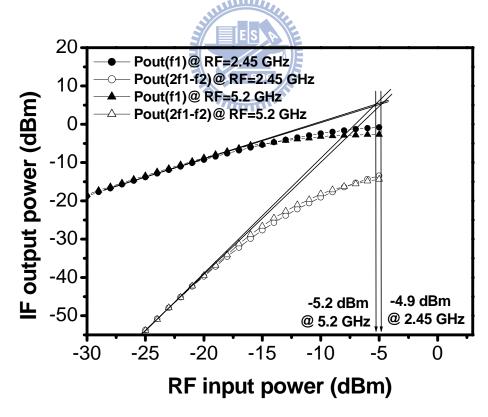

- Fig. 3.11 Measured results of fundamental output power and 41 IM3 for the proposed mixer with RF input frequency spacing of 10 MHz.

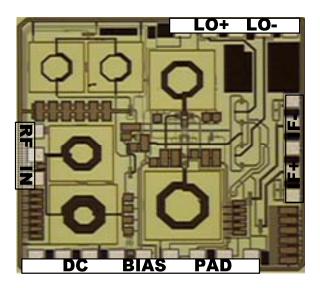

- Fig. 3.12 Microphotograph of the mixer. Die area is  $1.07 \times 1.07$  42 mm<sup>2</sup>.

- Fig. 4.1 Spectrum of the UWB system with large interferers. 45

- Fig. 4.2 Complete schematics of the first UWB LNA with 48 out-band rejection.

- Fig. 4.3 Simulated ideal power gain with and without out-band 50 rejection improvement.

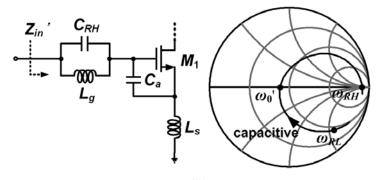

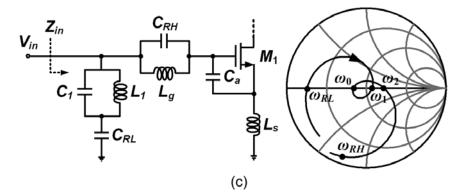

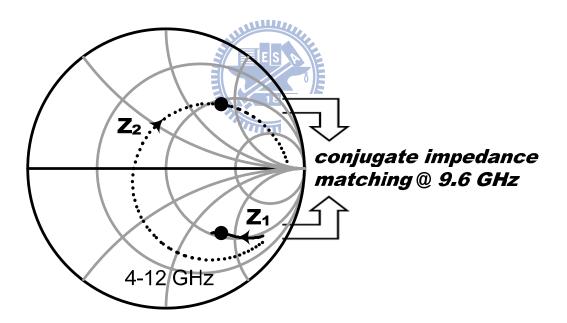

- Fig. 4.4 Input reflection coefficients on the Smith chart for (a) 52 the  $L_1C_1$ - $C_{RL}$  circuit with impedance  $Z_R$ , (b) the narrow-band input network with impedance  $Z_{in}$ , and (c) the total circuit with impedance  $Z_{in}$ .

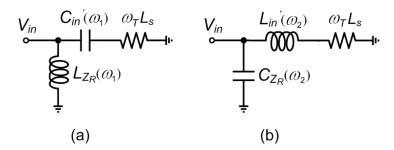

- Fig. 4.5 Equivalent circuits for the broad-band input network at 53 (a) the parallel resonance frequency  $\omega_1$  and (b) the parallel resonance frequency  $\omega_2$ .

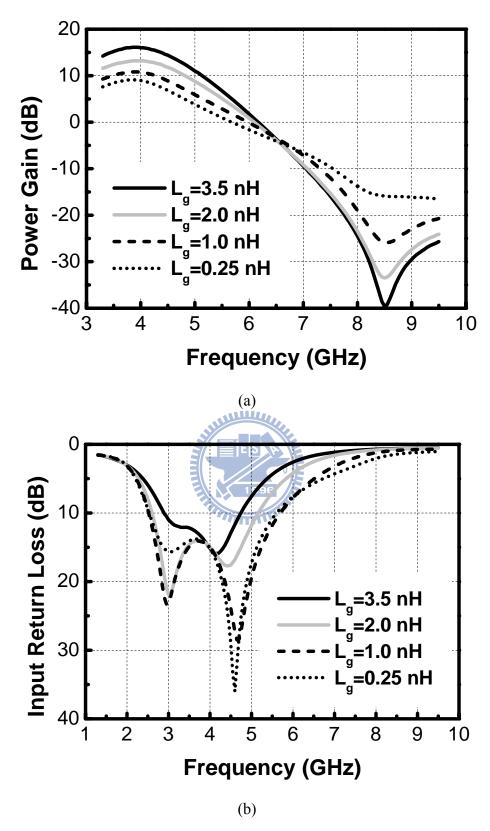

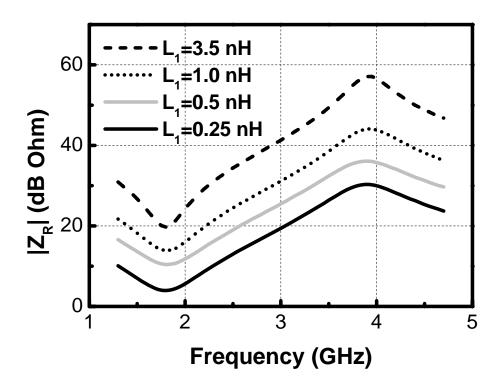

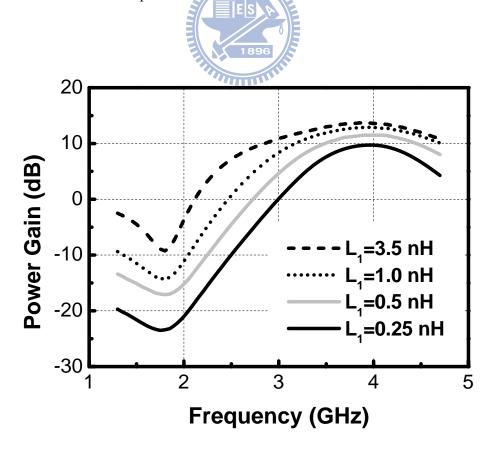

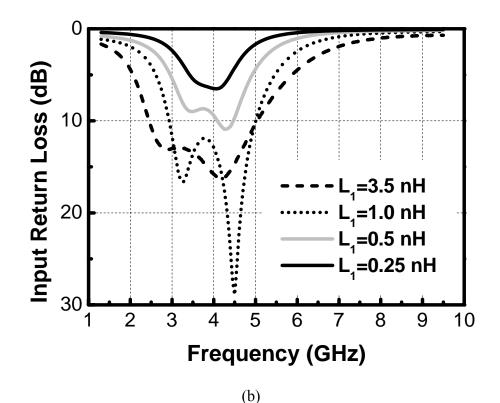

- Fig. 4.6 (a) Simulated power gain  $(S_{21})$  and (b) input return loss 55  $(1/S_{11})$  for different values of  $L_g$  with  $L_1 = 2.0$  nH,  $C_1 = 0.82$  pF, and  $C_{RL} = 2.95$  pF. The transmission zero  $\omega_{RH}$  is kept constant.

- Fig. 4.7 The impedance  $Z_R$  versus frequency with different 57 values of  $L_1$ . The transmission zero  $\omega_{RL}$  is kept constant.

- Fig. 4.8 (a) Simulated power gain  $(S_{21})$  and (b) input return loss 58  $(1/S_{11})$  for different values of  $L_1$  with  $L_g = 2.0$  nH,  $L_s = 0.5$  nH,  $C_{RH} = 0.17$  pF, and  $C_a = 0.23$  pF. The transmission zero  $\omega_{RL}$  is kept constant.

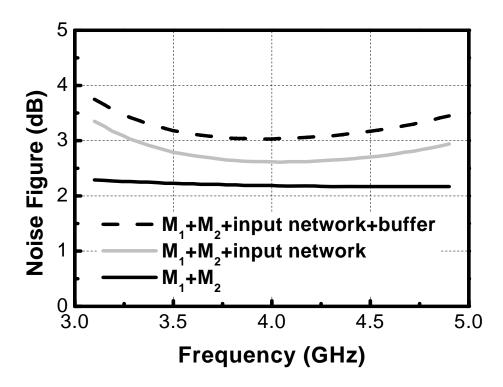

- Fig. 4.9 Simulated noise figure of the first UWB LNA due to 59 the active gain stages and the losses of the input network.

- Fig. 4.10 Microphotograph of the fabricated UWB LNA. Die 60 area is  $0.78 \times 0.8 \text{ mm}^2$ .

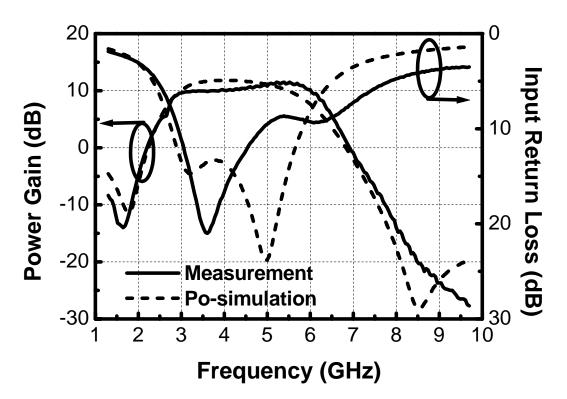

- Fig. 4.11 Measured and simulated power gain  $(S_{21})$  and input 61 return loss  $(1/S_{11})$  of the UWB LNA.

- Fig. 4.12 Measured and simulated noise figure of the UWB 61 LNA.

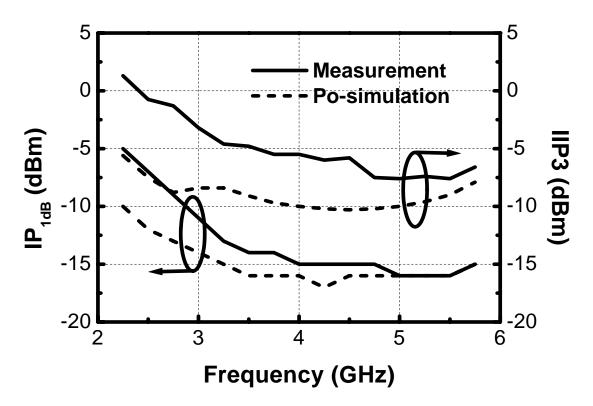

- Fig. 4.13 Measured and simulated  $IP_{1dB}$  and IIP3 of the UWB 62 LNA.

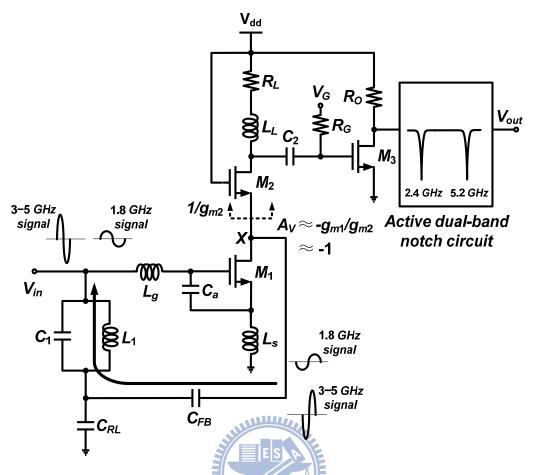

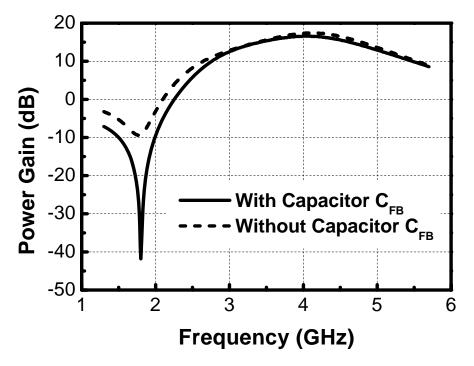

- Fig. 4.14 Principle of the interferer-canceling technique with a 64 feedback capacitor  $C_{FB}$  and active dual-band notch filter.

- Fig. 4.15 Simulated power gain  $(S_{21})$  with and without the 64

additional capacitor  $C_{FB}$ .

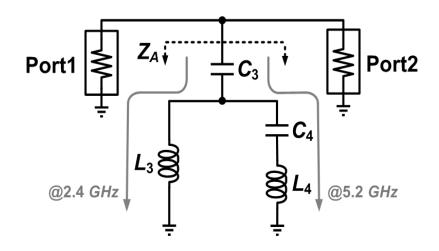

- Fig. 4.16The dual-band notch filter circuit.66

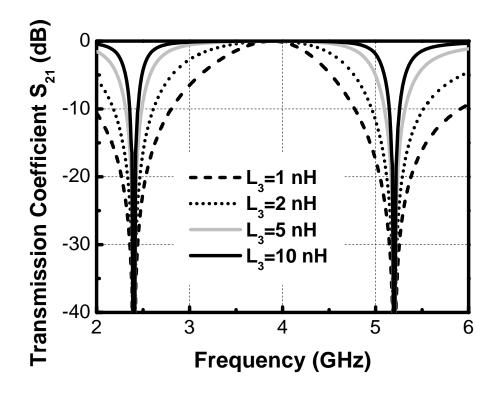

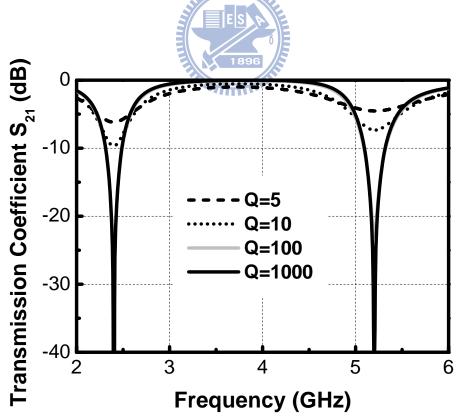

- Fig. 4.17 Simulated transmission coefficient  $S_{21}$  of the notch 67 filter for different values of  $L_3$ .

- Fig. 4.18 Simulated transmission coefficient  $S_{21}$  of the notch 67 filter for different values of Q with  $L_3 = 5$  nH.

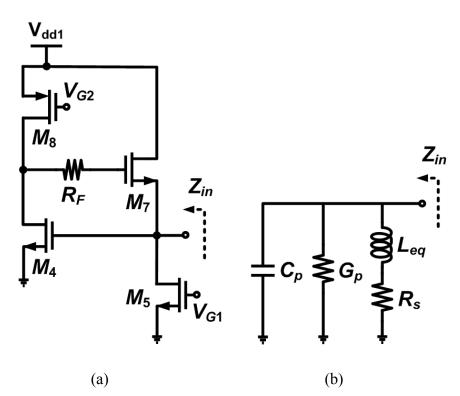

- Fig. 4.19 (a) Schematic and (b) equivalent circuit of the active 69 inductor with a resistor in the feedback path.

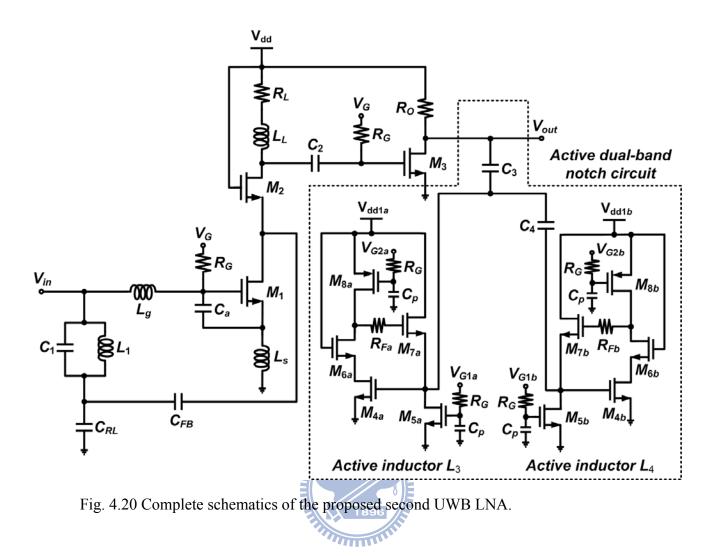

- Fig. 4.20 Complete schematics of the proposed second UWB 70 LNA.

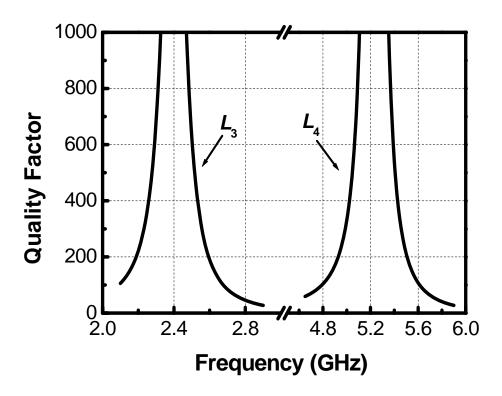

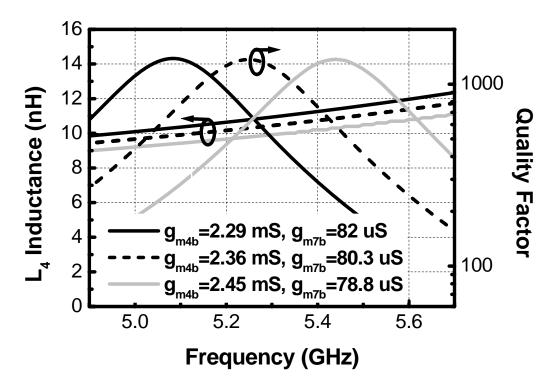

- Fig. 4.21 Simulated quality factor of the proposed active 71 inductors  $L_3$  and  $L_4$ .

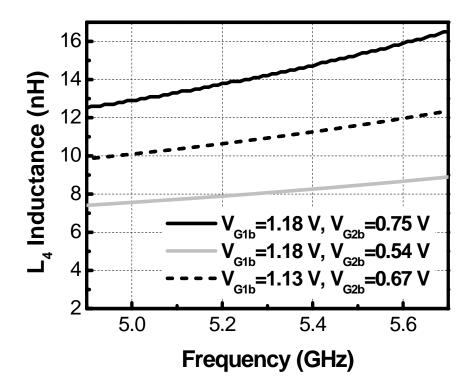

- Fig. 4.22 Inductance of an active inductor is related to the bias 72 voltages of the transistors.

- Fig. 4.23 Adjustable quality factor Q of an active inductor while 73 maintaining a similar inductance value.

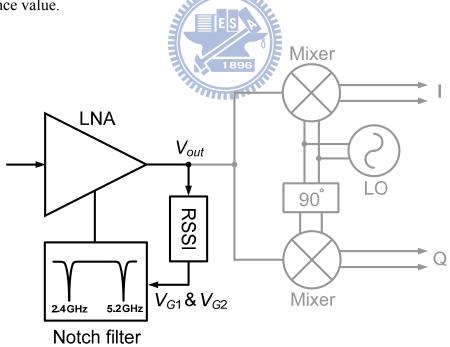

- Fig. 4.24 Principle of the feedback technique for setting the 73 notch frequency.

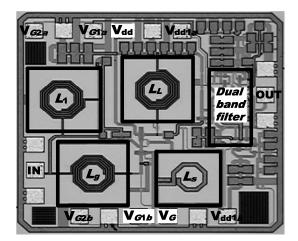

- Fig. 4.25 Microphotograph of the fabricated UWB LNA. Die 74 area is  $0.9 \times 0.85$  mm<sup>2</sup>.

- Fig. 4.26 Measured and simulated power gain  $(S_{21})$  and input 75 return loss  $(1/S_{11})$  of the second UWB LNA.

- Fig. 4.27 Measured and simulated noise figure of the second 75 UWB LNA.

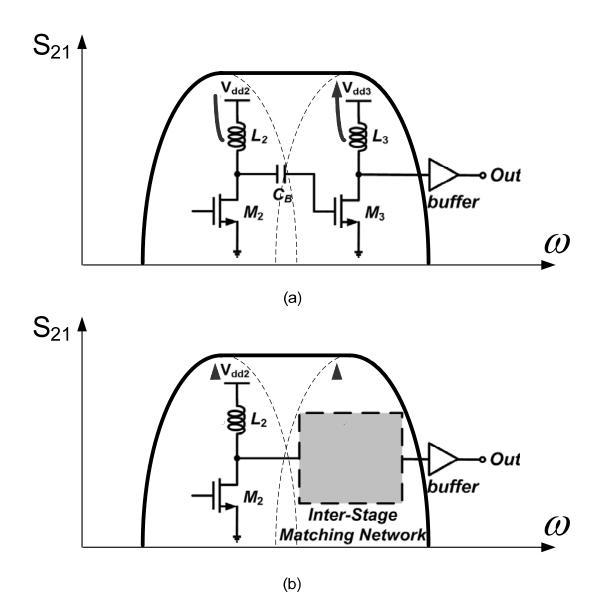

- Fig. 4.28 Bandwidth enhancement techniques (a) the 78 common-source stages with inductive loads and (b) the basic principle with inter-stage series resonators.

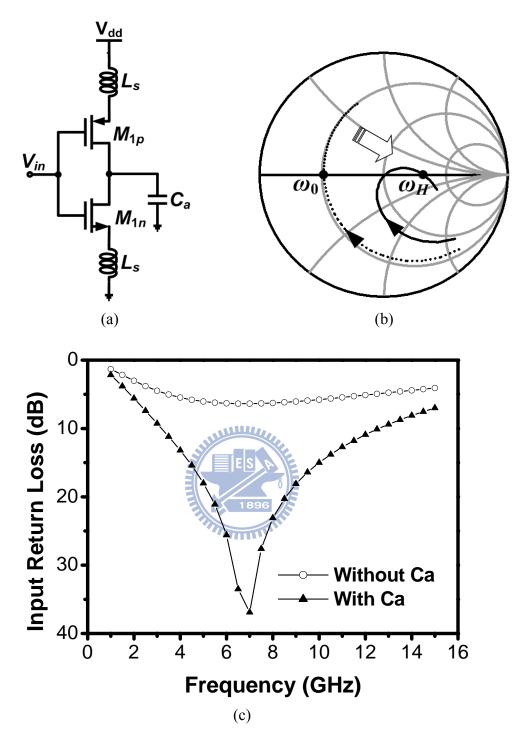

- Fig. 4.29 The proposed input matching circuit and its frequency 79 behavior.

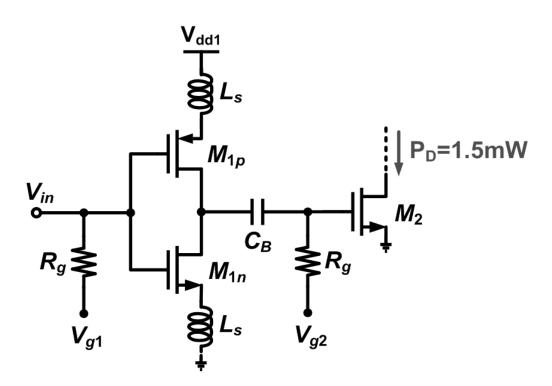

- Fig. 4.30 The capacitor  $C_a$  is substituted for the amplifier stage 80  $M_2$  with power consumption fixed at 1.5 mW.

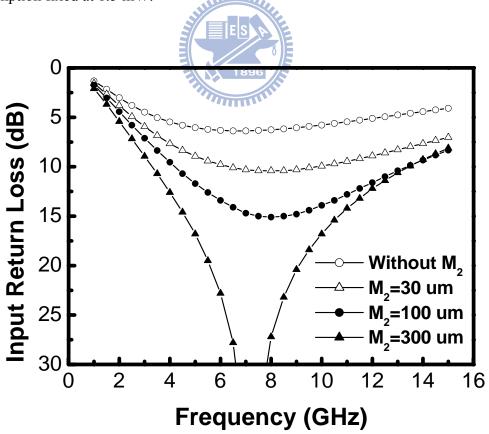

- Fig. 4.31 Simulated input return loss for different widths of the 80 transistor  $M_2$ .

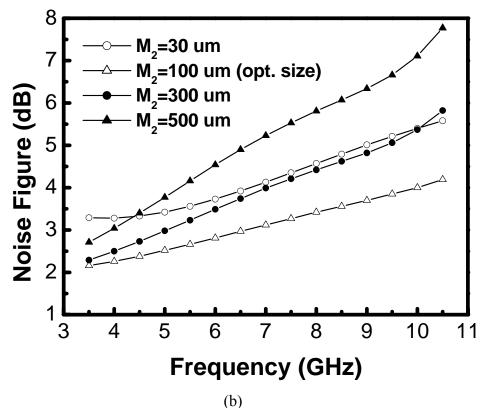

- Fig. 4.32 Simulated noise figure for different widths of the 81 transistor  $M_2$ .

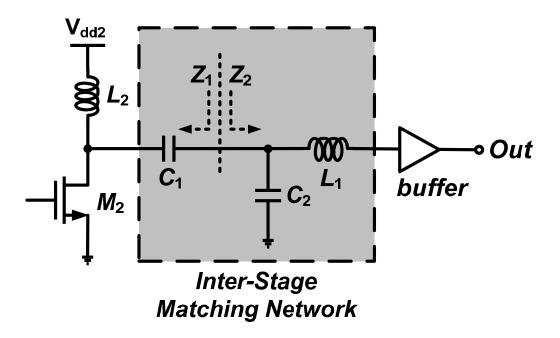

- Fig. 4.33Inter-stage matching network.82

- Fig. 4.34 Input reflection coefficients on the Smith chart for the 82 impedances  $Z_1$  (solid line) and  $Z_2$  (dashed line) shown

in Fig. 4.33.

|                       | III I Ig. 4.55.                                                         |          |

|-----------------------|-------------------------------------------------------------------------|----------|

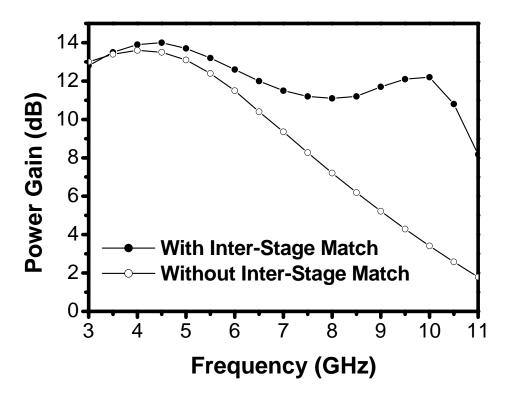

| Fig. 4.35             | Simulated power gain with and without the inter-stage matching network. | 83       |

| Eia 126               | e                                                                       | 07       |

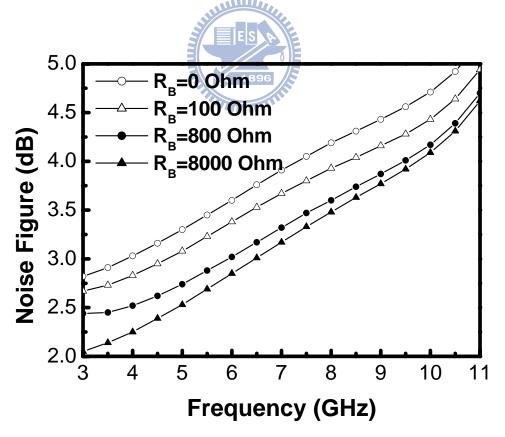

| Fig. 4.36             | Simulated noise figure for different values of the resistor $R_B$ .     | 83       |

| Fig. 4.37             | The architecture of the proposed UWB LNA with a                         | 84       |

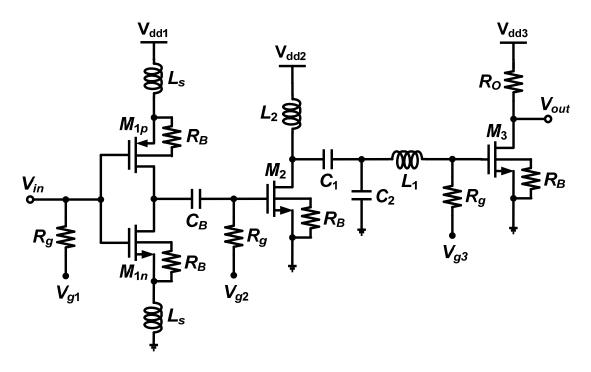

|                       | new input-matching technique.                                           |          |

| Fig. 4.38             | Microphotograph of the LNA. Die area is $0.81 \times 0.81$              | 85       |

| -                     | $\mathrm{mm}^2$ .                                                       |          |

| Fig. 4.39             | Measured S-parameters of the proposed UWB LNA.                          | 85       |

| Fig. 4.40             | Measured noise figure of the proposed UWB LNA.                          | 86       |

| Fig. 5.1              | The phase-noise suppression with the second harmonic                    | 89       |

|                       | tuned LC tank [67].                                                     |          |

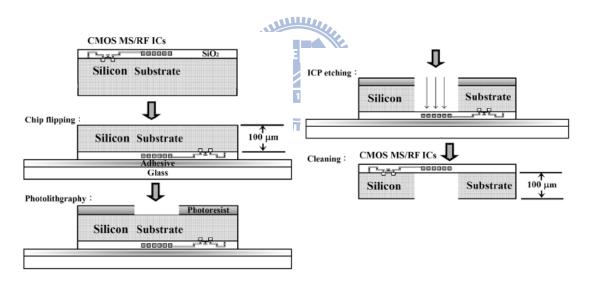

| Fig. 5.2              | Process steps of the backside ICP deep trench etching                   | 89       |

| C                     | technology [68].                                                        |          |

| Fig. 5.3              | Complete schematics of the proposed low-power VCO                       | 90       |

| e                     | with the phase-noise reduction techniques.                              |          |

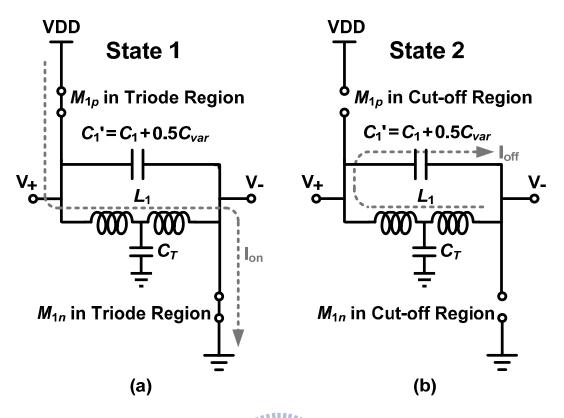

| Fig. 5.4              | The equivalent circuits of the proposed VCO when the                    | 91       |

|                       | voltage at node $V$ + is (a) high and (b) low.                          | -        |

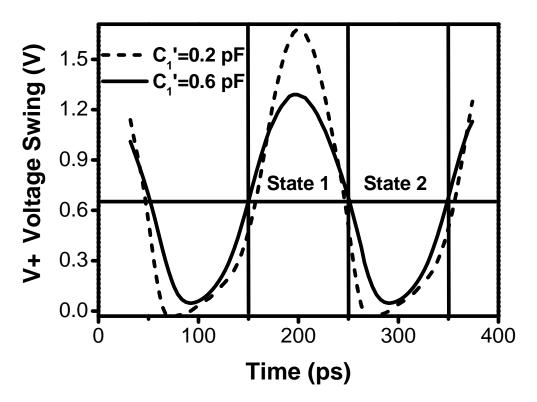

| Fig. 5.5              | Simulated V+ voltage swing for different values of                      | 92       |

| 1 18. 0.0             | $C_1$ .                                                                 | <u> </u> |

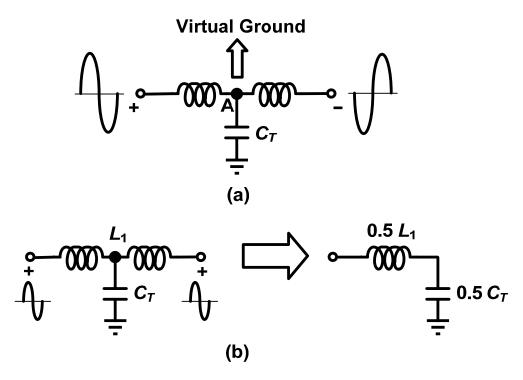

| Fig. 5.6              | Influence of the capacitor $C_T$ for (a) the fundamental                | 93       |

| 1 Ig. <i>J</i> .0     | signal and (b) the second harmonic signal.                              | ))       |

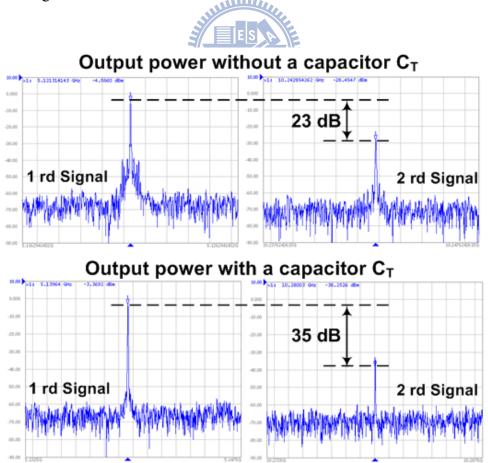

| Fig 57                |                                                                         | 93       |

| Fig. 5.7              | Measured output signals with and without the $C$                        | 93       |

| E . 5 0               | capacitor $C_T$ .                                                       | 05       |

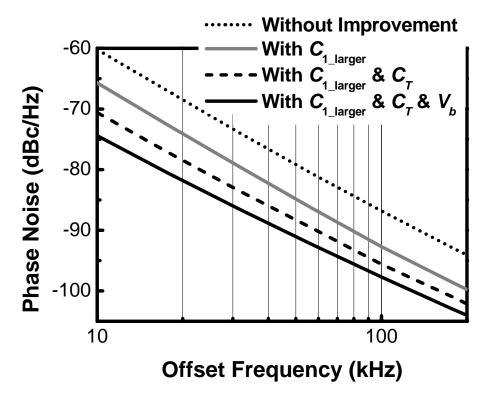

| Fig. 5.8              | Simulated phase noises with and without                                 | 95       |

| <b>D</b> ' <b>5</b> 0 | improvement.                                                            | 0.5      |

| Fig. 5.9              | Microphotograph of the VCO with $0.33 \times 0.45 \text{ mm}^2$         | 95       |

|                       | core die area.                                                          |          |

| Fig. 5.10             | Measured and simulated tuning ranges of the proposed                    | 96       |

|                       | VCO.                                                                    |          |

| Fig. 5.11             | Measured and simulated phase noises of the proposed                     | 96       |

|                       | VCO.                                                                    |          |

|                       |                                                                         |          |

## CHAPTER 1 INTRODUCTION

### **1.1 BACKGROUND**

The wireless communication is becoming more and more significant because of the convenience for human-being life and accelerating the transmission of the information in the last two decades. For the landscape of the wireless communication systems, the higher bandwidth of these radio bands, such as wireless local area network (WLAN), worldwide interoperability for microwave access, and ultra-wideband (UWB) significantly enables the higher data rate applications.

The IEEE 802.11 group which is also labeled as WiFi (Wireless Fidelity) establishes three sub-standards on the market, namely 802.11a operating at frequencies allocated around 5 GHz, and 802.11 b and g transmitting at 2.4 GHz. The b standard achieves a date throughput of around 11 Mb/s, and the more advanced a and g standards can support up to 54 Mb/s data rate by utilizing the orthogonal frequency-division multiplexing (OFDM) technique.

Worldwide interoperability for microwave access (WiMAX), described and specified in the IEEE 802.16e standard, is a new system for wireless broadband access to provide the high speed of service and broad coverage of about several miles. Due to the usage of the OFDM technique and the multiple-input, multiple-output (MIMO) concept, the data rate up to 75 Mb/s can be achieved at the operation frequencies 2.5, 3.5, and 5.2 GHz.

For the IEEE 802.15.3a group, the multi-band orthogonal frequency division multiplexing (MB-OFDM) UWB system uses the unlicensed UWB spectrum from 3.1

GHz to 10.6 GHz with a regulated frequency-power emission below -41.3 dBm to provide data communication capabilities up to 480 Mbps. The 7.5 GHz bandwidth is divided into 4 groups of 14 bands. Therefore, the occupied spectrum for each OFDM signal is 528 MHz.

In this thesis, the main research focus is on key components for multiband and UWB communication systems. It includes triple-band low-noise amplifiers (LNAs), a dual-band image rejection mixer, low-power UWB LNAs with out-band rejection properties, and a low phase-noise voltage-controlled oscillator (VCO). The research motivation will be depicted in the following subsection.

### **1.2 RESEARCH MOTIVATION**

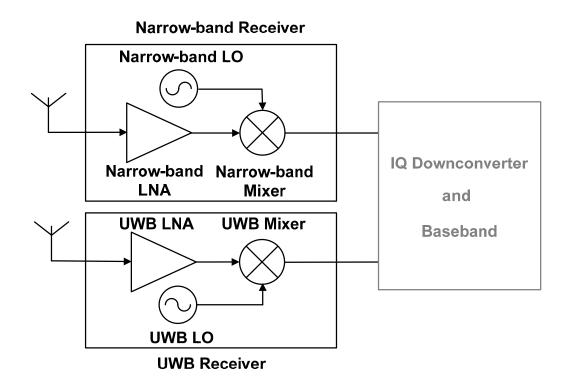

Recently, the wireless communication systems has rapidly expanded the demand for low-cost and low-power RF integrated circuits (RFICs) which can support multi-system operations. There is the trend to merge several applications into one device by reusing potential synergies between the different systems, as shown in Fig. 1.1. The study on exploring new different circuit topologies and design techniques of the key RFIC components in multi-band and UWB communication systems is proposed.

For the multi-band communication system, conventional design strategies have adopted different single-band receiver circuits in parallel for different frequency bands. However, it is unavoidable to result in a high implementation cost because of the large chip area and an increased chip current dissipation simultaneously. In order to avoid the above-mentioned drawbacks, a multi-band receiver has demonstrated the feasibility to take the place of the conventional structure for multi-band

Fig. 1.1 Several different applications merged into a system.

application. In addition, the noise figure of a receiver is particularly determined by the noise figure of the LNA located in front of the receiver. Therefore, the proposed noise-canceling technique can be applied in the LNA circuit to ameliorate the noise property.

Mixer is responsible for frequency conversion in RF transceiver, and the suppression of the image signal is an essential requisite. Generally, the multi-band image rejection mixer can be achieved by either Hartley or Weaver architecture, but the required multi-band quadrature signal generator will further increase the complication of the circuit implementation, which is undesired for low-cost and low-power application. In order to achieve smaller chip area and dc power consumption, the differential third-order notch filter with the cross-connected pair consisted of NMOS and PMOS transistors is designed.

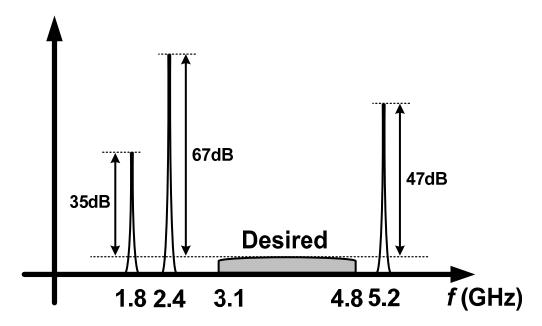

On the other hand, the minimum received power in the UWB system is 47 and

67 dB, in the worst case, lower than those of the WLAN interferer powers at 5.2 and 2.4 GHz, respectively. In addition, one tone is measured at 1.87 GHz in a smart-phone currently on the market, and the power level is 35 dB higher than the UWB signal. All of these interferers have a harmful effect on the received UWB signal; therefore, the designed LNA with out-band rejection property in UWB communication system is required.

For multiband or UWB communication applications, the RF signal is downconverted to the IF frequency using a local oscillator, which is generated by a frequency synthesizer. Phase noise is one of the most critical parameters for a local oscillator since it affects the overall performance of the communication system. Therefore, the designed low-noise VCO, which is a key component of the frequency synthesizer is proposed to optimize the phase-noise performance.

The aim of this dissertation is to develop key components for multiband and UWB communication systems including two triple-band LNAs, a dual-band image rejection mixer, three low-power UWB LNAs, and a low phase-noise VCO. The main results will be depicted below.

#### **1.3 THESIS ORGANIZATION**

It is the aim of this thesis to analyze and design RF receiver circuits for multiband and UWB communication applications. The thesis includes the design of two triple-band LNAs, a dual-band image rejection mixer, three low-power UWB LNAs, and a VCO with the phase-noise improvement.

Chapter 1 introduces the background, and describes the research motivation.

Chapter 2 presents the design of two triple-band LNAs fabricated in a 0.18- $\mu$ m

complementary metal oxide semiconductor (CMOS) process. The proposed triple-band LNAs have demonstrated the feasibility to effectively decrease the size of multi-band RF systems by using a switched component. Furthermore, the feedback structure is adopted to accomplish the partial noise cancelation and the wideband input matching simultaneously. The proposed noise power diminution by using an additional larger substrate resistor in MOS device can be employed in the nowadays LNA designs.

A 2.45/5.2 GHz Gilbert downconversion mixer with image rejection function is proposed and detailed in chapter 3. The mixer employs the differential, dual-band, third-order notch filter to attenuate the dual-band image signal while maintaining a superior in-band performance. The cross-connected pair consisted of NMOS and PMOS transistors in the proposed notch filter will further raise the *Q* value of on-chip inductor for improving the image rejection capability.

In chapter 4, three low-power UWB LNAs using 0.18- $\mu$ m CMOS technology are presented. By suitably introducing two additional capacitors in the traditional *LC* input network, two transmission zeros are generated to achieve the out-band rejection function. Moreover, a feedback structure and dual-band notch filter with low power active inductors further attenuate the out-band interferers without deteriorating the input matching bandwidth. After improving the out-band rejection capability, a new matching technique can be acquired easily by selecting an appropriate width of the transistor, which will effectively avoid the usage of the low-*Q* on-chip inductors in the input network for ameliorating the noise figure performance.

In chapter 5, a low-power VCO with phase-noise improvement in 0.18-µm CMOS technology is presented. The VCO adopts the design of a current-reused configuration because of its excellent low-power characteristic, and focuses on the promotion of phase noise without additional chip area and CMOS process steps. A 15

dB improvement at 10 kHz offset frequency can be attained due to the usage of a larger parallel capacitor, an extra harmonic-rejected capacitor, and an appropriate bulk bias voltage of transistor.

In chapter 6, conclusions are given.

### **CHAPTER 2**

# DESIGN OF THE TRIPLE-BAND LOW NOISE AMPLIFIER

### **2.1 INTRODUCTION**

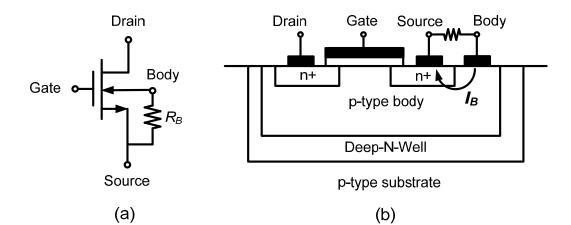

Recently, the widely used wireless communication systems have rapidly expanded the demand for low-cost and low-power RF integrated circuits which can support multi-band operations by a single system. Conventional design strategies have adopted different single-band transceiver circuits in parallel for different frequency bands [1]-[3]; however, it is unavoidable to result in a high implementation cost because of the large chip area, and simultaneously increase chip current dissipation. In order to improve the above-mentioned drawbacks, the topologies of the wideband LNA such as the resistive shunt-feedback structure [4], LC input network [5], common-gate 1/gm termination [6], and the distributed configuration [7] have been demonstrated and designed for multi-band application. Unfortunately, the broadband gain response will cause the unwanted interferers to impair the linearity of the receiver which is not desirable for the system considerations. To avoid this, the triple-band LNA shown in Fig. 2.1(a) has been devised in [8], [9], and it can suppress the out-band interferers while maintaining a sufficient in-band property. Nevertheless, the major drawback is the required high fabrication cost due to the usage of too many inductors. As a consequence, we propose two approaches by using a switched component to reduce the usage of inductors and the significant die area reduction will effectively decrease the cost of a multi-band RF system.

(a)

(b)

Fig. 2.1 (a) Triple-band LNA reported in [8], [9]. (b) A noise-canceling amplifier in [15]-[17].

In addition, it has become feasible to improve the noise performance of the LNA using the noise-canceling techniques. A source-degenerated cascode amplifier with an additional inductor at the drain of the main transistor is attractive for its excellent noise performance [10]-[12] and a 0.7 dB (from 5.5 to 4.8 dB) decrease in noise figure can be

achieved [10]. This is because the noise contribution from the cascode transistor can be reduced by using the inductor to cancel the effect of the parasitic capacitance at the drain of the main transistor. Inevitably, the extra inductor will occupy additional chip area, which makes it undesired for many applications. Inductively coupled plasma (ICP) deep-trench technique, which selectively removes the silicon underneath the inductors, is utilized to ameliorate the quality factor of on-chip inductors [13], [14]. A 0.5 dB noise figure decrease (from 2.28 to 1.78 dB) can be accomplished [13]; nevertheless, the extra CMOS process steps will increase the complication of the circuit implementation. Recently, a feedforward noise-canceling technique shown in Fig. 2.1(b) has been reported in [15]-[17]. The design principle of noise canceling is that the thermal noise of the common-gate amplifier can be neutralized by the voltage-sensing stage; however, the required common-source stage will make the total dc power consumption larger.

In this chapter, a momentous noise power diminution in MOS devices with an additional larger substrate resistor which can be employed in the nowadays LNA designs is presented and demonstrated. It can be observed that a maximum 32% noise reduction can be achieved due to the usage of larger resistance  $R_B$  without extra chip area, dc power and CMOS process steps.

This chapter is organized as follows. Section 2.2 introduces the principle of the proposed first triple-band LNA. Section 2.3 describes the detailed analyses of the second triple-band LNA. This chapter is summarized in Section 2.4. The target frequencies of the proposed triple-band LNAs are 2.5, 3.5, and 5.2 GHz, which can be used in the WiMAX system.

## 2.2 TRIPLE-BAND LOW NOISE AMPLIFIER WITH INPUT MATCHING DESIGN

It is known that the noise performance of LNA is dominated to the input stage. The proposed first triple-band LNA adopts a source-degenerated cascode amplifier, which selects the appropriate transistor size with finger width fixed at 5 µm to achieve input match and good noise figure simultaneously [18], [19]. Traditionally, the design criteria of the multi-band LNA such as that in the WiMAX application have used different LNAs for different frequency bands. Recently, a concept of triple-band LNA, as shown in Fig. 2.1(a), has been proposed [8], [9]. However, the chip area may be consumed while there are eight required inductors in the circuit.

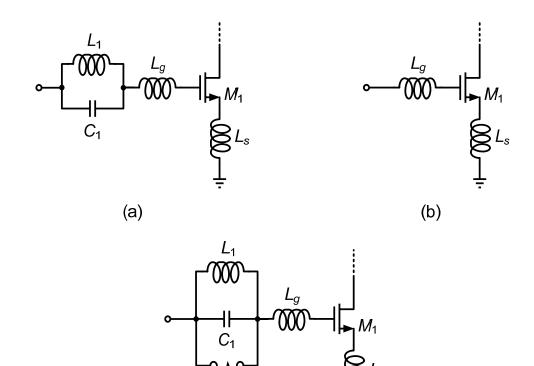

#### 2.2.1 Circuit Design and Analysis

Fig. 2.2(a) and (b) show the conventional dual-band and single-band input matching circuits, respectively. In this section, we have developed a novel manner for triple-band input matching, which is contrived by using dual-band input network with an additional switched component shown in Fig. 2.2(c). A significant area reduction and better noise figure can be achieved by reducing the usage of inductors in the input network. In the following analyses, it will facilitate the discussions to define that  $\omega_1$ ,  $\omega_2$ , and  $\omega_3$  correspond to 2.5, 5.2, and 3.5 GHz, respectively. When the switch is off, the circuit is equivalent to that shown in Fig. 2.2(a), and it is to be operated as a dual-band input network at 2.5 GHz and 5.2 GHz. On the other hand, as the switch is on, the circuit becomes that in Fig. 2.2(b), and it is operated at 3.5 GHz. To this end, the values of the circuit components such as  $L_s$ ,  $L_g$ ,  $L_1$ , and  $C_1$  of the proposed LNA

Fig. 2.2 (a) Schematic of a dual-band input matching. (b) Schematic of a single-band input matching. (c) A proposed triple-band input matching with an additional switched component.

(C)

SW1

Ls

circuit should be suitably designed in order to achieve the triple-band input matching. Based on the small-signal analysis, the input impedance for switch off status (Fig. 2.2 (a)) can be expressed as

$$Z_{in} = \frac{j\omega L_1}{1 - \omega^2 L_1 C_1} + j\omega (L_s + L_g) + \frac{1}{j\omega C_{gs}} + \frac{g_m L_s}{C_{gs}} .$$

(2.1)

To match the input port's impedance, the real term should be equal to 50  $\Omega$  and its imaginary term to zero, which yields

$$L_{s} = \frac{50C_{gs1}}{g_{m1}}$$

(2.2)

and

$$C_1(L_g + L_s)\omega^4 - (\frac{L_g + L_s}{L_1} + \frac{C_1}{C_{gs1}} + 1)\omega^2 + \frac{1}{C_{gs1}L_1} = 0, \qquad (2.3)$$

As can be seen in (2.3), the designed frequencies  $\omega_1$  and  $\omega_2$  (i.e., 2.5 and 5.2 GHz) satisfies

$$\omega_{1}^{2}\omega_{2}^{2} = \frac{1}{C_{1}(L_{g} + L_{s})C_{gs1}L_{1}}$$

(2.4)

and

$$\omega_{1}^{2} + \omega_{2}^{2} = \frac{\frac{L_{g} + L_{s}}{L_{1}} + \frac{C_{1}}{C_{gs1}} + 1}{C_{1}(L_{g} + L_{s})}.$$

(2.5)

From (2.4),  $L_1$  is obtained as

$$L_1 = \frac{1}{\omega_1^2 \omega_2^2 C_1 (L_g + L_s) C_{gs1}} , \qquad (2.6)$$

which, upon substitution in (2.5), yields

$$C_{1} = \frac{C_{gs1}}{(L_{g} + L_{s})(\omega_{1}^{2} + \omega_{2}^{2})C_{gs1} - (L_{g} + L_{s})^{2}\omega_{1}^{2}\omega_{2}^{2}C_{gs1}^{2} - 1}$$

(2.7)

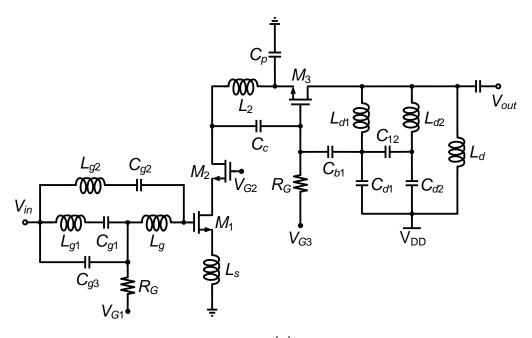

Fig. 2.3 Complete schematic of the proposed first triple-band LNA with input matching design.

On the other hand, when the switch is on (i.e., the single-band state for  $\omega_3=3.5$  GHz, Fig. 2.2 (b)), the criterion of a 50  $\Omega$  input impedance is still required and  $L_g$  can be expressed as

$$L_{g} = \frac{1}{\omega_{3}^{2}C_{gs1}} - L_{s} = \frac{1}{\omega_{3}^{2}C_{gs1}} - \frac{50C_{gs1}}{g_{m1}}, \qquad (2.8)$$

where (2.2) has been incorporated. As we will see, the precise values of  $L_s$ =0.25 nH,  $L_g$ =3.5 nH,  $L_1$ =2 nH, and  $C_1$ =0.9 pF can be predicted by drawing on (2.2), (2.8), (2.7), and (2.6) when the width of the transistor  $M_1$  (300 µm) is chosen with 10 mW power dissipation. The first triple-band LNA is shown in Fig. 2.3 and it is noticed that the equivalent circuit of a switched component exists parasitic capacitances, which cause

Fig. 2.4 Microphotograph of the first triple-band LNA with  $0.98 \times 0.94$  mm<sup>2</sup> die area.

$C_1$  should be adjusted. In addition, for testing purposes, an output buffer consisted of a source follower is included in the design circuit, which roughly introduces a 6 dB loss in the signal path [20].

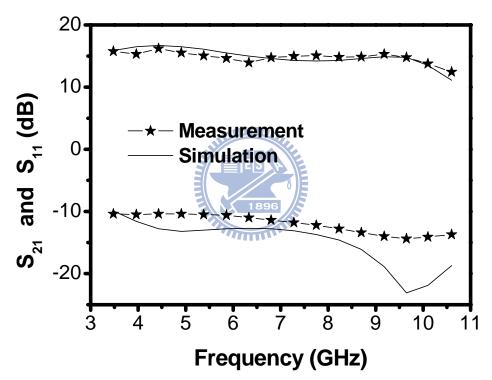

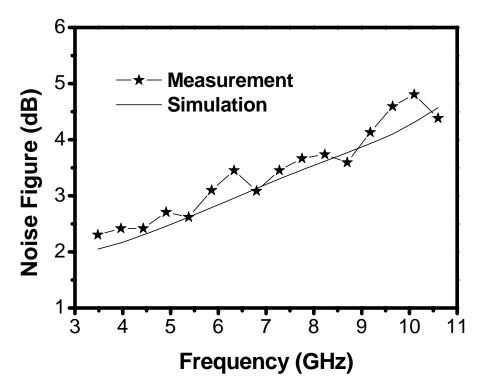

# 2.2.2 Simulation and Experimental Results

The die microphotograph of the first triple-band LNA is shown in Fig. 2.4, and measured by using on-wafer probing. The LNA chip without the output buffer draws a total 5.5 mA dc current from the 1.8 V supply voltage. The S-parameters of the designed LNA is measured using the Agilent 8510C vector network analyzer. The simulated and measured results of S- parameters are depicted in Fig. 2.5. The measured peak gains are 10/20.1/11 dB at 2.5/3.5/5.2 GHz while the input and output return losses are better than 10 dB in the operation frequencies. The noise figure is measured using the Agilent N8975A noise figure analyzer with Agilent 346C noise source. The simulated and measured noise figures at the same bias condition are depicted in Fig. 2.6. It is seen that the minimum values of the measured noise figure are equal to 3.3/3.6/4.6 dB at 2.5/3.5/5.2 GHz.

Fig. 2.5 Measured and simulated S-parameters of proposed first triple-band LNA.

Fig. 2.6 Measured and simulated noise figure of proposed first triple-band LNA.

## 2.3 TRIPLE-BAND LOW NOISE AMPLIFIER WITH NOISE REDUCTION

The first triple-band LNA can reduce chip area significantly by using dual-band input network with an additional switched component. However, it is unavoidable to worse noise figure result due to the usage of low-Q inductors in input network. To enhance the noise performance, we have tried the second LNA which utilizes the double-peak single-notch network [21] with an additional switch as the load impedance to achieve the same characteristic of the first LNA. Moreover, a common-drain stage in the feedback path is adopted to accomplish 50- $\Omega$  wideband input matching and partial noise cancellation simultaneously. The buffer transistor with a purely 50- $\Omega$  resistive load is employed to achieve output matching for testing purposes.

#### **2.3.1 Triple-Band Load Network**

The triple-band load network, as shown in Fig. 2.7(c), is operated by turning the switch  $M_{SW1}$  on and off. Evidently, this network is simplified into a *LC* tank operated in  $\omega_3$ =3.5 GHz when the switch  $M_{SW1}$  is off (i.e., Fig. 2.7(b)). Similarly, when the switch  $M_{SW1}$  is on, the dual-band load impedance operated in  $\omega_1$ =2.5 GHz and  $\omega_2$ =5.2 GHz is employed and expressed by

$$Z_{load} = \frac{j\omega L_d (1 - \omega^2 L_1 C_1)}{\omega^4 L_d C_d L_1 C_1 + \omega^2 (L_d C_d + L_1 C_1 + L_d C_1) + 1}$$

(2.9)

Fig. 2.7 (a) Schematic of a dual-band load network. (b) Schematic of a single-band load network. (c) A proposed triple-band load network with an additional switched component.

Equation (2.9) also represents that the two poles  $\omega_1$  and  $\omega_2$  can be obtained by letting the denominator equal null, or

$$\omega^4 L_d C_d L_1 C_1 + \omega^2 (L_d C_d + L_1 C_1 + L_d C_1) + 1 = 0 .$$

(2.10)

In addition,  $1/\sqrt{L_1C_1} = 1/\sqrt{L_dC_d}$  is satisfied to facilitate the design, which retains to provide similar amplitudes and symmetries in the two maxima of  $Z_{load}$ . It is noted that the proposed triple-band load network has three given target frequencies for the four

load components, which means that there is still one degree of freedom, let say  $C_d$ , left for the circuit design. Fig. 2.8(a) and (b) show the load impedance versus frequency with different  $C_d$  parameters. In general, the first step in the design criteria of the proposed load network is to select a lower  $C_d$  since the higher the load impedance, i.e., the LNA gain. However, a drawback which may make the design criteria unsatisfactory is a high implementation cost due to the requirement of the larger inductance  $L_1$  and  $L_d$ . Therefore, it should be taken into account the trade-off between the gain and die area punctiliously.

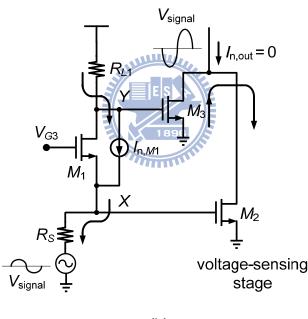

#### **2.3.2 Input Matching with Partial Noise Cancellation**

The design of the first stage is a common-source structure with a feedback common-drain amplifier in order to achieve the wideband input matching of 50- $\Omega$ . The input impedance  $Z_{in}$  shown in Fig. 2.9 is close to  $1/g_{m3}(1+g_{m1}Z_L)$ , which is interrelated to the bias voltage of the transistors  $M_1$  and  $M_3$  since  $g_{mi}$  is proportional to the current of transistors. Consequently, the input matching characteristic can be effectively tuned by adjusting the bias voltages  $V_{g2}$ ,  $V_{g3}$ , and the bias current  $I_4$  to compensate for the process variation. On the other hand, the introducing of a feedback structure with the common-drain stage also can attain the partial noise cancellation, which is demonstrated in the following analyses. As shown in Fig. 2.9, the noise voltage  $V_{nX}$  at node X is generated due to the thermal noise current  $i_n$  of the transistor  $M_1$ . The adopted feedback common-drain amplifier  $M_3$  will bring about the in-phase noise voltage  $V_{nx}$  at node Y, which can be further converted to node X with opposite phase (i.e., the noise voltage  $V_{nx}$ ) by the common-source cascode amplifier  $M_1-M_2$ . Therefore, the noise contributed by  $M_1$  is partially cancelled at the output node X, as can be observed from Fig. 2.10.

Fig. 2.8 The load impedance versus frequency with different C parameters. (a) A dual-band load network when the switch is on. (b) A single-band load network when the switch is off.

Fig. 2.10 Simulated noise figures with and without the noise-canceling technique.

#### 2.3.3 Noise Reduction with Larger Substrate Resistor

In order to further ameliorate the noise performance of a CMOS LNA, a significant noise power reduction in MOS device by using larger substrate resistor  $R_B$ , as shown in Fig. 2.11(a), is presented. To begin with, the complete noise equivalent circuit must be established to facilitate the demonstration of the proposed noise-reduction structure. It is well-known that the body effect transconductance can be expressed as

$$g_{mb} = \frac{\gamma}{2\sqrt{2\varphi_f + V_{SB}}} g_m \tag{2.11}$$

where  $\gamma$  is the body-effect coefficient,  $\varphi_f$  is the bulk fermi potential,  $V_{SB}$  is the voltage between body and source. If we make the assumption that the source voltage drops sufficiently below the bulk voltage, then it is observed intuitively from Fig. 2.11(b) that the current  $I_B$  is formed because of the forward-biasing. Contradictorily, the current  $I_B$  injected into the external substrate resistance  $R_B$  will bring about  $V_{SB} > 0$ . As a consequence, no current flows between body and source (i.e.,  $V_{SB}=0$ ) and this means that the body effect transconductance is inexistent in the noise equivalent circuit (see Fig. 2.11(c)) for the MOS device with a larger substrate resistor  $R_B$ . Furthermore, the dominant noise source modeled as a shunt current source in the output circuit of the device is channel thermal and the output noise power density arising from this source is

$$\overline{i_{out}^2} = 4kT\gamma' g_{d0} \left| \frac{i_{out}}{i_d} \right|^2$$

(2.12)

Fig. 2.11 (a) A NMOS device with a larger substrate resistance  $R_B$ =8 k $\Omega$ . (b) Structure of a NMOS with a larger substrate resistance  $R_B$ . (c) The noise equivalent circuit of a NMOS device with a larger substrate resistance  $R_B$ .

where  $\gamma'$  is a bias-dependent factor, and  $g_{d0}$  is the zero-bias drain conductance of the device [22, Chapter 7]. In general,  $1/sC_{sb} >> R_{sb}$  is satisfied and demonstrated in [23]; therefore, the substrate impedance  $Z_{sub}$  can be simplified to a simple series *CR* circuit (i.e.,  $C_{db}$  in series with  $(R_{dsb}+R_{sb})||R_{db}$ , and  $R_B$ ) as follows:

$$Z_{sub} \approx \frac{1}{j\omega C_{db}} + \left[\frac{R_{db}(R_{sb} + R_{dsb})}{R_{db} + R_{sb} + R_{dsb}} + R_B\right].$$

(2.13)

Fig. 2.12 Simulated the total MOS device noise factor F (NF=10log<sub>10</sub> F) with and without the additional resistance  $R_B$ =8 k $\Omega$  and the noise reduction when resistance  $R_B$  is used.

Fig. 2.13 Simulated noise figure with and without the additional resistor  $R_B=8 \text{ k}\Omega$ . (a) Dual-band status when the switch is on. (b) Single-band status when the switch is off.

(b)

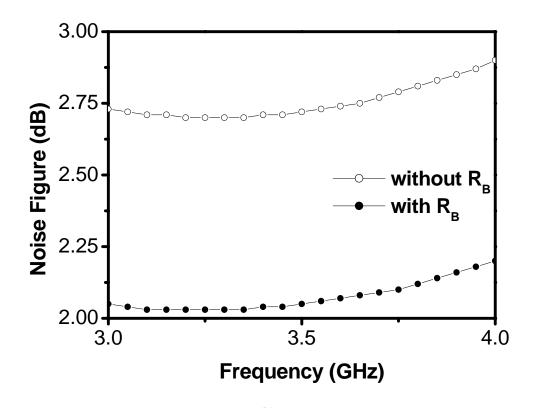

As we can see, a larger  $Z_{sub}$  by increasing the value of  $R_B$  will result in the reduction of  $i_{sub}$ . The noise factor F (NF=10log<sub>10</sub>F) contributed by total MOS device is shown in Fig. 2.12 and a significant noise power reduction in MOS device can be demonstrated by the additional resistor  $R_B$ . A maximum 32% noise reduction can be achieved without extra chip area, CMOS process steps and dc power. Fig. 2.13 shows the simulation results of noise figure with and without the additional resistor  $R_B$ . It can be observed that the 0.71/0.67/0.64 dB decrease in noise figure are attained at 2.5/3.5/5.2 GHz due to the usage of larger resistance  $R_B$ =8 k $\Omega$ .

#### **2.3.4 Simulation and Experimental Results**

The complete schematic and die microphotograph of the second triple-band LNA

Fig. 2.14 Complete schematic of the proposed second triple-band LNA with the load network design and the noise reduction resistance  $R_B$ .

are shown in Fig. 2.14 and Fig. 2.15, respectively. The die area including pads is  $0.75 \times 0.69 \text{ mm}^2$ , which has been measured by using on-wafer probing. The total dc power of the LNA chip without the output buffer is 14.2 mW. The simulated and measured results of S-parameters are depicted in Fig. 2.16. The measured peak gains are 12.3/15.3/13.1 dB at 2.5/3.5/5.2 GHz while the input and output return losses are better than 10 dB in the operation frequencies. The simulated and measured noise figures are depicted in Fig. 2.17 and the measured minimum noise figures at 2.5/3.5/5.2 GHz are 2.3/2.2/2.7 dB.

Fig. 2.15 Microphotograph of the second triple-band LNA with  $0.75 \times 0.69 \text{ mm}^2$  die

(a)

Fig. 2.17 Measured and simulated noise figure of the second triple-band LNA.

## **2.4 SUMMARY**

The triple-band LNAs with a switched resonator concept have been fabricated using 0.18- $\mu$ m CMOS technology and a significant die area reduction can be achieved. Furthermore, an additional larger substrate resistor  $R_B$  will diminish the output noise power density of MOS device and the 0.71/0.67/0.64 dB noise figure decrease can be attained at 2.5/3.5/5.2 GHz in the second approach of the triple-band LNA without extra chip area, dc power and CMOS process steps. The measured results, including the power gain, the return loss, and the noise figure, agree quite well with the simulated results. The presented triple-band LNAs are compared with recently published CMOS LNA and summarized in Table 2.1.

|      | TT 1  | Г      | G        | G          |             | D              |          |

|------|-------|--------|----------|------------|-------------|----------------|----------|

| Ref. | Tech. | Freq.  | $S_{11}$ | $G_{\max}$ | $NF_{\min}$ | $P_{\rm diss}$ | Area     |

|      | [µm]  | [GHz]  | [dB]     | [dB]       | [dB]        | [mW]           | $[mm^2]$ |

| [4]  | 0.18  | 3~6    | <-12     | 15.9       | 4.7         | 59.4           | 1.1      |

| [5]  | 0.18  | 2.8~7  | <-4      | 19.1       | 3           | 32             | 1.63     |

| [7]  | 0.18  | dc ~ 7 | <-16     | 8.6        | 4.2         | 9              | 1.16     |

| [24] | 0.13  | 2~5.2  | <-9      | 16         | 4.7         | 38             | 0.24     |

| [25] | 0.09  | 2.5~4  | <-10     | 10.6       | 4           | 16             | 0.77     |

| [26] | 0.13  | 3 ~ 5  | <-10     | 19.4 Ψ     | 3.5         | 31.5           | 1.6      |

| [27] | 0.18  | 3~4.8  | <-10     | 13.9       | 4.7         | 14.6           | 0.95     |

| [28] | 0.18  | 3~4.8  | <-7      | 14.3       | 3.45        | 13.5           | 1.8      |

| [29] | 0.18  | 2.44   | <-10     | 7.6        | 5.7         | 10.8           | 1.15     |

| [29] |       | 5.76   | <-6      | 8.6        | 6.8         |                |          |

|      | 0.25  | 1.8    | JULI     | 10.1       | 3.7         |                |          |

| [9]  |       | 2.45   | <-10     | 10.8       | 4.8         | 39.1           | 1.68     |

|      |       | 5.25   |          | 11.8       | 6.4         |                |          |

|      | 0.18  | 0.95   | <-7      | 18         | 4.6         |                |          |

| [30] |       | 2.4    | <-10     | 24         | 4.4         | 32.4           | 1.34     |

|      |       | 5.2    | <710     | 23         | 4.4         |                |          |

|      | 0.18  | 2.5    |          | 10         | 3.3         |                |          |

| LNA1 |       | 3.5    | <-10     | 20.1       | 3.6         | 10             | 0.92     |

|      |       | 5.2    |          | 11         | 4.6         |                |          |

| LNA2 | 0.18  | 2.5    |          | 12.3       | 2.3         |                |          |

|      |       | 3.5    | <-10     | 15.3       | 2.2         | 14.2           | 0.52     |

|      |       | 5.2    |          | 13.1       | 2.7         |                |          |

Table 2.1 Performance summary of previously published LNAs

## **CHAPTER 3**

# DESIGN OF IMAGE-REJECTION MIXER FOR DUAL-BAND OPERATION

## **3.1 INTRODUCTION**

The down-conversion mixer, which converts the high RF frequency to a low IF frequency, is a required building block of the transceiver. It is also an important component associated with the linearity of the front-end receivers. In general, Gilbert cell is a typical type of the active mixers, and the Gilbert mixer consists of three stages: transconductor stage, switching stage, and load stage. The linearity of Gilbert mixer will be dominated by the transconductor stage if the switching stage is ideal. In order to get higher conversion gain, good isolation, and better dynamic and static offsets, and help to improve the second and third order intermodulation rejection, the double balanced Gilbert mixer with differential RF, LO, and IF signals are commonly used for optimum operation.

In addition, the suppression of the image signal is an essential requisite for the RF receiver design. Generally, the dual-band image rejection mixer can be achieved by either Hartley or Weaver architecture, but the image rejection characteristic is restricted due to the magnitude mismatch and phase error of the quadrature signal. On the other hand, the required dual-band mixer with quadrature signal generator for dual-band operation will further increase the complication of the circuit implementation, which is undesired for low-cost and low-power application. In this chapter, we adopt the differential, dual-band, third-order, active notch filter to

Fig. 3.1 Block diagram of the Hartley down-converter.

Fig. 3.2 Block diagram of the Weaver down-converter.

attenuate the dual-band image signal while maintaining a superior in-band performance and achieve smaller chip area and dc power consumption than previous circuits [32]-[35].

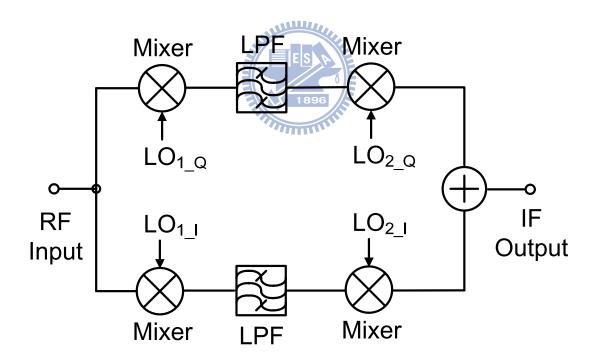

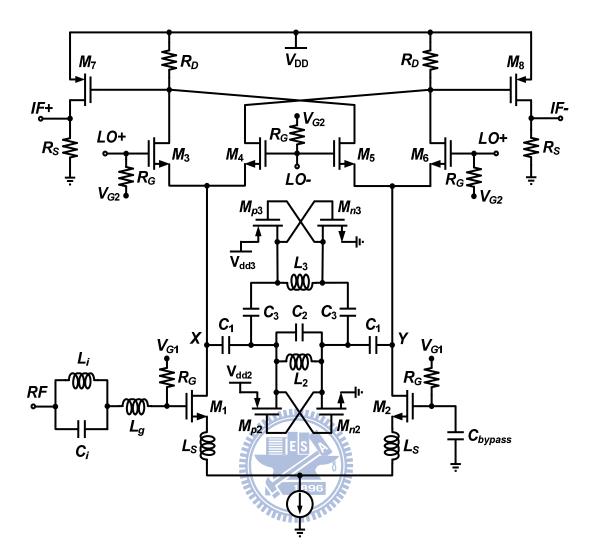

Fig. 3.3 Complete schematics of the proposed dual-band image rejection mixer.

# **3.2 CIRCUIT DESIGN**

The proposed dual-band image rejection mixer fabricated by 0.18-µm TSMC CMOS process is shown in Fig. 3.3 with the target dual-band frequencies at 2.4~2.48 and 5.15~5.35 GHz. The common-source differential pair ( $M_1$  and  $M_2$ ) with one of the inputs grounded by a capacitor can be regarded as a single-ended to differential balun. In addition, the proposed mixer adopts a source-degenerated amplifier with a dual-band input network ( $L_i$ ,  $C_i$ ,  $L_g$ ) to achieve a 50  $\Omega$  match at 2.45 and 5.2 GHz. The

Fig. 3.4 The nonlinear effect of a transistor with the bias voltage  $V_{G1}$ .

circuitry in between nodes X and Y is the proposed dual-band active notch filter to be discussed below.

#### **3.2.1 Effect of Nonlinearity**

In general, the nonlinear effect of a transistor in Fig. 3.4 is interrelated to the gate-to-source bias voltage and the second order transconductance coefficient  $g_m$  could be minimized while the maximum linear transconductance  $g_m$  is selected (i.e., the larger conversion gain, the superior second order harmonic suppression) [36]. Consequently, the second order harmonics behavior can be effectively diminished by adjusting the bias voltage  $V_{G1}$  to acquire a better conversion gain of mixer. Moreover, the dominant gain contributor of the proposed mixer is the input transconductance stage  $M_1-M_2$ . To obtain a sufficient gain, we must raise the dc current of  $M_1-M_2$  since the transconductance  $g_m$  is proportional to the current of transistor. Although it will

Fig. 3.5 A third-order notch filter reported in [37].

increase a small amount of dc power, the total dc power dissipation is still much smaller than previous circuits [32]-[35] made by the traditional Hartley or Weaver architectures.

3.2.2 Filter Design with Negative-Resistance Cells

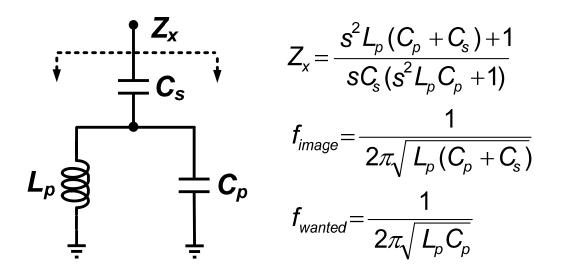

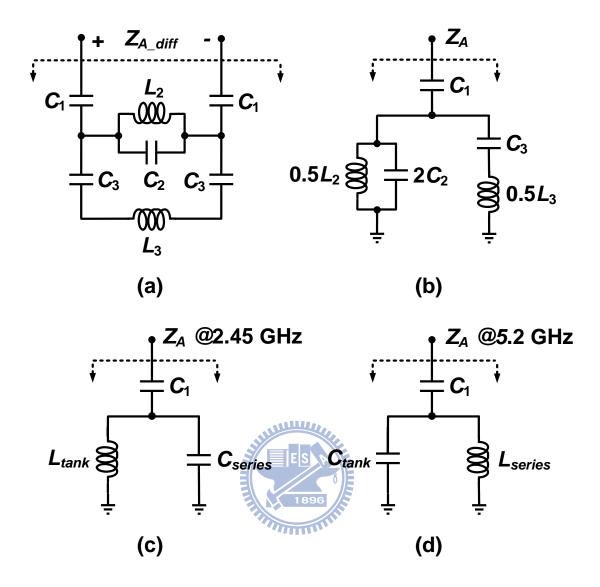

Fig. 3.5 shows a third-order notch filter, which can provide low and high impedance at the image and wanted frequencies, respectively to effectively attenuate the image signal without deteriorating the in-band performance [37]. In this study, a differential dual-band image suppression circuitry based on the third-order notch filter topology is proposed and shown in Fig. 3.6 (a). In the following analyses, we utilize the half circuit in Fig. 3.6 (b) to facilitate the discussions. It is obvious that the parallel *L*-*C* section is inductive and capacitive at low and high frequencies, respectively; however, it is reversed for the series *L*-*C* section. If the resonance frequency is appropriately designed, the  $0.5L_2$ - $2C_2$  and  $C_3$ - $0.5L_3$  circuit in Fig. 3.6 (b) at low frequency such as 2.45 GHz can be equal to an inductor  $L_{tank}$  and a capacitor  $C_{series}$

Fig. 3.6 (a) The proposed differential dual-band third-order notch filter. (b) The half circuit of (a). (c) Equivalent circuit at low frequency. (d) Equivalent circuit at high frequency.

shown in Fig. 3.6 (c). Similarly, Fig. 3.6 (d) can be acquired and comprehended by the above ratiocination. As a consequence, the proposed circuitry turns out to be the third-order notch filter in Fig. 3.5 at low and high frequencies simultaneously. After a straightforward derivation, the input impedance of the filter is given by

$$Z_{A} = \frac{s^{4} 0.25B(C_{1} + 2C_{2}) - s^{2}(0.5L_{2}C_{1} + A) + 1}{sC_{1}[s^{4} 0.5BC_{2} - s^{2}A + 1]}$$

(3.1)

where  $A=L_2C_2+0.5L_2C_3+0.5L_3C_3$ ,  $B=L_2L_3C_3$ , from which two zeros and two poles can be obtained in the positive frequency domain to provide low impedance at dual image frequencies and high impedance at dual wanted frequencies, respectively.

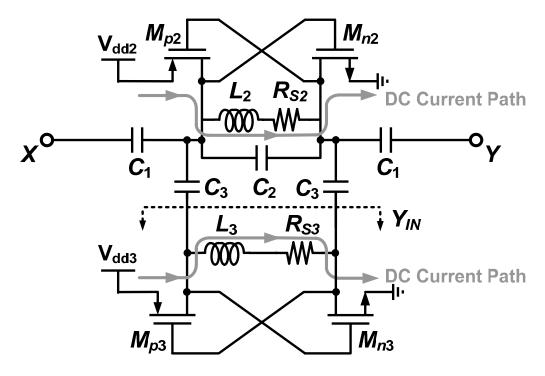

The proposed differential dual-band third-order notch filter can be utilized for the 2.45/5.2 GHz WLAN application. However, it should be taken into account that the maximum attenuation of the image rejection filter is restricted by the series resistance of on-chip inductor. To overcome this limitation, the negative-resistance cell by using cross-coupled transistors can be employed to improve the Q value of on-chip inductor. In this study, the cross-connected pair consisted of NMOS and PMOS transistors as a negative conductance generator is used and shown in Fig. 3.7. Power consumption and the usage of inductors can be cut in half compared to the traditional approach while providing the same negative conductance. The dc current path will be provided by the on-chip inductor and the impedance  $Y_{IN}$  can be expressed as

$$Y_{IN} \approx \frac{1}{j\omega L_3} + j(\frac{C_{gsn3}C_{gsp3}}{C_{gsn3} + C_{gsp3}}) + \frac{R_{S3}}{(\omega L_3)^2} - \frac{g_{mn3}g_{mp3}}{g_{mn3} + g_{mp3}}$$

(3.2)

As can be seen in (3.2), sufficient negative resistance can be generated to eliminate  $R_{S3}$  by adjusting the bias voltage  $V_{dd}$  since the  $g_{mn,p}$  is proportional to the current of transistors. It is obvious that the negative resistance facilitates to improve the maximum attenuation of the image rejection filter, but an overlarge value will bring about stability problem. A trade-off between the image rejection performance and stability should be carefully considered so as to make an optimum design. To avoid stability problem in this design, the negative resistor must be smaller than the series resistance of on-chip inductor. On the other hand, the process variation and temperature will influence the bias currents of the transistors to further deteriorate the

Fig. 3.7 The proposed differential dual-band notch filter with the negative-resistance cells consisted of NMOS and PMOS transistors.

filter performance, the externally controlled and adjustable bias voltages Vdd2 and Vdd3 are required to compensate for the process variation and temperature.

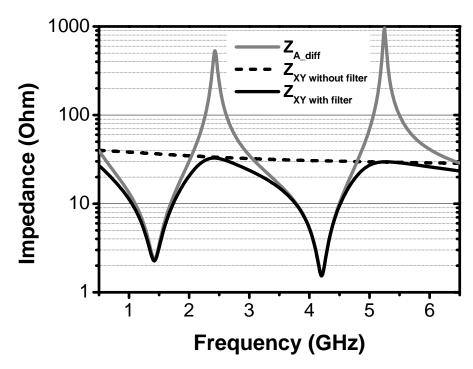

Based on the third order notch filter topology, the input impedance  $Z_{A_{diff}}$  of the proposed dual-band notch filter can also provide larger impedance in the both operation bandwidth (i.e., 2.4~2.48 and 5.15~5.35 GHz) to avoid the in-band signal at nodes *X* and *Y* having a leakage path to the proposed filter port and deteriorating the in-band performance.  $Z_{XY}$  without filter, as shown in Fig. 3.8, is the impedance between nodes *X* and *Y* without including the proposed notch filter, and the values at 2.45 and 5.2 GHz are 33 and 29 Ohm, respectively. The values of the impedance  $Z_{A_{diff}}$  at 2.4~2.48 and 5.15~5.35 GHz are more than 300 and 200 Ohm, and much larger than the input impedance  $Z_{XY}$  without filter. This means that the existence of the proposed notch filter in the dual-band operation frequencies will have no influence on the impedance between nodes *X* and *Y*, as can be observed from Fig. 3.8.

Fig. 3.8 The proposed notch filter in the dual-band operation frequencies has no influence on the impedance between nodes X and Y.

Consequently, the proposed dual-band image rejection mixer can achieve the sufficient image rejection without worsening the in-band characteristics.

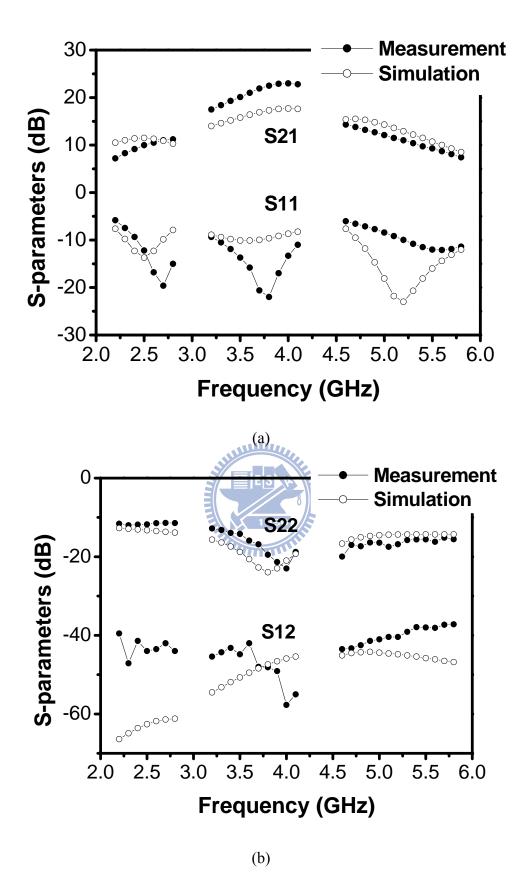

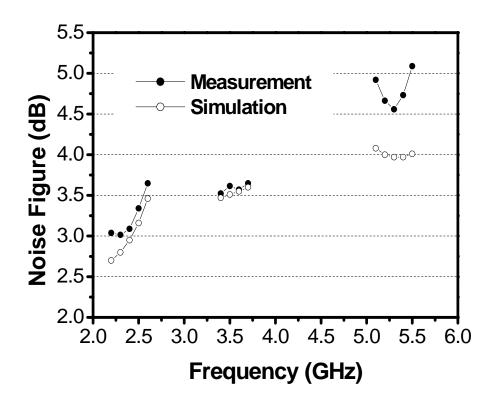

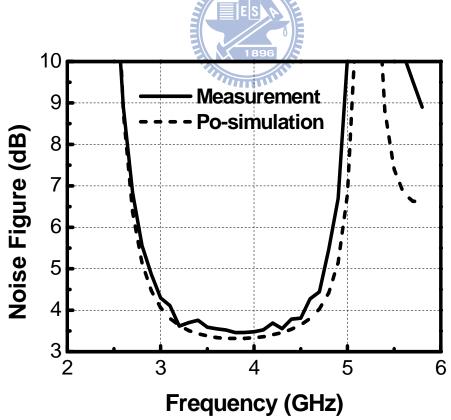

### **3.3 EXPERIMENTAL RESULTS**

The dual-band mixer chip with image rejection function was mounted on an FR4 test board for the measurement and the dc power dissipation was 10 mW. The simulated and measured results of input return loss are better than 10 dB in the operation bandwidth as depicted in Fig. 3.9. However, a non-negligible difference between simulation and measurement is obviously existent. We suppose that the bond-wire effect may cause the notch frequency drift because the dual-band mixer chip is mounted on an FR4 test board for the measurement. It can be demonstrated that the notch frequency will be affected due to the input bond wire; therefore, the

Fig. 3.9 Measured and simulated RF return loss of the proposed mixer.

length of bond wire must be as short as possible. On the other hand, as shown in Fig. 3.10, the measured conversion gain at RF = 2.45/5.2 GHz is 10.5/11 dB for IF=500 MHz and LO = 1.95/4.7 GHz. The maximum image rejection is 37 dB and 47 dB respectively. The measured minimum single sideband (SSB) noise figure at RF = 2.45/5.2 GHz is about 10/13 dB. The two-tone test with 10 MHz tone separation was performed using two Agilent 83640B signal generators and an Agilent 8564EC spectrum analyzer. The measured results of input-referred 1-dB compression point (*IIP*<sub>1dB</sub>) and input-referred third-order intercept point (*IIP3*) are depicted in Fig. 3.11. The values of the measured *IP*<sub>1dB</sub> and *IIP3* are -17/-16 dBm and -4.9/-5.2 dBm when RF=2.45/5.2 GHz. A die micro-photograph of the mixer proposed is shown in Fig. 3.12 with die area including pads of  $1.07 \times 1.07$  mm<sup>2</sup>.

Fig. 3.10 Conversion gain and noise figure of the proposed mixer.

Fig. 3.11 Measured results of fundamental output power and IM3 for the proposed mixer with RF input frequency spacing of 10 MHz.

Fig. 3.12 Microphotograph of the mixer. Die area is  $1.07 \times 1.07$  mm<sup>2</sup>.

# **3.4 SUMMARY**

A 2.45/5.2 GHz image rejection mixer with differential dual-band third-order notch filter has been fabricated and designed. The suppression of about 36/45 dB at the image frequencies can be achieved without worsening the in-band characteristics. In this study, the dc power consumption and chip area are smaller than the literature presented in [32]-[35] due to the reduction in the complexity of image rejection circuit mechanism. The presented mixer is compared with recently published mixers and summarized in Table 3.1.

| Item                       | This<br>work    | [31]   | [32]   | [33]   | [34]    | [35]               |

|----------------------------|-----------------|--------|--------|--------|---------|--------------------|

| RF (GHz)                   | 5.2/2.45        | 8 / 4  | 5.2    | 5.25   | 5.7/5.2 | 5.7/2.4            |

| Gain (dB)                  | 11/10.5         | -14/-8 | 11     | 14     | 18.5/20 | 8/9                |

| IP <sub>1dB</sub> (dBm)    | -16/-17         | -      | -17    | -18    | -15/-15 | -13/-11            |

| IRR<br>(dB)                | 45/36           | N/A    | 40     | 40     | 44/48 * | 40/40              |

| P <sub>diss</sub> (mW)     | 10              | 81     | 150    | 58     | -       | 126                |

| Area<br>(mm <sup>2</sup> ) | 1.2             | 2      | 7.5    | 4      | 5       | 4                  |

| IRR<br>Architecture        | Notch<br>Filter | N/A    | Weaver | Weaver | Weaver  | Weaver-<br>Hartley |

|                            |                 |        | 2µm    |        | 2µm     |                    |

| Tash                       | 0.18µm          | 0.18µm | GaInP/ | 0.18µm | GaInP/  | 0.18µm             |

| Tech.                      | CMOS            | CMOS   | GaAs   | CMOS   | GaAs    | CMOS               |

|                            |                 | Ĩ      | HBT    |        | HBT     |                    |

Table 3.1Comparison with previously published mixers

\* only at 5.7 and 5.2 GHz, not in the whole operation bandwidth

## **CHAPTER 4**

# ANALYSIS OF WIDE-BAND LOW NOISE AMPLIFIER WITH OUT-BAND REJECTION

### **4.1 INTRODUCTION**

UWB systems realize high data rate in the short-range wireless transmission, which are suitable for integration in various consumer electronics such as PCs, cellular phones, digital cameras, and personal digital assistants. The minimum received power in the UWB channel is 47 and 67 dB, in the worst case, lower than those of the wireless local area network interferer powers at 5.2 and 2.4 GHz, respectively [38]. In addition, a tone is measured at 1.87 GHz in a smart-phone currently on the market, and the power level is 35 dB higher than the UWB signal [39]. All of these interferers, as shown in Fig. 4.1, have a harmful effect on the received UWB signal; especially they can lead to the receiver gain compression and their possible intermodulation products can fall in-band. Although the interferers may further be attenuated by the baseband filter in the receiver, this does not address the problems of the intermodulation distortion and the receiver gain desensitization. In order to achieve reasonable performance for the above considerations, as summarized in Table 4.1, more than 10 dB attenuation over the bandwidth of each interferer with 20 dB peak attenuation is appropriate in the front-end [40]-[44]. On the other hand, a larger attenuation in the front-end also can relax the baseband filter achieving an implementation with the smaller group delay variations and lower dc power consumption [42].

Recently, a design of multiple-stopband filters is presented for the suppression of

Fig. 4.1 Spectrum of the UWB system with large interferers.

| NOTENTI LITER STEEL TEATIONS |              |                   |                  |  |  |  |

|------------------------------|--------------|-------------------|------------------|--|--|--|

| Standard                     | Notch center | 10 dB attenuation | Peak             |  |  |  |

| Stanuaru                     | freq. (GHz)  | bandwidth (GHz)   | attenuation (dB) |  |  |  |

| GSM-1800/1900                | 1.85         | 1.71~1.99         |                  |  |  |  |

| 802.11b/g                    | 2.44         | 2.4~2.48          | > 20             |  |  |  |

| 802.11a                      | 5.25         | 5.15~5.35         |                  |  |  |  |

Table 4.1NOTCH FILTER SPECIFICATIONS

interfering signals such as Global System for Mobile (GSM), WLAN, and WIMAX in UWB applications [40]. The coupled resonator stopband filter sections with bent resonators were adopted in order to more effectively suppress harmonics and the maximum rejection is about 25 dB at 1.8 GHz. However, this prototype of filter which was fabricated on the basis of the standard PCB process will increase the whole UWB system area. Moreover, the multiple receivers with equal-gain combining were employed to eliminate the narrowband interferers received in the two paths and combined out-of-phase to cancel each other by selecting the optimal LO phase [41]. A maximum 28 dB attenuation of the interferers was measured but it is unavoidable to

increase the system's complexity.

On the other hand, the topologies utilized for wideband amplifiers generally include the distributed configuration [45]–[46], resistive shunt-feedback structure [47]–[49], common-gate  $1/g_m$  termination [50]–[52], and *LC* input network [53]–[54]. The distributed amplifiers are attractive for their ultra-wide bandwidth; however, the major drawbacks are the large area and high dc power consumption, which make them unsuitable for many applications. The resistive shunt-feedback and common-gate  $1/g_m$  amplifiers can provide good impedance matching and moderate gain while dissipating small amounts of dc power but without the out-band rejection capability. Recently, a new topology of the broadband amplifier for out-band rejection, which adopted a notch filter circuit with negative-resistance cell embedded, has been reported in [26], [55]. Inevitably, the extra notch filter circuit made of inductors and cross-coupled transistors will occupy additional chip area and dc power simultaneously.

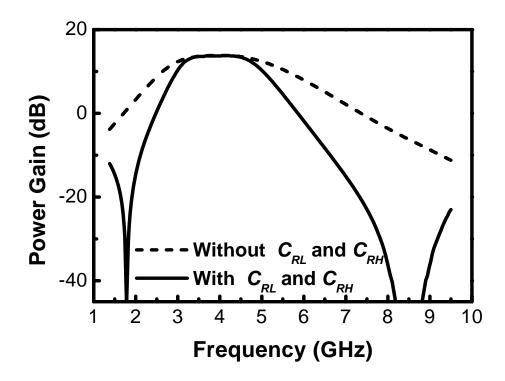

In this chapter, three low-power UWB LNAs using 0.18-µm CMOS technology are presented. In the first UWB LNA, a new wideband input impedance-matching network, which is based on the *LC* structure with focus on the improvement of out-of-band rejection capability, is presented. By suitably introducing two additional capacitors in the traditional *LC* input network, two transmission zeros at 1.8 GHz and 8.5 GHz are generated to achieve the out-band rejection property while without suffering from deterioration of the in-band performance.

As an improvement of the first approach, the second proposed UWB LNA introduces a capacitive feedback path to the input *LC* network for further enhancing the rejection capability at the lower band transmission zero (1.8 GHz). A maximum 32 dB improvement is attained due to the usage of a feedback capacitor. Also, a dual-band notch filter made of active inductors, which occupies only a small chip area,

is employed after the LNA core so as to attenuate the WLAN interferers at 2.4 GHz and 5.2 GHz while without influencing the noise figure of the LNA. The proposed active inductors are designed based on the cascode gain-boosting stage with a feedback resistor, which are with low consumption power while maintaining a sufficient Q value. The introducing of both the feedback capacitor and the dual-band notch filter achieves maximum rejections of about 50 dB on the out-band interferers, which is superior than those presented in the literature [26], [40]–[41], and [55].

After improving the out-band rejection capability, a new matching technique is presented to further ameliorate the noise figure performance in the third UWB LNA. The proposed broad-band input match can be acquired easily by selecting an appropriate width of the transistor, which will effectively avoid the usage of the low-*Q* on-chip inductors in the input network. Moreover, this UWB LNA chip also demonstrates the feasibility of inter-stage resonator to accomplish bandwidth enhancement without additional power consumption. The IC prototype achieves good performances such as a power gain of 16.2 dB, a better than 10 dB input return loss, and 2.3 dB minimum noise figure while consuming a dc power of only 6.8 mW. In this chapter, the circuit simulation is performed via Agilent's Advanced Design System (ADS) software with a TSMC design kit.

# 4.2 WIDE-BAND LOW NOISE AMPLIFIER WITH OUT-BAND REJECTION INPUT NETWORK

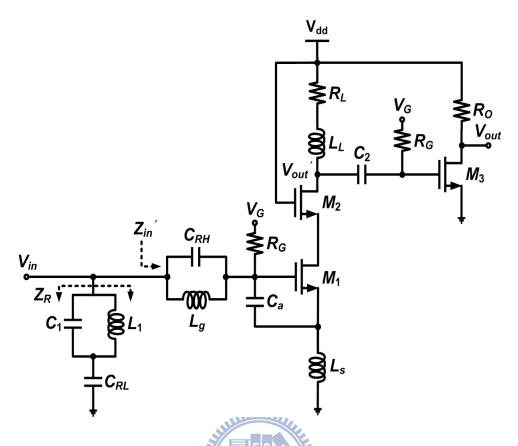

The first 3-to-5 GHz CMOS UWB LNA proposed here adopts a source-degenerated cascode configuration as shown in Fig. 4.2. An *LC* input network for wideband operation is utilized, with two new capacitors  $C_{RH}$  and  $C_{RL}$  for

Fig. 4.2 Complete schematics of the first UWB LNA with out-band rejection.

increasing the higher and lower out-band rejections, respectively. The load inductor  $L_L$  in series with the resistor  $R_L$  helps to enhance the gain flatness. The buffer transistor  $M_3$  with a purely resistive load  $R_O$  is employed for testing purposes.

## 4.2.1 Circuit Design and Analysis

### 4.2.1.1 Power Gain

The overall gain of the proposed LNA can be easily obtained as follows after a straightforward derivation:

$$S_{21} = \frac{(1+S_{11})v_{out}}{v_{in}} = (1+S_{11})\frac{v_{out}}{v_{in}} \cdot g_{m3}(R_o //Z_0)$$

(4.1)

where

$$\frac{v_{out}}{v_{in}} = \frac{g_{m1} \left(1 - \omega^2 L_g C_{RH}\right)}{\chi(\omega)} \cdot \left[ \left(R_L + j\omega L_L\right) / \frac{1}{j\omega C_L} \right]$$

(4.2)

with

$$\chi(\omega) = \omega^4 L_g L_s C_t C_{RH} - j\omega^3 L_g L_s g_{m1} C_{RH} - \omega^2 (L_g C_t + L_g C_{RH} + L_s C_t) + j\omega g_{m1} L_s + 1.$$

$$(4.3)$$

$Z_0$  is the 50- $\Omega$  source resistance,  $C_t = C_{gs1} + C_a$ , and  $C_L$  is the total capacitance between the drain of the transistor  $M_2$  and ground.  $S_{11}$  is the reflection coefficient at the input port. From (4.1) it is seen that, extra transmission zeros (i.e.,  $S_{21} = 0$ ) can be created when the following conditions are satisfied:

$$S_{11} = -1 \text{ or } \frac{v_{out}}{v_{in}} = 0 ,$$

(4.4)

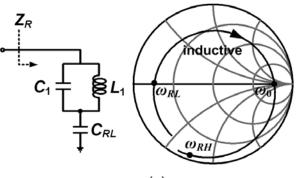

in which  $S_{11} = -1$  means that the input impedance of the LNA is short circuit, and it occurs as the impedance  $Z_R$ , i.e., the impedance of the  $L_1C_1$  tank in series with the capacitor  $C_{RL}$  (see Fig. 4.2), is equal to zero, where

$$Z_{R}(\omega) = \left[1 - \omega^{2} L_{1} \left(C_{RL} + C_{1}\right)\right] / j \omega C_{RL} \left(1 - \omega^{2} L_{1} C_{1}\right) .$$

$$(4.5)$$

By using (4.4), (4.2) and (4.5), the locations of transmission zeros can be predicted as

Fig. 4.3 Simulated ideal power gain with and without out-band rejection improvement.

$$\omega_{RH} = 1/\sqrt{L_g C_{RH}} , \quad \omega_{RL} = 1/\sqrt{L_1 (C_{RL} + C_1)^{896}}$$

(4.6)

The design criterion of the out-band rejection function can be derived from (4.6) with two transmission zeros at 1.8 and 8.5 GHz determined by the capacitors  $C_{RH}$  and  $C_{RL}$ , as shown in Fig. 4.3.

#### **4.2.1.2 Input-Matching Analysis**