## 國立交通大學

## 電機學院 電子與光電學程

## 碩士論文

在 PACDSP 平台上實現 MPEG-4 物件視訊編碼器

Software Implementation of MPEG-4 Object-based Video Encoder on

PACDSP Platform

1896

研究生: 黄炳智

指導教授:林大衛 教授

中華民國九十九年七月

## 在 PACDSP 平台上實現 MPEG-4 物件視訊編碼器 Software Implementation of MPEG-4 Object-based Video Encoder on PACDSP Platform

研究生: 黃炳智 Student: Ping-Chih Huang

指導教授:林大衛 Advisor: David W. Lin

國立交通大學 電機學院 電子與光電學程 碩士論文

A Thesis

Submitted to College of Electrical and Computer Engineering

National Chiao Tung University

in partial Fulfillment of the Requirements

for the Degree of

Master of Science

in

Electronics and Electro-Optical Engineering

July 2010

Hsinchu, Taiwan, Republic of China

中華民國九十九年七月

學生: 黃炳智 指導教授: 林大衛 博士

國立交通大學 電機學院 電子與光電學程碩士班

摘 要

MPEG-4 為一廣泛應用之多媒體訊號壓縮標準。本篇論文介紹在 PACDSP v3.0 平台上 MPEG-4 物件視訊編碼器之實現,本平台由一超長指令數位訊號處理器與一 ARM926EJ-S 處理器所組成。為了最佳化程式流程,我們也完成了許多的靜態分析,並且利用超長指令處理器架構上之特性來達到即時編碼。我們已完成在ARM 及 PACDSP 的平行運作,並驗證雙核心執行結果之正確性。

在我們的實作中,我們以 MPEG-4 參考軟體,MoMuSys 為基礎,當作驗證的比較對象。首先,我們分析了 MPEG-4 物件視訊編碼器之特性,並且對編碼流程有了初步的瞭解。接著,我們分析編碼之運算複雜度及超長指令處理器程式碼之平行度,並且藉此找到有效率的實現方法。在移動估測編碼中,我們利用螺旋搜尋法中的一項參數來降低編碼的運算量,並且沒有犧牲太多的影像品質,同時也利用 PACDSP 的架構以加速 SAD 的運算。在形狀編碼中,我們對 inter 編碼模式做調整以降低運算複雜度,並藉由增加程式碼的平行度來提升運算速度。在紋理編碼中,我們根據離散餘弦轉換(DCT)之特性來跳過多餘的運算。

為了加速執行的速度,我們把規律的運算分配至 DSP 的兩組運算單元以增加處理器之效能。我們也利用單指令多資料(SIMD)指令以及一般指令層級平行化來減少處理器之延遲。另外,我們也討論了離散餘弦轉換(DCT)和離散餘弦反轉換(IDCT)之效能與精確度,而且我們的離散餘弦反轉換(IDCT)實現能夠符合 IEEE 1180-1190 標準之規範。在所有的最佳化之後,我們在最好的情況下,在 intra 和 inter 編碼模式下,可分別達到每秒 43 和 35 張的 QCIF 畫面即時編碼。而整個程式的大小為 29 Kbytes,也小於 PACDSP 的程式快取記憶體大小 32 Kbytes。

在本篇論文當中,我們首先介紹了 MPEG-4 標準以及 PADSP 平台之概述。 接著討論靜態分析、最佳化方法、整體實作設計、以及實驗結果。最後簡單介紹 了雙核心實現的系統與機制。

## Software Implementation of MPEG-4 Object-based Video Encoder on PACDSP Platform

student: Ping-Chih Huang Advisors: Dr. David W. Lin

### Degree Program of Electrical and Computer Engineering National Chiao Tung University

#### **ABSTRACT**

A MPEG-4 is a widely-applied multimedia coding standard. This thesis presents an implementation of MPEG-4 object-based video encoder on the PACDSP v3.0 platform, which consists of a VLIW digital signal processor (DSP) and an ARM926EJ-S processor. We complete many analysis to optimize the program flow and utilize the advantage of VLIW processor to achieve real-time encoding. We have done the parallel operation on the ARM and PACDSP, and the dual-core encoding results is verified.

In our implementation, the MPEG-4 reference software, MoMuSys, is used as a golden model to verify our implementation. First, we analyze the statistics of the MPEG-4 object-based video encoder, and have an initial understand of the encoding flow. Second, we analyze the computation complexity of the coding, the VLIW program parallelism and find efficient algorithms for the implementation. In the motion coding, we use a parameter of spiral search to reduce the computation effort without too much quality loss and utilizes VLIW processor architecture to speed up SAD determination. In shape coding, we modify the inter mode coding to reduce computation complexity and increase the VLIW processor code parallelism to enhance the speed. In texture coding, we skip some computations according to the nature of discrete cosine transform (DCT).

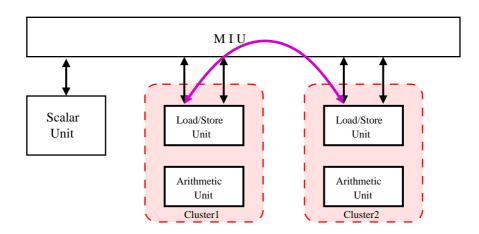

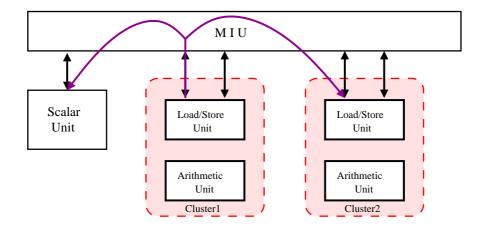

Third, to reduce the execution time, we distribute the regular computations to both clusters to increase the efficiency of the processor. Single instruction multiple data

(SIMD) instructions and general instruction level parallelism also utilized to reduce the processor stalls. We also discuss the efficiency and accuracy of DCT and IDCT, and the accuracy of our IDCT implementation can meet the IEEE 1180-1190 standard. After all the optimizations, we can encode the MPEG-4 video data for QCIF format over 43 and 35 frames per second in the best case for intra and inter encoding. The code size is 29 Kbytes, which is smaller than the 32-Kbyte instruction cache on PACDSP.

In this thesis, we first introduce the MPEG-4 standard and give an overview of the PACDSP platform. Then the static analysis, the optimization methods, the overall implementation design, and the experiment results are discussed. Finally, we brief the system and mechanism for the dual-core implementation on the PACDSP platform.

誠摯地感謝我的指導老師 林大衛 博士,老師親切和善的態度與不間斷的鼓勵下,讓我即使遭遇任何的困難,均能勇敢不氣餒的面對與克服。同時對於研究上所遭遇的瓶頸,每每能切中要點指引正確的方向,使我能順利地完成此研究。在此,向老師致上最高的感謝之意。

另外要感謝榮煌同學及政達同學,感謝他們熱心無私的協助,使我能解決許多疑難雜症。也要感謝學校及通訊電子與訊號處理實驗室的資源,讓我能專心致力於研究。最後,要感謝的是我的家人,在內人的支持與協助下讓我能夠心無旁騖的從事研究工作。謝謝所有幫助過我的師長、同儕與家人。謝謝!

## **Contents**

| 1 | Intr | oduction                                   | 1  |

|---|------|--------------------------------------------|----|

| 2 | Ove  | view of the MPEG-4 Video Standard          | 3  |

|   | 2.1  | Structure of MPEG-4 Video Data             | 3  |

|   | 2.2  | MPEG-4 Video Texture Coding                | 6  |

|   |      | 2.2.1 VOP Formation                        | 7  |

|   |      | 2.2.2 Shape Coding                         | 8  |

|   |      | 2.2.3 Motion Coder                         | 11 |

|   |      | 2.2.4 Texture Coder                        | 17 |

|   |      | D 1 3                                      | 21 |

|   | 2.3  |                                            | 23 |

| 3 | Ove  | view of PACDSP                             | 25 |

|   | 3.1  | Introduction                               | 25 |

|   | 3.2  | ISA and Pipeline Stages                    | 27 |

|   | 3.3  | Program Sequence Control Unit              | 27 |

|   |      | 3.3.1 Branch Instructions                  | 29 |

|   |      | 3.3.2 Loops                                | 30 |

|   |      | 3.3.3 Customized Function Units (CFUs)     | 31 |

|   |      | 3.3.4 Exception Handling                   | 31 |

|   |      | 3.3.5 Interrupt Handling                   | 32 |

|   | 3.4  | Scalar Unit                                | 32 |

|   |      | 3.4.1 General Purpose Scalar Register File | 32 |

|   |      | 3.4.2    | System Register and Predication Register   | 33 |

|---|------|----------|--------------------------------------------|----|

|   | 3.5  | VLIW     | Datapath                                   | 33 |

|   |      | 3.5.1    | Ping-Pong Register File                    | 36 |

|   |      | 3.5.2    | Address/Accumulator Registers              | 36 |

|   |      | 3.5.3    | Constant Registers                         | 37 |

|   |      | 3.5.4    | Status and Control Registers               | 37 |

|   |      | 3.5.5    | Addressing Modes                           | 38 |

|   |      | 3.5.6    | Data Communication                         | 40 |

|   | 3.6  | Condit   | ional Execution Control                    | 41 |

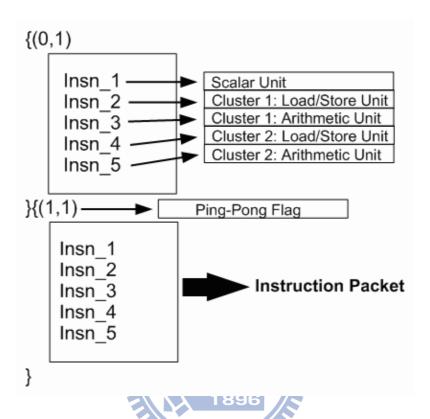

|   | 3.7  | Instruc  | tion Packet                                | 42 |

|   | 3.8  | DSP R    | unning Modes                               | 43 |

|   | 3.9  | Dual-C   | Core Platform and the Tool Chain           | 43 |

| 4 | Dua  | l-Core I | Program Development and Analysis           | 46 |

|   | 4.1  | Profile  | s of the MPEG-4 Object-Based Video Encoder | 46 |

|   |      | 4.1.1    | PACDSP Implemented Consideration           | 47 |

|   |      | 4.1.2    | Approach to Complexity Analysis [11]       | 51 |

|   |      | 4.1.3    | Profile Using the Profiler of ADS [10]     |    |

|   | 4.2  | Low-L    | evel Computational Analysis                | 53 |

|   |      | 4.2.1    | Motion Coder Analysis                      | 53 |

|   |      | 4.2.2    | Shape Coder Analysis                       | 57 |

|   |      | 4.2.3    | Texture Coder Analysis                     | 57 |

|   | 4.3  | Implen   | nentation Strategy on Dual-Core Platform   | 59 |

|   |      | 4.3.1    | Motion Coder Optimization                  | 59 |

|   |      | 4.3.2    | Shape Coder Optimization                   | 65 |

|   |      | 4.3.3    | Texture Coder Optimization                 | 68 |

|   | 4.4  | Dual-C   | Core Platform Implementation               | 70 |

| 5 | Furt | -        | timization of the PACDSP Code              | 72 |

|   | 5.1  | Feature  | es of PACDSP                               | 72 |

|   | 5.2  | Genera   | al Techniques of Code Optimization         | 73 |

|   |     | 5.2.1   | Memory Alignments for Efficient Data Load/Store         | 73 |

|---|-----|---------|---------------------------------------------------------|----|

|   |     | 5.2.2   | General Code Optimization Techniques                    | 74 |

|   | 5.3 | Implen  | mentation of SAD Calculation Using SIMD Instructions    | 77 |

|   | 5.4 | Fixed-  | Point DCT and IDCT                                      | 80 |

|   | 5.5 | Fixed-  | Point Quantization                                      | 85 |

|   |     | 5.5.1   | The H.263 Quantization Method                           | 85 |

|   |     | 5.5.2   | Lossless Fixed-Point Quantization Method                | 87 |

|   |     | 5.5.3   | Coding Quality and Bit Rates for Different QP Value     | 87 |

|   | 5.6 | Simula  | ation Results on PACDSP Instruction Set Simulator (ISS) | 90 |

|   |     | 5.6.1   | Statistics of Motion Estimation on ISS                  | 90 |

|   |     | 5.6.2   | Statistics of Shape Coding on ISS                       | 91 |

|   | 5.7 | Perfori | mance Analysis and Implementation Results               | 91 |

|   |     | 5.7.1   | PACDSP Code Size                                        | 92 |

|   |     | 5.7.2   | Frame Rate Estimation . E. S                            | 93 |

| 6 | Con | clusion | and Potential Future Work                               | 98 |

|   | 6.1 | Conclu  | usion                                                   | 98 |

|   | 6.2 | Potenti | ial Future Work                                         | 99 |

## **List of Figures**

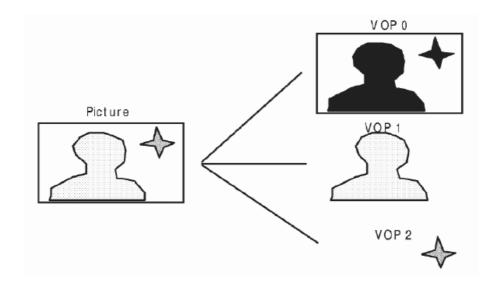

| 2.1  | Segmentation of a frame into VOPs (from [5])                             | 4  |

|------|--------------------------------------------------------------------------|----|

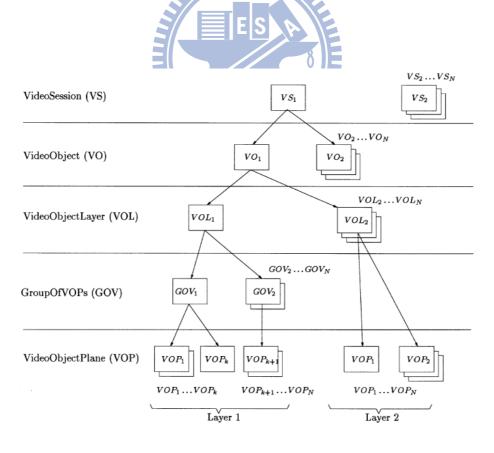

| 2.2  | Structure of coded video data (from [6])                                 | 4  |

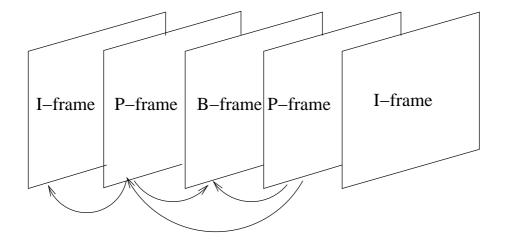

| 2.3  | Types of VOP                                                             | 6  |

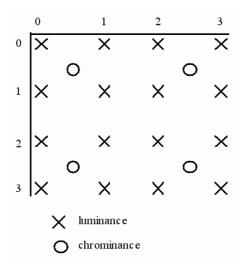

| 2.4  | Positions of luminance and chrominance samples in 4:2:0 data (from [7]). | 6  |

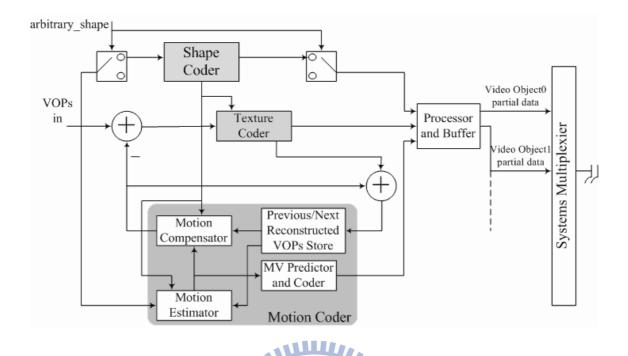

| 2.5  | Structure of VO encoder (from [5])                                       | 7  |

| 2.6  | Structure of VO encoder (from [5])                                       | 8  |

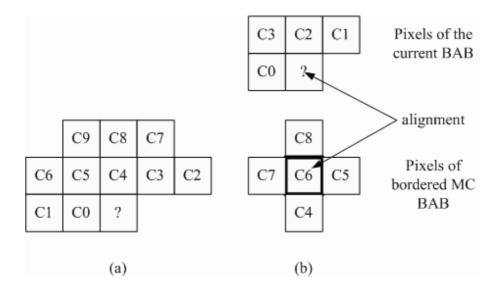

| 2.7  | Pixel templates used for (a) INTRA and (b) INTER context calculation of  |    |

|      | BAB. The current pixel to be coded is marked with "?" (from [4])         | 11 |

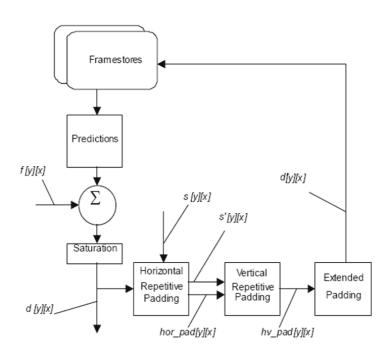

| 2.8  | Simplified padding process (from [4]).                                   | 12 |

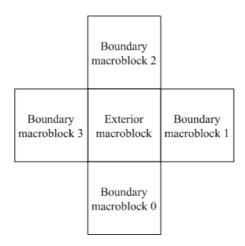

| 2.9  | Priority of boundary MBs surrounding an exterior MB (from [4])           | 12 |

| 2.10 | Bilinear Interpolation for half sample search (from [4])                 | 14 |

| 2.11 | Motion vector prediction (from [7])                                      | 15 |

| 2.12 | Quantizers in H.263. (a) For intra DC coefficient only. (b) For inter DC |    |

|      | and all AC coefficients                                                  | 19 |

| 2.13 | Prediction of DC coefficients of blocks in an intra MB (from [5])        | 20 |

| 2.14 | Prediction of AC coefficients of blocks in an intra MB (from [5])        | 21 |

| 2.15 | Scans for $8 \times 8$ blocks (from [4])                                 | 21 |

| 3.1  | Architecture of the PACDSP [1]                                           | 28 |

| 3.2  | PACDSP instruction set architecture [3]                                  | 28 |

| 3.3  | Pipeline stages of the PACDSP [3]                                        | 29 |

| 3.4  | The VLIW datapath register organization [1]                              | 35 |

| 3.5  | The four-way VLIW datapath of PACDSP [1]                                 | 36 |

|      |                                                                          |    |

| 3.6  | Address register file [1]                                                     | 39 |

|------|-------------------------------------------------------------------------------|----|

| 3.7  | Data exchange between two clusters [1]                                        | 41 |

| 3.8  | Data broadcast among clusters [1]                                             | 42 |

| 3.9  | Syntax of instruction packet [2]                                              | 44 |

| 3.10 | Simplified syntax of instruction packet [2]                                   | 44 |

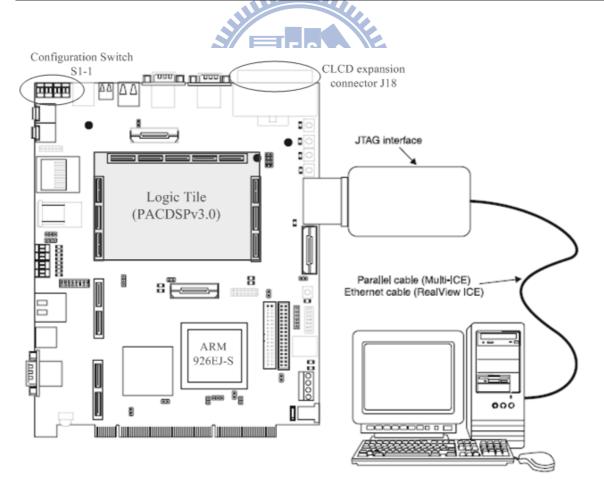

| 3.11 | PACDSP v3.0 system[10]                                                        | 45 |

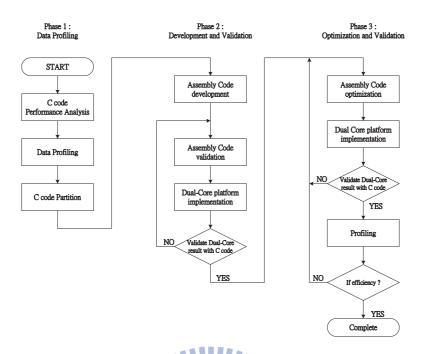

| 4.1  | Flow of Dual-core software encoder development                                | 47 |

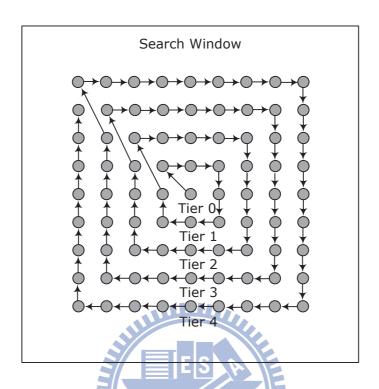

| 4.2  | Concept of spiral search                                                      | 56 |

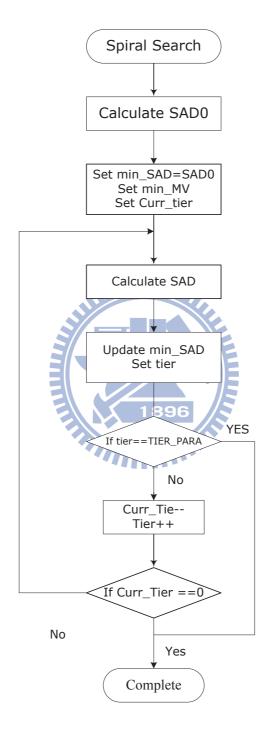

| 4.3  | Dataflow of spiral search with tier parameter                                 | 60 |

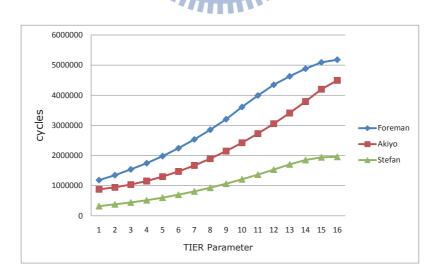

| 4.4  | Execution cycles with different TIER_PARA values                              | 61 |

| 4.5  | PSNR values with different tier_para values                                   | 62 |

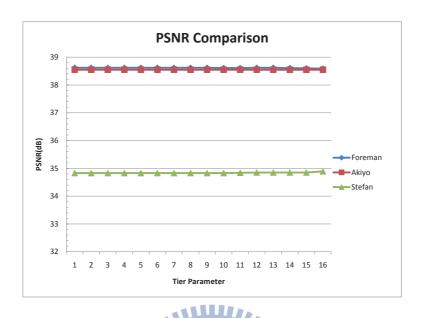

| 4.6  | SAD iteration                                                                 | 63 |

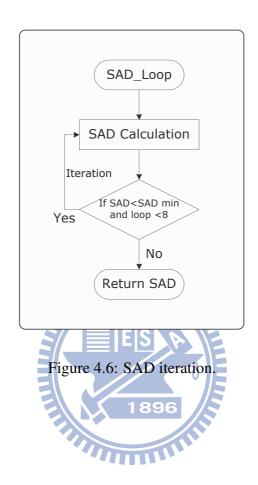

| 4.7  | SAD iteration                                                                 | 64 |

| 4.8  | Candidates for MVPs [4]                                                       | 65 |

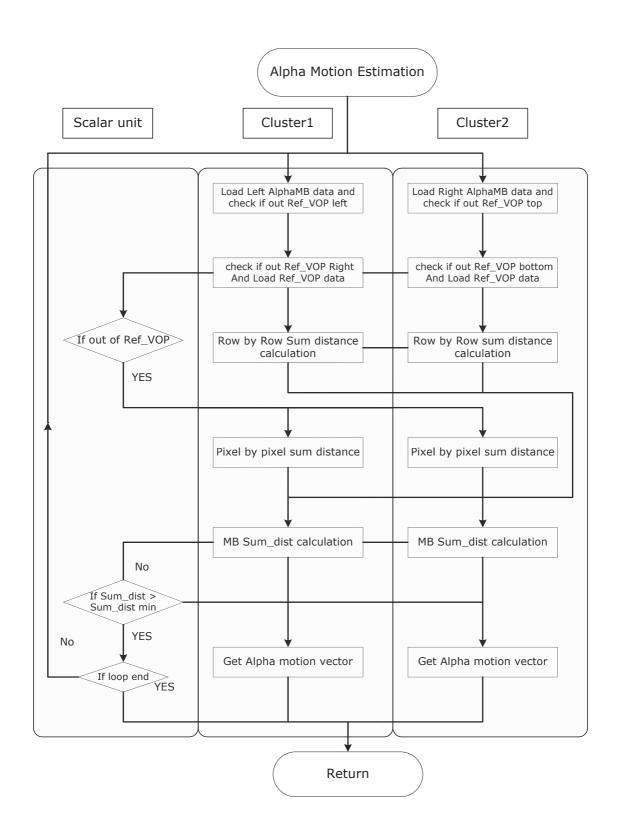

| 4.9  | Parallelized implementation of AlphaMotionEstimation                          | 67 |

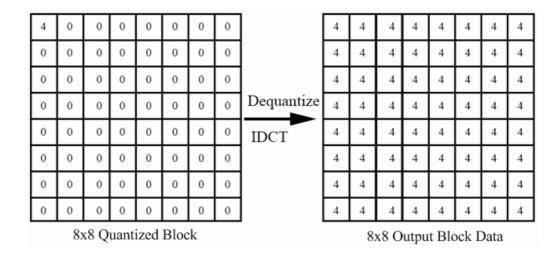

| 4.10 | DC spreading from quantized coefficient to output block [10]                  | 69 |

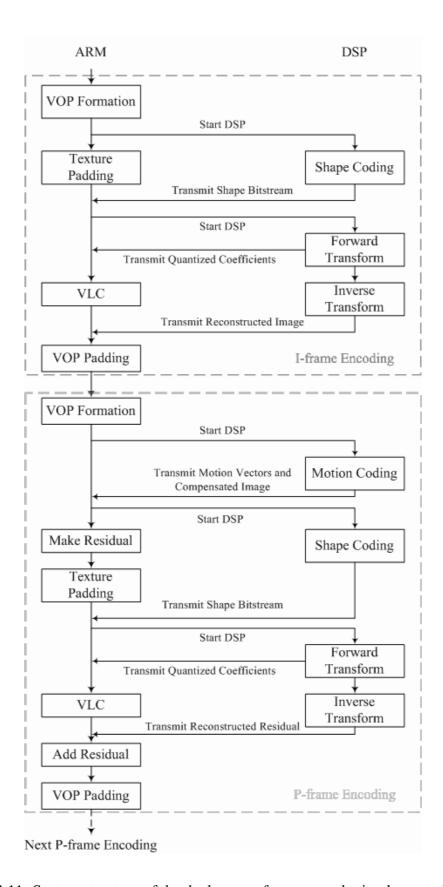

| 4.11 | System structure of the dual-core software encoder implementation [10]        | 71 |

| 5.1  | Example of memory alignment to reduce memory access cycles                    | 74 |

| 5.2  | Example of vector addition                                                    | 74 |

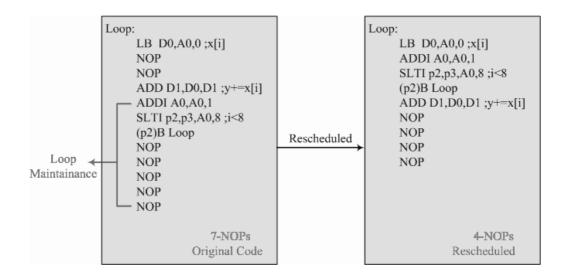

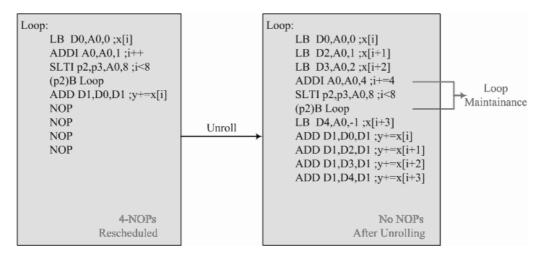

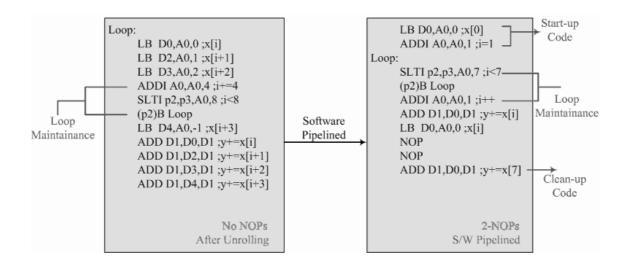

| 5.3  | Example of static rescheduling                                                | 76 |

| 5.4  | Example of loop unrolling                                                     | 76 |

| 5.5  | Example of software pipelining technique                                      | 77 |

| 5.6  | An example code for $16 \times 16$ SAD calculation on PACDSP                  | 78 |

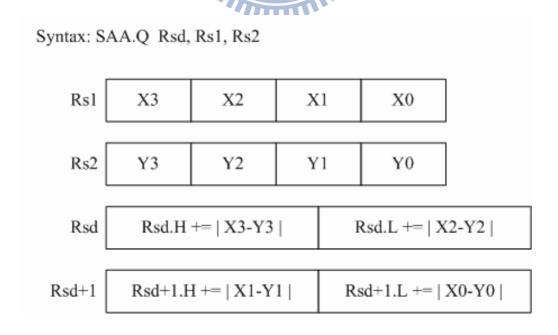

| 5.7  | Syntax and operation of the SAA.Q instruction                                 | 78 |

| 5.8  | Assembly code of masked $16 \times 16$ SAD calculation in our implementation. | 79 |

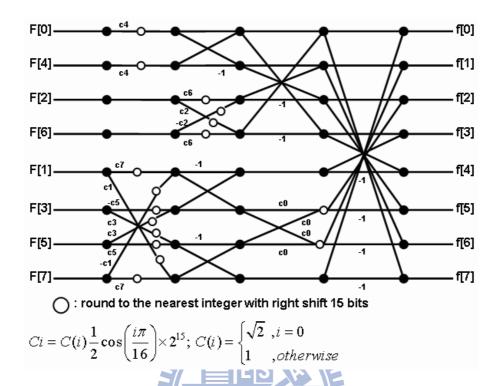

| 5.9  | The IDCT algorithm used in MoMuSys [8]                                        | 83 |

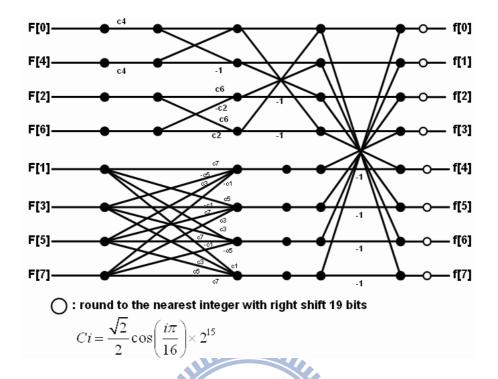

| 5.10 | The even-odd decomposition IDCT algorithm [13]                                | 84 |

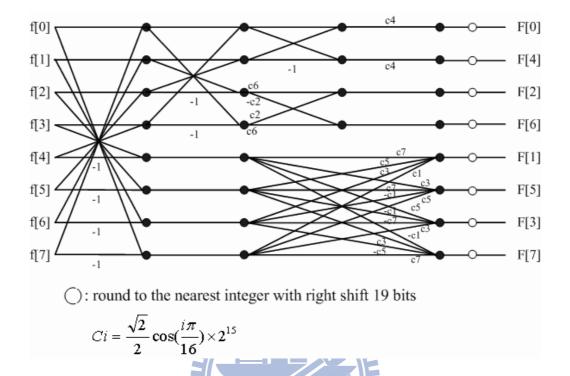

| 5 11 | The even-odd decomposition DCT algorithm [13]                                 | 86 |

## **List of Tables**

| 2.1  | List of BAB Types (from [4])                                       | 9  |

|------|--------------------------------------------------------------------|----|

| 2.2  | Shape Coding Modes and Their Main Usages (from [4])                | 10 |

| 2.3  | Default Quantization Matrix $(Q)$ [4]                              | 19 |

| 2.4  | Nonlinear Scaler for DC Coefficients (from [4])                    | 19 |

| 2.5  | Profiles and Tools in MPEG-4 Video (from [4])                      | 24 |

| 3.1  | Pipeline Stages and Their Jobs [3]                                 | 29 |

| 3.2  | System Register File [1]                                           | 34 |

| 3.3  | Definitions of AMCR (from [1])                                     | 38 |

| 3.4  | Syntax of Address Modes and Supporting Units [2]                   | 39 |

| 3.5  | Instruction Type in Each Instruction Slot [1]                      | 42 |

| 3.6  | Running Modes of the PACDSP v3.0 [1]                               | 45 |

| 4.1  | Functionalities of Our Implementation                              | 48 |

| 4.2  | Shape Coding Data Memory Usage                                     | 49 |

| 4.3  | Motion Estimation Data Memory Usage                                | 50 |

| 4.4  | Texture Coding Data Memory Usage                                   | 50 |

| 4.5  | Profile of Object-Based MPEG-4 Encoding of QCIF I-VOP on ADS [10]  | 53 |

| 4.6  | Profile of Object-Based MPEG-4 Encoding of QCIF P-VOP on ADS [10]  | 54 |

| 4.7  | Major Function in Motion Estimation (ME)[10]                       | 55 |

| 4.8  | Percentage of Early Termination in SAD Calculation Under Different |    |

|      | Scan Orders [10]                                                   | 55 |

| 4.9  | Motion Coder Analysis on PACDSP                                    | 56 |

| 4.10 | CAE Modes and Associated VOP Types                                 | 57 |

| 4.11 | Analysis of the Snapelinterivib function on PACDSP                     | 38 |

|------|------------------------------------------------------------------------|----|

| 4.12 | Texture Coder Analysis on PACDSP                                       | 58 |

| 4.13 | Execution Cycles of Motion Estimation for 1 P-VOP of QCIF on ISS       | 63 |

| 4.14 | ISS Simulation Results of Reduced-Complexity ShapeInterMB Function .   | 66 |

| 4.15 | Execution cycles of Shape Inter for 1 P-VOP of QCIF on ISS             | 68 |

| 4.16 | Number of Skipped Blocks in 100 Frames (1 I, 99 P)                     | 69 |

| 5.1  | Comparison of SAD Implementation on Different Platforms                | 80 |

| 5.2  | Comparison of Computational Complexity for 8-point IDCT                | 81 |

| 5.3  | Test of Compliance for Modified IEEE Std. 1180-1190 in MPEG-4          | 83 |

| 5.4  | Comparison of IDCT on Different Platforms [10]                         | 85 |

| 5.5  | Comparison of DCT on Different Platforms [10]                          | 86 |

| 5.6  | Fixed-Point Quantization Table                                         | 88 |

| 5.7  | Effects on Quality and Bit-Rate of Different QP values                 | 89 |

| 5.8  | Execution Time of Motion Estimation for 1 P-VOP of QCIF on ISS         | 90 |

| 5.9  | Execution Time of Shape Coding for 1 P-VOP of QCIF on ISS              | 91 |

| 5.10 | Execution Time of P-VOP Motion Estimation and Shape Coding after       |    |

|      | Optimization on PACDSP                                                 | 92 |

| 5.11 | Code Size Profile of Object-Based MPEG-4 Video Encoder on PACDSP .     | 94 |

| 5.12 | Frame Rate Estimation of Single-Core Implementation                    | 94 |

| 5.13 | Frame Rate Estimation for Intra Encoding of Dual-Core Implementation . | 96 |

| 5.14 | Frame Rate Estimation for Inter Encoding of Dual-Core Implementation . | 97 |

## Chapter 1

#### Introduction

In modern days, compression of audio-visual information has become commonplace. It is especially important for applications on mobile devices. Digital signal processors (DSPs) are typically used on these mobile devices for various signal processing functions. The present study concerns of an MPEG-4 video encoder on a dual-core platform which contains an ARM core and a PACDSP core.

The MPEG-4 standard for coding of audio-visual information has been widely adopted in various consumer products. Many compression tools are defined in the MPEG-4 standards, and they can be used in various environment to achieve desired tradeoff between performance and complexity. In this work, we implement the object-based part (with arbitrary binary shape) of the MPEG-4 encoder, employing the tools in simple profile without error-resilience.

PACDSP is a high performance, low cost VLIW (Very Long Instruction Word) DSP for multimedia applications [2]. Optimized architecture for data stream applications gives a strong reason for system designers to use PACDSP to implement media codecs. The instruction set architecture (ISA) of PACDSP is optimized for audio and video applications, so PACDSP is suitable for products with multi-standard codec requirement. In addition, the low power design for PACDSP makes it possible to use PACDSP on portable devices.

In our dual-core implementation in the best case, we can encode the MPEG-4 video data at 33 and 43 frames per second in QCIF size for intra and inter encodings, respectively.

This thesis is organized as follows. Chapter 2 gives an overview of the MPEG-4 standard. Chapter 3 introduces the architecture and specification of the PACDSP3.0 platform. Chapter 4 discusses the dual core development and the overall system design of our implementation. It is also discusses the algorithm analysis of MPEG-4 video encoder. Chapter 5 considers the architecture optimization technologies and their experiment results. We also compare our implementation with that of other processors and show the performance of the dual-core implementation. Finally, we give some conclusions in chapter 6 and list some potential future works.

## Chapter 2

# Overview of the MPEG-4 Video Standard

The contents of this chapter have been taken to a large extent from [4]-[7].

The MPEG-4 video standard provides core technologies allowing efficient storage, transmission and manipulation of video data in multimedia applications. It provides technologies to view, access and manipulate objects, with great error robustness at a large range of bit rates. The video work in MPEG-4 aimed at providing solutions in the form of tools and algorithms that enabled functionalities such as efficient compression, object scalability, spatial and temporal scalability, error resilience, and fine granularity scalability.

1111111

#### 2.1 Structure of MPEG-4 Video Data

An input video sequence can be defined as a sequence of frames or pictures, separated in time. MPEG-4 divides a frame into a number of video object planes (VOPs). A succession of VOPs is termed a video object (VO). Fig. 2.1 shows the decomposition of a picture into a number of separate VOPs. Each VO is encoded separately and multiplexed to form a bitstream that can be accessed and manipulated. The encoder sends, together with VOs, information about scene composition to indicate where and when VOPs of a VO are to be displayed. Fig. 2.2 shows the organization of the coded MPEG-4 video data in a top-down

Figure 2.1: Segmentation of a frame into VOPs (from [5]).

Figure 2.2: Structure of coded video data (from [6]).

hierarchical structure. The various structural levels are explained below.

- 1. VideoSession (VS): A video session is the highest syntactic structure of the coded visual bitstream and simply consists of an ordered collection of video objects.

- VideoObject (VO): A video object represents a complete scene or a portion of a scene with a semantic. In the simplest case this can be a rectangular frame, or it can be an arbitrarily shaped object corresponding to a physical object or background of the scene.

- 3. VideoObjectLayer (VOL): Each video object can be encoded in scalable (multi-layer) or non-scalable (single layer) form, depending on the application, represented by VOL. The VOL provides support for scalable coding. A video object can be encoded using spatial or temporal scalability, going from coarse to fine resolution.

- 4. GroupOfVideoObjectPlanes (GOV): Group of video object planes are optional entities. The GOV groups video object planes together. GOVs can provide points in the bitstream where VOPs are encoded independently from one another, and can thus provide random access points into the bitstream.

- 5. VideoObjectPlane (VOP): A VOP is a time sample of a video object.

As in MPEG-4 standard, there are four types of VOP, as illustrated in Fig. 2.3. These are briefly explained below:

- 1. An intra-coded (I) VOP is coded using information only from itself.

- 2. A predictive-coded (P) VOP is a VOP which is coded using motion-compensated prediction from a past reference VOP.

- 3. A bidirectionally predictive-coded (B) VOP is a VOP which is coded using motion-compensated prediction from a past and/or future reference VOP(s).

- 4. A sprite (S) VOP is a VOP for a sprite object or a VOP that is coded using prediction based on global motion compensation from a past reference VOP. We omit further introduction of the S VOP.

Figure 2.3: Types of VOP.

Figure 2.4: Positions of luminance and chrominance samples in 4:2:0 data (from [7]).

The macroblock (MB) is a basic coding structure constructing VOP. An MB contains a section of the luminance component of  $16 \times 16$  pixels in size and the corresponding sub-sampled chrominance components in 4:2:0 format. The luminance and chrominance samples are positioned as shown in Fig. 2.4. In this format, an MB is divided into 4 luminance blocks and 2 chrominance blocks, each  $8 \times 8$  pixels in size.

#### 2.2 MPEG-4 Video Texture Coding

The contents of this section have been taken to a large extent from [4]–[7].

Figure 2.5: Structure of VO encoder (from [5]).

Fig. 2.5 presents the structure of the VO encoder. The encoder is mainly composed of three parts: shape encoder, motion encoder and texture coder. The reconstructed VOP is obtained by combining the shape, texture and motion information. The part of shape coding constitutes the major difference between object-based and frame-based coding.

#### 2.2.1 VOP Formation

The video object shape information is obtained after segmentation. The shape information is hereafter referred to as alpha plane, which is used to form a VOP. There are two kinds of alpha planes in MPEG-4, binary alpha plane and gray scale alpha plane. For the binary alpha plane, the value 255 is assigned to pixels belonging to the objects and 0 is assigned to pixels outside the objects. The value of gray scale alpha plane is used for hybrid (of natural and synthetic) scenes generated by blue screen composition and is represented by an 8-bit component.

For the binary alpha plane, a rectangular bounding box enclosing the shape to be coded is formed such that its horizontal and vertical dimensions are extended to multiples of 16 pixels (MB size). For efficient coding, it is important to minimize the number of

Figure 2.6: A VOP in bounding box (from [5]).

macroblocks contained in the bounding box. Fig. 2.6 shows an example of an arbitrary shape VOP with bounding box and the MB structure.

#### 2.2.2 Shape Coding

After VOP formation, the alpha plane of VOP will be coded prior to coding motion vector and texture based on the VOP bounding box. Binary alpha planes are encoded by modified context-based arithmetic encoding (CAE) while grey scale alpha planes are encoded by motion-compensated discrete cosine transform (DCT) similar to texture coding. The bounded alpha plane is partitioned into blocks of  $16 \times 16$  samples called alpha block and the encoding/decoding process is done per alpha block.

#### **Binary Shape Coding**

CAE and motion compensation are the basic tools for encoding binary alpha blocks (BABs) which are the primary unit in binary shape coding. InterCAE and IntraCAE are the variants of the CAE algorithm used with and without motion compensation, respectively. The motion vectors which are differentially coded can be computed by searching for a best match position. Each BAB is coded in one of the following modes:

1. The block is all transparent. In this case no coding is necessary. Texture information is not coded for such blocks either.

Table 2.1: List of BAB Types (from [4])

| BAB Types | Semantic              | Used in                 |

|-----------|-----------------------|-------------------------|

| 0         | MVDs==0 and No Update | P-, B-, and S(GMC)-VOPs |

| 1         | MVDs!=0 and No Update | P-, B-, and S(GMC)-VOPs |

| 2         | Transparent           | All VOP Types           |

| 3         | Opaque                | All VOP Types           |

| 4         | IntraCAE              | All VOP Types           |

| 5         | MVDs==0 and InterCAE  | P-, B-, and S(GMC)-VOPs |

| 6         | MVDs!=0 and InterCAE  | P-, B-, and S(GMC)-VOPs |

Note: GMC = Global Motion Compensation.

- 2. The block is all opaque. Shape coding is not necessary in this case, but texture information needs to be coded.

- 3. The block is coded using IntraCAE without use of past information.

- 4. Motion vector difference (MVD) is zero but the block is not updated.

- 5. MVD is non-zero, but the block is not updated.

- 6. MVD is zero and the block is updated. InterCAE is used for coding the block update.

- 7. MVD is non-zero, and the block is coded by InterCAE.

Table 2.1 shows the BAB types and the VOP types they are used in.

If the encoder needs rate control and rate reduction, the encoder realizes these through size-conversion of binary alpha information. A 4:1 downsampled binary alpha block is used first. If the shape errors are greater than a designed threshold value, then a 2:1 downsampled binary alpha block is used next. If, again, it is found unacceptable, then an unsubsampled binary alpha block is used.

The MPEG-4 standard allows for 18 coding modes of each BAB: (intra/inter/inter MC)×(horizontal/vertical scanning)×(subsampling factor 0/1/2). The influence of different shape coding modes is not only on coding performance in the sense of coding

Table 2.2: Shape Coding Modes and Their Main Usages (from [4])

| Mode                                               | Main Usages                                                         |

|----------------------------------------------------|---------------------------------------------------------------------|

| Intra                                              | I frames, arbitrarily shaped still texture object, error resilience |

| Inter, inter MC                                    | P frames                                                            |

| Horizontal/vertical scanning                       | Low-bitrate shape coding                                            |

| Subsampling to block size $8\times8$ or $4\times4$ | Low-bitrate lossy shape coding                                      |

efficiency but also on computational complexity. Table 2.2 shows the main usages of each coding mode.

CAE is used to code each binary pixel of the BAB. Prior to coding the first pixel, the arithmetic encoder is initialized. Each binary pixel is then encoded in raster order. The process for encoding a given pixel is as follows:

- 1. Compute a context number.

- 2. Index a probability table using the context number.

- 3. Use the indexed probability to drive an arithmetic encoder.

When the final pixel has been processed, the arithmetic code is terminated. Fig. 2.7 shows the templates for the context calculation in INTRA and INTER modes.

#### **Gray Scale Shape Coding**

The gray scale shape coding has a structure similar to that of binary shape with the difference that each pixel can take on a range of values (usually 0 to 255) representing the transparency of that pixel. The pixel value 0 corresponds to a completely transparent pixel and 255 to a completely opaque pixel. Intermediate values of the pixel correspond to intermediate degrees of transparencies of that pixel.

Figure 2.7: Pixel templates used for (a) INTRA and (b) INTER context calculation of BAB. The current pixel to be coded is marked with "?" (from [4]).

#### 2.2.3 Motion Coder

Motion coding is essential for P-VOP and B-VOP to reduce temporal redundancy. The motion coder consists of a motion estimator, motion compensator, previous/next VOPs store and motion vector (MV) predictor and coder. Furthermore, in order to perform the motion prediction for VOP of arbitrary shape, a special padding technique is used for the reference VOP before motion estimation.

#### **Padding Process**

Fig. 2.8 shows a simplified diagram of the padding process. The value of luminance and chrominance samples outside the VOP are defined by the padding process.

A decoded MB d[y][x] is padded by referring to the corresponding decoded shape block s[y][x]. An MB that lies on the VOP boundary is padded by replicating the boundary samples of the VOP towards the exterior. This process is divided into horizontal repetitive padding and vertical repetitive padding. The remaining MBs that are completely outside the VOP are filled by extended padding.

• Horizontal repetitive padding: Each sample at the boundary of a VOP is replicated horizontally to the left and/or right direction in order to fill the transparent region

Figure 2.8: Simplified padding process (from [4]).

Figure 2.9: Priority of boundary MBs surrounding an exterior MB (from [4]).

outside the VOP of a boundary block. If there are two boundary sample values for filling, the two sample values are averaged.

- Vertical repetitive padding: The remaining unfilled transparent region from the above procedure are padded by a similar process as the horizontal repetitive padding but in the vertical direction.

- Extended padding: Exterior MBs immediately next to boundary MBs are filled by replicating the samples at the border of the boundary MBs. If an exterior MBs is next to more than one boundary MBs, one of the MBs is chosen, according to the priority shown in Fig. 2.9. The remaining exterior MBs (not located next to any boundary MBs) are filled with 128.

#### **Motion Estimation**

Motion estimation (ME) is a method of prediction between adjacent frames/pictures. In general, the ME techniques used in MPEG-4 can be seen as an extension of standard MPEG-1/2 or H.263 block matching techniques with modified block (polygon) matching to handle arbitrary-shaped VOPs.

For an arbitrary-shape VOP, the bounded VOP is first extended to the right-bottom side to multiples of MB size. The alpha value of the extended pixels is set to zero. The sum of absolute differences (SAD) is used for error measure, and is computed only for the pixels with nonzero alpha values.

The basic motion estimation may be performed on  $16 \times 16$  luminance MBs. The motion vector is specified to half-pixel accuracy. In many coding software implementations, the motion estimation is performed by full search to integer pixel accuracy vector and, using it as the initial estimate, a half pixel search is performed around it. Interpolation of MB is necessary because the motion vector may be non-integer. Fig. 2.10 illustrates the bilinear interpolation method.

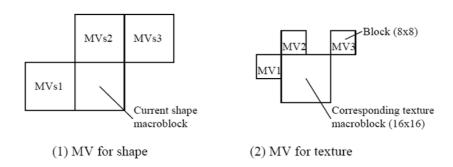

In the MPEG-4 standard, besides motion vector for  $16 \times 16$  MB, motion vector can be sent for individual  $8 \times 8$  blocks to reduce prediction errors more.

Figure 2.10: Bilinear Interpolation for half sample search (from [4]).

#### **Motion Vector Encoder**

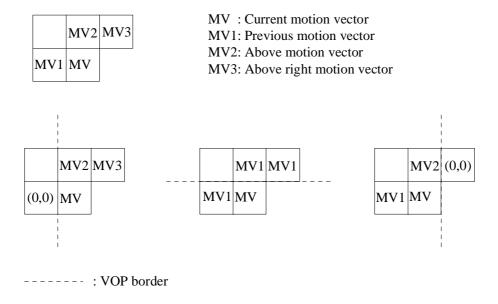

The motion vector (MV) must be coded when using INTER mode coding. Horizontal and vertical motion vectors are coded differentially by using a spatial neighborhood of three motion vectors that have already been coded (see Fig. 2.11). The differential coding of motion vectors is performed with reference to the reconstructed shape. In the special cases at the borders of the current VOP the following decision rules are applied:

- 1. If the MB of one and only one candidate predictor is outside the VOP, it is set to zero.

- 2. If the MBs of two and only two candidate predictors are outside the VOP, they are set to the third candidate predictor.

- 3. If the MBs of all three candidate predictors are outside the VOP, they are set to zero.

For horizontal and vertical components, the median value of the three candidates for the same component is used as predictor, denoted Px and Py, respectively:

$$Px = Median(MV1x, MV2x, MV3x),$$

$Py = Median(MV1y, MV2y, MV3y).$

Then, the differences, MVDx (= MVx - Px) and MVDy (= MVy - Py), are coded by variable-length coding (VLC).

Figure 2.11: Motion vector prediction (from [7]).

#### **Motion Compensation**

The motion compensator uses motion vectors to compute motion compensated prediction block, pred[i][j], from the same reference VOP. In addition to basic motion compensation processing, three alternatives are supported, namely, unrestricted motion compensation, four MV motion compensation and overlapped motion compensation.

For unrestricted motion compensation, the motion vectors are allowed to point outside the decoded area of a reference VOP. The pred[i][j] is defined as follows:

$$xref = \min(\max(xcurr + dx, vhmcsr), xdim + vhmcsr - 1),$$

$yref = \min(\max(ycurr + dy, vvmcsr), ydim + vvmcsr - 1),$

where  $vhmcsr = vop\_horizontal\_mc\_spatial\_ref$ ,  $vvmcsr = vop\_vertical\_mc\_spatial\_ref$ , (ycurr, xcurr) is the coordinate of a sample in the current VOP, (yref, xref) is the coordinate of a sample in the reference VOP, (dy, dx) is the motion vector, and (ydim, xdim) is the dimension of the bounding rectangle of the reference VOP.

One/two/four vectors decision is indicated by the MCBPC codeword and field\_prediction flag for each MB. If one motion vector is transmitted for a certain MB, this is considered four vectors with the same value as the MV. When two field motion vectors are transmitted, each of the four block prediction motion vectors has the value equal to the average of

the field motion vectors (rounded such that all fractional pixel offsets become half pixel offsets). If four vectors are used, each of the motion vectors is used for all pixels in one of the four luminance blocks in the MB.

Overlapped motion compensation is performed when the flag obmc\_disable = 0. Each pixel in an  $8 \times 8$  luminance prediction block is a weighted sum of three prediction values, divided by 8. The creation of each pixel  $\overline{P}(i,j)$ , in an  $8 \times 8$  luminance prediction block is according to :

$$\overline{P}(i,j) = \frac{(p(i+MV_x^0,j+MV_y^0)*H_0(i,j)+p(i+MV_x^1,j+MV_y^1)*H_1(i,j)+p(i+MV_x^2,j+MV_y^2)*H_2(i,j)+4)}{8},$$

where  $(MV_x^0, MV_y^0)$  denotes the motion vector for the current block,  $(MV_x^1, MV_y^1)$  the motion vector of the block above or below,  $(MV_x^2, MV_y^2)$  the motion vector of the block to the left or to the right, and  $H_0(i,j)$ ,  $H_1(i,j)$ , and  $H_2(i,j)$  are the weighting value of each pixel in the current block and neighbor blocks.

Since the VOP may be coded in P or B mode, there are three types of motion prediction, namely forward mode, backward mode, and bi-directional mode. The different modes make different predictions  $\bar{P}(i,j)$  as follows.

- 1. Forward mode: Only the forward vector (MVFx,MVFy) is applied in this mode. The prediction blocks  $\bar{P}_y(i,j)$ ,  $\bar{P}_u(i,j)$ ,  $\bar{P}_v(i,j)$  are generated from the forward reference VOP.

- 2. Backward mode: Only the backward vector (MVBx,MVBy) is applied. The prediction blocks  $\bar{P}_y(i,j)$ ,  $\bar{P}_u(i,j)$ ,  $\bar{P}_v(i,j)$  are generated from the backward reference VOP.

- 3. Bi-directional mode: Both the forward vector (MVFx,MVFy) and the backward vector (MVBx,MVBy) are applied. The prediction blocks  $\bar{P}_y(i,j)$ ,  $\bar{P}_u(i,j)$ ,  $\bar{P}_v(i,j)$  are generated from the forward and the backward reference VOPs by doing the forward and the backward predictions and then averaging both predictions pixel by pixel.

#### 2.2.4 Texture Coder

The texture information of a VOP is present in the luminance Y and two chrominance components Cb and Cr of the video signal. For a I-VOP the coded texture information represents the values of the luminance and chrominance components directly. A P-VOP or a B-VOP, the texture information represents the residual values remaining after motion-compensated prediction. The texture coder includes padding process (for object-based coding, and applied only if needed),  $8 \times 8$  two-dimensional (2D) DCT, quantization, coefficient prediction, coefficient scan and variable length coding (VLC).

#### **Padding Process**

When the shape of the VOP is arbitrary, two types of MB exits, those that lie inside the VOP and those that lie on the boundary of the VOP. The MBs that lie completely inside the VOP are coded using a technique identical to the technique used in H.263. The MBs that lie on the boundary of the shape need to be padded before texture coding. For residual error blocks after motion compensation, the region outside the VOP within the blocks are padded with zero. For intra blocks, the padding is performed in a three-step procedure called low pass extrapolation (LPE). This procedure is as follows:

1. Compute the arithmetic mean value m of the pixels f(i,j) in the blocks that belong to the VOP as

$$m = (1/N) \sum_{(i,j) \in VOP} f(i,j)$$

where N is the number of pixels situated in the VOP.

- 2. Assign m to each block pixel situated outside the VOP region.

- 3. Apply the following filtering operation to each block pixel f(i, j) outside the VOP region, in raster-scan order:

$$f(i,j) = \frac{f(i,j-1) + f(i-1,j) + f(i,j+1) + f(i+1,j)}{4}.$$

If one or more of the four pixels used for filtering are outside the block, the corresponding pixels are not included into the filtering operation and the divisor 4 is reduced accordingly.

#### **Discrete Cosine Transform (DCT) Coding**

Similar to MPEG-1 and MPEG-2, the transform coding in the MPEG-4 standard is based on 2D 8×8 DCT. Before quantization, the encoder does forward transform. After the inverse quantization, encoder does inverse transform for reconstructing the VOP.

#### Quantization

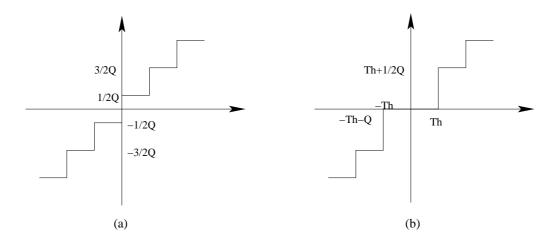

MPEG-4 video supports two quantization techniques, one referred to as the H.263 quantization method and the other, the MPEG quantization method. The H.263 quantization method has dead zone for intra and inter AC coefficients and has dead zone for intra DC coefficients. The MPEG quantization method is uniform with the default matrix shown in Table 2.3.

Fig. 2.12 shows the quantizer characteristics in H.263. It has uniform quantization for intra DC coefficients and nearly uniform midtread quantization for the inter DC and all AC coefficients. All coefficients in a MB go through the same quantizer step size Q, which can be changed in increments of 2 from 2 to 62 as desired.

Furthermore, in order to provide a higher coding efficiency, Table 2.4 shows a nonlinear scaler which is used for the DC coefficient of 8 × 8 block in MEPG-4 video. Note that the characteristics of nonlinear scaling are different between the luminance and chrominance blocks and depend on the quantizer used for the block.

#### **Intra Prediction**

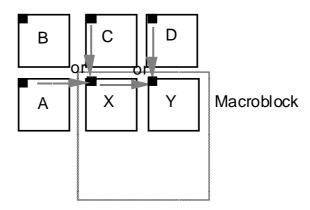

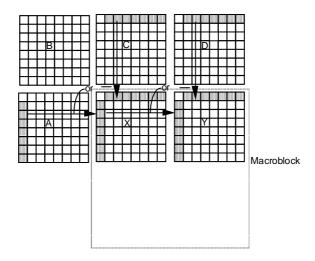

When coding an intra block, the DC coefficients and many AC coefficients are coded by intra prediction. Intra prediction is an operation used in MPEG-4 standards to reduce the spatial redundancy between  $8 \times 8$  blocks.

DC prediction is illustrated in Fig. 2.13. The quantized intra coefficients are predicted with three previous decoded DC coefficients. For example, the DC coefficients of block X is predicted from the DC coefficients of blocks A, B and C. Unlike MPEG-2, the method of prediction in MPEG-4 is gradient based. In computing the prediction of block X, if the absolute value of a horizontal gradient is less than the absolute value of a vertical gradient,

Figure 2.12: Quantizers in H.263. (a) For intra DC coefficient only. (b) For inter DC and all AC coefficients.

Table 2.3: Default Quantization Matrix (Q) [4]

|    |    |    | In | tra |    |    | E  | S  | A  | E  | In |    |    |    |    |

|----|----|----|----|-----|----|----|----|----|----|----|----|----|----|----|----|

| 8  | 16 | 19 | 22 | 26  | 27 | 29 | 34 | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 16 |

| 16 | 16 | 22 | 24 | 27  | 29 | 34 | 37 | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 16 |

|    |    |    |    |     |    |    | 38 |    |    |    |    |    |    |    |    |

| 22 | 22 | 26 | 27 | 29  | 34 | 37 | 40 | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 16 |

| 22 | 26 | 27 | 29 | 32  | 35 | 40 | 48 | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 16 |

| 26 | 27 | 29 | 32 | 35  | 40 | 48 | 58 | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 16 |

| 26 | 27 | 29 | 34 | 38  | 46 | 56 | 69 | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 16 |

| 27 | 29 | 35 | 38 | 46  | 56 | 69 | 83 | 16 | 16 | 16 | 16 | 16 | 16 | 16 | 16 |

Table 2.4: Nonlinear Scaler for DC Coefficients (from [4])

| Component   | D   | C Sca | ler for Q | Range   |

|-------------|-----|-------|-----------|---------|

|             | 1–4 | 5–8   | 9–24      | 25–31   |

| Luminance   | 8   | 2Q    | Q+8       | 2Q - 16 |

| Chrominance | 8   | (Q +  | - 13)/2   | Q - 16  |

Figure 2.13: Prediction of DC coefficients of blocks in an intra MB (from [5]).

then the quantized DC (QDC) of block C is used as the prediction, else the QDC value of block A is used.

The AC prediction depends on DC prediction, as shown in Fig. 2.14. The AC coefficients in the first row or in the first column are predicted with three previous decoded AC coefficients. The direction of prediction is the same as DC prediction.

#### Scan and VLC

1896

Fig. 2.15 shows three kinds of scan, alternate-horizontal, alternate-vertical and zigzag (the normal scan used in H.263 and MPEG-1), to scan the DC and AC coefficients and change the 2D block data to 1D data. The actual scan used depends on the coefficient prediction method used for the block. If the direction is vertical, then alternate-horizontal scan is used. If the direction is horizontal, then alternate-vertical scan is used. For all other blocks, zigzag scanned is used.

The coefficients after scan usually become a sequence with many zeros at the end. This kind of data stream is good for run-length coding. In the MPEG-4 standard, differential DC coefficients in intra blocks are encoded in VLC. However, the AC coefficients are encoded by the variable length codes for EVENTs, where an EVENT consists of a last non-zero coefficient indication (LAST), the number of successive zeros preceding the coded coefficient (RUN), and the non-zero value of the coded coefficient (LEVEL). Some statistically rare events have no VLC words to represent them. For them an escape coding method is used.

Figure 2.14: Prediction of AC coefficients of blocks in an intra MB (from [5]).

| 52       | 53       | 54       | 55       | 60       | 61       | 62       | 63       | 13       | 14       | 29       | 33       | 45       | 49       | 59       | 63       | 35       | 36       | 48       | 49       | 57       | 58       | 62       | 63       |

|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| 36<br>38 | 37<br>39 | 40<br>50 | 41<br>51 | 46<br>56 | 47<br>57 | 48<br>58 | 49<br>59 | 11<br>12 | 16<br>15 | 27<br>28 | 31<br>32 | 43<br>44 | 47<br>48 | 57<br>58 | 61<br>62 | 20<br>21 | 22<br>34 | 33<br>37 | 38<br>47 | 46<br>50 | 51<br>56 | 55<br>59 | 60<br>61 |

| 22       | 23       | 34       | 35       | 42       | 43       | 44       | 45       | 10       | 17       | 26       | 30       | 42       | 46       | 56       | 60       | 10       | 19       | 23       | 32       | 39       | 45       | 52       | 54       |

| 20       | 21       | 24       | 25       | 30       | 31       | 32       | 33       | 3        | 9        | 18       | 25       | 35       | 41       | 51       | 55       | 9        | 11       | 18       | 24       | 31       | 40       | 44       | 53       |

| 6        | 7        | 19       | 18       | 26       | 27       | 28       | 29       | 2        | 8        | 19       | 24       | 34       | 40       | 50       | 54       | 3        | 8        | 12       | 17       | 25       | 30       | 41       | 43       |

| 4        | 5        | 8        | 9        | 17       | 16       | 15       | 14       | 1        | 5        | 7        | 21       | 23       | 37       | 39       | 53       | 2        | 4        | 7        | 13       | 16       | 26       | 29       | 42       |

| 0        | 1        | 2        | 3        | 10       | 11       | 12       | 13       | 0        | 4        | 6        | 20       | 22       | 36       | 38       | 52       | 0        | 1        | 5        | 6        | 14       | 15       | 27       | 28       |

Figure 2.15: Scans for  $8 \times 8$  blocks (from [4]).

#### 2.2.5 Other Video Coding Tools [5]

In addition to texture video coding, there are some special tools defined in MPEG-4. In this section, we briefly introduce robust video coding and scalable coding.

#### **Robust Video Coding**

Error resilience is a particular concern over wireless networks. In the error resilient mode, the MPEG-4 video offers a number of tools as follows:

#### 1. Object priorities

The object based organization of MPEG-4 video facilitates prioritizing of the semantic objects based on their relevance. Further, the VOP types lend themselves

to a form of automatic prioritization. In particular, B-VOPs are noncausal and do not contribute to error propagation and thus can be transmitted at a lower priority or discarded in case of severe errors.

#### 2. Resynchronization

The encoder can enhance error resilience by placing resynchronization (resync) markers in the bitstream with approximately constant spacing, such as the beginning of each MB.

#### 3. Data partitioning

Data partitioning provides a mechanism to increase error resilience by separating the normal motion and texture data of all MBs in a video packet and send all the motion data first, followed by a motion marker, followed by all the texture data.

#### 4. Reversible VLCs

The reversible VLCs offer a mechanism for a decoder to recover additional texture data in the presence of errors since the special design of reversible VLCs enables decoding of codewords in both the forward (normal) and the reverse directions.

#### 5. Intra update and scalable coding

To prevent error propagation, intra update is a simple method to reduce the problem. However, more intra coding will reduce the coding efficiency. Another method is scalable coding, which can prevent error propagation without more intra coding.

#### **Scalable Coding**

The scalability tools in MPEG-4 video are designed to support applications beyond that supported by single layer video, such as internet video, wireless video, multi-quality video services, video database browsing, etc. In scalable video coding, it is assumed that given a coded bitstream, decoders of various complexities can decode and display appropriate reproductions of coded video.

Several different forms of scalability are provided in MPEG-4 video. Temporal and spatial scalability are the most basic scalability tools among them. The Fine Granularity Scalability (FGS) supports continuous scalability of bit rate and video quality.

#### 2.3 Profiles and Levels [4]

Although there are many tools in the MPEG-4 standard, not every MPEG-4 decoder will have to implement all of them. Similar to MPEG-2, profiles and levels are defined as subsets of the entire bitstreams syntax of all the tools. The purpose of defining conformance points in the form of profiles and levels is to facilitate interchange of bitstreams among different applications. There are eight profiles defined in MPEG-4: simple, core, main, simple scalable, animated & mesh, basic animated texture, still scalable texture and simple face. The details are given in Table 2.5.

Compared with previous standards, the simple profile of MPEG-4 is similar to the coding method in H.263. The difference is that the simple profile has error resilience but does not have B-frame coding. The simple scalable profile is the same as simple profile, but with rectangular scalability added. The core profile is the profile with all tools of the simple profile, temporal scalability, B-VOP coding and binary shape coding. The main profile is the profile with all tools in core profile, gray shape coding, interlace and sprite coding. The other profiles are for particular purposes, such as 2D dynamic mesh coding and facial animation coding.

Table 2.5: Profiles and Tools in MPEG-4 Video (from [4])

| 14010 2.0                  | Simple | Core  | Main | Simple    | Animated | Basic    | Still    | Simple |

|----------------------------|--------|-------|------|-----------|----------|----------|----------|--------|

| Tools                      |        | - 3.0 |      | Scalable  | 2D Mesh  | Animated | Scalable | Face   |

|                            |        |       |      |           |          | Texture  | Texture  | 1      |

| Basic                      |        |       |      |           |          |          |          |        |

| 1. I VOP                   |        |       |      |           |          |          |          |        |

| 2. P VOP                   | v      | v     | V    | v         | v        |          |          |        |

| 3. AC/DC Prediction        | ,      | ,     | ·    | ,         | ,        |          |          |        |

| 4. 4MV Unrestricted MV     |        |       |      |           |          |          |          |        |

| Error resilience           |        |       |      |           |          |          |          |        |

| 1. Slice Resynchronization | v      | v     | V    | v         | V        |          |          |        |

| 2. Data Partitioning       | ,      | ·     | ,    | ,         | ,        |          |          |        |

| 3. Reversible VLC          |        |       |      |           |          |          |          |        |

| Short Header               | V      | V     | V    |           | V        |          |          |        |

| B-VOP                      | ,      | V     | V    | v         | V        |          |          |        |

| Method 1/Method 2          |        | V     | V    |           | V        |          |          |        |

| quantization               |        |       | اا   | FISA      | / IE     |          |          |        |

| P-VOP based                |        |       |      |           | 216      |          |          |        |

| temporal scalability       |        |       |      |           | 8 IE     |          |          |        |

| 1. Rectangular             |        | v     | V    |           |          |          |          |        |

| 2. Arbitrary Shape         |        |       | ス    | 1896      |          |          |          |        |

| Binary Shape               |        | V     | V    |           | V        |          |          |        |

|                            |        | V     | V    |           | V        |          |          |        |

| Gray Shape                 |        |       | V    | I I I I I |          |          |          |        |

| Interlace                  |        |       |      |           |          |          |          |        |

| Sprite                     |        |       | V    | ***       |          |          |          |        |

| Temporal scalability       |        |       |      | V         |          |          |          |        |

| (rectangular)              |        |       |      |           |          |          |          |        |

| Spatial scalability        |        |       |      | V         |          |          |          |        |

| (rectangular)              |        |       |      |           | _        |          |          |        |

| Scalable still             |        |       |      |           | V        | V        | V        |        |

| texture                    |        |       |      |           |          |          |          |        |

| 2D dynamic mesh            |        |       |      |           | V        | V        |          |        |

| with uniform topology      |        |       |      |           |          |          |          |        |

| 2D dynamic mesh            |        |       |      |           | V        |          |          |        |

| with Delaunay topology     |        |       |      |           |          |          |          |        |

| Facial animation           |        |       |      |           |          |          |          | V      |

| parameters                 |        |       |      |           |          |          |          |        |

# Chapter 3

# **Overview of PACDSP**

The contents of this chapter have been taken to a large extent from [2]–[3].

## 3.1 Introduction

Programmable embedded solutions are attractive for their lower development efforts, upgradeability to support new applications and easier maintenance. These factors reduce time-to-market and extend time-in-market, and thus make the best profit-sense. Today's media processing demands extremely high computations with real-time constraints in audio, image or video applications. Instruction parallelism has been exploited to speed up the high-performance microprocessors, and VLIW machines have low-cost compiler scheduling with deterministic execution time and have thus become the trend of high performance DSP processors.

Conventional VLIW processors have poor code density, because the unused instruction slots must be filled by NOPs. Variable-length VLIW instruction packet eliminates NOPs by run-time instruction dispatch, unlike the conventional position-coded VLIW processors where each functional unit (FU) has a corresponding bit-field in the instruction packet. Indirect VLIW has an internal instruction buffer for the VLIW instruction packets. With this instruction buffer and the pre-fetch scheme, the VLIW processor can reduce instruction memory bandwidth requirement and power consumption of instruction fetches.

The complexity of the register file (RF) grows exponentially as more and more FUs are integrated on a chip and operate concurrently to achieve the performance requirements. Thus the RF is frequently partitioned into execution clusters with explicit interconnection networks among the clusters to significantly reduce the complexity at the cost of small performance penalty.

For high performance, the PACDSP is a VLIW processor with a single instruction multiple-data (SIMD) instruction set architecture (ISA). The software supported scheduling reduces hardware complexity and power consumption. Variable-length instruction and instruction packet solve the poor code density problem of the conventional VLIW architecture. Another feature of the PACDSP, cluster architecture, reduces not only ports and entries of the register files but also the power consumption of read/write operations.

Other key features of the PACDSP include the following:

- Scalable VLIW datapath for easy extension of the computing power.

- Heterogeneous register files for more straightforward operations, less port number and smaller entries in each RF to improve the performance and reduce power and area.

- Constant register file in each cluster for the storage of fixed data used in the applications to reduce the frequency of data movement which may cost significant power consumption.

- Inter-cluster communication by memory controller for reusing hardware resource and reducing the port number of ping-pong RF in order to reduce power and area and to increase the scalability.

- Optimized interrupt design with fast interrupt response time with hardware-supported context switch to reduce the processing time of interrupt service routine (ISR).

- Hierarchical encoding scheme reducing the dependency between instructions and packets to reduce area and latency of the dispatch unit.

- Dynamic power management for power saving.

• Customized FU interface that can be used to enhance DSP functionalities.

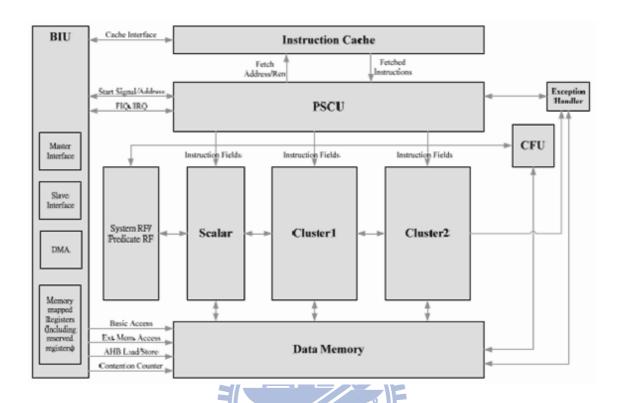

The architecture of the PACDSP v3.0 is shown in Fig. 3.1. The following sections will briefly introduce its pipeline stages and its core elements, including the Program Sequence Control Unit (PSCU), Scalar Unit, Clusters (VLIW Data path), and Customized Function Unit (CFU). Accelerators can be added via the CFU which can execute in different threads and synchronize the execution results through the scalar unit to enhance the computation power of the VLIW data path.

# 3.2 ISA and Pipeline Stages

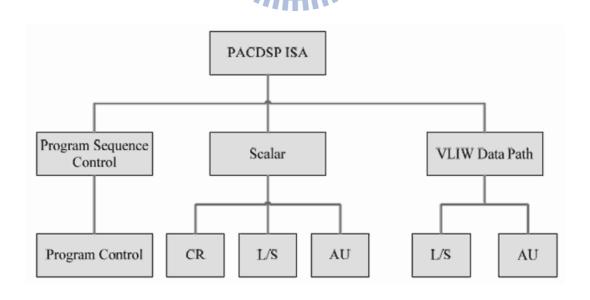

There are three major divisions in the PACDSP instruction set architecture (ISA): Program Sequence Control Unit, Scalar Unit and VLIW Data path. In each division, the instructions are divided into categories by function units. Fig. 3.2 depicts the ISA of the PACDSP.

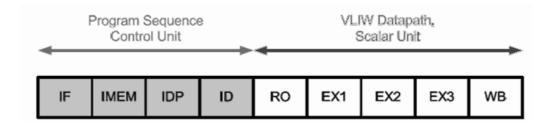

Fig. 3.3 shows the pipeline stages of PACDSP. The program sequence control unit operation can be divided into four stages, which are IF, IMEM, IDP, and ID. Scalar unit and VLIW data path operations are both divided into five stages, namely RO, EX1, EX2, EX3, and WB. The job of each pipeline stage is shown in Table 3.1.

# 3.3 Program Sequence Control Unit

The program sequence control unit (PSCU) is a main component in the DSP kernel. Basically, we can regard it as the combination of the control path and the instruction path. The control path effects the program counter updating, address fetch, pipeline control, hardware context shadowing, interrupt handling, exception handling, etc., according to the input control signals from elsewhere in the PACDSP. The instruction path is responsible for fetching, dispatching, and decoding of the instruction packets.

Figure 3.1: Architecture of the PACDSP [1].

Figure 3.2: PACDSP instruction set architecture [3].

Figure 3.3: Pipeline stages of the PACDSP [3].

Table 3.1: Pipeline Stages and Their Jobs [3]

| Stage | Job                       |  |

|-------|---------------------------|--|

| IF    | Instruction Fetch         |  |

| IMEM  | Instruction Memory Access |  |

| IDP   | Instruction Dispatch      |  |

| ID    | Instruction Decode        |  |

| RO    | Read Operand              |  |

| EX1   | Execution One             |  |

| EX2   | Execution Two             |  |

| EX3   | Execution Three           |  |

| WB    | Write Back                |  |

|       |                           |  |

#### 3.3.1 Branch Instructions

Branch instructions can be grouped into two categories, conditional branches and unconditional branches. There are three addressing modes defined in the PACDSP v3.0 for generating the branch target address:

THE PARTY OF THE P

#### • PC-relative

Add up to 32-bit signed immediate offset to the address in the PC register, and take the result as the branch target address, i.e.,

$$TA = PC + OFFSET$$

where TA is the target address, PC is the address in the Program Counter, and OFFSET is the immediate value defined in the branch instruction.

#### • Register

Take the value in the register as the target address, i.e.,

$$TA = Rs$$

where TA is the target address and Rs is the source register defined in the branch instruction.

#### • Register-relative

Add up to 32-bit signed immediate offset to the address saved in the register and take the result as the branch target address, i.e.,

$$TA = Rs + OFFSET$$

where TA is the target address, Rs is the source register defined in the branch instruction, and OFFSET is the immediate value defined in the branch instruction.

In some circumstances, a branch operation may need to save the return address to ensure correct working of the program when it returns. The branch instructions defined in the PACDSP support saving of the return address into the assigned register. The programmer should take care of the return addresses of nested loops. There are five branch delay slots in the PACDSP, and the programmer could put the branch-independent instructions in the delay slots for time efficiency. There are some constraints about instructions in the delay slots. Reference [3] gives details of the programming constraints.

#### **3.3.2** Loops

The programmer can use the LBCB or B instruction to describe program loops. LBCB is similar to branch, but instead of checking a predicate register (P0–P15), it checks a general purpose register (R0–R15) to decide whether to branch or not. There are 16 general purpose registers (R0–R15), hence up to 16 levels of nested loop can be supported with the use of the LBCB instruction.

A constraint in using LBCB to control a nested loop is that the outer loop should fully contain the inner loop. No exception will be generated if the constraint is violated, but the program behavior may be different from expectation. However, conditional branches can be used inside the nested loop to implement some special branch behaviors in higher level languages, for example, "break" and "continue" in C.

#### 3.3.3 Customized Function Units (CFUs)

The PACDSP provides Customized Function Unit Interface for extension use. The user can attach co-processors or customized function units to PACDSP and handle them through the scalar instructions. If an error happens in a customized function unit, it can inform the PACDSP and the PACDSP can process it based on the particular configuration. If the coprocessor's work is finished successfully, the PACDSP can use its results for further work. It is recommended that if a coprocessor is used, communication with it be made through this interface, or the user will have to pay much more effort to handle it.

## 3.3.4 Exception Handling

Unpredictable exceptions may occur during program execution. The exceptions need to be handled correctly for correct execution results. Exceptions may be caused by hardware (e.g., overflow), software, internal (e.g., undefined instruction), or external (e.g., coprocessor exception). When an exception happens whether PACDSP is running a program or not, PACDSP will check for mask information. If the exception is masked, PACDSP will ignore the exception and return to normal execution. If the exception is unmasked, it will be taken. PACDSP will freeze its pipeline, finish the instructions before the PC which introduced the exception, and recover the states for consistence. After the state is recovered, PACDSP will issue the exception handling interrupt service routine (ISR) to inform the MPU and the Embedded in circuit emulator (ICE), waiting for different commands to resolve the exception.

#### 3.3.5 Interrupt Handling

Two types of interrupt are supported by the PACDSP. One is fast interrupt request (FIQ), which has the higher priority, and the second is interrupt request (IRQ). The difference between them is that the FIQ has a fixed ISR address and the IRQ needs the ISR to check the IRQ source to obtain the proper ISR address.

In the PACDSP, the minimum latency from interrupt request to the first ISR instruction to be executed is 4 cycles for both types of interrupt, and it may be postponed when the ISR experiences cache miss.

#### 3.4 Scalar Unit

The scalar unit plays an important role in handling control-based tasks for PACDSP. It also has a simple capacity for data computing. Thus, the scalar unit is like a reduced instruction set computer (RISC) machine. Programmers can exploit computing capacity of the scalar unit to increase overall instruction-level parallelism (ILP) in compute-based task.

The scalar unit mainly consists of one adder, one down-counter, one comparator, one shifter and one logical arithmetic-logic unit ALU. The scalar unit has four major functions as follows:

- Program flow control.

- Data processing.

- Memory access.

- Data transfer.

## 3.4.1 General Purpose Scalar Register File

In the scalar unit of the PACDSP kernel, there are sixteen 32-bit general purpose registers named R0 to R15. These registers function as the loop boundary counter, the timer and

the address register in the LBCB, WAIT and Branch/Load/Store instructions, respectively. In other instructions, they are viewed as data registers.

#### 3.4.2 System Register and Predication Register

There are 16 system registers named as SR0 to SR15 in PACDSP. Table 3.2 shows the names, the widths, and the meaning of the system registers in PACDSP. Note that the bits in SR0 are used as predication registers and are named P0 to P15, where the value of P0 is always true. Most instructions of PACDSP can be executed conditionally according to the values of the predication registers.

## 3.5 VLIW Datapath

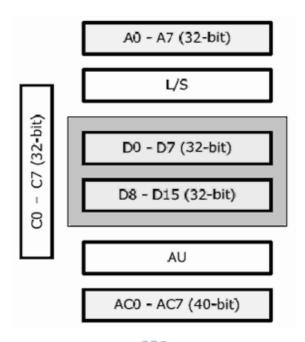

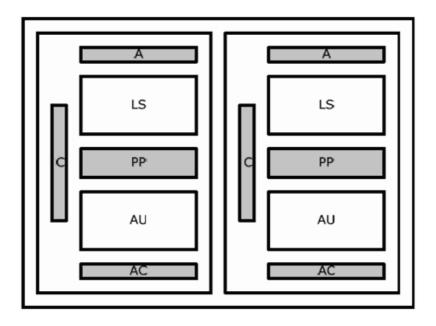

As shown in Fig. 3.4, the VLIW data path of PACDSP is constructed with distributed register file: ping-pong registers, accumulator registers, address registers, constant registers and some control flags.

ALLE TO

If the instruction must write into two consecutive destination registers, for example, DLW and FMUL.D, the destination register number has to be even because of banked structure.

The VLIW data path of PACDSP is constructed in two clusters, and each contains an arithmetic unit (AU) and a load/store unit (L/S) as shown in Fig. 3.5. Therefore, it can execute four instructions simultaneously, and is thus called a four-way VLIW data path. The VLIW data path supports SIMD (single instruction multiple data) operation. It executes in three modes: single (32-bit or 40-bit), dual (16-bit) and quad (8-bit). There are also three types of precision in the data path of PACDSP: full, integer and fractional.

#### **Arithmetic Unit (AU)**

The arithmetic unit comprises 40-bit modules which are divided according to functions. The function types supported by the AU are shown below:

• Arithmetic and comparison instructions.

Table 3.2: System Register File [1]

| No   | Name         | Size(bits) | Note                                       |

|------|--------------|------------|--------------------------------------------|

| SR0  | PREDN        | 16         | Predication information                    |

| SR1  | EN_INT       | 1          | Interrupt enable flag                      |

| SR2  | MSK_EXC      | 16         | Mask inside exception                      |

| SR3  | SWI_EXC      | 16         | Software exception                         |

| SR4  | CF0          | 32         | Custom function register 0                 |

| SR5  | CF1          | 32         | Custom function register 1                 |

| SR6  | CF2          | 32         | Custom function register 2                 |

| SR7  | CF3          | 32         | Custom function register 3                 |

| SR8  | SD_Status    | 8          | Mix information 0's shadow register        |

| SR9  | SD_CPC       | 32         | CPC's shadow register (ISR return address) |

| SR10 | SD_BCTG      | 32         | Branch target's shadow register            |

| SR11 | SD_R0        | 32         | R0's shadow register                       |

| SR12 | Mode         | 4          | Power mode register                        |

| SR13 | CFU_Info_Sel | 4          | CFU_Info select register                   |

| SR14 | EXC_Cause    | 16         | Exception cause                            |

| SR15 | Reserved     | 32         | N.A.                                       |

- Data transfer instructions.

- Bit manipulation instructions.

- Multiplication and accumulation instructions.

- Special instructions.

All data processing instructions in AU begin at the same stage but not finish at the same time due to different computing complexity.

#### **Load/Store Unit (L/S)**

The load/store unit (L/S) comprises 32-bit modules except for one 16-bit address generation unit (AGU) which is used to support the different addressing modes. The functional

Figure 3.4: The VLIW datapath register organization [1].

types supported by L/S are as follows:

- Arithmetic and comparison instructions.

- 1896

- Data transfer instructions.

- Bit manipulation instructions.

- Load and store instructions.

- Special instructions.

Like AU, all instructions in L/S begin at the same stage but not finish at the same time due to different computing complexity.

The L/S unit supports powerful double load/store instructions, which can load or store two operands in one instruction. It also supports instructions that load and store by bytes or half-words. These instructions make memory access easier and more convenient.

Figure 3.5: The four-way VLIW datapath of PACDSP [1].

## 3.5.1 Ping-Pong Register File

The ping-pong register file contains sixteen 32-bit registers which are divided into two groups: D0–D7 and D8–D15. The AU and the L/S units can access the ping-pong register file at the same time but the registers have to be in different groups. In other words, both units cannot read or write the same group simultaneously. All possible access conditions are as follows:

- LS reads D0–D7 and writes D0–D7, and AU reads D8–D15 and writes D8–D15.

- LS reads D0–D7 and writes D8–D15, and AU reads D8–D15 and writes D0–D7.

- LS reads D8–D15 and writes D0–D7, and AU reads D0–D7 and writes D8–D15.

- LS reads D8–D15 and writes D8–D15, and AU reads D0–D7 and writes D0–D7.

## 3.5.2 Address/Accumulator Registers

As shown in Fig. 3.4, the address registers (A0–A7) are all 32-bit and they are dedicated to the load/store (L/S) unit for memory accesses. PACDSP supports several addressing

modes. In modulo addressing mode, A0 and A2 are treated as pointers, A1 and A3 contain base addresses, A4 and A6 contain the values of end address plus one, and A5 and A7 are treated as displacements. So it can support two groups of modulo addressing: (A0,A1,A4,A5) and (A2,A3,A6,A7). In other addressing modes, they can be used as address storage or data processing storage according to the design of the user.

The accumulator registers (AC0–AC7) are 40-bit registers which are dedicated to the arithmetic unit (AU) for data manipulations. The most significant eight bits are guard bits for accumulation operations.

## 3.5.3 Constant Registers

To avoid high frequency of data movement in the register file, PACDSP provides a small constant register file to keep fixed data. The constant register file has eight 32-bit registers (C0–C7). They can be read as either the first operand or the second operand in instructions that use them. But one instruction cannot simultaneously access the constant register file as both of its source operands.

The constant register file can be read by both the AU and the L/S unit but can only be written by the L/S unit. All accesses to the constant register file must be pointed by the control flags CF0 and CF1, which are pointers to the constant registers. And they are calculated from the values contained in CF2 and CF3, which are the contents of the pointers.

## 3.5.4 Status and Control Registers

A status register and a control register are provided to monitor the DSP kernel status and handle the operation mode of the DSP kernel. The program status register records the operation status in each cluster and the scalar unit. It includes Overflow, Negative, and Carry bits, and instructions can only read the status register but not set it. There are several addressing modes supported by PACDSP. The addressing mode control register (AMCR) is a 16-bit register. This register is used to set the addressing mode for each address register. The addressing modes are related to where the operands are to be found

and how the address calculations are to be made. The definitions are shown in Table 3.3.

## 3.5.5 Addressing Modes

PACDSP supports these addressing mode for memory access: linear addressing mode, bit-Reverse addressing Mode, and modulo addressing mode for memory access. They can be altered by setting the AMCR. Table 3.4 shows the syntax of addressing modes that be used and the supporting units in each case.

Fig. 3.6 shows that the address register file A0–A7 is classified into even and odd banks in linear and bit-reversed addressing modes. Some addressing modes use two address registers, RsA and RsB, at the same time. They must be consecutive registers with RsA in the even bank and RsB in the odd bank.

#### **Linear Addressing Mode**

- Offset by immediate (RsA, displacement)

The operand address is the sum of the content of the address register RsA and the displacement (up to 24-bit signed integer, but the value range depends on the implementation of data memory).

- Offset by register (RsA, RsB)

The operand address is the sum of the contents of the address register RsA and the contents of the address register RsB.

- Post-increment by immediate (RsA, displacement+)

Table 3.3: Definitions of AMCR (from [1])

| AM[1] | AM[0] | Addressing Mode |

|-------|-------|-----------------|

| 0     | 0     | Linear          |

| 0     | 1     | Bit-reversed    |

| 1     | 0     | Modulo          |

| 1     | 1     | Reserved        |

Table 3.4: Syntax of Address Modes and Supporting Units [2]

| Addressing Mode                                        | Syntax                       | Suppo         | ort Unit |

|--------------------------------------------------------|------------------------------|---------------|----------|

| 1. Linear                                              |                              | Scalar        | Cluster  |

| Offset by Immediate                                    | RsA, displacement            | V             | V        |

| Offset by Register                                     | RsA, RsB                     | V             | V        |

| Post-increment by Immediate                            | RsA, displacement+           | V             | V        |

| Post-increment by Register                             | RsA, RsB+                    | V             | V        |