國立交通大學

電機資訊學院 電子與光電學程

碩士論文

數位化類比動態測試方法

A Digitalized Dynamic Analogy Test Methodology

研究生：王煌文

指導教授：李崇仁 蘇朝琴 教授

中華民國九十三年七月

數位化類比動態測試方法

A Digitalized Dynamic Analogy Test Methodology

研究 生：王煌文

Student : Huang-Wen Wang

指導 教授：李崇仁

Advisor : Chung-Len Lee

蘇朝琴

Chau-Chin Su

國立交通大學

電機資訊學院 電子與光電學程

碩士論文

A Thesis

Submitted to Degree Program of Electrical Engineering

Computer Science

College of Electrical Engineering and Computer Science

National Chiao Tung University

in Partial Fulfillment of the Requirements

for the Degree of

Master of Science

in

Electronics and Electro-Optical Engineering

July 2004

Hsinchu, Taiwan, Republic of China

中華民國九十三年七月

# 數位化類比動態測試方法

學生：王煌文

指導教授：李崇仁 教授

蘇朝琴 教授

國立交通大學電機資訊學院 電子與光電學程（研究所）碩士班

## 摘要

在本篇論文裏，我們提出一個新的數位化類比動態測試方法，它主要是以 IEEE std. 1149.4 所提出的 DFT 架構為基礎。我們所提出的方法是利用一對比較器去對一個待測的三角波信號取樣，經過統計比較器的輸出結果得到相關的機率，利用機率及統計的觀念分析這些機率值，最後得到待測信號的振幅與偏壓電壓值，經由程式的模擬我們驗證了這個測試方法是可行的。

# A Digitalized Dynamic Analogy Test Methodology

Student: Huang-Wen Wang

Advisors: Prof. Chung-Len Lee

Chau-chin Su

Degree Program of Electrical Engineering Computer Science

National Chiao Tung University

## ABSTRACT

In this thesis, a novel digitalized dynamic analogy test methodology is proposed based on IEEE std. 1149.4 DFT infrastructure. We use the comparator pair to sample the dynamic analogy signal and obtain the amplitude and dc bias by probability and statistical analysis. The experiment results by software simulation confirm the feasibility of the proposed methodology.

## 誌 謝

在交大讀書的這三年期間，我要感謝所有教過我的老師們，謝謝你們的教導。而其中，我最要感謝的是我的指導教授蘇朝琴老師，感謝蘇老師這三年來不斷的指導，使我能順利畢業。而我同時也要感謝我的家人，尤其是我的老婆，謝謝你們在背後支持我，讓我能夠無後顧之憂的致力於學業上。

## 目錄

|                                  |      |

|----------------------------------|------|

| 中文提要                             | I    |

| 英文提要                             | II   |

| 誌謝                               | III  |

| 目錄                               | IV   |

| 表目錄                              | V    |

| 圖目錄                              | VI   |

| 符號說明                             | VIII |

| 一、 緒論                            | 1    |

| 1-1 背景                           | 1    |

| 1-2 提出的測試方法                      | 2    |

| 二、 相關測試方法回顧                      | 4    |

| 2-1 概要                           | 4    |

| 2-2 PMU                          | 4    |

| 2-3 PE Card                      | 6    |

| 2-4 IEEE 1149.4 Internal Testing | 7    |

| 2-5 LCD 驅動 IC                    | 9    |

| 2-6 On-Line 靜態量測技術               | 14   |

| 三、 測試與量測方法                       | 17   |

| 3-1 概要                           | 17   |

| 3-2 系統架構                         | 17   |

| 3-3 公式推導                         | 19   |

| 3-4 計算三角波的振幅 $V_A$ 及偏壓電壓值 $V_X$  | 23   |

| 3-5 雜訊對系統的分析                     | 24   |

| 3-6 參考電壓的選擇                      | 34   |

| 3-7 信賴區間及取樣點數                    | 38   |

| 四、 程式模擬                          | 39   |

| 4-1 概論                           | 39   |

| 4-2 隨機取樣及均勻取樣的模擬                 | 39   |

| 4-3 不同的取樣點數的模擬                   | 43   |

| 4-4 雜訊影響的模擬                      | 47   |

| 4-5 雜訊與取樣點數的關係                   | 51   |

| 五、 結論                            | 56   |

| 參考文獻                             | 57   |

| 簡歷                               | 58   |

## 表目錄

|                  |    |

|------------------|----|

| 表 1 雜訊誤差機率.....  | 30 |

| 表 2 信賴水準的因子..... | 38 |

## 圖目錄

|      |                                                |    |

|------|------------------------------------------------|----|

| 圖 1  | PMU 的架構.....                                   | 5  |

| 圖 2  | PMU 的量測原理.....                                 | 5  |

| 圖 3  | Pin Electronic 電路.....                         | 6  |

| 圖 4  | IEEE std. 1149.4 的架構圖.....                     | 8  |

| 圖 5  | Internal test 電路.....                          | 9  |

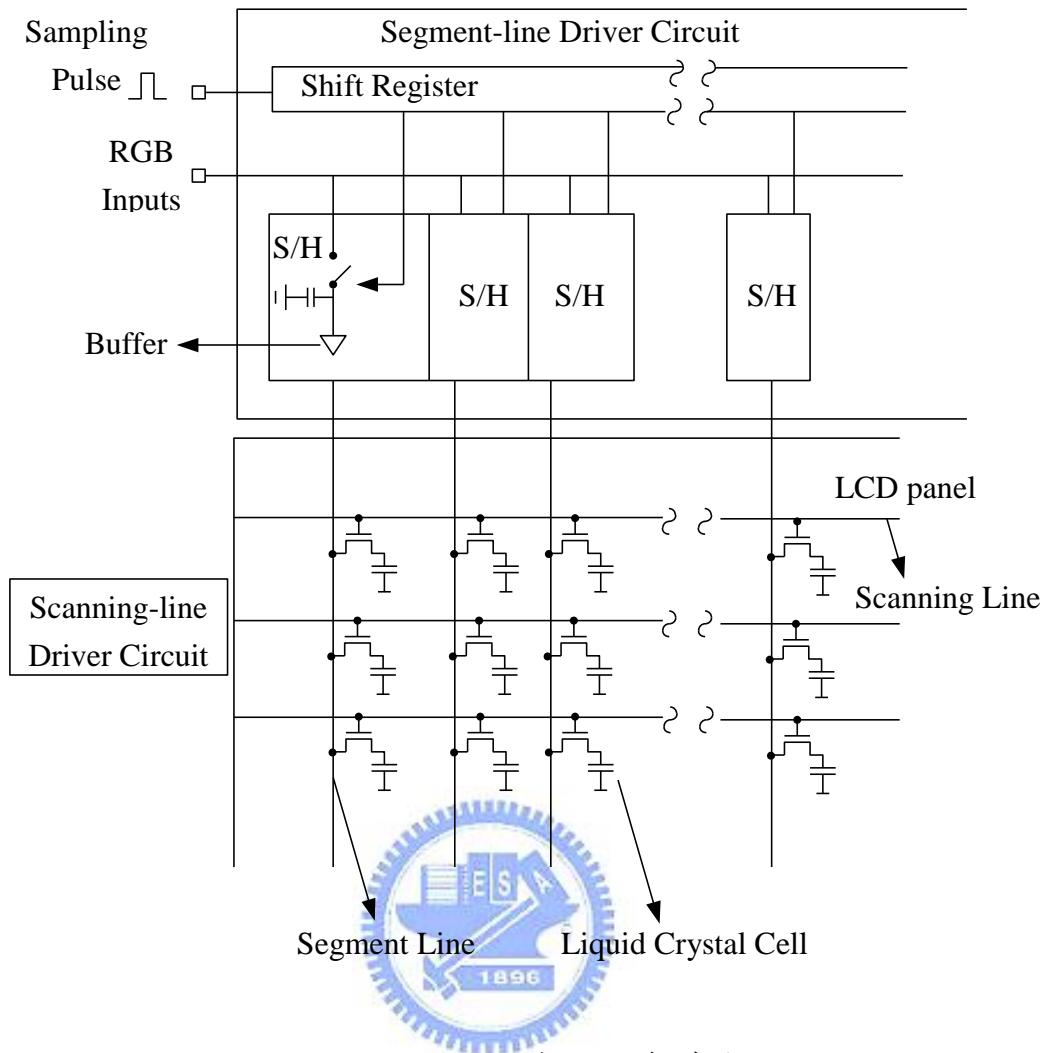

| 圖 6  | LCD 驅動 IC 的架構圖.....                            | 10 |

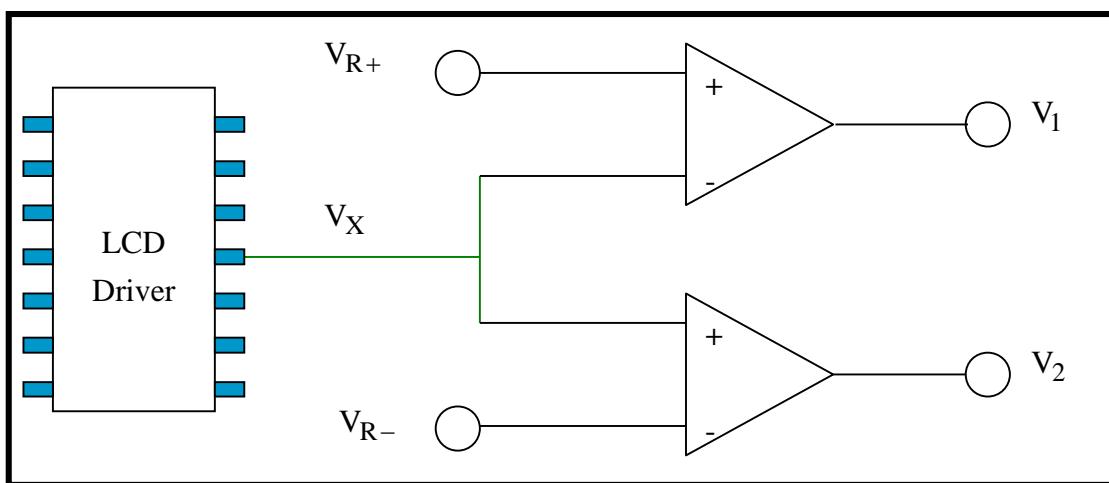

| 圖 7  | LCD 驅動 IC 測試架構圖.....                           | 11 |

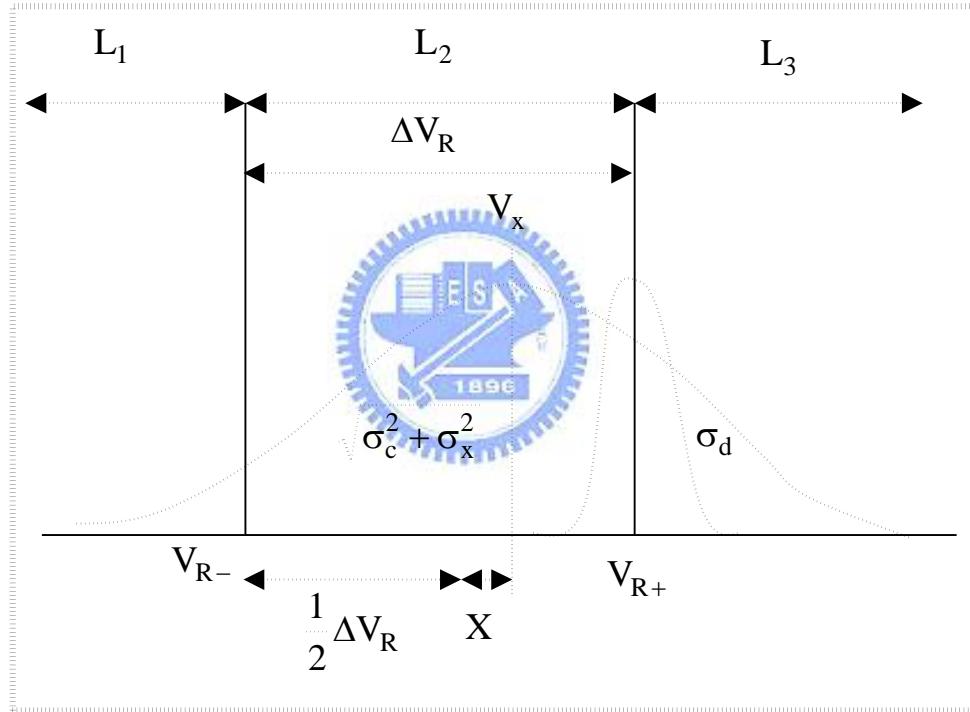

| 圖 8  | 簡化的雜訊模型.....                                   | 12 |

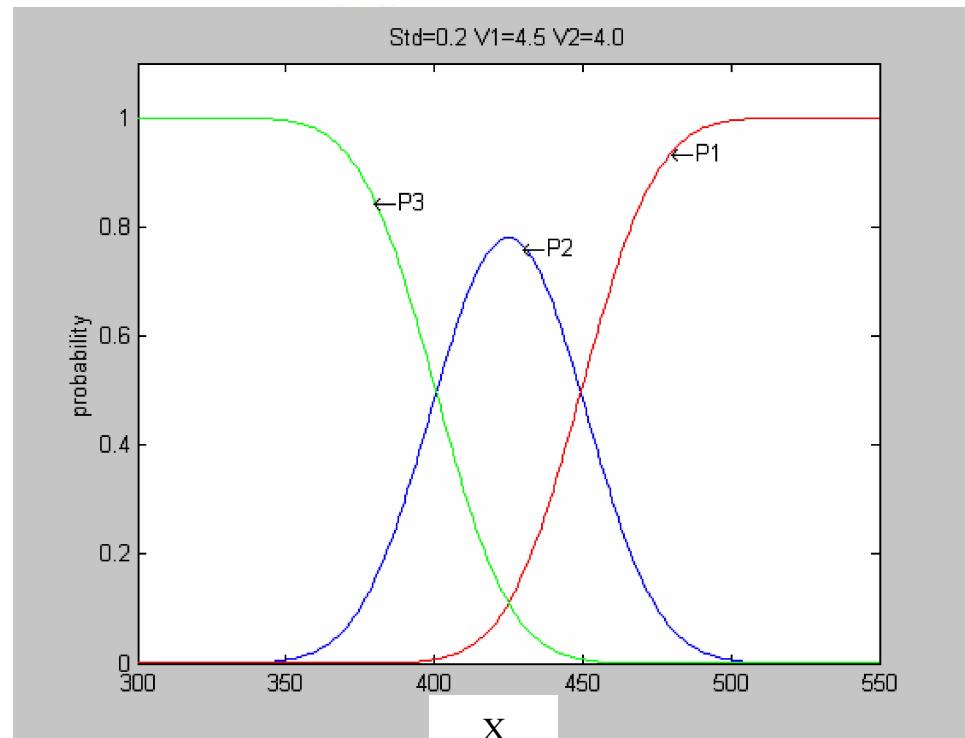

| 圖 9  | $P_{L1}$ , $P_{L2}$ , $P_{L3}$ 與 $X$ 的關係圖..... | 13 |

| 圖 10 | 運算放大器.....                                     | 14 |

| 圖 11 | 靜態監控的主要架構.....                                 | 15 |

| 圖 12 | 簡單的 QSMM 結構.....                               | 16 |

| 圖 13 | BIST 的架構.....                                  | 18 |

| 圖 14 | 簡單的三角波產生器.....                                 | 18 |

| 圖 15 | 整個分析方法的架構.....                                 | 19 |

| 圖 16 | 三角波與參考電壓的關係圖.....                              | 20 |

| 圖 17 | 三個機率的曲線圖.....                                  | 22 |

| 圖 18 | 不同的參考電壓對機率產生的影響.....                           | 23 |

| 圖 19 | 雜訊邊限的示意圖.....                                  | 25 |

| 圖 20 | $L_1 : V < V_{R-} < V_{R+}$ 的雜訊分布圖.....        | 26 |

| 圖 21 | $L_2 : V_{R-} < V < V_{R+}$ 的雜訊分布圖.....        | 27 |

| 圖 22 | $L_3 : V_{R-} < V_{R+} < V$ 的雜訊分布圖.....        | 28 |

| 圖 23 | 誤差機率的曲線.....                                   | 30 |

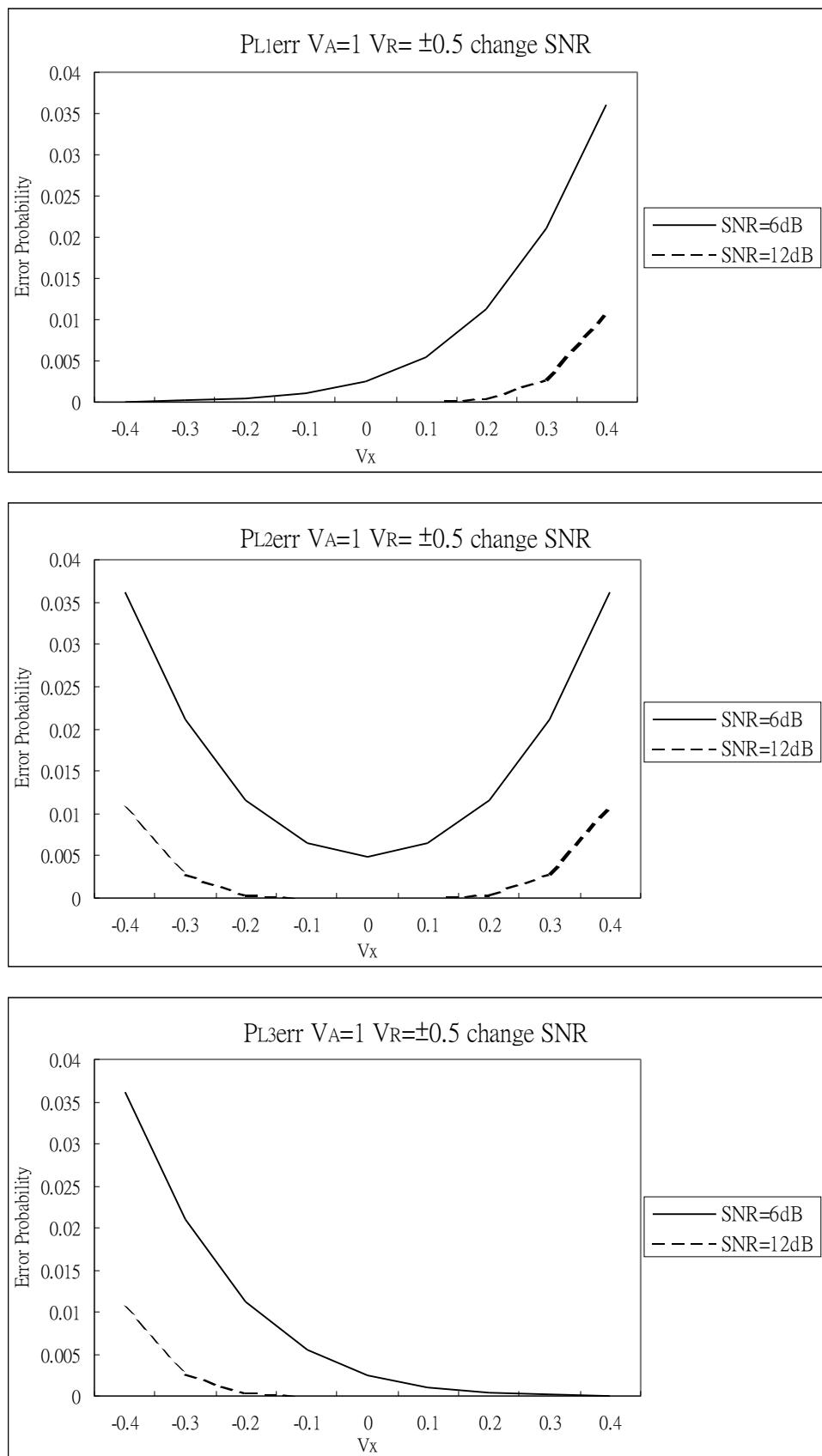

| 圖 24 | 誤差機率的曲線跟參考電壓關係圖.....                           | 31 |

| 圖 25 | 誤差機率的曲線跟雜訊的關係.....                             | 32 |

| 圖 26 | 誤差機率推導與模擬比較結果.....                             | 33 |

| 圖 27 | $P_{L1}$ 的誤差機率圖.....                           | 35 |

| 圖 28 | $P_{L2}$ 的誤差機率圖.....                           | 35 |

| 圖 29 | $P_{L3}$ 的誤差機率圖.....                           | 36 |

| 圖 30 | 不同參考電壓下的誤差圖.....                               | 36 |

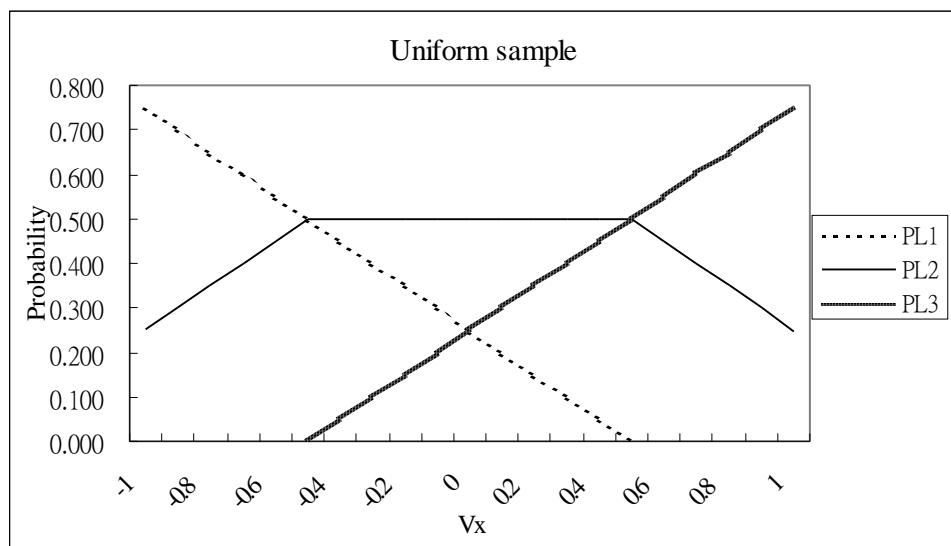

| 圖 31 | 均勻取樣的機率圖.....                                  | 40 |

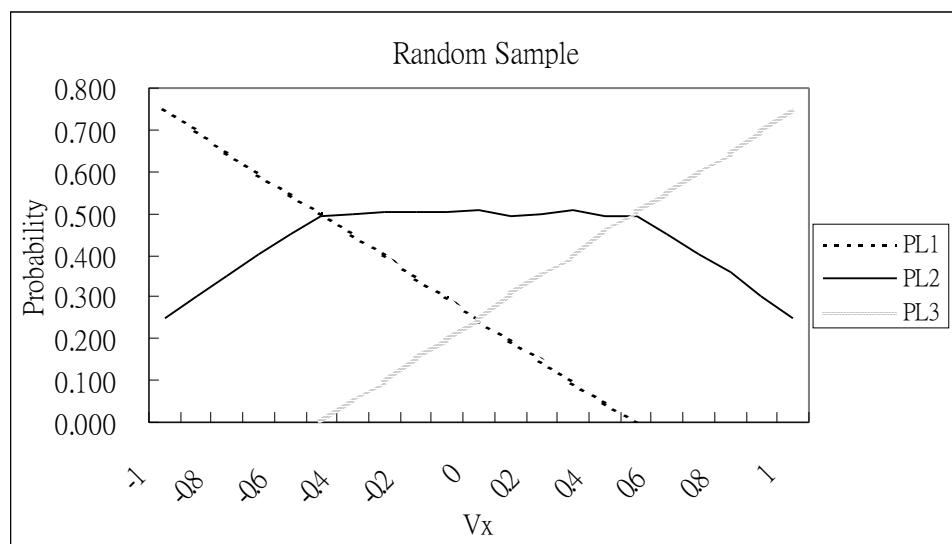

| 圖 32 | 隨機取樣的機率圖.....                                  | 41 |

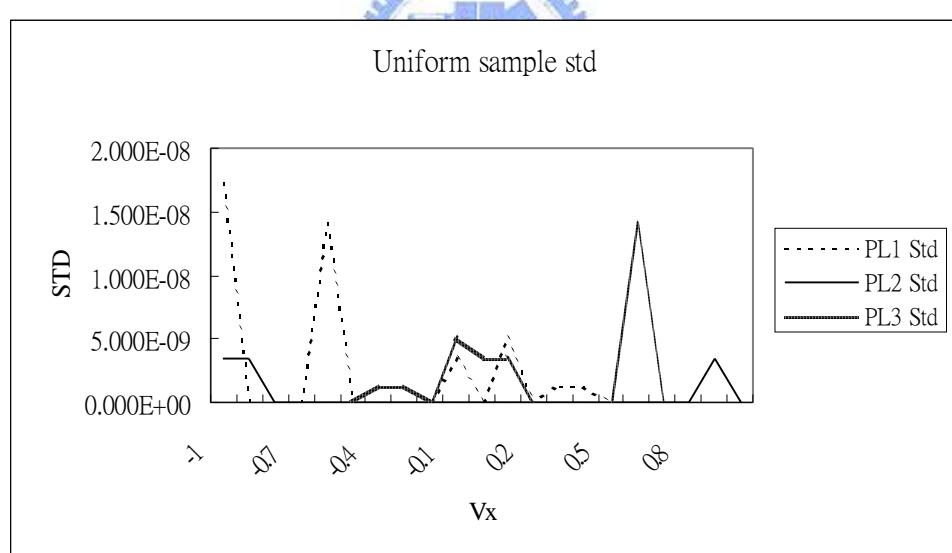

| 圖 33 | 均勻取樣的標準差圖.....                                 | 41 |

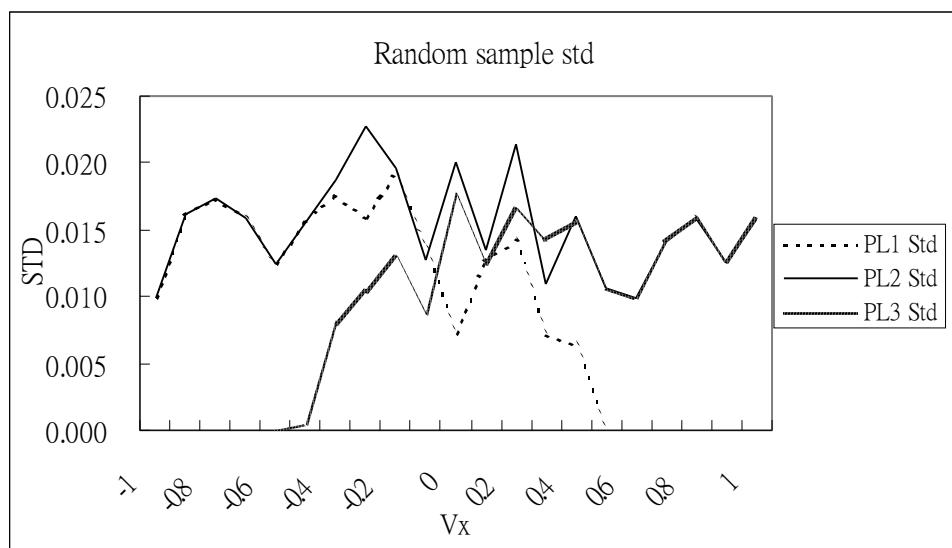

| 圖 34 | 隨機取樣的標準差圖.....                                 | 42 |

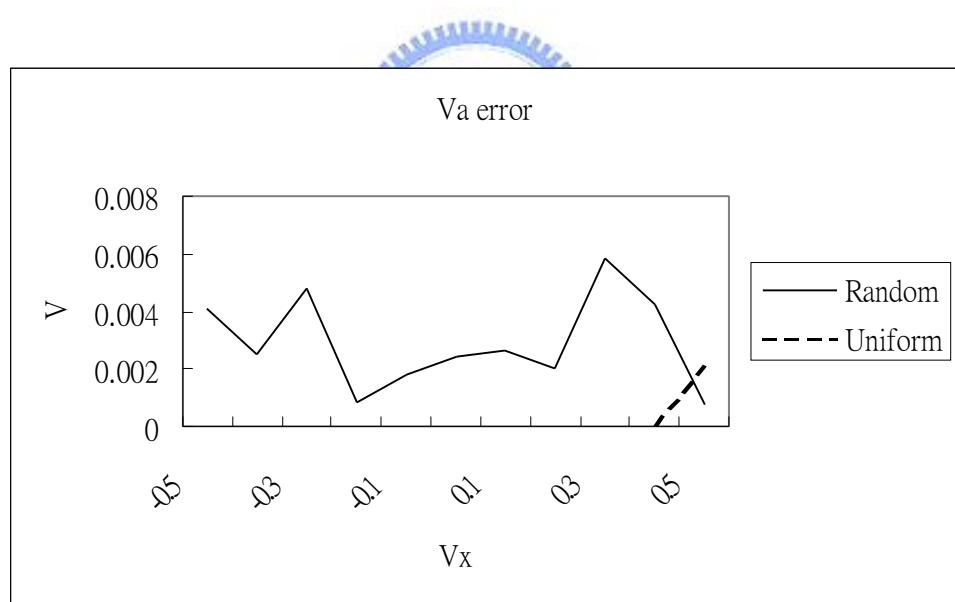

| 圖 35 | $V_A$ 的誤差圖.....                                | 42 |

|                                                                         |    |

|-------------------------------------------------------------------------|----|

| 圖 36 $V_X$ 的誤差圖.....                                                    | 43 |

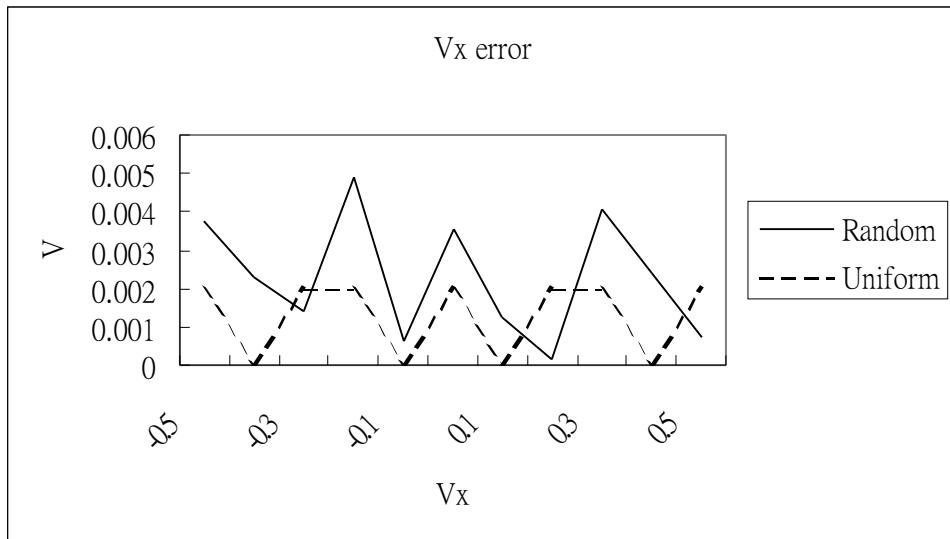

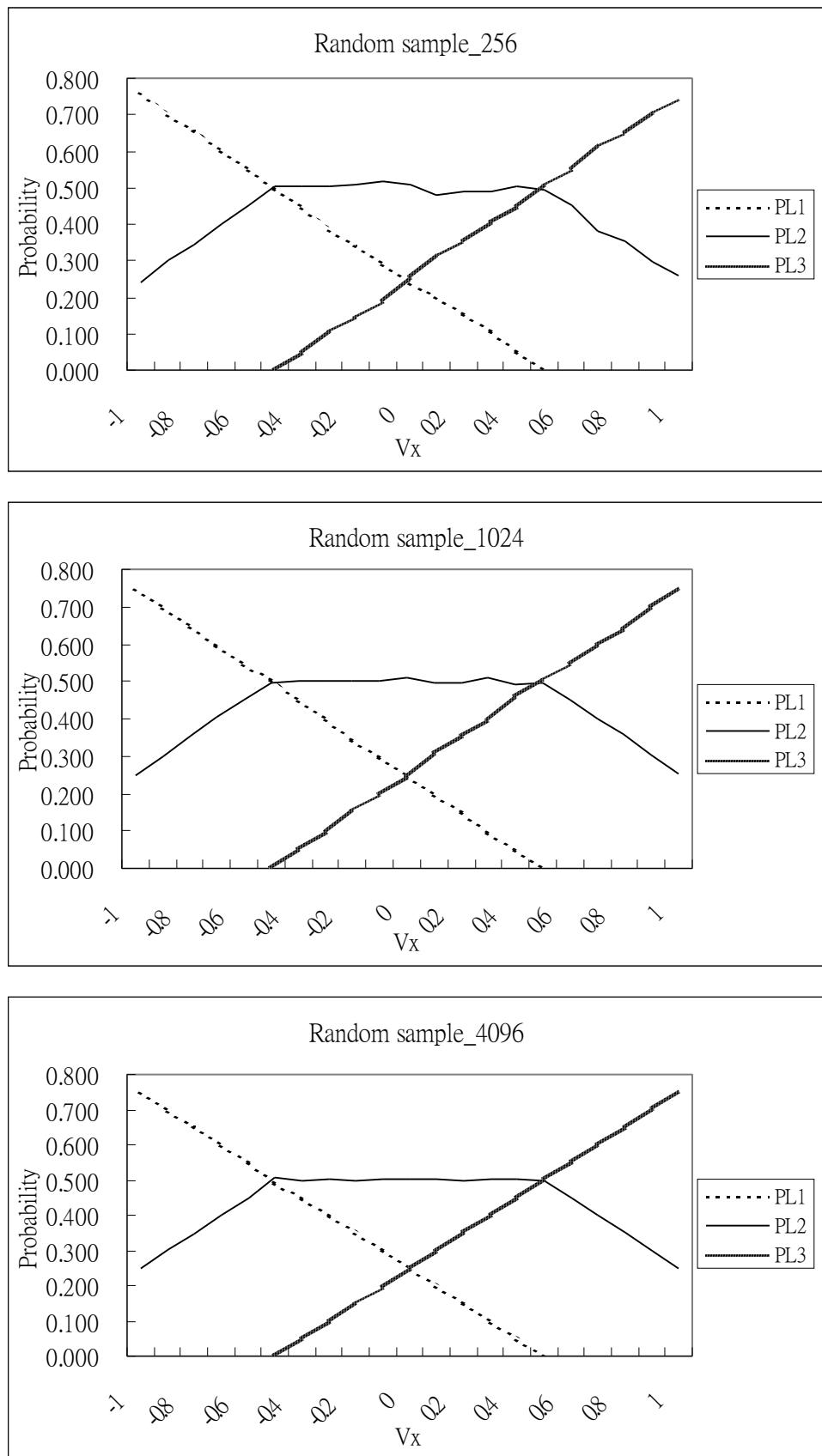

| 圖 37 256, 1024, 4096 機率圖.....                                           | 44 |

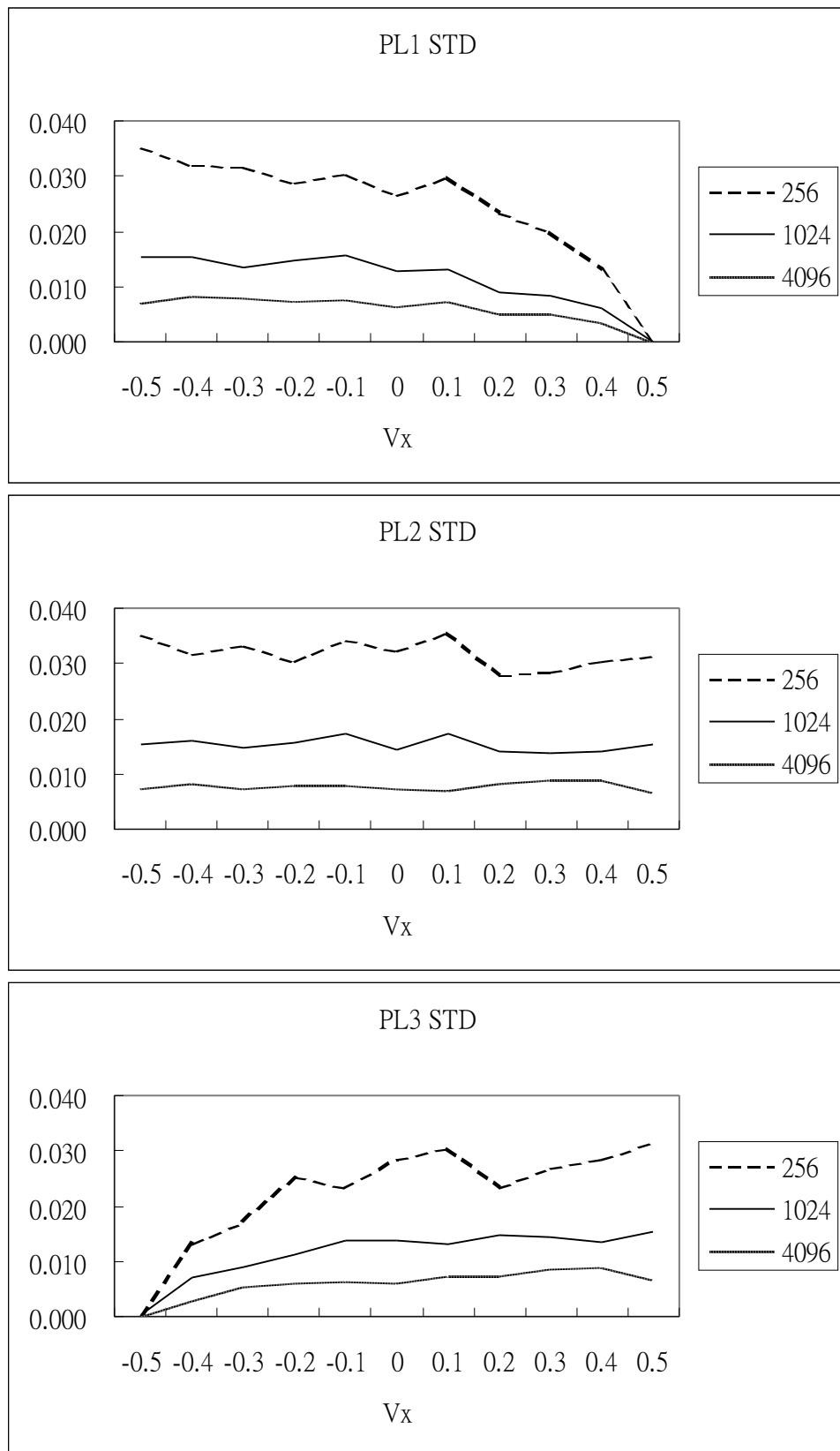

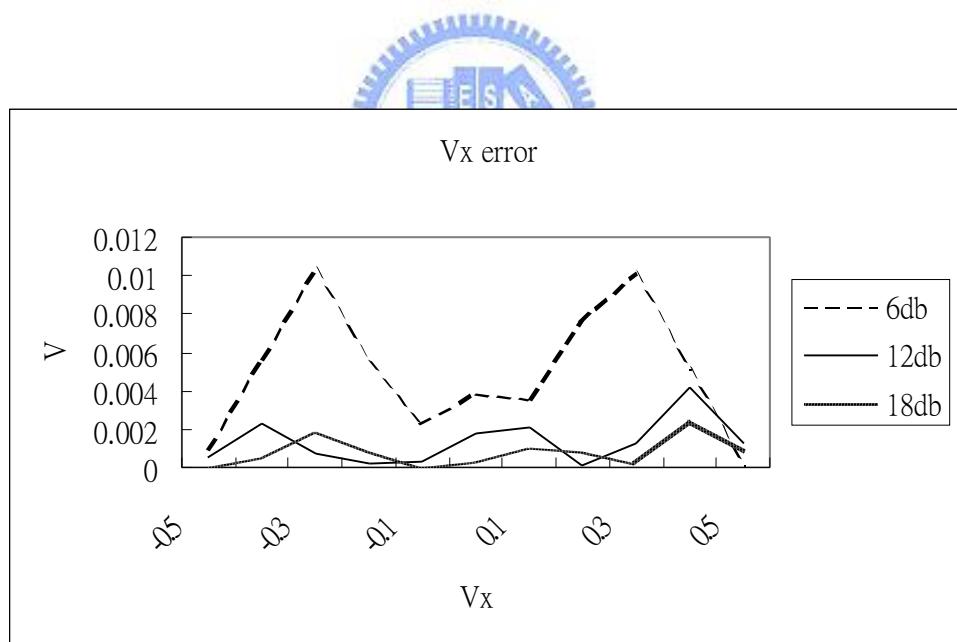

| 圖 38 256, 1024, 4096 標準差的圖.....                                         | 45 |

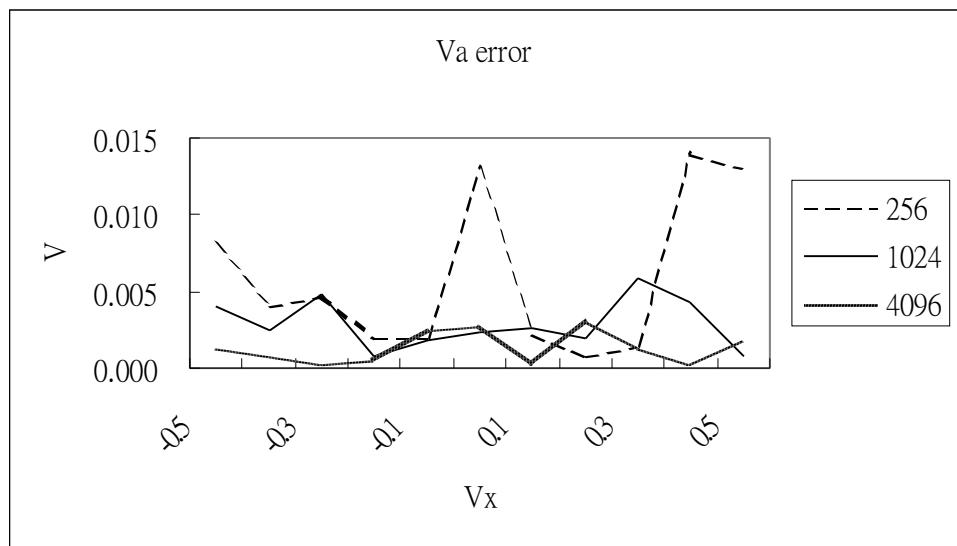

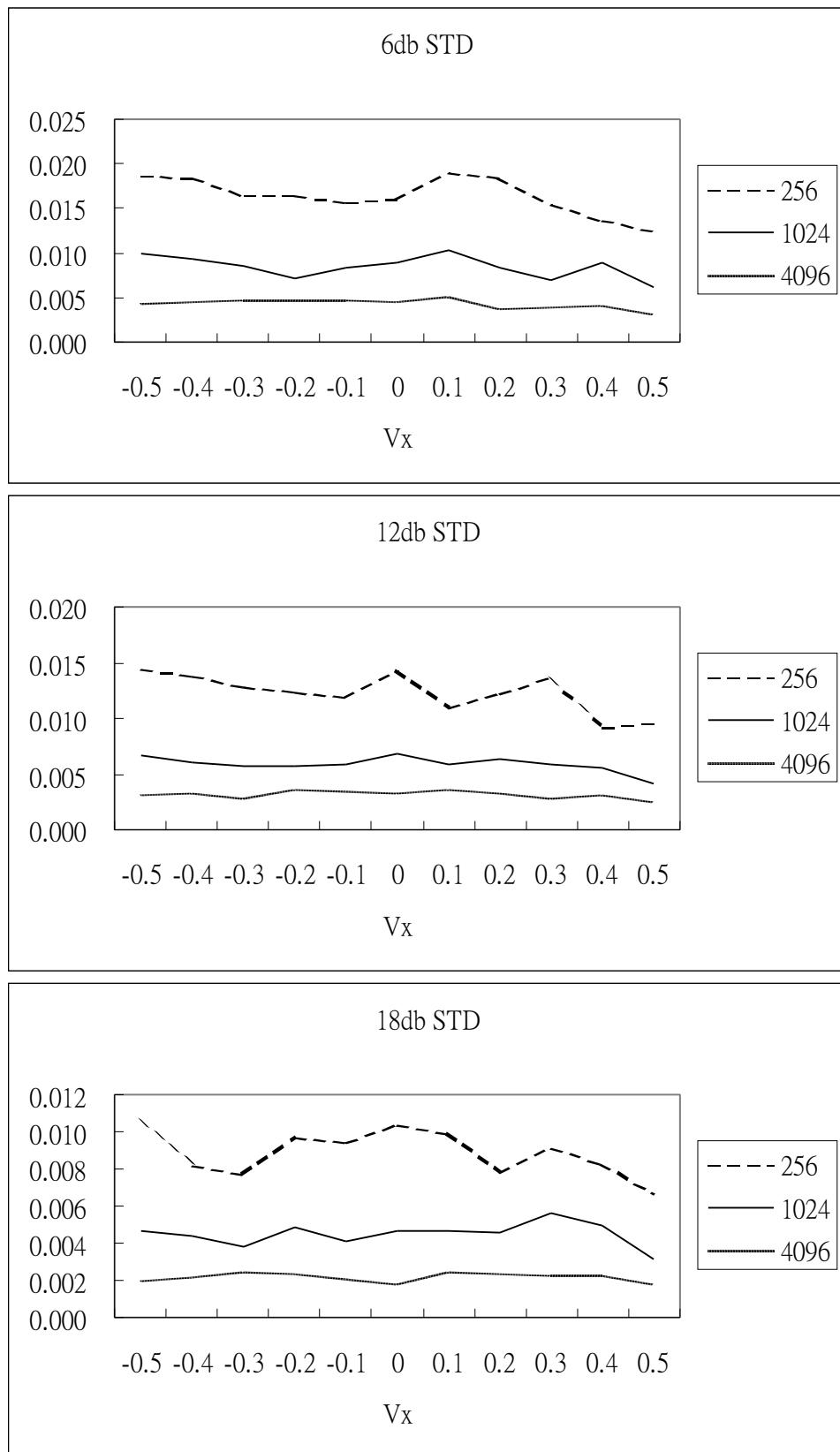

| 圖 39 $V_A$ 的誤差圖.....                                                    | 46 |

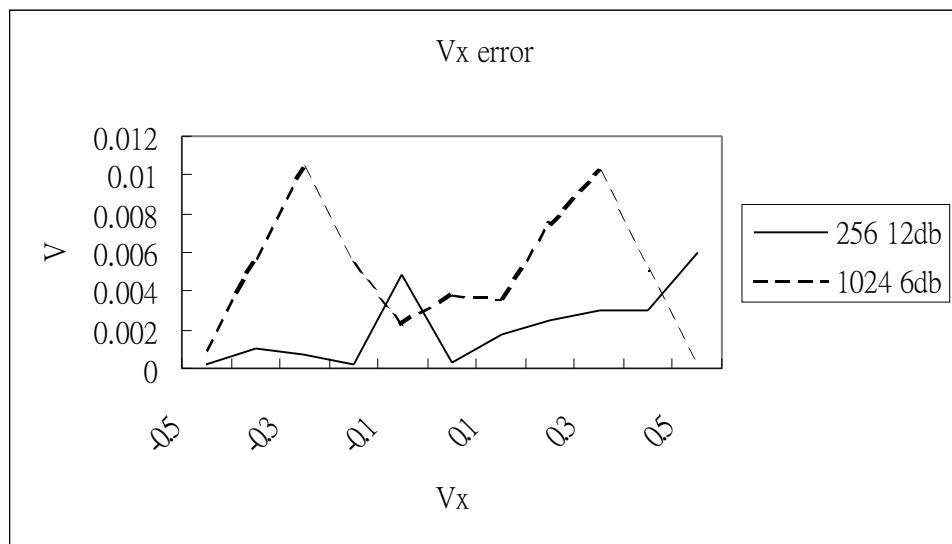

| 圖 40 $V_X$ 的誤差圖.....                                                    | 46 |

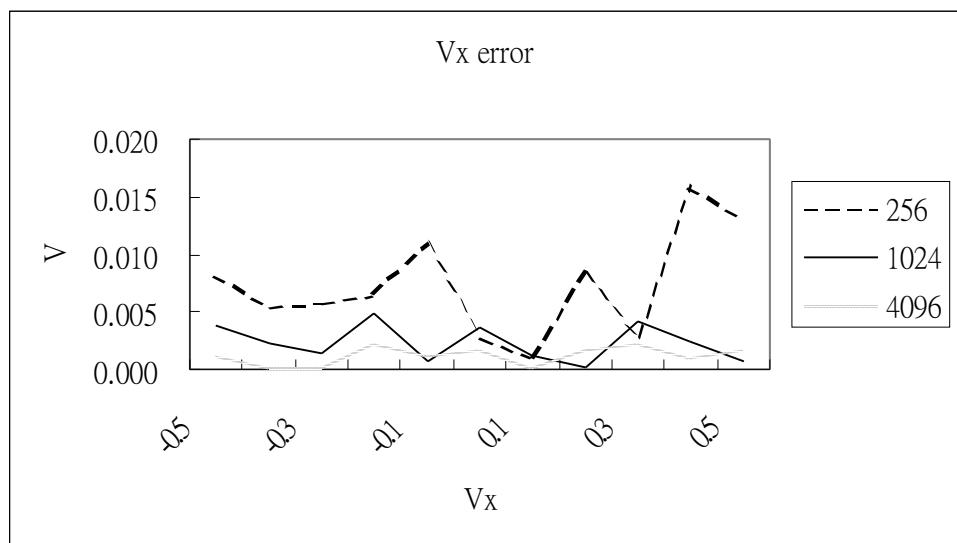

| 圖 41 $SNR = 6 \text{ dB}, 12 \text{ dB}, 18 \text{ dB}$ 的機率圖.....       | 48 |

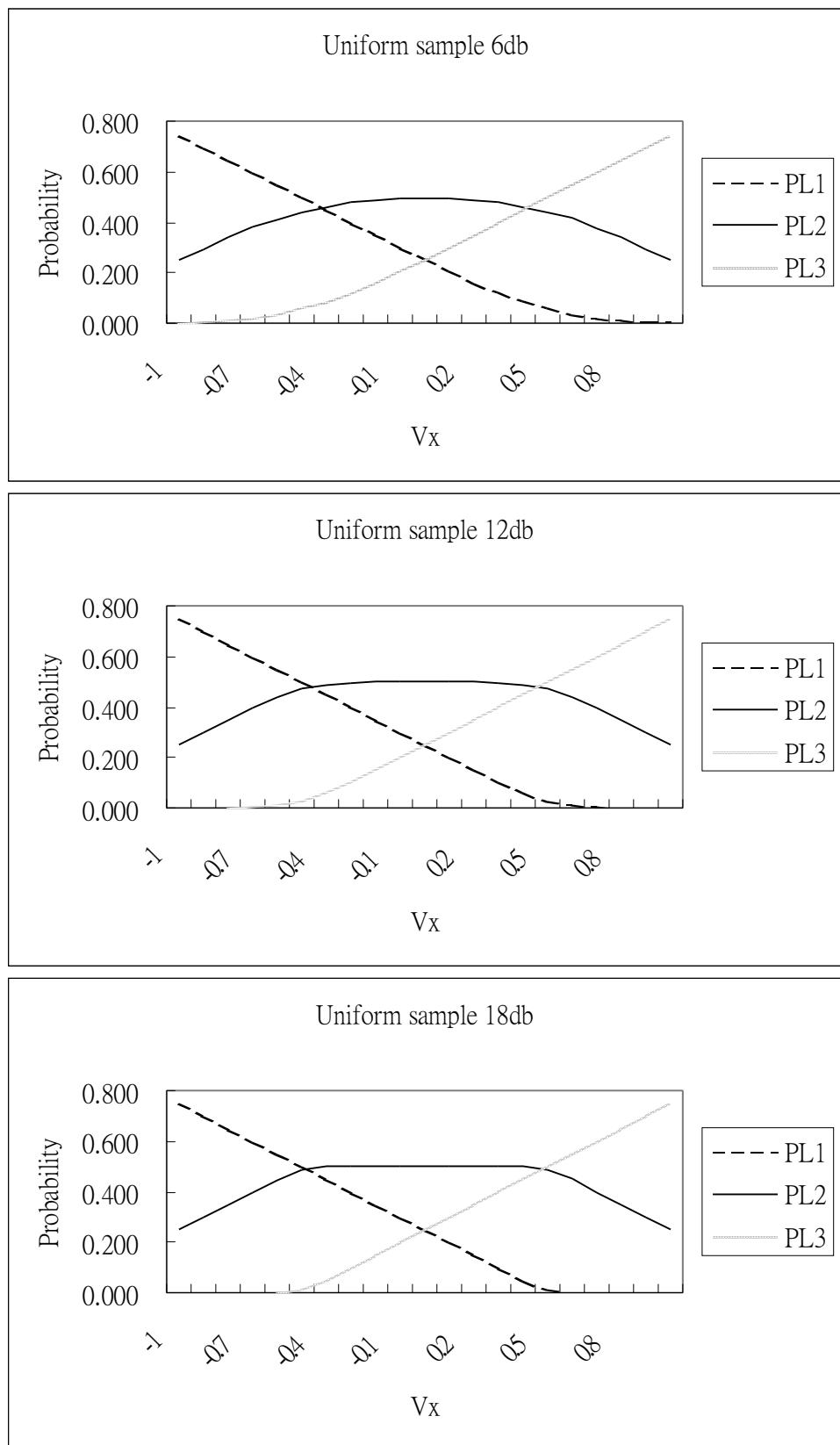

| 圖 42 $SNR = 6 \text{ dB}, 12 \text{ dB}, 18 \text{ dB}$ 標準差的圖.....      | 49 |

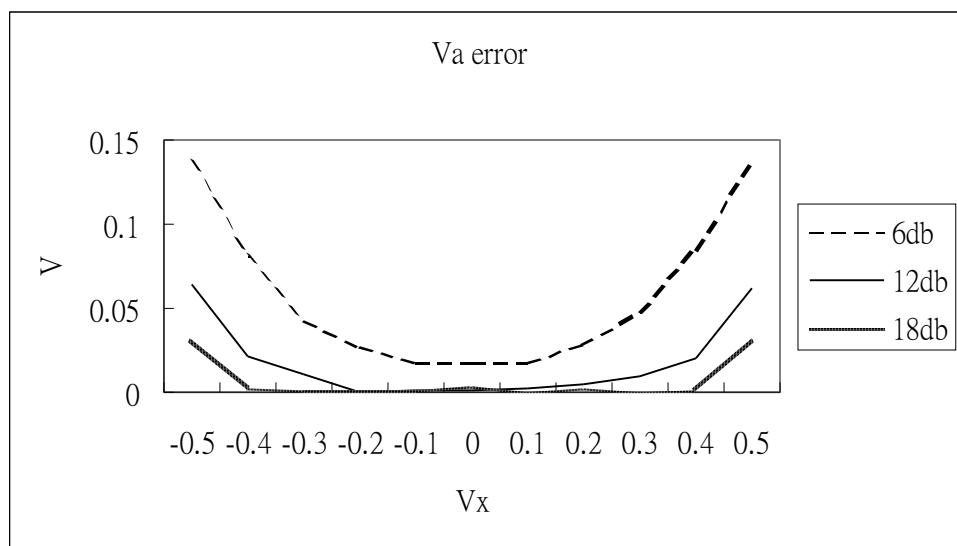

| 圖 43 $SNR = 6 \text{ dB}, 12 \text{ dB}, 18 \text{ dB}$ $V_A$ 的誤差圖..... | 50 |

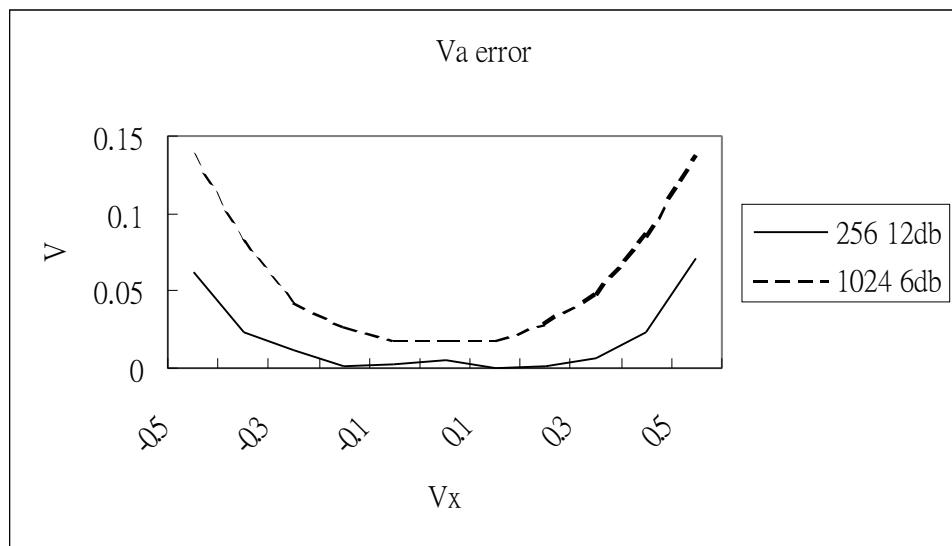

| 圖 44 $SNR = 6 \text{ dB}, 12 \text{ dB}, 18 \text{ dB}$ $V_X$ 的誤差圖..... | 50 |

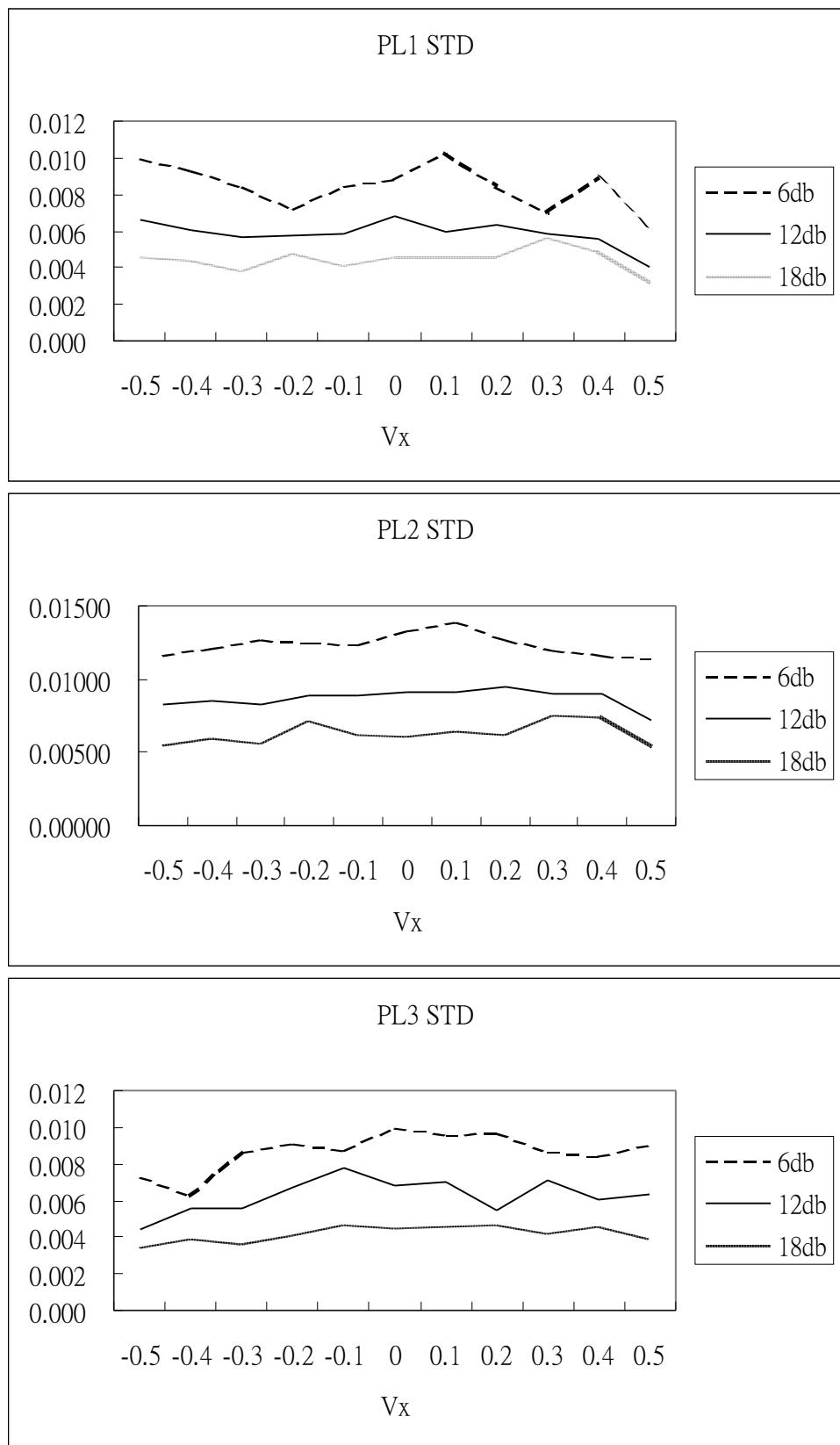

| 圖 45 不同的雜訊與取樣點數的標準差圖.....                                               | 52 |

| 圖 46 不同的雜訊與取樣點數的誤差圖.....                                                | 53 |

| 圖 47 誤差比較圖.....                                                         | 54 |

## 符號說明

$V_X$  : DC 偏壓

$V_{R+}$  : 參考電壓

$P_{L1}$  : 信號在 L1 的機率

$P_{L2}$  : 信號在 L2 的機率

$P_{L3}$  : 信號在 L3 的機率

$V_A$  : 振幅

$T_{PL1}$  : 信號在 L1 的時間區間

$T_{PL2}$  : 信號在 L2 的時間區間

$T_{PL3}$  : 信號在 L3 的時間區間

$\sigma_x^2$  : 信號的變異數

$\sigma_c^2$  : 共模信號的變異數

$\sigma_d^2$  : 差動信號的變異數

$\sigma_n$  : 雜訊的標準差

# 第一章 緒論

## 1-1 背景

近幾年來，由於積體電路製程上的進步，愈來愈多的電晶體被集積在同一个晶片上。設計業者可將不同形態的數位跟類比電路做在一起以獲得較好的效能，降低晶片面積及成本，這就是所謂的系統晶片 (System On Chip SOC) 或混合信號電路。雖然混合信號電路在 IC 設計上獲得了不少好處，但由於它將大量的信號處理功能由類比模組移到數位模組，因此類比輸出埠就變得比以前更為重要，它的性能直接影響了整個系統的效能。

然而，目前類比測試技術的發展還無法與數位測試技術相比。數位電路的輸入與輸出信號的量測可由邊界掃描來執行，這在 IEEE std. 1149.1 已經定義的非常清楚。當數位測試的 patterns 被放進待測元件時，錯誤可以經由大量已經建立的錯誤模型中輕易獲得，而且經過無數的經驗累積與不斷發展，數位的可測試設計 (*design for testability* DFT) 與內建自我測試 (*built-in self test* BIST) 已可建到綜合設計工具裏供 IC 設計人員自動擷取使用。相對於數位測試技術的成熟發展，目前大部份的類比電路測試還是著重於功能測試且

沒有足夠的錯誤模型可供參考。因此在類比測試領域，人們主要還是著重在類比 DFT/BIST 技術開發，而無法朝向綜合設計工具發展。

目前，混合信號測試匯流排相關的測試規範定義在 IEEE std. 1149.4。這個標準主要著重於印刷電路板層級的類比連接測試，它可解決部份的 controllability 以及 observation 問題，但對高頻、高速、高解析度的規格尚難克服。因此，有很多的 BIST 及 DFT 被提出來補充改進。

## 1-2 提出的測試方法

在本篇論文裏，我們提出一個新的數位化類比動態測試方法，它主要是以 IEEE std. 1149.4 所提出的 DFT 架構為基礎。我們所提出的方法是利用一對比較器去對一個待測的三角波信號取樣，經過統計比較器的輸出結果得到相關的機率，利用機率及統計的觀念分析這些機率值，最後得到待測信號的振幅與偏壓電壓值，我們將經由程式的模擬來驗證這個測試方法的可行性。

我們所提出的測試方法有以下的優點。首先它只需要一對比較器就可用來量測類比動態信號，而比較器在一般的數位測試機的 PE Card (Pin Electronic) 上就有了，這表示我們可用數位測試機來量測類比動態信號。這對測試上的成本有很大的助益。再者，測試的時間跟測試的準確性可經由調整取樣的點數來決定。第三當我們比較用於參數測試的正弦波時，測試時間會比量測三角波時變得更短。第四我們可以利用數位訊號處理的技術來獲得更多的參數特性。

本篇論文主要分為五個章節，第一章是緒論，主要是描述本論文研究的動機及論文主題的簡單敘述。第二章是相關測試方法的回顧、主要是介紹一些測試量測的單元如：精準量測單元及電子集成卡的架構及運作原理，而本章的主題是回顧一些與本論文所提出的測試方法有關的一些文獻，如：LCD

驅動 IC 的量測及靜態量測技術。第三章是測試方法與量測方法，在這一章，我們會介紹整個系統的架構，然後介紹測試跟量測原理及公式的推導，一些機率及統計的觀念也會在這一章提及。第四章是程式模擬，在這一章我們將利用程式的模擬來驗證我們所提出的測試方法。我們會設定各種的模擬情況，觀察在不同的測試情形下我們所提出的測試方法會有怎樣的結果產生。第五章是結論的部份，在這一章節裡面我們會針對整篇論文做一個總結。

## 第二章 相關測試方法回顧

### 2-1 概要

在這一章，我們將介紹一些類比信號的量測方法與跟本論文所提出的測試方法相關的一些文獻回顧。首先，我們將就自動測試機的量測單元說起，其中包括了精準量測單元 (*Precision Measurement Unit PMU*) 及電子集成卡 (*Pin Electronics Card PE card*) 的架構及運作原理，接下來我們會討論 IEEE std. 1149.4 [1] 的內部測試方法，它是本論文所提出的測試方法的基礎。最後我們回顧與本論文所提出的測試方法相關的一些文獻，包括 LCD 驅動 IC 的測試及線上靜態量測技術。

### 2-2 PMU

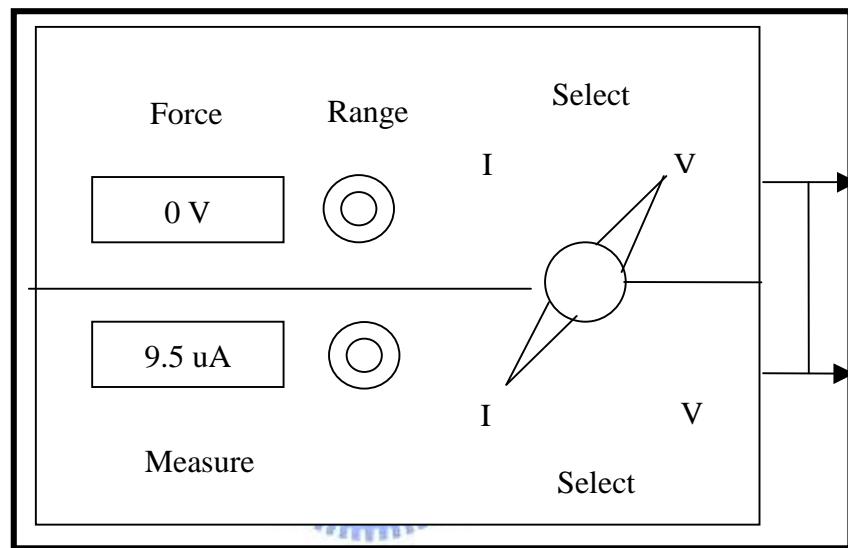

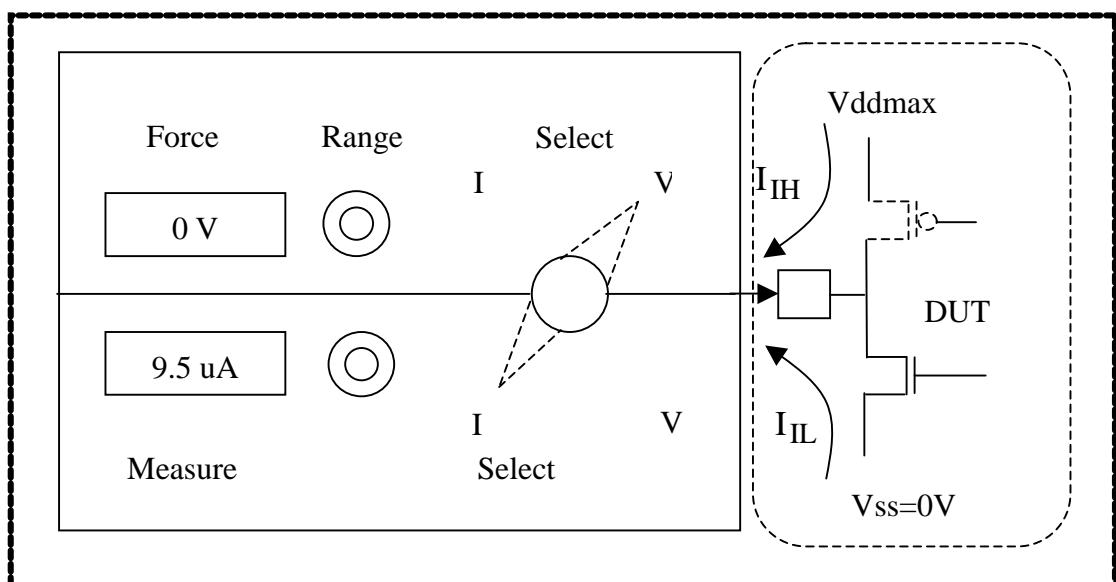

PMU 是自動測試機 (ATE) 量測 DC 電壓與電流的單元，它的主要架構示於 Figure 2.1。它的工作原理為送電壓量電流或是送電流量電壓。底下簡

述其量測輸入端漏電流的過程。

Figure 2.2 為 PMU 量測輸入端漏電流的示意圖，首先它會加  $V_{dd\ max}$  於 DUT 上，預設所有的輸入端為邏輯 “1” (“0”)，用 PMU 送  $V_{dd\ max}$  (0V) 於輸入端，約 1 到 5ms 後量測輸入端的  $I_{IH}$  ( $I_{IL}$ )，依照規格指示若  $I_{IH}$  大於  $10\mu A$  或  $I_{IL}$  小於  $-10\mu A$  則 DUT 是壞的，反之，則 DUT 是好的。

Fig. 2.1 PMU 的架構

Fig. 2.2 PMU 的量測原理

## 2-3 PE Card

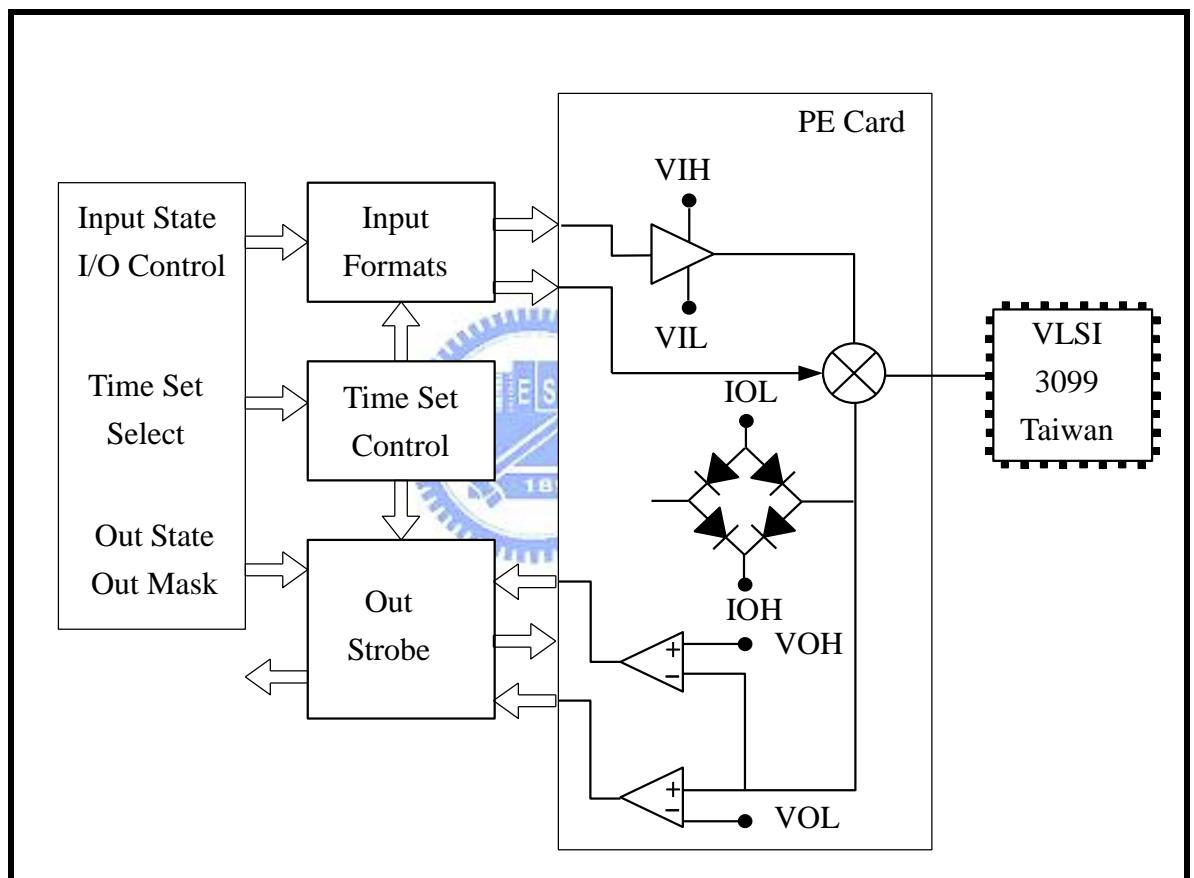

電子集成卡 (PE Card) 主要是位於測試機的測試頭內，Figure 2.3 是它的架構圖。

Fig. 2.3 Pin Electronic 電路

它主要是由可程式化的驅動器，一對比較器及一個動態電流負載三大部分所構成。驅動電路是由一個擁有兩個可程式化的邏輯準位  $V_{IH}$ 、 $V_{IL}$  的固定阻抗 ( $50\Omega$ ) 驅動器所組成，它可直接由 DAC 控制，驅動器一般需被設定在高阻抗狀態。比較器有兩個參考電壓  $V_{OH}$ 、 $V_{OL}$ ，它是被用來比較 DUT

傳回來的信號。如果傳回來的信號大於  $V_{OH}$ ，就被視為邏輯 “1”，如果傳回來的信號小於  $V_{OL}$ ，則被視為邏輯 “0”，如果傳回來的值介於  $V_{OH}$  跟  $V_{OL}$  之間，我們稱之為中點電壓，不過，這通常是個不正確的值。第三個部份是負載電路，它是由四個二極體及兩個電流源所構成，它主要是送出或抽取一個可程式化的電流到 DUT，量測它的驅動能力。

為了降低測試時間增加準確性，我們可使用比較器去取樣 DUT 的輸出，並利用我們第三章所提出的方法來分析它。

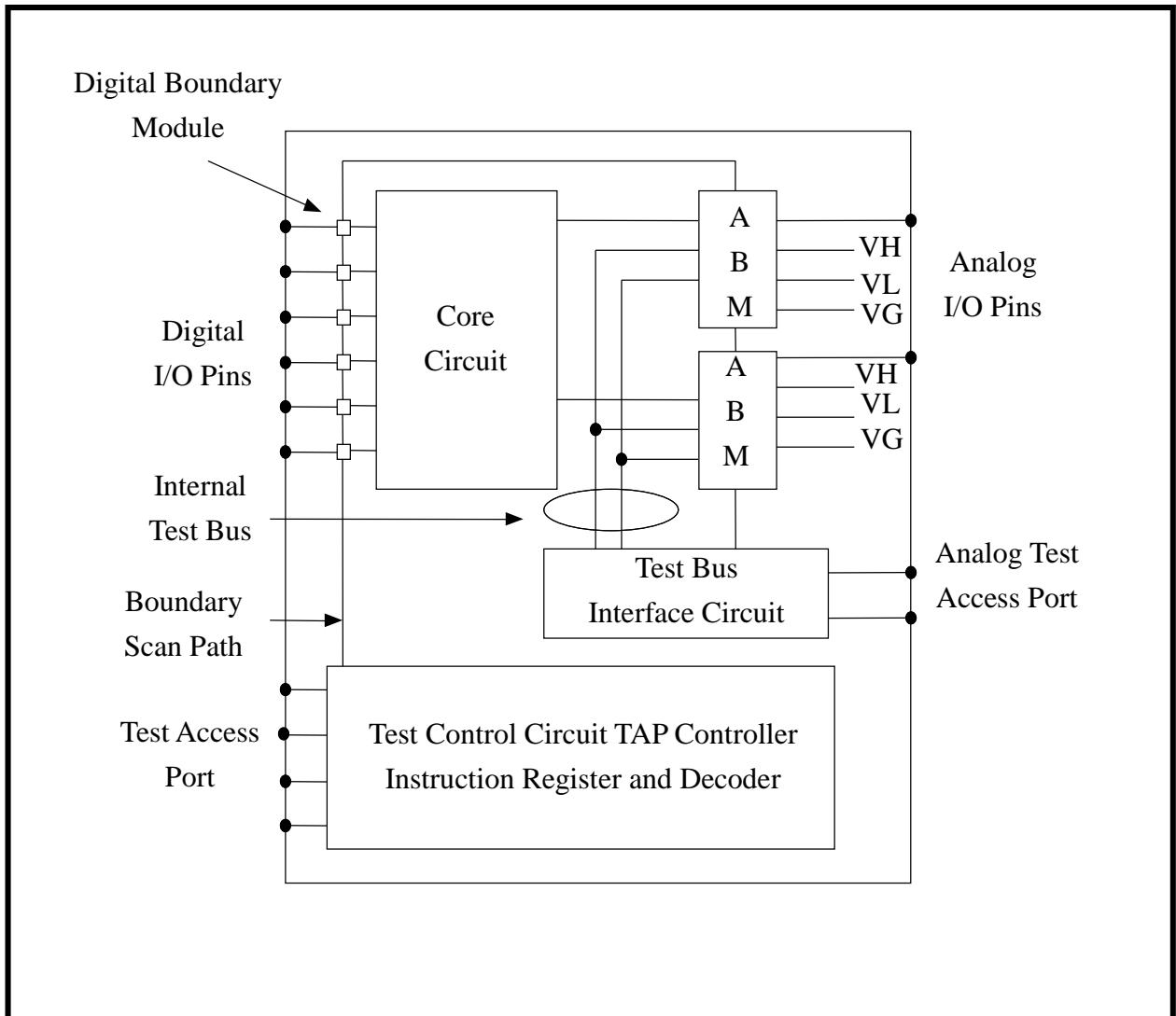

## 2-4 IEEE std. 1149.4 Internal Testing

IEEE std. 1149.4 [1] 是給混合信號測試匯流排使用，如 Figure 2.4 所示，其整個架構主要針對印刷電路板 (PCB) 的內部連接測試，分離元件的參數測試及 IC core 的功能測試。它只須兩個指定的接腳，一個接到類比測試接收端 1 (AT1)，負責提供類比輸入信號，一個接到類比測試接收端 2 (AT2)，負責偵測反應回來的類比信號。這個標準的目的是要降低混合信號測試的困難度，促進 DFT 的發展及推廣一致的設計與測試方法。

Fig. 2.4 IEEE std. 1149.4 的架構圖

Figure 2.5 為 IEEE std. 1149.4 測試匯流排界面電路 (TBIC) 的架構，它是由一個簡單的比較器及一些開關所組成。右邊的模組是必要的，左邊的則是選項的，信號經由比較器跟臨界電壓 ( $V_{TH}$ ) 比對，比對的結果由數位掃描鏈將資料掃描出來，最後由邏輯分析儀來分析取樣的資料。

Fig. 2.5 Internal test 電路

## 2-5 LCD 驅動 IC

液晶顯示器 (LCD) 是目前當紅的電子產品，它被廣範的應用在各種電子系統上。像可攜式的電子產品如：筆記型電腦，個人數位助理及行動電話等。由於它的低功率損耗，輕薄的外型及零幅射的特性，使得它漸漸取代了 CRT 在各項家電及電腦螢幕的地位。由於 LCD 的普及，因此 LCD 驅動 IC 在 IC 產業裡也形成了相當重要的一環，因為它的測試技術跟傳統數位和類比 IC 不同，所以需要特定的測試機來測試。在我們開始談 LCD 驅動 IC 的測試前，先讓我們來了解 LCD 驅動 IC 的架構及運作原理。

Fig. 2.6 LCD 驅動 IC 的架構圖

LCD 驅動 IC 基本上包含了三個主要部份，分別是移位暫存器，取樣保持電路及緩衝放大器。Figure 2.6 描述了整個 LCD 驅動 IC 的架構。底下我們簡單的介紹 LCD 驅動 IC 的工作原理。如 Figure 2.6 所示，移位暫存器在接到取樣脈衝的訊號後會依序將信號送到取樣保持電路，取樣保持電路會依據送來的資料重建邏輯 "0" 跟邏輯 "1" 的位準，為了達到高解析度的顯示，每一條線皆需要獨立的取樣保持電路。取樣保持電路一般必須工作在視頻訊號的頻寬，通常都遠大於 Nyquist rate。緩衝放大器決定輸出準位，通常由  $+Vs$  與  $-Vs$  提供，它會充電到所要達到的電壓並且顯示出想要的色彩。

在 LCD 的 cell 上。由以上的論述，我們可將 LCD 驅動 IC 視為一個 DAC，並用測 DAC 的方法來測試它。

對於 DAC 的量測，信號的準位我們可用先前提到的參數量測單元 (PMU) 來量測，然而由於 LCD 驅動 IC 的輸出通道太多，所需要的 PMU 數量將非常大。原有的類比及數位測試機無法適用，因此便有專用於測試 LCD 驅動 IC 的測試機，用來降低測試時間及增加生產量，不過這種測試機通常都非常的昂貴。如預期般的，傳統的 DC 量測單元在測試 LCD 驅動 IC 時，不管是在測試時間及準確度上皆有所困難。所以我們將於下面章節介紹一個更有效率的 LCD 驅動 IC 測試方法。

[2] 提出了用一對比較器來測試 LCD 驅動 IC 的方法。Figure 2.7 所示為其測試架構，其原理為利用電子集成卡 (PE Card) 上的一對比較器來比較 DUT 的輸出電壓。這裡  $V_{R+}$ 、 $V_{R-}$  是所設定的比較電壓，如 Figure 2.7 所示，輸出電壓  $V_X$  會跟所設定的  $V_{R+}$ 、 $V_{R-}$  比較，當  $V_X$  比  $V_{R+}$  小且大於  $V_{R-}$  時， $V_X$  等於  $V_C$ ，它的誤差等於  $0.5\Delta V_R$ 。這裡

$$V_C = \frac{1}{2}(V_{R+} + V_{R-}) \quad (2-1)$$

$$\Delta V_R = V_{R+} - V_{R-} \quad (2-2)$$

Fig. 2.7 LCD 驅動 IC 測試架構圖

雜訊通常是不想要的且被視為不好的信號。但這裡，雜訊卻可被用來決定電壓準位。Figure 2.8 為簡化的雜訊模型，這裡假設  $V_X$  不是在  $V_{R+}$  與  $V_{R-}$  的中間，其距離中心點的距離為  $X$ ， $\sigma_x^2$  為信號雜訊的變異數， $\sigma_c^2$  及  $\sigma_d^2$  為參考電壓的共模及差模的變異數。 $V_X$  可以大於或小於  $V_{R+}$  及  $V_{R-}$ ，這完全取決於雜訊的大小，經由重複的取樣得到大量的二元輸出，分析它的輸出得到相對的機率值，用此機率值來決定  $V_X$  距離  $V_C$  有多遠，即  $X$  值。

Fig. 2.8 簡化的雜訊模型

在單點取樣時，輸入信號可能落在  $L1 (V_X < V_{R-} < V_{R+})$ ， $L2 (V_{R-} < V_X < V_{R+})$ ， $L3 (V_{R-} < V_{R+} < V_X)$  三個區域之一，信號落在每一個區域的機率標示為  $P_{L1}$ ， $P_{L2}$  及  $P_{L3}$ ，其值如下，

$$P_{L1} = P_{V_X < V_{R-} < V_{R+}} = \int_{-\infty}^{V_{R-}} P_{V_X}(x) \int_{V_{R+}}^{\infty} P_{V_{R+}}(y) d_y d_x \quad (2-5)$$

$$P_{L2} = P_{V_{R-} < V_X < V_{R+}} = \int_{V_{R-}}^{\infty} P_{V_X}(x) \int_{V_X}^{\infty} P_{V_{R+}}(y) d_y d_x \quad (2-6)$$

$$P_{L3} = P_{V_{R-} < V_{R+} < V_X} = \int_{V_{R-}}^{\infty} P_{V_X}(x) \int_{V_{R+}}^{V_X} P_{V_{R+}}(y) d_y d_x \quad (2-7)$$

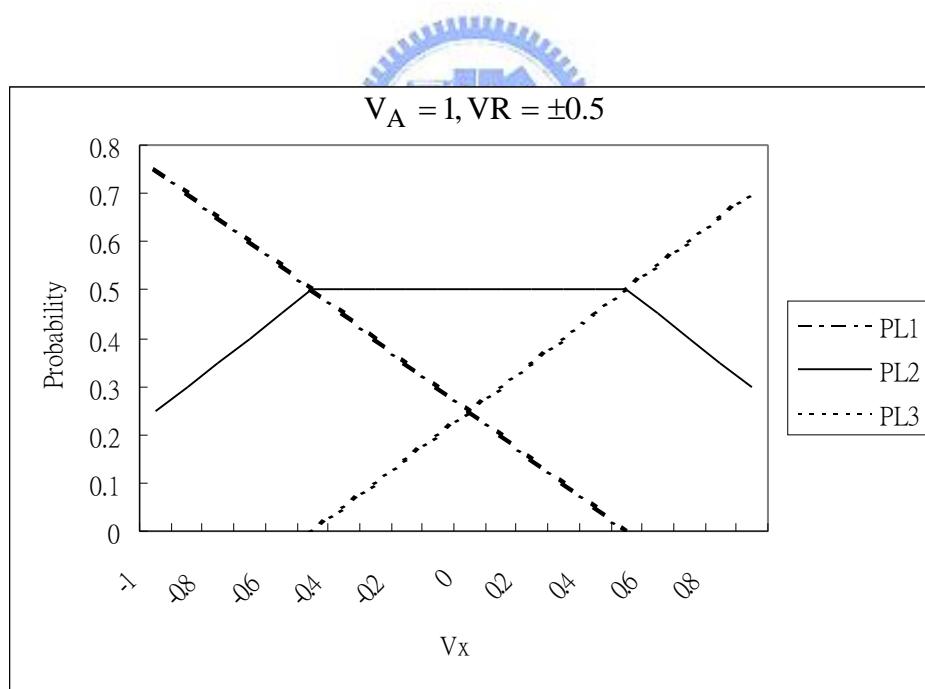

依據(2-5), (2-6), (2-7)式可得到  $P_{L1}$ ,  $P_{L2}$  及  $P_{L3}$  跟  $X$  的關係式, Figure 2.9

為機率跟  $X$  關係圖。由上可知，當一個未知  $X$  的信號被重覆取樣時，可經由統計輸出得到  $P_{L1}$ ,  $P_{L2}$  及  $P_{L3}$  的值，經由查表便可由這一組 ( $P_{L1}$ ,  $P_{L2}$ ,  $P_{L3}$ ) 得到想知道的  $X$  值，如此便可得到  $V_X$  的測量值。

Fig. 2.9  $P_{L1}$ ,  $P_{L2}$ ,  $P_{L3}$  與  $X$  的關係圖

## 2-6 On-Line 靜態量測技術

在類比電路裡，靜態或偏壓電壓及偏壓電流是觀察整個系統效能的一個很好的指標。舉電晶體 BJT 為例，轉換電導 ( $G_m$ ) 是偏壓電流的函數

$$G_m = \frac{I_C}{V_T}$$

，當偏壓電壓或偏壓電流飄移時，則表示系統的效能也跟著飄移。

Fig. 2.10 運算放大器

Figure 2.10 是一個運算放大器，偏壓電流決定了整個運算放大器的增益及其它的參數，在系統的應用上，靜態監控可確保系統工作在安全範圍。在過去，也有一些線上監控的技術被提出，如電容開關濾波器 [3]，運算放大

器 [4]，及類比檢查電路 [5, 6]，這些大部份都是建立在類比量測領域，而 [7] 提出了用數位方法來量測線上的靜態電壓。

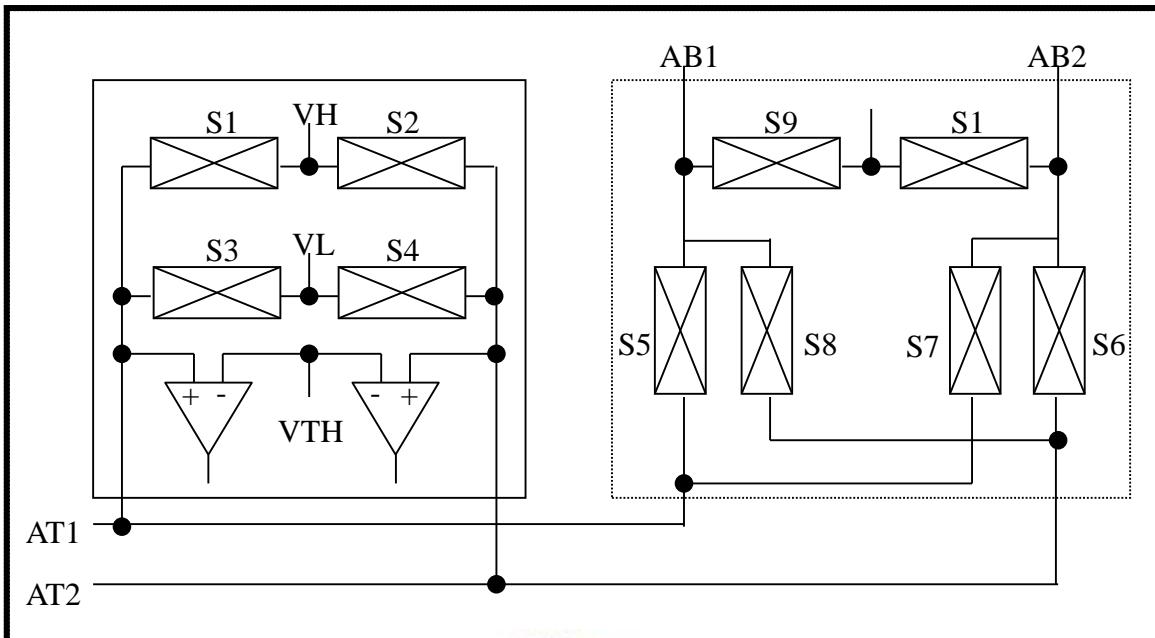

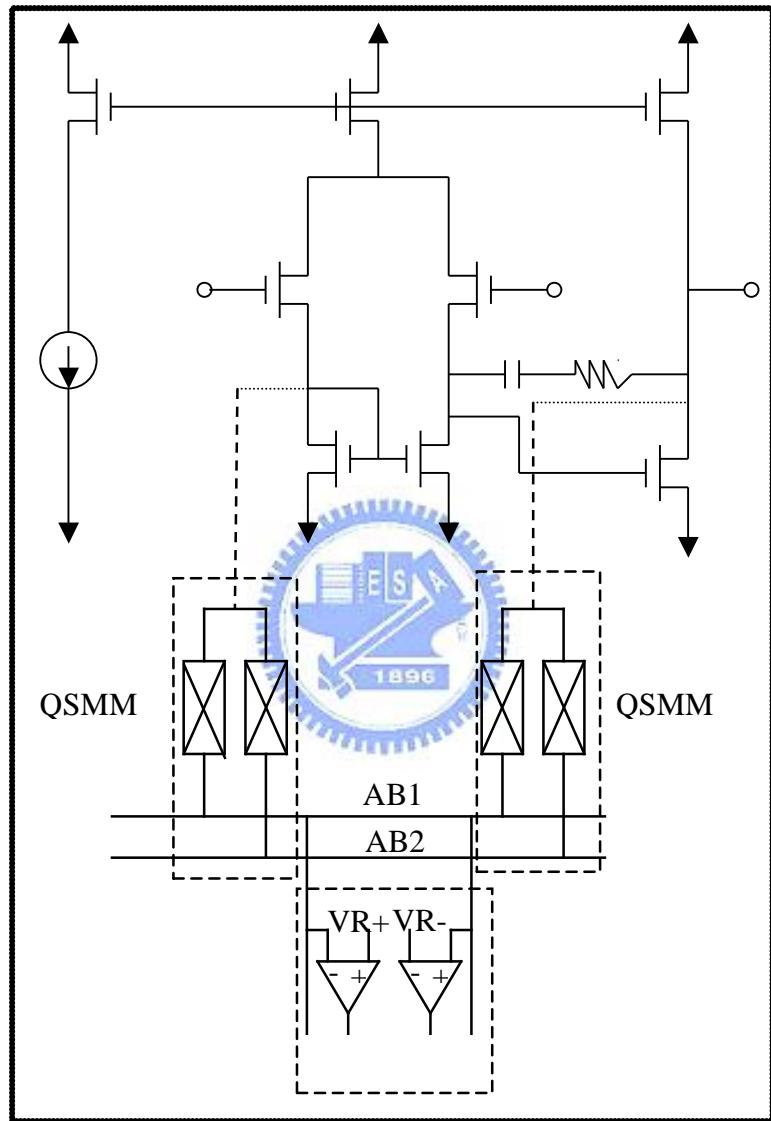

Fig. 2.11 靜態監控的主要架構

Figure 2.11 是靜態監控的主要架構，靜態監控模組(QSMM)主要是當做內部電路節點與 AB1，AB2 的開關，當要進行監控時 QSMM 便會連接內部

電路節點到 AB1，AB2，使得量測得以進行。QSMM 主要是由兩個開關所組成，開關的一端連接到想要量測觀察的節點，另一端則接到內部測試匯流排(AB1/AB2)。

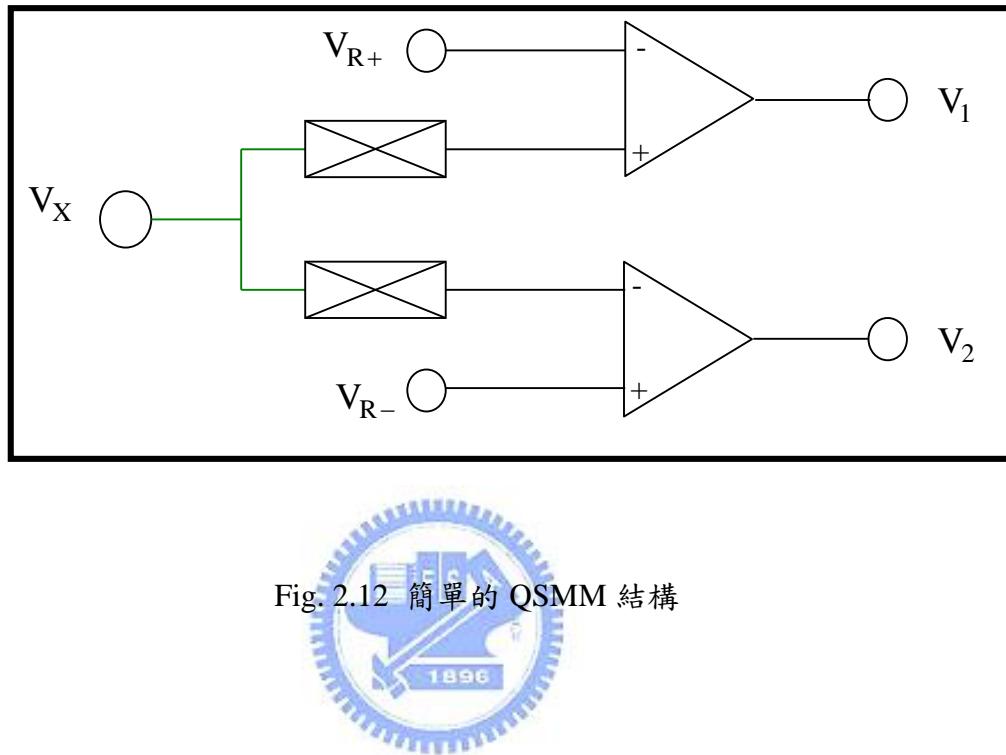

Fig. 2.12 簡單的 QSMM 結構

Figure 2.12 是一個簡單的 QSMM 結構，偏壓電壓  $V_X$  被連接到比較器上跟參考電壓  $V_{R+}$ ， $V_{R-}$  做比對，其原理如同前一節 LCD 驅動 IC 量測原理一樣，這裡我們就不多做說明。

由以上的回顧，我們發現不管是 2-5 節所提的 LCD 驅動 IC 測試，或是 2-6 節的線上靜態電壓量測技術，皆是靜態電壓的量測技術，它們都不能處理內建測試裡動態信號測試問題。再這一篇論文裡，我們所提出的測試方法將可解決類比動態信號的測試問題。

## 第三章 測試與量測方法

### 3-1 概要

在這一章的一開始，我們會先介紹整個測試方法的架構，它是由一個負責取樣待測信號的比較器為主體所組成的。然後我們會介紹測試跟量測原理及推導相關公式，我們會利用機率及統計的觀念來分析資料找出信號的特性，雜訊對系統的影響也會在這一章裡討論。

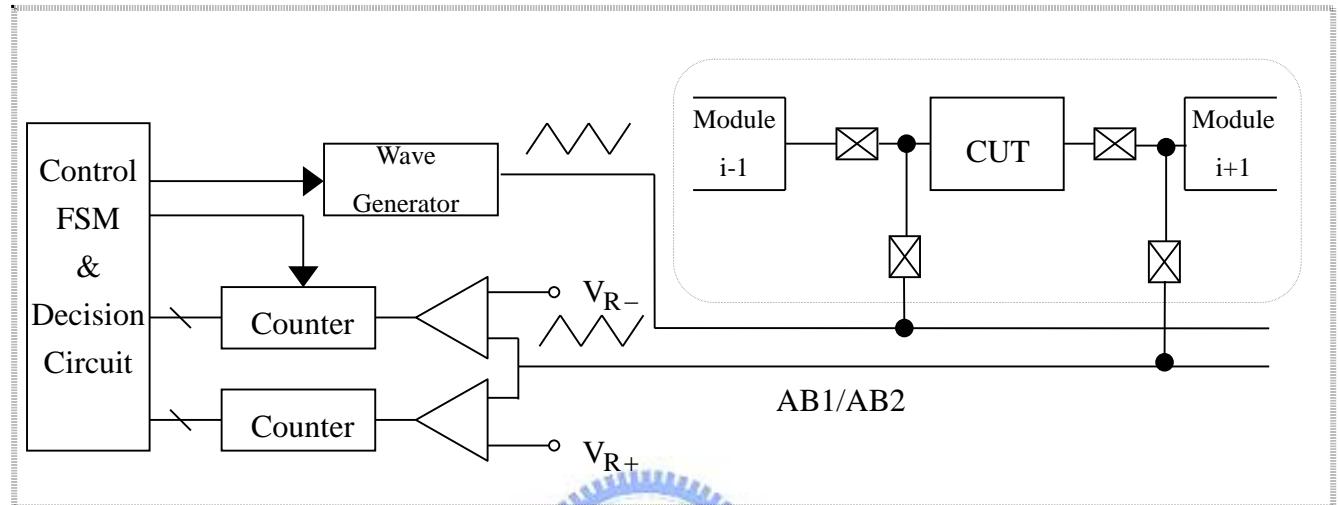

### 3-2 系統架構

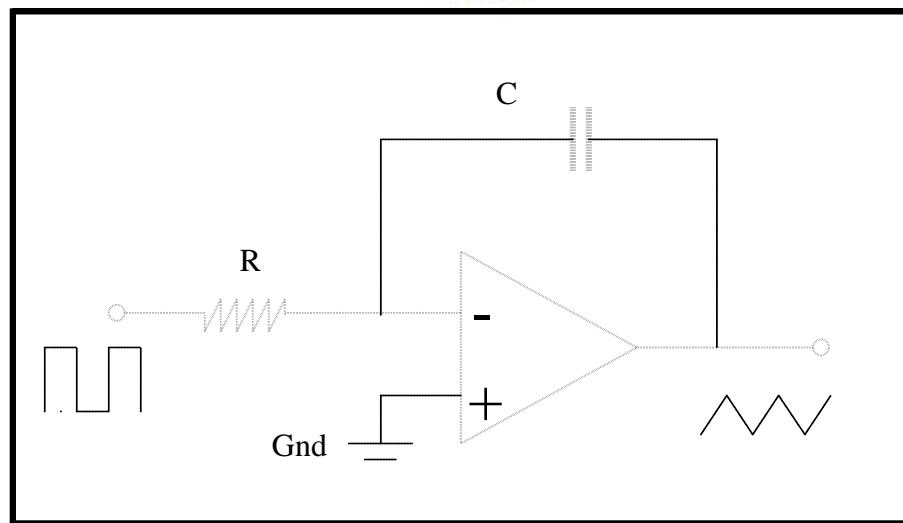

Figure 3.1 所示為我們所提出的數位化動態類比測試方法的架構圖，這裡我們使用三角波的波形產生器來當信號源，這是因為三角波是十分常用的類比信號且它容易由簡單的電路產生。Figure 3.2 所示為簡單的三角波產生器，它只需要一個方波跟一個積分器就可組成。三角波由波形產生器產生之後，經由 AB1/AB2 送到待測晶片 (*Chip Under Test CUT*) 的輸入端，CUT 所產生的輸出再由 AB1/AB2 送到比較器與參考電壓  $V_{R+}$ ， $V_{R-}$  做比較，這裡  $V_{R+}$ ， $V_{R-}$  可由電壓供應器接上一個大的旁路電容來完成。比較器比對

的結果由計數器計數邏輯 ”1” 來決定，經過一段適當的取樣時間，我們便可由計數器的記錄，來分析 CUT 輸出的結果，至於如何分析在下面章節會詳細說明。

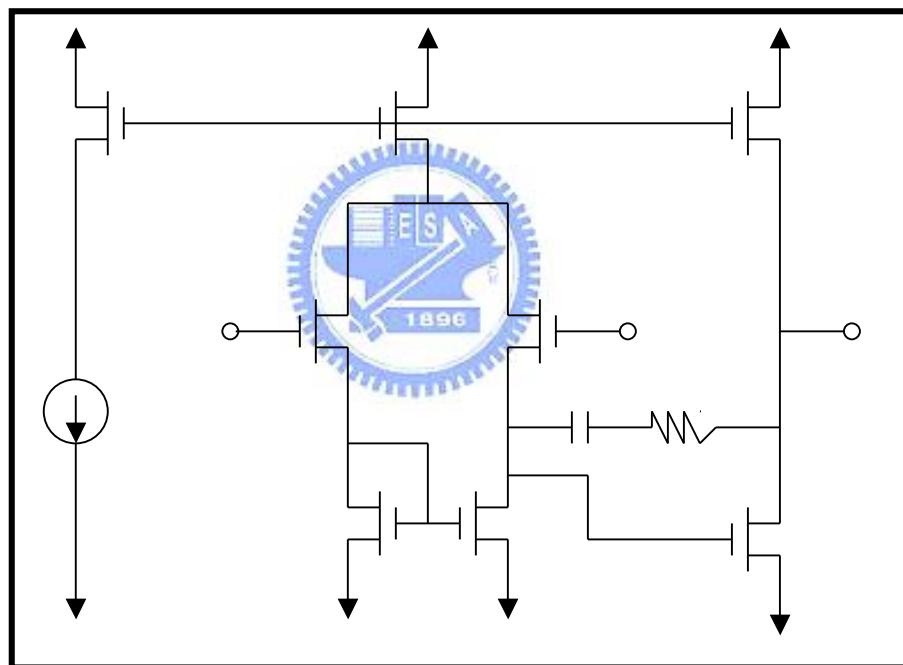

Fig. 3.1 BIST 的架構

Fig. 3.2 簡單的三角波產生器

### 3-3 公式推導

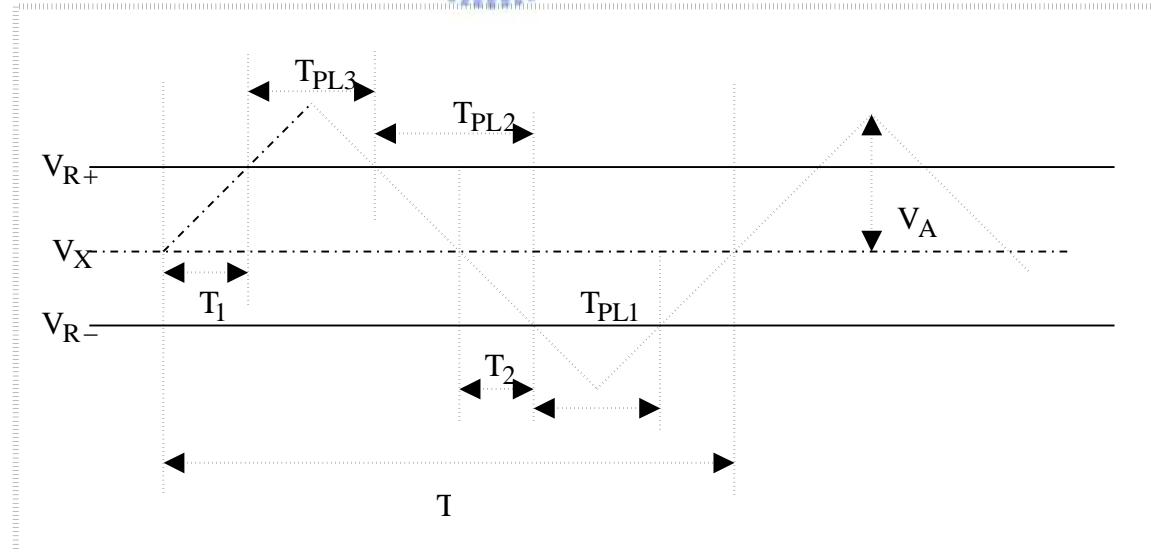

我們所提出的測試方法，是讓待測的三角波信號通過一對擁有參考電壓  $V_{R+}$ ， $V_{R-}$  的比較器，經過分析比較器的輸出結果，求得三角波的振幅及偏壓電壓。Figure 3.3 描述整個分析方法的架構。這裡三角波的週期是  $T$ ，振幅是  $V_A$ ，偏壓電壓值是  $V_X$ ， $V_{R+}$ ， $V_{R-}$  是我們所設定的比較器參考電壓，當三角波跟兩個參考電壓做比較時，信號可能會落在以下三個區域：

$$L_1 : V < V_{R-} < V_{R+}$$

$$L_2 : V_{R-} < V < V_{R+}$$

$$L_3 : V_{R-} < V_{R+} < V$$

其相對的時間區間依序為： $T_{PL1}$ ， $T_{PL2}$ ， $T_{PL3}$ 。

Fig. 3.3 整個分析方法的架構

我們可由 (3-1) 式得到  $T_{PL1}$  ,  $T_{PL2}$  ,  $T_{PL3}$  如 (3-2) , (3-3) , (3-4) 所示

$$\begin{aligned}

\Delta V_R &= V_{R+} - V_{R-} \\

V_A &= Y * \Delta V_R \\

\text{Slop} &= \frac{V_A}{T/4} = m \\

T_1 &= \frac{(V_{R+} - V_X)}{m} \\

T_2 &= \frac{(V_X - V_{R-})}{m} \\

\frac{1}{2} T_{PL3} &= \frac{T}{4} - T_1 \\

\frac{1}{2} T_{PL1} &= \frac{T}{4} - T_2 \\

T_{PL1} &= \frac{T}{2} \left(1 - \frac{V_X - V_{R-}}{V_A}\right) \\

T_{PL2} &= T - T_{PL1} - T_{PL3} = \frac{T}{2V_A} (V_{R+} - V_{R-}) \\

T_{PL3} &= \frac{T}{2} \left(1 - \frac{V_{R+} - V_X}{V_A}\right)

\end{aligned} \tag{3-1} \tag{3-2} \tag{3-3} \tag{3-4}$$

三角波落在各區域的機率  $P_{L1}$  ,  $P_{L2}$  ,  $P_{L3}$  如 (3-5) 、 (3-6) 、 (3-7) 所示：

$$P_{L1} = \frac{T_{PL1}}{T} = 0.5 - \frac{V_X - V_{R-}}{2V_A} \tag{3-5}$$

$$P_{L2} = \frac{T_{PL2}}{T} = \frac{V_{R+} - V_{R-}}{2V_A} \tag{3-6}$$

$$P_{L3} = \frac{T_{PL3}}{T} = 0.5 - \frac{V_{R+} - V_X}{2V_A} \tag{3-7}$$

Fig. 3.4 三角波與參考電壓的關係圖

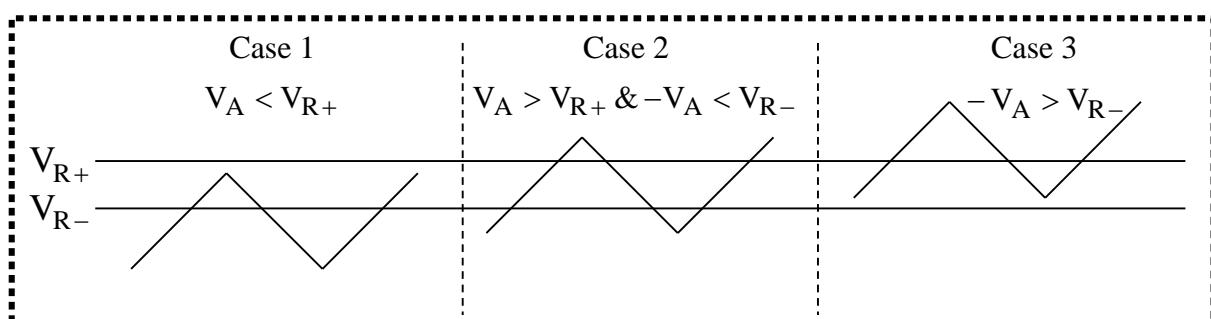

以上推導我們皆假設三角波的峰值超出  $V_{R+}$  ,  $V_{R-}$  , 如 Figure 3.4 , 依其峰值是否超出  $V_{R+}$  ,  $V_{R-}$  , 我們可區分為三種情形：

案例 1 :  $V_A < V_{R+}$  其機率為

$$\left\{ \begin{array}{l} P_{L1} = \frac{T_{PL1}}{T} = 0.5 - \frac{V_X - V_{R-}}{2V_A} \\ P_{L2} = 0.5 + \frac{V_X - V_{R-}}{2V_A} \\ P_{L3} = 0 \end{array} \right.$$

案例 2 :  $V_A > V_{R+}$   $-V_A < V_{R-}$  , 即我們先前所推導的情況。

$$\left\{ \begin{array}{l} P_{L1} = 0.5 - \frac{V_X - V_{R-}}{2V_A} \\ P_{L2} = \frac{V_{R+} - V_{R-}}{2V_A} \\ P_{L3} = 0.5 - \frac{V_{R+} - V_X}{2V_A} \end{array} \right.$$

案例 3 :  $-V_A > V_{R-}$  其機率為

$$\left\{ \begin{array}{l} P_{L1} = 0 \\ P_{L2} = 0.5 + \frac{V_{R+} - V_X}{2V_A} \\ P_{L3} = 0.5 - \frac{V_{R+} - V_X}{2V_A} \end{array} \right.$$

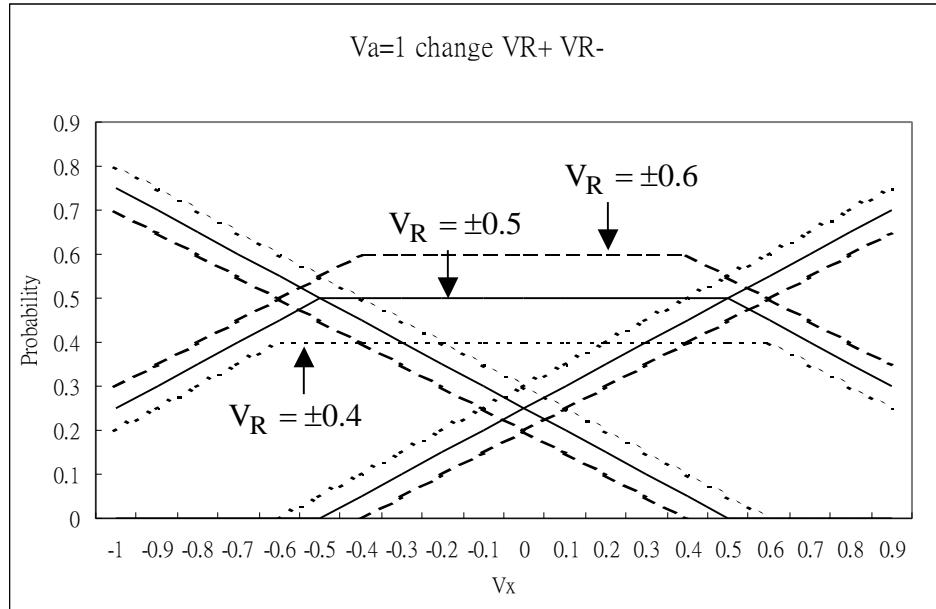

在這裡我們只討論案例 2 的情形，案例 1,3 可以循例得到，依據 (3-5)、(3-6)、(3-7) 式我們可得到如 Figure 3.5 三個機率的曲線圖。由公式我們知道參考電壓  $V_{R+}$  ,  $V_{R-}$  的值會影響機率的曲線。Figure 3.6 描述了不同的參考電壓對機率產生的影響。上面的推導我們皆假設  $V_A$  、  $V_X$  是已知的參數，但實際上的情形是，  $V_X$  ,  $V_A$  是未知的，是我們必需要去量測的值。因此，在實際測量上如何去獲得  $P_{L1}$  ,  $P_{L2}$  ,  $P_{L3}$  的值呢？以下我們將簡述其方法。

當我們經過一段適當的取樣時間，得到足夠的取樣數量後，我們便可從計數器的結果得到  $P_{L1}$ ， $P_{L2}$ ， $P_{L3}$  的值，假設全部的取樣數為  $N$ ，大於  $V_{R+}$  的取樣數為  $N_1$ ，小於  $V_{R-}$  的取樣數為  $N_2$ ，則  $P_{L1}$ ， $P_{L2}$ ， $P_{L3}$  的值如 (3-8)，(3-9)，(3-10) 所示：

$$P_{L1} = \frac{N_2}{N} \quad (3-8)$$

$$P_{L2} = \frac{N - N_1 - N_2}{N} \quad (3-9)$$

$$P_{L3} = \frac{N_1}{N} \quad (3-10)$$

當我們得到  $P_{L1}$ ， $P_{L2}$ ， $P_{L3}$  的值，我們便可計算  $V_A$ ， $V_X$  的值。

Fig. 3.5 三個機率的曲線圖

Fig. 3.6 不同的參考電壓對機率產生的影響

### 3-4 計算三角波的振幅 $V_A$ 及偏壓電壓值 $V_X$

由 Figure 3.4 的典型案例 2 來看，我們可由 (3-1)、(3-2) 聯立方程式來解出  $V_A$  及  $V_X$  值如(3-11)、(3-12)所示：

$$V_A = \frac{V_{R+} - V_{R-}}{2P_{L2}} \quad (3-11)$$

$$V_X = V_{R-} + \frac{0.5 - P_{L1}}{P_{L2}} (V_{R+} - V_{R-}) \quad (3-12)$$

這裡要注意的是，雖然案例二的機率公式有三個，但因為  $P_{L1} + P_{L2} + P_{L3} = 1$ ，故有一個式子是可以被忽略的，另外 Figure 3.4 的其它兩個案例是不正確的，因為對未知的  $V_A$ ， $V_X$  來說這兩個案例的聯立方程式是無解的，由以上的推論結果顯示，我們可以用數位的方法去量測類比波形的振幅及偏壓電壓值。

### 3-5 雜訊對系統影響的分析

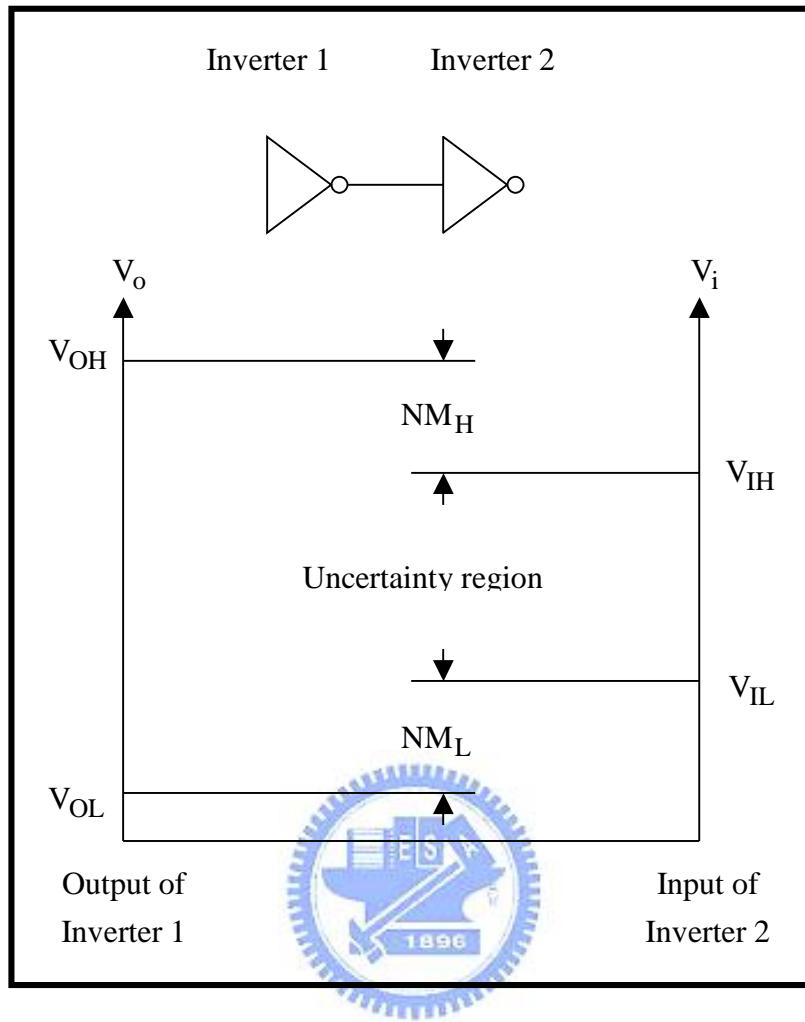

一般當系統在進行量測時，一些系統以外的信號會透過傳輸線影響系統測試或操作的結果，這些外來的信號我們一般稱之為雜訊，雜訊一般都是我們不想要的且被視為對整個系統有壞的影響。因此當我們在進行量測時都要盡量避免系統受到雜訊的干擾。在一般數位或類比電路的 data sheet 中都有所謂的雜訊邊限值，它所代表的就是系統能夠容忍雜訊的能力，當外來的雜訊大到超過雜訊邊限時，系統就有可能因為雜訊的影響而產生錯誤的動作。

Figure 3.7 為雜訊邊限的示意圖，這裡反向器 1 的邏輯 "0" 輸出位準為  $V_{OL}$ ，邏輯 "1" 輸出位準為  $V_{OH}$ ，反向器 2 的輸入低準位為  $V_{IL}$ ，輸入高準位為  $V_{IH}$ ，則其雜訊邊限為  $NM_L = V_{IL} - V_{OL}$ ， $NM_H = V_{OH} - V_{IH}$ 。今假設反向器 1 的輸出邏輯 "0" 準位為 0.2V，而反向器 2 的輸入低準位為 1.2V，則其雜訊邊限  $NM_L = 1.2 - 0.2 = 1V$ 。也就是說今天假設有一雜訊它的大小超過 1V，若此時反向器 1 輸出為邏輯 "0" 時，則反向器 2 就可能會操作在不確定的區域，造成系統運作錯誤。

Fig. 3.7 雜訊邊限的示意圖

一般來說，在混合信號電路中，當數位電路操作在非常高的頻率時，被耦合到類比部份的雜訊，可以被假設為具有高斯分佈的特性。所以我們這裡假設輸入信號的雜訊具有高斯分佈的特性，跟前面推導機率公式一樣，我們將依照三角波跟參考電壓  $V_{R-}$ ， $V_{R+}$  的關係，，將輸入信號區分為：

$L_1 : V < V_{R-} < V_{R+}$ ，  $L_2 : V_{R-} < V < V_{R+}$   $L_3 : V_{R-} < V_{R+} < V$  三個區域

來討論雜訊對量測的影響。

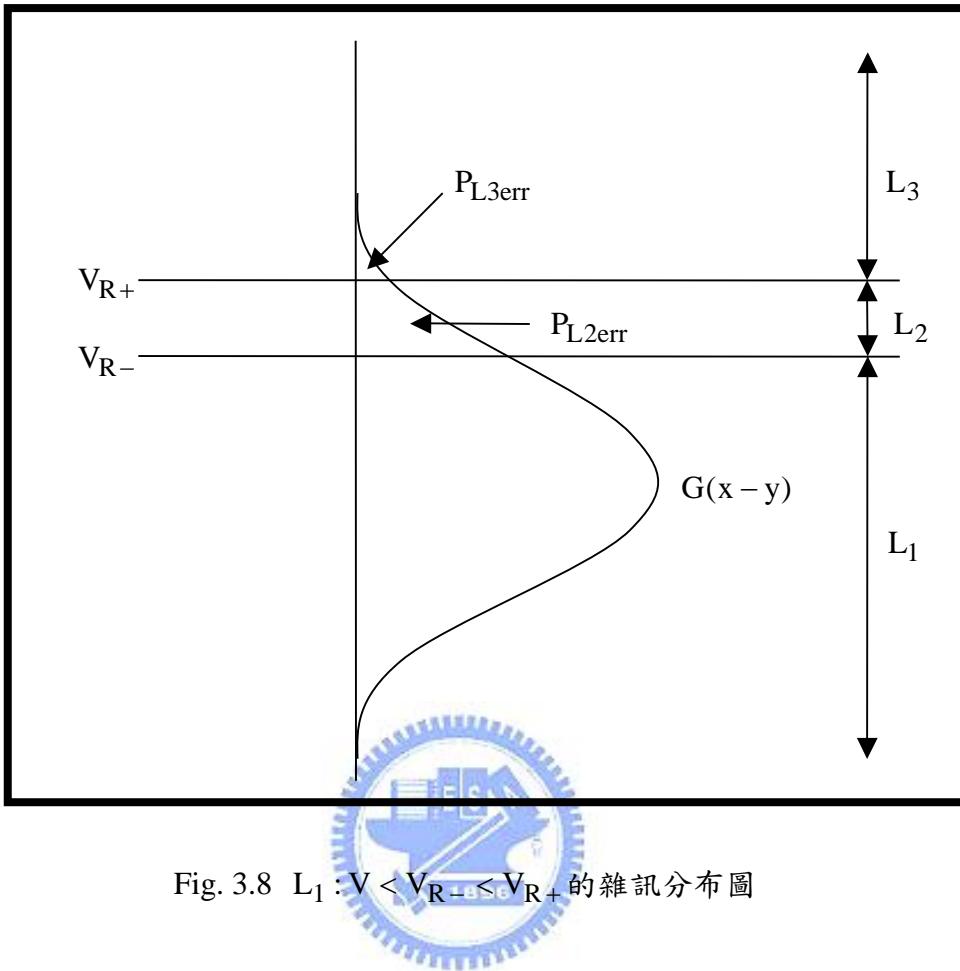

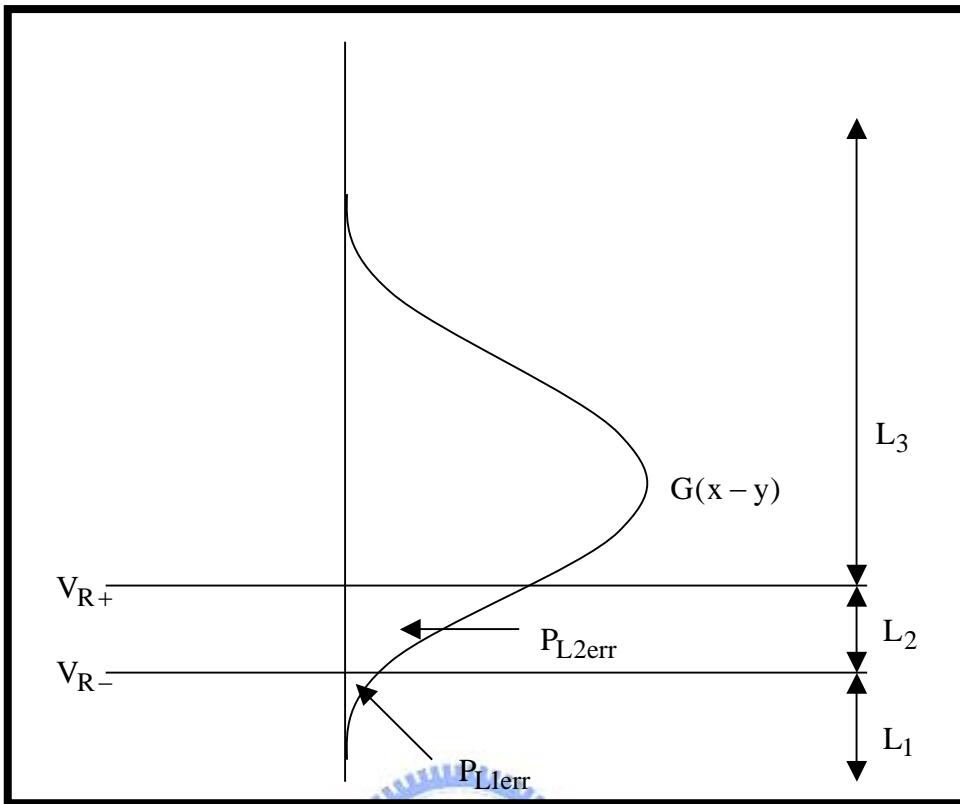

Fig. 3.8  $L_1 : V < V_{R-} < V_{R+}$  的雜訊分布圖

如 Figure 3.8 所示，當輸入信號落在  $L_1$  區，且有一個高斯分配的雜訊時，雜訊對量測可能造成的影響為將輸入信號由原來的  $L_1$  區移到  $L_2$  或  $L_3$  區，其誤差機率如(3-13)所示：

$$\left\{ \begin{array}{l} P_{L2err} = \frac{1}{2V_A} \int_{-V_A}^{V_{R-}} \int_{V_{R+}}^{V_A} G(x-y) dx dy \\ P_{L3err} = \frac{1}{2V_A} \int_{-V_A}^{V_{R-}} \int_{V_{R+}}^{\infty} G(x-y) dx dy \\ P_{L1err} = -(P_{L2err} + P_{L3err}) \end{array} \right. \quad (3-13)$$

$G(x-y)$  是具有高斯分布的雜訊輸入信號，其值如 (3-14) 所示：

$$G(x-y) = \frac{1}{\sqrt{2\pi}\sigma_n} e^{-\frac{(x-y)^2}{2\sigma_n^2}} \quad (3-14)$$

其中  $y$  為輸入信號， $\sigma_n$  為雜訊的標準差。

Fig. 3.9  $L_2 : V_{R-} < V < V_{R+}$  的雜訊分布圖

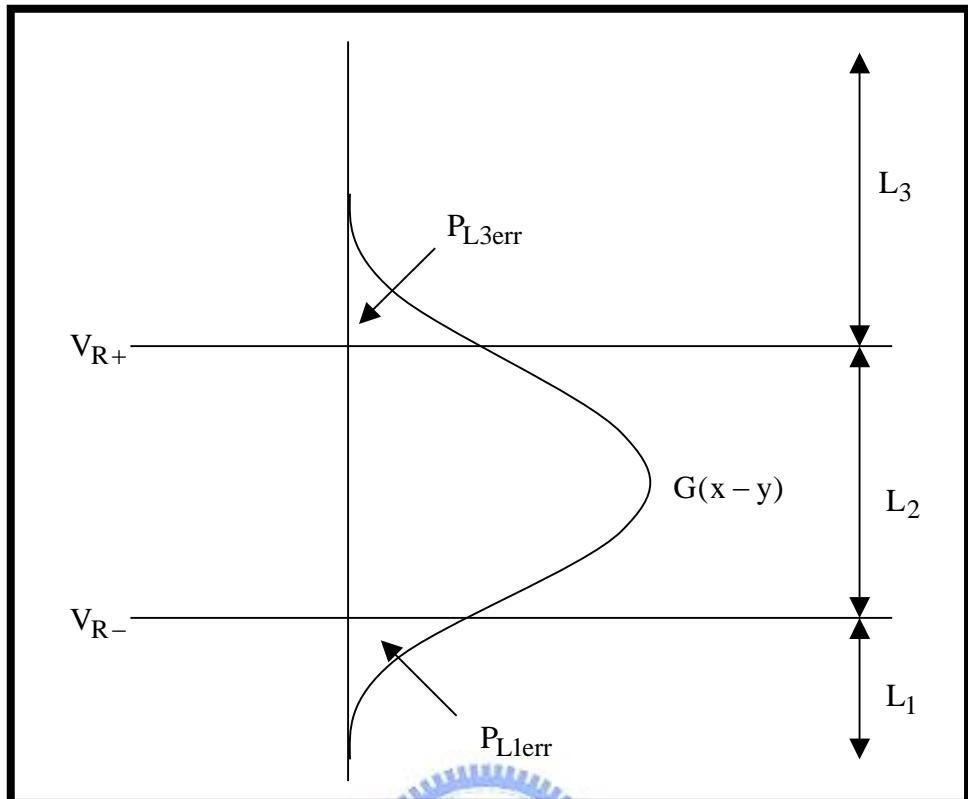

如 Figure 3.9 所示，當輸入信號落在  $L_2$  區時，雜訊對量測可能造成的影響為將輸入信號由原來的  $L_2$  區移到  $L_1$  區或  $L_3$  區，其誤差機率如 (3-15) 所示：

$$\left\{ \begin{array}{l} P_{L1err} = \frac{1}{2V_A} \int_{V_{R-}}^{V_{R+}} \int_{-\infty}^{V_{R-}} G(x-y) dx dy \\ P_{L3err} = \frac{1}{2V_A} \int_{V_{R-}}^{V_{R+}} \int_{V_{R+}}^{\infty} G(x-y) dx dy \\ P_{L2err} = -(P_{L1err} + P_{L3err}) \end{array} \right. \quad (3-15)$$

Fig. 3.10  $L_3 : V_{R-} < V_{R+} < V$  的雜訊分布圖

如 Figure 3.10 所示，當輸入信號落在  $L_3$  區時，雜訊對量測可能造成的影響為將輸入信號由原來的  $L_3$  區移到  $L_1$  區或  $L_2$  區，其誤差機率如 (3-16) 所示：

$$\left\{ \begin{array}{l} P_{L1err} = \frac{1}{2V_A} \int_{V_{R+}}^{V_A} \int_{-\infty}^{V_{R-}} G(x-y) dx dy \\ P_{L2err} = \frac{1}{2V_A} \int_{V_{R+}}^{V_A} \int_{V_{R-}}^{V_{R+}} G(x-y) dx dy \\ P_{L3err} = -(P_{L1err} + P_{L2err}) \end{array} \right. \quad (3-16)$$

將(3-14) , (3-15) , (3-16)的誤差機率加起來即為雜訊對整個三角波所造成 的誤差，其值如(3-17) , (3-18) , (3-19)所示：

$$P_{L1err(total)} = \frac{1}{2V_A} \left( \int_{V_{R-}}^{V_{R+}} \int_{-\infty}^{V_{R-}} G(x-y) dx dy + \int_{V_{R+}}^{V_A} \int_{-\infty}^{V_{R-}} G(x-y) dx dy \right. \\ \left. - \int_{-V_A}^{V_{R-}} \int_{V_{R-}}^{V_{R+}} G(x-y) dx dy - \int_{-V_A}^{V_{R-}} \int_{V_{R+}}^{\infty} G(x-y) dx dy \right) \quad (3-17)$$

$$P_{L2err(total)} = \frac{1}{2V_A} \left( \int_{-V_A}^{V_{R-}} \int_{V_{R-}}^{V_{R+}} G(x-y) dx dy + \int_{V_{R+}}^{V_A} \int_{V_{R-}}^{V_{R+}} G(x-y) dx dy \right. \\ \left. - \int_{V_{R-}}^{V_{R+}} \int_{-\infty}^{V_{R-}} G(x-y) dx dy - \int_{V_{R-}}^{V_{R+}} \int_{V_{R+}}^{\infty} G(x-y) dx dy \right) \quad (3-18)$$

$$P_{L3err(total)} = \frac{1}{2V_A} \left( \int_{V_{R-}}^{V_{R+}} \int_{V_{R+}}^{\infty} G(x-y) dx dy + \int_{-V_A}^{V_{R-}} \int_{V_{R+}}^{\infty} G(x-y) dx dy \right. \\ \left. - \int_{V_{R+}}^{V_A} \int_{-\infty}^{V_{R-}} G(x-y) dx dy - \int_{V_{R+}}^{V_A} \int_{V_{R-}}^{V_{R+}} G(x-y) dx dy \right) \quad (3-19)$$

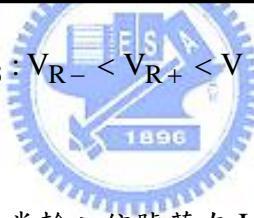

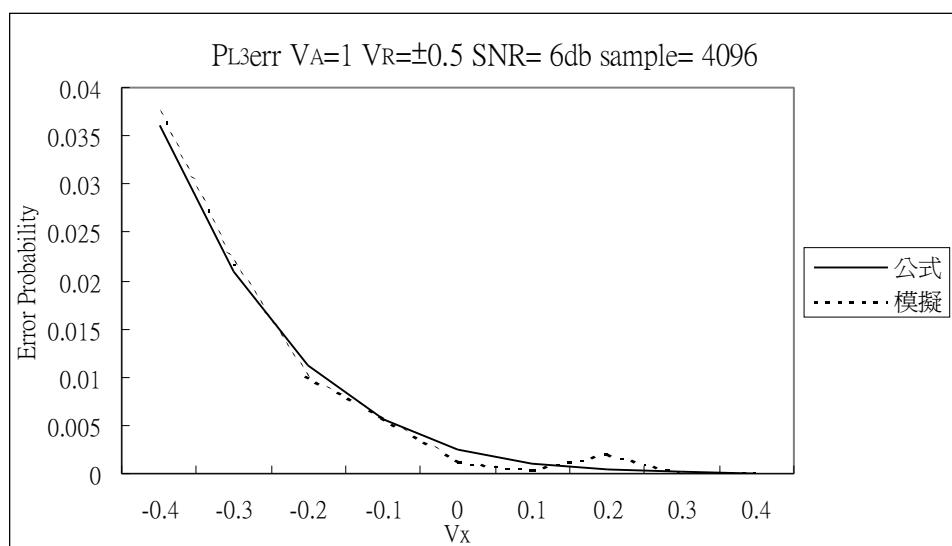

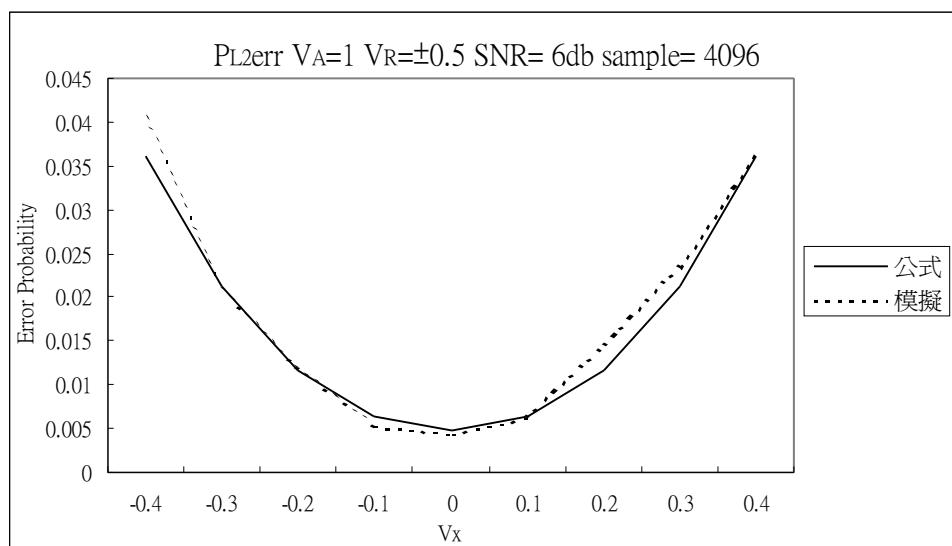

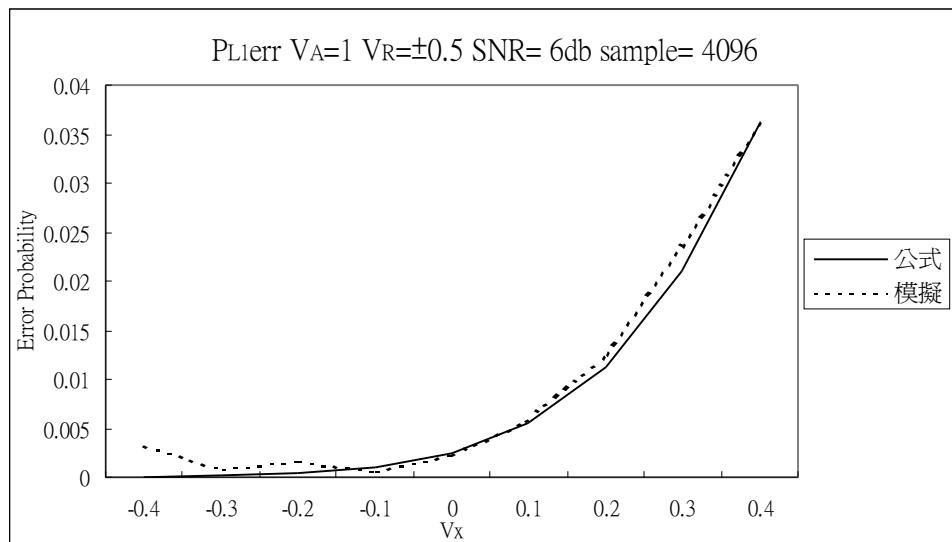

依據前面的計算，我們可以得到雜訊誤差機率的 Table 及曲線如 Table3-1 與 Figure 3.11 所示。誤差機率的曲線跟參考電壓及雜訊的大小有關，Figure 3.12 為誤差機率與參考電壓的關係圖。我們可以發現當偏壓電壓落再正負參考電壓之內時，誤差機率會隨參考電壓值變小而減少。Figure 3.13 為誤差機率與雜訊大小的關係圖，當雜訊越大時其機率誤差也跟著變大。為了驗證所推導的機率公式，我們在模擬中加入了隨機的高斯分佈的雜訊，Figure 3.14 為其模擬的結果。在這一個模擬中我們取了 4096 點來做比對，實心曲線跟片斷曲線分別代表推導的誤差機率值及模擬的誤差機率結果。由圖可看出雜訊的模擬跟機率推導是吻合的。

由 Table 3-1 我們可發現在  $SNR=6dB$  時雜訊所造成的機率誤差值最大為 0.036，其值非常的小，故雜訊對我們所提出的方法影響相當有限。

| Va=1 SNR=6dB |         |         |         | Va=1 SNR=12dB |         |         |

|--------------|---------|---------|---------|---------------|---------|---------|

| Vx           | PL1err  | PL2err  | PL3err  | PL1err        | PL2err  | PL3err  |

| -0.4         | 0.00005 | 0.03615 | 0.0361  | 0.00005       | 0.02105 | 0.021   |

| -0.3         | 0.00015 | 0.02115 | 0.021   | 0.00005       | 0.0113  | 0.0112  |

| -0.2         | 0.00035 | 0.0116  | 0.01125 | 0.00015       | 0.0057  | 0.0055  |

| -0.1         | 0.001   | 0.0065  | 0.0055  | 0.0004        | 0.0029  | 0.0025  |

| 0            | 0.00245 | 0.0049  | 0.00245 | 0.001         | 0.002   | 0.001   |

| 0.1          | 0.0055  | 0.0065  | 0.001   | 0.0025        | 0.0029  | 0.0004  |

| 0.2          | 0.01125 | 0.0116  | 0.00035 | 0.0055        | 0.0057  | 0.00015 |

| 0.3          | 0.021   | 0.02115 | 0.00015 | 0.0112        | 0.0113  | 0.00005 |

| 0.4          | 0.0361  | 0.03615 | 0.00005 | 0.021         | 0.02105 | 0.00005 |

Table 3.1 雜訊誤差機率

Fig. 3.11 誤差機率的曲線

Fig. 3.12 誤差機率的曲線跟參考電壓關係圖

Fig. 3.13 誤差機率的曲線跟雜訊的關係

Fig. 3.14 誤差機率推導與模擬比較結果

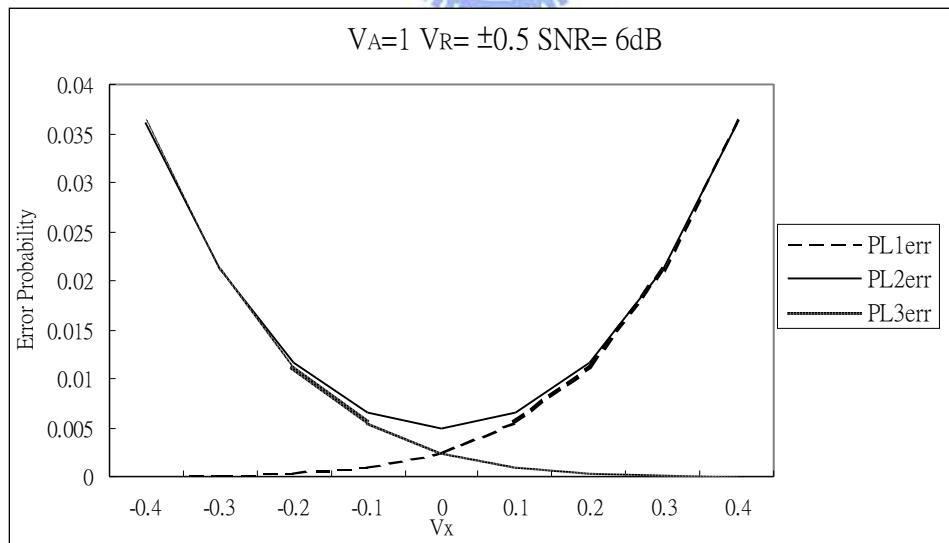

### 3-6 參考電壓的選擇

由前一節我們知道參考電壓跟雜訊對系統的影響有很大的關係，因此如何決定參考電壓以獲得較小的量測誤差是一個很重要的問題。這一節我們將探討如何選擇適當的參考電壓，為了研究這個問題我們做了以下的程式模擬，我們在不同的參考電壓下加入訊號與雜訊比為 6dB 的雜訊。這裡三角波的振幅設為 1V 偏壓電壓以每次 0.1V 的間距由 -1V 掃到 1V，參考電壓依序設為  $\pm 0.1V$ 、 $\pm 0.4V$ 、 $\pm 0.5V$  及  $\pm 0.6V$ 。

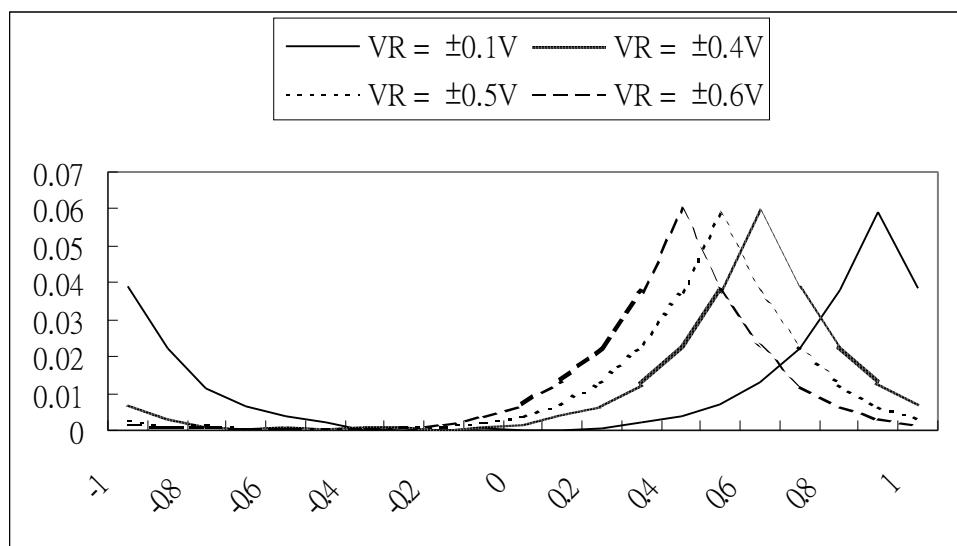

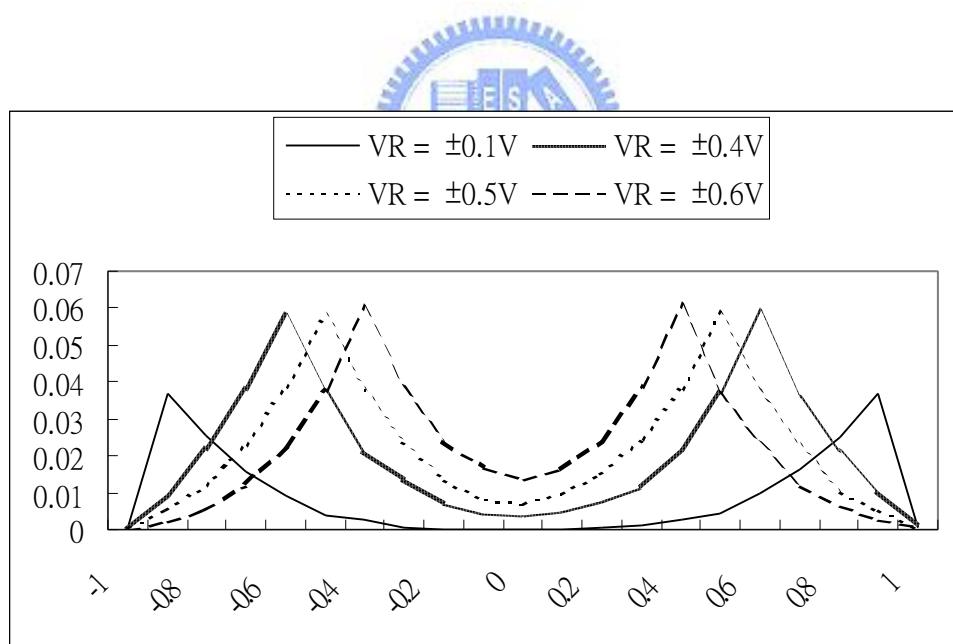

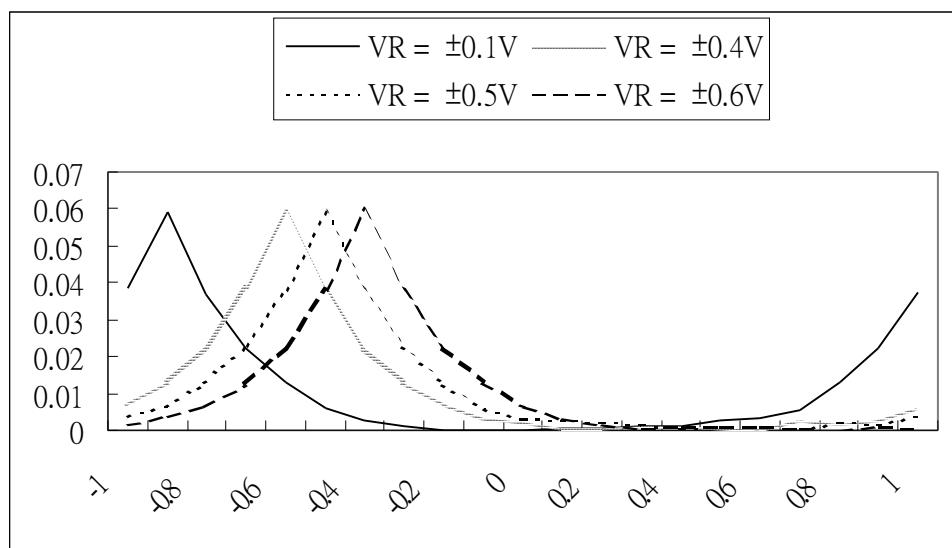

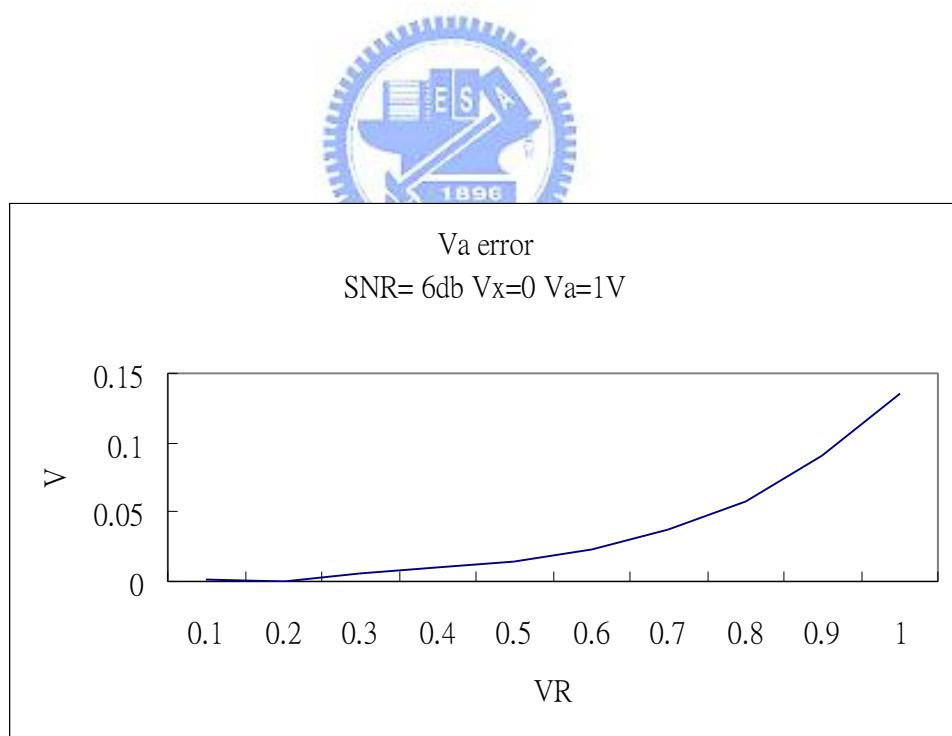

Figure 3.15 ~ Figure 3.17 分別是模擬出來的  $P_{L1}$ 、 $P_{L2}$  及  $P_{L3}$  的機率誤差圖，我們以 Figure 3.16 來加以說明。Figure 3.16 是  $P_{L2}$  的機率誤差圖，我們可以發現當偏壓電壓靠近  $\pm 1V$  時，誤差的大小依序為  $V_R = \pm 0.1V > V_R = \pm 0.4V > V_R = \pm 0.5V > V_R = \pm 0.6V$ 。但是當偏壓電壓  $-0.5V < V_X < 0.5V$  時，誤差的大小剛好相反，即  $V_R = \pm 0.6V > V_R = \pm 0.5V > V_R = \pm 0.4V$ 。這個結果表示當偏壓電壓  $V_X$  落在中心的範圍之內時，參考電壓設的越小則雜訊所引起的誤差就越小。反之，若偏壓電壓  $V_X$  落在外圍的範圍時，參考電壓設的越小則雜訊所引起的誤差反而越大。Figure 3.18 為  $V_A = 1V$ 、 $V_X = 0V$ 、 $V_R$  由  $\pm 0.1V$  掃到  $\pm 1V$  的誤差圖，我們可以發現當  $V_R$  越小時其誤差越小，而當  $V_R$  越大時其誤差就越大。

Fig. 3.15  $P_{L1}$  的誤差機率圖

Fig. 3.16  $P_{L2}$  的誤差機率圖

Fig 3.17  $P_{L3}$  的誤差機率圖

Fig 3.18 不同參考電壓下的誤差圖

### 3-7 信賴區間及取樣點數

當我們在抽取樣本時，除考慮選擇一個較好的抽樣方法外，亦必需考慮所要選取的樣本數。因為樣本數的多寡，會影響估計結果的正確性。當樣本數愈多，抽樣成本雖較高，但可獲得較多的資訊，其估計誤差會較小，正確性較高。反之，若樣本數較少，雖抽樣成本較低，但其估計誤差較大，故在選樣本時，應同時考慮抽樣成本與減少估計誤差所產生的利益，比較成本與效益後選擇一個最佳的樣本數。

所謂信賴水準是指我們對於估計出來的區間包含母體參數值的信心或信賴度。信賴水準以  $1 - \alpha$  表示， $\alpha$  代表錯誤的機率，例如 95% 的信賴水準是指在此信賴水準下所建立的區間有 95% 的機率會包含母體參數的真值。信賴區間是指在一個給定的信賴水準下所構成的一個區間，是由樣本統計量及抽樣誤差所構成的一個(包含上限，下限)的區間。這裡，我們假設輸入信號落在 L2 區域的機率是 P，而此事件只有落在跟不落在 L2 區域兩個可能，依據 Binomial Distribution 其變異數為：

$$\sigma^2 = P * (1 - P)$$

由中央極限定理，我們知道在取樣數很大時，不管原本的母體分配為何，樣本平均數的抽樣分配近似常態分配，其變異數為：

$$\sigma^2 = \frac{P * (1 - P)}{N}$$

這裡，N 是取樣點數，因此，信賴區間就等於：

$$m * \frac{\sqrt{P * (1 - P)}}{\sqrt{N}}$$

m 是表示信賴水準的因子，它與信賴水準的關係如 Table3.2 所示。當 m = 3 時表示信賴水準等於 99.73%，因此當我們想要在信賴水準為 99.73% 時，誤

差小於等於  $d$  值，則其須取樣的點數  $N$ ，須滿足以下的方程式：

$$N \geq 3^2 \frac{P * (1 - P)}{d^2}$$

| <b>m</b> | <b>Confidence level (%)</b> |

|----------|-----------------------------|

| 1        | 68.27                       |

| 1.96     | 95                          |

| 2        | 95.45                       |

| 2.58     | 99                          |

| 3        | 99.73                       |

| 4        | 99.99                       |

Table 3.2 信賴水準的因子

## 第四章 程式模擬

### 4-1 概論

在這一章我們將利用程式的模擬來驗證我們所提出的測試方法，我們會進行四種不同情況模擬。首先我們會模擬在不加雜訊及取樣點數相同的情形下，隨機取樣及均勻取樣的結果。接下來我們會觀察在不同的取樣點數下隨機取樣方式的結果。第三種情形我們會模擬雜訊大小對系統的影響。最後，我們比較在不同的取樣點數下，雜訊的大小跟取樣點數的關係。

### 4-2 隨機取樣及均勻取樣的模擬

在這一節裡，我們首先比較隨機取樣及均勻取樣的不同。在模擬程式裡，我們設定三角波的振幅  $V_A$  為 1V，比較器的參考電壓  $V_{R-}$ 、 $V_{R+}$  為  $\pm 0.5V$ ，取樣點數為 1024 點，三角波的偏壓電壓值  $V_X$  以每次 0.1V 的間隔由  $-1V$  增加到  $1V$ 。兩種取樣方法各做 64 次，取其平均值及標準差並反推其  $V_A$  及  $V_X$  值，計算  $V_A$  及  $V_X$  的誤差。

Figure 4.1 是均匀取樣的機率圖，我們可以看到均匀取樣的機率圖跟我們用公式推導所產生的機率圖非常相像，它的機率曲線幾乎都是平的。Figure 4.2 是隨機取樣的機率圖，因為量化誤差的關係，隨機取樣的機率圖形會有一些抖動，沒有辦法像均匀取樣那樣的平坦。Figure 4.3 是均匀取樣的標準差圖，均匀取樣的標準差幾乎都為 0。Figure 4.4 是隨機取樣的標準差圖，跟均匀取樣比起隨機取樣的標準差相對較大。Figure 4.5, Figure 4.6 是均匀取樣與隨機取樣的  $V_A$  及  $V_X$  誤差的比較圖，我們可以清楚看到隨機取樣的誤差大於均匀取樣的誤差。

Fig. 4.1 均匀取樣的機率圖

Fig. 4.2 隨機取樣的機率圖

Fig. 4.3 均匀取樣的標準差圖

Fig. 4.4 隨機取樣的標準差圖

Fig. 4.5  $V_A$  的誤差圖

Fig. 4.6  $V_X$  的誤差圖

#### 4-3 不同的取樣點數模擬

這一節裡，我們主要是模擬在取樣點數不同的情況下，隨機取樣方法的結果為何，模擬的參數幾乎都跟前一節一樣，不同點為我們這裡的取樣點數分別設為 256 點，1024 點及 4096 點。

Figure 4.7 是三個不同取樣點數的機率圖，我們可以發現當取樣點數由 256 點增加到 4096 點時機率曲線愈平坦，也就是說當取樣點數愈多時其圖形愈接近理論值。Figure 4.8 是三個不同取樣點數的標準差圖，256 點的標準差大約是 1024 點的 2 倍，而 1024 點的標準差大約是 4096 點的 2 倍。所以當取樣點數增加四倍時，標準差會減少為原來的一半，這符合了  $\sigma_n = \frac{\sigma}{\sqrt{n}}$  的公式。Figure 4.9、Figure 4.10 是三個不同取樣點數的  $V_A$  及  $V_X$  的誤差比較圖，由圖可清楚看出誤差的大小依序為 256 點  $>$  1024 點  $>$  4096 點，也就是說當取樣的點數越多所量測出來的結果誤差會越小。

Fig. 4.7 256, 1024, 4096 機率圖

Fig. 4.8 256, 1024,4096 標準差的圖

Fig. 4.9  $V_A$  的誤差圖

Fig. 4.10  $V_X$  的誤差圖

#### 4-4 雜訊影響的模擬

這一節裡，我們主要是模擬雜訊對系統的影響，我們加入的是具有常態分佈特性的雜訊，其訊號與雜訊比 SNR 分別為 6db、12db 及 18db，其相對應的雜訊標準差為  $\sigma_{6\text{db}} = 0.2893$ ， $\sigma_{12\text{db}} = 0.145$ ， $\sigma_{18\text{db}} = 0.0727$ 。

Figure 4.11 是三個不同雜訊的機率圖，我們可發現訊號與雜訊比為 6db 的機率曲線較訊號與雜訊比為 18db 的機率曲線彎曲，所以當雜訊愈大其圖形失真的越嚴重。Figure 4.12 是三個不同雜訊的標準差圖，由於我們設定的取樣方法是隨機取樣 1024 點其量化誤差較大，所以這裡比較看不出雜訊對標準差的影響。Figure 4.13、Figure 4.14 是三個不同雜訊的  $V_A$  及  $V_X$  誤差比較圖，我們很明顯的可以看出訊號與雜訊比為 6db 的誤差大於訊號與雜訊比為 18db 的誤差，也就是說當雜訊愈大其誤差也愈大。

Fig. 4.11 SNR = 6 dB, 12dB, 18dB 的機率圖

Fig. 4.12 SNR= 6dB, 12dB, 18dB 標準差的圖

Fig. 4.13 SNR= 6dB, 12dB, 18dB  $V_A$  的誤差圖

Fig. 4.14 SNR=6dB, 12dB, 18dB  $V_X$  的誤差圖

#### 4-5 雜訊與取樣點數的關係

再前面三節裏，我們知道當取樣點數越多則所得到的測試結果越準確，當雜訊越大時測試結果的誤差越大。這一節我們將討論雜訊的大小跟取樣點數間的關係。這裡取樣點數依序設為 256、1024 及 4096 點，加入的雜訊大小為  $SNR = 6dB$ 、 $12dB$  及  $18dB$ ，其相對應的雜訊標準差為  $\sigma_{6db} = 0.2893$ 、 $\sigma_{12db} = 0.145$  及  $\sigma_{18db} = 0.0725$ 。

Figure 4.15 表示不管雜訊大小為何，其標準差皆會隨著取樣點數的增加而減少。Figure 4.16 顯示當雜訊固定時，誤差的大小與取樣點數沒有太大的關係，這是因為我們取樣的方法為均勻取樣，當我們取 256、1024、4096 點時所取到的點都不同，故無法看到重複取樣的效果。一般來說，當取樣點數增加一倍時  $SNR$  將增加 3dB，也就是說  $SNR=12dB$  取樣點數為 256 的條件，跟  $SNR=6dB$  取樣點數為 1024 的條件所造成的誤差一樣。但由 Figure 4.17 我們發現其誤差並不相同， $SNR$  較大的條件下誤差還是較大，也就是說雜訊的大小主宰了誤差的大小，這是因為我們剛剛所提到的，不同的取樣點數所取到的點不同所造成的。

Fig. 4.15 不同的雜訊與取樣點數的標準差圖

Fig 4.16 不同的雜訊與取樣點數的誤差圖

Fig 4.17 誤差比較圖

## 第五章 結論

在這一篇論文裏，我們提出了一個以 IEEE std. 1149.4 DFT 架構為基礎的數位化類比動態測試方法。我們主要是利用一對設定好參考電壓的比較器對一個待測的三角波信號進行取樣，當完成適當的取樣點數後，我們可從比較器的二元輸出得到相關的機率值。經由計算一次聯立方程式我們便可得到待測三角波的偏壓電壓及振幅大小。為了探討我們提出的測試方法，我們對相關的機率進行公式推導，並且對影響機率值的各項參數進行個別的分析，進而了解各項參數對機率值的影響。對於一般系統最關心的雜訊影響方面，我們針對三角波與參考電壓的相對關係，將信號分成三個區域進行雜訊的分析，最後將這三個區域的雜訊影響整合起來得到了雜訊對三角波的整體影響。由公式推導及程式的模擬結果，我們發現雜訊對我們所提出的測試方法影響並不大，在訊號與雜訊比為 6dB 時其機率誤差值最大為 0.036。在測試準確度上面，我們介紹了信賴水準及信賴區間的觀念，並依據指定的信賴水準推導出最小誤差值與需要取樣的點數關係式。

為了驗證我們所提出的測試方法的可行性，我們進行了四種情況的程式模擬，首先，我們針對不同的取樣方法進行模擬。我們比較隨機取樣及均勻取樣兩種不同的取樣方式，結果證明隨機取樣因為有量化的誤差存在，其機率的標準差

及計算出來的振幅及偏壓電壓的誤差都比均勻取樣大。再來我們對不同的取樣點數進行模擬，我們分別取 256 點、1024 點及 4096 點，模擬結果告訴我們，當取樣的點數越多時機率的標準差及誤差會比取樣點數少時為佳，這符合我們的統計觀念。第三種模擬是雜訊的影響，我們加入了訊號與雜訊比為 6dB、12dB 及 18dB 的雜訊到訊號中，模擬結果與我們預期的一樣，當雜訊越大時所產生的誤差就越大。最後一個模擬是雜訊與取樣點數的關係，我們在個別的取樣點數上加入雜訊，一般而言當取樣點數增加一倍時 SNR 會改進 3dB，模擬的結果也證明了這個論點。最後的結論，由以上的模擬我們確定了本論文所提出的測試方法不僅簡單而且是可行的

## 參考文獻

- [1] IEEE Standard for a Mixed signal Test Bus , IEEE Std 1149.4 , IEEE , 1999.

- [2] W.J Wang, C.H. Wang, C.C Su, and I.S. Tseng, “A Novel LCD Driver Testing Technique Using Logic Test Channels,” Proc. Asia South Pacific Design Automation Workshop, 2003, pp.657-662.

- [3] J.L. Huertas, D. Vazquez, and A. Rueda, ”On-line testing of switching capacitor filter,” Proc. VLSI Test Symposium, 1992, pp.102-106.

- [4] J. Velasco-Medina, M. Nicolaidis, and M. Lubaszewski, “An approach to the on-line testing of operational amplifiers,” Proc. Asian Test Symposium, 1998, pp. 290-295.

- [5] H.B Yoon, A. Chatterjee, J.L.A. Hughes, “Optimal design of checksum-based checkers for fault detection in linear analog circuit,” Proc. Int’l Conference on VLSI Design, 1997, pp.393-397.

- [6] L. Schnell (edit), “Technology of electrical measurement,” John Wiley & Sons, 1993.

- [7] Chauchin Su; Chih-Hu Wang; Wei-Juo Wang; Tseng, I.S.; “1149.4 based on-line quiescent state monitoring technique,” Proc. IEEE VLSI Test Symposium, 2003, pp. 197-202.

## 簡歷

我的名字叫王煌文，民國六十一年生，家住彰化縣和美鎮，家裡成員包含爸爸，媽媽，哥哥，大嫂，我在家排行老么，自小即受到父母嚴格管教，故在待人處事方面皆能格守本分，在求學的路途上倒也一路順遂。從逢甲大學電子系畢業後即入伍服役，在軍中擔任班長一職，從中學到如何管教部屬及執行上級指派的任務，同時也學習到如何與各行各業的人相處，退伍後首先進入英群電腦公司擔任產品工程師，負責的產品是 CDROM，半年後進入世界先進公司擔任測試工程師，主要工作為測試機台的維護 Laser program 開發及不良產品的分析，於民國九年進交通大學碩士在職專班進修，並於九十三年取得碩士學位。