# 國立交通大學

## 電子工程學系 電子研究所

# 博士論文

適用於高能源效率晶片之 可感知變異超低電壓設計

Variation-Aware Ultra-Low Voltage Design for Energy Efficient Chips

研究生:張銘宏

指導教授:黃威教授

中華民國一〇一年六月

#

## 可感知變異超低電壓設計

### Variation-Aware Ultra-Low Voltage Design for Energy Efficient Chips

| 研 | 究 | 生 | : | 張銘宏 | Student : Ming-Hung Chang | 3 |

|---|---|---|---|-----|---------------------------|---|

|   |   |   |   |     |                           |   |

指導教授: 黃 威 教授 Advisor: Prof. Wei Hwang

### 國立交通大學

電子工程學系 電子研究所

### 博士論文

A Dissertation Submitted to Department of Electronics Engineering and Institute of Electronics College of Electrical and Computer Engineering National Chiao Tung University in partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in Electronics Engineering

> June 2012 Hsinchu, Taiwan, Republic of China

### 適用於高能源效率晶片之可感知變異超低電壓設計

學生:張銘宏

#### 指導教授:黃威教授

國立交通大學電子工程學系電子研究所博士班

#### 摘要

###

本論文提出一具備高能源效率設計之動態電壓頻率調整平台。高能源效率設計包括超低 電壓溫度感測器、可感知變異之頻率產生器、高可靠度之超低電壓靜態記憶體與先進先出記憶 體。以上述先進先出記憶體作為驗證電路,實現一個高穩定性的動態電壓頻率系統設計。

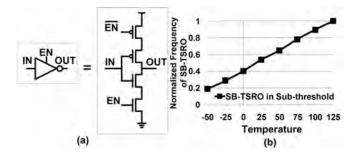

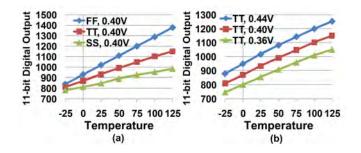

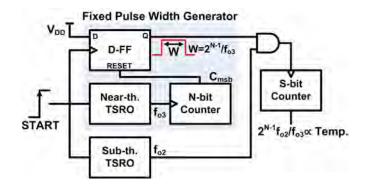

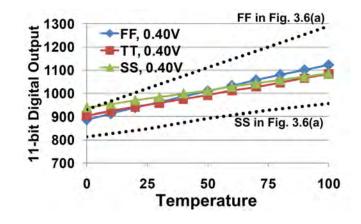

超低電壓全晶上頻率基底之溫度感測器可工作於 0.4V 與 0°C~100°C 溫度範圍內,每秒 可有效偵測 45k 次,使用一位元校正機制下,僅有-1.81°C~+1.52°C 的溫度誤差,其實現於 TSMC 65nm 製程下,使用面積為 990µm<sup>2</sup>。Logical effort 是數位設計者常用之技巧,但傳統 的 Logical effort 並未考慮 CMOS 操作於不同工作區間,以及溫度和製程對其造成的影響,本 論文提出一個可應用在 0.1V~1V 間的統一 Logical effort,並且可減少溫度和製程變化所造成 的延遲估計誤差。根據上述的統一 Logical effort,本論文設計一超低電壓頻率產生器,其內建 的感測器可提供資訊動態自我調整鎖定區間誤差,此技術實現於 UMC 65nm 製程下,可產生 625kHz 及 5MHz 最高頻率輸出分別在 0.2V 與 0.5V 下,且其消耗的功率僅各有 0.18µW 與 5.17µW,同時本頻率產生器可合成出 1/8 至 4 倍於參考頻率之輸出。

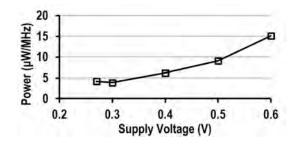

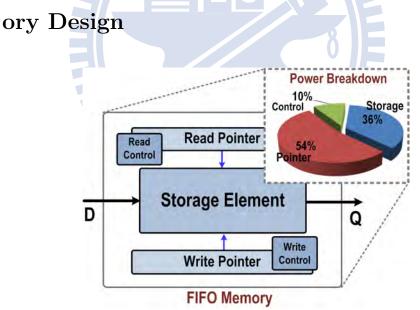

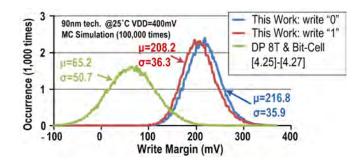

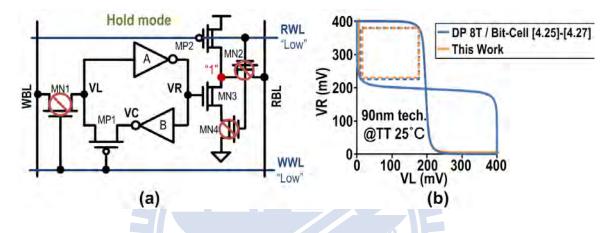

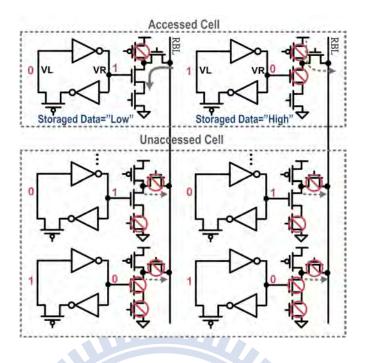

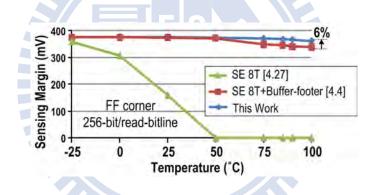

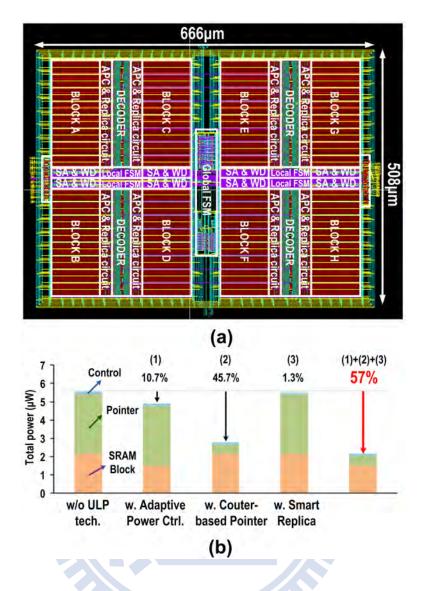

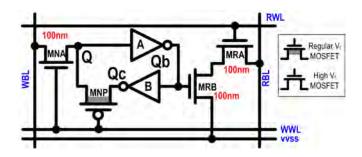

本論文設計一運用打斷正回授正反器迴圈以改善寫入能力之 9T 靜態記憶體,本記憶體同時具備讀取緩衝以增進寫入可靠度與降低漏電電流,位元交錯結構也可與本靜態記憶體交錯運用以提高軟錯誤的抵抗能力,本靜態記憶體實現於 UMC 65nm 製程下,可工作於電壓為 0.3V 以 909kHz 頻率操作且僅消耗最低能源 3.51µW。為提供無線近身網路系統良好的儲存單元,本論文設計一以 10T 靜態記憶體基底之先進先出記憶體,該先進先出記憶體實現於 UMC 90nm 製程下,可工作於電壓為 0.4V 以 50kHz 頻率操作寫入僅消耗最低能源 2.09µW,同時以 625kHz 頻率操作讀取僅消耗最低能源 2.25µW。

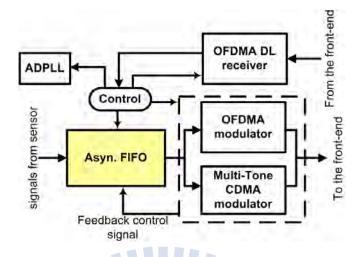

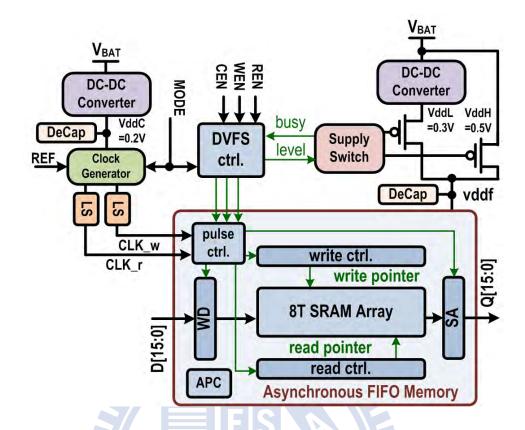

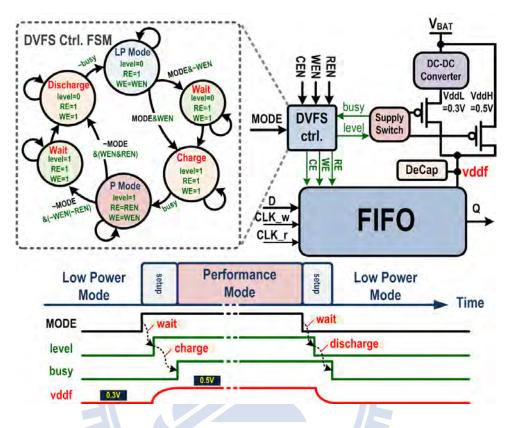

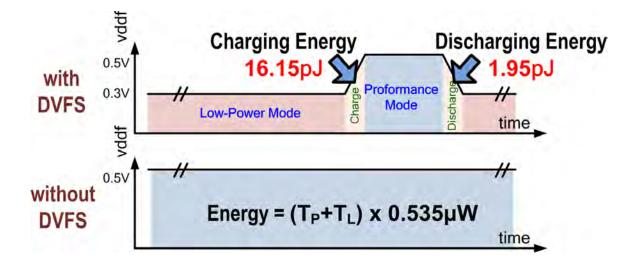

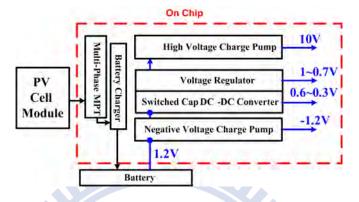

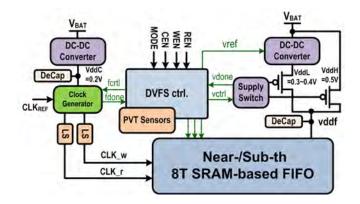

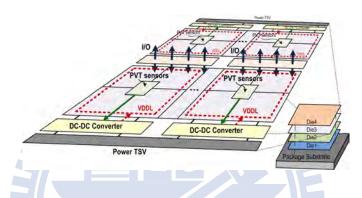

本論文提供一具備高能源效率設計之動態電壓頻率調整平台,以8T 靜態記憶體基底之先 進先出記憶體作為展示電路,提供兩種工作模式:低電壓(0.3V)與高效能(0.5V),若其持續工 作於低電壓模式時可節省 69.5%功率消耗,本平台可適用於高穩定性之無線近身網路應用。

## Variation-Aware Ultra-Low Voltage Design for Energy-Efficient Chips

Student : Ming-Hung Chang

Advisor : Prof. Wei Hwang

### Department of Electronics Engineering & Institute of Electronics National Chiao-Tung University

#### <u>Abstract</u>

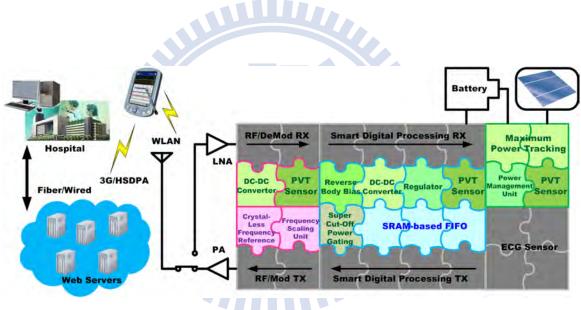

Energy efficient design is a k ey focus in emerging energy-constrained platforms. Dynamic voltage frequency scaling (DVFS) platform with energy-efficient designs are presented in this thesis. Ultra-low voltage temperature sensor and variation-aware clock generator are implemented to enable DVFS platform. Robust near-/sub-threshold SRAM/FIFO memories are designed as the test vehicle of DVFS platform.

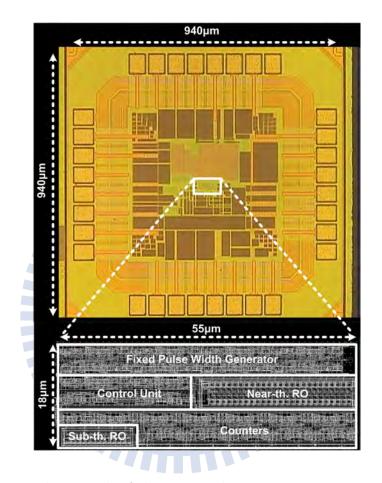

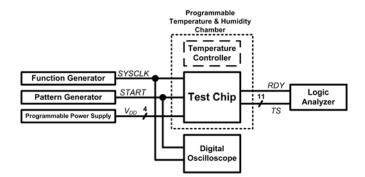

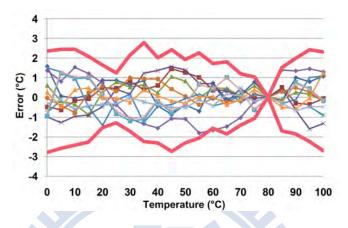

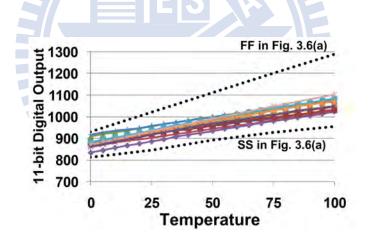

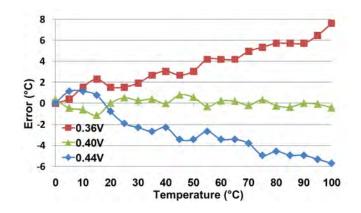

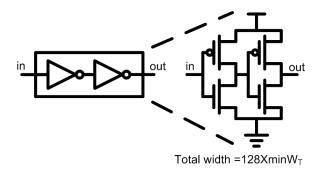

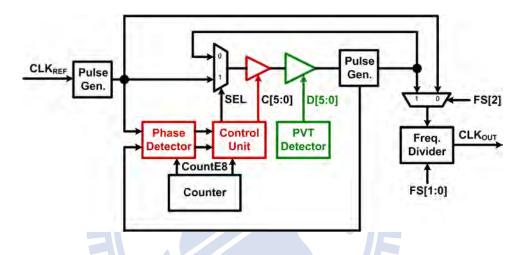

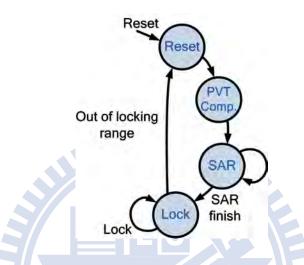

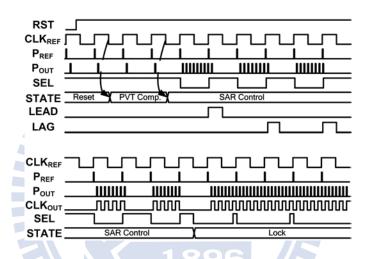

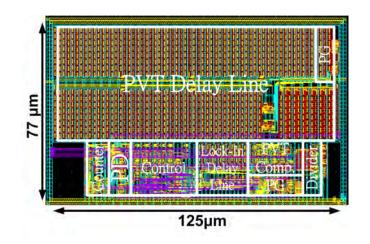

An ultra-low voltage fully integrated frequency-domain smart temperature sensor is presented. With one-point calibration, a -1.81°C~ +1.52°C inaccuracy over a 0°C~100°C temperature operation range has been measured for 12 test chips. At a conversion rate of 45k samples/s, the proposed temperature sensor consumes an average power of 520nW and achieves 0.49°C/LSB at 11-bit output resolution. It occupies only 990µm<sup>2</sup> in a TSMC 65-nm general purpose bulk CMOS process. The voltage-/temperature-induced delay estimation error of conventional logical effort is much more severe in near-/sub-threshold region. Super-/near-/sub-threshold logical effort models are presented eliminate delay estimation error caused by voltage and temperature variations. A to near-/sub-threshold programmable clock generator is also presented in this thesis. The major challenge of the ultra-low voltage (ULV) circuits is that the lock-in range of the delay line is easily affected by the environmental variations. In the proposed clock generator, there is a PVT compensation unit which consists of a set of delay line and a PVT detector. The unit is responsible for adjusting the lock-in range of clock generator to guarantee successful clock lock. In addition, it has the ability to generate the output clock with frequency from 1/8 to 4 times of the reference clock. The clock generator has been designed using UMC 65nm CMOS technology. The frequencies of reference clock are 625 KHz at 0.2V and 5MHz at 0.5V. The power consumptions are 0.18µW and  $5.17\mu$ W, respectively, at 0.2V and 0.5V. The core area of this clock generator is 0.01mm<sup>2</sup>.

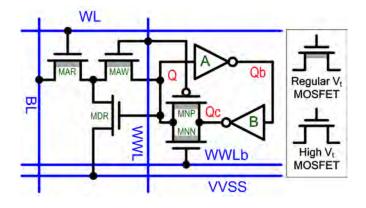

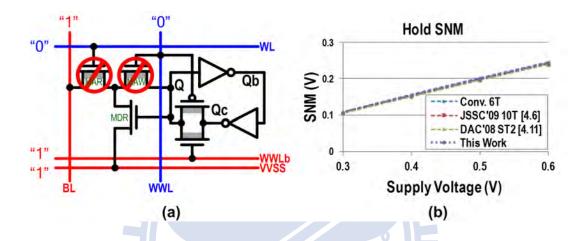

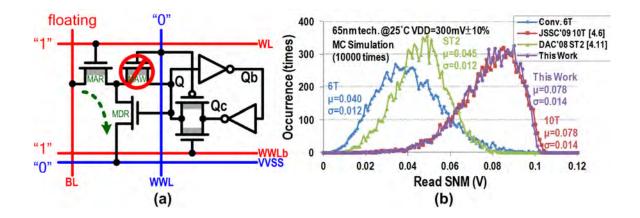

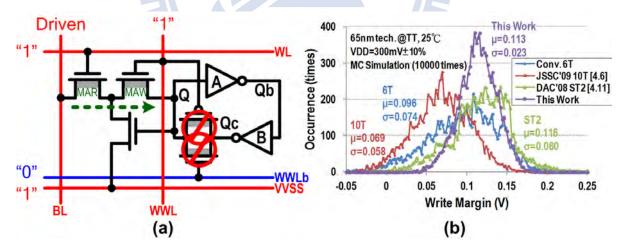

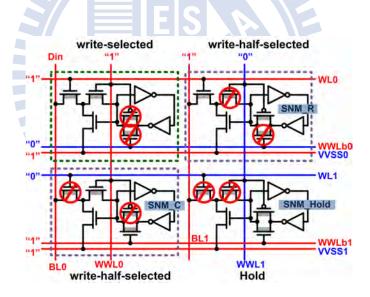

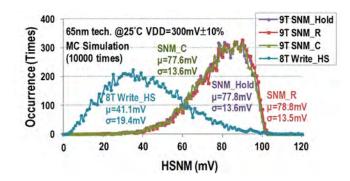

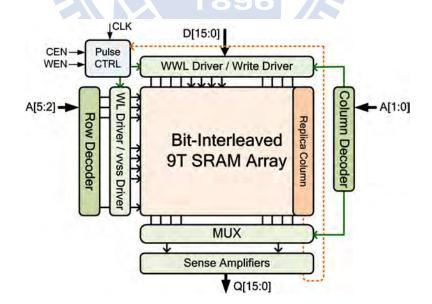

A 9T SRAM bit-cell is presented to enhance write ability by cutting off the positive feedback loop of SRAM cross-coupled inverter pair. In read mode, an access buffer is designed to isolate storage node from read path for better read robustness and leakage reduction. Bit-interleaving scheme is allowed by incorporating the proposed 9T SRAM bit-cell with additional write-wordlines (WWL/WWLb) for soft error tolerance. A 1Kbit 9T 4-to-1 bit-interleaved SRAM is implemented in 65nm bulk CMOS technology. The experimental results demonstrate that the test chip minimum energy point occurs at 0.3V supply voltage. It can achieve an operation frequency of 909kHz with 3.51µW active power consumption. An ultra-low power (ULP) 16Kbit SRAM-based first-in first-out (FIFO) memory is also presented for wireless body area networks (WBANs). The proposed FIFO memory is capable of operating in ultra-low voltage (ULV) regime with high variation immunity. An ULP near-/sub-threshold 10 transistors (10T) SRAM bit-cell is proposed to be the storage element for improving write variation in ULV regime and eliminate the data-dependent bit-line leakage. The proposed SRAM-based FIFO memory also features adaptive power control circuit, counter-based pointers, and a smart replica read/write control unit. The proposed FIFO is implemented to achieve a minimum operating voltage of 400mV in UMC 90nm CMOS technology. The write power is 2.09µW at 50kHz and the read power is 2.25µW at 625kHz.

Finally, a 512-word by 16-bit (8kb) subthreshold asynchronous first-in first-out (FIFO) memory is presented for wireless body area networks (WBANs). Meanwhile, A 1kb dynamic voltage scaling 8T SRAM-based FIFO memory is implemented to operate between 0.5V (near-threshold) and 0.3V (subthreshold) in UMC 65nm technology with 0.535µW at 625kHz and 0.163µW at 20kHz power consumption, respectively. The proposed DVS FIFO memory can provide up t o 69.5% power savings when low-power mode is always engaged, and there is no power overhead if the period of low-power mode is longer than 48.66µs. It is suitable for healthcare applications equipped with DVFS capability.

## Acknowledgements

I would like to thank my parents and brother for all the supports they have given me. Thank you for raising me and guiding me to be the person I am.

I am extremely grateful to my advisor, Prof. Wei Hwang, for providing me a good research environment and giving me the maximum freedom of research. Thank you for all the constructive comments and suggestions on my research.

I would also like to thank all the laboratory fellows and school mates, graduated or still in the school. Thank you for making the school life more delightful. Special thanks to MOEA u-PHI project and ITRI project teams, who had been a great help on my research.

To all my friends not mentioned here, thank you for being friends in my life.

# Table of Contents

| C             | hines  | e Abstract                                                          | i  |

|---------------|--------|---------------------------------------------------------------------|----|

| E             | nglisł | n Abstract                                                          | ii |

| $\mathbf{A}$  | cknov  | wledgement                                                          | iv |

| Ta            | able o | of Contents                                                         | v  |

| $\mathbf{Li}$ | st of  | Tables                                                              | ix |

| $\mathbf{Li}$ | st of  | Figures                                                             | x  |

| 1             | Intr   | oduction 1896                                                       | 1  |

| <b>2</b>      | Pric   | or Works Review                                                     | 3  |

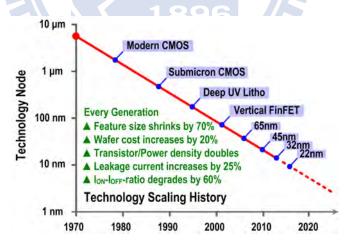

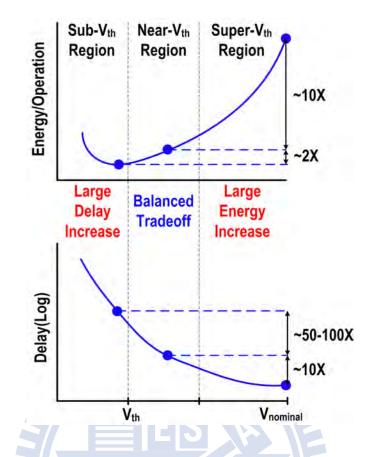

|               | 2.1    | Energy Efficient Techniques for Ultra-Low Voltage Designs           | 5  |

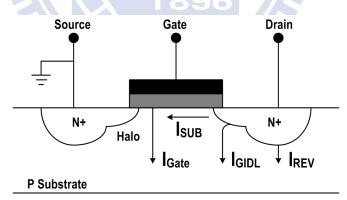

|               |        | 2.1.1 Subthreshold Regimes                                          | 6  |

|               |        | 2.1.2 Near-threshold Regimes                                        | 8  |

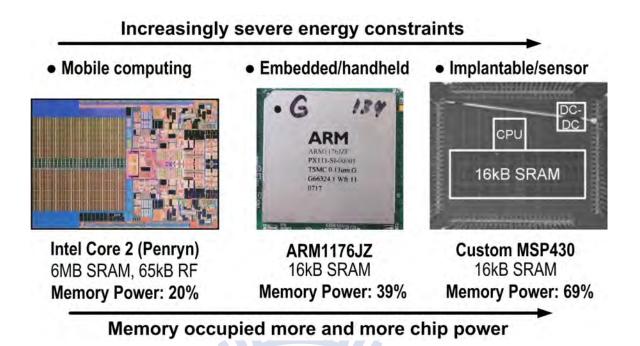

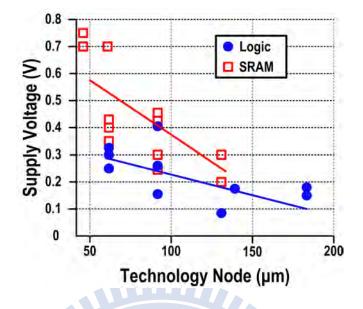

|               | 2.2    | Ultra-Low Voltage Memories                                          | 8  |

|               | 2.3    | Variation-Aware Circuits                                            | 11 |

|               | 2.4    | Dynamic Voltage Frequency Scaling                                   | 12 |

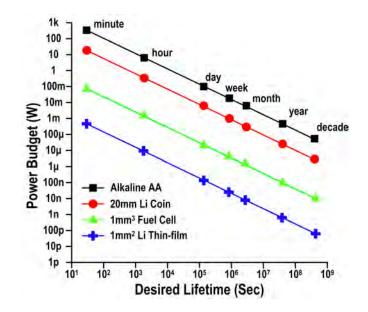

|               | 2.5    | Wireless Body Area Sensor Networks                                  | 14 |

| 3             | Ultı   | ra-Low Voltage Temperature Sensor and Clock Generator Design        | 16 |

|               | 3.1    | Ultra-Low Voltage Process-Invariant Frequency-Domain Smart Tempera- |    |

|               |        | ture Sensor Design                                                  | 17 |

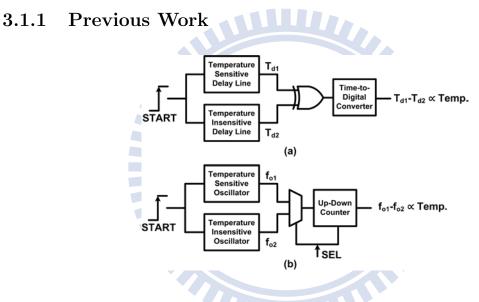

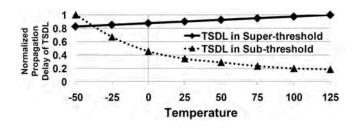

|               |        | 3.1.1 Previous Work                                                 | 19 |

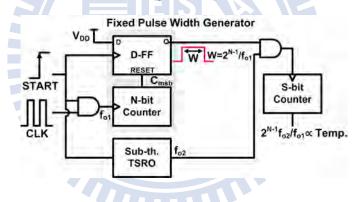

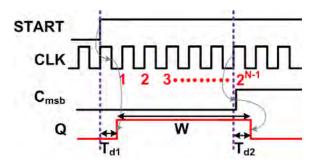

|     | 3.1.2  | Subthreshold Frequency-Domain Temperature Sensor Design 22 |                                                          | 22 |

|-----|--------|------------------------------------------------------------|----------------------------------------------------------|----|

|     |        | 3.1.2.1                                                    | Design Principles                                        | 23 |

|     |        | 3.1.2.2                                                    | Simulation Results                                       | 25 |

|     | 3.1.3  | Ultra-Lo                                                   | ow Voltage Frequency-Domain Temperature Sensor with Pro- |    |

|     |        | cess Var                                                   | iation Immunity Enhancement                              | 26 |

|     |        | 3.1.3.1                                                    | Design Principles                                        | 27 |

|     |        | 3.1.3.2                                                    | Implementation                                           | 29 |

|     | 3.1.4  | Experin                                                    | nental Results in 65nm CMOS                              | 31 |

|     | 3.1.5  | Summar                                                     | cy                                                       | 34 |

| 3.2 | Near-/ | Sub-thre                                                   | shold DLL-based Clock Generator with PVT-aware Locking   |    |

|     | Range  | Compen                                                     | sation                                                   | 36 |

|     | 3.2.1  | Unified                                                    | Logical Effort Models                                    |    |

|     |        | 3.2.1.1                                                    | Super-threshold Region                                   |    |

|     |        | 3.2.1.2                                                    | Near-threshold Region                                    | 39 |

|     |        | 3.2.1.3                                                    | Sub-threshold Region                                     |    |

|     | 3.2.2  |                                                            | enerator Architecture                                    |    |

|     | 3.2.3  | PVT-Av                                                     | ware Delay Line Design                                   | 44 |

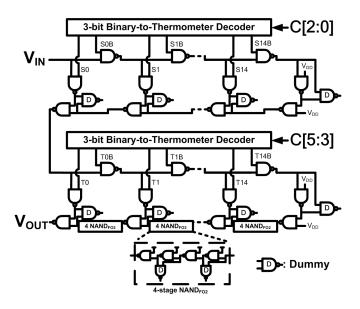

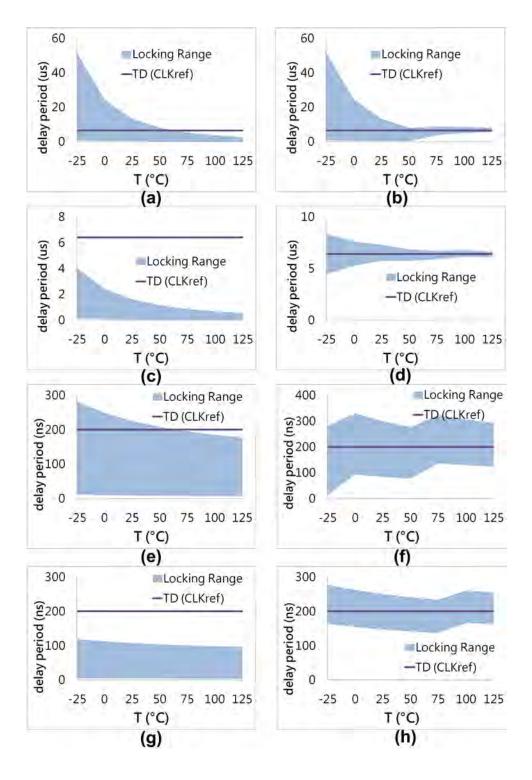

|     |        | 3.2.3.1                                                    | Variation-Aware Lock-in Delay Line Design                | 44 |

|     |        | 3.2.3.2                                                    | PVT Compensation Delay Line Design                       | 45 |

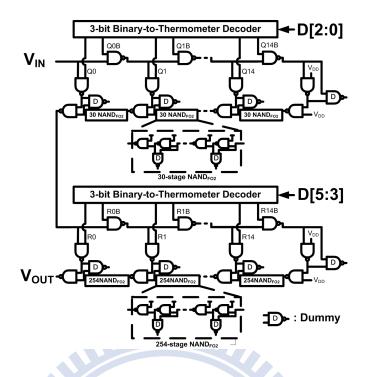

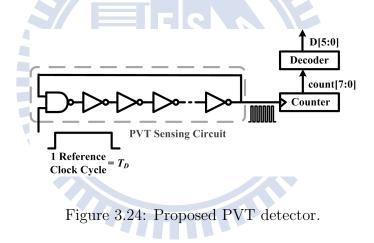

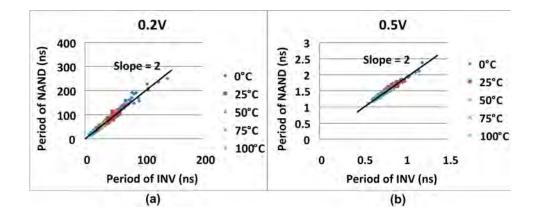

|     |        | 3.2.3.3                                                    | Delay Ratio of FO1-INV to FO2-NAND                       | 47 |

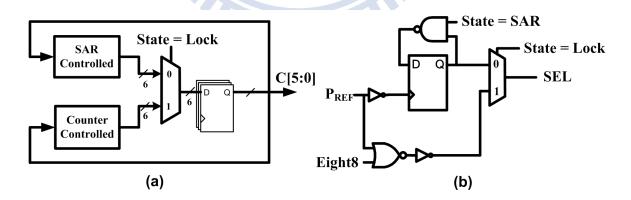

|     | 3.2.4  | Circuits                                                   | Implementation                                           | 48 |

|     |        | 3.2.4.1                                                    | Control Unit                                             | 48 |

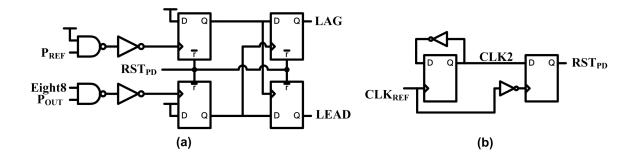

|     |        | 3.2.4.2                                                    | Phase Detector                                           | 49 |

|     |        | 3.2.4.3                                                    | Simulation Results                                       | 50 |

|     | 3.2.5  | Summar                                                     | cy                                                       | 52 |

| Ult | ra-Low | v Voltage                                                  | e Memory Design                                          | 54 |

| 4.1 | 9T Su  | bthreshol                                                  | d SRAM Design with Bit-Interleaving Scheme               | 56 |

|     | 4.1.1  | 9T Subt                                                    | hreshold SRAM Bit-Cell Design                            | 57 |

|     |        | 4.1.1.1                                                    | Basic Operations                                         | 58 |

|     |        | 4.1.1.2                                                    | Layout Considerations                                    | 60 |

4

|     | 4.1.2 | Iso-Area   | a SRAM Bit-Cell $V_{\min}$ Analysis $\ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 60 |

|-----|-------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     |       | 4.1.2.1    | Iso-Area Bit-Cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 60 |

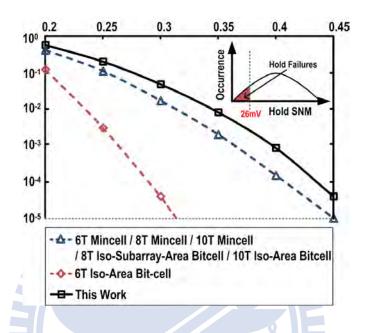

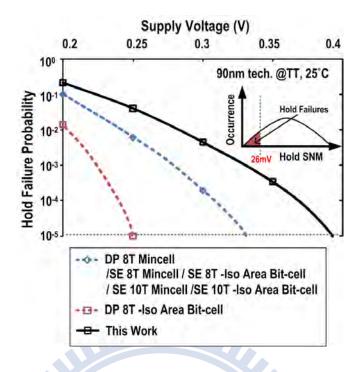

|     |       | 4.1.2.2    | Hold-Failure Probability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 62 |

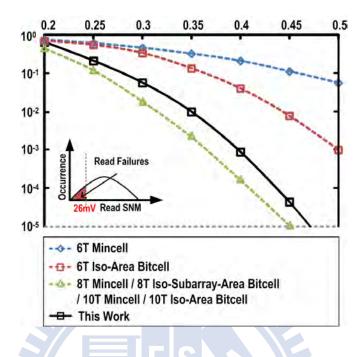

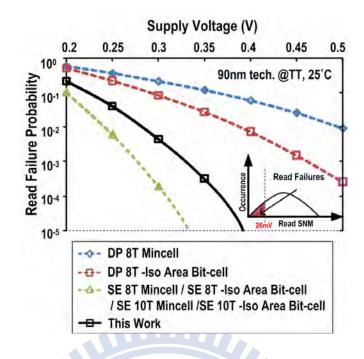

|     |       | 4.1.2.3    | Read-Failure Probability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 63 |

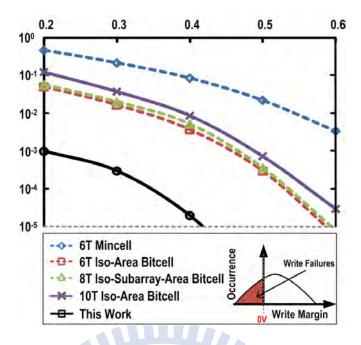

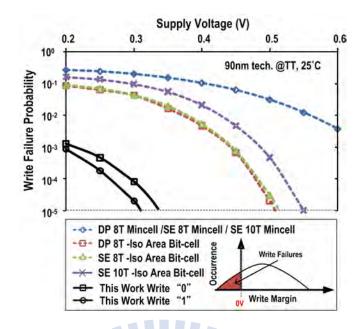

|     |       | 4.1.2.4    | Write-Failure Probability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 64 |

|     |       | 4.1.2.5    | Iso-Area $V_{\min}$ Comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 64 |

|     | 4.1.3 | 1Kbit 9    | $\Gamma$ SRAM Implementation and Measurement Results in 65nm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|     |       | CMOS       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 65 |

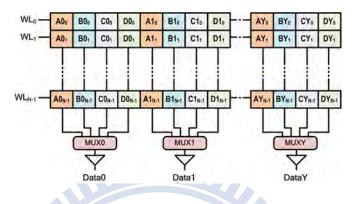

|     |       | 4.1.3.1    | Bit-Interleaving Scheme for Soft Error Rate Reduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 65 |

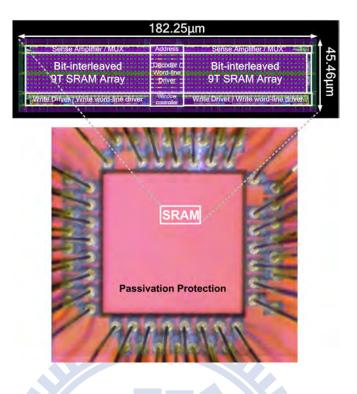

|     |       | 4.1.3.2    | 1Kbit 9T Bit-Interleaved SRAM Array Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 67 |

|     |       | 4.1.3.3    | Measurement Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 69 |

|     | 4.1.4 | Summar     | ry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 71 |

| 4.2 | Energ | y-Efficien | t 10T SRAM-based FIFO Memory Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 72 |

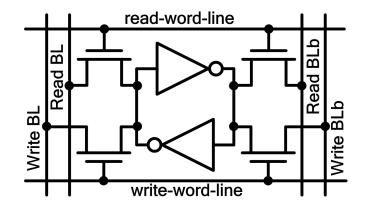

|     | 4.2.1 | 10T Nea    | ar-/Sub-threshold SRAM Bit-Cell Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

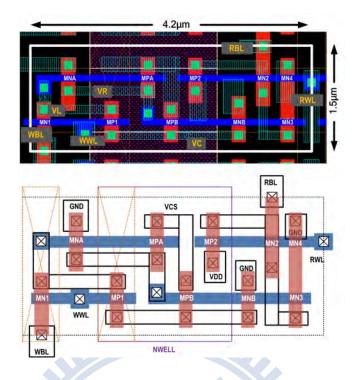

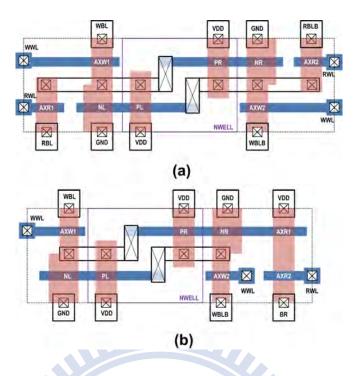

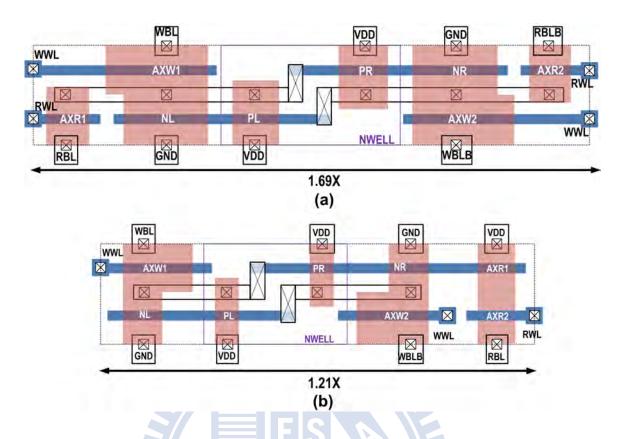

|     |       | 4.2.1.1    | Layout Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

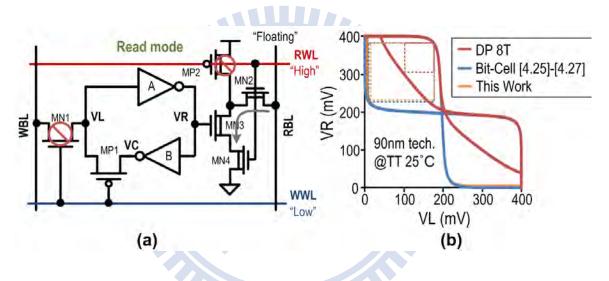

|     |       | 4.2.1.2    | Read Ability Improvement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

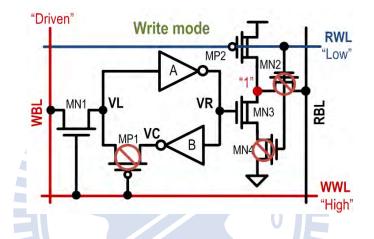

|     |       | 4.2.1.3    | Write Ability Improvement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|     |       | 4.2.1.4    | Bitline Leakage Reduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 78 |

|     | 4.2.2 | Iso-Area   | a Dual-Port SRAM Bit-Cell $V_{min}$ Analysis $\hdots \hdots \hdo$ | 80 |

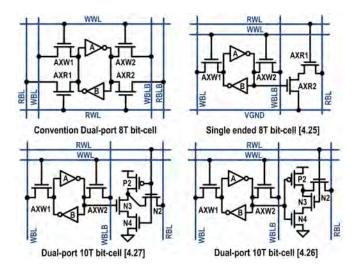

|     |       | 4.2.2.1    | Iso-Area Bit-Cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 80 |

|     |       | 4.2.2.2    | Hold-Failure Probability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 83 |

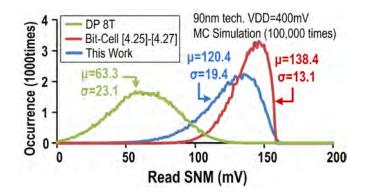

|     |       | 4.2.2.3    | Read-Failure Probability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 83 |

|     |       | 4.2.2.4    | Write-Failure Probability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 84 |

|     |       | 4.2.2.5    | Iso-Area $V_{min}$ Comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 85 |

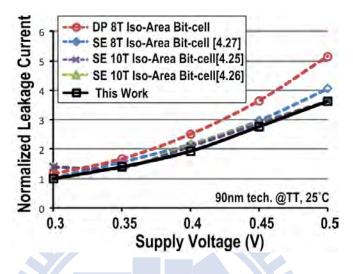

|     |       | 4.2.2.6    | Leakage Current Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 86 |

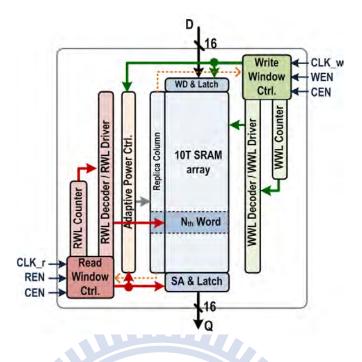

|     | 4.2.3 | 16Kbit I   | Near-threshold SRAM-based FIFO memory in 90nm CMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|     |       | for WB.    | ANs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 87 |

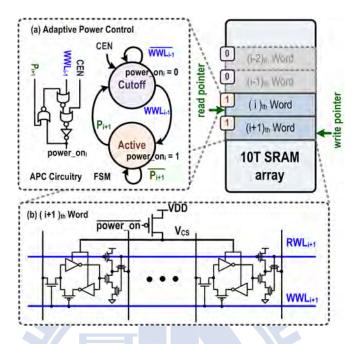

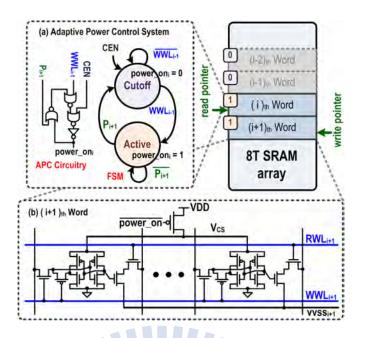

|     |       | 4.2.3.1    | Adaptive Power Control Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 87 |

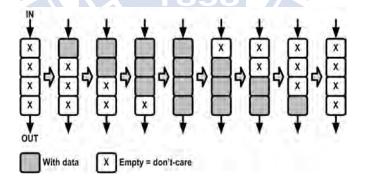

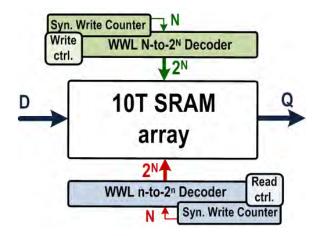

|     |       | 4.2.3.2    | Counter-based Pointer Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 89 |

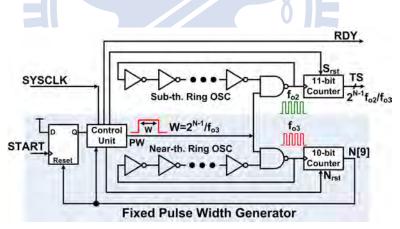

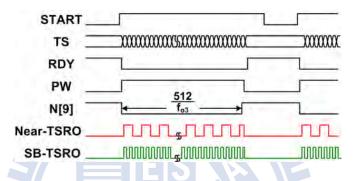

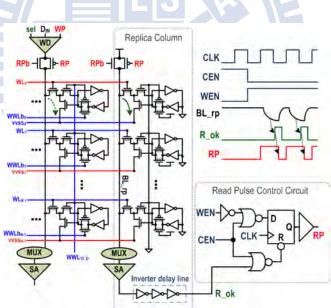

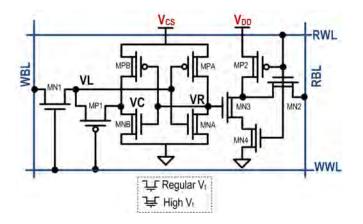

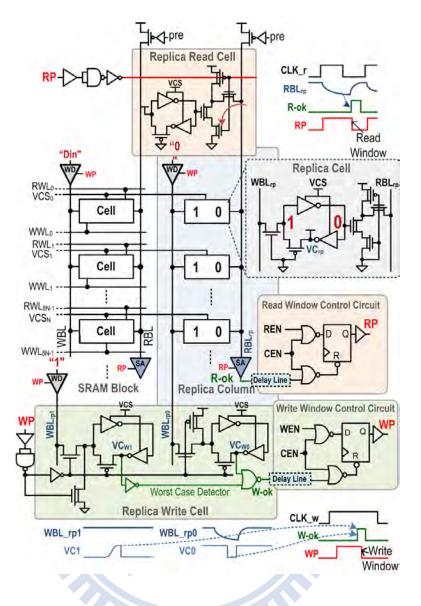

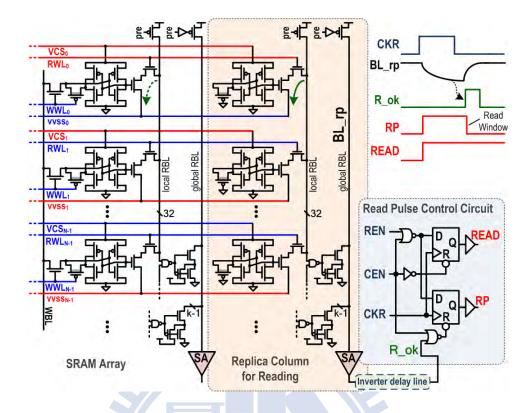

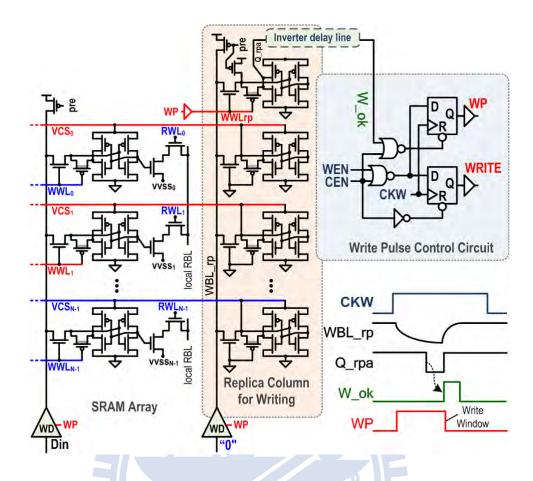

|     |       | 4.2.3.3    | Smart Replica Read/Write Control Units                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 91 |

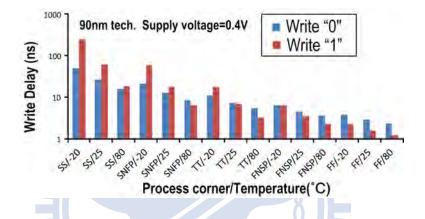

|    |                                                                       |                                | 4.2.3.4 Implementations and Simulation Results         | 93  |  |

|----|-----------------------------------------------------------------------|--------------------------------|--------------------------------------------------------|-----|--|

|    |                                                                       | 4.2.4                          | Summary                                                | 94  |  |

| 5  | Dyı                                                                   | namic                          | Voltage Frequency Scaling Platform                     | 95  |  |

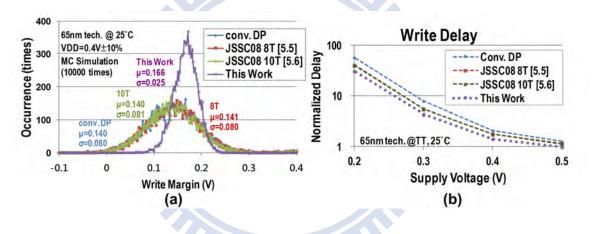

|    | 5.1                                                                   | Near-                          | /Sub-threshold Robust 8T SRAM Design                   | 98  |  |

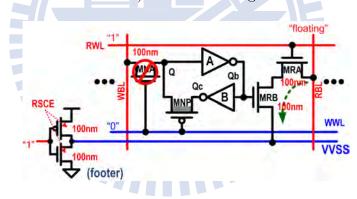

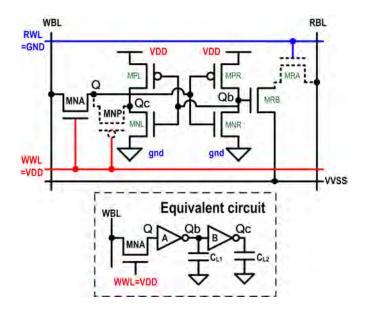

|    |                                                                       | 5.1.1                          | Basic Operations                                       | 100 |  |

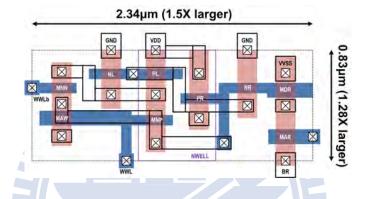

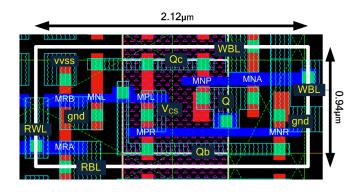

|    |                                                                       | 5.1.2                          | Layout Considerations                                  | 103 |  |

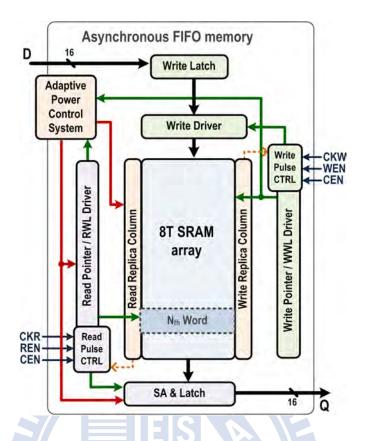

|    | 5.2                                                                   | Async                          | chronous 8T-SRAM-based FIFO Memory Design in 65nm CMOS | 104 |  |

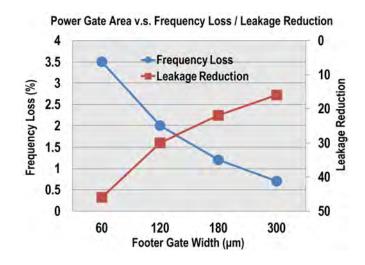

|    |                                                                       | 5.2.1                          | Adaptive Power Control System                          | 105 |  |

|    |                                                                       | 5.2.2                          | Read/Write Pulse Control Circuit Design                | 106 |  |

|    |                                                                       |                                | 5.2.2.1 Read Pulse Control Circuit                     | 106 |  |

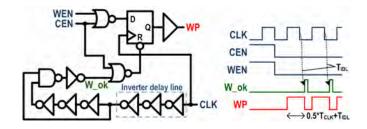

|    |                                                                       |                                | 5.2.2.2 Write Pulse Control Circuit                    | 107 |  |

|    | 5.3 1Kbit Dynamic Voltage Frequency Scaling 8T-SRAM-based FIFO Memory |                                |                                                        |     |  |

|    |                                                                       | in 65nm CMOS for DVFS Platform |                                                        |     |  |

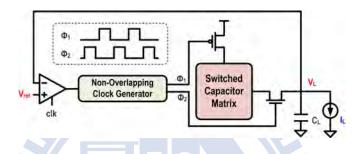

|    |                                                                       | 5.3.1                          | Switched Capacitor DC-DC Converter                     | 110 |  |

|    |                                                                       | 5.3.2                          | Supply Switch and DVFS Controller                      | 111 |  |

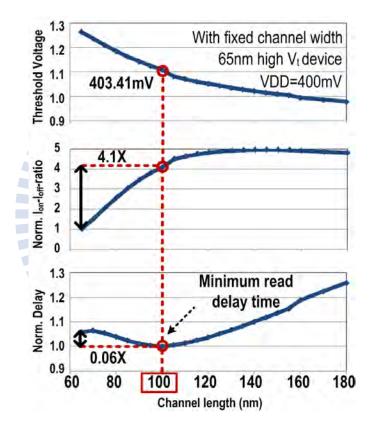

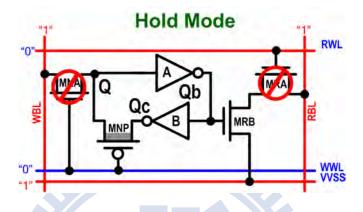

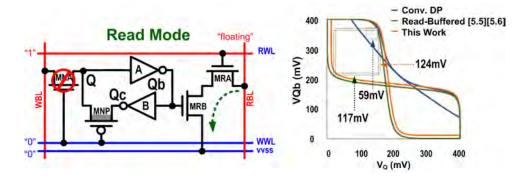

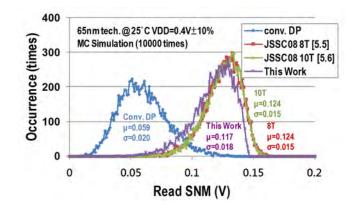

|    |                                                                       | 5.3.3                          | Implementation and Simulation Results                  | 113 |  |