Microelectronic Engineering 84 (2007) 2117-2120

www.elsevier.com/locate/mee

# Process-variation- and random-dopants-induced threshold voltage fluctuations in nanoscale CMOS and SOI devices

Yiming Li a,\*, Shao-Ming Yu b, Hung-Ming Chen c

<sup>a</sup>Department of Communication Engineering, National Chiao Tung University, Hsinchu, Taiwan <sup>b</sup>Department of Computer Science, National Chiao Tung University, Hsinchu, Taiwan <sup>c</sup>Taiwan Semiconductor Manufacturing Company, Ltd., Hsinchu, Taiwan

#### Abstract

In this paper, we investigate the threshold voltage fluctuation for nanoscale metal-oxide-semiconductor field effect transistor (MOSFET) and silicon-on-insulator (SOI) devices. The threshold voltage fluctuation comes from random dopant and short channel effects. The random-dopant-induced fluctuation is due to the random nature of ion implantation. The gatelength deviation and the line-edge roughness are mainly resulted from the short-channel effect. For the SOI devices, we should also consider the body thickness variation. In our investigation, the metal gate with high-κ material MOSFET is a good choice to reduce fluctuation of threshold voltage when comparing to the poly gate MOSFET and thin-body SOI devices.

Keywords: threshold voltage fluctuation; random dopant; process-variation; gate-length deviation; line-edge roughness; modeling and simulation

### 1. Introduction

As the dimension of complementary metal-oxidesemiconductor (CMOS) devices shrunk into sub-90nm scale, random-dopant-induced threshold voltage (Vt) fluctuations are pronounced [1-4, 6,7]. Fluctuation of threshold voltage is crucial for the

In this paper, we explore the threshold voltage fluctuation for planar metal-oxide-semiconductor field effect transistor (MOSFET) and silicon-oninsulator (SOI) devices. The fluctuation of threshold voltage comes from random dopant and short channel effects. The fluctuation of random effect derives mainly from the random nature of ion implantation. The fluctuation of short channel effect includes process-variation-induced gate length deviation and line edge roughness (as well as body thickness variation for SOI devices). The fluctuations are

E-mail address: ymli@faculty.nctu.edu.tw (Y. Li)

design window, yield, noise margin, stability, and reliability of ultra large-scale integration circuits.

<sup>\*</sup> Corresponding author. *Present address: P.O. Box 25-178, Hsinchu 300, Taiwan. Tel:* +886-3-571-2121 ext: 52974; fax: +886-3-5726639.

growing worse due to serious short-channel effect when the dimension of device is further scaled. The modeled threshold voltage fluctuation is firstly compared with the experimentally measured data for the 65nm high-performance and low-power devices, respectively. The investigation is advanced and finds that SOI device may suffer large body thickness variation and metal gate with high- $\kappa$  material MOSFET [8,9] is a good choice to reduce fluctuation of threshold voltage.

This paper is organized as follows. In Sec. 2, we state the analyzing method used for the fluctuation of threshold voltage with respect to the random-dopant fluctuation, the gate-length deviation, and the-line edge roughness, respectively. In Sec. 3, we show the simulation results among devices. Finally, we draw conclusions.

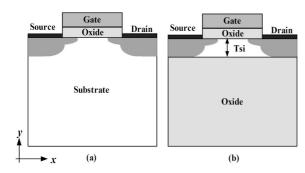

Fig. 1. A cross-sectional view of the simulated (a) planar MOSFET and (b) SOI device.

## 2. Computational approach

The fluctuation of threshold voltage is directly assumed to be contributed from the random dopant, the gate length deviation, and the line edge roughness. Therefore, the standard deviation of the total threshold voltage,  $\sigma_{Vt,total}$ , is

$$\sigma_{Vt,total}^2 = \sigma_{Vt,RD}^2 + \sigma_{Vt,Lg}^2 + \sigma_{Vt,LER}^2 \tag{1}$$

where  $\sigma_{Vt,RD}$  is the random-dopant-induced fluctuation,  $\sigma_{Vt,Lg}$  and  $\sigma_{Vt,LER}$  are fluctuations caused by the gate length deviation and line edge roughness. The  $\sigma_{Vt,Tsi}$  of the body thickness variation is further considered for the SOI devices [1,7]. The random-dopant-induced threshold voltage fluctuation is calculated with a perturbed quantum correction approach, which was developed in our recent work

[1,3,4]. Under the equilibrium condition, a two-dimensional quantum correction model together with the perturbation technique is firstly approximated by the finite volume method and then solved with the monotone iterative method for the explored devices. Thus,  $\sigma_{Vt,RD}$  of device can be calculated in a cost-effective manner. Figure 1 shows the structures of the examined planar MOSFET and thin-body SOI devices.

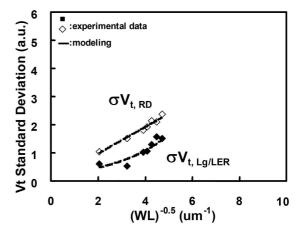

Fig. 2. The threshold voltage fluctuation comes from random-dopant and short channel effects for a 65nm high-performance device.

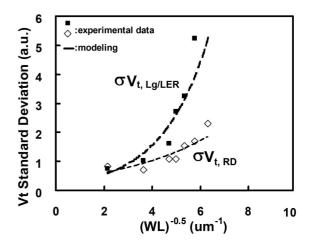

Fig. 3. The threshold voltage fluctuation comes from random-dopant and short channel effects for a 65nm lower-power device

Furthermore, we apply the statistical approach to evaluate the effect of  $\sigma_{Vt,Lg}$  and  $\sigma_{Vt,LER}$  [5]. The

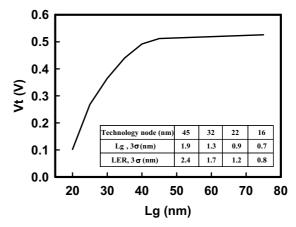

magnitude of the gate length deviation and the line edge roughness are extracted from the projections of the ITRS 2005 for different technology nodes [1]. We establish a look-up table of the threshold voltage versus gate length firstly, as shown in Fig. 4. It enables us to evaluate the threshold voltage with respect to the deviation of gate length, which following the roadmap of ITRS that  $3\sigma_{Lg} = 1.9$  nm for the 45nm node and  $3\sigma_{Lg} = 1.3$ nm for the 32nm technology node, as the inset table of Fig. 4. In a similar way, we calculate the effect of  $\sigma_{Vt,LER}$  where the deviation of the line edge roughness following the rules,  $3\sigma_{LER} = 2.4$ nm for the 45nm node and  $3\sigma_{LER} = 1.7$ nm for the 32nm node. Thus, we can calculate the standard deviation of threshold voltage resulting from the deviation of gate length and the roughness of line edge.

#### 3. Results and discussion

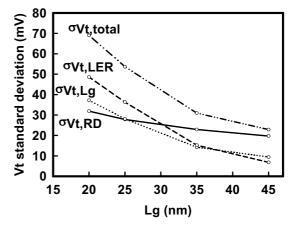

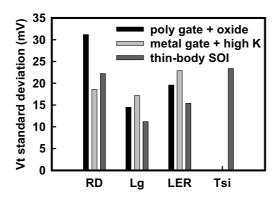

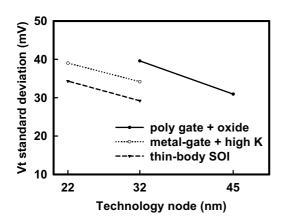

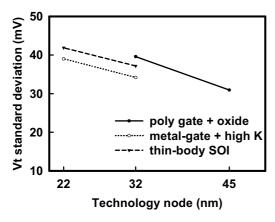

Figure 2 shows the different threshold voltage fluctuations for the 65nm high-performance MOSFET with varying device width. Figure 3 shows the result of the lower-power device. Our results have a good agreement with both the 65nm experiment data. We find that the threshold voltage fluctuations of the high-performance device are dominated by the short-channel effect; on the contrary, the Vt fluctuation of lower-power device are dominated by the random effect. The main difference of  $\sigma_{Vt,RD}$ between the high-performance and low-power devices comes from different dopant materials. In addition, for the high-performance device, the  $\sigma_{Vt,Lg}$ and  $\sigma_{\text{Vt,LER}}$  are much more sensitive to device width than that of the low-power devices. Furthermore, Fig. 5 shows all fluctuation components of a 35nm planar MOSFET. In this case, the short-channel effects exceed the random-dopant-induced fluctuation when Lg < 25nm, and dominate the total fluctuations for device with a small Lg. Figure 6 shows a comparison among the poly-gate MOSFET, the metal-gate with high-κ material MOSFET, and the thin-body SOI device. In this work, the dielectric constant of the high-κ material is simply set to be 24, EOT of the high-κ gate dielectric is 1.4nm and the work function of metal-gate is 4.4 eV. We also consider that fluctuation comes from the variation of the body thickness in this comparison. The magnitude of body thickness deviation is  $3\sigma_{Tsi} = 1.5$ nm. To be compared with Lg, the body thickness is Tsi = 5nm in this work [10,11]. The  $\sigma_{Vt,Tsi}$  overwhelms all the other fluctuation factors in the thin-body SOI devices. Figures 7 and 8 show the comparisons of the total Vt fluctuation without and with considering  $\sigma_{Vt,Tsi}$ . When considering  $\sigma_{Vt,Tsi}$ , the metal gate with high- $\kappa$  material MOSFET has smaller fluctuations compared with SOI devices.

Fig. 4. The threshold voltage versus the gate length for a 35 nm planar MOSFET. The inset table is the magnitude of the gate length deviation and the line edge roughness.

Fig. 5. Components of the threshold voltage fluctuation of the explored planar MOSFET, where the nominal Lg is 35nm and the oxide thickness is 1.7nm.

# 4. Conclusions

The threshold voltage fluctuation caused by the random dopant effect, the gate-length deviation, and the line-edge roughness are calculated and compared

Fig. 6. Components of the threshold voltage fluctuation for the poly-gate MOSFET, the metal-gate, and high- $\kappa$  materials MOSFET, and the thin-body SOI. The nominal Lg is 25nm.

Fig. 7. The threshold voltage fluctuation versus different technology nodes without considering the  $\sigma_{Vt,Tsi}$ .

Fig. 8. The threshold voltage fluctuation versus different technology nodes including  $\sigma_{Vt,Tsi}$ .

the line-edge roughness are calculated and compared for the nanoscale CMOS and SOI devices. When ignoring the  $\sigma_{Vt,Tsi}$ , the SOI devices have the smaller Vt fluctuation. However the body thickness variation should be considered for the SOI devices; and it seems that the metal-gate with high- $\kappa$  material MOSFET is a better solution for reducing Vt fluctuation.

# Acknowledgements

This work was supported in part by Taiwan National Science Council (NSC) under Contract NSC-95-2221-E-009-336 and Contract NSC-95-2752-E-009-003-PAE, by the MoE ATU Program under a 2006-2007 grant, and by the Taiwan Semiconductor Manufacturing Company (TSMC), Hsinchu, Taiwan under a 2005-2007 grant.

#### References

- [1] F-L. Yang, J-R. Hwang, Y. Li, Proc. of IEEE CICC (2006) 691-694.

- [2] G. Roy, A. R. Brown, F. Adamu-Lema, S. Roy, A. Asenov, IEEE Trans. Elec. Dev. 53 (2006) 3063-3070.

- [3] Y. Li and S.-M. Yu, Jpn. J. Appl. Phys. 45 (2006) 6860-6865.

- [4] Y. Li and S.-M. Yu, Journal of Computational Electronics 5 (2006) 125-129.

- [5] Y. Li and Y.-S. Chou, Proc. Int. Conf. on Solid State Devices and Materials (2005) 622-623.

- [6] Shiying Xiong and J. Bokor, IEEE Trans. Elec. Dev. 51 (2004) 228-232.

- [7] G. Tsutsui, M. Saitoh, T. Nagumo, T. Hiramoto, IEEE Trans. Nanotechnology 4 (2005) 369-373.

- [8] Y.T. Hou, T. Low, Bin Xu, M.-F. Li, G. Samudra, D.L. Kwong, Proc. Int. Conf. on Solid-State and Integrated Circuits Technology 1 (2004) 57-60.

- [9] P. Majhi, C. Young, G. Bersuker, H.C. Bersuker, G.A. Brown, B. Brown, R. Brown, P.M. Brown, H.R. Huff, Proc. of European Solid-State Device Research Conference (2004) 185-188.

- [10] H.-Y. Chen, C.-Y. Chang, C.-C. Huang, T.-X. Chung, S.-D. Liu, J.-R. Hwang, Y.-H. Liu, Y.-J. Chou, H.-J. Wu, K.-C. Shu, C.-K. Huang, J.-W. You, J.-J. Shin, C.-K. Chen, C.-H. Lin, J.-W. Hsu, B.-C. Perng, P.-Y. Tsai, C.-C. Chen, J.-H. Shieh, H.-J. Tao, S.-C. Chen, T.-S. Gau, F.-L. Yang, Dig. VLSI Tech. Symp. (2005) 16-17.

- [11] T. Ohtou, N. Sugii, T. Hiramoto, Prof. IEEE Silicon Nanoelectronics Workshop (2006) 15-16.