# 國立交通大學

## 電控工程研究所

### 博士論文

A Boost Converter with Charge-Reservoir Technique and Constant

Current Regulator for Improving the Efficiency of RGB LED

Backlight Module

研究生:謝俊禹

指導教授:陳科宏 副教授

中華民國九十九年十月

## 具有電荷儲存器和定電流機制的升壓電路用來改善 RGB 發光二極體背光模組效率

A Boost Converter with Charge-Reservoir Technique and Constant Current Regulator for Improving the Efficiency of RGB LED

#### **Backlight Module**

研究生:謝俊禹 Student: Chun-Yu Hsieh

指導教授: 陳科宏 Advisor: Dr. Ke-Horng Chen

國立交通大學電控工程研究所博士論文

#### A Thesis

Submitted to Department of Electrical and Control Engineering

College of Electrical Engineering National Chiao Tung University

in partial Fulfillment of the Requirements

for the Degree of Doctor

in

Electrical and Control Engineering

Oct. 2011

Hsinchu, Taiwan, Republic of China

中華民國九十九年十月

##

研究生:謝俊禹 指導教授 陳科宏 副教授

國立交通大學電機與控制工程學系(研究所)博士班

#### 摘 要

目前色序法在液晶面版沒有濾光片的控制理論中可有效地減低色分離與運動模糊效應。由於 RGB LEDs 並非都是一直被開啟的,而是依序開啟紅、綠、藍 LED,再藉由混光的效果去實現 LCD 面版之影像色彩,可使電源消耗量降低,也因為其高色域和低電源消耗的特性,此項創新成為今日 LCD 顯示市場的潮流。因為藍光和綠光 LEDs 和紅光 LEDs 擁有不一樣的材料特性,所以紅光 LEDs 的順向電壓就有別於藍光和綠光 LED,因此在傳統紅綠藍三原色的背光模組會需要不同的直流對直流升壓轉換器去驅動不同顏色的 LED,

本篇論文提出只利用一個升壓轉換器以減少成本以及 PCB 佈局面積,具有快速轉換電壓技術,利用降壓-儲能與升壓-放能(Buck-store and Boost-Restore (BSBR))技術以及電荷回收(Charge Recycling(CR))技術,可快速的轉換輸出電壓以提供不同供給電壓來依序驅動串聯紅,綠,藍(RGB)發光二極體(LED),來減低在定電流產生器上的電源損耗,在暫態的參考值追蹤時間之內,這一項創新的控制技術快速轉換電壓技術以及電荷回收技術,就被提出來增強追蹤參考電壓反應,當輸出電壓位準由低轉換至高供給電壓時,儲存在回收電容上的能量可以被用來對輸出電容充電,以將輸出電壓提升回高供給電壓位準。因此多餘的能量可被回收。實驗結果顯示出此技術的確可以有效的縮短追蹤參考電

壓的時間。此外,本項技術也另可提供一個調節電壓來驅動設立在液晶顯示器(LCD)系統上的副區塊。能源回收(CR)和降壓儲能升壓降能(BSBR)的最大效率分別可高達 90% 和 94%,而本升壓 LED 驅動器的最大效率則為 94.5%。實驗結果證明了本篇提出的降壓-儲能與升壓-放能技術(BSBR)可達到快速且有效率的追蹤參考電壓效能。

關鍵字: 參考電壓追蹤,電荷回收,場色序法,發光二極體背光模組

A Boost Converter with Charge-Reservoir

Technique and Constant Current Regulator for

Improving the Efficiency of RGB LED

Backlight Module

Student: Chun-Yu Hsieh Advisor: Dr. Ke-Horng Chen

Institute of Electrical and Control Engineering National Chiao-Tung University

#### **Abstract**

A Red, Green, and Blue (RGB) LED driver with the fast reference tracking (FRT) and charge-recycling (CR) techniques is proposed to implement a high efficiency and low cost RGB backlight module in color sequential notebook computers' display. The FRT technique can speed up the reference tracking performance and effectively improves the up-tracking performance. However, the down-reference tracking depends on the load current and output capacitor. Therefore, the charge-recycling and buck-store/boost-restore techniques are proposed to store extra energy on the re-cycling capacitor when the output voltage is switched from high- to low-voltage level and releases the reserved energy back to the output node at next period. Furthermore, the output voltage can be rapidly switched between two different voltage levels by FRT technique without consuming much power owing to the restored energy by the CR technique. The proposed BSBR technique not only stores and restores extra energy during the transient time of the reference tracking response to improve the efficiency but also enhances the reference tracking response to greatly reduce load transition time.

Experimental results show that the period of reference-tracking response can be improved. Furthermore, this BSBR technique also can provide a regulated voltage to drive the

sub-block implemented in the LCD system. The maximum efficiency of energy recycling with CR and BSBR technique is up to 90% and 94%, respectively. The total power consumption of a notebook computer's 15.4' LCD panel can be reduced from 5W in cold cathode fluorescent lamp (CCFL) backlight module to about 2-3W in RGB LED backlight module with the field color sequential (FCS) algorithm. Furthermore, after the implementation of the LED driver with the FRT and CR techniques, the power loss can be reduced to about 24% of that without the FRT and CR techniques,.

Keywords—Reference tracking, charge re-cycling, field color sequential, LCD, LED backlight, feedforward technique

.

#### 誌謝

在論文完成之際,心中感慨萬千,在這四年半的碩博班研讀期間,在交通大學的課程學習以及產學合作的研究經歷,讓我體認並且學習如何成長為一名獨立自主的研究人員。如今能順利取得博士學位,在此要感謝的,是帶領學生的指導教授—陳科宏老師;在大學時期,陳科宏老師開啟了我對類比電路以及電源管理設計的興趣,成了我人生生涯的轉換點。您總是能在談笑間開拓我的新思維,及其研究熱忱、執著與嚴謹的態度,都再再激勵筆者,引領我前往更寬闊精深的研究領域。給予筆者無條件悉心指導與啟發,恩澤浩瀚,實在難以回報。論文及 paper 的產出過程,有您一路指引,感激難以言表。

感謝口試委員 <u>郭斯彥教授、方偉騏教授、潘晴財教授、廖聰明教授、鄭桂忠教授、陳新教授、陳福川教授、王清松</u>教授及在<u>黃立仁</u>副總口試期間對論文的指導與斧正,使得論文能更瑧完善,讓我在幾度峰迴路轉後又見曙光,有了您們寶貴的意見,自己才能對整份研究有了更深切的感知。

感謝宏瑋學長平常細心教導我 paper 的寫作觀念以及基本電路的實現,感謝紹章學長、與箴學長以及碩班同學家祥、佳麟、維倫、鼎容、韋任同學們的平時互相激勵並擴大我的研究思維,也特別感謝小柯、國林同學及柏逢學長在佈局上給予的指導及幫助。還有昱輝、智宇、石頭、阿朱、亮亮、舒舒、暐中,謝謝你們願意與我相互分享、討論研究的想法,減少探索研究議題的時間。另外也感謝電控所系辦小姐嘉雯以及英芝、助理巧潔以及芃瑀在博班生涯給予很多的行政協助。

感謝中華映管股份有限公司、立錡科技教育基金會以及聯發科技教育基金會在學生 我的求學生涯給予了很多業界的指導以及經驗分享,最想感謝是我的父親、母親以及一 直在身邊陪伴我四年我的好朋友鈺婷,謝謝你們一直以來的包容與支持。感恩的心情已 非三言兩語能表達。

謝俊禹 謹誌

國立交通大學 電機與控制學系

二〇一〇 秋

### **Contents**

| Chine    | se Abstract                                                            | i    |

|----------|------------------------------------------------------------------------|------|

| Abstr    | act                                                                    | iii  |

| Ackno    | owledgament                                                            | v    |

| Contents | ·                                                                      | vi   |

| Figure C | Captions                                                               | viii |

| Table Ca | ptions                                                                 | xiv  |

| Chapter  | 1 Introduction                                                         | 1    |

| 1.1      | Background and the Backlight Module                                    | 1    |

| 1.2      | The Basic Theory of Field Color Sequential                             | 5    |

| 1.3      | The Analysis of Power Consumption and the Overall Efficiency in the RG | В    |

|          | LED Driver                                                             | 8    |

| 1.4      | Prior Arts                                                             | 13   |

| 1.5      | Motivation SIES PAGE                                                   | 20   |

| 1.6      | Thesis Organization.                                                   | 20   |

| Chapter  | 2 The Architecture of Constant Current Regulator for LED Driver        | 22   |

| 2.1      | The Characteristic of LED                                              | 22   |

| 2.2      | The Basic LED Current Regulators                                       | 23   |

| 2.3      | The Structure of LED Lighting System with HCC and PCC Technique        | 24   |

| 2.4      | The Successive Approximation Register (SAR) Design Methodology         | 31   |

| 2.5      | The Successive Approximation Register (SAR) Circuit Implementations    | 33   |

| 2.5.1    | The Implementation of the SAR-Controlled Modulator                     | 37   |

| 2.5.2    | The Implementation of the Adaptive Off-time Circuit                    | 40   |

| 2.5.3    | The Implementation of the On-chip Low-side Current Sensing and the     |      |

|          | Blanking Time Circuits                                                 | 42   |

| Chapter  | 3 The Proposed FRT Technique and CR Technique                          | 44   |

| 3.1      | The Analysis of FRT Technique and CR Technique                         | 44   |

| 3.1.1    | The Operation Principle of the FRT Technique                           | 44   |

| 3.1.2    | The Operation Principle of the CR Technique                            | 47   |

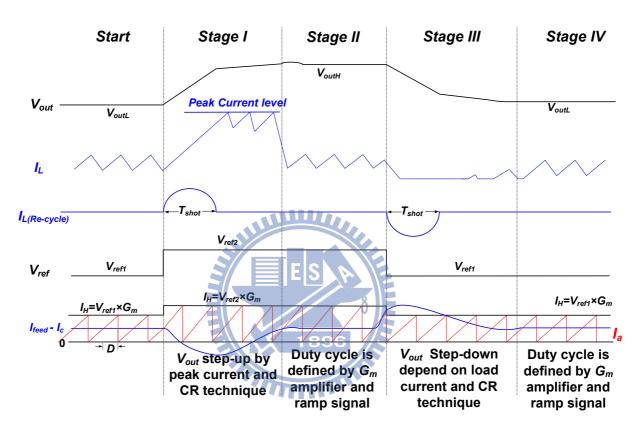

| 3.1.3    | Reference Tracking Procedure                                           | 52   |

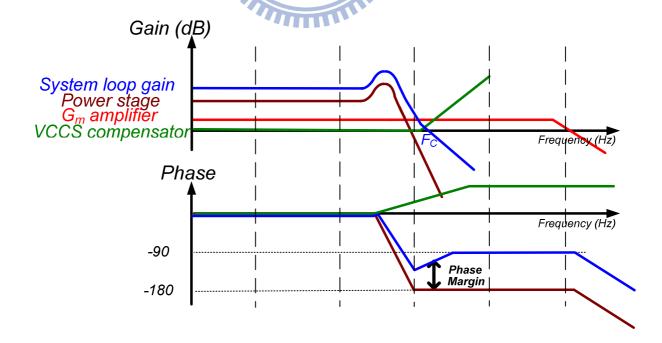

| 3.1.4              | The stability of the LED driver with the FRT and CR techniques                               | 54  |

|--------------------|----------------------------------------------------------------------------------------------|-----|

| 3.2                | Current Sensor and Charge Reservation Circuits                                               | 56  |

| 3.2.1              | The Design of the Voltage Control Current Source Compensator                                 | 56  |

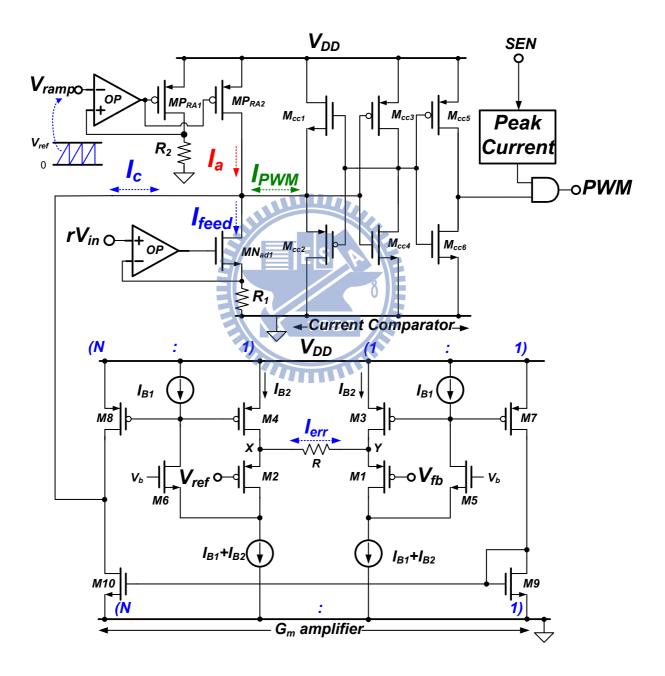

| 3.2.2              | The Implementation of the PWM Generator with FRT Technique                                   | 57  |

| 3.2.3              | The Proposed One-Shot Generator for Charge Recycling Technique                               | 60  |

| 3.2.4              | Proposed Constant Current Regulator                                                          | 62  |

| Chapter            | 4 The Proposed Buck-Store Boost-Restore (BSBR) Technique                                     | 64  |

| 4.1                | The Buck-Store and Boost-Restore Technique                                                   | 64  |

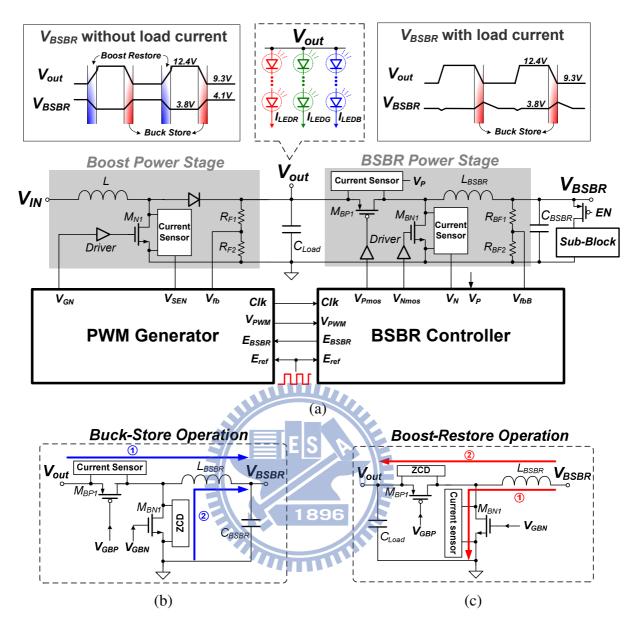

| 4.1.1              | Architecture of the BSBR Power Stage and Controller                                          | 66  |

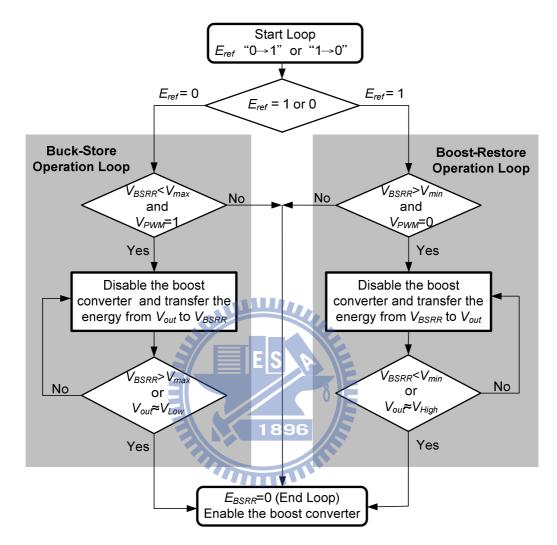

| 4.1.2              | The Tracking Algorithm of the BSBR Technique                                                 | 67  |

| 4.1.3              | The Efficiency of Charge Transition                                                          | 70  |

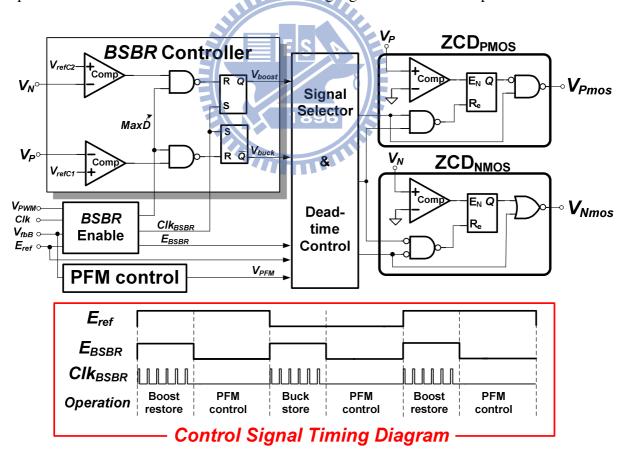

| 4.2                | The Circuit Implementation                                                                   | 71  |

| <b>4.2.1 4.2.2</b> | The Implementation of the Proposed BSBR Controller  The PWM Generator of the Boost Converter |     |

| Chapter            | 5 Measurement Results.                                                                       | 77  |

| 5.1<br>5.2         | The Measure Result of SAR Methodology The Measured Result of FRT and CR Technique            |     |

| 5.3                | The Measure Result of BSBR Technique                                                         | 90  |

| Chapter            | 6 Conclusions and Future Works                                                               | 97  |

| 6.1                | Conclusions                                                                                  | 97  |

| 6.2                | Future Works                                                                                 | 98  |

| Referenc           | ces                                                                                          | 100 |

| Publishe           | d Paper                                                                                      | 106 |

| Vita               |                                                                                              | 110 |

## Figure Captions

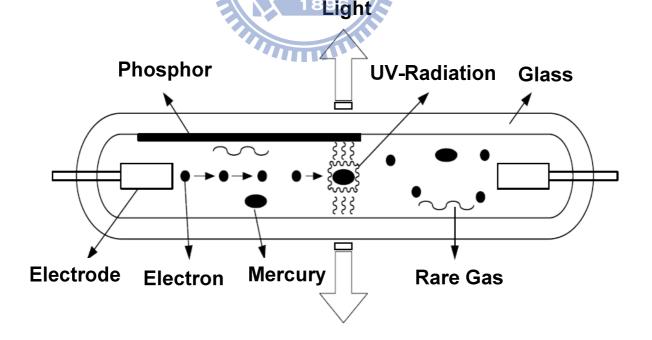

| Figure 1. The structure of cold-cathode fluorescent lamps (CCFL) backlight source              |

|------------------------------------------------------------------------------------------------|

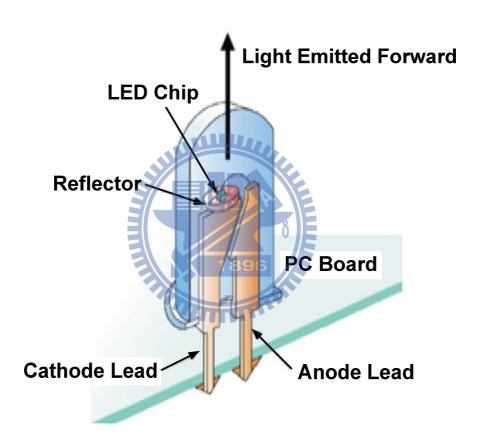

| Figure 2. The structure of light-emitting-diode (LED) backlight source                         |

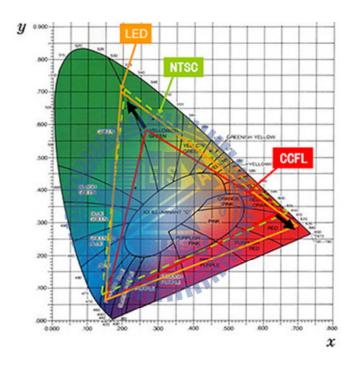

| Figure 3. International Commission on Illumination (CIE) Chromacity Diagram                    |

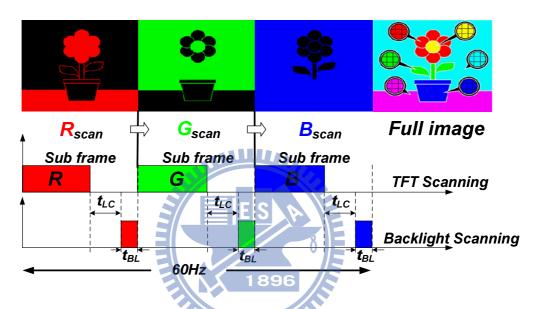

| Figure 4. The timing diagram of color sequential technique for the color filter-less LCD panel |

|                                                                                                |

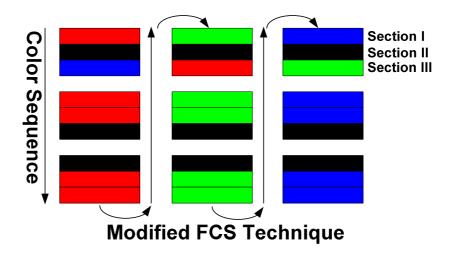

| Figure 5. The implementation of modified FCS algorithm for reducing the color breakup and      |

| improving the efficiency                                                                       |

| Figure 6. The current waveform of inductor, diode and power $MOS(I_{QI})$                      |

| Figure 7. Inductor current are CCM operation at heavy and medium loads10                       |

| Figure 8. Conventional RGB LED backlight with three DC-DC converters14                         |

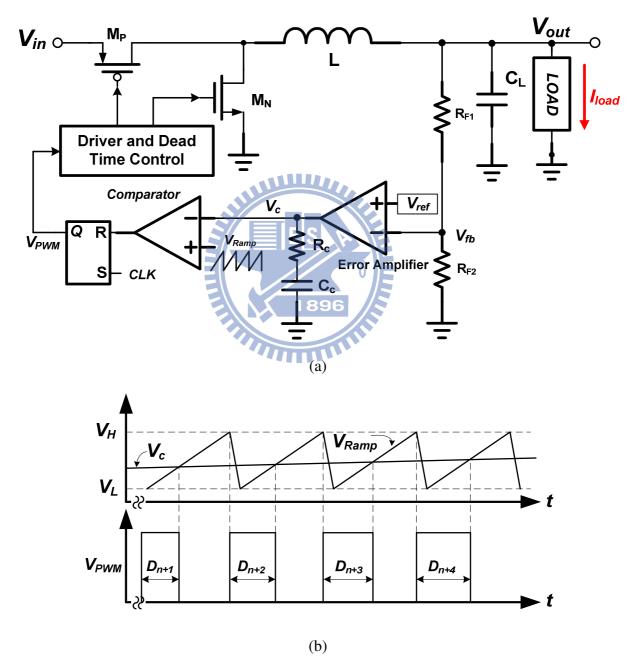

| Figure 9. (a)Conventional voltage-mode PWM buck converter. (b) The transient duty cycle o      |

| PWM signal $V_{PWM}$ at reference tracking16                                                   |

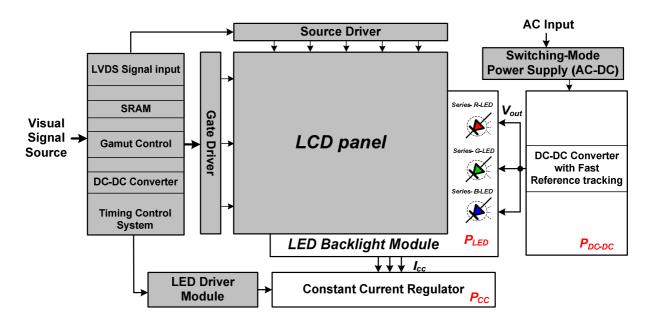

| Figure 10. A high efficiency RGB LED backlight with one DC-DC converter fo                     |

| implementation of conventional FCS algorithm                                                   |

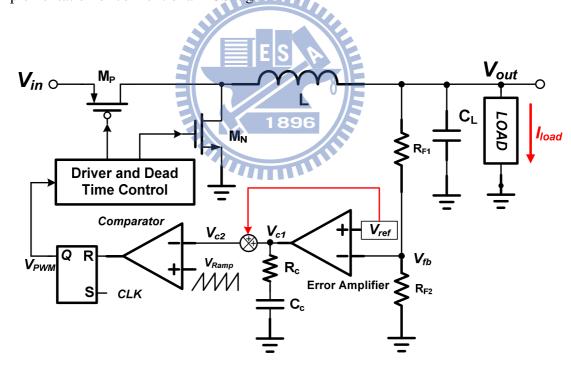

| Figure 11. Voltage-mode PWM buck regulator with end-point prediction (EPP) technique17         |

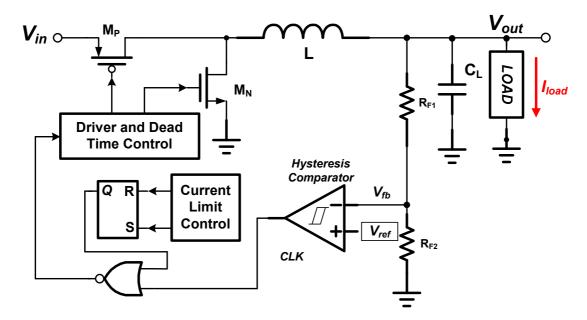

| Figure 12. System architecture of hysteresis buck converter with current limit control for fas |

| reference tracking                                                                             |

| Figure 13. The up- and down- reference tracking process.                                       |

| Figure 14 I-V curve characteristic of LED                                                      |

| Figure 15. A simplified current regulator for LED driver                                                        |

|-----------------------------------------------------------------------------------------------------------------|

| Figure 16. The prior art for LED lighting system. (a) The implementation of the LED driver                      |

| with the PCC technique. (b) The inductor current waveform of the PCC technique27                                |

| Figure 17. The prior art for LED lighting system. (a) The implementation of the LED driver                      |

| with the HCC technique. (b) The inductor current waveform of the HCC technique 30                               |

| Figure 18. The inductor current waveform at different the off-time values32                                     |

| Figure 19. The inductor current waveform at different the off-time values32                                     |

| Figure 20. The proposed LED current driver uses the SAR-controlled adaptive off-time                            |

| technique34                                                                                                     |

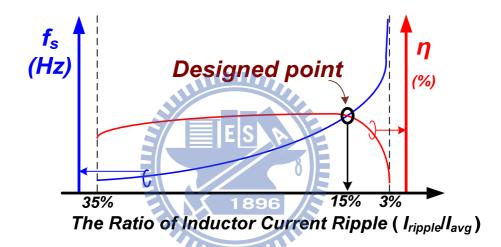

| Figure 21. The relation of the ratio of inductor current ripple $(I_{ripple} / I_{avg})$ , the power efficiency |

| $(\eta)$ , and the switching frequency $(f_s)$                                                                  |

| Figure 22. The structure of the SAR-controlled modulator                                                        |

| Figure 23. The three sub-modules in the implementation of the SAR-controlled modulator. (a)                     |

| The up-down 8-bit counter. (b) The 8-bit SAR gain code generator. (c) The over-control                          |

| logic circuit40                                                                                                 |

| Figure 24. (a) The implementation of a simple off-time circuit (b) The schematic of the                         |

| adaptive off-time circuit and the corresponding capacitor according to each bit of the                          |

| SAR code A[7:0]41                                                                                               |

| Figure 25. The design of the on-chip low-side current sensing circuit with the blanking time                    |

| circuit42                                                                                                       |

| Figure 26. The proposed LED driver contains the FRT, CR techniques, and the current balance                     |

| (CB) circuit45                                                                              |

|---------------------------------------------------------------------------------------------|

| Figure 27. (a) The PWM generator with FRT technique. (b) The determination of duty          |

| waveform in the PWM generator with FRT technique47                                          |

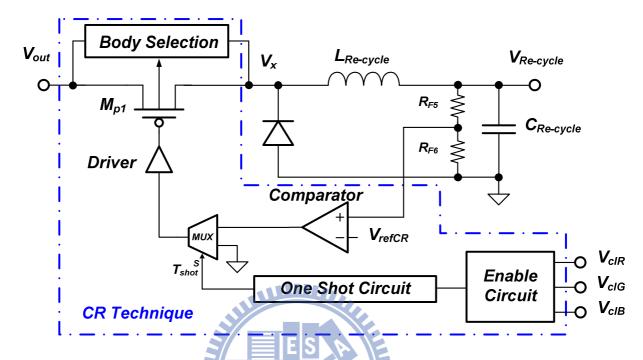

| Figure 28. The schematic of the charging-recycling technique                                |

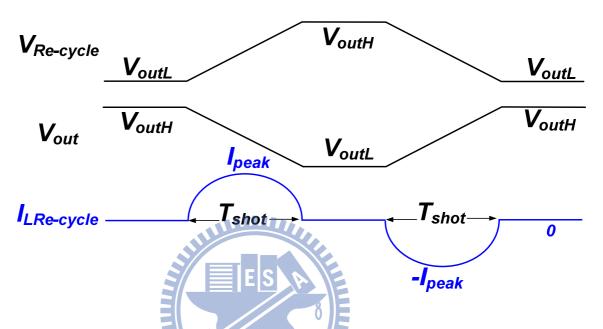

| Figure 29. The timing diagram of the proposed charge-recycling technique51                  |

| Figure 30. The timing diagram of the proposed charge-recycling technique52                  |

| Figure 31. The Bode plot of the proposed boost converter                                    |

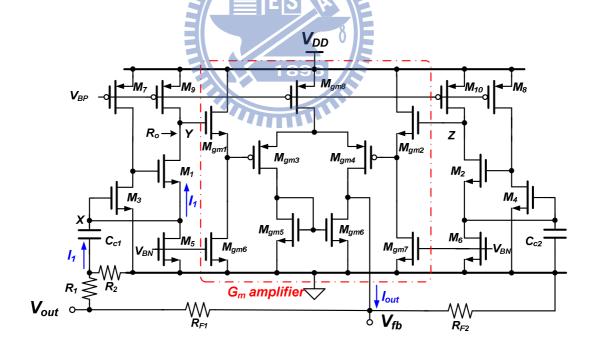

| Figure 32. The circuit of the VCCS compensator                                              |

| Figure 33. The PWM generator with FRT technique consists of voltage-to-current converters,  |

| $G_m$ amplifier, and current comparator                                                     |

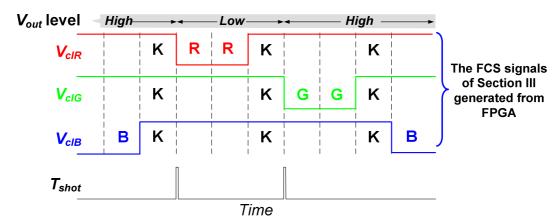

| Figure 34. The timing diagram of modifier FCS signal in Section I of the notebook and the   |

| one shot signal $T_{shot}$ .                                                                |

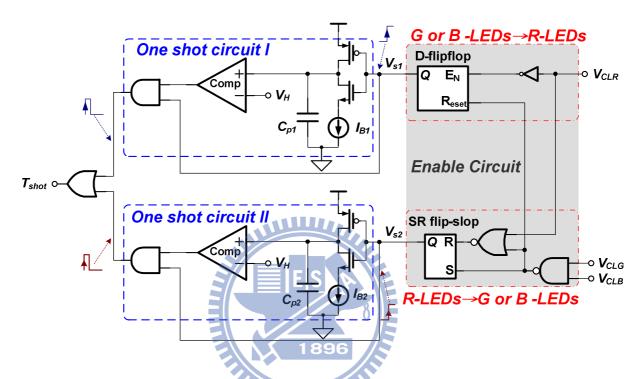

| Figure 35. The circuit of the one shot generator                                            |

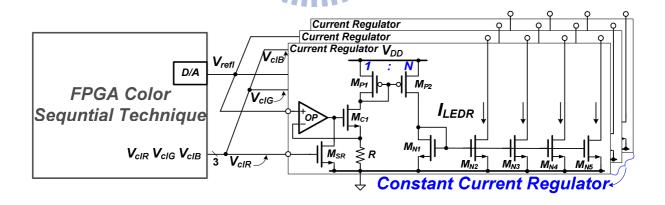

| Figure 36. The constant current regulator63                                                 |

| Figure 37. (a)The proposed boost converter with BSBR technique and the timing diagram of    |

| the voltage $V_{BSBR}$ with/without load current requested from another sub-block in the    |

| LCD driving system. The BSBR power stage can be simplified as (b) buck-store                |

| operation and (c) boost-restore operation66                                                 |

| Figure 38. The flowchart of the BSBR tracking algorithm                                     |

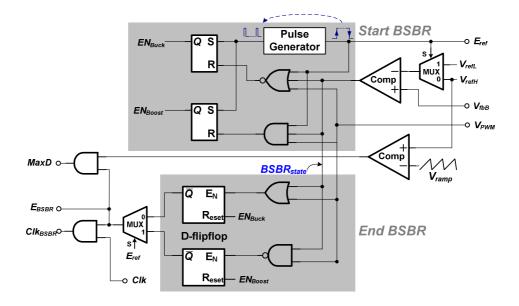

| Figure 39. The implementation of the proposed BSBR controller and the control signal timing |

| diagram 72                                                                                  |

| Figure 40. The function block of proposed BSBR Enable circuit                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

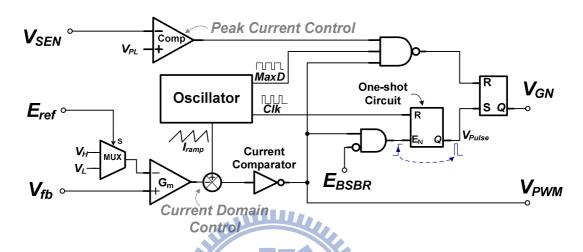

| Figure 41. The schematic of the PWM generator with characteristic of fast response and                                                                         |

| stability76                                                                                                                                                    |

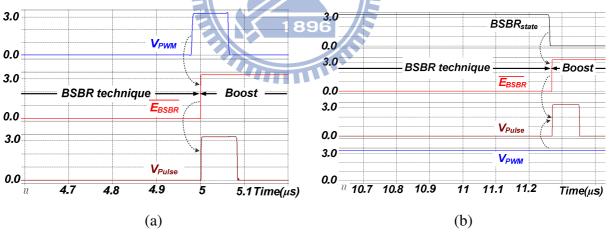

| Figure 42. The enable sequence of boost converter resulted from the end of BSBR tracking                                                                       |

| algorithm. (a) The buck-store operation is ended by the signal $V_{PWM}$ . (b) The                                                                             |

| boost–restore operation is ended by the signal <i>BSBR</i> <sub>state</sub>                                                                                    |

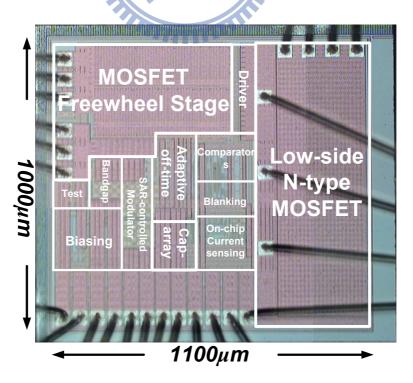

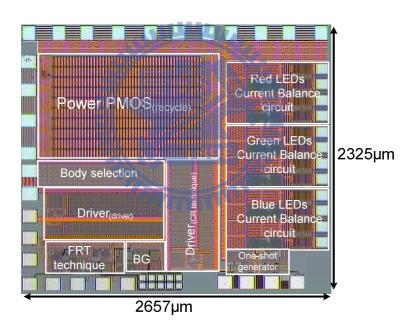

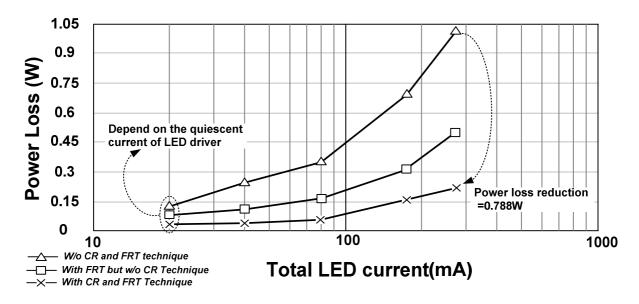

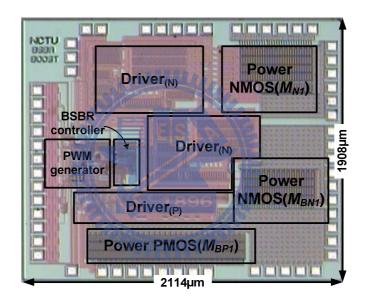

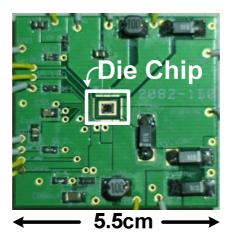

| Figure 43. Chip micrograph                                                                                                                                     |

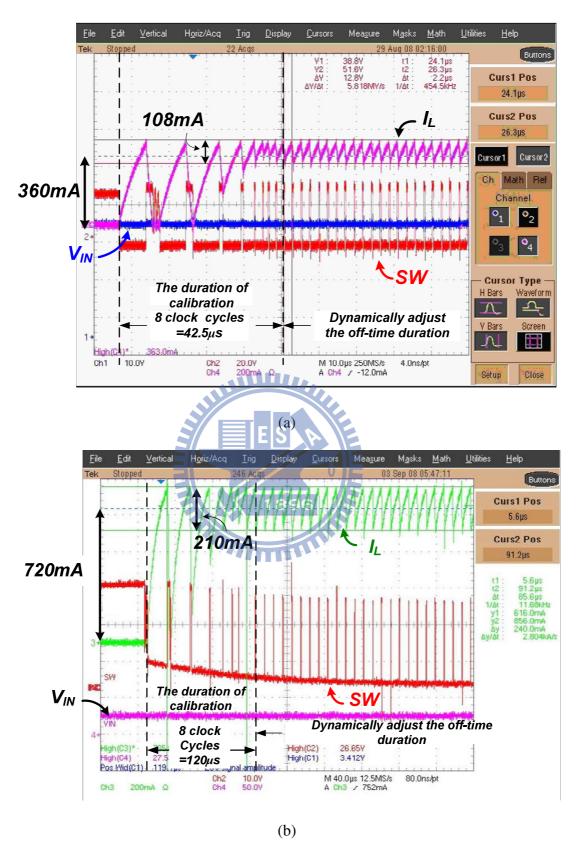

| Figure 44. Experimental results when the LED driving currents are (a) 360mA and (b) 720mA.                                                                     |

|                                                                                                                                                                |

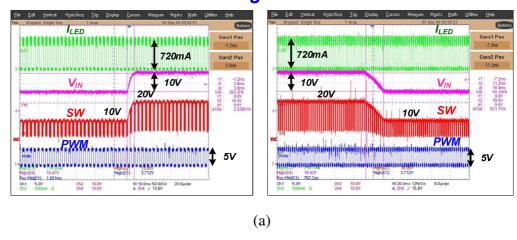

| Figure 45. Experimental results. (a) When the duty of the PWM dimming is 50 % and the                                                                          |

| input supply voltage changes from 10V to 20V or vice versa. (b) The waveforms of the SAR technique when the duties of the digital PWM signal are 25% and 50%80 |

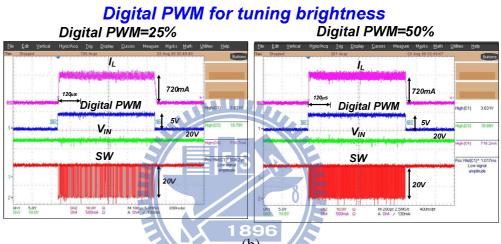

| Figure 46. Experiment results (a) The efficiency comparison between the HCC, PCC and SAR                                                                       |

| techniques. (b) The accuracy comparison between the HCC, PCC and SAR techniques                                                                                |

| at different input supply voltages                                                                                                                             |

| Figure 47. The chip micrograph                                                                                                                                 |

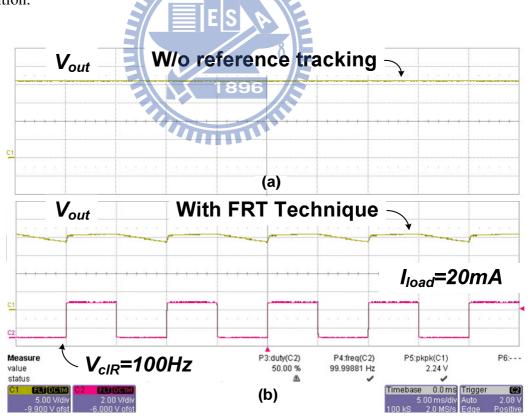

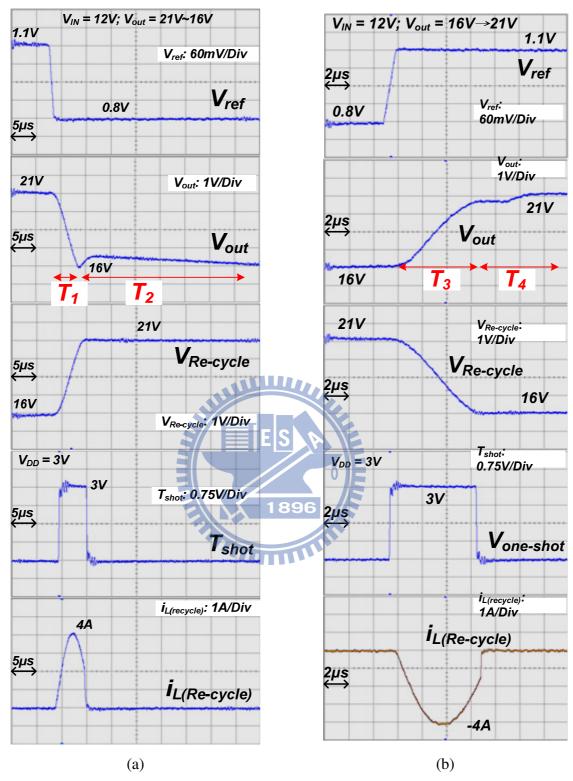

| Figure 48. (a) The waveforms of the LED driver without reference tracking technique. (b) The                                                                   |

| waveforms of the LED driver with the FRT Technique83                                                                                                           |

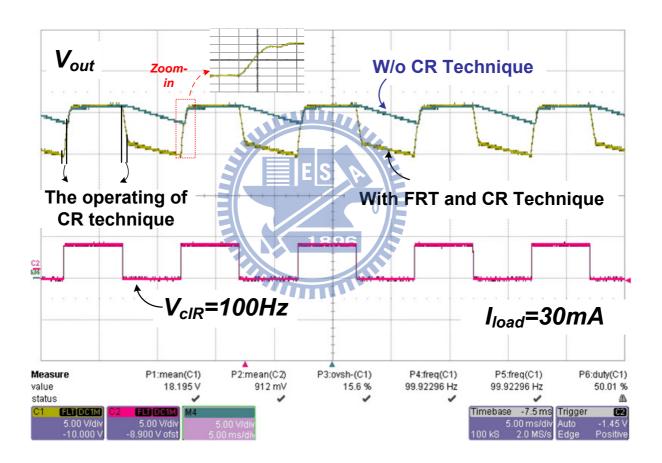

| Figure 49. The waveforms of the LED driver with or without the FRT and CR techniques84                                                                         |

| Figure 50. (a) When $V_{ref}$ changes from 1.1V for G- or B- LED to 0.8V for R-LEDs, the extra                                                                 |

| energy is stored in the auxiliary inductor $L_{(Re-cycle)}$ and capacitor $C_{Re-cycle}$ , which is                                                            |

| triggered by the one-shot generator. (b) When $V_{ref}$ changes from 0.8V for R-LED to                   |

|----------------------------------------------------------------------------------------------------------|

| 1.1V for G- or B- LEDs, the extra energy stored in the auxiliary inductor $L_{(Re-cycle)}$ and           |

| capacitor $C_{Re	ext{-}cycle}$ is released to the output node $V_{out}$ , which is also triggered by the |

| one-shot generator86                                                                                     |

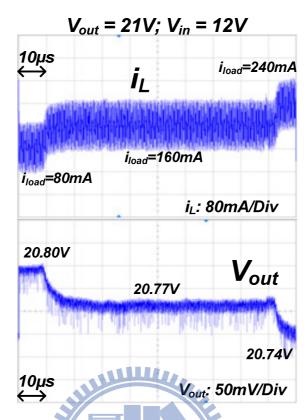

| Figure 51. Load regulation when load current changes from 80mA to 240mA                                  |

| Figure 52. Line regulation when input voltage changes from 8V to 13.5V and back to 8V when               |

| load current is 80mA                                                                                     |

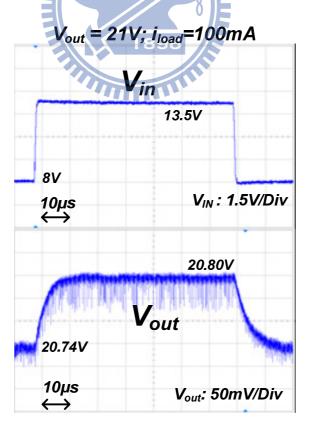

| Figure 53. Measured power loss of the LED driver with or without the FRT and CR techniques.              |

| 89                                                                                                       |

| Figure 54. Chip micrograph90                                                                             |

| Figure 55. The prototype for testing the RGB LED driver with the BSBR technique90                        |

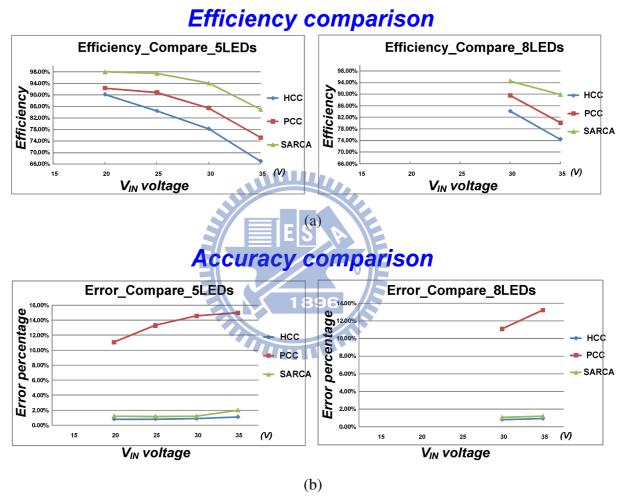

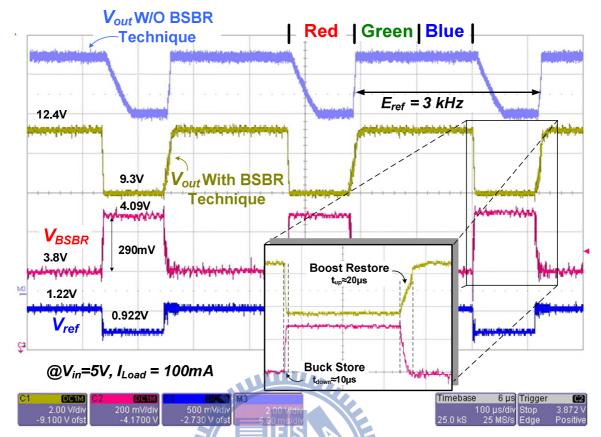

| Figure 56. Measured waveforms for reference tracking response with/without BSBR technique                |

| 93                                                                                                       |

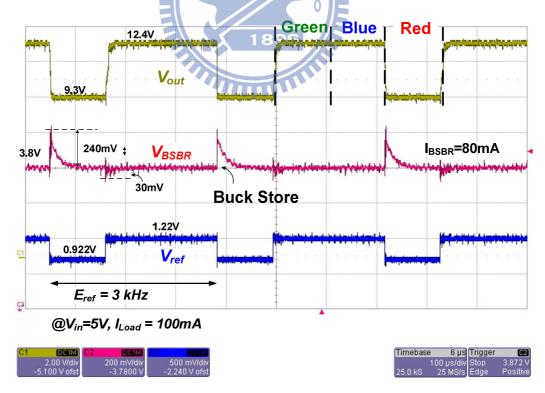

| Figure 57. Measured waveforms showing the BSBR power stage with 80mA load current                        |

| $(I_{BSBR})$ for forwarding white-LED. The PFM control and BSBR techniques are used to                   |

| maintain the voltage $V_{BSBR}$ above 3.8V94                                                             |

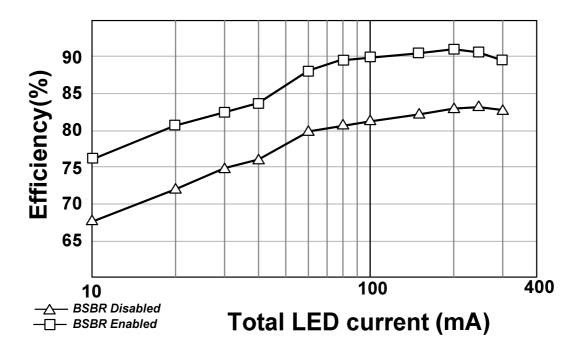

| Figure 58. Measured efficiency of the boost converter with and without BSBR technique                    |

| enabled under different load current when input voltage is 5V95                                          |

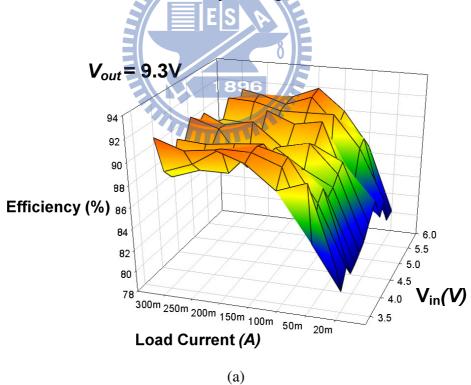

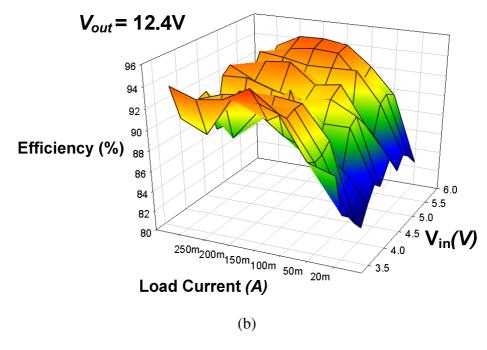

| Figure 59. Measured efficiency of the boost converter versus load current under different input          |

| voltages are illustrated (a) when output voltage is 9.3V and (b) when output voltage is                  |

| 12 AV                                                                                                    |

# Table Captions

| Table I: The Specifications of SAR Methodology        | 78 |

|-------------------------------------------------------|----|

| Table II: Performance Summary of FRT and CR Technique | 89 |

| Table III: Chin Features of BSBR Technique            | 91 |

# Chapter 1

### Introduction

### 1.1 Background and the Backlight Module

For high-quality display in liquid crystal display (LCD) panels, the selection of the backlight module becomes more and more important. The selection of backlight system not only affects the power consumption but also determines display quality. The major light sources of LCD panel are cold-cathode fluorescent lamps (CCFL) and light-emitting-diode (LED). The structure of CCFL is shown in Figure 1. Currently, the CCFL light source is widely used in LCD TV because of the light-emitting principle and the physical structure. In addition, the LCD TV is very close to the fluorescent tubes used in our daily life. The outstanding features of this light source are simple structure, less temperature rise on the surface, high brightness, easy to be processed into various shapes.

But, there are also quite a few shortcomings as follows:

- 1. In general, the working life of CCFL backlight source is 15,000 ~ 25,000 hours. The longer the LCD using, the more of the decline in brightness. After being used for 2~3 years, LCD panel will be becoming dimmed and turning yellow, as the result of the defects owing to shorter working life of CCFL.

- 2. Each pixel of the LCD panel consists of three rectangular color blocks of R, G, B, while the color expression of LCD panel entirely depend on the performance of backlight module and color filter. The 3 primary colors of color filter are expected to

luminance a white light as homogeneous as the sun light, but the CCFL backlight module cannot actually meet the design requirements, only achieve 70% of the NTSC standard.

- 3. As the CCFL is not a flat light source, in order to output the backlight, LCD's backlight module needs to be collocated with diffuser plate, light guide plate, reflector, and many other auxiliary components. While the Raster Black or Raster White screen is displayed, the brightness difference between the panel edges and center is obviously significant.

- 4. As the CCFL backlight has to contain a diffuser plate, reflector and other complex optical components, the size of LCD is no longer further reduced. Furthermore, in the aspect of power consumption, the use of CCFL as a backlight source of the LCD is also unsatisfied.

Figure 1. The structure of cold-cathode fluorescent lamps (CCFL) backlight source.

The other popular light source is LED which was invented in 1960. and the structure is shown in Figure 2. This light-emitting device can convert the electrical energy into light energy directly, with the outstanding features of low power consumption, high brightness and long working life. When LCD arrive in our world, it was recognized to be the terminator of CCFL, light bulbs and other lighting equipments, and have the opportunity to initiate a new era of lighting.

Figure 2. The structure of light-emitting-diode (LED) backlight source

Today's most popular and power-efficient backlight module is the white LED backlight in LCD panels since the power dissipation can be reduced about 40% compared to conventional CCFL backlight module. Moreover, since the backlight module will affect the color gamut, it is popular to make the use of LED backlight in the LCD panels for getting the higher color gamut. That is, the white-LED backlight has better color gamut than that of a

CCFL backlight. The disadvantage of the white-LED backlight is that it still needs the color filter to determine the color of the images since the operation of liquid crystal only determines the gray level of the image. In addition, the white-LED backlight generates only 70~80% National Television System Committee (NTSC) color gamut. Therefore, the color filter-less LCD panels with red, green, and blue (RGB) LED backlight can provide 110% NTSC color gamut as shown in Figure 3. Thus, the RGB LED backlight module becomes a trend of today's LCD display market to have better color gamut and low power consumption [1-2].

Figure 3. International Commission on Illumination (CIE) Chromacity Diagram

In addition to a good performance of color gamut, the adoption of the backlight source of RGB-LED can also enhance the contrast of LCD TV and HI-END display to achieve a more accurate gradation of gray level and layer sense of picture. LED backlight source is composed by a large number of tiny LED units that makes it successfully accomplishes the planarization of light source, any of them can attain an accurate LED brightness control, as well as the amendment of the brightness in the small region in accordance with the characteristics of the original image. The planarization of light source not only possesses excellent brightness uniformity, it does not

need a complex optical design. As a result, LCD can be made thinner, but also with a higher reliability and stability.

The ordinary working life of CCFL backlight source is about 25,000 hours, even a top-CCFL backlight source is nothing but 60,000 hours. At the end of working life, the LCD brightness will decrease significantly. However, there will be no such problem in using the panel of LED backlight source. The actual service life of a white LED backlight at this stage is 50,000~100,000 hours, which is basically the same as the life of LCD panel, but can be further enhanced potentially. Even if used 24-hours continuously, it still can work for 5 years.

In short, there are three main technical advantages for the LCD to use LED backlight source.

- 1. The planarization of light source.

- 2. In terms of color performance, the LED is far better than CCFL.

- 3. The luminous life of LED is far more than CCFL

#### 1896

In theory, the cost of LED backlight module should be lower than the CCFL. However, the price of LEDIi is still higher than the CCFL because the LED backlighting is still not mature enough, despite the LED manufacturers' great efforts, there are still a great price gap between CCFL and LED backlight module. Currently the price of LED backlight module components is about five times of the price of CCFL backlight. The larger panel size, the higher the costs of LED backlight technology. If without using the color filter and still can demonstrate the true colors, the cost of LED backlight module will be reduced by 30% and its popularity can then be speed up.

### 1.2 The Basic Theory of Field Color Sequential

According to the display method of the thin film transistor (TFT) LCD panel, the liquid crystal, which is functioned as a gate, is turned to the position determined by the content of the display data. Then, the light from backlight module only pass one of three color filters to

determine the correct color by the operation of the liquid crystal according to the image data. Therefore, the power loss due to the color filter is relatively large and the power consumption of the backlight module is difficult to be decreased because a lot of light is blocked by the color filter. Certainly, the best method is to remove the usage of the color filter.

Recently, the field color sequential (FCS) algorithm [3] that effectively reduced color breakup and motion blur effects can save much power consumption of the RGB LED backlight module without the requirement of color filter. The operation of the conventional FCS technique [3] shown in Figure 4. The frame per second (fps) for the FCS technique generally is 60Hz or 50Hz in the Europe. According to the FCS technique, one frame of data needs to be divided into three different color sub-frames, which are  $R_{scan}$ ,  $G_{scan}$ , and  $B_{scan}$  as shown in Figure 4. Thus, the full color of one image can be constituted by the three sub-frames. As a result, the sub-frame rate of the three sub-frames is 180Hz. The operation of one sub-frame contains three basic steps. The first step is the operation of Thin Film Transistor (TFT) scanning in order to get the image color data. Secondly, according to the image color data, liquid crystal is rotated to the correct position within liquid crystal time  $t_{LC}$ . Finally, after liquid crystal is turned to the correct position, the LED backlight module emits correct light through the LCD panels to display the image colors at the rest of time,  $t_{BL}$ , which indicates the lighting time to determine the brightness of backlight module. Because the RGB LED are not turned on simultaneously but sequentially, the power consumption can be reduced. However, the value of time  $t_{BL}$  is too small to provide the rated brightness since one frame is divided into three sub-frames. In order to extend the lighting time of backlight module, there are many techniques proposed [2-5] in high-performance color sequential display. Persistence of vision can make the color image appear in human's eyes without sacrificing the color gamut compared to conventional CCFL backlight. For portable devices like notebook computers, the largest power consumption comes from the backlight module.

Therefore, it is important to decrease the power consumption in backlight module of the notebooks without sacrificing any image quality. As a matter of course, the color filter-less LCD panel with the FCS technique proves to be the best choice to reduce the power consumption of the display panels in the design of notebooks. Consequently, the RGB LED backlight module with the FCS technique becomes more and more popular owing to the characteristics of low power consumption and high image quality.

Figure 4. The timing diagram of color sequential technique for the color filter-less LCD panel.

The power consumptions in the recently LCD panels are reduced to 15W in white LED backlight and 5W in color sequential RGB LED backlight system, respectively, compared to 30W in CCFL backlight. However, there is the color breakup effect when the RGB LED emit light in sequence in the FCS technique. Thus, a modified FCS algorithm is utilized to generate the color breakup-fewer patterns for reducing the side effect of color breakup [1] as shown in Figure 5. For the implementation of modified FCS algorithm, the LCD panel is divided into three sections to display different colors owing to the small-size panel of the notebooks. Furthermore, the RGB backlight module employs impulse-type display method instead of the hold-type display by CCFL backlight technique for eliminating the motion blur [1]. The

disadvantages of the conventional FCS technique can be alleviated by the implementation of the modified FCS algorithm.

Figure 5. The implementation of modified FCS algorithm for reducing the color breakup and improving the efficiency.

## 1.3 The Analysis of Power Consumption and the Overall Efficiency in the RGB LED Driver

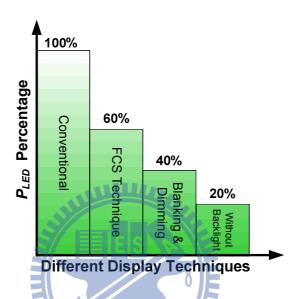

The comparison of power consumption between a conventional TFT-LCD with a white-LED backlight module and a FCS TFT-LCD with a RGB-LED backlight module is illustrated in Figure 6. Interestingly, the FCS technique can save 40% power compared to the conventional LCD display because there is no color filter that may reduce the brightness in the front of the LCD panel. Hence, the power consumption of the backlight module can be drastically minimized. Furthermore, this technique can be extended to contain the local blanking/dimming technique according to the locally averaged image data. That is, a higher power saving result can be achieved and thus the power reduction can be more than 60%. Actually, the minimum power consumption of the LCD display can be reduced to 20% of the conventional design when the backlight system is turned off. However, the image only contains gray levels at this moment. For portable devices like notebook computers, the largest

power consumption comes from the backlight module. The power consumptions in the recent LCD panels are reduced to 5W in white LED backlight and 3W in color sequential RGB backlight system, respectively, compared to 10W in CCFL backlight. Therefore, it is important to decrease the power consumption in backlight module of the notebooks without sacrificing any image quality.

Figure 6. The current waveform of inductor, diode and power  $MOS(I_{Ql})$

In addition, when the modified FCS technique is applied in the LCD panel, there is only one of three colors or black frame appearing in each section of the LCD panel. In general, the forward voltages of red, green, and blue LED are different to each other owing to the characteristic of material. Furthermore, the light illumination of LED is related to the amount of driving current and the forward voltage [6-7]. However, it is unreliable that the light illumination is controlled by utilizing the forward voltage when temperature and time is changed [8-9]. That is, it is inappropriate to make use of forward voltage to control the brightness of LED for getting high quality image of LCD panel. In order to get uniform and sufficient luminance, the LCD backlight module requires many LED to be series-and parallel-connection. The series connection ensures the series LED have the same conduction current. The parallel connection needs a constant current regulator circuit to maintain stable and

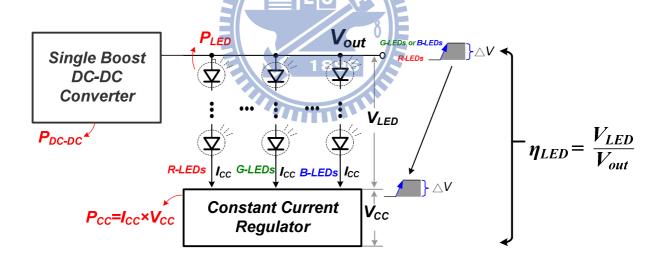

uniform light illumination in every series connection as shown in Figure 7. The Single Boost DC-DC converter is used to offer a sufficient voltage to overcome all the forward voltage  $V_{LED}$  of series LEDs. Owing to the great variation of LED material, each of the series LED forward voltage  $V_{LED}$  is different. Hence, the current balance circuit is designed as the current of LED  $I_{CC}$  that is independent of the voltage  $V_{CC}$ , which is the voltage across the current balance circuit. In general, the LED module will minimize the voltage  $V_{CC}$  [8-9] for reducing the power consumption because the power consumption is equal to the product of  $V_{CC}$  and  $I_{CC}$ . If the output voltage is larger than  $V_{LED}+V_{CC(min)}$ , the redundant voltage will be across the current balance circuit. Therefore, the power loss will be increased and the efficiency  $\eta_{LED}$  of the LED array, which depends on the ratio of the  $V_{LED}$  and the  $V_{out}$ , will be decreased. In order to improve the efficiency of LED backlight module, the value of the voltage  $V_{CB}$  must be minimized and the variation of the voltage  $V_{CB}$  will not affect the driving current  $I_{CB}$ .

Figure 7. Inductor current are CCM operation at heavy and medium loads

The power dissipation  $P_{module}$  in LED backlight module for the FCS technique is composed of three parts as expressed in (1).

$$P_{module} = P_{LED} + P_{CC} + P_{DC-DC} \tag{1}$$

$P_{LED}$  is the power consumption on the series-connected LED when the constant driving current flows through and forces the LED to emit light to the LCD panel. The constant driving current generated by the constant current generator consumes power dissipation  $P_{CC}$ , assuming the voltage across the constant current generator is  $V_{CC}$ . Besides, the power dissipation of the boost DC-DC converter is  $P_{DC-DC}$ . In the efficiency consideration of the backlight module, the power conversion efficiency of the switching DC-DC converter is higher than 90%. That is, the reduction of power loss  $P_{DC-DC}$  in the DC-DC converter is much smaller than those of other power dissipations and cannot be decreased remarkably. Thus, in order to reduce the overall power consumption of the LED backlight module, the primary consideration of reducing power consumption is focused on the  $P_{LED}$  and  $P_{CC}$ .

When the power consumption of conventional LCDs with white-LED backlight and FCS LCDs with RGB-LED backlight are compared under the same light illumination condition, the FCS technique can save 40% power compared to the conventional LCD display since there is no color filter that reduces the brightness of the LCD panel. Hence, the power consumption  $P_{LED}$  of the backlight module can be drastically minimized. The power dissipation on the constant current regulator is proportional to the current  $I_{CC}$  and the headroom voltage  $V_{CC}$  as shown in Figure 7. According to the aforementioned statement, the  $I_{CC}$  is designed to define the brightness of LCD panel which should not be reduced arbitrarily. Therefore, the LED backlight module is designed to minimize the voltage  $V_{CC}$  for reducing the power consumption [10-11]. Generally speaking, since the material characteristic of blue and green LED is indium gallium nitride (InGaN) and the material characteristic of red LED is aluminum gallium indium phosphate (AlGaInP) [12], the forward voltages of red LED are different from that of green and blue LEDs. That is, the forward voltage of green and blue LED is approximately 2.8~3.3V, and the forward voltage of red LED is close to 2.2~2.8V. Moreover, LED drivers use constant current regulator to provide the constant current for

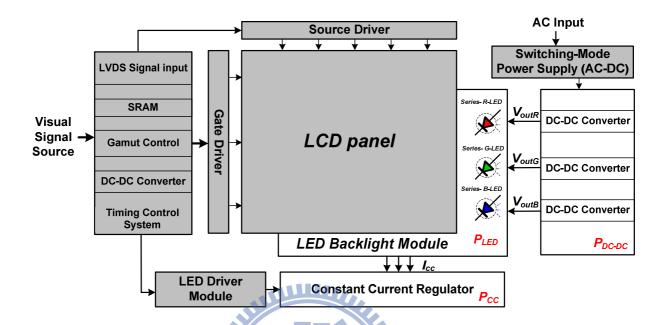

constant lumen. In general, the constant current generator occupied minimum about 0.4V to keep the characteristic of regular current and when the current is regulated to 25mA, the forward voltages of an R-LED and a G-LED (or B-LED) are close to 2.2V and 3V, respectively. As a result, the LED backlight driver would employ more DC-DC converter to provide different output voltage for overcoming the forward voltage of different color series-LEDs. Therefore, the LED with different colors require different supplying voltages [13]. That is, the implementation of the LED driver of the modified FCS algorithm needs nine DC-DC converters for driving the notebook's panel with the advantages of much power saving on the current balance circuit. However, the disadvantages are required the larger cost and the printed circuit board (PCB) area.

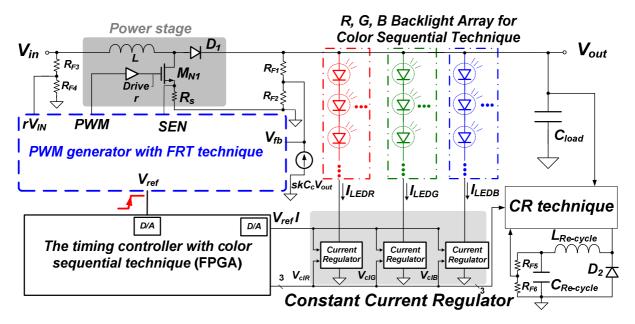

This thesis proposes two kinds implementations of the RGB backlight module for achieving the fast reference tracking. First method, the charge recycling (CR) technique and the fast reference tracking (FRT) are applied to a single boost converter. The other method is the buck-store and boost-store (BSBR) technique. The proposed fast reference tracking (FRT) can enhance the transient response of up- and down-reference tracking. The proposed CR and BSBR techniques can store extra charge and recycle it back to the output node when the backlight module switches between the R-LED and G-LED (or B-LEDs). The efficiency of CR and BSBR techniques can be up to about 90% and 94%, respectively, which is the common power efficiency in DC-DC converters. Moreover, the BSBR stage not only can operate the buck-store and boost-restore operations in order to achieve fast reference tracking performance but also can supply the regulated voltage  $V_{BSBR}$  by the Pulse Frequency Modulation (PFM) control when the stored charge needs to supply other sub-blocks of the system. The fast reference tracking performance can ensure the voltage across the constant current generator is minimized to achieve high efficiency. As a result, the equation of

luminance efficiency, which indicates the power transformation from the electric power to light luminance, can be written as (2).

$$\eta_{module} = \frac{K \times P_{LED}}{P_{LED} + P_{CC} + P_{DC-DC}}$$

(2)

K indicates the converting coefficient from electric power  $P_{LED}$  to luminance of light. This value of K depends on different display techniques and backlight characteristics. This thesis uses the FCS technique to enhance the value of K so that the backlight module can achieve better light luminance by means of smaller power dissipation  $P_{LED}$ . Furthermore, the DC-DC converter with the BSBR technique can efficiently store and recycle extra charge, and thereby reducing the value  $P_{CC}$  to improve the overall efficiency  $\eta_{module}$ . As a result, the proposed techniques can reduce the number of DC-DC converters and output component for reducing the cost and the printed circuit board (PCB) area. In addition, the high efficiency also can be acquired.

#### 1.4 Prior Arts

The conventional RGB LED backlight module with conventional FCS algorithm, which utilizes many output components and DC-DC converters for providing the different output voltages, is illustrated in Figure 8 [14-16] because the forward voltages of red, green, and blue LED are different to each other from the characteristic of material. Therefore, the cost and footprint area is an drawback in the conventional LED backlight module system. In addition, when the modified FCS algorithm is applied in the LED backlight module, the LCD panel is divided into three sections to display different colors for the small-size panel of the notebooks. There is only one of three colors or black frame appearing in each section of the LCD panel as shown in Figure 4. As a result, the LED driver with the modified FCS algorithm requires nine

DC-DC converters for driving the notebook's panel with the advantages of much power saving on the current balance circuit.

Figure 8. Conventional RGB LED backlight with three DC-DC converters.

In general, the six series LED are applied in the LED backlight module of notebook, and thus LED backlight module would supply 16 V and 21 V for 6 series R-LED and G- or B-LEDs, respectively. Since the bandwidth of the DC-DC converter is limited to the low-pass filter which is composed of the inductor and capacitor, the fast output voltage tracking between 16V and 21V is very difficult in the conventional DC-DC boost converters. Therefore, the LED with different colors require different supplying voltages [13]. That is, the implementation of the LED driver of the modified FCS algorithm needs nine DC-DC converters for driving the notebook's panel with the advantages of much power saving on the constant current regulator.

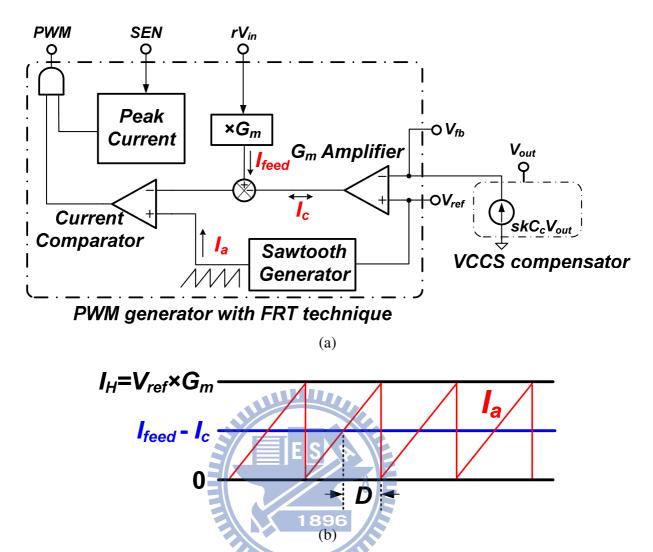

The conventional voltage-mode PWM buck converter is depicted in Figure 9 (a). The power stage is composed of power transistors  $M_P$ ,  $M_N$ , and low-pass filter which is formed by inductor L and capacitor  $C_L$ . The error amplifier with compensated resistor and capacitor

compare the reference voltage  $V_{ref}$  with feedback voltage  $V_{fb}$  to generate the error signal  $V_c$  for determining the duty cycle of PWM signal  $V_{PWM}$ . In addition, the duty cycle of continuous-conduction mode (CCM) buck converter has a relationship with output voltage and input voltage  $(V_{out}/V_{in})$ . Thus, the conversion equation is given by

$$\frac{V_{out}}{V_{in}} = D = \frac{V_c - V_L}{V_H - V_L} \tag{3}$$

where  $V_H$  and  $V_L$  are upper and lower bounds of the ramp signal VRamp. When the reference voltage  $V_{ref}$  is changed, the output voltage  $V_{out}$  would be varied by changing the duty cycle of PWM signal  $V_{PWM}$  as shown in Figure 9 (b). Since a large compensator capacitor is utilized to provide the dominant-pole for compensating the power system. The signal  $V_c$  would slowly raise to the steady state and the tracking response of output voltage is slow.

This thesis proposes a DC-DC converter with fast reference tracking to provide the output voltage for overcoming the different color of series-LEDs. The new implementation of the RGB backlight module is depicted in Figure 10 for achieving low cost and high efficiency. It is obvious that only one DC-DC converters are employed. The hardware cost and volume can be effectively reduced.

Several topologies and control techniques have been proposed to fast reference tracking output voltage. The reference tracking technique in [17] proposes the end-point prediction (EPP) for voltage-mode PWM buck regulator as shown in Figure 11. A voltage adder is required to sum the error signal  $V_{c1}$  and reference voltage  $V_{ref}$  to form the  $V_{c2}$  and generate the PWM signal. In addition, this technique design that the upper bound of ramp signal  $V_H$  is equal to

$$V_H = b \times V_{in} + V_L \tag{4}$$

where b is the ratio of feedback resistor ( $R_{Fl}$  and  $R_{F2}$ ). Therefore, the information of reference voltage and input voltage is acquired to generate the PWM signal for improving the transient response of reference tracking. However, the transient response of up-tracking still be clamped by the compensation capacitor.

Figure 9. (a)Conventional voltage-mode PWM buck converter. (b) The transient duty cycle of PWM signal  $V_{PWM}$  at reference tracking.

Figure 10. A high efficiency RGB LED backlight with one DC-DC converter for implementation of conventional FCS algorithm.

Figure 11. Voltage-mode PWM buck regulator with end-point prediction (EPP) technique

Another reference tracking technique in [18] is utilized by the hysteretic comparator and limiting current control to improve the transient response of reference tracking as shown in Figure 12.

Figure 12. System architecture of hysteresis buck converter with current limit control for fast reference tracking.

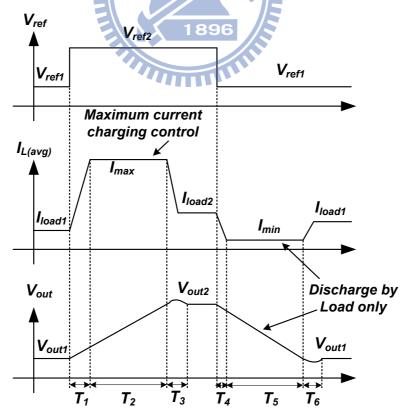

The up-tracking process can be divided into the following three phases as shown in Figure 13.

- 1. Inductor current ramp up phase  $(T_I)$ : During the period  $T_I$ , the average inductor current ramps up from the output (load) current to the maximum allowable current with full duty cycle. The Hysteresis buck converter can generate the full duty cycle. Thus, the inductor current can fast ramp up to maximum current.

- 2. Maximum current charging phase  $(T_2)$ : During the period  $T_2$ , the inductor current switches between two predefined levels such that the average inductor current is kept at  $I_{max}$ . The maximum current is charging the output capacitor at full speed until the output voltage reaches the predefined value  $V_{out2}$ .

- 3. Inductor current ramp down phase  $(T_3)$ : When the output voltage reaches the predefined value, the inductor current is then decreased to the new output load current. The load transient time depends on the control methodology of the converter. The total up-tracking time is  $T_1 + T_2 + T_3$ .

The down-tracking process also can be divided into the following three phases as shown in Figure 13.

- 1. Inductor current ramp down phase  $(T_4)$ : During the period  $T_4$ , the average inductor current ramps down from the load current to the minimum current level which is close to zero. The Hysteresis buck converter would not turn on the Power MOSFET  $M_P$ . Thus, the inductor current can fast ramp down to minimum current.

- 2. Maximum current charging phase  $(T_5)$ : During the period  $T_5$ , the output voltage is discharge by the load current and the down-tracking speed is dominated by the load resistor.

- 3. Inductor current ramp up phase  $(T_6)$ : When the output voltage reaches the predefined value, the inductor current is then increased to the new output load current. The total down-tracking time is  $T_4 + T_5 + T_6$ .

Figure 13. The up- and down- reference tracking process.

#### 1.5 Motivation

In order to effectively reduce the chip cost and footprint area of the LED backlight module, the reference tracking process is required to turn on the RGB LED in sequential. The prior arts of reference tracking technique are well-design on the up-reference tracking response, however, the down-reference tracking are always depending on the load resistor or releasing the energy to ground. This thesis proposed the fast reference tracking (FRT) and charge recycle (CR) techniques to implement the up- and down- reference tracking with fast response and high efficiency. The FRT technique can make the LED driver drives more than 6-series R- and G-/B- LED by fast increasing or decreasing the output voltage to correct voltage level. Furthermore, the CR technique is presented to store the extra energy when the output voltage is decreased from high-supplying voltage level for 6-series G-/B- LED to low-supplying voltage level for 6-series R-LEDs. Therefore, the CR technique can quickly decrease the output voltage and the stored energy can be sent back to the output node for rapidly increasing the voltage level back to the high-supplying voltage level. Therefore, the proposed LED driver with FRT and CR techniques achieve high efficiency conversion and low cost performance compared to the conventional design. Moreover, three DC-DC converters can be decreased to only one DC-DC converter at the sacrifice of power consumption. In addition, this thesis also proposed charge recycling buck-store and boost-restore (BSBR) technique. This technique can be implemented as buck and boost converter on a single converter to store and recycle the extra energy for reducing the power dissipation on the LED driver circuit and applied on the boost converter to control the voltage.

### 1.6 Thesis Organization

In the following chapters, an integrated LED driver with fast reference tracking techniques including the CR and BSBR control mechanism are presented in this thesis. In

addition, the current regulator and current balance circuit are also discussed in this thesis. The Chapter 2 would describe the architecture of constant current regulator for LED Driver with the SAR-controlled adaptive off-time technique. The characteristics of LED backlight module and LCD panel are introduced in this chapter. In addition, the advantages and the disadvantages of these prior arts would be discussed in Chapter 2. In the Chapter 3, the analysis of the reference tracking procedure with FRT and CR technique is presented. The FRT technique is utilized for rapidly switching between two different output voltages and the CR technique is proposed for saving much power dissipation during the transition between two different output voltages. Furthermore, the stability and transient response of the LED driver with FRT technique is also discussed in this chapter. The circuit implementation composed of the voltage control current source (VCCS) compensator, the PWM generator, and the one-shot generator would be detailed illustrated in Chapter 3. In Chapter 4, a new charge recycling buck-store and boost-restore (BSBR) technique is proposed to reduce the power dissipation on the LED driver circuit and is applied on the boost converter to control the voltage, 9.3V for 4 series R-LED and 12.4V for G- or B- LED in the LED backlight module. The architecture of the proposed BSBR control, the BSBR tracking algorithm and the energy transforming efficiency are also discussed in detail. Experimental results shown in Chapter 5. Finally, conclusions are made in Chapter 6.

.

### Chapter 2

### The Architecture of Constant Current Regulator for LED Driver

#### 2.1 The Characteristic of LED

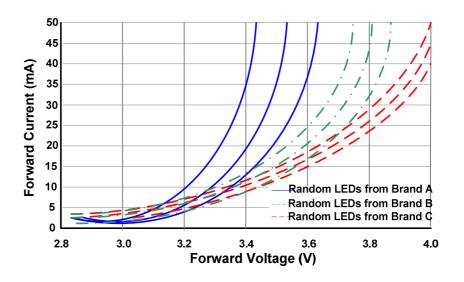

The LED I-V curve is shown in Figure 14. Because LED can be manufactured with smaller mismatch, the forward voltage variation of LED is expected. In addition, the forward voltage also varies with temperature and time. In order to get high quality image for LCD TV, it is impossible to regulate the forward voltage of LED to dimming the LED for changing the backlight brightness. In other words, the luminance is proportional to the level of driving current. The higher driving current will cause the higher brightness. As a result, by using the current to dimming the LED can prevent the variation of forward voltage and increase the brightness uniformity of LED backlight to get the high quality image of LCD TV.

Figure 14 I-V curve characteristic of LED

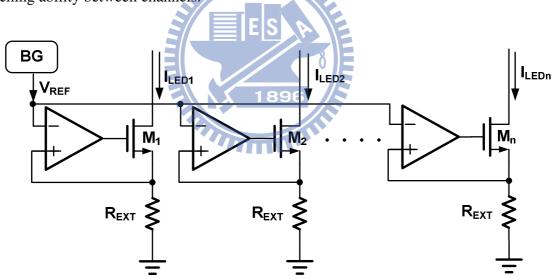

#### 2.2 The Basic LED Current Regulators

The most common method to drive LED current is shown in Figure 15. A simple current regulator is implemented for LED strings. This circuit includes operational amplifier, a reference voltage,  $V_{REF}$ , and the value of the external resistor,  $R_{EXT}$ , to determine the LED current. It is uses the constant-current source to regulate LED strings [19-20]. The constant-current source eliminates LED current changes due to variations in forward voltage. By using the constant-current source produces the constant LED brightness and strings uniformly. In Figure 15, LED can connect in a series and parallel to keep an identical current flowing in each LED, because the LED current  $I_{LED1} \sim I_{LEDn}$  are produced by the value as  $V_{REF} / R_{EXT}$ . Therefore, if the external resistances are matched, this circuit can increase the current matching ability between channels.

Figure 15. A simplified current regulator for LED driver.

Another important issue is LED dimming control. LED dimming control is needed in many applications. In applications as LCD backlighting, dimming provides brightness and contrast adjustment. In general, two types of dimming methods can be achieved, analog and pulse width modulation (PWM) [21]. In analog dimming, the changing of LED's forward current can change the brightness. For example, if an LED is at full brightness with 20 mA of

forward current, then 50% of the brightness is achieved by applying 50% of the maximum current to the LED. However, the drawback with analog dimming is that changes in forward current cause LED's color shift. This color shift may become unacceptable in displays requiring a true color representation. On the other hands, PWM dimming is achieved by applying full current to the LED at a modulated duty cycle. The LED brightness is controlled by adjusting the relative duty cycle. For example, 50% brightness level is achieved by turning the LED on time at full current for 50% of each period. The advantage of PWM dimming is that the forward current is always constant, so we just have to decide the maximum current for all the LED strings. Instead of analog dimming, by using this method, LED color does not vary with brightness. In order to keep the human eyes from seeing the LED turn on and off, the switching speed must be above 100 Hz. Therefore, the proposed method also includes the PWM dimming control circuit to maintain the benefits of PWM dimming. In order to eliminate the inrush current occurred at the instance of string turn on, we also proposed a delay method to reduce it. By using the delay method, the on time of all the strings will be split into several parts. In other words, turning on the strings gradually can reduce the charge current at the moment. The proposed circuit not only balances the current for LED strings but also is suitable for PWM dimming control.

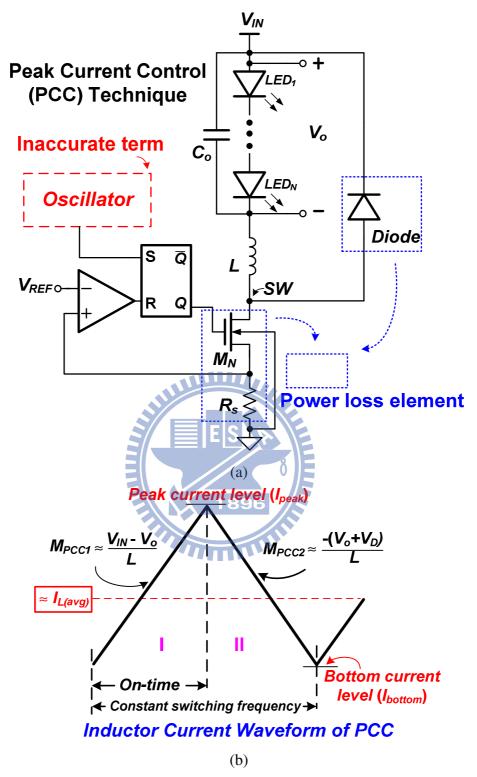

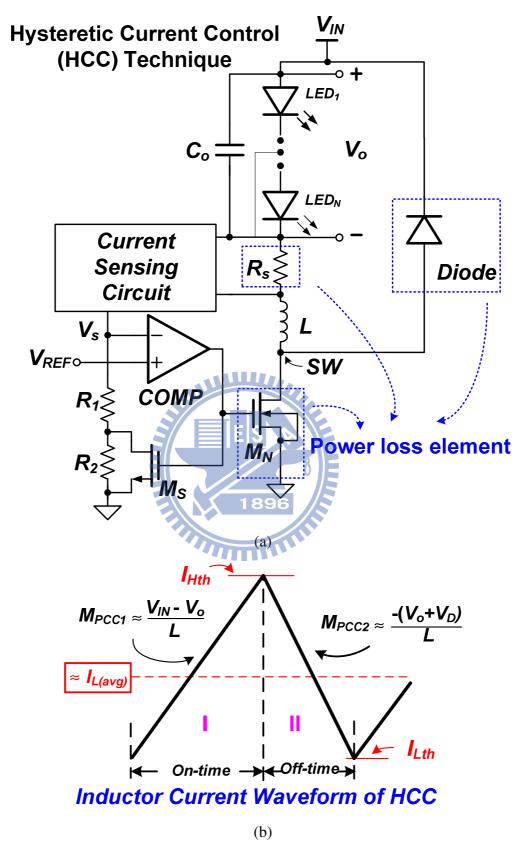

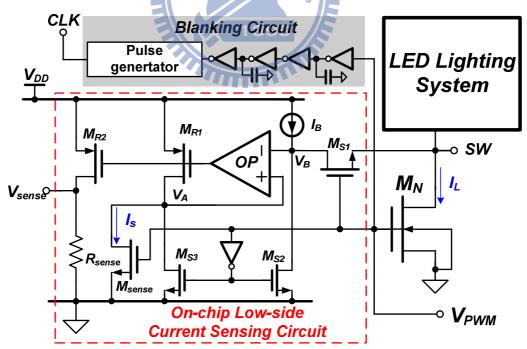

### 2.3 The Structure of LED Lighting System with HCC and PCC Technique

There is another structure of LED driver for lighting system. The design of the LED lighting system needs the regulated driving current technique to flow through the LED for uniform brightness. The prior arts of the LED driver are the hysteretic current control (HCC) and peak current control (PCC) techniques. The PCC technique uses a constant off-time to reduce the need for the connection of the sensing resistor in series with the LEDs, sacrificing

the accuracy. The PCC technique connects the sensing resistor at the source node of the N-type power MOSFET. As a result, the PCC technique has the advantage of high efficiency but low accuracy. Therefore, how to get high efficiency and accuracy at the same time becomes an important design issue in an LED lighting system. The implementation of the conventional PCC technique is shown in Figure 16(a). It includes an oscillator to periodically turn on the N-type power MOSFET  $M_N$ . When the inductor current is increased to the predefined peak current level, the N-type power MOSFET  $M_N$  will be turned off. As a result, the inductor current is discharged by the freewheel-diode. The inductor current also flows through the LEDs; thus, the average inductor current will determine the brightness of the LEDs. Considering the inductor current waveform in the steady state as shown in Figure 16(b), the inductor current ripple  $\Delta I_L$  can be expressed as (5).

$$\Delta I_L = \frac{V_{IN} - V_o}{L} t_{on} = \frac{V_o + V_D}{L} t_{off} \quad \text{where } V_o \approx nV_F$$

(5)

$V_F$  and  $V_D$  are the forward voltages of the LED and the freewheel-diode, respectively. The  $V_o$  is equal to the summation of the total forward voltage of LED in series. The  $t_{on}$  and  $t_{off}$  are the on-time and off-time of the N-type power MOSFET  $M_N$ , respectively. Owing to the constant switching frequency,  $t_{on}$  and  $t_{off}$  can be approximately described as (6) and (7), respectively. The forward voltage of freewheel-diode is ignored in (6).

$$t_{on} = DT_s = \frac{V_o}{V_{IN}}T_s \tag{6}$$

$$t_{off} = (1 - D)T_s = \left(1 - \frac{V_o}{V_{IN}}\right)T_s \tag{7}$$

$T_s$  and D are defined as the switching period and the duty cycle of the LED driver,

respectively [22]. Since the bottom current level is determined by the switching frequency, the average inductor current  $I_{L(avg.)}$  can be calculated as (8).

$$I_{L(avg)} = I_{peak} - \frac{V_o}{2L} t_{OFF} = I_{peak} - \frac{V_o T_s}{2L} \left( 1 - \frac{V_o}{V_{IN}} \right)$$

(8)

The value of the input voltage  $V_{IN}$  will affect the average inductor current. Moreover, the different numbers of LED in series which cause the different output voltage ( $V_o \approx nV_F$ ) influence the average inductor current. Hence, the brightness of the LED is drastically influenced by the variation of the input voltage. Furthermore, as shown in Figure 16(a), the major power dissipation of the LED driver in the PCC technique is caused by the external sensing resistor  $R_s$  and the diode during phases I and II, respectively. In phase I, the inductor current passes through the external sensing resistor  $R_s$  and the equivalent resistance of the  $M_N$  ( $R_{on}$ ) results in the energy consumption calculated as (9).

$$E_{phI(PCC)} = I_{L(avg)}^{2} \times (R_{on} + R_{s}) \times t_{on}$$

(9)

Moreover, the inductor current flows through the freewheel-diode to decrease the inductor current during phase II. Therefore, the freewheel-diode also brings the energy dissipation described as (10).

$$E_{phII(PCC)} = I_{L(avg)} \times V_D \times t_{off}$$

(10)

Figure 16. The prior art for LED lighting system. (a) The implementation of the LED driver with the PCC technique. (b) The inductor current waveform of the PCC technique.

The HCC technique utilizes two threshold current levels to accurately control the average inductor current  $I_{L(avg)}$ , thereby defining the switching frequency [22]. The

implementation of the fundamental HCC technique is shown in Figure 17(a). It includes the simplest implementation of the current sensing circuit composed of an external resistor,  $R_S$ . The inductor current waveform in the steady-state is shown in Figure 17(b). The two threshold current levels are defined as  $I_{Hth}$  and  $I_{Lth}$  indicating the high and low threshold current levels, respectively. When the switch  $M_S$  and the N-type power MOSFET  $M_N$  are turned on, the inductor current increases at a rate determined by  $(V_{IN} - V_o)/L$ . Thus, the current sensing circuit generates the sensing current via  $R_I$  and the switch  $M_S$  to produce the ramp voltage  $V_S$ . When the voltage  $V_S$  is higher than the  $V_{REF}$ , the switch  $M_S$  and the N-type power MOSFET  $M_N$  are turned off by the output of the comparator. Therefore,  $V_S$  has a step variation since the sensing current passes through both the resistors  $R_I$  and  $R_2$ , not only through  $R_I$ . In addition, the inductor current is discharged via the freewheel-diode back to  $V_{IN}$ , as such,  $V_S$  decays at a rate decided by the inductor current. The current ripple can be defined as (11):

$$\Delta I_L = I_{Hth} \times \frac{R_2}{R_1 + R_2} = I_{Lth} \times \frac{R_2}{R_1}$$

1896

The HCC technique can accurately design the low threshold current  $I_{Lth}$  and the inductor current ripple by defining the high threshold current  $I_{Hth}$  and utilize the suitable resistors  $R_1$  and  $R_2$ . Hence, the average inductor current can be accurately described as (12).

$$I_{L(avg)} = \frac{I_{Hth} + I_{Lth}}{2} \tag{12}$$

As a result, the HCC technique can achieve a more accurate average current than that of the PCC technique. Hence, the brightness of the LED can be effectively controlled by the HCC technique. However, the large inductor current flows through the sensing resistor  $R_s$  in the full period since the whole switching period needs the information of the inductor current

to compare it with the two threshold current levels. Thus, the energy dissipation by the conduction loss in phase I and phase II can be expressed as (13) and (14), respectively

$$E_{phI(HCC)} = I_{L(avg)}^{2} \times (R_{on} + R_{s}) \times t_{on}$$

(13)

$$E_{phII(HCC)} = \left(I_{L(avg)} \times V_D + I_{L(avg)}^2 \times R_s\right) \times t_{off}$$

(14)

According to (9) and (10), the power consumption depends on the sensing resistor  $R_s$  and the forward voltage of freewheel-diode  $V_D$  because the  $R_s$  is much larger than  $R_{on}$ . However, comparing (10) and (14), the power efficiency of the PCC technique is generally higher than the HCC technique because the inductor current passes through the sensing resistor during phase I instead of the full period. Thus, the conduction loss of the HCC technique is larger than that of the PCC technique. There is a trade-off between accuracy and efficiency in the design of the LED driver. The HCC technique can have more accurate average current but larger conduction loss. On the other hand, the PCC technique can achieve higher efficiency at the expense of accuracy. To achieve higher accuracy and efficiency at the same time, the current regulator with the SAR-controlled adaptive off-time technique is proposed.

Figure 17. The prior art for LED lighting system. (a) The implementation of the LED driver with the HCC technique. (b) The inductor current waveform of the HCC technique.

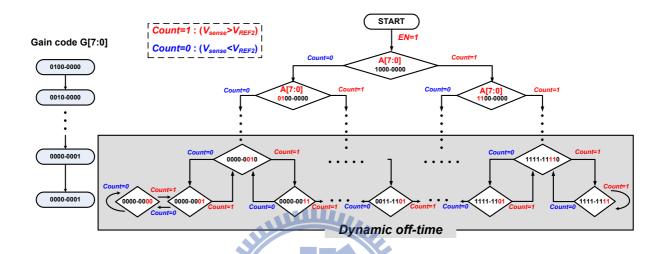

# 2.4 The Successive Approximation Register (SAR) Design Methodology

The conduction loss of phase I due to the sensing resistor [7], [21] can be reduced by means of the on-chip low-side current sensing circuit that can accurately define the peak current level [23]. Additionally, the removal of the external sensing resistor can also save the cost and footprint area, but this causes an inability to sense inductor current during phase II [16]. Thereby, the average inductor current is difficult to accurately control because the bottom level of inductor current depend on the constant off-time or fixed frequency. Therefore, the accuracy of the LED lighting system is deteriorated. The value of the off-time needs to be adaptively adjusted to ensure the accurate inductor current that can be controlled between the peak and bottom current levels. As a result, the average inductor current can be independent of the variation of the input voltage and the numbers of LED in series. To adaptively adjust the value of the off-time [24], it is proposed that the SAR-controlled adaptive off-time calibrate the off-time value. That is, the duration of the off-time can be adjusted to regulate the bottom current level.

The flow chart of the SAR-controlled adaptive off-time technique is shown in Figure 18. The 8-bit SAR code A[7:0] is used to decide the duration of the off-time. At the beginning, the SAR code A[7:0] has an initial value of "1000,0000" and the gain code G[7:0] is set to "0100,0000". Adding or subtracting the gain code G[7:0] leads to the accurate calibration values of the SAR code A[7:0] in the following eight switching cycles. When the duration of the off-time is too short, the current sensing signal  $V_{sense}$  at the beginning of the next switching cycle is larger than the expected value of VREF2 as shown in Figure 19. Thus, the average inductor current is larger than expected value to have an influence on the brightness of the LED. At this time, the gain codes G[7:0] would be added to the SAR code A[7:0] to

prolong the off-time. On the other hand, if the off-time is too long, the current sensing signal, Vsense, at the beginning of the next switching cycle will be smaller than the  $V_{REF2}$ . That is, the lumen of LED is relatively small due to the smaller average inductor current, and therefore, the SAR code A[7:0] will subtract the gain code G[7:0].

Figure 18. The inductor current waveform at different the off-time values.

Figure 19. The inductor current waveform at different the off-time values.

After the eight switching cycles, the SAR code A[7:0] can be dynamically adjusted by a minimum value of the gain code G[7:0], which is "0000,0001" according to the value of the comparison result of the voltage  $V_{sense}$  and the reference voltage  $V_{REF2}$ . Consequently, after the calibration duration, the adaptive off-time can ensure that the bottom level of the inductor

current will be close to the expected value. That is, the average inductor current can be independent of the variation of the input voltage.

The external sensing resistor is not needed any more since the on-chip low-side current sensing circuit can detect the peak current level and the SAR code A[7:0] adaptively adjusts the off-time. Therefore, the efficiency can be improved owing to the removal of the conduction loss of the external sensing resistor. Simultaneously, the accuracy is also guaranteed because the adaptive off-time can ensure the average inductor is independent of the variation of the input voltage. In other words, the SAR-controlled adaptive off-time has the advantages of high efficiency like the PCC technique and high accuracy like the HCC technique.

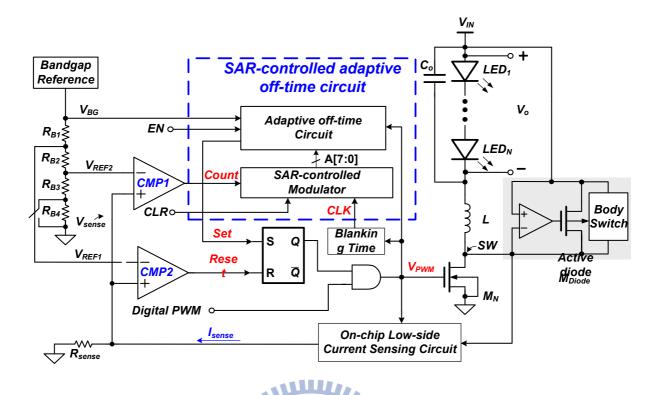

# 2.5 The Successive Approximation Register (SAR) Circuit Implementations

The implementation of the SAR-controlled adaptive off-time technique is illustrated in Figure 20. The external sensing resistor is replaced by the on-chip low-side current sensing circuit. As a result, the power dissipation of the on-chip low-side current sensing circuit is much smaller than that of the external sensing resistor. Furthermore, the freewheel-diode [25] is substituted by the active diode, which is the P-type power MOSFET  $M_{Diode}$ , in order to reduce the power dissipation during phase II. The digital signals EN and CLR are used to enable the LED driver and reset the initial digital code. The digital signal,  $Digital\ PWM$ , is the dimming signal for adjusting the brightness of the LED.

Figure 20. The proposed LED current driver uses the SAR-controlled adaptive off-time technique.

Two major circuits are used to enhance the accuracy of the LED driver. One is the SAR-controlled adaptive off-time control circuit and the other one is the on-chip low-side sensing circuit with the blanking time circuit. During phase I, the N-type power MOSFET is turned on to increase the inductor current. The current sensing circuit thus increases the sensing voltage  $V_{sense}$ . Once  $V_{sense}$  is larger than  $V_{REFI}$ , the output of the comparator 'CMP2' triggers the signal Reset to turn off the N-type power MOSFET  $M_N$ . The on-time duration  $t_{on}$  is decided. The peak level of inductor current can be expressed as:

$$I_{peak} = \frac{K \times V_{REF1}}{R_{sense}} \tag{15}$$

K refers to the sensing ratio. At this particular time, the active diode  $M_{Diode}$  will be turned on to discharge the inductor current. The forward voltage of the active diode is the source-drain voltage  $V_{SD}$  of P-type power MOSFET. The off-time duration  $t_{off}$  is controlled by the 8-bit

SAR code A[7:0] from the SAR-controlled modulator. After the off-time duration, the adaptive off-time module sends a signal *Set* to turn on the N-type power MOSFET to charge the inductor current again.

At the beginning, the SAR-controlled adaptive off-time technique calibrates the off-time duration depending on the output 'Count' of the comparator 'CMP1'. The signal 'Count' equaled to '1' or '0' means that the sensing current signal  $V_{sense}$  is higher or lower than the reference voltage  $V_{ref2}$ . After the calibration process, the bottom level of inductor current can be determined by the voltage  $V_{REF2}$ . Thus, the bottom level of the inductor current can be formulated as:

$$I_{bottom} = \frac{K \times V_{REF2}}{R_{sense}}$$

(16)

Therefore, the current ripple divided by the average current can be calculated as:

$$\frac{I_{ripple}}{I_{avg}} = \frac{2 \times (V_{REF1} - V_{REF2})}{(V_{REF1} + V_{REF2})}$$

(17)

As a result, the current ripple ratio can be maintained by the reference voltages  $V_{refl}$  and  $V_{ref2}$  and would not be influenced by the input voltage or the numbers of LED in series. Smaller current ripple has a more stable LED lumen. However, the ratio of the current ripple also defines the switching frequency as:

$$f_s = \frac{1}{L \times I_{ripple} \times (\frac{1}{V_o} + \frac{1}{V_{IN} - V_o})}$$

(18)

According to (18), a small inductor current ripple results in a faster switching frequency and increases power consumption. On the other hand, a high inductor current ripple results in

a slower switching frequency Therefore, power efficiency is increased because the switching loss is further reduced. However, the conduction power is increased due to large current ripple. Therefore, the inductor current ripple, which is about  $\pm 15\%$  of the average inductor current has a better power conversion efficiency as shown in Figure 21. The power efficiency would be reduced while the current ripple is smaller than  $\pm 15\%$ . Moreover, the current ripple can be increased to reduce the size of the inductor at the cost of reduced efficiency and, possibly, LED lifetime [26]. As a result, the suitable ratio of the inductor current ripple is  $\pm 15\%$ . This is popularly used in today's LED lighting products.

Figure 21. The relation of the ratio of inductor current ripple  $(I_{ripple} / I_{avg})$ , the power efficiency  $(\eta)$ , and the switching frequency  $(f_s)$ .

The LED driver needs to provide an accurate driving current for LED lighting systems. It should be noted that the SAR-controlled modulator can still dynamically adjust the off-time to rapidly react to the variations of the input voltage and the numbers of LED in series. In addition, the power dissipation during phases I and II can be reduced and expressed as (19) and (20), respectively.

$$E_{phI(SAR)} = I_{L(avg)}^{2} \times R_{on} \times t_{on}$$

(19)

$$E_{phII(SAR)} = I_{L(avg)} \times V_{SD} \times t_{off}$$

(20)

According to (15), the power dissipation in phase I is much less than those in (9) and (13). During phase II, the power dissipation can also be reduced through the use of small  $V_{DS}$  because of the active diode. Hence, the technique can minimize the conduction power loss and improve the accuracy of the driving current. The following subsections will describe the implementations of the sub-modules.

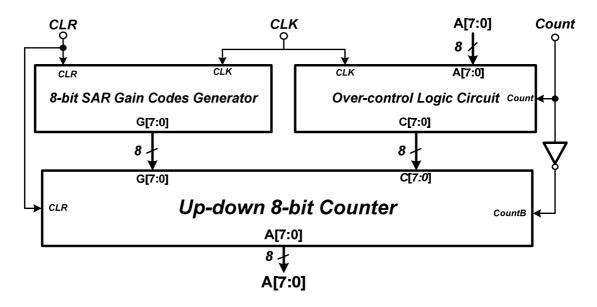

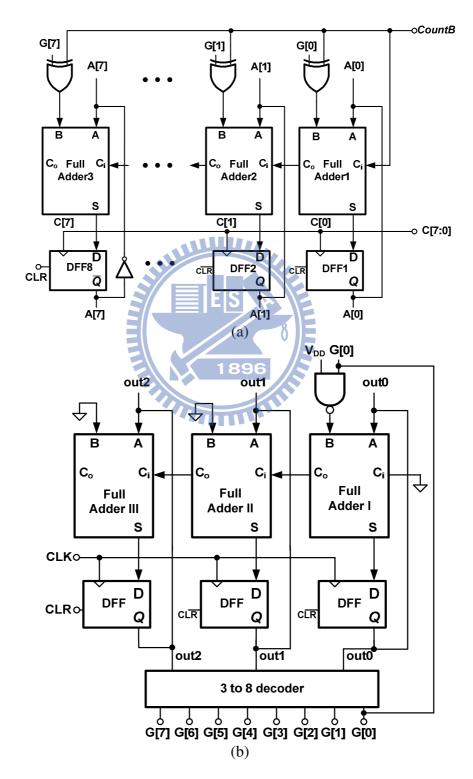

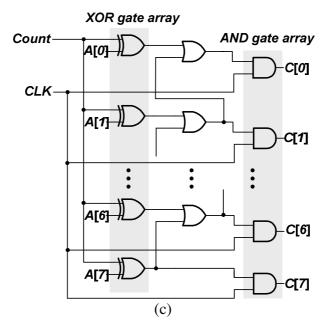

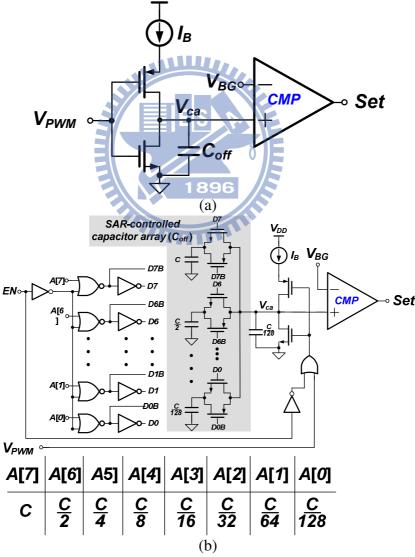

### 2.5.1 The Implementation of the SAR-Controlled Modulator

The implementation of the SAR-controlled modulator is composed of three sub-modules as shown in Figure 22. The three sub-modules are the up-down 8-bit counter, the 8-bit SAR gain code generator, and the over-control logic circuit. The up-down 8-bit counter is used to calculate a new 8-bit SAR code A[7:0] and a gain code G[7:0] according to the digital signal *Count*. The 8-bit SAR gain code generator provides G[7:0] to the up-down 8-bit counter to calculate the precise A[7:0]. The over-control logic circuit detects A[7:0] and generates C[7:0] to avoid the overflow issue.

Figure 22. The structure of the SAR-controlled modulator.

The circuit of the up-down 8-bit counter is the main module shown in Figure 23(a). Since A[7:0] starts from '10000000', the gate DFF8 utilizes the complement of the *Q* signal when the signal *CLR* is high. Therefore, A[7:0] starts from '10000000' after the clear state. The eight XOR gates and the signal *CountB* are used to decide if the operation is an addition or a subtraction. Additionally, *CountB* is also used as the carry-in signal of the first full-adder to achieve the correct calculation. When *CountB* is '1', G[7:0] will be converted into its 2's complement value. Hence, A[7:0] subtracts G[7:0] to prolong the off-time duration. On other hand, if *CountB* is '0', G[7:0] is not complemented. That is, the addition is proceeded by the SAR-controlled modulator and A[7:0] is equal to the sum of the previous value and G[7:0].

The 8-bit gain code generator is shown in Figure 23(b). G[7:0] starts from '01000000' to '00000001'. At the beginning, the binary code [out2, out1, out0] is set to '000' and converted by the 3-to-8 decoder so that G[7:0] can be set as '01000000.' Three full adders are used to generate the increasing binary code [out2, out1, out0] from '000' and G[7:0] is converted from '01000000' to '00000001' by the 3-to-8 decoder. Until G[0] is changed from '0' to '1', the input B of the full adder I becomes '0' and the binary code [out2, out1, out0] will be settled. This indicates the end point of the calibration of the SAR operation. Then, the SAR-controlled modulator starts to slightly adjust A[7:0] by setting the minimum G[7:0] as '00000001.'

The over-control logic circuit is depicted in Figure 23(c). The AND gate array is used to block the clock *CLK* when the overflow issue happens. When the value of the signal *CountB* is '1', the operation of the up-down 8-bit counter is the addition function. If A[7:0] is '111111111,' the output of the XOR gate array is '0' to block the clock signal *CLK*. Thus the over-control signal C[7:0] holds to '00000000.' For the subtraction function, the up-down 8-bit counter needs to prevent the value of the SAR code A[7:0] from continuously decreasing when A[7:0] is '00000000.' When the function of subtraction is enabled by the *CountB*, it

also prevents the overflow issue from happening through the XOR gate array. The SAR-controlled modulator with three sub-modules can generate A[7:0] through the digital signal *Count* to adjust the dynamic off-time. When *Count* is '0' or '1', the SAR code will subtract or add G[7:0] as '00000001.'

Figure 23. The three sub-modules in the implementation of the SAR-controlled modulator. (a) The up-down 8-bit counter. (b) The 8-bit SAR gain code generator. (c) The over-control logic circuit.

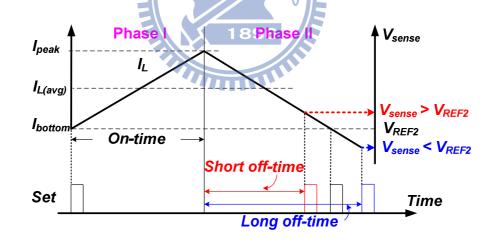

# 2.5.2 The Implementation of the Adaptive Off-time Circuit

The simple implementation of the constant off-time circuit is depicted in Figure 24(a). When the signal *control* is high, the non-inverting input of comparator  $V_{ca}$  is discharged to ground and the output of comparator Set is zero. When the signal *control* is changed to low, the constant biasing current  $I_B$  will flow into the capacitor  $C_{off}$  to increase  $V_{ca}$ . Once  $V_{ca}$  is larger than the voltage  $V_{BG}$ , the signal Set is changed to high to start the next switching cycle. Thus, the off-time duration can be expressed as (21).

$$t_{off} = \frac{C_{off} V_{BG}}{I_B} \tag{21}$$