## 國立交通大學

電機與控制工程學系

碩士論文

以90 奈米 CMOS 製程設計一應用於 前瞻串列式連結收發機 之超高速資料轉換器對

Design of a Very High Speed

Data Converter Pair in 90nm CMOS Process

for Advanced Serial Link Transceivers

研 究 生: 陳永順

指導教授:洪浩喬 教授

中華民國九十七年九月

#### 以90 奈米 CMOS 製程設計一應用於 前瞻串列式連結收發機之超高速資料轉換器對

## Design of a Very High Speed Data Converter Pair in 90nm CMOS Process for Advanced Serial Link Transceivers

研 究 生:陳永順 Student: Yung-Shun Chen

指導教授:洪浩喬 Advisor:Hao-Chiao Hong

國立交通大學 電機學院 電機與控制工程學系 碩士論文

#### A Thesis

Submitted to Department of Electrical and Control Engineering

College of Electrical Engineering

National Chiao Tung University

in partial Fulfillment of the Requirements

for the Degree of

Master

in

Electrical and Control Engineering

September 2008

Hsinchu, Taiwan, R.O.C

中華民國九十七年九月

## 以 90 奈米 CMOS 製程設計一應用於 前瞻串列式連結收發機之超高速資料轉換器對

研究生:陳永順 指導教授:洪浩喬 博士

國立交通大學 電機與控制工程學系碩士班

#### 摘 要

本論文提出一組以聯電 90nm CMOS Mixed-Mode 製程設計製作之應用 於前瞻串列式連結傳輸系統收發機之超高速資料轉換器對。該數位類比與類 比數位轉換器之規格皆為每秒一百億次取樣率、四位元解析度。數位類比轉 换器為電流導向的架構,且使用操作速度較快之電流式邏輯電路作為核心數 位電路的設計。此種電流式邏輯除了適用於低電壓的操作環境之外,也可達 到非常高速的切換能力並降低高速轉換中電源的抖動量。而其中較關鍵性的 元件-開關輸出電流源使用疊接電流源電路,以提供在高頻時較高的輸出阻 抗,使高頻操作的特性可以更好。另一方面,我們使用快閃式的架構來實現 超高速類比數位轉換器。透過串接多級具備主動式負回授技術的前置放大器 使比較器陣列具有超寬頻,與低功率的特點。而數位電路部份相同也採用電 流式邏輯電路作設計。為了解決高速資料轉換器測試上的困難,我們加入一 組可測試性電路並提供兩種測試模式,使實驗晶片可以進行全速運作下的動 態參數以及眼圖的量測。晶片量測結果顯示,在全速運作的測試模式下,輸 入一 1.111GHz 的弦波訊號,可得 27.0 dB 的訊號雜訊比以及 25.9 dB 的訊號 雜訊失真比,對應到四位元的有效位元數。眼圖量測結果顯示此設計能提供 達到每秒一百億位元的資料傳輸速率。在 1V 供應電源下,整個測試晶片共 消耗約 322.8 mW 之功率。

# Design of a Very High Speed Data Converter Pair in 90nm CMOS Process for Advanced Serial Link Transceivers

Student: Yung-Shun Chen Advisor: Dr. Hao-Chiao Hong

Department of Electrical and Control Engineering

National Chiao Tung University

#### **Abstract**

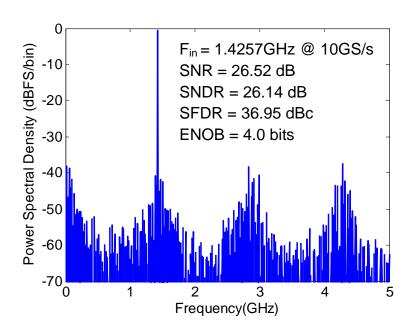

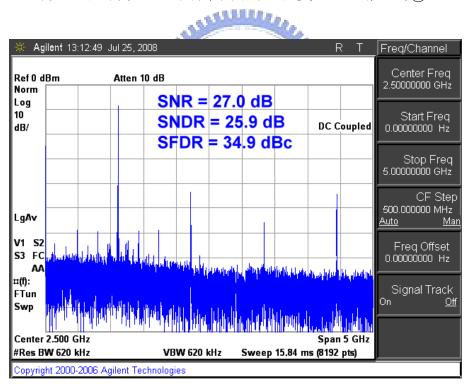

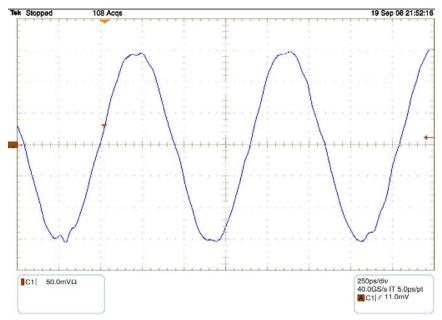

This thesis presents a very high speed data converter pair in UMC 90nm CMOS Mixed-Mode technology for the design of the transceivers of advanced serial links. The digital-to-analog (DAC) and the analog-to-digital (ADC) converters achieve a 10GS/s sampling rate and 4-bit resolution. The DAC uses the current-steering architecture. The digital circuitry is implemented with the current mode logic (CML) gates which have faster switching. The CML gates not only have less gate delays, but also are suitable for low voltage operation. In addition, they alleviate the issue of severe power-ground bouncing. We also applied the switched cascode current source (SCCS) to provide a higher output impedance at higher frequencies. The proposed ADC is a flash type ADC. The very wide bandwidth and low power comparators were realized by cascading multi-stage active negative feedback pre-amplifiers. To address the difficulty of testing the data converters at the rated 10GS/s. added design-for-testability (DfT) circuitry which provides two test modes including the at-speed test mode and the eye diagram mode. The measurement results of the test chip show that the data converter pair achieves an SNR of 27.0 dB and an SNDR of 25.9 dB with the 1.111GHz sinusoidal inputs in the at-speed test mode. It corresponds to an ENOB of 4.0 bits. The measured eye diagrams show that the

data converter pair can provide a data rate up to 10Gbps. The test chip including the DfT circuitry consumes 322.8 mW from a 1V supply.

#### 誌 謝

能夠順利完成碩士論文,我由衷地感謝我的指導教授 洪浩喬 博士。在這兩年多的研究生活中,老師所帶給我的不僅是研究課題上的訓練以及專業知識上的指導,更有意義的是從老師言行上可以學到的獨立思考、實事求是以及面對問題努力不懈的精神,這一切著實都讓我有切身的體悟並且受益良多。在人生的這一站,很慶幸也很榮幸能遇到洪老師,老師帶給我的影響,是十足深刻且深遠的。

感謝<u>蘇教授、李教授</u>以及<u>黃教授</u>百忙之中抽空擔任我的口試委員,同時指出 學生論文中的缺失,讓學生可以再多加思考,並使論文內容可以更趨完善。

感謝實驗室博士班的聖泉學長在研究上提供的一些寶貴意見與建議,同時也感謝諸多已畢業的學長:鼎鈞(Danny)、孟軒(Steven)、國銘(Kevin)、振綱(Vincent)以及榮洲(Allen)等等,謝謝你們,將寶貴的經驗與專業知識傳承於實驗室的學弟我們。尤其感謝提攜過我的振綱學長,因為你不厭其煩的對我要求,使我可以學得更多。而時常協助幫忙我的學弟韋傑(Jeff),更是要謝謝你,多虧你適時的幫助,讓我得以如期完成我的晶片。還要感謝實驗室的同窗:宗殷(Azure)與勇成(Cloud),因為你們的陪伴,讓碩一煩雜的修課作業與考試生活增添了許多樂趣。至於其他學弟:明達(Miller)與紹峰(Stanley),感謝你們在日常生活的互相協助與研究討論,讓實驗室有良好的研究氣氛與更多的歡笑聲。在 901 實驗室的八百多天個日子裡,能和你們在一起真的很開心。

另外,也感謝時常與我相互勉勵的舊識<u>志文</u>,特別是在趕論文的這段期間內 所给予我生活上的協助。

最後,也是最重要的,感謝我的最親愛的家人,我的父母及哥哥,感謝你們 無時無刻作為我最好的後盾並不斷的支持我,讓我可以無後顧之憂的完成學業。

謹以此論文獻給大家,感謝各位對我的幫助。

陳永順 謹識

中華民國九十七年九月

新竹を大

## 目錄

| 中文摘要                                              | I    |

|---------------------------------------------------|------|

| 英文摘要                                              | II   |

| 誌謝                                                | IV   |

| 目錄                                                | V    |

| 圖目錄                                               | VIII |

| 表目錄                                               | XII  |

| 第一章 緒論                                            | 1    |

| 1.1 研究背景                                          | 1    |

| 1.2 研究動機與目的                                       | 2    |

| 1.2 研究動機與目的                                       | 6    |

| S FIRST                                           |      |

| 第二章 資料轉換器對 ADC 與 DAC 之基本原理及架構                     | 7    |

| 8 5                                               |      |

| 2.1 資料轉換器(Data Converter)的基本操作原理                  |      |

| 2.1.1 類比數位轉換器 (Analog-to-Digital Converter, ADC)  |      |

| 2.1.2 數位類比轉換器 (Digital-to-Analog Converter, DAC)  |      |

| 2.2 資料轉換器的效能參數介紹[18][19][20][21][22]              |      |

| 2.2.1 静態參數 (Static Parameters)                    |      |

| 2.2.1.1 準確性 (Accuracy)                            |      |

| 2.2.1.2 解析度(Resolution)                           |      |

| 2.2.1.3 偏移誤差 (Offset Error)                       |      |

| 2.2.1.4 增益誤差(Gain Error)                          |      |

| 2.2.1.5 差分非線性誤差 (Differential Non-Linearity, DNL) |      |

| 2.2.1.6 累積非線性誤差(Integral Non-Linearity, INL)      |      |

| 2.2.1.7 缺碼及單調性 (Missing Code & Monotonicity)      |      |

| 2.2.2 動態參數 (Dynamic Parameters)                   |      |

| 2.2.2.1 量化雜訊 (Quantization Noise)                 |      |

| 2.2.2.2 訊號對雜訊比 (Signal-to-Noise Ratio, SNR)       | 21   |

| 2.2.2.3 訊號對雜訊失真比                                  |      |

| (Signal-to-Noise and Distortion Ratio, SNDR)      | 23   |

| 2.2.2.4 有效位元數 (Effective Number Of Bits, ENOB)    | 23   |

| 2.2.2.5 總諧波失真(Total Harmonic Distortion, THD)     | 24   |

| 2.2.2.6 無假訊號動態範圍                                  |      |

| (Spurious-Free Dynamic Range, SFDR)       | 24 |

|-------------------------------------------|----|

| 2.2.2.7 有效解析度頻寬                           |    |

| (Effective Resolution Bamdwidth, ERBW)    | 25 |

| 2.2.2.8 動態範圍 (Dynamic Range, DR)          | 26 |

| 2.3 ADC 及 DAC 各種架構簡介                      | 27 |

| 2.3.1 ADC 之各種架構                           | 27 |

| 2.3.2 DAC 之各種架構                           | 30 |

| 第三章 應用於前瞻串列式連結之超高速資料轉換器對之設計.              | 33 |

| 3.1 10GS/s 4-bit 數位類比轉換器 (DAC) 之設計        | 33 |

| 3.1.1 電流式邏輯 (Current Mode Logic, CML) 電路  | 35 |

| 3.1.2 數位電路之設計                             | 38 |

| 3.1.3 輸出電流源之設計                            | 39 |

| 3.2 10GS/s 4-bit 類比數位轉換器 (ADC) 之設計        | 44 |

| 3.2.1 分壓電阻串 (Resistor Ladder)             | 45 |

| 3.2.2 比較器電路之設計                            | 47 |

| 3.2.2.1 多級串接放大器的設計考量                      | 47 |

| 3.2.2.2 Gilbert-Cell                      | 53 |

| 3.2.2.1 多級串接放大器的設計考量                      |    |

| ( Active negative reedback Pre-Amplifier) | רר |

| 3.2.2.4 完整比較器電路之設計                        | 60 |

| 3.2.2.5 多級串接放大器 Slew-rate 之設計考量           |    |

| 3.2.3 泡沫錯誤更正電路 (Bubble Errors Correction) | 64 |

| 3.2.4 編碼電路之設計                             | 67 |

| 第四章 電路模擬結果                                | 71 |

| 4.1 10GS/s 4-bit DAC 之模擬結果                | 71 |

| 4.1.1 DAC 静態參數 (Static Parameters) 之模擬    | 71 |

| 4.1.2 DAC 動態參數 (Dynamic Parameters) 之模擬   | 72 |

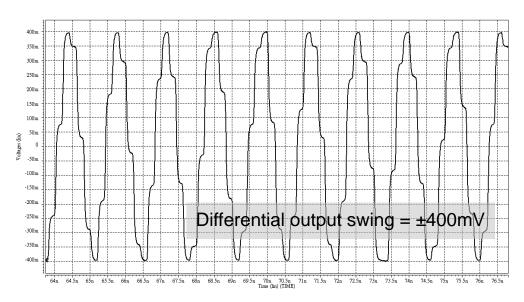

| 4.1.3 DAC 眼圖 (Eye Diagram) 之模擬            | 75 |

| 4.1.4 DAC 功率消耗之模擬                         | 76 |

| 4.2 10GS/s 4-bit ADC 之模擬結果                | 76 |

| 4.2.1 ADC 静態參數 (Static Parameters) 之模擬    | 76 |

| 4.2.2 ADC 動態參數 (Dynamic Parameters) 之模擬   | 78 |

| 4.2.3 ADC 功率消耗之模擬                         | 79 |

| 第五章 晶片可測試性設計、模擬與佈局                        | 81 |

| 5.1 可測試性設計 (Design-for-Testability, DfT)  | 81 |

| 5.1.1 测计档子 A (The Test Mode A)            |    |

| 5.1.2 測試模式 B (The Test Mode B)                      | 84  |

|-----------------------------------------------------|-----|

| 5.1.3 DfT 測試方式之驗證 (Verification of the DfT concept) | 85  |

| 5.2 各種測試模式下之模擬結果                                    |     |

| 5.2.1 測試模式 A (Test Mode A) 之模擬結果                    |     |

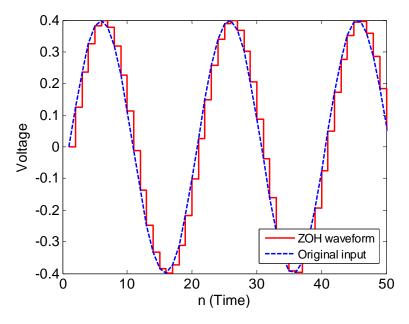

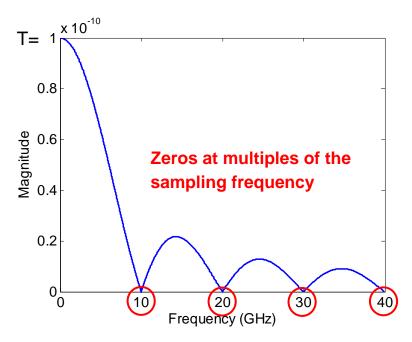

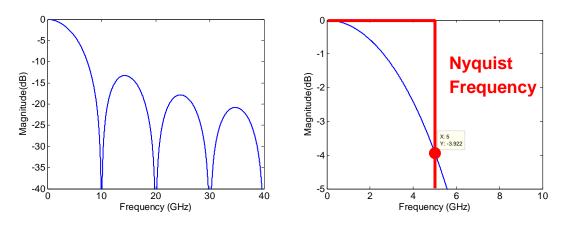

| 5.2.2 DAC 之 Zero-Order Hold (ZOH) 效應[50][51]        |     |

| 5.2.3 測試模式 B (Test Mode B) 之模擬結果                    |     |

| 5.2.4 測試晶片功率消耗之模擬                                   | 97  |

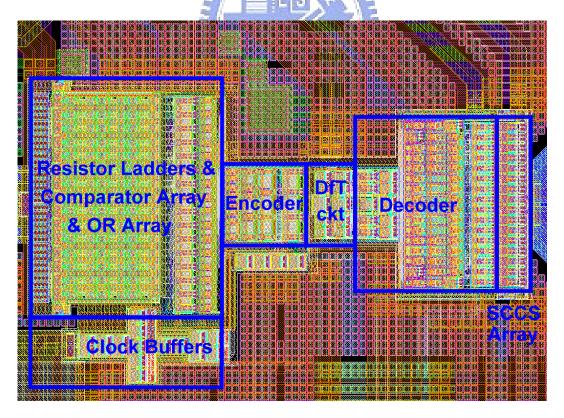

| 5.3 測試晶片之佈局 (Layout)                                | 98  |

|                                                     |     |

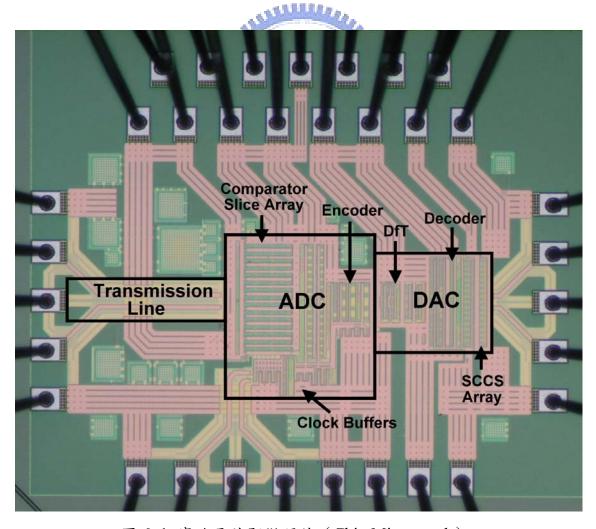

| 第六章 實驗晶片量測結果                                        | 101 |

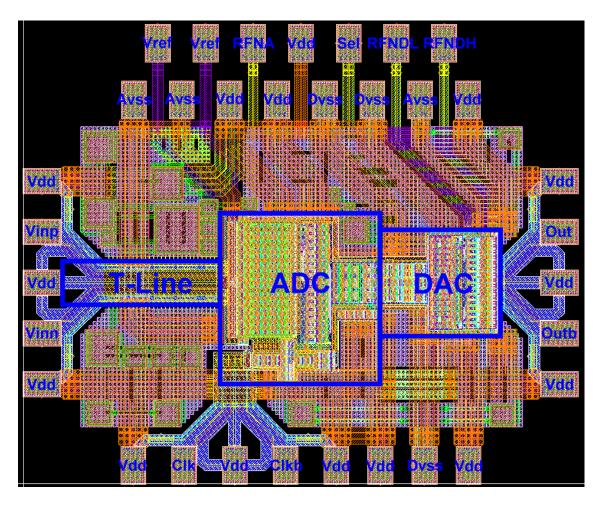

| 6.1 實體晶片顯微照 (Chip Micrograph)                       | 101 |

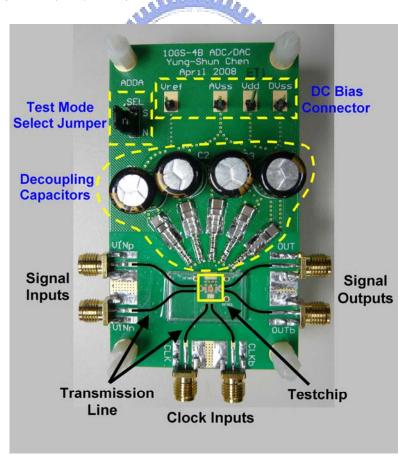

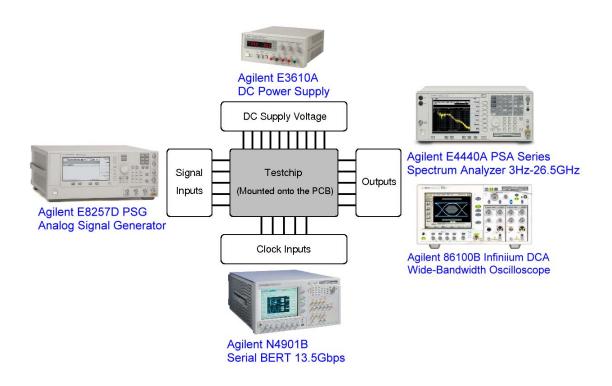

| 6.2 晶片實驗測試板及測量環境設定                                  | 102 |

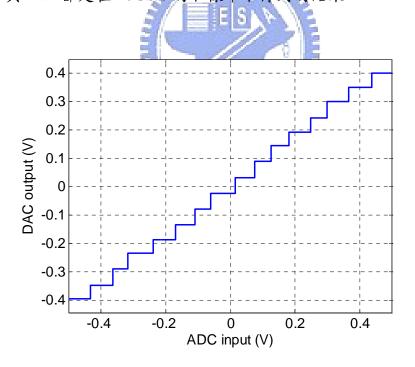

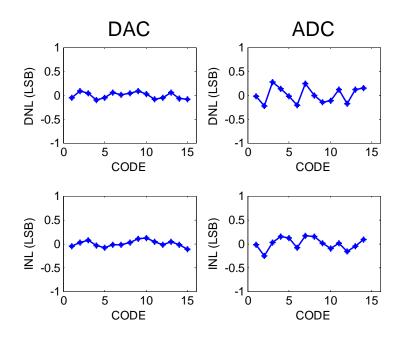

| 6.3 靜態參數 (Static Parameters) 量測結果                   | 104 |

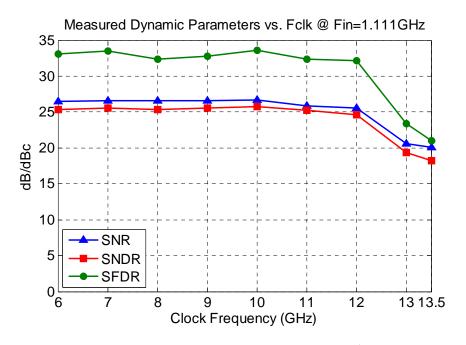

| 6.4 動態參數 (Dynamic Parameters) 量測結果                  | 105 |

| 6.4.1 取樣時脈訊號頻率對各種動態參數                               |     |

| (Clock Frequency vs. Dynamic Parameters)            | 105 |

| 6.4.2 輸入訊號頻率對各種動態參數                                 |     |

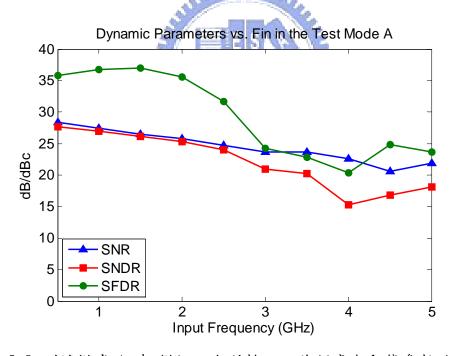

| (Input Frequency vs. Dynamic Parameters)            | 106 |

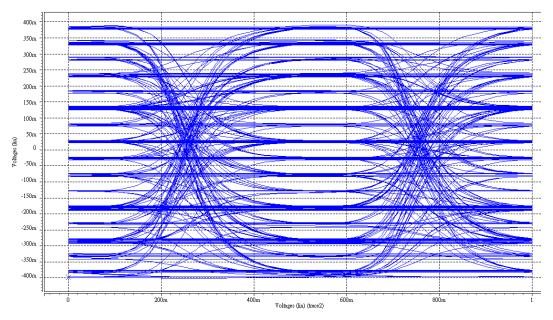

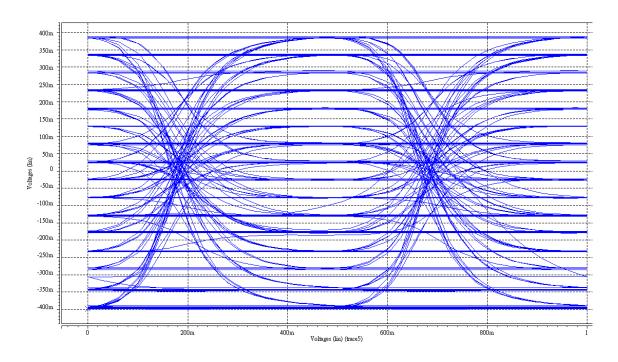

| 0.3 眼 阃(Eve Diagram)之 軍 澳                           | 114 |

| 6.6 功率消耗                                            | 117 |

| 6.7 量測結果總結與比較                                       |     |

| 1896                                                |     |

| 第七章 結論與未來展望                                         | 121 |

| William Control                                     |     |

| <b>全共</b> 计配                                        | 124 |

## 圖目錄

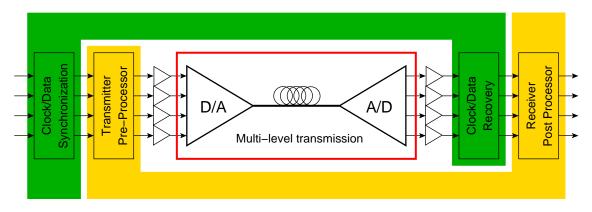

| 圖 1.1 串列連結 (Serial Link) 傳輸系統示意方塊圖                                       | 4  |

|--------------------------------------------------------------------------|----|

| 圖 2.1 類比訊號與數位訊號介面示意圖[17]                                                 | 8  |

| 圖 2.2 理想之三位元 ADC 輸入輸出轉換特性曲線                                              |    |

| 圖 2.3 理想之三位元 DAC 輸入輸出轉換特性曲線                                              |    |

| 圖 2.4 ADC 與 DAC 之偏移誤差 (Offset Error) 示意圖                                 | 13 |

| 圖 2.5 增益誤差 (Gain Error) 示意圖                                              | 14 |

| 圖 2.6 ADC 與 DAC 之差分非線性誤差 (DNL) 示意圖                                       |    |

| 圖 2.7 ADC 與 DAC 之累積非線性誤差 (INL) 示意圖                                       | 16 |

| 圖 2.8 ADC/DAC 缺碼 (Missing code) 與單調性 (Montonicity) 示意圖                   | 18 |

| 圖 2.9 ADC 之量化雜訊 (Quantization Noise)                                     | 20 |

| 圖 2.10 鋸齒波 (sawtooth) 訊號                                                 | 21 |

| 圖 2.11 非理想之 6 位元 ADC 輸出訊號頻譜                                              | 22 |

| 圖 2.12 動態範圍 (DR) 示意圖                                                     | 26 |

| 圖 2.13 各種常見 ADC 的架構與取樣速度之關係                                              | 28 |

| 圖 2.14 基本 Flash ADC 之架構                                                  | 29 |

| 圖 2.15 溫度計碼式 Current-Steering (Unary Current-Steering) 示意圖               | 32 |

| 圖 3.1 超高速 10GS/s 4-bit 數位類比轉換器 (DAC) 之方塊圖                                | 34 |

| 圖 3.2 基本電流式邏輯 (Current Mode Logic, CML) 電路之結構                            | 36 |

| 圖 3.3 各種常見之 CML 電路                                                       | 37 |

| 圖 3.4 電源擾動 (power/ground bounce) 經由寄生電感對電路產生之影                           | 響  |

| 同25(-) 如然四与阳田南子证的扶小四上(-) 扶小四上与远南鄉庙                                       |    |

| 圖3.5(a)一般簡單之開關電流源與輸出阻抗(b)輸出阻抗之頻率響應                                       |    |

| 圖 3.6 開關疊接電流源(Switched Cascode Current Source, SCCS)電路 图 2.7 問 問 品 拉 雷 茨 |    |

| 圖 3.7 開關疊接電流源輸出阻抗之頻率響應                                                   |    |

| 圖 3.8 開關疊接電流源電路陣列(SCCS Array)                                            |    |

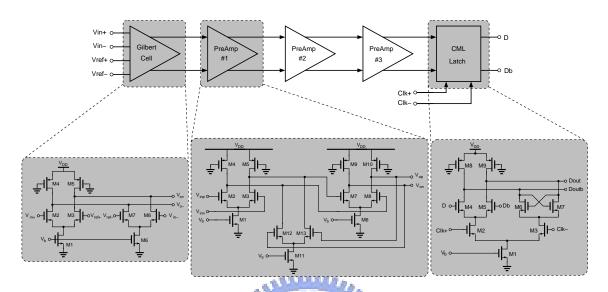

| 圖 3.9 超高速 10GS/s 4-bit 類比數位轉換器 (ADC) 之方塊圖                                |    |

| 圖 3.10 變動的輸入訊號經差動對之寄生電容耦合(couple)至分壓電腦                                   |    |

| 圖 3.11 模擬之 GBW <sub>S</sub> 與 Power 對 N 的關係圖 (對 N = 2 做正規化)              |    |

| 圖 3. $12 \text{ N} = 4$ 時對應至所需之 $GBW_S$ 約為 $17\text{GHz}$                |    |

| 圖 3. 13 輸入級比較器電路 (Gilbert-Cell) [40][41][42]                             |    |

| 圖 3. 14 主動式負回授 (Active negative feedback) 之前置放大器[34]                     |    |

| 圖 3. 14 主動式負回投 (Active negative rectibates) 之前 直放入器[54]                  |    |

| ■ 3.15 <b>工</b> 到 式 員 口 役                                                |    |

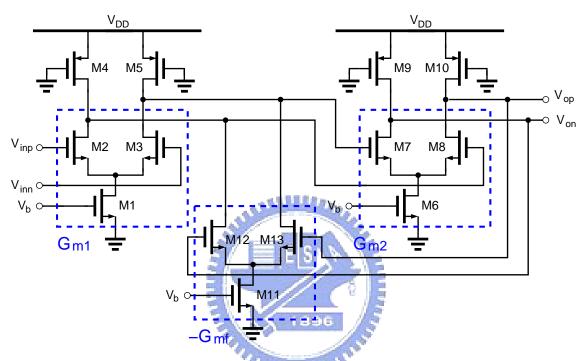

| 圖 3.17 包含多級串接放大器之完整比較器電路(Comparator slice)                               |    |

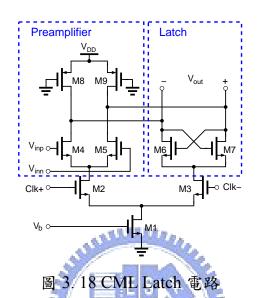

| 圖 3. 17 と古夕級中接放八韶之兄正に牧韶 电路(Comparator since)<br>圖 3. 18 CML Latch 電路     |    |

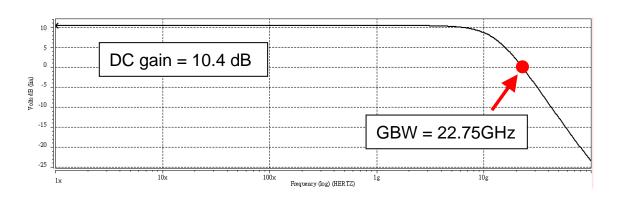

| 圖 3. 19 主動式負回授前置放大器(Active negative feedback Pre-Amplifi                 |    |

|    | 模擬之頻率響應圖                                                            | .63             |

|----|---------------------------------------------------------------------|-----------------|

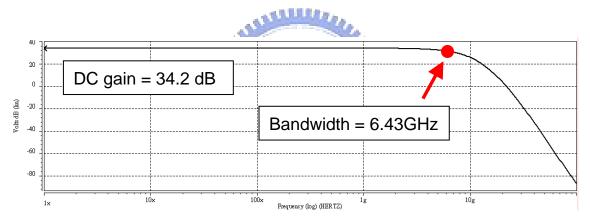

| 啚  | 3.20 完整比較器電路 (Comparator slice) 之頻率響應模擬結果                           |                 |

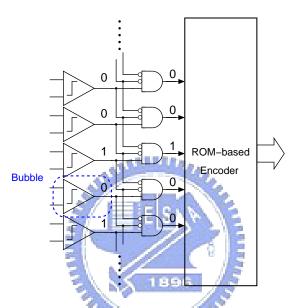

|    | 3.21 泡沫錯誤示意圖以及 ROM 編碼形式消除泡沫錯誤的邏輯電路                                  |                 |

| 啚  | 3. 22 因 offset 和 timing mismatch 發生的泡沫錯誤 (Bubble error) [49]        |                 |

|    |                                                                     | .66             |

| 啚  | 3. 23 使用 CML OR Array 消除可能發生的一階泡沫錯誤                                 | .67             |

| 啚  | 3. 24 Metastability 的問題發生於 4 位元溫度計碼轉二進碼編碼器之例-                       | 子               |

|    |                                                                     | .68             |

| 昌  | 3. 25 Metastability 的問題發生於 4 位元溫度計碼轉格雷碼編碼器之例-                       | 子               |

|    |                                                                     | .69             |

| 啚  | 3.264位元溫度計碼轉格雷碼(Thermometer-to-Gray)之編碼電路                           | .70             |

| _  |                                                                     |                 |

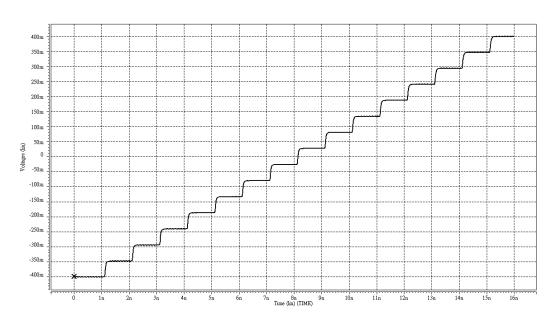

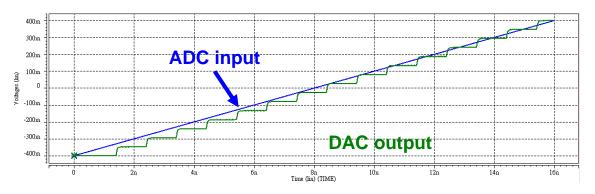

| 邑  | 4.1 取樣率為 10GS/s 時 DAC 輸入 Gray code 形式之漸增 ramp 訊號 >                  |                 |

| _  | 擬之差動輸出波形                                                            |                 |

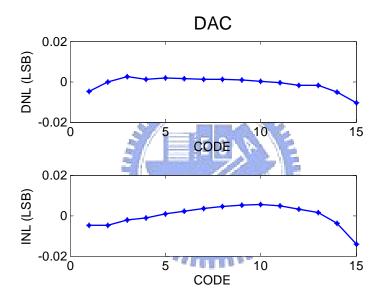

|    | 4.2 DAC 模擬之 DNL 與 INL (取樣率為 10GS/s)                                 |                 |

| 啚  | 4.3 取樣率為 10GS/s 時 輸入數位約 1.47GHz 之 sinusoidal 訊號 模擬                  |                 |

| _  | DAC 差動輸出時域波形                                                        | .73             |

| 昌  | 4.4 取樣率為 10GS/s 時 輸入 1.4257GHz 之 sinusoidal 訊號 模擬之 D.               |                 |

|    | 輸出訊號的頻譜                                                             |                 |

| 啚  | 4.5 取樣率為 10GS/s 時 DAC 模擬之各種輸入頻率與動態參數的關係                             |                 |

| _  |                                                                     | .74             |

| 邑  | 4.6 取樣率為 10GS/s 時 DAC 模擬之各種輸入頻率與 輸出訊號功率                             |                 |

| _  | (Signal-tone) 之關係 (in dBFS)                                         |                 |

|    | 4.7 取樣率為 10GS/s 時 DAC 模擬之眼圖 (Eye Diagram)                           |                 |

| 邑  | 4.8 取樣率為 10GS/s 時 ADC 輸入 25V/μs 的 ramp 訊號 模擬之 4 位 2                 |                 |

|    | y   M H                                                             | .77             |

|    | 4.9 ADC 模擬之 DNL 與 INL (取樣率為 10GS/s)                                 |                 |

| 啚  | 4. 10 輸入 1.4257GHz 之 sinusoidal 訊號且取樣率 10GS/s 時 模擬之 Al              |                 |

|    | 輸出訊號的頻譜                                                             |                 |

| 啚  | 4.11 取樣率為 10GS/s 時 ADC 模擬之各種輸入頻率與動態參數的關係                            |                 |

|    |                                                                     | .79             |

| 回  | 5 1 可测计从机计 (Dagian for Togtobility DfT) 为原购                         | 01              |

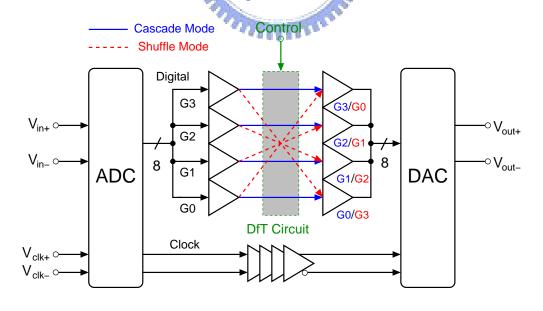

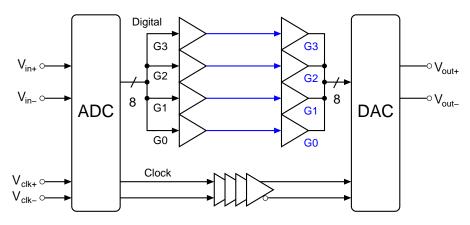

|    | 5.1 可測試性設計 (Design-for-Testability, DfT) 之電路                        |                 |

|    | 5.2 測試模式 A—Cascade Mode                                             |                 |

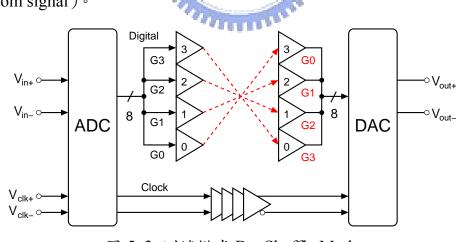

|    | • • • • •                                                           |                 |

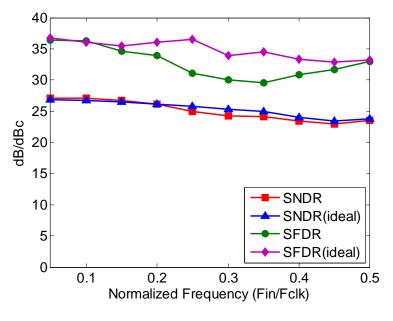

|    | 5.4 理想與實際設計之 4bits DAC 動態參數對輸入訊號頻率之模擬                               |                 |

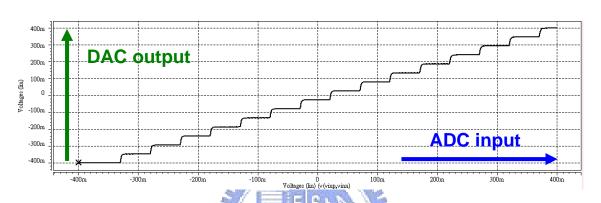

|    | 5.5 測試模式 A 中模擬之 ADC-DAC 輸入輸出轉換特性曲線                                  |                 |

| 回  | 5.6 輸入 1.4257GHz 之 sinusoidal 訊號且取樣率 10GS/s 時 測試模式 A                |                 |

| ভা | 模擬之輸出波形                                                             |                 |

| 回  | 5.7 輸入1.4257GHz之sinusoidal 訊號且取樣率10GS/s 時 測試模式 A                    |                 |

| ভা | 模擬所得之輸出訊號頻譜                                                         |                 |

| 回  | ) O 观点, 似果 T A B T 化异族 ( ) 全理 T T A T T T T T T T T T T T T T T T T | $\Delta \Delta$ |

| 昌 | 5.9 Zero-Order Hold (ZOH) 之訊號波形例子                       | .90       |

|---|---------------------------------------------------------|-----------|

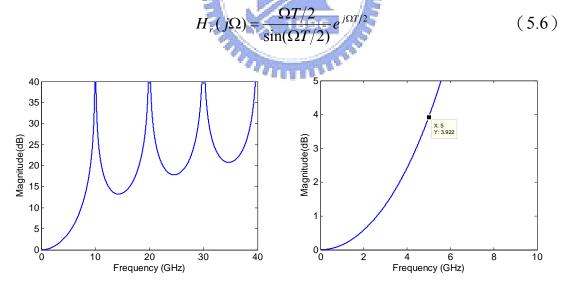

| 圖 | 5.10 取樣率為 10GS/s 之 ZOH 頻率響應 (振幅響應) 圖                    | .91       |

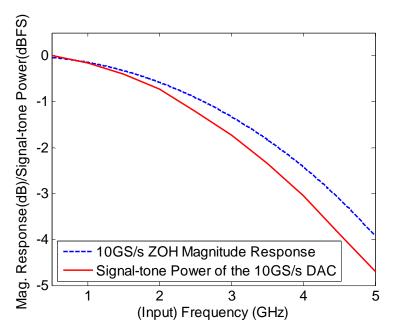

| 啚 | 5. 11 (a)10GS/s DAC 頻率響應之振幅響應圖(in dB) (b) Zoomed in 10G | Hz<br>.92 |

| 圖 | 5. 12 10GS/s DAC 之 Signal-tone Power 與 ZOH 振幅響應之頻率響應比   |           |

| 圖 | 5. 13 (a) 10GS/s 之 Anti-SINC 頻率響應之振幅響應圖 (b) Zoomed in   | .93       |

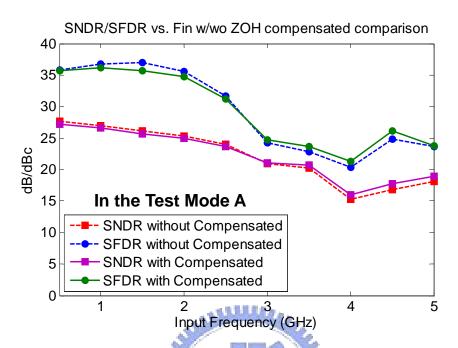

| 邑 | 5.14 測試模式 A 時 輸入訊號頻率對 SNDR/SFDR ZOH 效應補償前後              |           |

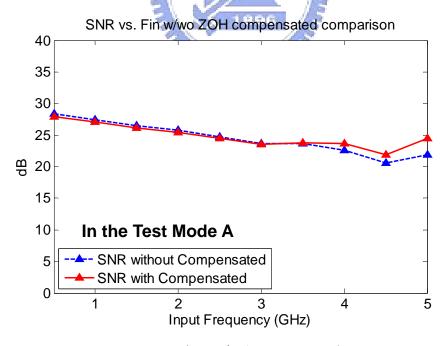

| 圖 | 5.15 測試模式 A 時 輸入訊號頻率對 SNR ZOH 效應補償前後之比較.                |           |

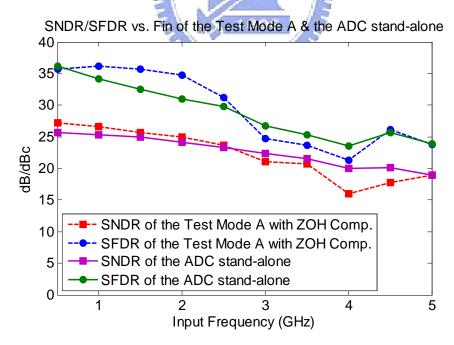

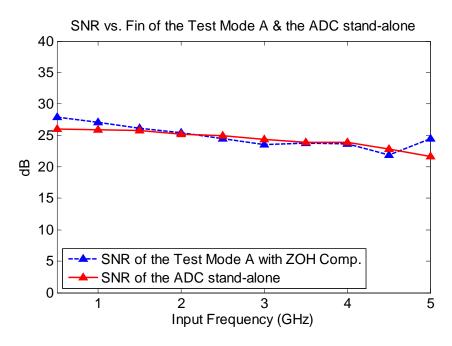

| 邑 | 5.16 測試模式 A 經 ZOH 效應補償後與單獨 ADC 之 SNDR/SFDR 對            |           |

| 圖 | 5.17 測試模式 A 經 ZOH 效應補償後與單獨 ADC 之 SNR 對輸入訊號率關係之比較        | 類<br>.96  |

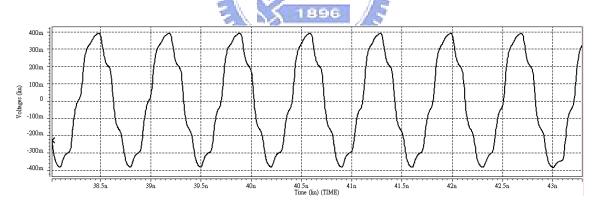

| 置 | 5. 18 測試模式 B 中 取樣率 10GS/s 時 輸出眼圖 (Eye Diagram) 之模       |           |

| 圖 | 5. 19 測試晶片 (test chip) 之佈局圖 (Layout)                    |           |

|   | 5. 20 ADC 與 DAC 核心之佈局                                   | .99       |

| 啚 | 5. 21 三明治 (sandwich) 電容之結構                              | 00        |

| 置 | 7                                                       | 01        |

| 昌 | 6.2 晶片實驗測試板                                             | 02        |

| 置 | 6.3 晶片測試環境設定(Measurement Setup)1                        | 03        |

| 邑 | 6.4 測試模式 A 中量測之輸入輸出轉換特性曲線1                              | 04        |

| 置 | 6.5 測量之 DAC 與 ADC 之 DNL&INL1                            | 05        |

| 置 | 6.6 測量之不同取樣訊號頻率與各動態參數的關係1                               | 06        |

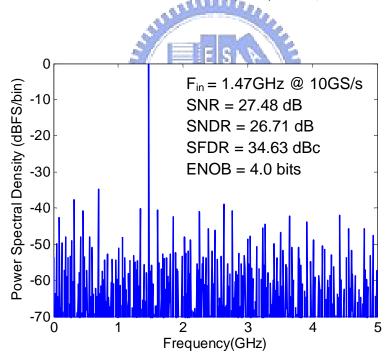

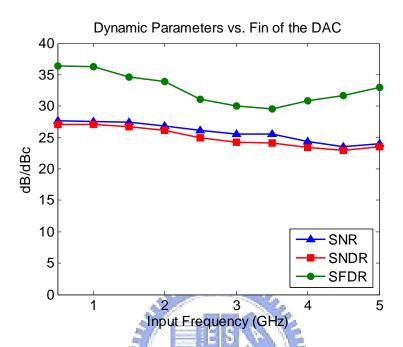

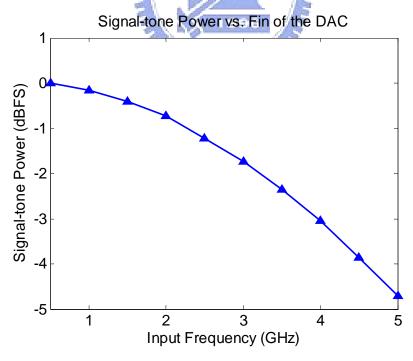

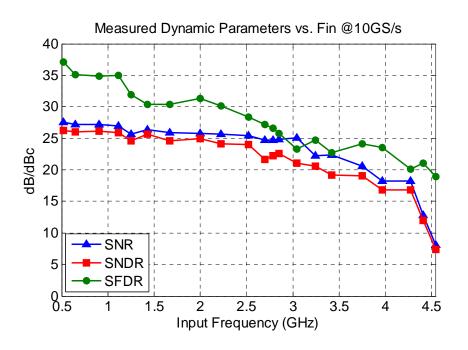

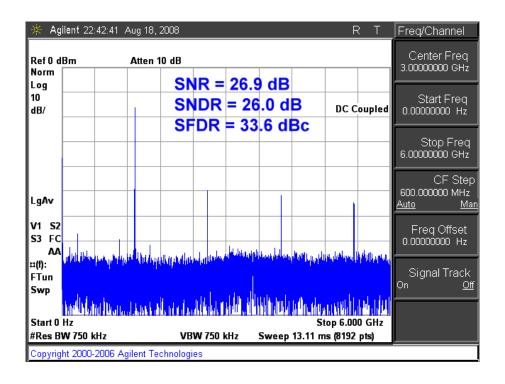

| 邑 | 6.7 測量之不同輸入訊號頻率與各種動態參數之關係 (@ 10GS/s)1                   | 07        |

| 昌 | 6.8 輸入 1.111GHz 之 sinusodial 訊號且取樣率為 10GS/s 時 測得之頻言     |           |

| 啚 | 6.9 輸入 1.111GHz 之 sinusodial 訊號且取樣率為 10GS/s 時 測得之波形     |           |

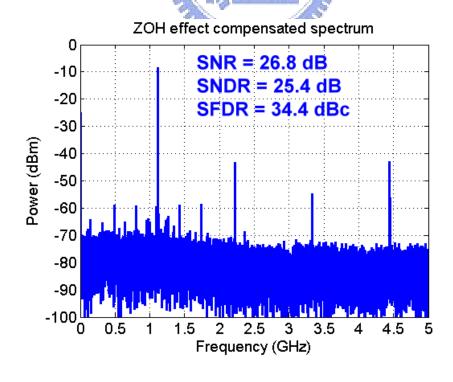

| 置 | 6.10 將圖 6.8 之頻譜結果作 ZOH 效應補償後所得之頻譜1                      |           |

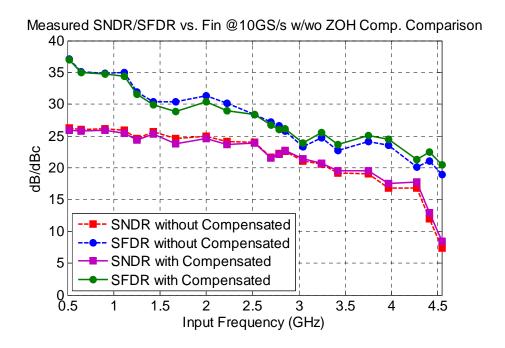

| 邑 | 6.11 測量之不同輸入訊號頻率對 SNDR/SFDR 參數 ZOH 效應補償前之比較 (@ 10GS/s)  |           |

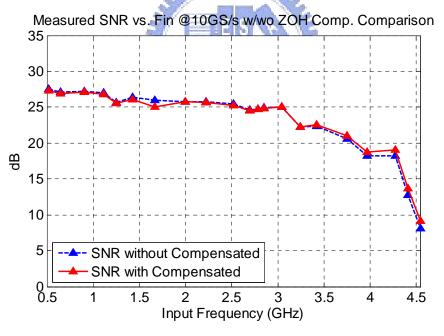

| 邑 | 6.12 測量之不同輸入訊號頻率對 SNR 參數 ZOH 效應補償前後之比較<br>(@ 10GS/s)    | 交         |

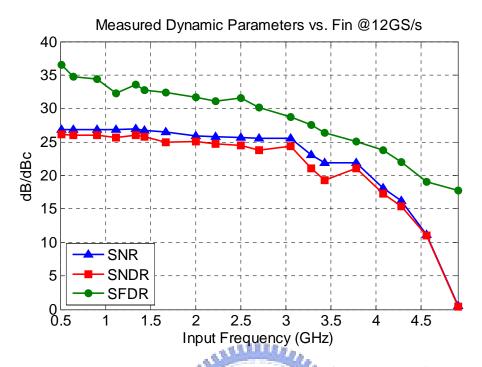

| 置 | 6.13 測量之不同輸入訊號頻率與各種動態參數之關係(@12GS/s)1                    |           |

| 圖 | 6. 14 輸入 1.33GHz 之 sinusodial 訊號且取樣率為 12GS/s 時 測得之頻     |           |

| 圖 6.15 測量之不同輸入訊號頻率對 SNDR/SFDR 參數 ZOH 效應補償前後                         |

|---------------------------------------------------------------------|

| 之比較 (@ 12GS/s)                                                      |

| 圖 6.16 測量之不同輸入訊號頻率對 SNR 參數 ZOH 效應補償前後之比較                            |

| (@ 12GS/s)                                                          |

| 圖 6.17 1GHz(1Gbps)之 clock rate 下測得之 Eye Diagram(Data rate = 4Gbps)  |

|                                                                     |

| 圖 6. 18 1.25GHz (1.25Gbps) 之 clock rate 下測得之 Eye Diagram (Data rate |

| =5Gbps )                                                            |

| 圖 6. 19 2GHz(2Gbps)之 clock rate 下測得之 Eye Diagram(Data rate =8Gbps)  |

| 116                                                                 |

| 圖 6. 20 2.5GHz(2.5Gbps)之 clock rate 下測得之 Eye Diagram (Data rate     |

| =10 <i>Gbps</i> )                                                   |

### 表目錄

| 表 1. 1 ADC 與 DAC 之規格            | 5   |

|---------------------------------|-----|

| 表 2.1 依解析度與取樣率區分 ADC 之種類[18]    | 28  |

| 表 2.2 以調變形式區分 DAC 之種類           | 30  |

| 表 3.1 一階及二階電路轉移函數之比較            | 48  |

| 表 4.1 DAC 數位及類比部份電路模擬之各別功率消耗比較表 | 76  |

| 表 4.2 ADC 類比及數位部份電路模擬之各別功率消耗比較表 | 80  |

| 表 5.1 模擬之各部份電路功率消耗表             | 97  |

| 表 6.1 測試晶片之功率消耗比較表              | 117 |

| 表 6. 2 Performance Summary      | 118 |

| 表 6. 3 Benchmark of the DAC     | 119 |

| 表 6. 4 Benchmark of the ADC     |     |

| ESIA                            |     |

#### 緒論

#### 1.1 研究背景

高速介面電路在現今被廣泛的應用在各種通訊傳輸系統中,尤其在現 今電腦系統的高度普及和運算處理速度已到了每秒數十億(GHz)的情況 下,伴隨而來的是資料傳輸量的大幅增加,面對此一趨勢,提升資料傳輸 率 (data rate)的需求顯得更為迫切。在高速有線通訊 (Wireline communication) 傳輸系統中,以往盛行的並列式匯流排(Parallel Bus)已 逐漸被串列式匯流排(Serial Bus)所取代,透過各種通訊調變的機制應用 實現在串列連結 (Serial Link) 傳輸的系統上,可達到甚至超越原本並列傳 輸系統提供的最大資料傳輸率,此外串列式傳輸可降低硬體設計及繞線的 複雜度,且增進系統的功率消耗效率,使每一瓦特(Watts)的功率能提供 更高的資料傳輸量 [1]。最為人熟知的例子就是目前個人電腦(PC)中所 具備大量的通用序列匯流排(USB; Univeral Serial BUS)[2]連接埠,從一 開始 USB 1.1 的 12Mbps 到現在 USB 2.0 所規範的 480Mbps, 演變之間傳輸 速度足足成長了有 40 倍之多,未來 USB 3.0 預計將可達到 4.8Gbps (600MB/s)的驚人傳輸速率。另外幾個顯著的例子是個人電腦中儲存系統 裝置介面的 Serial-ATA[3]以及使用低壓差動訊號 (LVDS; Low Voltage Differential Singaling)的匯流排介面的 PCI-Express[4]標準,兩者也都是透 過串列方式以點對點 (Point-to-Point) 的形式來進行訊號的傳輸,避免頻寬 共享而造成的傳輸資料率降低。

在未來運算平台的系統中可以預見的是晶片與晶片之間的通訊連線架構都不斷的要求介面電路可以提供更快的傳輸率,解決系統傳輸鏈結層的瓶頸,以因應高度整合下系統晶片(SoC;System on Chip)時代的來臨。因此高速的 I/O 單元等介面電路便成為其中的關鍵。

#### 1.2 研究動機與目的

數位通訊系統中串列傳輸的機制裡,若不將訊號經過特別處理,就是將訊號以位元流 (bit stream)的方式直接傳輸,即只傳送兩種邏輯準位的訊號,邏輯 "0"或邏輯 "1",當資料量日趨龐大時,就必須靠提升傳輸率來縮短傳輸時間,然而當系統的傳輸率一再的被增加之後,最後必然會面對到收發端電路以及傳輸線的頻寬所限制,造成資料傳輸率無法被提升,使得此種位元流的傳輸方式顯得不夠具備效益。因此為了有效提升資料傳輸率,許多種傳輸調變機制便被提出,其中在串列連結傳輸中,multi-level-per-symbol的多位準資料傳輸方式如 non-binary Pulse Amplitude Modulation (PAM) [5]或 Quadrature Amplitude Modulation (QAM)等已被大量應用,成為串列連結通訊系統中相當常見的技術。

在通訊中,最基本的符號(symbol)單位為位元(bit, binary digit),一個系統的訊息容量單位為每秒位元(bps, bits per second),而另一個用來度量訊息容量的單位是每秒符號(Baud rate, symbols per second)。使用 PAM 調變的系統中,將多個位元(multiple bits)表示成一個符號(symbol),因此若有 N 個位元,則表示出來的符號就有  $2^N$  個可能的狀態(State, S),故Baud rate 可計算得  $\log_2(S) = \log_2(2^N) = N$  (symbols per second),因此假設傳輸一個 symbol 的時間與原先傳送一個 bit 的時間 (bit time )相同的情況下,則經由 PAM 等 multi-level 調變機制後的位元率(bit rate, bps)將會變為原

本的log<sub>2</sub>(S)倍。以N=2為例,調變後便可得到4個可能的電壓位準狀態的類比輸出訊號(Buad rate = 2),且由低到高,每個電壓位準所對應代表的數位訊號分別為00、01、10及11,而相同假設傳輸一個 symbol 的時間與原先傳送一個 bit 的時間 (bit time)相同的情況下,接收端在相同時間內所得到的位元率變為原先的2倍,也就是只花費一個位元的時間而可以接收到兩位元的資料,相較於原本的單純只傳0"或"1"的位元流系統下,變成接收到一個位元資料所需的時間變為原先的一半,意即資料傳輸率變為原先的兩倍。同理如果Buad rate = 4,則相同時間區間內可以接收到的資料量就為原先的四倍。這主要是由於在相同的時間區間內類比訊號可表示的電壓準位要比數位訊號的兩個位準來得多,因此在相同的傳輸時間下,一條透過PAM 調變傳輸機制的傳輸線系統提供的最大傳輸資料量將為原先的N倍。

要實現此種具備 multi-level signaling modulation 如 PAM 的資料傳輸方式,常見的方法是在傳送端設計一組數位類比轉換器 (Digital-to-Analog Converter, DAC),使得經過串列至並列轉換 (serial to parallel conversion)機制的電路後將原本連續的位元流資料轉換成每 N 個位元為一組的並列訊號輸入到解析度為 N-bit 的 DAC 當中,進行多位準類比輸出訊號的調變轉換,便可經由傳輸線作串列式傳輸;而接收端為了將這些多位準的類比訊號正確解回原本代表的數位訊號,就必須使用一組類比數位轉換器 (Analog-to-Digital Converter, ADC),且解析度也同為 N-bit, 之後轉換解析成正確的數位結果再做進一步的處理,整個系統的示意方塊圖如圖 1-1 所示。

因此透過多位準調變(Multi-level signaling modulation)的方式應用在 串列連結傳輸通訊系統上,確實可以大大地增加傳輸率,提高系統的資料 吞吐量(throughput)。

圖 1.1 串列連結 (Serial Link) 傳輸系統示意方塊圖

另外從通訊通道(communication channel)中的傳輸量來討論,令人感興趣的問題是在一條帶有可加性白高斯雜訊(additive white Gaussian noise, AWGN)分佈中的通訊通道中,究竟最大可以傳遞的位元率(bps)是多少?根據 Hartley-Shannon Channel Capacity Law(或 Hartley-Shannon Theorem)[6]可知,通道訊息容量(Channel capacity, C)、通道頻寬(BW)與接收到訊號的功率大小與該頻寬區段內雜訊的比值(SNR, signal-to-noise ratio)的關係可以表示成式(1.1)的形式,因此可知給定通道頻寬 BW 及接收到的SNR,此定理提供了資料傳輸率理論上最大可達到的上限。

$$C = BW \log_2(1 + SNR)$$

(bps) (1.1)

所以在傳輸通道頻寬有限的情況下,透過提升此通訊系統的訊雜比 (SNR),如此一來整個通道的傳輸容量將可被大幅的提升。為實現這樣的系統,如同前述在收發端分別利用一組 ADC 與 DAC 作為系統的收發器 (transceiver),即可有效的提升系統的 SNR,大幅提升傳輸通道的訊息容量,因此此組資料轉換器對 (Data Converter Pair, ADC & DAC) 成為系統中最關鍵的電路。

本論文為經濟部學界科專計畫—「晶片系統傳輸鏈之電路系統設計與 驗證平台開發計畫」的執行成果之一。計畫目標主要是因應半導體技術已 進入奈米級(100nm)以下的世代,一個晶片將可容納數十億個電晶體,以 系統層次面向來說,諸多工作在不同之時脈頻率的矽智財(IP, Intellectual Property)將會同時整合在一個晶片內成為一個系統晶片(SoC),因此可以 預見的是屆時 SoC 的架構發展會遇到的問題就如同 PCB 的發展一樣,晶片 內網路(Network on Chip, NoC)將會變得相當複雜,各個元件裝置互連 (Interconnect)的訊號線傳輸速度將受限,成為整個系統效能的瓶頸。整 個計劃以 10Gbps 的傳輸速率為目標,基於此一目標而配合整個系統所設計 的超高速資料轉換器對(Very High Speed Data Converter Pair—ADC & DAC)因此成為非常關鍵的電路,主要特色是必須具備相當高速的取樣頻 率,配合中低解析度(Medium-low resolution)的能力即可,因此依照總計 畫整個傳輸鏈系統的需求,訂立出的資料轉換器對—ADC 與 DAC 之主要 規格如下表 1.1 所示。

表 1.1 ADC 與 DAC 之規格

|                            | ADC                                 | DAC                                        |

|----------------------------|-------------------------------------|--------------------------------------------|

| Supply Voltage             | 1896 1.0 V                          |                                            |

| Sampling Rate              | 10 G-Samples/s                      |                                            |

| Resolution                 | 4 bits                              |                                            |

| I/O Full Swing             | Differential ±400 mV                |                                            |

| I/O Tampingtion Internal 5 | Internal 50Ω                        | Internal $50\Omega$ // External $50\Omega$ |

| I/O Termination            | internal 30s2                       | (Double Terminaton)                        |

| Technology                 | UMC 90nm CMOS Mixed-Mode 1P9M Low-K |                                            |

在已知文獻中,能達成數 Giga-Samples/s 等級以上的超高速 ADCs 或 DACs,有相當大的一部分是使用 SiGe 或 GaAs 這類的製程來設計實現[7] —[10],使用此類製程在高速場合的應用確實會比較出色,但往往也消耗相當大的功率。而 CMOS 製程成本較為低廉且技術成熟,所以現階段多數積體電路設計仍是以 CMOS 為主流,另外由於 CMOS 的應力特性較佳,適合製作大面積晶片,所以是相當適合 SoC 發展的平台,綜觀目前積體電路(IC,

Integrated Circuit)設計,大多數都是 CMOS 製程為主,顯見使用 CMOS 設計的電路將有較佳的競爭力與較高的整合度。然而以 CMOS 製程設計高速電路是較為困難的地方,所以如果要採用 CMOS 製程來設計此種超高速 ADC 與 DAC 的話,除了電路上的技巧之外,從系統層次來看可以使用time-interleaved 型式的架構[7][11]—[16]使得等效輸出速率得以增加,但time-interleaved 架構會遭遇到相當龐大的硬體電路以及驚人的功率消耗等問題,使其在實際的應用上也有不少限制。在此我們研究設計的此組超高速資料轉換器對乃是針對不使用 time-interleaved 的架構,並以計畫協助提供的聯電 (UMC) 90nm CMOS Mixed-Signal Low-K 製程作研製。

#### 1.3 論文章節組織

本論文共分為七章。第二章首先介紹說明資料轉換器對(ADC & DAC)的基本原理及架構,同時解釋資料轉換器常見的各種效能評估參數。接下來的第三章將分析說明並討論我們所設計實現的此組超高速 10GS/s 4-bit資料轉換器對各部份電路的設計議題及設計考量。先是發送端 DAC 電路設計的說明,接者是接收端 ADC 的部份。第四章呈現完整的 DAC 與 ADC電路模擬結果。之後第五章對一般超高速資料轉換器電路在實際晶片測試的情況中容易遭遇到的問題作解說,並針對這些問題陳述我們在設計階段對整個 DAC 及 ADC 之測試晶片(test chip)所作的可測試性設計(Design-for-Testability, DfT),以及所加入的輔助測試電路,使測試晶片具有良好的可測試機制。接者顯示整合 DfT 電路後,完整測試晶片電路的模擬結果。然後藉由可測試機制電路的輔助,說明如何進行實驗晶片的量測。第六章詳述實驗晶片的測試環境設定以及完整的晶片量測結果。而最後在第七章對本論文做一總結。

## 資料轉換器對 ADC 與 DAC 之 基本原理及架構

本章節將介紹說明資料轉換器對—ADC 與 DAC 的基本操作原理以及各種用來評估描述其效能好壞的特性參數,由於這些參數在之後的內容中會時常被提及,因此能夠了解這些參數是能看懂模擬分析與量測結果的第一步。之後我們會簡單的說明目前 ADC 與 DAC 常見的幾種架構,並指明我們的設計所選用的架構。

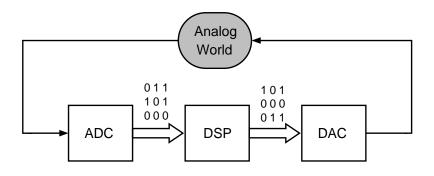

#### 2.1 資料轉換器 (Data Converter) 的基本操作原理

資料轉換器(Data Converter)指能夠將訊號形式轉換的 ADC 與 DAC 電路,廣泛地運用在各種通訊及電子裝置系統裡。在半導體技術快速進步的刺激下,使得數位系統如電腦資訊產業等的快速發展與之相輔相成,且基於數位訊號快速的處理能力與在各種通訊傳輸系統中的優勢下,更帶來數位化的潮流。為了有效率的應用數位訊號的諸多特點,必須使用的介面電路就是資料轉換器—ADC 與 DAC,由於真實世界的各種訊號都以類比的形式存在,欲藉由數位方式的處理則必須先經過 ADC 的作用將類比訊號轉換成數位訊號,然後透過各式各樣的數位訊號處理 (DSP, Digital Singal Processing) 技巧,使得訊號得以被更多元化以及更有效率的方式處理運用,經處理過後的訊號即可透過 DAC 的運作將訊號反向轉換成為類比的形式,使人類可以直接接受,整個系統的簡單示意圖如圖 2.1 所示。

圖 2.1 類比訊號與數位訊號介面示意圖[17]

#### 2.1.1 類比數位轉換器 (Analog-to-Digital Converter, ADC)

理想解析度(Resolution)為N位元的ADC將連續時間(continuous-time)的類比輸入訊號( $V_{in}$ )轉換編碼成一連串N個位元為一組數位碼的離散時間(discrete-time)訊號,其轉換的過程滿足下式(2.1)的關係[18]:

$$V_{in} = V_{FS} \sum_{k=1}^{n} \frac{b_{n-k}}{2^k} + V_Q = V_{FS} \left( \frac{b_{n-1}}{2} + \frac{b_{n-2}}{2^2} + \dots + \frac{b_1}{2^{n-1}} + \frac{b_0}{2^n} \right) + V_Q$$

(2.1)

其中 $V_{FS}$ 為滿刻度電壓(Full-Scale voltage),表示該 ADC 可處裡之最大類比電壓訊號(訊號不一定為電壓的形式,電流或其他的電氣訊號皆可,為方便說明故以電壓來表示)範圍; $b_{n-k}$ 表示每個個別輸出的數位位元,而 $V_Q$ 為類比數位轉換過程中必定會出現的量化誤差(Quantization Error),有關量化誤差的說明會在後面更詳細的討論到。將式(2.1)以最小單位刻度電壓( $V_{LSB}$ )來表示,可以寫成式(2.2)的形式:

$$V_{in} = \frac{V_{FS}}{2^{N}} \left( b_{n-1} 2^{N-1} + b_{n-2} 2^{N-2} + \dots + b_{1} 2^{N-(n-1)} + b_{0} 2^{N-n} \right) + V_{Q} = V_{LSB} \sum_{k=1}^{n} b_{n-k} 2^{N-k} + V_{Q}$$

$$(2.2)$$

式(2.2)中定義出了最小單位刻度電壓( $V_{LSB}$ )如式(2.3)所示,表示將輸入範圍允許的滿刻度範圍電壓 $V_{FS}$ 均分成  $2^{N}$  個準位,明確的定義出每個準位之間的的類比電壓差值為一個  $V_{LSB}$  的大小。

$$V_{LSB} \equiv \frac{V_{FS}}{2^N} \tag{2.3}$$

一般而言都把一個  $V_{LSB}$  的電壓值稱為一個 LSB(Least Significant Bit),這是一個無單位(Unitless)的名詞,是將電壓值歸一化(Normalized)的比值結果。例如習慣上可能會稱說有 1.5LSB 的誤差,實際的意思就是表示此誤差量的電壓值為  $V_{LSB}$  的 1.5 倍。

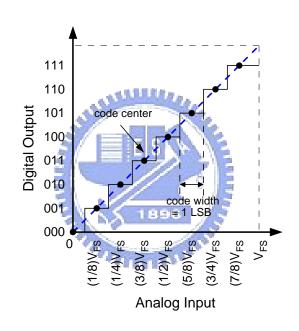

以一個解析度為三位元的理想 ADC 來說,其輸入輸出的轉換特性曲線如圖 2.2 所示。

圖 2.2 理想之三位元 ADC 輸入輸出轉換特性曲線

轉換特性曲線中每個數位的輸出碼(Digital Output)都對應到一小區段的類比輸入(Analog Input)訊號範圍,此一範圍就是1個LSB的寬度(code width),且每個LSB的中心點都座落在每個數位碼輸出區間內的正中間位置(code center)。在滿刻度電壓範圍內任意的類比輸入電壓,都會被解析成該電壓值大小與某個LSB的中心點(code center)差距最近所對應到的數位碼輸出,因此得到的數位碼輸出是該有限解析度之ADC將輸入轉換成輸出做最近似的結果,這說明ADC的轉換行為是多對一的結果,因此這之

間便產生了某種程度的誤差存在。考慮圖 2.2 中,由階梯轉換曲線中每個步階的中間點(code center)連接起來所代表的類比輸入訊號之斜虛線與數位輸出的轉換階梯狀曲線之差值,就是類比訊號被量化(Quantize)產生的誤差部分,稱之為量化誤差(Quantization Error),由於任意的 ADC 皆為有限的解析度,只能輸出有限個數的數位碼( $2^N$ ),因此即使是一個理想轉換特性的 ADC 必然也會產生若干的量化誤差。

#### 2.1.2 數位類比轉換器 (Digital-to-Analog Converter, DAC)

為簡單說明 DAC 的基本操作原理,一樣以理想的 DAC 來做探討,一解析度為 N 位元的 DAC 將 N 個位元為一組的數位的輸入轉換為類比輸出訊號,轉換的過程滿足式 (2.4) 的關係 [18]:

$$V_{out} = V_{FS} \sum_{k=1}^{n} \frac{b_{n-k}}{2^k} = V_{FS} \left( \frac{b_{n-1}}{2} + \frac{b_{n-2}}{2^2} + \dots + \frac{b_1}{2^{n-1}} + \frac{b_0}{2^n} \right) = V_{FS} \times D_{in}$$

(2.4)

$b_{n-k}$ 為每個個別輸入的數位位元(Digit)。以最小單位刻度電壓( $V_{LSB}$ )來表示的話,可以得到式(2.5)的結果:

$$V_{out} = \frac{V_{FS}}{2^{N}} \left( b_{n-1} 2^{N-1} + b_{n-2} 2^{N-2} + \dots + b_1 2^{N-(n-1)} + b_0 2^{N-n} \right) = V_{LSB} \sum_{l=1}^{n} b_{n-k} 2^{N-k}$$

(2.5)

從(2.4)與(2.5)的式子可以得知,在數位轉類比的程序中,不會產生類似於 ADC 的量化誤差項,這主要是因為數位類比的轉換行為是一組數位碼對應到一個固定的類比物理量輸出,是一對一的轉換結果,所以不會有取近似結果的情況發生,也就沒有誤差的成份發生。

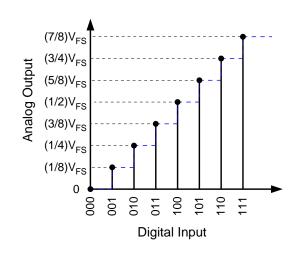

同樣以解析度為三位元的理想 DAC 來說,輸入對輸出轉換特性曲線如圖 2.3 所示。

圖 2.3 理想之三位元 DAC 輸入輸出轉換特性曲線

轉換特性曲線中明確的指出對於每個數位的輸入碼(Digital Input)都可以對應到一個滿刻度電壓範圍以內的類比輸出電壓。

#### 2.2 資料轉換器的效能參數介紹[18][19][20][21][22]

單純從 ADC 與 DAC 解析度的高低並無法完全的說明其實際上的轉換特性及效能好壞,真實設計出來的 ADC 或 DAC 可能會因許多方面因素的影響而偏離原本理想的特性轉換曲線。因此有許多用來描述分析 ADC 與DAC 的特性參數,且因應用領域的不同會強調不同的特性參數,這些參數包括:準確性 (Accurcay)、解析度 (Resolution)、偏移誤差 (Offest Error)、增益誤差 (Gain Error)、差分非線性誤差 (Differential Non-Linearity, DNL)、累積非線性誤差 (Intrgral Non-Linearity, INL)、訊號對雜訊比 (Signal-to-Noise Ratio, SNR)、訊號對雜訊失真比 (Signal-to-Noise and Distortion Ratio, SNDR)、有效位元數 (Effective Number Of Bits, ENOB)、總諧波失真 (Total Harmonic Distortion, THD)、無假訊號動態範圍 (Spurious-Free Dynamic Range, SFDR)、有效解析度頻寬 (Effective Resolution Bamdwidth, ERBW)與動態範圍 (Dynamic Range, DR)等。一

般可將 ADC 與 DAC 的特性參數分為粗略區分為靜態參數 (Static Parameters) 以及動態參數 (Dynamic Parameters),以下我們將分別介紹說明這些參數。

#### 2.2.1 静態參數 (Static Parameters)

對於 ADC 或 DAC 的靜態參數(Static Parameters)的獲得,必須對轉換器輸入低速的刺激訊號,該訊號的變化速度要夠緩慢,有時甚至會是輸入一個固定的訊號源(constant input stimulus)。靜態參數包含了準確性(Accurcay)、解析度(Resolution)、偏移誤差(Offest Error)、增益誤差(Gain Error)、差分非線性誤差(Differential Non-Linearity, DNL)、累積非線性誤差(Intrgral Non-Linearity, INL)。

#### 2.2.1.1 準確性 (Accuracy)

準確性的定義為當輸入一已知的訊號,而可預期到無誤差情況下轉換器的輸出結果與實際輸出包含所有各種靜態誤差量(包括量化誤差、偏移誤差、增益誤差和所有非線性成份)的總和,兩者之間的差異,主要就是用來指出 ADC 或 DAC 對理想特性轉換曲線的總偏移程度。

#### 2.2.1.2 解析度 (Resolution)

解析度對 ADC 與 DAC 而言分別為輸出和輸入數位訊號的位元數,以 N 來表示的話,一理想的 N-bit 轉換器而言,其將可處理範圍內的訊號( $V_{FS}$ ) 等量劃分成  $2^N$  個準位,也就是前述式子(2.3) 所定義的,每個準位大小即 為一個  $V_{LSB}$ 之值,也常稱為一個 LSB。可以注意到的是,解析度的高低直接影響了一個 LSB的大小,對 ADC 而言在固定  $V_{FS}$ 的情況下,就是直接影響到特性轉換曲線(圖 2.2) 裡每個輸出碼的寬度(code width)以及量化

#### 2.2.1.3 偏移誤差 (Offset Error)

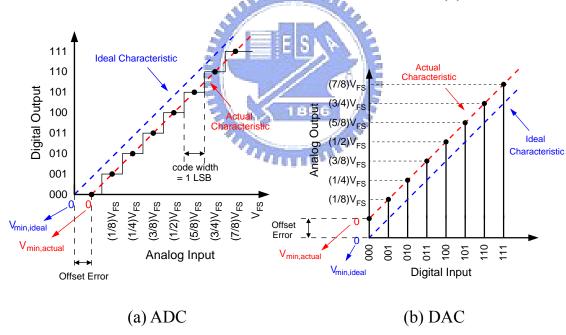

偏移誤差 (Offset Error, Eoffset) 描述的是 ADC 或 DAC 的輸入輸出特性轉換曲線中,0 點位置偏移的誤差。對 ADC 而言發生偏移誤差的情形指的是「輸入」的偏移誤差,使實際和理想的輸入輸出特性轉換曲線之間在輸入訊號為 0 時,存在的一個固定平移差異,如圖 2.4(a)所示,理想的轉換曲線中第一個使輸出轉態的電壓應該是 0.5LSB 的位置,實際轉換曲線中偏移此值的誤差量就是 ADC 的偏移誤差。另一方面對於 DAC 來說,發生偏移誤差是指「輸出」的偏移誤差,也就是假設輸入數位訊號皆為 0 時,輸出之類比訊號不為 0 的量,就是 DAC 的偏移誤差,如圖 2.4(b)所示。

圖 2.4 ADC 與 DAC 之偏移誤差 (Offset Error) 示意圖

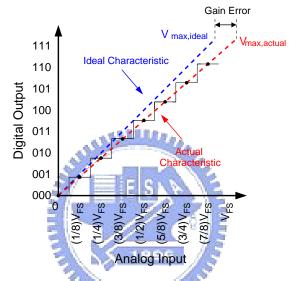

#### 2.2.1.4 增益誤差 (Gain Error)

增益誤差(Gain Error, Egain)指的是在沒有偏移誤差的情況下,實際與理想輸入輸出轉換特性曲線之間斜率的差異,對於理想的特性轉換曲線而言,其斜率大小應為1,因此增益誤差描述的就是實際特性轉換曲線斜率大

於 1 或小於 1 的誤差。如圖 2.5 所示,靠近左上方向的斜虛線是理想的情況,而靠近右下的斜虛線則是實際包含增益誤差的結果,以數學式來表達,就是實際特性曲線中最後一個最高轉態點( $V_{max,actual}$ )與理想特性曲線裡最後一個最高轉態點( $V_{max,ideal}$ )之間的差值,然後再做正規化(Normalize)使結果可表示為多少個 LSB 的大小,即式子(2.6)所示。

圖 2.5 增益誤差 (Gain Error) 示意圖

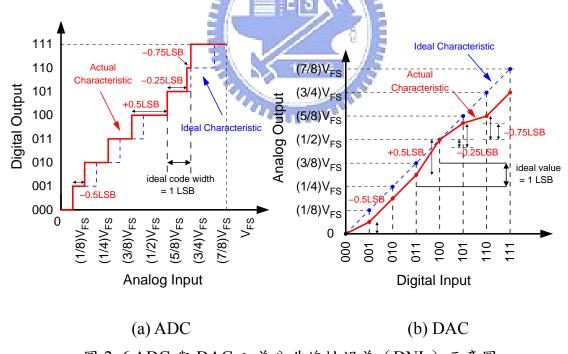

#### 2.2.1.5 差分非線性誤差 (Differential Non-Linearity, DNL)

差分非線性誤差(Differential Non-Linearity, DNL)的討論是先行將轉換器的特性轉換曲線中偏移誤差及增益誤差去除的情況下而得的,對 ADC來說,理想的轉換曲線每個步階寬度(step width)都應該相同為 1 個 LSB的大小,也就是這些步階大小都應為均勻(Uniform)分佈,而非線性將造成步階大小(step size)為非均勻(Non-uniform)的分佈,DNL 就是用來描述每個步階大小不為 1 個 LSB的分佈情況,所以將每兩個相鄰使輸出數位碼轉態的類比訊號準位間的差值再減去理想曲線中相同使數位碼轉態的類比訊號準位間的差值再減去理想曲線中相同使數位碼轉態的類比訊號差值(即 1 個 LSB)的結果就是兩個連續的輸出數位碼之間的 DNL

值,而相同為了以多少個 LSB 來表示,就必須再對 1 個 LSB 大小作正規化。以數學式表示可寫成式(2.7)的形式,其中  $V_{actual}(n)$ 為實際轉換曲線中使第 n 個碼轉態到下一個數位碼所對應到的輸入類比電壓準位值。

$$DNL(n) = \frac{(V_{actual}(n+1) - V_{actual}(n)) - V_{LSB}}{V_{LSB}} = \frac{V_{actual}(n+1) - V_{actual}(n)}{V_{LSB}} - 1 \text{ (LSB)}$$

(2.7)

另一方面由於 DAC 的轉換關係是一對一的轉換特性,當輸入的數位碼每加 1 之後,理想的類比輸出訊號也就直接增加一個  $V_{LSB}$  的大小,因此當實際的類比輸出訊號增量不為一個  $V_{LSB}$  的大小時,此誤差與理想的 1 個 LSB 相滅的結果即為 DNL 的值,同樣將結果對 1 個 LSB 作正規化即可得到以 LSB 為單位的 DNL 值,數學上表示的結果與式(2.7)相同,差別在於對 DAC 而言的  $V_{actual}(n)$ 為第 n 個數位輸入碼所產生對應到的第 n 個輸出類比電壓準位值,有別於 ADC 而言的「輸入」類比電壓值。

圖 2.6 ADC 與 DAC 之差分非線性誤差 (DNL) 示意圖

ADC 與 DAC 之 DNL 圖形上說明則分別顯示在圖 2.6(a)與 2.6(b)。從 圖中可以想見到的是,愈理想的 ADC 其每個步階的寬度(即相鄰兩個使輸出數位碼轉態的輸入類比電壓差值)就愈接近 1 個 LSB,使得 DNL 也愈趨

近於 0LSB。而愈理想的 DAC 其每相鄰的兩個輸出類比電壓之差值就愈接近1個 LSB,也是使 DNL 越趨近於 0LSB。

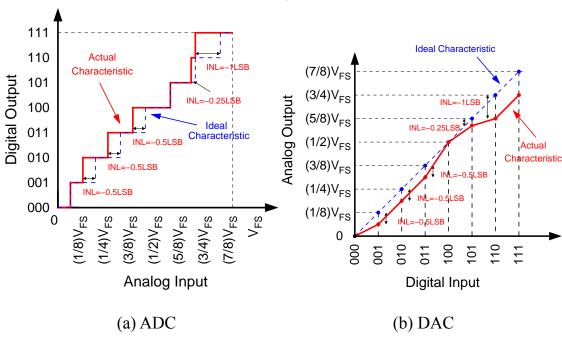

#### 2.2.1.6 累積非線性誤差 (Integral Non-Linearity, INL)

累積非線性誤差(Integral Non-Linearity, INL)也是將特性轉換曲線裡可能發生的偏移誤差以及增益誤差去除後而做的分析,INL 意義指的是實際轉換器的輸入輸出特性轉換曲線與理想的特性轉換曲線之間的誤差量,實際非理想 ADC 的轉換曲線由每個輸出數位碼的中間點(code center)連接而成,這些點與理想 ADC 轉換曲線中相對應的每個輸出數位碼中間點之間的差距就分別代表各個輸出數位碼的 INL值;DAC的輸入輸出轉換曲線可藉由連接每個輸入數位碼對應到的類比電壓輸出之值而得到,這些類比輸出電壓值的點與理想 DAC 轉換曲線中相對應的每個類比電壓輸出值的點之差值就是各個輸出的 INL值。數學式可寫成式(2.8)的形式,圖 2.7顯示了 ADC與 DAC 各別的 INL的示意圖。

$$INL(n) = \frac{V_{actual}(n) - V_{actual,min}}{V_{LSB}} - n \text{ (LSB)}$$

(2.8)

圖 2.7 ADC 與 DAC 之累積非線性誤差 (INL) 示意圖

從前述的討論以及圖 2.7 可知,要計算第 n 個碼的 INL 值,可以將第 1 個到第 n 個碼的 DNL 值作累加也可以得到相同結果,式子可寫成如(2.9) 式所示。

$$INL(n) = \sum_{i=1}^{n} DNL(i) \text{ (LSB)}$$

(2.9)

有時候計算 INL 時的比較參考對象可以不必是理想的轉換曲線,而是根據實際電路轉換曲線上的各個點來找出一條直線,該直線使原本發生最大 INL 值的數碼得以變得較小,而其他某些若干的 INL 卻可能會因此而稍微變大,以這條直線當參考對象的話,可以將原本每個碼的 INL 值作平均的作用,此直線通常稱為最佳符合線(Best-Fit Line)[23]。之所以有這樣的計算方式主要是因為有時在資料轉換器的設計上,設計者只在乎電路最大或最小的 INL 和 DNL 表現,因此在許多的技術文獻上,INL 或 DNL 各只標明出一組較大及較小的值,代表的就是該資料轉換器最大和最小的 INL 及 DNL。

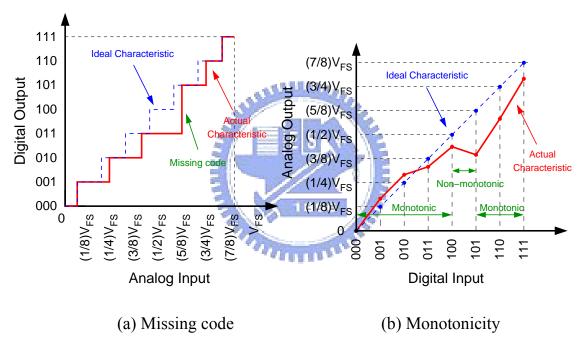

#### 2.2.1.7 缺碼及單調性 (Missing Code & Monotonicity)

缺碼(Missing Code)的描述是對 ADC 的轉換特性曲線來討論的,在容許的類比電壓輸入範圍內,固定有某個數位輸出碼一直無法被轉換出,該數碼對於該 ADC 而言就是遺漏掉的數位結果,這主要是由於實際電路的轉換曲線在某個轉態步階有過大的 DNL 響應,一般若是 ADC 的最大 DNL 超過 1 個 LSB 或是最大的 INL 超過 0.5 個 LSB 的情況下就會發生缺碼的問題,如圖 2.8(a)所示,實線代表實際 ADC 的轉換曲線,輸出 011 的下一個輸出直接為 101 而跳過了 100 這個結果,因此可以說 100 這個數位碼是該 ADC 無法輸出的缺碼。相同用來描述 DAC 的類似情形稱為單調性(Monotonicity),DAC 的類比輸出隨數位輸入訊號的增加而增加,滿足此

情形的響應我們都說 DAC 呈現單調性,反之若 DAC 的轉換曲線中發生數位輸入訊號增加,但類比輸出訊號卻反之降低(即轉換曲線中存在負斜率的區段)的情況就是非單調性(Non-monotonicity),同樣當 DAC 有超過 1個 LSB 的 DNL 或是超過 0.5 個 LSB 的 INL 的響應時,就會發生非單調性的問題,圖 2.8(b)描繪了 DAC 轉換曲線單調及非單調性的特徵,輸入數位訊號在 000 到 100 以及 101 到 111 這兩個區間內,輸出都隨輸入增加,但當輸入由 100 增加至 101 時,對應的類比輸出訊號卻不增反減,此即為非單調性的現象。

圖 2.8 ADC/DAC 缺碼 (Missing code) 與單調性 (Montonicity) 示意圖

#### 2.2.2 動態參數 (Dynamic Parameters)

前一小節提及的各種參數都是和輸入訊號無關的參數 (signal-independent或 memory-less),並不與轉換器輸入訊號的頻率有關, 所以稱之為靜態參數。另外相對於靜態參數的描述就是與輸入訊號相關的 (signal-dependent)動態參數(Dynamic Parameters),主要是用來特徵化資 料轉換器在實際的操作環境下,對於各種不同頻率的輸入訊號所能反映出 的效能,由於通訊系統當中的資料轉換器通常都會操作在較高的頻帶範圍,因此動態參數可以評估資料轉換器真實呈現的轉換效能。常見的動態參數包含訊號對雜訊比(Signal-to-Noise Ratio, SNR)、訊號對雜訊失真比(Signal-to-Noise and Distortion Ratio, SNDR)、有效位元數(Effective Number Of Bits, ENOB)、總諧波失真(Total Harmonic Distortion, THD)、無假訊號動態範圍(Spurious-Free Dynamic Range, SFDR)、有效解析度頻寬(Effective Resolution Bamdwidth, ERBW)與動態範圍(Dynamic Range, DR)等。

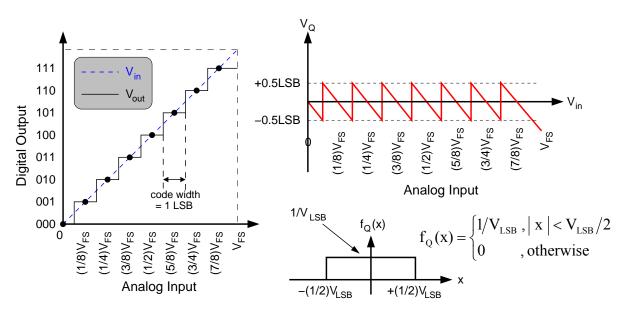

#### 2.2.2.1 量化雜訊 (Quantization Noise)

在討論各種動態參數之前,必須要先知道的是 ADC 進行轉換過程中會發生的量化誤差 (Quantization Error),量化誤差是由於 ADC「有限的解析度 N」而限制了該轉換器的訊號對雜訊比 (Signal-to-Noise Ratio, SNR),這裡要強調的是有限解析度的觀念,因為 ADC 的轉換主要就是量化 (Quantize)的結果,有限解析度 N 導致有限的 V<sub>LSB</sub>大小,因此當輸入類比電壓座落在某兩個連續使輸出數位碼轉態 (transition)的範圍內,該類比電壓都會被解析成此範圍內所對應到的數位結果,也就是說只要在該電壓範圍裡,不管輸入的電壓大小為何,都一律被解釋成相同的輸出,這之間的誤差就是量化誤差。

要注意的是,即使具有理想轉換曲線的 ADC 也會因有限的解析度而產生量化誤差,圖 2.9 顯示一具有理想特性轉換曲線的三位元 ADC 所產生量化誤差的說明,假設輸入  $V_{in}$  為斜坡(ramp)形式的類比訊號(圖 2.9 左圖之斜虛線),而產生階梯狀(staircase)形式的輸出  $V_{out}$ (圖 2.9 左圖之實線),取  $V_{out}$ 與  $V_{in}$ 之差( $V_{out}$ — $V_{in}$ )可得到圖 2.9 右上方圖的量化誤差  $V_Q$ 之結果,由於  $V_Q$  的響應類似雜訊般不斷上下變化,因此也常稱為量化雜訊

#### (Quantization Noise) •

圖 2.9 ADC 之量化雜訊 (Quantization Noise)

量化雜訊  $(V_Q)$  的重要特性是其大小都被限制在±0.5 個 LSB 之內,也就是在 $-(\frac{1}{2})V_{LSB}\sim +(\frac{1}{2})V_{LSB}$ 之間變化,更一般化定量  $V_Q$  的大小的方法是用統計的方式來描述,假設輸入訊號不是單純的斜坡函數輸入,而是大小在  $V_{FS}$  內快速變化的隨機訊號,使得隨機變數  $V_Q$  將均勻分佈(uniform distributed)在 $-(\frac{1}{2})V_{LSB}\sim +(\frac{1}{2})V_{LSB}$  以內,且  $V_Q$  的平均值為 0  $(V_{Q(avg)}=0)$ ,對應的機率密度函數(Probability density function) $f_Q(x)$ 如圖 2.9 右下圖所示,從中計算  $V_Q$  的均方根(root-mean-square)值,如數學式(2.9)所示。

$$V_{Q(rms)} = \left[ \int_{-\infty}^{\infty} x^2 f_Q(x) dx \right]^{\frac{1}{2}} = \left[ \frac{1}{V_{LSB}} \int_{-V_{LSB}/2}^{V_{LSB}/2} x^2 dx \right]^{\frac{1}{2}} = \frac{V_{LSB}}{\sqrt{12}}$$

(2.9)

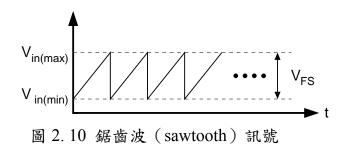

了解量化雜訊的均方根值之後,可計算 ADC「單純因量化雜訊」所導致的訊號對雜訊比(Signal-to-Niose Ratio, SNR)之結果。首先假設輸入訊號是在  $V_{FS}$  範圍內由最小值增加到最大值且重複不斷的鋸齒波(sawtooth)訊號,如圖 2.10 所示。

可計算此訊號的均方根值為 $V_{FS}/\sqrt{12}$ ,進一步求得 SNR 為:

$$SNR = 20 \log_{10} \left( \frac{V_{in(rms)}}{V_{Q(rms)}} \right) = 20 \log_{10} \left( \frac{V_{FS} / \sqrt{12}}{V_{LSB} / \sqrt{12}} \right) = 20 \log_{10} \left( 2^{N} \right) = 6.02 N \quad (dB) \quad (2.9)$$

而當輸入訊號變成在  $V_{FS}$  範圍內由最小值到最大值之間變化的弦波 (Sinusoidal) 時,此時輸入訊號的均方根值變為 $V_{FS}/2\sqrt{2}$ ,SNR 為:

$$SNR = 20 \log_{10} \left( \frac{V_{FS} / 2\sqrt{2}}{V_{LSB} / \sqrt{12}} \right) = 20 \log_{10} \left( \sqrt{\frac{3}{2}} \times 2^{N} \right) = 6.02N + 1.76 \text{ (dB)}$$

(2.10)

其中 N 為解析度。比較(2.9)與(2.10)的結果,可知當輸入為弦波訊號時,可得到比鋸齒波訊號還多 1.76dB 的 SNR 值。而從(2.10)式可知當解析度 N 每增加 1-bit,SNR 便可增加約 6dB,這也相當直觀的可以從 ADC 的特性轉換曲線中了解當解析度 N 愈高時,量化雜訊也就會愈小,進而使 SNR 獲得較高的結果。另外式(2.10)的結果:SNR = 6.02N + 1.76 (dB) 常被用來描述 N-bit ADC 所能達到的最大 SNR 值(Peak-SNR, PSNR)。

#### 2.2.2.2 訊號對雜訊比 (Signal-to-Noise Ratio, SNR)

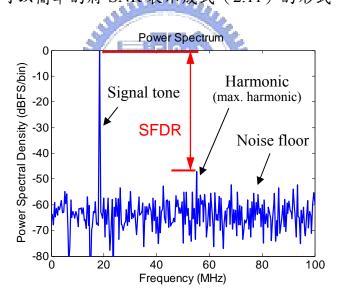

訊號對雜訊比(Signal-to-Noise Ratio, SNR)是指訊號與雜訊的比值, 前一小節討論到的 SNR 中,雜訊功率是只有量化雜訊的部份,然而對一個 實際的 ADC 來說,轉換過程中除了量化雜訊之外還會有電路本身所產生的 雜訊以及因溫度造成的熱雜訊(Thermal Noise),因此當計算到這些所有雜 訊功率總和之後求得的 SNR 值,才會是真正 ADC 所能呈現的 SNR,通常要觀測計算這些總雜訊功率的量可以從頻譜上的結果來求得,常見的方法是將 ADC 的輸出訊號經由快速傅立業轉換(Fast Fourier Transform, FFT)到頻域中,計算加總輸入訊號可能出現的頻率範圍內所有的雜訊功率,以Nyquist-rate ADC 來說,所關心的頻率範圍就是 DC 到 Nyquist 頻寬內所有雜訊的總和。而訊號功率是指 ADC 輸出的訊號頻譜中,座落在與 ADC 輸入訊號頻率相同位置上的音調(Signal tone)之功率。另外對 DAC 來說,雖然沒有量化雜訊的影響,但電路雜訊與熱雜訊依然存在,因此利用類似的方式可以計算得到 DAC 的 SNR。圖 2.11 顯示了一個頻譜的例子,主要輸入訊號的音調(Signal tone)以及雜訊水平(Noise floor)都清楚的被標示出,根據此圖可以簡單的將 SNR 表示成式(2.11)的形式。

圖 2.11 非理想之 6 位元 ADC 輸出訊號頻譜

$$SNR = 10 \cdot \log_{10} \left( \frac{P_{signal}}{P_{noise}} \right) = 10 \cdot \log_{10} \left( \frac{\text{Signal Power}}{\text{Total Noise floor Power}} \right) \text{ (dB)}$$

(2.11)

### 2.2.2.3 訊號對雜訊失真比

## (Signal-to-Noise and Distortion Ratio, SNDR)

訊號對雜訊失真比(Signal-to-Noise and Distortion Ratio, SNDR, 或 SINAD)的定義與 SNR 類似,差別在於 SNDR 除了將所有的雜訊功率加總之外,還多加入了頻譜上可能出現的多次諧波失真(Harmonic Distortion),因為電路本身有許多非線性因素,使得最後轉換器輸出的頻譜中出現諧波失真的訊號,將這些個別的諧波訊號加總得到總諧波失真功率  $P_{\text{harmonics}}$  再與總雜訊功率  $P_{\text{noise}}$  相加作為主訊號(Signal tone)以外的干擾量。圖 2.11 也標示出了諧波的位置,對應的數學式顯示在(2.12)式。

$$SNDR = 10 \cdot \log_{10} \left( \frac{P_{signal}}{P_{noise} + P_{harmonics}} \right)$$

$$= 10 \cdot \log_{10} \left( \frac{\text{Signal Power}}{\text{Total Noise and Distortion Power}} \right) \text{ (dB)} \quad (2.12)$$

由於 SNDR 比起 SNR 還多計算了諧波的功率,因此 SNDR 參數除了可以看到雜訊的影響之外,還可以得知非線性諧波失真的影響程度,此參數是資料轉換器中相當常見的參數,也是最嚴苛最重要的指標參數之一。

# 2.2.2.4 有效位元數 (Effective Number Of Bits, ENOB)

有效位元數(Effective Number Of Bits, ENOB)的計算是根據式(2.10)的結果: SNR = 6.02N + 1.76 (dB),不同解析度的轉換器將得到不同的最大 SNR 值,然而對於真實的轉換器而言,輸出訊號的頻譜可能存在若干因電路非線性的失真或是其他互調失真等的諧波訊號,此種情形用 SNDR 的結果來評估電路的真實效能會是比較客觀的標準,因此式(2.10)可被修正成:

$$SNDR = 6.02N + 1.76 \text{ (dB)}$$

(2.13)

其中也是假設輸入為弦波訊號的前提下得到的結果。從實際量測到的頻譜

中計算得到的 SNDR 再代入式 (2.13), 便可從該頻譜得知受測的資料轉換器究竟具備多少「有效的」解析度能力, 也就是有效位元數 N, 因此可以定義出一個資料轉換器的有效位元數為 (2.14) 式:

$$ENOB = \frac{SNDR - 1.76}{6.02}$$

(bits) (2.14)

SNDR與ENOB是最直接能表示資料轉換器實際效能的參數,因為可以直接看出設計的資料轉換器是否能達到原始設計規格所定義的解析度程度,而且也透露出此轉換器線性度的好壞。

# 2.2.2.5 總諧波失真 (Total Harmonic Distortion, THD)

總諧波失真(Total Harmonic Distortion, THD)是指在輸入訊號可能出現的頻帶範圍內(對 Nyquist-rate 的資料轉換器而言就是 DC 到 Nyquist 之間的頻寬),所有諧波訊號功率的總和對主輸入訊號(Signal tone)功率的比值,數學式可以寫成(2.15)式:

1896

$$THD = 10 \cdot \log_{10} \left( \frac{P_{harmonics}}{P_{signal}} \right)$$

$$= 10 \cdot \log_{10} \left( \frac{\text{Total Harmonic Distortion Power}}{\text{Signal Power}} \right) \text{ (dB)} \quad (2.15)$$

誠如先前所述,諧波訊號的產生可能是因為電路的非線性失真或其他互調 失真等所導致的,透過 THD 的描述可以知道轉換器在各種不同頻率下,非 線性影響的程度有多少。

# 2.2.2.6 無假訊號動態範圍 (Spurious-Free Dynamic Range, SFDR)

無假訊號動態範圍(Spurious-Free Dynamic Range, SFDR)定義的是在輸入訊號可能出現的頻帶範圍內,主輸入訊號(Signal tone)功率對最大的

假訊號(Spurious)或最大的諧波訊號(Harmonic)功率的比值,如式(2.16) 所示,且單位為dBc (in dB with respect to carrier),圖形上的說明如圖 2.11 所繪。

$$SFDR = 10 \cdot \log_{10} \left( \frac{P_{signal}}{P_{spurious(max)/harmonic(max)}} \right)$$

$$= 10 \cdot \log_{10} \left( \frac{\text{Signal Power}}{\text{Largest Spurious or Harmonic Power}} \right) \text{ (dBc)} \quad (2.16)$$

Spurious(或簡稱 Spur)係指頻譜中的突刺,這些明顯高於雜訊水平(Noise floor)的突刺可能是先前提及的各種諧波訊號,包含非線性失真諧波、互調失真諧波以及時序取樣點誤差所造成的諧波等等,由於通常這些諧波訊號的功率比雜訊還來得高許多,所以有時候可能會被其他頻帶的接收端給監聽到,因此也被稱為假訊號。

# 2.2.2.7 有效解析度頻寬 (Effective Resolution Bamdwidth, ERBW)

有效解析度頻寬(Effective Resolution Bandwidth, ERBW)係指當轉換器的輸入訊號頻率不斷增加到某個值時,使 SNDR 的響應相較於輸入訊號為低頻時下降 3dB 點的位置(以 ENOB 來看就是減少 0.5bit 之時),就是該轉換器的 ERBW,換句話說,從 SNDR 對輸入訊號頻率的圖(SNDR vs. Input frequency plot)來看,假設低頻輸入訊號時的 SNDR 為 SNDR<sub>low-freq</sub>,當 SNDR 的值變成(SNDR<sub>low-freq</sub>—3dB)之時所對應到的輸入訊號頻率位置便是ERBW 的結果,此參數主要是用來描述該資料轉換器所能處理的最大輸入訊號頻寬,對 ADC 而言,ERBW 通常受限於輸入級類比電路的頻寬以及ADC 的最大取樣率(maximal sampling frequency)。以 Nyquist-rate 的資料轉換器來說,其最大可能的輸入訊號頻率為 Nyquist-frequency,其值為取樣頻率的一半,因此良好的設計可使 ERBW 達到 Nyquist-frequency,意即該

資料轉換器能處理的輸入訊號頻寬可達理論值上限的 Nyquist-frequency。

另外計算 ERBW 時要注意的是通常下降 3dB 點的參考對象是低頻時候的 SNDR,而不是以理論上 N 位元資料轉換器所具備的最大的 SNDR (Peak-SNDR, $SNDR_{peak}=6.02N+1.76$ ) 為參考。

## 2.2.2.8 動態範圍 (Dynamic Range, DR)

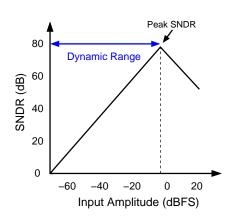

動態範圍(Dynamic Range, DR)定義為在固定某個輸入訊號的頻率下,作出 SNDR 對輸入訊號振幅(通常以 dBFS 來表示)的圖(SNDR vs. Input amplitude level plot),找出有最大 SNDR (Peak-SNDR) 時的輸入振幅到最小可被偵測到訊號時的 SNDR 值(通常為 SNDR=0 之時),這兩者之間的範圍就是動態範圍。對實際的資料轉換器來說,通常可以得到最大 SNDR的輸入振幅之位置都會略小於滿刻度電壓位準( $V_{FS}$ ,0-dBFS),以數學式表示則如式(2.17),簡單的示意圖如圖 2.12 所示。

$$DR = 10 \cdot \log_{10} \left( \frac{P_{signal(\text{max})}}{P_{signal(\text{min})}} \right) = 10 \cdot \log_{10} \left( \frac{\text{Maximum signal power}}{\text{Smallest signal power}} \right)$$

(2.17)

圖 2.12 動態範圍 (DR) 示意圖

## 2.3 ADC 及 DAC 各種架構簡介

本節將對常見 ADC 與 DAC 之架構做簡單的介紹,主要提及各架構所 具備的特性,但並不對各種架構做深入的探討。

#### 2.3.1 ADC 之各種架構

ADC 的架構相當多種,每種架構都有不同的特性,分別應用在各種不同的場合當中,ADC 的種類與特性主要都以解析度與取樣速度來做粗略的劃分,理想的轉換器其解析度與取樣速度當然都是越高越好,然而實際情形中,兩者往往卻是互相違背的,高解析度的設計就難以達到高取樣率的要求,而高速的取樣率也使得解析度的發展被侷限住。因此以這個指標來區分,大概可區分成三類,如表 2.1 所示。

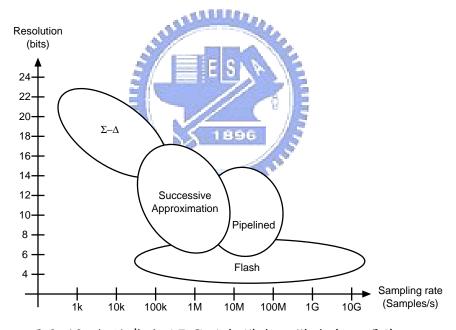

表 2.1 列出的數種架構中,較為常見的只有 Oversampling(超取樣)的  $\Sigma$ - $\Delta$  (sigma-delta)ADC、Successive-approximation(連續漸進式)ADC、Flash(快閃式)ADC 以及 Pipelined(管線式)ADC。 $\Sigma$ - $\Delta$ ADC 主要是利用 DSP 的技巧改變頻譜中量化雜訊的分佈,透過雜訊整形(Noise-Shaping)將雜訊推往較高頻的部份,之後經由數位濾波器隔絕掉大部分的雜訊能量,使得主訊號(Signal tone)出現的低頻段範圍內可以有較佳的 SNR 結果, $\Sigma$ - $\Delta$  ADC 可以提供超過 20bits 精確程度的解析度,但容許的訊號頻率範圍 也相對的較小,通常被應用在低速音頻訊號的領域中; Successive-approximation ADC 的操作速度可以較快一些,但由於製程上的若干限制使得可達到的解析度受到限制,只能提供中高等級的解析度,然 而此種 ADC 最大的特點是在可允許的解析度範圍內,不論解析度為何,整個 ADC 內只有一個比較器(Comparator)來轉換訊號,所以使得此類 ADC 除了具備速度稍快的優勢之外,能達到低耗能(Low power)的特點是其最

主要的賣點,且多增加位元數所帶來的硬體功率消耗並不會成等比例的增加,因此 Successive-approximation ADC 常被應用於低耗能的場合,如可攜式的電子裝置,以提高電池的續航力。

| Low-to-Medium         | Medium Speed,              | High Speed,        |

|-----------------------|----------------------------|--------------------|

| Speed,                | Medium Accuracy            | Low-to-Medium      |

| High Accuracy         |                            | Accuracy           |

| ■ Integrating         | ■ Successive-approximation | ■ Flash            |

| ■ Oversampling        | ■ Algorithmic (Cyclic)     | ■ Two-step         |

| $(\Sigma$ - $\Delta)$ |                            | ■ Interpolating    |

|                       |                            | ■ Folding          |

|                       |                            | ■ Pipelined        |

|                       |                            | ■ Time-interleaved |

表 2.1 依解析度與取樣率區分 ADC 之種類[18]

圖 2.13 各種常見 ADC 的架構與取樣速度之關係

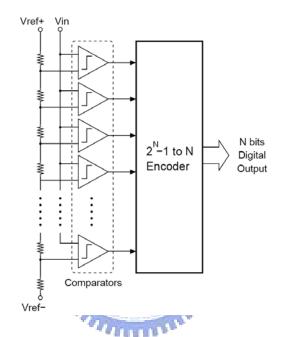

而 Flash (快閃式) ADC 是最直接也最直觀的 ADC,其使用一連串大量的比較器將輸入訊號直接解析轉換成對應的數位輸出訊號,因此非常適合在高速的應用場合中,欲達到 N-bit 的解析度就必須使用  $(2^N-1)$  個數的比較器,也因此會有大量的功率消耗以及過大的輸入寄生電容等問題,以設計積體電路的觀點來看,Flash ADC 只適合低解析度與相當高速的應用時

機;Pipelined(管線式)ADC 利用管線化平行處理的概念,將輸入訊號分級做轉換,任意時間裡每一級都不斷的在轉換訊號,使得操作速度可以較快,但仍無法達到 Flash ADC 的轉換速度,不過 Pipelined ADC 可提供高於 Flash ADC 程度的解析度,通常在 8~12 bit 而取樣率約為 100~200MHz 的應用中,Pipelined ADC 是相當好的選擇。此四種架構 ADC 的解析度與取樣速率的關係如圖 2.13 所示。

圖 2.14 基本 Flash ADC 之架構

從前面的討論中,可以知道對於我們需要的設計規格—10GS/s, 4-bit 的 ADC 來說, Flash 架構的 ADC 是最為適當的選擇,因此本論文所設計之資料轉換器對中的 ADC 即是使用 Flash 的架構。一個基本的 Flash ADC 架構簡圖如圖 2.14 所示,N-bit 的解析度需要( $2^N$ -1)個比較器(Comparator)個數;輸入類比訊號直接連接到這一連串比較器的輸入端,每個比較器將輸入訊號與分壓電阻串(Resistor ladder)所產生的參考電壓(reference voltage,  $V_{ref}$ )作比較,對每個比較器而言,若輸入訊號大於對應的參考電壓時,則該比較器輸出為邏輯"1",反之則輸出為邏輯"0",正常情況下這些比較器的輸出會是隨輸入訊號變化的溫度計碼(Thermometer code),再經

由後續的編碼器便可得到 N-bit 的數位輸出。由於 Flash ADC 是用並列式的 方式比較並轉換,每次轉換只需要一個取樣週期(或時脈週期, clock cycle) 的時間就可以得到一筆數位輸出,所以幾乎是高速應用 ADC 首選的架構。

#### 2.3.2 DAC 之各種架構

現今常見的 DAC 架構大致可區分為三類,分為電壓調變、電荷調變以及電流調變的方式,以此三種調變形式區分 DAC 之架構如表 2.2 所列。

電壓調變的 DAC 主要利用分壓電阻串將參考電壓 V<sub>ref</sub> 劃分出數個與解析度相關的類比電壓準位,再透過輸入的數位訊號作為控制開關的訊號決定出哪個位準的類比電壓訊號應被送至輸出端,該輸出的類比電壓訊號之大小即代表輸入數位碼所應該對應到的類比輸出結果,因此可達到數位轉類比的目的,但此種依賴分壓電阻產生結果的 DAC 對於分壓電阻的準確度要求必須相當的高,尤其當考慮製程中電阻可能存在的誤差量時,就會使得此種 DAC 不適用於高解析度上的設計。

電壓調變 電荷調變 電流調變

■ Resistor String

■ Folded Resistor String

■ Multiple Resistor

String

■ Charge-Redistribution

■ Binary-Weighted

Resistor

■ R-2R Based

■ Current-Mode

Binary-Weighted code

■ Current-Mode

Thermometer code

表 2.2 以調變形式區分 DAC 之種類

電荷調變式的 DAC 使用電容陣列儲存 2 的冪次方大小的電荷量,透過輸入的數位訊號作為控制開關的訊號,以控制各個電容作重置與重新分佈電荷(Charge-Redistribution)的動作,同時利用高精確度的運算放大器(OP)具備的輸入端虛短路(Virtual Short)的特性,將每次重新分佈電荷的結果

轉移到運算放大器負回授路徑的電容上,進而產生相對於輸入數位訊號的類比電壓。但實際設計上也會因製程的偏移等原因使得各個電容大小不會正好為2的幂次方的關係,造成儲存的電荷量大小產生誤差,使輸出結果受影響,且過大的電容值將會佔用相當大的晶片面積之外,也會限制可達到的轉換速度。

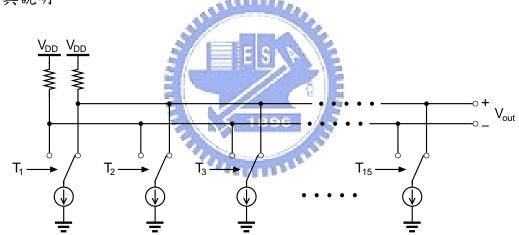

電流調變式DAC使用輸入數位訊號控制開關決定將有多少電流量會流 向輸出電阻,以便決定輸出類比電壓的大小。要產生如此形態的電流有幾 種方式,如果是採用直接二進位碼(Binary code)的控制方式的話,電流 源就必須呈現2的冪次方大小(binary-weighted current sources)的關係, 可藉由設計2的幂次方的電阻,然後在相同跨壓下產生2的幂次方的電流, 另一方面也可直接設計具備 2 的冪次方關係大小的主動式電流源,得到與 前者相同的效果,適當的控制這些電流導通至輸出就可以完成數位至類比 的轉換,但使用二進位碼的控制方式容易造成因數位碼的進位特性所導致 的輸出突波 (giltch) 現象,影響 DAC 的準確性。為解決此問題,通常使 用溫度計碼 (Thermometer code) 來控制電流開關會是較佳的選擇,討論溫 度計碼的特性,以 N-bit 為例,將有 $(2^{N}-1)$ 個數位輸入碼作為控制電流開 關的訊號,所以每個電流源的大小就可以設計成一樣 (unary current sources),且有較佳的匹配度,也可避免輸出產生突波的問題,且依此方式 設計出的 DAC 預期會有較佳的 DNL 與 INL,同時可確保輸出呈現單調性 (monotonicity) 的優點,所以對於解析度要求不太高的設計,使用溫度計 碼的方式會是較佳的解決方案。

前面所提及的架構中,電流調變式的 DAC 是目前速度最快的架構,顯然在我們所要設計的超高速—10GS/s DAC 當中,使用此種形式之 DAC 為最佳的選擇。電流源的選取當中,我們知道電流源的產生可以是被動式或主動式,被動式電流源的準確度將會受電阻的影響,所以對積體電路的設

計來說不是很好的選擇,而採用主動式電流的設計方式可以提供較高的準確度,且主動式電流的切換速度又可以較快,因此我們採用主動式電流源的電流調變 DAC 架構,此種架構的 DAC 一般都稱為 Current-Steering DAC,是目前轉換速度最快的架構,在高速、高解析度規格,Current-Steering 架構通常是設計 DAC 的首選,原因是 Current-Steering DAC 中不需要額外的放大器來做電流/電壓轉換的工作,需要的僅是一組電阻 (通常是 50Ω)來做電流/電壓轉換。而數位控制碼的選擇也就使用在低解析度設計上具備諸多優勢的溫度計碼,4bits 的情況下對應到 15bits 的溫度計碼,配合主動式電流源的設計示意圖如圖 2.15 所示,其中每個主動式電流源都提供相同大小的電流量,更詳細的電路設計以及設計上的考量將會在第三章加以分析與說明。

圖 2.15 溫度計碼式 Current-Steering (Unary Current-Steering) 示意圖

# 應用於前瞻串列式連結之 超高速資料轉換器對之設計

本章節將分析並討論此應用於前瞻串列式連結之超高速資料轉換器對 (Very High Speed Data Converter Pair for Advanced Serial Link Transceivers) 的設計,分為發送端的 DAC 與接收端的 ADC 兩部份來探討,兩者的主要設計規格都是定在每秒一百億次的取樣率且為四位元的解析度(10GS/s 4-bit DAC & ADC)。許多高速電路在設計上容易遇到的問題以及我們所使用的解決方法都將會被提及並討論,詳細的設計考量也將一一說明。

1896

# 3.1 10GS/s 4-bit 數位類比轉換器 (DAC) 之設計

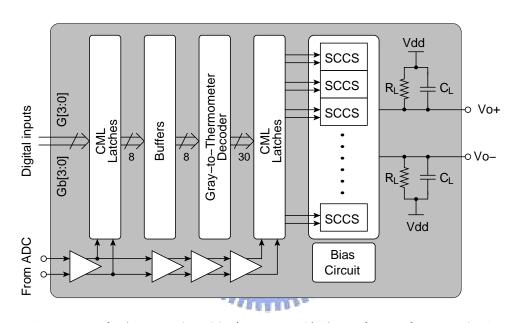

圖 3.1 顯示整個 10GS/s 4-bit DAC 的方塊圖,使用具有最快轉換速度的 Current-Steering 架構。且為了要滿足超高速數位訊號的切換,所有的數位 邏輯閘電路都是使用電流式邏輯(Current Mode Logic, CML)電路來設計。 CML 電路為全差動(fully-differential)式的架構,除了具有較佳的抗共模雜訊干擾(common-mode interference)能力之外,也具備許多適用於數位訊號高速切換的優勢,這些 CML 電路詳細的特點將會在後續的章節中說明。

DAC 的輸入先經過一排的 CML Latch 將輸入的各位元訊號取樣並同步 化,作時序上的校正 (retiming),以確保輸入訊號的正確性,再透過格雷 碼轉溫度計碼解碼器(Gray-to-Thermometer decoder)將 4-bit Gray code 轉成 15-bit Thermometer code,其中由於 CML Latch 電路缺乏對後級電路的驅動能力,因此在輸入的 CML Latch 與 Gray-to-Thermometer decoder 之間插入了 CML 的 buffer,以解決推力不足的問題。解碼後的 Thermometer code輸出再使用 15 個 CML Latch 將每個位元的訊號做同步,並用來控制輸出開關電流源電路,使輸出的 15 個開關疊接電流源可以被同時開啟或關閉,降低輸出發生突波(giltch)的可能性。

圖 3.1 超高速 10GS/s 4-bit 數位類比轉換器 (DAC) 之方塊圖

另外在轉換的過程中,訊號從輸入到輸出的轉換必定存在若干的延遲時間(delay),這些延遲的影響在高速取樣轉換的系統中顯得更為嚴重,以取樣率高達 10GS/s 的情形來說,半週期的時間只有 50ps,因此 DAC 數位電路部份的 critical path 所導致的延遲時間將非常容易超過容許的半週期時間範圍,因此在取樣時脈訊號的路徑上,我們使用常被應用在數位電路系統的 Wave-pipelining 技巧[24],在最前端輸入的 CML Latch 以及控制開關電流源電路的 CML Latch 兩者的取樣時脈訊號之間,使用了一串的 clock buffers,以補償這之間的延遲時間。而對於此種 DAC 架構影響效能最為關鍵的輸出開關電流源部份,我們採用開關疊接電流源(Switched Cascode

Current Source, SCCS) 電路來設計製作,其比一般傳統的開關電流源有更高的低頻輸出阻抗(output impedance)以及較寬的阻抗頻寬,使高頻的響應可以較佳。且整個 DAC 也都為全差動的形式,可降低共模雜訊及偶次諧波失真(even-harmonic distortion)的干擾。另外 DAC 的輸出端設計了一個on-chip 的  $50\Omega$  終端電阻,目的是為了達成高頻操作時與負載的阻抗匹配。

## 3.1.1 電流式邏輯 (Current Mode Logic, CML) 電路

由於我們的設計必須操作在非常快的速度,所以數位電路的選擇上使用標準的 CMOS 邏輯電路並無法勝任如此高速切換的需求,因此我們使用高速電路設計中常見的電流式邏輯電路(Current Mode Logic, CML) [25][26][27]做為數位電路設計的基本邏輯閘。

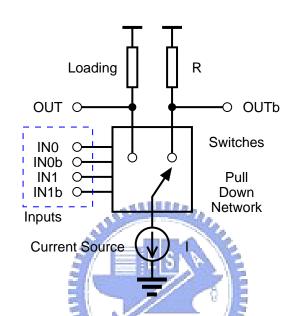

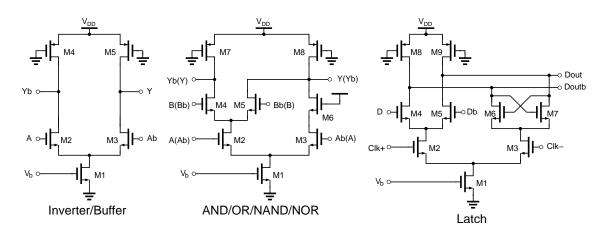

簡單的 N型 CML 電路結構的示意圖如圖 3.2 所示,具備一固定的電流源,同時為全差動式(fully differential)的架構;利用差動對(differential pair) 結構的電路作為開闢(switches)並根據輸入訊號的狀態來選擇將電流源 I 切換到輸出正端還是負端的提升電阻(pull up resistances, R),被切換流經電流的輸出端將產生  $\Delta V = I \times R$  的壓降,邏輯上來看待就如同低準位的輸出狀態,而另一端輸出由於沒有電流流經,故輸出為  $V_{DD}$  的值,也就是高準位的邏輯狀態,所以單端輸出得到的擺幅(swing)大小為  $\Delta V$  ,因此適當的設計電流源 I 與負載值 R 的大小可得到所需的擺幅;可以知道的是,CML電路所產生的擺幅大小無法達到軌對軌(rail-to-rail)的程度,也就是無法產生  $V_{DD}$  到  $V_{SS}$  之間如此大小的擺幅,且由於輸入是透過差動對的方式來切換電流源,因此差動輸入訊號的差值只需達到  $\sqrt{2}$  倍的過驅動電壓(overdrive voltage,  $V_{ov}$ )大小時,就可使該差動對發生全切換(fully switched),將電流源完全的引導至某一邊的輸出,故可知 CML 電路的輸入和輸出都是可以在比較小的擺幅情況下操作,使得當訊號轉態切換從低準

位邏輯拉升至高準位邏輯或是由高準位邏輯轉換到低準位邏輯時所需的復原(recovery)時間可以較短,使操作速度可以較快。另外 CML 是透過切換電流的方式來得到電壓輸出的邏輯結果,電流的切換速度明顯快得許多,使得 CML 在高速數位電路的應用中更具吸引力,且相對的 CML 電路所消耗的功率也較低,這些都是 CML 本身固有的特色。

圖 3.2 基本電流式邏輯 (Current Mode Logic, CML) 電路之結構

在我們設計的整個 DAC 與 ADC 中,數位電路部份的邏輯都是使用 CML 來設計。圖 3.3 顯示了幾個我們使用到的 CML 電路,包含 Inverter/Buffer、AND/OR/NAND/NOR 以及 Latch,其中可看出 CML 的 Inverter/Buffer 就是一個簡單的差動放大器結構,只是這裡的差動對輸入是處理大訊號(邏輯準位)的情況,所以是用作開關使用,而不是訊號放大器的特性;而 CML AND/OR/NAND/NOR 為同一種電路,基本上該電路所要執行的邏輯函數為何,是由輸入訊號所給入的位置(A, Ab, B, Bb 給定的位置)與輸出訊號所抓取的位置(Y, Yb 抓取的位置)所決定,每組差動對的電晶體也是用作開關使用,其中我們多加入了一個恆為導通狀態的dummy switch M6,目的是為了使兩端輸出往下看都可以看到相同數量的 MOS 電晶體疊接,可使輸出訊號較為匹配,電路也顯得較為對稱[28]。

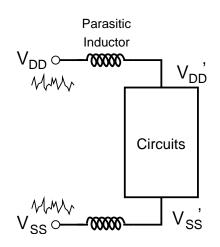

圖 3.3 各種常見之 CML 電路

另外值得一提的是 CML 電路因為具備固定的電流源,因此不論輸入訊 號的狀態為何,從 $V_{DD}$ 到 $V_{SS}$ 之間總是有一固定的電流在流動,因此當發 生邏輯轉態時產生的瞬間電流變化量並不明顯,這將使得電路中常見的電 源跳動 (power/ground bounce) 問題可以大幅降低,反之傳統標準 CMOS 邏輯電路會在轉態時產生瞬間電流從 VDD 或 VSS 對負載作快速的充放電, 使得瞬間的電流變化在 VDD 或 VSS 上出現,造成電源端產生明顯的跳動, 且此跳動的頻率與輸入訊號變化的頻率成正比,當考慮實際電路中電源端 的長導線所寄生的電感(parasitic inductor)或是實體晶片打線(wire bonding) 的寄生電感時,由於電感的跨壓與電感大小以及電感上瞬間電流變化量成 正比  $(V_L = L \frac{di}{dL})$ , 此處瞬間電流變化量就可以看成是電源跳動的部份,因 此可知當輸入訊號變化得越快,電源端的擾動變化也越快,造成寄生電感 上的跨壓也就越大,使得實際電路所接受到  $V_{DD}$  與  $V_{SS}$  的電壓大小偏離原 本供應的值,此現象如圖 3.4 所繪。因此可知,對於 CML 與標準 CMOS 邏輯電路而言,當輸入訊號頻率很高時,CML 電路產生的擾動會比 CMOS 邏輯電路還小得許多,再次凸顯出 CML 應用於高速電路的優勢。不過也由 於 CML 的固定電流源,使得 CML 電路所消耗的功率與操作頻率無關,不 同於 CMOS 邏輯電路的消耗功率與操作頻率成正比,但 CML 電路幾乎都 是應用在高速的場合中,所以此問題的影響程度並不明顯。

圖 3.4 電源擾動 (power/ground bounce) 經由寄生電感對電路產生之影響

#### 3.1.2 數位電路之設計

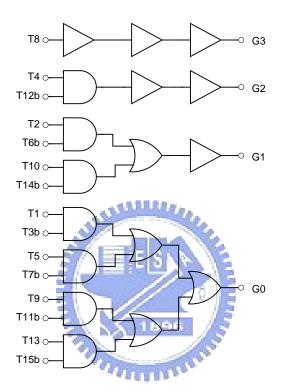

DAC 最主要的電路部份就是中間解碼器的核心,而基於實際測試時的考量,整個測試晶片的設計將會是以 ADC 串接 DAC 的方式以利於量測(詳細原因將在第四章做說明),且由於 ADC 編碼電路的編碼方式是使用較適合高速電路的 Gray code (理由將在後續作說明),因此 DAC 必須接受 ADC輸出的 Gray code 再進行解碼。另外輸出碼的形式使用先前第二章分析討論過可以降低 glitch error 以及得到較佳 DNL/INL 結果的 Thermomerter code,因此 DAC 的數位電路部份便是將輸入的 Gray code 轉換成 Thermometer code,再控制 15 個電流源電路切換電流至輸出電阻,產生對應於輸入數位訊號的類比輸出電壓。在這樣的安排設計之下,Gray-to-Thermometer decoder將 4-bit 的輸入轉換成 15-bit 的輸出,所以第一級 CML Latch 電路就必須設計能夠推動 15 組的解碼電路,這樣將會使得原本不具備太大驅動能力的CML Latch 消耗相當大的功率,所以我們在 CML Latch 與Gray-to-Thermometer decoder之間使用了 CML 的 buffer 來解決此問題。為了達到高速切換能力以及降低電源抖動的干擾,解碼器的數位邏輯電路都是使用 CML 為基本 cell 所組合而成。

4-bit Gray-to-Thermometer decoder 由 15 組的組合邏輯 (combinational

logic)電路所構成,每組電路將[G3:G0]的輸入分別轉成[T1:T15]的輸出, 且都只使用 CML AND/OR (NAND/NOR)的邏輯運算,為了不希望導致過 大的延遲,整個 Gray-to-Thermometer decoder 都設計成只有兩個 gate delay, 所以某些組的電路會使用具備 3 輸入的 CML AND/OR (NAND/NOR) 邏輯 電路,至於這 15 組詳細的邏輯電路就不在此贅述。

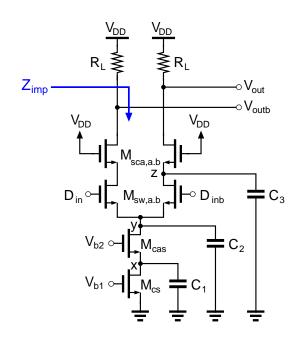

#### 3.1.3 輸出電流源之設計

在 Current-Steering DAC 中,類比電路的部份主要由開闢加上電流源所構成,而電流源的特性會直接影響 DAC 靜態及動態參數的好壞,例如若是電流源大小彼此不匹配,則會導致 DAC 顯現較差的 DNL 及 INL,也就是不夠線性,且如果電流源具備不夠的輸出阻抗,則 DAC 操作在較高的頻率下會造成動態參數的衰減[29][30][31],因此對於 Current-Steering DAC 而言,電流源是最為關鍵的電路,因此選擇適當的電流源架構將有助於 DAC 之最佳化設計。

在佈局電路對稱的前提下,基本上每個電流源所引出的電流大小會相當接近,不過由於製程上的未知偏移還是會使電流源之間產生若干的誤差,對於此種錯誤可以使用校正(calibrate)電路的方式來修正電流源的誤差,例如具備開關電流源演算法(Switched-Current Algorithmic)的Current-Steering DAC [18],利用記憶電流源(Memory cell)的方式儲存正確的偏壓大小,再透過開關切換將正確的偏壓送至真實影響輸出訊號的電流源,可降低電流源大小誤差的程度;另外使用 DEM(Dynamic Element Matching)[32]方式切換電流源的 DAC 可避免某些本身存在大量誤差的電流源總是被選擇到,使整體的精確度可獲得提升。然而透過電路修正技巧確實可得到高精確度的電流源,可設計實現高解析度的 DAC,但這些機制都不適用於非常高速切換的環境下,且由於高速、中低解析度 DAC 的設計

中,相對電流源準確度可容許的誤差範圍也較大,因此在我們 4-bit DAC 的設計中,輸出 15 個電流源的部份,將晶片佈局設計時盡量使走線及元件對稱匹配,期望可減輕降低可能發生的電流源不匹配問題。

另一方面,電流源有限的輸出阻抗(finite output impedance)也會大大地影響 Current-Steering DAC 的效能,實際開關電流源所具備的輸出阻抗是與輸入訊號相關的(signal-dependant)且會因電路寄生電容的影響使得輸出阻抗隨輸入訊號頻率增加而降低。這裡我們要更一般化的討論在高頻時電流源的輸出阻抗與輸入頻率變化的關係,考慮一般簡單的開關電流源如圖 3.5(a)所示,電晶體  $M_{CS}$ 操作在飽和區(saturation region)產生固定電流且經由  $M_{SW,a.b}$  根據輸入訊號切換選擇將此電流流經  $V_{out}$  或是  $V_{outb}$  的輸出;此種簡單的電流源能夠提供的輸出阻抗,也就是從輸出端看入的阻抗  $Z_{imp}$ ,

計算可得:  $Z_{imp} = (1 + g_{msw}r_{osw}) r_{oss} / sC_1 = g_{msw}r_{osw}r_{oss} / sC_1 + \frac{j\omega C_1}{g_{msw}}$   $Z_{imp} = (1 + g_{msw}r_{osw}) r_{oss} / sC_1 = g_{msw}r_{osw}r_{oss} / sC_1 + \frac{j\omega C_1}{g_{msw}}$   $Z_{imp} = (1 + g_{msw}r_{osw}) r_{oss} / sC_1 + \frac{j\omega C_1}{g_{msw}} / sC_1$

圖 3.5(a)一般簡單之開關電流源與輸出阻抗(b)輸出阻抗之頻率響應其中 C<sub>1</sub>等效為節點 x 到地所看到的總寄生電容。(3.1) 式顯示阻抗與頻率

為單一極點(pole)與零點(zero)的關係,極點頻率  $f_p = \frac{1}{2\pi r_{ocs}C_1}$  且零點頻率  $f_z = \frac{g_{msw}}{2\pi C_1}$ 。在一般的設計之中, $\frac{1}{r_{ocs}} < g_{msw}$ ,因此輸出阻抗的頻率響應如圖 3.5(b)所示。低頻時的等效輸出阻抗約只有  $g_m r_o^2$ ,當頻率超過  $f_p$  時輸出阻抗的響應開始變小,直到超過  $f_z$  時輸出阻抗降到約只剩  $M_{CS}$  的小訊號輸出阻抗  $r_{ocs}$ ,因此很明顯並不足以應用在相當高速的場合中,而且此種簡單的電流源電路會因輸入訊號切換差動對  $M_{SW,ab}$  之瞬間使電晶體通道內跑出的電荷導致圖 3.5(a)節點 x 產生相當程度的電壓變化( $\Delta V_x$ ),致使  $M_{CS}$  定義出的電流源大小因其  $V_{DS}$  的變化發生通道長度調變的效應(channel-length modulation),造成電流源的不穩定。

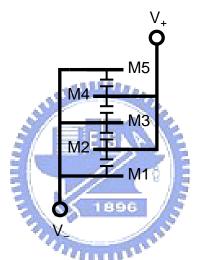

為了解決這些問題,我們使用開關疊接電流源(Switched Cascode Current Source, SCCS)[29],如圖 3.6 的架構來設計,在主要電流源電晶體 M<sub>CS</sub>上疊接 M<sub>CAS</sub>,並在差動輸入開闢 M<sub>SWab</sub>的上方也使用兩個恆為導通狀態的電晶體 M<sub>SCA,ab</sub>[33],由於開闢疊接電流源使用前級 CML Latch 的輸出作為控制訊號,而前級 CML Latch 因 10GHz 的高頻取樣訊號經由寄生電容所產生的時脈饋入(feed-through)效應,使得 CML Latch 輸出的數位訊號上帶有高速取樣訊號的擾動成分,因此若將此數位訊號直接用來切換電流源開闢電晶體 M<sub>SW,ab</sub>,則此受到干擾的控制訊號源將會經由 M<sub>SW,ab</sub>的寄生電容 C<sub>GD,SW,ab</sub>耦合(couple)至輸出端,使最後輸出的類比電壓訊號上也帶有 10GHz 成分的擾動,因此藉由開闢 M<sub>SW,ab</sub>上方疊接電晶體 M<sub>SCA,ab</sub>的作用除了可降低此一干擾。此外也由於整個電流源設計的輸出共模準位在偏高的情況下,使得 M<sub>SCA,ab</sub>操作在飽和區,進一步使得整個電流源的輸出阻抗可再增加約(8<sub>mme</sub> F<sub>cme</sub>)倍。

圖 3.6 開關疊接電流源 (Switched Cascode Current Source, SCCS) 電路

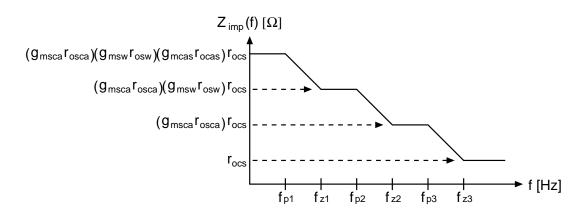

計算圖 3.6 開關疊接電流源的輸出阻抗,從輸出端往內看入的阻抗  $Z_{imp}$  約等於:

$$Z_{imp} \cong (g_{msca}r_{osca})(g_{msw}r_{osw})(g_{mcas}r_{ocas})r_{ocs} \frac{1 + \frac{j\omega C_3}{g_{msca}}}{1 + j\omega C_3r_{osw}} \frac{1 + \frac{j\omega C_2}{g_{msw}}}{1 + j\omega C_2r_{ocas}} \frac{1 + \frac{j\omega C_1}{g_{mcas}}}{1 + j\omega C_1r_{ocs}}$$

(3.2)

其中  $C_1$ 、 $C_2$ 與  $C_3$  各為節點 x、y、z 到地的等效寄生電容,式中顯示出經由雙重疊接(cascode)( $M_{cas}$ 與  $M_{sca,a,b}$  之疊接)的作用使得電流源的輸出阻抗被放大約  $(g_m r_o)^2$ 倍,且為三個極點與零點的響應,一般設計情況下對應的阻抗頻率響應如圖 3.7 所示,可看出此種形式的電流源電路不論是低頻或高頻時都比前述的簡單形式電流源具有更高的輸出阻抗,對整個 DAC 而言可得到較佳的 SFDR 響應[29],此外原本容易因輸入差動對開關  $M_{SW,a,b}$  切換造成的通道電荷逸出對節點 x 的電壓擾動也因疊接  $M_{CAS}$  的作用使得節點 x 產生的電壓變動量降低約為沒有疊接時的  $(g_m r_o)$ 倍,使得電流源電晶體  $M_{CS}$  獲得較穩定的  $V_{DS}$  電壓,進而產生較穩定的電流,因此使用疊接技巧對電流源電路的穩定性及準確性都可以獲得相當程度的提升。

圖 3.7 開關疊接電流源輸出阻抗之頻率響應

圖 3.8 顯示經由解碼電路輸出 15bits 的 Thermometer code 再經由 CML Latch 後所連接控制的 15 組開關疊接電流源電路陣列(SCCS Array),其中輸出端的負載是設計成 on-chip  $50\Omega$  的電阻,不過實際量測由於量測儀器也提供的  $50\Omega$  輸入阻抗,所以 DAC 的輸出實際上是 double termination 的方式,因此單位電流源被切換流至的輸出負載會是  $50//50=25\Omega$  的電阻值,而必須根據  $25\Omega$  double termination 的結果來設計單位電流源的電流量,使整個 DAC 的輸出可達到欲產生的擺幅(swing)大小。

圖 3.8 開關疊接電流源電路陣列 (SCCS Array)

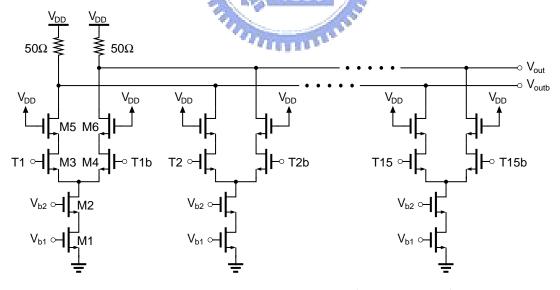

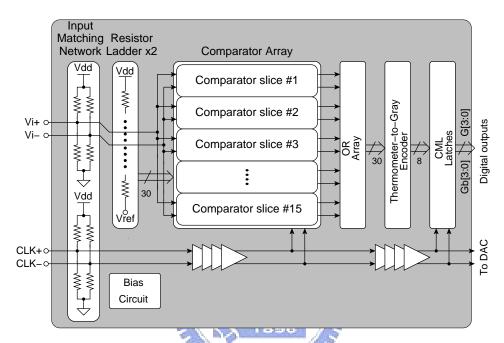

# 3.2 10GS/s 4-bit 類比數位轉換器 (ADC) 之設計

10GS/s 4-bit ADC 的方塊圖如圖 3.9 所示,誠如前一章所討論到的,若要設計相當高速且中低解析度的 ADC,則 Flash 架構會是最好的選擇,因此圖 3.9 所示的方塊圖正是 Flash 形式的架構。

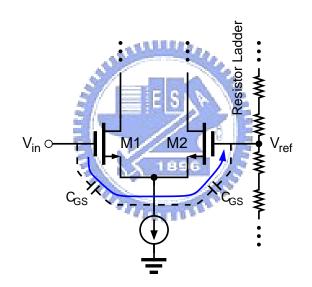

圖 3.9 超高速 10GS/s 4-bit 類比數位轉換器 (ADC) 之方塊圖

首先ADC的類比訊號輸入端與取樣時脈訊號的輸入端都是由一組分壓電阻所構成的網路,此組分壓電阻除了提供整個 ADC 輸入為 50Ω 的阻抗,以達成良好的匹配,使高頻訊號可以順利的輸入到電路當中之外,並將輸入端後級的電路偏壓在設計的共模準位(common-mode level)。為了要達到如此高速操作的需求,在系統層次的設計上,我們使用了幾種方式來解決這些可能發生的問題。首先對於 Flash ADC 而言的輸入級比較器電路,是相當關鍵的部份,為了必須能夠處理承受高達數 GHz 的高速輸入訊號,所以比較器必須達到相當增益且足夠頻寬需求之設計,顯然可知只使用一般的 latch-comparator[17]是不足以應付這樣的應用需求,因此在我們比較器電路的設計當中,使用了多級串接(multi-stage cascaded)的方式作設計,使

得比較器增益與頻寬的需求可同時被滿足。而構成比較器的前置放大器(Pre-Amplifier)電路中,我們使用能有效提升放大器增益頻寬乘積(gain-bandwidth product, GBW)的主動式負回授(Active negative feedback)放大器[34],以使得設計頻寬高達 5GHz 以內的類比輸入訊號都能夠被比較出結果並放大最後量化解析出正確的數位訊號;而在數位編碼器電路的設計方面,採用格雷碼(Gray code)的編碼方式,透過 Gray code 的特點可降低錯誤碼的發生機率。且為了要滿足超高速數位訊號的切換,所有的數位邏輯閘電路與 DAC 相同也都是使用 CML 電路來設計,達到最快的切換速度並降低 power/ground bounce 的干擾。

同樣由於輸入訊號經比較、放大並轉換的 propagation delay 時間以及比較放大後的數位訊號經過數位電路編碼的延遲時間也都相當容易超過半週期的 50ps,因此在 ADC 的取樣時脈訊號的路徑上,我們也使用了一連串的clock buffers 作 Wave-pipelining 的機制。將比較器的輸出以及整個 ADC 的最後輸出各使用一組電流式邏輯的 Latch (CML Latch)來取樣訊號,這中間編碼器的延遲時間就利用一串的 clock buffers 來做補償,將輸入的高速取樣訊號分級管線化傳遞下去,使得中間編碼器的延遲時間可以盡量被固定住,以降低 clock skew 對取樣時序的造成的負面影響,進而達到補償延遲過大的目的。整個 ADC 都為全差動的形式,可降低共模雜訊干擾或是電路的偶次諧波失真的影響。

大致說明整個 ADC 架構的主要特點之後,以下就分別將對各個比較主要 Block 的設計加以詳細說明。

# 3.2.1 分壓電阻串 (Resistor Ladder)

在 Flash ADC 中,對每個比較器都必須提供一個直流的參考比較對象, 通常這些參考電壓準位可以由一連串串聯的電阻所得到,根據所設計的解 析度 N 將滿刻度電壓  $(V_{FS})$  範圍劃分出  $(2^N-1)$  個參考準位,供給輸入級  $(2^N-1)$  個比較器做比較,以得到輸入訊號與參考電壓準位比較之結果。對於每個分壓電阻值的選取,討論如下:

考慮圖 3.10 為一輸入訊號  $(V_{in})$  與某參考電壓經由差動對 (differential pair, M1 and M2) 電路作比較的簡圖,理想上分壓電阻串產生的參考電壓  $(V_{ref})$  應為固定不變的電壓值,然而實際上變動的輸入訊號將會透過 M1 及 M2 寄生的  $C_{GS}$  電容去耦合 (couple) 影響到參考電壓的值,此行為稱之為訊號的饋入  $(signal\ feedthrough)$ ,尤其當輸入訊號頻率越高時,經由寄生電容 feedthrough 產生的干擾越明顯,使參考電壓受影響的程度也就越大。

圖 3.10 變動的輸入訊號經差動對之寄生電容耦合 (couple) 至分壓電阻串

可經由等效電路的化簡得知在分壓電阻串最中間的點受影響的程度會最大,更一般化的表示這個現象,在[20]及[35]中有詳細討論到,並得到式(3.3)的結果,其中 $V_{mid}$ 表示分壓電阻串最中間的點受到 feedthrough 影響而偏移原本應有之大小的差值, $f_{in}$  為輸入訊號的頻率,R 代表整個分壓電阻串所有電阻串聯的總和, $C_{tot}$ 表示由輸入端 couple 到分壓電阻串上 Vref端點的的總寄生電容值,簡單的一個差動對從輸入到參考電壓節點看到的coupling 電容為 $(1/2)C_{GS}$ ,若有 n 個並排的差動對連接到分壓電阻串上各自

的參考電壓節點,則總輸入端看到的 coupling 電容值為 $n(1/2)C_{GS}$ 。

$$\frac{V_{mid}}{V_{in}} = \frac{\pi}{4} f_{in} RC_{tot} \tag{3.3}$$

由式(3.3)可知,受影響的參考電壓之偏移量( $V_{mid}$ )與 R 成正比,意即若希望 feedthrough 影響量小的話,則 R 值的選取就必須較小,但相對較小的 R 值會使得分壓電阻串上流經較大的電流,產生較大的功率消耗。經由進一步的推導可計算出參考電壓偏移量( $V_{mid}$ )與解析度(N)、輸入訊號頻率( $f_{in}$ )以及總輸入端 couple 電容值( $C_{tot}$ )之間對分壓電阻串最大總電阻值( $R_{ladder,max}$ )之間的關係,如式(3.4),其中把( $V_{mid}/V_{in}$ )寫成( $\phi/2^N$ ) 是為了將 feedthrough 的影響量換成以 LSB 為單位的表示方式,如此一來 $\phi$ 的值即為設計者對於分壓電阻串最中間的點所允許之最大的 feedthrough 量,通常可將 $\phi$ 設定為 1 個 LSB 的大小,去求得整個分壓電阻串所能使用的最大 R 值,值得一提的是,設定 $\phi=1$ LSB 計算得到的總電阻 R 將是最差情況(worst case)下的討論,也因此設計時假定 $\phi=1$ LSB 去計算  $R_{ladder,max}$ 將可得到較為妥善的結果。

$$R_{ladder,\text{max}} = \frac{4\frac{V_{mid}}{V_{in}}}{\pi f_{in}C_{tot}} = \frac{4\phi}{\pi 2^{N} f_{in}C_{tot}}$$

(3.4)

## 3.2.2 比較器電路之設計

## 3.2.2.1 多級串接放大器的設計考量

對於我們的比較器電路設計,其至少必須要能夠提供約25倍也就是約28 dB 的增益,此值的獲得是將最小的一個LSB 的大小,也就是約25mV,比較放大到600mV以上的擺幅(swing),所以計算可得將近需要25倍的增益;另一方面可估計輸入訊號最大的頻率約為5GHz,也就是我們的應用

中,必須要設計出一個具有 25V/V 增益以及 5GHz 頻寬的比較器電路,顯然要達到這樣的設計目標,只使用單一級電路如 latched-comparator 的方式是無法達成的,單一級放大器的電路要同時滿足夠高的增益以及動輒數GHz 的頻寬,除了會有功率消耗相當大的問題之外,即使達到頻寬的需求,卻也很容易使得電路的增益變得相當低。所以為了解決此問題,較合適的方法是使用多級串接的放大器(multi-stage cascaded amplifier)來達成,以數級相同或不同的放大器串接,每一級提供適當大小的增益以及相對足夠的頻寬,就會比較容易達成增益與頻寬的設計目標。這裡我們要討論的是,在滿足設計目標的需求下,如何選取串接放大器的級數以及怎樣形式的放大器增益級(gain stage)電路可以有較佳的功率效益(power efficiency)和較為實際、可實現的放大器增益頻寬乘積(gain-bandwidth product, GBW)。尤其是我們的設計必須要達到 10GHz 的超高速而高速電路的設計往往會消耗掉驚人的功率,所以這些設計考量便顯得更為重要,因此能對多級串接的放大器做功率的最佳化,是在架構設計階段中不可或缺的考量。

常用放大器的選擇上,可以使用一階(the first-order)或二階(the second-order)的形式來設計,一階及二階電路的轉移函數(transfer function)顯示在表 3.1 中,此兩種形式的放大器各有較為適用的場合,我們主要就針對此兩種形式的放大器做探討,並選取出最適合我們設計規格所需的放大器類型以及放大器之架構。

表 3.1 一階及二階電路轉移函數之比較

| The first-order                             | The second-order                                                        |  |

|---------------------------------------------|-------------------------------------------------------------------------|--|

| $H(s) = \frac{A_0}{1 + \frac{s}{\omega_0}}$ | $H(s) = \frac{A_0 \omega_n^2}{s^2 + 2\zeta \omega_n s + \omega_n^2}$    |  |

| $A_0$ : DC-gain $\omega_0$ : -3dB bandwidth | $A_0$ : DC-gain $\omega_n$ : Natural frequency $\zeta$ : Damping factor |  |

連續串接(cascade)多級相同的放大器,串接起來後整體放大器的頻寬( $BW_{CA}$ )與單一級放大器所提供的頻寬( $BW_S$ )之間的關係可以推導 [34][36][37]成:

$$BW_S = \frac{BW_{CA}}{\sqrt[2^m]{\sqrt[N]{2} - 1}} \tag{3.5}$$

其中N表示串接放大器所使用的級數,m代表使用放大器的類型為一階或是二階的形式,m=1為一階的情況,而 m=2 則為二階的情形;式(3.5)的結果中,要注意的是在二階情況的推導中,是假設該二階的放大器具有最大平坦響應(maximally-flat response)的特性,也就是 $\zeta = \sqrt{2}/2$ 的情形。

(3.5)式明確指出了多級串接放大器提供的頻寬與單一級放大器頻寬之間的關係,故可知若欲設計之目標的為 $BW_{CA}$ 定值,當串接的級數越多,則每一級放大器的頻寬( $BW_s$ )就必須設計得越大。而對於一個放大器來說,頻寬增益乘積(gain-bandwidth product, GBW)在相同的功率下趨近一個定值(constant),因此只從頻寬的關係來討論是不足以描述某種架構的放大器形式在某一N值的選擇下,計算得到每一級所需要的頻寬是否貼近真實電路設計時可實現的情況,所以為了更一般化得到放大器確切能達到的增益跟頻寬,將(3.5)式改成用增益頻寬乘積來表達會是較好的方式,可直接評估出可達到的 GBW 是否較為實際。以 GBW 改寫後得到的結果如式(3.6)所示[38][39],其中 $GBW_s = A_s \times BW_s$ ,為單一級放大器的 GBW, $A_s$  為單一級放大器的低頻增益(BC-gain),BC-Qain),BC-Qain),BC-Qain),

$$GBW_S = BW_{CA} \times \frac{\sqrt[N]{A_{CA}}}{2\sqrt[N]{\sqrt[N]{2} - 1}}$$

(3.6)

將(3.6)式對 N 微分,可得到構成某多級串接放大器的每一級放大器最小

所需  $GBW_S$  所對應到的最佳化級數  $(N_{opt})$  的結果 [36] ,如下式 (3.7):

$$N_{opt} = \frac{\ln 2}{\ln \left(-\frac{\ln A_{CA}}{\ln^{\frac{2^{m}}{\sqrt{2}}} A_{CA}}\right)}$$

(3.7)

也就是說,使用  $N_{opt}$  的級數所設計的多級串接放大器,則每級的放大器所需的 GBW 會是最小的結果,可用來評估計算得到的 GBW 在某特定製程下是否為實際可實現的要求。另外使用最小要求 GBW 的設計可以減輕設計時的困難度;但如果單純只依  $N_{opt}$  的結果來設計多級串接放大器是不夠完善的,為了做最佳化的設計,除了 GBW 的變化之外,還有必須要考慮到的因素是多級串接放大器使用各種不同的級數與整體功率消耗 (power)之間的關係。簡單分析一個 CMOS 的共源極電壓放大器 (common-source amplifier),考慮放大器的轉導(transconductance)為  $g_m$ ,輸出負載電容為  $C_L$ ,偏壓電流為  $I_D$ ,這樣的放大器近似的增益頻寬乘積(GBW)可寫成式 (3.8) 的形式:

$$GBW = \frac{g_m}{C_L} \propto \frac{\sqrt{I_D}}{C_L} \tag{3.8}$$

因此從(3.8)式可以概略的估計出連續串接N級的多級放大器,可能的總功率消耗(Power)約可近似寫為[38]:

$$Power = \alpha \times N \times (GBW)^{2}$$

(3.9)

其中 $\alpha$  為與電路相關的某個正比係數 (proporational factor), 將 (3.9) 式對  $\alpha$  作 normalize, 可得:

$$Power = N \times (GBW)^2 \tag{3.10}$$

因此可利用(3.10)式的結果去更進一步描述多級串接放大器可能的總功率

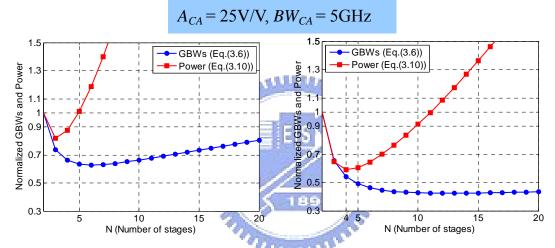

消耗。由(3.6)與(3.10)式的結果,可畫出多級串接放大器其  $GBW_S$ 與 Power 對不同級數 N 之間個關係圖。我們分別以一階及二階放大器的情況下進行討論,且給定我們的設計條件:整個多級串接放大器構成的比較器須要提供至少約 25 倍( $A_{CA}=25V/V$ ),且至少要有超過 5GHz 的頻寬,即  $BW_{CA}=5$ GHz;套入這些條件,進行模擬並將模擬得到之  $GBW_S$ 與 Power 的結果各自對 N=2 時的  $GBW_S$ 與 Power 做正規化 (normalized),畫出正規化後的  $GBW_S$ 與 Power 對級數 N 的結果如圖 3.11(a)的一階放大器情形與3.11(b)的二階放大器情況所示。

(a) With the first-order amplifiers (b) With the second-order amplifiers 圖 3.11 模擬之 *GBWs* 與 *Power* 對 N 的關係圖(對 N = 2 做正規化)

從圖 3.11(a)一階放大器的設計情形的關係可看出,導致有最低  $GBW_S$  的串接級數之 N 值為 6,然而此時對應到 Power 曲線的結果卻是一個較大功率消耗的情形;即使在同一張圖中具有最低功率消耗時之 N 值所對應到的  $GBW_S$  大小,此  $GBW_S$  的值對於一個一階放大器的設計情形卻也是一個無法實現的值。顯然一階放大器的設計不是個良好的設計方式。

另一方面圖 3.11(b)二階放大器的設計情況中,導致有最低  $GBW_S$  的串接級數之 N 值為 13,而串接如此多數級的放大器會使得每一級只需約 2 倍 (2V/V) 大小的增益,這種每級較低增益的放大器 (low-gain-per-stage) 連

續串接將非常容易使得雜訊(noise)被快速的累積(accumulate),在已知有關多級串接放大器設計的文獻[34][37][38]上,一般都建議設計的級數不超過5級才是較適當的選擇。此外圖 3.11(b)中也可以清楚的看出當 N 超過 5 之後,整個多級串接的放大器其 Power 曲線的變化呈現相當驚人的成長幅度,更加顯示出過多級數所造成的負面影響。且可看出當 N > 5 之後  $GBW_S$  曲線的變化相對並不大,可知 Power 的變化比  $GBW_S$  的變化來得明顯,因此我們根據 Power 的曲線找出導致有最低功率消耗時的 N 值,當 N = 4 時,對整個多級串接的放大器來說,可以有最低的功率消耗,且  $GBW_S$  的曲線在 N = 4 與 N = 5 的差異也不會變化太大,且以 N = 4 作設計相較於 N = 5 的設計可稍加提高每一級的增益,可對 noise 累積的問題有更好的降低效果。

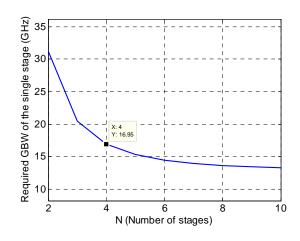

且考量到我們所設計的 ADC 將需要相當多數的比較器及放大器,為了符合超寬頻的設計情形下,每個放大器必然需要具備足夠大的頻寬,勢必會消耗可觀的功率,因此以功率消耗的觀點作為級數 N 的選取依據,應是適當的設計理念。在這裡我們便選取 N=4 的設計級數作為整個多級串接放大器所需的級數。根據 N=4 代入式 (3.6),而其他參數條件不變,得到每一級放大器最小所需的 GBW 約為 17GHz,如下圖 3.12 所示。

圖 3.12 N = 4 時對應至所需之 GBW<sub>S</sub> 約為 17GHz

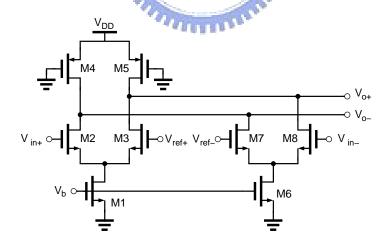

#### 3.2.2.2 Gilbert-Cell

對Flash ADC 而言,輸入級比較器電路是前端類比電路中最為關鍵的部份。在超高速的比較器當中通常不會使用太複雜的電路架構,所以我們使用簡單的差動對來設計高速比較器的電路,此外為了達成全差動形式的訊號比較,所以我們使用兩組具有相同負載的差動對來達成,且為開迴路(open-loop)的形式,更適合於高速比較的應用,電路如圖 3.13 所示。此種形式的電路在射頻(Radio Frequency, RF)通訊積體電路的設計中也常被稱為 Gilbert-Cell。在設計上,M2、M3 及 M7、M8 的寬長比(W/L ratio)會設計成一樣,且 M1 的寬長比也必須與 M6 相同,才能進行對稱的比較。在這樣的設計下,可知輸出對輸入的轉換關係可寫成

$$V_o = g_{m2,3} R_{on4,5} ((V_{in+} - V_{ref+}) - (V_{in-} - V_{ref-}))$$

(3.11)

其中 $R_{on}$  表示負載 M4 及 M5 的等效阻抗,式(3.11)指明出此電路的功能正是比較出輸入訊號與參考訊號的差值,並把該差值結果放大 $(g_{m}R_{on})$ 倍。

圖 3.13 輸入級比較器電路 (Gilbert-Cell) [40][41][42]

實際設計的考量上,由於所設計的 ADC 解析度為 4bits,在  $V_{FS}$  單端輸入為 400 mV 的情況下,得到的一個  $V_{LSB}$  大小為 25 mV,而輸入訊號的頻率將會高達數 GHz 的範圍,因此這樣的情形下,為了能順利正確的比較出

結果,此 Gilbert-Cell 較為適當的設計考量是電路的頻寬會較增益來得重要,加上此電路是整個 ADC 的輸入級,也必須注意到線性度(linearity)的問題,所以我們將 Gilbert-Cell 設計為具備低增益且超寬頻(low-gain and wide-bandwidth)的特性,使得輸入數 GHz 頻率範圍內的訊號都可被比較出結果。在這樣的設計下,Gilbert-Cell 輸出的最小差值訊號約為 1 個 LSB 的大小,這些差值可再經由後級連續串接的寬頻放大器作用,在很短的時間將微小的差值放大成數位電路可以判別的邏輯準位訊號。

由於 Gilbert-Cell 設計成低增益且超寬頻的特性,因此我們必須多考慮電路雜訊(noise)可能產生的干擾,分析圖 3.13 Gilbert-Cell 電路中單位頻寬輸出的雜訊電壓(noise voltage per unit bandwidth, $\overline{V_{n,out}^2}$ )約等於:

$$\overline{V_{n,out}^2} \cong 8kT \left(2\gamma g_m R_{on}^2 + R_{on}\right) \quad (V^2/Hz)$$

(3.12)

其中只考慮佔雜訊成份中絕大多數的熱雜訊(Thermal noise),式子中 $k=1.38\times10^{-23}$ (J/K)為波兹曼常數(Boltzmann constant),T 為絕對溫度,單位為°K,一般室溫下 $T\cong300$ °K, $\gamma$  為 MOS 的製程參數, $g_m$  為輸入差動對 M2、M3 及 M7、M8 的轉導值( $g_{m2}=g_{m3}=g_{m7}=g_{m8}=g_m$ ), $R_{on}$  為負載 M4 及 M5 的等效阻抗,將(3.12)式除上電路增益的平方( $\cong g_m^2 R_{on}^2$ ),可得到單位頻寬的輸入相關雜訊電壓(input-referred noise voltage per unit bandwidth)為:

$$\overline{V_{n,in}^2} \cong 8kT \left( 2\gamma \frac{1}{g_m} + \frac{1}{g_m^2 R_{on}} \right) \quad (V^2/Hz)$$

(3.13)

在 Gilbert-Cell 所設計的偏壓條件下,我們由(3.13)式計算當 $T \cong 300$  °K 且 次微米(submicron)製程中, $\gamma$  約為 2.5(以 0.25-μm 的製程參數而言)[43]

的情形下,單位頻寬的輸入相關雜訊電壓 $\overline{V_{n,in}^2}$  約等於  $2.96 \times 10^{-17}$  ( $V^2/Hz$ ),因此在我們所關心的頻寬範圍內 (DC-5GHz),總輸入相關的雜訊電壓 (total input-referred noise voltage) 約為:

$$\overline{V_{n,in,tot}^2} = \overline{V_{n,in}^2} \times 5G \cong 1.48 \times 10^{-7} \text{ (V}^2)$$

開根號可得到總輸入相關雜訊電壓的有效值(V<sub>rms</sub>)表示結果:

$$V_{n in tot} \cong 384.37 \ \mu V_{rms}$$

而利用 SPICE 對電路雜訊的模擬,結果顯示在 DC-5GHz 内的總輸入相關的雜訊電壓的有效值為  $311.35 \mu V_{rms}$ ,與手算的結果存在部分的差異,這主要應該是由於無法得知所使用製程之精確的  $\gamma$  值,但手算與模擬的結果也都顯示出雜訊的干擾量仍遠小於 1 個 LSB 的大小。

另外值得一提的是,圖 3.13 中差動輸入訊號( $V_{in+}$ 與  $V_{in-}$ )與差動型式參考電壓( $V_{ref+}$ 與  $V_{ref-}$ )的安排是比較好的結果[40],因為如果把  $V_{in-}$ 從 M8 的 gate 端改接到 M3 的 gate 端,而把  $V_{ref+}$ 從 M3 的 gate 端移至 M8 的 gate 端,如此將很容易因為  $V_{in+}$ 和  $V_{in-}$ 之間如果發生差值很大的情況時,會造成 M2、M3 形成的差動對中有一顆電晶體進入截止(cut-off)工作區,使得電路無法正確的表示出比較的結果,基於此一觀點,採用圖 3.13 的連接方式會是比較好的選擇。

# 3.2.2.3 主動式負回授之前置放大器 (Active negative feedback Pre-Amplifier)

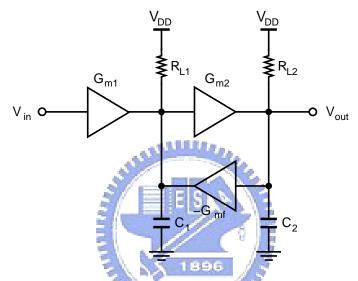

由前述的討論可知,多級串接放大器的設計中,每一級放大器的形式 選用二階的放大器來設計製作會有較具效益的功率消耗,且為了在有限的 功率消耗下設計出 GBW 較大的放大器,因此我們參考使用了 B. Razavi 所 提出的主動式負回授(Active negative feedback)放大器[34]架構,如圖 3.14 所示。此放大器主要是由高速放大器電路中廣為人知的 Cherry-Hooper Amplifier [44]改良而來的,將原本 Cherry-Hooper Amplifier 中 shunt-shunt feedback 的被動電阻性負回授改成主動式電晶體的負回授方式,能更進一步提升電路的增益頻寬之乘積 (GBW)。

圖 3.14 主動式負回授 (Active negative feedback) 之前置放大器[34]

此類超高速的放大器常見於光纖通訊系統接收端中 Limiting Amplifier 的設計上[37],光纖通訊的領域中,傳輸率動輒都在數 Gbps 的範圍之間,而 Limiting Amplifier 在光纖通訊中所扮演的重要角色就是將前端轉阻放大器(Transimpedance Amplifier, TIA)所送出微小且變化相當快速的訊號放大成具有數位邏輯準位的訊號,因此 Limiting Amplifier 的設計訴求就是能夠提供高增益且寬頻(high-gain & wide-bandwidth)的特性,另一方面,在超高速 ADC 的設計當中,所要使用到的前置放大器(Pre-Amplifier)也正是需要這樣的特性,因此對於我們的設計,使用此種寬頻的放大器將比較後的微小差值作快速的放大,使類比的差值變成數位型態的結果,應是相

當合適的選擇。

對圖 3.14 的電路作分析,可將其等效成圖 3.15 的架構, $G_{m1}$ 、 $R_{L1}$ 和  $G_{m2}$ 、 $R_{L2}$  分別代表兩級串接放大器之轉導(transconductance)及其負載,對應到圖 3.14 中, $G_{m1}$  由  $M1\sim M3$  所構成, $G_{m2}$  由  $M6\sim M8$  所組成,而- $G_{mf}$  為主動式負回授等效的轉導值,由圖 3.14 的  $M11\sim M13$  連接而成,另外  $C_1$  與  $C_2$  分別為第一級與第二級輸出節點的等效寄生電容。

圖 3.15 主動式負回授放大器之等效架構[34]

推導圖 3.15 電路的轉移函數可得到式 (3.14) 的結果,再對照標準的 二階轉移函數 ((3.15) 式),可計算得到式 (3.16)、(3.17) 以及 (3.18) 的結果。

$$H(s) = \frac{V_{out}}{V_{in}}(s) = \frac{\frac{G_{m1}G_{m2}}{C_1C_2}}{s^2 + \frac{R_{L1}C_1 + R_{L2}C_2}{R_{L1}C_1R_{L2}C_2}s + \frac{1 + G_{mf}G_{m2}R_{L1}R_{L2}}{R_{L1}C_1R_{L2}C_2}}$$

(3.14)

$$H(s) = \frac{A_0 \omega_n^2}{s^2 + 2\zeta \omega_n s + \omega_n^2}$$

(3.15)

對照 (3.14) 與 (3.15) 式,可得:

$$A_0 \omega_n^2 = \frac{G_{m1} G_{m2}}{C_1 C_2} \quad \text{If.} \quad \omega_n^2 = \frac{1 + G_{mf} G_{m2} R_{L1} R_{L2}}{R_{L1} C_1 R_{L2} C_2}$$

(3.16)

再計算 $A_0$ 與 $\zeta$ :

$$A_0 = \frac{G_{m1}G_{m2}R_{L1}R_{L2}}{1 + G_{mf}G_{m2}R_{L1}R_{L2}}$$

(3.17)

$$\zeta = \frac{1}{2} \frac{R_{L1}C_1 + R_{L2}C_2}{\sqrt{R_{L1}C_1R_{L2}C_2(1 + G_{mf}G_{m2}R_{L1}R_{L2})}}$$

(3.18)

另一方面,對一個簡單的差動放大器而言,其增益頻寬乘積(GBW), 通常也近似於單增益頻率(unity-gain frequency,  $\omega_T$ ),可寫成 $G_m/C_L$ ,因此 式(3.16)表示成:

$$A_0 \omega_n^2 = \frac{G_{m1} G_{m2}}{C_1 C_2} = \left(\frac{G_m}{C_L}\right)^2 = (\omega_T)^2$$

$$A_0 \omega_n = \omega_T \frac{\omega_T}{\omega_{n-1-1-1}}$$

(3.19)

其中假設 $(G_{m_1}/C_1)\cong (G_{m_2}/C_2)=(G_m/C_L)=\omega_T$ ,又假設系統具有最大平坦響應 (maximally-flat response)的情況下,即 $\zeta=\sqrt{2}/2$ 之時,該二階系統的 $\omega_n$  會等同於該系統的-3 dB 點頻寬,也就是 $\omega_n=\omega_{-3dB}$ ,因此式(3.19)可寫成:

$$A_0 \omega_{-3dB} = \omega_T \frac{\omega_T}{\omega_{-3dB}} \tag{3.20}$$

$$A_0 f_{-3dB} = f_T \frac{f_T}{f_{-3dB}} \tag{3.21}$$

其中  $A_0$  為整個主動式負回授放大器系統的低頻增益, $f_{-3dB}$  為整個主動式負回授放大器增益降 3 dB 時的頻率,也就是頻寬,而  $f_T$  為單一個一階放大器的單增益頻率(unity-gain frequency)。對一般的放大器來說,單增益頻率可

近似為放大器的增益頻寬之乘積( $GBW=A_0f_{-3dB}\cong f_T$ )。而從(3.21)式的結果可知,整個二階主動式負回授的放大器之增益頻寬乘積(GBW)等於單一個一階放大器的單增益頻率( $f_T$ )再乘上( $f_T/f_{-3dB}$ )倍,且一般正常設計下,單一個一階放大器的 $f_T$ 會比整個主動式負回授二階放大器的 $f_{-3dB}$  還來得大許多,故可知使用主動式負回授的放大器其GBW會比單一個放大器的GBW 還大了( $f_T/f_{-3dB}$ )倍。也就是主動式負回授的放大器對於 $A_0>3$  dB 的設計情形能將其GBW提升( $f_T/f_{-3dB}$ )倍,說明了主動式負回授的技巧確實可有效的增加電路的GBW。另外簡單計算此種主動式負回授放大器的GBW( $GBW_{active-feedback}$ )( $\zeta=\sqrt{2}/2$  時)可得:

母の

$$GBW_{active-feedback} = A_0 \omega_{-3dB}$$

を  $G_{mf}$  を  $\sqrt{\frac{G_{mf} G_{m2}}{C_1 C_2}} = \frac{G_{m1}}{C} \times \sqrt{\frac{G_{m2}}{G_{mf}}}$  (3.22) は中:

$$A_0 = \frac{G_{m1} G_{m2} R_{L1} R_{L2}}{1 + G_{mf} G_{m2} R_{L1} R_{L2}} \cong \frac{G_{m1}}{G_{mf}}$$

$$\omega_{-3dB} = \omega_n = \sqrt{\frac{1 + G_{mf} G_{m2} R_{L1} R_{L2}}{R_{L1} C_1 R_{L2} C_2}} \cong \sqrt{\frac{G_{mf} G_{m2}}{C_1 C_2}}$$

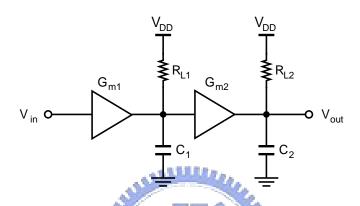

且假設 $C_1 = C_2 = C$ 。而檢視一般簡單的二階放大器,簡圖如圖 3.16 所示。其中  $G_{m1}$ 、 $R_{L1}$ 和  $G_{m2}$ 、 $R_{L2}$ 分別代表兩級串接放大器的轉導值及負載, $C_1$ 及  $C_2$  分別等效為第二級輸入及輸出節點的總寄生電容。其對應的轉移函數,可推得:

$$H(s) = \frac{V_{out}}{V_{in}}(s) = \frac{\frac{G_{m1}G_{m2}}{C_1C_2}}{s^2 + \frac{R_{L1}C_1 + R_{L2}C_2}{R_{L1}C_1R_{L2}C_2}s + \frac{1}{R_{L1}C_1R_{L2}C_2}}$$

(3.23)

對應(3.15)式,並假設圖 3.16 二階放大器的第一級與第二級為相同的,即具有相同的轉導以及相同的負載: $G_{m1} = G_{m2} = G_m$ 、 $R_{L1} = R_{L2} = R$ 以及  $C_1 = C_2 = C$  時,則可得知:

$$A_0 = G_{m1}G_{m2}R_{L1}R_{L2} = (G_mR)^2 \quad \text{I.} \quad \omega_n = \sqrt{\frac{1}{R_{L1}C_1R_{L2}C_2}} = \frac{1}{RC}$$

(3.24)

圖 3.16 一般傳統二階放大器之等效架構

可計算出此種一般的二階放大器之 GBW generat 約為

$$GBW_{general} = \sqrt{\sqrt{2-1}} \times G_m^{-2} \frac{R}{C} \cong 0.644 \times G_m^{-2} \frac{R}{C}$$

(3.25)

比較(3.22)與(3.25)式,可知主動式負回授的二階放大器與一般的二階放大器兩者 GBW 的大小其實都是根據設計的參數而定,但在多數的設計情形下,使用主動式負回授的二階放大器會在不產生過多的功率消耗下,而獲得較大的 GBW 結果,說明了主動式負回授的放大器更適用於高速電路的特色。

# 3.2.2.4 完整比較器電路之設計

圖 3.17 為整個比較器之電路 (Comparator slice),由寬頻的比較功能電路 Gilbert-Cell 作為輸入級,並以連續三級串接的主動式負回授前置放大器

(Active-negative feedback Pre-Amplifier) 將 Gilbert-Cell 比較後的差進行放大的工作,最後再使用一個 CML Latch 電路[17][40]把比較放大後的結果擷取並儲存維持取樣時脈訊號的半週期時間。

圖 3.17 包含多級串接放大器之完整比較器電路 (Comparator slice)

CML Latch 電路重繪如圖 3.18 所示,其提供兩種運作的階段(phase),當 Clk+為 high, Clk-為 low, M2 導通而 M3 關閉,這時電路操作在放大模式(amplification phase),由 M4、M5、M8 及 M9 構成的一階差動放大器可對輸入訊號做放大的工作,因此在此模式下,此電路可視為一階的放大器。反之當 Clk+為 low, Clk-為 high 時, M2 關閉 M3 導通,此時變成 M6、M7 與負載 M8、M9 作用,電路操作在再生模式(regeneration phase)[45][46],藉由 M8、M9 形成的正回授(positive feedback)機制將先前放大模式中,雙端輸出的差值再拉大(regeneration)並將結果儲存在正回授的迴路中。可知 CML Latch 電路提供半週期時間為一階放大器的形式,因此結合了第一級 Gilbert-Cell 與最後一級 CML Latch 所提供的半週期為一階放大器特性的作用之後,因此整個 Comparator slice 的確是由 4 組二階形式的放大器連續串接的近似結果,滿足先前 3.2.2.1 小節所討論的結果。

此外最後一級 CML Latch 電路在 regeneration phase 提供的正回授機制

可使得整個 Comparator slice 電路將最初的輸入訊號與參考電壓之間比較後的差值再拉得更開,更有利於後級數位電路的判別。值得說明的是,為了確保在 regeneration phase 狀態下可以將輸出結果永久的儲存,則必須要滿足 $g_{m6.7}R_{on8.9} > 1$ 的設計條件,其中 $R_{on8.9}$ 為 M8 及 M9 等效的阻抗。

實際電路設計中,我們將 CML Latch 電路操作在放大模式時的增益設計得較小,而把頻寬拉得較大一些,使電路操作在放大模式時提供稍低的增益,之後再讓下一個 phase 的正回授機制把訊號差拉大。觀察圖 3.17 的整個比較器電路中,第一級的 Gilbert-Cell 設計成高頻寬的輸入訊號比較能力,其缺乏對增益的貢獻,且最後一級的 CML Latch 放大並储存比較後的結果。可以預見的是,單純把 Gilbert-Cell 與 CML Latch 串接起來形成的二階放大器能達到的 GBW 將會不及使用 Active negative feedback 前置放大器的 GBW 程度,因此在整個 Comparator slice 中,小訊號放大,也就是增益部份的貢獻 (gain contribution)主要由中間連續三級的前置放大器所提供,為達到先前討論所計算的約 28 dB 的增益,可知平均每一級必須提供約 10 dB 左右的增益,且前置放大器每一級的增益頻寬乘積 (GBWs) 也將必須設計成比 17GHz 還來的大。單一 Active negative feedback 前置放大器的交流分析的模擬結果如圖 3.19 所示,低頻增益約為 10.4 dB,且 GBW 達到約

22.75GHz。而整個 Comparator slice (圖 3.17) 的頻率響應模擬的結果,如圖 3.20 所示,低頻增益約為 34.2 dB,且-3 dB 頻寬可達 6.43GHz,增益與頻寬都合乎先前對比較器電路設計時的討論。

圖 3.19 主動式負回授前置放大器(Active negative feedback Pre-Amplifier) 模擬之頻率響應圖

圖 3.20 完整比較器電路 (Comparator slice) 之頻率響應模擬結果

而在比較器電路 offset 影響的考量上,由於對於我們 4bits ADC 的設計情況來說,在 supply voltage 為 1V 的設計環境下,offset 等影響要到超過 1個 LSB 的 25mV 或是 0.5個 LSB 的 12.5mV 之機率顯然相對低得許多。且由於無法確切得知所使用製程之 mismatch 等的製程參數,以致於無法計算出可能的 offset 大小。有部份文獻[45][47][48]等使用特定電路機制來消除可能發生的 offset 等問題,在[45]之 4GS/s ADC 的設計中使用了電流式 DAC的方式來 trimming 前置放大器輸出節點的 offset。而[47]的 3.2GS/s 的 ADC則藉由數位訊號來控制調整前置放大器負載的電阻值。這些方法都可以達

到消除 offset 的效果,但其所加入的電路或是較大尺寸的開關電晶體都會在放大器的高速輸出訊號節點多引入了額外且不可忽略的寄生電容,使得前置放大器和比較器的頻寬受到嚴重的影響。因此為了使我們的設計能夠達到 10GS/s 的超高速,我們作了速度(speed)及準確度(accuracy)的 trade-off。

#### 3.2.2.5 多級串接放大器 Slew-rate 之設計考量

前述討論之差動多級串接放大器的設計中,目的是要將比較後的差值 訊號逐級放大成數位形式準位的訊號。考慮當第一級或第二級放大的輸出 訊號若已具備相當程度的擺幅 (swing), 此訊號將使其後差動放大器的差 動對 (differential pair) 發生全切換 (fully switched) 的現象,開啟某一側 的電晶體而關閉另一側的電晶體,使得電路變成操作在大訊號的模式之 中。而這些差動對在達到完全開啟或關閉之間的行為稱之為 slewing。對於 此種高速變化的大擺幅訊號,影響電路能否跟隨輸入變化的因素就是 slew-rate 的問題,也就是 slew-rate 影響頻寬的問題。對一具有 V。振幅大小 且頻率為 $\omega$ 。的大擺幅輸入訊號,則電路所應具備的 slew-rate 至少應大於  $V_0 \omega_0$ 之值。因此在我們的設計情況下,對於輸入最大可能之 $V_0$ 約為  $400 \mathrm{mV}$ , 且  $f_0$  最大為 5GHz ( $\omega_0 = 2\pi \times f_0$ ),可計算得前置放大器所需之 slew-rate 必 須大於 12.56V/ns,此值提供了前置放大器最小所需之 slew-rate 的設計指 標。我們可藉由計算前置放大器 tail current 與輸出總負載電容(C<sub>L</sub>)的比 值  $(I/C_L)$  可計算出約略的 slew-rate, 由模擬結果計算出我們所設計的前置 放大器,其 slew-rate 約可達到 22V/ns,滿足此小節對 slew-rate 需求的討論。

## 3.2.3 泡沫錯誤更正電路(Bubble Errors Correction)

在 Flash ADC 的架構中,輸入訊號經由比較器與各個參考電壓比較之

後的輸出,由上而下應該是一連串的 0,然後接者一連串的 1 (以正邏輯的觀點來看),此類型的數位碼稱之為溫度計碼 (Thermometer code)。然而實際的比較結果卻可能發生一連串的 1 之中突然出現一個 0,且此 0 通常會出現在靠近一連串 1 頂端的位置,造成之後的編碼電路輸出錯誤的結果,如圖 3.21 所示。此種現象稱為泡沫錯誤 (Bubble error,有時也稱為 Sparkle),就像是裝水的試管中,靠近水面的位置下產生一個氣泡或泡沫。

圖 3.21 泡沫錯誤示意圖以及 ROM 編碼形式消除泡沫錯誤的邏輯電路

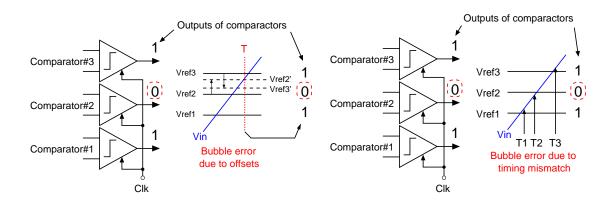

此現象的成因可能是由於製程變異使得每個比較器電路產生不同程度的偏移(offset)量,結果各個比較器比較的參考電壓也因此可能會有所偏移,如圖 3.22(a)所示,第二個比較器的參考電壓 Vref2 往上偏移到 Vref2'的位置,且三個比較器的參考電壓 Vref3 往下偏移到 Vref3'的位置,使得在時間 T 的時候得到的比較結果產生泡沫錯誤,此種情形特別容易發生在處理輸入訊號與參考電壓很靠近的比較器(一連串 1 最頂端所對應的比較器),因為對該比較器而言,輸入與參考電壓的差值不明顯,進而使得原本應為 1 的輸出變成 0 的輸出,產生泡沫錯誤;此外電路雜訊(noise)和高速取樣時脈的抖動量(clock jitter)造成的取樣時序偏移(timing mismatch)也會導致泡沫錯誤,如圖 3.22(b)中因為每個比較器取樣訊號的延遲時間不

一,使得比較器 1~3 分別在不同的時間 T1、T2 及 T3 的時間點取樣,導致取樣比較後的結果產生泡沫錯誤,此種情形導致的泡沫錯誤會因越高速的輸入訊號而變得更加容易發生[49]。

(a) Bubble error due to offsets (b) Bubble error due to timing mismatch 圖 3. 22 因 offset 和 timing mismatch 發生的泡沫錯誤 (Bubble error) [49]

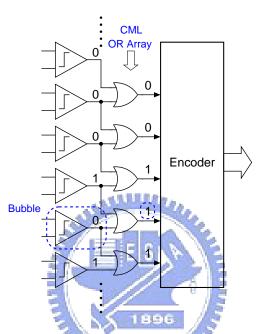

另外圖 3.21 也顯示了 Flash ADC 中數位編碼電路使用常見的 ROM 編碼方式來設計的例子。ROM 的編碼機制是必須先將比較器輸出的溫度計碼轉成一連串 0 中只有一個 1 的 "1-of-N code",且 1 的位置會落在原本溫度計碼 0 與 1 交界的轉態點中,最上面 1 的位置,如果只是要作如此數碼的轉換,使用兩輸入的邏輯閘便可達成,而同時為了要消除較為可能發生的一階泡沫錯誤(the 1<sup>st</sup>-order Bubble error)時,就必須再多使用一個輸入來作邏輯上的操作,也就是使用三輸入的邏輯閘,故可知以 ROM 編碼形式設計的編碼器,若要消除 n 個可能的泡沫錯誤,就必須使用 (n+2) 個輸入的邏輯閘。雖然 ROM 的編碼方式是較為簡單且直觀的,但可達到的操作速度相當有限,因此當使用 Flash 的架構把速度往上提升時,ROM 的編碼方式便顯得不敷使用,因此我們藉由 CML 電路可操作在非常高速的優勢,設計直接以 CML 電路為基本 cell 的編碼器電路,同時也就不需要將溫度計碼轉成 1-of-N code 的機制,且消除泡沫錯誤的電路直接使用兩層開關邏輯能夠處理兩個輸入的 CML OR gate 來消除一階的泡沫錯誤,此種方式欲達到

消除 n 個泡沫錯誤的功能,就必須使用 (n+1) 個輸入的邏輯閘。對於我們設計的 4-bit ADC 來說,在電路佈局時做到對稱匹配的情況下,發生兩個以上泡沫錯誤的機率比一階的泡沫錯誤發生機率還低得許多,因此我們使用一連串兩個輸入的 CML OR gate (CML OR Array) 消除一階可能的泡沫錯誤,如圖 3.23 所示。

圖 3.23 使用 CML OR Array 消除可能發生的一階泡沫錯誤

## 3.2.4 編碼電路之設計

在討論分析編碼器電路的設計之前,必須要先知道的是比較器電路中常見的 metastability 現象。當比較器輸入的訊號與參考電壓差值很小時,使得在很短的時間週期內,比較器輸出無法穩定平衡至有效的邏輯準位,在Flash ADC 中就是指當輸入訊號非常靠近某個比較器對應的比較參考電壓,使得該比較器無法判知正確的輸出邏輯準位,這將使得該比較器後級所驅動的邏輯閘出現未知(unknown)的邏輯狀態,進而使編碼電路產生錯誤的數位碼輸出。若編碼電路使用 ROM 的形式設計,當發生 metastability之時,可能會造成沒有任何1條或是有超過1條的 ROM 選擇線(ROM lines)被選取到,導致整個錯誤的數位輸出碼。

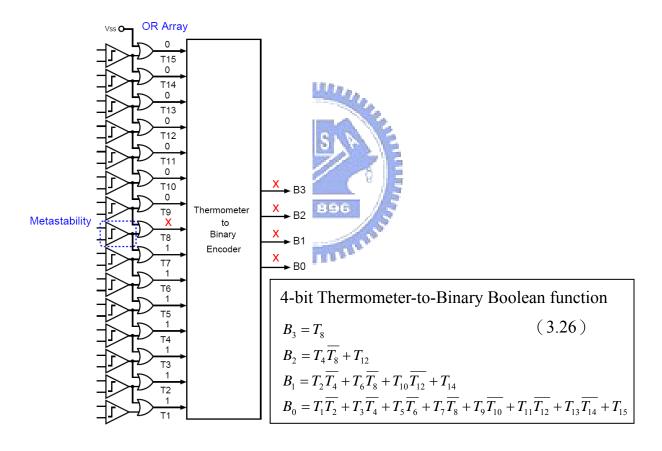

另一方面討論若是使用邏輯閘為基礎(logic gate based)的溫度計碼轉二進碼編碼器(Thermometer-to-Binary Encoder)之情形,如圖 3.24 所示當metastability 的問題發生於 4 位元溫度計碼轉二進碼編碼器,假設比較器輸出 T8 發生 metastability 的現象,輸出呈現 unknown(X)的狀態,而根據(3.26)式之 4 位元溫度計碼轉二進碼的布林函數(boolean function)可知 T8 的 unknown 狀態將導致整個 4 位元二進碼輸出(B[3:0])的結果也都為unknown 的狀態。因此可知使用 binary-code 的編碼器相當容易因為metastability 的問題造成輸出產生兩個位元以上的錯誤輸出碼。

圖 3.24 Metastability 的問題發生於 4 位元溫度計碼轉二進碼編碼器之例子

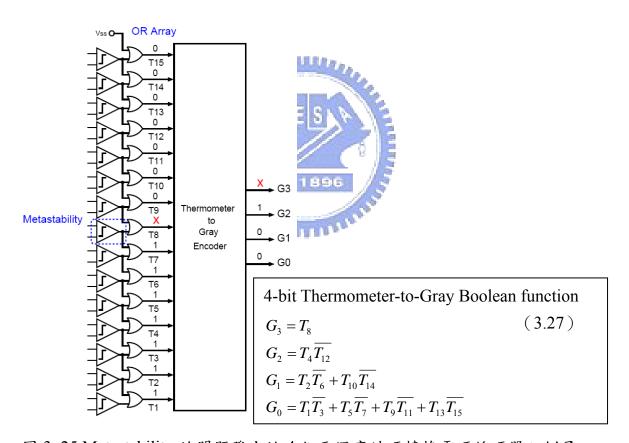

Flash ADC 中另一種以邏輯閘為基礎且常用的編碼為溫度計碼轉格雷碼 (Thermometer-to-Gray Encoding)的方式。格雷碼 (Gray code)的一個重要特性就是其任意相鄰的兩個數碼之間只有一個位元不同,所以 Gray code 輸出的電路每個位元轉態的次數將會大幅的減少,以電路的觀點來看

就是充放電(charge/discharge)的次數會降低,因開關切換所導致的雜訊或是其他干擾就都可以變小許多。因此 Gray code 的編解碼方式相當有利於高速訊號的操作,常被應用於高速的系統當中。在 4 位元溫度計碼轉格雷碼的編碼機制中,如圖 3.25 所示的例子,同樣假設當比較器輸出 T8 發生了metastability,然後根據式(3.20)的 4 位元溫度計碼轉格雷碼的布林函數可知,輸出結果將只有 G3 一個位元是 unknown 的,且無論 metastability 發生在哪個比較器上,只要只有一個 metastability 發生,輸出的數位碼最多都只會有一個位元受到影響。可知使用 Gray code 的編碼器發生兩個以上錯誤輸出的機率相對會小得許多。

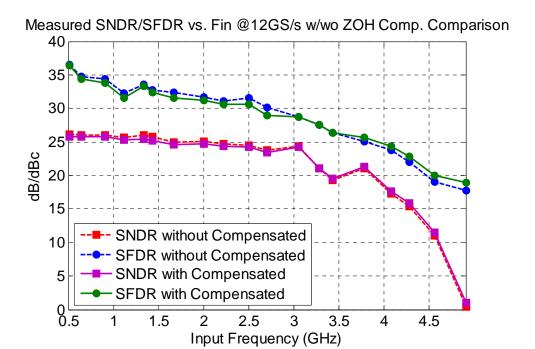

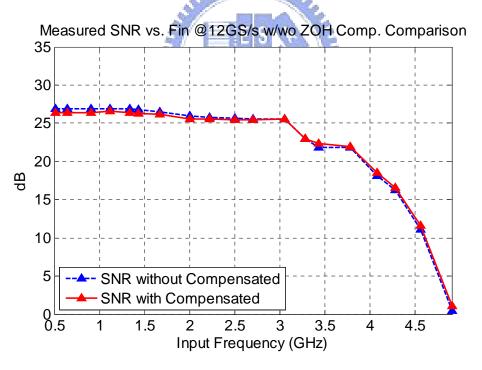

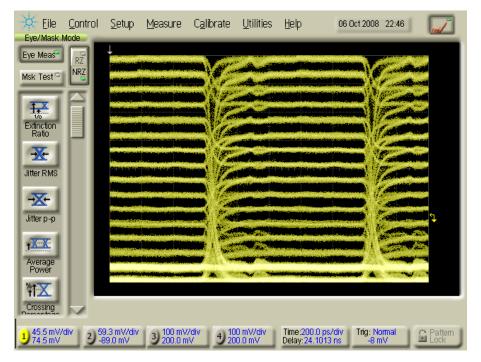

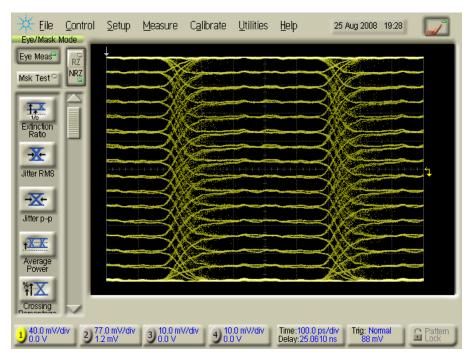

圖 3.25 Metastability 的問題發生於 4 位元溫度計碼轉格雷碼編碼器之例子