# 國立交通大學

# 材料科學與工程學系 博士論文

應用在金氧半電晶體之原子層沉積氧化鋁與 砷化銦鎵、砷化銦介面之研究

Study of Atomic Layer Deposition Al<sub>2</sub>O<sub>3</sub>/InGaAs, InAs Interfaces for MOSFET Application

研究生: TRINH HAI DANG (金海光)

指導教授: 張翼博士

中華民國一百年八月

# Study of Atomic Layer Deposition Al<sub>2</sub>O<sub>3</sub>/InGaAs, InAs Interfaces for MOSFET Application

研究生:金海光 Student: Trinh Hai Dang

指導教授:張 翼 博士 Advisor: Prof. Edward Yi Chang

國立交通大學 材料科學與工程研究所 博士論文

## **A Dissertation**

Submitted to Department of Materials Science and Engineering

College of Engineering

National Chiao Tung University

In Partial Fulfill of the Requirements

For the Degree of

Doctor of Philosophy

August 2011

Hsinchu, Taiwan, Republic of China

中華民國一百年八月

# 摘要

本論文集中研究減少 InGaAs 和 InAs 原生氧化層藉由使用數種表面處理和氣體退火條件去改善原子氣相沉積(ALD)Al<sub>2</sub>O<sub>3</sub>/InGaAs, Al<sub>2</sub>O<sub>3</sub>/InAs 介面品質。三甲基鋁(TMA)製程及濕式化學溶液製程這兩種製程的結合與影響被提出。

使用乾式 TMA 來減少 InGaAs, InAs 表面的原生氧化層只有在第一次脈衝有效,接下來便無效。本研究中指出原生氧化層可以被顯著的移除,藉由使用濕式化學溶液製程,例如 HCl 或 sulfide(硫化物)。然而,結合兩種方法(濕式化學溶液製程與 TMA 預先處理)對於 InGaAs,InAs 表面處理是最為有效的方式。

Al<sub>2</sub>O<sub>3</sub>/InAs MOSCAPs 的電性指出對於改善 Al<sub>2</sub>O<sub>3</sub>/InAs 介面品質 HCl 加上 TMA 比起 sulfide 加上 TMA 是更有效果的。這個結果是由以下實驗觀察所得:ALD Al<sub>2</sub>O<sub>3</sub> 薄膜在 200°C 下沉 積。300°C 下沉積 ALD Al<sub>2</sub>O<sub>3</sub> 薄膜再次驗證。同時本研究模擬 Al<sub>2</sub>O<sub>3</sub>/InAs 結構在低頻的 C-V。結果顯示界面缺陷密度(D<sub>11</sub>)分佈表現出 U 形在最小的 D<sub>11</sub>分佈位於 InAs 傳導帶最低處,i.e. 類施體陷阱在此能隙裡支配。這些類施體陷阱會顯著的減少藉由使用濕式化學溶液製程加上 TMA 預先處理。

藉由使用濕式化學溶液製程加上 TMA 預先處理和在純氫氣裡沉積後退火,對於  $Al_2O_3/In_0s_3Ga_047As$  界面品質有顯著提昇。使用 ex-situ 方法,強力的 C-V 反轉行為第一次被觀察到在  $Al_2O_3/In_0s_3Ga_047As$  MOSCAP。低  $D_{11}$  分佈可藉由模擬觀察到,同時模擬及電導法可確認最小  $D_{11}$  值 ~ $10^{11}$  eV $^1$ cm $^{-2}$ 。

Al<sub>2</sub>O<sub>3</sub>/InGaAs,InAs 的電性表現不僅受與表面處理方法影響,同時也跟半導體本身性質有關。這些半導體參數例如:能隙、電子遷移率及 Al<sub>2</sub>O<sub>3</sub>/InGaAs 結構的 C-V、I-V 本質濃度特性都被討論。

#### **ABSTRACT**

This dissertation concentrates on the study of the reduction of InGaAs and InAs native oxides by using several kinds of surface treatments and gas annealing conditions to improve the atomic layer deposition (ALD) Al<sub>2</sub>O<sub>3</sub>/InGaAs, Al<sub>2</sub>O<sub>3</sub>/InAs interfaces qualities. Effects of trimethyl aluminum (TMA) treatment, wet chemical surface treatments, and a combination of these two kinds of treatments are investigated.

The use of dry TMA treatment for the reduction of InGaAs, InAs native oxides at surface was only effective in the first pulse and then it became effectless. The study shows that the native oxides could be significantly removed by using wet chemical solution treatments such as HCl or sulfide. However, the combination of wet chemical solution treatments plus TMA pretreatment is the most effective way for InGaAs, InAs surface treatment.

Electrical characterization of Al<sub>2</sub>O<sub>3</sub>/InAs MOSCAPs showed that the HCl plus TMA treatment was more effective in the improvement of Al<sub>2</sub>O<sub>3</sub>/InAs interface quality than that of sulfide plus TMA treatment. This conclusion was observed for the samples which were deposited with ALD Al<sub>2</sub>O<sub>3</sub> films at 200°C and was confirmed again for the samples deposited with ALD Al<sub>2</sub>O<sub>3</sub> films at 300°C. Low-frequency C-V simulations were performed for the Al<sub>2</sub>O<sub>3</sub>/InAs structures and the extracted interface traps density D<sub>it</sub> profiles present a U-shape with the minimum of the D<sub>it</sub> profiles located around the InAs conduction band minimum, i.e. donor-like traps dominates inside the bandgap. These donor-like traps were significant reduced by using wet chemical plus TMA treatments.

By using the chemical solution plus TMA treatment along with post deposition annealing in pure  $H_2$  gas, a significant improvement of  $Al_2O_3/In_{0.53}Ga_{0.47}As$  interface quality was obtained. A strong C-V inversion behavior was first time observed in  $Al_2O_3/In_{0.53}Ga_{0.47}As$  MOSCAP by using an ex-situ method. Low  $D_{it}$  profile extracted by simulation was observed and the minimum  $D_{it}$  value of  $\sim 10^{11}$  eV<sup>-1</sup>cm<sup>-2</sup> was confirmed by both simulation and conductance method.

The electrical characteristics of Al<sub>2</sub>O<sub>3</sub>/InGaAs, InAs not only depend on the surface treatment methods but also depend on the properties of semiconductors themselves. The effect of semiconductor parameters such as bandgap, electron mobility, and intrinsic concentration on the C-V, I-V characteristics of Al<sub>2</sub>O<sub>3</sub>/InGaAs structures are discussed.

## **ACKNOWLEDGMENTS**

The author gratefully acknowledges Chiao Tung University (NCTU), Taiwan and the Compound Semiconductor Device Laboratory (CSD Lab), NCTU, Taiwan for supporting this research.

I firstly would like to express my deep gratitude to my supervisor, Prof. Edward Yi Chang for his guidance, support and patience during my Ph.D time at CSD Lab. I appreciate the freedom in research he provided and the taking care he intended for me at the beginning I joined NCTU. He is always kind to me and his encouragement was a driving force for me in study. I really admire his ability in working and research.

This work could not succeed without the support of some people to them I'd like to give my thanks. I am really indebted to Dr. Lin Yueh Chin, Wong Yuen Yee, Yu Chih Chieh (ITRC), Dr. Kuo Chien I, Nguyen Hong Quan, Dr. Lin Kung Liang, and Tran Binh Tinh for their constant help of experiments and valuable discussions. Thanks to them not only in the research but also the good friendships and the fun they brought to me, especially Yuen Yee, Hong Quan. I also appreciate Dr. Chung Yu Lu, Dr. Chang Chia Ta, Hsieh Yi Fan, Dr. Chang Chia Yuan, Chung Chen Chen, and Chiu Yu-Sheng for their kindly supports of experiments.

Many thanks to my colleagues and good friends including Le Minh Thu, Bui Duc Tinh, Dai Van Truong, Do Thi Hien, Oh Chi Way, Nguyen Chi Lang for the enjoyable times we shared together. Thanks also to my NCTU-FSA team including Maria, Sumer, Martin, Leo, and Korniyenko and NCTU-VSA members for the wonderful extracurricular activities, parties and jolly football matches. My Ph.D. time would be less meaningful without them.

Last but not least, this work dedicates to my dearest parents, my wife and my brothers. I wish to thank to my parents who are always beside me all time and give me a strong hope and belief. Thanks to my wife, Them who has been brought to me the love, happiness and joy. I am so happy to have her in my life. Thanks to my younger brothers, Tat Dat and Trong Duc for their fondness for me. They are also a motive power for me to strive for this work.

# **DEDICATION**

To

My dearest Parents, my Wife, and my Brothers

# **CONTENTS**

| Abstract (Chinese)                                         | i    |

|------------------------------------------------------------|------|

| Abstract (English)                                         | ii   |

| Acknowledgment                                             | iii  |

| Dedication                                                 | iv   |

| Contents                                                   | v    |

| List of figures                                            | viii |

| List of tables                                             | xiv  |

| List of symbols                                            | xv   |

| List of acronym                                            | xvii |

| 1. Introduction                                            | 1    |

| 1.1. An Overview of planar Si-based CMOS Technology        | 2    |

| 1.2. High k, metal gate solutions                          | 4    |

| 1.3. Scaling challengers and future trends                 |      |

| 1.3.1. Scaling challengers                                 |      |

| 1.3.2. Future trends                                       | 10   |

| 1.4. III-V compound semiconductors for CMOS technology: mo |      |

| challenges and current progress                            | 11   |

| 1.4.1. Motivation                                          | 11   |

| 1.4.2. Challengers                                         | 14   |

| 1.4.3. Current progress                                    | 15   |

| 1.5. Problem statement and objective of the dissertation   | 17   |

| 1.6. Organization of the dissertation                      | 18   |

| References                                                 | 19   |

| 2. FABRICATION AND CHARACTERIZATION METHODS                | 25   |

| 1.2. Fabrication techniques                                | 26   |

| 2.1.1. Atomic layer deposition (ALD)                       | 26   |

| 2.1.2. Electron beam evaporation                           | 30   |

| 2.2 Fabrication process                                    | 21   |

| 2.3. Analytical techniques                                                                                 | 33                   |

|------------------------------------------------------------------------------------------------------------|----------------------|

| 2.3.1. X-ray photoelectron spectroscopy (XPS)                                                              | 33                   |

| 2.3.2. High-resolution transmission electron spectroscopy (HRTEM)                                          | 39                   |

| 2.4. Electrical techniques                                                                                 | 41                   |

| 2.4.1. Capacitance-voltage (C-V), conductance voltage (G-V) measurements                                   | 41                   |

| 2.4.2. Current-voltage (I-V, J-V) measurements                                                             | 45                   |

| 2.4.3. Conductance and conductance map methods                                                             | 46                   |

| References                                                                                                 | 51                   |

| 3. EFFECTS OF WET CHEMICAL AND TMA TREATMENTS ON THE INTERFACE PROPE                                       | RTIES                |

| IN ALD OF AL <sub>2</sub> O <sub>3</sub> ON INAS                                                           | 52                   |

| 3.1. Introduction                                                                                          | 53                   |

| 3.2. Experiment                                                                                            | 53                   |

| 3.3. Results and discussion                                                                                |                      |

| 3.3.1 Effect of TMA treatment                                                                              | 54                   |

| 3.3.2. A combination of wet chemical treatments and TMA pretreatment                                       |                      |

| 3.4. Conclusions                                                                                           |                      |

| References                                                                                                 | 61                   |

| 4. ELECTRICAL CHARACTERIZATION OF AL <sub>2</sub> O <sub>3</sub> /n-InAs MOSCAPs with va                   | RIOUS                |

| SURFACE TREATMENTS                                                                                         | 64                   |

| 4.1. Introduction                                                                                          | 65                   |

| 4.2. Experiment                                                                                            | 65                   |

| 4.3. Results and discussion                                                                                | 66                   |

| 4.3.1. X-ray photoelectron spectroscopy                                                                    | 66                   |

| 4.3.2. Capacitance-voltage characteristics                                                                 | 67                   |

| 4.3.3. Simulation and D <sub>it</sub> profiles extraction                                                  | 69                   |

| 4.4. Conclusions                                                                                           | 70                   |

| References                                                                                                 | 72                   |

| 5. THE INFLUENCES OF SURFACE TREATMENT AND GAS ANNEALING CONDITIONS O                                      | N THE                |

| INVERSION BEHAVIORS OF THE ATOMIC LAYER DEPOSITION AL <sub>2</sub> O <sub>3</sub> /N-IN <sub>0.53</sub> GA | 1 <sub>0.47</sub> AS |

| MOCCAR                                                                                                     | 7.4                  |

| 5.1. Introduction                                                                                                     | 75              |

|-----------------------------------------------------------------------------------------------------------------------|-----------------|

| 5.2. Experiment                                                                                                       | 75              |

| 5.3. Results and discussion                                                                                           | 76              |

| 5.3.1. Capacitance-voltage characterization                                                                           | 76              |

| 5.3.2. X-ray photoelectron analysis                                                                                   | 78              |

| 5.3.3. D <sub>it</sub> extraction by simulation and conductance methods                                               | 80              |

| 5.4. Conclusions                                                                                                      | 81              |

| References                                                                                                            | 83              |

| 6. INVESTIGATION OF ELECTRICAL CHARACTERISTICS OF AL <sub>2</sub> O <sub>3</sub> /N-IN <sub>x</sub> GA <sub>1-x</sub> | As $(x = 0.53,$ |

| 0.7) AND INAS CAPACITORS                                                                                              | 85              |

| 6.1. Introduction                                                                                                     | 86              |

| 6.2. Experiment                                                                                                       | 86              |

| 6.3. Results and discussion                                                                                           | 87              |

| 6.3.1. X-ray photoelectron spectroscopy analysis                                                                      | 87              |

| 6.3.2. High-resolution transmission electron microscopy micrographs                                                   | 87              |

| 6.3.3. Electrical characteristics                                                                                     |                 |

| 6.4. Conclusions                                                                                                      | 93              |

| References                                                                                                            | 95              |

| 7. CONCLUSIONS                                                                                                        | 97              |

| Biography                                                                                                             | 99              |

| List of publications                                                                                                  | 100             |

# LIST OF FIGURES

| Figure 1.1. "The number of transistors incorporated in a chip will approximately double             |

|-----------------------------------------------------------------------------------------------------|

| every 24 months": Moore's Law Timeline (solid) and the number of transistors per chip               |

| in Intel's products (line plus symbols). The inset is Moore's original prediction graph in          |

| 1965                                                                                                |

| Figure 1.2. Scaling of logic technology node and correspond transistor's physical gate              |

| length (According to Intel's introduction until 2009 and ITRS update 2008)3                         |

| Figure 1.3. Leakage current versus voltage for various thicknesses of SiO <sub>2</sub> layers       |

| Figure 1.4. At the gate oxide thickness of 1.2 nm (5 layer of atoms), the wave describing           |

| the probable location of an electron is broader than the gate oxide and the electron can            |

| simply appear on the other side of gate oxide, means that direct tunneling of electrons             |

| through the insulation. New high k gate oxide is needed to plug the leak5                           |

| Figure 1.5. Static dielectric constant versus band gap for candidate gate oxides                    |

| Figure 1.6. a-Electron density in PolySi gate is not large enough to screen the effect of           |

| high k dipoles on semiconductor lattice points, lead to strong phonon-electron scattering;          |

| b-Experimental evidence of phonon scattering in the high k dielectric. The net value of             |

| the temperature (T) sensitivity factor, $d(1/\mu_{eff})/dT$ , is negative when coulombic scattering |

| dominates and positive when phonon scattering dominates. [21]; c-Metal gate with high               |

| electron density can screen out the vibrations, reduce effect of phonon scattering; d-              |

| Experimental (symbols) and simulation (dash lines) data show the improvement of                     |

| electron mobility by using high k/metal gate stack                                                  |

| Figure 1.7. The improvements of leakage current and drive currents by using high k                  |

| metal gate generations9                                                                             |

| Figure 1.8. Illustration of the exponential decrease in switching energy (left) and the             |

| simultaneously increasing device power density (middle) as a consequence of device                  |

| downscaling. The increase of power density causes of power consumption issue, lowering              |

| supply voltage is not an easy way to reduce power consumption due to the increase of off            |

| state current, I <sub>off</sub> (right)10                                                           |

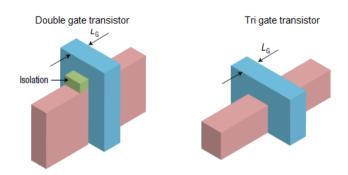

| <b>Figure 1.9.</b> Non-planar transistors: Double-gate transistor (left) and tri-gate transistor (right)                                                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Figure 1.10.</b> Electron velocities as a function of field of Si, Ge and III-V compound semiconductors. III-V compound semiconductors exhibit high saturation velocity at low electric field                                                                                                          |

| <b>Figure 1.11.</b> III–V HEMTs characteristics compared with standard silicon MOSFETs a, Intrinsic gate delay. b, Normalized energy-delay product of n-channel InSb and InGaAs HEMTs                                                                                                                     |

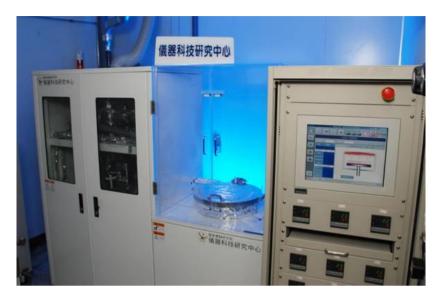

| <b>Figure 2.1.</b> The 8 inch ALD system at instrument technology and research center (ITRC), Hsinchu, Taiwan. This system was mostly used for the deposition of high k oxides in this work                                                                                                               |

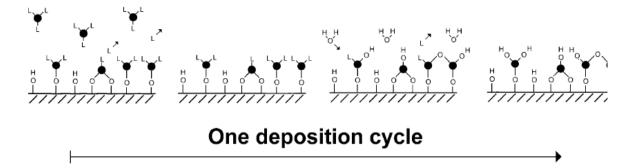

| <b>Figure 2.2.</b> Schematic illustration describing an ALD deposition cycle leading to the formation of a binary oxide film consisting of metal (•) and oxygen (•) atoms. L refers to the precursor ligand                                                                                               |

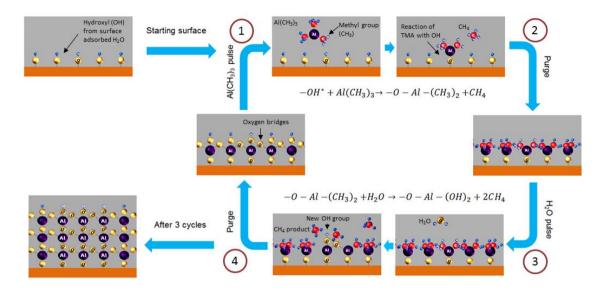

| <b>Figure 2.3.</b> Schematic describing the alternating TMA and H <sub>2</sub> O pulses in ALD chamber leading to form sequence Al <sub>2</sub> O <sub>3</sub> layers                                                                                                                                     |

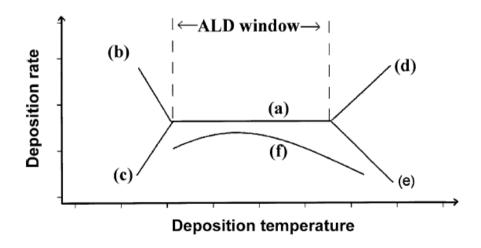

| <b>Figure 2.4.</b> Scheme of (a) ALD processing window limited by (b) precursor condensation (c) insufficient reactivity, (d) precursor decomposition and (e) precursor desorption. If deposition rate is dependent on the number of available reactive sites as in (f), no actual ALD window is observed |

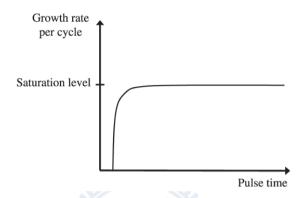

| <b>Figure 2.5.</b> Saturation of surface reactions in ALD processes is experimentally verified by observing that the deposition rate per cycle stabilizes to a constant level with increasing precursor pulse time or dose                                                                                |

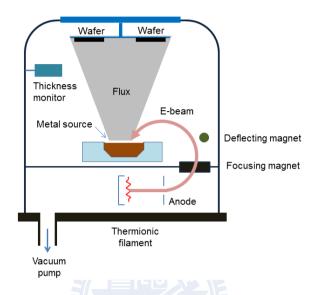

| <b>Figure 2.6.</b> Schematic of electron beam evaporation system for metal deposition31                                                                                                                                                                                                                   |

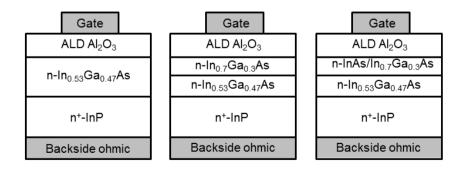

| <b>Figure 2.7.</b> The Al <sub>2</sub> O <sub>3</sub> /InGaAs, InAs MOSCAPs structures used in this work31                                                                                                                                                                                                |

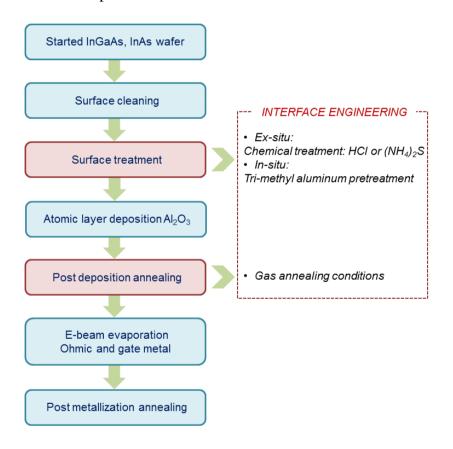

| <b>Figure 2.8.</b> Process flow of Al <sub>2</sub> O <sub>3</sub> /InGaAs, InAs MOSCAPs fabrication, focusing on the interface engineering                                                                                                                                                                |

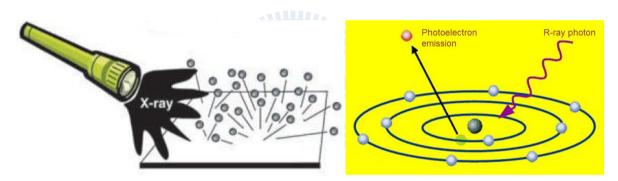

| <b>Figure 2.9.</b> Surface irradiated by sufficient energy X-ray photon beam will emit photoelectrons: phenomenon (left) and principle schematic (right)                                                                                                                                                  |

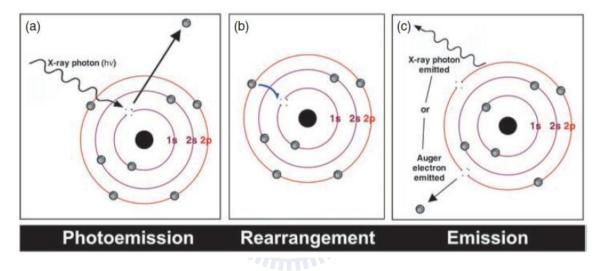

| Figure 2.10. (a) The X-ray photon transfers its energy to a core-level electron leading to                      |

|-----------------------------------------------------------------------------------------------------------------|

| photoemission from the n-electron initial state. (b) The atom, now in an (n-1)-electron                         |

| state, can reorganize by dropping an electron from a higher energy level to the vacant                          |

| core hole. (c) Since the electron in (b) dropped to a lower energy state, the atom can rid                      |

| itself of excess energy by ejecting an electron from a higher energy level. This ejected                        |

| electron is referred to as an Auger electron. The atom can also shed energy by emitting an                      |

| X-ray photon, a process called X-ray fluorescence                                                               |

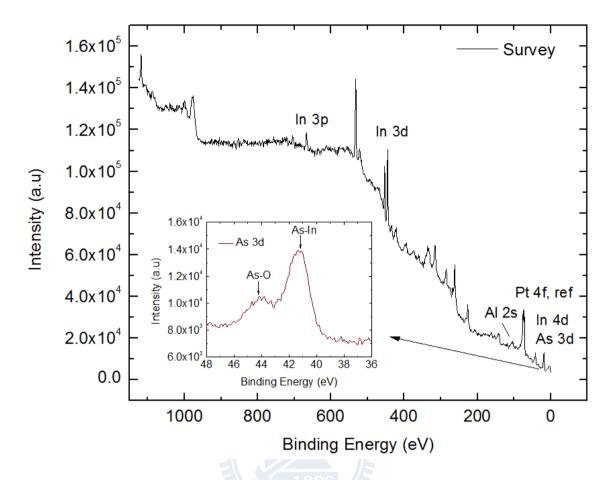

| Figure 2.11. XPS survey scan of Al <sub>2</sub> O <sub>3</sub> /InAs sample, the inset shows As 3d spectra 36   |

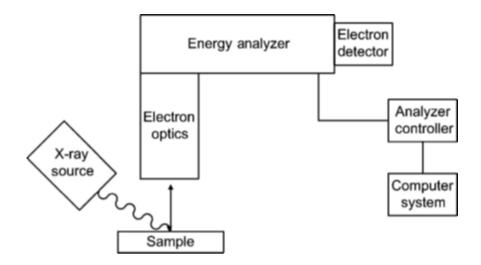

| <b>Figure 2.12.</b> Schematic design of an X-ray photoelectron spectrometer                                     |

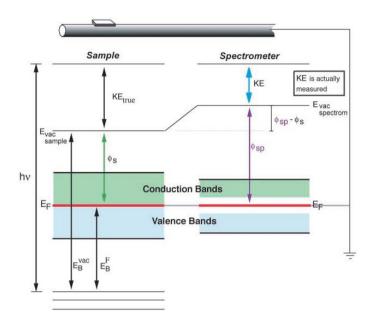

| Figure 2.13. The energy level diagram for an electrically conducting sample that is                             |

| grounded to the spectrometer. The Fermi levels of the sample and spectrometer are                               |

| aligned ( $E_{F(s)} = E_{F(sp)}$ ) so that $E_B$ is referenced with respect to $E_F$ . The measurement of $E_B$ |

| is independent of the sample work function, $\phi_{\text{s}},$ but is dependent on the spectrometer             |

| work function, φ <sub>sp</sub>                                                                                  |

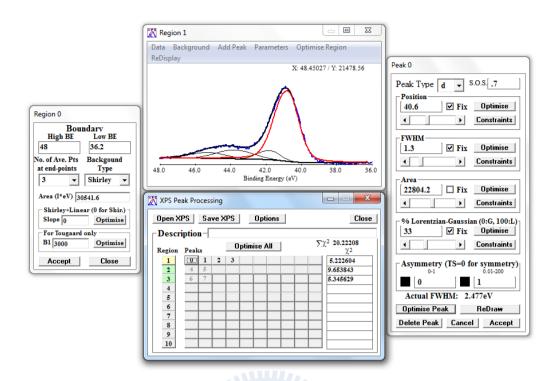

| Figure 2.14. The control windows of XPSPEAK software, version 4.1                                               |

| <b>Figure 2.15.</b> Principle schematic of a transmission electron microscopy (TEM)                             |

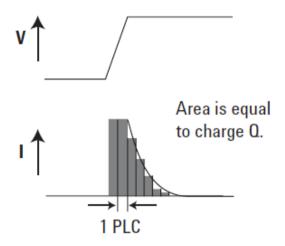

| <b>Figure 2.16.</b> Rectangular approximation method used by 4156C43                                            |

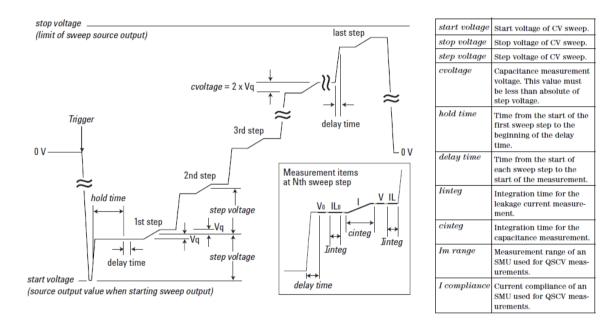

| <b>Figure 2.17.</b> QSCV measurement sequence                                                                   |

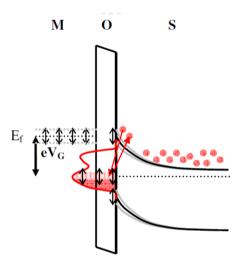

| Figure 2.18. Band diagram of an n-type MOS structure with a bias voltage $V_{\rm G}$ applied                    |

| between metal and semiconductor                                                                                 |

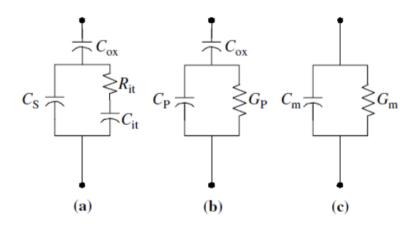

| Figure 2.19. Equivalent circuits for conductance measurements: (a) MOSCAP with                                  |

| interface trap time constant $\tau_{it} = R_{it}C_{it}$ , (b) simplified circuit of (a), (c) measured circuit,  |

| (d) including series r <sub>s</sub> resistance and tunnel conductance G <sub>t</sub>                            |

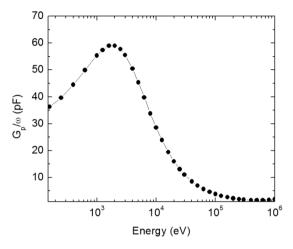

| Figure 2.20. $G_p/\omega$ versus frequency of an $Al_2O_3/In_{0.53}Ga_{0.47}As$ MOSCAP device49                 |

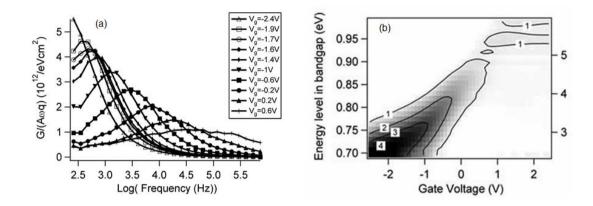

| Figure 2.21. a-G/A $\omega$ q as a function of frequency at different gate bias voltages, A is area             |

| of MOSCAP; b- $\mbox{G/A}\omega\mbox{q}$ contours as a function of both frequency and gate voltage, a           |

| more efficient and intuitive way to visualize the movement of Fermi level50                                     |

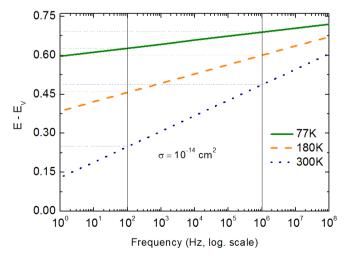

| Figure 2.22. Characteristic trapping frequencies for electron in n-In <sub>0.53</sub> Ga <sub>0.47</sub> As at  |

| different temperatures 50                                                                                       |

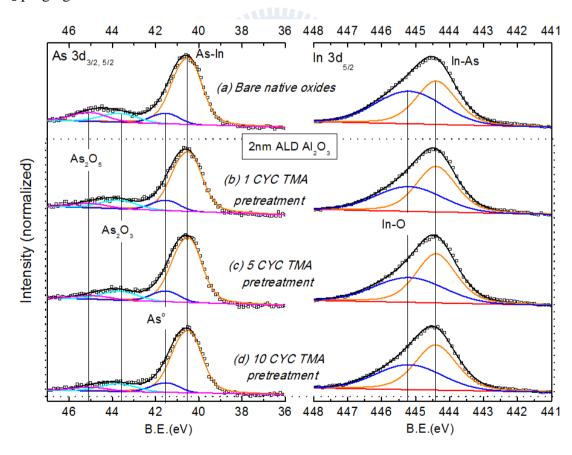

| Figure 3.1. XPS spectra of As 3d and In $3d_{5/2}$ InAs samples: a-bare chip without surface                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| treatment and after 1, 5, 10 cycles of in situ TMA pretreatment (b-d), followed by 20                                                                                                                                                                                                                                                                                                                                                                                   |

| cycles (~2 nm) of ALD Al <sub>2</sub> O <sub>3</sub> deposition                                                                                                                                                                                                                                                                                                                                                                                                         |

| Figure 3.2. XPS As 3d and In 3d <sub>5/2</sub> spectra of InAs samples after a-HCl and b-(NH <sub>4</sub> ) <sub>2</sub> S                                                                                                                                                                                                                                                                                                                                              |

| treatments and the wet-chemical-treated samples after 10 cycles of TMA pretreatment                                                                                                                                                                                                                                                                                                                                                                                     |

| followed by 20 cycles of ALD Al <sub>2</sub> O <sub>3</sub> (c and d)57                                                                                                                                                                                                                                                                                                                                                                                                 |

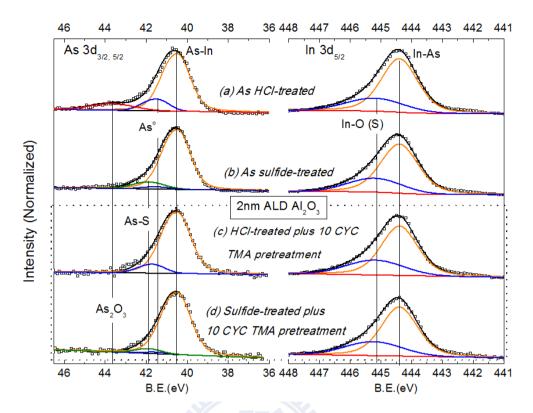

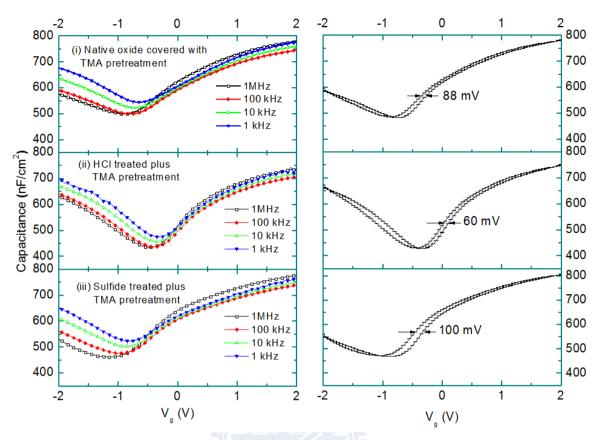

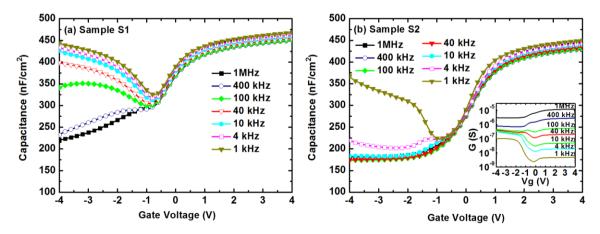

| <b>Figure 3.3.</b> Multiple frequency C-V responses and bidirectional curves at frequency of 1                                                                                                                                                                                                                                                                                                                                                                          |

| MHz for 10nm ALD $Al_2O_3/n$ -InAs MOSCAP structures: a-Pure TMA pretreatment, b-                                                                                                                                                                                                                                                                                                                                                                                       |

| HCl treatment plus TMA pretreatment, c-sulfide treatment plus sulfide pretreatment. The                                                                                                                                                                                                                                                                                                                                                                                 |

| frequency dispersions per decade are 2.3, 1.8, and 2.3% for samples in sequence a to c, respectively                                                                                                                                                                                                                                                                                                                                                                    |

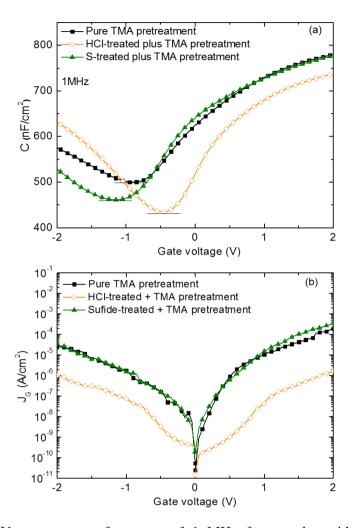

| Figure 3.4. a- C-V responses at frequency of 1 MHz for samples with different surface                                                                                                                                                                                                                                                                                                                                                                                   |

| treatments. b- Leakage current density versus gate voltage (J-V) of the same samples 59                                                                                                                                                                                                                                                                                                                                                                                 |

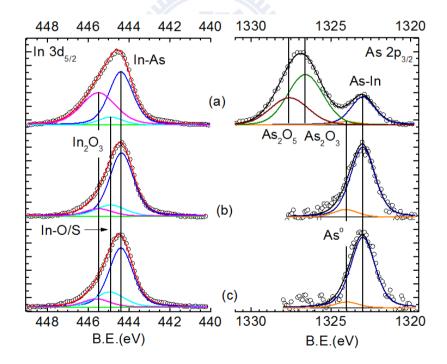

| <b>Figure 4.1.</b> The In $3d_{5/2}$ and As $2p_{3/2}$ XPS spectra of a- native-oxide-covered InAs surface; b- 1.5 nm ALD Al <sub>2</sub> O <sub>3</sub> /HCl+TMA treated InAs interface; c- 1.5 nm ALD Al <sub>2</sub> O <sub>3</sub> /sulfide+TMA treated InAs interface. Native oxides including In <sub>2</sub> O <sub>3</sub> , As <sub>2</sub> O <sub>3</sub> , and As <sub>2</sub> O <sub>5</sub> were significantly reduced after the use of surface treatments |

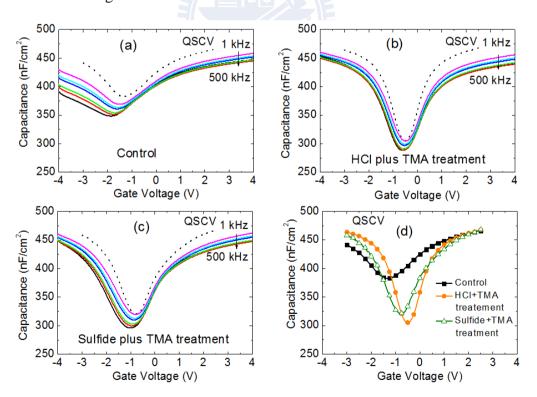

| <b>Figure 4.2.</b> Multi-frequency C-V responses (solid lines) and QSCV curves (dashed lines) in a- control sample, b- HCl plus TMA sample, and c- sulfide plus TMA treated sample of 18 nm ALD Al <sub>2</sub> O <sub>3</sub> /InAs MOSCAPs; d- QSCV curves of all three samples, for comparison                                                                                                                                                                       |

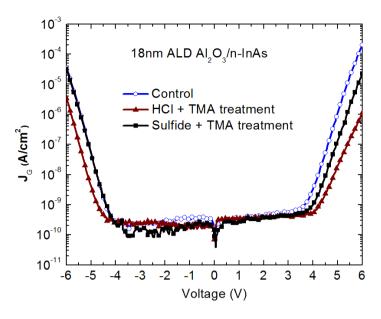

| <b>Figure 4.3.</b> Leakage currents versus gate voltage of samples                                                                                                                                                                                                                                                                                                                                                                                                      |

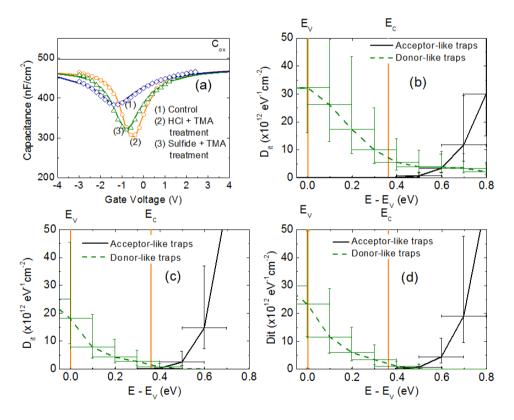

| Figure 4.4. a- Experimental data (symbols), simulated C-V curves (solid lines) of ALD                                                                                                                                                                                                                                                                                                                                                                                   |

| 18 nm Al <sub>2</sub> O <sub>3</sub> /n-InAs MOSCAP samples with various surface treatments. Interface state                                                                                                                                                                                                                                                                                                                                                            |

| density profiles of all three samples, extracted from simulation, are shown as well: b-                                                                                                                                                                                                                                                                                                                                                                                 |

| control sample, c- HCl plus TMA treated sample, d- sulfide plus TMA treated sample 70                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 5.1. Multi-frequency C-V responses in a- TMA treated-; b- sulfide + TMA treated                                                                                                                                                                                                                                                                                                                                                                                  |

| Al <sub>2</sub> O <sub>3</sub> /n-In <sub>0.53</sub> Ga <sub>0.47</sub> As MOSCAPs, with post deposition annealing in N <sub>2</sub> gas. The inset in                                                                                                                                                                                                                                                                                                                  |

| figure 5.1b shows the conductance - voltage (G-V) characteristics of the sample S276                                                                                                                                                                                                                                                                                                                                                                                    |

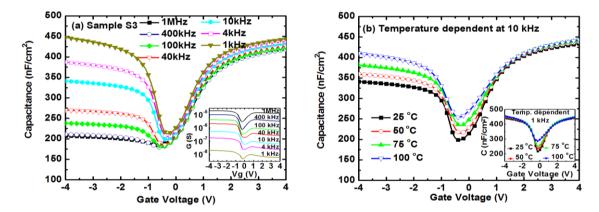

| Figure 5.2. a- Multi a frequency C-V responses in sulfide + TMA treated Al <sub>2</sub> O <sub>3</sub> /n-               |

|--------------------------------------------------------------------------------------------------------------------------|

| $In_{0.53}Ga_{0.47}As$ MOSCAPs, with post deposition annealing in $H_2$ gas; b- The temperature                          |

| dependent C-V responses at 10 kHz of the same sample. The inset in Fig. 5.2a shows the                                   |

| conductance-voltage (G-V) characteristics; the inset in Fig. 5.2b shows the temperature                                  |

| dependent C-V responses at 1 kHz                                                                                         |

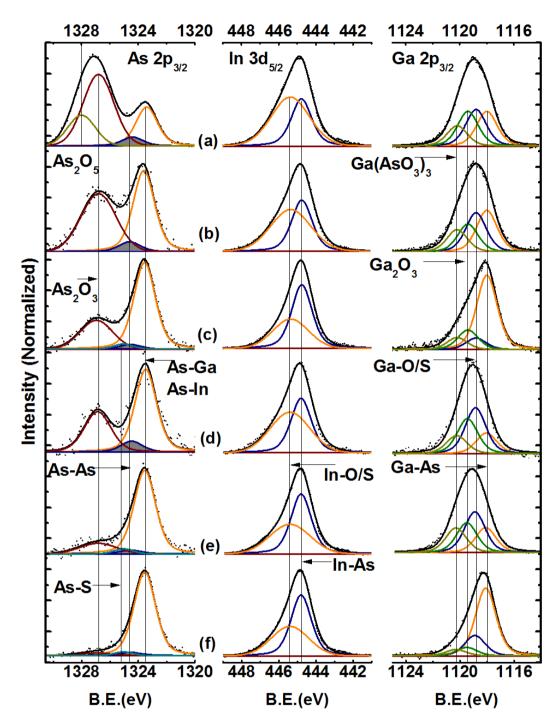

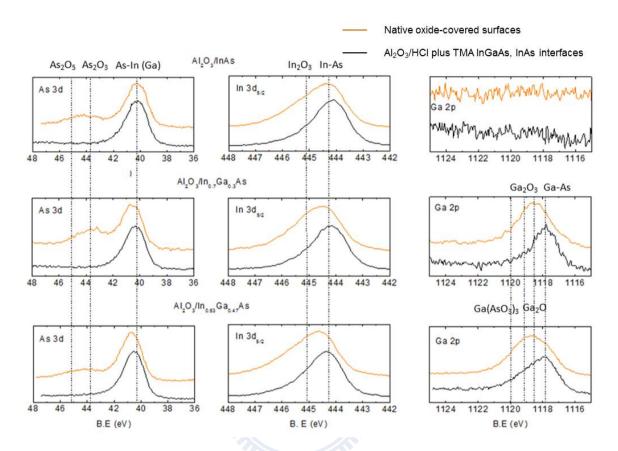

| Figure 5.3. The As 2p <sub>3/2</sub> , In 3d <sub>5/2</sub> , Ga 2p <sub>3/2</sub> XPS spectra of a Native oxide-covered |

| InGaAs surface; b- TMA treated sample, with ALD Al <sub>2</sub> O <sub>3</sub> , as deposited; c- sulfide +              |

| TMA treated sample, with ALD Al <sub>2</sub> O <sub>3</sub> , as deposited; d- TMA treated sample, with ALD              |

| $Al_2O_3$ , after PDA in $N_2$ ; e- Sulfide + TMA treated sample, with ALD $Al_2O_3$ , after PDA in                      |

| $N_2$ ; f- Sulfide + TMA treated sample , with ALD $Al_2O_3$ , after PDA in $H_2$ 79                                     |

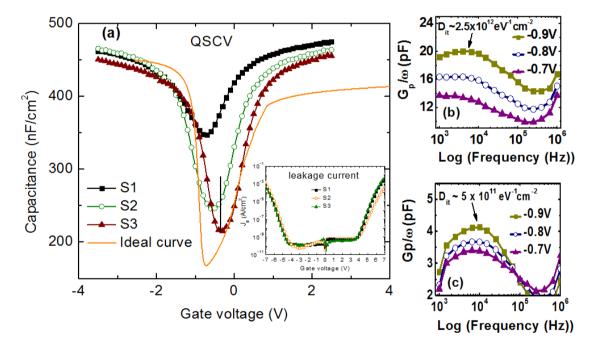

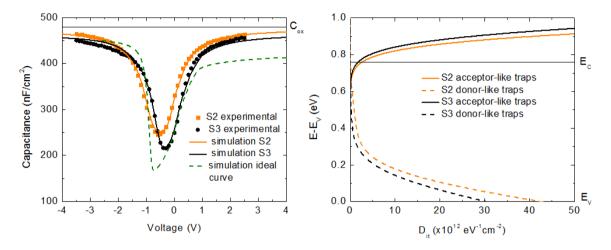

| Figure 5.4. a-The comparison of QSCV responses of sample S1, sample S2 and sample                                        |

| S3 and ideal C-V curve (without D <sub>it</sub> ) obtained by simulation. The inset shows the leakage                    |

| of samples for ensuring the accuracy of measurement; b- and c- The $G_p/\omega$ - $f$ curves of                          |

| sample S1 and sample S2, where $G_p$ is the parallel conductance and $\boldsymbol{\omega}$ is the measured               |

| angular frequency80                                                                                                      |

| Figure 5.5. a- Quasi-static C-V data of sample S2 and S3 (symbols) are fitted well with                                  |

| corresponding simulated data (solids). The ideal C-V curve is also showed as well (dash                                  |

| line); b- "U-shape" Dit profiles of samples S2 and S3 extracted from simulation                                          |

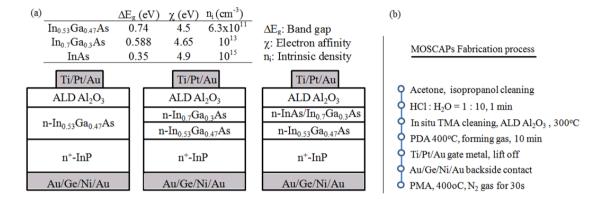

| Figure 6.1. a- Parameters of InGaAs compound and schematic of Al <sub>2</sub> O <sub>3</sub> /n-InGaAs                   |

| MOSCAPs structures with the In content is 0.53, 0.7, and 1; b- Summary of process flow                                   |

| for MOSCAP fabrication                                                                                                   |

| <b>Figure 6.2.</b> As 3d and In 3d <sub>5/2</sub> XPS spectra of (a) native-oxide-corvered InAs surface and              |

| (b) 1.5 nm Al <sub>2</sub> O <sub>3</sub> /InGaAs, InAs structures, as deposition. After using surface treatment         |

| and oxide depositon, As-related oxides were reduced to under XPS detection level, the                                    |

| Ga-O and In-O bonds were also significant removed                                                                        |

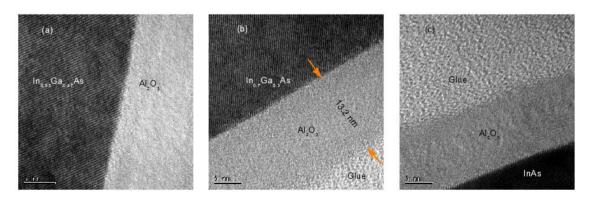

| <b>Figure 6.3.</b> High-resolution transmission electron microscopy micrographs of 13nm ALD                              |

| Al <sub>2</sub> O <sub>3</sub> /InGaAs structures after PDA at 400°C in forming gas, showing abrupt                      |

| Al <sub>2</sub> O <sub>3</sub> /InGaAs, InAs interfaces                                                                  |

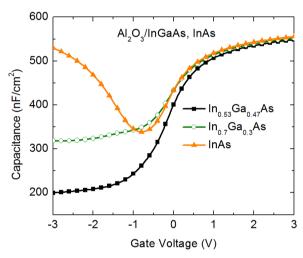

| Figure 6.4. Capacitance voltage responses at measured frequency of 1 MHz of                                              |

| Al <sub>2</sub> O <sub>3</sub> /In <sub>x</sub> Ga <sub>1-x</sub> As MOSCAPs with different In content                   |

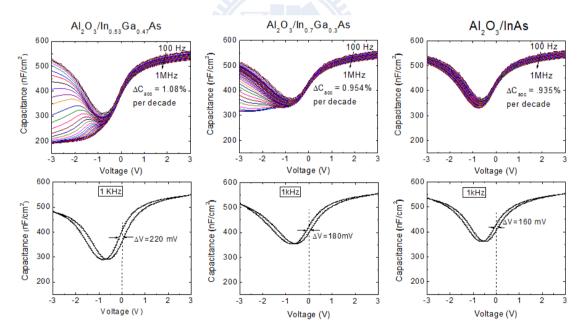

| Figure 6.5. Multi-frequency and bidirectional C-V responses of of Al <sub>2</sub> O <sub>3</sub> /In <sub>x</sub> Ga <sub>1-x</sub> As                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOSCAPs with different In content90                                                                                                                                       |

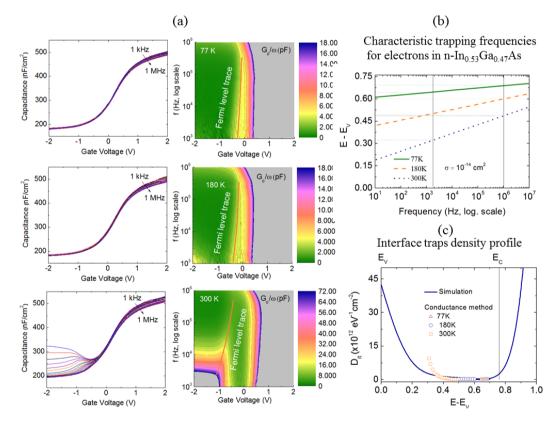

| Figure 6.6. Multi-frequency C-V responses and conductance contours $G_p/\omega$ (f, V) at                                                                                 |

| different temperatures (77 K, 180 K and 300 K) of $Al_2O_3/In_{0.53}Ga_{0.47}As$ . Peaks of                                                                               |

| conductance shows the traces of Fermi level movement (solid lines)91                                                                                                      |

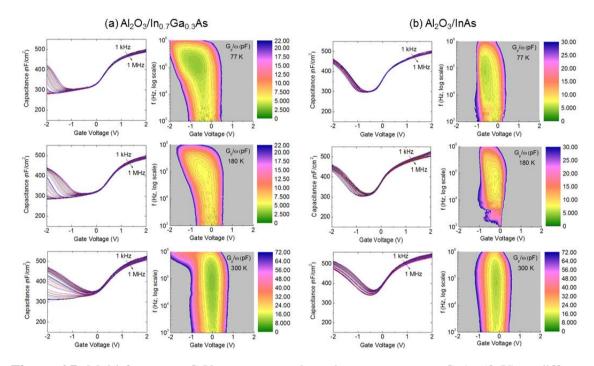

| Figure 6.7. Multi-frequency C-V responses and conductance contours $Gp/\omega$ (f, V) at                                                                                  |

| different temperatures (77 K, 180 K and 300 K) of $Al_2O_3/In_{0.7}Ga_{0.3}As$ , $Al_2O_3/InAs$                                                                           |

| MOSCAPs. Conductance contours are closed due to the contribution of inversion layer                                                                                       |

| and thus, the Fermi level traces could not show up92                                                                                                                      |

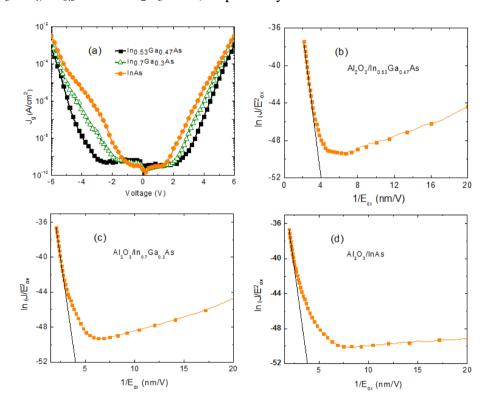

| Figure 6.8. a- leakage current increases with increasing of In content in InGaAs. The                                                                                     |

| $Flower-Nordheim\ plot\ for\ b-\ Al_{2}O_{3}/In_{0.53}Ga_{0.47}As,\ c-\ Al_{2}O_{3}/In_{0.7}Ga_{0.3}As\ and\ d-Al_{2}O_{3}/InAs(a)=0.00000000000000000000000000000000000$ |

| structures                                                                                                                                                                |

# LIST OF TABLES

| Table 1.1. Band gap, bulk carrier mobility, and intrinsic carrier density of S | i, Ge and III- |

|--------------------------------------------------------------------------------|----------------|

| V compounds                                                                    | 12             |

| <b>Table 2.1.</b> Relationships between characteristics and advantages of ALD  | 29             |

# LIST OF SYMBOLS

| Symbol                         | Unit              | Description                                                                |

|--------------------------------|-------------------|----------------------------------------------------------------------------|

| A                              | $m^2$             | Area                                                                       |

| $C_{dep}$                      | F/m <sup>2</sup>  | MOS capacitance in depletion                                               |

| $C_{it}$                       | F/m <sup>2</sup>  | Interface trap capacitance                                                 |

| $C_{ox}$                       | F/m <sup>2</sup>  | Oxide capacitance                                                          |

| $C_{m}$                        | F/m <sup>2</sup>  | Measured capacitance                                                       |

| $C_{s}$                        | F/m <sup>2</sup>  | Semiconductor capacitance                                                  |

| $D_{it}$                       | $eV^{-1}m^{-2}$   | Interface trap density, interface states density                           |

| ΔΕ                             | eV                | Energy difference between a trap and a band                                |

| $E_B$                          | eV                | Electron binding energy                                                    |

| $E_{C}$                        | eV                | Conductance band minimum level                                             |

| $E_g$                          | eV                | Semiconductor bandgap                                                      |

| $E_{i}$                        | eV                | Intrinsic energy level                                                     |

| $E_{F}$                        | eV                | Fermi level                                                                |

| $E_{V}$                        | eV                | Valence band maximum level                                                 |

| $\epsilon_0$                   | F/m               | Vacuum dielectric permittivity                                             |

| $\varepsilon_{\mathrm{SiO}_2}$ | -                 | Relative dielectric permittivity (dielectric constant) of SiO <sub>2</sub> |

| $\epsilon_{ m k}$              | -                 | Relative dielectric permittivity (dielectric constant) of high k           |

|                                |                   | materials                                                                  |

| f                              | Hz                | Frequency                                                                  |

| $G_p$                          | S                 | Parallel conductance                                                       |

| $G_{m}$                        | S                 | Measured conductance                                                       |

| $I_d$                          | A, A/m            | Drain current in a MOSFET                                                  |

| $I_{g}$                        | A                 | Gate current in a MOSCAP structure                                         |

| k                              | J/K               | Boltzmann's constant                                                       |

| $m_e$                          | kg                | Electron mass                                                              |

| m*                             | kg                | Effective electron mass                                                    |

| $n_i$                          | $\mathrm{m}^{-3}$ | Intrinsic carrier concentration                                            |

| $N_A$                          | $\mathrm{m}^{-3}$ | Density of acceptor dopant atoms                                           |

| $N_{\rm C}$                    | $m^{-3}$          | Density of states in conductance band                                      |

| Symbol            | Unit              | Description                               |

|-------------------|-------------------|-------------------------------------------|

| $N_D$             | m <sup>-3</sup>   | Density of donor dopant atoms             |

| $N_{\mathrm{V}}$  | $\mathrm{m}^{-3}$ | Density of states in valence band         |

| ω                 | Hz                | Angular frequency                         |

| q                 | C                 | Elementary charge                         |

| $Q_{\mathrm{M}}$  | C                 | Metal charge in MOSCAP structure          |

| $Q_s$             | C                 | Semiconductor charge in MOSCAP structure  |

| σ                 | $m^2$             | Trap capture cross section                |

| T                 | K, °C             | Temperature                               |

| $t_{ox}$          | m                 | Oxide thickness                           |

| $	au_{it}$        | S                 | Interface trap time constant              |

| $V_{\mathrm{F}}$  | V                 | Flat band voltage of MOSCAP               |

| $V_{\mathrm{G}}$  | V                 | Gate voltage in a MOSCAP                  |

| $v_{th}$          | m/s               | Thermal velocity of a charge carrier      |

| $\mu,\mu_n,\mu_p$ | $m^2/V.s$         | Mobility, mobility of electrons and holes |

| χ                 | eV                | Electron affinity                         |

# LIST OF ACRONYMS

| Symbol | Description                                      |

|--------|--------------------------------------------------|

| ALD    | Atomic Layer Deposition                          |

| ALE    | Atomic Layer Epitaxy                             |

| ALCVD  | Atomic Layer Chemical Vapor Deposition           |

| CMOS   | Complement Metal Oxide Semiconductor             |

| C-V    | Capacitance-Voltage                              |

| CET    | Capacitance Equivalent Thickness                 |

| EOT    | Equivalent Oxide Thickness                       |

| ESCA   | Electron Spectroscopy for Chemical Analysis      |

| HRTEM  | High-resolution Transmission Electron Microscopy |

| G-V    | Conductance-Voltage                              |

| I-V    | Current-Voltage                                  |

| MBE    | Molecular Beam Epitaxy                           |

| MOS    | Metal Oxide Semiconductor                        |

| MOSCAP | Metal Oxide Semiconductor Capacitor              |

| MOSFET | Metal Oxide Semiconductor Transistor             |

| PDA    | Post Deposition Annealing                        |

| PMA    | Post Metal Annealing                             |

| QSCV   | Quasi-static Capacitance-Voltage                 |

| TMA    | Trimethyl Aluminum                               |

| XPS    | X-ray Photoelectron Spectroscopy                 |

# Chapter 1

# INTRODUCTION

This chapter begins with describing briefly the evolution of semiconductor industry from its commencement to present. Downscaling the parameters of devices according to Moore's Law is the key feature to continue the development of complementary metal-oxide-semiconductor (CMOS) technology. High k metal gate is a revolutionary change in the CMOS technology up to now. The scaling challenges and future trends in CMOS research are also discussed in this chapter. The motivation, challenges and current progress of high k/III-V MOSFET-one of the possible solution for future CMOS technology, are presented. Finally, the last part of this chapter presents the problems statement of the study on  $Al_2O_3/InGaAs$  interface engineering and the organization of this dissertation.

#### 1.1.An Overview of planar Si-based CMOS Technology

In November 2009, Intel announced that it would state production of microprocessors based on the newest 32 nm generation of logic technology [1]. This latest innovation in semiconductor industry demonstrates the progress of complementary metal-oxide-semiconductor (CMOS) technology from its commencement to present. The progress of semiconductor industry depends closely on the development of the metal-oxide-semiconductor field effect transistor (MOSFET), the key component in integrated circuits.

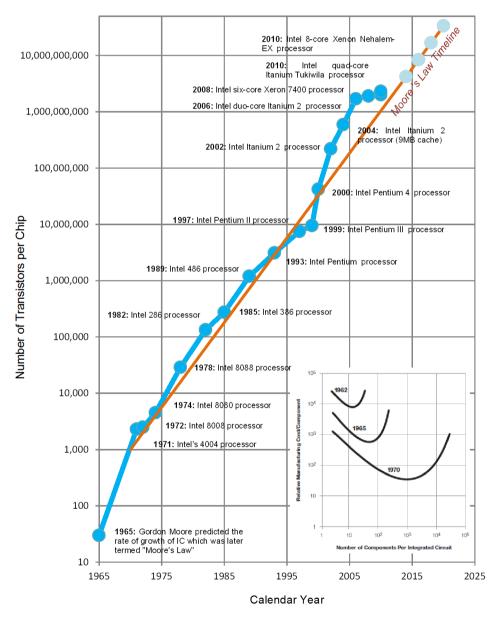

**Figure 1.1.** "The number of transistors incorporated in a chip will approximately double every 24 months": Moore's Law Timeline (solid) and the number of transistors per chip in Intel's products (line plus symbols). The inset is Moore's original prediction graph in 1965 [2].

Looking back to the past, the first transistor was invented by Brattain, Barden and Shockley in 1947 and the first integrated circuit was made independently of germanium by Jack Kilby in 1958 and of silicon by Robert Noyce in 1959. The first MOSFET on a silicon substrate was invented by Kahng and Atalla in 1960, 30 years after its principle was proposed by Lilienfield in 1930. Because SiO<sub>2</sub>/Si interface has very good quality and stability which allows the fabrication of high performance MOSFET, CMOS technology has been based on the high quality SiO<sub>2</sub>/Si interface.

In 1965 Electronics Magazine published a paper by Gordon Moore in which he predicted that the number of transistors incorporated in a chip will approximately double every 24 months [2]. This prediction is general known as Moore's Law (Moore's original prediction graph is shown in the inset of Fig. 1.1). Moore's Law has been guiding principle for the semiconductor industry for over 40 years [3], since Intel Corporation was co-founded by Gordon Moore and Robert Noyce in 1968. From that time, by downscaling device feature size, semiconductor industry has passed several generations and made a rapid pace of improvements in its products. Figure 1.1 shows the Moore's Law time line and the number of transistors per chip of Intel's products [2, 4]. The transistors per chip doubled after 2-years cadence has been preserved up to now. The number of transistors per chip was thousands in the early-1970s and has increased rapidly to billions recently.

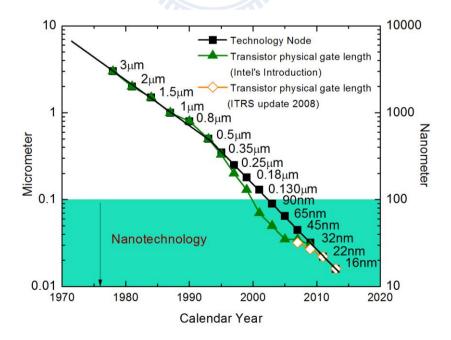

**Figure 1.2.** Scaling of logic technology node and correspond transistor's physical gate length (According to Intel's introduction until 2009 and ITRS update 2008)

Downscaling is the only effective way to increase the transistors density and to achieve high performance and low power consumption of logic CMOS operation. The MOSFET gate length and gate oxide thickness are the two critical parameters when shrinking its vertical and horizontal dimensions. To avoid short channel effect and maintain the electrostatic control of the channel when scaling gate length, the gate oxide thickness has to scale proportionally. As shown in Fig. 1.2, recently, the equivalent oxide thickness (EOT) and gate length have been reduced to 0.9 nm and 30 nm, respectively, in the 32 nm generation [1]. According to the International Technology Roadmap for Semiconductor 2008 (ITRS), the expected transistor's physical gate length for the next 22 nm generation is 20-22 nm in the end of 2011 and 16 nm for the following generation (Fig. 1.2).

Previously, the new generations of transistor technology had been developed simply by shrinking its vertical and horizontal dimensions. Since beginning of 2000s, the downscaling has not been so smooth any more. The 130 nm generation required the replacement of aluminum interconnects by cooper for lower resistance. The 90 nm generation used the strained silicon transistor for performance improvement. The 45nm generation introduced revolutionary high k dielectric and metal gate for improved performance and lower leakage current. The 32 nm generation requires a 2<sup>nd</sup> generation of high k metal gate transistors for future improvements in performance and power consumption. The introduction of high k metal gate technology is regarded as the biggest transistor advancement in 40 years by Intel's Co-Founder Gordon Moore.

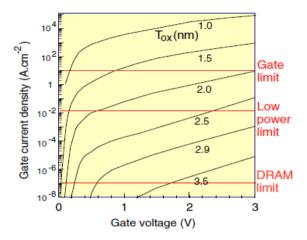

#### 1.2. High k, metal gate solutions

As mention above, reduction of gate oxide thickness always accompanies with the downscaling of CMOS technology. So far, we had no problem with the scaling thickness of SiO<sub>2</sub> or SiON as gate oxides and that had achieved MOSFET's devices with excellent performance. However, when the thickness of oxide reduces to smaller than 1.2 nm, the leakage problem becomes serious. At that thickness the leakage current becomes too high due to the direct tunneling of electrons through oxide (Fig. 1.3) [5, 6]. This high value of leakage current does not meet fully the requirement given by ITRS. Moreover, the reliability of the device is hampered by the time-dependent dielectric breakdown of ultrathin oxide layer [7, 8], as well as by bias temperature instabilities [9].

Figure 1.3. Leakage current versus voltage for various thickness of SiO<sub>2</sub> layers [5, 6]

A MOSFET is a capacitance-operated device, where the source-drain current depends on the gate capacitance:

$$C = \frac{\varepsilon_o \varepsilon_k A}{t} \tag{1.1}$$

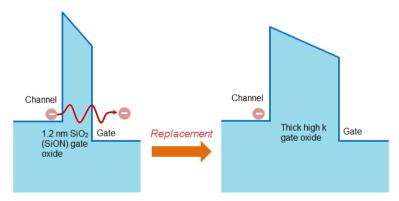

where  $\varepsilon_0$  is the permittivity of free space,  $\varepsilon_k$  is the relative permittivity, A is the area and t is oxide thickness. Since the leakage current is much dependent on the oxide thickness, to maintain the high value of capacitance with thick gate oxide, the value of  $\varepsilon_k$  need to increase. That means the gate oxide of silicon device has to be replaced by other materials with higher  $\varepsilon_k$  value, called high k oxides. High k value, in other words, can be described as physical thick but electrically thin materials [10]. Fig 1.4 shows the direct tunneling problem can be solved by replacing SiO<sub>2</sub> (SiON) with a physically thicker layer of high k materials [5, 10].

**Figure 1.4.** At the gate oxide thickness of 1.2 nm (5 layer of atoms), the wave describing the probable location of an electron is broader than the gate oxide and the electron can simply appear on the other side of gate oxide, meaning that direct tunneling of electrons through the insulation. New high k gate oxide is needed to plug the leak [10]

The concept of equivalent thickness oxide (EOT) is used to define an "electrical thickness" of new high k gate oxide [11]. The EOT refers to the thickness of any dielectric ( $t_k$ ) scaled by the ratio of its dielectric constant ( $\epsilon_k$ ) to that of SiO<sub>2</sub> ( $\epsilon_{SiO_2}$ )

$$EOT = t_k \frac{\varepsilon_{SiO_2}}{\varepsilon_k} = t_k \frac{3.9}{\varepsilon_k} \tag{1.2}$$

The extraction of EOT requires to fit capacitance-voltage (C-V) characteristics of the MOS structure, taking into account quantum confinement effect in accumulation and inversion layer [12]. Besides, another useful quantity for comparison between gate dielectrics is the capacitance equivalent thickness (CET), which is defined as [12]:

$$CET(V) = \frac{\varepsilon_o \varepsilon_{SiO_2}}{C(V)} = \frac{3.9 \varepsilon_o}{C(V)}$$

(1.3)

where C is the capacitance (per unit area) of MOS structure measured at a given gate bias. The extraction of CET does not require to fit C-V data, but depends on the chosen gate bias. CET can also be influenced by gate leakage in leaky devices [12].

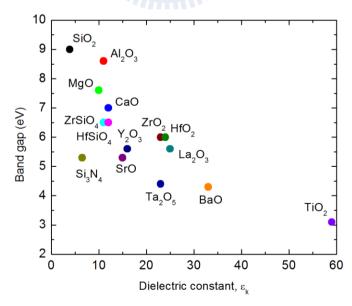

The interest in high k dielectric research to replace SiO<sub>2</sub> started in the 1980s and renewed in the mid-1990s when the problem of leakage has become more serious. Figure 1.5 shows the parameters (dielectric constant versus band gap) of the candidate oxides [5, 13].

Figure 1.5. Static dielectric constant versus band gap for candidate gate oxides [5, 13]

In general, the relationship between dielectric constant and the band gap is reverse as shown in Fig. 1.5. Thus, the selected high k oxide has to be trade-off between dielectric

constant and band gap. Band gap must be large enough to have conductance band (CB) and valence band (VB) offsets with semiconductor over 1 eV to minimize the carriers' injection into its bands [5, 12]. In practice, the CB offset is smaller than VB offset, so that this limits the choice of oxide to those with band gaps over 5 eV [5, 12, 13]. The relative dielectric constant should be somewhere between 10 and 30. Besides, other important requirements for selecting high k also have to be considered, including: thermodynamic stability with Si (and also future channel materials), low interface charge traps (typically less than  $10^{11}$  eV<sup>-1</sup>cm<sup>-2</sup>), low bulk electrically active defects, and kinetically stable and compatible to process at high temperature [5, 12].

In terms of band gap and  $\varepsilon_k$  values, many high k materials have been selected for study for gate oxide application including Al<sub>2</sub>O<sub>3</sub>, ZrO<sub>2</sub>, HfO<sub>2</sub>, Y<sub>2</sub>O<sub>3</sub>, La<sub>2</sub>O<sub>3</sub>, and various lanthanides as well as their silicates and aluminates [13-16]. After thorough research, HfO<sub>2</sub> and its silicate, HfSiO<sub>x</sub> have emerged as promising candidates because of their excellent thermal stability with Si. HfO<sub>2</sub> with a  $\varepsilon_k$  value between 16-20, energy band gap of about 5.4 eV, CB and VB offsets with Si of 1.5 eV and 3.4 eV respectively, has been used for the 45 nm and the recent 32 nm generations.

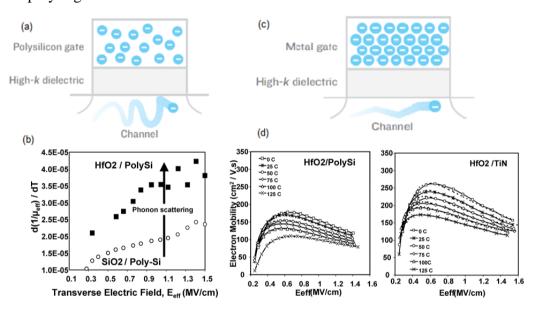

Transistors with high k gate dielectric were processed with pretty much identical to the existing transistor with SiO<sub>2</sub> (SiON) gate dielectric. However, it was found that, high k gate dielectric transistors had suffered a few problems including (1) it took more voltage to turn them on than it should have, and (2) once the transistor was on, the charge move sluggishly though them, slowing the device's switching speed [10]. The first problem is known as Fermi level pinning (FLP) at polysilicon gate and high k dielectric interface [10, 17]. The effective work function (EWF) of polysilicon could not be altered easily by doping when it was used with high k dielectric. It was found that the EWF of polysilicon/HfO<sub>2</sub> stack is determined by Si-Hf bonds instead of Fermi level of polysilicon gate [17]. The EWF of polysilicon in that case was fixed at certain point near the Si conductance band edge, resulting in very high threshold voltage V<sub>th</sub> in PMOS devices. The second problem is known as low charge-carrier mobility or the channel mobility degradation when using high k gate dielectrics [18, 19]. Essentially, high k materials are made up of dipoles and having a large polarization. This large polarization leads to strong vibrations in a semiconductor's crystal lattice (phonons), resulting in the increase of electron-scattering (Fig. 1.6.a) and thus, reducing their mobility [20]. Research by M. V. Fischetti et al. also showed that the metal gate with high electron density can screen out

the effect of phonons on channel electrons (Fig. 1.6.c) [10, 20]. Experimental data by R. Chau et al. shows clearly effect of phonon-electron scattering by using high k/polySi gate stack (Fig. 1.6.b) and the electron mobility can be improved by using high k/metal gate stack (Fig. 1.6.d) [21]. Besides, the bond between the high k dielectric and the metal gate would be so much better than that between high k and polySi. Thus, the use of gate metal with sufficient value of work function can eliminate the FLP problem of polysilicon gate and allow moderating the threshold voltage of devices. By using gate metal, it is also possible to achieve lower CET value at inversion regime, lower gate resistance, and eliminate the boron penetration into the dielectric and transistor channel as suffering in case of polySi gate.

**Figure 1.6.** a-Electron density in PolySi gate is not large enough to screen the effect of high k dipoles on semiconductor lattice points, lead to strong phonon-electron scattering; b-Experimental evidence of phonon scattering in the high k dielectric. The net value of the temperature (T) sensitivity factor,  $d(1/\mu_{eff})/dT$ , is negative when coulombic scattering dominates and positive when phonon scattering dominates. [21]; c-Metal gate with high electron density can screen out the vibrations, reduce effect of phonon scattering; d-Experimental (symbols) and simulation (dash lines) data show the improvement of electron mobility by using high k/metal gate stack [21].

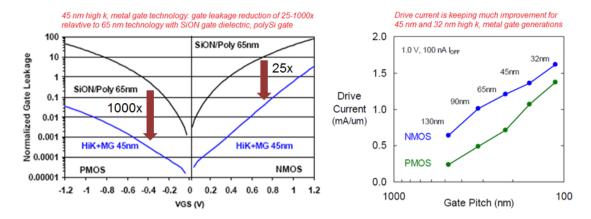

So far, we have discussed about the replacement of high k dielectric for SiO<sub>2</sub> (SiON) to solve leakage problem. Then, the problems suffering from high k/ Si channel and high k/polySi contact have been also discussed and gate metal replaces for polySi is a solution for these problems. For conclusions, let us take a look to see how good the improvements of devices are for the generations of high k metal gate MOSFETs (Fig. 1.7) [22-24].

**Figure 1.7.** The improvements of leakage current and drive currents by using high k metal gate generations [22-24]

#### 1.3. Scaling challenges and future trends

#### 1.3.1. Scaling challengers

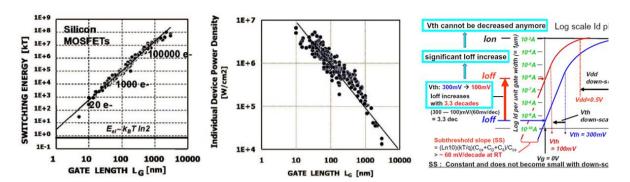

Beyond the 32 nm generation, the CMOS technology faces a number of scaling challenges which need to be addressed. Off-state current, I<sub>off</sub> increases from the degraded drain-induces barrier lowering (DIBL) and subthreshold slope (SS). These degradations cause by short channel effect (SCE) which leads to limitation for the effective gate length, l<sub>eff</sub> shorter than 15 nm [25]. The decrease of gate oxide thickness for better channel control accompanies with a penalty of increased leakage current and increased channel doping concentration. The increase of channel doping concentration results in the decrease of carrier mobility (due to impurity scattering) and the increase of random dopant fluctuations which leads to degrading the minimum operating voltage. Decreasing gate pitch increases the parasitic capacitance contribution for both contact to gate and epi to gate thus increase overall gate capacitance. Decreasing source/drain opening size results in increasing drain resistance, thus decreasing drive current [22, 25].

The power consumption is also the limiting factor of the logic MOS [26]. As downsizing the device's features, the switching energy of MOSFETs decrease but the power density increases (see Fig. 1.8) and thus, cause of system power consumption [27]. One of effective way to decrease the dynamic power consumption is lowering supply voltage. However, in order to reduce supply voltage, the threshold voltage has to be reduced. This results in the significant increase of off- state current due to the increase of the subthreshold leakage current with low threshold voltage (Fig. 1.8, right) [26].

**Figure 1.8.** Illustration of the exponential decrease in switching energy (left) and the simultaneously increasing device power density (middle) as a consequence of device downscaling [27]. The increase of power density causes of power consumption issue, lowering supply voltage is not an easy way to reduce power consumption due to the increase of off state current,  $I_{off}$  (right) [26].

### 1.3.2. Future trends

For future CMOS technology, the interests have been focused on both structures and materials. In term of structures, the transition from present planar structure to non-planar structure such as multiple gate or multiple channel FET (MuGFETs or MuCFETs) has been proposed to deal with SCE degradation. These devices include double gate FET (DGFETs), tri gate FET, surround gate FET, and Si nanowire (Fig. 1.9) [3, 22, 26, 28]. A significant improvement of SCE and short-channel characteristics with high drive current performance has been demonstrated in tri gate transistors. These results demonstrate that the benefits of all different silicon innovations can be combined to extend and continue the CMOS scaling and performance trends [28]. The non-planar Si CMOS technology is expected to apply for 22 nm node and may be for 16 nm node generations. Beyond 16 nm, silicon will suffer its fundamental limits and will no longer provide the performance improvement of devices for downscaling.

Figure 1.9. Non-planar transistors: Double-gate transistor (left) and tri-gate transistor (right) [28]

In term of materials, much interest has been generated and good progress has been made in the research of non-silicon electronic materials for future logic applications, and their integration onto the silicon platform. The most studied materials are Ge, III-V compound semiconductors such as GaAs, InGaAs, InAs, and InSb, semiconductor nano wire, carbon nanotubes (CNTs), and graphene. In general, these materials have significantly higher intrinsic carriers (electron or hole) mobility than Si, and they have potential for enabling the future high-speed applications at very low power-supply voltages. Among these materials, Ge and III-V compounds are the most mature and practical because they can be integrated into a Si CMOS front-end process more easily than the other alternatives. Moreover, the knowledge about III-V compounds is much more than others because they have been used in communication and optoelectronic products for a long time. The ITRS's 2009 version predicted that III-V/Ge will replace Si as channel materials in 16 nm node CMOS technology and beyond. The advantages of III-V's properties against Si as channel material will be discussed in the next part.

# 1.4. III-V compound semiconductors for CMOS technology: motivation, challenges and current progress

#### 1.4.1. Motivation

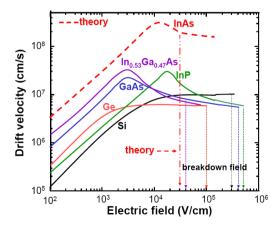

The key advantage of III-V compound semiconductors as compared to Si is their high electron mobility and high low-field saturation velocity. The electron mobility enhancement in III-V compounds comes from their lower electron effective mass than that of Si. Figure 1.10 and table 1.1 show electron drift velocities versus electric field and the parameters (carrier mobility, band gap, intrinsic density) of Si, Ge and III-V compounds.

**Figure. 1.10.** Electron velocities as a function of field of Si, Ge and III-V compound semiconductors. III-V compound semiconductors exhibit high saturation velocity at low electric field

**Table. 1.1.** Band gap, bulk carrier mobility, and intrinsic carrier density of Si, Ge and III-V compounds (data from reference [29])

|                                          | Si                   | Ge                   | GaAs                 | In <sub>0.53</sub> Ga <sub>0.47</sub> As | In <sub>0.7</sub> Ga <sub>0.3</sub> As | InAs                 | InSb                 |

|------------------------------------------|----------------------|----------------------|----------------------|------------------------------------------|----------------------------------------|----------------------|----------------------|

| Band gap, $E_g$ (eV)                     | 1.12                 | 0.66                 | 1.424                | 0.74                                     | 0.588                                  | 0.354                | 0.17                 |

| Bulk e mobility cm <sup>2</sup> /V s     | 1400                 | 3900                 | 8500                 | 12000                                    | 20000                                  | 40000                | 77000                |

| Bulk hole mobility cm <sup>2</sup> /V s  | 450                  | 1900                 | 400                  | 300                                      | 300÷400                                | 500                  | 850                  |

| Intrinsic concentration cm <sup>-3</sup> | 10                   | 2×10 <sup>13</sup>   | 2.1×10 <sup>6</sup>  | 6.3×10 <sup>11</sup>                     | 10 <sup>13</sup>                       | 10 <sup>15</sup>     | 2×10 <sup>16</sup>   |

| Conduction band DOS cm <sup>-3</sup>     | 3.2×10 <sup>19</sup> | 1.0×10 <sup>19</sup> | 4.7×10 <sup>17</sup> | $2.1 \times 10^{17}$                     | -                                      | $8.7 \times 10^{16}$ | $4.2 \times 10^{16}$ |

In very short channel length MOSFETs, the carriers exhibit quasi-ballistic transport. In this case the drive current is not depended on saturation velocity but is determined by carrier injection from the source to drain, i.e. injection velocity,  $v_{inj}$  [30]. The carrier injection relates directly to the carrier mobility at low field and thus, the concept of mobility continues to have relevance to ultra-short channel MOSFETs [30]. The use of III-V materials as an alternative channel for Si is due to their advantages in two major requirements for high-performance logic devices: increased speed and reduced power consumption while the integration density keeps increasing [31].

In term of device's speed, the intrinsic delay time  $\tau_i$  can be approximated as:

$$\tau_i \approx \frac{Q}{I_{Dsat}} \approx C_G \frac{V_D}{I_{Dsat}}$$

(1.4)

which assumes switching the channel charge Q on the gate capacitance  $C_G$  by a constant "ON" drain current  $I_{Dsat}$  between two logic states with a voltage swing across the channel equal to power supply voltage. The current is measured in saturation with equal gate and drain voltage,  $V_{GS}=V_{DS}=V_D$ . For channel materials comparison, it is good enough to approximate the intrinsic delay time as:

$$\tau_i \approx \frac{L_G}{v_{inj}} \tag{1.5}$$

The extrinsic delay time  $\tau_{ext}$  can be estimate as:

$$\tau_{ext} \approx C_{ext} \frac{V_D}{I_{Dsat}} \tag{1.6}$$

where  $C_{ext}$  is total capacitance including gate capacitance  $C_G$  and interconnect parasitic capacitance. Because III-V compound have low effective mass and high electron mobility, the injection velocity in these materials is much higher than that of silicon, as shown in Fig. 1.10 and table 1.1 (injection velocity was measured ~ 2.5-3 × 10<sup>7</sup> cm/s in InGaAs and InAs, at least two time higher than strain n-Si MOSFETs [32, 33]). According to equations (1.4), (1.5) and (1.6), this high injection velocity explains why III-V MOSFETs are expected to get higher switching speed, higher drive current than Si MOSFETs.

In term of power, MOSFETs have mostly capacitive input impedance and a certain energy is require to recharge the gate capacitance [31]. The charging energy depends on distribution of carrier in the channel and capacitance change below threshold. Therefore, it is assumed that the dynamic energy is proportional to  $C_gV_D^2$  per bit and it combines with intrinsic delay time  $\tau_i$  to become intrinsic energy-delay product (EDP<sub>i</sub>):

$$EDP_i = \frac{C_G V_D^2 \tau_i}{W} \tag{1.7}$$

where W is the channel width. Related to materials properties, the switching energy is proportional to  $Q^2/C_g$  or just  $\propto n^2$  (n is the electron concentration in the channel, proportional to electron effective mass  $m^*$ ) for intrinsic power, if only the channel materials-related are considered and  $C_{ext}V_D^2$  if large extrinsic capacitance is charging. Then the intrinsic and extrinsic energy-delay products can be expressed through the materials-related parameters:

$$EDP_i \propto \frac{n^2}{v_{inj}} \propto m^{*\frac{5}{2}} \text{ and } EDP_{ext} \propto \frac{V_D^3}{nv_{inj}} \propto \frac{V_D^3}{\sqrt{m^*}}$$

(1.8)

From here, it is clear to see that the III-V channel is considerably more favorable than Si in reducing energy-delay products even in the architectures with large parasitic. This because in the ballistic regime (ultra-short channel) with large parasitic, EDP improvement results from the ability to get high drain current at low voltage overdrive  $V_D$ - $V_T$  where  $V_T$  is threshold voltage. Due to high low field electron mobility in III-V compounds, the supply voltage  $V_D$  can be reduced while the value of  $V_T$  can keep relative high to maintain low threshold leakage current i.e., low static power [31].

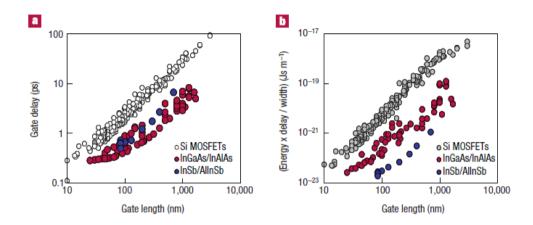

**Figure. 1.11**. III–V HEMTs characteristics compared with standard silicon MOSFETs a, Intrinsic gate delay. b, Normalized energy-delay product of n-channel InSb and InGaAs HEMTs [28, 34]

For highlight the advantages of III-V compounds in speed and power improvements, recent work on InGaAs, InSb n-channels high electron mobility transistors (HEMTs) have demonstrated the significantly reduction of gate intrinsic delay as well as EDPs as compared to standard Si MOSFETs (Fig. 1.11) [28, 34]. Both n- and p- channel InSb HEMTs have been demonstrated very high speed at a low supply voltage of only 0.5 V [35, 36]. Compared with state-of-the-art silicon transistors, these n-channel III–V transistors show either a 1.5-fold improvement in intrinsic speed performance at the same power, or 10-fold reduction in power for the same speed performance [35]. The p-channel HEMTs also show either a 2-fold improvement in intrinsic speed performance at the same power, or 10-fold reduction in power for the same speed performance as compared to p-channel Si MOSFETs [36].

Another advantage of III-V materials is the band structure. InGaAs, InAs compounds have large band off-set with the barrier and large separation between high electron-effective-mass L- and X-valleys and low electron-effective-mass  $\Gamma$ -valley. This allows to get high number of electrons in the  $\Gamma$ -valley and consequently get high drive current [31].

#### 1.4.2. Challenges

Although III-V based MOSFETs give a significantly advantages for future CMOS technology, there are some challenges which need to be addressed. Although band structure have large separation between valleys, III-V materials have low density of state (DOS) in the low effective-mass  $\Gamma$ -valley (Tab. 1.1) [29]. This low DOS tends to reduce inversion charge ( $Q_{inv}$ ) and hence reduce drive current. The small direct band gap of III-V

MOSFETs inherently gives rise to very large band to band tunneling (BTBT) leakage current as compared to Si. They also have a high permittivity and hence are more prone to short channel effect (SCE). Non-planar technique may also need to be applied to III-V MOSFETs to improve the electrostatics with scaling [28].