# 國 立 交 通 大 學

工學院半導體材料與製程設備學程

## 碩 士 論 文

退火溫度和表面處理對IGZO元件的影響

Effect of anneal temperature and plasma treatment on the performance of IGZO

研 究 生 : 高 逸 群

指 導 教 授 : 吳 耀 銓 教 授

中華民國 一〇〇 年 六 月

退火溫度和表面處理對IGZO元件的影響

Effect of anneal temperature and plasma treatment on the

performance of IGZO

研究 生：高逸群

Student : Yi-Chun Kao

指導教授：吳耀銓 博士

Advisor : Dr. Yew-Chung Sermon Yu

國 立 交 通 大 學

工學院半導體材料與製程設備學程

A Thesis

Submitted to Degree Program of Semiconductor Material and Process

Equipment

College of Engineering

National Chiao Tung University

in Partial Fulfillment of the Requirements

for the Degree of

Master of science

in

Degree Program of Semiconductor Material and Process Equipment

June 2011

Hsinchu, Taiwan, Republic of China

中華民國 一〇〇 年 六 月

# 退火溫度和表面處理對IGZO元件的影響

研究生：高逸群

指導教授：吳耀銓博士

國立交通大學工學院半導體材料與製程設備學程碩士班

## 摘要

近年來平面顯示器的規格隨著面板尺寸越來越大及解析度越來越高的需求，對陣列製程的要求也越來越嚴格，例如金屬導線對阻抗值的要求，由早期的Mo製程，到後來的鋁合金製程，到現在常用的純鋁製程，接下來的銅製程，這些製程不斷改進，都是為了解決面板在大型化和高解析度化後所面臨的RC負載問題。解決面板的導線阻抗問題後，再來則是寄生電容的負載問題和元件的充電問題。從常用的非晶矽元件發展到低溫多晶矽元件，主要是為了提升元件充電能力，進而縮小元件尺寸。

雖然低溫多晶矽元件可以改善非晶矽元件的元件特性，但設備投資成本較高，且元件均勻性容易因為雷射退火條件不易控制，而造成元件均勻性不佳。

因此，有許多研究單位和面板製造商投資大量成本來開發氧化物半導體，從早期的ZnO元件到後來各種不同的氧化物半導體，都相繼發表。但氧化物半導體最大的問題則是元件穩定性不佳，所以，各家製造商都會在現有材料中摻雜各種不同的元素，改善元件穩定性。

目前最熱門的其中一個材料就是氧化銻鎵鋅，也被視為最有機會取代非晶矽材料之一，因此我們也希望利用不同的退火條件和表面處理的方式來改善氧化銻鎵鋅元件穩定性，進而開發適合氧化銻鎵鋅元件的製程流程。所以我們對IGZO薄膜做以下不同退火參數和表面處理參數的探討。

在330°C的退火溫度下，可以得到比較高的導通電流，若再經過N<sub>2</sub>O

電漿表面處理後的元件，其元件的穩定度也會相對的提高。元件在經過N<sub>2</sub>O表面處理和2個小時的330°C退火後元件的Ion電流為6.4E-5A，mobility 11 cm<sup>2</sup>/V-s，元件在V<sub>gs</sub> 50V；V<sub>d</sub>=V<sub>s</sub>=0V條件下劣化，在經過2000秒後，啓始電壓漂移量為2.62V；元件在V<sub>gs</sub> 5Vh和V<sub>d</sub>=15V and V<sub>s</sub>=0條件下劣化，在經過2000秒後，啓始電壓漂移量為0.44V。

# **Effect of anneal temperature and plasma treatment on the performance of IGZO**

**Student : Yi-Chun Kao**

**Advisor : Dr. Yew-Chung Sermon Wu**

**Degree Program of Semiconductor Material and Process Equipment**

**College of Engineering

National Chiao Tung University**

## **Abstract**

In recent years, as far as the specifications of the flat panel displays are concerned, with the need to scale up the panel size and increase the resolution, the requirements of the array process are becoming more demanding. Take the requirement of the metal line resistance for example, the processes have been improved from the earlier Mo process, Al alloy process, pure Al process used frequently nowadays, to the coming Cu process, all of these process improvements have been made to solve the problem on the RC load effect faced with while scaling up the panels and increasing the resolution. After solving the problem on the metal line resistance of panels, there still are problems on the parasitic capacity loading effect and the device charging. The main purpose to develop the frequently used Amorphous Silicon devices into Low Temperature Poly Silicon devices is to improve the charging ability of devices, and further, to shrink the device size.

Although Low Temperature Poly Silicon devices can improve the device performance of Amorphous Silicon devices, the costs of facility investment are higher and the device uniformity would be subject to the laser anneal conditions and becomes hard to control, which would in turn result in the bad device uniformity.

Therefore, a great number of the research institutes and the LCD makers are investing an enormous amount of money to develop the

**metal oxide semiconductors. The earlier ZnO devices and later metal oxide semiconductors have been sequentially launched. The biggest problem, however, is that the device stability is not good. Therefore, every manufacturer now is doping various elements into the current materials in order to improve the device stability.**

**Currently, one of the most popular materials is IGZO which is considered as one of the materials that are most likely to replace Amorphous Silicon. So we also hope to utilize different thermal anneal conditions and plasma treatment methods to improve the IGZO device stability, and further, to develop the process flows that are suitable for the IGZO devices. That is why we are probing into the IGZO thin film with various thermal anneal parameters and plasma treatment parameters as follows.**

**Devices can get higher operation current after 330°C anneal. And the IGZO film use the N<sub>2</sub>O treatment, the devices will get a better stability. Devices using the N<sub>2</sub>O surface treatment and 2hr 330°C final anneal, Ion of the devices is about 6.4E-5A, the mobility of the devices is about 11 cm<sup>2</sup>/V-s, the V<sub>th</sub> shift of the device is about 2.62V at stress time 2000 seconds in V<sub>gs</sub> 50V and V<sub>d</sub>=V<sub>s</sub>=0V. the V<sub>th</sub> shift of the device is about 0.44V at stress time 2000 seconds in V<sub>gs</sub> 5V and V<sub>d</sub> 15V and V<sub>s</sub> 0V .**

# 誌謝

在交大碩士班求學過程中，雖然經過五年的時間，這在一段漫長的光陰自己也學了許多過去所不懂的知識，也更充實自己。雖然一邊工作和一邊求學，這樣的生活總是非常的緊湊，看也因為老師的細心指導和家人的鼓舞，自己終於也能夠撐到這最後一課。

在此，我要感謝指導教授吳耀銓博士，能夠指導自己如何做好一份明確的研究方法，了解如何去組織問題的思考邏輯，並經過一連串的實驗和分析，來成就一份詳細的研究資料，更從研究實驗過程中來找出合理的結果。在此也感謝老師在論文指導上給予最大的寬容以及用心的修正學生在研究過程產生的錯誤。尤其是在論文接近完成的日子裏，不厭其煩的指導。對於兼顧工作和求學的我得到最有效的學習。

在此也有感謝口試委員陳智教授及侯智元博士，能夠在百忙之中撥空參與學生的論文計畫書口試，並給予寶貴的意見與指導。使得論文的研究方向和內容更加完善。

當然，更要感謝我的家人給予我的支持和鼓勵，讓我在工作之於還能夠專心的在課業上學習。尤其是自己的妻子嘉吟，除了白天上班之外，晚上還必須一個人照顧二個寶貝天昱和姝媛，更讓我在無後顧之憂的狀況完成這五年的學習。還有我的爸爸、媽媽，感謝你們的養育之恩，處處包容，更能用心陪伴我從小學習到工作，甚至於到

工作過程中的求學也一路鼓勵我，支持我到最後完成學業。

最後，還是要再次感謝在求學和工作過求中一路相伴的同學和同事，也因為有大家的幫忙，能讓自己得到更多的知識和學問，順利的完成學業。

學生 高逸群

# 目錄

|           |     |

|-----------|-----|

| 中文提要..... | i   |

| 英文提要..... | iii |

| 謝誌.....   | V   |

| 目錄.....   | vii |

| 圖目錄.....  | X   |

| 表目錄.....  | xiv |

|                                |    |

|--------------------------------|----|

| 第1章 前言 .....                   | 1  |

| 1-1 Metal oxide TFT 的歷史發展..... | 2  |

| 1-2 IGZO材料介紹.....              | 4  |

| 第2章 元件製程及設備介紹.....             | 6  |

| 2-1 元件製程流程.....                | 6  |

| 2-2 PVD和CVD製程介紹.....           | 8  |

| 2-2-1 PVD製程介紹.....             | 8  |

| 2-2-2 反應性濺鍍.....               | 10 |

| 2-2-3 CVD製程介紹.....             | 11 |

| 2-3 分析量測儀器介紹.....              | 13 |

| 2-3-1 X光光電子光譜儀.....            | 13 |

|                                        |    |

|----------------------------------------|----|

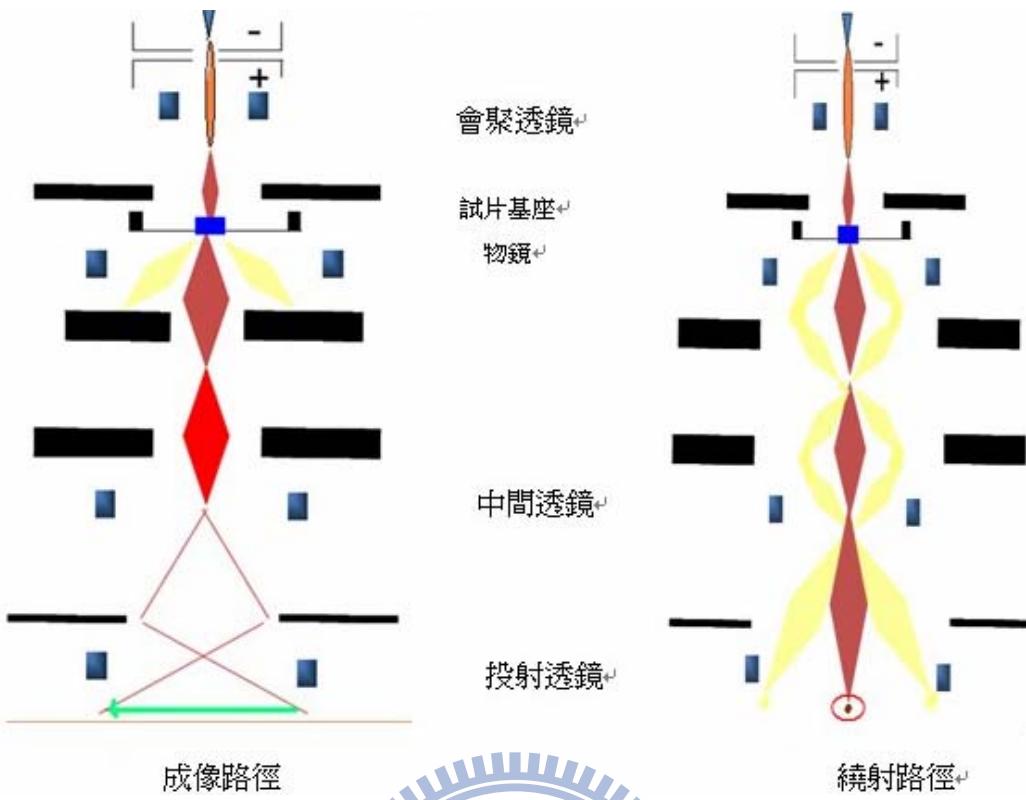

| 2-3-2 穿透式電子顯微鏡.....                    | 15 |

| (Transmission Electron Microscopy)     |    |

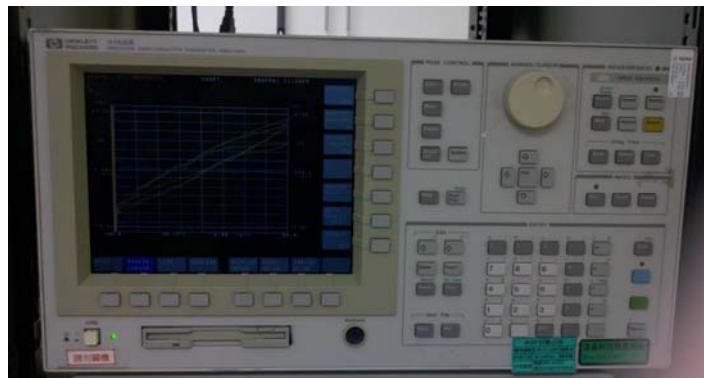

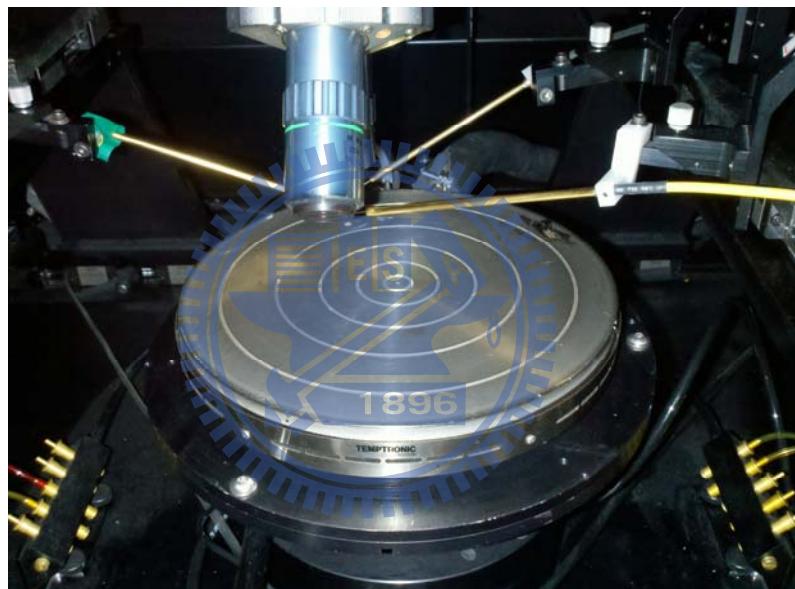

| 2-3-2 HP 4156和Probe station.....       | 17 |

| 第3章 實驗流程及數據分析.....                     | 18 |

| 3-1 實驗動機.....                          | 18 |

| 3-2 元件量測方式及參數.....                     | 19 |

| 3-3 實驗方式.....                          | 21 |

| 3-3-1 IGZO退火溫度對元件特性的影響.....            | 21 |

| 3-3-2 IGZO表面處理對元件的影響.....              | 23 |

| 第4章 實驗結果及討論.....                       | 25 |

| 4-1 元件電性改善.....                        | 25 |

| 4-1-1 電漿處理對和退火溫度對元件的影響.....            | 25 |

| 4-2 元件磁滯現象.....                        | 26 |

| 4-2-1 退火溫度對磁滯的改善.....                  | 26 |

| 4-2-2 N <sub>2</sub> 電漿處理對磁滯現象改善.....  | 28 |

| 4-2-3 N <sub>2</sub> O電漿處理對磁滯現象改善..... | 29 |

| 4-3 元件的stress改善.....                   | 32 |

| 4-3-1 電漿處理對PBTS現象改善.....               | 32 |

| 4-3-2 電漿處理對熱載子效應現象改善.....              | 35 |

|                               |    |

|-------------------------------|----|

| 4-4 討論.....                   | 38 |

| 4-4-1 退火溫度對TFT通道區阻抗的影響.....   | 38 |

| 4-4-2 電漿表面處理對TFT通道區阻抗的影響..... | 39 |

| 4-4-3 IGZO表面氧鍵結分析.....        | 42 |

| 4-4-4 電漿表面處理對IGZO薄膜的影響.....   | 44 |

| 第5章 結論.....                   | 46 |

| 5-1 後續工作.....                 | 47 |

| 參考文獻.....                     | 48 |

# 圖目錄

## 第1章

|                                                   |   |

|---------------------------------------------------|---|

| 圖1-1 (a) 非晶的IGZO <sub>4</sub> 結構圖.....            | 2 |

| 圖1-1 (b) 單晶的IGZO <sub>4</sub> 結構圖.....            | 2 |

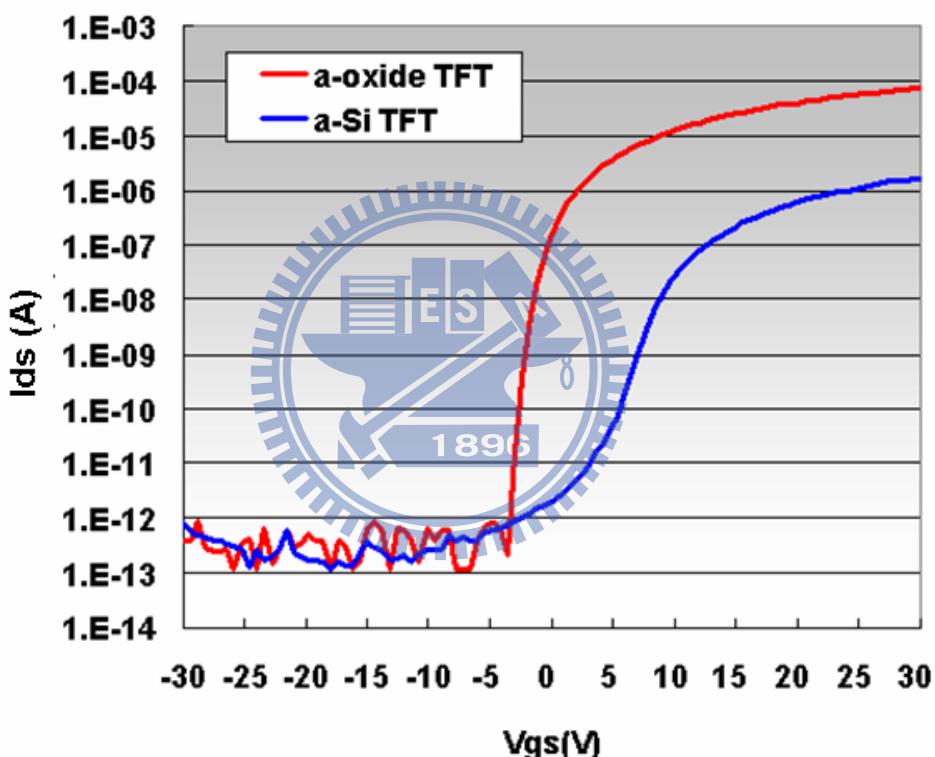

| 圖1-2 a-Si和IGZO元件的I-V圖.....                        | 4 |

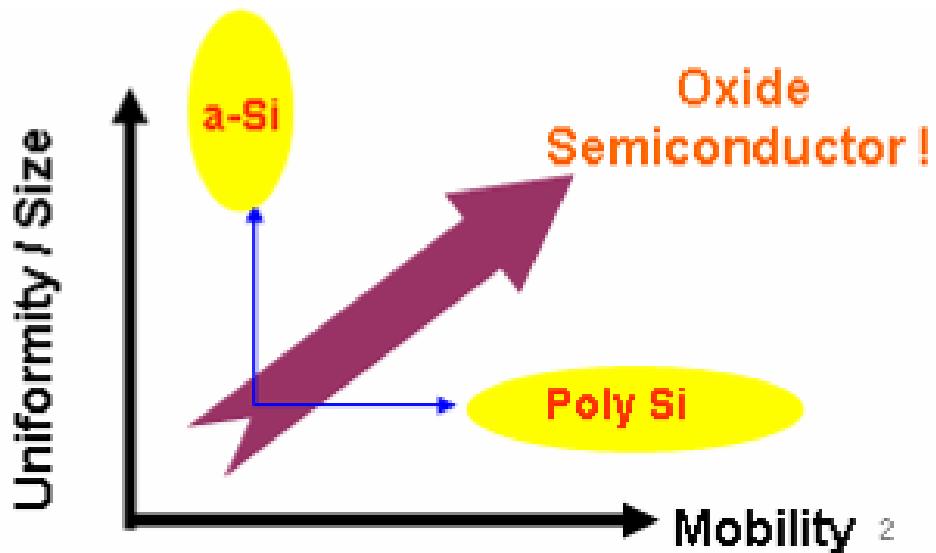

| 圖1-3 a-Si、poly Si和oxide semiconductor元件比特性比較..... | 5 |

## 第2章

|                                                                   |    |

|-------------------------------------------------------------------|----|

| 圖2-1 閘極cross section.....                                         | 6  |

| 圖2-2 IGZO semiconductor layer cross section.....                  | 6  |

| 圖2-3 Source electrode and Drain electrode layer cross section.... | 7  |

| 圖2-4 Passivation layer cross section.....                         | 7  |

| 圖2-5 物理濺鍍示意圖.....                                                 | 8  |

| 圖2-6 氣相沉積示意圖.....                                                 | 11 |

| 圖2-7 PECVD系統的結構示意圖.....                                           | 12 |

| 圖2-8 XPS系統照片 .....                                                | 13 |

| 圖2-9 砂晶片表面的XPS光譜.....                                             | 14 |

| 圖2-10 穿透式電子顯微鏡.....                                               | 15 |

| 圖2-11 TEM成像原理.....                                                | 16 |

|       |                          |    |

|-------|--------------------------|----|

| 圖2-12 | HP 4156 TFT元件分析量測機台..... | 17 |

| 圖2-13 | probe station.....       | 17 |

## 第3章

|      |                                                                    |    |

|------|--------------------------------------------------------------------|----|

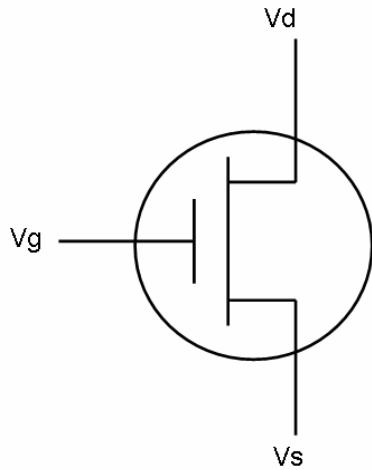

| 圖3-1 | TFT三端元件示意點.....                                                    | 19 |

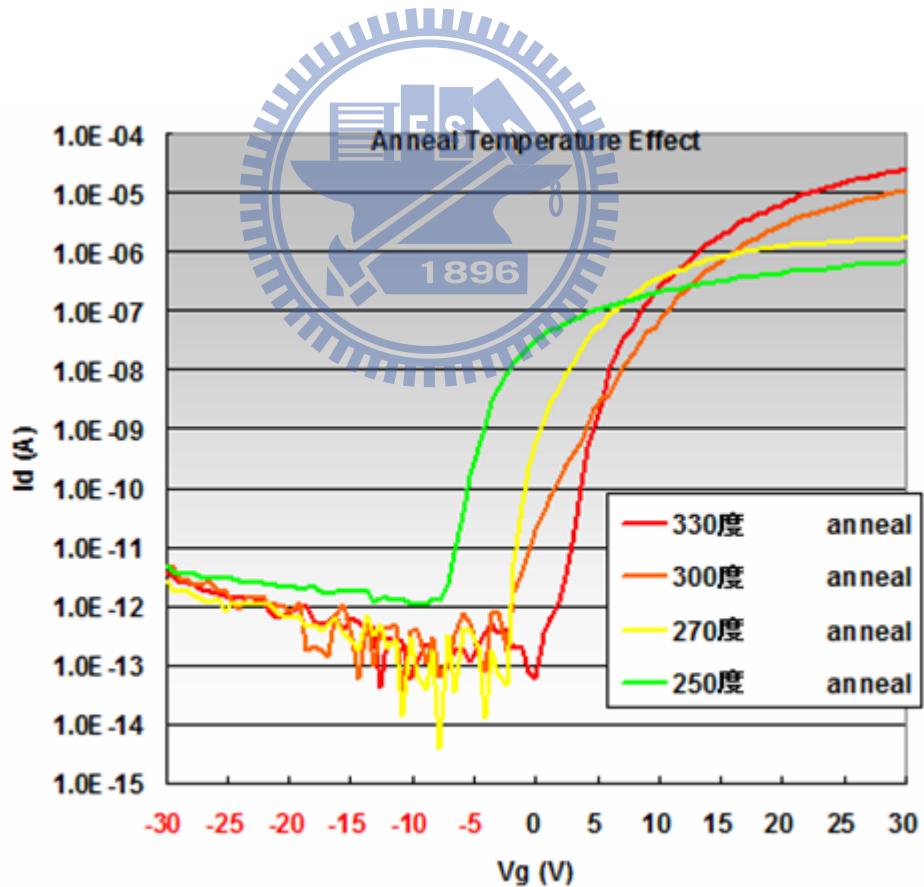

| 圖3-2 | 不同退火溫度下的Id-Vg.....                                                 | 21 |

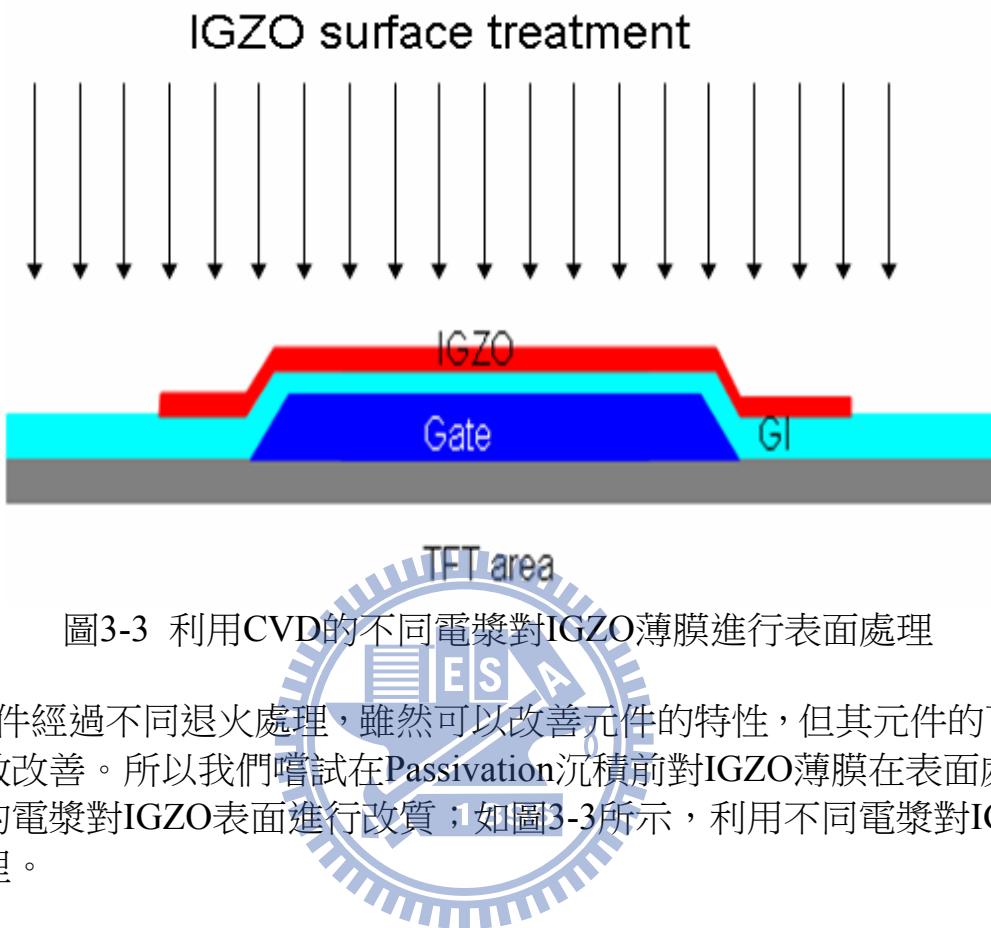

| 圖3-3 | 利用CVD的不同電漿對IGZO薄膜進行表面處理.....                                       | 23 |

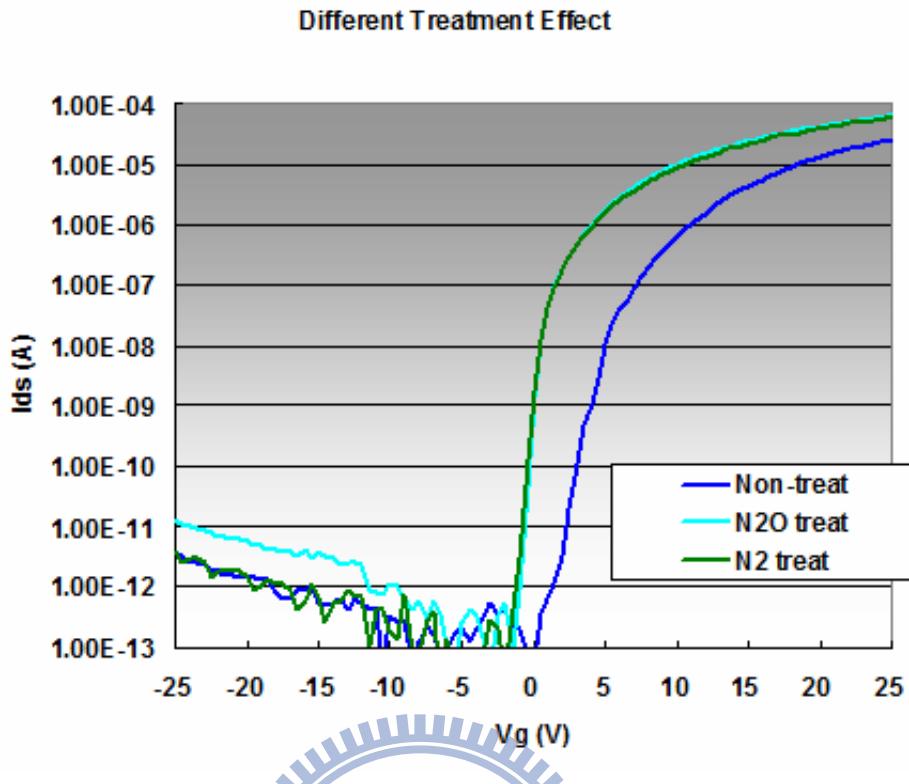

| 圖3-4 | 在不同CVD電漿對IGZO薄膜表面處理後，再經過 $330^{\circ}\text{C}$ 退火，其元件Id-Vg的表現..... | 24 |

## 第4章

|      |                                                                     |    |

|------|---------------------------------------------------------------------|----|

| 圖4-1 | 不同電漿處理和退火溫度對On current的影響.....                                      | 25 |

| 圖4-2 | 退火溫度 $270^{\circ}\text{C}$ 下，磁滯現象的表現.....                           | 26 |

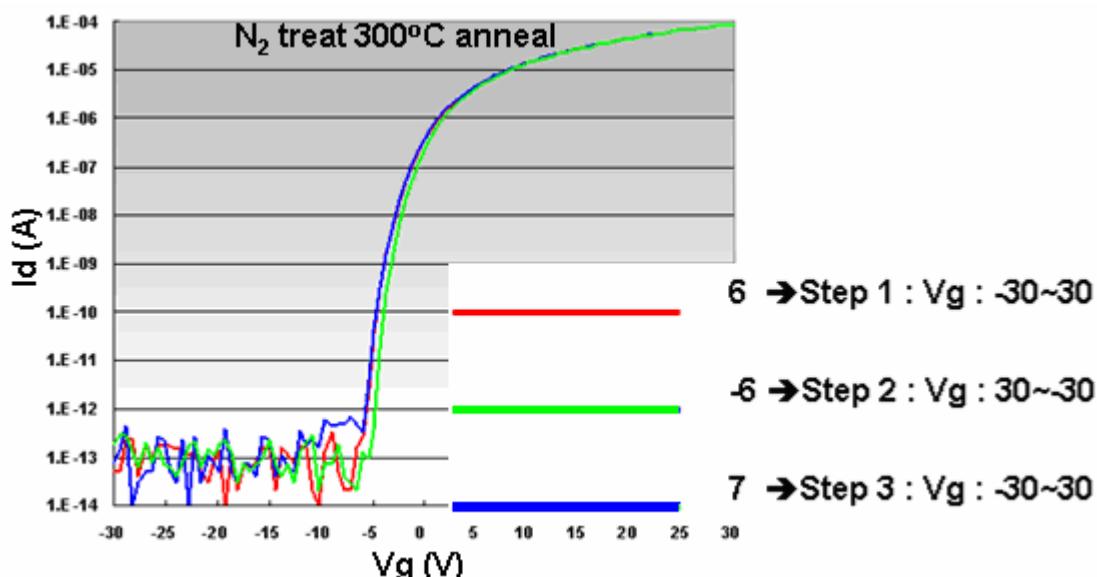

| 圖4-3 | 退火溫度 $300^{\circ}\text{C}$ 下，磁滯現象的表現.....                           | 26 |

| 圖4-4 | 退火溫度 $330^{\circ}\text{C}$ 下，磁滯現象的表現.....                           | 27 |

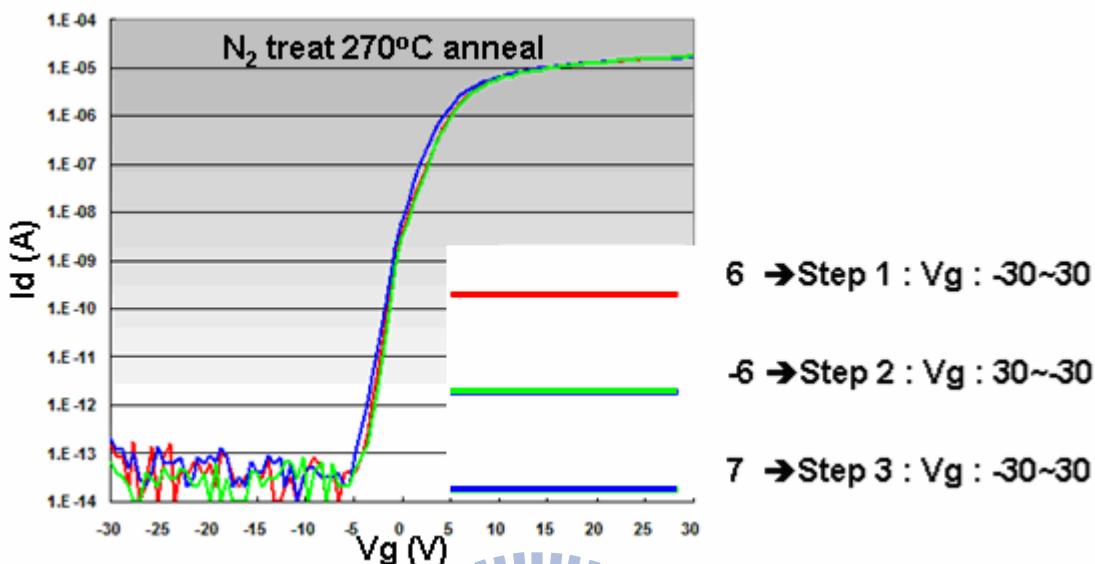

| 圖4-5 | IGZO表面做 $\text{N}_2$ 電漿處理，再利用 $270^{\circ}\text{C}$ 退火下，磁滯現象表現..... | 28 |

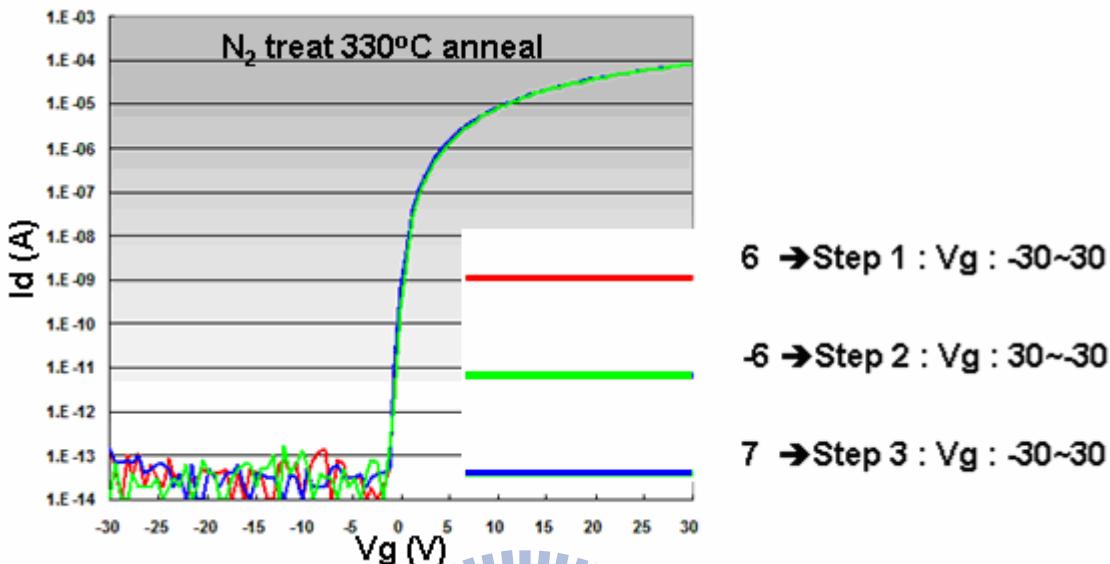

| 圖4-6 | IGZO表面做 $\text{N}_2$ 電漿處理，再利用 $330^{\circ}\text{C}$ 退火下，磁滯現象表現..... | 28 |

| 圖4-7 | IGZO表面做 $\text{N}_2$ 電漿處理，再利用 $330^{\circ}\text{C}$ 退火下，磁滯現象        |    |

|               |                                                                                      |           |

|---------------|--------------------------------------------------------------------------------------|-----------|

| 表現.....       | 29                                                                                   |           |

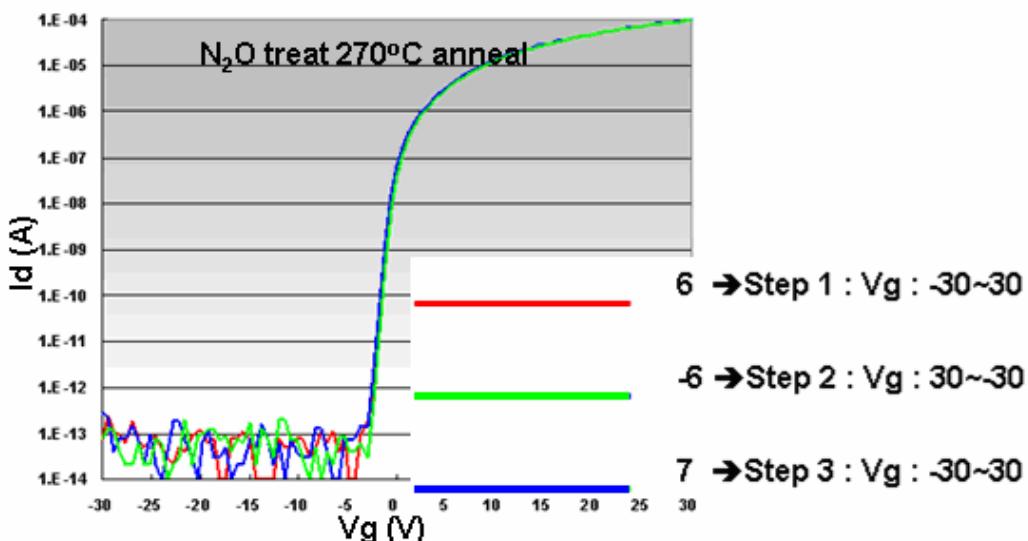

| <b>圖 4-8</b>  | <b>IGZO 表面做 <math>N_2O</math> 電漿處理，再利用 <math>270^\circ C</math> 退火下，磁滯現象表現.....</b>  | <b>29</b> |

| <b>圖 4-9</b>  | <b>IGZO 表面做 <math>N_2O</math> 電漿處理，再利用 <math>300^\circ C</math> 退火下，磁滯現象表現.....</b>  | <b>30</b> |

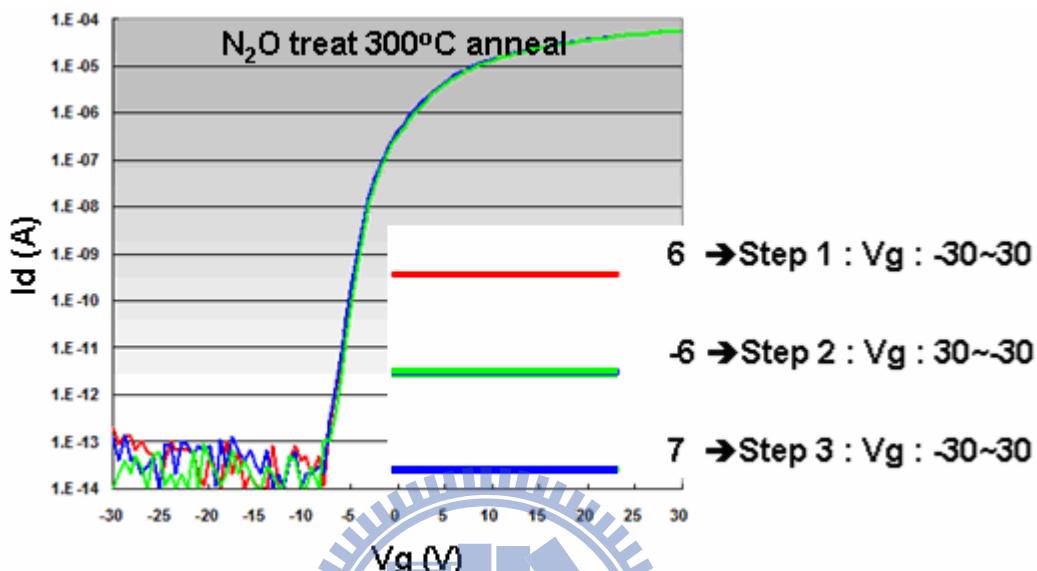

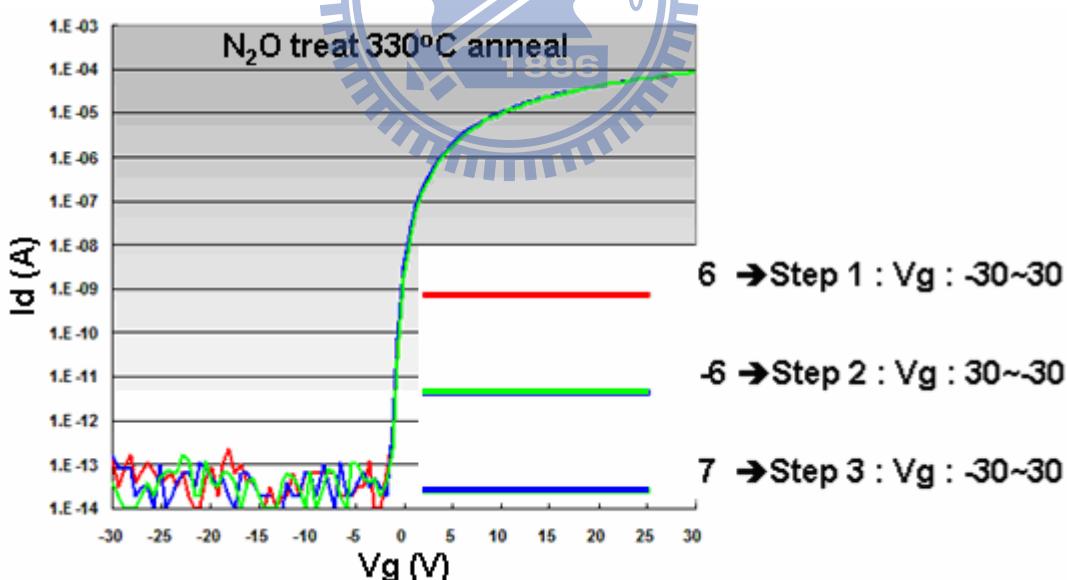

| <b>圖 4-10</b> | <b>IGZO 表面做 <math>N_2O</math> 電漿處理，再利用 <math>300^\circ C</math> 退火下，磁滯現象表現 .....</b> | <b>30</b> |

| <b>圖 4-11</b> | <b>IGZO non-treat 利用 <math>330^\circ C</math> 退火，PBTS 表現.....</b>                    | <b>32</b> |

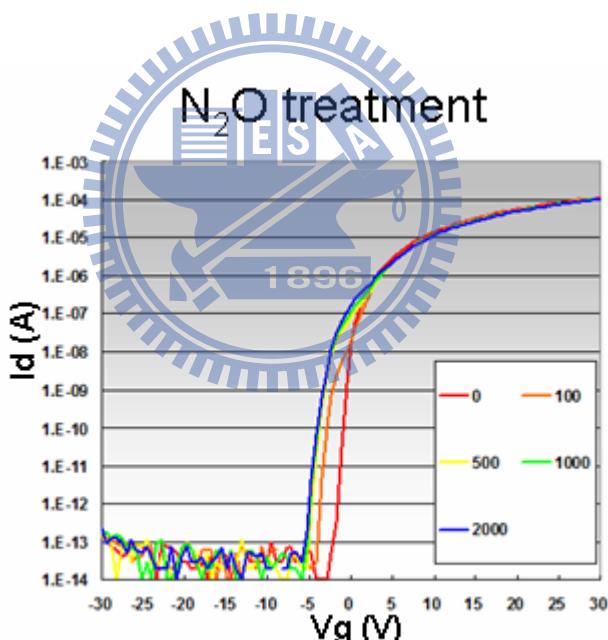

| <b>圖 4-12</b> | <b>IGZO 表面做 <math>N_2O</math> 電漿處理，再利用 <math>330^\circ C</math> 退火，PBTS 表現.....</b>  | <b>33</b> |

| <b>圖 4-13</b> | <b>IGZO 表面做 <math>N_2O</math> 電漿處理，再利用 <math>330^\circ C</math> 退火，PBTS 表現.....</b>  | <b>33</b> |

| <b>圖 4-14</b> | <b>IGZO 表面電漿處理，經 <math>330^\circ C</math> 退火，元件的 PBTS 效應....</b>                     | <b>34</b> |

| <b>圖 4-15</b> | <b>IGZO non-treat 利用 <math>330^\circ C</math> 退火，熱載子現象表現.....</b>                    | <b>35</b> |

| <b>圖 4-16</b> | <b>IGZO 表面做 <math>N_2</math> 電漿處理，再利用 <math>330^\circ C</math> 退火，熱載子現象表現.....</b>   | <b>35</b> |

| <b>圖 4-17</b> | <b>IGZO 表面做 <math>N_2O</math> 電漿處理，再利用 <math>330^\circ C</math> 退火，熱載子現象表現.....</b>  | <b>36</b> |

| <b>圖 4-18</b> | <b>IGZO 表面電漿處理，經 <math>330^\circ C</math> 退火，元件的熱載子效應....</b>                        | <b>37</b> |

|        |                                                                    |    |

|--------|--------------------------------------------------------------------|----|

| 圖 4-19 | 在 $V_g=15V$ 下，不同 $L$ 下的 TFT 寄生阻抗值.....                             | 38 |

| 圖 4-20 | TLM 計算在無表面處理的 IGZO 元件通道區阻抗.....                                    | 39 |

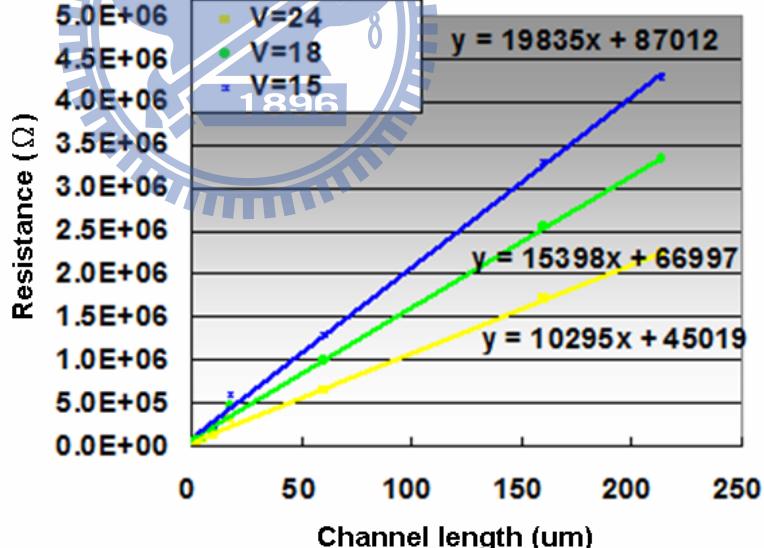

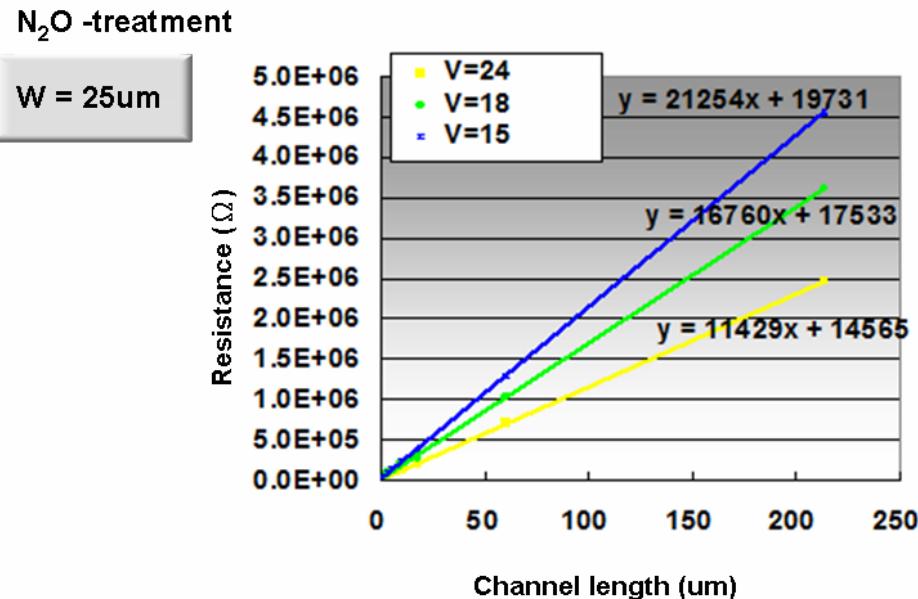

| 圖 4-21 | TLM 計算在 $N_2$ 表面處理的 IGZO 元件通道區阻抗.....                              | 39 |

| 圖 4-22 | TLM 計算在 $N_2O$ 表面處理的 IGZO 元件通道區阻抗.....                             | 40 |

| 圖 4-23 | 利用 TLM 所計算出的 channel resistance.....                               | 41 |

| 圖 4-24 | XPS analysis for as-deposited IGZO.....                            | 42 |

| 圖 4-25 | XPS analysis for after IGZO high temperature anneal...             | 42 |

| 圖 4-26 | XPS analysis for after IGZO treat and high temperature anneal..... | 43 |

| 圖 4-27 | XPS-Oxygen鍵結分析.....                                                | 43 |

| 圖 4-28 | IGZO 在高溫 $330^\circ C$ 退火後的膜質變化.....                               | 44 |

| 圖 4-29 | IGZO 表面做 $N_2$ 電漿處理後，經過高溫 $330^\circ C$ 退火後的膜質變化.....              | 44 |

| 圖 4-30 | IGZO 表面做 $N_2O$ 電漿處理後，經過高溫 $330^\circ C$ 退火後的膜質變化.....             | 45 |

# 表目錄

|      |                                              |    |

|------|----------------------------------------------|----|

| 表3-1 | 不同退火溫度下的元件參數.....                            | 22 |

| 表3-2 | 不同表面處理後的元件參數.....                            | 24 |

| 表4-1 | 不同電漿處理和退火溫度下的On current.....                 | 25 |

| 表4-2 | IGZO表面電漿處理後的元件PBTS改善效果.....                  | 34 |

| 表4-3 | IGZO表面電漿處理後的元件熱載子效應劣化改善效果.....               | 37 |

| 表4-4 | 在 $V_g=15V$ 下不同退火溫度下的channel resistance..... | 38 |

| 表4-5 | TFT在利用TLM所計算出的channel resistance.....        | 40 |

| 表4-6 | IGZO表面電漿處理再經過退火後的膜質變化比較表.....                | 45 |

# 第1章 前言

近年來平面顯示器的技術發展，除了在追求顯示器朝更大面積發展之外；也開始朝向更高解析、更輕薄、且更低成本的方向來做開發；除此之外也將顯示器做成可撓曲式，使其可以更方便的攜帶。而在如何提高顯示器的效能（如更高解析度和可撓曲顯示面板）的研究裡，除了開發各種軟式的基板與合用的顯示材料之外（如有機發光二極體），薄膜電晶體的效能提升也是必要的。而現在已經商品化的LCD；多以低溫多晶矽（Low Temperature poly-silicon，LTPS）和非晶矽(a-Si:H)，作為TFT 的主動通道層，在非晶矽的發展已經相當的成熟，但a-Si TFT載子遷移率(carrier mobility)仍在 $1\text{cm}^2/\text{V}\cdot\text{s}$ 以下。

而LTPS雖然有很高的載子遷移率(carrier mobility)，但其ELA（Excim laser anneal）機台並不容易大型化，且其投資成本相當高，所以其發展也相當受限。而且不論a-Si TFT或LTPS製程，其製程溫度都必須高於 $300^\circ\text{C}$ 以上，並不容易應用在可撓曲基板上。

而有機薄膜電晶體（Organic Thin Film Transistors，OTFT），若採用較低成本的塗佈技術來製作，其製作溫度較低。但有機的材料容易受環境中的水氣和氧氣影響產生劣化；而且OTFT 的載子遷移率也不高，目前僅做到和a-Si TFT相同而已。

而除了上述三種TFT 外，近年來金屬氧化物薄膜電晶體（Metal oxide Thin Film Transistors）也漸漸受到重視，其元件有遠大於a-Si TFT元件的載子遷移率和較LTPS低的投資成本和較佳的元件均勻性；而大部份的金屬氧化物半導體都是不透光，如此一來也能開發透明的TFT，提高每個畫素的透光面積，不須增加背光源的輸出功率，即能達到更高的亮度，所以是很有發展潛力的。

# 1-1 Metal oxide TFT 的歷史發展

在FPD元件薄膜材料研究方面，以矽半導體薄膜為基礎的a-Si:H TFT 技術已相當成熟，成為目前量產且暢銷的主動式液晶顯示器之重要元件。不過其製程溫度相當高( $380^{\circ}\text{C}$ )、不透光、光漏電流大、且遷移率低( $0.1\sim 1 \text{ cm}^2/\text{V}\cdot\text{s}$ )。以多晶矽(poly-Silicon)薄膜為基礎的低溫多晶矽(low temperature poly-Silicon LTPS)TFT技術則擁有很高的遷移率( $10\sim 200\text{cm}^2/\text{V}\cdot\text{s}$ )，所以引起廣泛的關注與研究。不過其製程溫度卻更高( $500^{\circ}\text{C}$ )，且漏電流大。

1-1 (a) 非晶的IGZO<sub>4</sub>結構圖 [1]

1-1 (b) 單晶的IGZO<sub>4</sub>結構圖 [1]

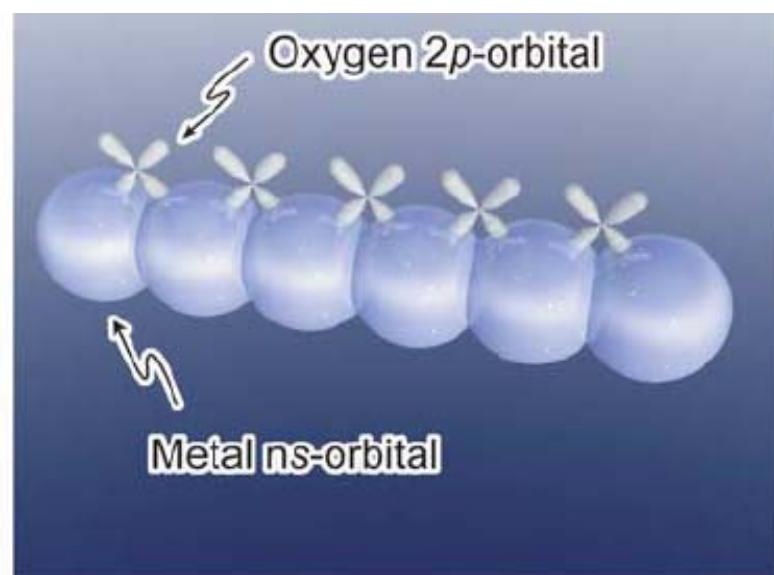

早期利用ZnO薄膜所製成的透明薄膜電晶體已被廣泛的研究，但是ZnO需要使用高溫製程來提高結晶度，才能得到理想的性能。Hideo Hosono的研究團體，也是從事以ZnO作透明電晶體的研究；而後慢慢加入各種元素摻雜，所以InGaZnO<sub>4</sub>中的銦(In)和鎵(Ga)是被試出來的；在Hideo Hosono團隊嘗試出以非晶的InGaZnO<sub>4</sub>薄膜來做成透明電晶體，(非晶的InGaZnO<sub>4</sub>結構圖1-1(a)所示；而單晶的InGaZnO<sub>4</sub>結構圖1-1(b)所示)；在室溫下以脈衝雷射蒸鍍(Pulsed Laser Deposition, PLD)蒸鍍非晶態的InGaZnO<sub>4</sub>薄膜作為主動通道層(semiconductor layer)，並以ITO來作為元件的源極(source)、汲極(drain)、閘極(gate)；及以Y<sub>2</sub>O<sub>3</sub>來做為絕緣層。且其所報導的TFT元件的載子遷移率可達 $10\text{cm}^2/\text{V}\cdot\text{s}$ ；on/off電流比可達 $10^3$ ；漏電流(leak current)約 $10^{-10}\text{A}$ 。在IGZO此類多元摻雜的金屬氧化物被發現後，也漸漸的有人在各不同的多元金屬氧化物下做研究，如IZO，IZTO，GZO，ZnO:Al.....等。

## 1-2 IGZO材料介紹

IGZO靶材的主要成份為InO : ZnO : GaO做為主要的組成，再透過燒結方式形成IGZO的靶材，依照不同的InO : ZnO : GaO成份比，可以燒結出不同比例的靶材，目前廣範被拿來討論的組成比主要有2種，分別是In: Ga : Zn : O原子比為1:1:1:4及2:2:1:7二種。

IGZO此類的金屬氧化物半導體，具有高穿透度的特色，所以其可以製作透明的TFT元件，如果再搭配上ITO等透明的導電材，更可以製作出全透明的元件，更可以作出高透穿度的面板。

圖1-2 a-Si和IGZO元件的I-V圖

而IGZO也因為其載子移動率遠高於a-Si TFT（圖1-2 a-Si和IGZO元件的I-V比較圖），而且因為IGZO薄膜本身也為為非晶的結構，所以它沒有Poly Si TFT的grain boundary，所以元件不會因為通道區落在grain boundary上會，而使得元件產生均勻性不佳的問題。

圖1-3 a-Si、poly Si和oxide semiconductor元件比特性比較

圖1-3 a-Si、poly Si和oxide semiconductor元件比特性比較，其元件特性介於非晶矽元件和複晶矽元件之間，而在元件均勻性上的表現也和非晶矽差異不大，因為不需要高溫結晶製程或ELA製程，故在大型化的基礎上只須要使用傳統的PVD機台，所以也比較容易大型化。

# 第2章 元件製程及設備介紹

## 2-1 元件製程流程

元件製作採用半導體製程中使用的薄膜沉積、黃光微影和化學蝕刻等技術來製作TFT元件：

首先，使用無鹼玻璃當元件的製作的基板，在進行製程前先使用UV光來清潔玻璃表面的有機污染物，再來使用清水洗清玻璃表面。

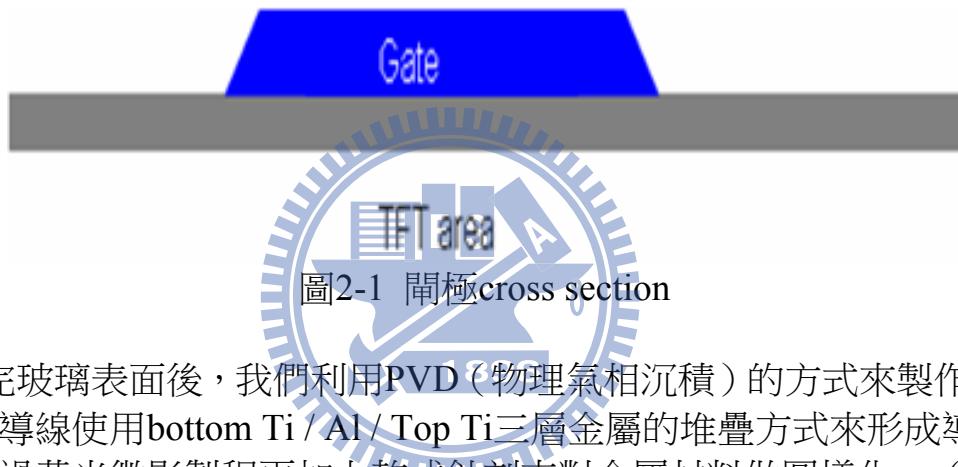

在做完玻璃表面後，我們利用PVD（物理氣相沉積）的方式來製作閘極導線材料，其導線使用bottom Ti / Al / Top Ti三層金屬的堆疊方式來形成導線材料，之後再透過黃光微影製程再加上乾式蝕刻來對金屬材料做圖樣化。（圖2-1 閘極cross section）

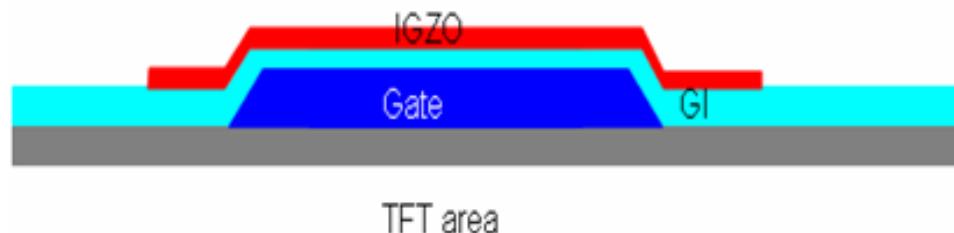

在完成閘極導線的製程後，接著我們利用PECVD（化學氣相沉積）的方式來形成SiNx薄膜當做TFT的GI（gate insulator；閘極介電質層）。

圖2-2 IGZO semiconductor layer cross section

在完成閘極介電質層後，我們使用PVD（物理氣相沉積）方式，對IGZO靶材做反應性濺鍍，其方式為在濺鍍過程中，利用Ar對IGZO靶材轟擊產生的IGZO

原子，並在腔體內通入O<sub>2</sub>氣體，在電漿環境中其會解離成氧電漿，進而和Ar轟擊出來的IGZO原子在基板成膜時產生氧化反應，進而有效控制IGZO膜內的O<sub>2</sub> Vacancy濃度。可調整IGZO TFT元件的特性，在沉積完IGZO薄膜後，我們在利用黃光製程加上濕式蝕刻方式（利用草酸來對IGZO進行蝕刻）來形成元件的半導體區域。如圖2-2所示（IGZO semiconductor layer cross section）

圖2-3 Source electrode and Drain electrode layer cross section

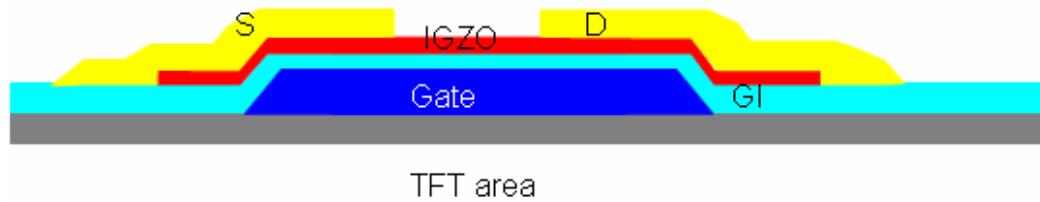

再來接著使用PVD（物理氣相沉積）的方式來製作源極和汲極導線材料，其導線仍使用bottom Ti / Al / Top Ti三層金屬的堆疊方式來形成導線材料，之後再透過黃光微影製程再加上乾式蝕刻來對金屬材料做圖樣化。如圖2-3（Source electrode and Drain electrode layer cross section所示）。

圖2-4 Passivation layer cross section

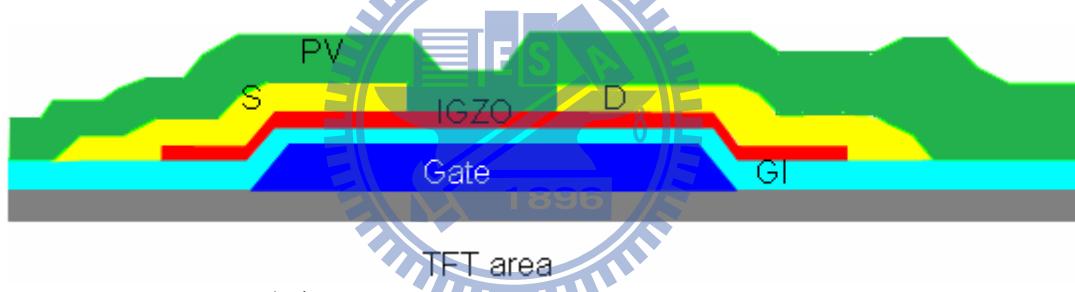

最後再利用PECVD方式來沉積SiO<sub>2</sub>，覆蓋在元件表面，當元件的保護層材料，避免元件受到外界環境的影響。如圖2-4所示（Passivation layer cross section）

## 2-2 PVD和CVD製程介紹

### 2-2-1 PVD製程介紹

PVD顧名思義是以物理機制來進行薄膜沉積，而非使用化學反應的製程技術的方式來沉積，物理機制是物質的相變化現象，如蒸鍍(Evaporation)，蒸鍍源由固態轉化為氣態，濺鍍 (Sputtering)，蒸鍍源則由氣態轉化為電漿態。

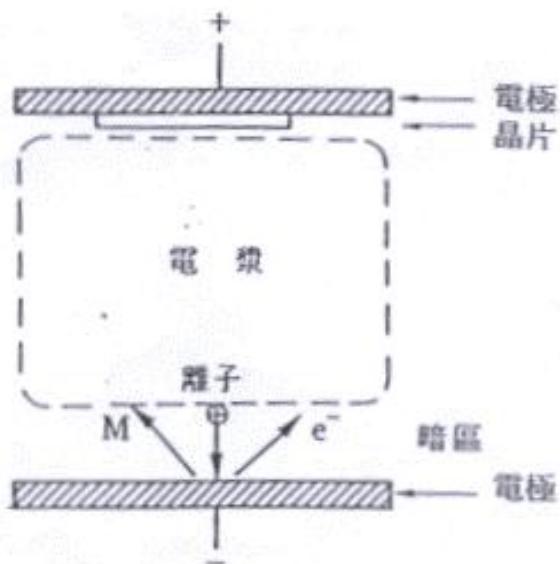

電漿 (Plasma) 是將各種不同成份的氣體利用RF power將其部份離子化。其操作在兩個相對應的金屬電極板上施以電壓，假如電極板間的氣體分子濃度在某一特定的區間，電極板表面因離子轟擊 (Ion Bombardment) 所產生的二次電子(Secondary Electrons)，在電極板所提供的電場下，將獲得足夠的能量，而與電極板間的氣體分子因撞擊而進行所謂的解離 (Dissociation)，離子化 (Ionization)，及激發 (Excitation) 等反應，而產生離子、原子、原子團 (Radicals)，及更多的電子，以維持電漿內各粒子間的濃度平衡。

濺鍍的原理是於真空腔體中通入惰性氣體，氣體內少量的自由電子受到外加電場作用時，電子在電場中會被加速而得到能量，且在低壓下分子間的平均自由路徑 (mean free path) 較長，因此電子可以得到較長的加速距離而獲得較高的能量。這些能量較高的電子經由碰撞將動能轉移至惰性氣體上，使得氣體分子被離子化，氣體離子再經由電場作用撞擊到靶材表面，使得靶材原子濺射出來，進而沉積在基材表面。這種利用電漿獨特的離子轟擊，以動量轉換的原理，稱之為濺鍍 (sputtering Deposition)。

圖2-5 物理濺鍍示意圖

圖2-5中顯示一個DC電漿的陰極電板遭受離子轟擊的情形。脫離電子的帶正電荷離子，在暗區的電場加速下，將獲得極高的能量。當離子與陰電極產生轟擊之後，基於動量轉換的原理，離子轟擊除了會產生二次電子以外，還會把電極板表面的原子給撞擊出來，這個動作，我們稱之為濺擊（Sputtering）這些被擊出的電極板原子將進入電漿裡，然後利用擴散（Diffusion）方式，傳遞到基材表面，進行成膜。

基於以上的模型，濺鍍的沉積機制，大致上可以區分為以下幾個步驟：

- (1)電漿內所產生的部份離子，將脫離電漿並往陰極板移動。

- (2)經加速的離子將轟撞在陰電極板的表面除產生二次電子外，且因此而擊出電極板原子。

- (3)被擊出的電極板原子將進入電漿內，且最後傳遞到另一個放置有基板的電極板的表面。

- (4)這些被吸附在晶片表面的吸附原子，將進行薄膜的沉積。

## 2-2-2 反應性濺鍍

反應性濺鍍是在濺鍍靶材的過程中，通入須要和濺射出來的物質反應的氣體，使其可以在基材上產生化學反應，進而形成所須要的薄膜。但是通入濺鍍腔體內的反應氣體不僅會和濺射出來的原子產生反應，其也會和靶材表面產生化學反應，而在靶材表面形成化合物，由於靶材表面所形成之化合物的濺鍍速率和原本靶材材料的濺鍍速率不同，如此一來也會改變原本靶材的材料沉膜特性。

IGZO在成膜過程中是在反應室腔體內通入適量的O<sub>2</sub>氣體，使O<sub>2</sub>能夠補足IGZO膜內的氧原子，但O<sub>2</sub>會和靶材反應導致靶材的導電度變慢，進而影響濺鍍的製程。因此過量的O<sub>2</sub>反而會讓濺鍍的速率變得緩慢。

## 2-2-3 CVD製程介紹

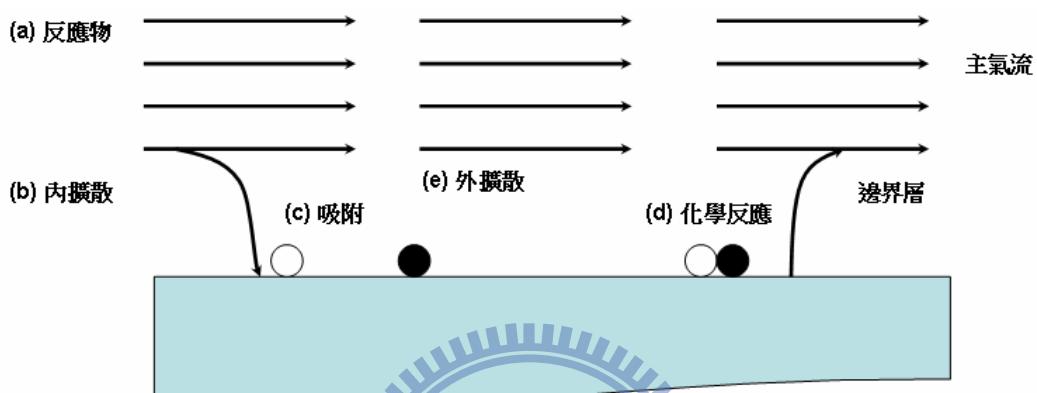

在半導體製程上，CVD反應的環境，包括：溫度、壓力、氣體的供給方式、流量、氣體混合比及反應器裝置等等。基本上氣體傳輸、熱能傳遞及反應進行三方面，亦即反應氣體被導入反應器中，藉由擴散方式經過邊界層（boundary layer）到達基板表面，而由基板表面提供反應所需的能量，反應氣體就在基板表面產生化學變化，生成固體生成物，而沉積在基板表面。

圖2-6 氣相沉積示意圖

圖2-6中顯示在化學氣相沉積程所包含的主要機制。其中可以分為下列五個主要的步驟：

- 首先在沉積室中導入反應氣體，以及稀釋用的惰性氣體所構成的混合氣體，『主氣流』（mainstream）。

- 主氣流中的反應氣體原子或分子往內擴散移動通過停滯的『邊界層』（boundary layer）而到達基板表面。

- 反應氣體原子被『吸附』（adsorbed）在基板上。

- 吸附原子在基板表面遷徙，並且產生薄膜成長所須要的表面化學反應。

- 表面化學反應所產生的氣相生成物被『脫附』（desorbed），並且往外擴散通過邊界層而進入主氣流中，並由沉積室中被排除。

圖2-7 PECVD系統的結構示意圖

在我們使用的CVD為電漿輔助式化學氣相沉積( PECVD )，此架構下的CVD系統使用電漿的輔助能量，可使成膜的反應溫度降低。在PECVD中由於電漿作用而會有光線產生，因此又稱為『輝光放電』( glow discharge ) 系統。圖( 2-7 )是一個PECVD系統的結構示意圖。圖中沉積室通常是由上下的兩片電極板，以及金屬或玻璃的腔壁所構成的。腔體內有上下兩塊電極，基板則是放置於下電極板上。電極板會加熱至100°C至400°C之間的溫度範圍。當在二個電極板間外加一個13.56MHz的『射頻』( radio frequency，縮寫RF ) 電壓時，在二個電極之間會有輝光放電的現象。工作氣體則是由沉積室外緣處導入，並且作徑向流動通過輝光放射區域，而在沉積室中央處由真空幫浦加以排出。

PECVD的沉積原理與一般的CVD之間並沒有太大的差異。電漿中的反應物是化學活性較高的離子或自由基，而且基板表面受到離子的撞擊也會使得化學活性提高。這兩項因素都可促進基板表面的化學反應速率，因此PECVD在較低的溫度即可沉積薄膜。PECVD通常是用來沉積SiO<sub>2</sub> 與Si<sub>3</sub>N<sub>4</sub> 等介電質薄膜。PECVD的主要優點是具有較低的沉積溫度；缺點是薄膜中常含有大量的氫原子。

## 2-3 分析量測儀器介紹

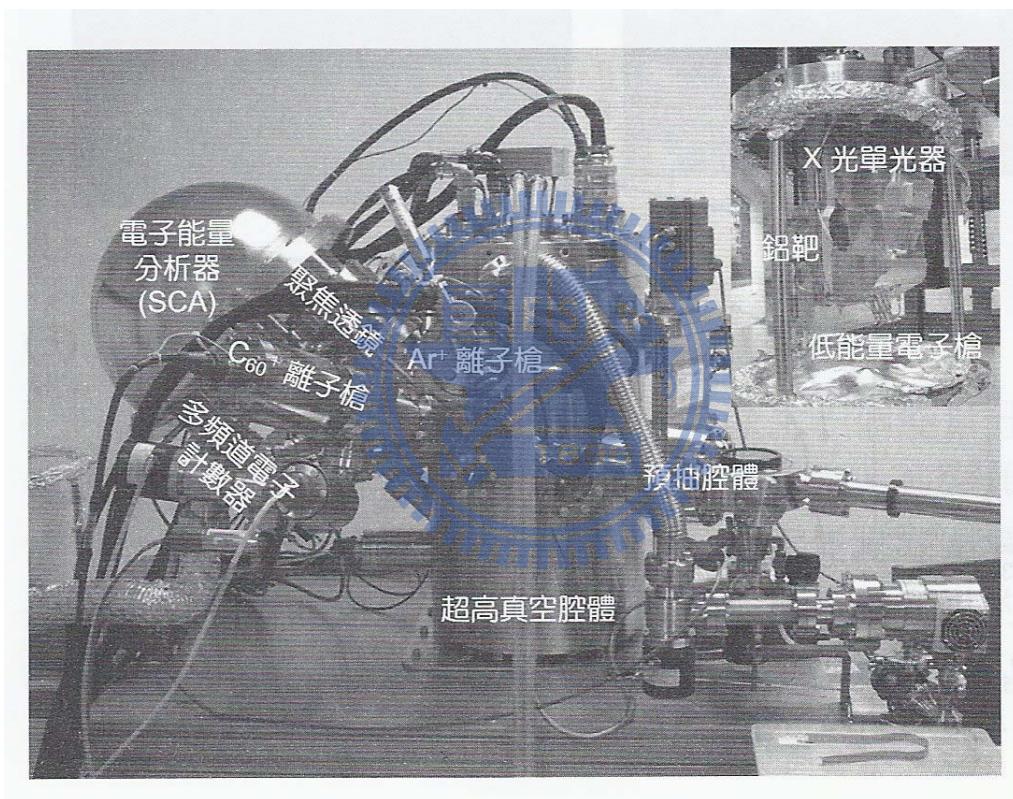

### 2-3-1 X光光電子光譜儀

X光光電子光譜儀 (X-ray photoelectron spectroscopy ,XPS) 亦稱為化學分析電子光譜 (electron spectroscopy chemical analysis, ESCA)，如圖2-8所示；其為目前應用最廣泛的表面分析技術之一。其利用具有高能量的X光光子可以穿透到原內層，經由能量轉移，進而淚發內層電子。游離出來的電子，其所攜能量與特定的原子軌域之束縛能相關，可經比對用以鑑別原子種類，因此XPS可以用來分析樣品的元素組成。

圖2-8 XPS系統照片 [15]

此外雖然原子內層電子的束縛能主要受原子核的影響，但外層電子的鍵結環境，也會造成束縛能的些微改變並造成光譜上峰值的位移。此差異稱為化學位移，經由分析元素峰值的化學位移，我們可以得到該元素化學狀態的資訊。除了定性上的分辨元素種類及鍵結環境外，經由對圖譜峰值的積分，樣品的化學組成也可進一步地進行定量分析。

在此分析的主要以元素束縛能為主，何謂束縛能：其定義為電子簽原子內，移除到無限遠的距離所需要的能量；此能量主要受原子的電子組態所影響。換

言之，電子的束縛能可作為鑑別元素的本徵特性。在XPS中，經由量測電子的束縛能，即便在週期表上相鄰的元素，也可以輕易的分辨。

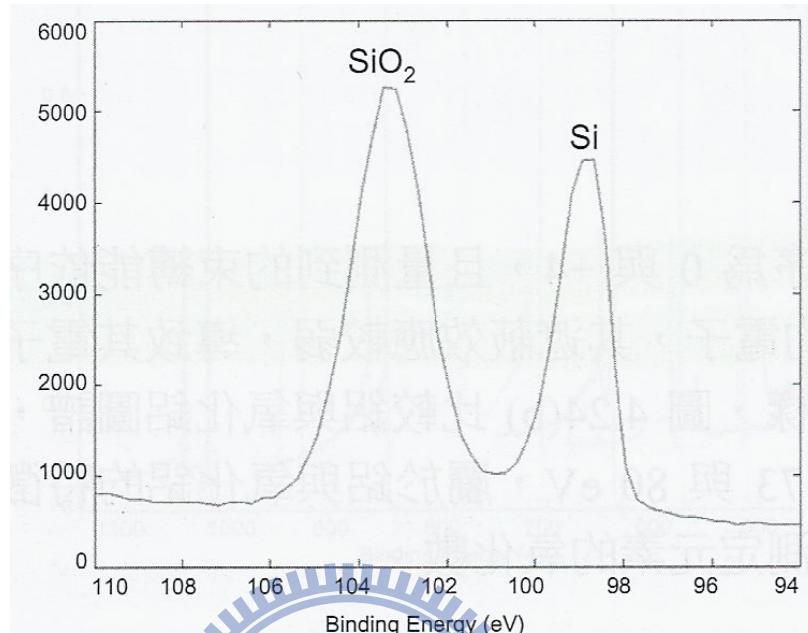

圖2-9 硅晶片表面的XPS光譜[15]

如圖2-9以矽與二氧化矽為例，其氧化數依序為0與+4，且量測到的束縛能依序為99.7和103eV。由於高氧化數的原子具有較少的電子，其遮蔽效應較弱，導致其電子與原子核的連結較為緊密，進而提高其束縛能。

## 2-3-2 穿透式電子顯微鏡 TEM

(Transmission Electron Microscopy)

圖2-10 穿透式電子顯微鏡 [2]

穿透式電子顯微鏡的外觀如圖2-10所示。穿透式電子顯微鏡是利用高能量電子束（一般約在100keV~1MeV）穿透厚度低於100nm以下之薄樣品，和薄樣品內的各種組織產生不同程度的電子散射。散射後的電子以不同的行徑通過後續的透鏡組合和透鏡光圈，形成明暗對比之影像，而這些明暗對比之微結構影像；而再藉由螢光板來呈現。因此穿透式電子顯微鏡分析即擷取穿透薄樣品之直射電子（Transmitted Electron）或是彈性散射電子（Elastic Scattered Electron）成像，或作成繞射圖案（Diffraction Pattern；DP）進而解析薄樣品微結構組織與晶體結構。

一般而言，除了電子顯微鏡本身的性能，樣品之厚度是否夠薄(<100nm)與夠平坦均勻，也決定穿透式電子顯微影像之品質。

圖2-11 TEM成像原理 [2]

**TEM成像機制** 穿透式電子顯微鏡如同光學顯微鏡，如圖2-11所示，用來放大微小區域，穿透式電子顯微鏡不單只能用來觀察物質，還能進一步分析物質。其利用電磁透鏡（Electromagnetic Lens）來偏折、聚焦加速的電子，使電子撞擊材料，產生穿透電子束與彈性散射電子束，而後這些電子束再經過電磁透鏡放大、聚焦，最後形成影像（Image）或繞射圖形（Diffraction Pattern）。

## 2-3-3 HP 4156和Probe station

圖2-12 HP 4156 TFT元件分析量測機台

圖2-13 probe station

# 第3章 實驗流程及數據分析

## 3-1 實驗動機

因為IGZO元件容易受到外界環境因素的影響，而使元件之可靠度不佳；如空氣中的水氣容易影響到元件的表面鍵結條件，而使得元件容易產生啓始電壓漂移的現象。而為了有效改善IGZO元件的穩定性，並提升元件的信賴性；我們嘗試使用元件的表面處理方式和改變元件的退火溫度來改善TFT元件的特性。

## 3-2 元件量測方式及參數

圖3-1 TFT三端元件示意點

如圖3-1所示，為三端元件的閘極（ $V_g$ ） 、汲極（ $V_d$ ） 、源極（ $V_s$ ）：

- **Id-Vg量測方式：**

- ✓ 閘極端接電壓由 $V_g$  : -30V~30V每0.5V一個step

- ✓ 汲極端接電壓設定為10V ( $V_d=10V$ )

- ✓ 源極端接地 ( $V_s=0V$ )

- **磁滯量測方式：**

- ✓ 第一個步驟：

- ✧ 閘極端接電壓由 $V_g$  : -30V ~ 30V每0.5V一個step

- ✧ 汲極端接電壓設定為10V ( $V_d=10V$ )

- ✧ 源極端接地 ( $V_s=0V$ )

- ✓ 第二個步驟：

- ✧ 閘極端接電壓由 $V_g$  : 30V ~ -30V每0.5V一個step

- ✧ 汲極端接電壓設定為10V ( $V_d=10V$ )

- ✧ 源極端接地 ( $V_s=0V$ )

- ✓ 第三個步驟：

- ✧ 閘極端接電壓由 $V_g$  : -30V ~ 30V每0.5V一個step

- ✧ 汲極端接電壓設定為10V ( $V_d=10V$ )

- ✧ 源極端接地 ( $V_s=0V$ )

- PBTS ( Positive Bias temperature stress ) :

- ✓ 第一步量測元件I-V電性，而後再加劣化條件，劣化的條件如下：

- ✧ 閘極端接電壓設定Vg : 50V

- ✧ 沖極端和源極端接地 ( Vd=Vs=0V )

- ✧ Stress time : 0 / 100 / 200 / 500 / 1000 / 2000

- ✧ Stress後量測Id-Vg

- 热載子劣化效應 ( Hot carrier stress ) :

- ✓ 第一步量測元件I-V電性，而後再加劣化條件，劣化的條件如下：

- ✧ 閘極端接電壓設定Vg : 5V

- ✧ 沖極設定電壓Vd : 30V

- ✧ 源極端接地 ( Vd=Vs=0V )

- ✧ Stress time : 0 / 100 / 200 / 500 / 1000 / 2000

- ✧ Stress後量測Id-Vg

### 3-3 實驗方式

#### 3-3-1 IGZO退火溫度對元件特性的影響

退火溫度可以提高對IGZO元件的元件特性，適當的退火溫度可以讓IGZO元件變的穩定，但是過高的退火溫度會使元件劣化。所以我們利用不同的退火溫度來調整元件的特性，改善元件的特性，此次實驗中使用的退火溫度從 $250^{\circ}\text{C}$ 到 $330^{\circ}\text{C}$ 並做2小時的退火處理，不使用超過 $330^{\circ}\text{C}$ 的主要原因是因為元件的退火溫度若過高元件容易產生裂化現象。

➤ 實驗條件：

- ✓ 利用常壓的oven；並在chamber通入氮氣，對元件做退火處理。

- ✓ 退火溫度條件為： $250^{\circ}\text{C}$  /  $270^{\circ}\text{C}$  /  $300^{\circ}\text{C}$  /  $330^{\circ}\text{C}$

- ✓ 退火時間：2小時

圖3-2 不同退火溫度下的 $\text{Id}-\text{Vg}$

在不同退火溫度下，其退火溫度越高，可以元件的on current及元件的載子移動率（ $\mu$  : mobility）提高；所示如圖3-2，其元件參數如表3-1所示。

表3-1 不同退火溫度下的元件參數

|                                 | 250°C   | 270°C   | 300°C   | 330°C   |

|---------------------------------|---------|---------|---------|---------|

| V <sub>th</sub> (V)             | -3.82   | 0.86    | 4.72    | 5.19    |

| Mobility (cm <sup>2</sup> /V·S) | 0.12    | 0.31    | 2.99    | 7.05    |

| S.S                             | 1.47    | 1.53    | 2.55    | 1.34    |

| I <sub>on</sub> (A)             | 6.7E-7  | 1.7E-6  | 1.1E-5  | 2.6E-5  |

| I <sub>off</sub> (A)            | 1.8E-12 | 2.6E-13 | 3.1E-13 | 6.4E-12 |

| On/off ratio                    | 3.8E+5  | 6.4E+6  | 3.6E+7  | 4.1E7   |

### 3-3-2 IGZO表面處理對元件的影響

圖3-3 利用CVD的不同電漿對IGZO薄膜進行表面處理

在元件經過不同退火處理，雖然可以改善元件的特性，但其元件的可靠度仍無法有效改善。所以我們嘗試在Passivation沉積前對IGZO薄膜在表面處理；利用不同的電漿對IGZO表面進行改質；如圖3-3所示，利用不同電漿對IGZO薄膜進行處理。

實驗條件：

此實驗的方式是利用CVD chamber產生各種不同的電漿環境，再利用不同電漿對IGZO薄膜進行表面處理，使薄膜表面的狀態產生一些改善，藉以提高元件的特性。

- 電漿條件為： $N_2$ 電漿 /  $N_2O$ 電漿.。

圖3-4 在不同CVD電漿對IGZO薄膜表面處理後，再經過330°C退火，其元件Id-Vg的表現

在不同N<sub>2</sub>和N<sub>2</sub>O電漿環境處理後，其元件特性可以得到改善，如圖3-4 元件在電漿環境表面處理後，經過330°C退火後的Id-Vg表現；在經過表面處理的TFT元件，其的次臨界電壓和on current可以獲得改善，其元件的參數如表3-2所示。

表3-2不同表面處理後的元件參數

|                                 | Non treat | N <sub>2</sub> | N <sub>2</sub> O |

|---------------------------------|-----------|----------------|------------------|

| V <sub>th</sub> (V)             | 5.19      | 0.04           | 0.12             |

| Mobility (cm <sup>2</sup> /V·S) | 7.05      | 10.47          | 10.92            |

| S.S                             | 1.34      | 0.53           | 0.46             |

| I <sub>on</sub> (A)             | 2.6E-5    | 5.99E-5        | 6.39E-5          |

| I <sub>off</sub> (A)            | 6.4E-13   | 6.07E-13       | 2.50E-12         |

| On/off ratio                    | 4.1E+7    | 8.94E+7        | 2.56E+7          |

# 第4章 實驗結果及討論

## 4-1 元件電性改善

### 4-1-1 電漿處理對和退火溫度對元件的影響

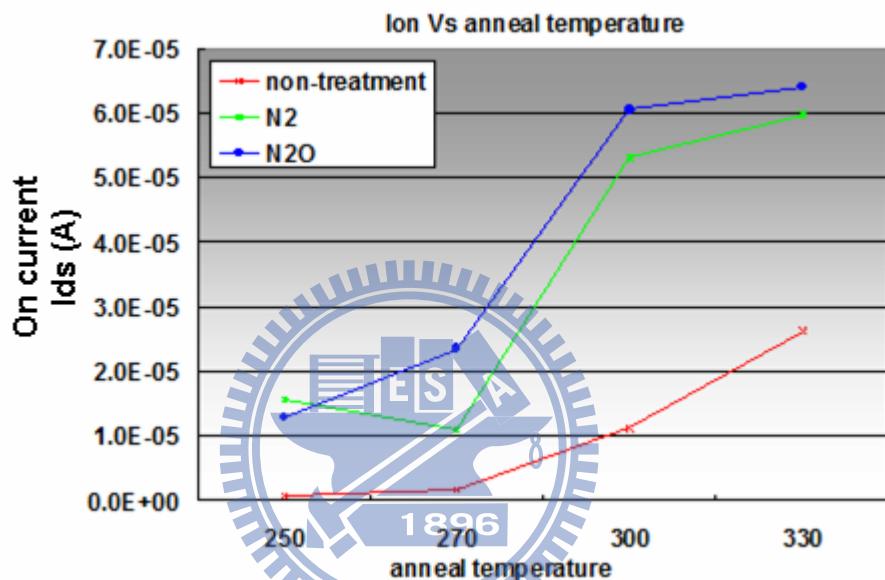

圖4-1不同電漿處理和退火溫度對On current的影響

而且其元件的on current也會隨著退火溫度提高而升高；如圖4-1所示；其on current提高後的各參數值如表4-1所示。

表4-1 不同電漿處理和退火溫度下的On current

| Anneal temperature |              | 250°C     | 270°C     | 300°C     | 330°C     |

|--------------------|--------------|-----------|-----------|-----------|-----------|

| On current         | Non treat    | 6.72E-7 A | 1.65E-6 A | 1.12E-5 A | 2.62E-5 A |

|                    | $N_2$ treat  | 1.55E-5 A | 1.1E-5 A  | 5.30E-5 A | 5.99E-5 A |

|                    | $N_2O$ treat | 1.28E-5 A | 2.34E-5 A | 6.04E-5 A | 6.39E-5 A |

## 4-2 元件磁滯現象

### 4-2-1 退火溫度對磁滯的改善

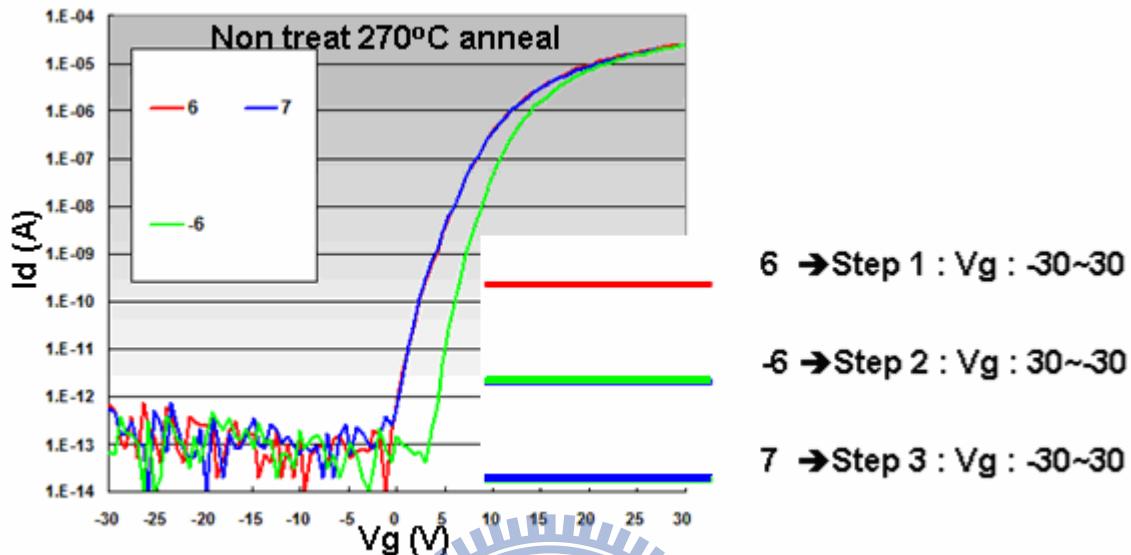

圖4-2 退火溫度 $270^{\circ}\text{C}$ 下，磁滯現象的表現

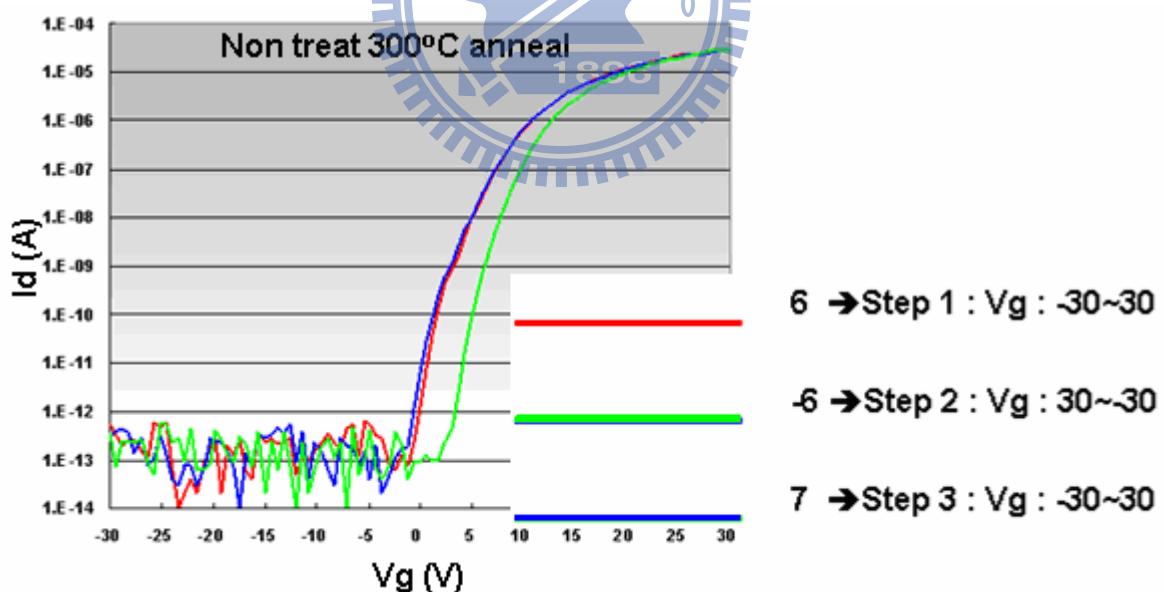

圖4-3 退火溫度 $300^{\circ}\text{C}$ 下，磁滯現象的表現

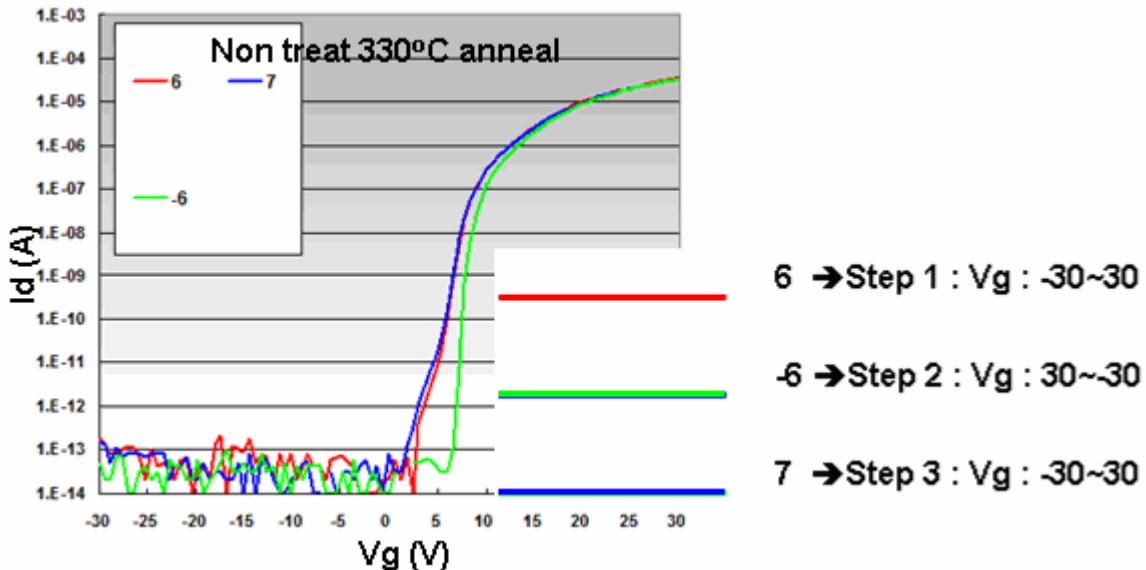

圖4-4 退火溫度 $330^{\circ}\text{C}$ 下，磁滯現象的表現

退火溫度對元件有改善作用，但在高溫的退火溫度修補了元件內的部份缺陷，在越高溫的退火，對元件的修補能力越佳；如圖4-2、圖4-3和圖4-4所示，其元件分別在 $270^{\circ}\text{C}$ 、 $300^{\circ}\text{C}$ 和 $330^{\circ}\text{C}$ 三種不同的退火溫度，對元件特性的改善；在 $330^{\circ}\text{C}$ 經過二小時的退火後，其磁滯量測後的結果仍然會出現輕微的磁滯現象，但已經大幅改善低溫退火時的磁滯現象；這也意味著元件的界面缺陷也大幅降低；但仍然無法完全消除，表示其元件只經過單純的退火溫度提高並無法完全消除界面缺陷。

圖4-2和圖4-3中可以很明顯的若元件只有經過 $270^{\circ}\text{C}$ 和 $330^{\circ}\text{C}$ 退火，當元件從閘極（ $V_g$ ）電壓由負電壓量測到正電壓，再接著由正電壓量測到負電壓時，可明顯的發現元件的 $V_{th}$ 會有差異性；即當 $V_g$ 由負給到正時，元件的界面處會因為此一外加電壓進而產生額外的缺陷，故當元件由正電壓給到負電壓時，其 $V_{th}$ 會往正的偏移。

圖4-4中元件的磁滯問題，很明顯的在經過， $V_{th}$ 的差異性會變得比較小，雖然仍無法完全消除，但比 $270^{\circ}\text{C}$ 和 $330^{\circ}\text{C}$ 退火下的條件已經改善許多。

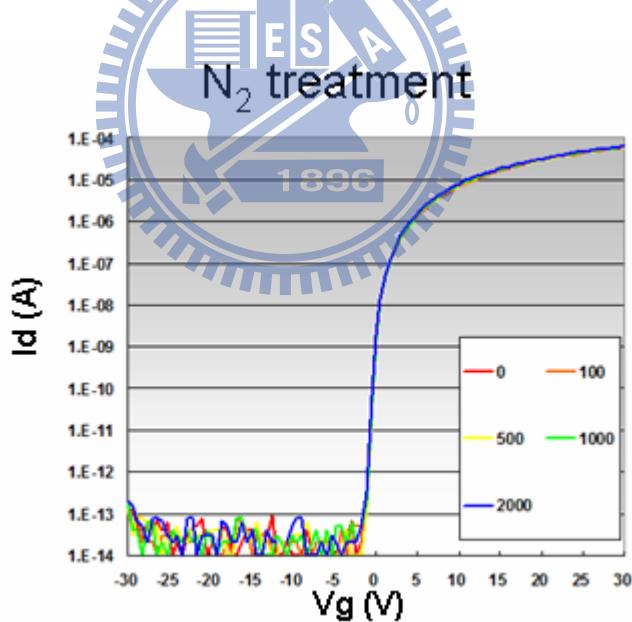

## 4-2-2 N<sub>2</sub>電漿處理對磁滯現象改善

圖4-5 IGZO表面做N<sub>2</sub>電漿處理，再利用270°C退火下，磁滯現象表現

因為單純的退火處理無法完全消除IGZO元件的界面缺陷，所以我們試著對IGZO表面做N<sub>2</sub>的電漿處理，藉以改善元件的特性。在此我們可以發現在經過N<sub>2</sub>的電漿處理的元件，在270°C二小時的高溫退火後，元件的磁滯現象已經比未經過電漿處理的元件改善許多（如圖4-5所示）。

圖4-6 IGZO表面做N<sub>2</sub>電漿處理，再利用300°C退火下，磁滯現象表現

若我們再提高元件的退火溫度到 $300^{\circ}\text{C}$  2小時的高溫退火，元件的磁滯現象表現也會因為高溫退火和IGZO表面的退火處理而變的比較輕微（如圖4-6所示）。

圖4-7 IGZO表面做 $\text{N}_2$ 電漿處理，再利用 $330^{\circ}\text{C}$ 退火下，磁滯現象表現

在經過更高溫 $330^{\circ}\text{C}$  2小時的退火後幾乎無磁滯現象的產生（如圖4-7所示）。無論元件的 $\text{Vg}$ 是由負電壓量測到正電壓；或是由正電壓量測到負電壓，皆不會產生 $\text{V}_{\text{th}}$ 偏移的現象。由此可知，IGZO表面經過 $\text{N}_2$ 電漿處理後，除了可以改善元件的啓始電壓和on current外，亦可以改善IGZO元件的界面缺陷。

#### 4-2-3 $\text{N}_2\text{O}$ 電漿處理對磁滯現象改善

圖4-8 IGZO表面做 $\text{N}_2\text{O}$ 電漿處理，再利用 $270^{\circ}\text{C}$ 退火下，磁滯現象表現

相同的，若我們試著對IGZO表面做N<sub>2</sub>O的電漿處理，使用N<sub>2</sub>O的電漿處理，主要是希望可以利用N<sub>2</sub>O氣體在電漿環境中所解離出來的O原子可以對IGZO的薄膜進行修補的動作。所以在N<sub>2</sub>O電漿處理後的元件，在270°C二小時的退火後，元件的磁滯現象已經幾乎消除（如圖4-8所示）。

圖4-9 IGZO表面做N<sub>2</sub>O電漿處理，再利用300°C退火下，磁滯現象表現

圖4-10 IGZO表面做N<sub>2</sub>O電漿處理，再利用300°C退火下，磁滯現象表現

若再提高退火溫度到300°C和330°C二小時的退火其磁滯現象也不會再出現（如圖4-9和如圖4-10所示）。

所以在表面電漿處理的實驗中可以知道，IGZO薄膜在利用表面電漿處理再經過高溫的退火後，可以改善膜內的缺陷，IGZO在使用薄膜N<sub>2</sub>O做表面電漿處

理的效果會比利用N<sub>2</sub>電漿做表面處理來得有效，使用N<sub>2</sub>O做電漿處理也可以在更低溫的退火下得到比較佳的元件。

## 4-3 元件的stress改善

### 4-3-1 電漿處理對PBTS現象改善

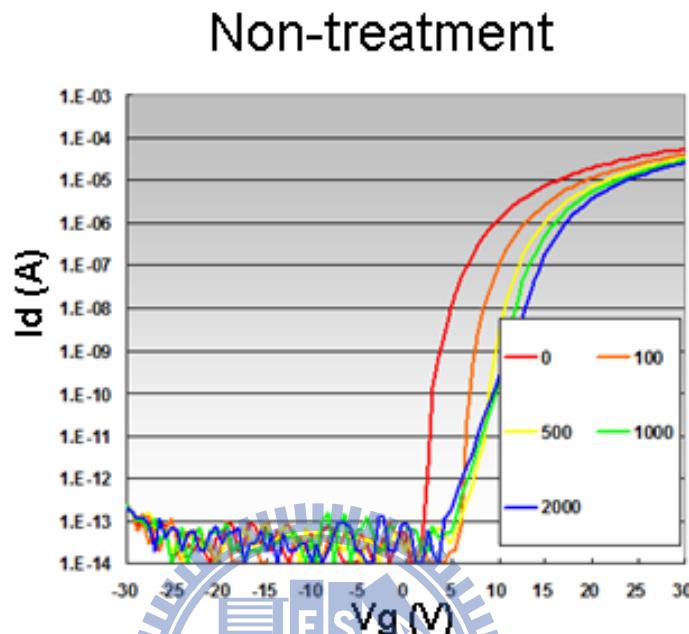

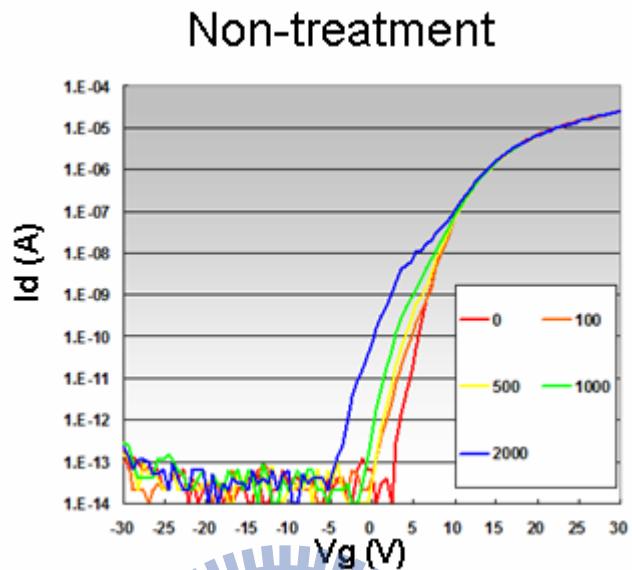

圖4-11 IGZO non-treat利用330°C退火，PBTS表現

在stress的表現下，沒有經過電漿表面處理的元件，在閘極施以50V( $V_g=50V$ )的電壓並在源極和汲極接地( $V_d=V_s=0V$ )，使元件在正電場下產生劣化效果，在 $V_g=50V$ 的作用下，元件界面會產生新的缺陷，在元件導通過程中產生更大的能障，進而使得元件須要更大的啓始電壓才能使半導體層能夠達到導通，(如圖4-11所示)；在 $V_g=50V$ 的劣化時間越長，其元件的啓始電壓會隨之變大。

- 測試條件：

- ✓ PBTS (Positive Bias temperature stress) 條件：

- ✓ 閘極端接電壓設定 $V_g : 50V$

- ✓ 汲極端和源極端接地

- ✓ Stress time (單位: s) : 0 / 100 / 500 / 1000 / 2000

## $N_2$ treatment

圖4-12 IGZO表面做 $N_2$ 電漿處理，再利用330°C退火，PBTS表現

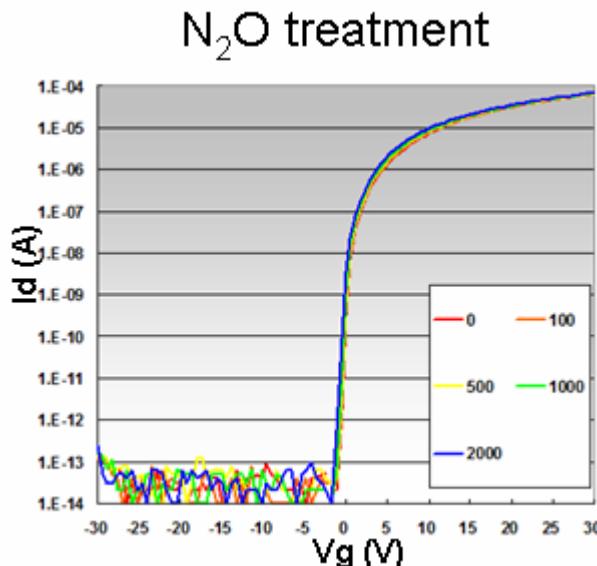

圖4-13 IGZO表面做 $N_2O$ 電漿處理，再利用330°C退火，PBTS表現

若IGZO在經過 $N_2$ 或 $N_2O$ 的表面電漿處理後，其元件在 $V_g=50V$ 下的劣化現象大幅的減小；其明顯的改善了元件的劣化現象；如圖4-12  $N_2$ 表面電漿處理後的劣化現象和圖4-13  $N_2O$ 表面電漿處理後的劣化現象。

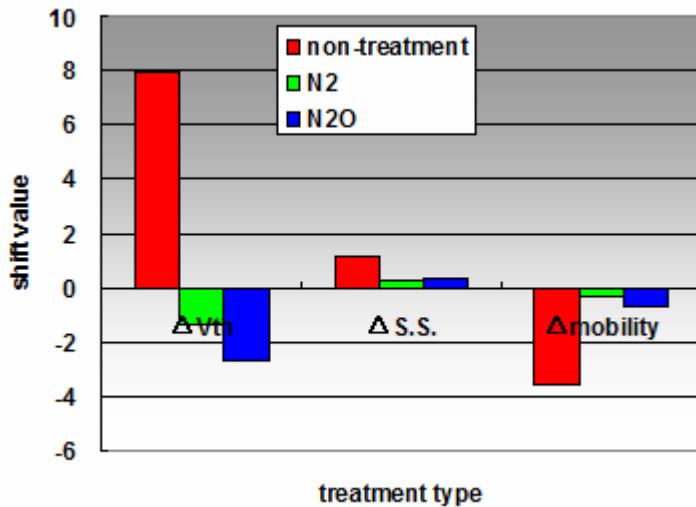

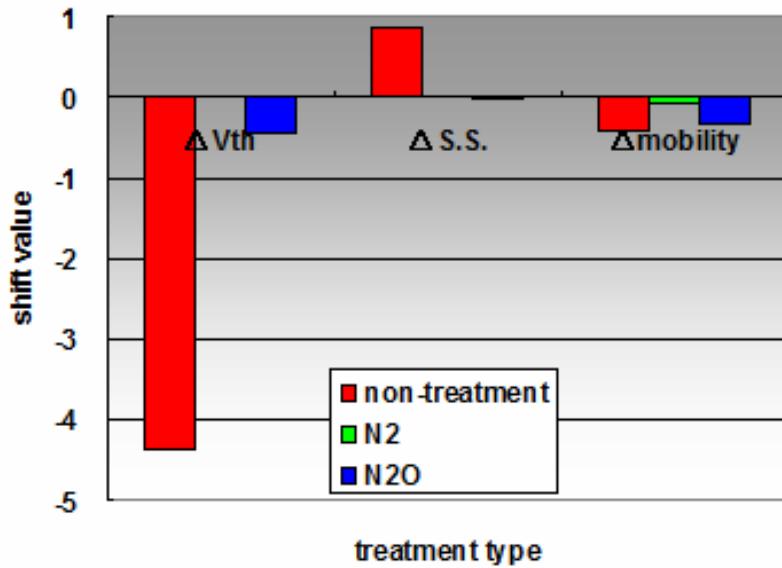

圖4-14 IGZO表面電漿處理，經330°C退火，元件的PBTS效應

圖4-14所示；再經過不同表面電漿處理後，元件在經過 $V_g=50V$ 的劣化條件下，其元件的特性的改善效果；在啓始電壓的漂移幅度，在經過電漿表面處理過後的元件，皆可以得到大幅的改善，由原本在劣化2000秒漂移大於7V的條件下，改善到小於3V，在元件的次臨界電壓方面，在不經過電漿處理的元件會劣化約1.13 V；若經過電漿表面處理後的元件，可以改善至小於0.4V，在元件的mobility方面，在經過表面電漿處理的元件也可以得到改善；其元件變化值如表4-2所示。

表4-2 IGZO表面電漿處理後的元件PBTS改善效果

| Positive stress  | $\Delta V_{th}$ | $\Delta S.S.$ | $\Delta mobility$ |

|------------------|-----------------|---------------|-------------------|

| non-treatment    | 7.97            | 1.13          | -3.57             |

| N <sub>2</sub>   | -1.41           | 0.28          | -0.35             |

| N <sub>2</sub> O | -2.62           | 0.35          | -0.50             |

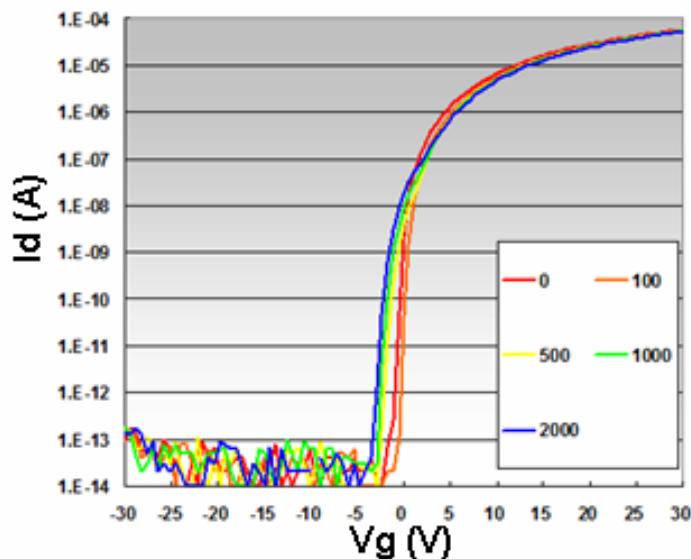

#### 4-3-2 電漿處理對熱載子效應現象改善

圖4-15 IGZO non-treatment利用 $330^{\circ}\text{C}$ 退火，熱載子現象表現

圖4-16 IGZO表面做 $\text{N}_2$ 電漿處理，再利用 $330^{\circ}\text{C}$ 退火，熱載子現象表現

圖4-17 IGZO表面做N<sub>2</sub>O電漿處理，再利用330°C退火，熱載子現象表現

若在熱載子效應的發生條件下 ( $V_g=5V$  and  $V_d=5V$  and  $V_s=0V$ )，沒有經過電漿表面處理的元件，使元件會在  $I_{ds}$  產生電流的條件下，經過長時間的劣化效果，即是若元件在長時間的電流破壞，元件在經過熱載子劣化後，不經過電漿處理的元件其漏電會隨著劣化時時越長，漏電也會隨著越來越大，（如圖4-15 所示）；但經過電漿表面處理後的元件，即使得元件的劣化可以改善。（如圖4-16 N<sub>2</sub>表面電漿處理和圖4-17 N<sub>2</sub>O表面電漿處理）

- 热载子效应劣化 (Hot carrier stress) 条件：

- ✓ 閘極端接電壓設定  $V_g : 5V$

- ✓ 汲極設定電壓  $V_d : 5$

- ✓ 源極端接地

- ✓ Stress time ( 單位: s ): 0 / 100 / 500 / 1000 / 2000

圖4-18 IGZO表面電漿處理，經330°C退火，元件的熱載子效應

圖4-18所示；再經過不同表面電漿處理後，元件在經過熱載子條件劣化下，元件的特性的改善效果；在啓始電壓的漂移幅度，在經過電漿表面處理過後的元件，皆可以得到大幅的改善，由原本在劣化2000秒漂移大於4V的條件下，經過表面電漿處理後，其元件的啓始電壓漂移能夠得到完全的抑制，在元件的次臨界電壓和mobility方面，在經過電漿處理的元件也能夠完全的不受到影響。其元件變化值如表4-3所示。

表4-3 IGZO表面電漿處理後的元件熱載子效應劣化改善效果

| hot carrier stress | $\Delta V_{th}$ | $\Delta S.S.$ | $\Delta mobility$ |

|--------------------|-----------------|---------------|-------------------|

| non-treatment      | -4.36           | 0.84          | -0.42             |

| N <sub>2</sub>     | -0.01           | 0.03          | -0.09             |

| N <sub>2</sub> O   | -0.44           | -0.01         | -0.32             |

## 4-4 討論

### 4-4-1 退火溫度對TFT通道區阻抗的影響

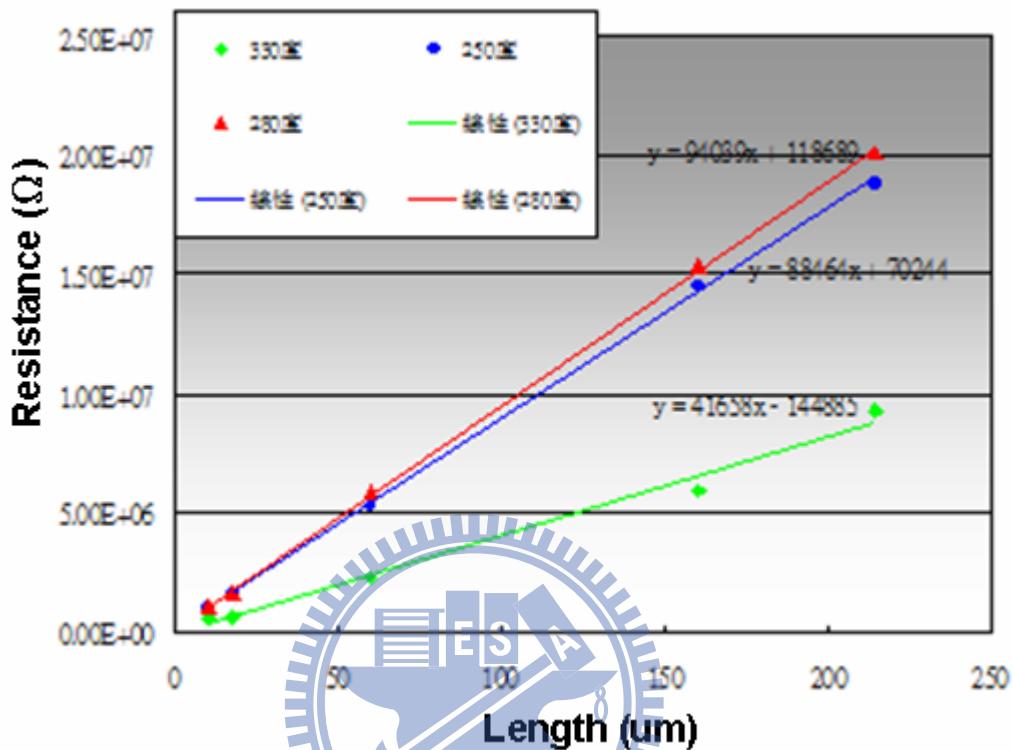

圖4-19 在 $V_g=15V$ 下不同Length下的TFT寄生阻抗值

由圖4-19中可以得知，越高的退火溫度有助於減少元件通道區的阻抗，當元件通道區的阻抗值下降，則可以反應出來元件的on current會提高。不同退火溫度下的通道區阻抗，如表4-4所示。

表4-4 在 $V_g=15V$ 下不同退火溫度下的channel resistance

| @ $V_g=15V$ and 退火溫度 | Channel resistance ( $K\Omega/\text{um}$ ) | Channel resistance ( $\Omega$ ) @ $L=10\text{um}$ |

|----------------------|--------------------------------------------|---------------------------------------------------|

| 330°C                | 42                                         | 42                                                |

| 280°C                | 88                                         | 88                                                |

| 250°C                | 94                                         | 94                                                |

## 4-4-2 電漿表面處理對TFT通道區阻抗的影響

Non -treatment

圖4-20 TLM方式計算在無表面處理的IGZO元件通道區阻抗

$N_2$  -treatment

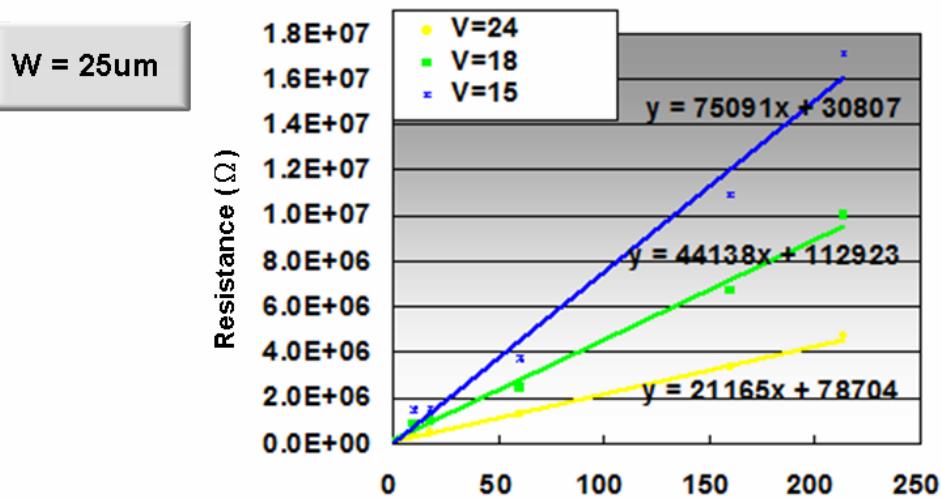

W = 25um

圖4-21 TLM方式計算在 $N_2$ 表面處理的IGZO元件通道區阻抗

圖4-22 TLM方式計算在N<sub>2</sub>O表面處理的IGZO元件通道區阻抗

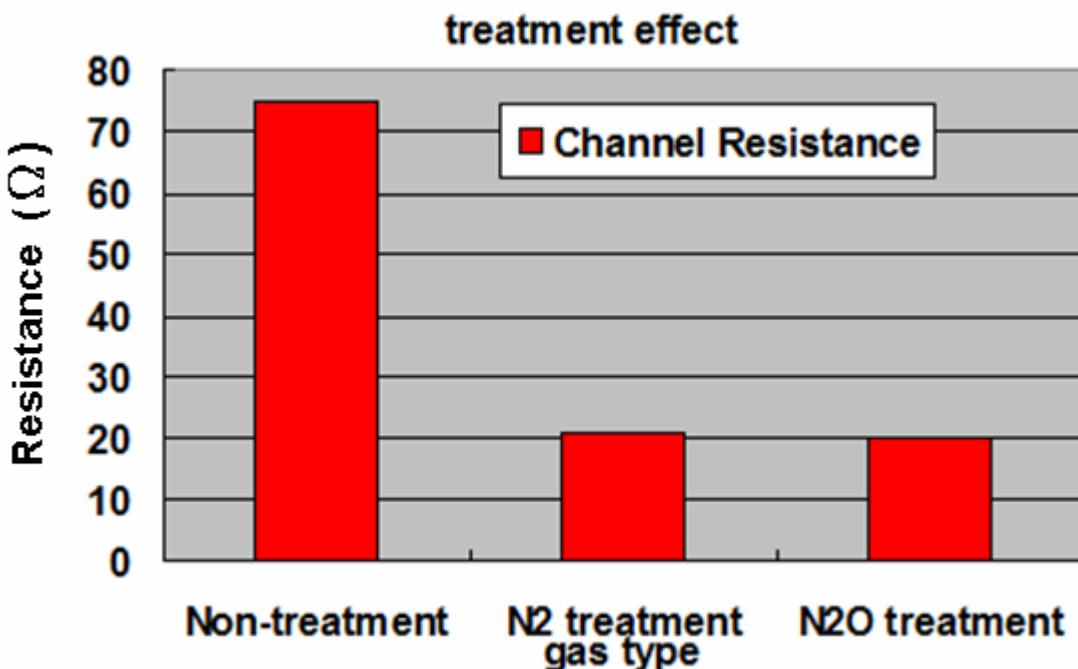

對IGZO膜表面做電漿處理，可以降低其IGZO元件的通道區阻抗值，如圖4-20無表面處理的IGZO元件通道區阻抗、圖4-21 N<sub>2</sub>表面處理的IGZO元件通道區阻抗和圖4-22 N<sub>2</sub>O表面處理的IGZO元件通道區阻抗。其各種電漿處理過後，再經過330°C二小時的高溫退火，所得到的通道區阻抗，如表4-5 在通道寬度W=25 um下的通道阻抗值。

表4-5 TFT在利用TLM所計算出的channel resistance

| @Vg=15V<br>and treatment condition | Channel resistance<br>(KΩ/um) | Channel resistance<br>(Ω) @L=10 um |

|------------------------------------|-------------------------------|------------------------------------|

| Non-treat                          | 75                            | 75                                 |

| N <sub>2</sub> treat               | 21                            | 21                                 |

| N <sub>2</sub> O treat             | 20                            | 20                                 |

圖4-23 利用TLM所計算出的channel resistance

由結果可知；IGZO在經過N<sub>2</sub>或N<sub>2</sub>O表面電漿處理過；可以有效改善通道的阻抗值，也可以提高元件的導通電流。圖4-23也可以明顯看出來，有經過表面處理的元件，可以降低元件的通道阻抗。

#### 4-4-3 IGZO表面氧鍵結分析

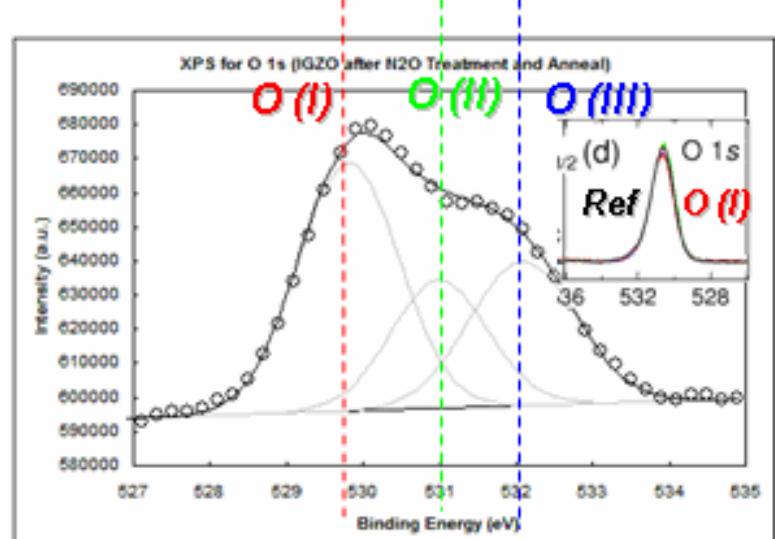

##### XPS表面氧分析

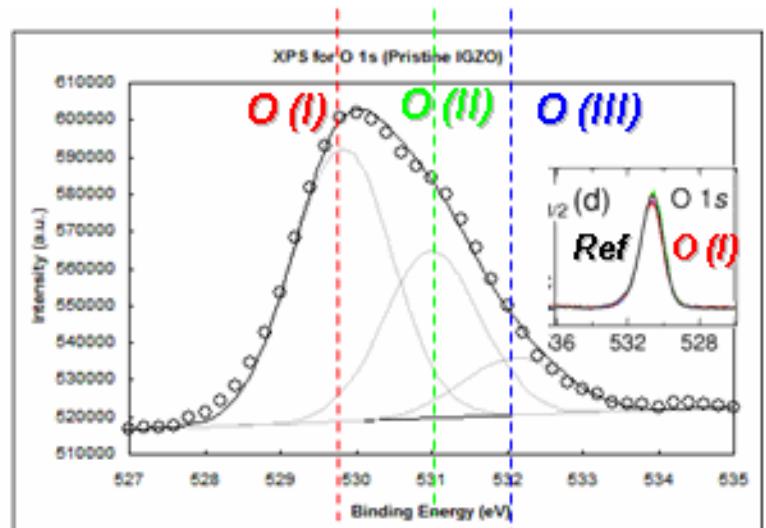

圖4-24 XPS analysis for as-deposited IGZO

##### XPS表面氧分析

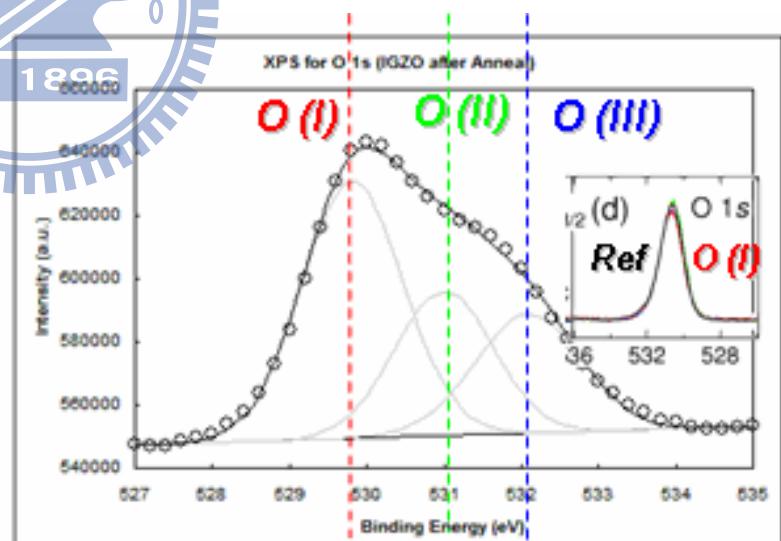

*Thermal Anneal*

O (I) Oxygen w/o vacancy

O (II) Oxygen w/ vacancy

O (III) Hydroxyl M-OH

圖4-25 XPS analysis for after IGZO high temperature anneal

## XPS表面氧分析

O (I) Oxygen w/o vacancy

O (II) Oxygen w/ vacancy

O (III) Hydroxyl M-OH

圖4-26 XPS analysis for after IGZO treat and high temperature anneal

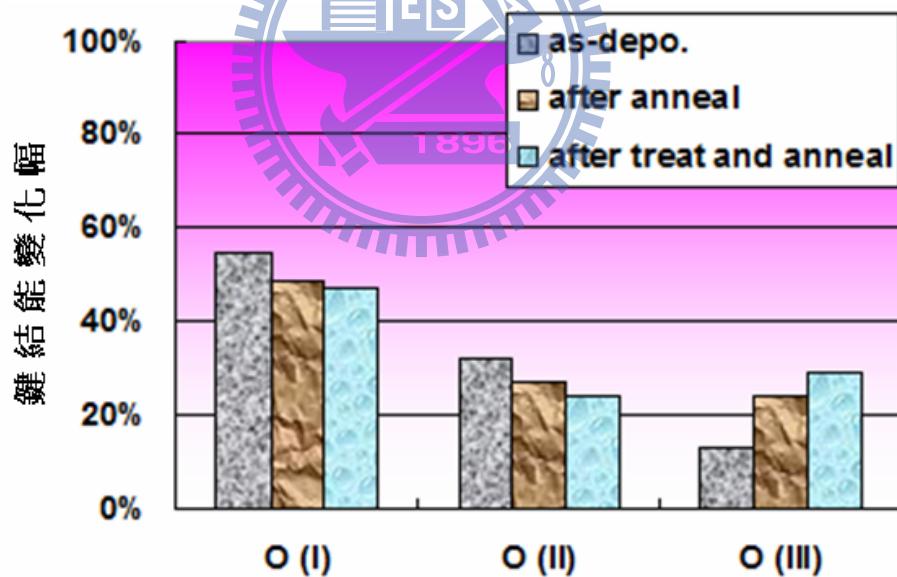

圖4-27 XPS-Oxygen鍵結分析

在確認經過退火處理和表面電漿處理後，元件的特性可以獲得適當的改善後，我們利用了XPS分析了元件的表面在經過高溫退火處理和表面電漿處理後的氧鍵結狀況，如圖4-24、圖4-25和圖4-26可以看出來，無論是在經過高溫退火處理或電漿表面處理後的IGZO膜厚，其氧鍵結狀況皆會發生改變，其M-OH鍵變多了，表面其薄膜內部的金屬和OH鍵更加完整，且其氧和氧缺都濃度也下降了，可見得薄膜內部的缺陷量也變得更少，金屬鍵結變得更完整。

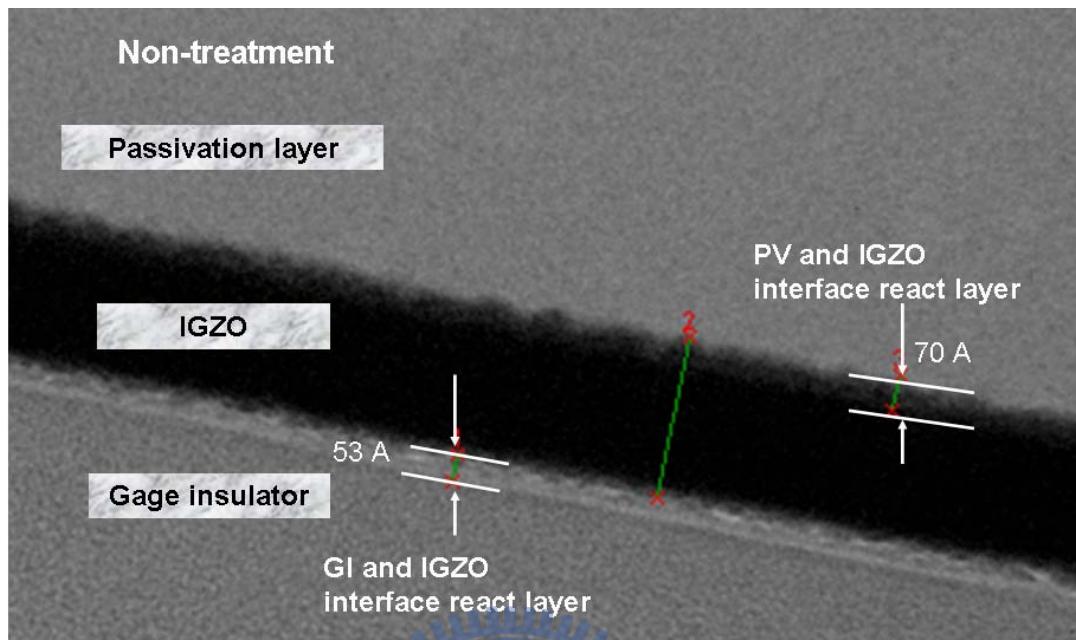

#### 4-4-4 電漿表面處理對IGZO薄膜的影響

圖4-28 IGZO在高溫330°C退火後的膜質變化

圖4-29 IGZO表面做N<sub>2</sub>電漿處理後，經過高溫330°C退火後的膜質變化

圖4-30 IGZO表面做N<sub>2</sub>O電漿處理後，經過高溫330°C退火後的膜質變化

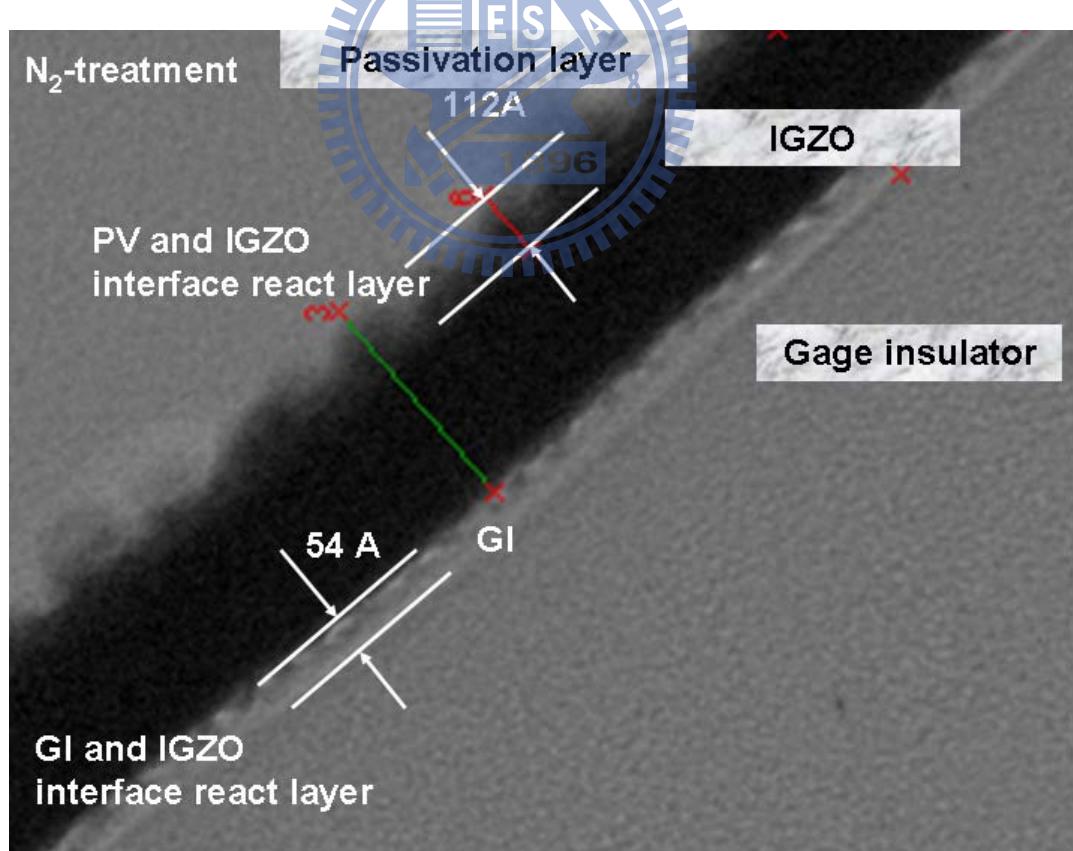

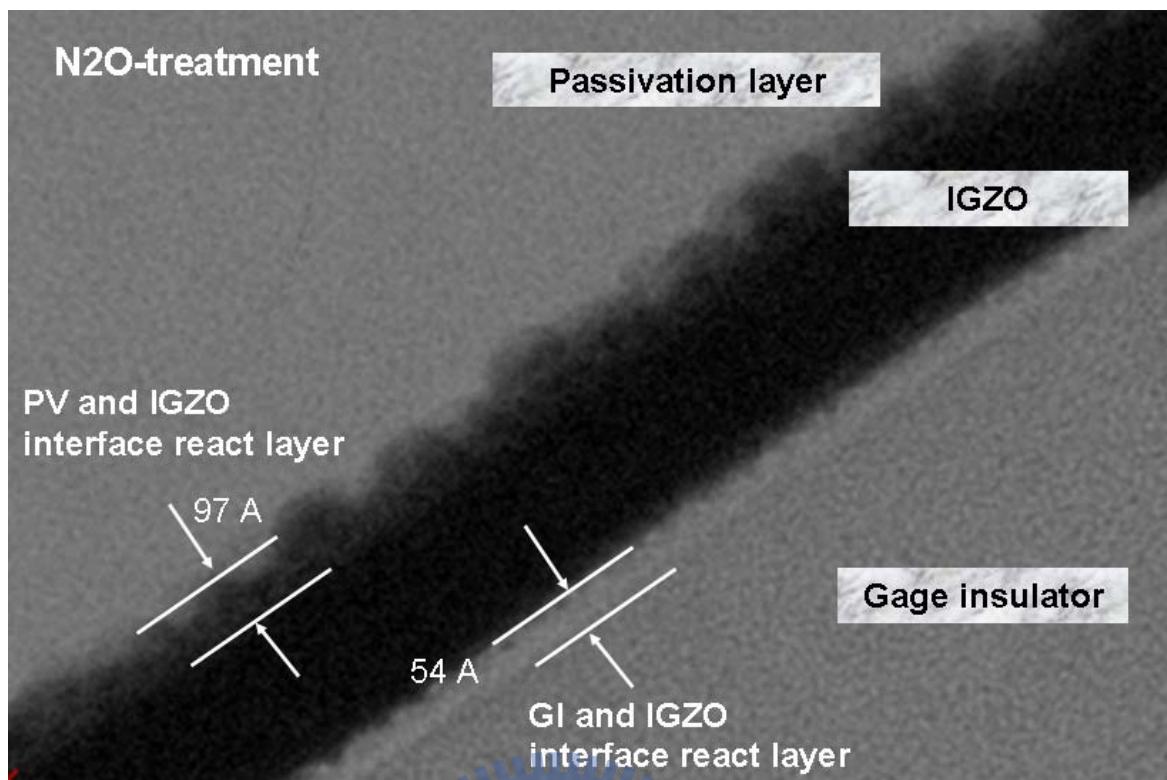

電漿表面處理對IGZO薄膜的影響到底如何呢？我們利用TEM分析看到，再經過N<sub>2</sub>（如圖4-25所示）或N<sub>2</sub>O（如圖4-26所示）表面處理的IGZO薄膜可以明顯的看得出來，薄膜表面會比未經過電漿處理的薄膜表面（如圖4-24所示）生成一層較厚的界面層出來，該層界面應為IGZO表面的因為電漿處理過後額外生成的一層氮化層；有助於改善元件的抗劣化現象。

而在IGZO和GI的界面在三層不同的電漿條件下，經過高溫退火後也會生成一層界面層，但該層薄膜並不會因為電漿處理的條件不同，產生不同的膜厚，可知電漿處理並未影響到IGZO和GI的界面層。在經過IGZO表面電漿處理後並經過高溫退火處理後的IGZO薄膜界面變化的程度如表4-7所示。

表4-6 IGZO表面電漿處理再經過退火後的膜質變化比較表

|                                 | Non treat (Å)  | N2O treat (Å) | N2 treat (Å) |

|---------------------------------|----------------|---------------|--------------|

| GI / IGZO interface react layer | 53             | 54            | 54           |

| PV / IGZO interface react layer | 70             | 97            | 112          |

| PV / IGZO interface             | Thermal effect |               | 70           |

|                                 | Treat effect   | 0             | 27           |

|                                 |                |               | 42           |

# 第5章 結論

TFT LCD朝向大型化發展，無論是面板廠的製程設備，已經發展到10代線的面板廠，還有液晶面板尺寸的大型化，由早期的32吋到現在的55吋和65吋，面板的尺寸也越來越大，解析度也越來越高，所以在薄膜電晶體的材料和元件的特性改善也相對變的重要許多。

在元件的特性改善方式，氧化物半導體的發展和應用也漸漸的重要，因為氧化物半導體有優於非晶矽元件的特性，其設備也有比低溫多晶矽容易大型化的優點，因此氧化物半導體也足以成為次世代元件材料的候選者。

從此次針對IGZO氧化物半導體元件的研究中，我們可以確認幾個對元件有正向改善效果的因子，其一： 在高溫退火後元件的特性則可以最有效的改善，由其是在退火溫度達 $330^{\circ}\text{C}$ 時，經過二個小時的退火後，導通電流明顯提高。其半導體層的導通阻抗也明顯的降低。

IGZO薄膜表面在N<sub>2</sub>或N<sub>2</sub>O表面電漿處理後，且經過高溫的退火處理，皆可穩定並提高元件的特性。N<sub>2</sub> and N<sub>2</sub>O treatment也大幅改善了元件在劣化實驗PBTS (positive gate bias stress) 和熱載子效應 (hot carrier stress) 下的啓始電壓和次臨界電壓偏移現象；元件在這些劣化過程都會比未經過表面電漿處理的元件來得穩定。

由分析實驗中發現在經過IGZO薄膜的表面電漿處理和高溫退火，IGZO和保護層之間會因為電漿處理的原因，使其表面產生一層含氮化的反應層 (~100A)；此層有助於提高IGZO元件對元件劣化的穩定能力，且元件在電漿表面處理有助於IGZO界面的缺陷修補；進而改善元件的信賴性。

## 5-1 後續工作

當TFT LCD的陣列製程在非晶矽amorphous silicon製程中，元件已經無法達到未來平面顯示器所須求的規格，提高元件的性能就是一條必須要走的路；現行的LTPS製程也因為機台大型化不易，再加上設備和製程都較原本的非晶矽高出許多，另一種半導體材料進入到這個市場也會變得有其利基點。未來能達到和非晶矽相同的設備和製程簡易性的材料，金屬氧化物半導體就有其優點。

雖然金屬氧化物半導體沒有和複晶矽的元件一樣佳的元件特性，但在操作電流也比現行的非晶矽要高上10倍以上，但其材料特性容易受到外界環境和製程環境的影響，使得元件可靠度不佳，這也是目前不易被大量生產的主要因素，因此未來如何找到一個好的方式，有效的來控制元件的穩定性，也變成相當重要的課題。

# 參考文獻

- [01] Hideo Hosono , Natot Kikuchi , Naoyuki Ueda , Hiroshi Kawazoe , " Working hypothesis to explore novel wide band gap electrically conducting amorphous oxides and examples " , Journal of Non-Crystalline Solids 198-200 (1996) pp. 165-169

- [02] Kenji Nomura , Hiromichi Ohta , Akihiro Takagi , Toshio Kamiya , Masahiro Hirano , Hideo Hosono , " Room temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors " , NATURE , vol 432 , 25 NOVEMBER 2004 , pp. 488-492

- [03] <http://highscope.ch.ntu.edu.tw/wordpress/?p=1599>

- [04] Jaechul Park , Sangwook Kim , Changjung Kim , Sunil Kim , Ihun Song , Huaxiang Yin , Kyoung-Kok Kim , Sunghoon Lee , Kiha Hong , Jaecheo Lee , Jaekwan Jung , Eunha Lee , Kee-Won Kwon , Youngsoo Park , " High performance amorphous gallium indium zinc oxide thin-film transistors through N<sub>2</sub>O plasma passivation " APPLIED PHYSICS LETTERS , vol 93 , 053505(2008)

- [05] Byung Du Ahn , Hyun Soo Shin , Hyun Jae Kim , Jin-Seong Park , Jae Kyeong Jeong , " Comparison of the effects of Ar and H<sub>2</sub> plasmas on the performance of homojunctioned amorphous indium gallium zinc oxide thin film transistors " , APPLIED PHYSICS LETTERS , vol 93 , 203506 (2008)

- [06] Ayumu Sato , Katsumi Abe , Ryo Hayashi , Hideya Kumomi , Kenji Nomura , Toshio Kamiya , Masahiro Hirano , Hideo Hosono , " Amorphous In-Ga-Zn-O coplanar homojunction thin-film transistor " APPLIED PHYSICS LETTERS , vol 94 , 133502(2009)

- [07] Minkyu Kim , Jong Han Jeong , Hun Jung Lee , Tae Kyung Ahn , Hyun Soo Shin , Jin-Seong Park , Jae Kyeong Jeong , Yeon-Gon Mo , Hye Dong Kim , " High mobility bottom gate InGaZnO thin film transistors with SiO<sub>x</sub> etch stopper " APPLIED PHYSICS LETTERS , vol 90 , 212114(2007)

- [08] JOHN G. J. CHERN , PETER CHANG , RICHARD F. MOTTA , MEMBER IEEE , NORM GODINHO , " A New Method To Determine MOSFET

Channel Length” , IEEE ELECTRON DEVICE LETTERS , VOL. EDL-1 , N O. 9 , SEPTEMBER , 1980 , pp. 170-173

- [09] Jaeseob Lee , Jin-Seong Park , Young Shin Pyo , Dong Bum Lee , Eun Hyun Kim , Denis Stryakhilev , Tae Woong Kim , Dong Un Jin , and Yeon-Gon Mo , ” The influence of the gate dielectrics on threshold voltage instability in amorphous indium-gallium-zinc oxide thin film transistors” , APPLIED PHYSICS LETTERS 95 , 123502(2009)

- [10] Jin-Seong Park , Jae Kyeong Jeong , Yeon-Gon Mo , Hye Dong Kim , ” Improvements in the device characteristics of amorphous indium gallium zinc oxide thin film transistors by Ar plasma treatment” , APPLIED PHYSICS LETTERS , vol 90 , 262106 (2007)

- [11] Ken Hoshino , David Hong , Hai Q. Chiang , John F. Wager , ” Constant Voltage Bias Stress Testing of a-IGZO Thin-Film Transistors” , IEEE TRANSACTIONS ON ELECTRON DEVICES , VOL. 56, NO. 7 , JULY 2009 , pp. 1365-1370

- [12] Rahul Shringarpure , Lawrence T. Clark , ” Localization of Gate Bias Induced Threshold Voltage Degradation in a-Si:H TFTs , ” IEEE ELECTRON DEVICE LETTERS , VOL. 29, NO. 1, JANUARY 2008 , pp. 93-95

- [13] Sung-Soo Park , Won-Ho Choi , Dong-Ho Nam , Kwang-il Chai , Jae-Kyeong Jeong , Hi-Deok Lee , Ga-Won Lee , ” Performance and Stability Characterization of Bottom Gated Amorphous Indium Zinc Oxide Thin Film Transistors Grown by RF and DC Sputtering” , Japanese Journal of Applied Physics , 48 (2009) 04C134

- [14] Kyoung-Seok Son , Tae-Sang Kim , Ji-Sim Jung , Myung-Kwan Ryu , Kyung-Bae Park , Byung-Wook Yoo , Jung-Woo Kim , Young-Gu Lee , Jang-Yeon Kwon , Sang-Yoon Lee and Jong-Min Kim , ” Late-News Paper: 4 inch QVGA AMOLED Driven by the Threshold Voltage Controlled Amorphous GIZO (Ga<sub>2</sub>O<sub>3</sub>-In<sub>2</sub>O<sub>3</sub>-ZnO) TFT” , SID 08 DIGEST , 42-4L , pp. 633-636

- [15] 國家實驗研究院儀器科技研究中心 , ” 奈米檢測技術” 全華出版社 , pp. 163-185