Home Search Collections Journals About Contact us My IOPscience

## High Breakdown P-Channel InSb MOSFET

This content has been downloaded from IOPscience. Please scroll down to see the full text.

1990 Jpn. J. Appl. Phys. 29 L398

(http://iopscience.iop.org/1347-4065/29/3A/L398)

View the table of contents for this issue, or go to the journal homepage for more

Download details:

IP Address: 140.113.38.11

This content was downloaded on 28/04/2014 at 19:52

Please note that terms and conditions apply.

## **High Breakdown P-Channel InSb MOSFET**

S. L. Tu, W. H. Lan, T. S. Chiou<sup>†</sup>, S. J. Yang<sup>†</sup> and K. F. Huang<sup>††</sup>

Institute of Electro-Optical Engineering, National Chiao Tung University, Hsinchu, Taiwan

†Chung-Shan Institute of Science and Technology Lung-Tan, Taoyuan, Taiwan, R.O.C.

†Department of Electrophysics, National Chiao Tung University, Hsinchu, Taiwan

(Received December 11, 1989; accepted for publication February 8, 1990)

P-channel InSb MOSFET is fabricated by anodic oxidation and SiO evaporation for the MOS gate structure and by Cd diffusion for the source and drain. A breakdown voltage exceeding 11 V is obtained in the drain junction, which renders the drain current saturation fully observable. An on-off ratio of 10<sup>4</sup> in the drain current is also obtained, indicating that the present InSb MOSFET is useful for a good switching operation.

KEYWORDS: InSb p-n junction, MOSFET

InSb p-n junction diodes have been shown to be excellent photodiodes in the spectral range of 3-5  $\mu$ m.<sup>1,2)</sup> It is also known that InSb has a very high electron mobility and a high saturation velocity. These intrinsic properties make InSb an attractive material for the application to high-speed MOSFET devices. Furthermore, monolithic approach to infrared imaging by the integration of MOSFET with photodiodes on InSb becomes highly desirable if considerations such as readout noise and switching speed are taken.<sup>3)</sup> Though the photodiodes are reported to have excellent properties, the characteristics of fabricated InSb MOSFETs are still not satisfactory enough to be used in the monolithic approach. Shappir, Margalit and Kidron<sup>4)</sup> had successfully fabricated an InSb p-channel MOS transistor with the source and drain defined by mesa etching in a Cd diffused p layer and the gate formed by evaporation of chromium and gold on top of a SiO<sub>2</sub> layer. However, a large drain current due to tunneling at the surface of the p<sup>+</sup> drain region under the overlapping gate caused the subthreshold characteristics to be insufficient for the switching operation. Fujisada<sup>3)</sup> fabricated a planar-type p-channel InSb MAOSFET by anodic oxidation and sputtering for the MAOS gate, and Be ion implantation for the source and drain. An excellent on-off ratio of the order of 105 was obtained in the drain current. However, the device showed a maximum voltage of only -2 V, which was not large enough to observe complete saturation of the drain current. This imposed a limit on the FET, and efficiency operation in the saturation region was impossible. In order to have good subthreshold characteristics and high drain junction breakdown voltage, suppression of the tunnel current at the surface along with a high-quality InSb p-n junction is required.

In this letter, we report a p-channel MOSFET fabricated by a two-temperature-zone Cd diffusion for the source and drain on  $(\overline{111})$ -oriented n-type InSb with a carrier concentration of  $1 \times 10^{14}$  cm<sup>-3</sup> at 77 K. The two-temperatur-zone diffusion technique was described in a previous publication.<sup>5)</sup> The diffusion was carried out with the Cd source at 380°C and InSb substrate at 440°C. Since the diffusion was carried out with separate Cd

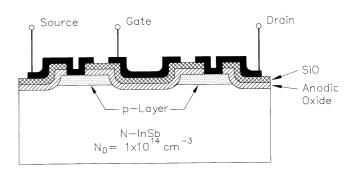

source and InSb substrate temperatures, it is believed that, while still being able to maintain the substrate surface morphology, the carrier concentration at the surface of the p<sup>+</sup> drain region can be increased sufficiently to protect against the formation of a field-induced junction due to band bending. This advantage provided by the twotemperature diffusion technique is crucial for the preparation of high-quality InSb FET since the field-induced junction formed under the gate overlapping the reverse biased drain junction is known to usually be the origin of the surface tunnel current and the cause of early drain junction breakdown. 6 The source and drain regions were then defined by etching through the diffused p-layer forming a mesa structure. The wafer was then anodized in 0.1 N KOH solution by a Keithley 220 current source at a current density of  $7 \times 10^{-4} \,\mathrm{A/cm^2}$  for 5 minutes. The resulting anodized oxide had a thickness of roughly 700 Å. After the anodic oxidation, a SiO layer with a thickness of 1500 Å was evaporated onto the surface; then the contact windows were etched by a plasma etcher, followed by Cr-Au evaporation. Figure 1 shows a cross-sectional view of the InSb MOSFET used in this study. The channel length and width were 50  $\mu$ m and 200  $\mu$ m, respectively. All the *I-V* characteristics were measured in the dark at 77 K with the source of the FET connected to the ground.

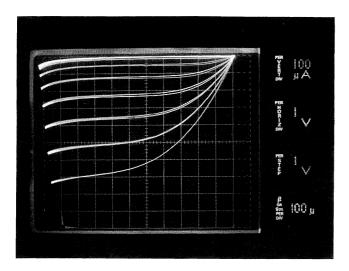

Shown in Fig. 2 are the drain current-drain voltage characteristics for different gate voltages. The device clearly displays typical MOS characteristics in the ohmic

Fig. 1. Cross-section view of InSb MOSFET used in this work.

Fig. 2. Drain current-Drain voltage characteristics as a function of gate voltage. Horizontal:  $1 \text{ V/div. Vertical: } 100 \,\mu\text{A./div. Gate Voltage: } 10 \text{ steps with } 1 \text{ V increments.}$

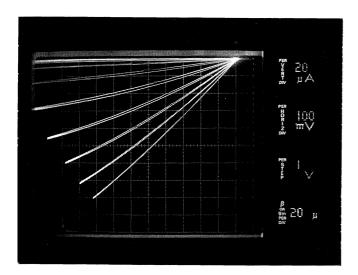

Fig. 3. Drain current-drain voltage in the ohmic region. Horizontal: 100 mV/div. Vertical:  $20 \, \mu\text{A/div.}$  Gate voltage: 10 steps with 1 V increments.

and saturation regions. The high breakdown voltage (exceeding 11 V) enables clear observation of the saturation region, which was not observed in the device reported previously by Fujisada.<sup>3)</sup>

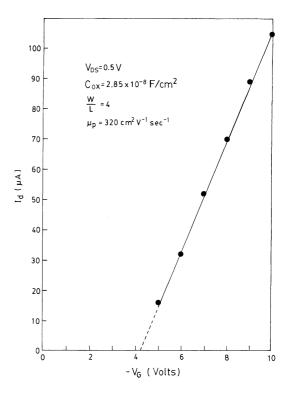

The *I-V* characteristics in the ohmic region are shown in Fig. 3. The drain current in this region versus gate voltage for  $V_{\rm DS}$ =500 mV, as taken from Fig. 3, is plotted in Fig. 4. The data fit the well-known approximate relation,

$$I_{\rm D} = (w/L)C_{\rm ox}\mu V_{\rm D}(V_{\rm G} - V_{\rm T}),$$

where w and L are the length and width of the channel, respectively,  $C_{\rm ox}$  is the gate oxide capacitance per unit area, and  $V_{\rm T}$  is the threshold voltage. From the slope of the straight line and its intersection with the abscissa, the surface hole mobility  $\mu_{\rm p}$  and threshold voltage are determined to be  $320~{\rm cm}^2/{\rm V}\cdot{\rm s}$  and  $4.2~{\rm V}$ , respectively. It is also observed from Fig. 2 that the drain current begins to

Fig. 4. Drain current plotted against gate voltage for  $V_{DS} = 500 \text{ mV}$ .

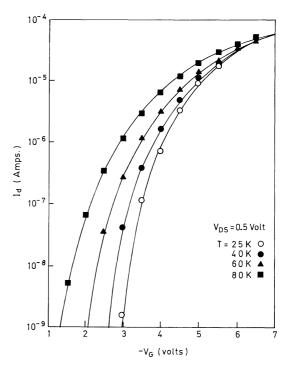

Fig. 5. Transfer characteristics of InSb MOSFET with temperature as a parameter.

saturate at a drain voltage  $V_{\rm D_{\rm sat}} = V_{\rm G} - V_{\rm T}$ , which also agrees well with the MOS transition theory. The threshold voltage was found to depend on the history of the gate voltage application, as has been reported by Fujisada. This is understandable because the well-known hysteresis effect is usually present in such MOS structures.

Shown in Fig. 5 are the I-V characteristics for  $V_{\rm DS}$  = 500 mV in the subthreshold region at four different temperatures T=25, 40, 60, 80 K. For voltages below the threshold, the drain current depends roughly exponentially on the gate voltage. Since leakage current due to tunneling at the surface of the p<sup>+</sup> drain region under the gate is known to increase sharply with the decrease of the gate voltage, 7) the present MOS transistor clearly showed no indication of such a large leakage current. The subthreshold swing, defined usually as the gate voltage swing required to reduce the current by one order, can be calculated from Fig. 5. The subthreshold swing at 80 K determined from the current varied from 10<sup>-6</sup> to 10<sup>-8</sup> amps was roughly 600 mV/order. This value is to be compared with that of roughly 700 mV/order calculated from the reported data of Fujisada.3 Also noted in Fig. 5 is that the subthreshold swing is reduced to 400 mV/order as the temperature is decreased to 25 K. This improvement is expected, but does not agree exactly with the predicted kT/q dependence.<sup>8)</sup> An on-off ratio of the order of 104 was obtained in the drain current. This is comparable to that reported by Fujisada.3)

In conclusion, we have fabricated a p-channel InSb MOSFET with high breakdown voltage and good subthreshold behavior. Breakdown voltage exceeding 11 V

was observed, which rendered the drain current saturation region fully observable. An on-off ratio of 10<sup>4</sup>, comparable to that of devices reported previously, is also realized. It is believed that such a high-quality MOSFET was made possible by using the so called two-temperature-zone Cd diffusion technique. The problems of threshold voltage shift and low channel mobility are still present. An oxide deposition process, such as LTCVD, with the vapor etch technique may be the solution to these problems.

## References

- C. Y. Wei, K. I. Wang, E. A. Taft, J. M. Swab, M. D. Gibbons, W. Davern and D. M. Brown: IEEE Trans. Electron Devices ED-27 (1980) 170.

- R. D. Thom, T. L. Koch, J. D. Langan and W. J. Parrish: IEEE Trans Electron Devices ED-27 (1980) 160.

- 3) H. Fujisada: Jpn. J. Appl. Phys. 24 (1985) L835.

- J. Shappir, S. Margalit and I. Kidron: IEEE Trans. Electron Devices ED-22 (1975) 960.

- S. L. Tu, K. F. Huang and S. J. Yang: Jpn. J. Appl. Phys. 28 (1989) L1874.

- S. Margalit, J. Shappir and I. Kidron: J. Appl. Phys. 46 (1975) 3999.

- 7) H. Fujisada and M. Kawada: Jpn. J. Appl. Phys. 24 (1985) L76.

- 8) S. M. Sze: *Physics of Semiconductor Devices* (Wiley, New York, 1981) 2nd ed., p. 451.