國立交通大學

電子工程學系 電子研究所

碩士論文

氟化製程應用於金氧半場效

電晶體鈍化層之特性與研究

Characteristics and Investigation of FSG

Passivation Layer on HfO<sub>2</sub>/SiON

Gate Stack MOSFETs

研究 生：莊哲輔

Che-Fu Chuang

指 導 教 授：羅 正 忠 博 士

Dr. Jen-Chung Lou

邱 碧 秀 博 士

Dr. Bi-Shiou Chiou

中華民國 九十八 年 七 月

氟化製程應用於金氧半場效

電晶體鈍化層之特性與研究

Characteristics and Investigation of FSG

Passivation Layer on HfO<sub>2</sub>/SiON

Gate Stack MOSFETs

研究 生：莊哲輔

Student : Che-Fu Chuang

指 導 教 授：羅正忠 博 士

Advisor : Dr. Jen-Chung Lou

邱碧秀 博 士

Dr. Bi-Shiou Chiou

A Thesis

Submitted to

Department of Electronics Engineering & Institute of Electronics

College of Electrical and Computer Engineering

National Chiao Tung University

In Partial Fulfillment of the Requirements

For the Degree of Master of Science

In

Electronic Engineering

July 2009

Hsinchu, Taiwan, Republic of China

中華民國 九十八 年 七月

# 氟化製程應用於金氧半場效 電晶體鈍化層之特性與研究

研究生：莊哲輔

指導教授：羅正忠 博士

邱碧秀 博士

國立交通大學 電子工程學系 電子研究所

根據2008 ITRS PIDS Meeting所訂出最新金氧半場效電晶體之閘極奈米尺寸的演變趨勢，因受到新穎閘極材料無法持續之前最低可容忍漏電流規範，使得高效能和低功率應用的奈米微電子元件需延緩三或五個製程世代，本文中提出與現有製程具高度匹配性的四氟化碳電漿處理( $CF_4$  plasma treatment)技術，利用氟化矽玻璃(FSG)當n型金氧半場效電晶體鈍化層的製程，在最後Sintering修補金屬界面斷鍵過程中，使氟原子有效擴散至高介電閘極本體和通道界面處，實驗結果顯示元件的電特性和可靠度可藉由通入適量的 $CF_4$ 氣體達到明顯的改善，因此

可改善遷移率衰退以提昇驅動電流表現、較低次臨界擺幅和閘極漏電流、閘極引起汲極漏電流有明顯降低輸出等。

此外也分析可靠度劣化程度，在正偏壓-溫度應力(PBTS)和熱載子應力(HCS)可靠度特性上都有改善的效果，觀察到在電壓應力破壞下，均有較小的臨界電壓的偏移、較少的本體電子捕捉與界面狀態密度改變而引起元件的不穩定性，且在正電壓應力(PBS)與熱載子應力比較之下，熱載子應力造成的可靠度衰減相較於正電壓應力有顯著嚴重趨勢。這些元件電特性獲得改善及具有高度穩定性的可靠度呈現，造成的原因是來自於氟原子併入高介電閘極主體以及閘極層與通道界面間，不僅僅可減少界面狀態的懸空鍵結(interface dangling bond)和較低界面狀態產生，且進一步有效減少高介電閘極主體電荷捕捉情形。

最後在應力測試後再進行回復(relaxation)的行為，可分離HCS是由cold和hot載子兩個成份構成熱載子應力引起臨界電壓的偏移效應，其中cold載子具有逃逸(de-trapping)特性而hot載子會殘留在介電層形成永久傷害，不管在PBS或是HCS的回復行為，明顯觀察到氟化鈍化層元件有較少載子捕捉情形(應力下)及較高逃逸能障使得有較少逃逸現象產生(回復下)，這與先前討論Frenkel-Poole傳導機制，其比一般鈍化層有較深的載子捕捉位置有好的關連性。

# Characteristics and Investigation of FSG Passivation Layer on HfO<sub>2</sub>/SiON Gate Stack MOSFETs

Student : Che-Fu Chuang

Advisor : Dr. Jen-Chung Lou

Dr. Bi-Shiou Chiou

Department of Electronics Engineering & Institute of Electronics

College of Electrical and Computer Engineering

National Chiao-Tung University

According to establishing the newest evolutionary trend for the gate nano scale of MOSFETs from ITRS PIDS Meeting in 2008 year, the nano microelectronic devices applied high performance and low power function circuits must put off three or five process generation because the novel gate materials can be unable to sustain the criterion of the least gate leakage current tolerably previous works. A process-compatible CF<sub>4</sub> plasma treatment technique for fabricating fluorinated silicate oxide (FSG) as a passivation layer of n-MOSFETs is demonstrated in this work. Fluorine was effectively diffused into the high-k gate dielectric and the interface between channel and gate

dielectric during sintering step. Experimental results reveal that remarkably improved device performance and reliability can be achieved with appropriate  $\text{CF}_4$  gas introduced. Thus, the electrical characteristics improvement exhibits driving current enhanced due to mobility improvement, good subthreshold slope, low gate leakage current, obviously reduced GIDL current and so on.

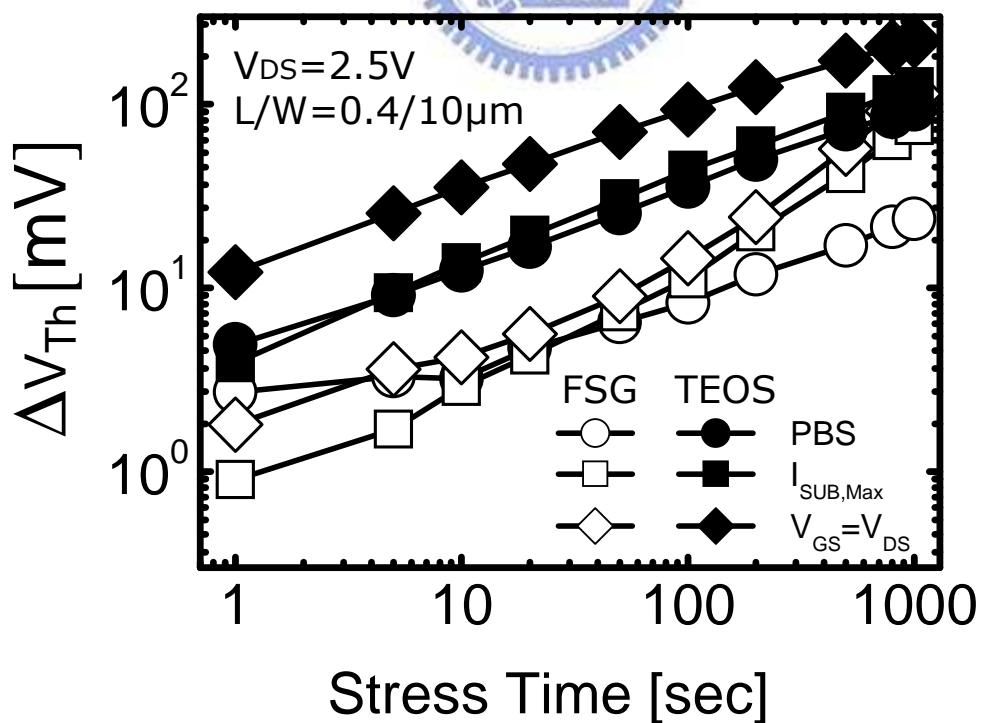

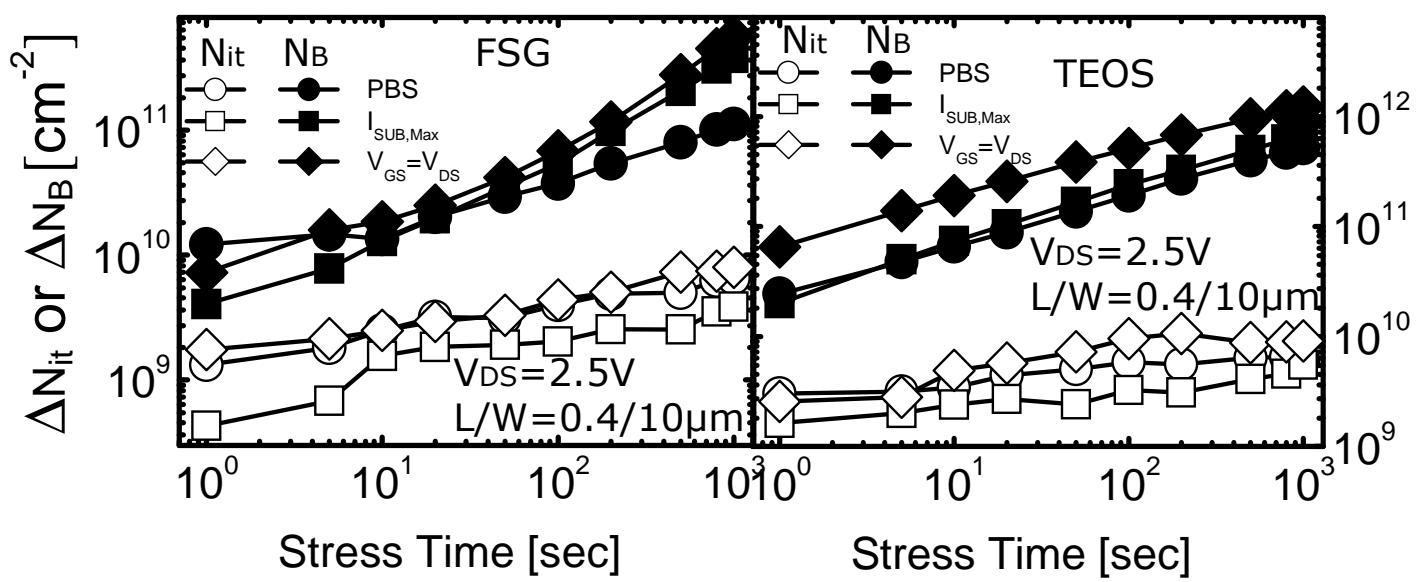

In addition, the fluorinated P.L. ( the abbreviation of passivative layer) also improves the device reliability with respect to positive bias temperature stress (PBTS) and hot-carrier stress (HCS). We observe that less threshold voltage shift, less generated bulk trap density and interface state density shift during voltage stressing, which suppressing the instability characteristics due to device damage. For n-MOSFET devices with TEOS P.L. or FSG P.L., compared PBS and HCS, we find that the HCS phenomenon on reliability degradation is more serious than PBS. It shows the improvement of electrical characteristics and good stability as well as reliability in devices for FSG P.L. as a result of the fluorine atoms incorporated into high-k gate dielectric and the interface between gate dielectric and channel, which not only reducing interface dangling bonds and lower generation rates of interface states, but also effectively lowering carrier trapping in high-k dielectric further.

Finally, the relaxation behavior after hot carrier stressing test could

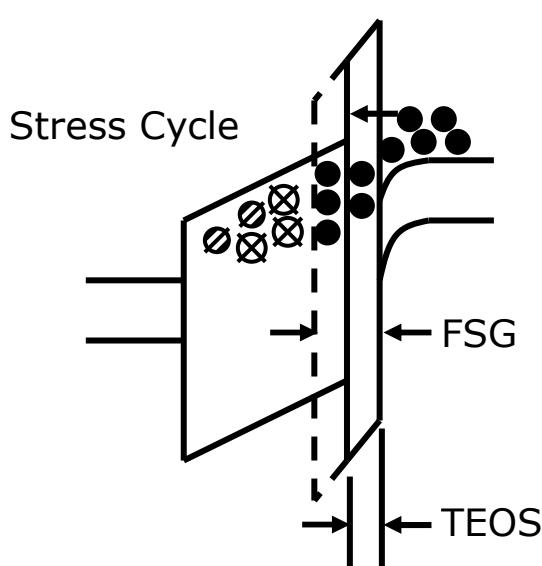

separate cold carrier from hot carrier, which the effect of total threshold voltage shift coming of cold and hot carriers. The cold carrier contribution is shown to be reversible while hot carrier trapping induces permanent damage of the dielectric. It is clearly noted for devices of fluorinated passivation layer that less carriers are captured in high-k bulk dielectric and interface (stress cycle) but less captured carriers take place de-trapping behavior due to higher de-trapping barrier height (relaxation cycle). As observed above, it shows a good correlation between F-P transport mechanism and de-trapping behavior that the position of carriers trapping for FSG P.L. are deeper than that for TEOS P.L..

## 誌謝

隨著實驗進度和成果一天一天的完成，也代表在交大校園的碩士生涯將慢慢地告一段落，雖然在實驗、生活和各方面上協助過我的人許多為一面之緣，但是你們的熱忱和愛心讓小弟不得不先和你們致上深深的敬意。再來，能順利完成這個學位，當然要非常地感謝我的兩位指導教授-羅正忠博士及邱碧秀博士，他們在實驗研究與論文上不但給予充分詳實的指導與鼓勵外，也讓我從他們身上學到很多寶貴知識和學問，更重要的是，學到老師處理事情的態度和方法，讓我深刻感受到在實驗研究應該朝勤奮不懈、實事求是及結合最新科技新知與技術的研究精神去努力外，還要懂得在社會上為人處事與永遠保持接受新事物和挑戰的心態去迎接未來的大小考驗。

此外也要感謝實驗室學長及學弟妹的幫忙與照顧，尤其佳樺、元愷、國洲、信富、小陸、晨修、嘉宏、岳展各學長們在實驗操作及量測方面不遺餘力的教導以減少我摸索時間，最重要的是智仁學長在論文上給我相當大幫忙，讓我茫茫然地從不知道研究目標為那個方向才是適合我的，直到本文的完成，感謝學長平時用心指導與 meeting 上導正我錯誤觀念及教導如何掌握研究重點並實現之，另外威良學長也是讓我非常感謝的，總是把自己豐富的學識素養主動與學弟妹分享及生活上的關懷，且常常提起 paper 重要性及如何從中研讀重點和解疑惑，讓我在學習效率增進不少，這兩位學長總在遇到實驗瓶頸導引我往明確的下一步前進和量測分析給予我適時的指導與糾正，所以以萬分的心意來致上。同時，也感謝陳維邦、周坤億、黃崧宏、李振銘等學長和我同屆的伙伴們，翊裳、汶錦、信宇、侑廷、介銘、天佑、志文等同學及朋友在這兩年來的互相扶持與研究中相互討論和砥勵，當然尚勳、文新及芳毓三位學弟妹除了本身具有強烈學習慾與求知慾的潛力研究生特質外，也誠摯感謝你們平時和實驗上對於我的幫忙與協助。

最後，要是沒有爺爺、父親-明俊、母親-麗雪、愛車成痴的大哥、兩位仙女下凡的姐姐及好男人的大姐夫等家庭成員，在我遇到各種風風雨雨及阻撓、低潮期，總是用溫暖的心來溶解快要結凍的沈重步伐，才使我更有動力大步往前該有的人生目標，感謝平日對於小弟我的關懷及照顧，也因為你們，我才能夠專心完成碩士學業，總之，感謝這些幫忙過我和沒提及但烙印在我心中的人。

# Contents

|                                        |     |

|----------------------------------------|-----|

| <b>Abstract (Chinese)</b> .....        | I   |

| <b>Abstract (English)</b> .....        | III |

| <b>Acknowledgments (Chinese)</b> ..... | V   |

| <b>Contents</b> .....                  | VI  |

| <b>Table Captions</b> .....            | IX  |

| <b>Figure Captions</b> .....           | XVI |

|                   |                                                     |

|-------------------|-----------------------------------------------------|

| <b>Chapter 01</b> | <b>Introduction to High-k Gate Dielectrics</b>      |

| 1.1               | General Background.....01                           |

| 1.2               | Motivation.....04                                   |

| 1.3               | Recent High-k Gate Dielectrics.....07               |

|                   | 1.3.1 Criteria for High-k Gate Dielectrics.....07   |

|                   | 1.3.2 Challenges to High-k Technology.....10        |

| 1.4               | Overview of Enhancing Robustness by Fluorine.....11 |

| 1.5               | Organization of the Thesis.....13                   |

| 1.6               | References.....16                                   |

|                   |                                                                                                                    |

|-------------------|--------------------------------------------------------------------------------------------------------------------|

| <b>Chapter 02</b> | <b>Effects of FSG Passivation from Various CF<sub>4</sub> Flow on the Properties of HfO<sub>2</sub> Thin Films</b> |

| 2.1               | Introduction.....22                                                                                                |

| 2.2               | Experimental Procedure.....23                                                                                      |

|                   | 2.2.1 Device Fabrication Flow.....24                                                                               |

|                   | 2.2.2 Suitable Measurement Setup.....26                                                                            |

| 2.3               | Result and Discussions.....27                                                                                      |

|                   | 2.3.1 Basic Device Characteristics.....27                                                                          |

|                   | 2.3.2 Current Transport Mechanism.....31                                                                           |

|                   | 2.3.3 GIDL Effect on Off-State Leakage.....35                                                                      |

| 2.4               | Summary.....37                                                                                                     |

| 2.5               | References.....39                                                                                                  |

| <b>Chapter 03</b> | <b>Reliability Issues of FSG Passivation on HfO<sub>2</sub> Gate Dielectrics</b>                                   |

| 3.1               | Briefly Reliability Review.....64                                                                                  |

| 3.2               | Effects of Various P.L. on PBTI Characterization.....66                                                            |

|                   | 3.2.1 Static and Dynamic Trapping Measurements Setup.....66                                                        |

|                   | 3.2.2 Threshold Voltage ( $V_{th}$ ) Instability.....67                                                            |

|                   | 3.2.3 The Characteristics of Charge De-trapping.....72                                                             |

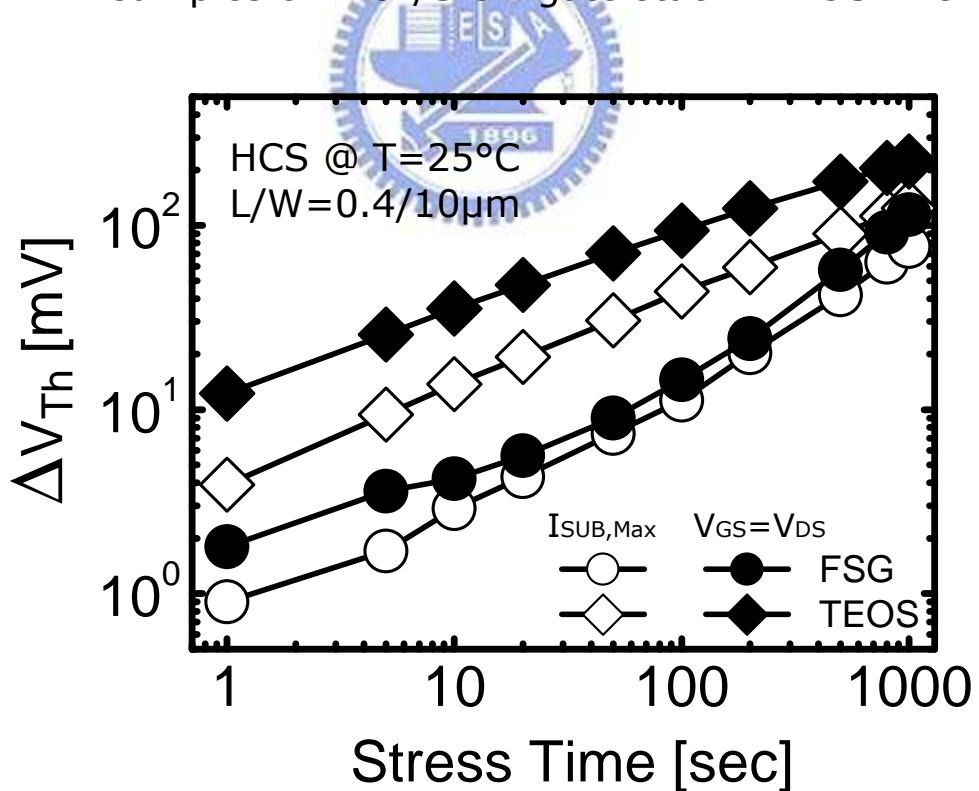

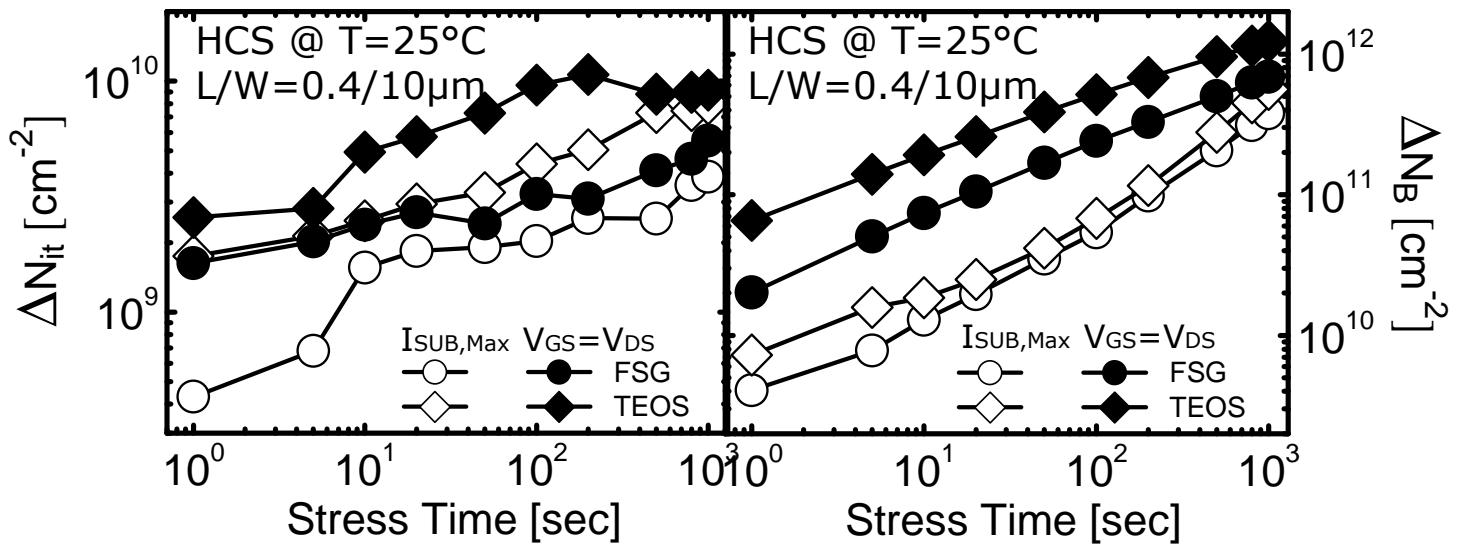

| 3.3               | Reliability Impact of Various P.L. on HCS .....74                                                                  |

|                   | 3.3.1 HCS Measurement Setup.....74                                                                                 |

|                   | 3.3.2 Cold and Hot Carrier Charge Trapping Effects.....75                                                          |

| 3.4               | Summary.....78                                                                                                     |

| 3.5               | References.....80                                                                                                  |

## Chapter 04      Conclusions and Suggested Future Works

|                     |                                   |     |

|---------------------|-----------------------------------|-----|

| 4.1                 | Conclusions.....                  | 100 |

| 4.2                 | Suggestions for Future Works..... | 102 |

| Vita (Chinese)..... |                                   | 103 |

# Table Captions

## Chapter 01

Table 1.1 2008 International Semiconductor Technology Roadmap predicts rapid reduction in the future technology trends for high performance logic, LOP, and LSTP devices.

## Chapter 02

Table 2.1 Conditions of gas flow rates to deposit FSG passivation layers.

Table 2.2 Trend of electrical properties for  $\text{HfO}_2/\text{SiON}$  gate stack n-MOSFET for all splits of different passivation layer.

# Figure Captions

## Chapter 01

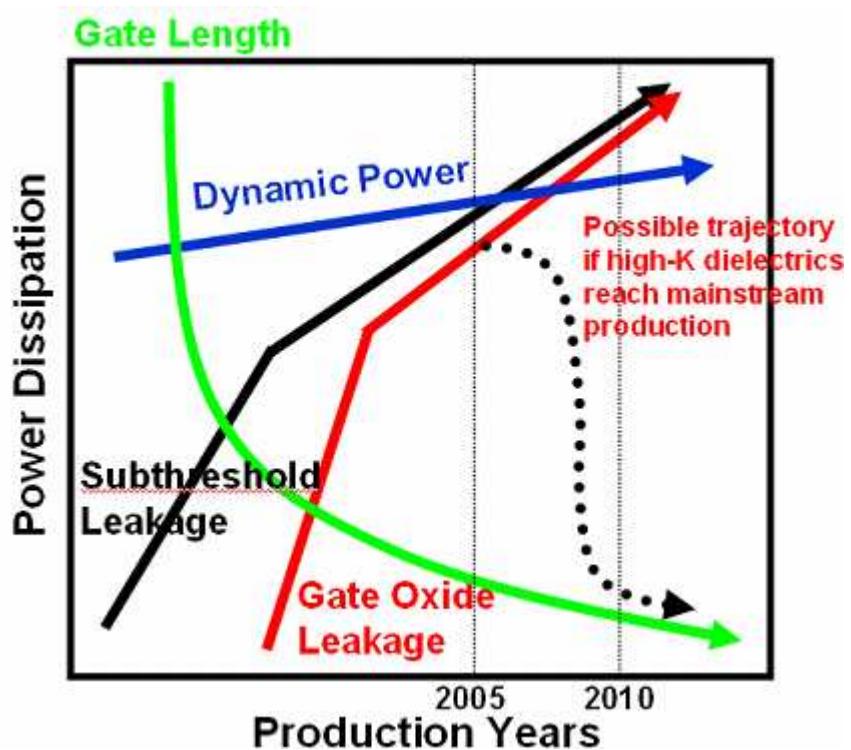

Fig. 1.1 Power dissipation (dynamic + static power) with each generation

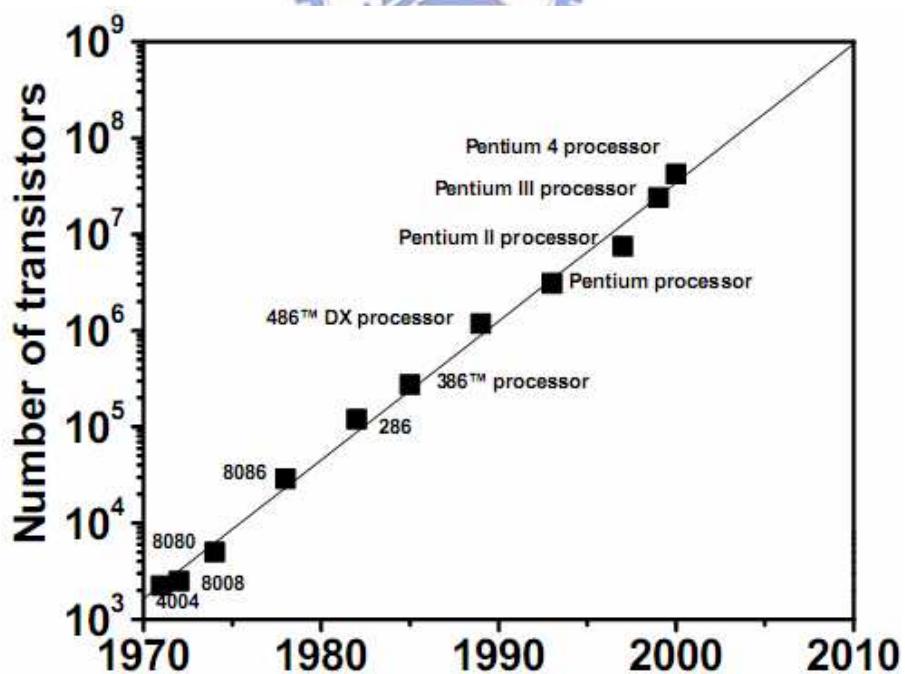

Fig. 1.2 The number of transistors in Intel processors increases exponentially over the years

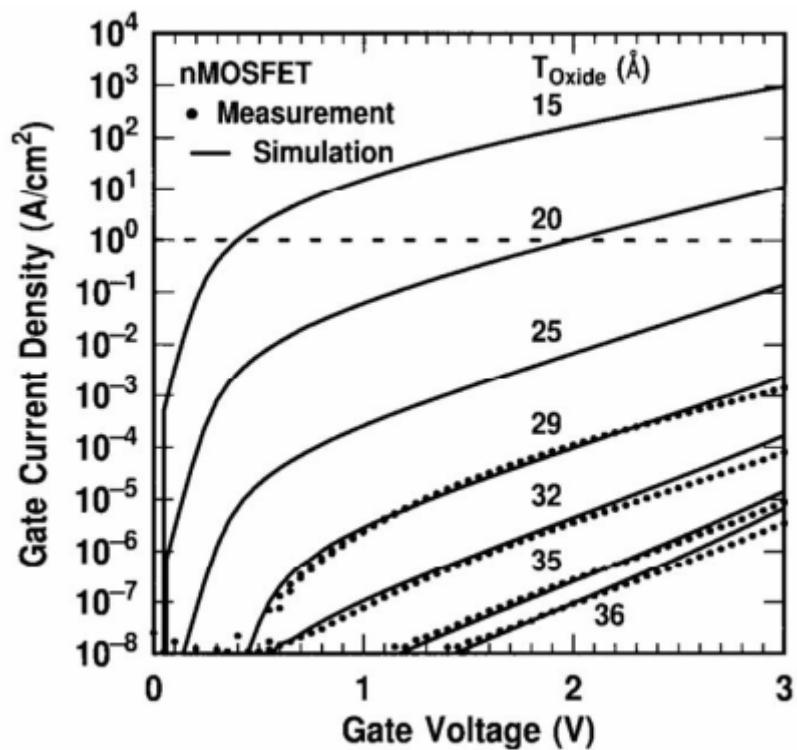

Fig. 1.3 Measured and simulated  $I_g$ - $V_g$  characteristics under inversion conditions of  $\text{SiO}_2$  N-MOSFET devices

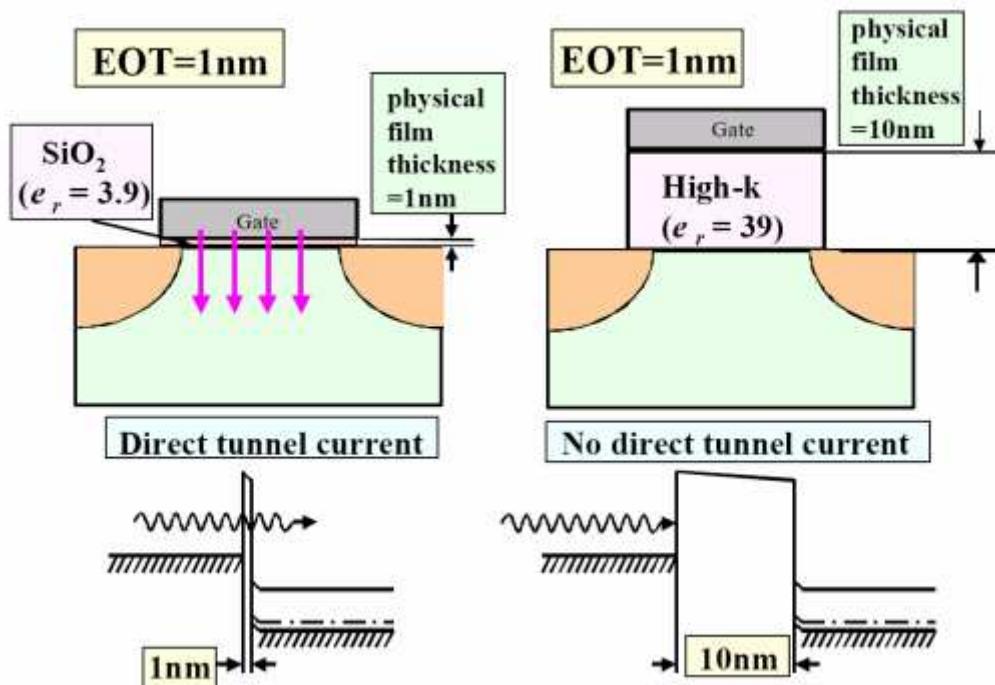

Fig. 1.4 By using high-k material to suppress gate direct-tunneling current.

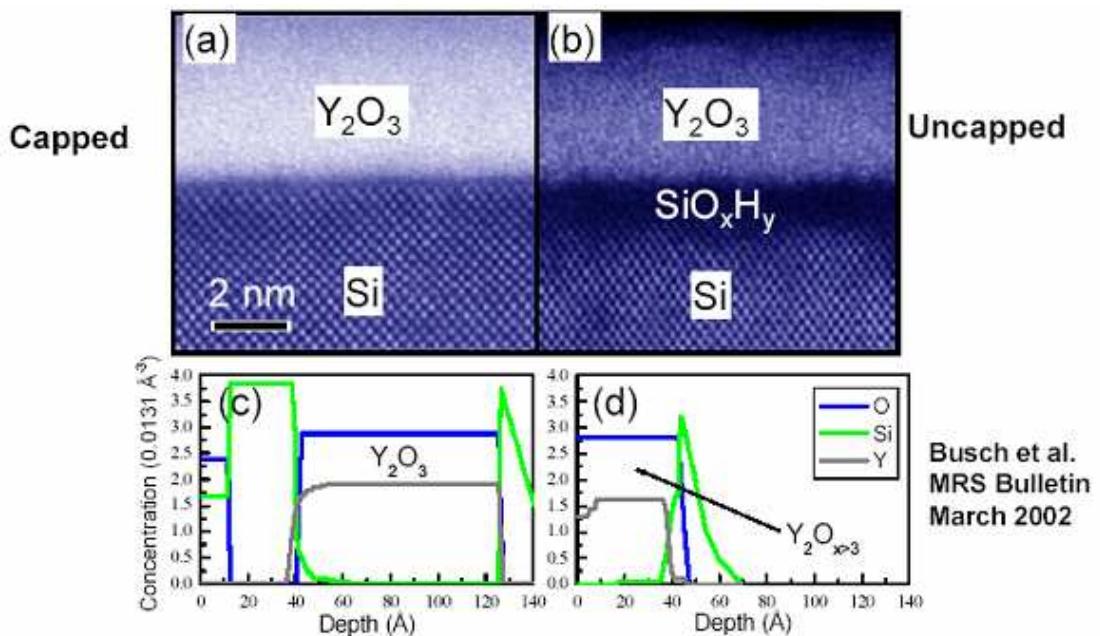

Fig. 1.5 TEM and SIMS analysis of  $\text{Y}_2\text{O}_3$  high-k dielectric with capped and uncapped samples. Uncapped  $\text{Y}_2\text{O}_3$  sample shows additional interfacial layer due to oxygen diffusion.

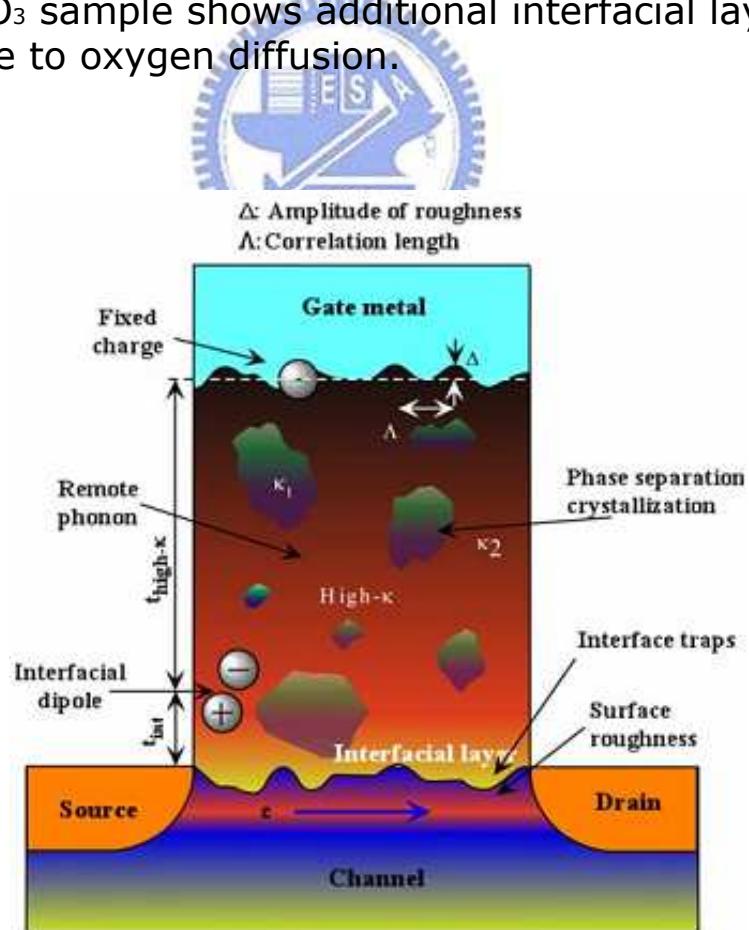

Fig. 1.6 Schematic representation of factors contributing to carrier mobility degradation in a high-k oxide layer.

## Chapter 02

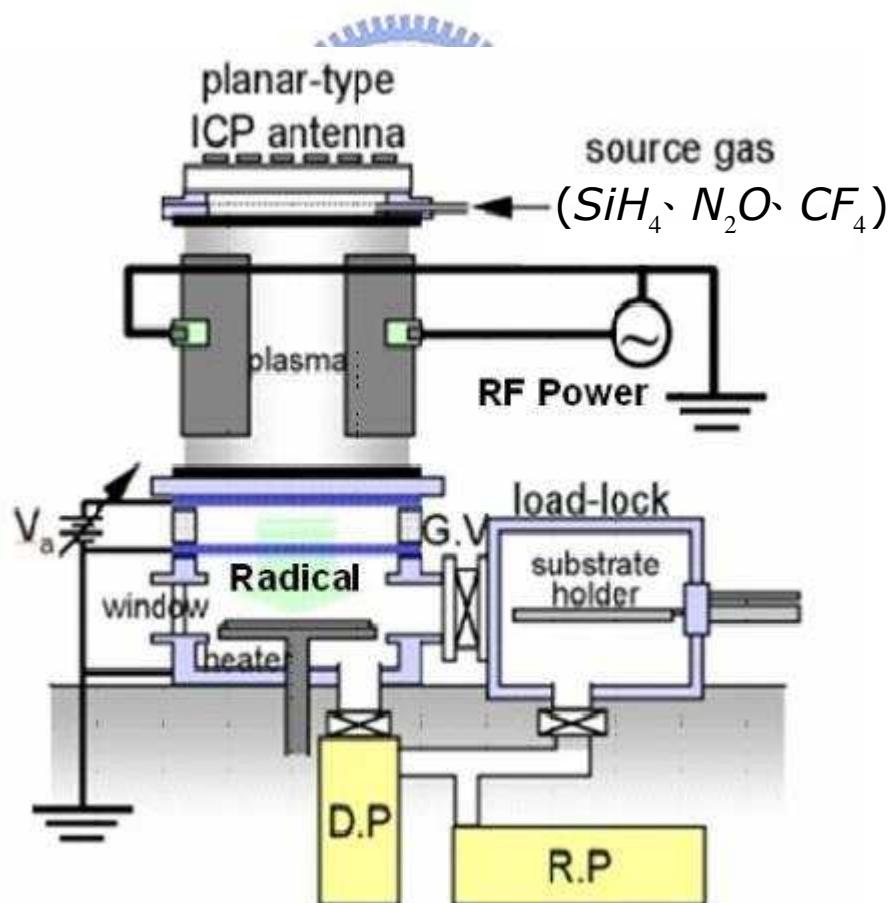

Fig. 2.1 The PECVD system used in this experiment.

Fig. 2.2 The process flow of n-MOSFETs with FSG passivation layer.

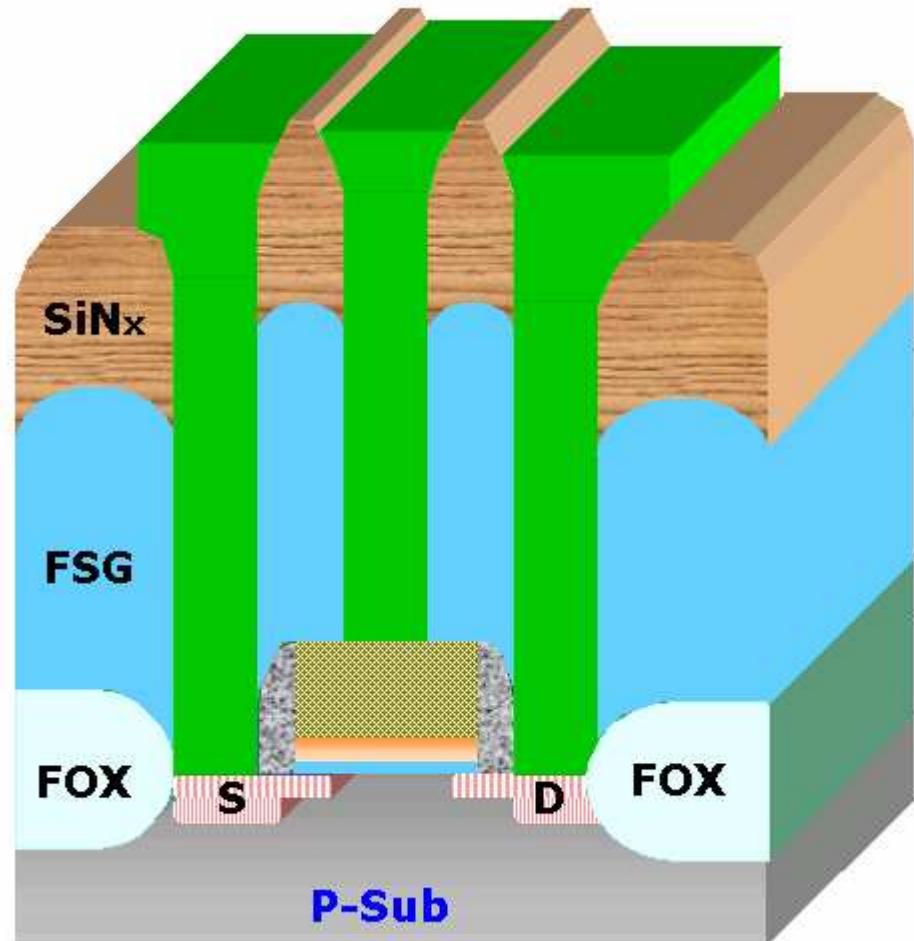

Fig. 2.3 Cross section of  $\text{HfO}_2/\text{SiON}$  n-MOSFET with FSG passivation layer.

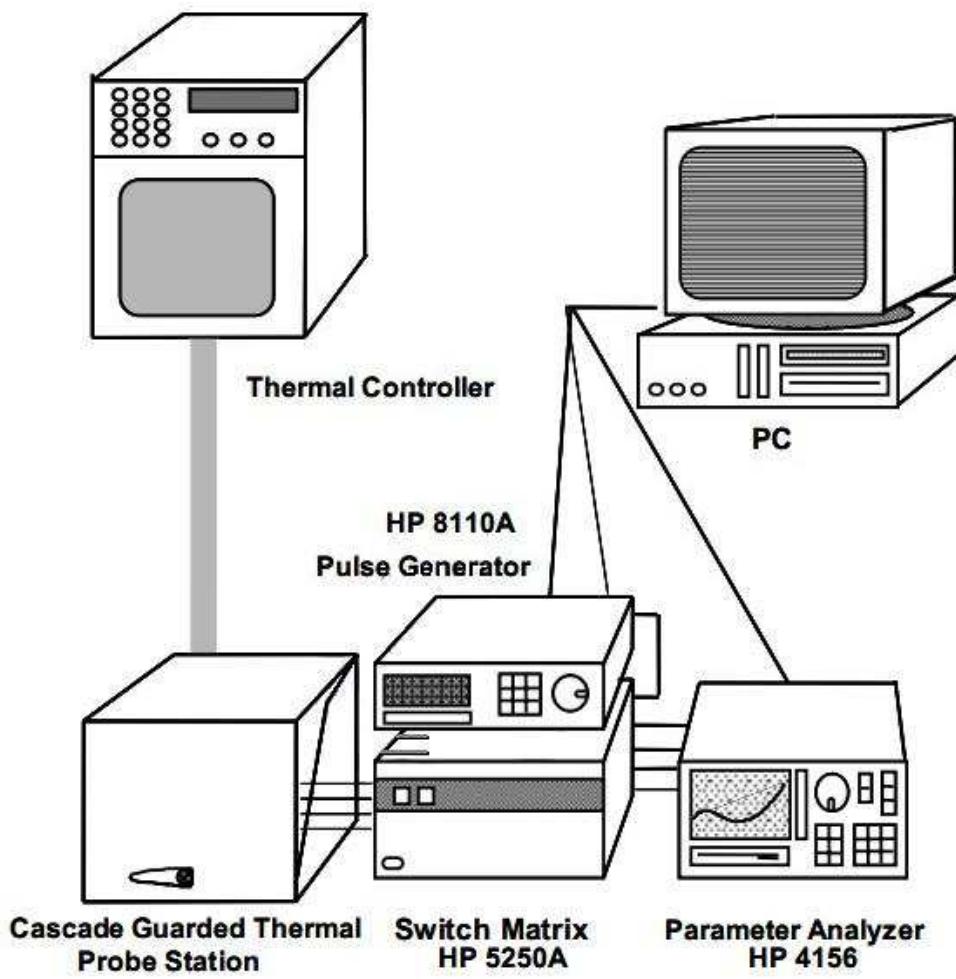

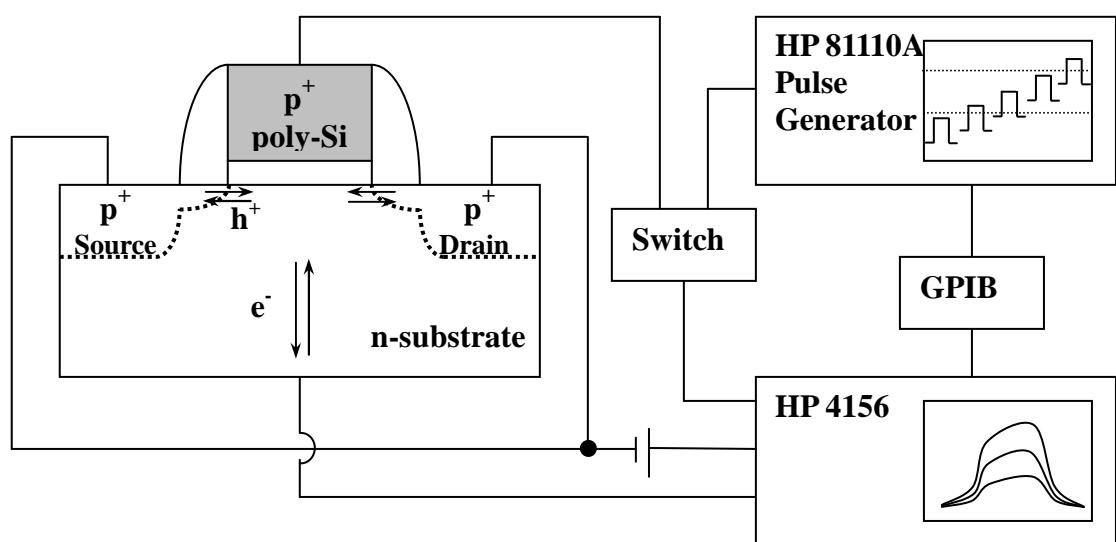

Fig. 2.4 The experimental setup for the basic electrical characteristics and long-term reliability test measurements.

Fig. 2.5 Basic experimental setup of charging pumping measurement.

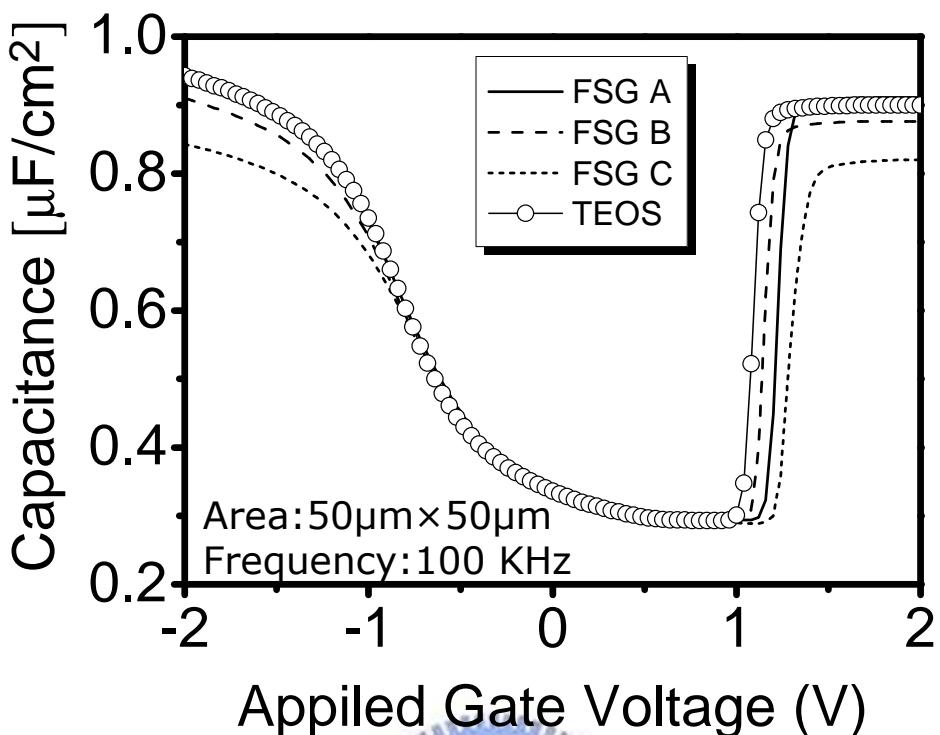

Fig. 2.6 The C-V characteristics of  $\text{HfO}_2$  gate dielectrics with various  $\text{CF}_4$  as precursor gas.

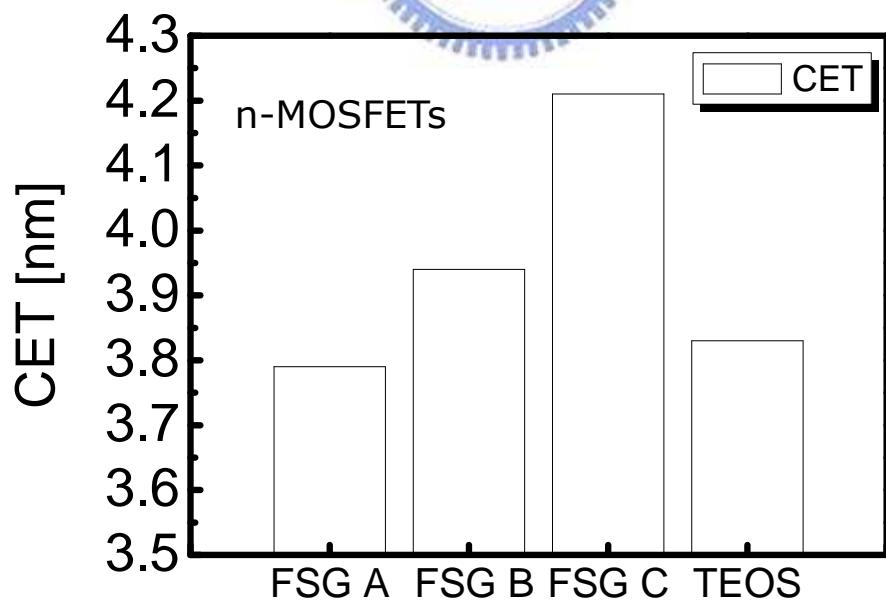

Fig. 2.7 Comparison of CET for all splits, including fluorinated and

as-deposited samples.

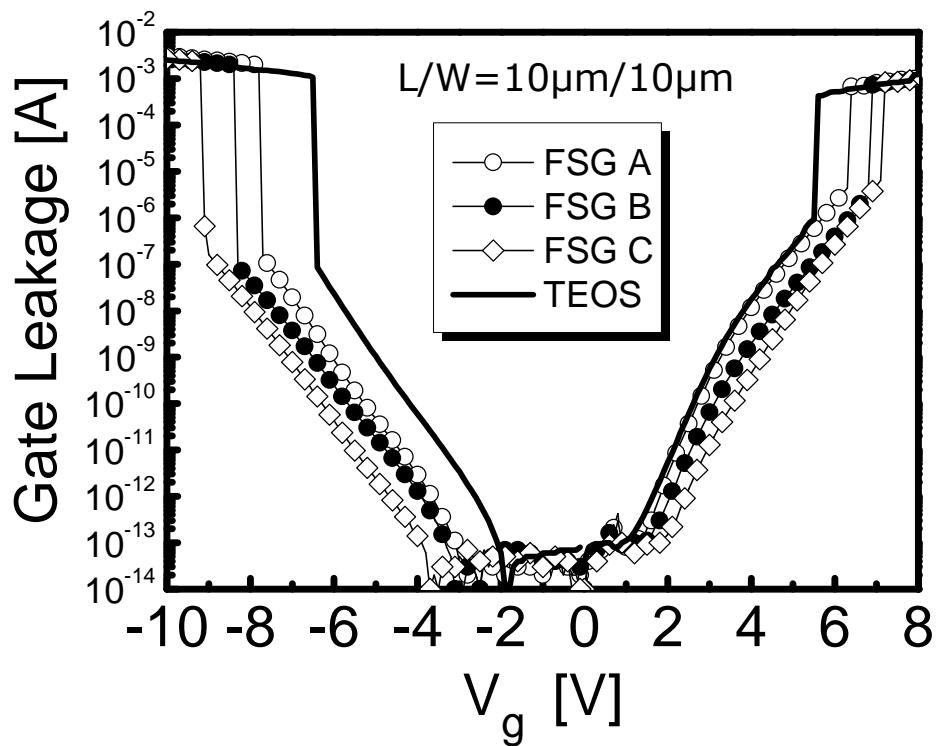

Fig. 2.8 Gate leakage current as a function of gate voltages of  $\text{HfO}_2/\text{SiON}$  gate stack with (symbol line) and without (solid line)  $\text{CF}_4$  gas incorporation both under inversion and accumulation regions

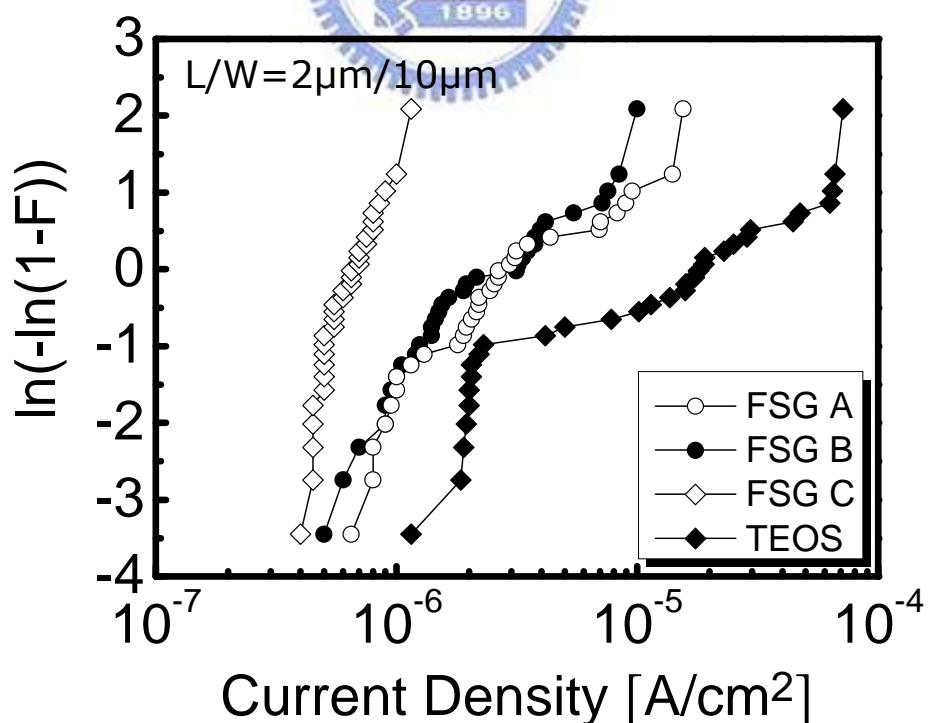

Fig. 2.9 The Weibull plot distributions at  $V_{\text{GS}}-V_{\text{Th}} = 1.0\text{V}$  of  $J_g$  for all samples.

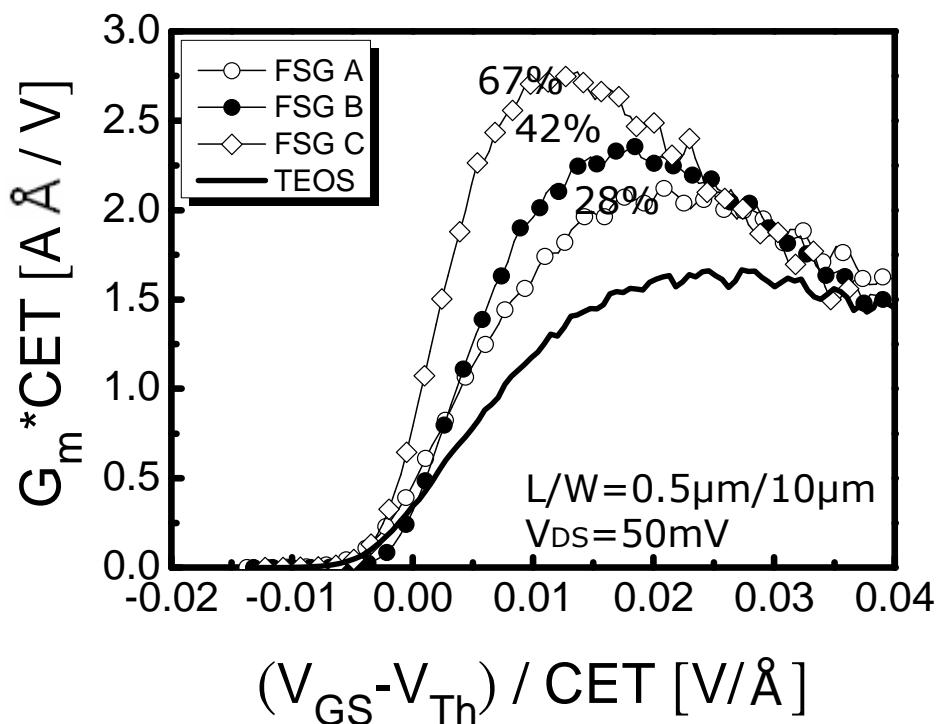

Fig. 2.10 Normalized transconductance as a function of gate voltage for TEOS and FSG passivation layer.

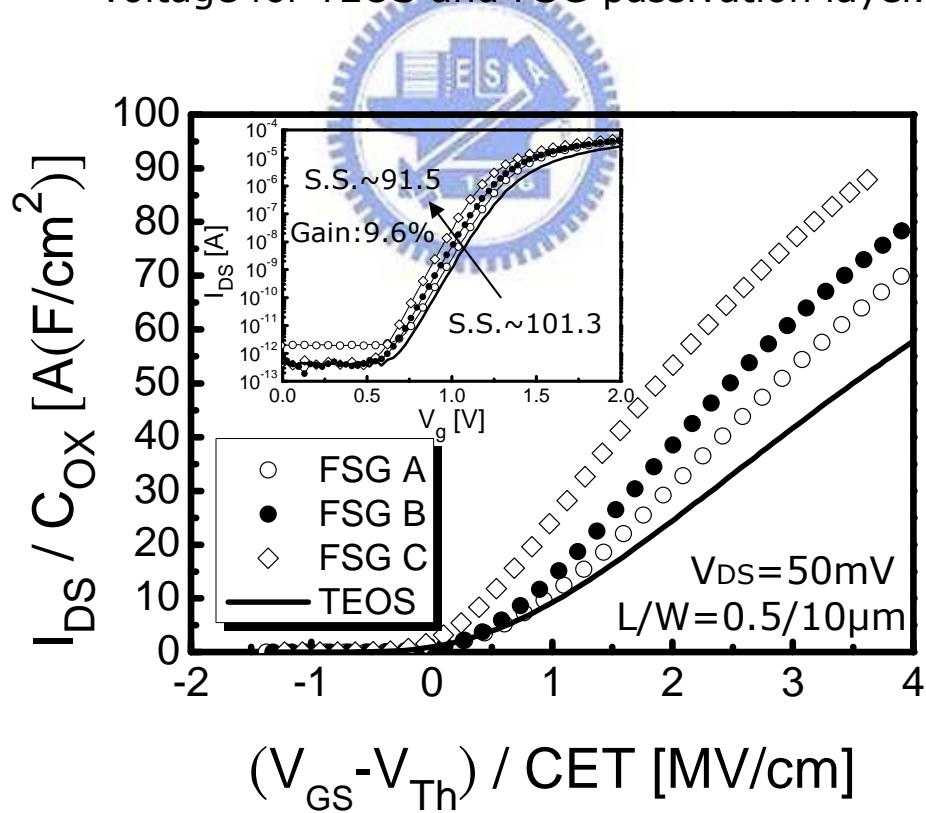

Fig. 2.11 Normalized NMOS  $I_{\text{DS}}$  of fluorinated device is 24% higher above than that for the control device, and the subthreshold properties is inset in the figure.

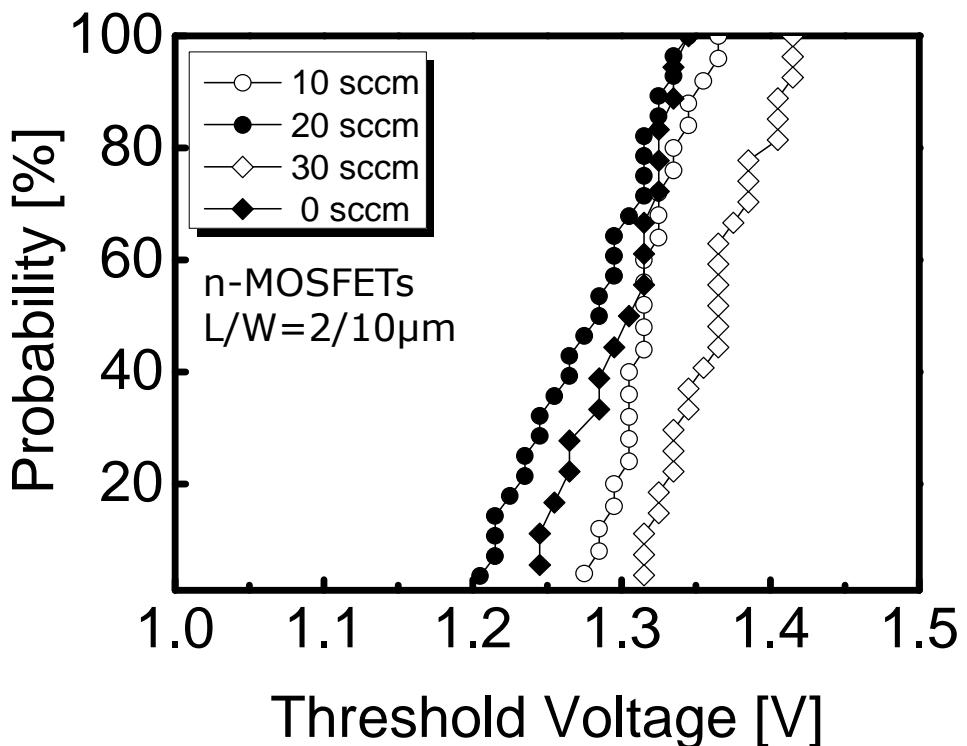

Fig. 2.12 Cumulative probability of the threshold voltage ( $V_{\text{Th}}$ ).

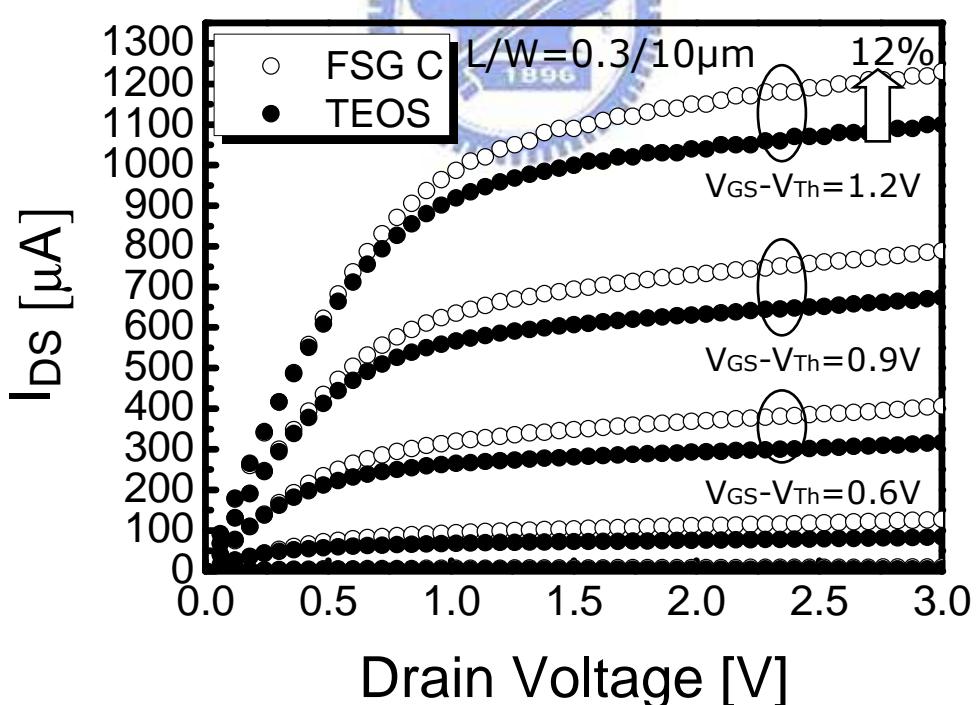

Fig. 2.13 Drain current versus drain voltage ( $I_D-V_D$ ) curves of FSG C and TEOS P.L. under various normalized gate biases which 0V, 0.3V, 0.6V, 0.9V, and 1.2V, respectively.

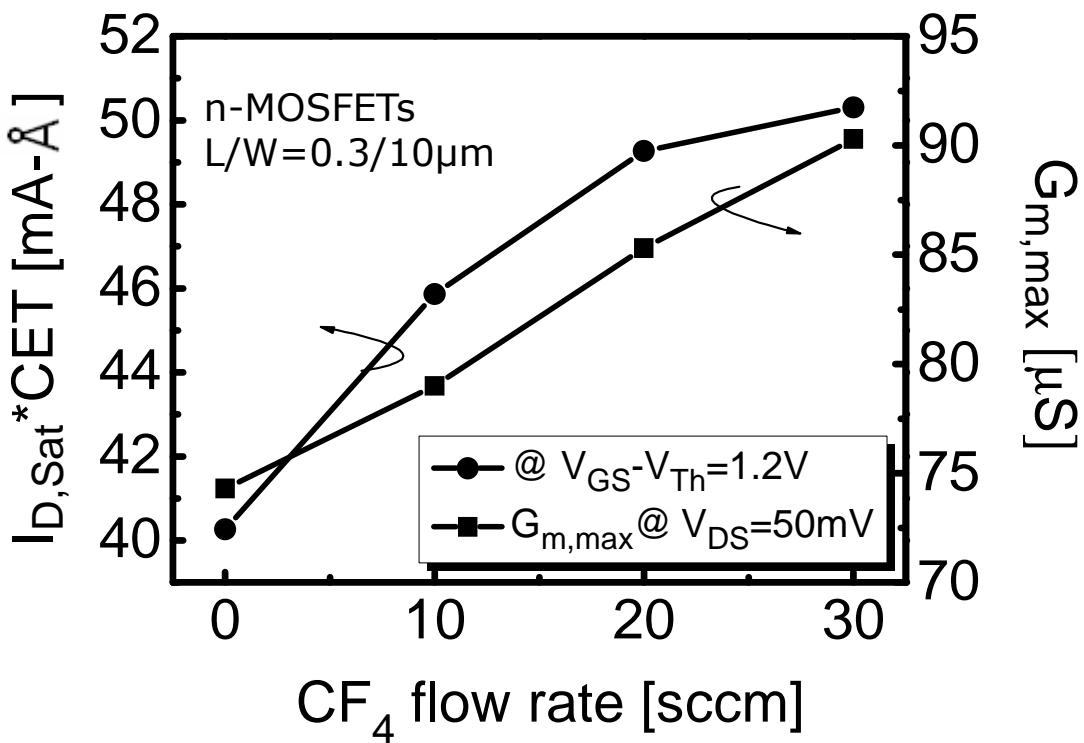

Fig. 2.14 Comparsion of normalized saturation drain current and  $G_{\text{m},\text{max}}$  for various flow of  $\text{CF}_4$  gas introduced.

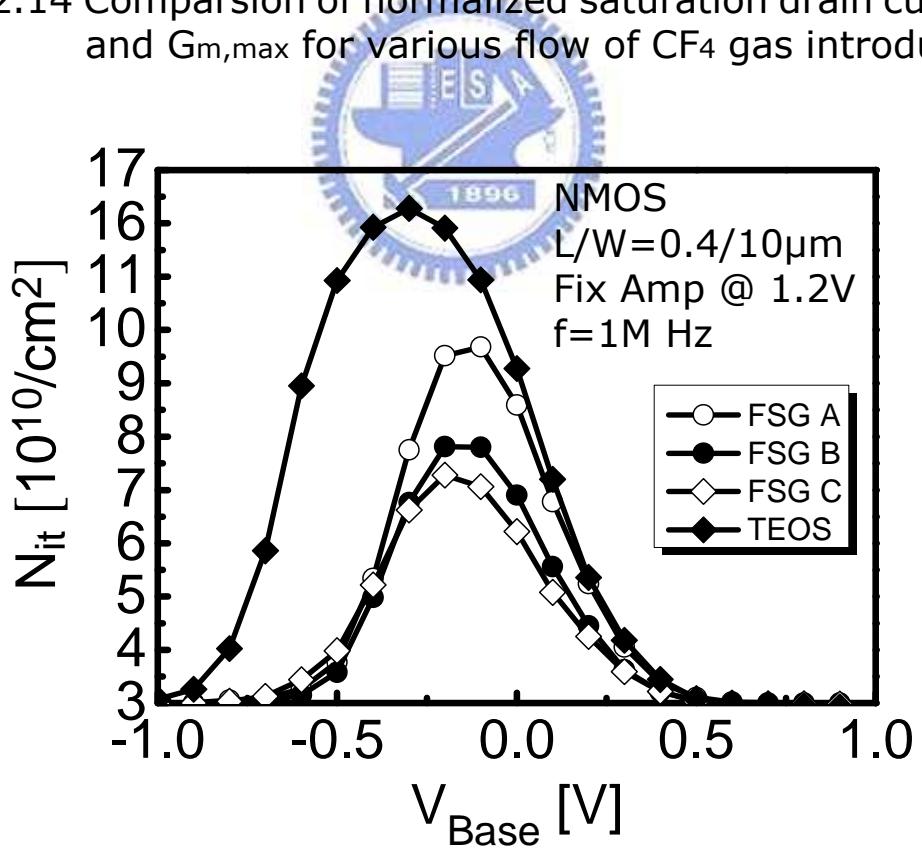

Fig. 2.15 Interface states density as a function of  $V_{\text{Base}}$  for  $\text{HfO}_2/\text{SiON}$  high-k gate stacks with FSG and TEOS P.L..

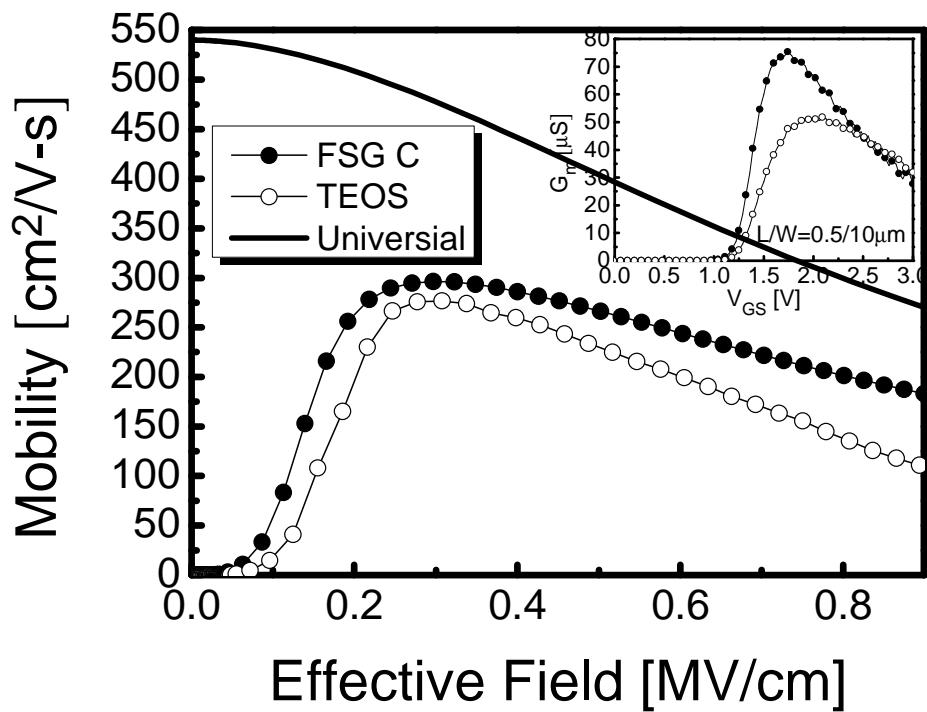

Fig. 2.16 Electron mobility for fluorinated device is enhanced as compared with the control device. Inset comparison of transconductance max peak ( $G_{\text{m},\text{max}}$ ).

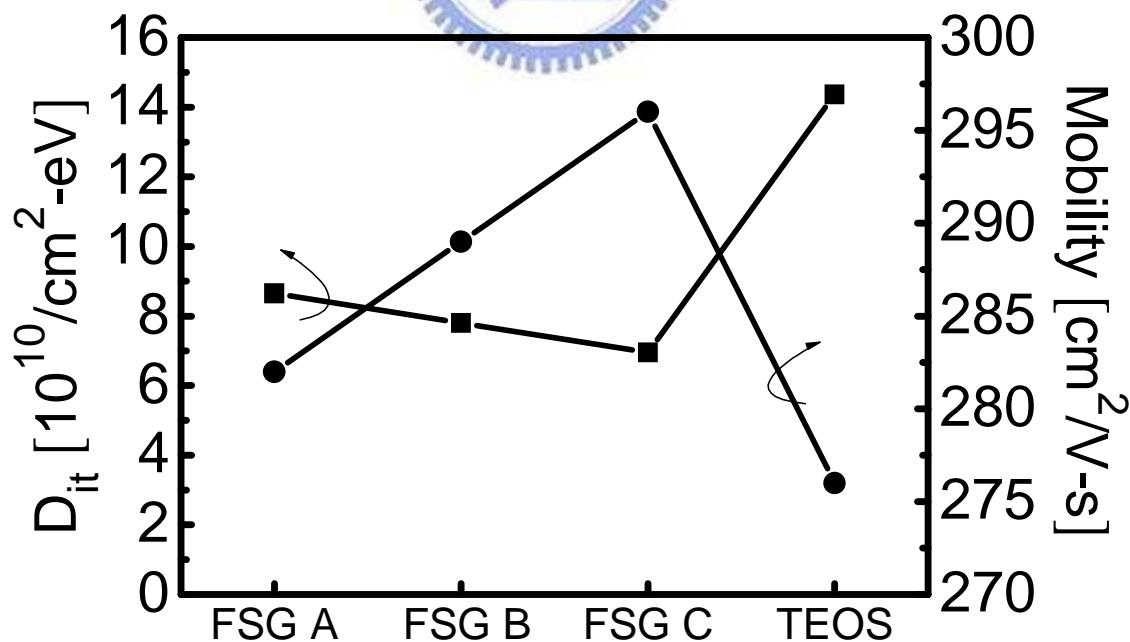

Fig. 2.17 Comparsion of interface states density correlated with electron mobility for all splits.

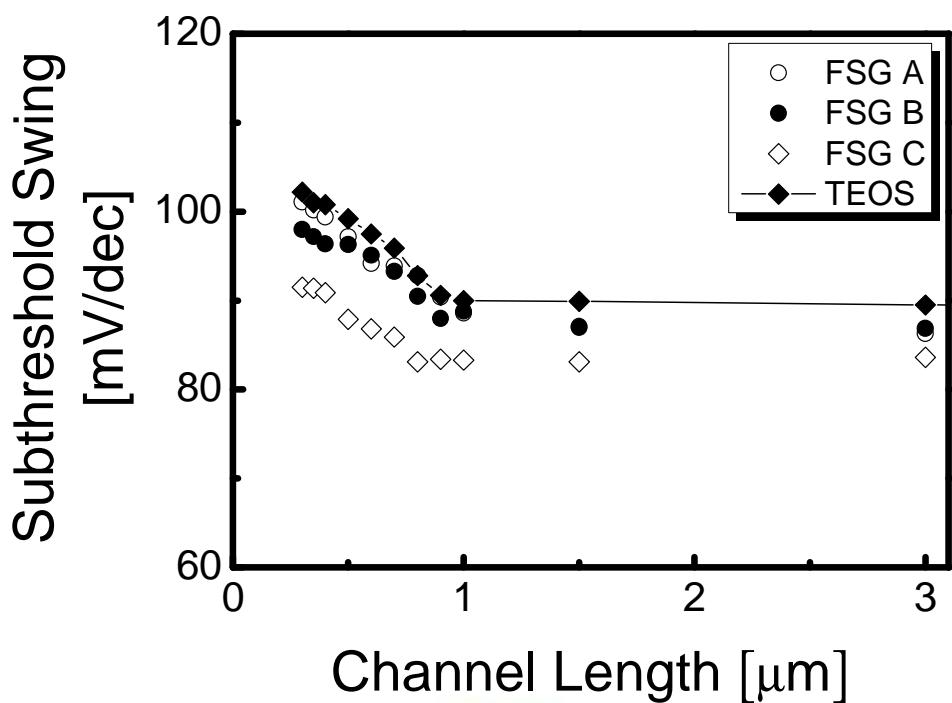

Fig. 2.18 The subthreshold swing versus channel length for all splits of  $\text{HfO}_2/\text{SiON}$  gate stack n-MOSFETs.

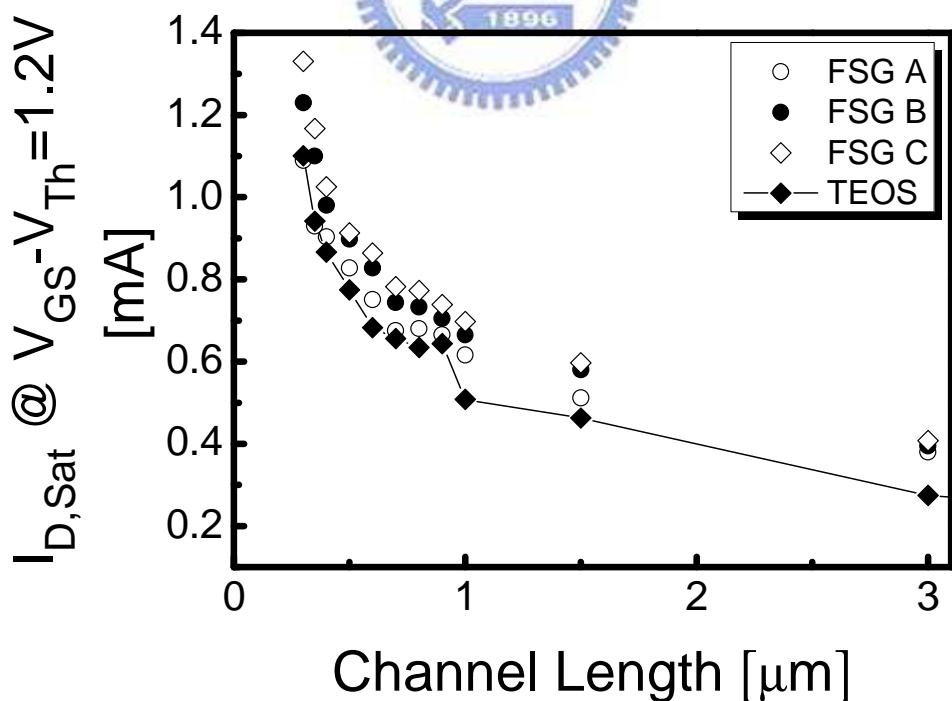

Fig. 2.19 The drain current versus channel length for all splits of  $\text{HfO}_2/\text{SiON}$

gate stack n-MOSFETs.

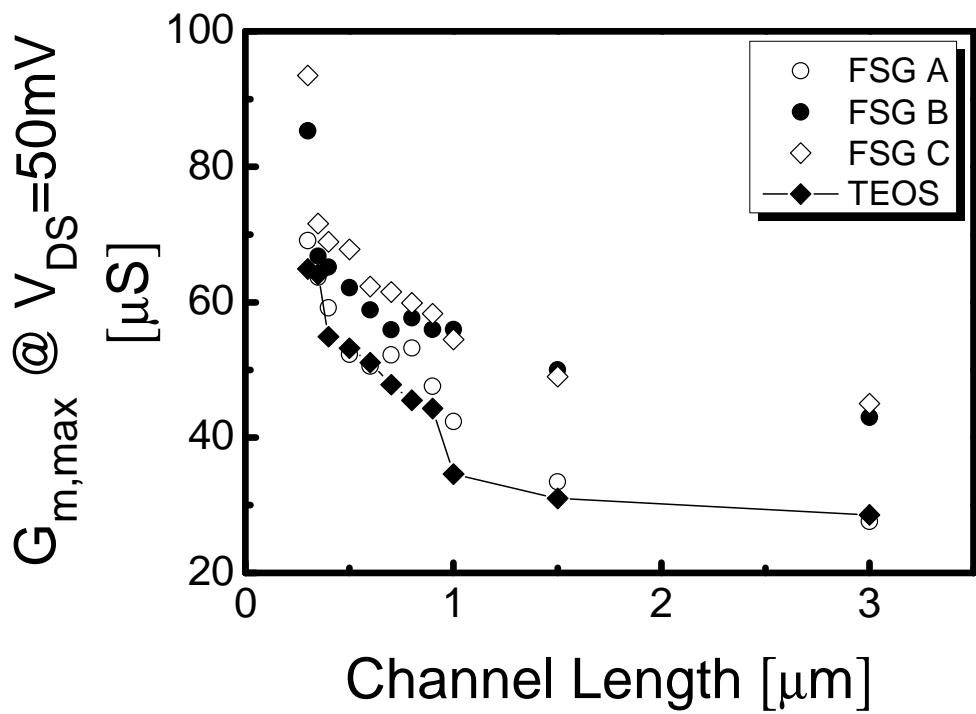

Fig. 2.20 The maximum transconductance versus channel length for all splits of HfO<sub>2</sub>/SiON gate stack n-MOSFETs.

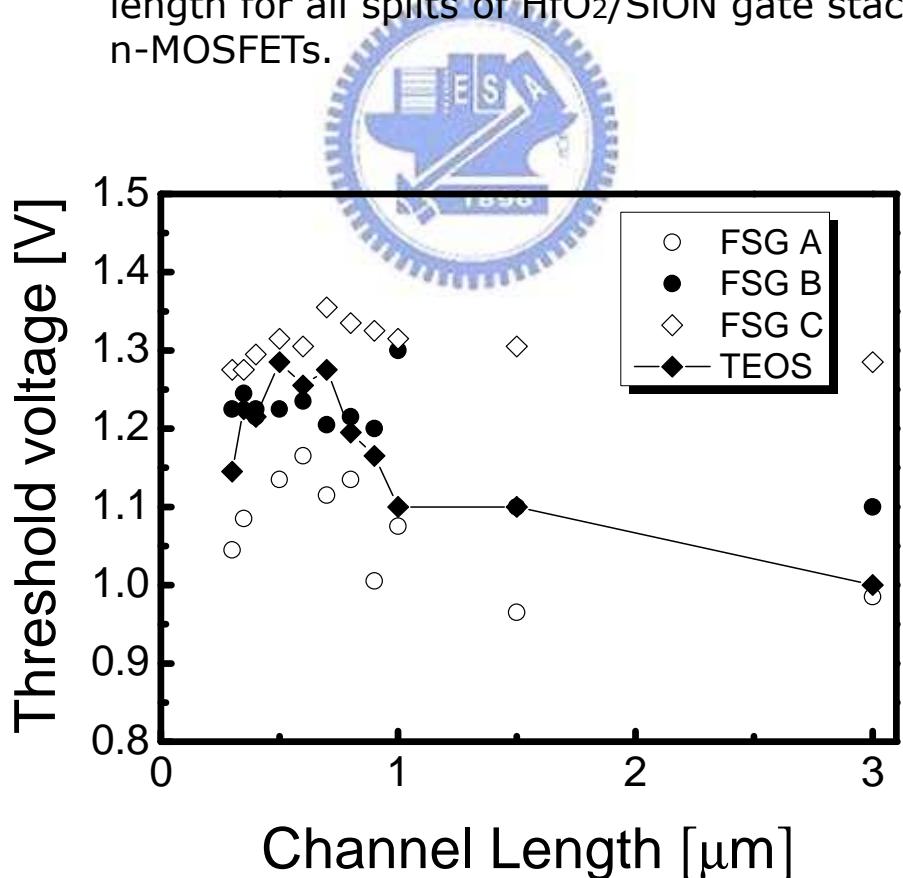

Fig. 2.21 Threshold voltage roll off characteristics for all splits of HfO<sub>2</sub>/SiON gate stack n-MOSFETs.

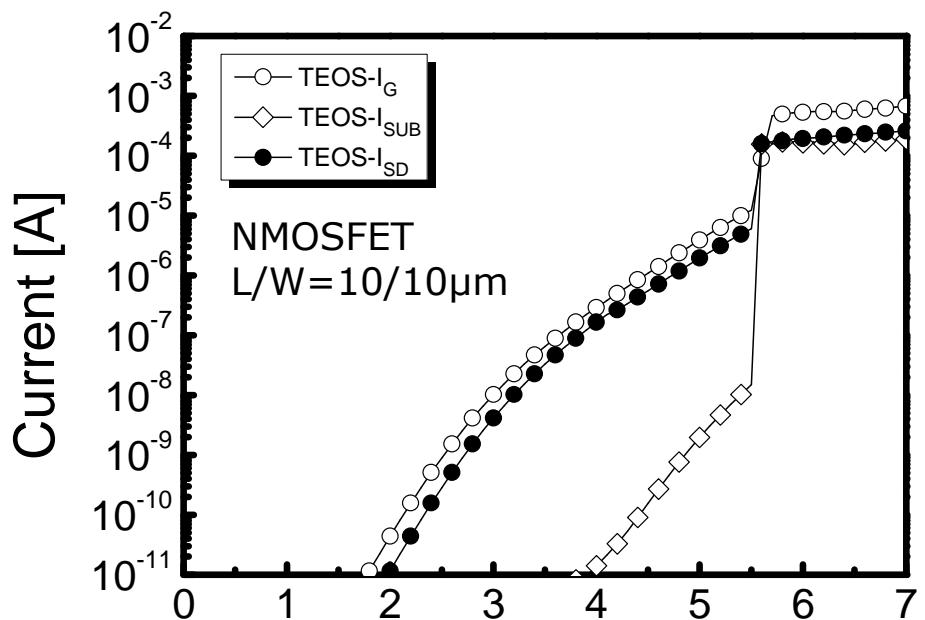

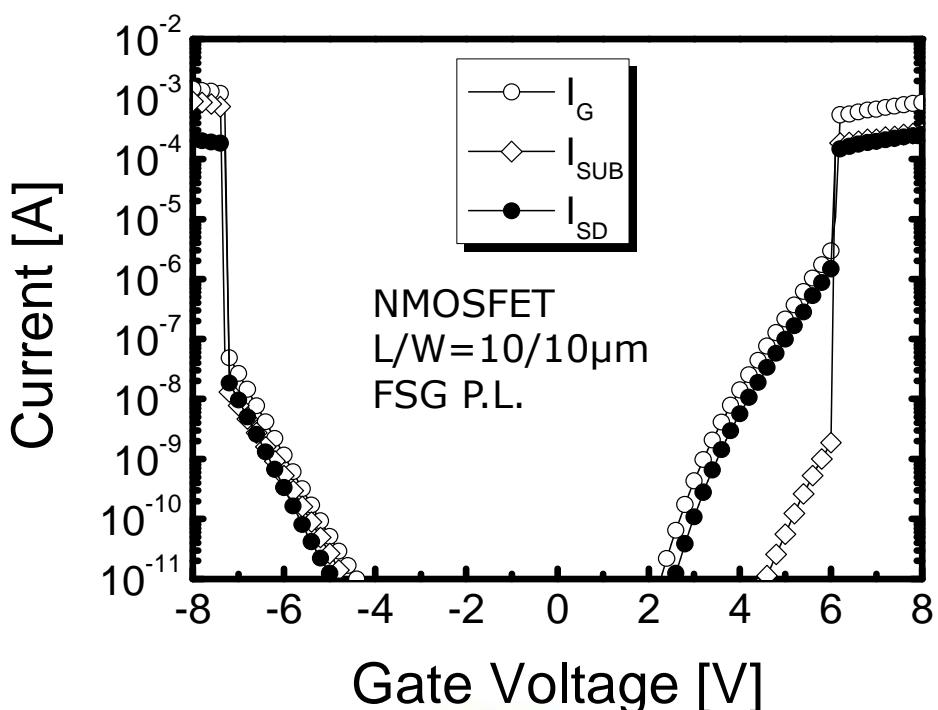

Fig. 2.22 Carrier separation under (a) inversion region and (b) accumulation region in the TEOS sample.

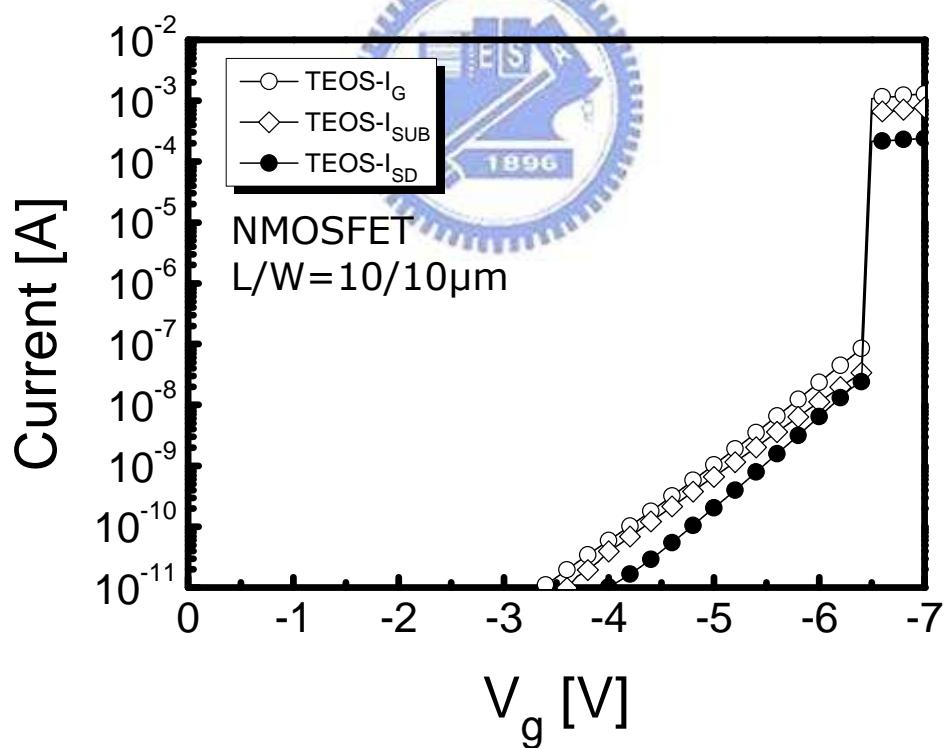

Fig. 2.23 Carrier separation of (a) FSG and (b) TEOS samples under both inversion and accumulation regions.

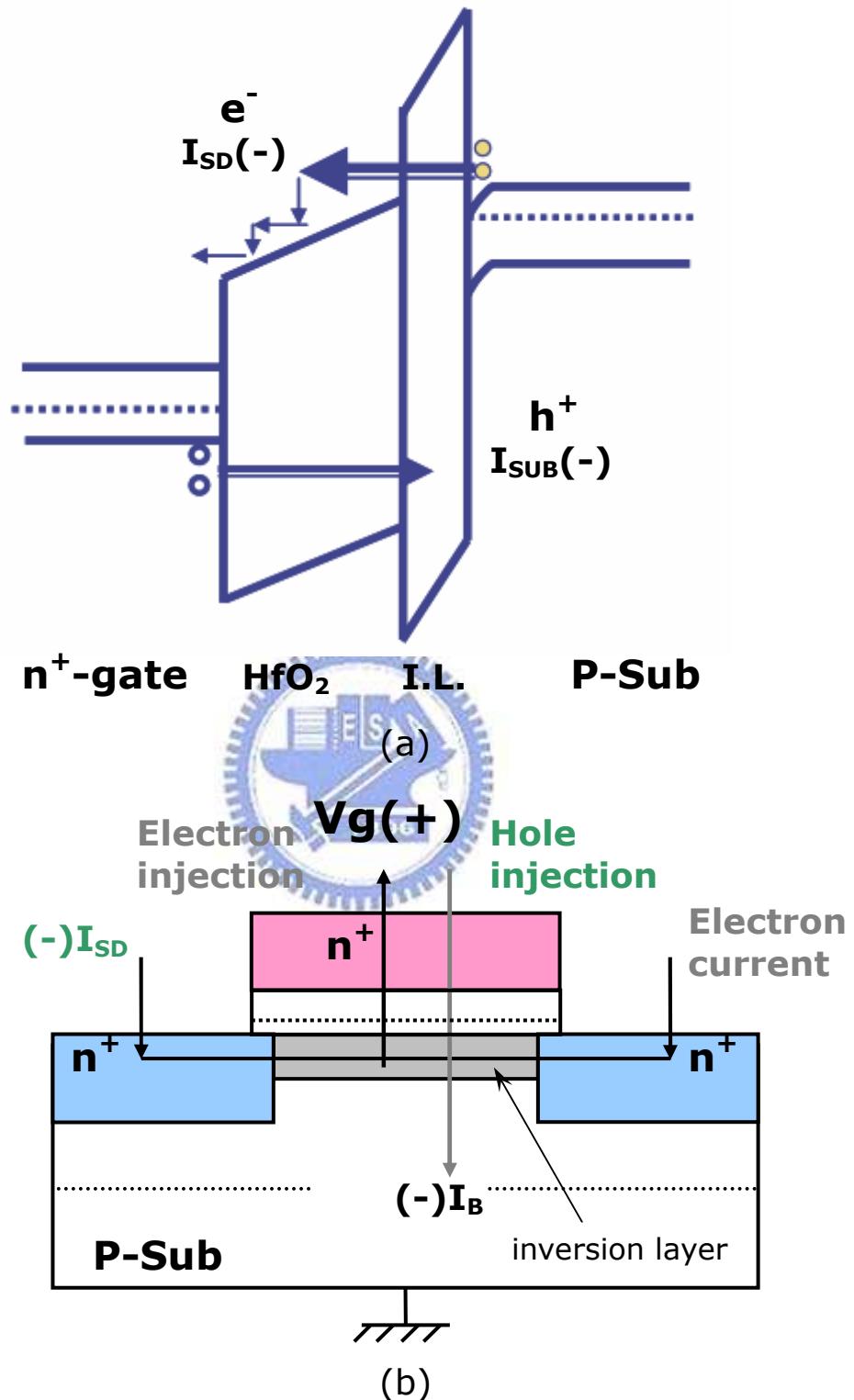

Fig. 2.24 Poly-gate n-MOSFET with HfO<sub>2</sub>/SiON gate stack under inversion region (a) band diagrams, and (b) schematic illustration of carrier separation experiment.

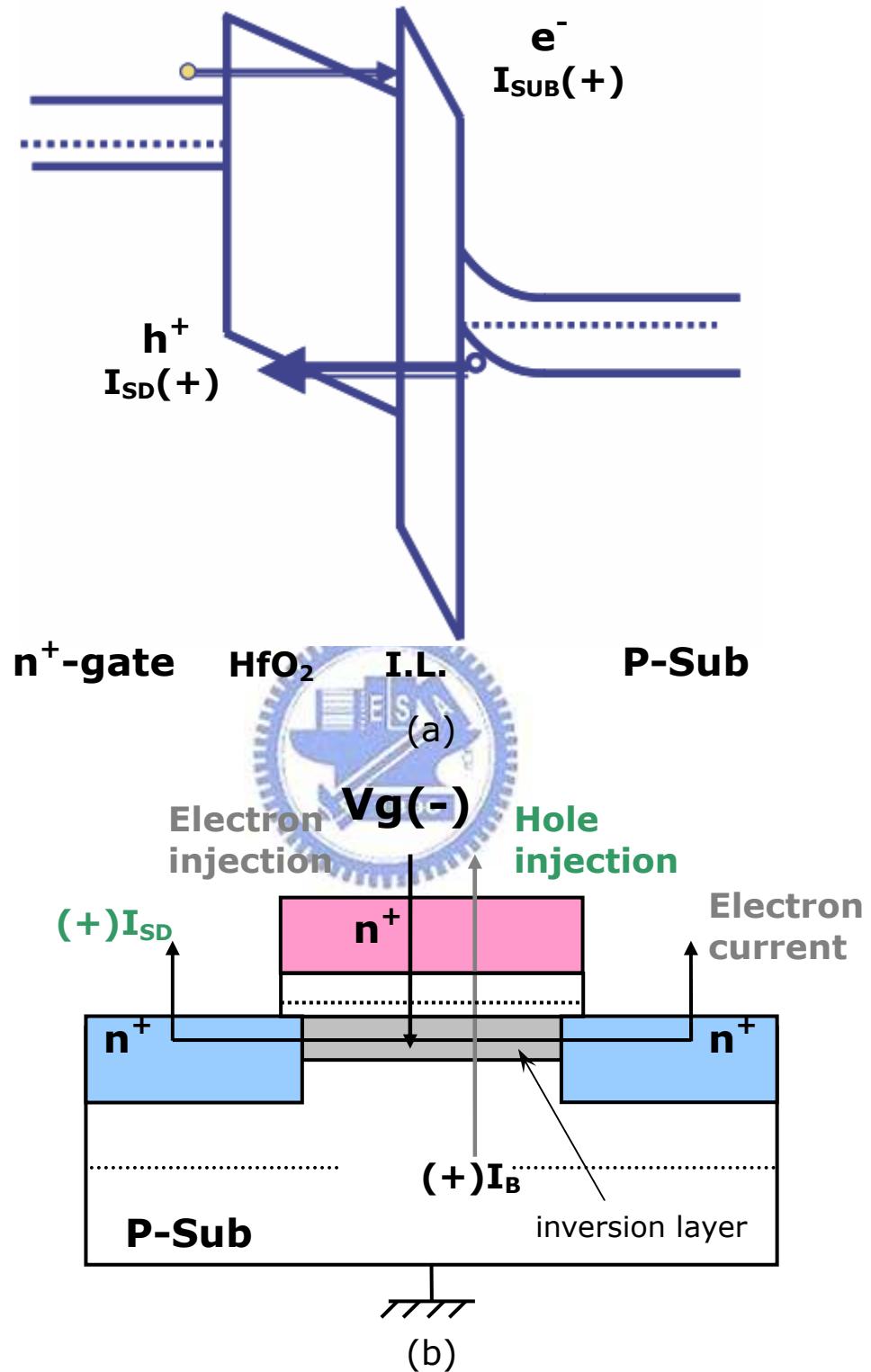

Fig. 2.25 Poly-gate n-MOSFET with HfO<sub>2</sub>/SiON gate stack under accumulation region (a) band diagrams, and (b) schematic illustration of carrier separation experiment.

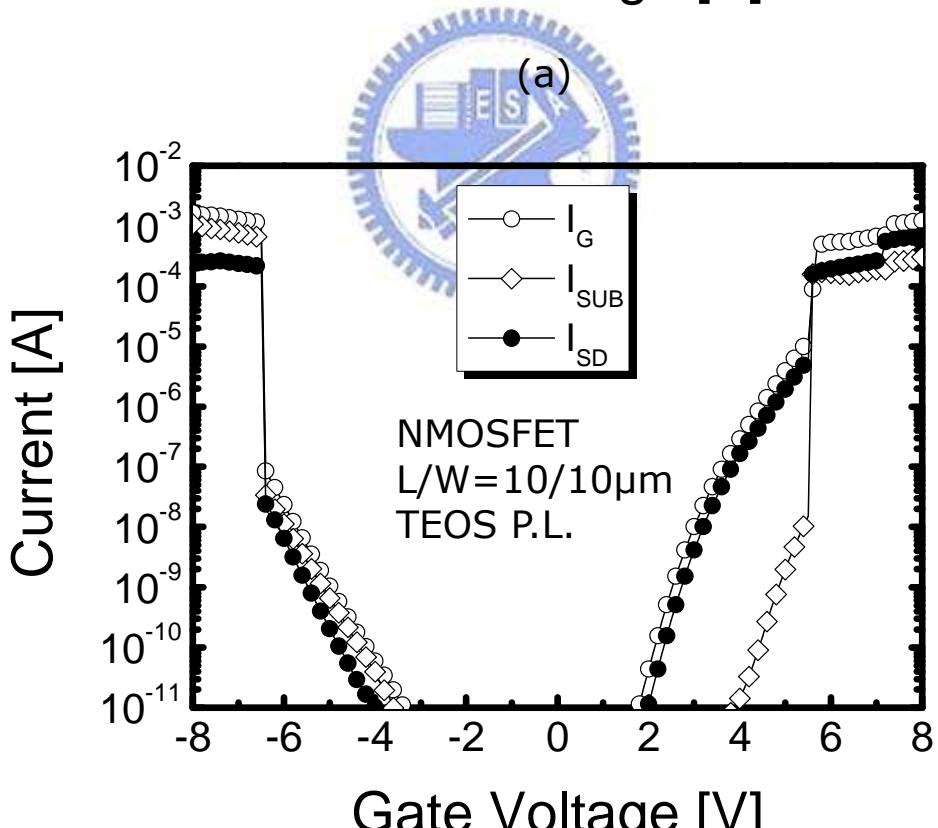

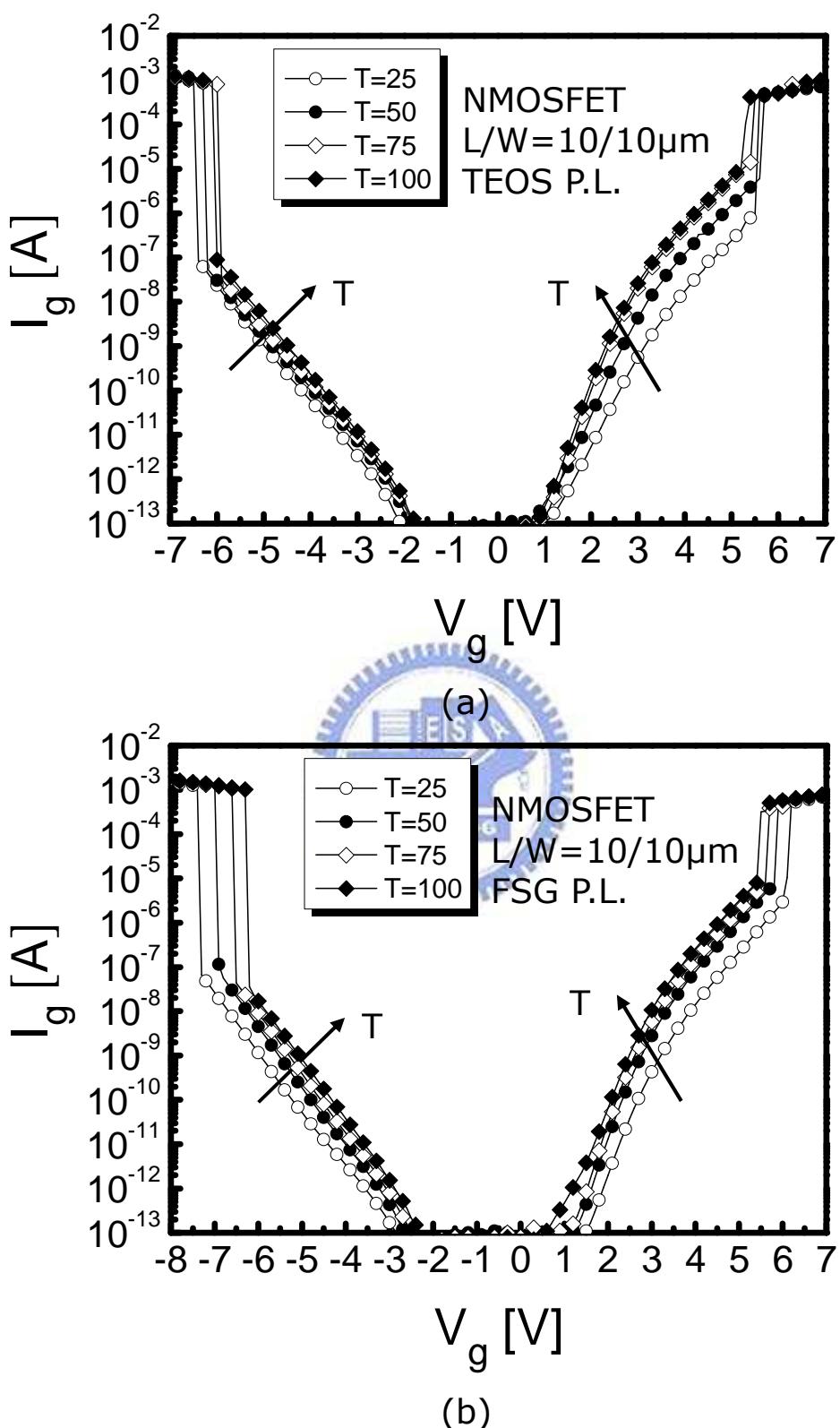

Fig. 2.26 Gate leakage current versus gate bias for fresh n-channel devices at various temperatures (a) TEOS P.L. (b) FSG P.L..

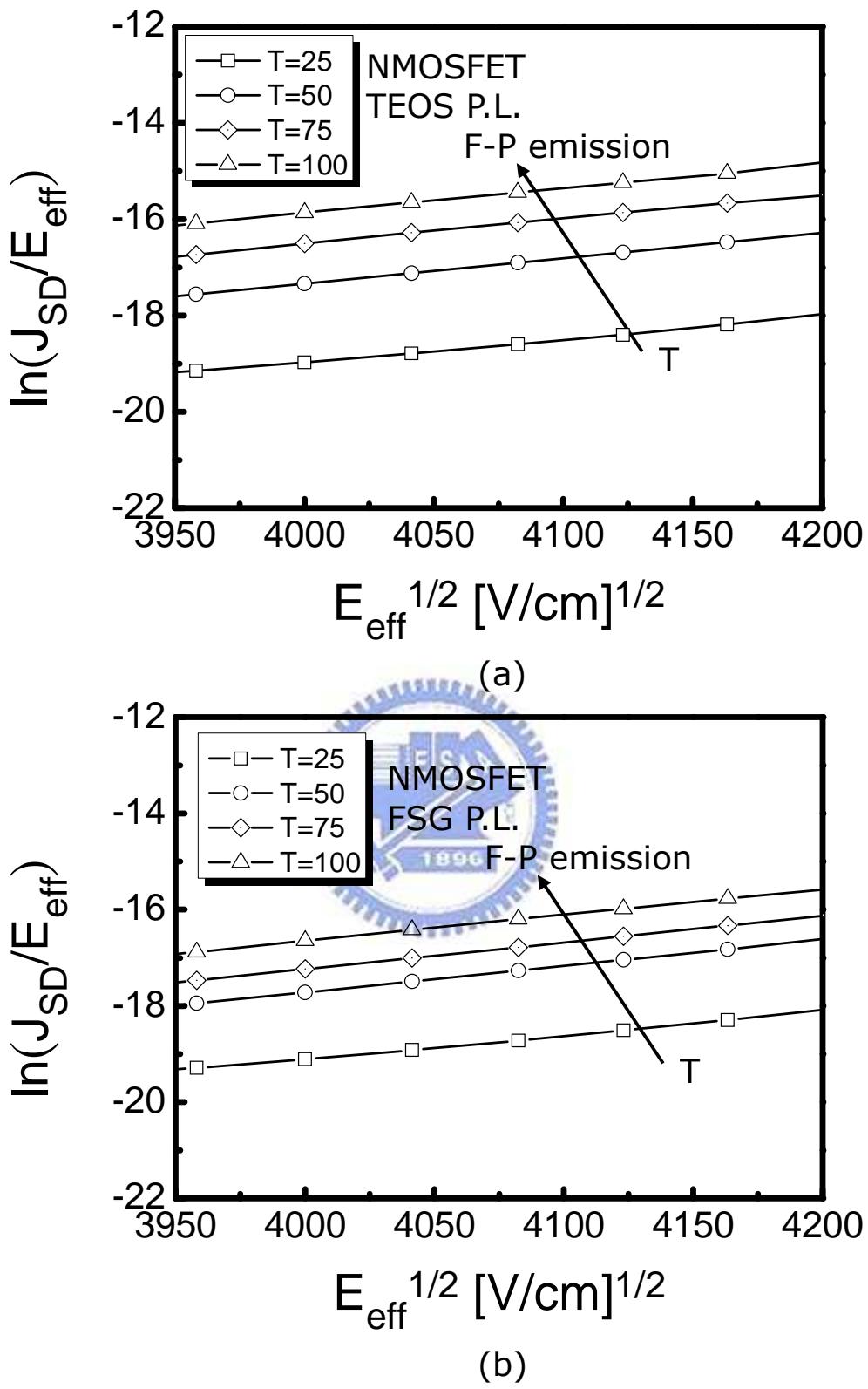

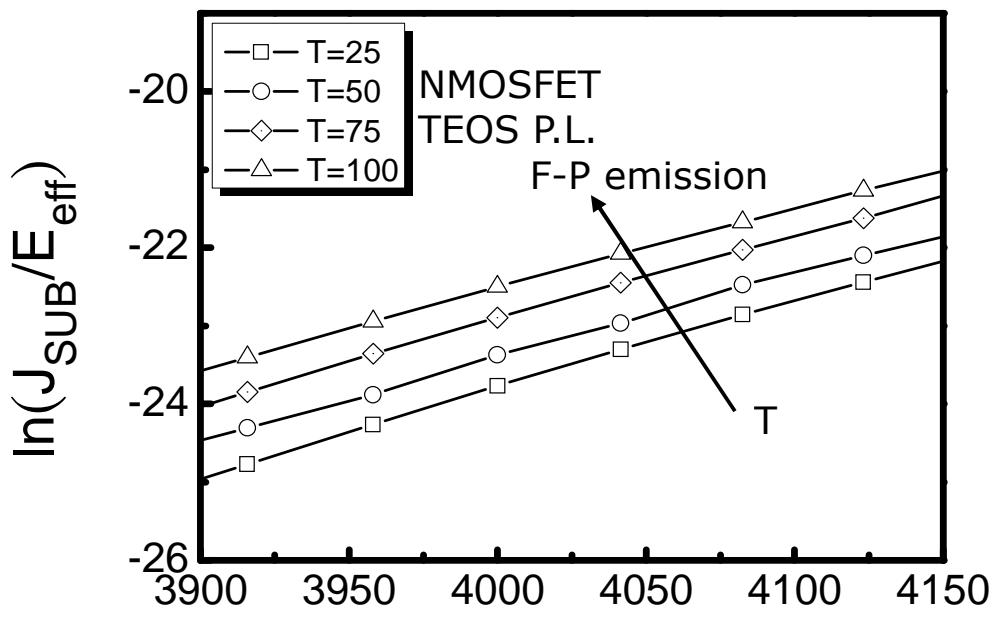

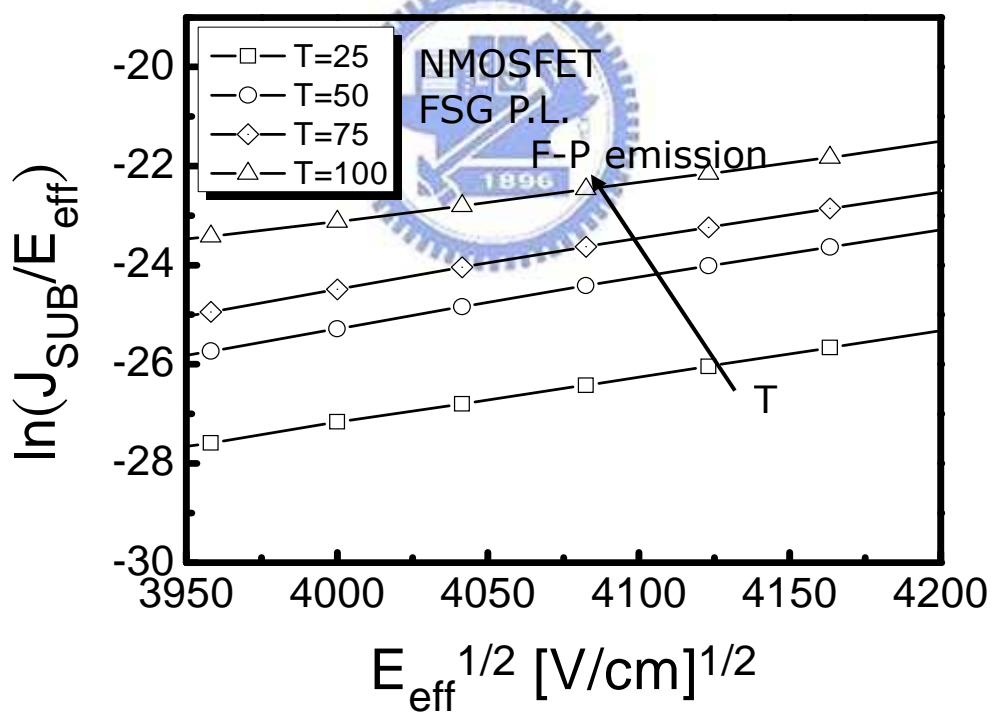

Fig. 2.27 Conduction mechanism for source/drain current fitting under inversion region (a) TEOS (b) FSG P.L..

Fig. 2.28 Conduction mechanism for substrate current fitting under inversion region (a) TEOS (b) FSG P.L..

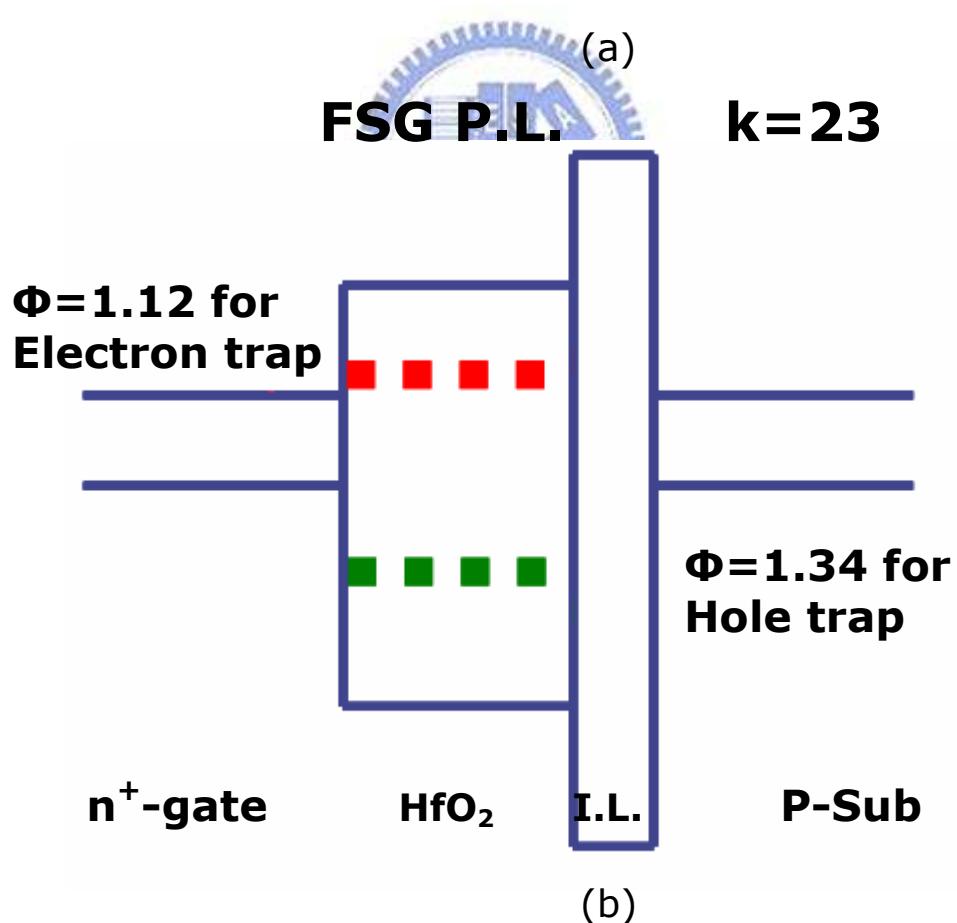

Fig. 2.29 Band diagrams for (a) TEOS and (b) FSG P.L., illustrating the conduction mechanism of Frenkel-Poole emission.

Fig. 2.30 Schematic energy band diagram of the gate-drain overlap region.

Fig. 2.31 The band diagrams before (solid line) and after (dashed line) capturing electrons by bulk traps.

Fig. 2.32 Gate-induced leakage current characteristics of  $I_D$ - $V_{GS}$  transfer curves for all splits of NMOSFETs.

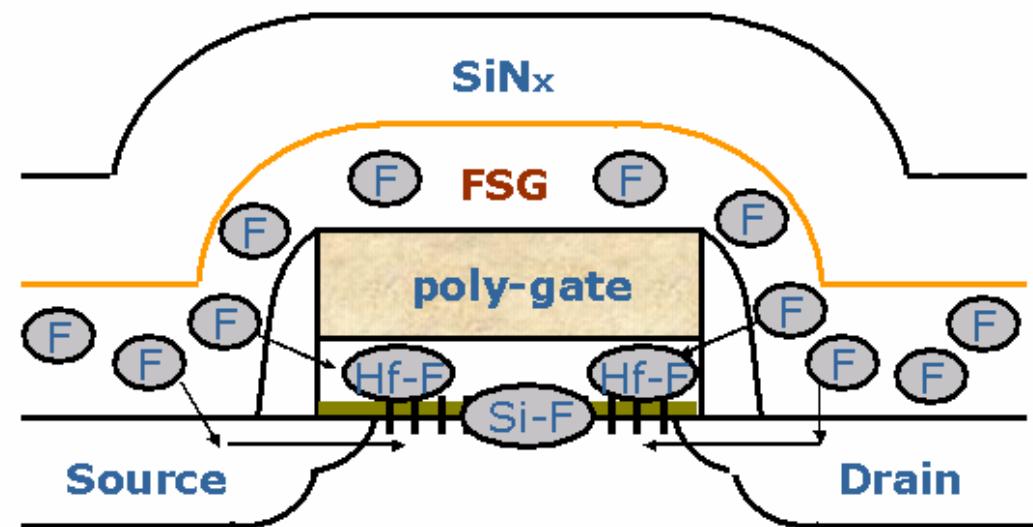

Fig. 2.33 In FSG P.L. devices, a large amount of F atoms incorporating to passivating the bulk and interface trap charges of  $HfO_2/SiON$  gate stack n-MOSFET.

## Chapter 03

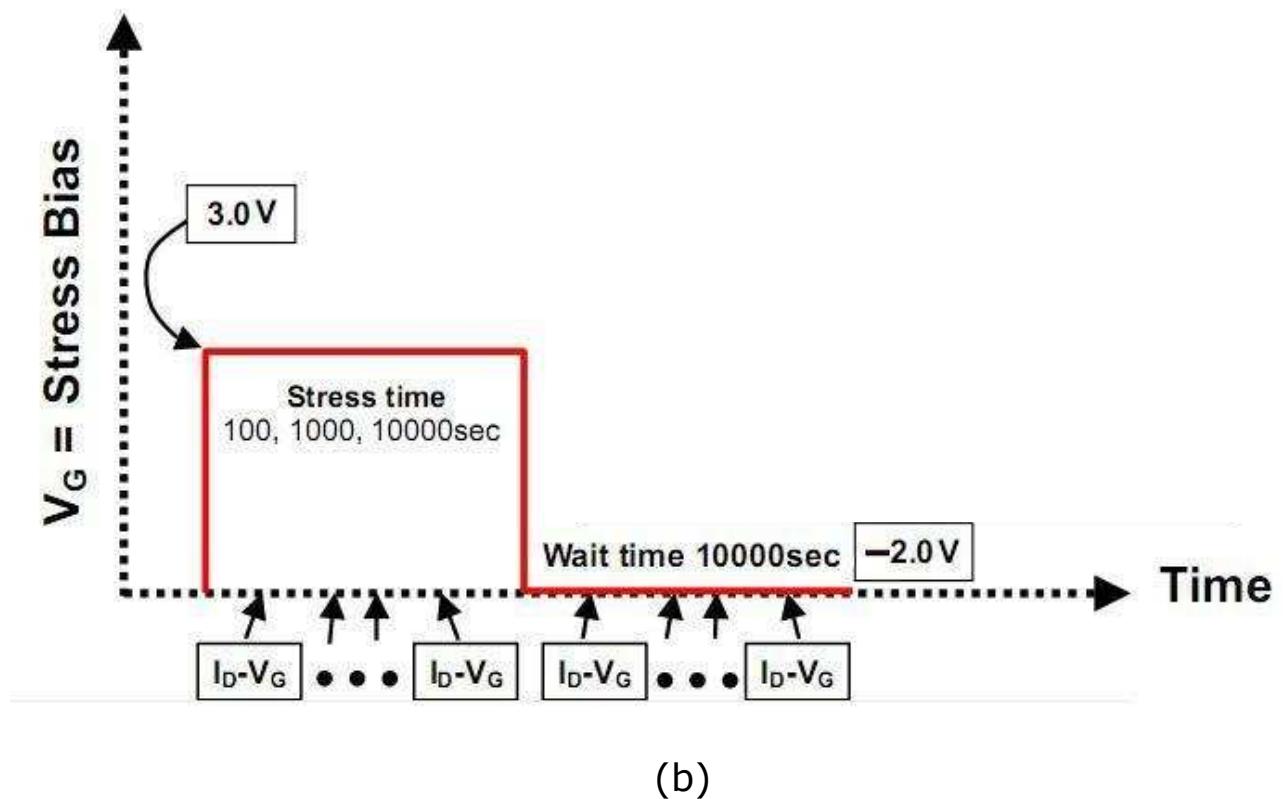

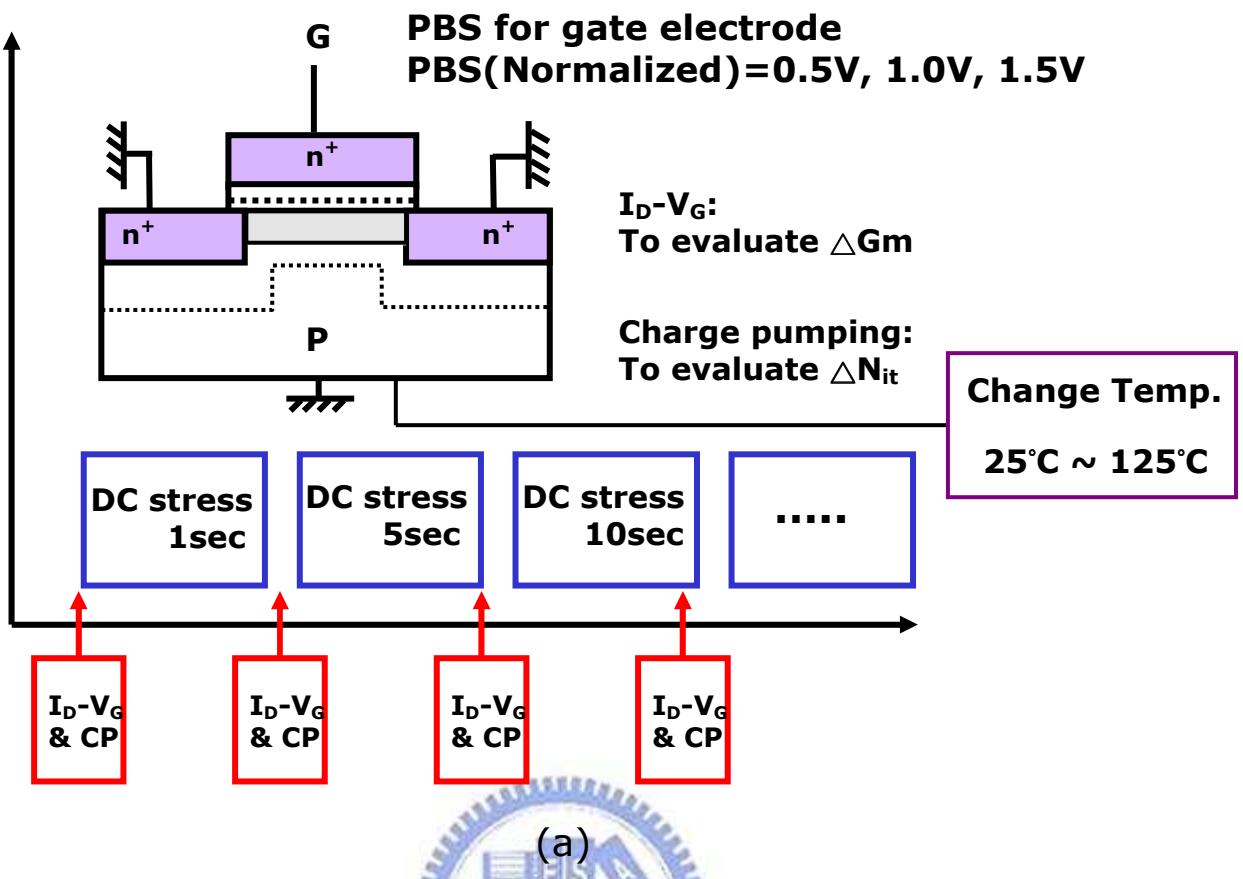

Fig. 3.1 Schematic of measurement setup for (a) static PBTS (b) dynamic trapping.

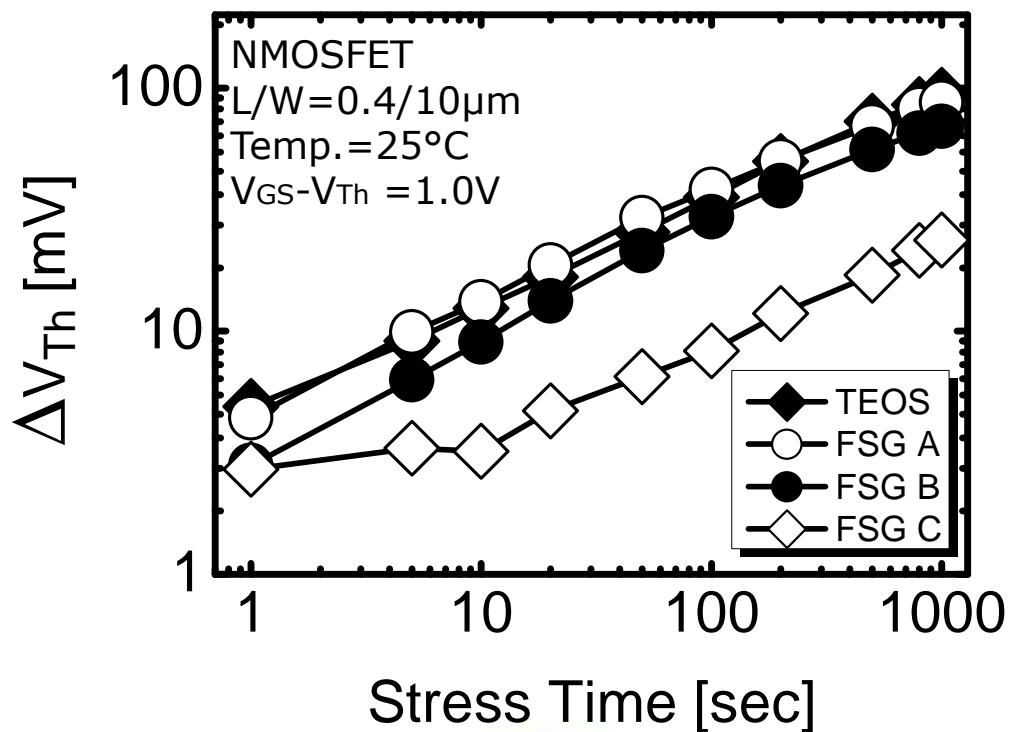

Fig. 3.2 PBT-stress-time dependence of  $\Delta V_{Th}$  for TEOS and FSG having different flow rate of  $CF_4$  gas at 25°C.

Fig. 3.3 PBT-stress-time dependence of  $\Delta V_{Th}$  for TEOS and FSG having different flow rate of  $CF_4$  gas at 25°C.

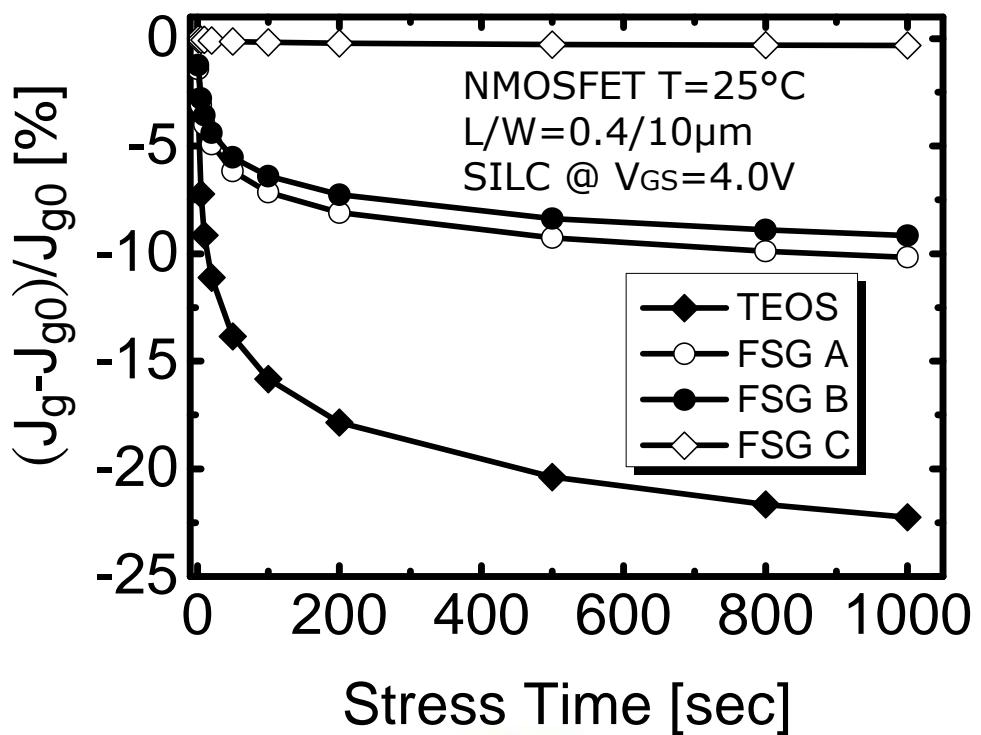

Fig. 3.4 The normalized gate current density  $((J_g - J_{g0})/J_{g0})$  at a constant gate voltage of 4.0V versus stress time of all splits.

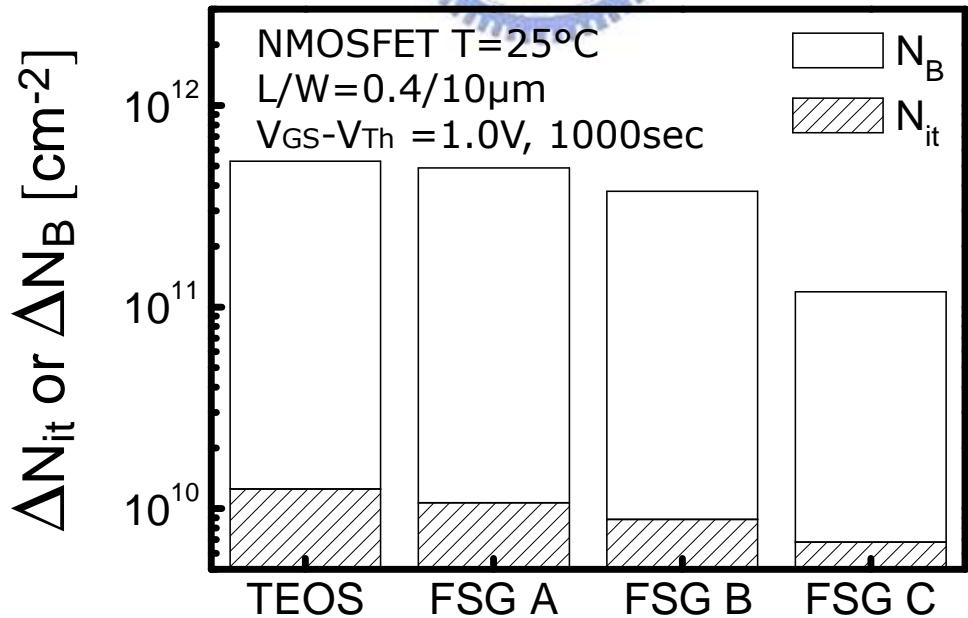

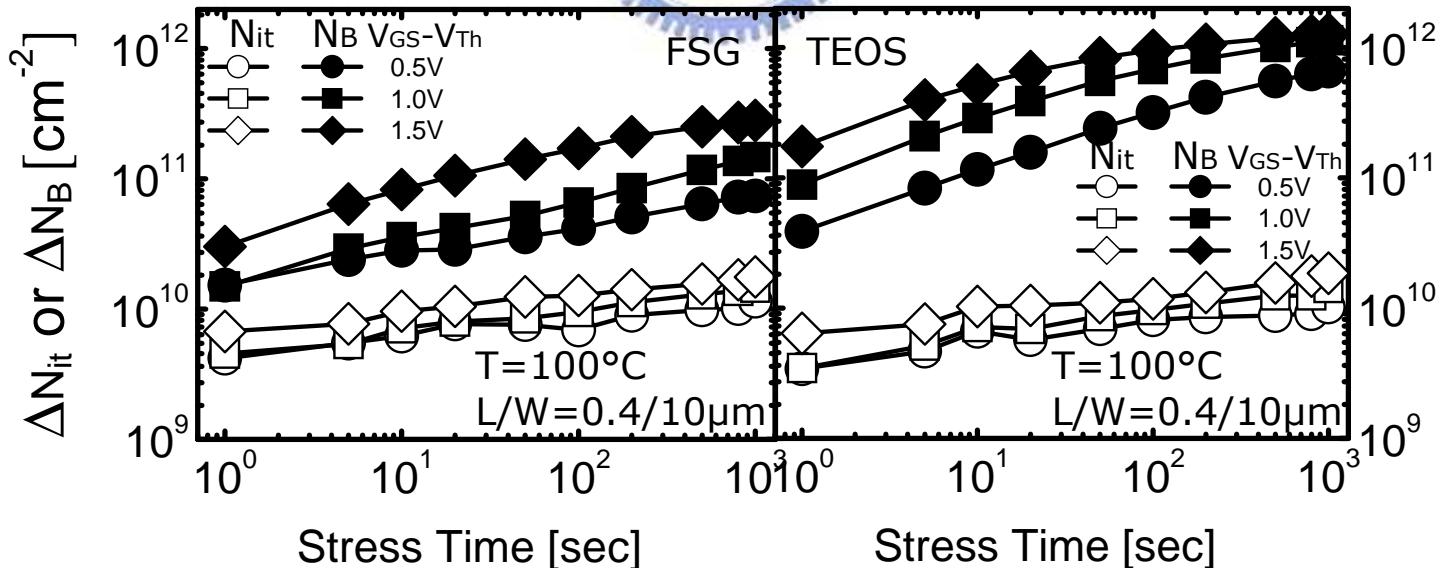

Fig. 3.5 Separation of total captured trap density into  $\Delta N_{it}$  and  $\Delta N_B$  component for all splits after 1000s PBT stress.

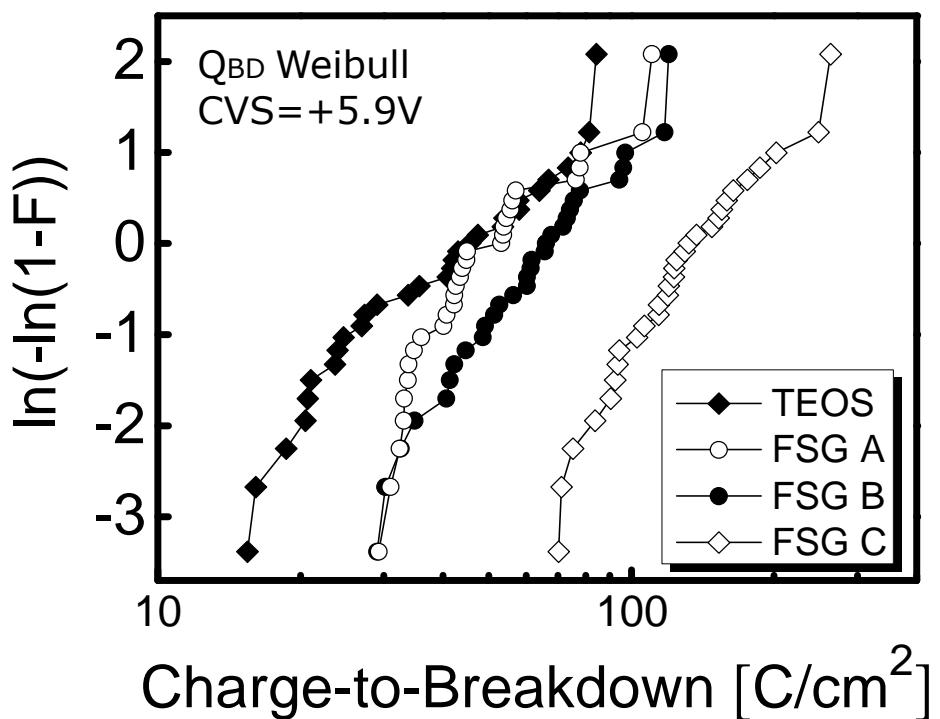

Fig. 3.6 Weibull plot of charge-to-breakdown for all samples under a constant voltage stress of 5.9V.

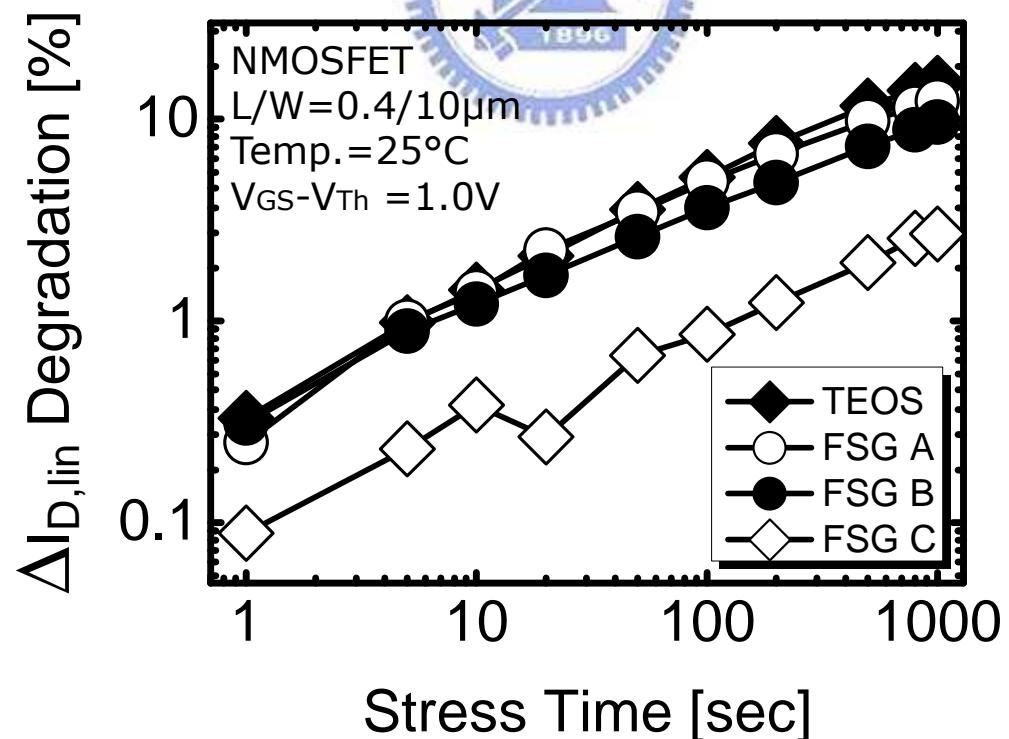

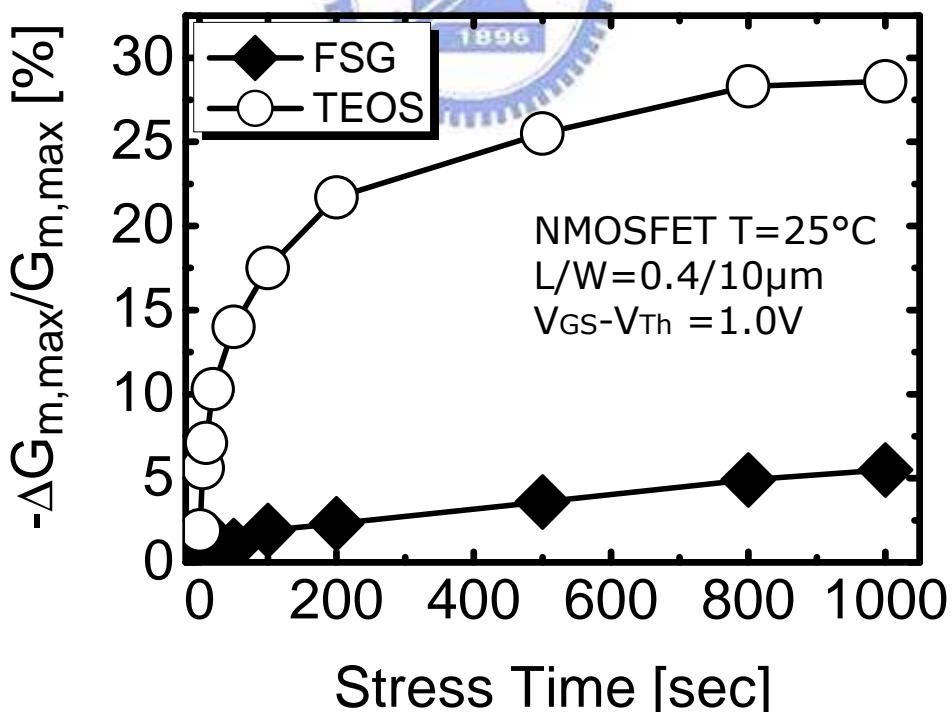

Fig. 3.7 Transconductance degradation versus stress time for both samples with  $V_{GS} - V_{Th} = 1.0V$  at 25°C.

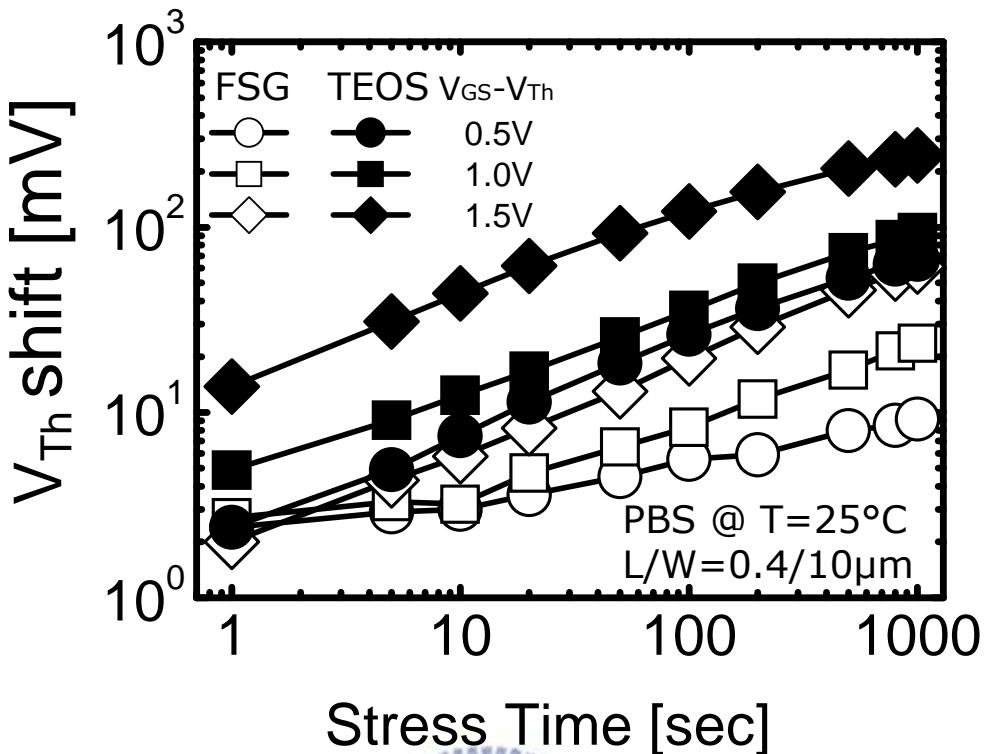

Fig. 3.8 Time dependences of PBS-induced  $V_{Th}$  degradation at various normalized stress biases from 0.5 to 1.0 per steps of 0.5V at 25°C.

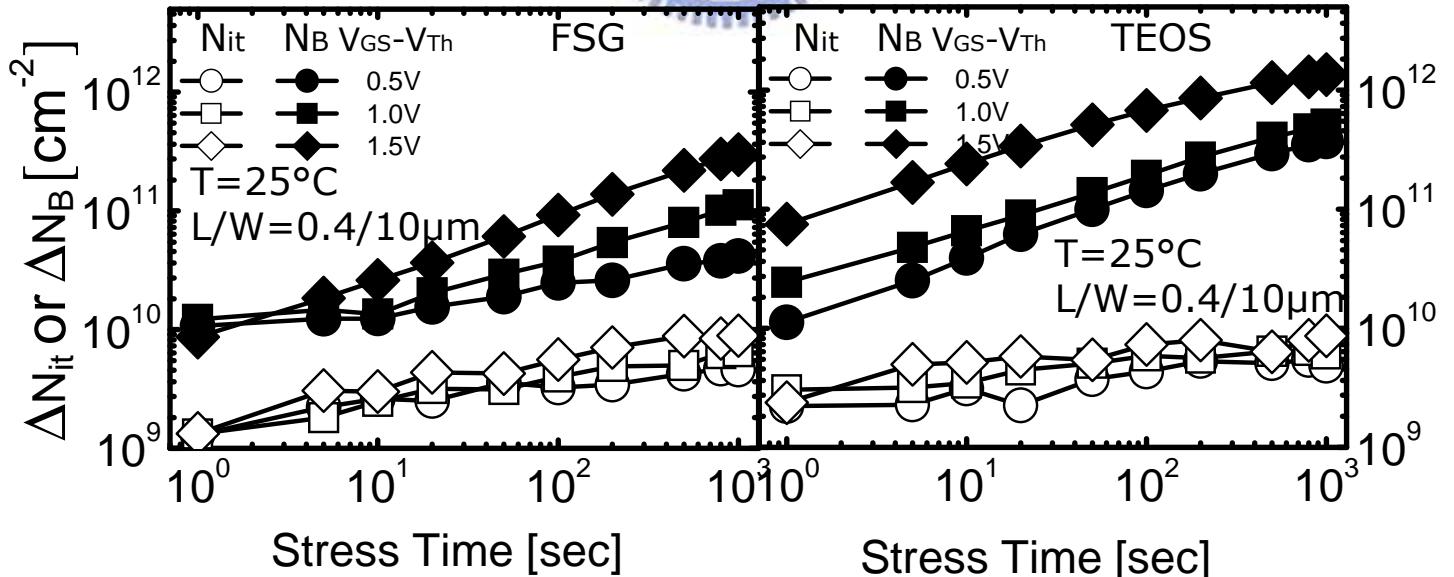

Fig. 3.9 Time dependences of PBS-induced  $N_{it}$  and  $N_B$  degradation at various normalized stress biases from 0.5 to 1.0 per steps of 0.5V at 25°C.

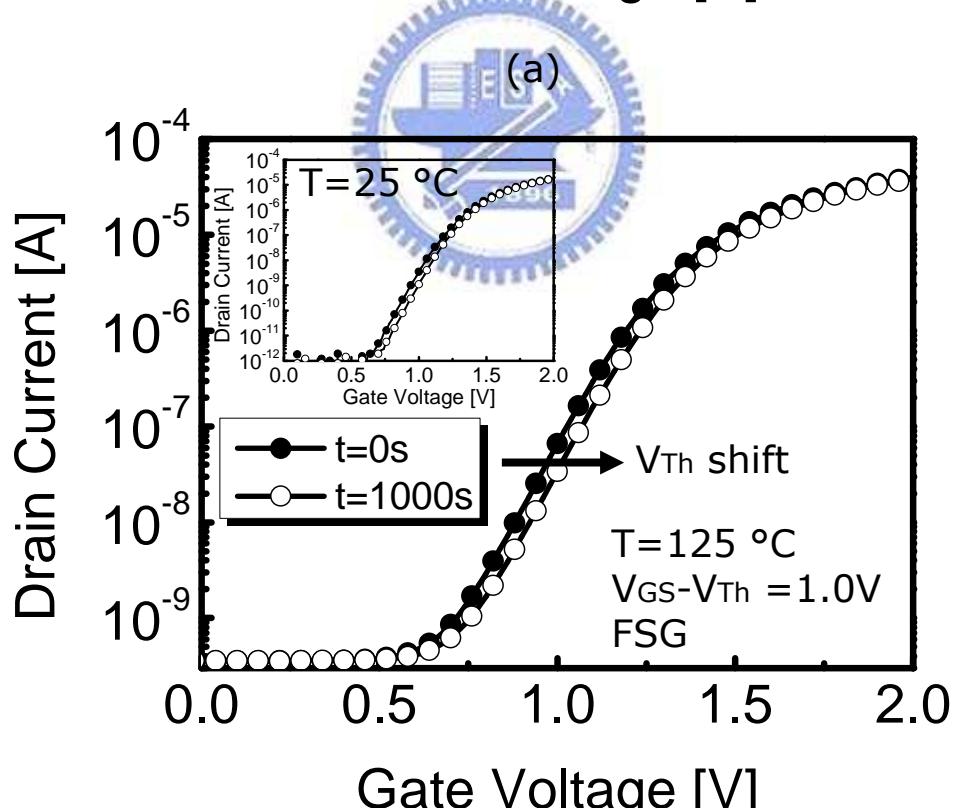

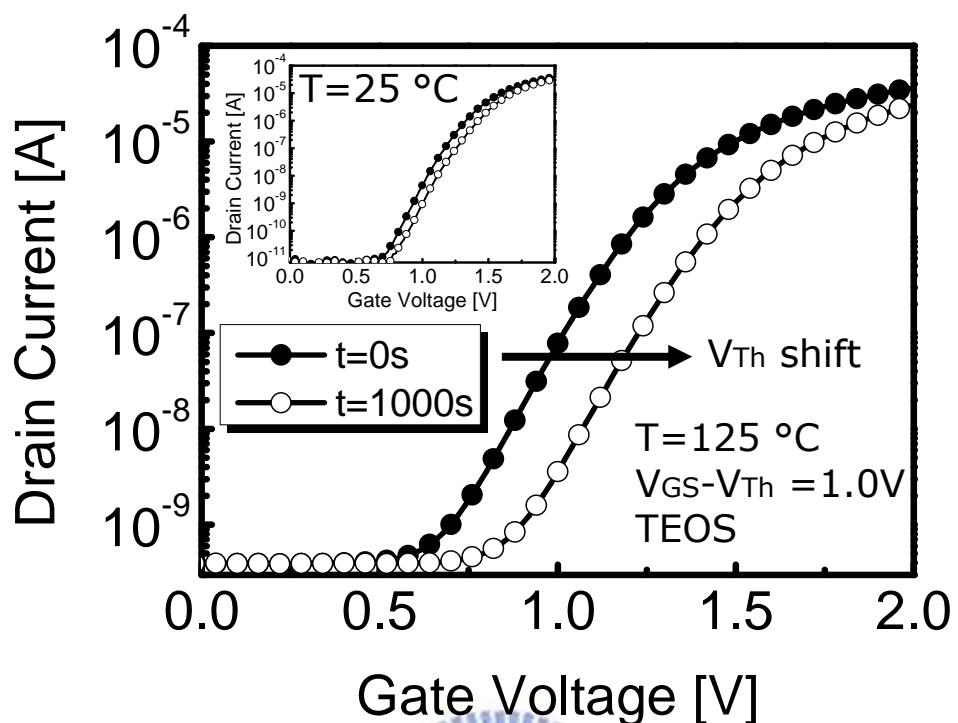

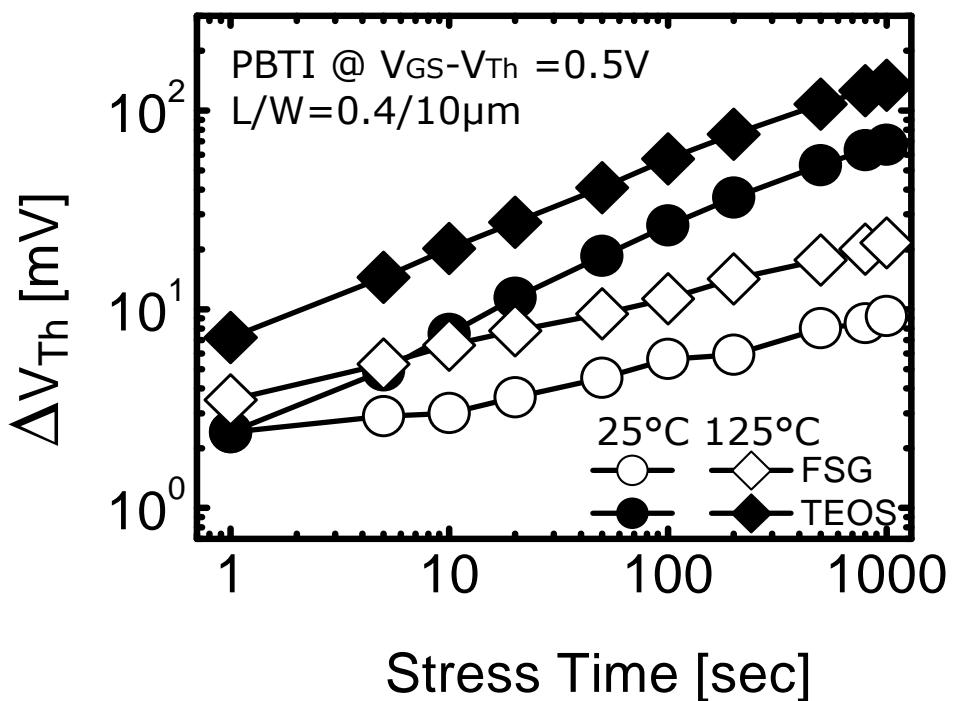

Fig. 3.10  $I_D$ - $V_{GS}$  characteristics for  $HfO_2/SiON$  n-MOSFETs before stress and after stress 1000s at 125°C (a) TEOS P.L. (b) FSG P.L. sample.

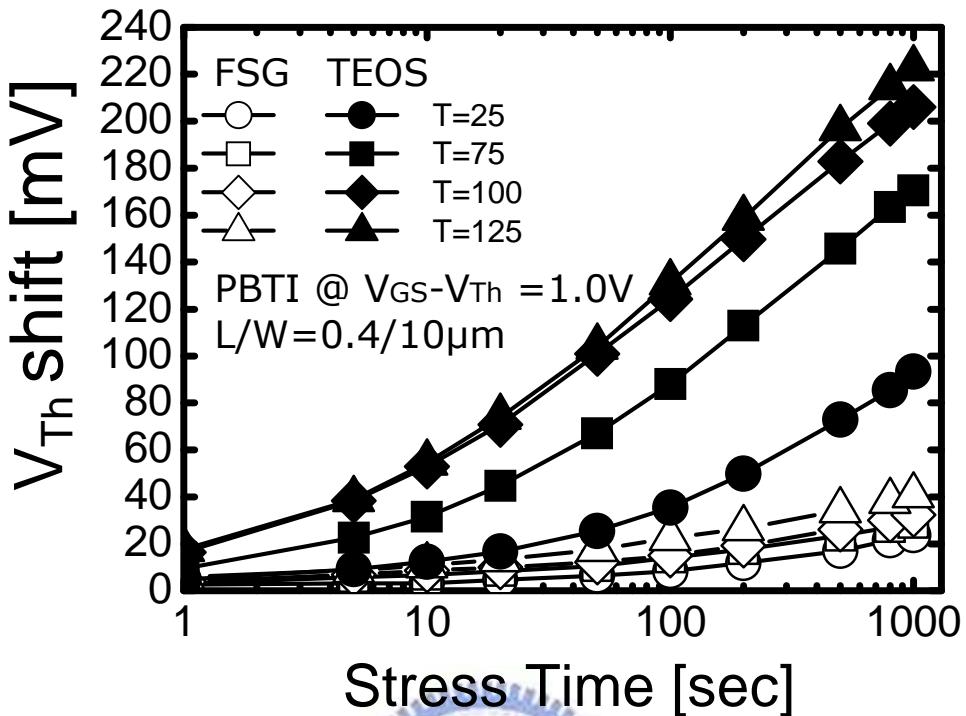

Fig. 3.11 Threshold voltage shift as a function of stress time under +1.0V

normalized gate bias voltage at various temperatures.

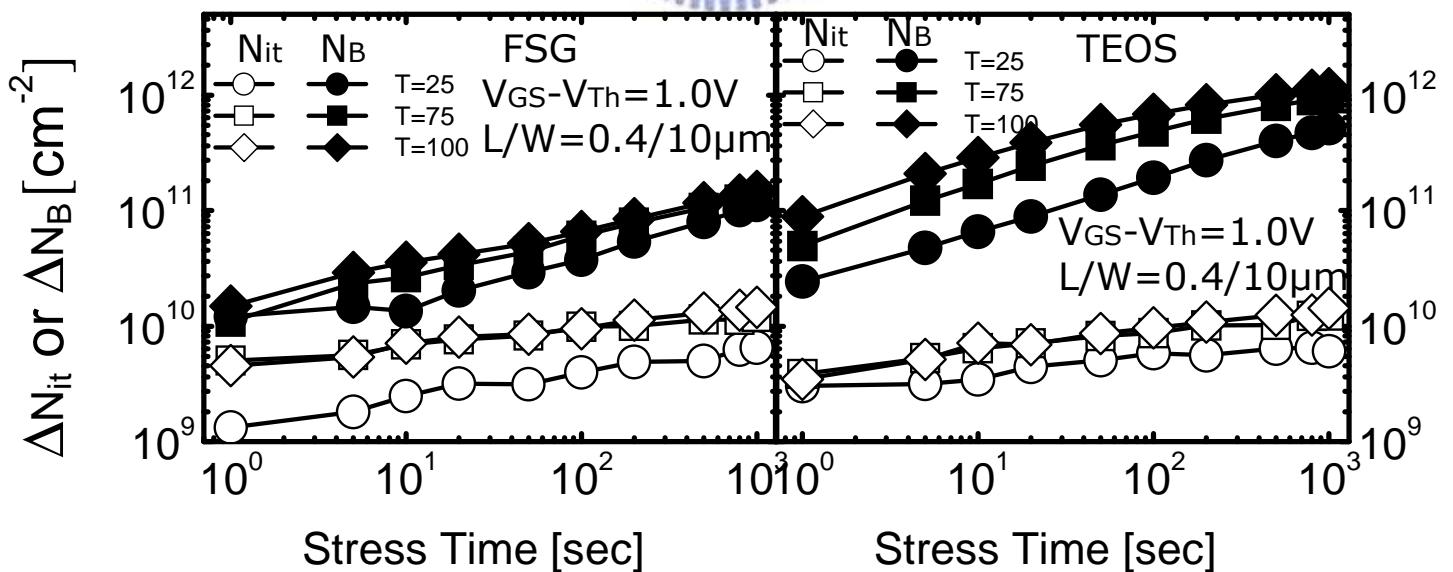

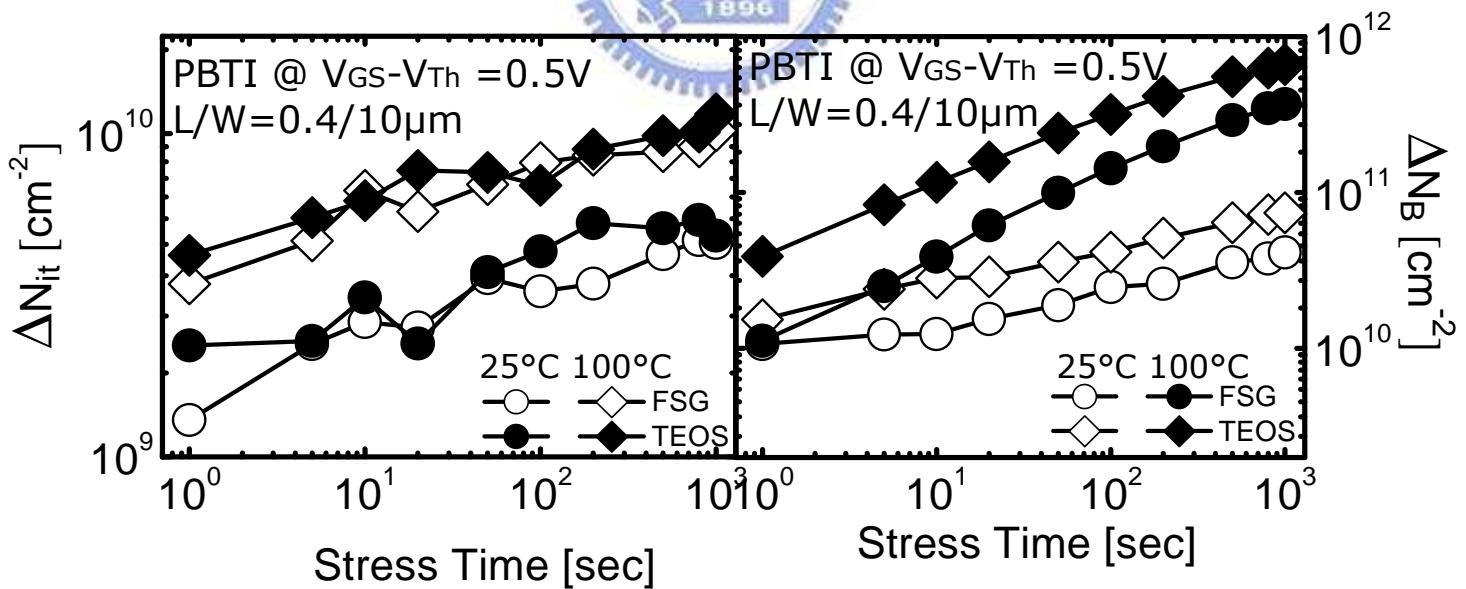

Fig. 3.12 Interface trap density and bulk trap density shift as a function of stress time under BTS at different stress temperature,  $V_{GS}-V_{Th}=1.0V$ .

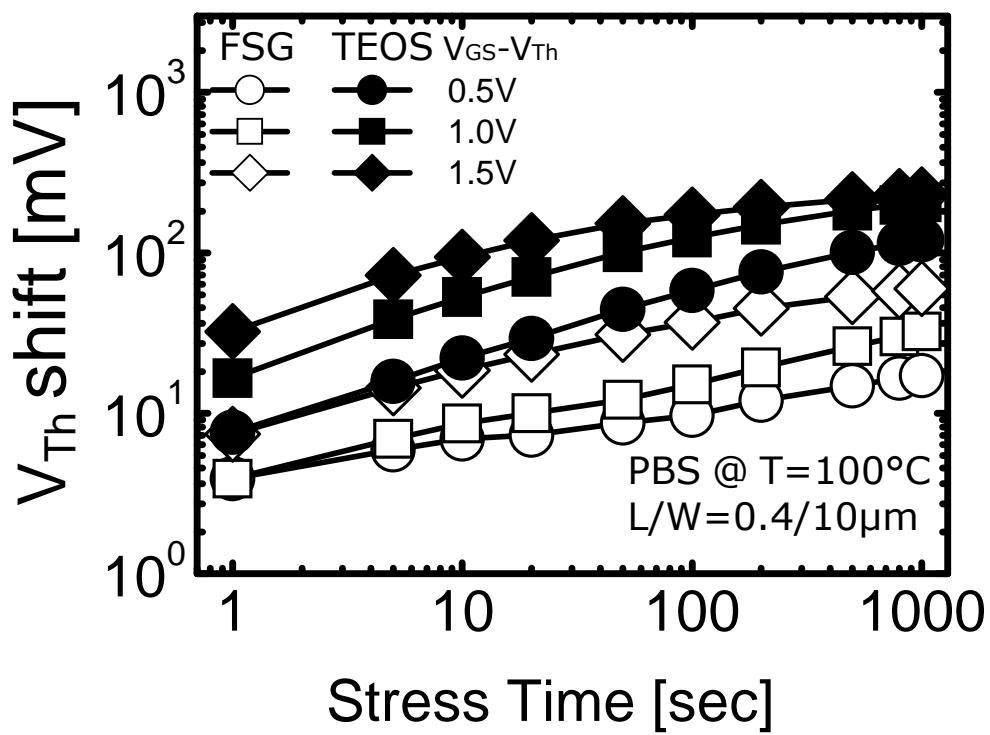

Fig. 3.13 Time dependences of PBS-induced  $V_{Th}$  degradation at various normalized stress biases from 0.5 to 1.0 per steps of 0.5V at 100°C.

Fig. 3.14 Time dependences of PBS-induced  $N_{it}$  and  $N_B$  degradation at various normalized stress biases from 0.5 to 1.0 per steps of 0.5V at 100°C.

Fig. 3.15 Threshold voltage shift as a function of stress time under BTS at different stress temperature,  $V_{GS}-V_{Th}=0.5V$  for FSG and TEOS samples.

Fig. 3.16 Interface trap density and bulk trap density shift as a function of stress time under BTS at different stress temperature,  $V_{GS}-V_{Th}=0.5V$  for FSG and TEOS samples.

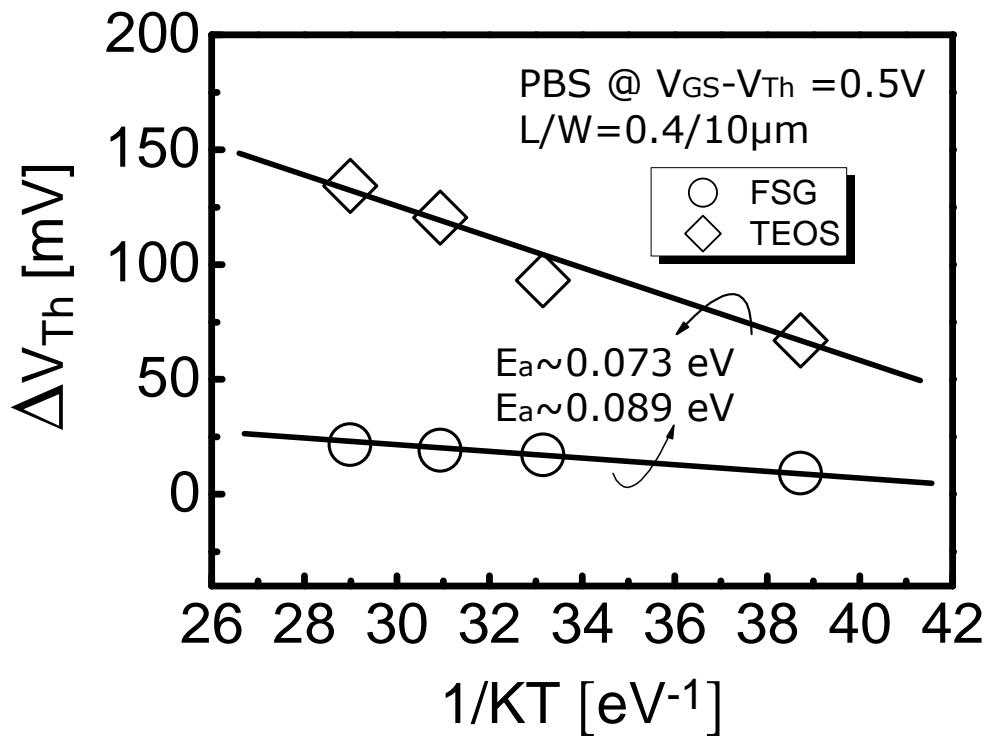

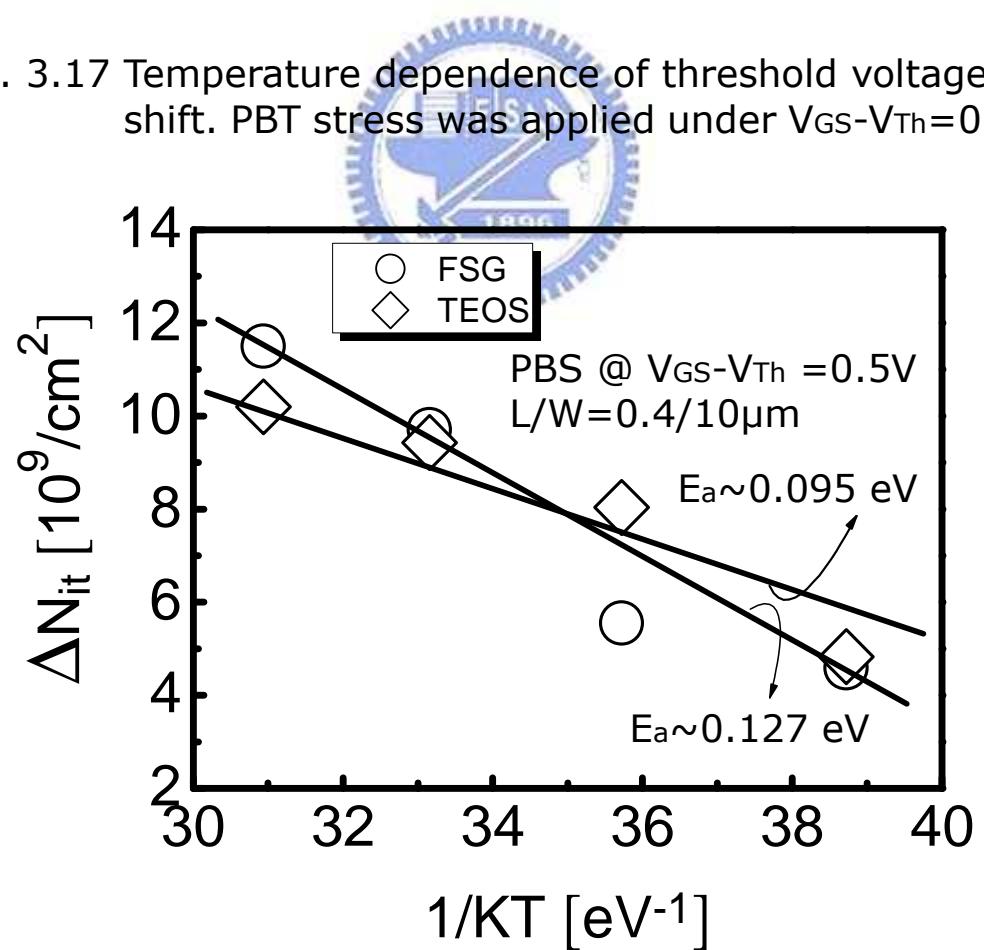

Fig. 3.17 Temperature dependence of threshold voltage shift. PBT stress was applied under  $V_{GS}-V_{Th}=0.5V$ .

Fig. 3.18 Temperature dependence of interface traps shift. PBT stress was applied under  $V_{GS}-V_{Th}=0.5V$ .

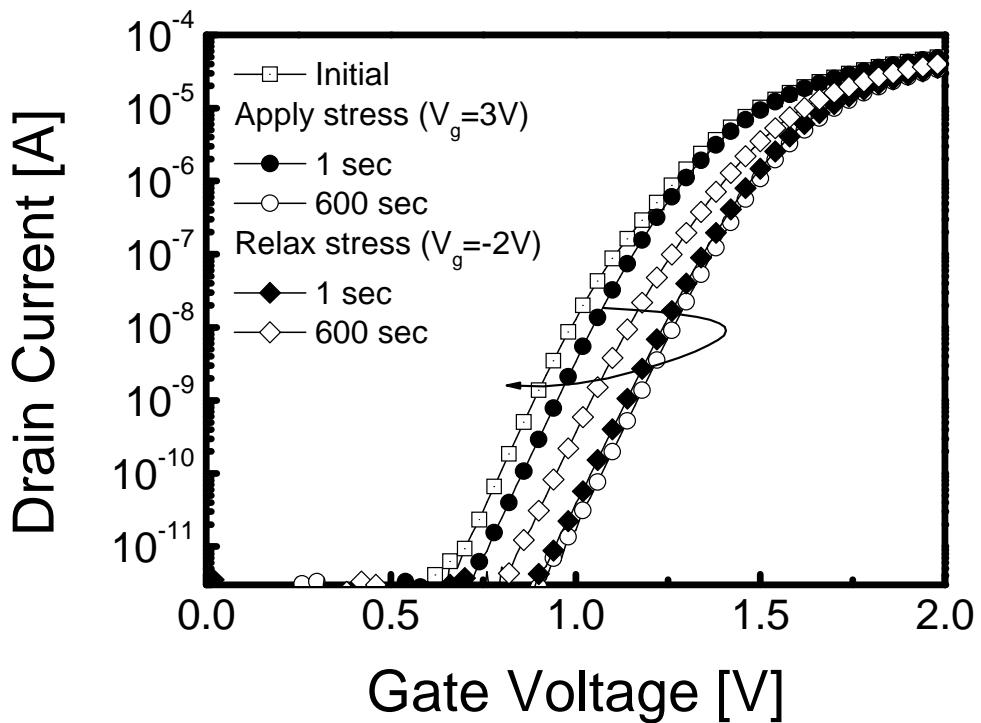

Fig. 3.19  $I_D-V_{GS}$  characteristic during a constant voltage stress with a subsequent relaxation period.

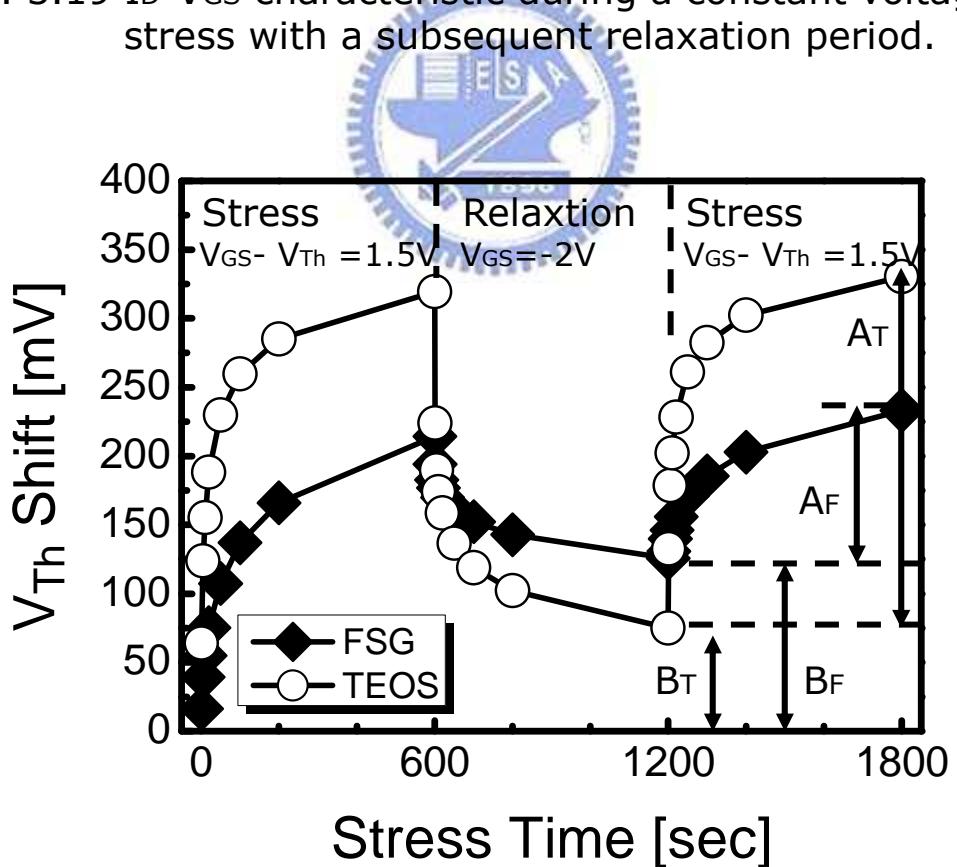

Fig. 3.20 Threshold voltage shift with de-trapping bias  $-2 V$  dependence after positive voltage stress on both samples.

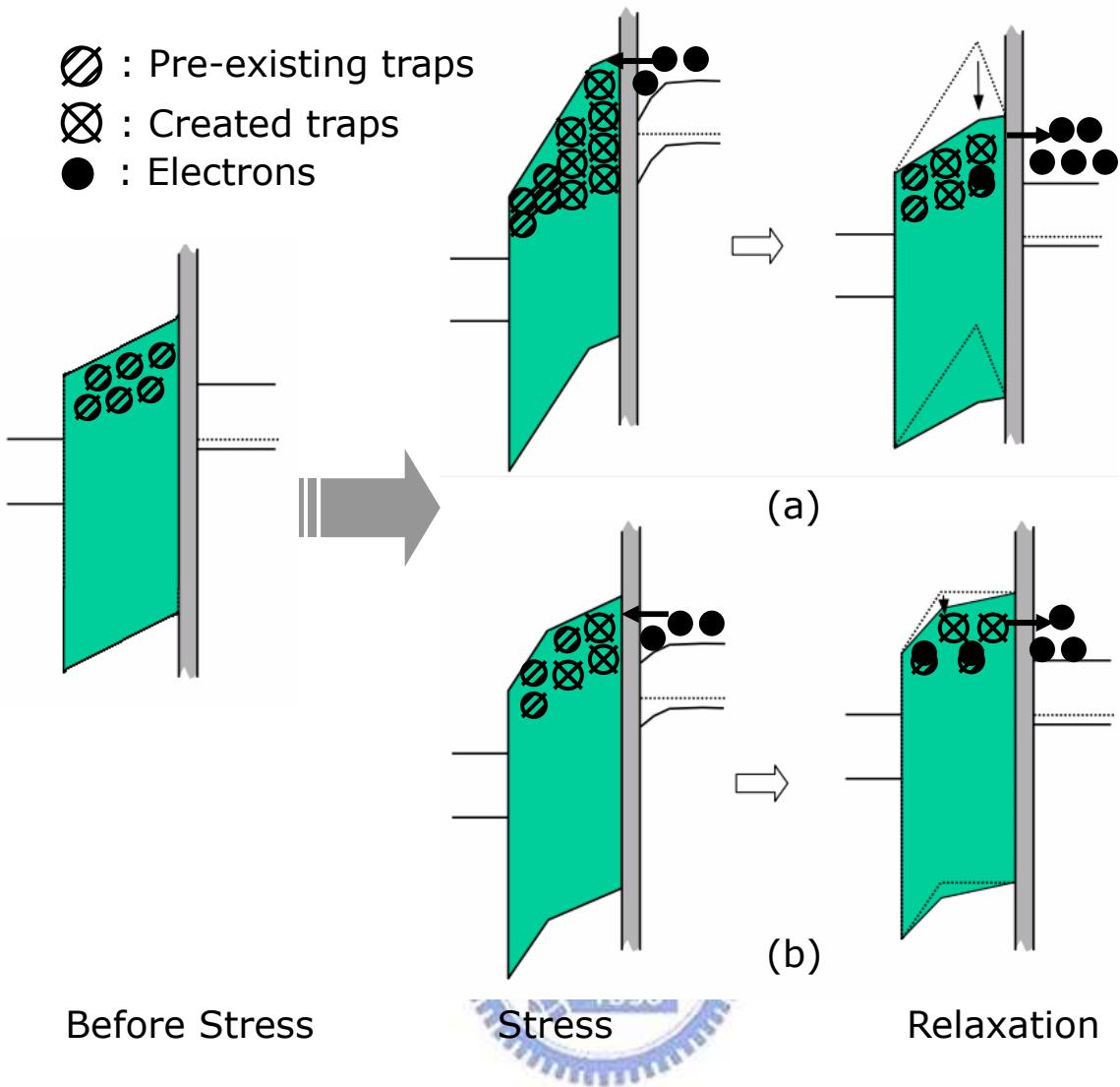

Fig. 3.21 Schematic explanation of stress and relaxation process with different bias conditions for (a) TEOS (b) FSG P.L..

Fig. 3.22 Schematic explanation of more charge trapping stored in thicker CET during stress cycle.

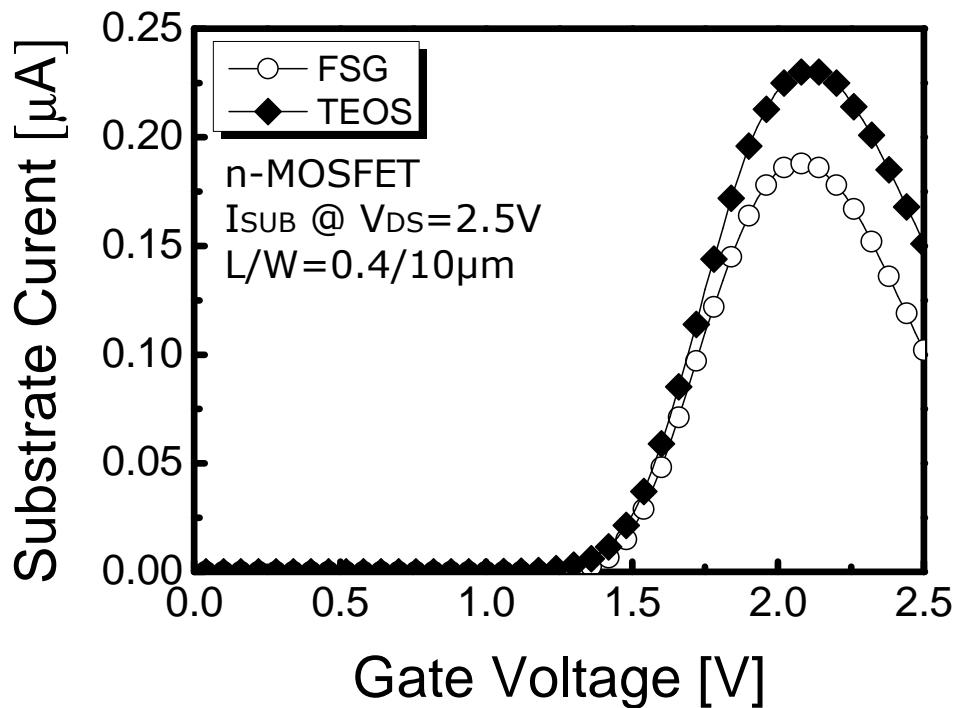

Fig. 3.23 Substrate current versus gate voltage for both samples of  $HfO_2/SiON$

gate stack n-MOSFETs.

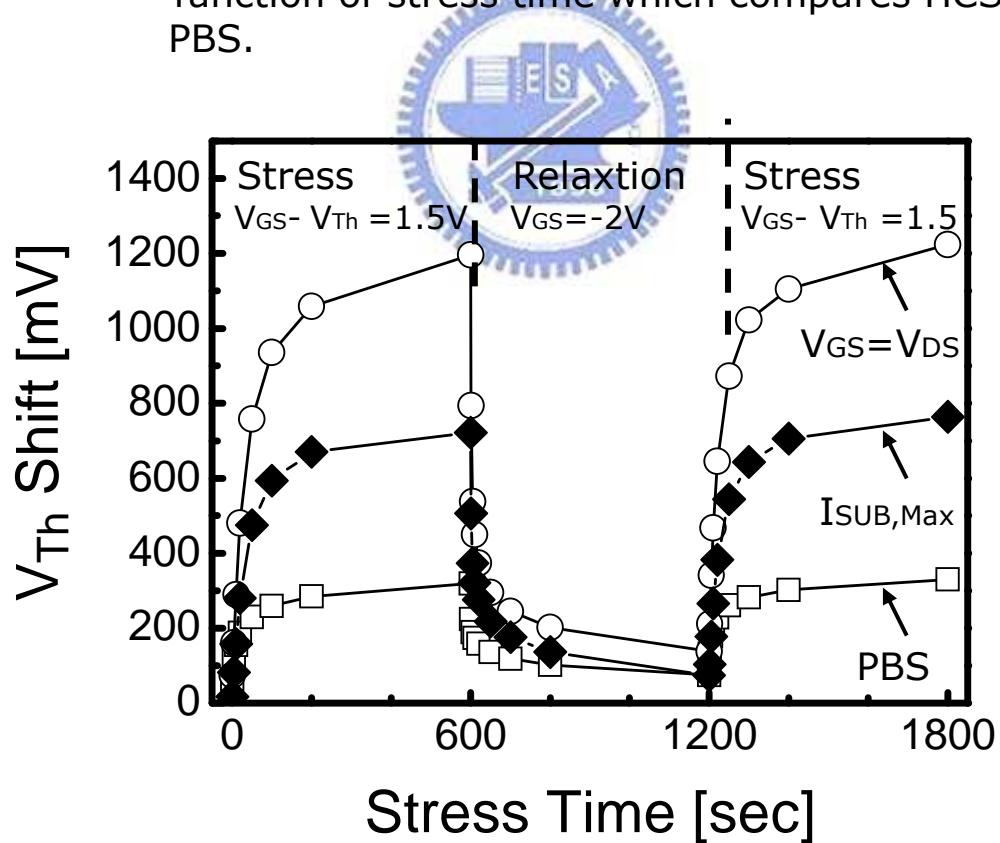

Fig. 3.24 Threshold voltage shift as a function of stress time with HCS which compares FSG P.L. with TEOS P.L..

Fig. 3.25 Interface trap and bulk trap density shift as a function of stress time with HCS which compares FSG P.L. with TEOS P.L..

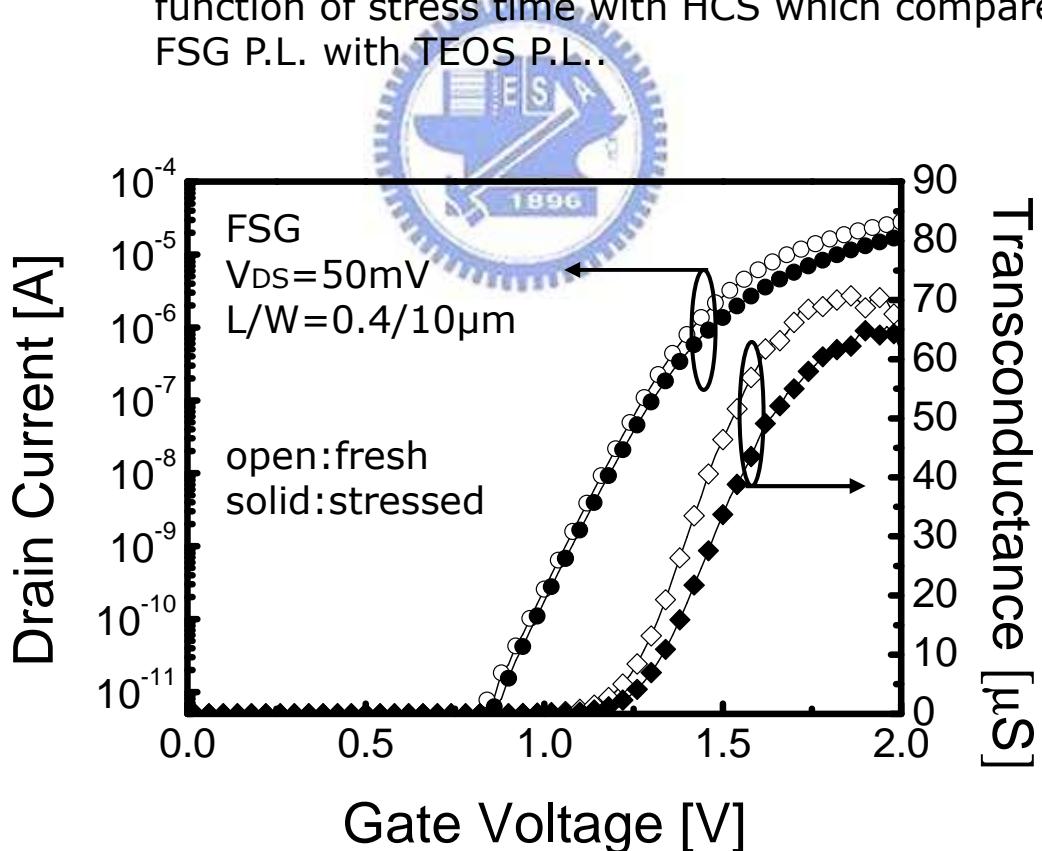

Fig. 3.26  $I_D$ - $V_{GS}$  characteristics and transconductance of devices with FSG P.L. before and after 1000 sec hot-electron stressing.

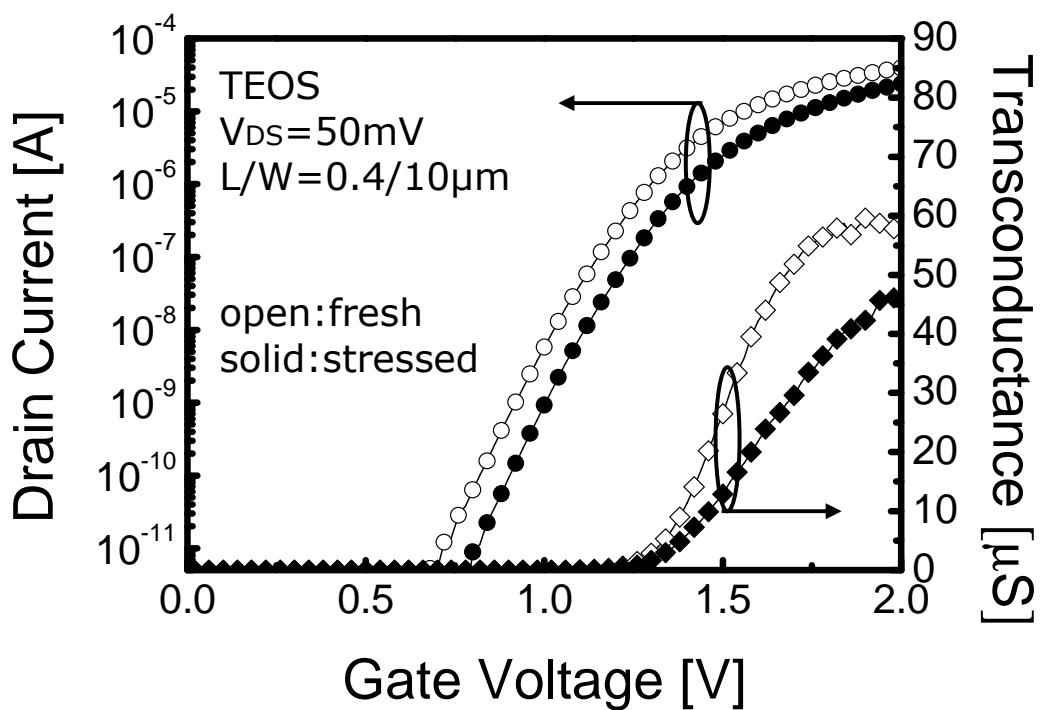

Fig. 3.27  $I_D$ - $V_{GS}$  characteristics and transconductance of devices with TEOS P.L. before and after 1000 sec hot-electron stressing.

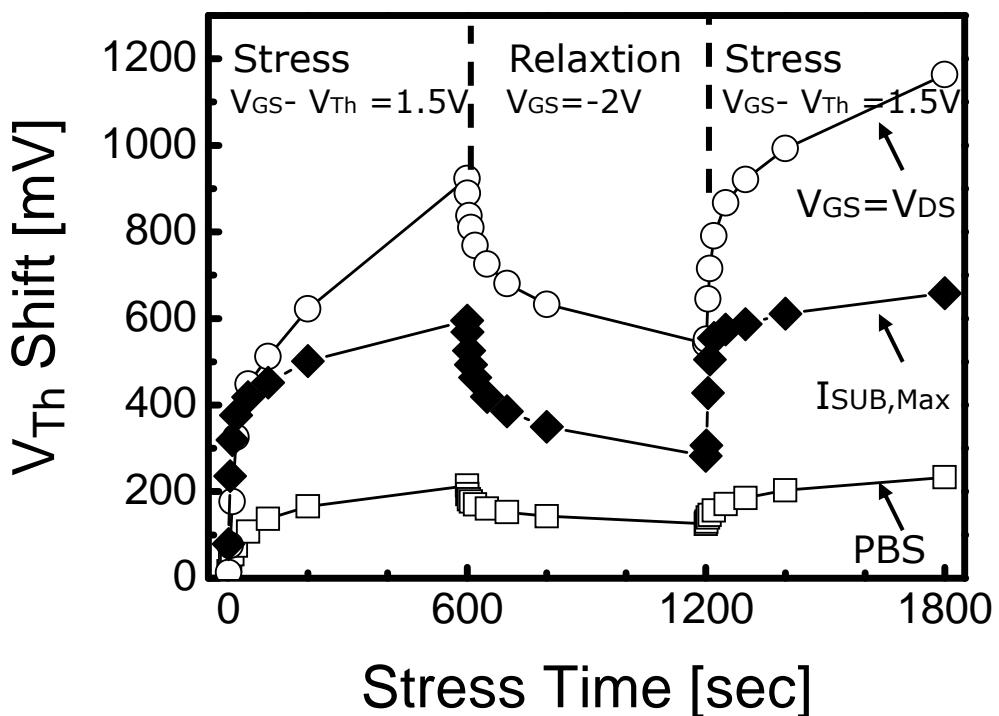

Fig. 3.28 Threshold voltage shift as a function of stress time which compares HCS with PBS.

Fig. 3.29 Interface trap and bulk trap density shift as a function of stress time which compares HCS with PBS.

Fig. 3.30 Threshold voltage changes during HCS and PBS followed by a detrapping step ( $V_g = -2V$ ) 600 sec for the TEOS sample.

Fig. 3.31 Threshold voltage changes during HCS and PBS followed by a detrapping step ( $V_g = -2V$ ) 600 sec for the FSG sample.

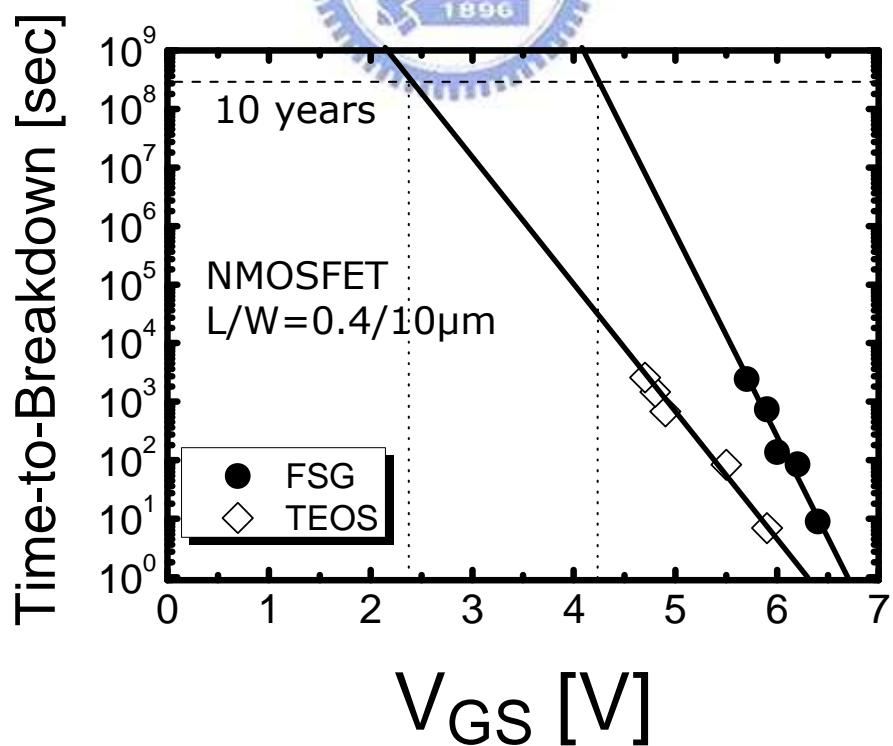

Fig. 3.32 Comparison of  $T_{BD}$  lifetime projection as a function  $V_{GS}$  of FSG P.L. larger than TEOS P.L..

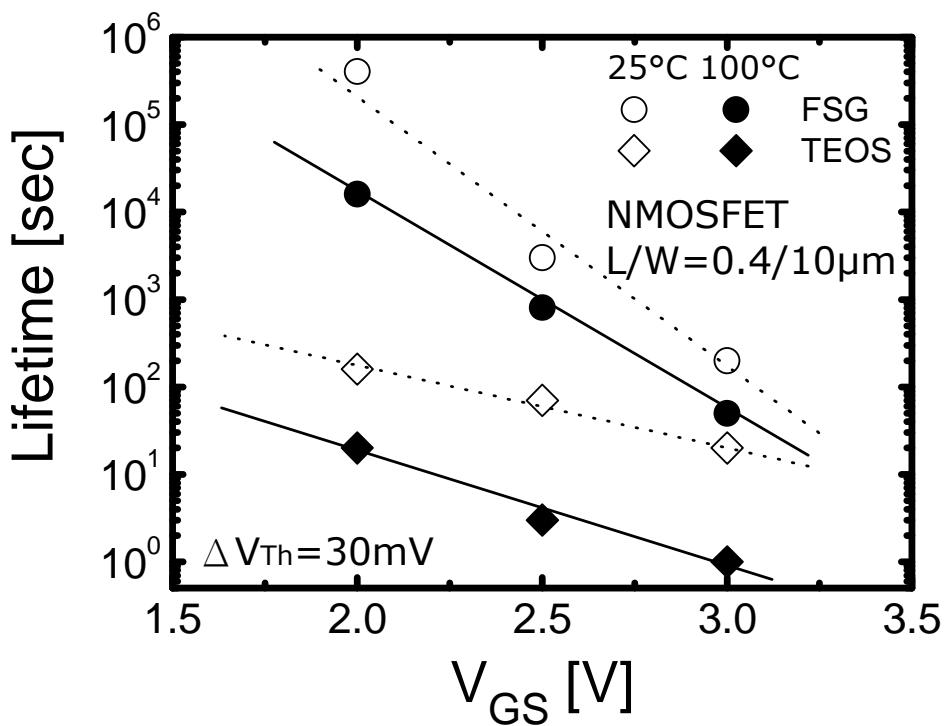

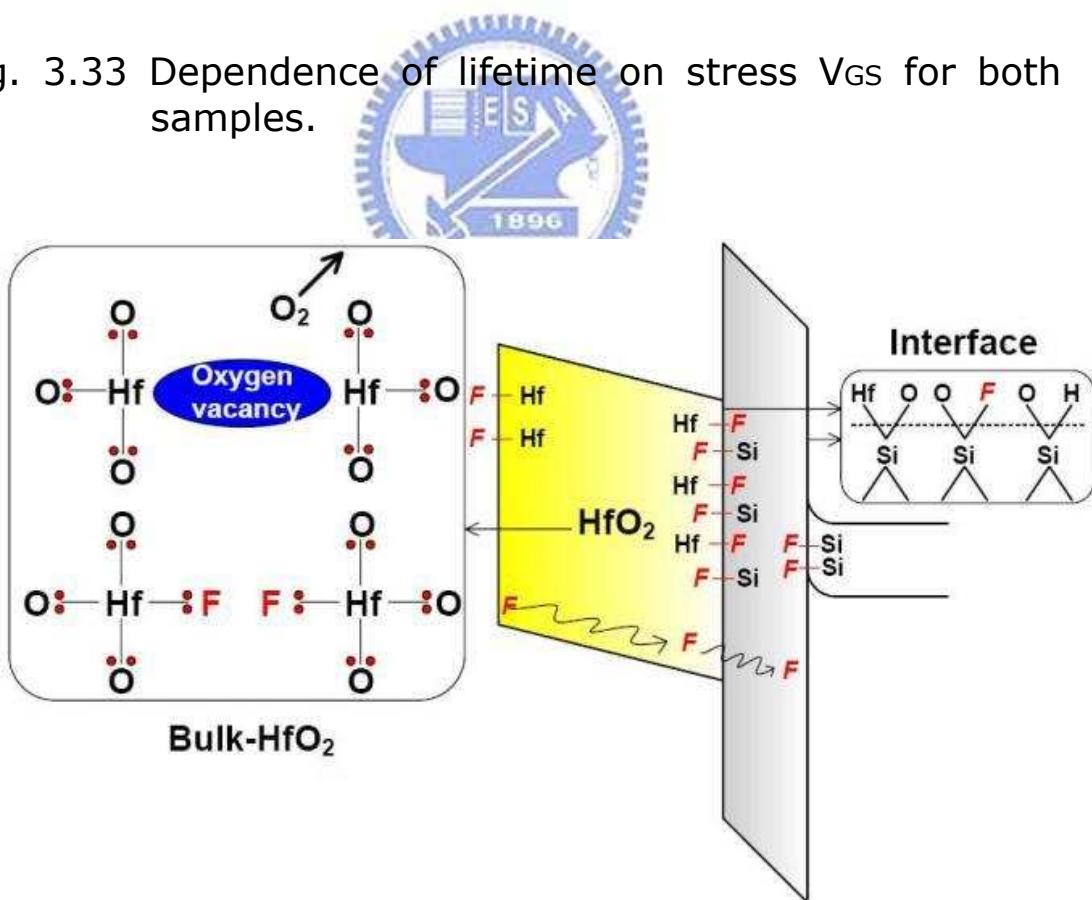

Fig. 3.33 Dependence of lifetime on stress  $V_{GS}$  for both samples.

Fig. 3.34 Schematic of reliability improvement for the FSG passivation layer due to fluorine incorporation.

# CHAPTER 01

## Introduction to High-k Gate Dielectrics

### 1.1 General Background

In order to provide better performance and higher packing density on the limited space, scaling down of the channel length is essential in ULSI fabrication technologies [1-2]. One of the main scaling issues in the advanced CMOS devices in the sub-100 nm regime is the thinning of gate oxide that is required for higher drive current and to improve the gate control over the channel, which reduces the short channel effects [3-4]. When dielectric ( $\text{SiO}_2$ ) thickness approaches 1 nm in CMOS devices scale, new materials such as high-k dielectrics and metal gate electrodes are required [5-6]. According to the ITRS roadmap, the  $\text{SiO}_2$  gate dielectric film thickness should be scaled down to 1.0 nm for 35nm technology node. Such an ultra-thin  $\text{SiO}_2$  film consists of only a few atomic layers, causing a considerably large direct-tunneling current through the film, as dictated in Equation (1-1) and in turn resulting in significant increase of power consumption. The direct tunneling current which depends on physical film thickness will cause an intolerable level of off-current, resulting in huge power dissipation and heat.

$$I_{DT} \propto [\exp - \sqrt{\frac{2mq\phi}{(h/2\pi)^2} T_{phys}}] \quad (1.1)$$

When it comes to leakage, it eventually degrades overall power consumption described as Equation (1-2).

$$P = ACV^2f + VI_{leak} \quad (1.2)$$

A is the fraction of gate actively switching and C is the total capacitance load of all gate. The dynamic power component ( $ACV^2f$ ) and static power component ( $VI_{leak}$ ) defines overall power consumption. As gate oxide is scaled down further, static power consumption will exponentially increase due to source of leakage such as gate oxide leakage and subthreshold leakage current (see Fig. 1.1). High-k materials have been shown to reduce the tunneling leakage current (i.e., suppressing gate oxide leakage and subthreshold leakage current), further reducing static power consumption, and metal electrodes are needed due to their better comparability with high-k dielectrics and absence of the depletion effect. In order to meet the ITRS (International Technology Roadmap for Semiconductor) 2008 requirements, Table 1.1 [7], replacing polysilicon by metal gates is critical.

On the trace to the physical limit, the scaling of CMOS technology is reluctant to depart far away from the Moore's Law. The famous "Moore's Law", proposed by Gordon Moore in 1965, states that the number of transistors on integrated circuits doubles every 24 months. For the past four decades, the advancement in the IC industry more or less follows this intelligent foresight in its pursuing better performance with lower cost. It can be said that "Moore's Law" is the

basis for the overwhelmingly rapid growth of the computing power. In order to keep close pace with "Moore's Law", the shrinkage of the transistor dimension is needed. Fig. 1.2 illustrates how the number of metal oxide semiconductor field effect transistors (MOSFETs) in Intel processors has increased historically [8].

According to the first order current-voltage relation in Equation (1-3) and (1-4), the driving current of a MOSFET can be given as

$$I_{D,sat} = \frac{1}{2} C_{gs} \mu_n \frac{W}{L_{eff}} (V_{GS} - V_{Th})^2 \quad (1.3)$$

$$C_{gs} = \frac{k \epsilon_0 A}{T_{inv}} \quad (1.4)$$

Where  $V_{GS}$  is the applied gate to source,  $L_{eff}$  is the effective channel length,  $W$  is the channel width,  $V_{Th}$  is the threshold voltage,  $\mu_n$  is the mobility for electrons,  $C_{gs}$  is the gate capacitance,  $k$  is the dielectric constant,  $\epsilon_0$  is the permittivity of free space and  $T_{inv}$  is the electrical film thickness. In an attempt to improve the current drivability of a MOSFET, all parameters contained in the above formula can be accordingly adjusted. With reduced threshold voltage, smaller effective channel length, and increased gate capacitance as well as gate-to-source voltage, we can achieve better current drivability and higher device density, which mean a better performance and much more transistors on the chip. However, some approaches will bring about serious drawbacks, and for instance, a large  $V_{GS}$  will degrade the reliability while too small a  $V_{Th}$  will result in statistical fluctuation

in thermal energy at a typical operation circumstance of up to 100 °C. So a bigger  $C_{gs}$  and shorter  $L_{eff}$  will be needed to maintain device performance.

In the front-end process area, there remain many technological challenges to be overcome to achieve further scaling and growth of the industry [9]:

- ◆ New gate stack processes and Materials

- ◆ Surfaces and interfaces control

- ◆ CMOS integration of new memory materials and processes

- ◆ Critical dimension and effective channel length control

- ◆ Scaled MOSFET dopant introduction and control

In this chapter, the first challenge will be discussed in detail because the challenge are the key motivation to this Thesis.

## 1.2 Motivation

Polysilicon gate and  $\text{SiO}_2$  gate dielectric for the MOSFET devices have been perfect materials throughout MOSFET history till now. However, as the device dimension shrinks into deep sub-micron regime,  $\text{SiO}_2$  as a gate oxide is facing serious challenges which seem to be almost impossible to overcome. As shown in Fig. 1.3, we can see that when the gate oxide thickness scales down to 2 nm, the leakage current will exceed the limit of  $1\text{A}/\text{cm}^2$  set by the allowable stand-by power dissipation. Further scaling of oxide thickness to below 2 nm, the direct tunneling current will increase exponentially, causing

intolerable power consumption. For easily sensing the seriousness of leakage problem: as  $\text{SiO}_2$  thickness is reduced, leakage current increases exponentially ( $\sim 10x/2\text{\AA}$ ) [10]. In addition, reliability issues become a serious concern for such a thin  $\text{SiO}_2$  dielectric only  $10\text{-}15\text{\AA}$  thick. It points out that  $\text{SiO}_2$  thickness uniformity across a 12 inch wafer imposes even more crucial difficulty in the growth of such a thin film, since even a mono-layer difference in thickness represents a large percentage difference and thus can result in the variation of threshold voltage ( $V_{Th}$ ) across the wafer. To circumvent these problems, high- $k$  dielectrics have been investigated extensively as possible replacement to the  $\text{SiO}_2$  film as gate insulators.

By using gate dielectrics with higher dielectric, electrically equivalent oxide thickness (EOT) in order to maintain the same gate capacitance can be obtained with a thicker physical thickness. Therefore, the quantum direct tunneling gate leakage current can be significantly reduced, as shown in Fig. 1.4. Selecting a gate dielectric with a higher permittivity than that of  $\text{SiO}_2$  is a clearly indispensable to extend the lifespan of the famous Moore's law. From (1.3), we can notice that the current drivability is strongly related to the electrical thickness of the gate oxide, while, from (1.2), the leakage is related to the physical thickness of the gate oxide. In order to maintain the same  $C_{gs}$  value, (1.4) can be rewritten as follows (1-5) :

$$T_{high-k} = \frac{k_{high-k}}{k_{ox}} EOT = \frac{k_{high-k}}{3.9} EOT \quad (1.5)$$

Where the term  $EOT$  represents the theoretical thickness of  $\text{SiO}_2$ . So by increasing the gate dielectric constant, the same equivalent oxide thickness can be obtained with a thicker physical thickness, which in turn contributes to the reduced gate leakage current (i.e., direct tunneling), without sacrificing the performance. Also the reliability issues become a huge concern for this thin regime of  $\text{SiO}_2$  film because the direct tunneling electrons make it more vulnerable for given conditions and eventually cause a possible threshold voltage fluctuation or even dielectric breakdowns of devices, which result in a malfunction or failure of device [11]. Therefore, searching a material with a high dielectric constant to replace  $\text{SiO}_2$  is urgently needed.

Lately there has been increased interest in the possibility that fluorine might help protect devices against negative bias temperature instability (NBTI) [12]. It has been shown that the presence of fluorine improves the lifetime of devices under such conditions. Since NBTI has emerged as one of the main reliability issues for today's ultrathin oxides, this improvement is particularly significant. Fluorine is one of the extrinsic species that can be found in microelectronic devices. It is usually introduced through the use of a molecular precursor or by direct implantation of F ions [13-16]. The presence of fluorine in devices has been known to have certain beneficial effects on their operation, such as hot-carrier immunity [15], improved dielectric integrity [16], and reduced flicker noise [14]. In conventional, fluorine ion implantation (FII) technique is mostly adopted to introduce

fluorine atoms into the poly-Si or silicon substrate channel. However, this method may be not suitable for large-area electronics. Moreover, a subsequent high temperature process is required to activate implanted fluorine atoms and recover the damage created by implantation. It is known that excessive fluorine annealing replaces Si–O bonds with Si–F bonds, which generates reactive oxygen atoms. The oxygen atoms, which react with silicon substrate, form thick interfacial  $\text{SiO}_x$  layer [17-18]. Consequently, these processes can cause additional damage due to the high energetic ion implantation. To minimize damage, effective and process-compatible techniques to introduce fluorine atoms into high-k gate dielectric stacks are needed to be developed. In the latter chapters, we will present improvement results for the new process-compatible fluorination technique that is critical to the role of fluorine in the operation of high-k gate dielectric stacks devices.

## 1.3 Recent High-k Gate Dielectric

### 1.3.1 Criteria for High-k Gate Dielectrics

There are couples of key issue to select proper high-k dielectric material. The first one is that although the k value should be as high as possible, however, it should not be too high, otherwise it could result in degradation of the electrical properties due to increased fringing field from the gate to the source/drain of the transistor, i.e., field induced barrier lowering (FIBL) which degrade short channel

effects of MOSFETs [19]. On the same token, the  $k$  value should not be too low, otherwise it defeats the whole purpose of substituting for high  $k$  materials. Secondly, thermal stability of materials with silicon and its interface quality are important. For all thin gate dielectrics, the interface with Si substrate plays a key role, and in most cases is the dominant factor in determining the overall electrical properties. Therefore, the high- $k$  materials require an interfacial reaction barrier to minimize the undesirable reactions with Si substrate. In addition, Figure 1.5 shows the characteristics of oxygen diffusion through high- $k$  dielectric materials [20]. Due to the rapid oxygen diffusion, an additional interfacial layer forms between the high- $k$  dielectric and Si substrate. But, this interfacial layer is obviously not helpful to scale down the device size because of its low permittivity. Therefore, proper capping technology might be required to avoid undesired interfacial reaction with high- $k$  dielectric. Thirdly, the higher band offset indicates that the carriers (i.e., electron or hole) are less likely to be injected from the anode or cathode into a dielectric film. Fourthly, Gate and fabrication process compatibility need to be considered. The structural approach of conventional poly-silicon gate electrode on high- $k$  material does not seem to be a good method any more. A poly depletion effect results in increase of EOT [21-22]. Boron diffusion through high- $k$  dielectric degrades  $V_{th}$  instability and reliability characteristics [22]. Moreover, Fermi level pinning characteristic affects narrow down of on-off margin in operation voltage of CMOS

[23]. Finally, the electrical reliability of new high-k dielectric must also be considered critical for application in CMOS technology. Whether or not a high-k dielectric satisfies the strict reliability criteria is still under investigation, and many areas of these studies are not well understood yet. However, a few preliminary projections for reliability such as stress induced leakage current (SILC), time-dependent dielectric breakdown (TDDB), bias temperature stress (BTS) appear to be encouraging for adopting high-k material as a future gate dielectric.

The high-k materials as advanced gate dielectric to replace conventional  $\text{SiO}_2$  should meet following properties :

- 1) High dielectric constant (12~60)

- 2) Large energy band gap ( $>5\text{eV}$ ) and barrier height ( $\phi_B > V_{DD}$ )

- 3) Low leakage current at the operating voltage ( $J < 10^{-3} \text{A/cm}^2 @ V_{DD}$ )

- 4) Thermal stability on Si at high temperature

- 5) High crystalline temperature due to favorable amorphous phase

- 6) High resistance to oxygen and impurity penetration

- 7) Low interface states ( $D_{it} < 10^{11} / \text{cm}^2\text{eV}^{-1}$ ) with Si-substrate and low bulk charge (negligible hysteresis and frequency dependence)

- 8) Low EOT ( $T_{inv} < 1 \text{nm}$ ) and gate leakage current

- 9)  $V_{FB}$  and Hysteresis  $< 20\text{mV}$

- 10) Less mobility degradation

- 11) No Fermic level pinning effect for high-k film contacting with

gate electrode, i.e., tunable work function of gate electrode

- 12) Compatibility with gate electrode material

- 13) Reliability (No charge trapping, TDDB>10years)

### 1.3.2 Challenges to High-k Technology

Compared with the conventional  $\text{SiO}_2$  oxide and poly-Si electrode, the high-k oxides present many challenges in the context of compatibility with the Si MOSFET technology. In addition to incompatibility with annealing temperatures used for activating poly-gates, the relatively poor quality, compared to  $\text{SiO}_2$ , of the high-k oxide materials causes charge trapping and makes the Si MOSFET gate unstable. The channel mobility degradation, and threshold voltage shift induced by high-k materials also need to be addressed.

The high-k gate layer has soft optical phonons and the long-range dipole associated with the interface excitations would degrade the effective electron mobility in the inversion layer of the Si substrate [24]. Yang et al. [25] summarized the effects of all of the scattering and degradation mechanisms on the inversion channel carrier mobility, as shown in Fig. 1-6. The mobility issue is complicated by the fact that mobility values demonstrate dependence on the gate stack EOT. Therefore, different process solutions may be needed for high performance (small EOT) and low power (greater EOT) applications. Process solutions yielding  $\sim 80\%$  universal  $\text{SiO}_2$  mobility have been reported only for EOT  $\sim 15 \text{ \AA}$  [26].

The threshold voltage ( $V_{Th}$ ) shift of the poly-Si/high-k stack is another challenge that must be considered. Reliability characteristics of the Hf-based dielectric such as time dependent dielectric breakdown (TDDB), bias temperature instability (BTI), and hot carrier induced degradation (HCI) have been actively investigated in connection with expected application of these materials in the high-k gate stack. One of main issues for high-k gate stack is the charge trapping characteristics during reliability test. Initial observation of instability was studied through capacitance-voltage (CV) characteristics in flat-band voltage change and current-voltage (IV) change. Since electrons can be trapped and detrapped in the high-k dielectrics with a minimal residual damage to its atomic structure [27], a threshold voltage instability associated with electron trapping/detrapping in high-k layer can significantly affect the transistor parameters and complicate the evaluation of the effects of stress-induced defect generation phenomenon on the high-k gate stacks, which typically is not an issue in the case of  $\text{SiO}_2$  dielectrics. Since those charge trapping affect significantly on  $V_{Th}$  measurement and reliability characteristics, comprehensive study is required to detail understand.

## 1.4 Overview of Enhancing Robustness by Fluorine

Silicon oxide is the insulator of CMOS, and it normally has few defects. At Si: $\text{SiO}_2$  interfaces, the defect density is further lowered by

hydrogenation, with any Si dangling bonds  $P_b$  centers converted to Si-H bonds. Historically fluorine incorporation into gate dielectric is known as an effective way to passivate the interface traps in the conventional  $\text{SiO}_2$  gate dielectric and it can improve device reliability because it was known that fluorine incorporation in the  $\text{SiO}_2$  gate dielectrics replaces Si-H bonds with Si-F bonds, Si-F bonds rather strong than Si-H bonds. But the high-k oxides itself exist more much bulk trap charges than silicon oxide and suffer from a high density of charge traps. This causes transient instability of the gate threshold voltage, coulombic scattering of carriers in the Si channel, and possible reliability problems. Recent work indicates that the main charge trap is the oxygen vacancy  $V_o$  [28]. The high-k oxides differ from Si:H or  $\text{SiO}_2$ , that is, they all have ionic bonding. As a result of implanted fluorine that was found to have a large beneficial effect on charge trapping [29-31], F was found to substitute at the  $V_o$  site and passivates it. Thus F is one of the best passivant for defects in an ionic oxide because it is the only element that is more electronegative than oxygen and its bond length is similar. It can improve both the device performance and also reliability by way of F to passivate vacancies in ionic oxides such as  $\text{HfO}_2$  because vacancies are more likely to be charged.

However, an excess amount of F incorporation increases oxide thickness. It is known that excessive F annealing replaces Si-O bonds with Si-F bonds, which generates reactive oxygen atoms. The oxygen

atoms, which react with silicon substrate, form thick interfacial  $\text{SiO}_x$  layer [17-18]. Moreover, another drawback after an excess amount of fluorination is a net negative charge observed at the high-k oxide and interfacial layer interface such as  $\text{HfO}_2/\text{SiO}_2$ , while also increasing the leakage current density [32]. The higher leakage current may also result in part from possible barrier height lowering for electron transport through the high-k oxide stacks. On the other hand, boron diffusion and penetration in thin gate oxide down to 17 Å with poly-Si gate have been the troublesome problem for p-type MOSFETs [33]. It shows even a moderate dose of F in  $\text{SiO}_2/\text{Si}$  with poly-Si gate such as significantly enhanced boron penetration through  $\text{SiO}_2$  from  $P^+$  poly-Si gate to substrate and an increase in the physical thickness of  $\text{SiO}_2$  [34].

Therefore, tuning the F ion concentration at the  $\text{HfO}_2/\text{SiO}_2$  interface may be an essential aspect of such a defect passivation scheme. Previous work studies suggest an insight into this problem. It was observed that the concentration of interstitial F ions was reduced by two orders of magnitude after a 400 °C FGA. Hydrogen annealings seem to be able to remove excess F ions which are not strongly bonded in the bulk region of the  $\text{HfO}_2$  films [35].

## 1.5 Organization of the Thesis

This thesis consists of four chapters. The main topics are focused on the effects of fluorine incorporation into passivation dielectric of

n-MOSFETs with  $\text{HfO}_2/\text{SiON}$  gate stack, evaluated in terms of reliability and performances. We study systematically the electrical characteristics of  $\text{HfO}_2/\text{SiON}$  with FSG passivation dielectric, its reliability issues, and the behavior of charge trapping. In addition to this chapter that is dedicated to introduce the reason of the high-k dielectrics on CMOS technology and systematic discuss the effects of fluorine incorporating on MOSFETs with high-k gate dielectric stacks, this thesis is organized as follows :

In chapter 02, we describe the experimental procedure for fabricating n-MOSFETs test devices with  $\text{HfO}_2/\text{SiON}$  gate stack as well as FSG passivation dielectric. Fluorine profile and amount was modulated by  $\text{CF}_4$ -plasma gas flow into  $\text{HfO}_2$  n-MOSFET. Then, show some basic electrical characteristics with and without FSG passivation dielectric, i.e., I-V and C-V characteristics, split C-V to obtain mobility, to evaluate the amount of interface states and bulk traps through charging pumping technique, and carrier separation to obtain leakage current mechanisms etc.

In chapter 03 presents the effects of FSG passivation dielectric on  $\text{HfO}_2$  n-MOSFET reliability. Charge trapping characteristics, i.e., static PBTI and dynamic trapping analysis with stress dependent high-k film quality, threshold voltage, interface state and high-k bulk trap density shifts as indicating factors will be discussed. Besides, hot carrier reliability of the  $\text{HfO}_2/\text{SiON}$  dielectric with the FSG passivation dielectric is also investigated. Finally, the lifetime extraction based on

DC stress suggests that the high-k dielectric with FSG passivation dielectric can provide optimistic results.

In chapter 04, we conclude with summaries of the experimental results above and suggest the possible future researches in this area.

## 1.6 Reference

- [1] R. H. Dennard, F. H. Gaenslen, H. Yu, V. L. Rideout, E. Basson, and A. R. Lebanc, "Design of Ion-Implanted MOSFET's with very small Physical Dimensions," *IEEE J. Solid State Circuits*, SC-9, p.256, 1974

- [2] G. E. Moore, "Progress in Digital Intergrated Eletronics," *IEEE IEDM Tech. Dig.*, p.11, 1975

- [3] A. Hori and B. Mizuno, "CMOS device technology toward 50nm region performance and drain architecture", *IEDM Tech. Dig.*, p. 641,1999.

- [4] B. E. Weir, P. J. Silverman, M. A. Alam, F. Baumann, D. Monroe, A. Ghetti, J.Bude, G. L. Timp, A. Hamad, and T. M. Oberdick, *Tech. Dig. IEDM*, p. 437 (1999).

- [5] M. Cao, P. V. Voorde, M. Cox, and W. Greene, *IEEE Elec. Dev. Lett.*, 19, 291 (1998).

- [6] C-Y. Hu, D. L. Kencke, and S. Banerjee, "Determining effective dielectric thickness of MOS structures in accumulation mode", *Appl. Phys. Lett.*, 66 (13), p. 1638 (1995).

- [7] The International Technology Roadmap for Semiconductor, Semiconductor Industry Association, San Francisco, CA, 2008.

- [8] Mark Bohr, "Intel's 90 nm Technology: Moore's Law and More", Intel Developer Forum Fall 2002

- [9] D. Park, Y. King, Q. Lu, T. King, C. Hu, A. Kalnitsky, S. Tay, and C. Cheng,"Transistor characteristics with Ta2O5 gate dielectric", *IEEE Elec. Dev. Lett.*, 19, p. 441,1998

- [10] S.-H. Lo, D. A. Buchanan, Y. Taur, W. Wang, "Quantum-Mechanical Modeling of Electron Tunneling Current from the Inversion Layer of Ultra-Thin Oxide nMOSFET's, " *IEEE Electron Device Lett.*, Vol. 18, pp.209, 1997.

- [11] J. H. Stathis, "Physical and predictive models of ultra thin oxide reliability in CMOS devices and circuits", *IEEE Transactions on Device and Materials Reliability*, Vol. 1, pp. 43 -59, 2001.

- [13] T. B. Hook, E. Adler, F. Guarin, J. Lukaitis, N. Rovedo, and K. Schruefer, *IEEE Trans. Electron Devices* 48, 1346 (2001)

- [13] D. Krüger, J. Dabrowski, P. Gaworzewski, R. Kurps, and K. Pomlun, *J. Appl. Phys.* 90, 3578 (2001)

- [14] T. B. Hook, E. Adler, F. Guarin, J. Lukaitis, N. Rovedo, and K. Schruefer, *IEEE Trans. Electron Devices* 48, 1346 (2001)

- [15] E. da Silva, Y. Nishioka, Y. Wang, and T. Ma, *IEEE Electron Device Lett.* 9,38 (1988).

- [16] P. Chowdhury, A. I. Chou, K. Kumar, C. Lin, and J. C. Lee, *Appl. Phys. Lett.* 70,37 (1997).

- [17] L. Tsetseris, X. J. Zhou, D. M. Fleetwood, R. D. Schrimpf, and S. T. Pantelides, "Dual role of fluorine at the Si–SiO<sub>2</sub> interface," *Appl. Phys. Lett.*, vol. 85, no. 21, p. 4950, Nov. 2004.

[18] A. Kazor, C. Jeynes, and I. W. Boyd, "Fluorine enhanced oxidation of silicon at low temperatures," *Appl. Phys. Lett.*, vol. 65, no. 12, pp. 1572–1574, Sep. 1994

[19] B. Cheng et al, "The impact of high-k gate dielectrics and metal gate electrodes on sub-100 nm MOSFETs" *IEEE Trans. Electron Devices*, Vol. 46, P. 1537, Jul. 1999.

[20] B. W. Busch, O. Pluchery, Y. J. Chabal, D. A. Muller, R. L. Opila, J. Kwo, E. Garfunkel, "Materials Characterization of Alternative Gate Dielectrics", *Materials Research Society Bulletin*, 27, pp. 206-221, 2002.

[21] Laegu Kang, Katsunori Onishi, Yongjoo Jeon, Byoung Hun Lee, Chang Seok Kang, Wen-jie Qi, Renee Nieh, Sundar Gopalan, Rino Choi, and Jack C. Lee, *IEDM Tech. Dig.*, p. 35, 2000.

[22] K. Onishi, Laegu Kang, Rino Choi, E. Dharmarajan, S. Gopalan, Y.J. Jeon, Chang Seok Kang, Byoung Hun Lee, R. Nieh, and J. C. Lee, "Dopant Penetration Effects on Polysilicon Gate HfO<sub>2</sub> MOSFET's", *VLSI Tech. Dig.*, p.131 , 2001.

[23] Shiraishi K, Yamada K, Torii K, Akasaka Y, Nakajima K, Kohno M, et al. Physics in Fermi level pinning at the PolySi/Hf-based high-k oxide interface. *Technical Digest International Symposium VLSI*, 2004, p.108-9

[24] M.V. Fischetti, D.A. Neumayer, E.A. Cartier, *J. Appl. Phys.* 90,4587 (2001).

[25] L. Yang, J.R. Watling, J.R. Barker, A. Asenov, in *Physics of Semiconductors*, vol. 27, ed. by J. Menedez, C.G. Van de Walle (AIP Press, 2005), p. 1497

[26] S. Inumiya et al., *Symp. VLSI Tech.*, 2003 p. 17.

[27] R. Degraeve, T. Kauerauf, A. Kerber, E. Cartier, B. Govoreanu, P. Roussel, L. Pantisano, P. Blomme, B. Kaczer, and G. Groeseneken, "Stress polarity dependence of degradation and breakdown of SiO<sub>2</sub>/High-k stacks", *IRPS*, p.23, 2003.

[28] K. Xiong, J. Robertson, M. C. Gibson, and S. J. Clark, *Appl. Phys. Lett.* 87, 183505 2005.

[29] H. H. Tseng, P. J. Tobin, E. A. Herbert, S. Kalpat, M. E. Ramon, L. Fonseca, Z. X. Jiang, J. K. Schaeffer, R. I. Hegde, D. H. Triyoso, D. C. Gilmer, *Tech. Dig. - Int. Electron Devices Meet.* 2005, 713.

[30] M. Inoue, S. Tsujikawa, M. Mizutani, K. Nomura, T. Hayashi, K. Shiga, J. Yugami, J. Tsuchimoto, Y. Ohno, and M. Yoneda, *Tech. Dig. - Int. Electron Devices Meet.* 2005, 425.

[31] K. I. Seo, R. Sreenivasan, P. C. McIntyre, and K. C. Saraswat, *Tech. Dig. - Int. Electron Devices Meet.* 2005,429.

[32] K. I. Seo, R. Sreenivasan, P. C. McIntyre, and K. C. Saraswat, *Tech. Dig. - Int. Electron Devices Meet.* 2005,429.

[33] M. Cao, P. V. Voorde, M. Cox, and W. Greene, "Boron diffusion and penetration in ultrathin oxide with poly-Si gate," *IEEE Electron Device Lett.*, vol. 19, no. 8, pp. 291–293, Aug. 1998.

[34] Y. Mitani, H. Satake, Y. Nakasaki, and A. Toriumi, "Improvement

of charge-to-breakdown distribution by fluorine incorporation into thin gate oxides," IEEE Trans. Electron Devices, vol. 50, no. 11, pp. 2221–2226, Nov. 2003.

[35] K. I. Seo, R. Sreenivasan, P. C. McIntyre, and K. C. Saraswat, Tech. Dig. - Int. Electron Devices Meet. 2005, 429.

| Year of Production                                                                                      | 2007  | 2008  | 2009  | 2010  | 2011  | 2012   | 2013   | 2014   | 2015   |

|---------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|--------|--------|--------|--------|

| MPU Printed Gate Length (nm)                                                                            | 54    | 47    | 41    | 35    | 31    | 28     | 25     | 22     | 20     |

| MPU Physical Gate Length (nm)                                                                           | 32    | 29    | 27    | 24    | 22    | 20     | 18     | 17     | 15     |

| Equivalent physical oxide thickness for bulk MPU/ASIC $T_{ox}$ (nm) for 3E20-doped poly-Si              | 1.3   | 1.2   | 1.2   | 1     | 0.68  | 0.54   | 0.41   |        |        |

| Equivalent physical oxide thickness for bulk MPU/ASIC $T_{ox}$ (nm) for metal gate                      |       |       | 1     | 0.95  | 0.88  | 0.75   | 0.65   | 0.6    | 0.53   |

| Gate dielectric leakage at 100 °C (A/cm <sup>2</sup> ) bulk high-performance                            | 180.0 | 450.0 | 650.0 | 830.0 | 900.0 | 1000.0 | 1100.0 | 1200.0 | 1330.0 |

| Drain extension $X_t$ (nm) for bulk MPU/ASIC                                                            | 11    | 11    | 11    | 11    | 11    | 10     | 9      | 8.5    | 7.7    |

| Allowable junction leakage for bulk MPU/ASIC (μA/μm)                                                    | 0.06  | 0.13  | 0.25  | 0.48  | 0.71  | 0.7    | 0.64   | 0.69   | 0.72   |

| Physical gate length low operating power (LOP) (nm)                                                     | 38    | 32    | 29    | 27    | 24    | 22     | 18     | 17     | 15     |

| Equivalent physical oxide thickness for bulk low operating power $T_{ox}$ (nm) for 1.5E20-doped poly-Si | 1.3   | 1.2   | 1.1   | 0.7   | 0.7   | 0.6    | 0.5    |        |        |

| Equivalent physical oxide thickness for bulk low operating power $T_{ox}$ (nm) for metal gate           |       |       | 1.1   | 1     | 1     | 0.9    | 0.8    |        |        |

| Gate dielectric leakage at 100°C for bulk (A/cm <sup>2</sup> ) LOP                                      | 40.0  | 78.0  | 86.0  | 95.0  | 100.0 | 110.0  | 140.0  |        |        |

| Physical gate length low standby power (LSTP) (nm)                                                      | 45    | 38    | 32    | 29    | 27    | 22     | 18     | 17     | 15.3   |

| Equivalent physical oxide thickness for bulk low standby power $T_{ox}$ (nm) for 1.5E20-doped poly-Si   | 1.9   | 1.2   | 1.1   | 1     | 0.9   | 0.8    | 0.7    |        |        |

| Equivalent physical oxide thickness for bulk low standby power $T_{ox}$ (nm) for metal gate             |       |       | 1.5   | 1.4   | 1.3   | 1.2    | 1.1    |        |        |

| Gate dielectric leakage at 100°C for bulk (A/cm <sup>2</sup> ) LSTP                                     | 0.067 | 0.081 | 0.094 | 0.110 | 0.120 | 0.130  | 0.150  |        |        |

| Poly-Si or metal gate electrode thickness (approximate) (nm)                                            | 50    | 46    | 40    | 36    | 32    | 28     | 26     | 22     | 20     |

Manufacturable solutions exist, and are being optimized

Manufacturable solutions are known

Interim solutions are known

Manufacturable solutions are NOT known

Table 1.1 2008 International Semiconductor Technology Roadmap predicts rapid reduction in the future technology trends for high performance logic, LOP, and LSTP devices.

Fig. 1.1 Power dissipation (dynamic + static power) with each generation

Fig. 1.2 The number of transistors in Intel processors increases exponentially over the years

Fig. 1.3 Measured and simulated  $I_g$ - $V_g$  characteristics under inversion conditions of  $\text{SiO}_2$  N-MOSFET devices

Fig. 1.4 By using high-k material to suppress gate direct-tunneling current.

Fig. 1.5 TEM and SIMS analysis of  $\text{Y}_2\text{O}_3$  high- $\kappa$  dielectric with capped and uncapped samples. Uncapped  $\text{Y}_2\text{O}_3$  sample shows additional interfacial layer due to oxygen diffusion.

Fig. 1.6 Schematic representation of factors contributing to carrier mobility degradation in a high- $\kappa$  oxide layer.

# CHAPTER 02

## Effects of FSG Passivation from Various CF4 Flow on the Properties of HfO2 Thin Films

### 2.1 Introduction

In order to improve device performance, thinner gate insulators are required for deep sub-micron metal semiconductor field effect transistors (MOSFETs). In this situation, high-k dielectrics are effective for suppressing gate leakage current. However, a major issue in applying high-k dielectrics is that it inherently possess a high density of structural defects, both intrinsic and process/integration related. Thus, Performance degradation for high-k is a concern, particularly for the low power applications where the high-k dielectric thickness is in the range containing high defect density. High defect density in the bulk of high-k gate dielectric and the interfaces in the gate stack structure are the major causes for bias temperature instability (BTI) of  $V_{th}$  instability (or reliability degradation) [1] as well as mobility degradation [2-3]. In order to eliminate these traps, a variety of nitridation techniques were proposed to incorporate nitrogen into the high-k films. Previous studies show that fluorine passivation is very robust and can be used to improve the reliability of high-k dielectric MOSFETs [4-6]. Several research studies have demonstrated the application of fluorine ion implantation techniques to improve the electrical characteristics of high-k dielectric MOSFETs

by eliminating inherent bulk traps. However, it is worth pointing out that an additional thermal annealing process is required to activate the fluorine ions and cure the damage created by fluorine ion implantation, which can result in forming thicker EOT.

In this work, we studied the defect passivation with fluorine in a hafnium oxide High-K gate dielectric with poly-si gate. The novel fluorinated gate stack device exceeds the BTI targets with sufficient margin. Fluorinated silicate glass (FSG) films have also been utilized in the intermetal dielectric (IMD) layer, and in the fluorinated gate dielectric for integrated circuit (IC) manufacturing technology [7-8]. It has been demonstrated that the addition of fluorine atoms into  $\text{SiO}_2$  can reduce the film dielectric constant to 3.2 or lower, which leads to reduced cross-talk, RC time delay, and power consumption. Using FSG film to serve as IMD can meet the requirement of multilevel interconnection in ultralarge-scale integrated circuit (ULSI) applications. Moreover, the fluorinated gate dielectric can improve the gate oxide/Si substrate interface immunity against hot-carrier impact, and exhibits better dielectric breakdown characteristics [9]. On the other hand, Kim et al. have proposed using the FSG film to serve as a diffusion source to introduce fluorine atoms into the poly-Si film [10].

## 2.2 Experimental Procedure

The experiment propose a simple and effective fluorine passivation technique that involves the use of a FSG passivation layer

embedded in the  $\text{HfO}_2/\text{SiON}$  gate dielectric. In the proposed fluorine passivation method, we introduce the fluorine atoms into the  $\text{HfO}_2$  bulk material and other interfaces from the FSG passivation layer.

### 2.2.1 Device Fabrication Flow

First, we use local oxidation of silicon (LOCOS) process was used for device isolation. n-MOSFET device was fabricated on 6-inch p-type Si with (1 0 0)-orientation. After removing the 300Å sacrificial oxide, RCA clean was performed with HF-dip last, and immediately followed by a conventional RTA at 800 °C for 30 sec in  $\text{N}_2\text{O}$  ambient to form about 1 nm interfacial oxynitride layer (SiON). Afterwards,  $\text{HfO}_2$  film of approximately 30Å was deposited by atomic vapor deposition (AVD<sup>TM</sup>) in an AIXTRON Tricent<sup>®</sup> system at a substrate temperature of 500 °C, followed by 600 °C  $\text{N}_2$  RTA for 30 sec in order to improve the film quality. The physical thickness of the SiON and  $\text{HfO}_2$  films was measured by optical N&K analyzer. A 200 nm poly-silicon was deposited by low pressure chemical vapor deposition (LPCVD). Subsequently, gate electrode was defined by I-line lithography stepper and etched by ECR etching system. After removing sidewall spacer, S/D extension implantation was implemented by As implantation. Spacer formation was carried out by plasma-enhance chemical vapor deposition (PECVD) and then S/D implantation was executed by Arsenic implantation. Rapid thermal anneal (RTA) was performed at 950 °C for 30 sec in  $\text{N}_2$  ambient to activate dopants.

Afterward, a 3000 Å-thick FSG passivation layer (or PMD dielectric) was deposited by PECVD at 300 °C with SiH<sub>4</sub>, N<sub>2</sub>O, and CF<sub>4</sub> as precursor gases (see Fig. 2-1). To investigate the effect of various fluorine contents on the device performances, the SiH<sub>4</sub> and N<sub>2</sub>O flow rates were adjusted at 4 and 60 sccm, and a variety of flow rates 10, 20, and 30 sccm were used to introduce CF<sub>4</sub> into the PECVD chamber and deposit various FSG passivation layers. The various CF<sub>4</sub> flow rates of 10, 20, and 30 sccm correspond to the FSG A, FSG B, and FSG C passivation layers, respectively. Table 2.1 lists the conditions of precursors to grow FSG passivation layers. For comparison, the control sample was deposited with a 3000 Å-thick conventional PECVD-TEOS passivation layer. Since the FSG film shows poor thermal stability and the fluorine atoms may diffuse out of the FSG film during post thermal annealing, a 1000 Å-thick SiN<sub>x</sub> capping layer on the FSG film was successively deposited by PECVD to improve the thermal stability of the FSG film and avoid the diffusion of fluorine atoms out of the FSG film [11]. After passivation layer formation and contact hole patterning. And Al-Si-Cu metallization was deposited by PVD system and then patterning. Finally, sintering process at 400 °C for 30 minutes in N<sub>2</sub> ambient is eventually executed to finish our novel fluorinated devices in this thesis.

The main process flow is summarized in Fig. 2-2 and schematic cross section of HfO<sub>2</sub>/SiON n-MOSFETs with FSG passivation layer is illustrated in Fig. 2-3.

## 2.2.2 Suitable Measurement Setup

The experimental setup for the I-V, C-V, charge pumping and reliability measurements of MOS device is illustrated in Fig. 2-4. Based on the PC controlled instrument environment, the complicated and long-term characterization procedures for analyzing the intrinsic and degradation behavior in MOSFET's can be easily achieved.

Current-voltage (I-V) and capacitance-voltage (C-V) characteristics were evaluated by a HP4156A precision semiconductor parameter analyzer and an HP4284 LCR meter, respectively. The capacitance equivalent thickness (CET) of the gate dielectrics was obtained from high frequency (100 KHz) capacitance-voltage (C-V) curve at strong inversion without considering quantum effect. The interface trap density ( $N_{it}$ ) was analyzed using the charging pumping method. A 1MHz for frequency and 10 ns for rising/falling time square pulse waveform provided by HP8110A with fixed amplitude level ( $V_A$ ) is applied to NMOS gate. We keep  $V_A$  at 1.2V while increase  $V_{Base}$  from -1.0V to 0.9V by step 0.1V, i.e., the base voltage varied from inversion to accumulation. The parameter analyzer HP4156A is used to measure the charge pumping current ( $I_{CP}$ ). Fig. 2-5 shows the configuration of measurement setup used in our charging pumping experiment. A MOSFET with gate area  $A_G$  gives the charging pumping current as Equation (2-1) :

$$I_{CP} = qA_G fN_{it} \quad (2-1)$$

Interface trap density could be extracted from the above equation. The total trap density increase,  $\Delta N_T$ , which includes the increase of interface trap density and bulk trap density was calculated from  $\Delta V_{Th}$  by assuming that the charge was trapped at the interface between the dielectric and the substrate. It expresses as follows Equation (2-2) :

$$\Delta N_T = \frac{C \Delta V_{Th}}{q A_G} \quad (2-2)$$

and bulk trap density also can be calculated as follows Equation (2-3) :

$$\Delta N_B = \Delta N_T - \Delta N_{it} \quad (2-3)$$

For mobility characterization, the electron mobility for n-MOSFETs was extracted using split C-V method .

## 2.3 Result and Discussions

### 2.3.1 Basic Device Characteristics

The C-V curves (100 KHz) of FSG A, B, C, and control samples are show in Fig. 2-6. The capacitance of the sample with  $CF_4$  gas introduced decreases compared to that of the as-deposited sample, which no obvious difference in C-V curves in substance. When  $CF_4$  gas flow rate is lower than 20 sccm, it indicates a slight increase of CET in FSG A and FSG B. However, the introduced  $CF_4$  gas is much more than the allowable F concentration, residual damage for the CET after sintering step can be observed. The resultant CET increment faster may be an excess amount of F incorporation into high-k film stacks [12-13] or the absorption of moisture from the atmosphere in the

plasma-deposited FSG film is the principle root-cause, which many studies indicated that the phenomenon of moisture ( $H_2O$ ) absorption in the plasma-deposited FSG film has been observed because the Si-F bonds present are highly reactive with moisture [14-15]. Fig. 2-7 was investigated with respect to CET and flat-band voltage ( $V_{FB}$ , not shown) [16] for the samples. We can see the fact that the  $V_{FB}$  has shifted to positive direction as the  $CF_4$  flow rate increases and EOT is also affected by the presence of F atoms. This is point out that decrease of positively charged traps or increase of negatively charged traps [17-19].

Fig. 2-8 shows the gate leakage current of n-MOSFET with  $HfO_2/SiON$  gate stack under both inversion and accumulation modes. It can obviously noted that with FSG passivation layer, the leakage current is significantly suppressed for both polarities. Specially, the reduction under normal operation condition, i.e., inversion mode, is around 40% of magnitude lower. One of the reasons for the exhibited gate leakage current reduction may be a thicker CET for two splits of fluorinated devices. Hence, it extrapolates that the  $CF_4$  gas flow rate even up to 30 sccm doesn't deteriorate gate leakage current, and on the contrary, the reduction extent of gate leakage current is dependent on the flow rate of  $CF_4$  gas introduced into FSG passivation from measurement data of Weibull distributions shown in Fig. 2-9. Fig. 2-10 demonstrates the transconductance ( $G_m$ ) as a function of gate voltage for both gate dielectrics. The  $G_m$  is normalized by CET

(Capacitance Equivalent Thickness), which is 37.9Å, 39.4Å, 42.1Å, and 38.3Å for FSG A, B, C, and control sample, respectively. The peak transconductance is 28%, 42%, and 67% for FSG passivation with respect to TEOS passivation. Fig. 2-11 shows the improved normalized linear drain-current  $I_D$  which FSG P.L. is 24% higher above than TEOS P.L. and the inset of subthreshold slope (S.S.) reduced 9.6% for the CF<sub>4</sub> introduced samples, indicating that fluorinated CMOS HfO<sub>2</sub> has better interface characterization. Previous study [20] on Zr-silicate indicates that electron transport in the channel can be degraded by the coulomb scattering of negative charges in the bulk film, and Fischetti et. al [21] also points out that electron mobility in the inversion layer is affected by remote phonon scattering due to ionic polarization in high-k films. Therefore, the peak transconductance degradation in HfO<sub>2</sub>/SiON stack is probably due to charges or traps in the bulk film, as evidenced by the positive shift in C-V curve in Fig. 2-6, even if the interface-state densities are kept to be small. Besides, as shown Fig. 2-12, the  $V_{Th}$  distribution is less affected by the addition of F for FSG A and B while a increased  $V_{Th}$  can be observed for FSG C, which also corresponding with the  $V_{FB}$  trend (not shown) due to negatively charged traps.

Fig. 2-13 presents the excellent output drive current characteristics ( $I_D - V_{DS}$ ) under various normalized gate biases ( $V_{GS} - V_{Th}$ ), which almost 12% enhancement in magnitude of  $I_{D,Sat}$

for FSG P.L. with respect to TEOS P.L.. The gate voltage has been normalized with respect to threshold voltage to minimize the effect of threshold voltage. We also understand that normalized  $I_{D,Sat}$  and transconductance max peak depends on the flow rate of  $CF_4$  gas or the amount of fluorine incorporated from Fig. 2-14. The improvements are believed to be intimately related not only to the better interface quality but also to the reduced bulk trap density. To quantify the interface state density by the CP current measurement, which the CP peak height is approximately proportional to the interface state density ( $N_{it}$ ) along the channel, Fig. 2-15 can be seen that the trend is quite consistent with that in subthreshold swing, as shown in inset of Fig. 2-11. Channel mobility is dependant on the nature of gate dielectric between Si substrate and high-k gate dielectric.  $CF_4$ -introduced high-k gate dielectrics suffer from CET increased whereas mobility can be enhanced shown in Fig. 2-16. The peak mobility for FSG C device is 7% higher than the control, and the high field mobility at 0.8MV/cm is 49% higher than the control, which is correlated with the higher  $G_{m,max}$  (see inset of Fig. 2-16) and higher output current characteristics. The electron mobility at 0.8MV/cm for the fluorinated device is 68% of  $SiO_2$  universal curve. Clearly, as the amount of introduced  $CF_4$  gas become elevated, peak mobility increasing with decreasing interface state density implying the weak and dangling bonds, associated with interface and trap states, are passivated and released strain bonds by fluorine atoms, leading to the

enhanced electrical characteristics show in Fig. 2-17.

Fig 2-18 indicates the subthreshold swing of devices with different passivation layers as a function of channel length. And we find that subthreshold swing for FSG P.L. shows the better interface states than TEOS P.L.. Thus, the FSG P.L. will improve the subthreshold swing in device. The relation between drain current and channel length for all splits of  $\text{HfO}_2/\text{SiON}$  gate stack n-MOSFET is shown in Fig. 2-19 and  $G_m$  is in Fig. 2-20. When channel length becomes shorter, the improvement is more obvious. Fig 2-21 shows the  $V_{Th}$ -roll-off characteristics with different passivation layers. When channel length is less than  $1\mu\text{m}$ ,  $V_{Th}$ -roll-off phenomenon is more serious for TEOS P.L. while the FSG devices effectively suppress this behaviour to the same extend with increasing the amount of  $\text{CF}_4$  gas flow. In short, it was found that all fundamental electrical properties, including the CET, flat-band voltage, threshold voltage, drive current, interface state density ( $N_{it}$ ), swing, mobility, gate leakage current, and short channel effect are almost non-degradation instead of surprise enhancement for device performance between the four splits with FSG and TEOS P.L..

### 2.3.2 Current Transport mechanism

Using the carrier separation method, the carrier type is investigated for the fresh devices. The carrier of gate leakage can be separated into holes and electrons. Fig 2-22 (a) and (b) are carrier

separation results for the TEOS sample under inversion and accumulation regions, respectively. It is shown that the S/D current that electrons tunnel through gate stack dominates the gate leakage for the inversion region while the substrate current that holes tunnel through gate stack dominates the gate leakage for the accumulation region. The carrier separation results for the FSG sample are shown in Fig. 2-23 (a). The case for the accumulation region is similar to the TEOS sample (see Fig. 2-23 (b)), i.e., holes from the substrate dominate the gate leakage. However, the case for the inversion region is different from the TEOS sample, where  $I_{SD}$  is obviously suppressed.

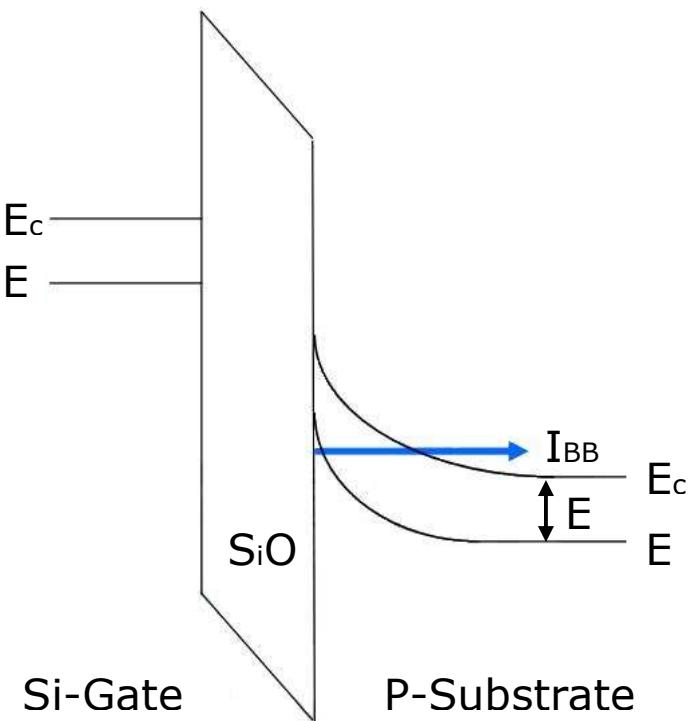

These trends can be explained by the band diagram shown in Fig. 2-24 (a) and carrier separation experiment shown in Fig. 2-24 (b). The substrate current  $I_{SUB}$  corresponds to the hole current from the gate, while the S/D current  $I_{SD}$  corresponds to the electron current from Si substrate under inversion region. Holes supply from the gate valence band in n-MOSFETs is limited by the generation rate of minority holes in  $n^+$  gate. On the other hand, the probability of carriers from S/D that tunnel through gate stack is strongly affected by tunneling distance and barrier height of  $\sim 1.0$  nm interfacial oxynitride layer. As a result of the asymmetry of the  $\text{HfO}_2/\text{SiON}$  band structure, it is more difficult for holes to tunnel through gate stack, as compared to electrons. Consequently, the current through the gate stack should be smaller for holes, as compared to electrons. In

n-MOSFETs, electron current from the channel is the predominant injection current under stressing. The leakage component under accumulation region could also be explained by band diagrams shown in Fig. 2-25 (a), and the current component flow in carrier separation experiment is shown in Fig. 2-25 (b). In addition, we can see that the magnitude of the leakage current in inversion is larger than that in accumulation. A plausible explanation can be understand from the asymmetric band diagram's point of view.

Fig. 2-26 (a) and (b) show gate current  $I_g$  as a function of  $V_g$  for the HfO<sub>2</sub>/SiON gate stacks measured at several different temperatures up 100 °C in inversion and accumulation regions, respectively, for two different passivation layers. The current is temperature dependent that increases with increasing temperature. This implies that the conduction mechanism of gate current is trap-related, i.e., trap-assisted tunneling (TAT), Frenkel-Poole, etc.

Base on the equation of Frenkel-Poole (F-P) :

$$I \propto V \exp\left(\frac{2a\sqrt{V}}{T} - \frac{q\phi_B}{k_B T}\right) \quad (2-4)$$

$$J = B * E_{ox} \exp\left(\frac{-q(\phi_B - \sqrt{qE_{ox} / \pi\epsilon_H\epsilon_0})}{k_B T}\right) \quad (2-5)$$

$$\ln\left(\frac{J}{E_{ox}}\right) = \frac{q\sqrt{q / \pi\epsilon_H\epsilon_0}}{k_B T} \sqrt{E_{ox}} - \frac{q\phi_B}{k_B T} \quad (2-6)$$

Where B is a constant in terms of the trapping density in the HfO<sub>2</sub> film,  $\phi_B$  is the barrier height,  $E_{ox}$  is the electric field in HfO<sub>2</sub> film,  $\epsilon_0$

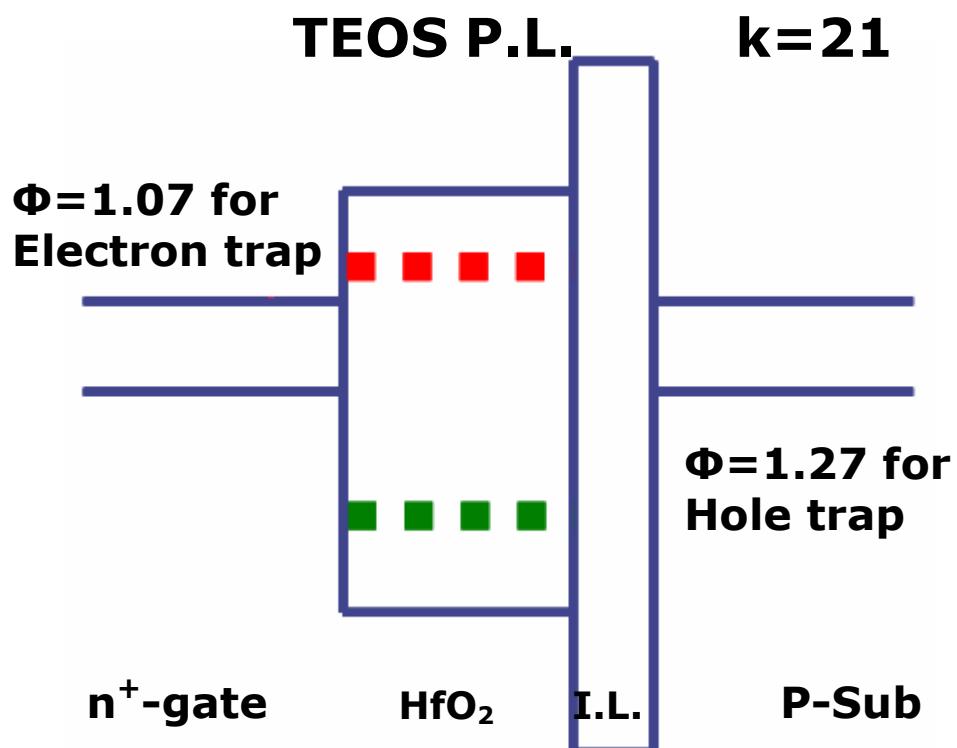

is the free space permittivity,  $\epsilon_h$  is  $\text{HfO}_2$  dielectric constant,  $k_B$  is Boltzmann constant, and T is the temperature measured in Kelvin. Fig. 2-27 shows the F-P plot for the source/drain current in inversion region. Fig. 2-28 shows the F-P plot for the substrate current in inversion region. The solid lines are fitting curves for all temperatures. In the high voltage  $I_{SD}$  and  $I_{SUB}$ , an excellent linearity for each current characteristic can be obtained, indicating that FSG and TEOS passivation layers exhibit the F-P conduction mechanism for the gate leakage current in nature. The barrier height  $\phi_B$  and the dielectric constant  $\epsilon_h$  of  $\text{HfO}_2/\text{SiON}$  gate stacks can be calculated from the intercept of y axis and the slope of the fitting curves according to Equation (2-6). The  $\epsilon_h$  value is found to be around 21 for the TEOS sample and around 23 for the FSG sample. On the other hand, the fitting parameters for the hole and electron barrier heights are 1.34eV and 1.12eV, respectively, for the FSG sample, as compared to 1.27eV and 1.07eV for the TEOS sample. Note that the barrier height for electrons has changed from 1.07eV for TEOS to 1.12eV for FSG sample, and for holes has changed from 1.27eV for TEOS to 1.34eV for FSG sample. This indicates that the trap position has moved closer to the conduction and valence band of the poly-si gate after FSG P.L. process. The band diagrams are shown in Fig. 2-29 (a) and (b) for the TEOS and FSG P.L. sample, respectively. We consider the case when the injected carriers flow across  $\text{HfO}_2/\text{SiON}$  by hopping via the trap

sites with energy barrier  $\phi_B$ , whose value depends on the fabrication process [22]. This experimental results indicate that the position of traps level in the FSG sample can be deeper than the TEOS sample, and the energy barrier  $\phi_B$  for electrons is clearly lower than that for holes about 0.2eV in both samples.

## 2.4 GIDL Effect on Off-State Leakage

Gate-induced drain leakage (GIDL) is attributed to the band-to-band tunneling (BBT) process taking place in the deep-depleted drain region underneath the gate oxide. Electron-hole pairs are generated by the tunneling of valence band electrons into the conduction band and subsequently collected by the drain and substrate separately. The schematic energy band diagram of the gate-drain overlap region is shown in Fig. 2-30. The BBT ( $I_{BBT}$ ) could be simplified as Equation (2-7) [23] :

$$I_{BBT} = AE_s \exp\left(-\frac{B}{E_s}\right) \quad (2-7)$$

where A is a constant,  $E_s$  and B can be approximated as :

$$E_s = \frac{V_{DG} - 1.2}{3T_{ox}} \quad (2-8)$$

$$B = \frac{8\pi\sqrt{2m^*}}{3qh} \sqrt{E_g} \quad (2-9)$$

where h is Plank's constant,  $m^*$  is the effective mass, and  $E_g$  is the energy bandgap. From these equations, it should be noted that

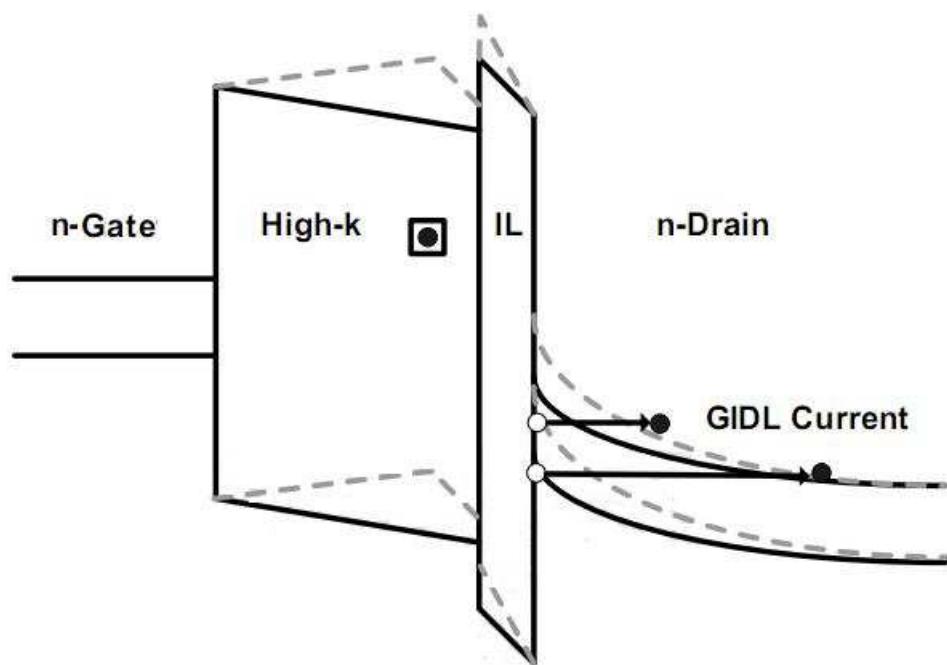

BBT current is dependent on  $E_g$ . Therefore, if  $E_g$  decreases, the band-to-band tunneling current ( $I_{BBT}$ ) increases. Although Hf-based high-k dielectrics have been investigated to reduce gate leakage current, it has been observed that bulk traps significantly enhance the GIDL current in devices with high-k dielectrics [24]. Hence, bulk traps enhanced gate-induced leakage (BTE-GIDL) current will be found to improve for the devices with FSG passivation layer.

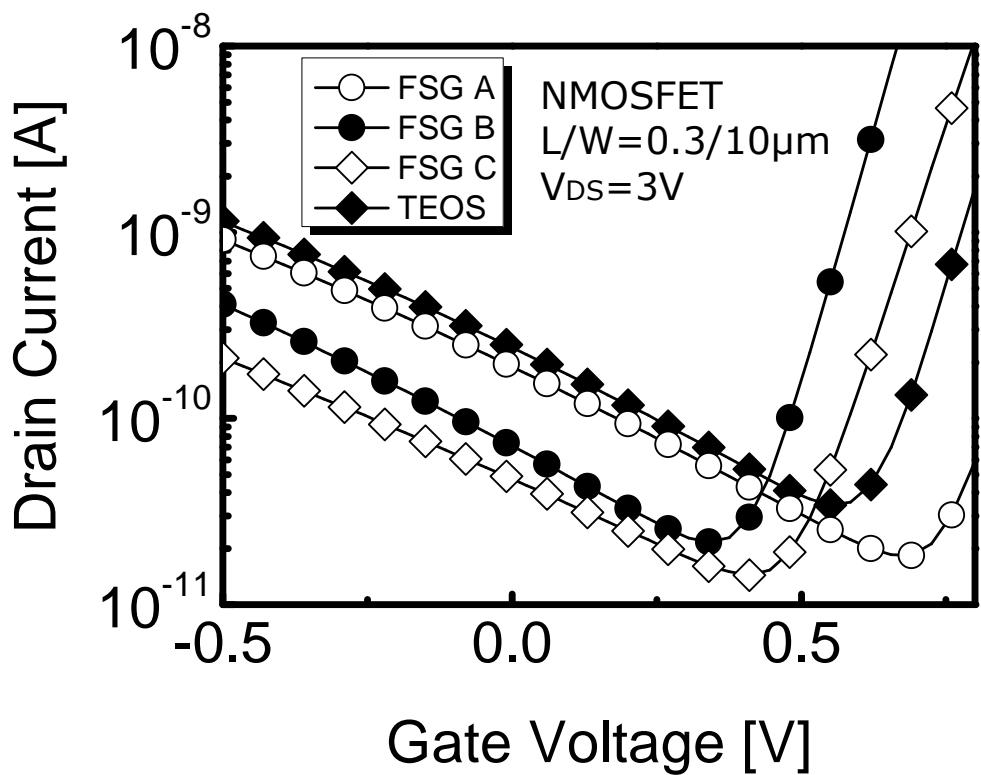

To suppress the BTE-GIDL, the role of charge trapping in high-k film should be understood in detail. As shown in Fig. 2-31, the band diagrams before and after electron trapping are denoted by the solid line and the dashed line, respectively. At low  $V_{DG}$  (TAT mechanism), the much lower electron barrier height for poly-gate/high-k than that for hole at high-k/I.L. interface, electron injected from poly-gate dominates trapping mechanism. The charges induced by injected electrons raise the bands, which decrease the tunneling distance and increase the GIDL current. The higher number of bulk traps in high-k that combines with the narrower tunneling distance give rise to higher BTE-GIDL current. At high  $V_{DG}$  (BBT mechanism), both electrons and holes are injected into the high-k dielectric, the band position is less bended due to recombination. Another possible mechanism is attributed to the trap-assisted tunneling from traps located at the remote high-k/I.L. interface [24]. Fig. 2-32 shows the  $I_D - V_{GS}$  transfer characteristics of all splits at larger drain biasing ( $V_{DS} = 3V$ ).

We can observe that the GIDL current decreases for three splits of fluorinated devices. Especially, the GIDL improvement of FSG C samples was more obvious. The results indicate that the reduction of bulk traps in FSG C sample is more than the others due to more fluorine incorporation into  $\text{HfO}_2/\text{SiON}$  effectively passivating defect, resulting in less electron trapping in  $\text{HfO}_2/\text{SiON}$  contributing to BTE-GIDL. Therefore, the improvement of GIDL on off-state leakage current can be observed for the fluorinated devices.

## 2.4 Summary

In this chapter, a novel fluorinating technique method for high-k dielectric passivation, using a FSG process as n-MOSFETs passivation layer was presented. We have performed a systematical investigation of electrical characteristics. Significant device performance improvement in devices with FSG P.L. were found, such as the excellent subthreshold swing, increased transconductance, higher current drive, improved channel electron mobility, and alleviated SCE etc., as compared to the control TEOS sample. As shown in Fig. 2-33, for FSG P.L., the number of interface states by using charge pumping method can be diminished that is attributed to the passivated interface traps by the incorporation of fluorine atoms generated from  $\text{CF}_4$  gas in deposition process of PECVD chamber. Specially, the presence of fluorine in the FSG devices lead to a decrease in the numbers of bulk traps from intrinsic hysteresis effect

[25-26] shown in Table 2-2, which summarizing the impact of the FSG passivation layer for HfO<sub>2</sub>/SiON gate stack n-MOSFETs. Experimental results show a good correlation between the bulk trap density and the BTE-GIDL. It was observed that incorporating fluorine into HfO<sub>2</sub>/SiON gate stack to minimize the bulk traps could effectively reduce the BTE-GIDL.

## 2.5 References

- [1] S. Zafar, A. Callegari, E. Gusev, and M. V. Fischetti, "Charge trapping related threshold voltage instabilities in high permittivity gate dielectric stacks," *J. Appl. Phys.* Vol. 93, pp.9298, 2003

- [2] E. Gusev, D. A. Buchanan, and E. Cartier, "Ultrathin high-K gate stacks for advanced CMOS devices", *IEDM Tech. Dig.*, pp451, 2001

- [3] H. -J. Cho, C. Y. Kang, C. S. Kang, R. Choi, Y. H. Kim, M. S. Akbar, C. H. Choi, S. J. Rhee, and J. C. Lee, "The effects of nitrogen in HfO<sub>2</sub> for improved MOSFET performance", *IEEE semiconductor Device Research Symposium*. pp68, 2003.