# 國 立 交 通 大 學 電子工程學系電子研究所 博士 論 文

先進互補式金氧半電晶體及快閃式記憶元件中單 一電荷效應之統計性研究 Statistical Study of Single Charge Phenomena in Advanced CMOS and Flash Memory

研究生:邱榮標

指導教授 : 汪大暉 教授

中華民國 一〇二 年 二月

## 先進互補式金氧半電晶體及快閃式記憶元件中單一電荷效

## 應之統計性研究

Statistical Study of Single Charge Phenomena in Advanced

## CMOS and Flash Memory

| 研 | 究 | 生 | : | 邱榮標 | Student : Jung-Piao Chiu |

|---|---|---|---|-----|--------------------------|

|   |   |   |   |     |                          |

指導教授:汪大暉

Advisor : Tahui Wang

國立交通大學

電子工程學系 電子研究所

Submitted to Department of Electronics Engineering and Institute of Electronics College of Electrical and Computer Engineering National Chiao Tung University in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in

**Electronics Engineering**

February 2013 Hsinchu, Taiwan, Republic of China

先進互補式金氧半電晶體及快閃式記憶元件中單一電荷效應之統計性研究

學生:邱榮標

#### 指導教授:汪大暉博士

國立交通大學 電子工程學系 電子研究所

#### 摘 要

本篇論文主要著重在單電子效應於先進互補式金氧半電晶體(advanced CMOS)及快閃式記憶元件(flash memory)之應用。高介電閘極氧化層(high-k)之可 靠性議題,如電壓溫度引致不穩定(BTI)、隨機電報雜訊(RTN)之研究,亦有所探 討。更利用蒙地卡羅模擬進一步驗證理論及實驗。

第一章首先描述本論文中單電子效應之應用研究成果。首先探討高介電閘極 材料(high-k)金氧半電晶體元件中,藉由量測NBTI加速測試中,單一電荷捕捉及 釋放所造成的臨界電壓及特徵時間變化,進一步探討在奈米級元件的可靠性議 題。接下來吾人討論於pMOSFET中,同為單電子效應之RTN及NBTI的異同, 並利用 reaction-diffusion(RD)模型及蒙地卡羅方法模擬NBTI 缺陷之產生。此外, 吾人於此篇論文最後,討論於快閃式記憶元件中寫入載子對於RTN之影響,主 要探討浮動閘極(floating gate)、平面(planar)及鰭狀(FinFET)氮化矽(SONOS)快閃 式記憶元件中,載子寫入前後RTN之變化。

在第二章中,吾人探討了在小面積 high-k 元件中,NBTI 造成之總臨界電壓 變化(ΔV<sub>t</sub>)分佈及其形成原因。吾人量測大量小面積元件之單電荷產生特徵時間及 其造成之臨界電壓變化。吾人發現單電荷產生之特徵時間有數 decade 之廣,並

i

提出用 reaction-diffusion(RD)模型中之反應活化能角度詮釋此一現象,更進一步 由特徵時間分佈萃取出反應活化能分佈。最後吾人提出一統計模型,此模型基於 RD 模型之基礎加入反應活化能分佈及單電荷造成之臨界電壓變化分佈。最後以 蒙地卡羅模擬重現實驗ΔV<sub>t</sub>分佈及其和 NBTI 操作時間的關係。

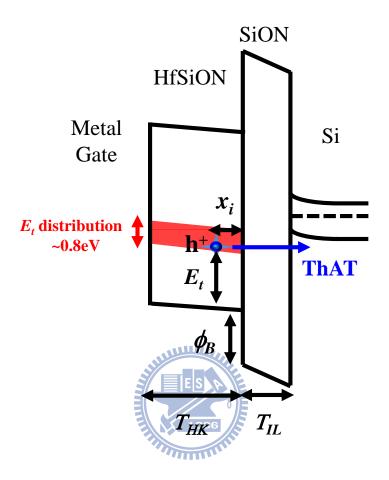

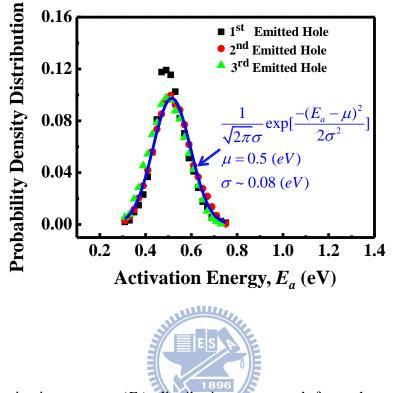

第三章延續第二章之主題,探討小面積 high-k 元件中,NBTI 造成之總臨界 電壓變化(ΔV<sub>t</sub>)分佈及其形成原因。不同於其他可靠度議題,NBTI 在操作電壓移 除後有一特殊之回復現象。利用類似前一章的方法,吾人量測大量小面積元件之 單電荷逸散特徵時間及其造成之臨界電壓變化。吾人以「熱助穿隧」模型解釋, 並由缺陷能量分佈、空間分佈及反應活化能分佈進一步探討並萃取反應活化能分 佈。最後提出一統計模型,以熱助穿隧模型為基礎加上反應活化能分佈,完整解 釋並預測回復現象造成之ΔV<sub>t</sub>分佈及其和回復時間之關係。

## ESA

單電子效應的應用除了 NBTI之外,另一個重要的可靠度議題就是 RTN。這 兩種現象之機制確有相似之處,近年來甚至有人認為 NBTI 是 RTN 在特殊偏壓 條件下的產物。在第四章,吾人量測並比較製程產生之 RTN 缺陷(fresh RTN)、 NBTI 操作產生之 RTN 缺陷(post-NBTI stress RTN)、NBT 測試過程中之單電荷引 致臨界電壓變化,結果發現 NBTI 測試過程中之平均單電荷引致臨界電壓變化量 大於製程產生之缺陷。為此吾人用 RD 模型進行 3D 模擬,結果顯示因為 NBTI 測試產生之缺陷位置較容易出現在主要電流滲透路徑,進而產生較大之單電荷引 致臨界電壓變化。也間接證明 NBTI 之缺陷為新產生之缺陷,和製程產生之 RTN 缺陷不同。

在第五章中,吾人探討 SONOS 元件的寫入電荷對於 RTN 引致臨界電壓變化 量的影響。吾人量測並模擬 RTN 在浮動式閘極(floating gate)、平面式 SONOS、 鰭式 SONOS 之振幅大小,並記錄其在寫入/抹除前後的變化。研究發現 RTN 在

ii

平面式 SONOS 寫入/抹除前後有大量的變化,而浮動式閘極幾乎在寫入/抹除前 後擁有同樣大小之 RTN。主要是因為 SONOS 中氮化矽層儲存之電荷為一離散的 狀態,使寫入/抹除前後之電流滲透路徑改變,而浮動式閘極因為電荷儲存層為 導體,故 RTN 之大小不會因為寫入/抹除動作而有變化。最後吾人發現當 SONOS 由平面式結構進入鰭式結構, RTN 在寫入/抹除前後之變化量會被大幅度的壓 抑,主要是因為電流導通路徑的限縮,及高度之對稱性使得寫入電荷對於電流導 通路徑擁有等量的影響。

在第六章中, 吾人研究了 nanowire-like 結構中的 RTN 振幅。在較寬的通道 寬度元件中,電流導通路徑主要由隨機參雜決定, RTN 振幅也由缺陷位置和電 流滲透路徑決定。但在 nanowire-like 結構,電流路徑被侷限於一個一維的通道, 一個參雜僅能改變區域導通瓶頸(導電率), 而無法改變導通路徑。在本章中, 吾 人嘗試提出一個模型來描述 nanowire-like 結構的 RTN 振幅分佈。模型顯示 RTN 振幅的機率分佈遵守 Poisson 分佈, 吾人亦利用蒙地卡羅模擬來證實理論。此外, 如上一章提到的,由於在 SONOS 元件中寫入載子和通道參雜對於電流滲透路徑 有一些類似的特性,此一理論亦可延伸並用於未來 nanowire-like 結構的 SONOS 快閃式記憶元件。

最後於第七章,吾人將對本論文做個總結。

關鍵字:蒙地卡羅模擬,先進互補式金氧半電晶體,氮化矽快閃式記憶元件,浮 動式閘極快閃式記憶元件,高介電閘極氧化層,負電壓溫度引致不穩 定,隨機電報雜訊,反應-擴散模型,熱助穿隧模型,單電荷產生,單 電荷散逸,反應活化能萃取,缺陷位置萃取,電流通道滲透效應,布瓦 松分佈

iii

## Statistical Study of Single Charge Phenomena in Advanced CMOS and Flash Memory

Student : Jung-Piao Chiu

Advisor : Dr. Tahui Wang

Department of Electronics Engineering & Institute of Electronics National Chiao Tung University

#### ABSTRACT

This thesis will focus on single charge phenomena characterization and its applications to advanced CMOS and non-volatile flash memory. The reliability issues, such as negative bias temperature instability (NBTI) and random telegraph noise (RTN) in advanced gate dielectric (high-*k*), are studied statistically. Monte Carlo simulations are also performed to corroborate our model and experiment data.

In Chapter 1, applications of single charge phenomena statistics are firstly addressed. The second and the third chapters are the investigations of threshold voltage shifts arise from NBTI stress and post-NBTI recovery, respectively. And the fourth chapter is the study of NBTI and RTN amplitude distributions in high-k gate dielectric pMOSFETs. The program charge effect on RTN amplitude and its device structural dependence in SONOS flash memory is investigated in Chapter 5. Finally, an RTN amplitude distribution model is proposed in Chapter 6.

In Chapter 2, origins of a NBTI induced  $\Delta V_t$  distribution in small-area HfSiON gate dielectric pMOSFETs are explored and characterized. We measure individual

trapped hole creation times and corresponding threshold voltage shifts during NBTI stress in a large number of devices. Wide dispersion of trap creation characteristic times in several decades is observed, which we attribute to an activation energy distribution in the reaction-diffusion (RD) model. We extract an activation energy distribution including a local electric field effect from measured characteristic times. A statistical model for an NBTI  $\Delta V_t$  distribution by employing the RD model and convolving extracted activation energy and a single trapped hole induced  $V_t$  shift is developed. Our model reproduces measurement results of an overall NBTI induced  $\Delta V_t$  distribution and its stress time evolutions well.

In Chapter 3, NBTI trapped charge characteristics and recovery mechanisms are examined by a statistical study of individual trapped charge emissions in small-area HfSiON/metal gate pMOSFETs. We measure trapped charge emission times in NBTI recovery in a large number of devices. The characteristic time distributions of the first three emitted holes are obtained. The distributions can be well modeled by using a thermally-assisted tunnel (ThAT) detrapping model. NBTI trapped charge energy and spatial distributions and its activation energy distribution in the ThAT model are discussed and extracted. We develop a statistical NBTI recovery  $\Delta V_t$  model based on the ThAT and an extracted activation energy distribution. Our model can reproduce a recovery  $\Delta V_t$  distribution and its temporal evolutions in small-area devices very well.

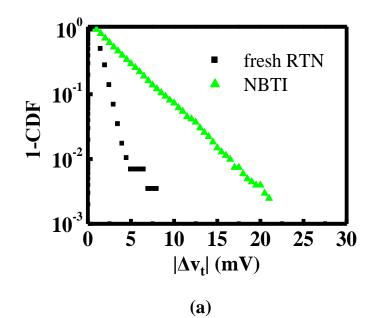

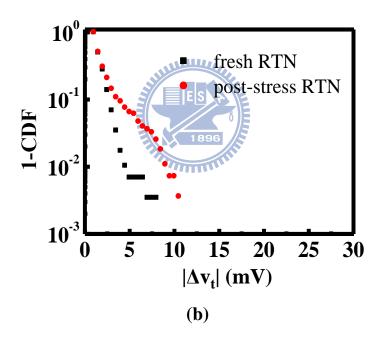

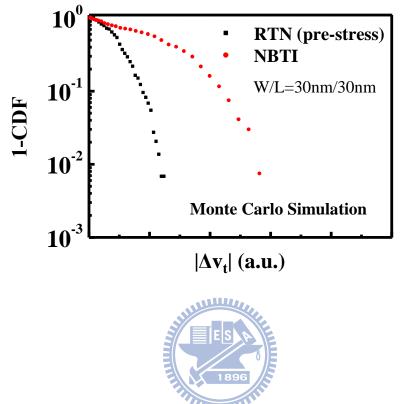

RTN and NBTI stress induced threshold voltage (V<sub>t</sub>) fluctuations in high-k gate dielectric and metal-gate pMOSFETs are investigated in Chapter 4. We measured RTN amplitude distributions before and after NBTI stress. RTN in post-stressed devices exhibits a broader amplitude distribution than the pre-stress one. In addition, we trace a single trapped charge induced  $\Delta V_t$  in NBTI stress and find that the average  $\Delta V_t$  is significantly larger than a  $\Delta V_t$  caused by RTN. A 3D atomistic simulation is performed to compare a single-charge induced  $\Delta V_t$  by RTN and NBTI. In our simulation, the probability distribution of a NBTI trapped charge in the channel is

calculated from the reaction-diffusion model. Our simulation confirms that the NBTI induced  $\Delta V_t$  indeed has a larger distribution tail than RTN due to a current-path percolation effect.

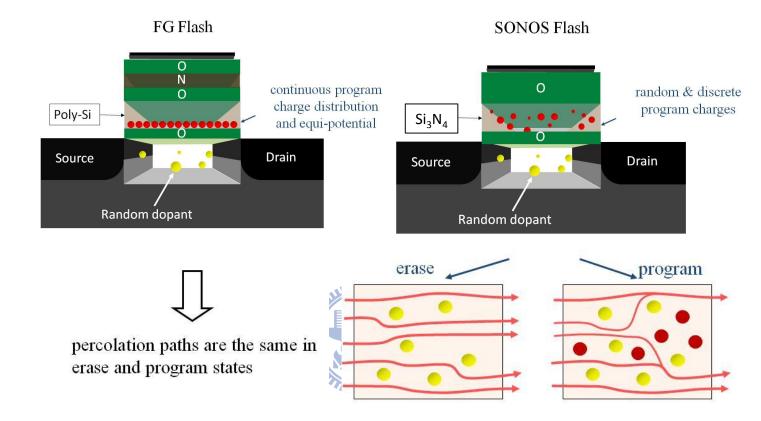

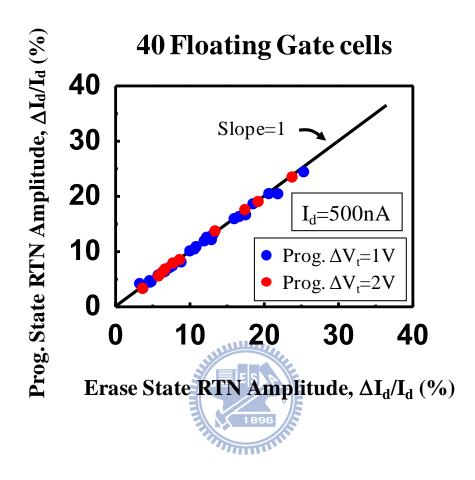

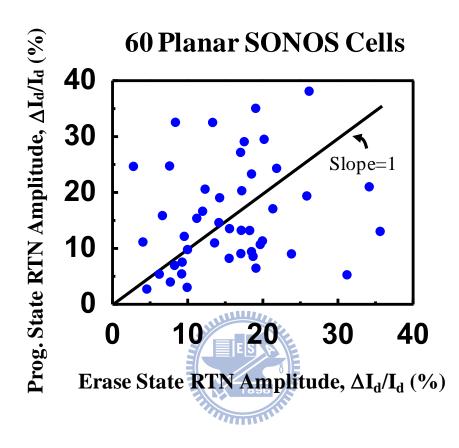

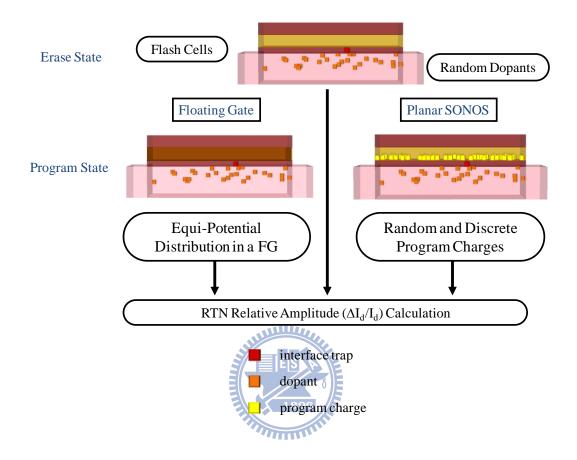

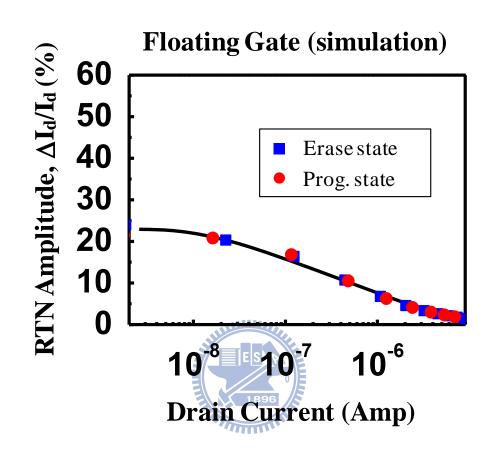

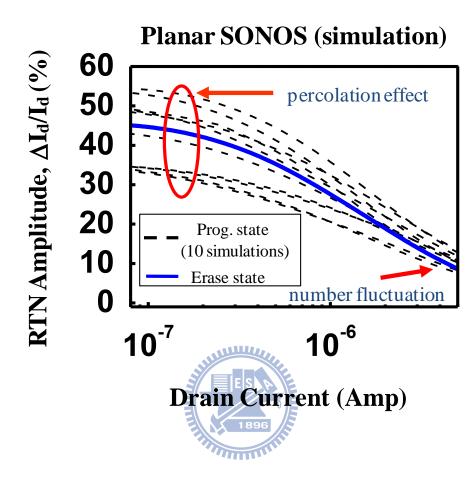

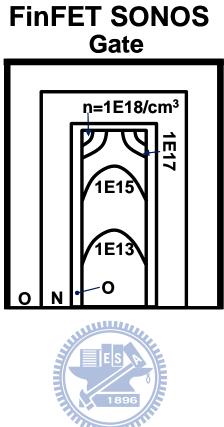

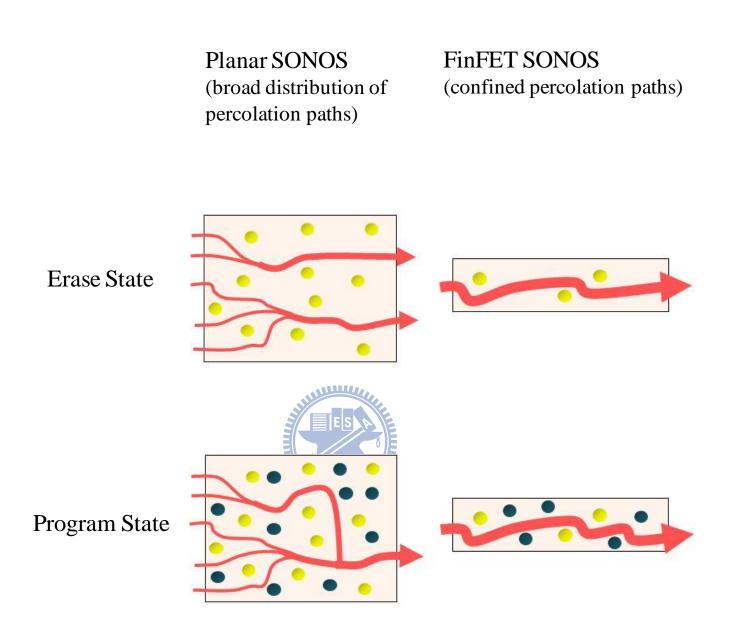

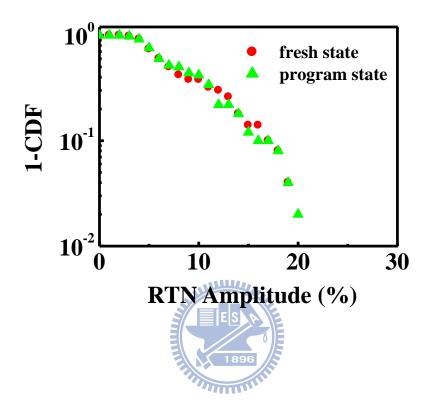

Nitride program charge effect on the amplitude of RTN in SONOS flash cells is investigated in Chapter 5. We measure and simulate RTN amplitudes in floating gate flash, planar SONOS, and FinFET SONOS cells. We find that a planar SONOS has a wide spread in RTN amplitudes after programming while a floating gate flash cell has identical RTN amplitudes in erase and program states. The spread of program-state RTN in a planar SONOS is attributed to a current-path percolation effect caused by random discrete nitride charges. The RTN amplitude spread can be significantly reduced in a surrounding gate structure, such as FinFET SONOS, due to a higher degree of symmetry in a program charge distribution.

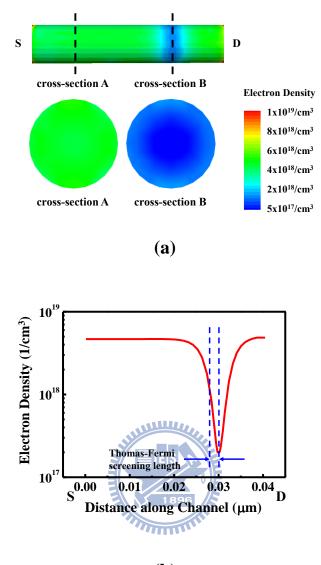

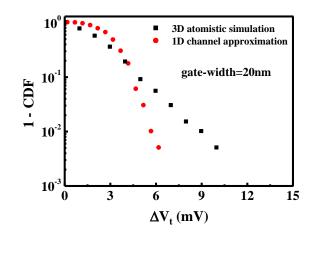

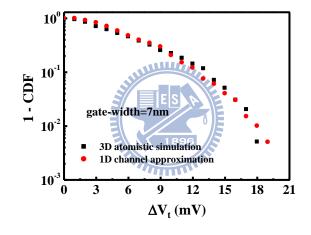

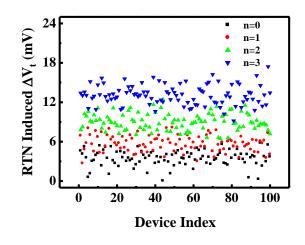

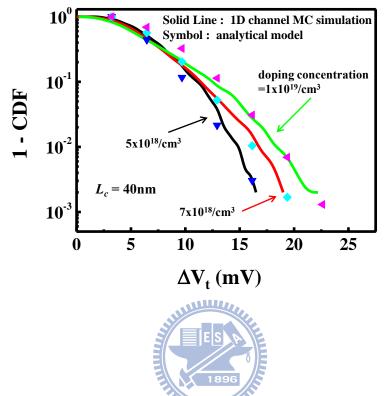

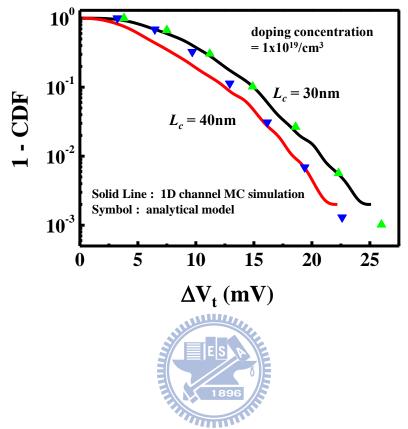

In Chapter 6, amplitudes of RTN in MOSFETs possessing a nanowire-like channel are explored and modeled analytically. In large gate width MOSFETs, conducting current paths are modulated by random substrate dopants and large-amplitude RTN is attributed to a current path percolation effect. In ultra-thin body and narrow gate width MOSFETs, a current flow is physically confined to a one-dimension-like channel. A dopant charge does not alter a current path, but only modulates a local channel conductivity near the dopant. In this work, we attempt to derive an analytical RTN model for circuit simulation based on random dopant induced local conductivity modulation in a one-dimensional channel. We make an assumption that RTN amplitudes are linearly dependent on the number of dopants in the vicinity of an RTN trap. An influence range of a dopant charge is evaluated approximately from the Thomas-Fermi screening theory. The validity of this assumption is examined by numerical device simulation or experiment. Our model shows that RTN induced threshold voltage shifts exhibit a Poisson distribution. A Monte Carlo analysis of RTN induced  $\Delta V_t$  by using a 3D device simulator is performed to compare with our model. Reasonably good agreement between our model and the Monte Carlo RTN simulation is obtained for various doping concentrations and channel lengths.

Conclusions are finally made in Chapter 7.

Keyword: Monte Carlo simulation, advanced CMOS, SONOS, floating-gate flash, high-*k*, NBTI, RTN, reaction diffusion (RD) model, thermally-assisted-tunneling (ThAT) model, single charge creation, single charge emission, activation energy extraction, percolation effect, trap position extraction, Poisson distribution

#### ACKNOWLEDGEMENT

I would first like to express my deep gratitude to my advisor, Prof. Tahui Wang. His insightful guidance and encouragement are indispensable to the accomplishment of this dissertation.

I also show my appreciation to all of the committee members for their invaluable comments and suggestions. Moreover, I would like to acknowledge Dr. Chih-Sheng Chang and all the members in ATRD for their kindly support during my part-time job at TSMC.

During my study, many important people have influenced me. I would like to thank Dr. C. J. Tang, Dr. H. C. Ma, and Dr. C. C. Cheng for their guidance during my initial stage of Ph.D. study. In particular, the assistance in executing routine measurements and simulations from Mr. T. Y. Lin, Mr. C. Y. Wang, Mr. S. S. Liang Mr. M. W. Wang, Mr. H. D. Hsieh and Mr. C. W. Li is also greatly appreciated. I am also indebted to the Wang and Chung group members of Emerging Device and Technology Lab, who had made life fun. Thanks to all who accompany me, their encouragement made me become more aggressive.

Scholarship from the department of electronics engineering at NCTU and from ZyXEL is deeply acknowledged for easing my financial pressure. I would also appreciate the National Science Council for providing me the travel grants to present papers in international conferences.

Finally, I would present my deepest love to my parents. Their love is the most important power supporting me. This dissertation is dedicated to them.

#### 謝誌

首先,感謝指導教授汪大暉博士。沒有汪教授的教誨與鼓勵,這本論文將無法完成。

特別感謝論文口試委員在百忙之中給予寶貴的建議與指教。另外,在台灣積 體電路製造公司工讀期間,前瞻技術研發部部經理張智勝博士及所有全體同仁在 研究與工作上的大力協助,在此由衷感謝。

在求學過程中,感謝學長唐俊榮博士、馬煥淇博士以及鄭志昌博士不吝分享 所學,讓我快速進入狀況。此外,感謝學弟東陽、志宇、書祥、明瑋、泓達以及 啟偉分擔實驗及模擬的工作。因為有你們的協助,使得這本論文更加充實。同時 也感謝前瞻元件與技術實驗室所有成員,他們為我的博士班生涯增色許多。感謝 所有陪伴過我的人,你們的支持鼓勵是我前進的動力。

感謝國立交通大學電子研究所及朱順一合動科技提供獎學金,減輕我的經濟 壓力。在此向國科會(National Science Council)致上誠摯的謝意,提供經費補助, 讓我前往國際會議發表論文。

最後,我要感謝長久以來支持我的家人,他們的愛是我的重要支柱。這本論 文,獻給他們。

ix

## CONTENTS

| Chinese Abstract<br>English Abstract<br>Acknowledgement<br>Contents<br>Table Captions<br>Figure Captions<br>List of Symbols |                                                                                                                           |        |

|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--------|

| Chapter 1                                                                                                                   | Introduction                                                                                                              | 1      |

| 1.1                                                                                                                         | Backgrounds                                                                                                               | 1<br>3 |

| 1.2                                                                                                                         | Description of the Problem                                                                                                |        |

| 1.3                                                                                                                         | Organization of this Dissertation                                                                                         | 4      |

| Chapter 2                                                                                                                   | Statistical Characterization of Individual Charge Trapping Times and Modeling of $\Delta V_t$ Distribution by NBTI Stress | 10     |

| 2.1                                                                                                                         | Preface                                                                                                                   | 10     |

| 2.2                                                                                                                         | Characterization of Individual NBTI Trapped Charge Creation                                                               | 12     |

|                                                                                                                             | 2.2.1 Devices and Measurement Setup                                                                                       | 12     |

|                                                                                                                             | 2.2.2 Single Charge Creation Induced $\Delta v_t$ Distribution                                                            | 13     |

|                                                                                                                             | 2.2.3 Characteristic Times for Trapped Charge Creation                                                                    | 13     |

|                                                                                                                             | 2.2.4 Activation Energy Distribution                                                                                      | 15     |

| 2.3                                                                                                                         | Modeling of an NBTI Induced $\Delta V_t$ Distribution                                                                     | 16     |

|                                                                                                                             | 2.3.1 Measured NBTI Induced $\Delta V_t$ Distribution                                                                     | 16     |

|                                                                                                                             | 2.3.2 Monte Carlo Simulation Flow                                                                                         | 17     |

|                                                                                                                             | 2.3.3 Monte Carlo Simulation Results and Discussion                                                                       | 18     |

| 2.4                                                                                                                         | Summary                                                                                                                   | 19     |

| Chapter 3                                                                                                                   | Statistical Characterization and Modeling of a $\Delta V_t$ Distribution and Its Temporal Evolutions in NBTI Recovery     | 34     |

| 3.1                                                                                                                         | Preface                                                                                                                   | 34     |

| 3.2                                                                                                                         | Statistical Characterization of NBTI Recovery                                                                             | 35     |

|                                                                                                                             | 3.2.1 Single Charge Emission Induced $\Delta v_t$ Distribution                                                            | 35     |

|                                                                                                                             | 3.2.2 Trapped Charge Emission Times                                                                                       | 36     |

|                                                                                                                             | 3.2.3 Trapped Charge Spatial and Energy Distributions                                                                     | 37     |

|                                                                                                                             | 3.2.4 Activation Energy Distribution                                                                                      | 39     |

|                                                                                                                             | 3.2.5 Reproducible Feature of NBTI Recovery                                                                               | 41     |

|                                                                                                                             | 3.2.6 Comparison with Charge Trapping/De-trapping<br>Model                                                                | 41     |

| 3.3                                                                                                                         | Modeling of a Recovery $\Delta V_t$ Distribution                                                                          | 43     |

|                                                                                                                             | 3.3.1 Measured NBTI Induced $\Delta V_t$ Distribution                                                                     | 43     |

|                                                                                                                             | 3.3.2 Monte Carlo Simulation Flow                                                                                         | 43     |

|                                                                                                                             | 3.3.3 Monte Carlo Simulation Results and Discussion                                                                       | 44     |

| 3.4        | Summary                                                                                                                    | 44  |

|------------|----------------------------------------------------------------------------------------------------------------------------|-----|

| Chapter 4  | A Comparative Study of NBTI and RTN Amplitude<br>Distributions in High-k Gate Dielectric pMOSFETs                          | 61  |

| 4.1        | Preface                                                                                                                    | 61  |

| 4.2        | Measurement Results and Discussion                                                                                         | 62  |

|            | 4.2.1 Devices and Measurement Setup                                                                                        | 62  |

|            | 4.2.2 Distribution of Single Charge Induced v <sub>t</sub> shifts                                                          | 62  |

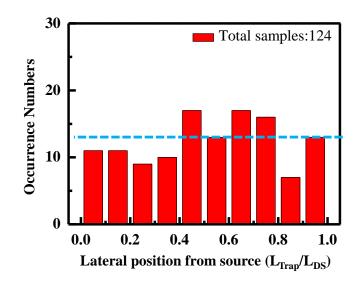

|            | 4.2.3 Trap Position Extraction                                                                                             | 63  |

| 4.3        | Simulation of a NBTI Stress Induced $\Delta v_t$                                                                           | 63  |

| 110        | 4.3.1 3D atomistic Monte Carlo Simulation Method                                                                           | 63  |

|            | 4.3.2 Results and Discussion                                                                                               | 64  |

| 4.4        | Summary                                                                                                                    | 66  |

| Chapter 5  | Program Charge Effect on Random Telegraph Noise<br>Amplitude and Its Device Structural Dependence in<br>SONOS Flash Memory | 76  |

| 5.1        | Preface                                                                                                                    | 76  |

| 5.2        | Program Charge Effect on RTN Amplitude in Floating Gate<br>and SONOS Flash Memory                                          | 77  |

|            | 5.2.1 Measurement of RTN Amplitude in MLC Flash                                                                            | 77  |

|            | 5.2.2 Statistics Result of Program-state and Erase-state<br>RTN                                                            | 78  |

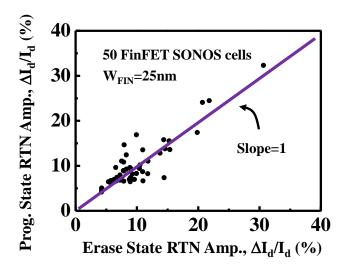

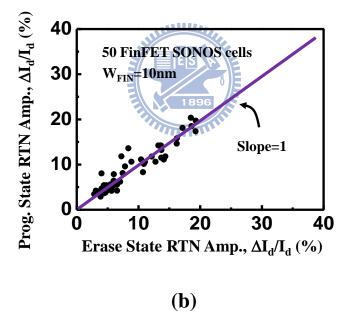

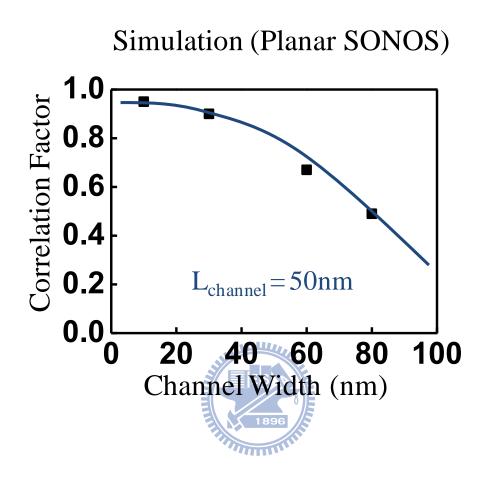

|            | 5.2.3 Correlation Factor for Program-state and Erase-state<br>RTN                                                          | 78  |

|            | 5.2.4 P/E Cycle Dependence of RTN                                                                                          | 79  |

|            | 5.2.5 3D Atomistic Simulation of RTN                                                                                       | 79  |

| 5.3        | Device Structural Dependence on RTN in SONOS Flash                                                                         | 80  |

|            | Memory                                                                                                                     |     |

|            | 5.3.1 Program Charge Effect on RTN in FinFET SONOS                                                                         | 80  |

|            | 5.3.2 Degree of Inversion in FinFET SONOS                                                                                  | 81  |

|            | 5.3.3 Channel Width Effect on Program Charge Induced                                                                       | 81  |

|            | Percolation Effect                                                                                                         |     |

| 5.4        | Summary                                                                                                                    | 82  |

| Chapter 6  | Physical Origin and Analytical Modeling of RTN<br>Amplitude Distribution in MOSFETs with a Nanowire<br>Like Channel        | 103 |

| 6.1        | Preface                                                                                                                    | 103 |

| 6.2        | One-Dimensional Channel RTN Simulation                                                                                     | 105 |

| 6.3        | Analytical RTN Amplitude Distribution Model                                                                                | 108 |

| 6.4        | Results and Discussion                                                                                                     | 109 |

| 6.5        | Summary                                                                                                                    | 110 |

| Chapter 7  | Conclusions                                                                                                                | 121 |

| References |                                                                                                                            | 124 |

### xi

Vita Publication List 139 140

## TABLE CAPTIONS

#### Chapter 2

Table 2.1Comparison of trapped charge creation and emission characteristics in NBTI24stress and NBTI recovery. *i* is a sequence number in trapped charge creation in<br/>NBTI stress or trapped charge emission in NBTI recovery.24

### Chapter 5

Table 5.1Measured RTN correlation factors in FG flash, planar SONOS and FinFET89SONOS cells.

#### FIGURE CAPTIONS

#### **Chapter 1**

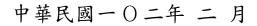

- Fig. 1.1Projections of gate leakage current and equivalent oxide thickness (EOT) from6ITRS roadmap for low-standby-power applications.

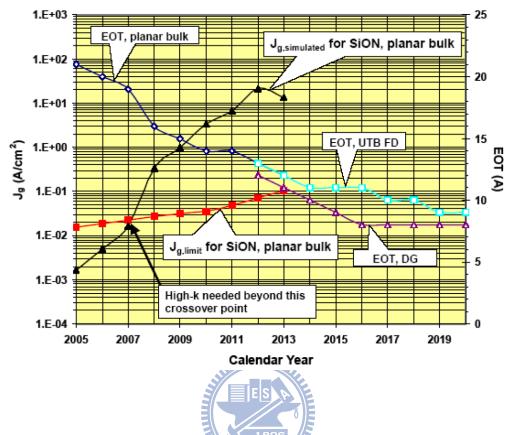

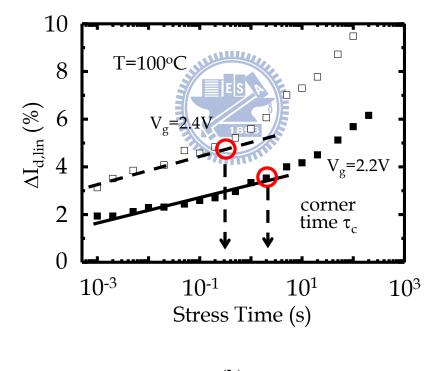

- Fig. 1.2 A typical two-level RTN waveform resulting from electron capture/emission at 7 an oxide trap.  $\tau_c$  and  $\tau_e$  are electron capture and emission times, respectively.  $\Delta I_d$  is RTN amplitude.

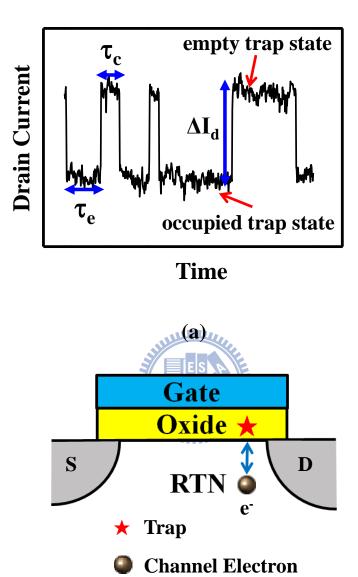

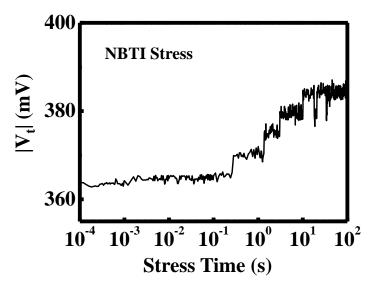

- Fig. 1.3 Typical  $V_t$  traces during NBTI stress (a) and recovery (b). Each step-like 8 "quantum jump" represents a single charge capture/emission.

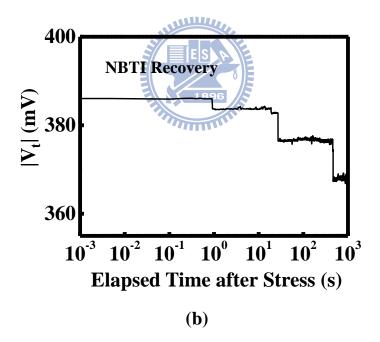

- Fig. 1.4 (a) Estimation of threshold voltage shift as a function of process node [1.39] (b) 9 measured V<sub>t</sub> distribution of a 4-level MLC with level enlarged [1.39] and (c) noise distributions of 90nm, 70nm, and 50nm flash memory technologies [1.40].

#### **Chapter 2**

Juli

- Fig. 2.1 Comparison between  $I_d$  degradation traces in (a) nowadays (b) previous devices. 20

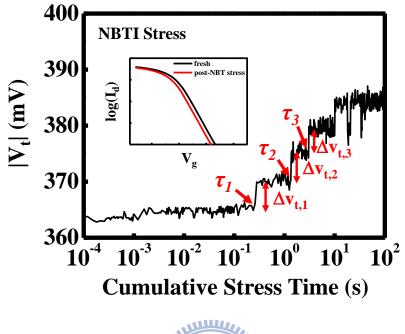

- Fig. 2.2 Example  $V_t$  trace in NBTI stress in a high-k gate dielectric pMOSFET.  $\tau_1$ ,  $\tau_2$  21 and  $\tau_3$  are the 1<sup>st</sup>, the 2<sup>nd</sup> and the 3<sup>rd</sup> trapped hole creation times.  $\Delta v_{t,1}$ ,  $\Delta v_{t,2}$  and  $\Delta v_{t,3}$  are the 1<sup>st</sup>, the 2<sup>nd</sup> and the 3<sup>rd</sup> trapped hole induced threshold voltage shifts. The inset shows subthreshold  $I_d$ – $V_g$  before and after NBTI stress.

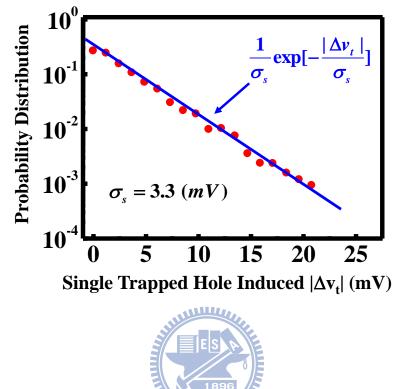

- Fig. 2.3 The probability density function of a single trapped charge (hole) induced 22 threshold voltage shift. The solid line represents an exponential fit.

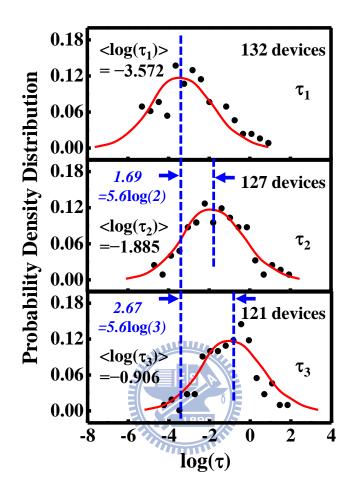

- Fig. 2.4 The probability distribution of a trapped hole creation time in NBTI stress 23 collected from about 130 devices.  $\tau_1$ ,  $\tau_2$  and  $\tau_3$  are the 1<sup>st</sup>, the 2<sup>nd</sup> and the 3<sup>rd</sup> trapped hole creation times, respectively. The solid line represents a Gaussian fit.

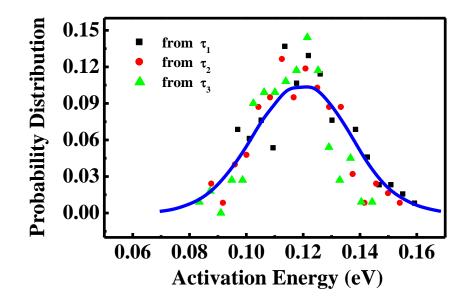

- Fig. 2.5 Effective activation energy distributions extracted from measured trap creation 25 times,  $\tau_1$ ,  $\tau_2$  and  $\tau_3$ . The solid line represents a Gaussian-distribution fit to the  $E_{eff}$  translated from  $\tau_1$ .

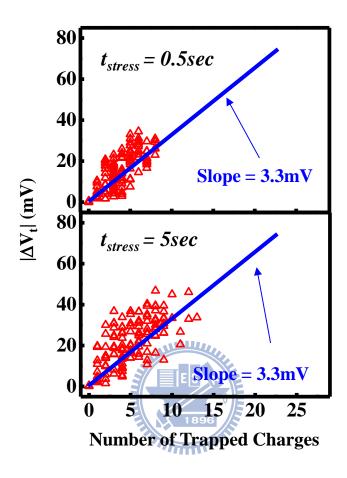

- Fig. 2.6 NBTI induced  $\Delta V_t$  versus number of trapped holes in a device at a stress time of 26 0.5sec (a) and 5sec (b). Each data point represents a device. The slope of a straight line represents an average  $\Delta v_t$  caused by a single trapped hole.

xiv

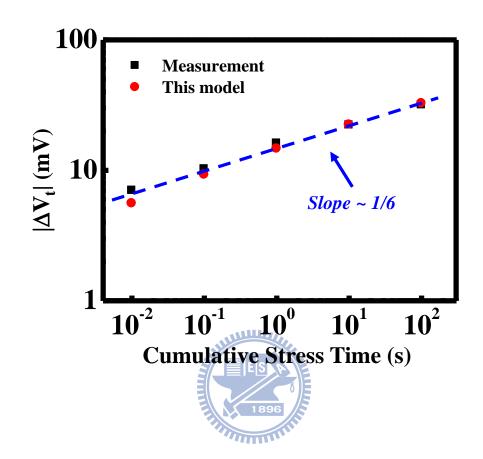

- Fig. 2.7 The mean of the  $\Delta V_t$  distribution versus NBTI stress time from measurement 27 and from our model.

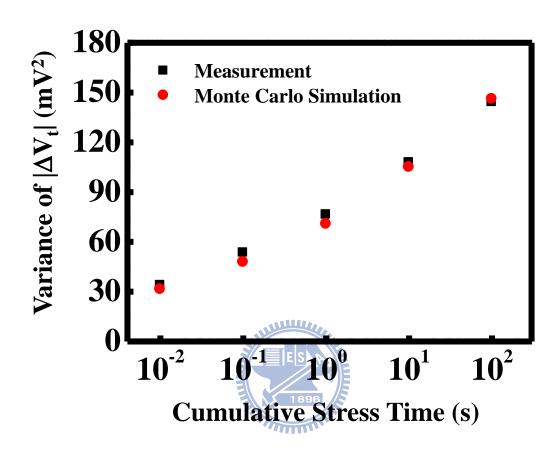

- Fig. 2.8 The variance of the  $\Delta V_t$  distribution versus NBTI stress time from measurement 28 and from our model.

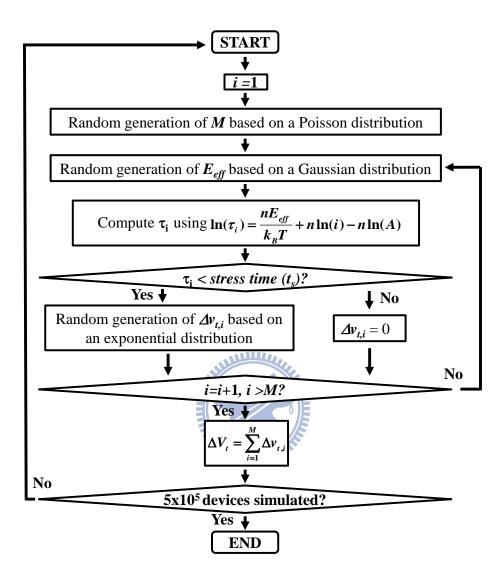

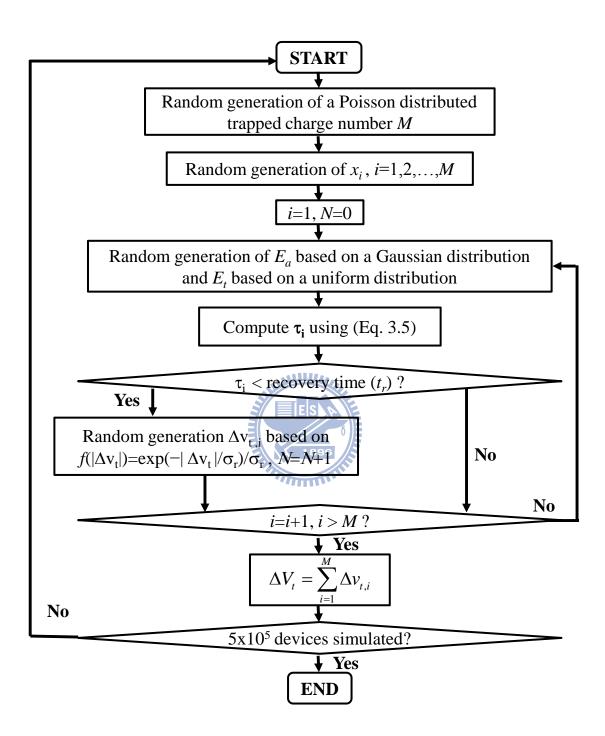

- Fig. 2.9 A Monte Carlo simulation flowchart. *M* is the number of precursors in a device. 29 A precursor density of  $1 \times 10^{12}$  cm<sup>-2</sup> is assumed.

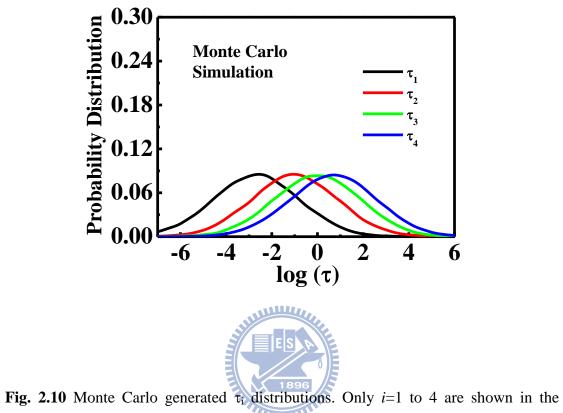

- Fig. 2.10 Monte Carlo generated  $\tau_i$  distributions. Only *i*=1 to 4 are shown in the figure. 30

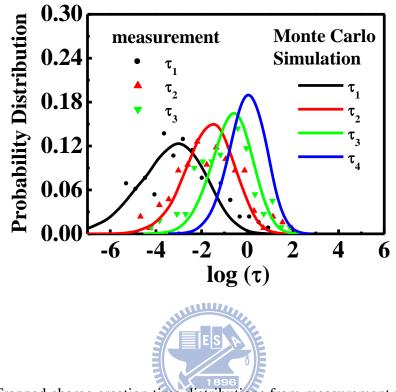

- Fig. 2.11 Trapped charge creation time distributions from measurement (symbols) and 31 from Monte Carlo simulation (lines) after the re-ordering. The Monte Carlo simulated  $\langle \log(\tau_2) \rangle \langle \log(\tau_1) \rangle$  is 1.68 and  $\langle \log(\tau_3) \rangle \langle \log(\tau_1) \rangle$  is 2.67.

- Fig. 2.12 Complementary cumulative distribution functions (1-CDF) of NBTI induced 32  $\Delta V_t$  from measurement and from our model. The stress time is 0.01sec, 1sec and 100sec, respectively. The inset shows the probability distributions of  $\Delta V_t$  from measurement and this model.

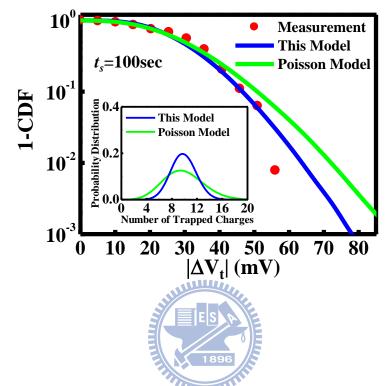

- Fig. 2.13 Comparison of NBTI induced  $\Delta V_t$  distributions (1-CDF) calculated from this 33 model and from the Poisson model. The dots are measurement result. The inset shows trapped charge number distributions from the two models. The stress time is 100 sec.

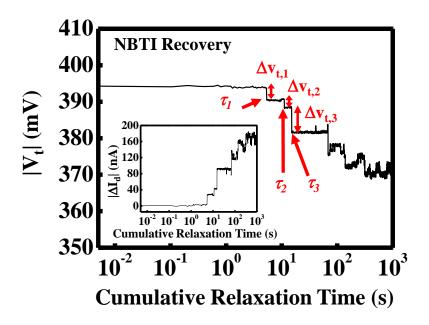

- Fig. 3.1 Example  $\Delta I_d$  and  $V_t$  traces in NBTI relaxation.  $\tau_1$ ,  $\tau_2$  and  $\tau_3$  are the 1<sup>st</sup>, the 2<sup>nd</sup> 46 and the 3<sup>rd</sup> trapped hole emission times, respectively.  $\Delta v_{t,i}$  (i=1,2,3) represents a single emitted charge induced threshold voltage shift.

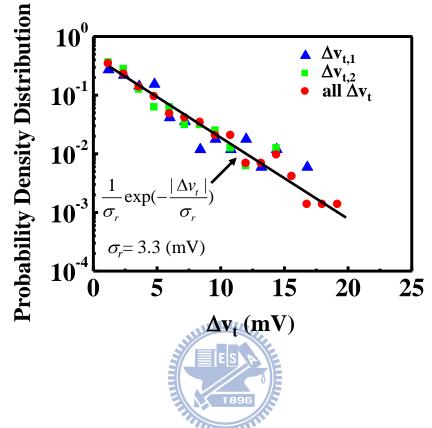

- Fig. 3.2 The magnitude distributions of  $\Delta v_{t,1}$ ,  $\Delta v_{t,2}$  and all collected  $\Delta v_{t,i}$  from NBTI 47 recovery traces in 170 high-k/metal gate pMOSFETs. The solid line represents an exponential fit.

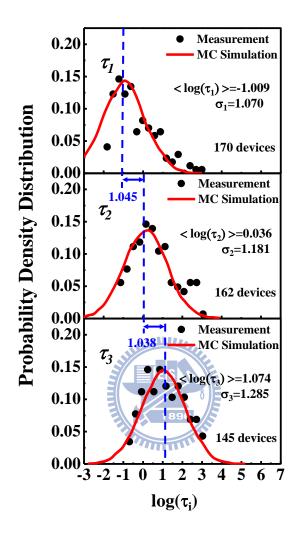

- Fig. 3.3 The probability density distributions of a trapped charge (hole) emission time in 48 a log( $\tau$ ) scale.  $\tau_1$ ,  $\tau_2$  and  $\tau_3$  are the 1<sup>st</sup>, the 2<sup>nd</sup> and the 3<sup>rd</sup> trapped hole emission times, respectively. The mean ( $\langle log(\tau_i) \rangle$ ) and the standard deviation ( $\sigma_i$ ) of the distributions are indicated in the figure. The symbols are measurement result and the solid lines are from Monte Carlo simulation. A Monte Carlo simulation procedure is given in Fig. 3.10.

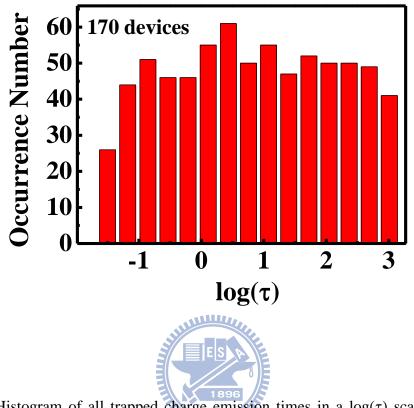

- Fig. 3.4 Histogram of all trapped charge emission times in a  $log(\tau)$  scale collected from 49 170 devices. The occurrence number distribution is rather uniform in a period from  $10^{-2}$ s to  $10^{3}$ s.

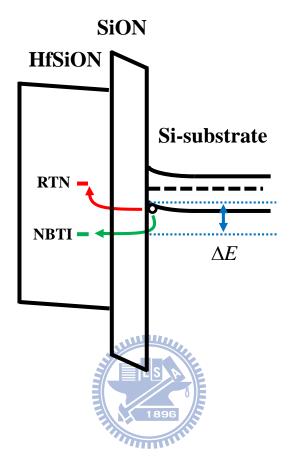

- Fig. 3.5 Schematic representation of a band diagram of a high-k/metal gate pMOSFET 50 in relaxation.  $x_i$  and  $E_t$  represent a trapped charge position and energy.

- Fig. 3.6 Activation energy  $(E_a)$  distributions extracted from the  $\tau_1$ ,  $\tau_2$  and  $\tau_3$ , 51 respectively.  $\tau_0$  in Eq. (4) is chosen such that the mean of the  $E_a$  is about 0.5eV. The solid line is a Gaussian-distribution fit.

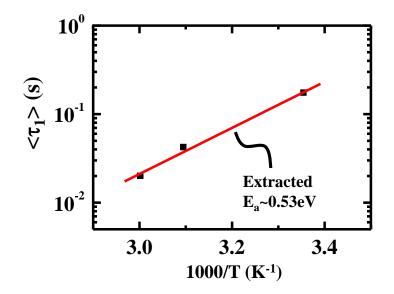

- Fig. 3.7 The dependence of  $\langle \tau_1 \rangle$  on recovery temperature. The extracted activation 52 energy is about 0.5eV. Each data point is an average of ten readings.

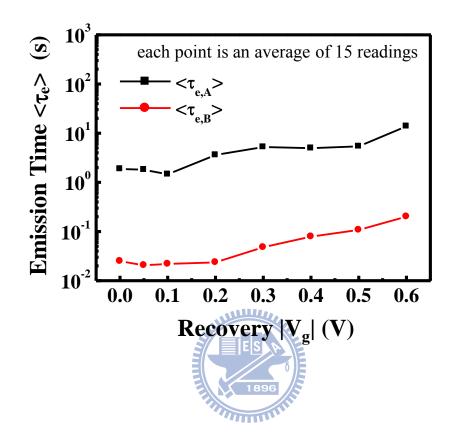

- Fig. 3.8 Dependence of trapped electron emission times on recovery gate voltage. 15 53 measurements are made for each recovery  $V_g$  to take average.

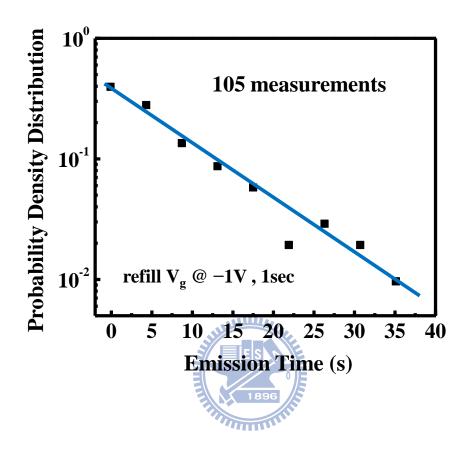

- Fig. 3.9 A PDF plot of an emission time measured from an individual trap. 54

- Fig. 3.10 An illustration of difference of trap energy between NBTI and RTN defects. 55

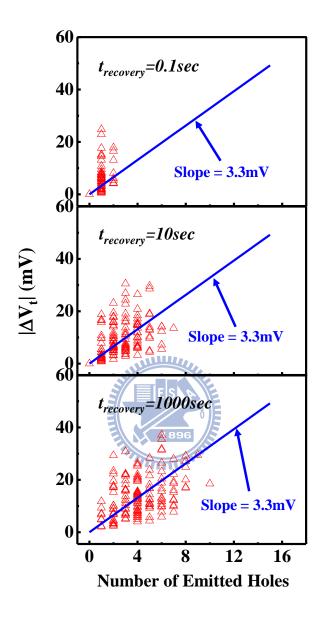

- Fig. 3.11 A total  $V_t$  shift  $(\Delta V_t)$  versus number of emitted trapped holes in a device at a recovery time of 0.1s, 10s and 1000s. Each data point represents a device. The slope of a straight line represents an average  $\Delta v_t$  caused by a single trapped hole emission.

- Fig. 3.12 The evolution of  $\Delta V_t$  with a recovery time. The solid line represents an average 57 of measured  $\Delta V_t$  traces in 170 devices. The symbols are the mean of Monte Carlo simulated  $\Delta V_t$  distributions. A logarithmic time dependence of  $\Delta V_t$  is obtained.

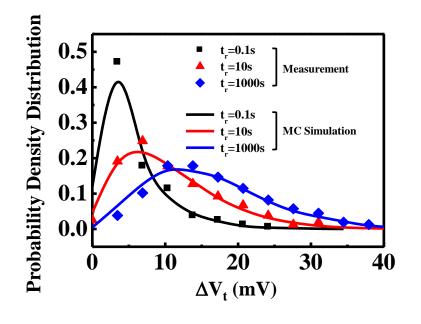

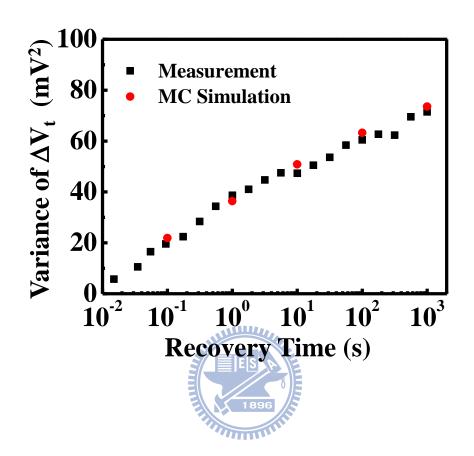

- Fig. 3.13 Simulation flowchart of a Monte Carlo based  $\Delta V_t$  distribution model for NBTI 58 recovery in small area devices.

- Fig. 3.14 The probability density distributions of NBTI recovery  $\Delta V_t$  in 80nmx30nm 59 pMOSFETs from measurement and from a Monte Carlo simulation. The recovery time is 0.1s, 10s, and 1000s.

- Fig. 3.15 The variance of a recovery  $\Delta V_t$  distribution versus a recovery time in 60 80nmx30nm pMOSFETs from measurement and from a Monte Carlo simulation.

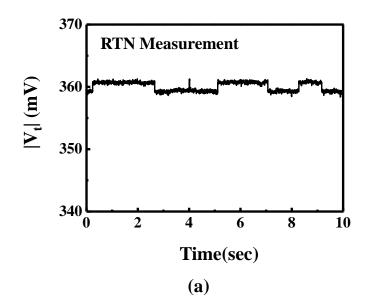

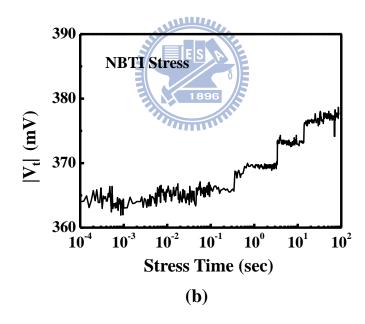

- Fig. 4.1 (a) RTN measured at  $V_D$ =-0.05V and a target I<sub>D</sub> of -500nA. The V<sub>t</sub> waveform 68 is obtained from the measured drain current divided by a transconductance. (b) Threshold voltage trace in NBTI stress. The stress condition is  $|V_g-V_t|$ =1.5V and the measurement condition is the same as RTN measurement.

- Fig. 4.2 (a) Cumulative probability distribution of a single trapped charge induced  $\Delta v_t$  in 69 RTN vs. NBTI. RTN is measured in fresh devices. (b) Cumulative probability distributions of a single-charge induced  $\Delta v_t$  for RTN in fresh devices and in post-NBTI stress devices. The minimum detectable  $\Delta v_t$  is about 1mV.

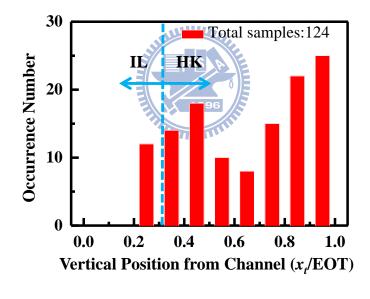

- Fig. 4.3 (a) RTN trap position distribution along the channel extracted from 124 devices. 70 L<sub>trap</sub> is the distance of a trap from the source and L<sub>DS</sub> denotes a channel length.

(b) RTN trap position distribution along the channel extracted from 124 devices. *x<sub>t</sub>* is the distance of a trap from the channel.

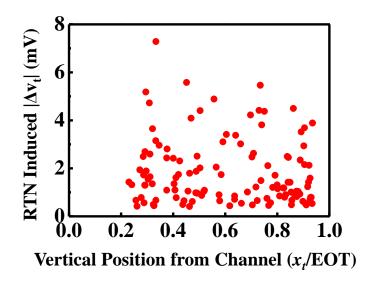

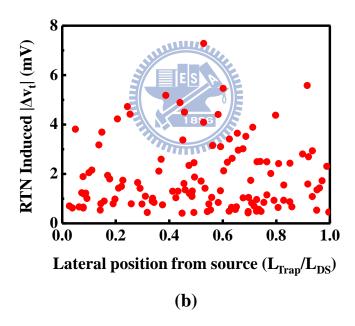

- Fig. 4.4 RTN amplitude distributions versus trap vertical (a) and lateral (b) positions. 71

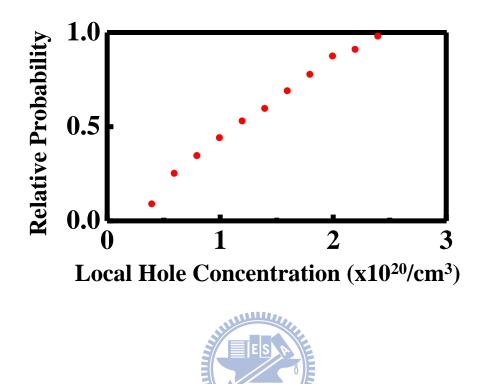

- Fig. 4.5 Relative NBTI trap creation probability versus a local surface hole 72 concentration. A local hole concentration and a surface electric field are calculated from a 3D device simulation with random and discrete substrate dopants. In the calculation,  $E_0$  in Eq. (2) is 1.1MV/cm.

- Fig. 4.6 Complementary cumulative probability distributions of RTN and NBTI 73 amplitudes from 3D atomistic simulation. The simulated devices have a gate length of 30 nm and a gate width of 30nm. The NBTI trapped charge position in the simulation is selected according to its creation probability calculated from Eq. (4.2).

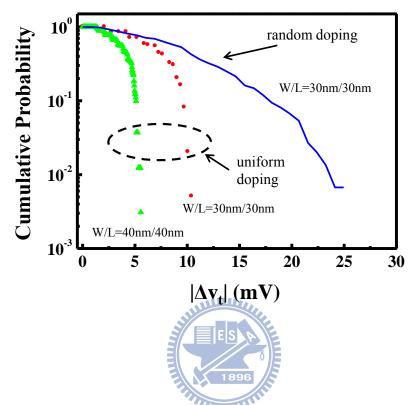

- Fig. 4.7 Cumulative probability density distributions of RTN induced  $\Delta v_t$  amplitude in 74 devices with W/L=30nm/30nm w/ and w/o random doping and W/L=40nm/40nm.

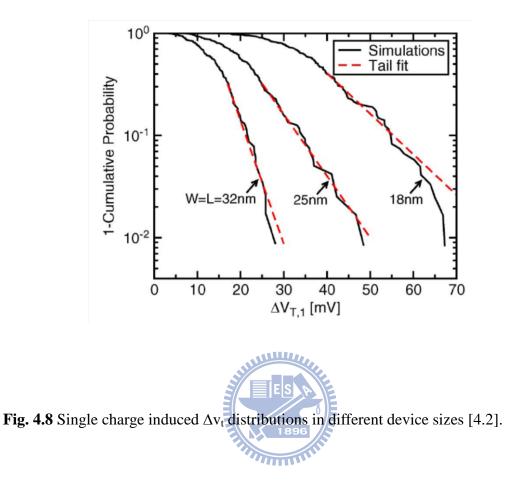

- Fig. 4.8 Single charge induced  $\Delta v_t$  distributions in different device sizes [4.2]. 75

- Fig. 5.1 An illustration of two different program charge storage characteristic resulting 84 distinct outcome of percolation path. Continuous distribution in FG flash and random discrete distribution in SONOS flash.

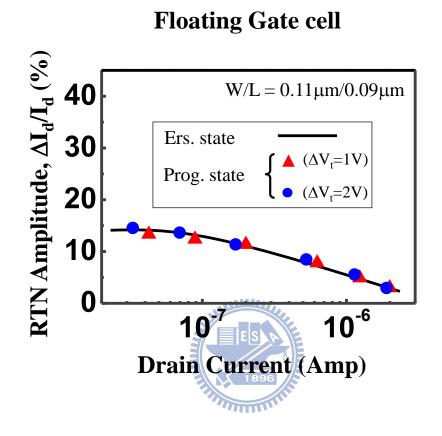

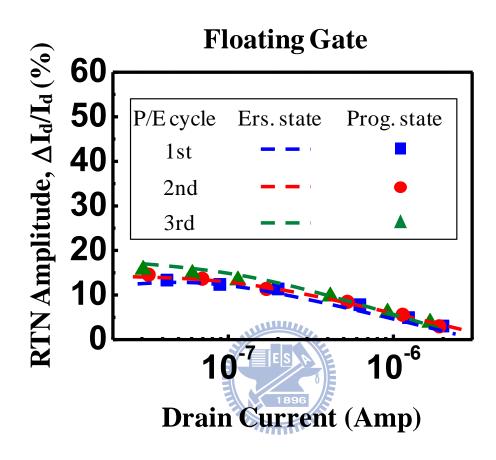

- Fig. 5.2RTN amplitude versus drain current in a FG flash cell at two program window :851V, 2V. The drain voltage in measurement is 0.7V and the gate voltage is

varied.

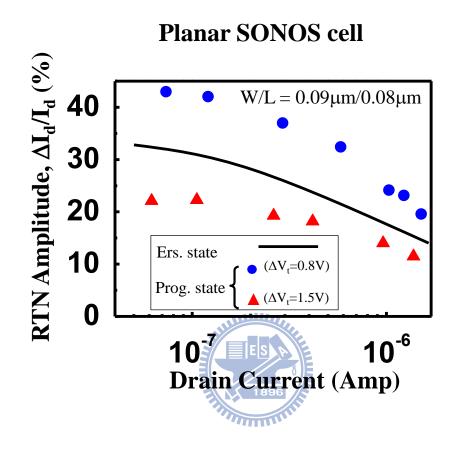

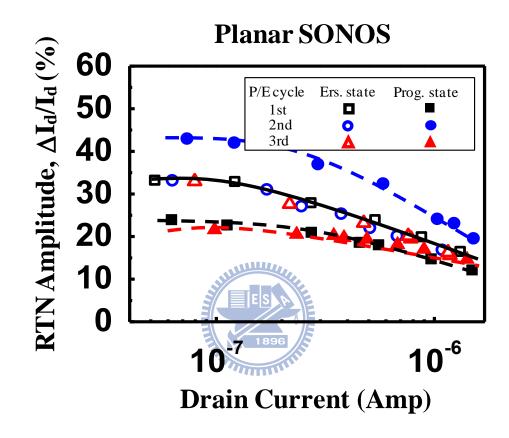

- Fig. 5.3 RTN amplitude versus drain current in a SONOS flash cell at two program 86 window : 0.8V, 1.5V. The drain voltage in measurement is 0.7V and the gate voltage is varied.

- Fig. 5.4 Measured program-state RTN amplitude versus erase-state RTN amplitude in 87 40 FG flash cells. The RTN amplitude is measured at  $I_d$ =500nA @V<sub>d</sub>=0.7V. The device dimension is W/L=0.11 $\mu$ m/0.09 $\mu$ m. The program window is 1V or 2V.

- Fig. 5.5 Measured program-state RTN amplitude versus erase-state RTN amplitude in 88 60 planar SONOS cells. The RTN amplitude is measured at  $I_d$ =500nA @V\_d=0.7V. The SONOS cells have W/L=0.09µm/0.08µm, a 2.8nm tunnel oxide, a 6nm Si<sub>3</sub>N<sub>4</sub> and a 6nm top oxide.

- Fig. 5.6 RTN amplitude versus drain current in a FG flash cell in three P/E cycles. The 90

Vt window is 1V. The drain voltage in measurement is 0.7V and the gate voltage is varied.

- Fig. 5.7 RTN amplitude versus drain current in a SONOS cell in three P/E cycles. The 91

Vt window is 1V. The drain voltage in measurement is 0.7V and the gate voltage is varied.

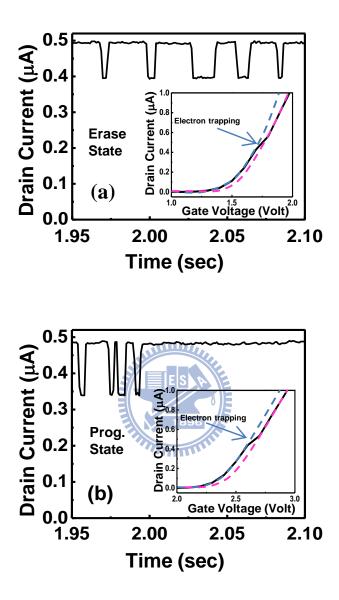

- Fig. 5.8 Measured RTN waveform and  $I_d$  versus  $V_g$  plot (a) in erase-state and (b) in 92 program-state of a SONOS cell. Electron trapping at an interface trap is manifested by a current discontinuity in the  $I_d$ - $V_g$  plot.

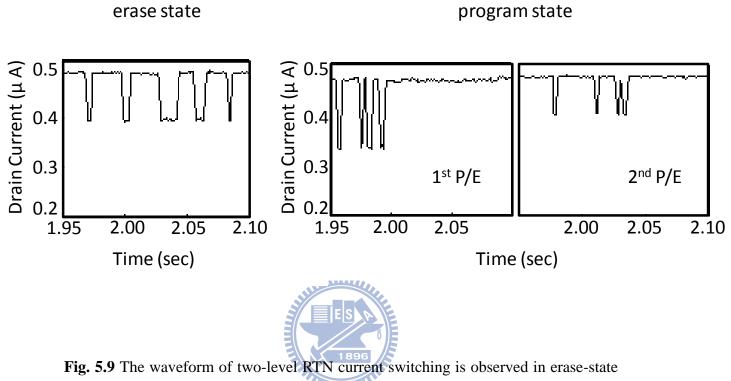

- Fig. 5.9 The waveform of two-level RTN current switching is observed in erase-state 93 and  $1^{st}$  and  $2^{nd}$  program-state.

- Fig. 5.10 Simulation flow chart of our 3D atomistic simulation for RTN amplitude at 94 program state and erase state for both FG flash and planar SONOS flash.

- Fig. 5.11 Simulated RTN amplitude versus drain current in a FG flash cell. Program-state 95 and erase-state have the same placement of substrate random dopants. The RTN trap is placed in the middle of the device.

- Fig. 5.12 Simulated RTN amplitude versus drain current in a planar SONOS cell.

96 Program-state and erase-state have a fixed placement of substrate dopants. Ten different sets of random program charges are simulated. An RTN amplitude due to number fluctuation is calculated with continuous substrate doping and program charges.

- Fig. 5.13 Cross-section of a FinFET SONOS and the electron concentration contour in the 97

FinFET SONOS obtained from a 2D simulation.

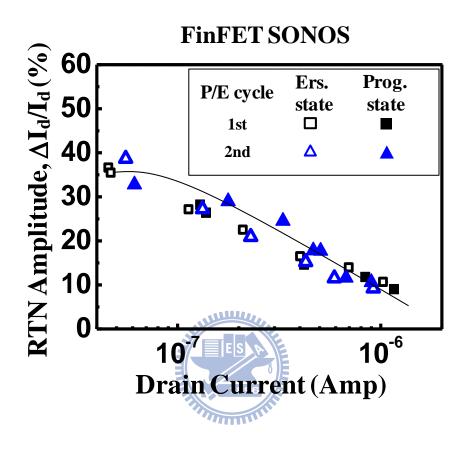

- Fig. 5.14 RTN amplitude versus drain current in a FinFET SONOS cell for two P/E 98 cycles.

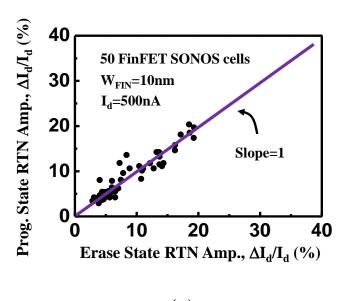

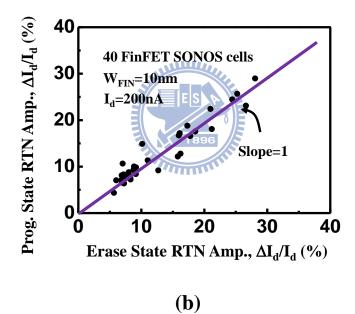

- Fig. 5.15 Program-state RTN amplitude versus erase-state RTN amplitude in FinFET 99 SONOS cells. The fin width is 10nm. (a) RTN is measured at  $I_d$ =500nA and (b) RTN is measured at  $I_d$ =200nA.

- Fig. 5.16 In a planar SONOS, percolation paths are widely distributed in the gate width 100 direction. In a FinFET SONOS, conducting paths are confined to a small region in the corner of the Si fin.

- Fig. 5.17 Measurement of the correlation factor in FinFET SONOS with two different fin 101 width, 10 nanometer and 25 nanometer. The correlation factor increases from 0.82 to 0.94 as the fin width reduces from 25 nanometer to 10 nanometer.

- Fig. 5.18 A 3D RTN simulation in planar SONOS with different channel width. The 102 correlation factor is calculated based on a sample size of 40 devices.

- Fig. 6.1 3D atomistic simulation of an electron concentration distribution in a cylindrical 112 channel MOSFET. The diameter of the channel is 6nm. (a) Electron concentration distributions in two cross-sections, A and B. B has a dopant charge at the center and A does not have a dopant charge. (b) An electron density distribution along the channel. The Thomas-Fermi screening length  $(\left[kT/4\pi n_e e^2\right]^{1/2})$  is shown in the figure.

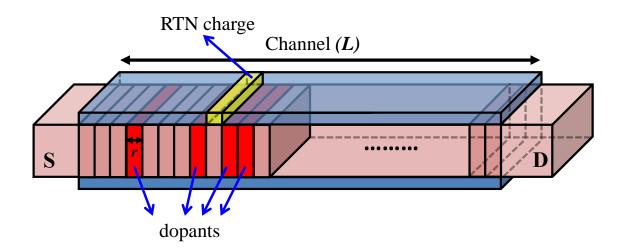

- Fig. 6.2 Illustration of a one-dimensional channel RTN simulation scheme. The 113 simulated MOSFET has a double gate structure. The channel is divided into many 1nm slices. In simulation, a dopant charge is placed uniformly in a slice and an RTN charge is placed in a 1nm bar on top of the channel.

- Fig. 6.3 Complementary cumulative distribution function (1-CDF) of RTN induced  $\Delta V_t$  114 from a 3D atomistic simulation and from the 1D channel RTN simulation. The devices have a doping concentration of  $1 \times 10^{19}$ /cm<sup>3</sup> and a channel length of 40nm. The gate width is 20nm in (a) and 7nm in (b).

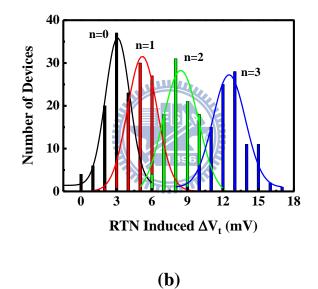

- Fig. 6.4 1D channel Monte Carlo simulation of RTN induced  $\Delta V_t$ . The channel length is 115 40nm and each device has 14 dopants. A dopant number in the RTN trap section (*n*) is equal to 0, 1, 2 and 3, respectively. For each *n*, we simulate 100 devices.

(a) RTN induced V<sub>t</sub> shifts in totally 400 devices. (b) The distribution of RTN induced  $\Delta V_t$  for each *n*.

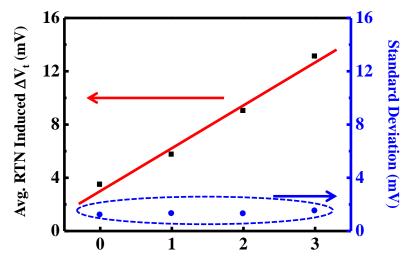

- Fig. 6.5 Average RTN amplitude and a standard deviation versus a dopant number in an 116 RTN trap section (*n*).

- Fig. 6.6 Measured average RTN induced  $\Delta V_t$  versus a CHE program window in 45 117 SONOS cells. A linear relationship between the  $\Delta V_t$  and a program  $V_t$  window is obtained.

- Fig. 6.7 Complementary cumulative distribution function of RTN induced  $\Delta V_t$  from 1D 118 channel Monte Carlo RTN simulation and from this analytical model. The doping concentration is  $1 \times 10^{19}$ /cm<sup>3</sup>,  $7 \times 10^{18}$ /cm<sup>3</sup> and  $5 \times 10^{18}$ /cm<sup>3</sup> respectively. The gate length is 40nm.

- Fig. 6.8 Complementary cumulative distribution function of RTN induced  $\Delta V_t$  from 1D 119 channel Monte Carlo RTN simulation and from this analytical model for two different gate lengths,  $L_c$ =30nm and 40nm. The doping concentration is  $1 \times 10^{19}$ /cm<sup>3</sup>.

- Fig. 6.9 Complementary cumulative distribution function of RTN amplitude distribution 120 in FinFET SONOS cells with a fin width=10nm. A Poisson-like shape is obtained.

## LIST OF SYMBOLS

| $\Delta V_t$    | Threshold voltage shift in total during stress/recovery                       |

|-----------------|-------------------------------------------------------------------------------|

| $\Delta v_t$    | Single charge induced threshold voltage shift during stress/recovery          |

| $\sigma_{s}$    | Standard deviation of NBTI stress induced $\Delta v_t$                        |

| t               | Time                                                                          |

| n               | Power factor in RD model                                                      |

| Ν               | Total number of stress created traps                                          |

| $\Delta I_d$    | Drain current shift in total during stress/recovery                           |

| $g_m$           | Transconductance                                                              |

| SS              | Subthreshold swing                                                            |

| i               | Trap creation/emission sequence number                                        |

| $	au_i$         | Characteristic time of <i>i</i> -th charge creation/emission                  |

| <>              | Mean value                                                                    |

| $\sigma_{i}$    | Standard deviation of $\mathbf{r}_i$                                          |

| $N_t$           | Bulk trap number                                                              |

| γ               | Electric field acceleration parameter [1.28]                                  |

| F               | Electric field                                                                |

| $E_D$           | Activation energy combined for $D_{H2}$ , $k_H$ , and $k_{H2}$ [1.28]         |

| W               | Device channel width                                                          |

| L               | Device channel length                                                         |

| $D_0$           | Pre-factor of Arrhenius diffusivity in RD model                               |

| $K_{F0}$        | Pre-factor of Arrhenius generation rate in RD model                           |

| $K_{R0}$        | Pre-factor of Arrhenius recombination rate in RD model                        |

| k <sub>B</sub>  | Boltzmann constant                                                            |

| Т               | Temperature                                                                   |

| $E_{e\!f\!f}$   | Effective activation energy including a local electric field effect in stress |

| Μ               | Precursor number                                                              |

| $\sigma_{r}$    | Standard deviation of NBTI recovery induced $\Delta v_t$                      |

| $E_a$           | Effective activation energy of trap emission in NBTI recovery                 |

| T <sub>IL</sub> | Interfacial later thickness                                                   |

|                 |                                                                               |

| X <sub>i</sub>          | Distance of the <i>i</i> -th trapped charge from HK/IL interface |

|-------------------------|------------------------------------------------------------------|

| $E_t$                   | Trap energy                                                      |

| $\Phi_{\!B}$            | HK/IL conduction band offset                                     |

| $m_{IL}^{*}$            | Effective mass of hole in IL                                     |

| <i>m<sub>HK</sub></i> * | Effective mass of hole in HK                                     |

| $m_0$                   | Free electron mass                                               |

| q                       | Electronic charge                                                |

| ħ                       | Reduced Planck constant                                          |

| d                       | HK thickness                                                     |

| $\Delta x$              | Distance between adjacent trapped charges                        |

| $\tau_{c}$              | RTN capture time                                                 |

| $	au_e$                 | RTN emission time                                                |

| $\sigma_0$              | Trap cross section                                               |

| V <sub>th</sub>         | Thermal velocity                                                 |

| f                       | Correlation factor                                               |

| $H_{\mathrm{fin}}$      | Fin height of a FinFET SONOS                                     |

| $W_{\mathrm{fin}}$      | Fin width of a FinFET SONOS                                      |

| l                       | Thomas-Fermi screening length                                    |

| $\mathcal{E}_{Si}$      | Dielectric constant of silicon                                   |

| C(N,n)                  | Binomial coefficient                                             |

| λ                       | Mean value in a Poisson distribution                             |

|                         |                                                                  |

## Introduction

#### **1.1 Backgrounds**

The dimensions of the smallest demonstrated prototypes of silicon based CMOS devices [1.1][1.2] have been rapidly approaching the physical limit. Continual downscaling boosts device performance to meet the Moore's Law at the expense of growing leakage problems. The gate leakage currents [1.3] and the channel leakage currents [1.4] increase rapidly with decreasing gate dielectric thickness and with shorter channel length respectively. The resultant intolerable standby power consumption has made further scaling impractical. To resolve this issue, introduction of high permittivity (high-k) materials as the gate dielectrics [1.5][1.6] have been proposed to suppress gate leakage current due to physical thickness and keep the equivalent-oxide-thickness (EOT) reasonably small at the same time to maintain the high performance, as shown in Fig. 1.1. Part of this work thus concentrates on the high-k dielectric reliability.

In nowadays high-k technology, Hf-based materials are most promising and their film chemistry [1.7][1.8], process optimization [1.9][1.10], as well as reliability assessment and analysis [1.11]-[1.13] are being extensively studied. Recently, HfSiON has been successfully integrated into CMOS devices as gate dielectric for low power applications with good reliability, comparable mobility (as SiO<sub>2</sub>), and greatly reduced gate leakage [1.9][1.11].

As one of the most important degradation modes in CMOS technologies, the negative bias temperature instability (NBTI) has been known since the 1970s [1.14].

The reaction-diffusion (RD) model [1.14]-[1.17] and a charge trapping model [1.18]-[1.23] are commonly adopted for NBTI degradation. The RD model can well describe the mean of an NBTI induced  $\Delta V_t$  distribution, or a  $\Delta V_t$  in a large area device. However, hydrogen back-diffusion [1.17] in the framework of the RD model was not able to explain a NBTI recovery phenomenon which shows a log(t) dependence of  $\Delta V_t$  on relaxation time [1.24][1.25]. Since it was suggested that RD model cannot explain NBTI recovery transient and the shape of AC duty cycle dependence [1.21]. This apparent failure of RD framework has inspired a reintroduction of "well-based" charge trapping model [1.21]-[1.23][1.26]. However, the charge trapping model fails to explain the power-law dependence of  $\Delta V_t$  evolution on stress time.

Aforementioned, unlike most reliability effects, NBTI V<sub>t</sub> degradation recovers partly after the removal of stress [1.27]. Wang et al used a fast transient technique to characterize NBTI recovery and found a log(t) dependence of  $\Delta V_t$  on relaxation time [1.24]. A log(t) dependence was also reported in [1.25] where the authors proposed a dispersive transport model within the RD framework to overcome the apparent deficiency of the RD model in relaxation time dependence. Alam et al ascribed a log(t) recovery transient to a fast charge detrapping process on top of slower N<sub>it</sub> re-passivation as encapsulated by the RD model [1.28][1.29]. More recently, Grasser et al used a time dependent defect spectroscopy method to investigate NBTI recovery and concluded that NBTI recovery is due to thermally-assisted discharging of traps and no diffusion process is involved [1.23].

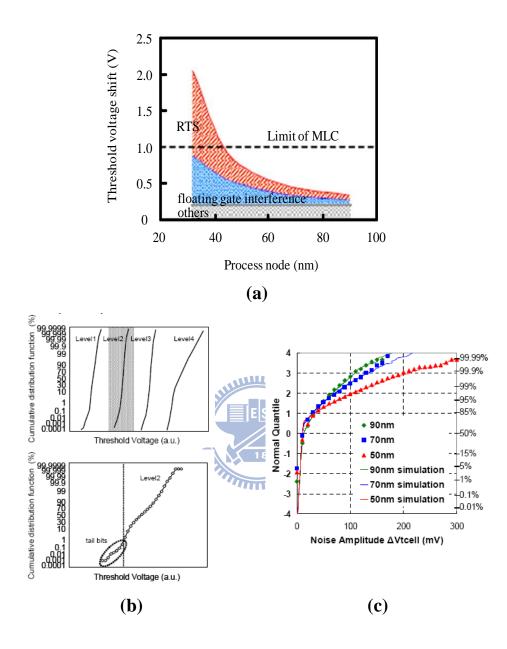

In addition to NBTI, random telegraph noise (RTN) phenomenon arising from charge emission and capture at an interface trap site [1.30]-[1.33] has been recognized as a new scaling concern in both advanced CMOS [1.34]-[1.36] and flash memory

[1.37]-[1.42]. Typical two-level RTN pattern is shown in Fig. 1.2.

With respect to flash memory devices, they play an important role in VLSI industry with their wide applications. NOR-type flash memory is suitable for code storage applications, such as mobile phones and handheld devices. On the other hand, NAND-type flash memory is suitable for data storage applications, such as USB and solid-state-disk (SSD). Part of this work thus concentrates on the RTN effect on flash memory cells.

#### **1.2 Description of the Problem**

As device dimensions reduce to a nanometer scale, the number of traps generated by NBTI stress varies significantly from a device to a device due to stochastic process of trap generation and dispersion of activation energy in the RD model. In these nanoscale transistors, NBTI induced  $\Delta V_t$  scatters widely and it is no longer sufficient to consider just the mean value of  $\Delta V_1$  in circuit simulation. An accurate model of an entire  $\Delta V_t$  distribution and its stress time evolution is needed in a worst-case circuit simulation to ensure that the tail of  $\Delta V_t$  distribution does not cross the reliability criteria during the specified lifetime of an integrated circuit [1.43]-[1.45]. While the mean of an NBTI  $\Delta V_t$  distribution, or a  $\Delta V_t$  in a large area device, can be well described by the RD model [1.14][1.16][1.17][1.28], the RD model alone is insufficient to predict an entire  $\Delta V_t$  distribution in small area devices with stress time. On the other hand, the post-NBT recovery has the same issue that ThAT model alone is insufficient to predict an entire  $\Delta V_t$  distribution in small area devices with recovery time. As a result, we develop statistical models for both NBTI stress and recovery by characterization of single charge creation/emission (Fig. 1.3) using fast transient measurement technique.

Furthermore, as the technology node is scaled down, RTN also becomes a more and more important reliability issue in both CMOS and flash memory technologies. A single charge trapping/detrapping will induce a large fluctuation in read current and thus a read failure. As a result, the RTN amplitude and its trap positions are also studied in this dissertation.

In terms of charge storage devices, two state-of-the-art structures attract great attention. One is floating gate (FG) flash and the other is charge trapping (CT) flash. Recently, 3D structures have been proposed for flash memory arrays.  $V_t$  fluctuations originated from a large-amplitude RTN tail will cause a read error and become a prominent issue in designing a multilevel-cell (MLC) flash memory in 45nm technology node and beyond, as shown in Fig. 1.4. We will thus focus on the RTN amplitude distributions and its dependence on program window in FG, planar SONOS and FinFET SONOS flash memory cells.

At present, RTN amplitude model is an empirical formula. However, the underlying RTN physical mechanism must be understood in order to make meaningful projection of device/circuit lifetime. Since it's hard to derive a 3D RTN amplitude model directly, we start from 1D device structures which are also promising candidates in future VLSI technology. We use a 3D Monte Carlo simulation to verify our model.

#### **1.3 Organization of this dissertation**

This dissertation consists of seven chapters. The scope of the dissertation mainly focuses on the applications of single charge phenomena in advanced CMOS and SONOS flash memory. Following the introduction, the characterization and physical mechanisms of the NBTI degradation in a small-area high-k/metal-gate pMOSFET

are described in Chapter 2. A statistical model for an NBTI induced  $\Delta V_t$  distribution by employing the RD model and convolving extracted activation energy including a local electric field effect and a single trapped hole induced Vt shift is developed. NBTI trapped charge characteristics and recovery mechanisms are proposed in Chapter 3 by a statistical study of individual trapped charge emissions in small-area HfSiON/metal-gate pMOSFETs. We develop a statistical NBTI recovery  $\Delta V_t$  model based on the ThAT and an extracted activation energy distribution. In Chapter 4, we compare the RTN and NBT-stress induced  $\Delta V_t$  amplitude distributions. A 3D atomistic simulation is performed to compare a single-charge induced  $\Delta V_t$  by RTN and NBTI. In Chapter 5, nitride program charge effect on the amplitude of RTN in flash cells is investigated. We measure and simulate RTN amplitudes in floating gate flash, planar SONOS, and FinFET SONOS cells. In Chapter 6, an RTN amplitude distribution model in nanowire-like structures is developed. A Poisson distribution is proposed and partly verified using measurement in SONOS flash memory cells. Finally, conclusions are drawn in Chapter 7.

**Fig. 1.1** Projections of gate leakage current and equivalent oxide thickness (EOT) from ITRS roadmap for low-standby-power applications.

Fig. 1.2 A typical two-level RTN waveform resulting from electron capture/emission at an oxide trap.  $\tau_c$  and  $\tau_e$  are electron capture and emission times, respectively.  $\Delta I_d$  is RTN amplitude.

**(b)**

**(a)**

**Fig. 1.3** Typical  $V_t$  traces during NBTI stress (a) and recovery (b). Each step-like "quantum jump" represents a single charge creation/emission.

**Fig. 1.4** (a) Estimation of threshold voltage shift as a function of process node [1.39] (b) measured  $V_t$  distribution of a 4-level MLC with level enlarged [1.39] and (c) noise distributions of 90nm, 70nm, and 50nm flash memory technologies [1.40].

## Statistical Characterization of Individual Charge Trapping Times and Modeling of $\Delta V_t$ Distribution by NBTI Stress

#### **2.1 Preface**

Negative bias temperature instability has been recognized as a major concern in scaled high-permittivity (high-k) gate dielectric pMOSFETs because of its significant impact on performance and reliability in digital and analog circuits [1.43][2.1]-[2.6]. NBTI caused noise margin degradation in a SRAM cell and frequency degradation in a ring oscillator have been reported [2.1]. NBTI severity aggravates as supply voltage reduces in device scaling. In addition to digital circuits, NBTI is of particular importance for analog applications where the ability to match device characteristics to a high precision is critical [2.3]. For instance, in digital-to-analog converters, NBTI can pose a serious reliability issue as a small V<sub>t</sub> shift in bias current source can cause large gain errors [2.4].

As device dimensions reduce to a nanometer scale, the number of traps generated by NBTI stress varies significantly from a device to a device due to stochastic process of trap generation and dispersion of activation energy in the RD model. In these nanoscale transistors, NBTI induced  $\Delta V_t$  scatters widely and it is no longer sufficient to consider just the mean value of  $\Delta V_t$  in circuit simulation. An accurate model of an entire  $\Delta V_t$  distribution and its stress time evolution is needed in a worst-case circuit simulation to ensure that the tail of  $\Delta V_t$  distribution does not cross the reliability criteria during the specified lifetime of an integrated circuit [1.43]-[1.45]. While the mean of an NBTI  $\Delta V_t$  distribution, or a  $\Delta V_t$  in a large area device, can be well described by the RD model [1.14][1.16][1.17][1.28], the RD model alone is insufficient to predict an entire  $\Delta V_t$  distribution in small area devices.

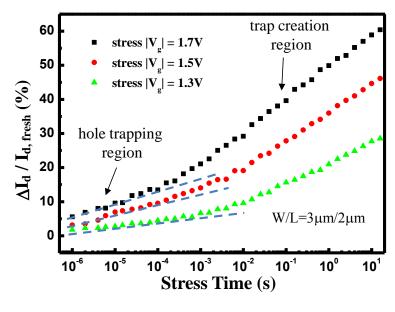

We first measured an  $I_d$  degradation in a large-area device (Fig. 2.1(a)). As compared with our earlier works [1.18], initial trap density is suppressed (from 50% to 20%) due to the improvement of device fabrication technique. Consequently, a RD model rather than a charge trapping model is more adaptable to our present measurement results.

A Vt shift in an NBTI stressed device can be expressed as the sum of each individual trapped charge induced  $\Delta v_t$ , i.e.,  $\Delta V_t = \sum_{i=1}^N \Delta v_{t,i}$ , where N is a total number of stress created traps in a device and  $\Delta v_t$  denotes a single trapped charge caused V<sub>t</sub> shift. Two factors affect a  $\Delta V_t$  distribution. One is the dispersion of  $\Delta v_t$  and the other is fluctuations in number of traps N in stressed devices. The origin and the magnitude distribution of  $\Delta v_t$  have been investigated thoroughly [2.7][2.8]. Previous characterization and 3D atomistic simulation show that a  $\Delta v_t$  exhibits an exponential distribution approximately, i.e.,  $f(|\Delta v_t|) = \exp(-|\Delta v_t|/\sigma_s)/\sigma_s$ , due to a random substrate dopant induced current-path percolation effect [2.7][2.9]. To derive a  $\Delta V_t$  distribution, we still need a distribution model for a trap number N. In literature, a Poisson distributed N was usually assumed [2.7][2.8][2.10]. The Poisson model is, however, based on a notion that individual trapped charge creations during NBTI stress are independent. In other words, each new trap creation in a device has the same probability regardless of how many traps have been created. Nevertheless, the RD model and measurement result show that NBTI degradation obeys a power-law dependence on stress time, i.e.,  $t^{1/n}$  with  $n \sim 6$  [1.28][2.11], implying that a new trap creation rate decreases with an increasing trapped charge number. Therefore, the use of a Poisson model is contradictory to the RD model and measurement result and may exaggerate *N* and a  $\Delta V_t$  distribution tail significantly. To resolve this discrepancy, Alam et al simulated a trap number distribution by using a Markov Chain Monte Carlo method [2.12] to consider stochastic process of trap generation within a RD framework. However, they did not consider the dispersion of activation energy in the RD model. As a result, their simulated trap characteristic time distribution is much narrower than measurement result in [2.13].

In this work, we characterize NBTI trap creation and  $V_t$  shifts in small area devices. Unlike a large-area device, NBTI induced  $V_t$  degradation proceeds in discrete steps in small area devices [2.9][2.13]. Due to the discrete nature of a  $V_t$  evolution, we are able to measure individual trapped charge creation times and each trapped charge induced  $V_t$  shift. An effective activation energy distribution including a local electric field in the RD model will be extracted from measured trapped charge creation times. A Monte Carlo model employing the RD model and an extracted activation energy distribution will be developed to simulate an NBTI  $\Delta V_t$  distribution and its stress time evolutions.

#### 2.2 Characterization of Individual NBTI Trapped Charge Creation

#### 2.2.1 Devices and Measurement Setup

The devices have a drawn gate length of 30nm, a gate width of 80nm and a high-k (HfSiON) gate dielectric with an equivalent oxide thickness of ~1nm. Similarly to [1.19], the characterization is performed in a stress-measurement-stress (SMS) sequence. In NBTI stress phase,  $V_{gs}$ =-1.8V and  $V_d$ =0V at room temperature. In measurement phase, the drain voltage is -0.05V and the gate voltage is adjusted to have a drain current of about 500nA in a fresh device. Drain current variations are traced with a switch delay time less than 1µs using Agilent B1500.

#### 2.2.2 Single Charge Creation Induced $\Delta v_t$ Distribution

A corresponding  $\Delta V_t$  trace is obtained from a measured  $\Delta I_d$  divided by a transconductance. An example  $V_t$  trace is shown in Fig. 2.2. To check on interface trap creation, we monitor transconductance  $(g_m)$  and subthreshold swing (SS) degradations during the stress. The subthreshold  $I_d$ – $V_g$  characteristics before and after an NBTI stress are shown in the inset of Fig. 2.2. An almost parallel shift after stress is observed, thus indicating that  $V_t$  degradation is mainly caused by fixed trapped charge creation rather than interface trap creation. Both SS and  $g_m$  degradations are less than 5% in the stress period. For simplicity, a constant transconductance is used when converting  $\Delta I_d$  into a  $V_t$  trace in Fig. 2.2. Each abrupt  $V_t$  change ( $\Delta v_{t,i}$ ) in Fig. 2.2 is due to a single trapped hole creation, where *i* denotes a trapped charge creation sequence number.

We collect all  $\Delta v_{t,i}$  in about 130 devices. The magnitude distribution of  $\Delta v_t$  is plotted in Fig. 2.3. The solid line in Fig. 2.3 represents an exponential fit with a slope  $(\sigma_s)$  of 3.3mV.

#### 2.2.3 Characteristic Times for Trapped Charge Creation

In addition to  $\Delta v_t$ , individual trapped charge creation times are clearly defined in Fig. 2.2. We collect the first three trapped hole creation times, i.e.,  $\tau_i$ , *i*=1,2,3, in about 130 devices. The probability density functions (PDFs) of log( $\tau_i$ ) are shown in Fig. 2.4. It should be remarked that about 3% devices have less than 3 traps created in a stress period of 100sec. Table 2.1 shows the mean ( $\langle log(\tau_i) \rangle$ ) and the standard deviation ( $\sigma_i$ ) of the three log( $\tau_i$ ) distributions. For comparison, the  $\langle log(\tau_i) \rangle$  and  $\sigma_i$  in NBTI recovery from [2.14] are also shown in the Table 2.1. Distinctly different features between stress mode and recovery mode are noticed. We find that  $\langle \log(\tau_i) \rangle - \langle \log(\tau_1) \rangle \rangle \sim n \log(i)$  and the standard deviations  $\sigma_1 \rangle \sigma_2 \rangle \sigma_3$  in NBTI stress while  $\langle \log(\tau_{i+1}) \rangle - \langle \log(\tau_i) \rangle \rangle$  constant and the standard deviations  $\sigma_1 \langle \sigma_2 \langle \sigma_3 \rangle$  in NBTI recovery. The detail explanations for the features in NBTI recovery has been given in Chapter 3. In this Chapter, we are focused on the characteristics of stress.

The measured  $\tau_i$  spreads over several decades of time. There are two possible reasons for the wide spread. One is the stochastic process of trap generation in the RD model and the other is the dispersion of activation energy including a local electric field effect (effective activation energy ( $E_{eff}$ ) hereafter). Other parameters in the RD model or other processes are unlikely to cause such wide spread. The stochastic process of trap generation has been investigated in [2.12] by using a Markov chain Monte Carlo method. Their simulated trap creation time distribution is much tighter than our measured result. Consequently, we attribute the wide spread of trap characteristic times mainly to the dispersion of activation energy arising from different local chemistry in the RD model. Furthermore, the fitting parameters vary a lot from Alam's own publications. In other words, the stochastic process is negligible, as compared to the dispersion of activation energy distribution will be developed.

According to the RD model, the stress time dependence of the number of NBTI generated traps in a device is shown below [1.28],

$$N_{t} = A \exp(\frac{2\gamma F}{3}) \exp[\frac{-E_{D}}{k_{B}T}]t^{\frac{1}{n}}, \ n \sim 6,$$

(2.1)

and

$$A = WLD_0^{1/6} \left[ \frac{K_{F0}[SiH][h^+]}{pK_{R0}} \right]^{2/3},$$

(2.2)

where W is a gate width, L is a gate length,  $K_{F0}$ ,  $K_{R0}$  and  $D_0$  are the pre-factors of forward and reverse reaction rate constants and diffusivity in a Arrhenius activation energy, respectively [2.11], and p is the local channel hole concentration. The effective activation energy ( $E_{eff}$ ) in Eq. (2.1) is defined as

$$E_{eff} = E_D - \frac{2}{3}\gamma F k_B T.$$

(2.3)

By re-arranging the terms in Eq. (2.1), the relationship between the *i*-th trapped charge creation time ( $\tau_i$ ) and effective activation energy is shown below

$$\log(\tau_i) = \frac{nE_{eff}}{2.3k_BT} + n\log(i) - n\log(A).$$

(2.4)

From the above equation, the relationship of the mean of the  $log(\tau_i)$  is obtained,

$$<\log(\tau_i)>-<\log(\tau_1)>=n\log(i),\tag{2.5}$$

*n* is about 5.6 in our measurement in an initial stress stage. Thus, we can therefore obtain  $\langle \log(\tau_2) \rangle = \langle \log(\tau_1) \rangle = 5.6 \log(2) = 1.69$  and  $\langle \log(\tau_3) \rangle = \langle \log(\tau_1) \rangle = 5.6 \log(3) = 2.67$  without regard to activation energy. The calculated result from Eq. (2.5) is in reasonable agreement with the measurement result in Table 2.1.

#### 2.2.4 Activation Energy Distribution

In the following, we will extract an activation energy distribution from measured trap characteristic times. By re-arranging the terms in Eq. (2.4), effective activation energy can be readily obtained as follows,

$$E_{eff} = \frac{2.3k_BT}{n} [\log(\tau_i) - n\log(i) + n\log(A)].$$

(2.6)

We can translate the measured  $\log(\tau_i)$  distribution into a relative activation energy distribution by subtracting a term  $n\log(i)$  from it. Extracted  $E_{eff}$  distributions from  $\tau_1$ ,  $\tau_2$  and  $\tau_3$ , respectively, are shown in Fig. 2.5. Generally, the  $E_{eff}$  distributions from the  $\tau_1$ ,  $\tau_2$  and  $\tau_3$  have a reasonable match. Note that the  $E_{eff}$  from the  $\tau_1$  is slightly broader than the other two distributions, as pointed out in Table I. The pre-factor A in Eq. (2.6) is chosen such that an average value of  $E_{eff}$  is about 0.12eV [2.15]. The solid line in Fig. 2.5 represents a Gaussian distribution fit to the  $E_{eff}$  of  $\tau_1$  with a mean of 0.12eV and a standard deviation of 0.015eV.

# **2.3** Modeling of an NBTI Induced $\Delta V_t$ Distribution

# 2.3.1 Measured NBTI Induced $\Delta V_t$ Distribution

We measure NBTI induced  $\Delta V_t$  distributions at different stress times. We record the number of generated traps and a total  $V_t$  shift in each device. Fig. 2.6 shows the measurement result at a stress time of 0.5sec and 5sec. The *y*-axis is  $\Delta V_t$  and the *x*-axis is the number of trapped holes. Each data point represents a device. The measurement data points scatter along a straight line, as shown in Fig. 2.6. The slope of the line is about 3.3mV, i.e., an average single-charge induced V<sub>t</sub> shift. A straight line with a slope of 3.3mV is drawn as a reference father than a real average value.  $\Delta V_t$  and NBTI trap number distributions spread as stress time increases. We extract the mean and the variance of the  $\Delta V_t$  distributions. An average of  $\Delta V_t$  in 130 devices is plotted in Fig. 2.7. The mean follows a power law dependence on stress time  $(t^{1/n})$ in five decades of time with *n* about 6. The variance of the  $\Delta V_t$  distribution also increases with stress time, as shown in Fig. 2.8. In our earlier work, we reported a two-stage  $V_t$  degradation by BTI stress [1.18]. The first stage is ascribed to the charging of pre-existing high-k dielectric traps and exhibits a log(t) dependence. The second stage degradation is caused by high-k dielectric trap creation and follows a power law dependence on stress time. In this work, we do not observe the stage of log(t) degradation in our stress period possibly because of fewer pre-existing traps in the current samples.

# 2.3.2 Monte Carlo Simulation Flow

A statistical model based on a Monte Carlo (MC) approach is developed to calculate the number of traps (*M*) and entire  $\Delta V_t$  distributions. A Monte Carlo flowchart is shown in Fig. 2.9. In our MC simulation, a Poisson-distributed precursor number (*M*) in each device is assumed with a mean value of 24 in an 80nmx30nm device, which corresponds to a precursor density of  $10^{12}$  cm<sup>-2</sup> [2.16]. A sequence number (*i*) is assigned to each precursor in a device. The activation energy of each precursor is chosen according to the measured  $E_{eff}$  distribution in Fig. 2.5. A trapped charge creation time is then computed from Eq. (2.4). The simulated  $\log(\tau_i)$  distributions are shown in Fig. 2.10. Each distribution has the same shape as the activation energy. Due to a significant overlap of the distributions, some precursors with a larger sequence number are converted to a trapped charge earlier than the ones with a smaller *i*. Thus, we re-order trapped charge creation sequence number in each device. The  $\tau_i$  distributions after the re-ordering are shown in Fig. 2.11. The measured

result is also shown in the figure for comparison. Two points should be noted. First, after the re-ordering, the standard deviation of  $log(\tau_i)$  decreases with an increasing *i*. This feature is consistent with the measurement result in Table 2.1. Second, The shape of the  $log(\tau_i)$  distribution with *i*=1 is least affected by the re-ordering. Consequently, we used the measured result of  $\tau_1$  to extract an  $E_{eff}$  distribution in Fig. 2.5.

#### 2.3.3 Monte Carlo Simulation Results and Discussion

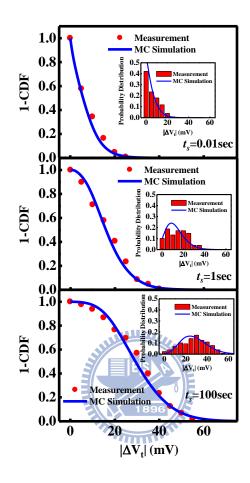

For a stress time  $t_s$ , the number of trapped charges N is computed by counting all the precursors with  $\tau_i$  (*i*=1,2,...,*M*) less than  $t_s$ . For each counted trapped charge, a  $\Delta v_t$ is selected based on an exponential distribution,  $f(|\Delta v_t|) = \exp(-|\Delta v_t|/\sigma_s/\sigma_s)$ , with  $\sigma_s$ =3.3mV. A  $\Delta V_t$  at a stress time  $t_s$  can be computed by summing up all the  $\Delta v_t$ , i.e.,  $\Delta V_t = \sum_{i=1}^{N} \Delta v_{t,i}$ . In total,  $5 \times 10^5$  devices are simulated. The mean and the variance of the simulated  $\Delta V_t$  distributions versus stress time are shown in Fig. 2.7 and Fig. 2.8, respectively. Our simulation is in good agreement with measurement results. In addition, we compare measured and simulated  $\Delta V_t$  distributions at different stress times. Complementary cumulative distribution functions (1-CDF) of NBTI induced  $\Delta V_t$  at a stress time of  $t_s$ =0.01sec, 1sec and 100sec are plotted in Fig. 2.12. The inset of the figure is the probability density function of  $\Delta V_t$ . Good agreement between our model and measurement is obtained. We also compare our model with the Poisson distributed trap number model [2.7]. To examine the difference in a  $\Delta V_t$  distribution tail, complementary cumulative distribution functions (1-CDF) of the two models at a stress time of 100sec are plotted in Fig. 2.13 with a logarithmic scale in y-axis. The probability distributions of a trapped charge number from the two models are plotted in the inset. The Poisson model apparently yields a broader distribution in trapped charge number (N) and thus a larger  $\Delta V_t$  tail. The difference between the two models

increases with stress time as more trapped charges are created.

# 2.4 Summary

We characterize NBTI trap creation in a large number of high-k dielectric pMOSFETs. Origins of an NBTI induced  $\Delta V_t$  distribution have been identified. The broad distribution of trap creation times is attributed to an activation energy distribution in the RD model. An activation energy distribution including a local electric field effect has been extracted from measured trap characteristic times. We develop a statistical model to simulate an NBTI induced  $\Delta V_t$  distribution in small area devices. The correlation between an activation energy distribution and an NBTI  $\Delta V_t$  distribution has been established. Our model can reproduce the measurement results of an NBTI  $\Delta V_t$  distribution and its stress time evolutions well.

**(a)**

**(b)**

Fig. 2.1 Comparison between  $I_d$  degradation traces in (a) nowadays (b) previous devices.

**Fig. 2.2** Example  $V_t$  trace in NBTI stress in a high-k gate dielectric pMOSFET.  $\tau_1$ ,  $\tau_2$  and  $\tau_3$  are the 1<sup>st</sup>, the 2<sup>nd</sup> and the 3<sup>rd</sup> trapped hole creation times.  $\Delta v_{t,1}$ ,  $\Delta v_{t,2}$  and  $\Delta v_{t,3}$  are the 1<sup>st</sup>, the 2<sup>nd</sup> and the 3<sup>rd</sup> trapped hole induced threshold voltage shifts. The inset shows subthreshold  $I_d$ – $V_g$  before and after NBTI stress.

Fig. 2.3 The probability density function of a single trapped charge (hole) induced

threshold voltage shift. The solid line represents an exponential fit.

**Fig. 2.4** The probability distribution of a trapped hole creation time in NBTI stress collected from about 130 devices.  $\tau_1$ ,  $\tau_2$  and  $\tau_3$  are the 1<sup>st</sup>, the 2<sup>nd</sup> and the 3<sup>rd</sup> trapped hole creation times, respectively. The solid line represents a Gaussian fit.

**Table 2.1** Comparison of trapped charge creation and emission characteristics inNBTI stress and NBTI recovery. *i* is a sequence number in trapped charge creation inNBTI stress or trapped charge emission in NBTI recovery.

|                                            | NBTI Stress                                                                          | NBTI Recovery                                                                         |

|--------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| $\tau_{i}$                                 | <i>i-th</i> trapped hole<br>creation time                                            | <i>i-th</i> trapped hole<br>emission time                                             |

| mean of $log(\tau)$<br>(< $log(\tau)$ >)   | $<\log(\tau_1) >= -3.572$<br>$<\log(\tau_2) >= -1.885$<br>$<\log(\tau_3) >= -0.906$  | $<\log(\tau_1) >= -1.009$<br>$<\log(\tau_2) >= 0.036$<br>$<\log(\tau_3) >= 1.074$     |

| standard deviation of $log(\tau) (\sigma)$ | $\sigma_1 = 1.436$<br>$\sigma_2 = 1.379$<br>$\sigma_3 = 1.282^{\circ}$               | $\sigma_1 = 1.070$<br>$\sigma_2 = 1.181$<br>$\sigma_3 = 1.285$                        |

| distinctive features                       | $< \log(\tau_i) > - < \log(\tau_1) >$ $= n \log(i)$ $\sigma_1 > \sigma_2 > \sigma_3$ | $< log(\tau_{i+1}) > - < log(\tau_i) >$ $= constant$ $\sigma_3 > \sigma_2 > \sigma_1$ |

Fig. 2.5 Effective activation energy distributions extracted from measured trap creation times,  $\tau_1$ ,  $\tau_2$  and  $\tau_3$ . The solid line represents a Gaussian-distribution fit to the  $E_{eff}$  translated from  $\tau_1$ .

Fig. 2.6 NBTI induced  $\Delta V_t$  versus number of trapped holes in a device at a stress time of 0.5sec (a) and 5sec (b). Each data point represents a device. The slope of a straight line represents an average  $\Delta v_t$  caused by a single trapped hole.

Fig. 2.7 The mean of the  $\Delta V_t$  distribution versus NBTI stress time from measurement and from our model.

Fig. 2.8 The variance of the  $\Delta V_t$  distribution versus NBTI stress time from measurement and from our model.

Fig. 2.9 A Monte Carlo simulation flowchart. *M* is the number of precursors in a device. A precursor density of  $1 \times 10^{12}$  cm<sup>-2</sup> is assumed.

**Fig. 2.10** Monte Carlo generated  $\tau_i$  distributions. Only *i*=1 to 4 are shown in figure.

**Fig. 2.11** Trapped charge creation time distributions from measurement (symbols) and from Monte Carlo simulation (lines) after the re-ordering. The Monte Carlo simulated  $\langle \log(\tau_2) \rangle - \langle \log(\tau_1) \rangle$  is 1.68 and  $\langle \log(\tau_3) \rangle - \langle \log(\tau_1) \rangle$  is 2.67.

Fig. 2.12 Complementary cumulative distribution functions (1-CDF) of NBTI induced  $\Delta V_t$  from measurement and from our model. The stress time is 0.01sec, 1sec and 100sec, respectively. The inset shows the probability distributions of  $\Delta V_t$  from measurement and this model.

Fig. 2.13 Comparison of NBTI induced  $\Delta V_t$  distributions (1-CDF) calculated from this model and from the Poisson model. The dots are measurement result. The inset shows trapped charge number distributions from the two models. The stress time is 100 sec.

# Chapter 3

# Statistical Characterization and Modeling of a $\Delta V_t$ Distribution and Its Temporal Evolutions in NBTI Recovery

# **3.1 Preface**