# 國立交通大學

電機與控制工程學系

碩士論文

混合訊號前端積體電路應用於可攜式生醫訊號擷取系統

# A CMOS Mixed-Signal Front-End IC for Portable Biopotential Acquisition System

研究生: 余介恩

指導教授:林進燈 博士

周志成 博士

中華民國 九十八 年 六 月

#### 混合訊號前端積體電路應用於可攜式生醫訊號擷取系統

# A CMOS Mixed-Signal Front-End IC for Portable Biopotential Acquisition System

研究生: 余介恩 Student: Jie-En Yue

指導教授:林進燈 博士 Advisor: Dr. Chin-Teng Lin

周志成 博士 Dr.Chi-Cheng Jou

國立交通大學

電機與控制工程學系

Submitted to Department of Electrical and Control Engineering

College of Electrical Engineering

National Chiao Tung University

in Partial Fulfillment of the Requirements

for the Degree of Master

in

Electrical and Control Engineering

June 2008

Hsinchu, Taiwan, Republic of China

中華民國 九十八 年 六 月

#### 混合訊號前端積體電路應用於可攜式生醫訊號擷取系統

研究生:余介恩 指導教授:林進燈 博士

周志成 博士

國立交通大學電機與控制工程研究所

## 中文摘要

在人體所有的生理訊號中,其訊號振幅皆非常微弱,亦容易被受測者本身、量測環境及設備等因素所影響,故本論文提出適用於各種電生理訊號擷取之晶片設計。除了一般著重的低功率、低雜訊之外,同時提高共模訊號拒斥比(CMRR)與電源漣波拒斥比(PSRR),並將整體多通道前端電路整合實現在單一晶片上,不需要任何外接元件,除了兼具成本與晶片面積效益,亦可降低因複雜的接線對生理訊號在量測時所造成的干擾,使後端處理及分析的訊號品質能夠更為精確。另外,在系統加入了數位控制介面,根據不同生理訊號的需求,利用數位訊號去控制選擇所要的訊號放大倍率與系統頻寬。

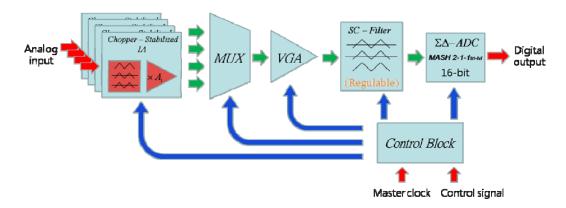

本論文所設計的生理訊號擷取晶片包含:截波穩定式儀表放大器(CHS-IA)、類比多工器、切換式電容低通濾波器(SC-LPF)、非重疊時脈產生器(Non-Overlapping Clock Generator)、切換電容式可變增益訊號放大器(SC-VGA)及多級雜訊移頻三角積分類比/數位轉換器(MASH 2-1-1 tri-level  $\Sigma\Delta$  ADC)等電路。整個電路設計使用 TSMC  $0.18\mu m$  CMOS 1P6M 製程技術來實現,而整體晶片面積為  $1.9198 \times 1.9198 \ mm^2$ 。由模擬結果顯示,在頻率 1024Hz 下,可獲得訊雜比  $90 \ dB$ , $16 \ d$  元解析度的效能。在操作電壓 1.8V 下,總消耗功率約  $998\mu A$ 。

關鍵字:生理訊號,腦電圖,截波穩定式儀表放大器,切換式電容低通濾波器,切換電容式可變增益訊號放大器,多級雜訊移頻三角積分類比/數位轉換器。

A CMOS Mixed-Signal Front-End IC for Portable

**Biopotential Acquisition System**

Student: Jie-En Yue

Advisor: Dr. Chin-Teng Lin

Dr.Chi-Cheng Jou

Department of Electrical and Control Engineering

National Chiao Tung University

**Abstract**

Due to properties of low-amplitude and non-stationary, most of biomedical

signals are easily influenced by examined persons, measured environment, and

electronic devices. A novel analog circuit design is proposed in this thesis, which is

suitable for various biomedical signal acquisitions. In addition to the consideration of

low power and low noise, the multi-channel mixed-signal front-end integrated circuit

(MSFEIC) is designed. This circuit is realized into a single chip without any external

component. It can not only reduce the number of outer components, but also enhance

a better signal-to-noise ratio enormously. In addition, to select system gain and

bandwidth corresponding to different amplitude and frequency of biomedical signals,

the controllable digital interface is also designed and integrated into MSFEIC.

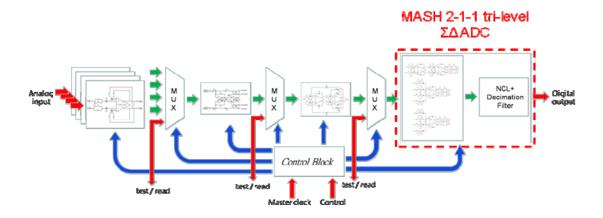

In this thesis, MSFEIC design is composed of four chopper-stabilized

instrumentation amplifiers (CHS-IA), a switched-capacitor variable gain amplifier

(SC-VGA), a switched-capacitor low-pass filter (SC-LPF), a non-overlapping clock

generator, and a cascaded 2-1-1 tri-level sigma-delta analog-to-digital converter

(MASH 2-1-1 tri-level  $\Sigma\Delta$  ADC). These circuits have been integrated into a single

iv

chip of the total area of 1.9198×1.9198*mm*<sup>2</sup> by using TSMC 0.18μm CMOS Mixed-Signal RF General purpose MiM Al 1P6M 1.8&3.3V process. For the simulation results, the proposed chip can achieve 90 dB of SNR, 16-bit resolution at 1024Hz. The total power consumption is about 998μW under 1.8V supply.

**Keyword:** Biomedical signal, chopper-stabilized instrumentation amplifier(CHS-IA), switched-capacitor low-pass filter (SC-LPF), switched-capacitor variable gain amplifier (SC-VGA), MASH 2-1-1 tri-level  $\Sigma\Delta$  ADC.

## 誌謝

本論文的完成,首先要感謝指導教授林進燈博士這兩年來的悉心指導,讓我 學習到許多寶貴的知識,在學業及研究方法上也受益良多。

其次,感謝協助指導資訊媒體實驗室的鍾仁峰博士、范倫達博士,在理論及實作 技巧上給予我相當多的幫助與建議,讓我獲益良多。此外,也衷心的感謝學長姐、 孟修、依伶、寓鈞、煒忠、儀晟、建昇、舒愷、孟哲、俊彥、紹航,同學昕展、 哲睿、有德、家欣的相互砥礪,以及學弟妹育航、智賢、璽文、佩瑄、聖翔在研 究過程中所給我的鼓勵與協助。

最後要感謝家人爸爸、媽媽、妹妹的支持,讓我能專心於學術上的研究,渡過所 有難關,謝謝!

人生值得感謝的人其實很多,感謝老天、感謝許多親人、朋友和同學,在生命的 旅途中,因為有你們,因為我們彼此珍惜、相互扶持,才能有無比的力量。謹以 本論文獻給我的家人及所有關心我的師長與朋友們。

## **Contents**

| 中文摘要                                                                                       |

|--------------------------------------------------------------------------------------------|

| ABSTRACTIV                                                                                 |

| 誌謝V                                                                                        |

| CONTENTSVI                                                                                 |

| LIST OF TABLESIX                                                                           |

| LIST OF FIGURESX                                                                           |

| CHAPTER 1 INTRODUCTION                                                                     |

| 1.1 BACKGROUND                                                                             |

| 1.2 MOTIVATION                                                                             |

| 1.3 THESIS ORGANIZATION                                                                    |

| CHAPTER 2 ARCHITECTURE SURVEY                                                              |

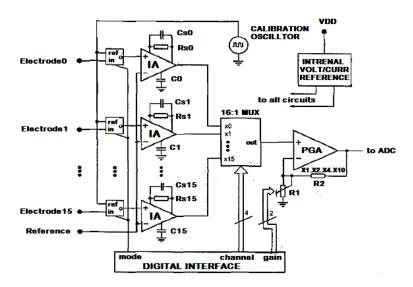

| 2.1 A CMOS IC FOR PORTABLE EEG ACQUISITION SYSTEMS                                         |

| 2.2 A CMOS ANALOG FRONT-END (AFE) IC FOR PORTABLE EEG/ECG MONITORING APPLICATIONS          |

| 2.3 LOW-POWER LOW-NOISE 8-CHANNEL EEG FRONT-END ASIC FOR AMBULATORY ACQUISITION SYSTEMS 15 |

| CHAPTER 3 A CMOS MIXED-SIGNAL FRONT-END IC FOR PORTABLE                                    |

| BIOPOTENTIAL ACQUISITION SYSTEM                                                            |

| 3.1 System Architecture                                                                    |

| 3.2 DESIGN ISSUES                                                                          |

| 3.2.1 Device Electronic Noise                                                              |

| 3.2.2 Charge Injection                                                                     |

| 3.2.3 Switch Body Effect                                                                   |

| 3.     | .2.4 Analog Nonlinearities in Cascaded Modulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 31  |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.3    | CIRCUIT DESIGN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 33  |

| 3.     | .3.1 Chopper-Stabilized Instrumentation Amplifier (CHS-IA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 33  |

| 3.     | .3.2 Switched-Capacitor Variable Gain Amplifier (SC-VGA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 39  |

| 3.     | .3.3 Switched-Capacitor Low-Pass Filter (SC-LPF)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 47  |

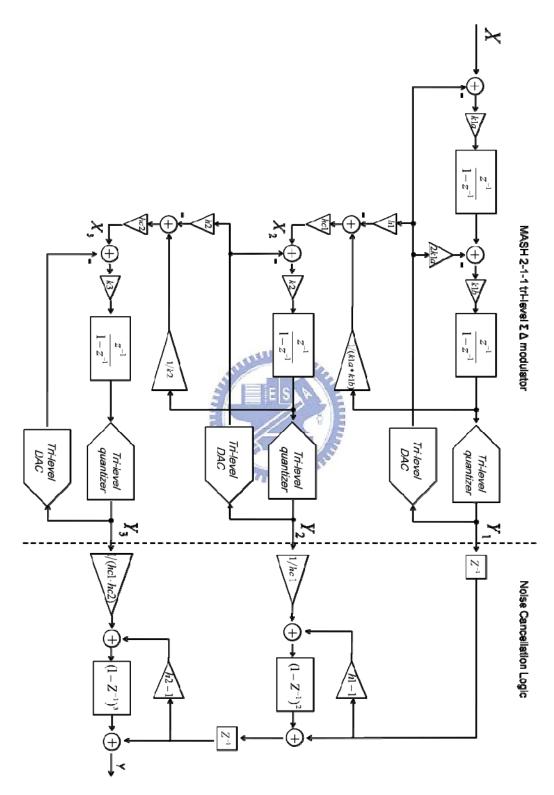

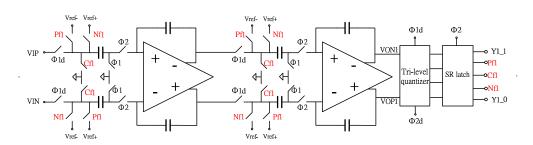

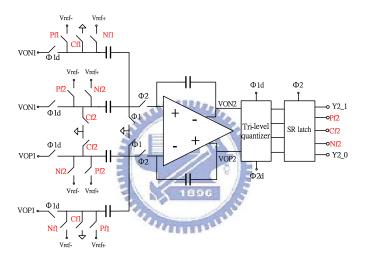

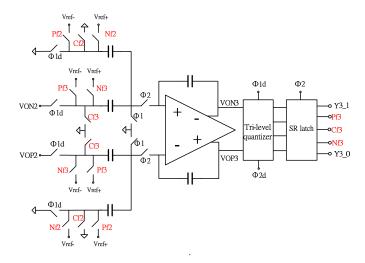

| 3.     | .3.4 MASH 2-1-1 tri-level ΣΔ Modulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 52  |

| 3.     | .3.5 Digital Decimation Filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 63  |

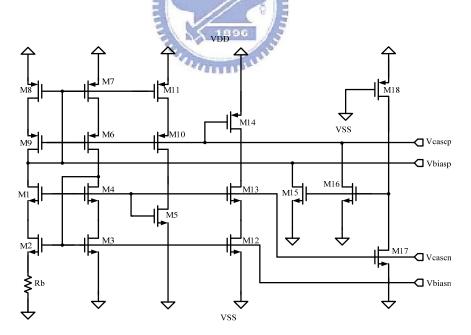

| 3.     | .3.6 Wide-Swing Constant-Gm Cascode Biasing Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 66  |

| СНАР   | PTER 4 CHIP IMPLEMENTATION, VERIFICATION AND T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | EST |

| PLATI  | FORM 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

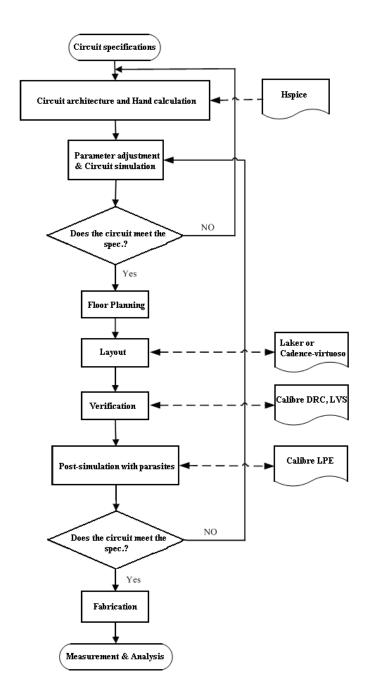

| 4.1    | Decical Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 67  |

| 4.1    | DESIGN FLOW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 07  |

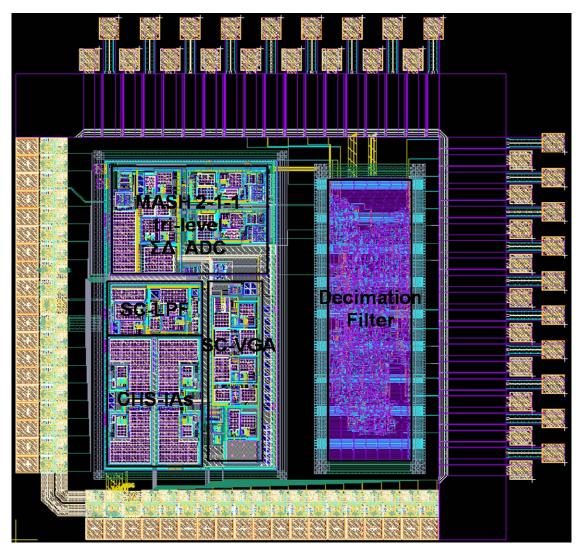

| 4.2    | LAYOUT CONSIDERATION AND IMPLEMENTATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 69  |

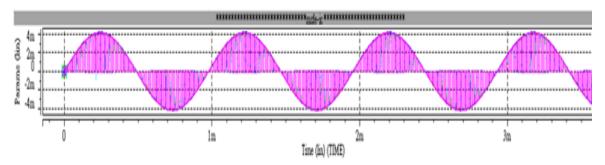

| 4.3    | POST-LAYOUT SIMULATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 71  |

| 4.4    | SPECIFICATION COMPARISON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|        | THE PARTY OF THE P |     |

| 4.5    | TEST PLATFORM DESIGN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 77  |

| СНАР   | PTER 5 CONCLUSIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 79  |

| 5.1    | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 79  |

| 5.2    | Future Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 79  |

| REFEI  | RENCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 80  |

| TCET E |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| APPE   | NDIX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 84  |

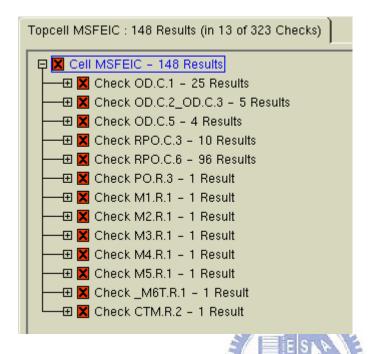

| A. DF  | RC Verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 84  |

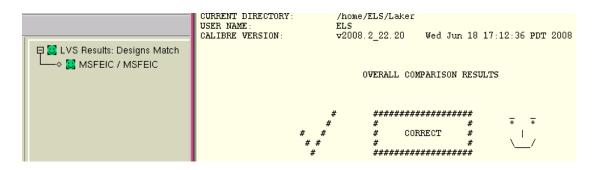

| B. LV  | 'S VERIFICATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 84  |

| C. TAI | PEOUT REVIEW FORM (FOR FULL-CUSTOM IC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 85  |

| D. T   | 'APEOUT REVIEW FORM (FOR CELL-BASED IC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 91  |

# **List of Tables**

| TABLE 1 THE SPECIFICATION OF MSFEIC.                             | 73 |

|------------------------------------------------------------------|----|

| TABLE 2 THE COMPARISON MSFEIC (ANALOG) WITH RELEVANT PAPERS      | 75 |

| Table 3 The comparison $\Sigma\Lambda$ -ADC with relevant papers | 76 |

# **List of Figures**

| FIG. 1-1 TYPICAL SETUP FOR EEG RECORDING.                                                       | 2    |

|-------------------------------------------------------------------------------------------------|------|

| FIG. 1-2 TRADITIONAL EEG RECORDING SYSTEM                                                       | 3    |

| Fig. 1-3 International 10-20 electrode placement system                                         | 4    |

| FIG. 1-4 BIOMEDICAL SIGNALS: AMPLITUDE/FREQUENCY RANGE                                          | 4    |

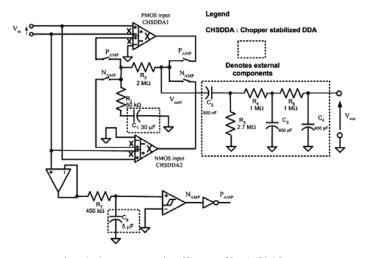

| FIG. 2-1 IC BLOCK DIAGRAM                                                                       | 7    |

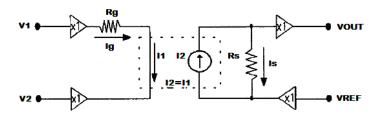

| FIG. 2-2 BLOCK DIAGRAM OF AN IA WITH CURRENT FEEDBACK                                           | 8    |

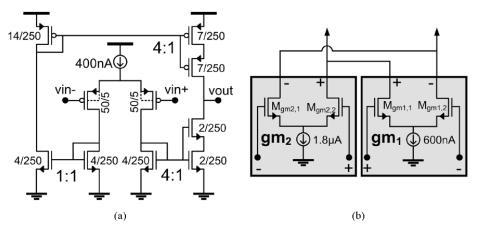

| FIG. 2-3 SIMPLIFIED IA CIRCUIT                                                                  | 9    |

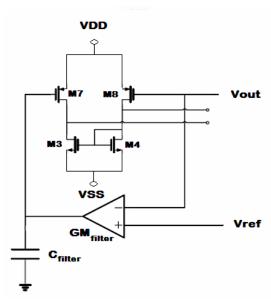

| FIG. 2-4 FEEDBACK LOOK REALIZING THE HIGH PASS FILTER FUNCTION                                  | 9    |

| FIG. 2-5 COMPLETE CIRCUIT OF THE IA                                                             | 10   |

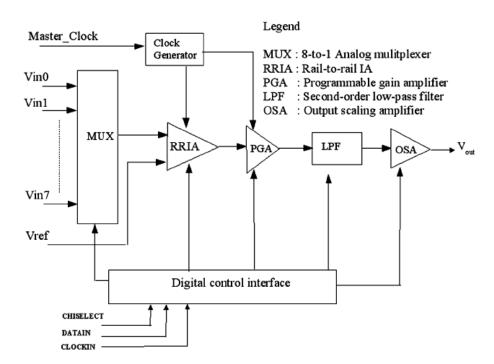

| FIG. 2-6 SYSTEM BLOCK DIAGRAM OF THE PROPOSED AFE IC                                            | 11   |

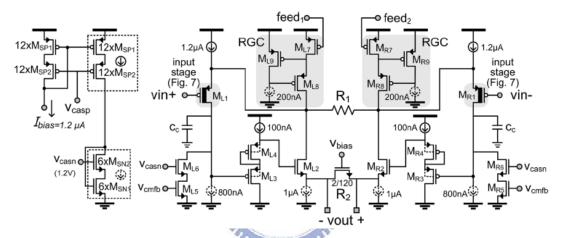

| Fig. 2-7 Non-inverting DDA for use an IA                                                        | 12   |

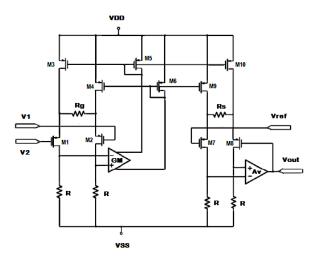

| FIG. 2-8 CIRCUIT SCHEMATIC OF THE PMOS CHSDDA                                                   | 13   |

| Fig. 2-9 Proposed Rail-to-rail IA                                                               | 13   |

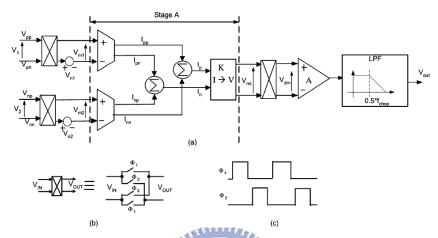

| FIG. 2-10 CHSDDA AND ITS ASSOCIATED CLOCK FOR THE CHOPPING SWITCHES                             | 14   |

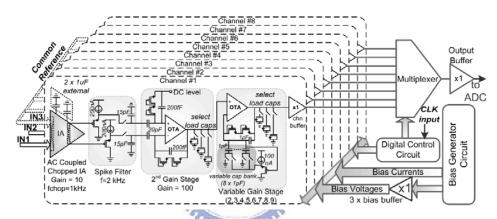

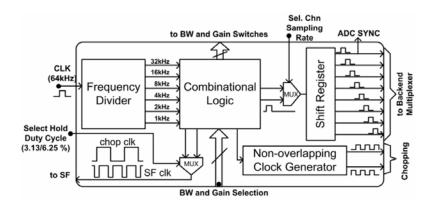

| FIG. 2-11 ARCHITECTURE OF THE IMPLEMENTED 8-CHANNEL EEG FRONT-END ASIC                          | .15  |

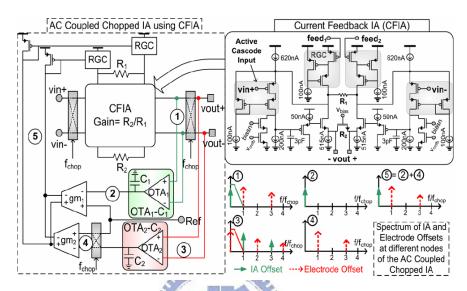

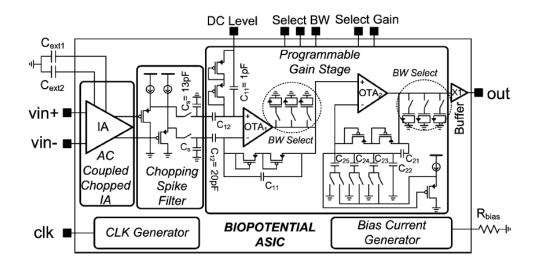

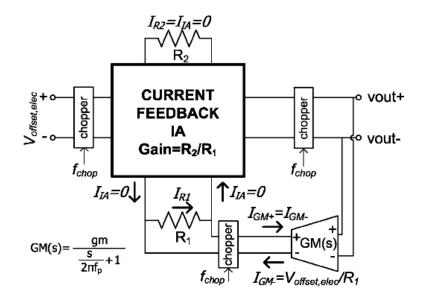

| FIG. 2-12 CFIA ARCHITECTURE AND THE AC COUPLED CHOPPED IA TOPOLOGY                              | 16   |

| FIG. 2-13 BLOCK DIAGRAM OF THE DIGITAL CONTROL CIRCUIT                                          | 16   |

| FIG. 2-14 ARCHITECTURE OF THE BIO-POTENTIAL READOUT FRONT-END FOR THE                           |      |

| ACQUISITION OF EEG, ECG, AND EMG SIGNALS                                                        | 17   |

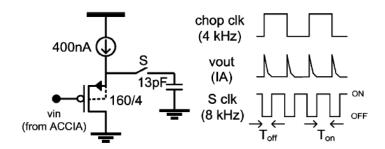

| FIG. 2-15 CONCEPT OF THE ACCIA                                                                  | 18   |

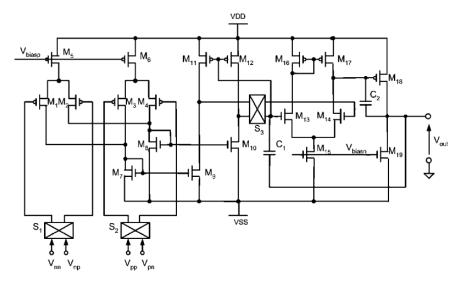

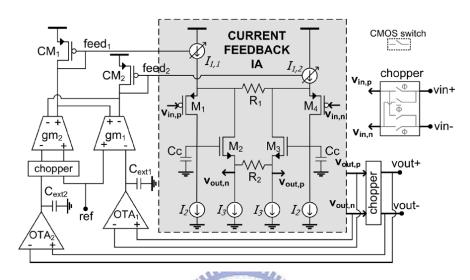

| FIG. 2-16 ACCIA IMPLEMENTED CIRCUIT                                                             | 19   |

| Fig. 2-17 Schematic of OTA : (a) $OTA_1$ - $C_{EXT1}$ and $OTA_2$ - $C_{EXT2}$ implemented circ | CUIT |

| (B) GM <sub>1</sub> AND GM <sub>2</sub> IMPLEMENTED CIRCUIT                                     | 19   |

| FIG. 2-18 SCHEMATIC OF CURRENT FEEDBACK IA IS USED IN ACCIC IMPLEMENTATIO                       | )N   |

|                                                                        | 20         |

|------------------------------------------------------------------------|------------|

| FIG. 2-19 SCHEMATIC OF CSF AND OPERATION PRINCIPLE                     | 20         |

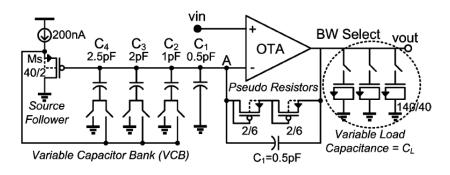

| Fig. 2-20 Schematic of the VGA                                         | 21         |

| FIG. 3-1 THE SIGNAL FLOW GRAGH OF MSFEIC                               | 23         |

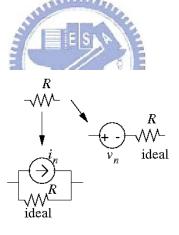

| FIG. 3-2 RESISTOR NOISE MODEL                                          | 25         |

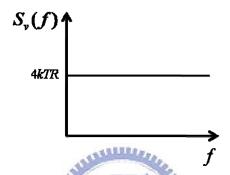

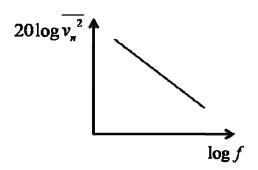

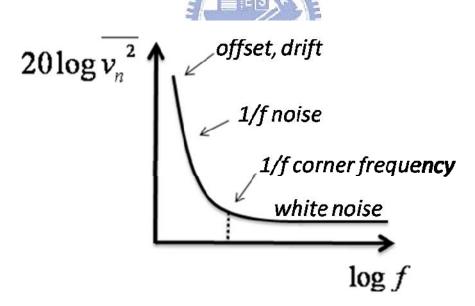

| FIG. 3-3 NOISE ONE-SIDED SPECTRAL DENSITY                              | 26         |

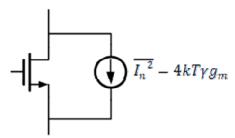

| FIG. 3-4 THERMAL NOISE OF A MOSFET                                     | 26         |

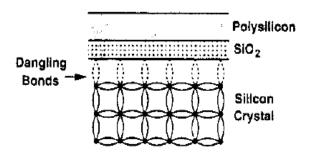

| FIG. 3-5 DANGLING BONDS AT THE OXIDE-SILICON INTERFACE                 | 27         |

| FIG. 3-6 FLICKER NOISE SPECTRUM                                        | 28         |

| FIG. 3-7 CONCEPT OF NOISE                                              | 28         |

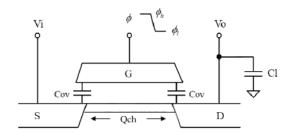

| FIG. 3-8 NON-IDEAL EFFECTS OF MOSFET SWITCH.                           |            |

| FIG. 3-9 CMOS SWITCH CONFIGURATION.                                    | 30         |

| Fig. 3-10 A cascaded fourth-order (2-1-1) modulator general form w     |            |

| ANALOG NONIDEALITIES.                                                  | 31         |

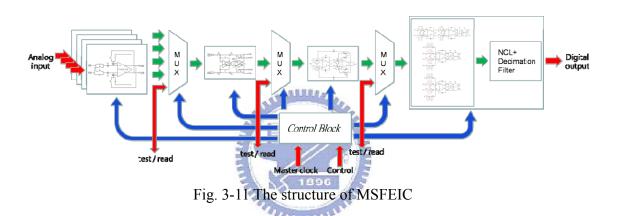

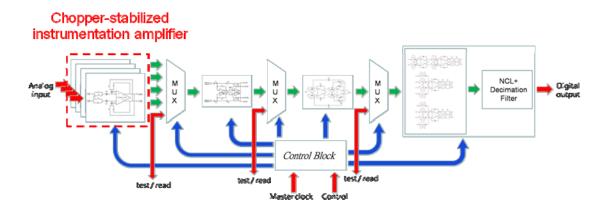

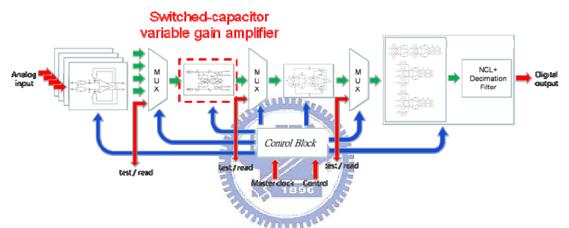

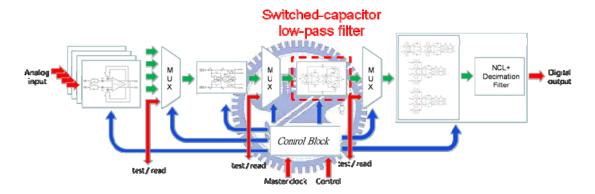

| Fig. 3-11 The structure of MSFEIC                                      | 33         |

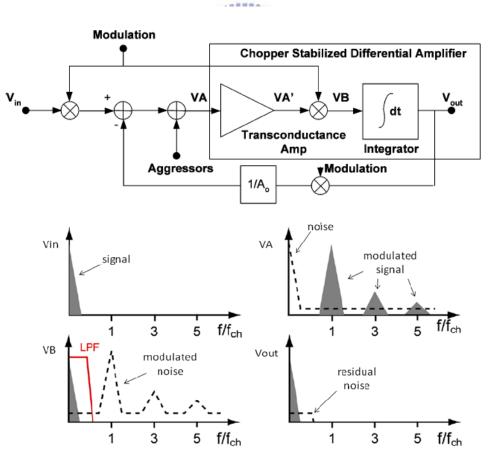

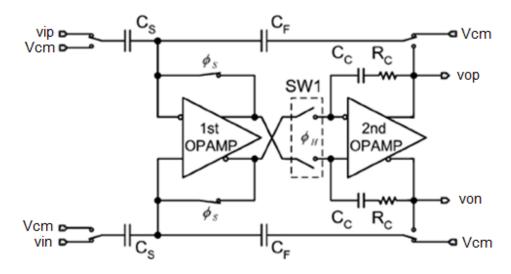

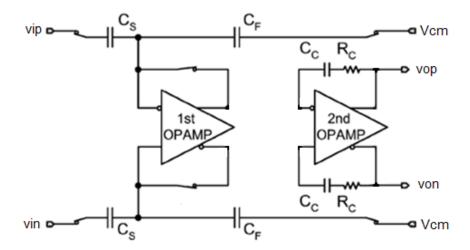

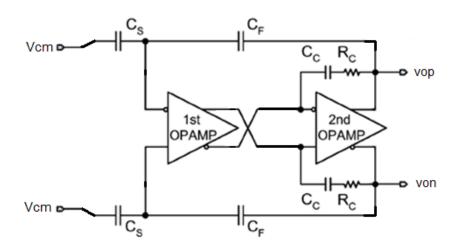

| FIG. 3-12 THE SIGNAL FLOW GRAGH OF CHS-IA                              | 34         |

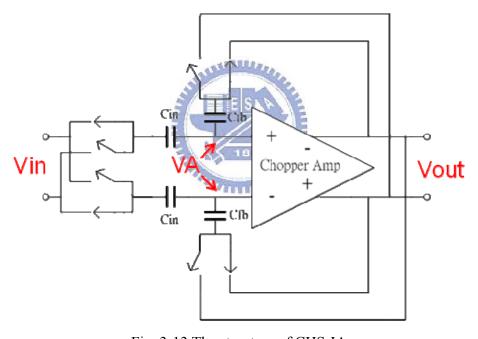

| FIG. 3-13 THE STRUCTURE OF CHS-IA.                                     | 35         |

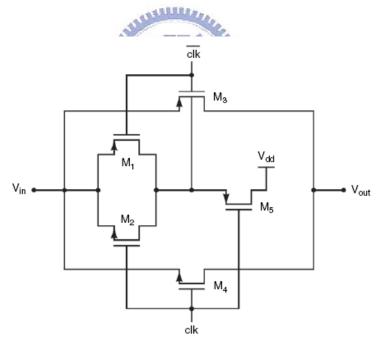

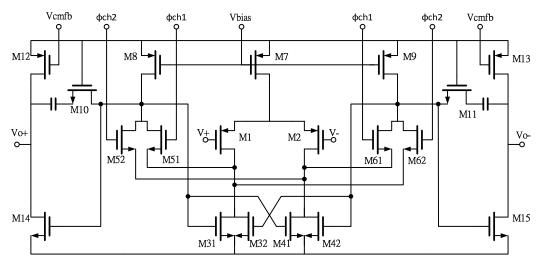

| Fig. 3-14 Chopper amplifier (Two stage amplifier with chopper switch   | ı)36       |

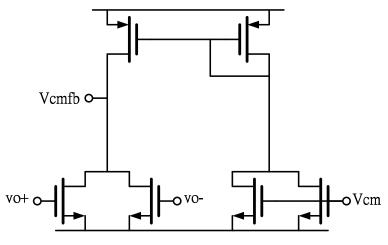

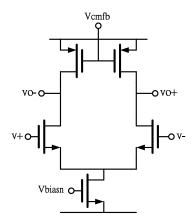

| FIG. 3-15 ACTIVE CMFB                                                  | 37         |

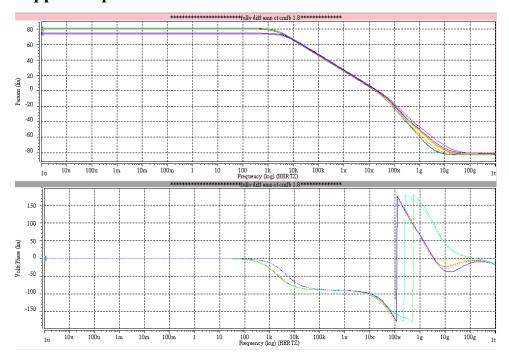

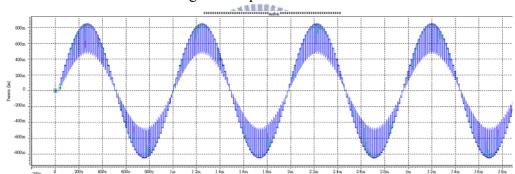

| FIG. 3-16 PRE-LAYOUT SIMULATION OF CHOPPER AMPLIFIER (CORNERS: TT, SS  | S, FF, FS, |

| SF Temperature: 0°C~100°C Power supply: 1.8V±10%)                      | 37         |

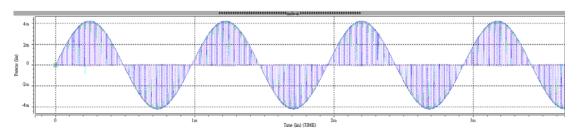

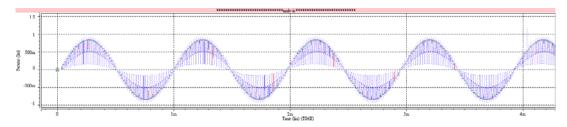

| Fig. 3-17 The output of CHS-IA in time-domain (Corners: TT, SS, FF, FS | S. SF      |

| Temperature: 0°C~100°C Power supply: 1.8V±10%)                         |            |

| TEM ERMORE. V 100 110 TOWER BOTTET. 1.0 V + 10/0j                      | 50         |

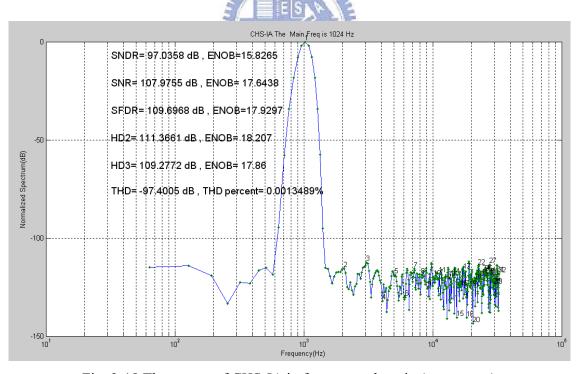

| FIG. 3-18 THE OUTPUT OF CHS-IA IN FREQUENCY-DOMAIN (WORST CASE)        | 38         |

| FIG. 3-19 THE STRUCTURE OF SC-VGA                                          | .40 |

|----------------------------------------------------------------------------|-----|

| Fig. 3-20 SC-VGA in sample phase $\Phi_{s}$                                | .41 |

| FIG. 3-21 SC-VGA IN HOLD PHASE $\Phi_{\mathbb{H}}$                         | .41 |

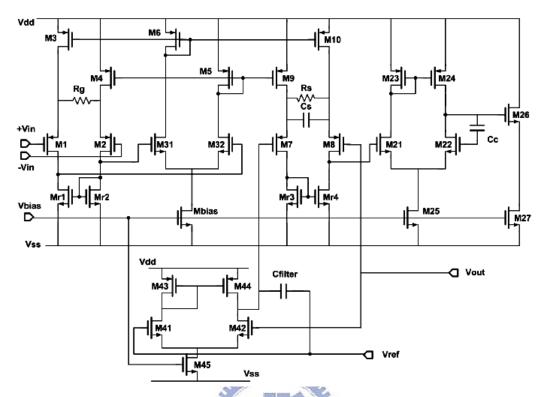

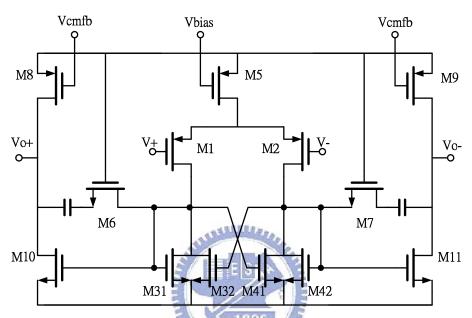

| FIG. 3-22 THE OPAMP USED IN SC-VGA                                         | .43 |

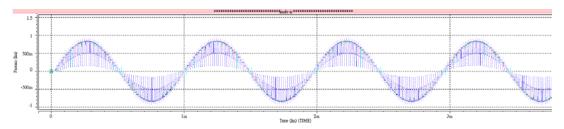

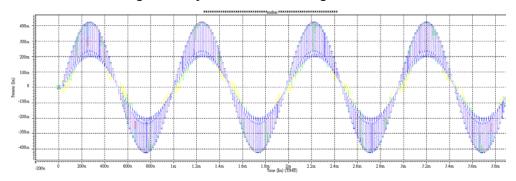

| FIG. 3-23 THE OUTPUT OF SC-VGA IN TIME-DOMAIN (GAIN=46 DB) (CORNERS: TT, S | SS, |

| FF, FS, SF TEMPERATURE: 0°C~100°C POWER SUPPLY:1.8V±10%)                   | .44 |

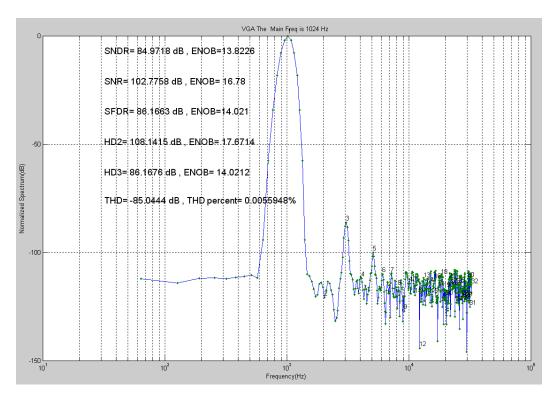

| Fig. 3-24 The output of SC-VGA in frequency-domain (gain=46 dB) (worst     |     |

| CASE)                                                                      | .44 |

| Fig. 3-25 The output of SC-VGA in time-domain (gain=40 dB) (Corners: TT, S | SS, |

| FF, FS, SF TEMPERATURE: 0°C~100°C POWER SUPPLY: 1.8V±10%)                  | .45 |

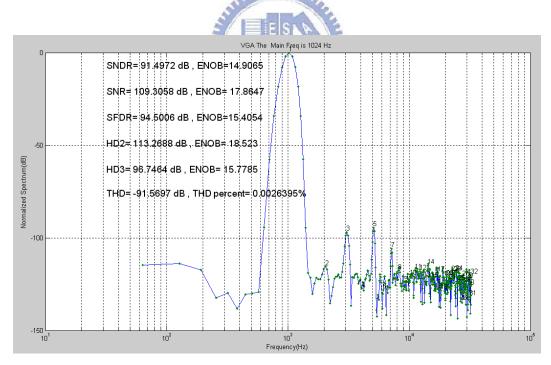

| FIG. 3-26 THE OUTPUT OF SC-VGA IN FREQUENCY-DOMAIN (GAIN=40 DB) (WORST     |     |

| CASE)                                                                      | .45 |

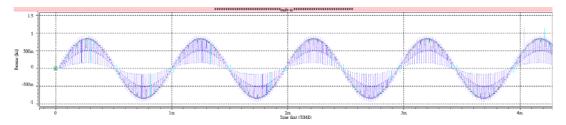

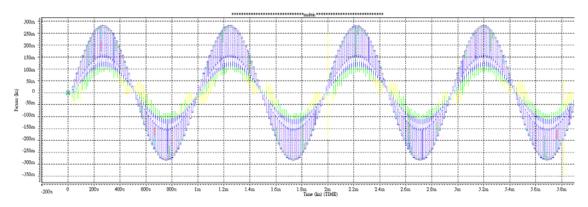

| FIG. 3-27 THE OUTPUT OF SC-VGA IN TIME-DOMAIN (GAIN=34 DB) (CORNERS: TT, S | SS, |

| FF, FS, SF TEMPERATURE: 0°C~100°C POWER SUPPLY: 1.8V±10%)                  | .46 |

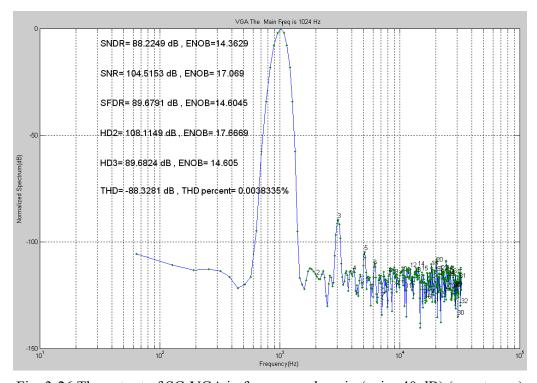

| FIG. 3-28 THE OUTPUT OF SC-VGA IN FREQUENCY-DOMAIN (GAIN=34 DB) (WORST     |     |

| CASE)                                                                      | .46 |

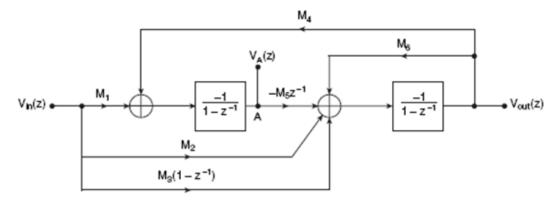

| FIG. 3-29 THE SIGNAL FLOW GRAGH OF SC-LPF                                  | .48 |

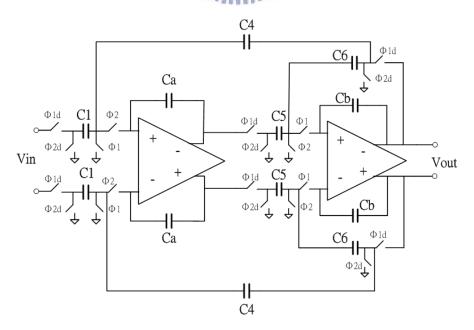

| FIG. 3-30 LOW-Q SC-LPF WITH SWITCHED-SHARING                               | .49 |

| FIG. 3-31 THE OUTPUT OF SC-LPF IN TIME-DOMAIN (CORNERS: TT, SS, FF, FS, SF |     |

| Temperature: 0°C~100°C Power supply: 1.8V±10%)                             | .50 |

| FIG. 3-32 THE OUTPUT OF SC-LPF IN FREQUENCY-DOMAIN (WORST CASE)            | .51 |

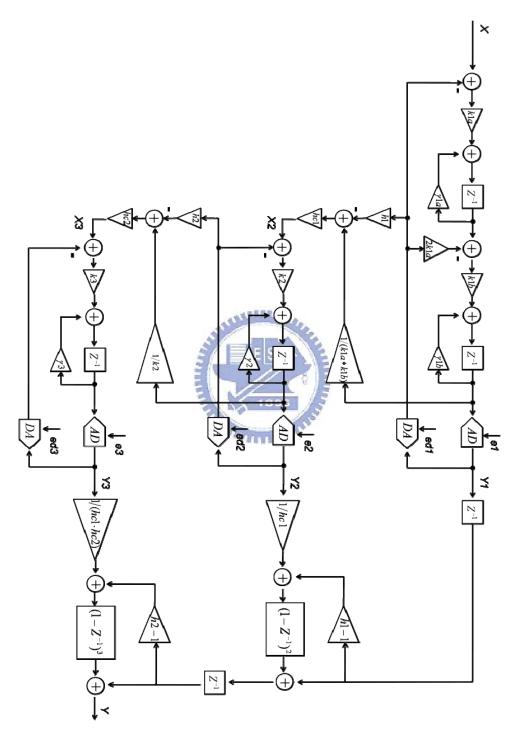

| Fig. 3-33 MASH 2-1-1 tri-level ∑∆ modulator with noise cancellation logic  | С   |

|                                                                            | .53 |

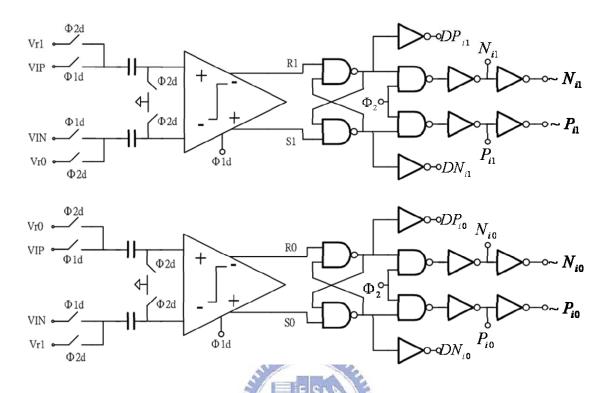

| Fig. 3-34 The SC diagram of MASH 2-1-1 tri-level $\Sigma\Delta$ modulator       | 55 |

|---------------------------------------------------------------------------------|----|

| Fig. 3-35 Tri-level quantizer and SR-latch ( $i=1\sim3$ )                       | 57 |

| Fig. 3-36 The output and feedback control signal ( $i=1\sim3$ ) of each stage   | 57 |

| FIG. 3-37 TWO STAGE OPERATIONAL AMPLIFIER                                       | 58 |

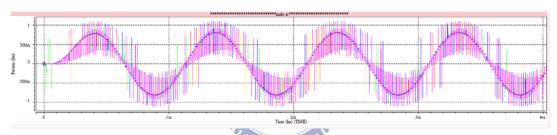

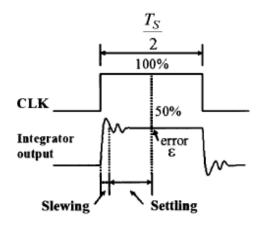

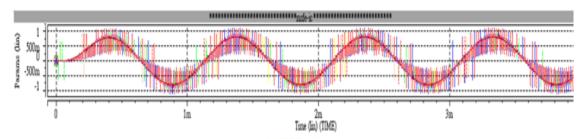

| FIG. 3-38 THE TRANSIENT BEHAVIOR FOR THE MODULATOR.                             | 59 |

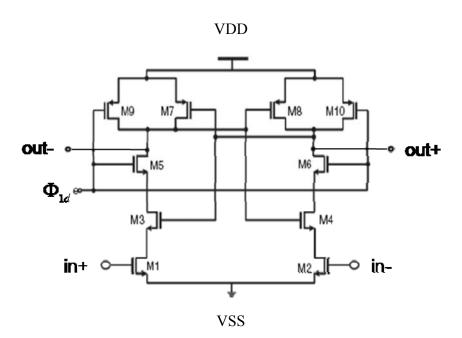

| FIG. 3-39 COMPARATOR.                                                           | 60 |

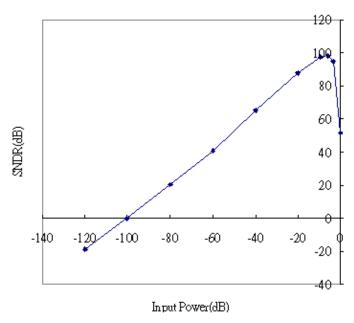

| FIG. 3-40 PLOT OF SIMULATED SNDR VERSUS INPUT LEVEL                             | 61 |

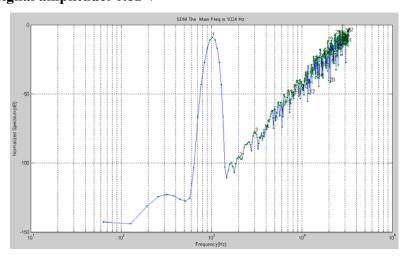

| Fig. 3-41 Output PSD of MASH 2-1-1 tri-level $\Sigma\Delta$ modulator at 64 kHz |    |

| SAMPLING RATE                                                                   | 61 |

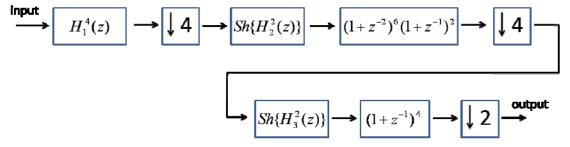

| FIG. 3-42 SIGNAL FLOW GRAGH OF DIGITAL DECIMATION FILTER                        | 64 |

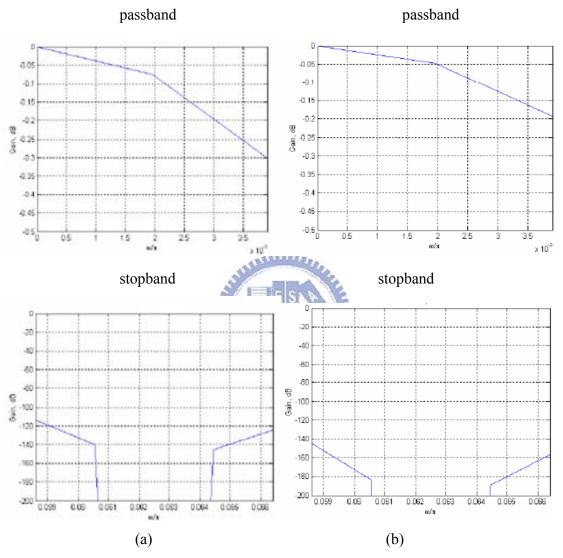

| FIG. 3-43 MAGNITUDE RESPONSE OF DECIMATION FILTER                               | 65 |

| Fig. 3-44 The architecture of the biasing circuit.                              | 66 |

| Fig. 4-1 Design flow                                                            | 68 |

| FIG. 4-2 COMPLETE MSFEIC LAYOUT.                                                | 70 |

| FIG. 4-3 OUTPUT OF CHS-IA                                                       | 71 |

| FIG. 4-4 OUTPUT OF SC-VGA FOR GAIN=72 DB                                        | 71 |

| FIG. 4-5 OUTPUT OF SC-VGA FOR GAIN=66 DB                                        | 71 |

| FIG. 4-6 OUTPUT OF SC-VGA FOR GAIN=60 DB                                        | 72 |

| FIG. 4-7 OUTPUT OF SC-LPF                                                       | 72 |

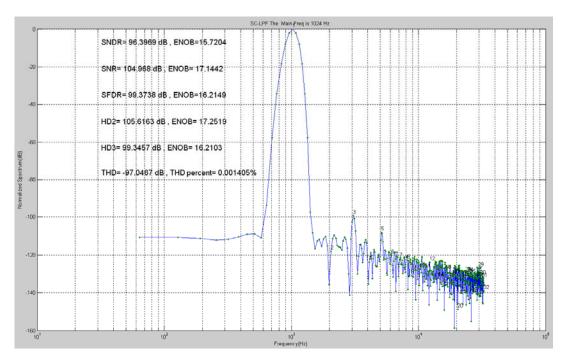

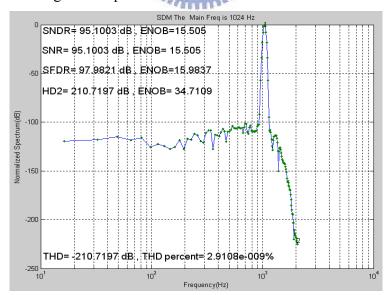

| Fig. 4-8 output of MASH 2-1-1 tri-level $\Sigma\Delta$ -ADC                     | 72 |

| FIG. 4-9 PSD OF SYSTEM OUTPUT.                                                  | 72 |

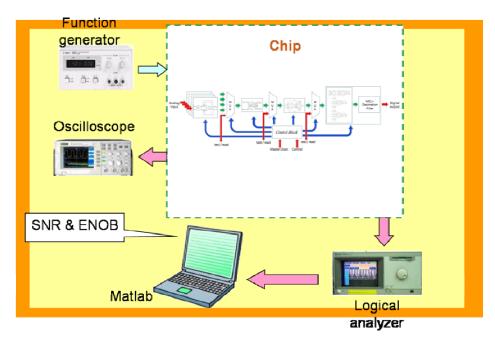

| FIG. 4-10 TEST PLATFORM.                                                        | 78 |

## **Chapter 1 Introduction**

#### 1.1 Background

The medical application of science and microelectronic technology recently has made significantly advances, thus improving human quality of life. Biomedical instruments are crucial in modern life. The biomedical signal acquisition instrument has already developed years ago. However, the amplitude of the biomedical signals is all very weak. Biomedical signals are very easy to be influenced by testing environment and biomedical signals of the person who examined. These effects make recording biomedical signals become more and more difficult. Among them, the interferences of the testing environment are including the temperature and humidity of the electronic components, capacity effect of the pads, power supply variation, electromagnetic wave, digital noise, etc. The interferences of the biomedical signals are including electroencephalogram (EEG), electro-oculogram (EOG), electromyography (EMG), electrocardiogram (ECG), respiration, perspiration, etc. Therefore, we should amplify measured biomedical signals effectively and restrain noise by an analog front-end (AFE) circuit.

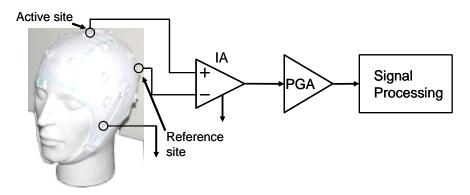

By a mixed-signal front-end (MSFE) circuit, the processed biomedical signals input a digital signal processor (DSP) and analyzed. Amplifying the measured signals and restraining noise play important parts of the biomedical signal acquisition system. Fig. 1-1 shows the typical setup for an EEG recording system which comprises the instrumentation amplifier (IA) as analog front-end (AFE), the programmable gain amplifier (PGA) for boosting the acquired EEG signal to levels for further analog signal processing [1]. Hence, the specification of analog front-end circuit affects the performance of the system directly.

Fig. 1-1 Typical setup for EEG recording

The instrumentation amplifier [2][3][4][5] has already been used in the analog front-end circuit of the biomedical signals recording system widely. The greatest advantages are effective restraining noise such factors as the measuring environment, electrical electrode, etc. and amplifying the weak biomedical signals to observable signals. Therefore, noise interference cannot lead to the signals distortion. Since all biomedical signals are low frequency signals, and the frequency of the noise is usually higher than the biomedical signals, the circuit in this study has a low-pass filter after an instrumentation amplifier. The low-pass filter goes one step future to get rid of noise [5][6][7] to assure the quality of the signals.

This research is the first stage in the biomedical signal acquisition and analysis system, so the performance of gain and restraining noise is extremely important. Its result will influence the efficiency of the whole system. The first generation analog front-end circuit of the biomedical signal recording system has been developed in our laboratory, and has already been accepted by 2008 IEEE International Symposium on Circuits and Systems [8]. This research direction and achievement are received the affirmation by the international academia. We will be devoted to this future development of the research base on the research results.

#### 1.2 Motivation

Medical treatment progresses more and more in recent years. Besides improving the medical technology that has already had, gradually paying attention to the important representative information of biomedical signals is sent out from our body each position. Examine and analyze these biomedical signals can go a step future to find out about the state of the body.

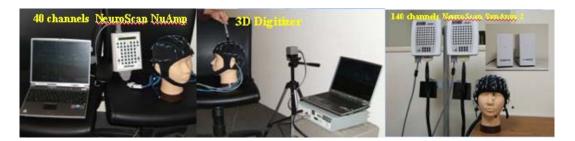

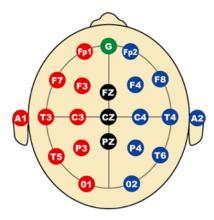

Giving an example of EEG, analyzing the potential signal of human brain is researched from Berger. Proposed in 1920. EEG is produced by many accumulated current of nerve cells under cerebral cortex. Through the research of decades, we can learn the state of mind of the persons who are examined EEG from the measured results [9][10]. Nevertheless, complicated EEG signals can be few processed to study. Computer operation is faster and faster in speed and the algorithms are progressing excellently in recent years, so processing measured EEG signals is enough for real-time. People pay attention to the discussion of human spiritual information gradually. The traditional EEG recording system is shown in Fig. 1-2. This system is composed of an international 10-20 electrode placement system as Fig. 1-3, a biomedical signal amplifier, an analog-to-digital converter (ADC), and a computer. Because the instrument of recording and analyzing is very bulky, it is very inconvenient to use. The difficult problems of reducing systematic volume and simplifying difficulty use of the system should be overcome.

Fig. 1-2 Traditional EEG recording system

Fig. 1-3 International 10-20 electrode placement system

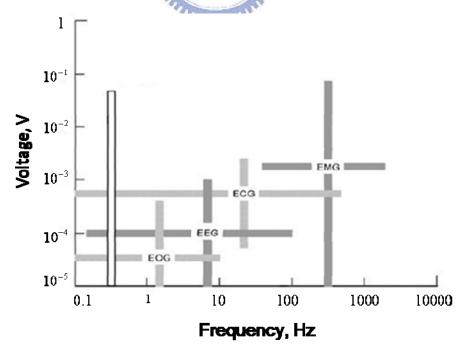

Generally, the commonly used biomedical signals of body have the characteristics illustrated in Fig. 1-4 and Table 1-1, including EEG, EOG, EMG, and ECG. Biomedical signals are all distributed over ultra-low amplitude and ultra-low frequency, so they are hard to process. For this reason, how to receive and amplify the real biomedical signals that are not distortion is an important issue in this study. Its frequency or amplitude is not a constant value even if it is the same kind of biomedical signals. So the signals must have different bandwidth and different voltage gain.

• Fig. 1-4 Biomedical signals: amplitude/frequency range

Table 1-1 The characteristics of biomedical signals

| Biomedical signal | Amplitude distribution | Frequency distribution |

|-------------------|------------------------|------------------------|

| EEG               | 1μV~100μV              | DC~150Hz               |

| ECG               | 100μV~10mV             | 0.01Hz~250Hz           |

| EOG               | 10μV~10mV              | DC~100Hz               |

| EMG               | 10μV~10mV              | 20Hz~1kHz              |

Furthermore, the use of very large scale integrated circuits (VLSI) dominates medical electronics applications, which range from small, battery-powered electronic implants to room-filling diagnostic imaging systems [11]. As in other VLSI applications, the design and processing of the technology chosen for medical devices depends on the specific applications involved. Product complexity, size, sales volume, cost objectives, and available power source all play significant roles in the specific process [12]. The fabrication of VLSI may be based on the bipolar, CMOS or BiCMOS technologies. However, portable instruments and implantable products, where low power consumption is a necessity, primarily use CMOS devices. CMOS technology has become popular in the last few years for implementing complex circuits and systems. The integration of the AFE circuit and other processing units on the same chip has brought a new era in biomedical systems [13][14][15]. The cost of electronic instruments is proportional to their size, the number of devices and interconnections they contain. VLSI circuits have done a great deal to reduce size, components, and interconnections, and thus the cost of the products that contain them.