verse resonance condition, we know that the sum of the immittances across X-X must equal zero, and can obtain the following equations:

(a) For odd TE<sub>m0</sub> modes:

$$\frac{b-d-t}{B_3 Z_1(b-d-t)-b \left| \tan \left[ \frac{\pi(s-w)}{\lambda_c} \right] \right|} + \frac{d}{B_2 Z_1 d + b \tan \left( \frac{s\pi}{\lambda_c} \right)} - \tan \left[ \frac{\pi(a-s)}{2} \right] = 0$$

(1)

(b) For even TE<sub>m0</sub> modes:

$$\frac{b-d-t}{B_3 Z_1 (b-d-t) - b / \tan \left[ \frac{\pi (s-w)}{\lambda_c} \right]} + \frac{d}{B_2 Z_1 d - b / \tan \left( \frac{\pi s}{\lambda_c} \right)} - \tan \left[ \frac{\pi (a-s)}{\lambda_c} \right] = 0$$

(2)

The discontinuity susceptance terms  $B_2 Z_1$  and  $B_3 Z_1$  are obtainable from Reference 3.

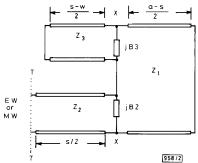

Fig. 2 Equivalent circuit of single T-septum guide

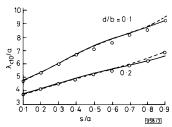

Fig. 3 Normalised cutoff wavelength of dominant mode in STSG b/a = 0.45, w/a = 0.1, t/b = 0.05Reference 2 -

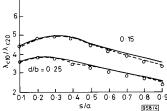

Fig. 4 Bandwidth characteristics of STSG b/a = 0.45, w/a = 0.1, t/b = 0.05• Reference 1 ---- Reference 2

A similar procedure was carried out for the double Tseptum guide (DTSG); the equivalent circuit and equations obtained are omitted

Numerical results: Numerical results for the cutoff wavelength of the dominant  $TE_{10}$  mode and bandwidth characteristics for the STSG are shown in Figs. 3 and 4, respectively. Results obtained by the Ritz-Galerkin technique<sup>1</sup> and the transmission line modelling method<sup>2</sup> are also included in Figs. 3 and 4; we can see that they are in good agreement.

Z. X. SHEN X. M. LOU S. F. LI 26th September 1989

Research Institute of Microwave Techniques Southeast University Nanjing, Jiangsu, People's Republic of China

- 1 MAZUMDER, G. G., and SAHA, P. K.: 'Rectangular waveguide with T-shaped septa', IEEE Trans., 1987, MTT-35, pp. 201-204

- 1-snapeu sepila, IEEE Trans., 1987, WIT-35, pp. 201-204

GEMMAN, F. J., and RIGSS, L. S.: 'Bandwidth properties of rectangular T-septum waveguides', ibid., 1989, MTT-37, pp. 917-919

MARCUWITZ, N.: 'Waveguide handbook' (McGraw-Hill, NY, 1951)

HOPFER, S.: 'The design of ridged waveguides', IRE Trans., Oct. 1955, MTT-33, pp. 20-29

## SIMPLE IMPLEMENTATION OF LOAD-SHARING BANYAN NETWORK AND ITS THROUGHPUT PERFORMANCE

Indexing terms: Telecommunications, Networks, Communication networks, Switching, Load-sharing banyan networks, Sorting cells, Routing cells

An implementation of a load-sharing banyan network based an implementation of a load-similing buryan network based on sorting and routing cells is proposed. Our implementation requires simple management and is easy to diagnose. An iterative algorithm is derived to analyse the throughput performance of the proposed load-sharing banyan network.

Introduction: Because of the properties such as self-routing and potential VLSI implementation, banyan networks are widely considered to construct the switching fabric in communication networks and to interconnect processing elements and memory modules in multiprocessor systems. In reality, it was proved1 that banyan networks are more cost-effective than crossbars for large systems. Unfortunately, banyan net-works are blocking, meaning that multiple connection requests between arbitrary pairs of inlets and outlets may not be granted simultaneously. As a result, the performance for a large banyan network may not be acceptable.

Lea<sup>2</sup> proposed the load-sharing concept to improve the per-formance of banyan networks. However, no implementation was considered. In this letter we propose a simple implementation based on two basic cells, the sorting cell and the routing cell. The sorting cell is nothing but a bitonic sorter<sup>3</sup> with two inputs, and the routing cell is a usual  $2 \times 2$  switching cell of a banyan network. The throughput performance of the proposed implementation is analysed under the uniform traffic

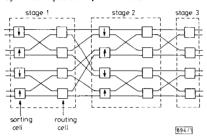

Implementation: A three-stage load-sharing banyan network is illustrated in Fig. 1. It is noted that the connection pattern between stages shown in Fig. 1 is for the baseline<sup>4</sup> network. However, since the baseline network is topologically equivalent to the banyan network, we do not distinguish between these two terms in this letter. Basically, a load-sharing banyan network is constructed by inserting sorting cells into a banyan network. For the *n*-stage load-sharing banyan network we propose, the routing cells in each stage, except the last one, are partitioned into  $2^{n-2}$  groups so that each group consists of two routing cells. If we use binary sequences of length n-1

to represent, from top to bottom, the routing cells in each stage, then two routing cells in stage i  $(1 \le i \le n-1)$  are in the same group if their representations differ only in the last bit. It is not hard to see that two routing cells belonging to the same group share their loads. Moreover, our implementation is simple because the connections inside the two building blocks are both bit-controlled and hence high-speed switching is achievable. Finally, since the connection patterns of the sorting cell and the routing cell of the load-sharing banyan network are the same, any single fault can be easily diagnosed by the techniques developed in Reference 5.

Fig. 1 Three-stage load-sharing banyan network

Throughput performance: To analyse the average throughput of the load-sharing banyan network we propose, the four input links (to sorting cells) of a pair of routing cells of the same group should be considered together. For convenience, the two input links of the upper (or lower) sorting cell are called the upper (lower) input links of a pair of routing cells. Similarly, the four output links of a pair of routing cells are also partitioned into two groups so that the two upper (or lower) output links, one from each routing cell, are called the upper (lower) output links. It is clear that the upper (lower) output links of a pair of routing cells in stage k $(1 \le k \le n-2)$  are the upper or lower input links of another pair of routing cells in stage k+1. Besides, blocking occurs only when three or four active connection requests received by the four input links are intended to be routed simultaneously to the upper or the lower output links.

We now analyse the throughput performance of our proposed load-sharing banyan network under the uniform traffic model. By uniform traffic model, it is meant that all the inlets have independent and identical input rates and each outlet is equally likely to be the destination of any connection request. Consider a pair of routing cells of the same group in stage k. Let  $h(k-1) = [h_0(k-1), h_1(k-1), h_2(k-1)], 1 \le k \le n$ , denote the probability distribution of the upper (and the denote the probability distribution of the upper (and the lower) input links, i.e.  $h_i(k-1)$ , i=0,1,2 represents the probability that the upper (or lower) input links receive totally i active connection requests at the beginning of a cycle. Given the input rate  $\rho$ , we clearly have  $h_0(0) = (1-\rho)^2$ ,  $h_1(0) = 2\rho(1-\rho)$  and  $h_2(0) = \rho^2$ . Let  $S(n, \rho)$  denote the average throughput of an n-stage load-sharing banyan network with input rate  $\rho$ . Then  $S(n, \rho)$  can be computed by the following iterative algorithm:

Step 1: Do

$$k = 0, n - 2$$

$$h_0(k+1) = \sum_{i=0}^{2} \sum_{j=0}^{2} h_i(k) h_j(k) (1/2)^{i+j}$$

$$h_1(k+1) = \sum_{i=0}^{2} \sum_{j=0}^{2} (i+j) h_i(k) h_j(k) (1/2)^{i+j}$$

$$h_2(k+1) = \sum_{i=0}^{2} \sum_{j=0}^{2} \sum_{i=2}^{i+j} {i+j \choose l} h_i(k) h_j(k) (1/2)^{i+j}$$

Step 2: Compute

$$S(n, \rho) = 1/2[h_1(n-1) + 3/2 h_2(n-1)]$$

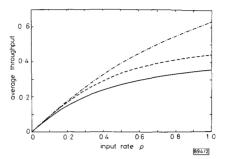

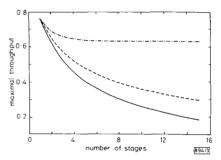

Fig. 2 shows the average throughputs of a pure banyan network, a load-sharing banyan network and a crossbar switch for 64 inlets and outlets. By sharing the loads of a pair of routing cells in each stage, the average throughput of the banyan network is increased by more than 20% for  $\rho \ge 0.4$ . Fig. 3 shows the curves of the maximal achievable throughput against number of stages for the same three networks. When  $n \ge 6$ , load-sharing results in more than 23% improvement.

Fig. 2 Average throughput against input rate for 64 inlets and outlets - load-sharing banyan

Fig. 3 Maximal throughput against number of stages banyan --- load-sharing banyan --- crossbar

Conclusion: We propose in this letter an implementation of a load-sharing banyan network which requires simple manage-ment and is easy to diagnose. The complexity of our proposed load-sharing banyan network is about twice of that of a pure banyan network, since the complexity of a sorting cell is roughly the same as that of a routing cell. Our implementation can be easily extended so that more routing cells in each stage form a group and share their loads to further improve the performance of banyan networks.

T.-H. LEE 15th September 1989

Department of Communication Engineering National Chiao Tung University Hsinchu, Taiwan 30050, Republic of China

## References

- PATEL, J. H.: 'Performance of processor-memory interconnections for multiprocessors', *IEEE Trans.*, 1981, C-30, pp. 771-780

LEA, C. T.: 'The load-sharing banyan network', *ibid.*, 1986, C-35, pp. 1025-1034

BATCHER, K. E.: 'Sorting networks and their applications'. Proc. spring joint computer conf., 1968, pp. 307-314

WU, C. L., and FENG, T. Y.: 'On a class of multistage interconnection networks'. *IEEE Trans.* 1980, C. 25, pp. 604, 265, pp. 604, 265,

- retworks', IEEE Trans., 1980, C-26, pp. 694–704

FENG, T. Y., and WU, C. L.: 'Fault-diagnosis for a class of multistage interconnection networks', ibid., 1981, C-30, pp. 743–758