## 國立交通大學

## 電信工程學系碩士班

## 碩士論文

使用矽製程蕭基二極體混頻器之 60GHz 單/ 雙次降頻接收機與應用於 WLAN 的單壓操 作 pHEMT 低雜訊放大器

60-GHz Single/Dual Conversion Receivers Using Silicon Schottky Diode Mixers and WLAN Single-Voltage-Supply pHEMT LNAs

研究生:王大維

指導教授:孟慶宗

中華民國 九十八年九月

#### 使用矽製程蕭基二極體混頻器之 60GHz 單/雙次 降頻接收機與應用於WLAN 的單壓操作 pHEMT 低雜訊放大器

60-GHz Single/Dual Conversion Receivers Using Silicon Schottky Diode Mixers and WLAN Single-Voltage-Supply pHEMT LNAs

研究生:王大維 Student: Tai-Wei Wang

指導教授:孟慶宗 博士 Advisor: Dr. Chin Chun Meng

國立交通大學

電信工程學系碩士班

碩士論文

A Thesis

Submitted to Department of Communication Engineering

College of Electrical and Computer Engineering

National Chiao Tung University

In Partial Fulfillment of the Requirements

For the Degree of

Master of Science

In

Communication Engineering

July 2009 Hsinchu, Taiwan, Republic of China

中華民國九十八年九月

## 使用矽製程蕭基二極體混頻器之60GHz單/雙次降頻接收機與應用於WLAN的單壓操作pHEMT低雜訊放大器

學生:王大維 指導教授:孟慶宗 博士

國立交通大學 電信工程學系碩士班

#### 摘、火火、要

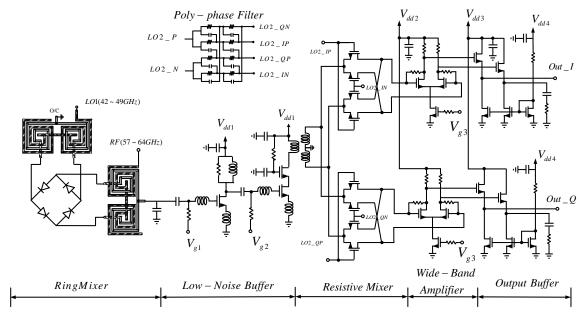

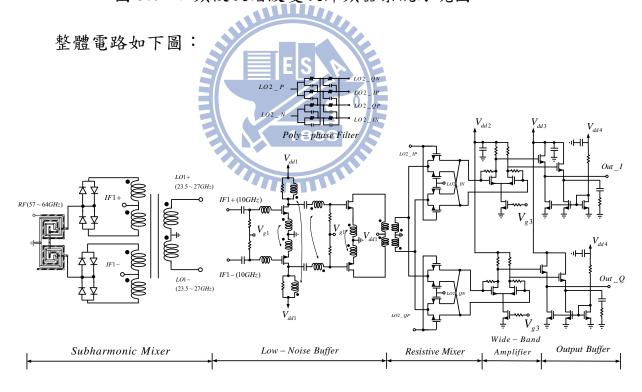

本篇論文主要分為兩個主題。其一,以 TSMC 0.18µm CMOS 及 TSMC 0.35µm SiGe BiCMOS 製程將馬爾尚巴倫、鼠徑分合波器、一對 二變壓器等傳統微波被動元件整合到矽晶片上,並實作出一百八十度單平衡式混頻器、環型雙平衡式混頻器、星型三平衡式混頻器等各種二極 體混頻器特殊結構,並提出 60GHz 雙次降頻器的接收機解決方案,第一級降頻為蕭基二極體混頻器,中間級加入了低雜訊緩衝級,第二次降頻採用了電阻式混頻器,正交中頻訊號經由寬頻緩衝級輸出。

其二,是以 WIN 0.15 PHEMT 製程來實作單壓操作的低雜訊放大器。共設計了工作頻率在 2.4~5.9 GHz 及 4.9~5.9 GHz 的兩個低雜訊放大器電路。

## 60-GHz Single/Dual Conversion Receivers Using Silicon Schottky Diode Mixers and WLAN Single-Voltage-Supply pHEMT LNAs

Student: Tai-Wei Wang Advisor: Chin-Chun Meng

Department of Communication Engineering National Chiao Tung University

#### **Abstract**

This thesis is divided into two parts. The first part we choose TSMC 0.18µm CMOS and TSMC 0.35µm SiGe BiCMOS technology to implement traditional microwave component such as marchard balun, rat-race hybrid coupler, and tri-filar on silicon substrate chip. 180 degree single-balanced mixer, double-balanced ring mixer, and triply-balanced star mixer are implemented in this thesis. We also propose the 60GHz dual down-converter solution. Schottky barrier diode mixer is adopted at first down-converter, and a low noise buffer is added to the inter-stage. Second down-converter is a resistive mixer with quarture LO signal. The output orthogonal IF signal is through the wide-band buffer.

In the second part, the low noise amplifier with single power supply is implemented with WIN 0.15um pHEMT technology. We design two kinds circuit at different frequency, which one is 2.4 to 5.9GHz and another one is 4.9 to 5.9GHz.

時光匆匆,二年的碩士生涯一下就過去了,其間受到了許多人的幫助與扶持,使得這本論文能順利的完成。首先要感謝指導老師<u>孟慶</u> 宗教授在課業與研究上的指導,並給予我參與許多計畫實作的機會,讓我在研究過程中逐漸累積了許多實貴的經驗,從正文計劃、科專計劃到立積計劃,兩年的磨練令我成長了不少,並對 RFIC 這門領域有了很深入的瞭解。此外,也很感謝抽空來參與學生口試的 B學士教授、黃張志揚教授以及鍾世忠教授,老師們在口試中所提出的問題以及見解使我獲益良多。而在晶片的量測過程中,更要感謝國家奈米元件實驗室全體同仁的協助,特別是<u>这德、書毓、榮彦、治華</u>這四位高手,我每次提出的高難度複雜架設也只有靠著這四大高手神乎其技的架設與下針技術才能辦到,兩年來要忍受我每次非人道的要求真是辛苦你們了。

博士班的<u>聖哲</u>學長不管在研究還是生活方面都給了我很大的啟發,曾大媽之名當之無愧;貼心的<u>珍儀</u>學姐總是能讓實驗室充滿了溫暖;亦師亦友的<u>宏儒</u>學長常陪我一起昏天黑地地栽在 NDL 量測,連續

量測時間紀錄大概無人能破,認真嚴謹的研究精神是我的榜樣;<u>金詳</u>學長真的很厲害,對於我提出的問題總是能提出獨具慧根的見解。大學時就是直屬的<u>揚鮮</u>學長給我許多微波方面的觀念,接手學長留下來的大作更是讓我對場論大師欽佩不已,此外也要感謝<u>雅惠、宜蓁、宜</u> 珊以及<u>威宇</u>等學長姊們的經驗傳承和指導,讓我的研究能夠順利進入 軌道。

泰麟不但是我做正文計劃及科專計畫的夥伴,也是常陪我量測的好夥伴,很強的熙良讓我在學業上獲益不少,也讓我見識到何謂老師的愛將, 欣怡總是默默地維護實驗室的整潔, 嘉苓、忠佑以及智凱學弟妹們除了在量測上提供了人力支援,同時也是實驗室歡樂的來源。

最後要感謝的是我的家人,一直以來都默默地在背後支持著我, 感謝周圍朋友們的關心,讓我能夠順利完成學業,僅以此論文聊表我 對大家的謝意。

## 目錄

| 中文摘要                                  | i    |

|---------------------------------------|------|

| 英文摘要                                  | ii   |

| 誌謝                                    | iii  |

| 目錄                                    | V    |

| 圖目錄                                   | viii |

| 表目錄                                   | xiii |

| 第一章 導論                                | 1    |

| 1.1 研究動機                              | 2    |

| 1.2 論文組織                              | 2    |

| 第二章 二極體混頻器分析與應用於V頻段之雙次降頻接收機 ······    | 3    |

| 2.1 前言                                | 4    |

| 2.2 二極體混頻器原理及分析                       | 4    |

| 2.2.1 單一二極體混頻原理                       | 4    |

| 2.2.2 反對稱式二極體                         | 5    |

| 2.2.3 90° 單平衡式二極體混頻器                  | 9    |

| 2.2.4 180°單平衡式二極體混頻器                  | 11   |

| 2.2.5 環形雙平衡式二極體混頻器                    | 13   |

| 2.2.6 星形雙平衡式二極體混頻器                    | 16   |

| 2.2.7 星形三平衡式二極體混頻器                    | 19   |

| 2.2.8 環形三平衡式二極體混頻器                    | 23   |

| 2.3 實作一 應用於高速資料傳輸之 V 頻段雙次降頻器 (使用 TSMC |      |

| 0.18um CMOS)                          | 27   |

| 2.3.1 系統頻率規劃                          | 27   |

| 2.3.2 整體系統架構                          | 28   |

| 2.3.3 環型二極體混頻設計                       | 29   |

| 2.3.4 低雜訊緩衝級設計                        | 30   |

| 2.3.5 正交訊號產生器                         | 30   |

| 2.3.6 電阻式混頻器與輸出緩衝級設計                  | 33   |

| 2.3.7 晶片量測結果                          | 33   |

| 2.3.8 結果與討論                           | 40   |

| 第三章 相位反轉鼠徑分合波器分析及使用蕭基二極體之次諧波混頻器       |      |

| 設計                                    | 43   |

| 3.1 前言                                | 44   |

| 3.2 Rat-race 理論分析                     | 44   |

|     | 3.2.1 Rat-race 的相位及轉(phase inverter)理論分析                       | 4  |

|-----|----------------------------------------------------------------|----|

|     | 3.2.2 衰減性相位反轉 rat-race 理論分析                                    | 4  |

|     | 3.2.3 衰減性相位反轉 rat-race 阻抗匹配分析                                  | 5  |

| 3.3 | 實作一 應用 phase inverter rat-race 的 60GHz 次諧波混頻器(使用               |    |

|     | TSMC 0.18um CMOS)                                              | 5  |

|     | 3.3.1 二極體混頻原理                                                  | 5  |

|     | 3.3.2 phase inverter rat-race 設計                               | 5  |

|     | 3.3.3 晶片量測結果                                                   | 5  |

|     | 3.3.4 結果與討論                                                    | 6  |

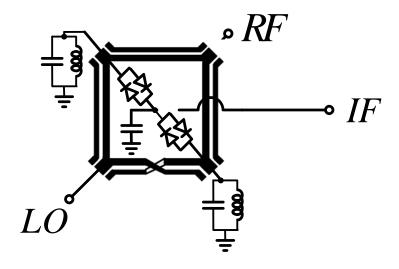

| 3.4 | 實作二 應用 phase inverter rat-race 的 60GHz 次諧波混頻器(使用               |    |

|     | TSMC 0.35um SiGe BiCMOS)                                       | 6  |

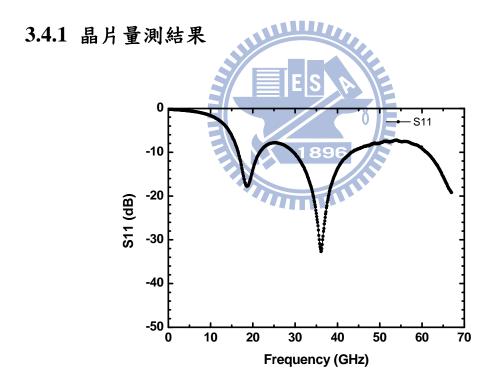

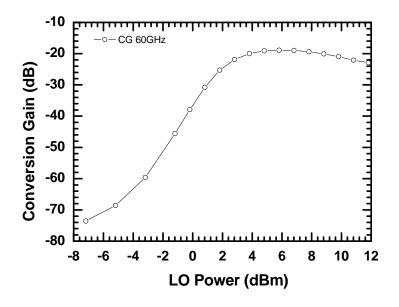

|     | 3.4.1 晶片量測結果                                                   | 6  |

|     | 3.4.2 結果與討論                                                    | 7  |

| 3.5 | 實作三 V 頻帶結合 phase inverter rat-race 的次諧波雙次降頻器                   |    |

|     | (使用 TSMC 0.18um CMOS)                                          | -  |

|     | 3.5.1 系統頻率規劃                                                   | 7  |

|     | 3.5.2 整體系統架構                                                   | -  |

|     | 3.5.3 晶片量測結果                                                   | -  |

|     | 3.5.4 結果與討論                                                    | 8  |

| 3.6 | 實作四 三平衡式星型二極體混頻器(使用 TSMC 0.35um SiGe                           |    |

|     | BiCMOS)                                                        | 8  |

|     | 3.6.1 混頻器工作原理                                                  | 8  |

|     | 3.6.2 晶片量測結果                                                   | 8  |

|     | 3.6.3 結果與討論                                                    | 9  |

| 3.7 | 實作五 V 頻帶結合 Tri-filar 變壓器的次諧波雙次降頻器(使用                           |    |

|     | TSMC 0.18um CMOS)                                              | (  |

|     | 3.7.1 系統頻率規劃                                                   | (  |

|     | 3.7.2 整體系統架構                                                   | Ç  |

|     | 3.7.3 次諧波混頻器原理                                                 | Ģ  |

|     | 3.7.4 差動式低雜訊緩衝級設計                                              | 9  |

|     | 3.7.5 晶片量測結果                                                   | Ģ  |

|     | 3.7.6 結果與討論                                                    | 10 |

|     | 應用於WLAN之單壓操作PHEMT低雜訊放大器設計 ···································· | 10 |

|     | 前言                                                             | 10 |

| 4.2 |                                                                | 10 |

|     | 4.2.1 電路結構與單壓操作原理                                              | 10 |

|     | 4.2.2 具有抗拒製程變異的偏壓電路設計分析                                        | 10 |

|     | 4.2.3 带有源極退化的低雜訊放大器分析                                          | 1. |

|     |                                                                |    |

| 4.3          | 實作    | 一單  | 壓操作之 | 2.4~5.9GHz 低雜訊放大器(使用 WIN 0.15um |     |

|--------------|-------|-----|------|---------------------------------|-----|

|              | pHE   | MT) |      |                                 | 115 |

|              | 4.3.1 | 晶片  | 量測結果 |                                 | 115 |

|              | 4.3.2 | 結果  | 與討論  |                                 | 120 |

| 4.4          | 實作    | 二單  | 壓操作之 | 5GHz 低雜訊放大器(使用 WIN 0.15um       |     |

|              | pHE   | MT) |      |                                 | 121 |

|              | 4.4.1 | 晶片  | 量測結果 |                                 | 121 |

|              | 4.4.2 | 結果  | 與討論  |                                 | 125 |

| 第五章          | 結論    |     |      |                                 | 127 |

| <b>參考文</b> [ | 試     |     |      |                                 | 130 |

### 圖目錄

| 第二章    |                                                       |    |

|--------|-------------------------------------------------------|----|

| 圖 2.1  | 單一二極體導電電流之波形                                          | 5  |

| 圖 2.2  | 反對稱二極體導電電流之波形                                         | 6  |

| 圖 2.3  | 反對稱二極體的電流分析                                           | 6  |

| 圖 2.4  | 90 度單平衡式二極體混頻器                                        | 9  |

| 圖 2.5  | 輸入LO 訊號在各二極體之電壓電流                                     | 9  |

| 圖 2.6  | 輸入 RF 訊號在各二極體之電壓電流                                    | 10 |

| 圖 2.7  | 180 度單平衡式二極體混頻器                                       | 11 |

| 圖 2.8  | 輸入LO 訊號在各二極體之電壓電流                                     | 11 |

| 圖 2.9  | 輸入 RF 訊號在各二極體之電壓電流                                    | 12 |

| 圖 2.10 | 環形雙平衡式二極體混頻器                                          | 13 |

| 圖 2.11 | 環形二極體混頻器 RF 及 LO 虛接地點                                 | 14 |

| 圖 2.12 | 輸入LO 訊號在各二極體之電壓電流 ··································· | 14 |

| 圖 2.13 | 輸入 RF 訊號在各二極體之電壓電流                                    | 14 |

| 圖 2.14 | 星形雙平衡式二極體混頻器                                          | 16 |

| 圖 2.15 | 星形二極體混頻器 RF 及 LO 虚接地點 0                               | 17 |

| 圖 2.16 | 輸入LO 訊號在各二極體之電壓電流                                     | 17 |

| 圖 2.17 | 輸入 RF 訊號在各二極體之電壓電流                                    | 17 |

| 圖 2.18 | 星形三平衡式二極體混頻器                                          | 19 |

| 圖 2.19 | 星形三平衡式二極體混頻器 RF 及 LO 虚接地點                             | 20 |

| 圖 2.20 | 輸入LO 訊號在各二極體之電壓電流                                     | 20 |

| 圖 2.21 | 輸入 RF 訊號在各二極體之電壓電流                                    | 21 |

| 圖 2.22 | 環形三平衡式二極體混頻器                                          | 23 |

| 圖 2.23 | 環形三平衡式二極體混頻器 RF 及 LO 虚接地點                             | 24 |

| 圖 2.24 | 輸入LO 訊號在各二極體之電壓電流                                     | 24 |

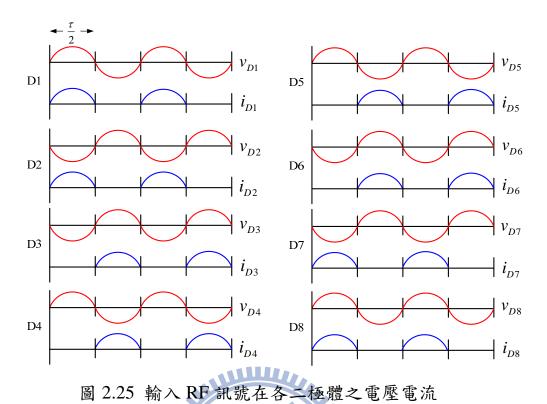

| 圖 2.25 | 輸入 RF 訊號在各二極體之電壓電流                                    | 25 |

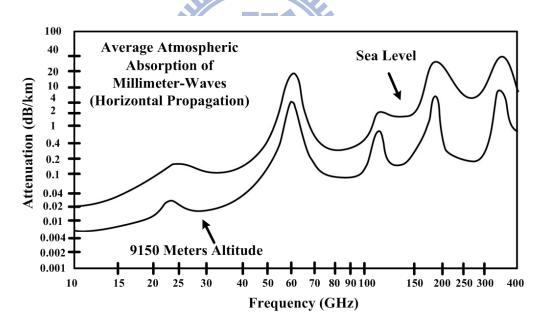

| 圖 2.26 | 微波在大氣中衰減的情形                                           | 27 |

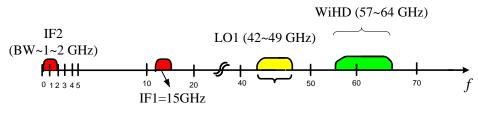

| 圖 2.27 | 頻帶設計                                                  | 28 |

| 圖 2.28 | 系統方塊圖                                                 | 28 |

| 圖 2.29 | V 頻段雙次降頻器電路圖                                          | 29 |

| 圖 2.30 | 第一級降頻器                                                | 29 |

| 圖 2.31 | 低雜訊緩衝級                                                | 30 |

| 圖 2.32 | 正交相位產生器                                               | 31 |

| 圖 2.33 | 電路頻率響應 (a)低通濾波 (b)高通濾波                                | 32 |

| 圖 2.34 | 正交訊號產生器                                        | 33 |

|--------|------------------------------------------------|----|

| 圖 2.35 | 電阻式混頻器與輸出緩衝級設計                                 | 33 |

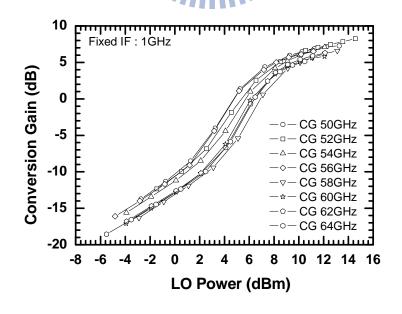

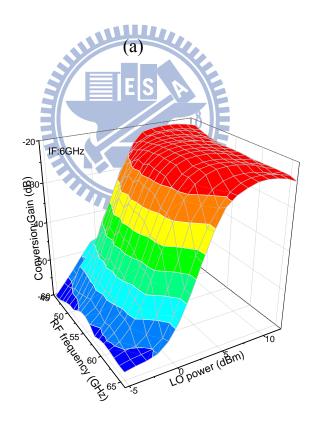

| 圖 2.36 | 轉換增益對射頻訊號頻率及本地訊號功率                             | 34 |

| 圖 2.37 | 轉換增益對第一本地訊號功率                                  | 34 |

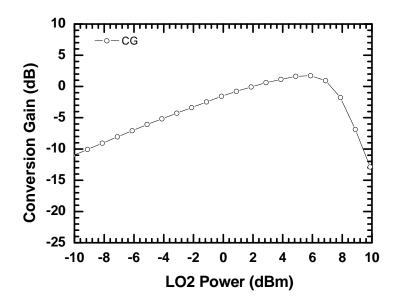

| 圖 2.38 | 轉換增益對第二本地訊號功率                                  | 35 |

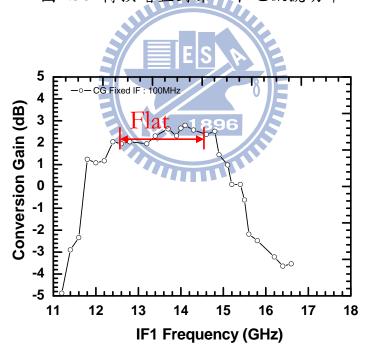

| 圖 2.39 | 第一中頻頻寬                                         | 35 |

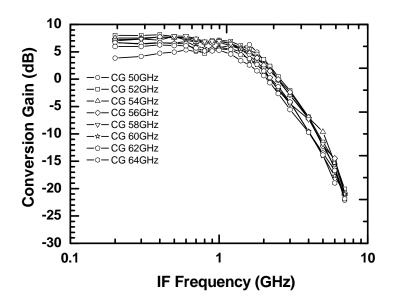

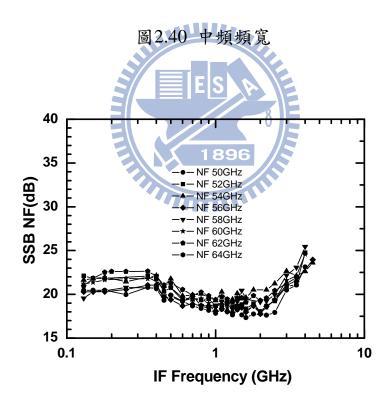

| 圖 2.40 | 中頻頻寬                                           | 36 |

| 圖 2.41 | 雜訊指數                                           | 36 |

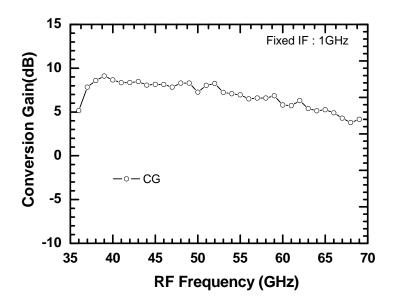

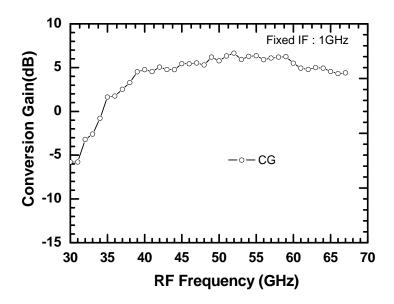

| 圖 2.42 | 射頻頻寬                                           | 37 |

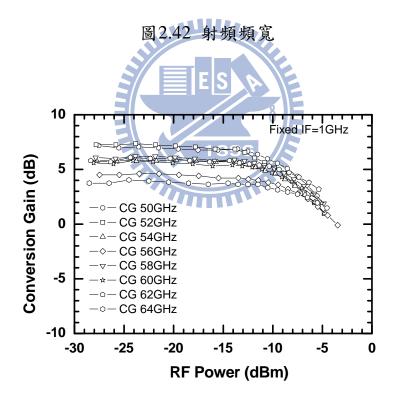

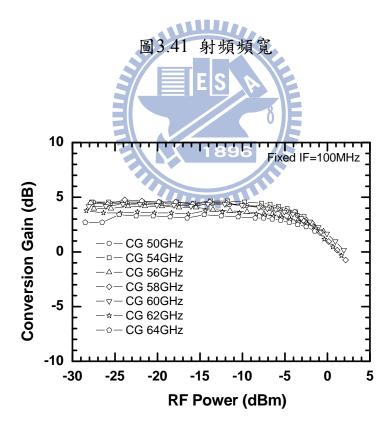

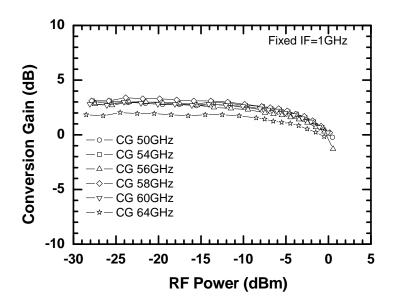

| 圖 2.43 | 換增益對射頻訊號功率                                     | 37 |

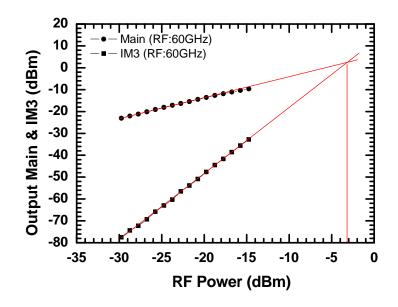

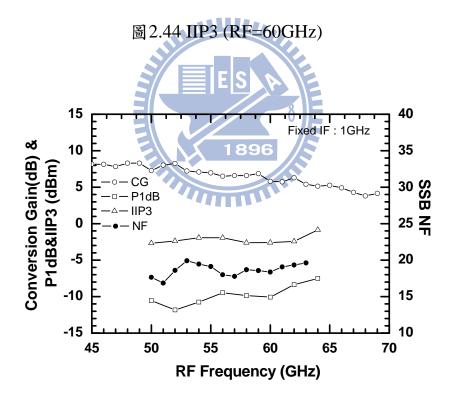

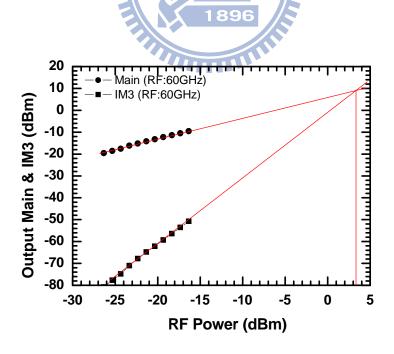

| 圖 2.44 | IIP3 (RF=60GHz)                                | 38 |

| 圖 2.45 | 轉換增益、P1dB、IIP3 與雜訊指數對射頻訊號頻率                    | 38 |

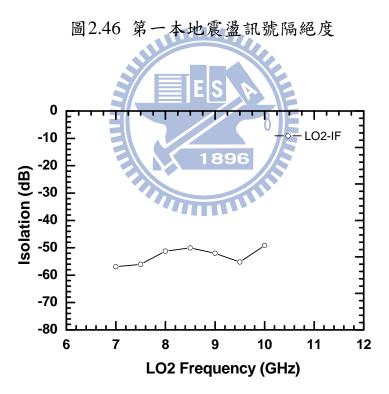

| 圖 2.46 | 第一本地震盪訊號隔絕度                                    | 39 |

| 圖 2.47 | 第二本地震盪訊號隔絕度                                    | 39 |

| 圖 2.48 | 輸出波形圖                                          | 40 |

| 圖 2.49 | Die Photo                                      | 40 |

|        |                                                |    |

| 第三章    |                                                |    |

| 圖 3.1  | 傳統式 Rat race                                   | 45 |

| 圖 3.2  | 相位反轉(phase inverter) rat-race 示意圖 0            | 45 |

| 圖 3.3  | 衰減性相位反轉之 rat-race 分合波器                         | 48 |

| 圖 3.4  | 反射損耗 V.S.頻率                                    | 52 |

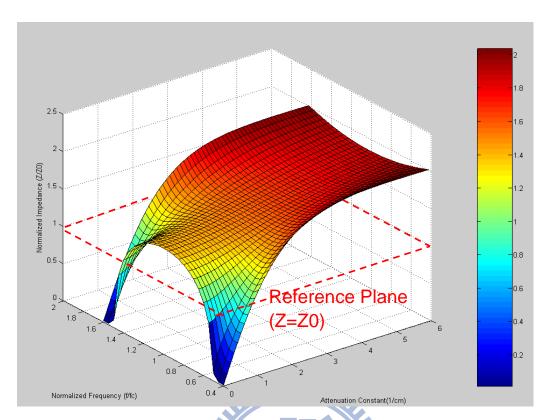

| 圖 3.5  | 正規化特性阻抗的實數部份                                   | 53 |

| 圖 3.6  | 正規化特性阻抗的虛數部份                                   | 53 |

| 圖 3.7  | 60GHz 次諧波混頻器電路圖                                | 56 |

| 圖 3.8  | 180°單平衡式二極體混頻器架構                               | 56 |

| 圖 3.9  | APDP 型式的 180°單平衡式二極體混頻器架構                      | 57 |

| 圖 3.10 | phase inverter rat-race 結構                     | 58 |

| 圖 3.11 | 反射損耗                                           | 58 |

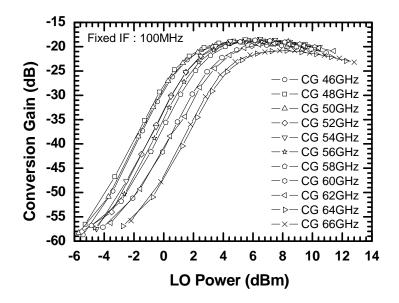

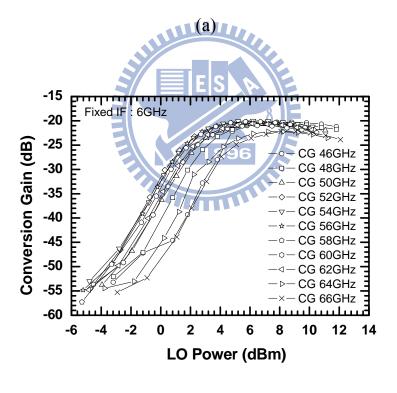

| 圖 3.12 | 轉換增益對射頻訊號頻率及本地訊號功率 (a)固定中頻訊號:                  |    |

|        | 100MHz (b)固定中頻訊號:6GHz ·······                  | 59 |

| 圖 3.13 | 轉換增益對本地訊號功率 (a)固定中頻訊號:100MHz (b)固定             |    |

|        | 中頻訊號:6GHz ···································· | 60 |

| 圖 3.14 | 射頻訊號頻寬 (a)固定中頻訊號:100MHz(b)固定中頻訊號:              |    |

|        | 6GHz                                           | 61 |

| 圖 3.15 | 轉換增益對射頻訊號功率 (a)固定中頻訊號:100MHz (b)固定             |    |

|        | 中頻訊號:6GHz ···································· | 62 |

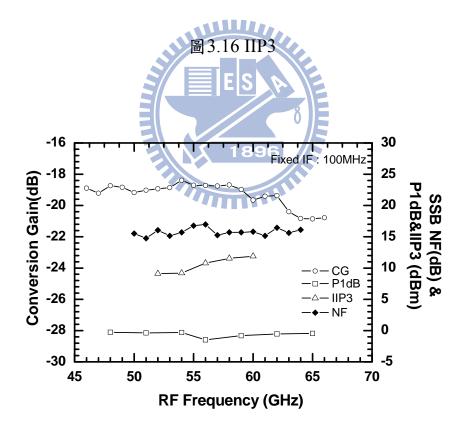

| 圖 3.16 | IIP3                                           | 63 |

| 啚 | 3.17 | 轉換增益、P1dB、IIP3 與雜訊指數對射頻訊號頻率 6                  |

|---|------|------------------------------------------------|

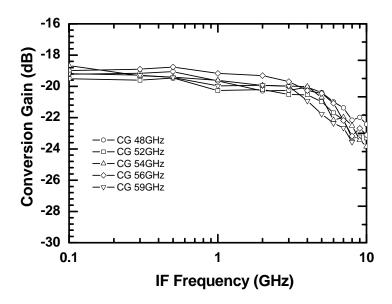

| 置 | 3.18 | 中頻頻寬                                           |

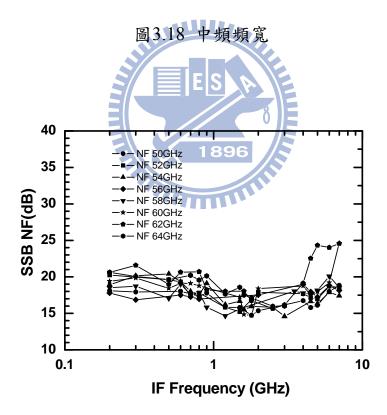

| 置 | 3.19 | 雜訊指數                                           |

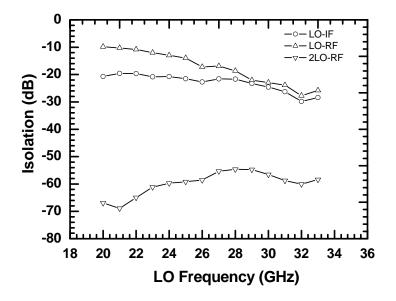

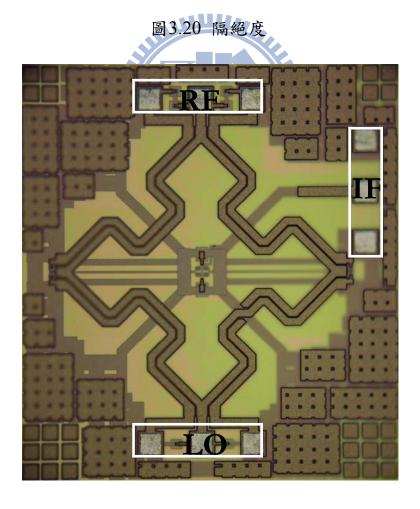

| 啚 | 3.20 | 隔絕度                                            |

| 置 | 3.21 | Die Photo 6.                                   |

| 昌 | 3.22 | 60GHz 次諧波混頻器電路圖 6                              |

| 昌 | 3.23 | 反射損耗 6                                         |

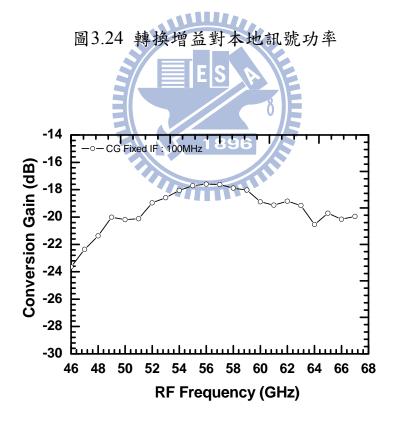

| 昌 | 3.24 | 轉換增益對本地訊號功率 6                                  |

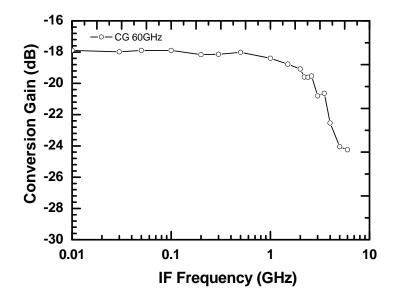

| 昌 | 3.25 | 射頻訊號頻寬 6                                       |

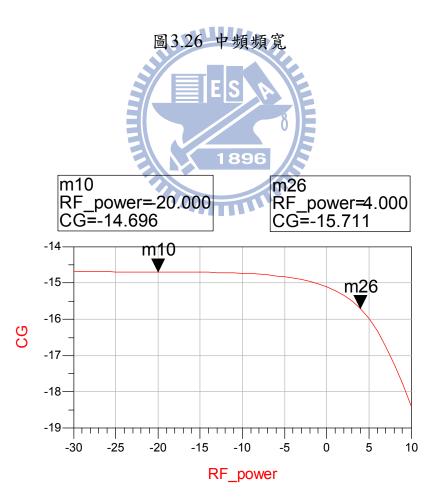

| 啚 | 3.26 | 中頻頻寬                                           |

| 啚 | 3.27 | 轉換增益對射頻訊號功率 (模擬結果)                             |

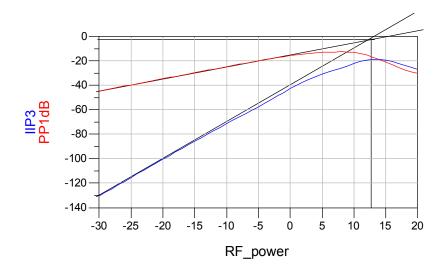

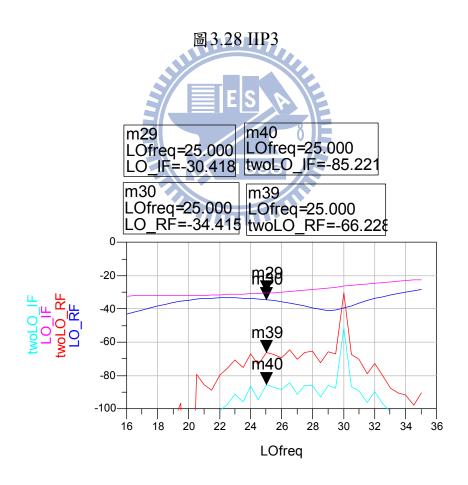

| 置 | 3.28 | IIP3                                           |

| 置 | 3.29 | 隔絕度(模擬結果) 7                                    |

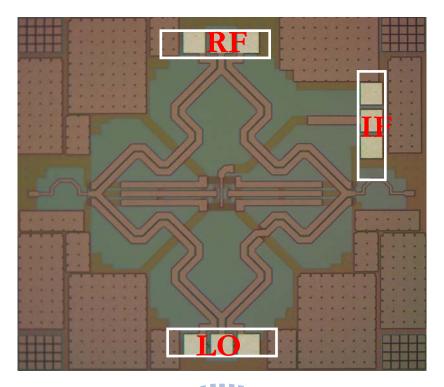

| 昌 | 3.30 | Die Photo 72                                   |

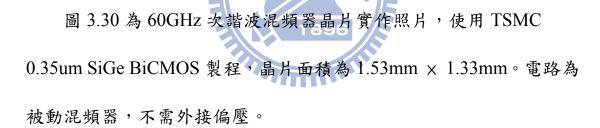

| 昌 | 3.31 | V-Band Transfer 方塊圖 (a)Receiver (b)Transmitter |

| 昌 | 3.32 | 頻帶設計 7.                                        |

| 昌 | 3.33 | V 頻段次諧波雙次降頻器電路圖 ························ 7     |

| 昌 | 3.34 | 反射損耗 7                                         |

| 昌 | 3.35 | 轉換增益對射頻訊號頻率及本地訊號功率 7                           |

| 置 | 3.36 | 轉換增益對第一本地震盪訊號功率                                |

| 置 | 3.37 | 轉換增益對第二本地震盪訊號功率 7                              |

| 置 | 3.38 | 第一中頻頻寬 7                                       |

| 置 | 3.39 | 中頻頻寬                                           |

| 昌 | 3.40 | 雜訊指數                                           |

| 昌 | 3.41 | 射頻頻寬                                           |

| 昌 | 3.42 | 轉換增益對射頻訊號功率 (a)固定中頻訊號:100MHz (b)固定             |

|   |      | 中頻訊號:1GHz                                      |

| 圖 | 3.43 | IIP38                                          |

| 圖 | 3.44 | 轉換增益、P1dB、IIP3 對射頻訊號頻率                         |

| 圖 | 3.45 | 第一本地震盪訊號隔絕度                                    |

| 圖 | 2.46 | 第二本地震盪訊號隔絕度                                    |

| 圖 |      | 輸出波形圖                                          |

| 圖 |      | Die Photo                                      |

|   |      | 三平衡式星型二極體混頻器電路圖                                |

|   |      | 平面式 Tri-filar                                  |

|   |      | 反射損耗                                           |

|   |      | 轉換增益對射頻訊號頻率及本地訊號功率                             |

|   |      | 轉換增益對本地震盪訊號功率                                  |

| 圖 3.5 | 4 射頻頻寬      |                  |      | <br>89  |

|-------|-------------|------------------|------|---------|

| 圖 3.5 | 5 中頻頻寬      |                  |      | <br>89  |

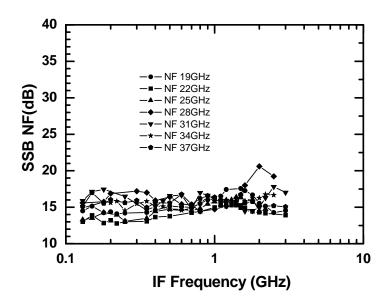

| 圖 3.5 | 6 雜訊指數      |                  |      | <br>90  |

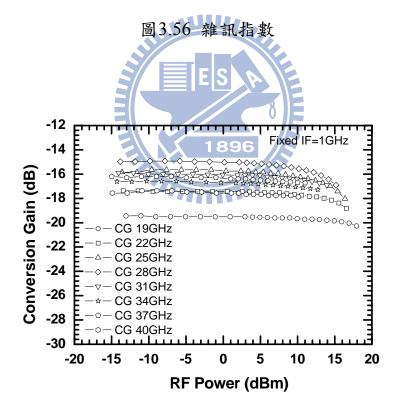

| 圖 3.5 | 7 轉換增益對     | 射頻訊號功率           |      | <br>90  |

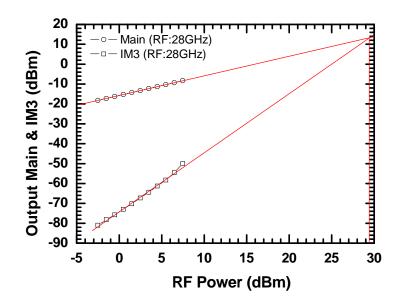

| 圖 3.5 | 8 IIP3      |                  |      | <br>91  |

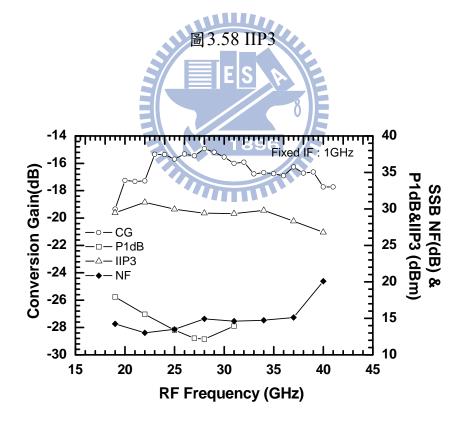

| 圖 3.5 | 9 轉換增益、]    | PldB、IIP3 對射頻訊   | .號頻率 | <br>91  |

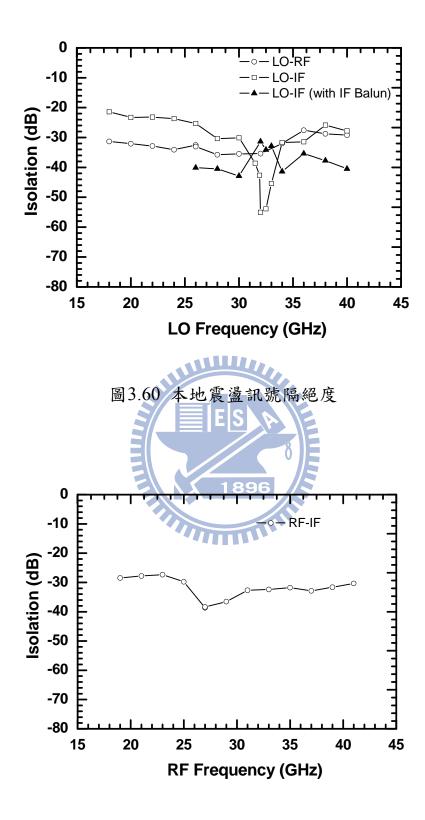

| 圖 3.6 | 0 本地震盪訊     | 虎隔絕度             |      | <br>92  |

| 圖 3.6 | 1 射頻訊號隔     | 超度               |      | <br>92  |

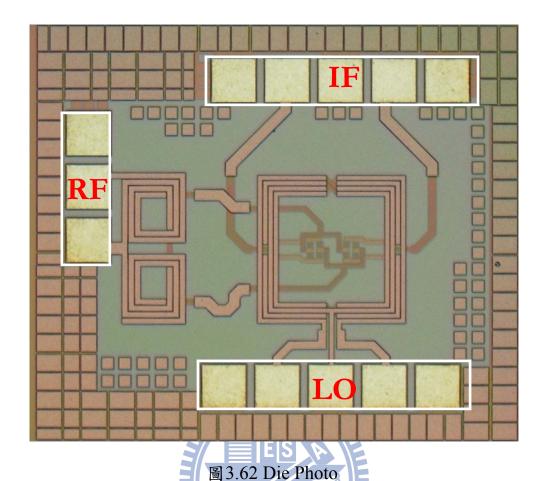

| 圖 3.6 | 2 Die Photo |                  |      | <br>93  |

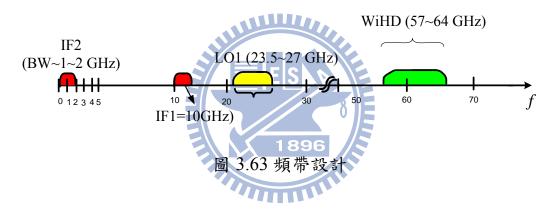

| 圖 3.6 | 3 頻帶設計      |                  |      | <br>95  |

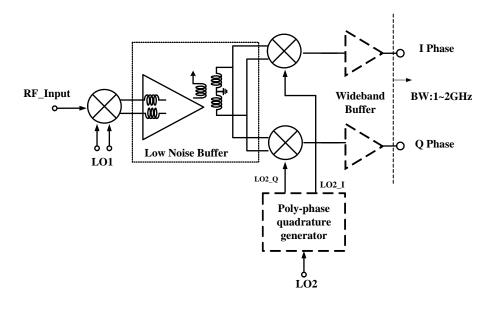

| 圖 3.6 | 4 V 頻段次諧;   | 皮雙次降頻器系統方        | 塊圖   | <br>96  |

| 圖 3.6 | 5 V 頻段次諧;   | 皮雙次降頻器電路圖        |      | <br>96  |

| 圖 3.6 | 6 次諧波二極     | <b>置混頻器</b>      |      | <br>97  |

| 圖 3.6 | 7 差動式低雜     | <b>飛緩衝級</b>      |      | <br>98  |

| 圖 3.6 | 8 反射損耗      |                  |      | <br>98  |

| 圖 3.6 | 9 轉換增益對     | 射頻訊號頻率及本地        | 訊號功率 | <br>99  |

| 圖 3.7 | 0 轉換增益對     | 第一本地震盪訊號功        | 率    | <br>99  |

| 圖 3.7 | 1 轉換增益對     | 第二本地震盪訊號功        | 率    | <br>100 |

| 圖 3.7 | 2 中頻頻寬      |                  |      | 100     |

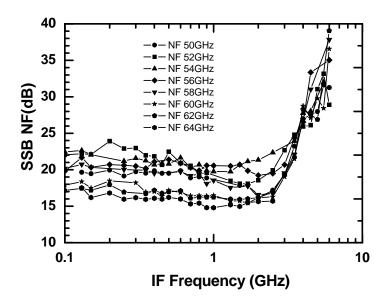

| 圖 3.7 | 3 雜訊指數      |                  | 8 =  | 101     |

| 圖 3.7 | 4 射頻頻寬      |                  | 206  | <br>101 |

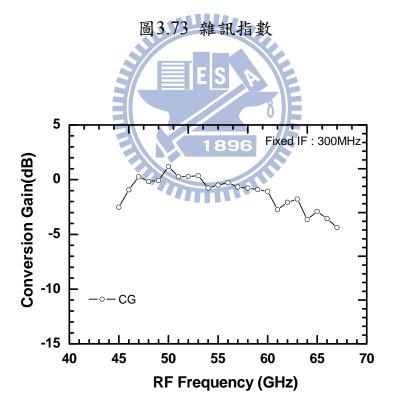

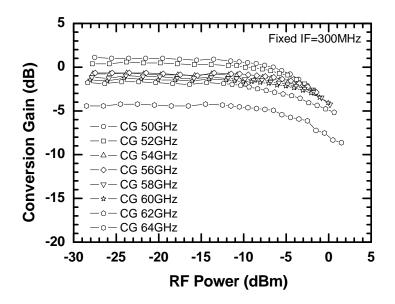

| 圖 3.7 | 5 轉換增益對     | 射頻訊號功率           |      | 102     |

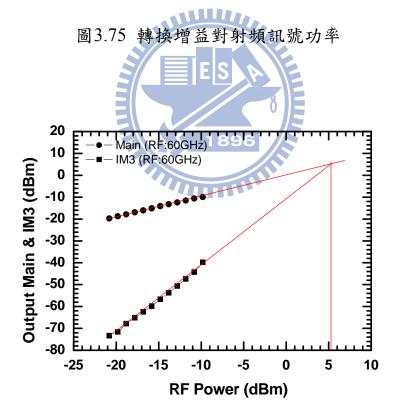

| 圖 3.7 | 6 IIP3      |                  |      | 102     |

| 圖 3.7 | 7 轉換增益、]    | PldB、IIP3 對射頻訊   | .號頻率 | 103     |

| 圖 3.7 | 8 第一本地震     | 盪訊號隔絕度           |      | 103     |

| 圖 3.7 | 9 第二本地震     | 盪訊號隔絕度           |      | <br>104 |

| 圖 3.8 | 0 輸出波形圖     |                  |      | <br>104 |

| 圖 3.8 | 1 Die Photo |                  |      | <br>105 |

|       |             |                  |      |         |

| 第四立   |             |                  |      |         |

| 圖 4.1 |             |                  |      | 108     |

| 圖 4.2 |             | 器的電路架構 (a)直流     |      | 109     |

| 圖 4.3 |             |                  |      | 110     |

| 圖 4.4 |             | <b>上阻抗的共源極放大</b> |      | 113     |

| 圖 4.5 |             | 化阻抗的共源極放大        |      | 114     |

| 圖 4.6 | 寬頻低雜訊       | 放大器電路圖           |      | 115     |

| 圖 4.7 |             |                  |      | 116     |

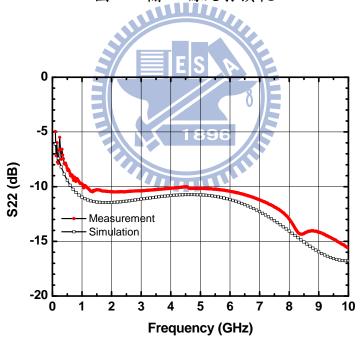

| 圖 4.8 | 輸出端反射:      | <b>損耗</b>        |      | <br>116 |

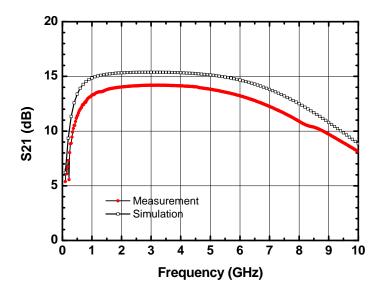

| 圖 4.9  | 增益 ·                     | 117 |

|--------|--------------------------|-----|

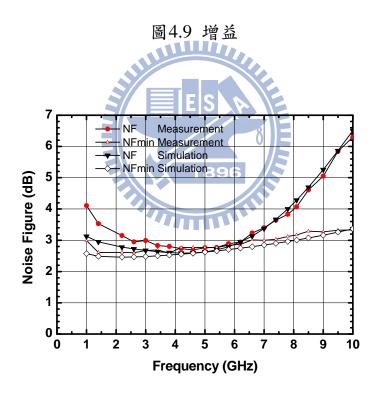

| 圖 4.10 | 雜訊指數與最低雜訊指數              | 117 |

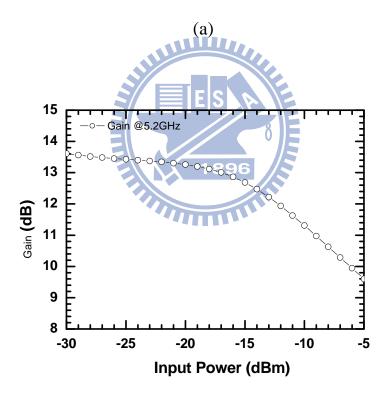

| 圖 4.11 | P1dB (a)2.4GHz (b)5.2GHz | 118 |

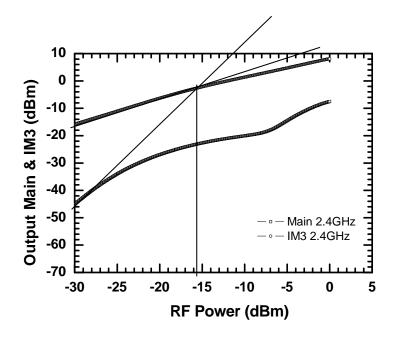

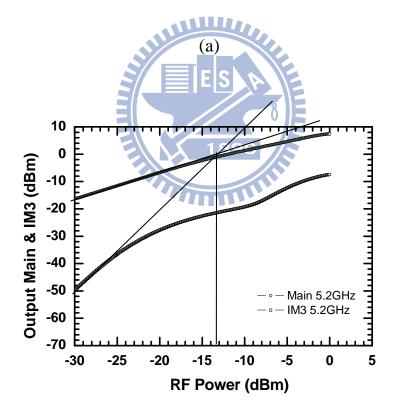

| 圖 4.12 | IP3 (a)2.4GHz (b)5.2GHz  | 119 |

| 圖 4.13 | Die Photo                | 120 |

| 圖 4.14 | 5GHz 低雜訊放大器電路圖           | 121 |

| 圖 4.15 | 輸入端反射損耗                  | 122 |

| 圖 4.16 | 輸出端反射損耗                  | 122 |

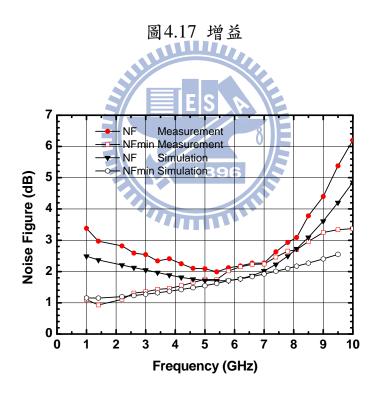

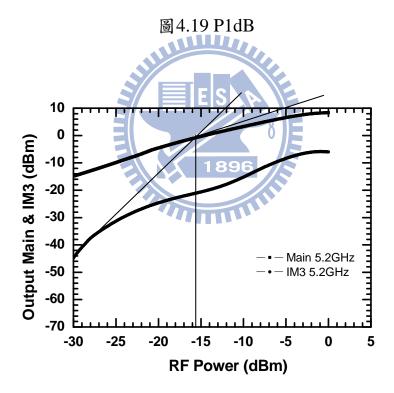

| 圖 4.17 | 增益                       | 123 |

| 圖 4.18 | 雜訊指數與最低雜訊指數              | 123 |

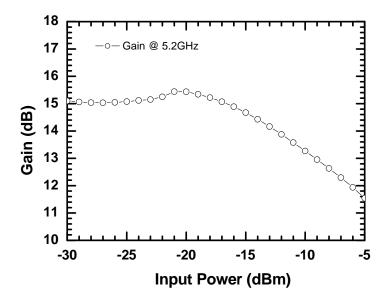

| 圖 4.19 | P1dB                     | 124 |

| 圖 4.20 | IP3                      | 124 |

| 圖 4.21 | Die Photo                | 125 |

## 表目錄

| 表 2.1 V 頻段雙次降頻器量測   | 規格表            | <br>42  |

|---------------------|----------------|---------|

| 表 3.1 60GHz 次諧波混頻器量 | <b>也測量測規格表</b> | <br>67  |

| 表 3.2 次諧波混頻器量測數據    | 整理             | <br>73  |

| 表 3.3 V 頻段次諧波雙次降頻   | [器量測規格表        | <br>85  |

| 表 3.4 三平衡式星型二極體混    | 頻器量測規格表        | <br>94  |

| 表 3.5 V 頻段次諧波雙次降頻   | 器量測規格表         | <br>106 |

| 表 4.1 寬頻低雜訊放大器量測    | 規格表            | <br>121 |

| 表 4.2 5GHz 低雜訊放大器量  | 測規格表           | <br>126 |

# 第一章

1

第一章 導論

#### 1.1 研究動機

近幾年來無線通訊發展迅速,為了追求高質量的傳輸需要愈來愈大的頻寬,幾百 MHz 的頻寬已不敷使用,為了能有更大的頻寬傳輸機勢必要將操作頻率往上提升到毫米波頻段,而60GHz 正是目前最為火熱的頻段,這個頻段有數 GHz 的頻寬足夠拿來作為高速資料的傳輸,並且60GHz 頻段的訊號在大氣中的傳送衰減很大,訊號相互干擾的程度較小,適合拿來作室內短距離的傳輸。而因為波長與頻率成反比,頻率的提高有助於將傳統微波的被動元件微小化到可實現在晶片中。0.18um CMOS 為目前最主流的製程之一,因其技術已發展成熟製作成本相較低廉,且目前數位電路都是以0.18um CMOS 為主,若能將射頻電路部份以0.18um CMOS 製程來實現的話,就可將數位電路整合進來成單一晶片系統,如此不但可以降低生產成本,更可以讓系統整合的複雜度降低。

#### 1.2 論文組織

本論文共有五個章節,第一章為導論,說明本論文的研究動機與目的。第二章探討各種二極體混頻器的特性,並使用 TSMC 0.18um COMS 製程實作一 V 頻段雙次降頻器。第三章分析了 phase inverter ratrace 在損耗性基材上的特性,並利用它來設計次諧波混頻器,此外也使用了一對二變壓器來實現三平衡式混頻器與 V 頻帶次諧波混頻器。第四章使用 WIN 0.15um PHEMT 製程來設計單壓操作的低雜訊放大器。第五章則對所有電路設計與實作結果做個結論。

## 第二章

二極體混頻器分析與 應用於V頻段之 雙次降頻接收機

#### 2.1 前言

在微波及豪米波電路中常使用蕭基二極體(schottky diode)來作為 混頻器,蕭基二極體具有切換速度快的特性,本章節將利用實作在 silicon 基材的蕭基二極體設計 V 頻段的降頻器。

#### 2.2 二極體混頻器原理及分析

在本章節中會介紹的二極體混頻器的混頻原理,並分析各種型式的二極體混頻器特性[1]。

#### 2.2.1 單一二極體混頻原理

混頻的一種常見的方法,是利用元件本身的非線性效應,一個二極體的 I-V 特性如下:

$$i(v) = f(v) = I_s \left( \exp\left(\frac{qv}{\eta KT}\right) - 1 \right)$$

是為非線性的關係,用太樂展開式展開:

$$i(v) = f(0) + f'(0)v + \frac{f''(0)}{2}v^2 + \frac{f'''(0)}{3!}v^3 + \cdots$$

$$= g_1 v + g_2 v^2 + g_3 v^3 + \dots = \sum_{n=1}^{\infty} g_n v^n$$

$$f(0) = 0$$

,  $g_1 = f'(0)$ ,  $g_2 = \frac{f''(0)}{2}$ ,  $g_1 = \frac{f'''(0)}{3!}$ , .....

若將訊號 $v(t) = v_0 \cos \omega t$  加在二極體上,電壓及電流訊號可表示為:

$$i(v) = \sum_{m=1}^{\infty} g_m v^m = \sum_{m=1}^{\infty} g_m v_0^m \cos^m(\omega t) = \sum_{m=0}^{\infty} v_m \cos(m\omega t)$$

也就是流過二極體的電流會含有v(t)的諧波項

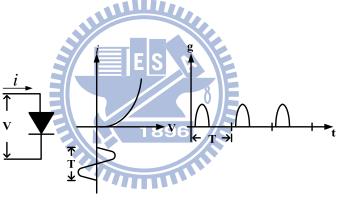

當二極體外加 LO 訊號時時其導電電流之波形及電導

(Conductance) g(t)之波形將如圖 2.1。若將 g(t)用傅立葉級數展開

將形如:

$$g(t) = \sum_{m=-\infty}^{\infty} g_n e^{jn\omega_{LO}t}$$

此時若再加上 RF 訊號因二極體的電導為非線性,在二極體上之 RF 訊號將含有 RF 的諧波,可以表成

$$V_{RF}^{'} = \sum_{m=-\infty}^{\infty} V_m e^{jm\omega_{RF}t}$$

;則由V<sub>RF</sub>及 g(t)產生的二極體電流可以表成

$$i_{d} = V_{RF} g(t) = \sum_{m=-\infty}^{\infty} \sum_{n=-\infty}^{\infty} g_{n} V_{m} e^{j(m\omega_{RF} + n\omega_{LO})t}$$

此電流含有所有 LO 及 RF 斜坡訊號的交乘項,可以用來當作混頻器 使用。

圖2.1 單一二極體導電電流之波形

#### 2.2.2 反對稱式二極體

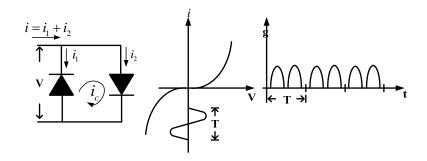

若在原本的單一二極體加入一個二極體,將其方向與原來的相反對接,這樣的接法稱之為反對稱二級體對(anti parallel diode pair),首 先來觀察單一二極體與反對稱二極體的 I-V 圖,如圖 2.2:

圖2.2 反對稱二極體導電電流之波形

反對稱連接的二極體對其 I-V 圖延伸至 LO 訊號的負半週,這使得 LO 訊號在正半週時導通 D1 二極體,在負半週時導通 D2 二極體,注意我們定義 D1 二極體的電流方向為正。從時域來看,在 LO 訊號的一個週期內 RF 訊號路徑被開啟兩次,相較於單一二極體混頻器的情形,所以我們可以簡單的得出,LO 訊號頻率只需要單一二極體混頻器的一半,此種混頻器我們可稱之為次諧波混頻器(sub-harmonic mixer),接著我們來分析這種次諧波混頻器的特性,考慮圖 2.3:

圖 2.3 反對稱二極體的電流分析。

我們定義 D1 二極體的電流為  $i_1$ ,D2 二極體的電流為  $i_2$ ,一迴路電流為  $I_c$ ,輸出電流為 I,則:

$$i_1 = I_S(e^{\alpha V} - 1)$$

$$i_2 = -I_S(e^{-\alpha V} - 1)$$

由電流式對電壓微分可得轉導 g:

$$g_1 = \alpha \cdot I_S e^{\alpha V}$$

$$g_2 = \alpha \cdot I_S e^{-\alpha V}$$

整個反對稱二極體混頻器轉導 G:

$$G = g_1 + g_2 = \alpha I_S \cdot (e^{\alpha V} + e^{-\alpha V})$$

由轉導的角度去分析其特性是由於反對稱次諧波二極體的通道 是由LO訊號去推動,令驅動電壓V:

$$V = V_{LO} \cos \omega_{LO} t$$

將上式代入前式,我們可以得到:

$$G = 2\alpha i_S \cdot \left[ I_o(\alpha V_{LO}) + I_2(\alpha V_{LO})\cos 2\omega_{LO}t + I_4(\alpha V_{LO})\cos 4\omega_{LO}t + \dots \right]$$

其中 $I_n(\cdot)$ 為 modified Bessel function  $\circ$

我們由上式可以看出,轉導G內只含有LO的偶次項,將包含著RF的電壓 $V_{total} = V_{LO}\cos\omega_{LO}t + V_{RF}\cos\omega_{RF}t$ 代入,我們可以得到全部輸出電流I:

$$\begin{split} I &= G \cdot V_{total} \\ &= A \cos \omega_{LO} t + B \cos \omega_{RF} t + C \cos 3\omega_{LO} t \\ &+ D \cos 5\omega_{LO} t + E \cos(2\omega_{LO} + \omega_{RF}) t \\ &+ F \cos(2\omega_{LO} - \omega_{RF}) t + G \cos(4\omega_{LO} + \omega_{RF}) t \\ &+ H \cos(4\omega_{LO} - \omega_{RF}) t + \dots \end{split}$$

大寫英文字母為係數要視二極體的製程與特性來決定,輸出電流 含的頻率成份除了 $\omega_{LO}$ 與 $\omega_{RF}$ 之外,尚有奇數次項,也就是說會輸出 頻率成份:

$$m \cdot \omega_{RF} \pm n \cdot \omega_{LO}$$

$m \pm n$  is odd integer.

此結果揭示了反對稱二極體混頻器的重要特性,此式也成立在當只有一個輸入訊號的時候,也就是說m=1 n=0 或m=0 n=1,此時輸出頻率為輸入頻率的奇整數倍,亦即反對稱二極體混頻器即成為一奇整數倍頻器。至於偶數項次諧波則被侷限在反對稱二極體混頻器對內,考慮電流 $I_c$ :

$$I_c = \frac{i_1 - i_2}{2}$$

$$= \frac{1}{2}I_s(e^{\alpha V} + e^{-\alpha V} - 2)$$

$$= I_s(\cosh \alpha V - 1)$$

ES

我們將 $V_{total} = V_{LO} \cos \omega_{LO} t + V_{RF} \cos \omega_{RF} t$  代入上式,我們可以得出迴路電流 $I_c$ 的泰勒展開式: 1896

$$\begin{split} I_{c} &= I_{s} [1 + \frac{(V_{LO} \cos \omega_{LO} t + V_{RF} \cos \omega_{RF} t)^{2}}{2} + \dots - 1] \\ &= \frac{I_{s}}{2} [V_{LO}^{2} \cos^{2} \omega_{LO} t + V_{RF}^{2} \cos^{2} \omega_{RF} t + 2V_{LO} V_{RF} \cdot \cos \omega_{LO} t \cos \omega_{RF} t + \dots] \\ &= \frac{I_{s}}{2} \{ \frac{V_{LO}^{2} + V_{RF}^{2}}{2} + \frac{V_{LO}^{2}}{2} \cos 2\omega_{LO} t + \frac{V_{RF}^{2}}{2} \cos 2\omega_{RF} t \\ &+ V_{LO} V_{RF} [\cos(\omega_{LO} - \omega_{RF}) t + \cos(\omega_{LO} + \omega_{RF}) t] + \dots \} \end{split}$$

我們可以看到,迴路電流 $I_c$ 中含有直流項 $\frac{{V_{LO}}^2 + {V_{RF}}^2}{2}$ ,以及其他偶次項諧波,所以 $I_c$ 含頻率成份:

$$m \cdot \omega_{RF} \pm n \cdot \omega_{LO}$$

$m \pm n$  is even integer.

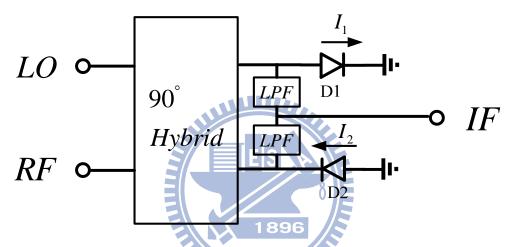

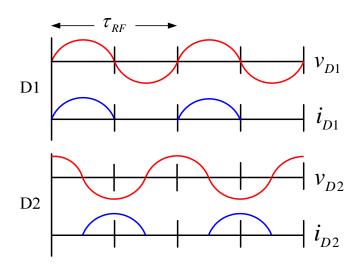

#### 2.2.3 90°單平衡式二極體混頻器

圖2.4 為90度單平衡式二極體混頻器,由兩個方向相反的二極體組成, RF及LO各輸入90度相位訊號,IF訊號由兩個二極體取出相加,為了防止RF及LO訊號溢漏到IF端,在IF端放置了低通濾波器。

圖2.4 90度單平衡式二極體混頻器

圖2.5 輸入LO 訊號在各二極體之電壓電流

圖2.6 輸入 RF 訊號在各二極體之電壓電流

$$\begin{split} &i_{1} = \sum_{m=-\infty}^{\infty} \sum_{n=-\infty}^{\infty} g_{n} V_{m} e^{j(n\omega_{LO} + m\omega_{RF})t} \\ &i_{2} = \sum_{m=-\infty}^{\infty} \sum_{n=-\infty}^{\infty} g_{n} V_{m} e^{j(n\omega_{LO}(t + \tau_{LO}/4) + m\omega_{RF}(t - \tau_{RF}/4))} \\ &= \sum_{m=-\infty}^{\infty} \sum_{n=-\infty}^{\infty} g_{n} V_{m} e^{j(n\omega_{LO}t + m\omega_{RF}t)} e^{jn\omega_{LO}(\tau_{LO}/4)} e^{-jm\omega_{LO}(\tau_{RF}/4)} \\ &\omega_{LO} \frac{\tau_{LO}}{4} = 2\pi f_{LO} \frac{\tau_{LO}}{4} = \frac{\pi}{2} \\ &\omega_{RF} \frac{\tau_{LO}}{4} = 2\pi f_{RF} \frac{\tau_{RF}}{4} = \frac{\pi}{2} \\ &\rightarrow i_{2} = \sum_{m=-\infty}^{\infty} \sum_{n=-\infty}^{\infty} g_{n} V_{m} e^{j(n\omega_{LO}t + m\omega_{RF}t)} e^{j^{n\pi/2}} e^{-j^{m\pi/2}} \\ &= i_{1} e^{j^{n\pi/2}} e^{-j^{m\pi/2}} = (j)^{n} (-j)^{m} i_{1} \end{split}$$

可以得到中頻輸出電流為

$$i_{IF} = i_2 - i_1 = \lceil (j)^n (-j)^m - 1 \rceil i_1$$

當作基本降頻器時 $f_{IF} = f_{RF} - f_{LO}$ , 取 $m=1 \cdot n = -1$ 代入:

$$i_{IF} = [(j)^n (-j)^m - 1]i_1 = -2i_1 = -2\sum_{m=-\infty}^{\infty} \sum_{n=-\infty}^{\infty} g_n V_m e^{j(n\omega_{LO} + m\omega_{RF})t}$$

RF及LO互接在90度分合波器的 isolation port 上,訊號隔絕度由90度分合波器的特性決定。

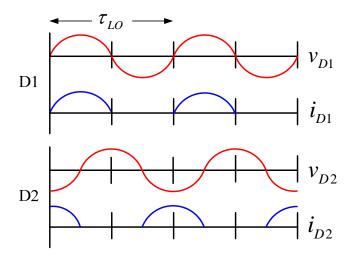

#### 2.2.4 180°單平衡式二極體混頻器

圖2.7 為180度單平衡式二極體混頻器,由兩個方向相反的二極體組成,LO輸入差動訊號RF輸入同相位訊號,IF訊號由兩個二極體取出相加,為了防止訊號溢漏到IF端,在IF端放置了低通濾波器。

圖2.7 180度單平衡式二極體混頻器

圖2.8 輸入LO 訊號在各二極體之電壓電流

圖2.9 輸入 RF 訊號在各二極體之電壓電流

分別就 LO 的 n 次項諧波及 RF 的 m 次項諧波觀察各個二極體的

電流;

LO的n次項諧波:

$$i_1 = \sum \sum g_n v_m e^{j(n\omega_{LO}t + m\omega_{RF}t)}$$

$$i_2 = \sum \sum g_n v_m e^{j(n\omega_{LO}t + m\omega_{RF}t)} e$$

$$\omega_{\scriptscriptstyle LO} \frac{\tau_{\scriptscriptstyle LO}}{2} = 2\pi f_{\scriptscriptstyle LO} \frac{\tau_{\scriptscriptstyle LO}}{2} = \pi$$

$$\rightarrow i_2 = e^{jn\pi}i_1 = (-1)^n i_1$$

RF的m次項諧波:

$$i_2 = e^{jn\pi}i_1 = i_1$$

可以得到中頻輸出電流為

$$i_{IF} = i_2 - i_{d1} = [(-1)^n - 1]i_1$$

觀察上式可以發現,當 n 為偶數時中頻輸出電流為零,亦即 LO 的偶次方諧波訊號不會由中頻輸出。當作基本降頻器時  $f_{IF}=f_{RF}-f_{LO}$ ,取 m=1、 n=-1 代入:

$$i_{IF} = \left\lceil (-1)^n - 1 \right\rceil i_1 = i_1 = \sum \sum g_n v_m e^{j(n\omega_{LO}t + m\omega_{RF}t)}$$

RF 及 LO 互接在180度分合波器的 isolation port 上,訊號隔絕度由巴倫的特性決定。

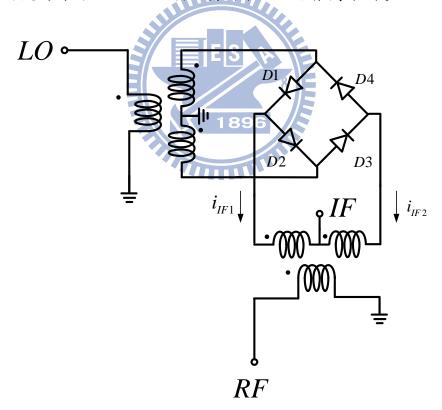

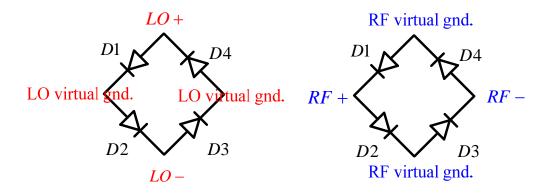

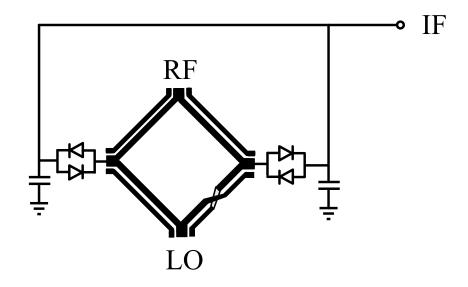

#### 2.2.5 環形雙平衡式二極體混頻器

圖2.10 為環形雙平衡式二極體混頻器,由四個二極體組成環形結構,RF及LO經過巴倫產生差動訊號各由輸入環形二極體混頻器,IF訊號由 RF 巴倫的 isolation port 取出。因為輸入訊號為差動訊號會在電路中產生虛接地如圖2.11,電路中不需要處理二極體混頻器接地問題,這使得環形二極體混頻器實作在IC 將會簡單許多。

圖2.10 環形雙平衡式二極體混頻器

圖2.11 環形二極體混頻器 RF 及 LO 虛接地點

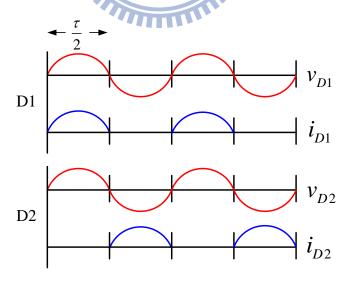

圖2.12 輸入 LO 訊號在各二極體之電壓電流

圖2.13 輸入 RF 訊號在各二極體之電壓電流

為了簡化分析定義二極體 D1 的電流為參考電流 $i_{a1}$ ,分別就 LO 的n次項諧波及 RF的m次項諧波觀察各個二極體的電流相位關係如下;

LO的n次項諧波:

$$i_{d4} = (-1)^n i_{d1}$$

$$i_{d3} = (-1)^n i_{d2}$$

RF 的 m 次項諧波:

$$i_{d2} = (-1)^m i_{d1}$$

$$i_{d3} = (-1)^m i_{d4}$$

同時考慮 LO的n次項諧波及 RF的m次項諧波:

$$LO \& RF \Rightarrow i_{d3} = (-1)^{n+m} i_{d1}$$

故可以得到中頻輸出電流為 1890

$$i_{IF1} = i_{d1} - i_{d2} = \left[1 - (-1)^m\right] i_{d1}$$

$$i_{IF2} = i_{d3} - i_{d4} = \left[ (-1)^{n+m} - (-1)^n \right] i_{d1}$$

$$i_{IF} = i_{IF1} + i_{IF2} = \left\lceil (-1)^{n+m} - (-1)^n - (-1)^m + 1 \right\rceil i_{d1} = \left\lceil 1 - (-1)^n \right\rceil \left\lceil 1 - (-1)^m \right\rceil i_{d1}$$

觀察上式可以發現,當 n 為偶數或 m 為偶數時,中頻輸出電流 為零,亦即 LO 及 RF 的偶次方諧波訊號不會由中頻輸出。當作基本 降頻器時  $f_{IF}=f_{RF}-f_{LO}$ ,取 m=1、 n=-1 代入:

$$i_{IF} = \lceil (-1)^n - 1 \rceil \lceil (-1)^m - 1 \rceil i_{d1} = 4i_{d1}$$

再來分析各訊號的隔絕度,因為 RF 及 LO 差動訊號各由對方的 虚接地點輸入如圖2.11,故當二級體的對稱性及巴倫都理想的情況下 RF及LO無訊號互耦,IF訊號由RF巴倫的 isolation port 取出,RF到IF的隔絕度由RF巴倫的特性決定,因RF巴倫的兩端是接在LO的虛接地點上,在理想的情況下LO訊號不會溢漏到IF端。

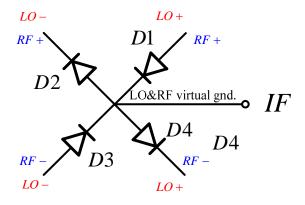

#### 2.2.6 星形雙平衡式二極體混頻器

圖2.14 為星形雙平衡式二極體混頻器,由四個二極體組成星形結構,IF 訊號由星形結構中央取出。RF 及 LO 經過一對二變壓器產生兩組差動訊號輸入星形二極體混頻器,同樣因為輸入訊號為差動訊號會在電路中產生虛接地點如圖2.15,電路中不需要處理二極體混頻器接地問題。

圖2.14 星形雙平衡式二極體混頻器

圖2.15 星形二極體混頻器 RF 及 LO 虛接地點

圖2.16 輸入 LO 訊號在各二極體之電壓電流

圖2.17 輸入 RF 訊號在各二極體之電壓電流

為了簡化分析定義流過二極體 D1 的電流為參考電流  $i_{a1}$  ,分別就 LO 的 n 次項諧波及 RF 的 m 次項諧波觀察各個二極體的電流相位關係如下;

LO的n次項諧波:

$$i_{d4} = (-1)^n i_{d1}$$

$$i_{d3} = (-1)^n i_{d2}$$

RF的m次項諧波:

$$i_{d2} = (-1)^m i_{d1}$$

$$i_{d3} = (-1)^m i_{d4}$$

同時考慮 LO的n次項諧波及 RF的m次項諧波:

$$LO \& RF \Rightarrow i_{d3} = (-1)^{n+m} i_{d1}$$

故可以得到中頻輸出電流為 1896

$$i_{IF} = i_{d1} - i_{d2} + i_{d3} - i_{d4}$$

$$= \left\{ \left\lceil 1 - (-1)^m \right\rceil + \left\lceil (-1)^{n+m} - (-1)^n \right\rceil \right\} i_{d1} = \left\lceil (-1)^m - 1 \right\rceil \left\lceil (-1)^n - 1 \right\rceil i_{d1}$$

觀察上式可以發現,當 n 為偶數或 m 為偶數時,中頻輸出電流為零,亦即 LO 及 RF 的偶次方諧波訊號不會由中頻輸出。當作基本降頻器時  $f_{IF}=f_{RF}-f_{LO}$ ,取 m=1、 n=-1 代入:

$$i_{IF} = \lceil (-1)^n - 1 \rceil \lceil (-1)^m - 1 \rceil i_{d1} = 4i_{d1}$$

再來分析各訊號的隔絕度,IF訊號由星形二極體混頻器的虛接 地點抽出,當二級體的對稱性及一對二變壓器都理想的情況下RF及 LO 訊號不會溢漏到 IF 端。而 RF 或 LO 的差動訊號會相加流至一對 二變壓器的 sum port,故理想上 RF 及 LO 無訊號互耦。

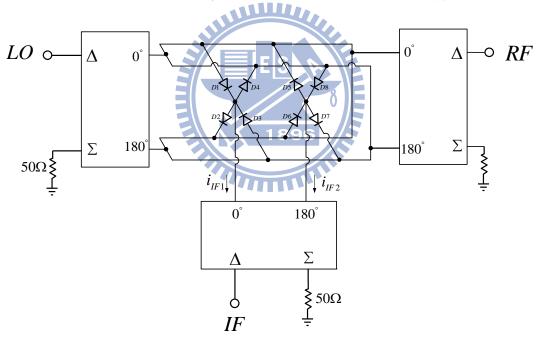

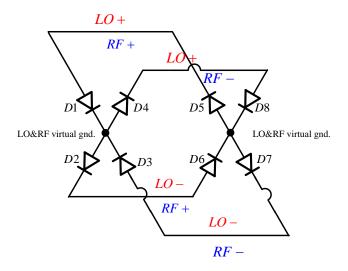

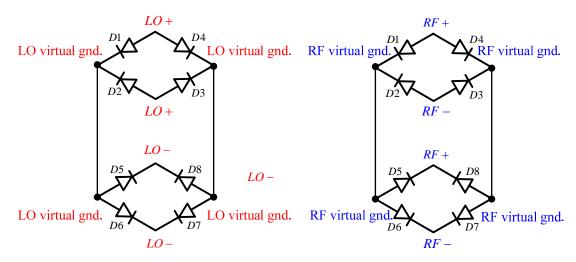

#### 2.2.7 星形三平衡式二極體混頻器

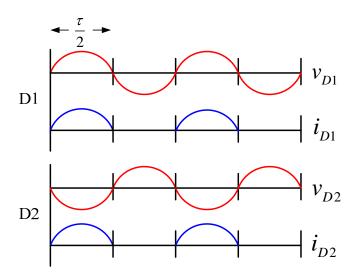

圖2.18 為星形三平衡式二極體混頻器,由兩組星形二極體混頻器反接而成,RF及LO經過一對二變壓器產生兩組差動訊號輸入星形二極體混頻器,如同星形雙平衡式二極體混頻器差動訊號會在電路中產生虛接地點如圖2.19,電路中不需要處理二極體混頻器接地問題。

混頻訊號各由兩組星形結構中央抽出,並經過 IF 巴倫輸出。

圖2.18 星形三平衡式二極體混頻器

圖2.19 星形三平衡式二極體混頻器 RF 及 LO 虚接地點

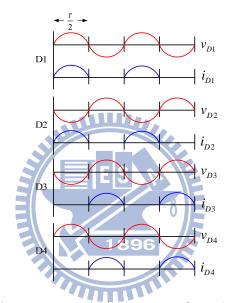

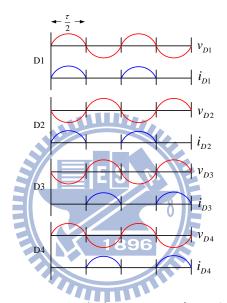

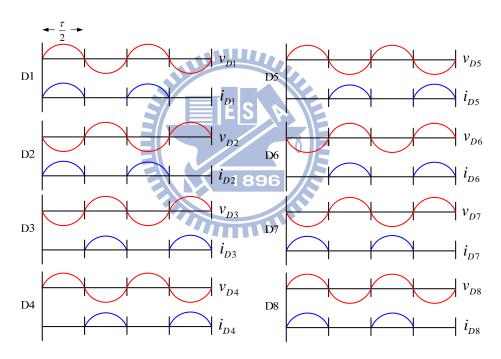

圖2.20 輸入LO訊號在各二極體之電壓電流

圖2.21 輸入 RF 訊號在各二極體之電壓電流

為了簡化分析定義流過二極體 D1 的電流為參考電流 $i_{d1}$ ,分別就 LO 的 n 次項諧波及 RF 的 m 次項諧波觀察各個二極體的電流相位關係如下;

$$i_{d_2} = (-1)^m i_{d_1}$$

$$i_{d_3} = (-1)^n (-1)^m i_{d_1}$$

$$i_{d_4} = (-1)^n i_{d_1}$$

$$i_{d_5} = (-1)^n (-1)^m i_{d_1}$$

$$i_{d_6} = (-1)^n i_{d_1}$$

$$i_{d_7}=i_{d_1}$$

$$i_{d_8} = (-1)^m i_{d_1}$$

故可以得到中頻輸出電流為:

$$\begin{split} i_{IF1} &= i_{d_1} - i_{d_2} + i_{d_3} - i_{d_4} \\ &= i_{d_1} [1 - (-1)^m + (-1)^n (-1)^m - (-1)^n] \\ &= i_{d_1} \{1 - (-1)^m - (-1)^n [1 - (-1)^m] \} \\ &= i_{d_1} [1 - (-1)^n] [1 - (-1)^m] \\ i_{IF2} &= -i_{d_5} + i_{d_6} - i_{d_7} + i_{d_8} \\ &= i_{d_1} [-(-1)^n (-1)^m + (-1)^n - 1 + (-1)^m] \\ &= i_{d_1} \{(-1)^n [1 - (-1)^m] - [1 - (-1)^m] \} \\ &= i_{d_1} [1 - (-1)^m] [(-1)^n - 1] \\ &= -i_{IF1} \\ i_{IF} &= i_{IF1} - i_{IF2} = 2i_{IF1} \\ &= 2[1 - (-1)^n] [1 - (-1)^m] i_{d_1} \end{split}$$

觀察上式可以發現,當 n 為偶數或 m 為偶數時,中頻輸出電流為零,亦即 LO 及 RF 的偶次方諧波訊號不會由中頻輸出。當作基本降頻器時  $f_{IF}=f_{RF}-f_{LO}$ ,取 m=1、 n=-1 代入:

$$i_{IF} = 2[1-(-1)^n][1-(-1)^m]i_{d1} = 8i_{d1}$$

當二級體的對稱性及一對二變壓器都理想的情況下隔絕度與星 形雙平衡式二極體混頻器相同,但因製程因素導致二級體不對稱性 或一對二變壓器不理想的時候,RF及LO溢漏訊號會出現在兩組星 形二極體混頻器的中央抽取處,因為 $i_{F2}$ 衡等於負的 $i_{F1}$ ,經過 IF 巴倫後溢漏訊號會相消掉,可以進一步提升到 IF 的隔絕度。

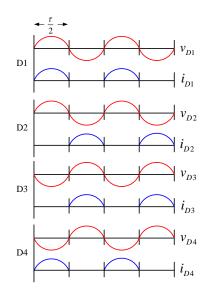

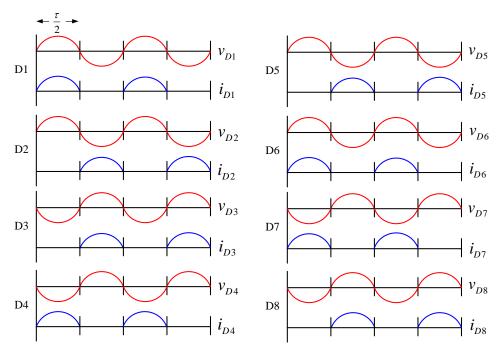

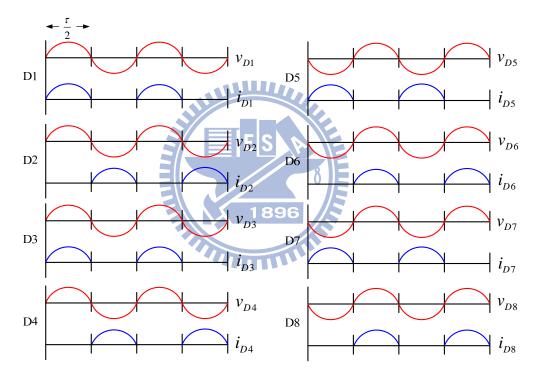

#### 2.2.8 環形三平衡式二極體混頻器

圖2.22 為環形三平衡式二極體混頻器,由兩組環形二極體混頻器反接而成,RF及LO經過一對二變壓器產生兩組差動訊號輸入星形二極體混頻器,如同環形雙平衡式二極體混頻器差動訊號會在電路中產生虛接地點如圖2.23,電路中不需要處理二極體混頻器接地問題。

圖 2.22 環形三平衡式二極體混頻器

圖 2.23 環形三平衡式二極體混頻器 RF 及 LO 虛接地點

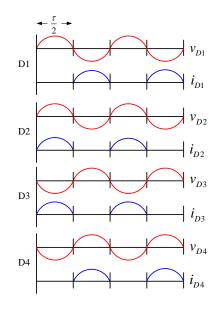

圖 2.24 輸入 LO 訊號在各二極體之電壓電流

為了簡化分析定義流過二極體 D1 的電流為參考電流ia, 分別就 LO的n次項諧波及RF的m次項諧波觀察各個二極體的電流相位關 係如下;

$$i_{d_2} = (-1)^n i_{d_1}$$

$$i_{d_3} = (-1)^m i_{d_1}$$

$$i_{d_4} = (-1)^n (-1)^m i_{d_1}$$

$$i_{d_5} = (-1)^m i_{d_1}$$

$$i_{d_6} = (-1)^n (-1)^m i_{d_1}$$

$$i_{d_7}=i_{d_1}$$

$$i_{d_8} = (-1)^n i_{d_1}$$

故可以得到中頻輸出電流為:

$$\begin{split} i_{IF1} &= i_{d1} - i_{d_2} - i_{d_3} + i_{d_6} \\ &= i_{d_1} [1 - (-1)^n - (-1)^m + (-1)^n (-1)^m] \\ &= i_{d_1} [1 - (-1)^n] [1 - (-1)^m] \\ i_{IF2} &= i_{d_3} - i_{d_4} - i_{d_7} + i_{d_8} \\ &= i_{d_1} [(-1)^m - (-1)^n (-1)^m - 1 + (-1)^n] \\ &= i_{d_1} \{(-1)^m [1 - (-1)^n] - [1 - (-1)^n] \} \\ &= i_{d_1} [1 - (-1)^n] [(-1)^m - 1] \\ &= -i_{d_1} [1 - (-1)^n] [1 - (-1)^m] \\ &= -i_{IF1} \end{split}$$

$$= 2[1 - (-1)^n] [1 - (-1)^m] i_{d_1}$$

$$= 2[1 - (-1)^n] [1 - (-1)^m] i_{d_1}$$

觀察上式可以發現,當 n 為偶數或 m 為偶數時,中頻輸出電流為零,亦即 LO 及 RF 的偶次方諧波訊號不會由中頻輸出。當作基本降頻器時  $f_{IF}=f_{RF}-f_{LO}$ ,取 m=1、 n=-1 代入:

$$i_{IF} = 2[1-(-1)^n][1-(-1)^m]i_{d1} = 8i_{d1}$$

當二級體的對稱性及一對二變壓器都理想的情況下隔絕度與環形雙平衡式二極體混頻器相同,但因製程因素導致二級體不對稱性或一對二變壓器不理想的時候,RF及LO溢漏訊號會出現在兩組環形二極體混頻器的IF兩端抽取處,因為 $i_{IF2}$ 衡等於負的 $i_{IF1}$ ,經過IF巴倫後溢漏訊號會相消掉,可以進一步提升到IF的隔絕度。

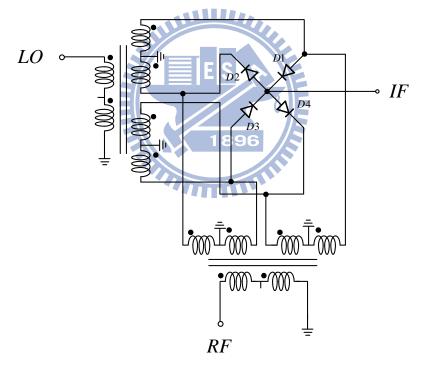

## 2.3 實作一 應用於高速資料傳輸之V頻段雙次降頻器 (使用 TSMC 0.18um CMOS)

為了滿足大的資料傳輸率的無線通信需求,一個非常大的頻寬是必要的,由美國聯邦通信委員會(FCC)所定義的一個乾淨、無執照的頻段:57-64GHz 將是滿足這個需求最好的選擇,此規範所定義的資料傳輸率至少有1Gbps,甚至超過2Gbps,而且在60GHz 這個頻段,大氣中的氧氣吸收率達極大值(10~15dB/km),見圖2.26。這可以減少通道間的相互干擾,有利於短距離通信。操作在60GHz 這樣高的頻率,其對應的波長礼相對的小,使得在做電路設計時,不論是天線的長度設計或是電路內部的走線,也相對的變小。[2]-[4]

圖2.26 微波在大氣中衰減的情形

#### 2.3.1 系統頻率規劃

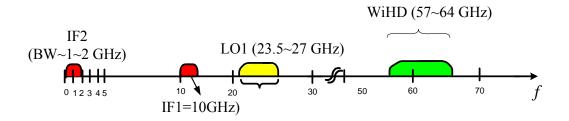

圖 2.27 頻帶設計

#### 2.3.2 整體系統架構

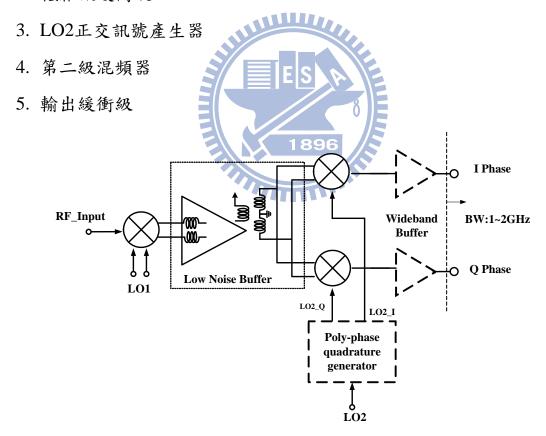

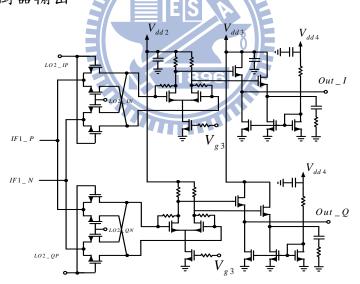

V 頻段雙次降頻器的架構如圖2.28所示,整個電路包含以下幾個部分:

- 1. 環型二極體混頻器

- 2. 低雜訊緩衝級

圖 2.28 系統方塊圖

整體電路如下圖:

圖 2.29 V 頻段雙次降頻器電路圖

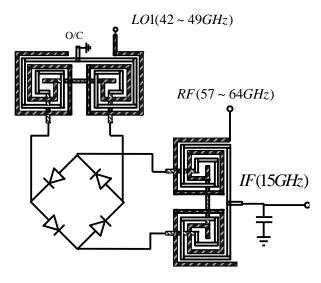

#### 2.3.3 環型二極體混頻設計

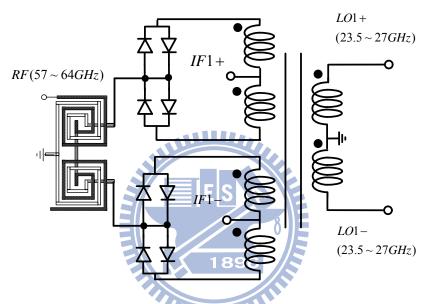

基頻降頻器使用 2.2.5 節的環形雙平衡式二極體混頻器,並搭配實作在晶片上的平面繞線式馬爾尚巴倫[5]-[7]產生差動訊號饋入雙平衡式環型二極體混頻器,IF 訊號由 RF端的馬爾尚巴倫接地點取出,並以並聯電容取代原本的接地點,如此也可以阻絕高頻訊號進入後面的電路。而為了減少傳輸線損耗並縮小面積,使用了 slow wave 的概念,在馬爾尚巴倫下面以 Metall 作浮接遮蔽[8]-[9]。

圖 2.30 第一級降頻器

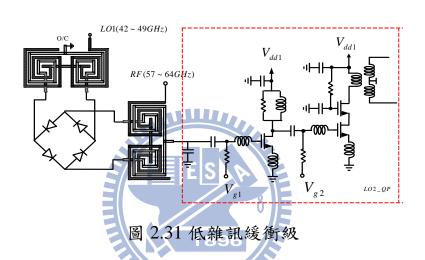

#### 2.3.4 低雜訊緩衝級設計

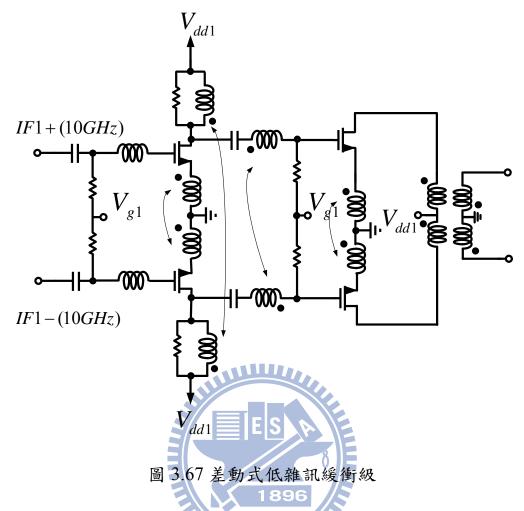

為了抑制後面電路的雜訊及提高整體接收機的增益,在第一及第二級混頻的中間插入了低雜訊緩衝級,設計方式與一般低雜訊放大器雷同,原理在此並不贅述。輸出訊號經過變壓器轉為差動訊號,以做為第二級降頻分為 I、Q 通道。

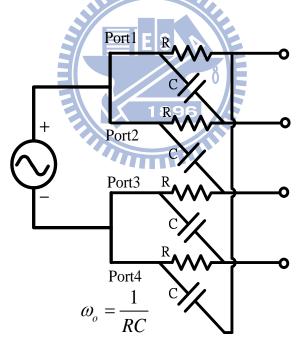

#### 2.3.5 正交訊號產生器

正交訊號產生方式不外乎五種方法[10],方法一,除頻器

(Divider) ,除二除頻器可以將差動訊號轉換為正交訊號,但輸入的差動訊號頻率需要為正交訊號頻率的兩倍,因此在高頻電路設計上將會有困難。方法二,正交相位壓控振盪器(Quadrature VCO),架構有很多種,電路特性則是在 phase noise 與 quadrature accuracy 之間做取捨。方法三,沒有總(Coupler),大部分都還是實作在 MMIC運用中,因為在低頻很難將傳輸線整合進 IC 裡,即使利用繞線縮小面積整合在 IC 上,都很難確保相位的準確度以及振幅的平衡。方法四,環形震盪器(Ring Oscillators),雖然可以提供比 LC 震盪器更寬頻

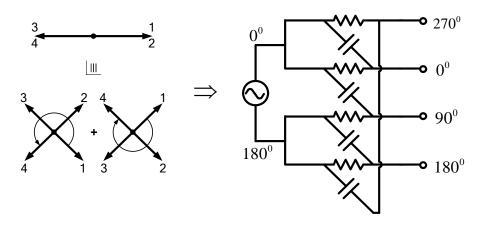

的震盪頻率,但利用此架構無法產生準確的正交訊號與 phase noise,將會惡化整個系統。方法五,由 RC-CR 所組成的正交相位產生器 (polyphase filter),如圖2.32所示,由於製程上的誤差,實作上必須利用多級的 RC-CR 來確保正交相位準確,但相對的電阻損耗也會變大,並且電阻的自振頻率與寄生效應並不適合運用在高頻電路設計。

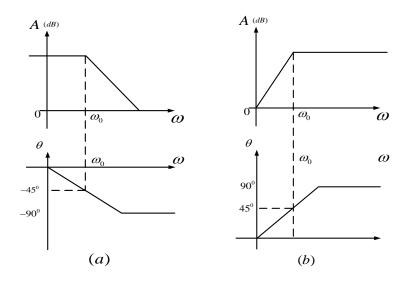

此次實作是以 polyphase 觀念為出發點並加以變化,因此下面將 討論 polyphase 工作原理,如果把輸入端 port1和 port2相接,port3和 port4相接,並且在這兩個輸入端給予差動訊號,這樣輸出端便可以 產生0°、90°、180°、270°四個不同相位的訊號,分析它的原理之前必 須先知道高通濾波器與低通濾波器的頻率響應,其頻率響應如圖2.26

圖2.32 正交相位產生器

圖2.33 RC 電路頻率響應 (a)低通濾波 (b)高通濾波

在極點頻率  $\omega_0$  = 1/RC 時,其相位分別超前 45° (-45°) 及落後 45° (+45°)。 利用重疊原理,把 Port2,Port3,Port4均接地,從 Port1輸入1 $\angle$ 0° V,根據圖2.33的相位響應關係,輸出端 port1相當於訊號經過 RC 低通濾波器之後,相位領先45°(-45°),輸出端 port2相當於訊號經過 CR 高通濾波器之後,相位落後45°(+45°),依此類推可以在 Port1/3產生270°,90°,Port2/4產生180°,0°的訊號,如此一來可以得 quadrature phase,此即正交相位產生器的工作原理。

我們也可以用較簡單的方式來分析正交相位訊號產生的原理,如圖 2.34:當輸入訊號為差動訊號時,由重疊原理可以看為正頻率與負頻率訊號的相加,由於 RC-CR 多重相位濾波器的正頻可過、負頻不可過的特性,可以得到一組相差 90 度的 I、Q 訊號。而為了抗拒製程變異導致能夠產生正交訊號的頻率不準,在此使用兩級多重相位濾波器以增加頻寬。

圖 2.34 正交訊號產生器

#### 2.3.6 電阻式混頻器與輸出緩衝級設計

第二級近頻器採用電阻式混頻器,為了增加輸出中頻頻寬,本電路在混頻器輸出端採用並聯-並聯回授的寬頻放大器,中頻訊號最後由共汲極緩衝器輸出。

圖 2.35 電阻式混頻器與輸出緩衝級設計

#### 2.3.7 晶片量測結果

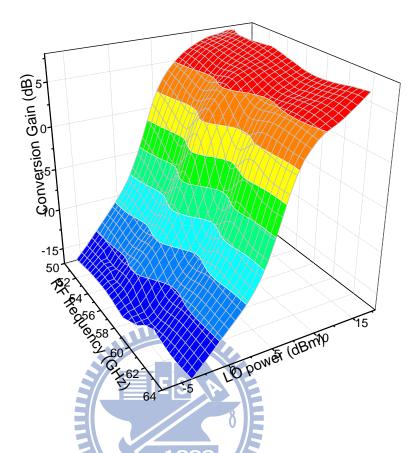

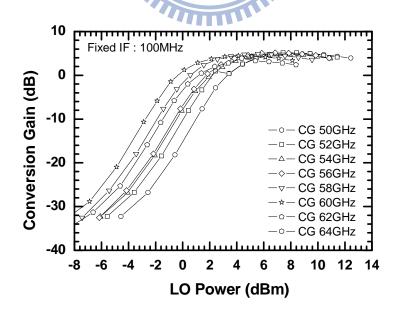

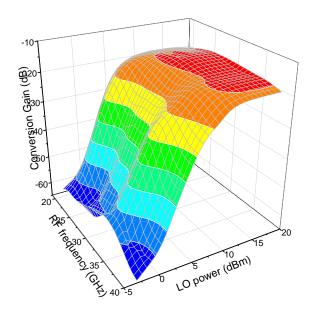

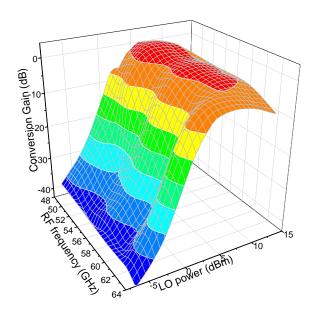

圖 2.36 轉換增益對射頻訊號頻率及本地訊號功率

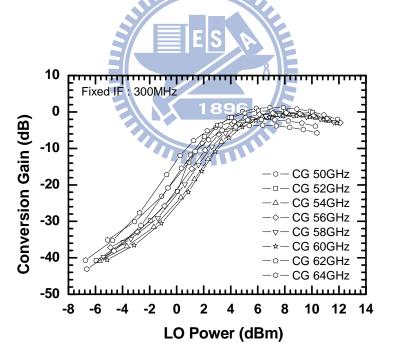

圖2.37 轉換增益對第一本地訊號功率

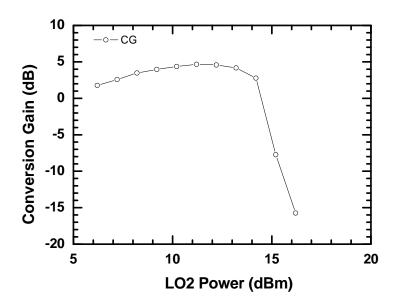

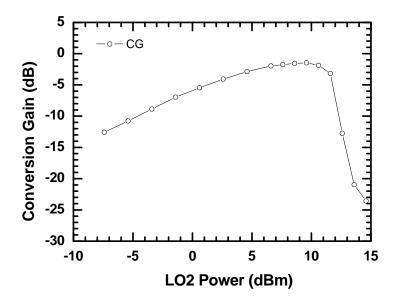

圖2.38 轉換增益對第二本地訊號功率

圖2.39 第一中頻頻寬

圖2.41 雜訊指數

圖2.43 轉換增益對射頻訊號功率

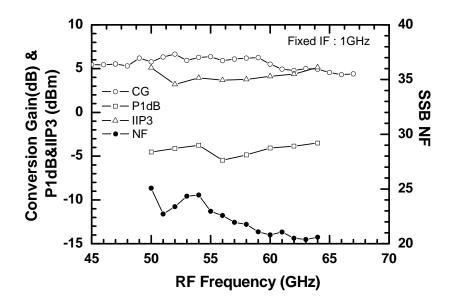

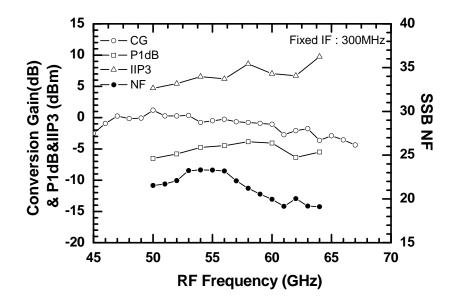

圖2.45 轉換增益、PldB、IIP3與雜訊指數對射頻訊號頻率

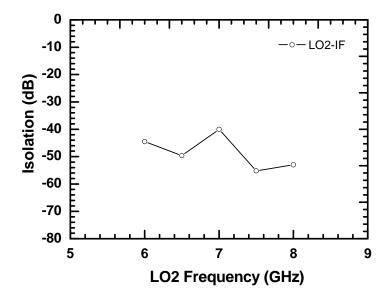

圖2.47 第二本地震盪訊號隔絕度

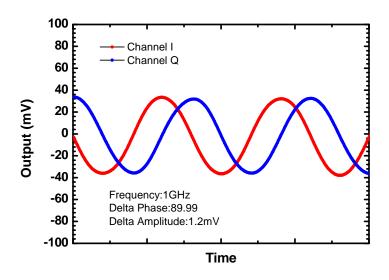

圖2.48 輸出波形圖

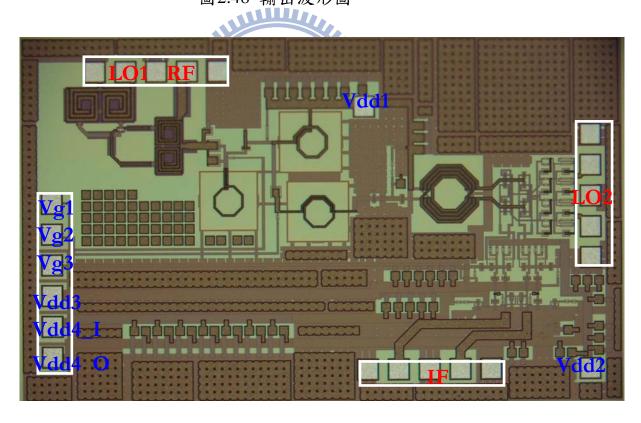

圖 2.49 Die Photo

#### 2.3.8 結果與討論

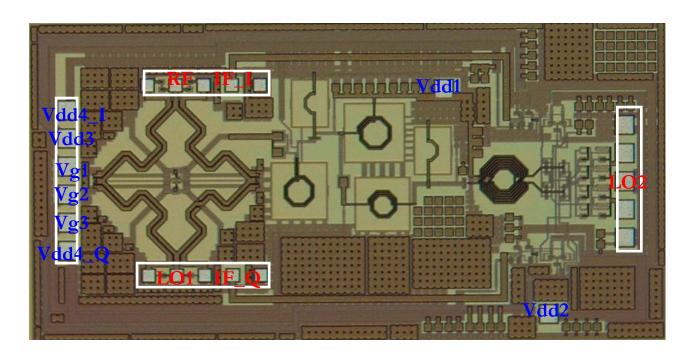

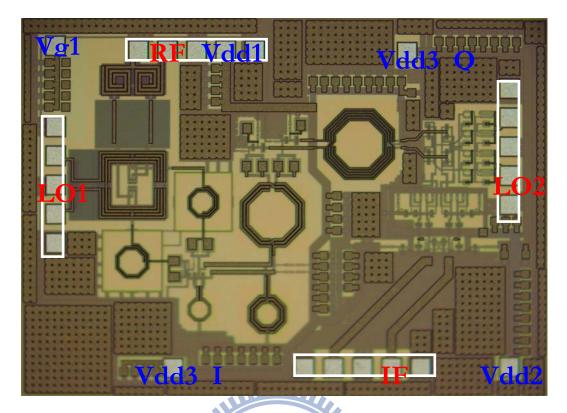

圖 2.49 為 TSMC 0.18um CMOS V 頻段雙次降頻器晶片實作照

片,晶片面積為 1.95mm × 1.18mm,使用 on wafer 量測,RF、LO1、LO2、IF 埠皆採用 GSGSG pad,左面使用 6pin DC 排針,右邊兩個角落各放置一個 DC pad。

從圖 2.37 轉換增益對 LO1 輸入功率做圖中可看出來蕭基二極體操作在剛 turn on 的區域,因此轉換增益對射頻頻率做圖在高頻有掉下來的趨勢,這跟 LO1 選取在較高的頻率有很大的關係,此時儀器輸出的 LO1 功率已達到飽和無法再增加,在 LO 功率足夠的情況下最大的轉換增益有 9dB。

為了要讓最後中頻輸出頻寬盡量的大,我們必須選擇最佳的第一中頻頻率,由圖 2.39 我們選擇第一中頻頻率為 13GHz 來進行量測,最後中頻輸出頻寬為 1.6GHz,射頻頻寬為 36.5~62GHz,IP1B 為-10dBm,IIP3 為-2.5dBm。因為第一級是被動混頻器整體電路雜訊指數較一般降頻器來得要高,但最後整個完整接收機系統會以覆晶封裝方式在最前端整合使用 GaAs 材料的低雜訊放大器,雜訊指數會再進一步的被壓制掉,本電路量測出來的雜訊指數約為 18~20dB。整體量測數據整理如表 2.1:

| Process           | TSMC 0.18um CMOS            |

|-------------------|-----------------------------|

| Conversion Gain   | 9 dB                        |

| RF 3dB Bandwidth  | 36.5 ~ 62 GHz               |

| IF 3dB Bandwidth  | 1.6 GHz                     |

| LO Power          | 14 dBm                      |

| Noise Figure      | 18~20 dB                    |

| IP1dB             | -10 dBm                     |

| IIP3              | -2.5 dBm                    |

| LO1-RF Isolation  | < -28dB                     |

| LO2-IF Isolation  | < -50dB                     |

| Power Consumption | 82 mW                       |

| Die Size          | 1.95 x 1.18 mm <sup>2</sup> |

表 2.1 V 頻段雙次降頻器量測規格表

# 第三章

相位反轉鼠徑分合波器分析

及使用蕭基二極體之

次諧波混頻器設計

#### 3.1 前言

在本章節我們首先將會討論微波電路中很常用到的Rat-race分合波器,並將它實現且應用在積體電路中。傳統的Rat-race,共需要 1.5 λ的傳輸線長度,在晶片中會占去很大的面積,所以必須採取一些微小化的方式。以下將討論從傳統式的 rat-race[1],使用相位反轉(phase inverter)的技術[2]讓電路的縮小,並應用在二極體次諧波混頻器電路上面。因為將 rat-race 整合在 IC 時,矽基板為低阻值的損耗性(lossy)材料(電阻率約 10 Ω·cm),故我們也針對 phase inverter rat-race 具損耗時的特性做討論[3]。為了更進一步地縮小晶片面積,我們也同時考慮使用一對二變壓器(Tri-filar)來操作二極體混頻器。本章電路以TSMC 0.18um CMOS 和 TSMC 0.35um SiGe BiCMOS 製程設計與製做。

#### 3.2 Rat-race 理論分析

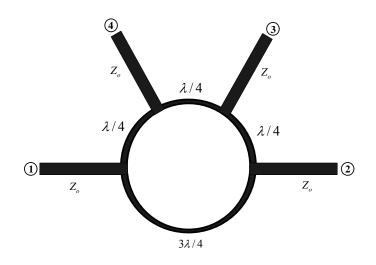

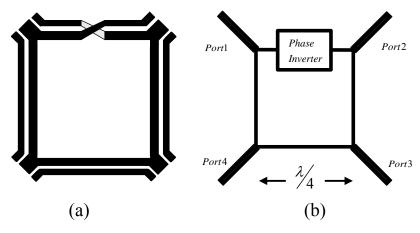

圖 3.1 為傳統式 rat-race 的結構,相關理論幾乎在所有的微波電路相關書籍均可找到,在此不再贅述。本節將針對 phase inverter 微小化方式做理論分析與設計考量[2],最後再討論 phase inverter rat-race 製做在損耗性基板上的特性及相關推導。

圖 3.1 傳統式 Rat race

#### 3.2.1 Rat-race 的相位反轉(phase inverter)理論分析

傳統式 rat-race 因其  $3\lambda/4$  的長度相當長有佔據電路過大的面積以及頻寬很窄的缺點,故我們可利用  $\lambda/4$  長度加上 180 度相位反轉 (phase inverter)取代傳統環型 rat-race 的  $3\lambda/4$  的長度,同時使電路結構更加對稱,也克服了窄頻的缺點。我們以 K. Wu 於 1999 所提出的 微小化 rat-race 做為設計依據[2]。圖 3.2 為相位反轉(phase inverter)的 rat-race。

圖 3.2 相位反轉(phase inverter) rat-race 示意圖

我們由奇、偶模半電路來做 phase inverter 電路分析,求得奇、偶模的 ABCD 矩陣[2]:

$$\begin{bmatrix} A & B \\ C & D \end{bmatrix}_e = \begin{bmatrix} \cos\theta_1 + j\frac{b_1}{Y_1}\sin\theta_1 & j\frac{1}{Y_1}\sin\theta_1 \\ b_2\cos\theta_1 + jY_1\sin\theta_1 + b_1b_2j\frac{1}{Y_1}\sin\theta_1 + b_1\cos\theta_1 & j\frac{b_2}{Y_1}\sin\theta_1\cos\theta_1 \end{bmatrix}$$

$$\begin{bmatrix} A & B \\ C & D \end{bmatrix}_0 = \begin{bmatrix} \cos \theta_1 + j \frac{b_2}{Y_1} \sin \theta_1 & j \frac{1}{Y_1} \sin \theta_1 \\ b_1 \cos \theta_1 + j Y_1 \sin \theta_1 + b_1 b_2 j \frac{1}{Y_1} \sin \theta_1 + b_2 \cos \theta_1 & j \frac{b_1}{Y_1} \sin \theta_1 \cos \theta_1 \end{bmatrix}$$

繼續將 ABCD 矩陣轉為 S 參數:

#### 偶模 S 參數:

$$S_{11e} = \frac{-Z_0 \cos \theta_1 (b_1 + b_2) + jZ_1 \sin \theta_1 (b_2 - b_1) + jZ_0 Y_1 \sin \theta_1 (-1 - b_2 b_1 Z_1^2 + Y_0^2 Z_1^2)}{2 \cos \theta_1 + (Z_0 \cos \theta_1 + jZ_1 \sin \theta_1) (b_1 + b_2) + jZ_0 Y_1 \sin \theta_1 (1 + b_2 b_1 Z_1^2 + Y_0^2 Z_1^2)}$$

$$S_{12e} = S_{21e} = \frac{1892}{2\cos\theta_1 + (Z_0\cos\theta_1 + jZ_1\sin\theta_1)(b_1 + b_2) + jZ_0Y_1\sin\theta_1(1 + b_2b_1Z_1^2 + Y_0^2Z_1^2)}$$

$$S_{22e} = \frac{-Z_0 \cos \theta_1 \left(b_1 + b_2\right) + jZ_1 \sin \theta_1 \left(b_1 - b_2\right) + jZ_1 Z_0 \sin \theta_1 \left(-1 - b_1 b_2 Z_1^2 + Y_0^2 Z_1^2\right)}{2 \cos \theta_1 + \left(Z_0 \cos \theta_1 + jZ_1 \sin \theta_1\right) \left(b_1 + b_2\right) + jZ_0 Y_1 \sin \theta_1 \left(1 + b_2 b_1 Z_1^2 + Y_0^2 Z_1^2\right)}$$

#### 奇模 S 參數:

$$S_{11o} = \frac{-Z_0 \cos \theta_1 (b_1 + b_2) + jZ_1 \sin \theta_1 (b_1 - b_2) + jZ_0 Y_1 \sin \theta_1 (-1 - b_1 b_2 Z_1^2 + Y_0^2 Z_1^2)}{2 \cos \theta_1 + (Z_0 \cos \theta_1 + jZ_1 \sin \theta_1) (b_1 + b_2) + jZ_0 Y_1 \sin \theta_1 (1 + b_2 b_1 Z_1^2 + Y_0^2 Z_1^2)}$$

$$S_{12o} = S_{21o} = \frac{2}{2\cos\theta_1 + Z_0\cos\theta_1(b_2 + b_1) + jZ_1\sin\theta_1(b_1 + b_2) + jZ_1Y_1\sin\theta_1(1 + b_1b_2Z_1^2 + Y_0^2Z_1^2)}$$

$$S_{22o} = \frac{-Z_0 \cos \theta_1 (b_1 + b_2) + jZ_1 \sin \theta_1 (b_2 - b_1) + jZ_0 Y_1 \sin \theta_1 (-1 - b_1 b_2 Z_1^2 + Y_0^2 Z_1^2)}{2 \cos \theta_1 + (Z_0 \cos \theta_1 + jZ_1 \sin \theta_1) (b_1 + b_2) + jZ_0 Y_1 \sin \theta_1 (1 + b_1 b_2 Z_1^2 + Y_0^2 Z_1^2)}$$

轉換而得的S參數,將奇模與偶模做重疊原理得:

$$S_{34} = S_{43} = \frac{1}{2} (S_{11e} - S_{11o}) = \frac{jZ_1 \sin \theta_1 (b_2 - b_1)}{2 \cos \theta_1 + (Z_0 \cos \theta_1 + jZ_1 \sin \theta_1) (b_1 + b_2) + jZ_0 Y_1 \sin \theta_1 (1 + b_1 b_2 Z_1^2 + Y_0^2 Z_1^2)} = -S_{12}$$

由上面的推導最後可以看出 phase inverter 提供了 180 度的效果,可以取代傳統環型 rat-race 的  $\frac{3}{4}\lambda$  傳輸線已達到微小化的目的。

#### 3.2.2 衰減性相位反轉 rat-race 理論分析

過去 rat-race 分合波器的發展皆是以理想傳輸線為運算基礎,也就是無損耗的傳輸線,但是當我們將被動電路整合至晶片中,在損耗性基板上實現時,是否依然還是可以得到一樣的結論呢?接下來我們將衰減常數納入考慮來分析其結果。[5]

首先,我們針對一段具有衰減的傳輸線作分析,ABCD 矩陣為:

$$\begin{bmatrix} A & B \\ C & D \end{bmatrix} = \begin{bmatrix} \cosh(\gamma \ell) & Z \sinh(\gamma \ell) \\ Y \sinh(\gamma \ell) & \cosh(\gamma \ell) \end{bmatrix}$$

此時的 ABCD 矩陣因為帶有衰減常數,所以其元素,不再為單純的三角函數,而是 hyperbolic 函數。另外我們將兩臂的特性阻抗  $Z_a \cdot Z_b$  對特徵阻抗  $Z_o$  作正規化,亦即: $\hat{z}_a = \frac{Z_a}{Z_0}$  , $\hat{z}_b = \frac{Z_b}{Z_0}$  [6]。

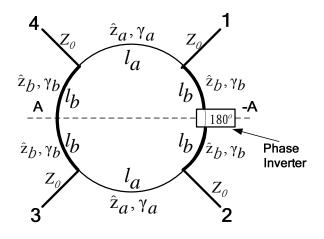

圖 3.3 衰減性相位反轉之 rat-race 分合波器

圖 3.3 為一個衰減性的 phase inverter rat-race 分合波器,我們同樣的用奇、偶模半電路分析之。其中 180° phase inverter 在對稱結構下的奇、偶模半電路,各有 90°的相位差。在偶模半電路,當開路端加上 90°相位差後,就會變成短路;同樣的,在奇模半電路中,短路加上 90°相位差變成開路。

由此分析我們可以知奇、偶模的 ABCD 矩陣:

$$\begin{bmatrix} A & B \\ C & D \end{bmatrix}_{e} = \begin{bmatrix} 1 & 0 \\ \frac{1}{\hat{z}_{b}} \coth(\gamma_{b}l_{b}) & 1 \end{bmatrix} \begin{bmatrix} \cosh(\gamma_{a}l_{a}) & \hat{z}_{a} \sinh(\gamma_{a}l_{a}) \\ \frac{1}{\hat{z}_{a}} \sinh(\gamma_{a}l_{a}) & \cosh(\gamma_{a}l_{a}) \end{bmatrix} \begin{bmatrix} 1 & 0 \\ \frac{1}{\hat{z}_{b}} \tanh(\gamma_{b}l_{b}) & 1 \end{bmatrix}$$

$$= \begin{bmatrix} \cosh(\gamma_{a}l_{a}) + \frac{\hat{z}_{a}}{\hat{z}_{b}} \tanh(\gamma_{b}l_{b}) \sinh(\gamma_{a}l_{a}) & \hat{z}_{a} \sinh(\gamma_{a}l_{a}) \\ \frac{1}{\hat{z}_{b}} \cosh(\gamma_{a}l_{a}) [\tanh(\gamma_{b}l_{b}) + \coth(\gamma_{b}l_{b})] + \sinh(\gamma_{a}l_{a}) [\frac{1}{\hat{z}_{b}} + \frac{\hat{z}_{a}}{\hat{z}_{b}^{2}}] \cosh(\gamma_{a}l_{a}) + \frac{\hat{z}_{a}}{\hat{z}_{b}} \coth(\gamma_{b}l_{b}) \sinh(\gamma_{a}l_{a}) \end{bmatrix}$$

$$\begin{bmatrix} A & B \\ C & D \end{bmatrix}_{o} = \begin{bmatrix} 1 & 0 \\ \frac{1}{\hat{z}_{b}} \tanh(\gamma_{b}l_{b}) & 1 \end{bmatrix} \begin{bmatrix} \cosh(\gamma_{a}l_{a}) & \hat{z}_{a} \sinh(\gamma_{a}l_{a}) \\ \frac{1}{\hat{z}_{a}} \sinh(\gamma_{a}l_{a}) & \cosh(\gamma_{a}l_{a}) \end{bmatrix} \begin{bmatrix} 1 & 0 \\ \frac{1}{\hat{z}_{b}} \coth(\gamma_{b}l_{b}) & 1 \end{bmatrix}$$

$$= \begin{bmatrix} \cosh(\gamma_{a}l_{a}) + \frac{\hat{z}_{a}}{\hat{z}_{b}} \coth(\gamma_{b}l_{b}) \sinh(\gamma_{a}l_{a}) & \hat{z}_{a} \sinh(\gamma_{a}l_{a}) \\ \frac{1}{\hat{z}_{b}} \cosh(\gamma_{a}l_{a}) [\tanh(\gamma_{b}l_{b}) + \coth(\gamma_{b}l_{b})] + \sinh(\gamma_{a}l_{a}) [\frac{1}{\hat{z}_{b}} + \frac{\hat{z}_{a}}{\hat{z}_{b}^{2}}] & \cosh(\gamma_{a}l_{a}) + \frac{\hat{z}_{a}}{\hat{z}_{b}} \tanh(\gamma_{b}l_{b}) \sinh(\gamma_{a}l_{a}) \end{bmatrix}$$

利用變數代換得到

$$\begin{bmatrix} A & B \\ C & D \end{bmatrix}_e = \begin{bmatrix} a & b \\ c & d \end{bmatrix}$$

,  $\begin{bmatrix} A & B \\ C & D \end{bmatrix}_o = \begin{bmatrix} d & b \\ c & a \end{bmatrix}$ , 其中

$$a = \cosh(\gamma_a l_a) + \frac{\hat{z}_a}{\hat{z}_b} \coth(\gamma_b l_b) \sinh(\gamma_a l_a)$$

$$b = \hat{z}_a \sinh(\gamma_a l_a)$$

$$c = \frac{1}{\hat{z}_b} \cosh(\gamma_a l_a) [\tanh(\gamma_b l_b) + \coth(\gamma_b l_b)] + \sinh(\gamma_a l_a) [\frac{1}{\hat{z}_a} + \frac{\hat{z}_a}{\hat{z}_b^2}]$$

$$d = \cosh(\gamma_a l_a) + \frac{\hat{z}_a}{\hat{z}_b} \tanh(\gamma_b l_b) \sinh(\gamma_a l_a)$$

我們可以發現奇、偶模的 ABCD 矩陣元素只有 A、D 位置相反,是因為偶模時由左邊看進去和奇模時由右邊看進去的情形是一樣的,所以會得到上述的結果。

繼續將 ABCD 矩陣轉換為 S 參數:

$$\begin{bmatrix} S_{11} & S_{14} \\ S_{41} & S_{44} \end{bmatrix}_e = \begin{bmatrix} \frac{a+b-c-d}{a+b+c+d} & \frac{2}{a+b+c+d} \\ \frac{2}{a+b+c+d} & \frac{-a+b-c+d}{a+b+c+d} \end{bmatrix}$$

$$\begin{bmatrix} S_{11} & S_{14} \\ S_{41} & S_{44} \end{bmatrix}_o = \begin{bmatrix} \frac{d+b-c-a}{a+b+c+d} & \frac{2}{a+b+c+d} \\ \frac{2}{a+b+c+d} & \frac{-d+b-c+a}{a+b+c+d} \end{bmatrix}$$

$$[S] = \begin{bmatrix} \frac{S_{11e} + S_{11o}}{2} & \frac{S_{11e} - S_{11o}}{2} & \frac{S_{14e} - S_{14o}}{2} & \frac{S_{14e} + S_{14o}}{2} \\ \frac{S_{11e} - S_{11o}}{2} & \frac{S_{11e} + S_{11o}}{2} & \frac{S_{14e} + S_{14o}}{2} & \frac{S_{14e} - S_{14o}}{2} \\ \frac{S_{41e} - S_{41o}}{2} & \frac{S_{41e} + S_{41o}}{2} & \frac{S_{44e} + S_{44o}}{2} & \frac{S_{44e} - S_{44o}}{2} \\ \frac{S_{41e} + S_{41o}}{2} & \frac{S_{41e} - S_{41o}}{2} & \frac{S_{44e} - S_{44o}}{2} & \frac{S_{44e} + S_{44o}}{2} \end{bmatrix}$$

$$= \frac{1}{a+b+c+d} \begin{bmatrix} b-c & a-d & 0 & 2\\ a-d & b-c & 2 & 0\\ 0 & 2 & b-c & d-a\\ 2 & 0 & d-a & b-c \end{bmatrix} = \begin{vmatrix} S_{11} & S_{21} & S_{31} & S_{41}\\ S_{21} & S_{11} & S_{41} & S_{31}\\ S_{31} & S_{41} & S_{11} & -S_{21}\\ S_{41} & S_{31} & -S_{21} & S_{11} \end{vmatrix}$$

其中

$$S_{11} = \frac{\sinh{(\gamma_a l_a)} \left(\hat{z}_a - 1/\hat{z}_a - \hat{z}_a/\hat{z}_b^2\right) - 1/\hat{z}_b \cosh{(\gamma_a l_a)} \left[\tanh{(\gamma_b l_b)} + \coth{(\gamma_b l_b)}\right]}{2\cosh{(\gamma_a l_a)} + 1/\hat{z}_b \left[\hat{z}_a \sinh{(\gamma_a l_a)} + \cosh{(\gamma_a l_a)}\right] \left[\tanh{(\gamma_b l_b)} + \coth{(\gamma_b l_b)}\right] + \sinh{(\gamma_a l_a)} \left[\hat{z}_a + 1/\hat{z}_a + \hat{z}_a/\hat{z}_b^2\right]}$$

$$S_{21} = \frac{\hat{z}_a/\hat{z}_b \sinh{(\gamma_a l_a)} \left[\tanh{(\gamma_b l_b)} - \coth{(\gamma_b l_b)}\right]}{2\cosh{(\gamma_a l_a)} + 1/\hat{z}_b \left[\hat{z}_a \sinh{(\gamma_a l_a)} + \cosh{(\gamma_a l_a)}\right] \left[\tanh{(\gamma_b l_b)} + \coth{(\gamma_b l_b)}\right] + \sinh{(\gamma_a l_a)} \left[\hat{z}_a + 1/\hat{z}_a + \hat{z}_a/\hat{z}_b^2\right]}$$

$$S_{31} = 0$$

$$S_{41} = \frac{2}{2\cosh{(\gamma_a l_a)} + 1/\hat{z}_b \left[\hat{z}_a \sinh{(\gamma_a l_a)} + \cosh{(\gamma_a l_a)}\right] \left[\tanh{(\gamma_b l_b)} + \coth{(\gamma_b l_b)}\right] + \sinh{(\gamma_a l_a)} \left[\hat{z}_a + 1/\hat{z}_a + \hat{z}_a/\hat{z}_b^2\right]}$$

$$Loss = -10 \times \log\left(\left|S_{11}\right|^2 + \left|S_{21}\right|^2 + \left|S_{31}\right|^2 + \left|S_{41}\right|^2\right)$$

由以上結果可知,無論在有無衰減的條件下,port 3 都是一個理想的 isolation port。而  $S_{43} = -S_{21}$  亦可證明  $180^\circ$  phase inverter 可以達到相位反轉,並且與頻率無關。

當分合波器的環臂為等長,並且具有相同的傳播常數與特性阻抗時,亦即 $l_a=2l_b=l$ ,  $\gamma_a=\gamma_b=\gamma=\alpha+j\beta$ ,  $\hat{z}_a=\hat{z}_b$ , 代入上述 S 參數結果如下:

$$S_{21} = \frac{-\sinh(\gamma\ell)[\frac{\cosh(\gamma\ell/2)}{\sinh(\gamma\ell/2)} - \frac{\sinh(\gamma\ell/2)}{\cosh(\gamma\ell/2)}]}{2\cosh(\gamma\ell) + 1/\hat{z}[\hat{z}\sinh(\gamma\ell) + \cosh(\gamma\ell)][\tanh(\gamma\ell/2) + \coth(\gamma\ell/2)] + \sinh(\gamma\ell)[\hat{z} + 2/\hat{z}]}$$

$$=\frac{-\sinh(\gamma\ell)[\frac{\cosh^2(\gamma\ell/2)-\sinh^2(\gamma\ell/2)}{\sinh(\gamma\ell/2)\cosh(\gamma\ell/2)}]}{2\cosh(\gamma\ell)+1/\hat{z}[\hat{z}\sinh(\gamma\ell)+\cosh(\gamma\ell)][\tanh(\gamma\ell/2)+\coth(\gamma\ell/2)]+\sinh(\gamma\ell)[\hat{z}+2/\hat{z}]}$$

$$= \frac{-\sinh(\gamma\ell)[2\operatorname{csch}(\gamma\ell)]}{2\operatorname{cosh}(\gamma\ell) + 1/\hat{z}[\hat{z}\sinh(\gamma\ell) + \cosh(\gamma\ell)][\tanh(\gamma\ell/2) + \coth(\gamma\ell/2)] + \sinh(\gamma\ell)[\hat{z} + 2/\hat{z}]}$$

$$= \frac{-2}{2\operatorname{cosh}(\gamma\ell) + 1/\hat{z}[\hat{z}\sinh(\gamma\ell) + \cosh(\gamma\ell)][\tanh(\gamma\ell/2) + \coth(\gamma\ell/2)] + \sinh(\gamma\ell)[\hat{z} + 2/\hat{z}]}$$

$$= -S$$

所以當分合波器的環臂為等長,並且具有相同的傳播常數與特性阻抗時,訊號由 port1 輸入,在 port 2、4 可以得到功率、相位相反的輸出,port3 為 isolation port。以同樣方法也可以推導出,當訊號由 port4 輸入時,在 port 1、3 可以得到功率、相位相反的輸出,port2 為 isolation port。

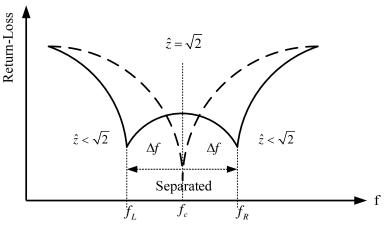

### 3.2.3 衰減性相位反轉 rat-race 阻抗匹配分析

$$S_{11} = \frac{\sinh\left(\gamma_a l_a\right) \left(\hat{z}_a - 1/\hat{z}_a - \hat{z}_a/\hat{z}_b^2\right) - 1/\hat{z}_b \cosh(\gamma_a l_a) \left[\tanh(\gamma_b l_b) + \coth(\gamma_b l_b)\right]}{2\cosh(\gamma_a l_a) + 1/\hat{z}_b \left[\hat{z}_a \sinh(\gamma_a l_a) + \cosh(\gamma_a l_a)\right] \left[\tanh(\gamma_b l_b) + \coth(\gamma_b l_b)\right] + \sinh(\gamma_a l_a) \left[\hat{z}_a + 1/\hat{z}_a + \hat{z}_a/\hat{z}_b^2\right]} = 0$$

$$\rightarrow \sinh(\gamma_a \ell_a)(\hat{z}_a - 1/\hat{z}_a - \hat{z}_a/\hat{z}_b^2) - 1/\hat{z}_b \cosh(\gamma_a \ell_a)[\tanh(\gamma_b \ell_b) + \coth(\gamma_b \ell_b)] = 0$$

$$\rightarrow \sinh(\gamma \ell)(\hat{z} - \frac{2}{\hat{z}}) - \frac{1}{\hat{z}}\cosh(\gamma \ell)[\tanh(\gamma \frac{\ell}{2}) + \coth(\gamma \frac{\ell}{2})] = 0$$

$$\rightarrow \tanh(\gamma \ell)(\hat{z}^2 - 2) = \tanh(\gamma \frac{\ell}{2}) + \coth(\gamma \frac{\ell}{2})$$

$$\rightarrow \tanh(\gamma \ell)(\hat{z}^2 - 2) = 2\coth(\gamma \ell)$$

$$\rightarrow \hat{z}^2 = 2 + 2\coth^2(\gamma \ell)$$

$$\rightarrow \hat{z} = \sqrt{2 + 2\coth^2(\gamma \ell)} = \sqrt{2[1 + \coth^2(\alpha + j\beta)\ell]}$$

$$\gamma \ell = (\alpha + j\beta)\ell = \alpha(\frac{\lambda_c}{y}) + j\frac{2\pi}{\lambda}(\frac{\lambda_c}{y}) = \alpha\frac{c}{f_c\sqrt{\varepsilon_r}}\frac{1}{y} + j\frac{2\pi}{y}(\frac{f}{f_c})$$

首先來看 $\hat{z}$ 的實數部份(圖 3.5),圖形在 $f/f_c$ =1平面的兩邊為完全對稱,在無損耗的情況下,當 $\hat{z} < \sqrt{2}$  滿足阻抗匹配的頻率解有兩個 $f_L$ 、 $f_R$ ,當 $\hat{z} = \sqrt{2}$  時兩個解會重疊即為 $f_C$ ,可以經由改變 $\hat{z}$  將phase inverter rat-race 的頻寬拓展開來(圖 3.4) [7]-[8],如此可以比原本傳統的 rat-race coupler 有更大的頻寬。而當衰減係數增加的時候, $\Delta f$  會隨之增加,如此一來也可以增加頻寬。

圖 3.4 反射損耗 V.S.頻率

圖 3.5 正規化特性阻抗的實數部份

圖 3.6 正規化特性阻抗的虛數部份

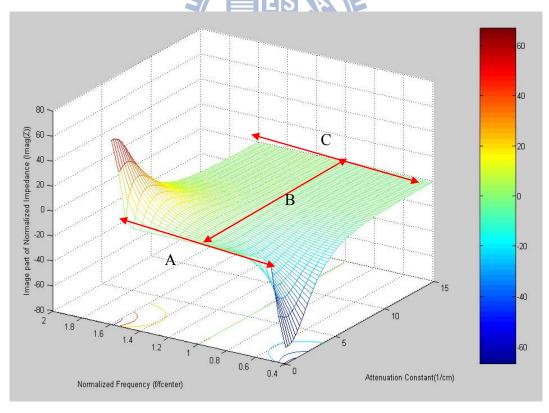

~ 2 的虚數部份如圖 3.6 所示,在有損耗的情況下 2 的虚部不會為 零,這將會造成失真,觀察圖 3.6,我們發現僅有三個地方可以滿足 Z 的虛部趨近於零,即圖 3.1 中的線段 A、B、C,以下各分別討論這三 種情況。

$$Z_{im} = im \left\{ \sqrt{\frac{R + j\omega L}{G + j\omega C}} \right\} \rightarrow 0$$

(1)

$$L = C = 0$$

or  $R \gg L \& G \gg C$

即意味著高導體損耗及高介質損耗(圖 3.6 中的線段 C),如此一來 rat-race 各埠的嵌入損耗也都會相當的大,就算之的虛部近似於零也 無法實際拿來使用。

(2)

$$R = G = 0$$

即理想傳輸線的情況(圖 3.6 中的線段 A),在此條件下 $\hat{z}$  永遠都是一個實數,除非匹配點的 $\theta > 45$ 。 1896

$$(3) \ \frac{R}{L} = \frac{G}{C}$$

即圖 3.6 中的線段 B,也就是無失真傳輸線的情況,在此條件下衰減係數會是跟頻率無關的常數而傳播係數會跟頻率呈線性關係。

$$\gamma = \alpha + j\beta = \sqrt{(R + j\omega L)(G + j\omega C)}$$

$$\xrightarrow{\frac{R}{L} = \frac{G}{C}} \gamma = \sqrt{(R + j\omega L)(\frac{RC}{L} + j\omega C)} = \sqrt{\frac{C}{L}(R + j\omega L)}$$

$$\alpha = R\sqrt{\frac{C}{L}}$$

$$\beta = \omega \sqrt{LC}$$

當在傳輸線無損耗的情況下

$$\alpha = 0 \Longrightarrow$$

$$\coth(j\beta\ell) = \frac{e^{j\beta\ell} + e^{-j\beta\ell}}{e^{j\beta\ell} - e^{-j\beta\ell}} = j \frac{\cos\beta\ell}{\sin\beta\ell} = j \cot\beta\ell$$

$$\hat{z} = \sqrt{2(1 - \cot^2 \beta \ell)} \xrightarrow{\theta = \beta \ell} \hat{z} = \sqrt{2(1 - \cot^2 \theta)}$$

這與在理想傳輸線下得到的結果相同[2],因此無論是理想傳輸線還是衰減性傳輸線,本節所得到的結論都可以適用,理想傳輸線可視為衰減性傳輸線的特例情況 $(\alpha=0)$ 。

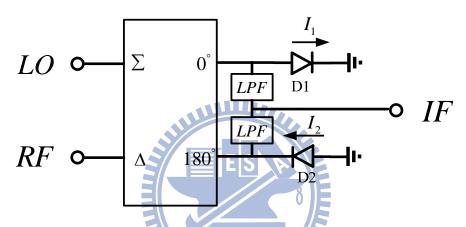

# 3.3 實作一 應用 phase inverter rat-race 的 60GHz 次 諧波混頻器(使用 TSMC 0.18um CMOS)

本電路使用 on-chip 的 phase inverter rat-race 作為 180°單平衡式 二極體混頻器,利用其寬頻特性使 RF 及 LO 埠同時達到阻抗匹配。 RF 訊號由 phase inverter rat-race 的 sum port 輸入, LO 由 differtial port 輸入, RF 及 LO 互為 isolation port[9], 並用反對稱二極體(anti-parallel diode pair APDP)來產生次諧波混頻。整體電路如下圖:

圖 3.7 60GHz 次諧波混頻器電路圖

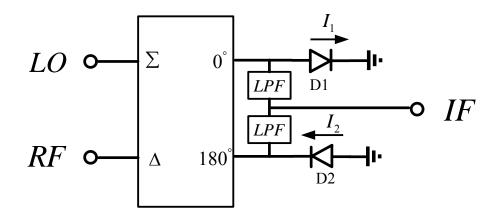

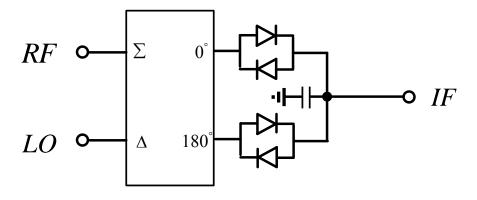

## 3.3.1 二極體混頻原理

本電路採用如圖 3.8 的 180°單平衡式二極體做為混頻器的架構,不同的是在此以反對稱式二極體取代原本的兩顆二極體來產生次諧 1896 波混頻(圖 3.9),如此將更有效地抑制 RF 及 LO 訊號的偶次方諧波項。 混頻器相關理論在章節 2.2.2 及 2.2.4 有詳細推導分析。

圖 3.8 180°單平衡式二極體混頻器架構

圖 3.9 APDP 型式的 180° 單平衡式二極體混頻器架構

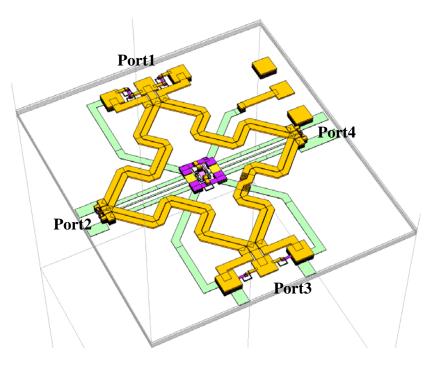

#### 3.3.2 phase inverter rat-race 設計

Rat-race 訊號以共平面波導(coplanar waveguide CPW)方式輸入,再轉換為共平面微帶線(coplanar strip-line CPS),二極體混頻器放置於rat-race 中央以節省佈局面積, port 2、4(圖 3.10)饋入混頻器的傳輸線設計成共平面波導型式以減少損耗,IF 由反對稱二極體的一端抽出,並並聯兩個旁路電容作為 RF 及 LO 訊號的地,並阻絕高頻訊號漏至 IF 端。被動電路部份是使用 Sonnet 軟體模擬其電磁效應,再將模擬結果的 S 參數和二極體部份一起模擬。RF 訊號由圖 3.10 的 port 1 輸入,在 port 2、4 會有同相位訊號,而 LO 訊號由 port 3 輸入,在 port 2、4 會有差動訊號,port 1、3 互為 isolation port。

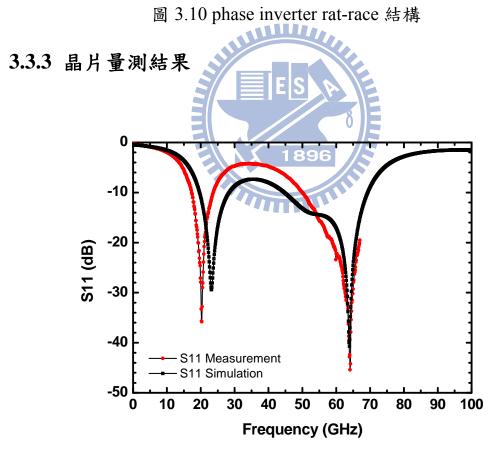

圖3.11 反射損耗

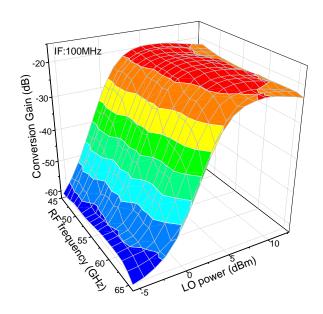

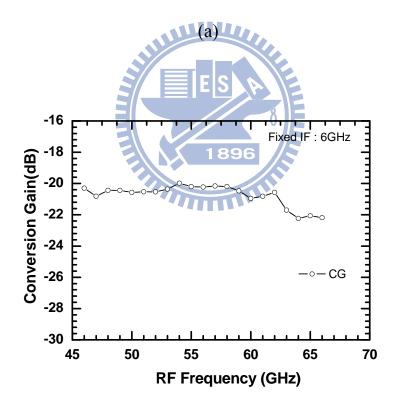

圖3.12 轉換增益對射頻訊號頻率及本地訊號功率 (a)固定中頻訊

號:100MHz (b)固定中頻訊號:6GHz

圖3.13 轉換增益對本地訊號功率 (a)固定中頻訊號:100MHz (b)固

定中頻訊號:6GHz

圖3.14 射頻訊號頻寬 (a)固定中頻訊號:100MHz(b)固定中頻訊號:6GHz

圖3.15 轉換增益對射頻訊號功率 (a)固定中頻訊號:100MHz(b)固定

中頻訊號:6GHz

圖3.17 轉換增益、P1dB、IIP3與雜訊指數對射頻訊號頻率

圖3.19 雜訊指數

圖3.21 Die Photo

## 3.3.4 結果與討論

圖 3.21 為 60GHz 次諧波混頻器晶片實作照片,使用 TSMC 0.18um CMOS 製程,晶片面積為 0.74mm × 0.82mm。電路為被動混頻器,不需外接偏壓。

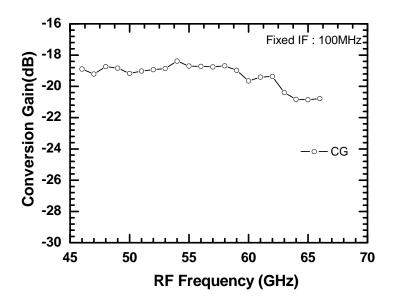

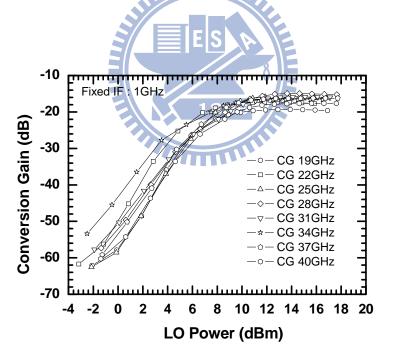

圖 3.11 為 rat-race 混頻器的輸入阻抗匹配,可以看出量測結果與模擬相當貼近,在 RF 及 LO 輸入頻帶皆有-10dB 以下的阻抗匹配。因為蕭基二極體的阻抗與推動功率有關,理論上實際系統應用 LO 可以使用 VGA 調整在不同頻率輸出不同的功率使頻寬更大更平坦,圖 3.12 為轉換增益在不同頻率下輸入不同 LO 功率的結果展示,圖 3.14 為在不同頻率下選擇最佳的 LO 功率的頻寬,射頻頻寬為 46~67GHz,LO 輸入功率為 4 到 6dBm、此時的轉換損耗為 18.4dB。中頻頻寬為 7GHz,量測出的雜訊指數為 16dB 與被動混頻器的轉換損耗大約相等。IP1B 為-1dBm,IIP3 為 9~12dBm,在工作頻帶內 LO 到 IF 的隔絕度小於-20dB,LO 到 RF 的隔絕度小於-10dB 較不理想,二倍頻 LO 到 RF 的隔絕度小於-55dB。整體量測數據整理如表 3.1:

| Process           | TSMC 0.18um CMOS            |

|-------------------|-----------------------------|

| S11               | <-10dB @ 50~67 GHz          |

| Conversion Gain   | -18.4 dB                    |

| RF 3dB Bandwidth  | 46 ~ 66 GHz                 |

| IF 3dB Bandwidth  | 7 GHz                       |

| LO Power          | 4 ∼ 6 dBm                   |

| Noise Figure      | 16 dB                       |

| IP1dB             | -1 dBm                      |

| IIP3              | 9~12 dBm                    |

| LO-IF Isolation   | < -20 dB                    |

| LO-RF Isolation   | <-10 dB                     |

| 2LO-RF Isolation  | <-55 dB                     |

| Power Consumption | 0 mW                        |

| Die Size          | 0.74 x 0.82 mm <sup>2</sup> |

表 3.1 60GHz 次諧波混頻器量測量測規格表

# 3.4 實作二 應用 phase inverter rat-race 的 60GHz 次 諧波混頻器 (使用 TSMC 0.35um SiGe BiCMOS)

本電路將 180°單平衡式二極體混頻器實現在 0.35um SiGe BiCMOS 上,並用 on-chip 的 phase inverter rat-race 產生差動訊號, RF 訊號由 phase inverter rat-race 的 sum port 輸入,LO 由 differtial port 輸入,RF 及 LO 互為 isolation port,並用反對稱二極體(anti-parallel diode pair APDP)來產生次諧波混頻,為了讓 rat-race 有更寬的頻寬使用了 LC 並聯諧振腔來匹配二極體混頻器。整體電路如下圖:

圖 3.22 60GHz 次諧波混頻器電路圖

圖3.23 反射損耗

圖3.25 射頻訊號頻寬

圖3.27 轉換增益對射頻訊號功率 (模擬結果)

圖3.29 隔絕度(模擬結果)

圖3.30 Die Photo

#### 3.4.2 結果與討論

圖 3.23 為 rat-race 混頻器的輸入阻抗匹配,在 RF 及 LO 輸入頻帶皆有-8dB 以下的阻抗匹配。LO 輸入功率為 6dBm 時的轉換損耗為 18dB,射頻頻寬為 48~67GHz,中頻頻寬為 3.7GHz,部分資料尚未量測完畢故先放模擬結果。整體量測數據整理如表 3.2 所示:

| Process           | TSMC 0.35um SiGe BiCMOS     |

|-------------------|-----------------------------|

| S11               | <-8dB @ 57.4~67 GHz         |

| Conversion Gain   | -18 dB                      |

| RF 3dB Bandwidth  | 48 ~ 67 GHz                 |

| IF 3dB Bandwidth  | 3.7 GHz                     |

| LO Power          | 6 dBm                       |

| Noise Figure      | -                           |

| IP1dB             | 4 dBm (Simulation)          |

| IIP3              | 13 dBm (Simulation)         |

| LO-IF Isolation   | < -27 dB (Simulation)       |

| 2LO-IF Isolation  | < -85 dB (Simulation)       |

| LO-RF Isolation   | < -34 dB (Simulation)       |

| 2LO-RF Isolation  | < -66 dB (Simulation)       |

| Power Consumption | 0 mW                        |

| Die Size          | 1.53 x 1.33 mm <sup>2</sup> |

表 3.2 次 谐波混頻器量測數據整理

# 3.5 實作三 V頻帶結合 phase inverter rat-race 的次諧 1896 波雙次降頻器 (使用 TSMC 0.18um CMOS)

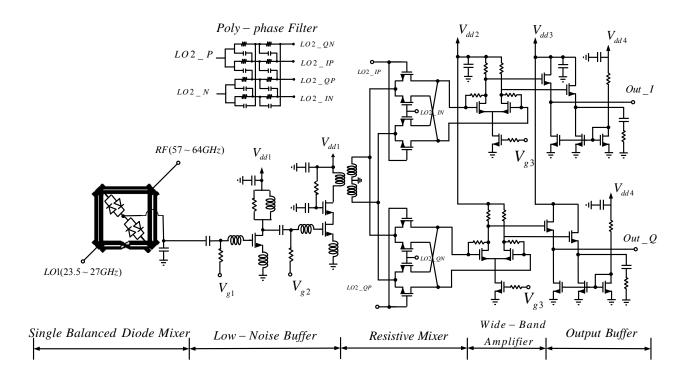

圖 3.31 為 V 頻帶傳輸機示意圖,本章為 V 頻帶次諧波雙次降頻器的實作,如圖 3.31(a)的紅色方框部份。RF 需入訊號為 57 到 64GHz,第一級 LO 選在 23.5 到 27GHz 將 RF 訊號第一次降頻到 10GHz,此頻率為一般 0.18um CMOS 電路可以工作的頻率,第二次降頻將訊號分成 I、Q 通道並降頻到 2GHz 以下,中頻下降至低頻後可以透過後面的 ADDA 將訊號轉成數位訊號用 DSP 的方式來作運算。

圖 3.31 V-Band Transfer 方塊圖 (a)Receiver (b)Transmitter

圖 3.31(a)將整個 V 頻段傳輸系統區分為兩個部份,低雜訊放大 器採用 PHEMT 製程來實現,砷化鎵晶片元件雖較矽晶片元件價格來 得要高,但它具有高轉導、高操作截止頻率、低雜訊等等優秀條件, 適合拿來設計毫米波低雜訊放大器。而其餘元件包括數位電路可以囊 括在同一顆 0.18um CMOS 晶片上面,接收器只需要兩個晶片就可以 完成,如此可以壓低量產的生產成本,整合的部分可以採用覆晶封裝 (Flip-Chip)技術來降低高頻損耗問題。同樣地,圖 3.31(b)為傳送機系 統也可以分為功率放大器及其餘電路兩個部份。

## 3.5.1 系統頻率規劃

圖 3.32 頻帶設計

# 3.5.2 整體系統架構

V 頻段次諧波雙次降頻器電路包含以下幾個部分:

- 1.結合 phase inverter rat-race 的二極體混頻器

- 2.低雜訊緩衝級

- 3.LO2正交訊號產生器

- 4.第二級混頻器

- 5.輸出緩衝級

整體電路如下圖:

圖 3.33 V 頻段次諧波雙次降頻器電路圖

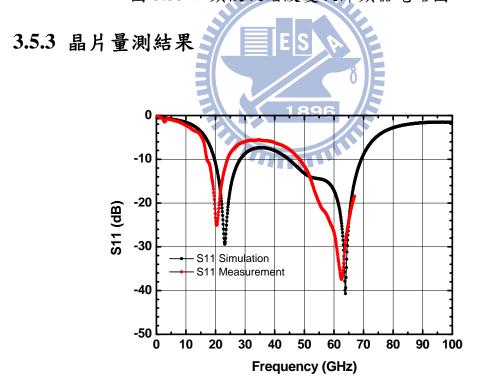

圖 3.34 反射損耗

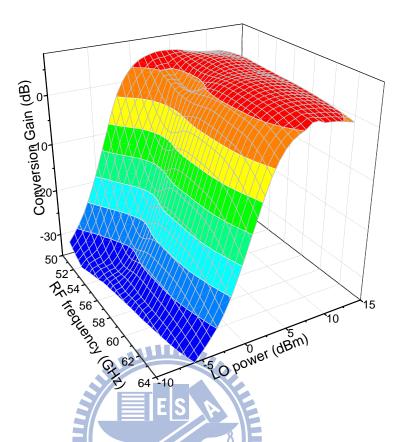

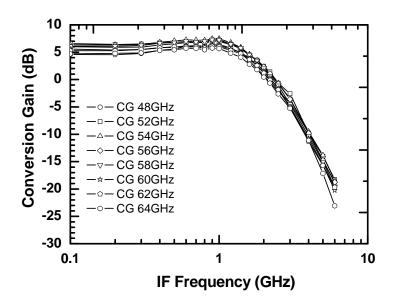

圖 3.35 轉換增益對射頻訊號頻率及本地訊號功率

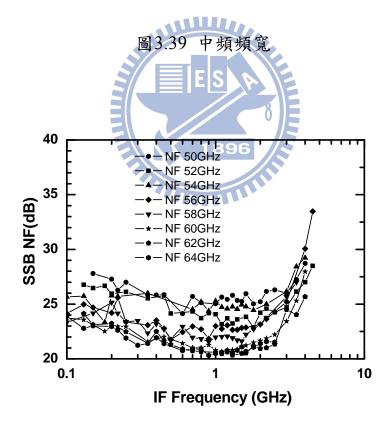

圖3.36 轉換增益對第一本地震盪訊號功率

圖3.38 第一中頻頻寬

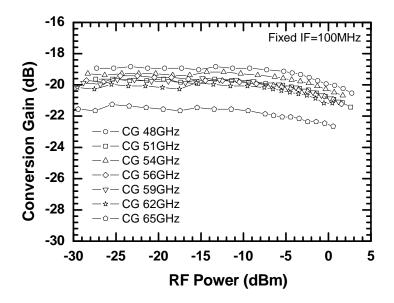

圖3.40 雜訊指數

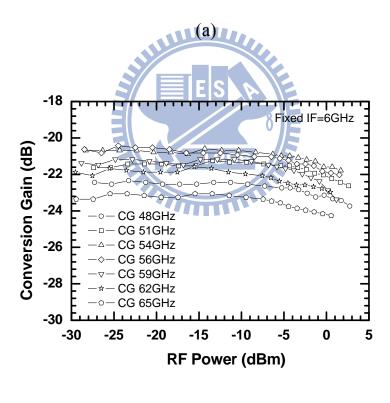

(a)

圖3.42 轉換增益對射頻訊號功率 (a)固定中頻訊號:100MHz(b)固定

中頻訊號:1GHz

(b)

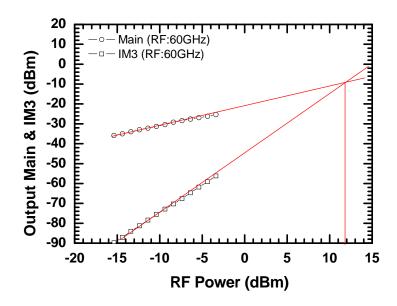

圖3.43 IIP3

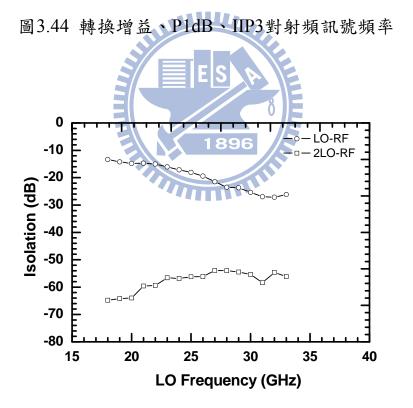

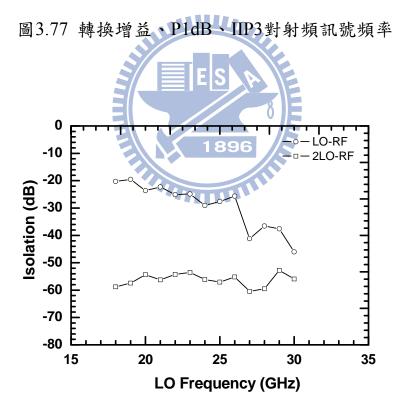

圖3.45 第一本地震盪訊號隔絕度

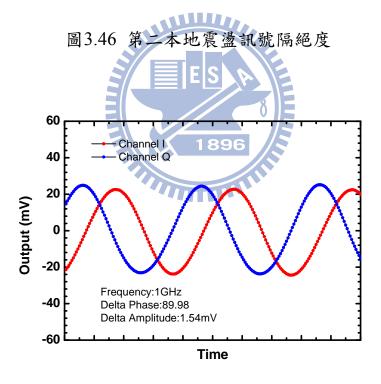

圖3.47 輸出波形圖

圖3.48 Die Photo

## 3.5.4 結果與討論

圖 3.48 為 V 頻段次諧波雙次降頻器晶片實作照片,使用 TSMC 1896 0.18um CMOS 製程,晶片面積為 2.26mm × 1.13mm,使用 on wafer 量測,RF、LO1、LO2、IF 埠皆採用 GSGSG pad,左面使用 6pin DC 排針,右邊兩個角落各放置一個 DC pad。

在不同的頻率選擇最佳的 LO1 輸入功率來量測頻寬,如圖 3.35 的最高陵線,LO 輸入功率為 4 到 6dBm 時的轉換增益為 6dB,圖 3.41 為在不同頻率下選擇最佳的 LO 功率的頻寬,射頻頻寬為 38~67GHz,中頻輸出頻寬為 1.75GHz,IP1B 為-5dBm,IIP3 為 4.5dBm,在工作頻帶內 LO 到 RF 的隔絕度小於-13dB 較不理想,二倍頻 LO 到 RF 的

隔絕度小於-55dB。因為第一級是被動混頻器整體電路雜訊指數較一般降頻器來得要高,但最後整個完整接收機系統會以覆晶封裝方式在最前端整合使用 GaAs 材料的低雜訊放大器,雜訊指數會再進一步的被壓制掉,整體電路量測出來的雜訊指數為 20~25dB。整體量測數據整理如表 3.3 所示:

| Process           | TSMC 0.18um CMOS            |

|-------------------|-----------------------------|

| S11               | <-10dB @ 48~67 GHz          |

| Conversion Gain   | 6 dB                        |

| RF 3dB Bandwidth  | 38 ~ 67 GHz                 |

| IF 3dB Bandwidth  | 1.75 GHz                    |

| LO Power          | 6 dBm                       |

| Noise Figure      | 20~25 dB                    |

| IP1dB             | ES > -5 dBm                 |

| IIP3              | 4.5 dBm                     |

| LO1-RF Isolation  | <-13 dB                     |

| 2LO1-RF Isolation | 1896 /<-54 dB               |

| LO2-IF Isolation  | <-40 dB                     |

| Power Consumption | 70.9 mW                     |

| Die Size          | 2.26 x 1.13 mm <sup>2</sup> |

表 3.3 V 頻段次諧波雙次降頻器量測規格表

# 3.6 實作四 三平衡式星型二極體混頻器 (使用 TSMC 0.35um SiGe BiCMOS)

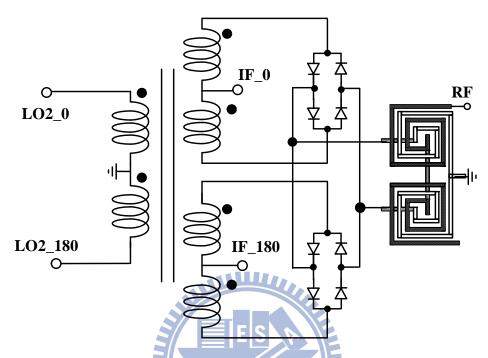

在本節中我們將利用一對二變壓器(Tri-filar)來設計一個工作在 40GHz 的三平衡式星型二極體混頻器,因為採用了平面繞線的方 法,Tri-filar可以實作在晶片中,本電路採用TSMC 0.35 SiGe BiCMOS 製程來設計。整體電路如下圖:

圖 3.49 三平衡式星型二極體混頻器電路圖

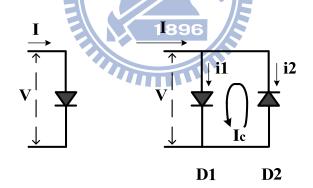

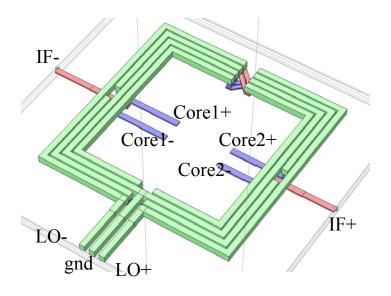

## 3.6.1 混頻器工作原理

RF端首先經由馬爾尚巴倫產生差動訊號,LO由外接巴倫匯入差動訊號,經由圖 3.50 平面式繞線的 Tri-filar[10]分至兩組星型二極體上,二極體混頻器放置於 Tri-filar 的中心以減少佈局面積,中頻差動訊號由 Tri-filar 的中央抽頭處取出,RF及 LO 匯入點各為對方之虛接地點,若 Tri-filar 分出的訊號平衡性夠好的話可以有不錯的隔絕度。三平衡式星型二極體混頻器的相關理論分析可以參照章節 2.2.7。

圖 3.50 平面式 Tri-filar

圖 3.51 反射損耗

圖 3.52 轉換增益對射頻訊號頻率及本地訊號功率

圖3.53 轉換增益對本地震盪訊號功率

圖3.55 中頻頻寬

圖3.57 轉換增益對射頻訊號功率

圖3.59 轉換增益、PldB、IIP3對射頻訊號頻率

圖3.61 射頻訊號隔絕度

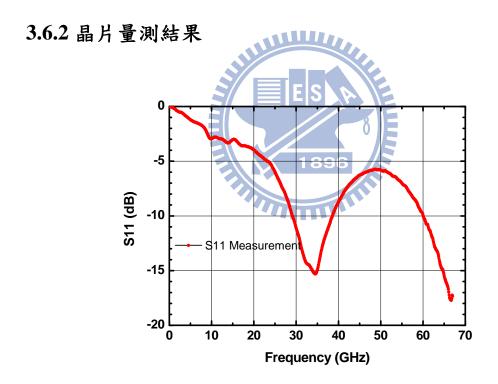

3.6.3 結果與討論

圖 3.62 為 TSMC 0.35um SiGe BiCMOS 三平衡式星型二極體混頻 器晶片實作照片,晶片面積為 0.79mm × 0.92mm。電路為被動混頻 器,不需外接偏壓。

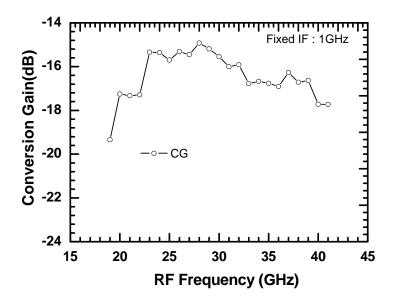

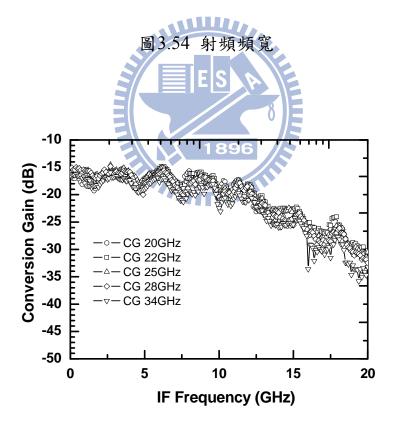

1896

因為蕭基二極體的阻抗與推動功率有關,理論上實際系統應用 LO 可以使用 VGA 調整在不同頻率輸出不同的功率使頻寬更大更平坦,圖 3.52 為轉換增益在不同頻率下輸入不同 LO 功率的結果展示,圖 3.54 為在不同頻率下選擇最佳的 LO 功率的頻寬,射頻頻寬為

19~41GHz, LO 輸入功率為 12dBm,此時的轉換損耗為 15dB。中頻頻寬為 9GHz,量測出的雜訊指數為 15dB 與被動混頻器的轉換損耗大約相等。因考量儀器最大輸出功率,P1dB 最高頻率只能量到31GHz,量測出的 IP1B 為 12~17dBm,IIP3 為 29dBm,此電路的線性度表現非常好。在工作頻帶內 LO 到單端輸出的 IF 隔絕度小於-21dB,當 IF 是以外接巴倫輸出時 LO 到 IF 的隔絕度小於-30dB,LO 到 RF 的隔絕度小於-25dB。整體量測數據整理如表 3.4:

| Process           | TSMC 0.35um SiGe BiCMOS |

|-------------------|-------------------------|

| S11               | √-10dB @ 29~39GHz       |

| Conversion Gain   | -15 dB                  |

| RF 3dB Bandwidth  | F S 19~41GHz            |

| IF 3dB Bandwidth  | 9 GHz                   |

| LO Power          | 12 dBm                  |

| Noise Figure      | 1896 / 15 dB            |

| IP1dB             | 12~17 dBm               |

| IIP3              | 29 dBm                  |

| LO-IF Isolation   | < -21 dB / -30 dB       |

| LO-RF Isolation   | < -25 dB                |

| Power Consumption | 0 mW                    |

| Die Size          | 0.79 x 0.92 mm2         |

表 3.4 三平衡式星型二極體混頻器量測規格表

# 3.7 實作五 V 頻帶結合 Tri-filar 變壓器的次諧波雙次降頻器 (使用 TSMC 0.18um CMOS)

在 3.5 節中的結合 phase inverter rat-race 的 V 頻帶次諧波雙次降頻器,第一次降頻訊號是由反對稱二極體混頻出來的同相位訊

號,並結合在一起送入低雜訊緩衝級,由低雜訊緩衝級最後面的變壓器轉成差動訊號,以第二級降頻器轉換成 I、Q通道。多次的分合波機制有可能造成訊號損耗或不平衡的狀況,那是否可以僅在第一次降頻即產生差動第一中頻訊號,而其後的低雜訊緩衝級就直接對差動訊號來工作,如此將訊號分開的機制就交由第一級降頻器來完成,本章節就以搭配 Tri-filar 的次諧波雙次降頻器來實現這個目標。

## 3.7.1 系統頻率規劃

# 3.7.2 整體系統架構

V 頻帶結合 Tri-filar 變壓器的次諧波雙次降頻器的架構如圖3.49 所示,整個電路包含以下幾個部分:

- 1.次諧波二極體混頻器

- 2.差動式低雜訊緩衝級

- 3.LO2正交訊號產生器

- 4.第二級混頻器

#### 5.輸出緩衝級

圖 3.64 V 頻段次諧波雙次降頻器系統方塊圖

圖 3.65 V 頻段次諧波雙次降頻器電路圖

# 3.7.3 次諧波混頻器原理

本混頻器使用四組反對稱式二極體來作為次諧波混頻器(圖

3.66),射頻訊號由馬爾尚巴倫產生差動訊號輸入兩對反對稱式二極體,LOI 訊號由外接巴倫輸入差動訊號,經由 Tri-filar 分至反對稱式二極體,中頻差動訊號由 Tri-filar 的中央抽頭處取出,RF 及 LO 匯入點各為對方之虛接地點,若 Tri-filar 分出的訊號平衡性夠好的話可以有不錯的訊號隔絕度。

圖 3.66 次諧波二極體混頻器

## 3.7.4 差動式低雜訊緩衝級設計

為了抑制後面電路的雜訊及提高整體接收機的增益,在第一及第二級混頻的中間插入了低雜訊緩衝級,設計方式與一般低雜訊放大器雷同,在此並不贅述。因為第一級降頻器已經將訊號分為差動輸出,低雜訊緩衝級也以差動方式來設計,為了降低佈局面積,以繞線變壓器來取代原本的繞線電感。

# 3.7.5 晶片量測結果

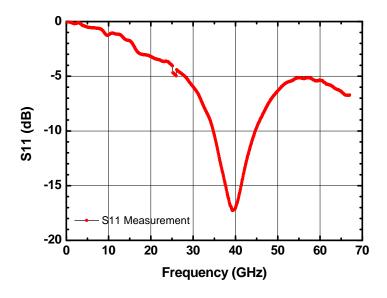

圖 3.68 反射損耗

圖 3.69 轉換增益對射頻訊號頻率及本地訊號功率

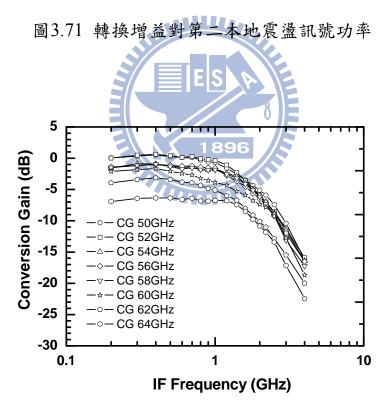

圖3.70 轉換增益對第一本地震盪訊號功率

圖3.72 中頻頻寬

圖3.74 射頻頻寬

圖3.76 IIP3

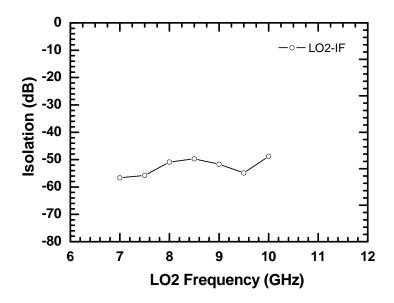

圖3.78 第一本地震盪訊號隔絕度

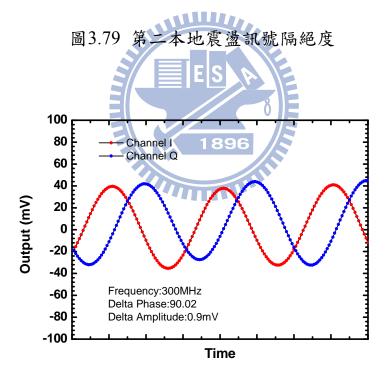

圖3.80 輸出波形圖

圖 3.81 Die Photo

#### 3.7.6 結果與討論

圖 3.81 為 V 頻帶結合 Tri-filar 變壓器的次諧波雙次降頻器晶片實作照片,使用 TSMC 0.18um CMOS 製程,晶片面積為 1.8mm × 1.3mm,使用 on wafer 量測,RF、LO1、LO2、IF 埠皆採用 GSGSG pad,並在四個角落各放置一個 DC pad。

在不同的頻率選擇最佳的 LO1 輸入功率來量測頻寬,如圖 3.69 的最高陵線,LO輸入功率為 6 到 8dBm 時的轉換增益為 0dB,圖 3.74 為在不同頻率下選擇最佳的 LO 功率的頻寬,射頻頻寬為 45~64GHz,中頻輸出頻寬為 1.5GHz, IP1B 為-4dBm, IIP3 為 6~9dBm。在工作頻帶內 LO 到 RF 的隔絕度小於-20dB,二倍頻 LO 到 RF 的隔絕度小

於-54dB。因為第一級是被動混頻器整體電路雜訊指數較一般降頻器來得要高,但最後整個完整接收機系統會以覆晶封裝方式在最前端整合使用 GaAs 材料的低雜訊放大器,雜訊指數會再進一步的被壓制掉,整體電路量測出來的雜訊指數為 19~23dB。整體量測數據整理如表 3.5 所示:

| Process           | TSMC 0.18um CMOS          |

|-------------------|---------------------------|

| S11               | <-10dB @ 35~45 GHz        |

| Conversion Gain   | 0 dB                      |

| RF 3dB Bandwidth  | 45 ~ 64 GHz               |

| IF 3dB Bandwidth  | 1.5 GHz                   |

| LO Power          | 6~8 dBm                   |

| Noise Figure      | 19~23dB                   |

| IP1dB             | ES 4 dBm                  |

| IIP3              | 6~9 dBm                   |

| LO-RF Isolation   | <-20 dB                   |

| 2LO-RF Isolation  | 1896                      |

| Power Consumption | 92.4 mW                   |

| Die Size          | 1.8 x 1.3 mm <sup>2</sup> |

表 3.5 V 頻段次諧波雙次降頻器量測規格表

第四章 應用於WLAN 之單壓操作PHEMT 低雜訊放大器設計

# 4.1 前言

在無線通訊系統中,低雜訊、高增益、低功率消耗之增益放大器 為關鍵性元件之一。HEMT 元件雖有高截止頻率、低雜訊等等良好的 特性,但閘極需給以一負電壓操作,在實際應用上需要另給一顆電源 晶片產生負電壓,如此整體系統將變得複雜且會增加成本,本章會介 紹應用於 WLAN 使用單壓(正壓)操作的低雜訊放大器電路,並以電流 重複利用的觀念降低整體的功率消耗。最後以穩懋 0.15um PHEMT 製程實作操作頻率在 2.4~5.9GHz 及 4.9~5.9GHz 的低雜訊放大器。

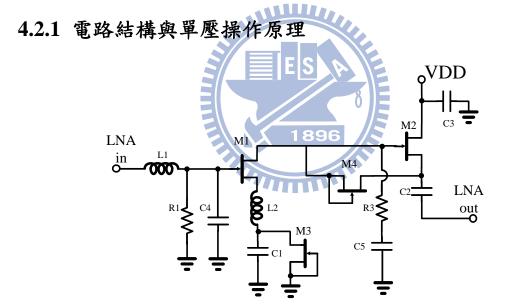

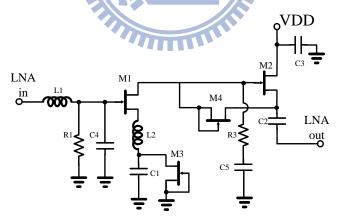

#### 4.2 電路工作原理

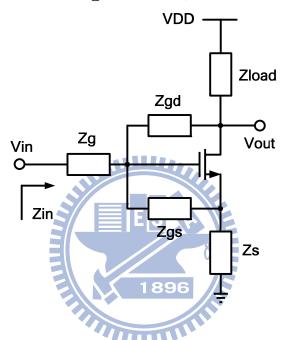

圖 4.1 低雜訊放大器的電路架構

圖 4.1 為本章低雜訊放大器架構,M3 為提供 M1 的直流電流源 [3],輸入端靠並聯電阻 R1 提供零伏偏壓,如此 $V_{GS1}$  將由負的 $V_{DS3}$  決定,同理 M4 提供 M2 的直流偏壓,如此就不需另外提供負電壓來偏壓電晶體的閘極。以直流來看是共電流的疊接電路如圖 4.2(a),因此可以得到較低的功率消耗[4]。依照經驗法則[1],電晶體偏壓在

$I=15\%\sim25\%$   $I_{dss}$  時電晶體貢獻的雜訊最小,本電路選擇 M1 及 M2 偏壓 在  $1/4I_{dss}$  。

圖 4.2 低雜訊放大器的電路架構 (a)直流部份 (b)訊號部份

對高頻信號來說是看到的是兩級的放大電路如圖 4.2(b),第一級放大器為共源極(common-source)放大器,提供電路主要的增益;第二級放大器為共汲極(common-drain)放大器,做輸出阻抗匹配。在第一級放大器的汲極加入了電阻 R3 則進一步提供了電路的穩定度。

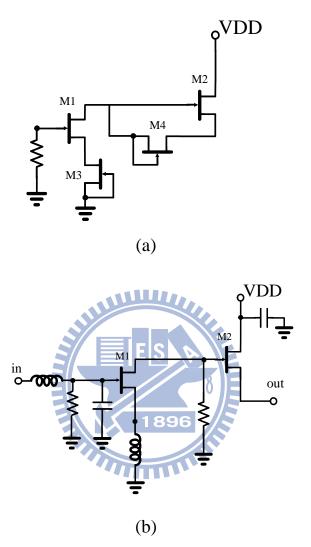

# 4.2.2 具有抗拒製程變異的偏壓電路設計分析

圖 4.3 為圖 4.1 中的第一級直流部份,因為電路對稱的關係

$V_{\scriptscriptstyle B} = \frac{1}{2} V_{\scriptscriptstyle DD}$ 。 M2 的源極與閘極短路在一起,  $V_{\scriptscriptstyle gs\,2} = 0$  ,為提供 M1 的直流電流源。

圖 4.3 以電流援偏壓的共源極放大器

如圖 4.3, $V_{GS1} + V_{DS2} = 0$   $\rightarrow V_{GS1} + \frac{1}{2} \mu_n C_{ox} \left(\frac{W}{L}\right)_1 (V_{GS1} - V_T)^2 \times \frac{1}{\mu_n C_{ox}} \left(\frac{W}{L}\right)_2 (-V_T)$ 假設短通道效應未發生  $V_T = -V_P \Rightarrow V_P : pinch \ off \ voltage$   $V_T = -V_P \Rightarrow V_P : pinch \ off \ voltage$

$$V_{GS1} + \frac{\frac{1}{2} \left(\frac{W}{L}\right)_{1} \left(V_{GS1} + V_{P}\right)^{2}}{\left(\frac{W}{L}\right)_{2} V_{P}} = 0$$

$$\rightarrow V_{GS1} \left(\frac{W}{L}\right)_{2} V_{P} + \frac{1}{2} \left(\frac{W}{L}\right)_{1} \left[V_{GS1}^{2} + 2V_{GS1}V_{P} + V_{P}^{2}\right] = 0$$

$$\rightarrow V_{GS1}^{2} + 2 \left[1 + \frac{\left(\frac{W}{L}\right)_{2}}{\left(\frac{W}{L}\right)_{1}}\right] V_{GS1}V_{P} + V_{P}^{2} = 0$$

為簡化上式,令

$$r = \frac{\left(\frac{W}{L}\right)_2}{\left(\frac{W}{L}\right)_1}$$

代入上式

$$V_{GS1}^2 + 2(1+r)V_{GS1}V_P + V_P^2 = 0$$

$$V_{GS1} = -\left[ (1+r) - \sqrt{(1+r)^2 - 1} \right] V_P$$

定義

$$k = (1+r) \Rightarrow$$

$$-V_{GS1} = \left\lceil k - \sqrt{k^2 - 1} \right\rceil V_P = V_{DS2} \triangleq V_A$$

上式得到的是圖 4.3 中 A 點的電壓,為 k 的函數,而  $k=r+1=\frac{\left(\frac{W}{L}\right)_2}{\left(\frac{W}{L}\right)_1}+1$

由 M2 及 M1 的大小比例決定,因為電晶體的大小的比值不會隨著製程變異而變化,故V<sub>A</sub>不會因為製程變異而漂移。

在本章的設計中,M2的大小是M1的四分之一

$$k = \frac{\left(\frac{W}{L}\right)_2}{\left(\frac{W}{L}\right)_1} + 1 = \frac{5}{4}$$

$$V_A = \left[k - \sqrt{k^2 - 1}\right]V_P = \frac{1}{2}V_P$$

那接下來討論V<sub>A</sub>是否有可能大於V<sub>P</sub>

假設

$$V_A = \left[k - \sqrt{k^2 - 1}\right]V_P < V_P \Leftrightarrow$$

$$\Leftrightarrow k - \sqrt{k^2 - 1} < 1$$

$$\Leftrightarrow k-1 < \sqrt{k^2-1}$$

$$\Leftrightarrow k^2 - 2k + 1 < k^2 - 1$$

$$\Leftrightarrow k > 1$$

因為

$$k=r+1=\frac{\left(\frac{W}{L}\right)_2}{\left(\frac{W}{L}\right)_1}+1恆大於 1,所以 $V_A$ 恆小於 $V_P$$$

也就說 M2 不可能會偏壓在飽和區而會是在線性區,其特性會類似電阻。

接下來討論滿足 M1 操作在飽和區需要的條件

$$V_{GS1} = -\left\lceil k - \sqrt{k^2 - 1} \right\rceil V_P$$

$$V_{GS1} - V_T = -\left\lceil k - \sqrt{k^2 - 1} \right\rceil V_P - V_T$$

$$= \left\lceil \left(1 - k\right) + \sqrt{k^2 - 1} \right\rceil V_P > 0$$

$$V_{DS1} = V_B - V_A$$

$$=V_{\scriptscriptstyle B}+\left\lceil -k+\sqrt{k^2-1}\right\rceil V_{\scriptscriptstyle P}$$

$\geq V_{GS1} - V_T$  (M1 in saturation region)

$$= \left\lceil \left(1 - k\right) + \sqrt{k^2 - 1} \right\rceil V_P$$

$$\Leftrightarrow V_{\scriptscriptstyle B} \geq V_{\scriptscriptstyle P}$$

所以只要B點電壓大於 $V_o$ ,M1就可以操作在飽和區,也就是說 $V_{DD}$ 要大於兩倍的 $V_o$ 。

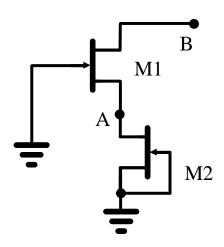

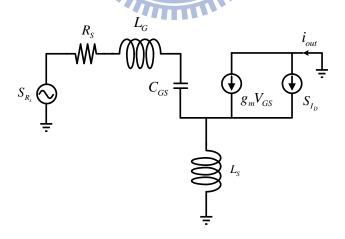

# 4.2.3 带有源極退化的低雜訊放大器分析

一個放大器的雜訊可以寫為[6]

$$\begin{split} F &= F_{\min} + \frac{y_n}{g_s} \big| y_s - y_o \big|^2 \\ &= F_{\min} + 4r_n \frac{\big| \Gamma_s - \Gamma_{opt} \big|}{\Big( 1 - \big| \Gamma_s \big|^2 \Big) \cdot \big| 1 + \Gamma_{opt} \big|^2} \end{split}$$

從中可以發現,若 $\Gamma_s = \Gamma_{opt}$ ,那麼系統雜訊就會等於最小雜訊;若 能將 $Z_{opt}$ 選擇至接近50歐姆,在此條件下輸入阻抗也就能愈接近50歐姆,以助於系統量測以及與前端天線連接。

先簡單地看一帶有源極退化阻抗的共源極放大器(common-source amplifier with source degeneration),如圖4.4

圖4.4 帶有源極退化阻抗的共源極放大器模型

假設 Zgd 很大可以忽略,放大器的輸入阻抗可以寫為[7]

$$Z_{in} = Z_g + Z_{gs} + Z_s \left( 1 + g_m Z_{gs} \right)$$

在微波理論中,在單一頻率下,任何穩定的放大器可以在源極端利用無損耗的被動元件(lossless passive components)使得其輸入阻抗為實數[8]。由於低雜訊放大器通常是放在接收機的前端、天線的後級,故需將輸入阻抗匹配至50歐姆系統。為了避免用電阻做匹配直接提供雜訊,將Zg、Zgs和Zs用被動元件設計,並使它們的和為零;

然而,實際上的被動元件一定有其寄生電阻,故在設計中只能期望三者之和愈小以達到最小的額外增加雜訊。根據這個準則,放大器的輸入阻抗可以另外寫為

$$Z_{in} = g_m Z_{gs} Z_s + R_{\min}$$

其中 Rmin 為 Zg、Zgs 和 Zs 所提供的實數和。

由於 Zgs 實際上就是電晶體內部的 Cgs 提供的阻抗,若要將輸入 阻抗匹配至50歐姆, Zs 應該放一電感來消除 Cgs 的虛部,其值應為

$$L_s = R_{in} \frac{C_{gs}}{g_m} \approx \frac{R_{in}}{\omega_T}$$

若 Rin 固定為50歐姆,那麼截止頻率愈高的元件,源極電感性退化的電感值便可以減小,所佔用的晶片面積也可以縮小,也可以有效地幫助降低雜訊。

圖4.5 帶有源極退化阻抗的共源極放大器小訊號模型

截止頻率高的元件除了可以幫助源極端的電感不需太大佔面積之外, 圖4.5為源極電感性退化的小訊號模型,雜訊指數可以被分析為[9]

$$\begin{split} F = & \frac{S_{i_D} / 4 + S_{RS} \left( \frac{\omega_T}{\omega_0} \frac{1}{2R_S} \right)^2}{S_{RS} \left( \frac{\omega_T}{\omega_0} \frac{1}{2R_S} \right)^2} = 1 + \frac{S_{I_D}}{S_{R_S}} \frac{1}{4 \left( \frac{\omega_T}{\omega_0} \frac{1}{2R_S} \right)^2} \\ = & 1 + \frac{4kT \Gamma g_m}{4kTR_S} \frac{1}{4 \left( \frac{\omega_T}{\omega_0} \frac{1}{2R_S} \right)^2} = 1 + \frac{\Gamma g_m R_S}{\left( \frac{\omega_T}{\omega_0} \right)^2} \end{split}$$

當元件截止頻率愈高,整體雜訊指數可以愈低:另一方面,電晶體的gm 愈大,也可以降低雜訊指數。

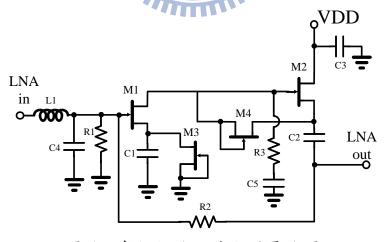

# 4.3 實作一 單壓操作之 2.4~5.9GHz 低雜訊放大器

# (使用 WIN 0.15um pHEMT)

整體電路如下圖所示:

圖 4.6 寬頻低雜訊放大器電路圖

與圖 4.1 的差別在於加上了回授電阻 R2 稍微提高了雜訊指數但是同時提供了電路的穩定性以及寬頻的阻抗匹配。

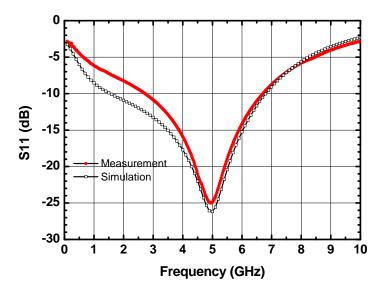

# 4.3.1 晶片量測結果

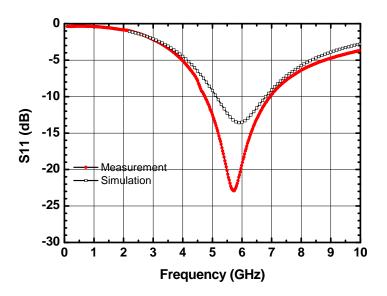

圖4.7 輸入端反射損耗

圖4.8 輸出端反射損耗

圖4.10 雜訊指數與最低雜訊指數

(b)

圖4.11 P1dB (a)2.4GHz (b)5.2GHz

(b)

圖4.12 IP3 (a)2.4GHz (b)5.2GHz

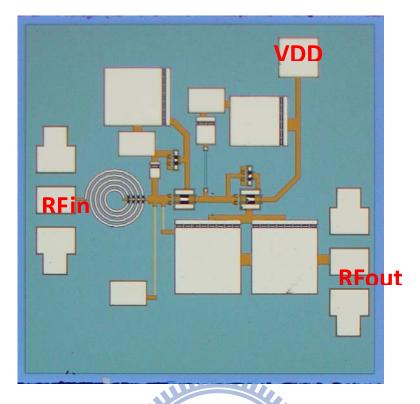

圖4.13 Die Photo

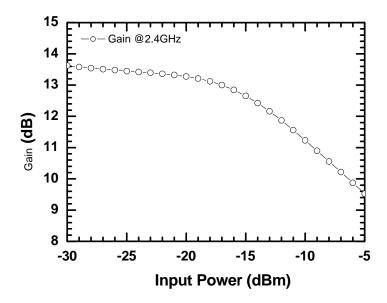

#### 4.3.2 結果與討論

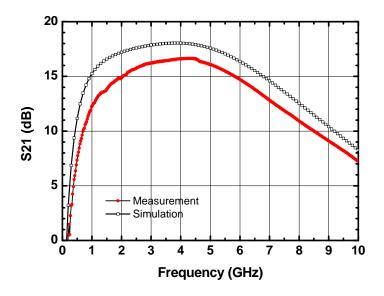

圖 4.13 為 2.4~5.9GHz 寬頻低雜訊放大器電路晶片實作照片,使用製程為 WIN 0.15um PHEMT 5GHz,晶片面積為 1mm × 1mm,以 5 伏偏壓操作。在工作頻率範圍內有超過 13.3dB 的增益,雜訊指數低於 3dB 且與最低雜訊指數非常貼近,輸入及輸出端反射損耗各小於-9.1 及-10.3dB, IP1B 為-15dBm。量測數據整理如表 4.1:

| Process      | WIN 0.15um pHEMT          |

|--------------|---------------------------|

| Frequency    | 2.4~5.9 GHz               |

| $V_{ m DD}$  | 5V                        |

| Current      | 12 mA                     |

| Gain         | > 13.3 dB                 |

| Noise Figure | < 3 dB                    |

| NFmin        | < 2.8 dB                  |

| S11          | < -9.1 dB                 |

| S22          | <-10.3 dB                 |

| IP1dB        | -15 dBm @ 2.4GHz          |

|              | -15 dBm @ 5.2GHz          |

| IIP3         | -15.6 dBm @ 2.4GHz        |

|              | -13.2 dBm @ 5.2GHz        |

| Die Size     | $1 \times 1 \text{ mm}^2$ |

表 4.1 寬頻低雜訊放大器量測規格表

# 4.4 實作二 單壓操作之 5GHz 低雜訊放大器(使用

# WIN 0.15um pHEMT)

整體電路如下圖所示:

1896

圖 4.14 5GHz 低雜訊放大器電路圖

# 4.4.1 晶片量測結果

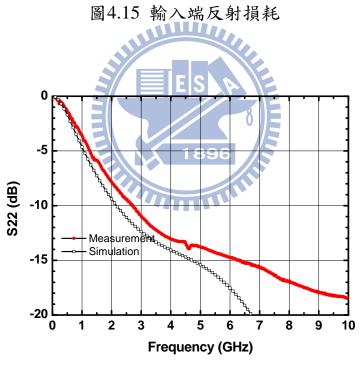

圖4.16 輸出端反射損耗

圖4.18 雜訊指數與最低雜訊指數

圖4.20 c

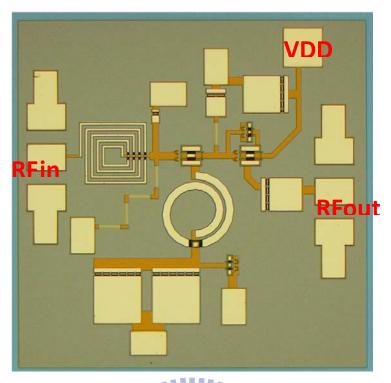

圖4.21 Die Photo

# 4.4.2 結果與討論

圖 4.21 為 5GHz 低雜訊放大器電路晶片實作照片,使用製程為 1896 WIN 0.15um PHEMT 5GHz,晶片面積為 1mm × 1mm,以 3 伏偏壓操作。在工作頻率範圍內有超過 14.9dB 的增益,雜訊指數低於 2.1dB 且與最低雜訊指數非常貼近,輸入及輸出端反射損耗各小於-11.3 及 -13.7dB, IP1B 為-13dBm, IIP3 為-10.9dBm。量測數據整理如表 4.2:

| Process      | WIN 0.15um pHEMT          |

|--------------|---------------------------|

| Frequency    | 4.9~5.9 GHz               |

| $V_{DD}$     | 5V                        |

| Current      | 12 mA                     |

| Gain         | > 14.9 dB                 |

| Noise Figure | < 2.1 dB                  |

| NFmin        | < 2 dB                    |

| S11          | <-11.3 dB                 |

| S22          | <-13.7 dB                 |

| IP1dB        | -13 dBm                   |

| IIP3         | -15.5 dBm                 |

| Die Size     | $1 \times 1 \text{ mm}^2$ |

表 4.2 5GHz 低雜訊放大器量測規格表

第五章 結論 128

論文第二章實現了在 TSMC 0.18um CMOS 製程上設計 V 頻段雙次降頻器的目標,轉換增益為 9dB,中頻輸出頻寬有 1.6GHz,IP1B 為-10dBm,IIP3 為-2.5dBm,雜訊指數為 18~20dB,直流功率消耗 82mW,但因為 LO 設計頻率較高受限於儀器輸出的飽和功率,轉換增益會隨著頻率增加而降低,若能有足夠的 LO 功率應可以得到更寬的射頻頻寬。

論文第三章針對基頻降頻器 LO 頻率過高無法輸入太大的 LO 功 率的問題做了修正,犧牲轉換增益使用次諧波混頻器來降低LO頻 率,實作一及實作二使用 TSMC 0.18um CMOS 及 0.35um SiGe BiCMOS 製程來實作結合了 phase inverter rat-race 的次諧波二極體混 頻器,LO推動功率為6dBm,轉換損耗及雜訊指數約為18.4dB,IP1B 為-1dBm, IIP3 約為 10dBm, 頻寬為 46~66GHz 相當地寬, 這要歸功 於 phase inverter rat-race 寬頻的特性。而實作三使用了 phase inverter rat-race 設計的 V 頻段次諧波雙次降頻器有 6dB 的轉換增益,中頻輸 出頻寬有 1.75GHz, IP1B 為-5dBm, IIP3 為 4.5dBm, 雜訊指數為 20~25dB,直流功率消耗 70.9mW。實作四為使用一對二變壓器設計 的三平衡式星型混頻器,LO推動功率為12dBm,轉換損耗及雜訊指 數約為 15dB,IP1B 為 12~17dBm,IIP3 為 29dBm,頻寬為 19~41GHz, 此電路有相當好的線性度表現。而實作五將V頻段次諧波雙次降頻 器的第一級改用一對二變壓器來設計,LO推動功率為7dBm時有0dB 的轉換增益,中頻輸出頻寬有 1.5GHz, IP1B 為-4dBm, IIP3 為 6~9dBm,雜訊指數為19~23dB,直流功率消耗92.4mW。

論文第四章使用 WIN 0.15um PHEMT 製程來設計單壓操作的低雜訊放大器。2.4~5.9GHz 寬頻低雜訊放大器在工作頻率範圍內有超過13.3dB 的增益,雜訊指數低於 3dB,輸入及輸出端反射損耗各小於-9.1

第五章 結論 129

及-10.3dB, IP1B為-15dBm。而設計在4.9~5.9GHz的低雜訊放大器電路在工作頻率範圍內有超過14.9dB的增益,雜訊指數低於2.1dB 且與最低雜訊指數非常貼近,輸入及輸出端反射損耗各小於-11.3及-13.7dB, IP1B為-13dBm, IIP3為-10.9dBm。

# 參考文獻

#### 第二章:

- [1] 張志揚,"微波工程II上課講義,"交通大學電信工程學系.

- [2] C. H. Doan, "Design of CMOS for 60GHz Applications," *ISSCC 2004 Digest of Tech. Papers*, 2005, pp. 440-538

- [3] B. Razavi, "A 60GHz Direct-Conversion CMOS Receiver," *ISSCC 2005 Digest of Tech. Papers*, 2005, pp. 400-606

- [4] A. Niknejad, R. Brodersen, "TEAM: 60GHz CMOS Radio for Gb/s WLAN," DARPA/MTO TEAM PI Review, Jun 29-30, 2005. Reston, VA, USA

- [5] K. S. Ang and I. D. Robertson, "Analysis and design of impedance-transforming planar Marchand baluns," *IEEE Trans. Microwave Theory Tech.*, vol. 49, no. 2, pp. 402-406, Feb. 2001.

- [6] H.-J. Wei, C.-C. Meng, P.-Y. Wu; K.-C. Tsung, "K-Band CMOS Sub-Harmonic Resistive Mixer With a Miniature Marchand Balun on Lossy Silicon Substrate," *IEEE Microw.Wireless Compon. Lett.*, vol.18, issue 1, pp. 40-42, Jan 2008.

- [7] T. Y. Yang, W.R. Lian, C. C. Yang, and H. K. Chiou, "A Compact V Band Star Mixer Using Compensated Overlay Capacitors in Dual Baluns," *IEEE Microw. Wireless Compon. Lett.*, vol.17, issue 7, pp. 537-539, July 2007.

- [8] T. S. D. Cheung, J. R. Long, K. Vaed, R. Volant, A. Chinthakindi, C. M. Schnabel, J. Florkey, and K. Stein, "On-chip interconnect for mm-wave applications using an all-copper technology and wavelength reduction," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2003, pp. 396–397.

- [9] T. S. D. Cheung and J. R. Long, "Shielded Passive Device for Silicon-Based Monolithic Microwave and Millimeter-Wave Integrated Circuits," *IEEE JSSC*, VOL. 41,NO. 5, MAY 2006.

- [10] 李約廷,"雙頻道可調式吉伯特混頻器、雙頻道差動低雜訊放大器與毫米波驅動放大器,"交通大學碩士論文,2007.

#### 第三章:

- [1] B. R. Heimer, L. Fan, and K. Chang, "Uniplanar hybrid couplers using asymmetrical coplanar striplines," IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES, vol.45, no.12, Dec. 1997.

- [2] T. Q. Wang and K. Wu, "Size-reduction and band-broadening design technique

- of uniplanar hybrid ring coupler using phase inverter for M(H)MIC's," IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES, vol.47, no.2, Feb. 1999.

- [3] 吳柏誼, "鼠徑分合波吉伯特混頻器及次諧波混頻器設計," 交通大學碩士論文, 2007.

- [4] K. Wu, and T. Wang, "Size-Reduction and Band-Broadening Design Technique of Uniplanar Hybrid Ring Coupler Using Phase Inverter for M(H)MIC's," *IEEE Trans. Microw. Theory Tech.*, vol. 47, no. 2, pp. 198-206, Feb. 1999.

- [5] S.-C. Tseng, C.-C. Meng, C.-H. Chang, S.-H. Chang, and G.-W. Huang, "A Silicon Monolithic Phase-Inverter Rat-Race Coupler Using Spiral Coplanar Striplines and Its Application in a Broadband Gilbert Mixer," *IEEE Trans. Microw. Theory Tech.*, vol. 56, no. 8, pp. 1879-1888, Aug. 2008.

- [6] 張世賢, "在考慮衰減常數存在下,相位反轉 Rat-Race 分合波器之設計," 交通大學碩士論文, 2007.

- [7] C.-Y. Chang, C.-C. Yang, and D.-C. Niu, "A multioctave bandwidth rat-race singly balanced mixer," *IEEE Microw. and Guided wave lett.*, vol. 9, no. 1, pp. 37-39, Jan. 1999.

- [8] C.-Y. Chang and C.-C.Yang, "Anovel broadband Chebyshev-response rat-race ring coupler," *IEEE Trans. Microw. Theory Tech.*, vol. 47, no. 4, pp. 455–462, Apr. 1999

- [9] C. Wang, J. Gu, and X. Sun, "Low Cost Compacted Ka-band Rat-Race Mixer", in 2005 Asia-Pacific Microw. Conf., pp. 4pp, Dec. 2005.

- [10] J. R. Long, "monolithic transformers for silicon RF IC design," *IEEE J. Solid-State Circuits*, vol. 35, no. 9, pp. 1368–1382, Sep. 2000.

#### 第四章:

- [1] H. Morkner, M. Frank, and B. Ingram "A novel 3V, 7 mA PHEMT GaAs Active MMIC Mixer/LNA" for Wireless Applications" *IEEE MTT-S Digest*, 1995.

- [2] H. Morkner, M. Frank, and D. Millicker "A high performance 1.5 dB low noise GaAs PHEMT MMIC amplifier for low cost 1.5-8 GHz commercial applications", 1993 Microwave and Millimeter-Wave Monolithic Circuits Symposium, pp. 13-16.

- [3] M. Frank, "The Current Source as a Microwave Biasing Element", *US Patent* #4,912,430.

- [4] M. Frank, 'The 2 to 6 GHz Block GaAs MMIC Amplifier", *Microwave Journal*, Aug.1990, pp 83-92.

- [5] Henrik Morkner, Mike Frank and Shun Yajima, "A 1.7mA Low Noise Amplifier with Integrated Bypass Switch for Wireless 0.05-6 GHz Portable Applications,"

- 2001 IEEE Radio Frequency Integrated Circuits Symposium, pp.235-238.

- [6] G. Gonzalez, *Microwave Transistor Amplifiers Analysis and Design*, 2<sup>nd</sup> ed. New Jersey: Prentice Hall, 1996.

- [7] H. Hashemi and A. Hajimiri, "Concurrent multiband low-noise amplifiers-theory, design, and applications," *IEEE Trans. Microw. Theory Tech.*, vol. 50, no. 1, pp. 288-301, Jan. 2002.

- [8] D. Pozar, *Microwave Engineering*, 3<sup>rd</sup> ed. New York: Wiley, 2005.

- [9] F. Svelto, "Wireless receiver architectures and front-end design in CMOS," *IEEE SSCS Taipei Chapter Short Course*, Dec, 2007.