# 國立交通大學

# 電子工程學系電子研究所

# 博士論文

用於管道模式類比對數位轉換器的

# Background Calibration Techniques for Pipelined Analog-to-Digital Converters

- 研究生:劉鴻志

- 指導教授 : 吳介琮

- 中華民國 九十四 年 十 月

### 用於管道模式類比對數位轉換器 的背景校準技術

### Background Calibration Techniques for Pipelined Analog-to-Digital Converters

研究生 : 劉鴻志 Student : Hung-Chih Liu 指導教授 : 吳介琮 Advisor : Jieh-Tsorng Wu

> 國立交通大學 電子工程學系 電子研究所 博士論文

> > A Dissertation

Submitted to Department of Electronics Engineering College of Electrical Engineering and Computer Science National Chiao-Tung University in partial Fulfillment of the Requirements for the Degree of **Doctor of Philosophy**

> in Electronics Engineering October 2005 Hsin-Chu, Taiwan, Republic of China

> > 中華民國九十四年十月

### 用於管道模式類比對數位轉換器 的背景校準技術

學生:劉鴻志 指導教授:吳介琮

國立交通大學電子工程學系 電子研究所

基於 DSP 信號處理設備的迅速增長,促使了對於一個類比對數位轉換器具有更高的轉換率和更高的解析度的需要.因為連續的振幅資訊的量子化需要類比模式操作,類比對數位轉換器限制了 DSP 系統的實輸量.管道模式類比對數位轉換器被證明能夠運作在很高速,但他們的解析度被限制於元件的不匹配,有限的運算放大器增益,直流補償,電荷注入錯誤和元件的非線性.自已校準和背景校準技術已被開發用來改正這些非線形性.數位式自已校準是一個非常有為的技術,它可以改善基於交換電容器的管道模式類比對數位轉換器的準確性.數位式自已校準最有吸引力的特點是附加最少的類比電路.因而,類比精確度問題被變換成複雜的數位信號處理電路,允許這種方法受益於 CMOS 元件的縮小技術.

數位式自已校準具有低複雜和高準確性好處,但多數實施需要管道級的重組,不 可避免地打亂正常類比對數位轉換器的操作.為了減少這缺點,數個背景校準技術 已被開發使類比對數位轉換器可以連續地校準他們的內部管道級來跟隨環境的變 動,同時執行正常類比對數位的轉換.背景校準的付出是迅速地越來越少,因為隨著 縮小技術的進步,所需的數位電路佔據越來越少的面積.

本論文提出一個 15 位元每秒 40 百萬取樣以交換電容器實現的 CMOS 管道模式類比對數位轉換器. 高解析度的達成是應用一個基於相似性的背景校準技術能監

測重要管道級的轉移特性和連續地改正數字輸出代碼.這個校準可以改正錯誤由於 元件不匹配和有限的運算放大器增益.這個類比對數位轉換器使用 0.25 微米 1P5M CMOS 的技術製造.操作在每秒 40 百萬的採樣率時,這個類比對數位轉換器達成最 大 SNDR 的值是 73.5 dB, 最大 SFDR 的值是 93.3 dB. 晶片面積是 3.8 × 3.6 mm<sup>2</sup>, 並 且操作於 2.5 伏特的電力消耗是 370 mW.

### Background Calibration Techniques for Pipelined Analog-to-Digital Converters

Student : Hung-Chih Liu Advisor : Jieh-Tsorng Wu

#### Department of Electronics Engineering

The rapid growth of DSP-based signal processing equipments prompted a need for a analog-to-digital converter (ADC) with higher conversion rates and higher resolutions. Since quantization of continuous amplitude information requires analog operations, ADCs often limit the throughput of DSP based systems. Pipelined ADCs have been shown to work at very high speeds but their resolution is limited by component mismatches, operational amplifier (opamp) finite gain, offsets, charge injection errors and component nonlinearity. Self calibration and background calibration techniques have been developed to correct for these non-linearities. Digital self-calibration is a very promising technique to improve the accuracy of switched capacitor based pipeline ADCs. The most attractive feature of digital self-calibration is the minimum extra analog circuit involved. Thus, analog precision problems are translated into the complexity of digital signal processing circuits, allowing this approach to benefit from CMOS device scaling. Digital self-calibration has the advantage of low complexity and high accuracy, most implementations need reconfiguration of the pipeline stages, which inevitably disrupt the normal A/D operation. To diminish this deficiency, several background calibration schemes have been developed to enable ADCs to continuously calibrate their internal pipeline stages to track environmental changes while simultaneously performing the normal A/D conversions. The cost of background calibration is decreasing rapidly because the required digital circuits occupy less and less area in scaled technologies.

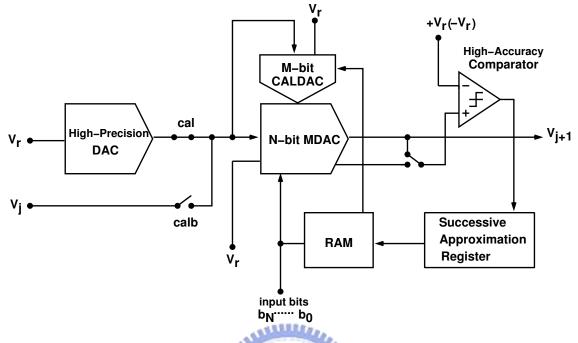

This thesis presents a 15-b 40 MS/s switched-capacitor CMOS pipelined ADC. High resolution is achieved by using a correlation-based background calibration technique that can continuously monitor the transfer characteristics of the critical pipeline stages and correct the digital output codes accordingly. The calibration can correct errors associated with capacitor mismatches and finite opamp gains. The ADC was fabricated using a 0.25  $\mu$ m 1P5M CMOS technology. Operating at a 40 MS/s sampling rate, the ADC attains a maximum signal-to-noise-plus-distortion ratio (SNDR) of 73.5 dB and a maximum spurious-free-dynamic-range (SFDR) of 93.3 dB. The chip occupies an area of 3.8 × 3.6 mm<sup>2</sup>, and the power consumption is 370 mW with a single 2.5 V supply.

### Acknowledgements

First, I would like to thank my advisor Prof. Jieh-Tsorng Wu for his support and guidance in my research. Whenever I encounter the difficulties or problems, he is always patient to give me the direction and encouragement.

I wish to thank my classmates, Miss Zwei-Mei Lee for C model buildup and simulation and chip layout. I also thank Mr. Ju-Ming Chou, Mr. Chang-Tsung Fu, and Mr. Chi-Wei Fan for their support. The authors would like to thank Ting-Hao Wang, Jane Lu, and Ruei-Shiuan Tzeng of the Silicon Integrated System Corp. for engineering support, and Cheng-Yeh Wang of the National Chiao-Tung University for valuable technical discussions. The authors also thank the National Chip Implementation Center for chip fabrication. Without their help, this project would never be done well.

Finally, I would like to express my greatest appreciation to my wife, Miss Judith Cheng, my children, and other members of my family for their unconditional support and encouragement.

HUNG-CHIH LIU

National Chiao-Tung University 2005, October

# Contents

| 中  | 文摘      | æ                                        | i    |

|----|---------|------------------------------------------|------|

| Er | nglish  | Abstract                                 | iii  |

| Ac | cknow   | ledgements                               | v    |

| Li | st of 7 | Tables                                   | xi   |

| Li | st of H | Figures 2                                | xiii |

| 1  | Intro   | oduction                                 | 1    |

|    | 1.1     | Motivation                               | 1    |

|    | 1.2     | Organization                             | 5    |

| 2  | Prin    | ciples of Pipelined ADCs                 | 7    |

|    | 2.1     | Introduction                             | 7    |

|    | 2.2     | Generalized Mathematical Description     | 8    |

|    | 2.3     | Minimal Base-2 Converter                 | 11   |

|    | 2.4     | Error Sources in a Pipelined Stage       | 13   |

|    | 2.5     | Digital Error Correction with Redundancy | 16   |

|    | 2.6     | Pipelined ADC Examples                   | 20   |

|    |         | 2.6.1 Example 1                          | 20   |

|    |         | 2.6.2 Example 2                          | 21   |

|    |         | 2.6.3 Example 3                          | 23   |

|    | 2.7     | CMOS Circuit Implementation              | 28   |

|   | 2.8  | Summary                                                 | 32 |

|---|------|---------------------------------------------------------|----|

| 3 | Pipe | elined ADC Calibration Techniques                       | 35 |

|   | 3.1  | Introduction                                            | 35 |

|   | 3.2  | Analog Calibration Techniques                           | 36 |

|   | 3.3  | Digital Calibration Techniques                          | 38 |

|   |      | 3.3.1 Foreground Calibration Techniques                 | 40 |

|   |      | 3.3.2 Correlation-Based Background Calibration          | 49 |

|   | 3.4  | A New Digital Background Calibration technique          | 52 |

|   | 3.5  | Other Background Calibration Techniques                 | 59 |

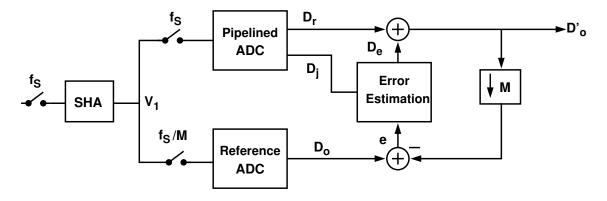

|   |      | 3.5.1 Background Calibration Using Reference ADC        | 59 |

|   |      | 3.5.2 DNC Plus GEC Background Calibration               | 61 |

|   |      | 3.5.3 Redundant Residue Mode for Background Calibration | 64 |

|   | 3.6  | Summary                                                 | 67 |

| 4 | A 15 |                                                         | 69 |

|   | 4.1  |                                                         | 69 |

|   | 4.2  | Architecture                                            | 70 |

|   |      |                                                         | 70 |

|   |      | 4.2.2 Stage Accuracy Requirement                        | 72 |

|   | 4.3  | Analog Circuits                                         | 75 |

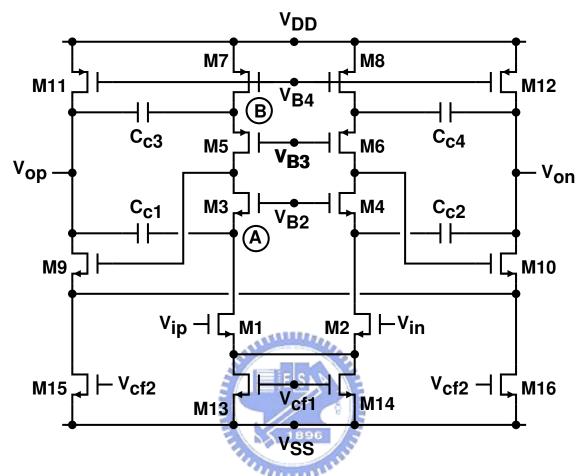

|   |      | 4.3.1 Operational Amplifier                             | 76 |

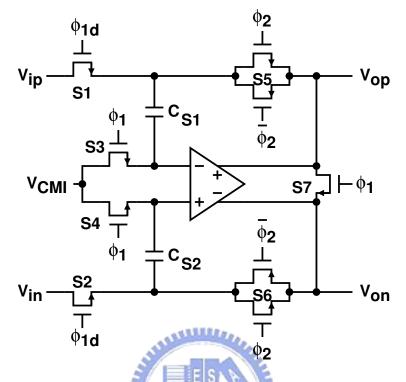

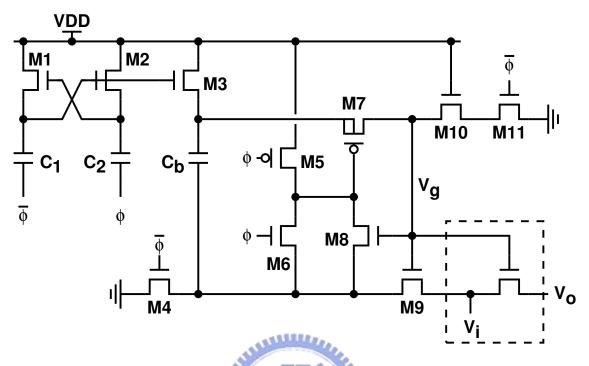

|   |      | 4.3.2 Sample-and-Hold Amplifier                         | 78 |

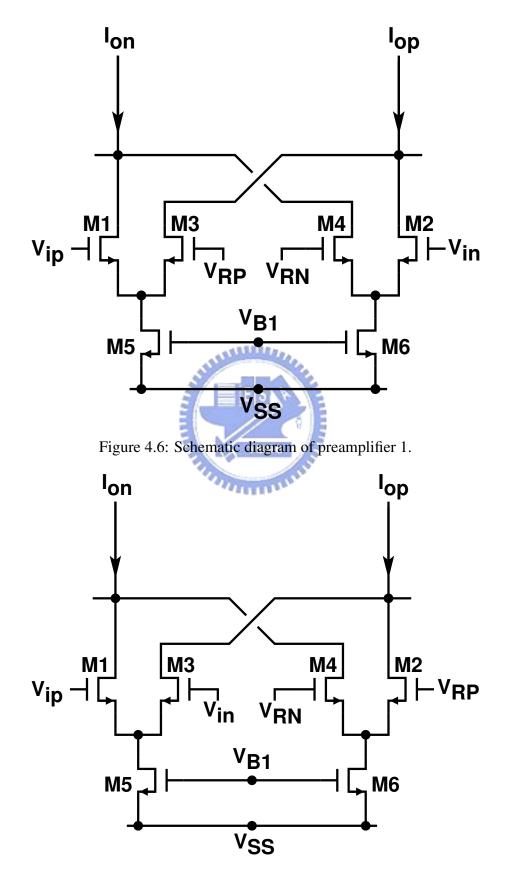

|   |      | 4.3.3 Comparator                                        | 82 |

|   | 4.4  | Digital Circuits                                        | 86 |

|   | 4.5  | Experimental Results                                    | 88 |

|   | 4.6  | Summary                                                 | 94 |

| 5 | Sum  | nmary and Future Works                                  | 95 |

|   | 5.1  | Summary                                                 | 95 |

|   | 5.2  | Recommendations for Future Investigation                | 97 |

### Bibliography

ix

# **List of Tables**

| 2.1 | Static parameters of the 1.5bit/stage                     | 21 |

|-----|-----------------------------------------------------------|----|

| 2.2 | Static parameters of the DRD stage                        | 22 |

| 2.3 | Static parameters of the 1-bit/stage                      | 26 |

| 2.4 | Static parameters of the overrange stage                  | 26 |

|     | Transistor dimensions of the opamp used in the first MDAC |    |

| 4.2 | Transistor dimensions of the comparator                   | 86 |

| 4.3 | ADC performance summary                                   | 94 |

# **List of Figures**

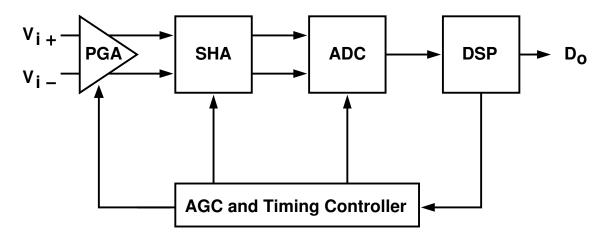

| 1.1  | Block diagram of a DSP-based system                                    | 2  |

|------|------------------------------------------------------------------------|----|

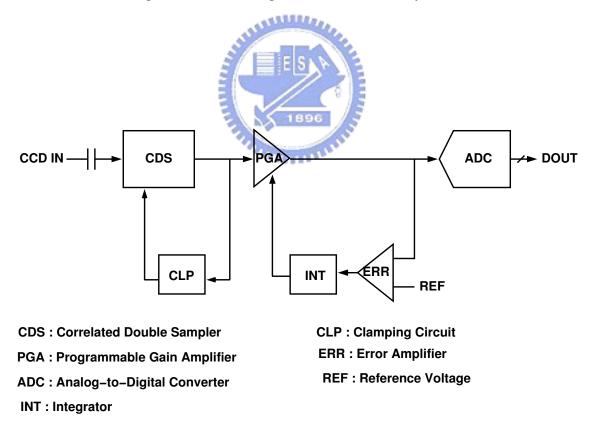

| 1.2  | Conventional CCD front-end scheme.                                     | 2  |

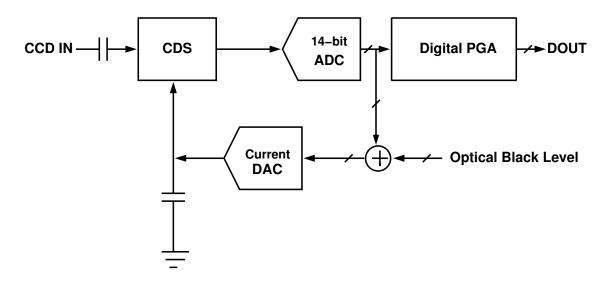

| 1.3  | New CCD front-end scheme                                               | 3  |

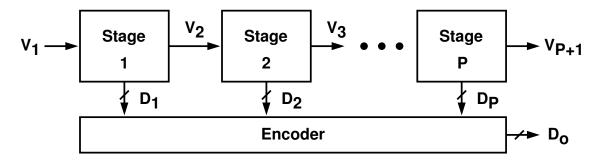

| 2.1  | A pipelined ADC.                                                       | 7  |

| 2.2  | Block diagram of a pipeline stage                                      | 8  |

| 2.3  | A pipelined ADC                                                        | 12 |

| 2.4  | Transfer curve of a pipelined stage with threshold offsets             | 14 |

| 2.5  | Transfer curve of a pipelined stage with non-ideal DAC references      | 15 |

| 2.6  | non-ideal-DAC effect on the whole ADC characteristic                   | 15 |

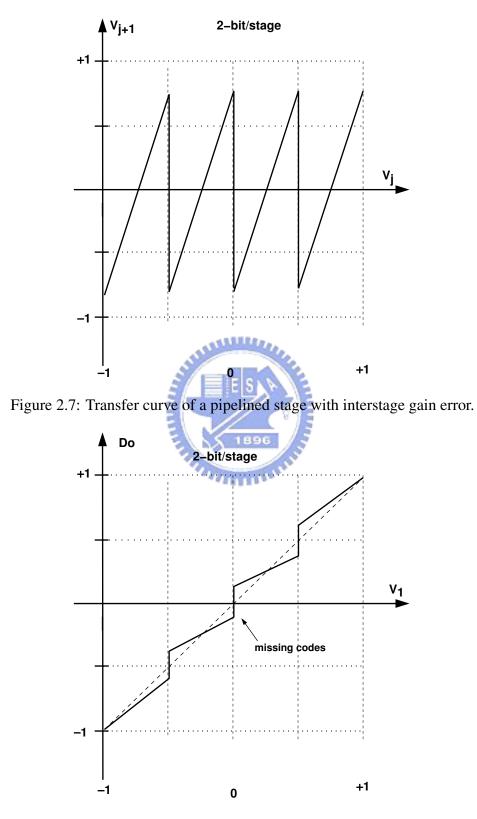

| 2.7  | Transfer curve of a pipelined stage with interstage gain error         | 17 |

| 2.8  | interstage-gain-error effect on the whole ADC characteristic           | 17 |

| 2.9  | Redundant stages                                                       | 18 |

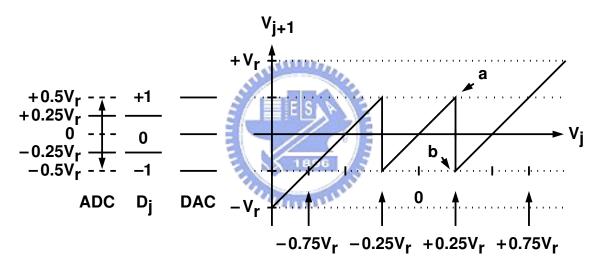

| 2.10 | Transfer function of 1.5-bit per stage with dynamic range doubling     | 22 |

| 2.11 | Conversion result of the DRD example.                                  | 23 |

| 2.12 | Transfer characteristic for the 1-bit converter                        | 24 |

| 2.13 | Overrange transfer characteristic.                                     | 25 |

| 2.14 | Architecture of the ADC including overrange stages                     | 25 |

| 2.15 | A SHA schematic.                                                       | 28 |

| 2.16 | A general model of a SC pipeline stage.                                | 29 |

| 2.17 | A radix-2 1.5-bit switched-capacitor (SC) pipeline stage               | 30 |

| 2.18 | The conversion characteristic of the radix-2 1.5-bit SC pipeline stage | 30 |

| 2.19 | The operations of the radix-2 1.5-bit SC pipeline stage.               | 31 |

| 2.20 | A 1.5bit stage with dynamic range doubling                                   | 32 |

|------|------------------------------------------------------------------------------|----|

| 3.1  | Block diagram illustrating the analog self-calibration system                | 37 |

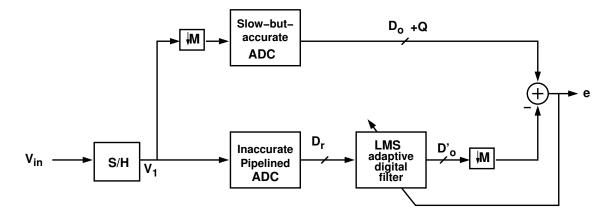

| 3.2  | Error correction of pipelined ADC with adaptive least mean square algo-      |    |

|      | rithm                                                                        | 39 |

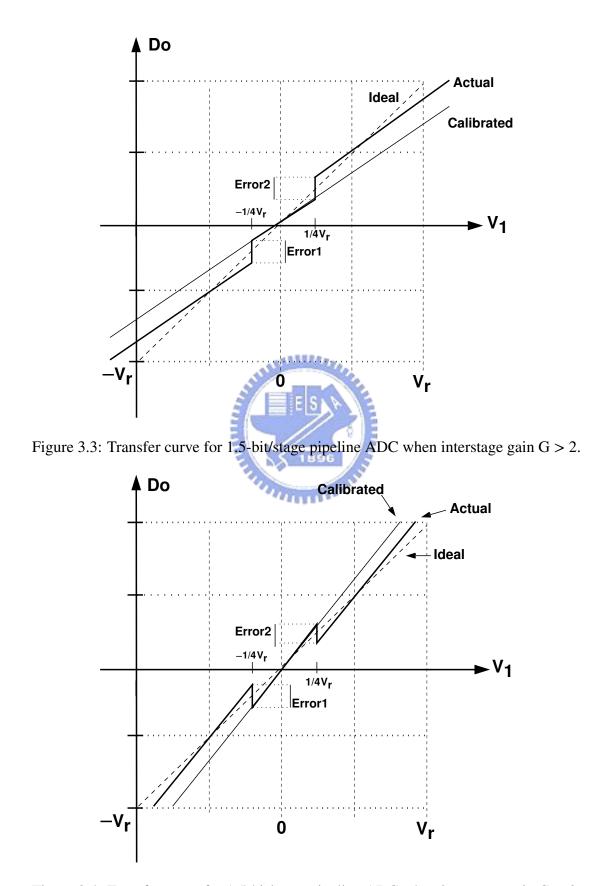

| 3.3  | Transfer curve for 1.5-bit/stage pipeline ADC when interstage gain $G > 2$ . | 41 |

| 3.4  | Transfer curve for 1.5-bit/stage pipeline ADC when interstage gain $G < 2$ . | 41 |

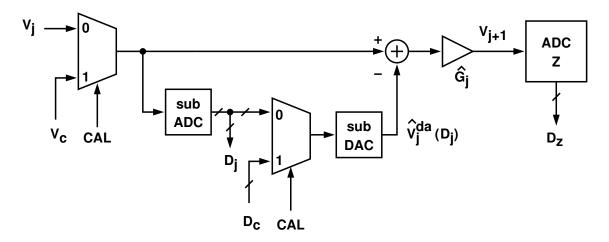

| 3.5  | Digital calibration of the <i>j</i> -th pipeline stage                       | 43 |

| 3.6  | The conversion characteristic of a radix-2 1.5-bit SC pipeline stage under   |    |

|      | calibration.                                                                 | 44 |

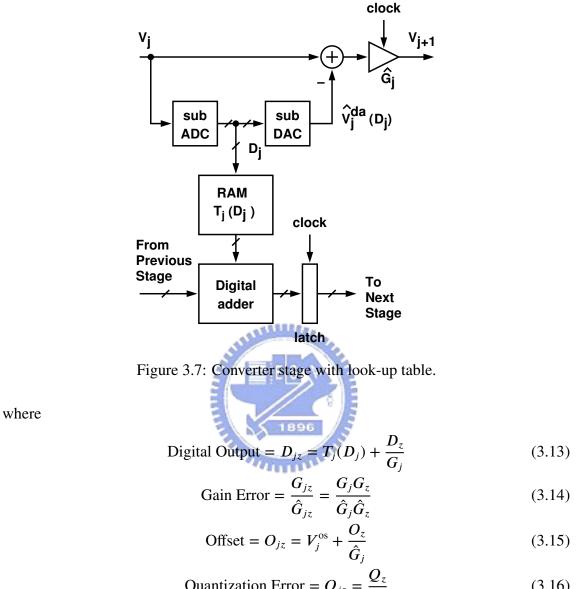

| 3.7  | Converter stage with look-up table                                           | 46 |

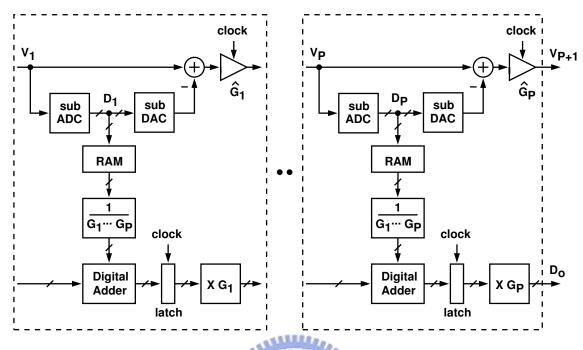

| 3.8  | Pipelined ADC architecture with look-up table.                               | 48 |

| 3.9  | The gain calibration loop to illustrate the correlation-based calibration    |    |

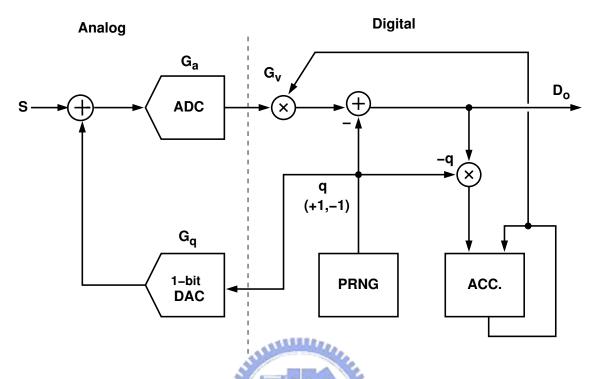

|      | method                                                                       | 50 |

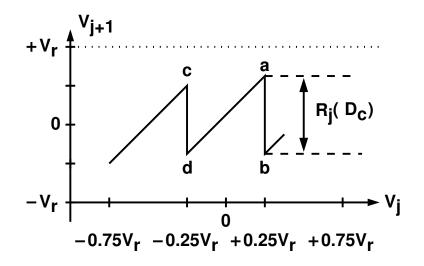

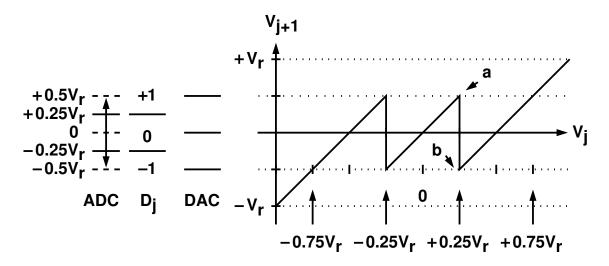

| 3.10 | The conversion characteristic of the radix-2 1.5-bit SC pipeline stage       | 52 |

| 3.11 | A radix-2 1.5-bit switched-capacitor (SC) pipeline stage                     | 52 |

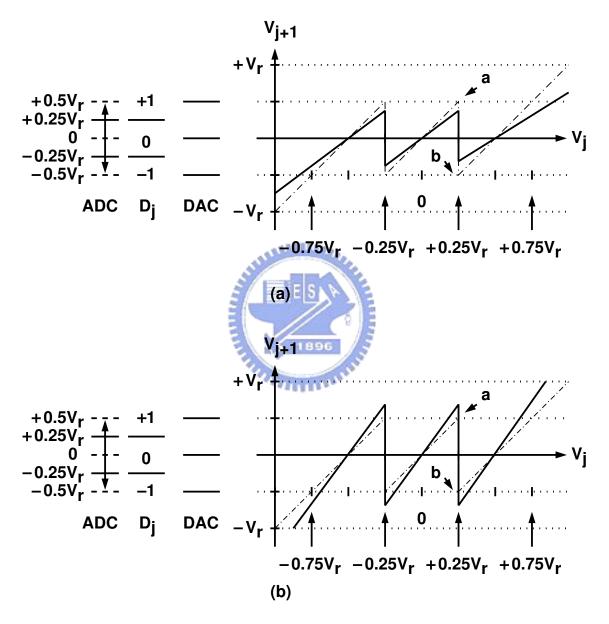

| 3.12 | Nonideal transfer function. (a) Gain $< 2$ . (b) Gain $> 2$                  | 54 |

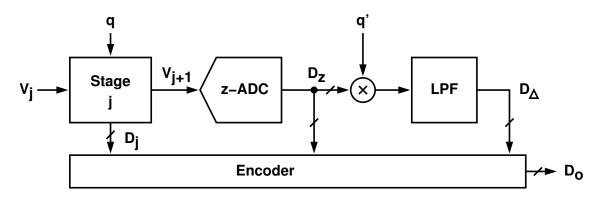

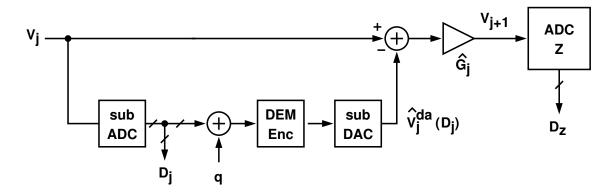

| 3.13 | A radix-2 1.5-bit SC pipeline stage for background calibration               | 55 |

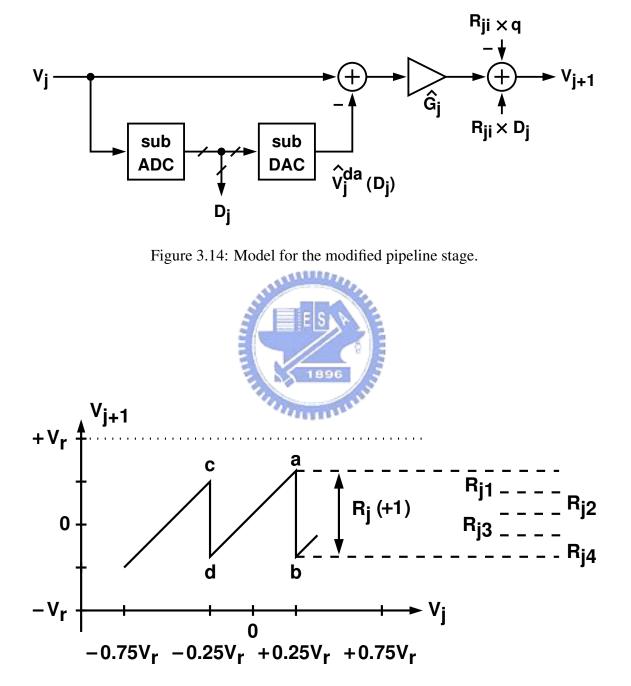

| 3.14 | Model for the modified pipeline stage                                        | 56 |

| 3.15 | The relationship between $R_{ji}$ and $R_j$                                  | 56 |

| 3.16 | Background calibration block diagram.                                        | 58 |

| 3.17 | Background calibration using reference ADC                                   | 59 |

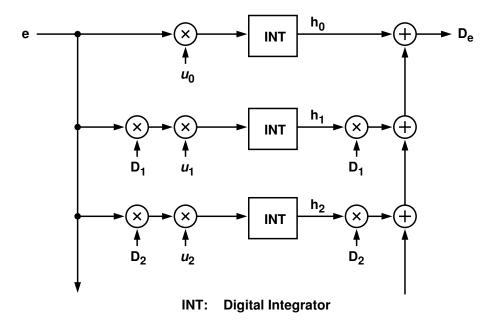

| 3.18 | Least-Mean-Square (LMS) error estimator.                                     | 61 |

| 3.19 | DNC plus GEC calibration of <i>j</i> -th stage                               | 62 |

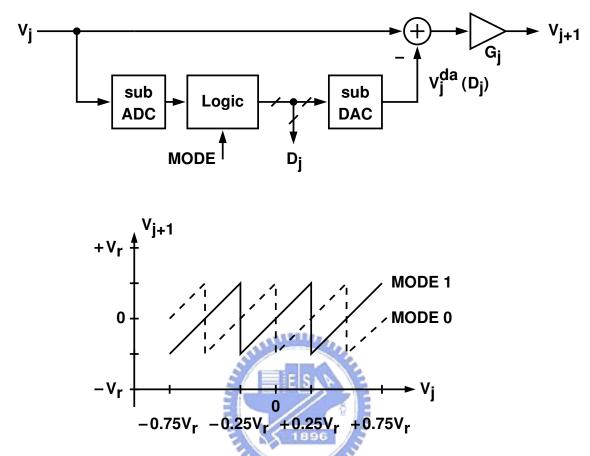

| 3.20 | Pipeline stage with two-residue transfer characteristics                     | 64 |

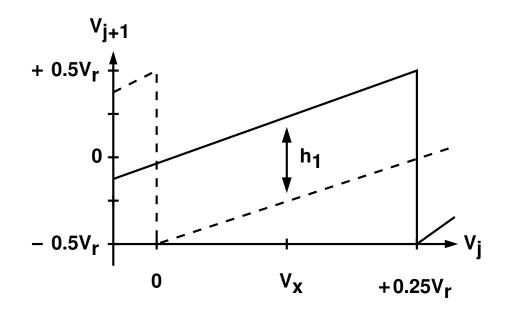

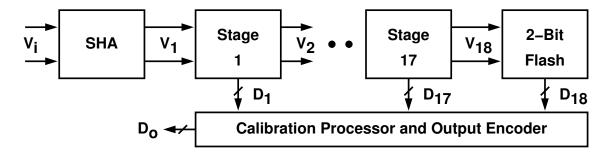

| 3.21 | Ideal residue segment detail                                                 | 65 |

| 3.22 | Distance estimate from closest cumulative count                              | 66 |

| 3.23 | Non-linear residue segment details                                           | 66 |

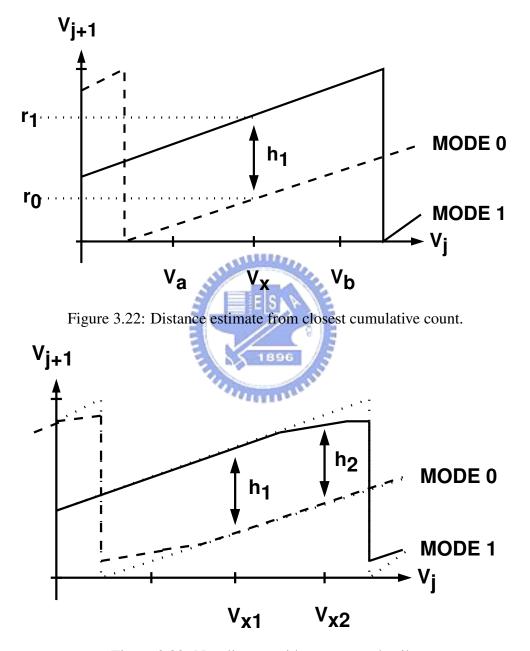

| 4.1  | Block diagram of the ADC prototype.                                          | 70 |

| 4.2  | (a) Schematic of the 1.5-bit MDAC; (b) non-overlapping clock phases          | 71 |

| 4.3  | Simplified schematic diagram of operational amplifier.                       | 76 |

| 4.4  | Simplified schematic diagram of sample-and-hold amplifier (SHA)           | 79 |

|------|---------------------------------------------------------------------------|----|

| 4.5  | Boostrapped clock generator for SHA's input sampling switches [1]         | 82 |

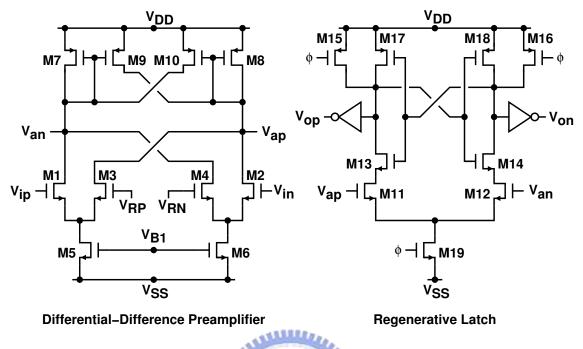

| 4.6  | Schematic diagram of preamplifier 1                                       | 84 |

| 4.7  | Schematic diagram of preamplifier 2                                       | 84 |

| 4.8  | Schematic diagram of comparator.                                          | 85 |

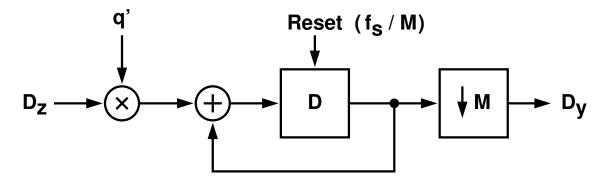

| 4.9  | Block diagram of $R_{ji}$ extractor.                                      | 87 |

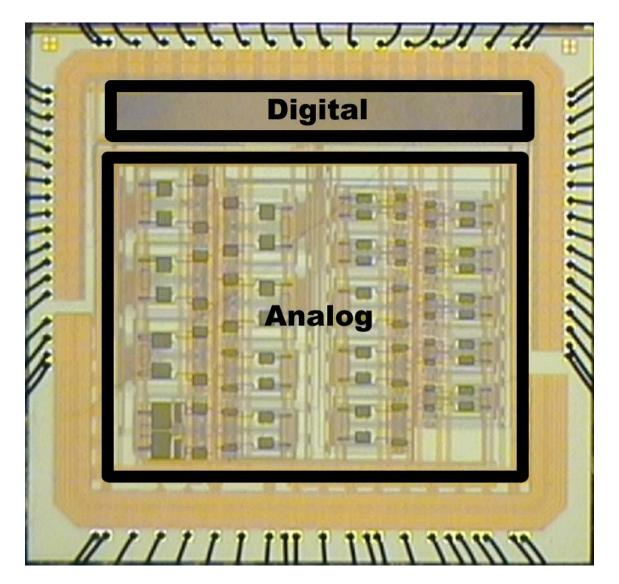

| 4.10 | ADC chip micrograph.                                                      | 89 |

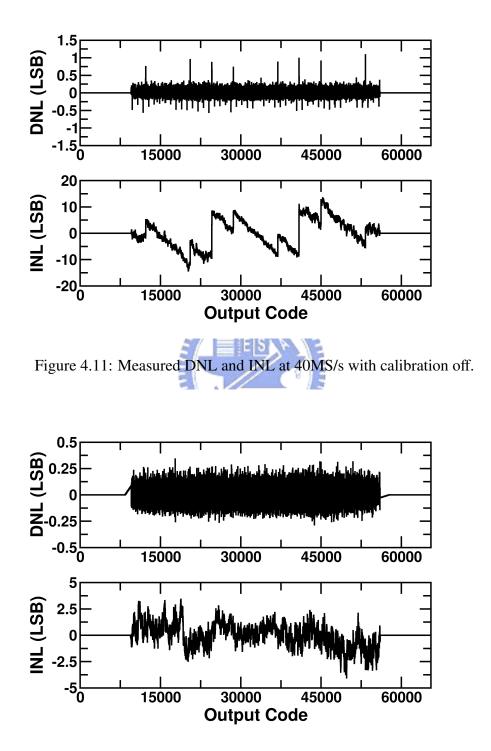

| 4.11 | Measured DNL and INL at 40MS/s with calibration off                       | 91 |

| 4.12 | Measured DNL and INL at 40MS/s with calibration on                        | 91 |

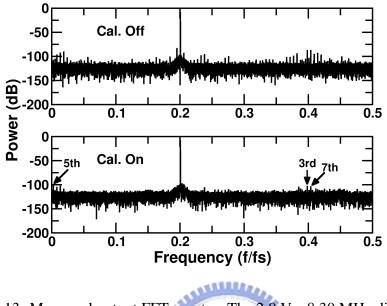

| 4.13 | Measured output FFT spectra. The 2.0 $V_{pp}$ 8.30 MHz differential sinu- |    |

|      | soidal input is sampled at 40 MS/s                                        | 92 |

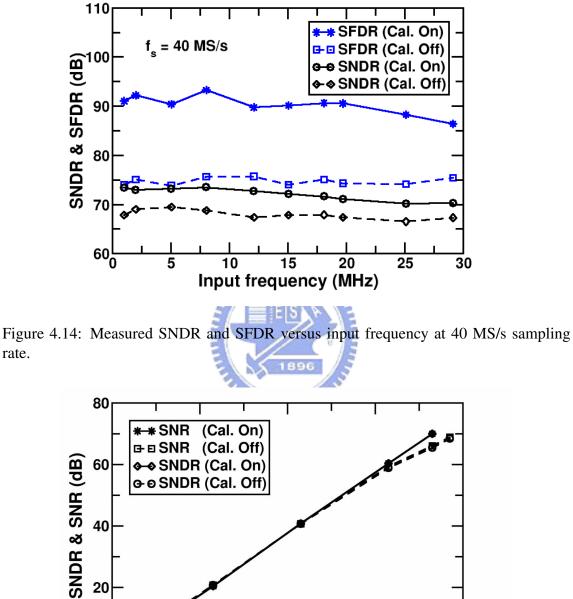

| 4.14 | Measured SNDR and SFDR versus input frequency at 40 MS/s sampling         |    |

|      | rate                                                                      | 93 |

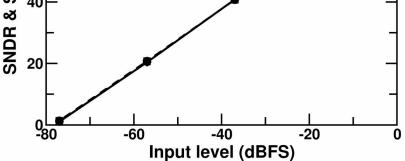

| 4.15 | Measured SNDR and SNR versus input level. The 1 MHz differential          |    |

|      | sinusoidal input is sampled at 40 MS/s                                    | 93 |

|      |                                                                           |    |

## **Chapter 1**

### Introduction

### **1.1 Motivation**

With the continuing exponential advances of integrated circuit process technology, the number of transistors per square millimeter of silicon doubles every 18 months. At the same time transistors have become more and more faster, making possible ever-increasing clock rates and the implementations of highly sophisticated architectures and algorithms in digital circuits. This trend will set to continue for at least another decade without slowing down.

and the second

However, the use of modern sub-micron CMOS transistor in analog circuits design is not too much beneficial. Two major limitations on analog components are reduced powersupply voltages and high output conductance that make the design of high linear, high dynamic range analog building blocks an increasingly challenging task. Thus, more and more analog functions are being implemented with digital signal processing techniques. Digital signal processing (DSP) has been proved over the past decade to be a robust and cost effective way of signal processing. Fig. 1.1 shows the basic topology of a DSP-based system. A programmable-gain amplifier (PGA) is usually placed in front of the ADC, adapting the loss variation of the signal transmission path in order to ease the dynamic range requirement for the ADC. Thus, PGA usually determines the overall linearity of the system. The interface between the real world analog signal and DSP function block is implemented by an analog-to-digital converter (ADC).

Figure 1.1: Block diagram of a DSP-based system.

Figure 1.2: Conventional CCD front-end scheme.

Figure 1.3: New CCD front-end scheme.

For example, in portable digital imaging equipment such as camcorders and digital still cameras, there is a strong need for low-noise, low-power, and robust CCD front-ends. Conventional front-ends shown in Fig. 1.2 usually utilize a complex analog programmable gain amplifier which realizes a gain curve linear in dB as a function of the gain code in front of a 10-bit ADC and thus most signal conditions necessary for the CCD systems were performed in the analog domain. The analog PGA consumes substantial power, adds more noise, has difficulty in realizing high gain and has an inherent non-linearity problem of gain curve. A new CCD front-end scheme shown in Fig. 1.3 utilizes all digital PGA to solves above problems associated with the analog PGA and realizes much better performance [2]. However, A high resolution of the ADC is inevitably required to compensate for the lost information associated with the digital amplification by the digital PGA. Another examples of applications are broadband communication transceivers such as Gigabit Ethernet, Cable Modems, ADSL,...etc. The feasibility of ADSL systems depends highly on the feasibility of both D/A and A/D converters of its analog frontend (AFE) since typical specifications require very high resolutions (13-16 bits) for input signal bandwidths up to 1.104 MHz.

From the discussions above, the rapid growth of DSP-based signal processing equipments prompted a need for a ADC with higher conversion rates and higher resolutions. Since quantization of continuous amplitude information requires analog operations, ADCs often limit the throughput of DSP based systems. The Pipelined architecture offers a good trade-off among power, sampling rate and chip area for Nyquist-rate ADC when compared to flash ADC, subrange ADC and successive approximation ADC. While the speed of pipelined ADCs has exceeded 100 mega-samples per second (MSPS) in CMOS technology [3] [4] [5] [6] [7], the commonly achieved resolution is still bound within the range of 8-12 effective number of bits (ENOBs) due to a variety of issues that arise. For instance, a switched-capacitor (SC) implementation is sensitive to mismatch in the capacitors that set the digital-to-analog converter (DAC) levels and interstage gain, variations in the finite gain of the operational amplifier (opamp), the accuracy of the reference voltage, and charge injection from switches. While several of these effects can be minimized by special design techniques and careful layout, but some are difficult to circumvent. Most pipelined ADCs with more than 12-bit resolution will usually require some kind of linearity enhancement techniques.

Trimming or calibration are traditionally used to overcome this problem. Trimming has the advantage of being transparent to the user, but it cannot track variations over time caused by component aging and temperature changes. Self-calibration schemes exist that can alleviate this limitation. Although the calibration can be accomplished in the analog domain [8], fully digital approaches are preferred in deep sub-micron technologies owing to the lower cost of the added digital circuitry [9] [10] [11] [12] [13] [14] [15].

While digital self-calibration has the advantage of low complexity and high accuracy, most implementations need reconfiguration of the pipeline stages, which inevitably disrupt the normal A/D operation. Thus, in applications that cannot afford idle time, the ADCs can only be calibrated in the power-on state. This power-on calibration may become insufficient for high-resolution ADCs, whose accuracy requirement for the interstage gain cannot tolerate significant variation in opamp's dc gain. Furthermore, the opamp's dc gain is hard to maintain against supply-voltage and temperature variation.

To diminish this deficiency, several background calibration schemes have been developed to enable ADCs to continuously calibrate their internal pipeline stages to track environmental changes while simultaneously performing the normal A/D conversions. The cost of background calibration is decreasing rapidly because the required digital circuits occupy less and less area in scaled technologies. In this thesis, we employ a robust background calibration scheme to correct the static A/D conversion errors [16] [17] [18]. Random analog signals are sequentially injected into the critical pipeline stages through the split capacitors for measuring the stages's transfer characteristics. All static errors due to component mismatches and finite opamp gains are corrected in the digital domain. This calibration scheme requires only slight modifications to the standard pipeline stages. No additional high-resolution ADC is needed. For the critical analog signal path, no extra capacitive loading is added, thus its operating speed is not degraded. This calibration scheme is also robust since its effectiveness does not rely on the input's amplitude distribution. The measurement results of this 15-bit 40-MS/s ADC chip fabricated in a 0.25- $\mu$ m CMOS technology demonstrate the feasibility of this calibration scheme.

### **1.2 Organization**

The organization of the thesis is as follows:

Chapter 2 gives a overview of the pipelined A/D architecture. Error sources in single pipeline stage are discussed. A generalized mathematical approach is introduced to analyze pipeline ADC. The theory of redundancy and digital correction is also addressed. Several SC implementations of pipeline stage are studied. In Chapter 3, a pipelined ADC architecture is presented and its limitations are studied. several existing calibration schemes are reviewed. The proposed background calibration scheme is introduced and shows how the static errors due to component mismatches can be overcome. Chapter 4 describes the design of the ADC prototype. The key components such as the sample-and-hold circuit, opamps, the comparator and calibration blocks are described. An experimental prototype ADC has been fabricated, and its measurement results are presented along with discussion on key performances. Finally, chapter 5 draws conclusions and makes recommendations for future work.

CHAPTER 1. INTRODUCTION

### Chapter 2

### **Principles of Pipelined ADCs**

WILLIAM DA

#### 2.1 Introduction

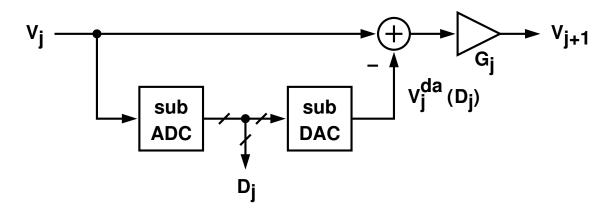

Fig. 2.1 shows the common topology of a pipelined ADC, which consists of a cascade of P stages. Each pipeline stage needs not be identical. Fig. 2.2 gives a basic configuration which comprises an sample-and-hold amplifier (SHA), a low resolution coarse ADC (sub-ADC), a DAC (sub-DAC), and a subtracter. In operation, each stage initially samples and holds the output from the previous stage and the held input is then converted into a low resolution digital code by the sub-ADC and back into an analog representation by the sub-DAC. Finally, the SHA amplifies the difference between the held analog signal and the reconstructed analog representation to give the residue for the next stag.

The primary advantage of pipelined ADCs is that they provide high throughput rates and occupy small die areas. Both advantages stem from the use of S/H technique which

Figure 2.1: A pipelined ADC.

Figure 2.2: Block diagram of a pipeline stage.

allows each of the stages to operate concurrently; that is, at any time, the first stage operates on the most recent sample while all other stages operate on residues from previous samples. If the sub-ADCs are realized with flash converters, pipelined architectures require only two main clock phases per conversion. Hence the maximum throughput rate can be quite high. In additional, since all stages operate concurrently, the number of stages used to obtain a given resolution is not constrained by the required throughput rate. The speed of a pipelined ADC is limited only by the settling of the interstage SHA.

The sections in chapter 2 are arranged as follows: Section 2.2 describes the generalized mathematical description which is applied to characterize the transfer function of multistage ADC. Section 2.3 gives the definition of minimal base-2 converter. Section 2.4 presents the error sources of the pipeline stage. Section 2.5 shows how to translate the minimal pipeline stage into the redundant stage and how the digital error correction works. Section 2.6 introduces the application of generalized mathematical description on three pipelined ADC examples with different redundant schemes. The CMOS circuit implementations of the pipeline stages are shown in Section 2.7. Finally, the summary is drawn in Section 2.8.

#### 2.2 Generalized Mathematical Description

To develop a generalized view of multistage A/D conversion, a single stage is taken into concern first. The input signal is assumed to be bipolar, while analysis in a unipolar case

could be readily derived from the bipolar result. Besides, it is always possible to view a unipolar signal as a bipolar one centered around the mid-scale reference level.

Let  $V_1$  be the bipolar input signal to the stage and  $V_r$  be the system reference level. To simplify the analysis, it is sometimes more convenient to work with a normalized input  $V_{1n}$  defined as

$$V_{1n} = \frac{V_1}{V_r}$$

(2.1)

where

$$-1 \le V_{1n} \le 1 \tag{2.2}$$

Fig. 2.2 shows a converter stage, here dubbed the *j*-th stage. The analog input  $V_j$  is compared with a number of reference levels,  $V_j^{ref}$ , using a sub-ADC, which consists of a comparator string and a voltage divider that operates off the main reference. The comparator outputs provide a rough digital representation, called  $D_j$ , of the input voltage in thermometer format. A flash section with M comparators generates M + 1 possible codes. The sub-ADC is followed by a reconstructing sub-DAC. Depending on the value of  $D_j$ , its output can be one of M + 1 possible voltages,  $V_j^{da}(D_j)$ , which is then subtracted from the input signal.

The difference signal  $(V_j - V_j^{da}(D_j))$  is then amplified by a SHA. The amplifier with a gain of  $G_j$  amplifies the difference signal to a level compatible with the input range of the following stage. The resultant signal is called the residue and noted as  $V_{j+1}$ .  $G_j$ can assume any value greater than 1, positive or negative. It is possible that there is an input-referred offset which cannot be distinguished from the variation of the  $V_j^{da}(D_j)$ 's. The S/H action allows for several stages to be cascaded in a pipelined fashion. Cascading more stages yields a higher resolution.

Refer back to Fig. 2.1 where there are P nominally identical stages, numbered from P (last, or least significant stage) to 1 (input, or most significant stage). For each stage (designated by its number, j, in subscript), the digital code  $D_j$  can be expressed as a function of the input voltage  $V_j$ . The M + 1 possible digital words for  $D_j$  are hereby

designated as integers: 0 (for 00...0), 1 (for 10...0)  $\cdots$  through M (for 11...1) [12].

$$D_{j} = \begin{cases} 0 \text{ for } V_{j} < V_{j}^{ref}[0] \\ 1 \text{ for } V_{j}^{ref}[0] \leq V_{j} < V_{j}^{ref}[1] \\ \dots \\ M \text{ for } V_{j}^{ref}[M-1] < V_{j} \end{cases}$$

(2.3)

For any given  $D_j$ , a general equation can be derived for the residue  $V_{j+1}$  as a function of  $V_j$ .

$$V_{j+1} = G_j \times \left[ V_j - V_j^{da}(D_j) \right]$$

(2.4)

Inverting (2.4) gives the input  $V_j$  as a function of output  $V_{j+1}$ :

$$V_{j} = V_{j}^{da}(D_{j}) + \frac{V_{j+1}}{G_{j}}$$

(2.5)

The expression for the input voltage of stage j can then be expanded to

$$V_{j} = V_{j}^{da}(D_{j}) + \frac{V_{j-1}^{da}(D_{j-1})}{G_{j}} + \frac{V_{j-1}}{G_{j}G_{j-1}}$$

(2.6)

Further expanding the expression and evaluating it for j = 1 gives the input voltage  $V_1$  of the pipelined converter with *P* stages as [19]:

$$V_1 = V_1^{da} + \frac{V_2^{da}}{G_1} + \frac{V_3^{da}}{G_1 G_2} + \dots + \frac{V_P^{da}}{G_1 G_2 \dots G_{P-1}} + Q$$

(2.7)

where  $Q = V_{P+1}/(G_1G_2...G_P)$  represents the quantization error of the entire A/D conversion. This general equation is based on the assumptions that the basic linear inputoutput relationship holds for each stage. In order for this to be true, there must be no over-ranging at any point in the multistage ADC system.

The ADC's digital output,  $D_o$ , is calculated from  $D_j$ , for  $j = 1, \dots, P$ , by applying (2.7) and letting  $D_o = V_1 - Q$ . Both  $V_j^{da}$  and  $G_j$ , for  $j = 1, \dots, P$ , are design parameters available to the designer. The first P terms of (2.7) are the ones of use while the last term is neglected. Representing the inherent quantization error, this last term originates from the fact that the analog residue of the last stage is not converted, unlike its siblings in previous stages. It decreases drastically as the number of converter stages (P) or the gain of the interstage amplifiers  $G_j$  increase.

The same reasoning applies to cyclic converters as well, in which the residue from a single stage is fed back to that same stage for successive conversions. Algorithmically, there is no difference between such arrangement and a pipeline one. (2.7) applies to both equally, as long as the stage subscript *j* is interpreted as the designation of a sample in time rather than a stage in a spatial arrangement.

#### 2.3 Minimal Base-2 Converter

The ADC's digital output  $D_o$  is most easily obtained from the  $D_j$  when the stages are designed for what we call "minimal" (as opposed to "redundant") operation [12]. The procedure is further simplified when the converter is based on a radix of 2, i.e., when the gain of all interstage amplifiers is exactly a power of 2. Many multi-stage converter designs are of the minimal base-2 type.

A minimal design is characterized by an integer nominal gain value  $G_j$  and reference levels  $V_j^{ref}$  chosen so as to divide the input range (assumed to be normalized between -1and 1) in as many equal parts as the absolute value of the gain,  $G_j$ . Hence, the number of comparators, M, is  $|G_j| - 1$ . The  $V_j^{ref}$  are integer multiples of a fixed voltage increment,  $\Delta V = 2/|G_j|$ , so that  $V_j^{ref}(D_j) = -1 + (D_j + 1)\Delta V = -1 + (D_j + 1)2/|G_j|$ , for  $0 \le D_j < M$ .

The number of sub-DAC levels  $V_j^{da}(D_j)$  is equal to G. the  $V_j^{da}(D_j)$ 's of each stage are also integer multiples of  $\Delta V = 2/|G_j|$ . For positive and negative G the  $V_j^{da}(D_j)$  are given by  $V_j^{da}(D_j) = -1 + (D_j + 1/2)\Delta V = -1 + (D_j + 1/2)2/|G_j|$  for  $0 \le D_j \le M = G_j - 1$ .

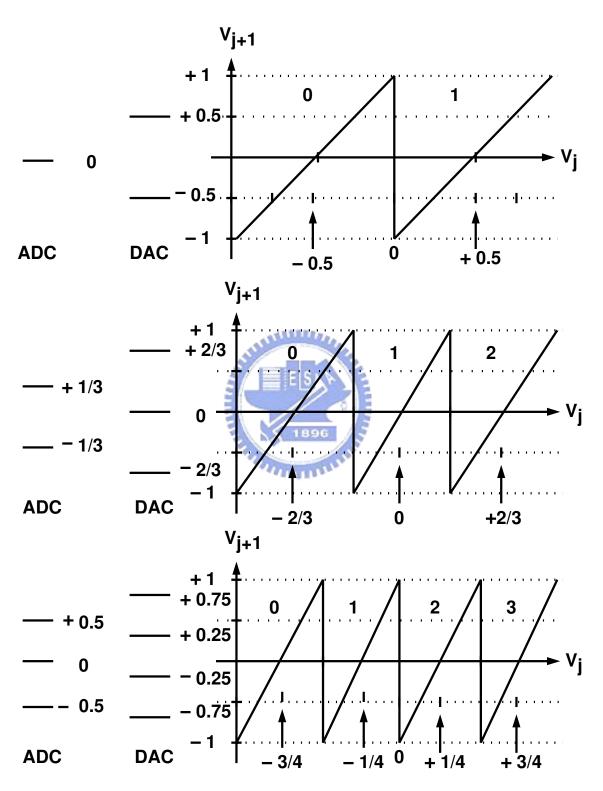

Fig. 2.3 demonstrates three minimal designs for stages with nominal gain of 2, 3 and 4, respectively. It also shows the transfer function of each stage, i.e., the relationship between  $V_j$  and  $V_{j+1}$ . Assuming ideal components, the transfer function of each stage exhibits a regular saw-tooth behavior. As long as the input signal to a stage is within the nominal input range,  $-1, \dots, 1$ , its residue is guaranteed to be within the same range. Since all stages are equal, the residue will fit the input range of the next stage. The last residue will be limited to  $-1, \dots, 1$ , and the resultant quantization error, Q, will be limited

$$0 \le Q \le \frac{2}{G_1 G_2 \dots G_P} \approx \frac{2}{|G^P|} \tag{2.8}$$

Figure 2.3: Minimal Design.

*Q* represents the inherent uncertainty on the conversion result and *G* is the nominal gain. In a classic, ideal *N*-bit converter, the corresponding quantization error range would be  $2/2^N$ , which is also defined as 1 LSB (for "least significant bit"). By extension, we are denning 1 LSB as follows:

$$1LSB = \frac{2}{|G|^p}$$

(2.9)

Similarly, the relationship between the input range and the range of the quantization error (1 LSB) can be expressed as the effective number of bits,  $N_{eff}$ .

$$N_{eff} = \log_2(\frac{2}{1\text{LSB}}) = P\log_2(|G|)$$

(2.10)

The effective number of bits per stage,  $n_{eff}$  is given by:

$$n_{eff} = \log_2(|G|) \tag{2.11}$$

For a minimal base-2 converter,  $G = 2^n$ . (Note that  $n_{eff} = n$ .) It is easy to derive the binary conversion result – simply convert the  $D_j$  of successive stages from *M*-bit thermometer code to *n*-bit straight binary, and combine the *P* individual *n*-bit words into an *N*-bit (with N = nP) conversion result through concatenation. Furthermore,  $0 \le Q \le$  $2/2^{nP} = 2/2^N = 1$  LSB. This expression is consistent with the conventional definition of an *N*-bit converter

#### 2.4 Error Sources in a Pipelined Stage

The performance of a pipelined ADC is limited by the nonlinearity of the sub-ADC and sub-DAC, as well as the gain error of the interstage SHA. The nonlinearity in the sub-ADC is due to comparator offsets and reference voltage errors. Both errors lead to a decision-level shift of the sub-ADC. The non-ideal effects in the sub-DAC include offset, gain error, and nonlinearity. Gain error in the interstage SHA stems from by a variety of sources. In a pipeline using switched capacitor gain stages, these error sources could include capacitor mismatches and finite opamp gains. In this section, we will discuss these sources and derive interpretations for them [20] [21].

The flash ADC in each pipelined stage compares the stage input to a set of reference voltages and output the resultant digital code. Unless otherwise stated, it is assumed

Figure 2.4: Transfer curve of a pipelined stage with threshold offsets.

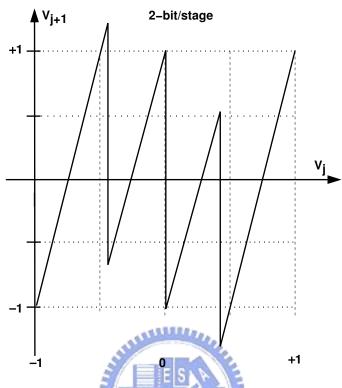

that the sub-DAC and gain block in the stage are ideal. The comparator tries to find out the difference of between the two input signals whilst an internal offset voltage factors into this difference. Thus when the two inputs are close to each other, the comparator may make a wrong decision and a wrong reference is subtracted from the input. The aforementioned internal offsets are due to comparator offsets and reference voltage errors. Both errors result in a decision level shift(or threshold offset) of the sub-ADC. For the 2bit/stage case, the effect of this decision-level shift on the residue transfer is shown in Fig. 2.4. As can be seen, the residue voltage can be larger than the input range of the following stage, resulting in the saturation of the next stage. As a result, missing decision level occurs.

After the input is digitized by the sub-ADC, a sub-DAC converts the derived code back to an analog signal. It can be shown that the offset of the sub-DAC gives rise only to a constant equivalent input offset of the ADC. On the other hand, the gain error and the nonlinearity in the sub-DAC limit the resolution of the whole ADC. The sub-DAC gain error has the same effect on performance as the interstage SHA gain error. The nonlin-

Figure 2.6: non-ideal-DAC effect on the whole ADC characteristic.

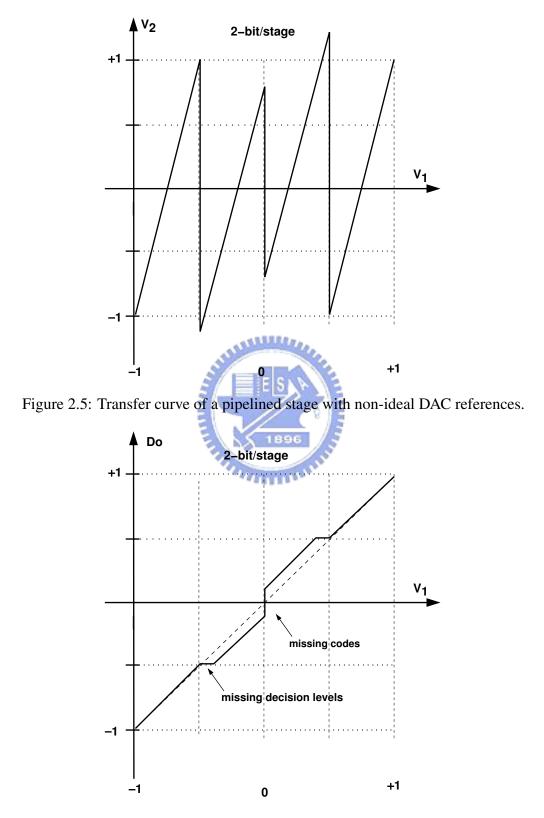

earity of the sub-DAC is the most important error source in a pipelined ADC. Fig. 2.5 gives the transfer curve of a pipelined stage with non-ideal DAC while Fig. 2.6 shows its effect on the overall ADC characteristic (Assume only the first stage is nonideal, the remaining stages are ideal). As can be seen, the sub-DAC nonlinearity results in both missing code and missing decision levels (i.e. saturation of the next stages). The primary source of the non-ideal sub-DAC reference levels in switched-capacitor implementation is capacitor mismatch.

The difference between the input analog signal and the sub-DAC analog output is then amplified by SHA. The transfer curve of a pipelined stage with interstage gain error is shown in Fig. 2.7. Fig. 2.8 demonstrates its effect on the overall ADC characteristic. As can be seen, too small of an interstage gain results in missing codes of the entire ADC, while too large of an interstage gain leads to missing decision levels. If there are mismatches in stage gains in the pipeline, the overall transfer curve will be a zigzag curve instead of a straight line as in the ideal case.

In a CMOS technology, SC circuit techniques are commonly used to implement a pipelined ADC. In this case, the non-ideal effects in the interstage amplifier are determined by the capacitor mismatches, finite opamp gain and gain-bandwidth product (GBW).

Manna Manna

### 2.5 Digital Error Correction with Redundancy

It is not difficult to see from the discussion in last section that a multistage ADC with the minimal configuration is highly sensitive to errors in the threshold offsets, the sub-DAC errors and the interstage gain errors. Nevertheless, a digital error correcting scheme based on (2.7), which will be discussed in Chapter 3, can be employed to compensate for the sub-DAC and gain errors. As long as each term on the right hand side of (2.7), except Q, is derived from the actual values of converter components rather than nominal values, an almost exact approximation to the input voltage can be achieved. Note that the errors do not stem directly from incorrect reference levels. This is actually quite self-evident since  $V_j^{ref}$ 's do not appear in (2.7). Errors in reference levels weigh on the system indirectly in that the residue of one stage exceeds the input range of the next stage, causing missing decision levels.

Figure 2.8: interstage-gain-error effect on the whole ADC characteristic.

Figure 2.9: Redundant stages.

Assuming ideal interstage amplifiers (i.e. linear over a wide range of input signals), (2.7) remains valid even when the comparator makes a wrong decision. But when a residue exceeds the input range of the subsequent stage, this causes the next residue to be even further out of range. Finally, the last residue value becomes so large that (2.8) no longer holds. The quantization error becomes significant. In addition, some of the amplifiers may clip, which makes things even worse.

The problem can be solved by increasing the input range of each stage beyond the nominal output range of the previous stage. This guarantees that the residues remain limited and the overall quantization error is less than 1 LSB. The input range can be increased using a design where  $M > |G_j| - 1$ . This is done by either increasing the comparator number or decreasing the interstage gain with respect to the minimal design.

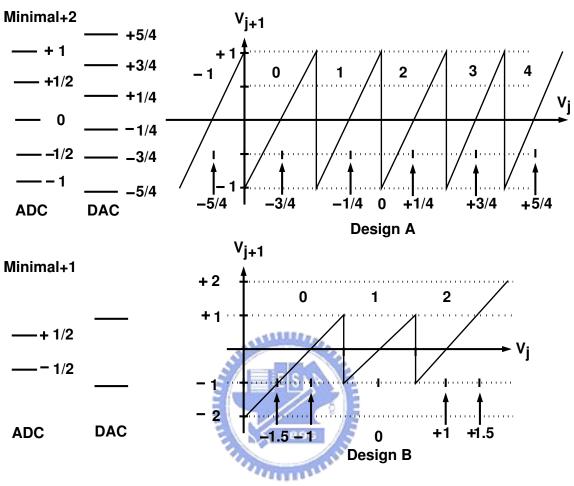

The former approach is often preferred because the nominal gain can remain integer – even a power of 2. Two possible designs of redundant stage with nominal gain of 4 and 2 are shown in Fig. 2.9, as well as their transfer curves.

Design A uses two extra (redundant) comparators compared with the minimal case, at the top and bottom of the range.  $V_j^{ref}(D_j) = -1 + (D_j + 1)\Delta V = -1 + (D_j + 1)2/|G_j|$ , for  $-1 \le D_j < M + 1$  and  $V_j^{da}(D_j) = -1 + (D_j + 1/2)\Delta V = -1 + (D_j + 1/2)2/|G_j|$ for  $-1 \le D_j \le M + 1$ , where *M* equals 3. One can verify that this provides an overrange capability of  $\pm 2/|G_j|$ . We will call this arrangement *minimal* + 2 [12].

Design B uses one redundant comparator compared with the minimal case and offsets both the  $V_j^{ref}(D_j)$  and the  $V_j^{da}(D_j)$  by minus a half  $\Delta V$ .  $V_j^{ref}(D_j) = -1 + (D_j + 1/2)\Delta V =$  $-1 + (D_j + 1/2)2/|G_j|$ , for  $0 \le D_j < M + 1$  and  $V_j^{da}(D_j) = -1 + D_j\Delta V = -1 + 2D_j/|G_j|$ for  $0 \le D_j \le M + 1$ , where M equals 1. This arrangement has been described as implementing a "Redundant Signed Digit" (RSD) algorithm or the 1.5b/stage algorithm [22] [23]. We hereby call it "minimal + 1." One can verify that this provides an overrange capability of  $\pm 2/(2|G_j|)$ .

Either of the two redundant schemes mandate modifications in the derivation of the conversion result of (2.7) from  $D_j$  and  $V_j^{da}(D_j)$  for the base-2 converters, resulting in slightly more complex logic circuitries [24] [25]. However, the gain in robustness can be spectacular.

As a summary, to build pipelined ADCs with large tolerance to component nonidealities, one can employs redundancy technique that provides an overrange capability to permits large decision level shift and prevents threshold offsets from limiting the resolution of the converter. In this section, the method for the minimal base-2 converter to be translated into some specific types of redundant schemes is revealed, once the relationship between  $D_j$  and  $V_j^{da}(D_j)$  is derived, the conversion result can be found by substituting it into (2.7). In this technique, the sum of the individual stage resolutions is greater than the total resolution. The redundancy is then removed by a digital-correction algorithm, eliminating altogether the effects of sub-ADC nonlinearity and interstage offset on the overall linearity. In many previous implementations, the digital-correction algorithms have applied addition and subtraction to correct errors.

## 2.6 Pipelined ADC Examples

In this section, three examples of multistage ADC are examined. In each case the ADC operation is presented with the aid of the generalized mathematical description developed in Section 2.2. The examples contain detailed description of static input-output characteristics and digital code assignments. The treatment in this section is at the system/algorithm level. The objective here is to review multistage ADC architecture with different algorithmic features such as digital correction/redundancy and code assignment scheme.

Before processing, first a review of binary representation of real numbers is presented. A real number *r* lying between 0 and 1 (i.e. a unipolar number) with binary representation  $B = b_1 b_2 b_3 \cdots b_P$ , where the bits  $b_i$  have value either 0 or 1, can be written as

$$r = \frac{b_1}{2^1} + \frac{b_2}{2^2} + \frac{b_3}{2^3} + \dots + \frac{b_N}{2^N} = \sum_{i=1}^N \frac{b_i}{2^i}$$

(2.12)

In some sense, the terms in the above summations can be regarded as binary fractions. For this purpose of this work, the following representation of a bipolar number r lying between -1 and +1 is used:

$$r = -1 + 2\sum_{i=1}^{N} \frac{b_i}{2^i}$$

(2.13)

This is similar to the unipolar number representation referenced to -1 with a total range of value 2.

### 2.6.1 Example 1

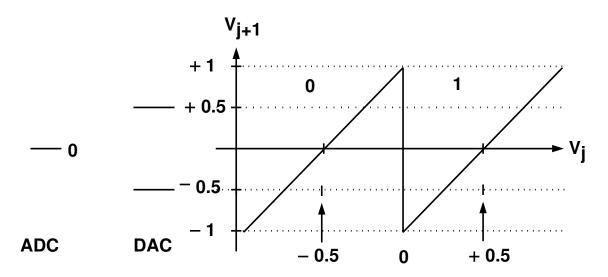

This example illustrates a pipelined ADC with 1 bit stage which has one extra redundancy comparator. This scheme has been described earlier in previous section. We have called it "minimal+1". The scheme also has been employed in a high-speed CMOS pipeline implementation [22]. In this example, the stage has a gain of two but has two threshold levels. The transfer characteristic is shown in Fig. 2.9. The terminology "1.5 bits per stage" is sometimes used to describe this stage [22] [26]. Note that the overall converter resolution is P + 1 bits with P stages. The static parameters are listed in Table 2.1.

| Input range              | $[-1, +1]$ (normalized to $V_r$ )        |

|--------------------------|------------------------------------------|

| sub-ADC threshold levels | $\{-1/4, 1/4\}$                          |

| 3 digital codes          | $\{0, 1, 2\}$ or $\{00, 01, 10\}$        |

| 3 sub - DAC levels       | $\{-1/2, 0, 1/2\}$                       |

| Interstage gain          | G = 2                                    |

| Number of bits           | n = 2(net, after digital correction:n=1) |

Table 2.1: Static parameters of the 1.5bit/stage.

The single pipelined stage input-output relation is

$$V_{j+1} = 2 \times \left[ V_j - V_j^{da}(D_j) \right]$$

(2.14)

From (2.7), the expression for the quantized analog output can be expressed as:

$$V_{1n} = V_1^{da} + \frac{V_2^{da}}{2} + \frac{V_3^{da}}{2^2} + \dots + \frac{V_P^{da}}{2^{P-1}} = \sum_{j=1}^P \frac{V_j^{da}(D_j)}{2^{j-1}}$$

(2.15)

Next, the relation between the digital codes and the corresponding sub-DAC levels is

$$V_j^{\rm da}(D_j) = \frac{-1}{2} + \frac{D_j}{2}$$

(2.16)

where  $D_j = 0, 1, 2$ . Substituting this expression into (2.15) gives

$$V_{1n} = \sum_{j=1}^{p} \frac{-\frac{1}{2} + \frac{D_j}{2}}{2^{j-1}} = -1 + \frac{1}{2^{p}} + \sum_{j=1}^{p} \frac{D_j}{2^j}$$

(2.17)

Thus, the  $1/2^{P}$  term in (2.17) is simply a shift of 1/2 LSB. The  $D_{j}$  in (2.17) may be considered 2-bit numbers. Therefore, the summation in (2.17) corresponds to *addition* with one bit overlapped between adjacent stages [19].

### 2.6.2 Example 2

This example illustrates a pipelined ADC with 1-bit stage but the first stage has three redundancy comparators. In this example, the first stage has a gain of two but has four threshold levels. We call it "minimal+3", and the remaining stages are 1.5-bit-per-stage. The transfer characteristic is shown in Fig. 2.10.

Figure 2.10: Transfer function of 1.5-bit per stage with dynamic range doubling.

| Table 2.2. Static parameters of the DKD stage. |                                                   |  |

|------------------------------------------------|---------------------------------------------------|--|

|                                                |                                                   |  |

| Input range                                    | [-1, +1](normalized to $V_r$ )                    |  |

| 4 sub - ADC threshold levels                   | {-3/4, -1/4, 1/4, 3/4}                            |  |

| 5 digital codes                                | $\{-1, 0, 1, 2, 3\}$ or $\{-01, 00, 01, 10, 11\}$ |  |

| 5 sub - DAC levels                             | {-1, -1/2, 0, 1/2, 1}                             |  |

| interstage gain                                | G = 2                                             |  |

| Number of bits                                 | n = 2(net, after digital correction: n = 1)       |  |

Table 2.2: Static parameters of the DRD stage.

This scheme has been employed in an 80 MHz 10b pipeline ADC [27], while a similar technique with 3-bit MDAC in the first stage of a pipeline ADC has been presented [28]. The two additional comparators determine whether the input signal is smaller than -3/4 or larger than 3/4, and in these two range the stage implements the algorithm  $(2V_j + 2)$  or  $(2V_j - 2)$ , respectively. It can be seen in Fig. 2.10 that the amplifier output swing is now halved with respect to the previous implementation (i.e. 1.5-bit stage), a property that propagates to all the following stages, still of the conventional 1.5-bit type. The authors call this method as Dynamic-Range-Doubling (DRD) algorithm. The static parameters of the DRD stage are listed in Table 2.2.

Here, as in Algorithm Example 1, the individual stage input-output relation for DRD

| -01   |

|-------|

| 01    |

| 01    |

| -0001 |

Figure 2.11: Conversion result of the DRD example.

is

$$V_{j+1} = 2 \times \left[ V_j - V_j^{da}(D_j) \right]$$

(2.18)

As can be seen, for the first stage the relation between the digital codes and the corresponding sub-DAC levels is the same as (2.16).

$$V_j^{\rm da}(D_j) = \frac{-1}{2} + \frac{D_j}{2}$$

(2.19)

where  $D_j = -1, 0, 1, 2, 3$ . Substituting this expression into (2.18) gives the expression for the amplitude-quantized analog output as that in (2.17),

$$V_{1n} = -1 + \frac{1}{2^p} + \sum_{j=1}^p \frac{D_j}{2^j}$$

(2.20)

The  $1/2^{P}$  term in (2.17) is simply a shift of 1/2 LSB, and the summation in (2.20) employs an overlapped addition to generate the final code. The presence of a negative number (-1) complicates thing a little somewhat. What it actually means that the range is extend slightly since a code more negative than all 0's is now possible.

To see how this works out, consider a pipeline ADC consisting a cascade of one DRD stage and two 1.5-bit stages. Let the input be  $V_{1n} = -1 + \varepsilon$ , where  $\varepsilon$  is a positive voltage of magnitude much smaller than 1 LSB at the overall ADC resolution. The outputs from the three stages are as follows:  $D_1 = -1 = -01$ ,  $D_2 = 0 = 01$ ,  $D_3 = 0 = 01$  The final output is then obtained from an overlapped addition as given in Fig. 2.11. It can be seen that the output code is -1. This could be used as an indication of the underrange signal.

### 2.6.3 Example 3

This example illustrates a pipelined ADC with overrange capability. Fig. 2.12 shows the transfer characteristic of a 1-bit stage. In this case the interstage gain is two and there is

Figure 2.12: Transfer characteristic for the 1-bit converter.

only one transition boundary in the transfer characteristic. Due to the lack of redundancy, if the analog residue in one stage is outside the -1 to +1 range, this analog residue is amplified by two at each subsequent stage and eventually reaches the limiting region of the output voltage at a later stage. This scenario determines the missing decision levels in the overall transfer characteristic. This can usually be avoided by using a "radix< 2" conversion stage for the ADC [10] [13]. The drawback with such an approach is that a gain< 2 per stage is obtained by using extra capacitors and switches that eventually become a significant part of the stage loading, which becomes especially troublesome at high conversion speeds.

A better solution is to use overrange stages with an analog input range larger than one from -1 to +1, such that any residue input outside the -1 to +1 region will be converted back to the nominal -1 to +1 range [14] [29].

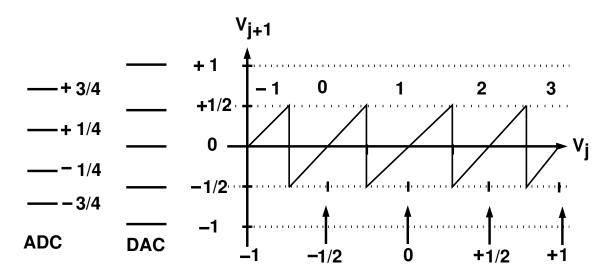

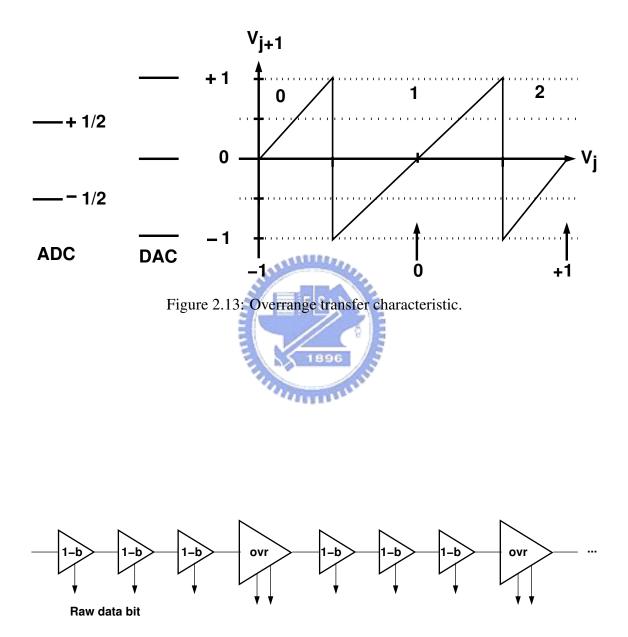

Fig. 2.13 shows the transfer characteristic of one overrange stage. This scheme has been presented in an single-ended 20 MHz 12-bit pipeline ADC [14]. Such an overrange stage has a nominal gain of two, equivalent to resolving one bit of resolution, but at the same time it can correct residues up to 1/2 outside the nominal -1 to +1 range for the input voltage.

Consider a pipeline ADC consisting of a cascade of P stages. An overrange stage is inserted every three 1-bit stages, as shown in Fig. 2.14. Whether it's one overrange

Figure 2.14: Architecture of the ADC including overrange stages.

| Input range                | $[-1, + 1]$ (normalized to $V_r$ ) |

|----------------------------|------------------------------------|

| 1 sub-ADC threshold levels | {0}                                |

| 2 digital codes            | $\{0, 1\}$                         |

| 2 sub - DAC levels         | {-1/2, 1/2}                        |

| interstage gain            | G = 2                              |

| Number of bits             | n = 1                              |

Table 2.3: Static parameters of the 1-bit/stage.

stage per three 1-bit stages or any number of 1-bit stages depends on the magnitude of the worst-case errors that might occur in the analog path.

| and the second sec |                                             |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|--|

| Input range 🔬                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $[-1, + 1]$ (normalized to $V_r$ )          |  |

| 2 sub - ADC threshold levels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ES \{-1/2, 1/2}                             |  |

| 3 digital codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $\{0, 1, 2\}$ or $\{00, 01, 10\}$           |  |

| 3 sub - DAC levels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | {-1, 0, 1}                                  |  |

| interstage gain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | G = 2                                       |  |

| Number of bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | n = 2(net, after digital correction: n = 1) |  |

| TITLE .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                             |  |

Table 2.4: Static parameters of the overrange stage.

The static parameters of the 1-bit per stage and the overrange stage are respectively listed in Table 2.3 and Table 2.4. The input-output relationship of individual stages for the 1-bit stage and overrange stage is given by

$$V_{j+1} = 2 \times \left[ V_j - V_j^{da}(D_j) \right]$$

(2.21)

As in the Algorithm Example 1, writing the expression for the amplitude-quantized analog output voltage gives

$$V_{1n} = V_1^{da} + \frac{V_2^{da}}{2} + \frac{V_3^{da}}{2^2} + \dots + \frac{V_P^{da}}{2^{P-1}} = \sum_{j=1}^{P} \frac{V_j^{da}(D_j)}{2^{j-1}}$$

(2.22)

Again, a relation between the digital codes and the corresponding DAC levels is in need. By looking at the codes  $D_j$  and the corresponding DAC levels  $V_j^{da}(D_j)$ , it is clear that the relation between them is given by, for the 1-bit per stage

$$V_j^{\rm da}(D_j) = \frac{-1}{2} + D_j \tag{2.23}$$

where  $D_j=0, 1$ , and for the overrange stage

$$V_j^{\rm da}(D_j) = -1 + D_j \tag{2.24}$$

where  $D_i = 0, 1, 2$ .

Substituting this expression into (2.21) gives

$$V_{1n} = \left(-\frac{1}{2} + D_{1}\right) + \frac{1}{2}\left(-\frac{1}{2} + D_{2}\right) + \frac{1}{4}\left(-\frac{1}{2} + D_{3}\right) + \frac{1}{8}\left(-1 + D_{4}\right) + \frac{1}{16}\left(-\frac{1}{2} + D_{5}\right) + \cdots$$

$$= \sum_{j=1}^{p} \frac{-\frac{1}{2}}{2^{j-1}} + \sum_{j=1}^{\left\lfloor\frac{p}{4}\right\rfloor} \frac{-1}{2^{4j}} + \sum_{j=1}^{p} \frac{D_{j}}{2^{j-1}}$$

$$= -1 + \left(\frac{1}{2^{p}} - \frac{1}{15}\left(1 - \left(\frac{1}{2^{4}}\right)^{\left\lfloor\frac{p}{4}\right\rfloor}\right)\right) + 2\sum_{j=1}^{p} \frac{D_{j}}{2^{j}}$$

$$= bipolar \ code + coding \ of \ f \ set + raw \ out \ put$$

$$(2.25)$$

The -1 on the right-hand side of (2.25) is expected, since this is a bipolar system. The next three terms in the bracket on the right-hand side constitute the coding offset. While smarter coding schemes may exist, the only difference is the expression of coding offset. Because the coding offset is a constant value depending on the number of pipeline stages (*P*), the actual conversion results can be easily obtained by adding the raw output and the coding offset.

The advantage of the generalized mathematic description presented in Section 2 is now evident: for a given stage transfer characteristic and given dc parameters, it provides a systematic way to work out a precise approach to combine the stage output codes  $D_j$  in order to generate the correct amplitude-quantized ADC output. Furthermore, it facilitates thorough study of the use of different static parameters, e.g., shifted sub-ADC thresholds or sub-DAC levels, or different code assignment schemes. It also allows examination of how such possible alternative schemes weigh on the complexity of the precise way that the outputs codes are combined to produce the final ADC output.

# 2.7 CMOS Circuit Implementation

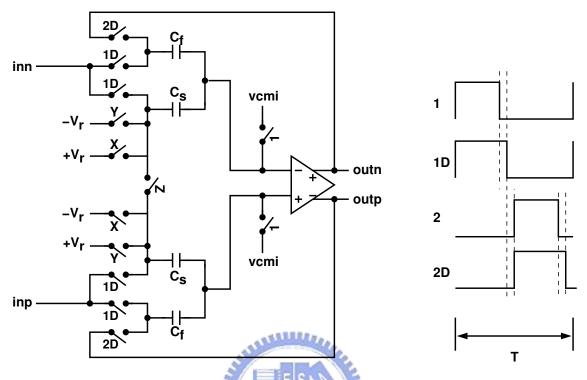

In CMOS technologies, a pipeline stage for A/D conversion generally consists of a set of voltage-mode comparators and a switched-capacitor (SC) multiplying digital-to-analog converter (MDAC). The MDAC combines the functions of a sample-and-hold, a digital-to-analog converter, a subtracter and a voltage-mode amplifier [30] [9].An SC MDAC employs an opamp with a capacitor feedback network to provide linear voltage amplification.

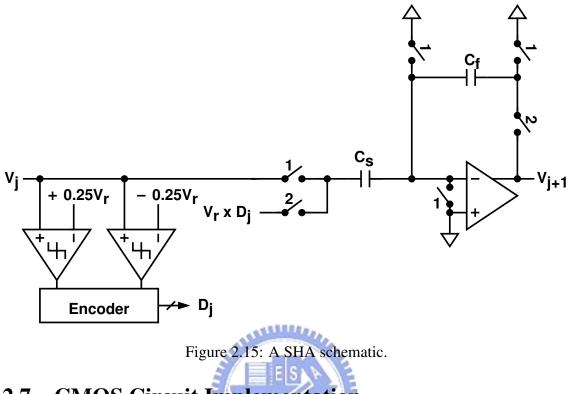

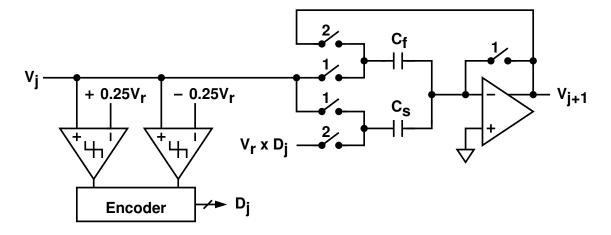

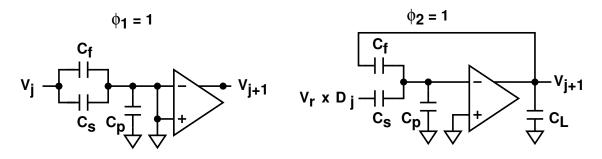

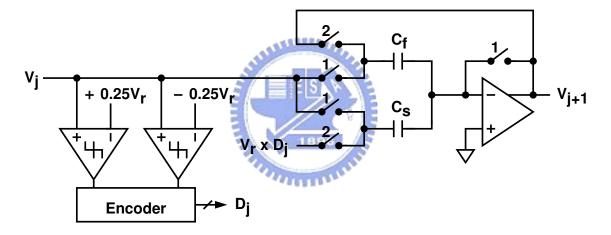

Fig. 2.15 gives the schematic of a conventional sample-and-hold amplifier (SHA) applied to a radix-2 1.5-bit switched-capacitor pipeline stage. The  $\phi_1$  and  $\phi_2$  are standard non-overlapping clocks. Each switch is closed when its controlling clock signal is high and open otherwise. Assume that the opamp is ideal except being with a limited gain  $A_0$ . The sub-ADC is made of two comparators with thresholds at  $+0.25V_r$  and  $-0.25V_r$ , respectively. When clock  $\phi_1$  is high,  $V_j$  is sampled onto the capacitor  $C_s$ , the capacitor  $C_f$  is reset to ground. The digital code,  $D_j \in \{-1, 0, +1\}$ , is obtained by comparing  $V_j$  with  $+0.25V_r$  and  $-0.25V_r$ . When clock  $\phi_2$  is high,  $C_f$  is connected to the opamp output, and  $C_s$  is connected to one of the three possible voltage  $\{-V_r/2, 0, +V_r/2\}$  depending on the

Figure 2.16: A general model of a SC pipeline stage.

outcome of the comparator. The output  $V_{j+1}$  can be written as:

$$V_{j+1} = \hat{G}_j \times \left[ V_j - \hat{V}_j^{da}(D_j) - V_j^{os} \right]$$

(2.26)

with

$$\hat{G}_{j} = \frac{C_{s}}{C_{f}} \times \frac{1}{1 + \frac{1}{A_{0}} \cdot \frac{C_{s} + C_{f} + C_{p}}{C_{f}}}$$

(2.27)

and

$$\hat{V}_j^{\rm da}(D_j) = \frac{V_r}{2} \times D_j \tag{2.28}$$

where  $C_p$  denotes the parasitic capacitance associated with the opamp's negative input. The realized *j*-th stage gain factor,  $\hat{G}_j$ , is a function of capacitor ratios, and the opamp's dc gain,  $A_0$ . The  $V_j^{os}$  term accounts for the offset effect of the *j*-th stage, including opamp's input-referred offset voltage and charge injection from analog switches. If the opamp gain  $A_0$  is infinite and the capacitor matching is perfect with  $C_s = 2C_f$ , the close loop gain  $G_j$  is exactly two.

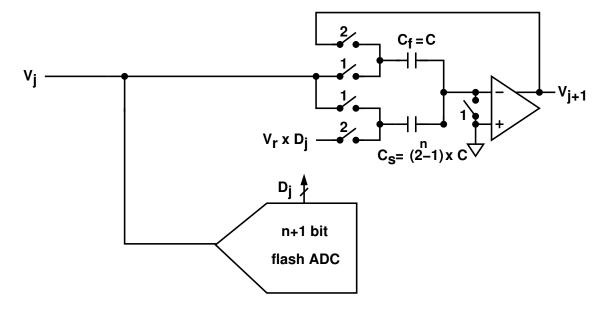

A variation on the scheme mentioned above is to use the same physical capacitor for both acquisition and residue amplification, namely, with the two actions sharing the feedback capacitor  $C_f$ . Fig. 2.16 illustrates the particular configuration of interest here.

Figure 2.17: A radix-2 1.5-bit switched-capacitor (SC) pipeline stage.

Figure 2.18: The conversion characteristic of the radix-2 1.5-bit SC pipeline stage.

It has a resolution of n + 1 bits per stage, and an interstage gain of  $2^n$  [26]. The sub-DAC function is performed by a set of capacitors with a reference voltage source  $V_r$ . When the input signal is applied, each stage samples and quantizes the signal to its perstage resolution of n + 1 bits, subtracts the quantized analog voltage from the signal by connecting the bottom plate of capacitors  $C_S(=(2^n-1)\times C)$  to  $V_r$ , and passes the amplified residue to the next stage for finer conversion. The sub-ADC section is composed of  $(2^{n+1}-$ 2) comparators. The digital correction can tolerate the offset voltage of each comparator up to  $\pm V_r/2^{n+1}$ . The net resolution per stage after digital correction and redundancy removal is *n* bits.

Figure 2.19: The operations of the radix-2 1.5-bit SC pipeline stage.

For n = 1, Fig. 2.17 reduced to a radix-2 1.5-bit switched-capacitor pipeline stage with shared feedback capacitor. The corresponding conversion characteristic is shown in Fig. 2.18. The sub-ADC is composed of two comparators with thresholds at  $+0.25V_r$  and  $-0.25V_r$ , respectively. The opamp and the two capacitors,  $C_f$  and  $C_s$ , form a multiplying digital-to-analog converter, which performs the functions of sample-and-hold, digital-toanalog conversion, subtraction and voltage amplification. As shown in Fig. 2.19, when clock  $\phi_1$  is high,  $V_j$  is sampled onto capacitor  $C_f$  and  $C_s$ . The digital code,  $D_j \in$  $\{-1, 0, +1\}$ , is obtained by comparing  $V_j$  with  $+0.25V_r$  and  $-0.25V_r$ . When clock  $\phi_2$ is high,  $C_f$  is connected to the opamp output, and  $C_s$  is connected to one of the three possible voltage  $\{-V_r, 0, +V_r\}$  depending on the outcomes of the comparators. Chargeconservation analysis shows that the  $\hat{G}_j$  is

$$\hat{G}_{j} = \frac{C_{s} + C_{f}}{C_{f}} \times \frac{1}{1 + \frac{1}{A_{0}} \cdot \frac{C_{s} + C_{f} + C_{p}}{C_{f}}}$$

(2.29)

and

$$\hat{V}_j^{\rm da}(D_j) = V_r \cdot \frac{C_s}{C_s + C_f} \times D_j \tag{2.30}$$

Let  $A_0 = \infty$  and  $C_s = C_f$ , an ideal transfer characteristic is obtained with  $G_j = 2$  and  $V_i^{da}(D_j) = 0.5V_r \times D_j$ .

By sharing the feedback capacitor  $C_f$ , a key advantage of this configuration is the improved feedback factor obtained when compared with the SHA mentioned above. Detailed discussion regarding this will be presented in later Chapter.

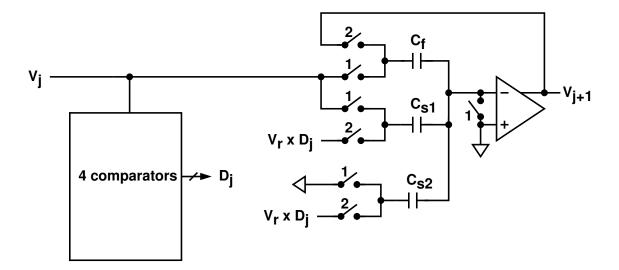

Fig. 2.20 shows a schematic of the DRD implementation mentioned in the algorithm example 2 of Section 2.6. The sub-ADC is composed of four comparators with thresholds at  $-0.75V_r$ ,  $-0.25V_r$ ,  $0.25V_r$  and  $+0.75V_r$  respectively. When clock  $\phi_1$  is high,  $V_j$  is

Figure 2.20: A 1.5bit stage with dynamic range doubling.

sampled onto capacitor  $C_f$  and  $C_{s1}$ . The  $C_{s2}$  is on the reset state. The digital code,  $D_j \in \{-2, -1, 0, +1, +2\}$ , is obtained by comparing  $V_j$  with  $-0.75V_r$ ,  $-0.25V_r$ ,  $0.25V_r$ and  $+0.75V_r$ . When clock  $\phi_2$  is high,  $C_f$  is connected to the opamp output, and  $C_{s1}$  and  $C_{s2}$  are connected to one of the three possible voltage  $\{-V_r, 0, +V_r\}$  depending on the outcomes of the comparators. Again, the output  $V_{j+1}$  is the same as (2.26) but the  $\hat{G}_j$  is

$$\hat{G}_{j} = \frac{C_{s1} + C_{f}}{C_{f}} \times \frac{1}{1 + \frac{1}{A_{0}} \cdot \frac{C_{s1} + C_{s2} + C_{f} + C_{p}}{C_{f}}}$$

(2.31)

and

$$\hat{V}_{j}^{da}(D_{j}) = \frac{V_{r}}{2} \cdot \frac{C_{s1} + C_{s2}}{C_{s1} + C_{f}} \times D_{j}$$

(2.32)

If the opamp gain  $A_0$  is infinite and the capacitor matching is perfect with  $C_{s1} = C_f$ , the close loop gain  $G_j$  is exactly two.

## 2.8 Summary

In this chapter, the generalized mathematical description can be considered as a systematic approach to analyze and think about multistage A/D converter algorithms. Error sources in the pipeline stage are described in details. Minimal base-2 A/D converters are highly sensitive to suffer several nonlinearities caused by these error sources. An efficient method

#### 2.8. SUMMARY

is presented to describe the redundant schemes extended from the minimal base-2 architectures and also remove the magic or mystery of digital error correction. The usefulness of generalized mathematical description is proved by the illustrations of three examples of multistage ADC with different redundant schemes. Finally, The CMOS circuit implementations of the pipeline stage are presented, and the static errors of the MDAC are almost caused by component mismatches, finite opamp gain and the parasitic capacitance associated with the opamp's negative input.

# **Chapter 3**

# **Pipelined ADC Calibration Techniques**

willing,

## 3.1 Introduction