# 應用於低暗電流和高光譜反應之互補式金氧半影 像感測器分析與設計

## THE ANALYSIS AND DESIGN OF CMOS IMAGERS FOR LOW-DARK-CURRENT AND HIGH-SPECTRAL-RESPONSE APPLICATIONS

研究生:施育全 Student: Yu-Chuan Shih 指導教授: 吳重兩 Advisor: Chung-Yu Wu

國立交通大學電子工程系電子研究所 博士論文

A Dissertation Submitted to

Institute of Electronics

College of Electrical Engineering and

Computer Science

National Chiao Tung University

In Partial Fulfillment of Requirements

For the Degree of

Doctor of Philosophy

In

Electronic Engineering

June 2004 Hsinchu, Taiwan, Republic of China

中華民國九十三年六月

事由:推薦電子研究所博士班研究生施育全提出論文並參加國立交通大學博士論文口試。

說明:本校電子研究所博士班研究生施育全已完成電子研究所規定之學 科及論文研究訓練。 有關學科部分,施君已修畢 18 學分(請查閱學籍資料),通過資

有關學科部分,施君已修畢 18 學分(請查閱學籍資料),通過資格考試及英文語文能力測驗;有關論文研究部分,施君已完成『應用於低暗電流和高光譜反應之互補式金氧半影像感測器分析與設計』論文初稿,並已有數篇相關之論文與專利發表或送審,茲列舉如下:

#### (A) JOURNAL PAPERS

- [1] Ude Lu, Ben C.-P. Hu, <u>Yu-Chuan Shih</u>, Yuh-Shyong Yang, Chung-Yu Wu, Chiun-Jye Yuan, Ming-Dou Ker, Tung-Kung Wu, Yaw-Kuen Li, You-Zung Hsieh, Wensyang Hsu, and Chin-Teng Lin, "CMOS chip as luminescent sensor for biochemical reactions," *IEEE Sensors Journal*, vol. 3, pp. 310-316, June 2003.

- [2] Chung-Yu Wu, <u>Yu-Chuan Shih</u>, Jeng-Feng Lan, Chih-Cheng Hsieh, Chien-Chang Huang, and Jr-Houng Lu, "Design, optimization, and performance analysis of new photodiode structures for CMOS active-pixel-sensor (APS) imager applications," *IEEE Sensors Journal*, vol. 4, pp. 135-144, Feb. 2004.

- [3] <u>Yu-Chuan Shih</u> and Chung-Yu Wu, "A new CMOS pixel structure for low-dark-current and large-array-size imager applications," accepted by *IEEE Transactions on Circuits and Systems I*, Feb. 2004.

- [4] <u>Yu-Chuan Shih</u> and Chung-Yu Wu, "Optimal design of CMOS pseudo-active-pixel-sensor (PAPS) structure for low-dark-current and large-array-size imager applications," accepted by *IEEE Sensors Journal*, Mar. 2004.

#### (B) CONFERENCE PAPERS

[1] <u>Yu-Chuan Shih</u> and Chung-Yu Wu, "The design of high-performance 128 x 128 CMOS image sensors using new current-readout techniques," in *Proc. IEEE*

International Symposium on Circuits and Systems, May 1999, vol. 5, pp. 168-171.

- [2] <u>Yu-Chuan Shih</u> and Chung-Yu Wu, "A new CMOS imager using the pseudo-active-pixel-sensor (PAPS) circuit for high resolution applications," in *Proc. Enropean Conference on Circuit Theory and Design*, Aug. 2001, vol. 2, pp. 57-60.

- [3] <u>Yu-Chuan Shih</u> and Chung-Yu Wu, "An optimized CMOS pseudo-active-pixel-sensor structure for low-dark-current imager applications," in *Proc. IEEE International Symposium on Circuits and Systems*, May 2003, vol. 1, pp. 809-812.

#### (C) PATENTS

[1] Chung-Yu Wu, <u>Yu-Chuan Shih</u>, Jeng-Feng Lan, Chih-Cheng Hsieh, Chien-Chang Huang, and Jr-Houng Lu, "The photodiode with the characteristics of low-leakage-current effects (可減少漏電流影響之光電二極體)," R.O.C. Patent No. 575969, Feb. 11, 2004.

總言之,施君已具備國立交通大學電子研究所應有的訓練水準。因此推薦施君參加國立交通大學電子研究所博士論文口試。

國立交通大學電子研究所教授 吳重雨 博士

# 應用於低暗電流與高光譜反應之互補式 金氧半影像感測器分析與設計

研究生:施育全 指導教授:吳重兩

#### 國立交通大學電子工程系電子研究所

#### 摘要

本論文提出、分析並設計應用於互補式金氧半(CMOS)主動式像素影像感測器(Active Pixel Sensor imager)之新型光二極體架構和應用於低暗電流和大陣列數目影像感測器之新型互補式金氧半像素架構。論文中主要包含下列三個主要部份:(1)應用於互補式金氧半主動式像素影像感測器之新型光二極體架構設計、最佳化與成果分析;(2)應用於低暗電流與大陣列數目靜態影像感測器之新型互補式金氧半像素架構;(3)應用於低暗電流與大陣列數目影像感測器之五補式金氧半虛擬主動式像素感測器(Pseudo Active Pixel Sensor)的最佳化設計。

首先,由於暗電流在互補式金氧半影像感測器的主動式像素感測單元中主要產生於經過局部氧化矽(LOCOS)過程後的鳥嘴區和高掺雜濃度沉積引起的表面損害。此外,淺和深的 pn 接面分別可以改善短波長光和長波長光的光感應度。為了減少暗電流和增加整體的光譜反應,吾人提出並分析利用 p 型基體和輕微掺雜濃度的感測器佈植 SN-當 pn 接面光二極體與其鳥嘴區分別被 SN-和 p-field 佈植包圍住的兩種新型光二極體架構。在  $5~\mu m \times 5~\mu m$  的主動式像素感測單元中,採用了提出的光二極體架構並經過  $0.35~\mu m$  1P3M N-well 互補式金氧半技術的製造。從量測結果顯示,在  $5~\mu m \times 5~\mu m$  主動式像素感測單元中,兩種吾人提出的光二極體架構與傳統架構及別的光二極體架構比較下,在 2~V 反相偏壓時有 30.6~mV/sec 和 35.2~mV/sec 的較低暗電流和較高的光譜反應。

其次,根據傳統的主動式像素感應器的像素架構,吾人提出一稱之為『虛擬主動式像素感應器』(Pseudo Active Pixel Sensor)的新型像素架構

並應用於靜態互補式金氧半影像感測器中。這個新型的像素架構和傳統 被動式像素影像感測器(Passive Pixel Sensor imager)及主動式像素影像感 測器相比,具有低漏電流、高訊號雜訊比例和高填充係數等優點。一種 稱之為『行零偏壓緩衝直接注入式』(Zero-bias Column Buffer-Direct-Injection)的讀出電路架構也被提出,此種讀出電路偏壓光二 極體和位於行匯流排的雜散 pn 接面於 0 V 或接近 0 V 來減少光二極體的 暗電流和列開關的漏電流。改良式的雙重三角取樣(Double Delta Sampling) 電路也被使用來減少固定樣式雜訊(fixed pattern noise)、時脈回饋雜訊和 通道電荷注入。352 x 288(CIF)格式的互補式金氧半虛擬主動式像素影像 感測器實驗晶片是經由 0.25 μm 1P5M N-well 互補式金氧半技術製造。像 素的大小是 5.8 μm x 5.8 μm。像素讀出速率從 100 kHz 到 10 MHz, 相當 於最大的畫面速率(frame rate)超過30 frames/sec。這個提出的靜態互補式 金氧半影像感測器還具有 58%的填充係數、3110 μm x 2760 μm 的晶片面 積和操作在 3.3 V 電源供應時產生的 24 mW 功率消耗。這個實驗性的晶 片已經成功地證明了新提出的虛擬主動式像素感測器架構並且可以應用 在低暗電流和高解析度的大陣列數目靜態互補式金氧半影像感測器系統 設計。

最後,根據吾人提出的虛擬主動式像素感測器的像素架構,一應用 於互補式金氧半影像感測器的像素架構稱為『最佳化虛擬主動式像素感 測器』(Optimal Pseudo Active Pixel Sensor)亦被提出、分析和設計。在像 素中被共享的零偏壓緩衝器可保持光二極體和位於像素匯流排的雜散pn 接面偏壓於 0 V或接近 0 V來減少光二極體的暗電流和像素開關的漏電 流。每單位像素面積的光電流與暗電流比例(PDRPA)這個係數可以定義用 來描述最佳化虛擬主動式像素感測器的性能特徵。當零偏壓緩衝器被四 個像素共用時被發現具有最大的PDRPA。此外、行取樣電路和輸出相關 雙重取樣電路也被用來減少固定樣式雜訊、時脈回饋雜訊和通道電荷注 入。352 x 288(CIF)格式的互補式金氧半最佳化虛擬主動式像素影像感測 器實驗晶片是經由 0.25 μm 1P5M N-well互補式金氧半技術設計和製造。 在這個製造的互補式金氧半影像感測器當中,每四個像素共用一個零偏 壓緩衝器下的PDRPA值等於 37.7  $\mu m^{-2}$ 。它也具有 8.2  $\mu m \times 8.2 \mu m$ 的像素 大小、42%的填充係數和 3630 μm x 3390 μm的晶片面積。量測到的最大 畫面速率是 30 frames/sec、暗電流為 82 pA/cm<sup>2</sup>。量測到的光動態範圍是 65dB。與主動式像素感測器架構和傳統的被動式像素感測器架構相比較 時,吾人所提出的最佳化虛擬主動式像素感測器架構具有較小的暗電

流、較高的填充係數和較高的光動態範圍。

根據以上的結果,我們深信吾人所提出新型光二極體架構可以被應用在具有小像素面積、高解析度和高品質的互補式金氧半影像感測系統中。此外,具有小像素面積、高填充係數和低暗電流等優點特徵之吾人所提出的新型互補式金氧半虛擬主動式像素影像感測器架構,將可以被應用在大陣列數目靜態互補式金氧半影像感測器設計中。吾人所提出之互補式金氧半最佳化虛擬主動式像素影像感測器和虛擬主動式像素感測器、主動式像素感測器、被動式像素感測器等互補式金氧半影像感測器相比較下有較低的暗電流,同時也比互補式金氧半主動式像素影像感測器有較高的填充係數。因此,吾人所提出之最佳化虛擬主動式像素感測器架構應用在高品質的互補式金氧半影像感測器時會具有較高的潛力。

#### THE ANALYSIS AND DESIGN OF CMOS IMAGERS FOR LOW-DARK-CURRENT AND HIGH-SPECTRAL-RESPONSE APPLICATIONS

Student: Yu-Chuan Shih Advisor: Chung-Yu Wu

## Department of Electronics Engineering & Institute of Electronics National Chiao Tung University

### **ABSTRACT**

In this thesis, new photodiode structures for CMOS active pixel sensor (APS) imagers and new CMOS pixel structures for low-dark-current and large-array-size imager applications are proposed, analyzed, and designed. The main parts of this thesis include: (1) design, optimization, and performance analysis of new photodiode structures for CMOS APS imager applications; (2) a new CMOS pixel structure for low-dark-current and large-array-size still imager applications; (3) optimal design of CMOS pseudo active pixel sensor (PAPS) structure for low-dark-current and large-array-size imager applications.

Firstly, it is known that the dark current in the APS cell of a CMOS imager is mainly generated in the regions of bird's beak after the LOCOS (local oxidation of silicon) process as well as the surface damage caused by the implantation of high doping concentration. Furthermore, shallow and deep pn junctions can improve the photo-sensitivity for light of short and long wavelengths, respectively. Two new photodiode structures using p-substrate and lightly-doped sensor implant SN– as pn junction photodiode with the regions of bird's

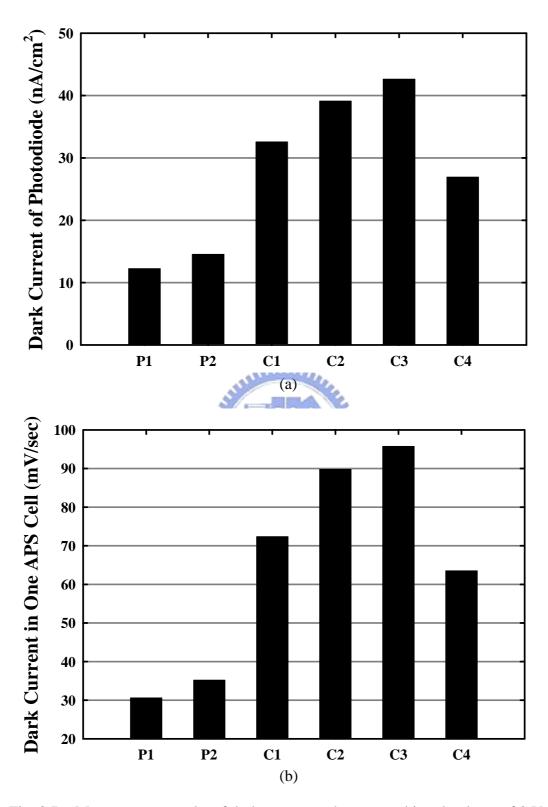

beak embraced by SN– and p-field implant, respectively, are proposed and analyzed to reduce dark current and enhance the overall spectral response. 5  $\mu$ m x 5  $\mu$ m APS cells fabricated in a 0.35  $\mu$ m single-poly-triple-metal (1P3M) N-well CMOS process are designed by using the proposed photodiode structures. As shown from the experimental results, the two proposed photodiode structures of 5  $\mu$ m x 5  $\mu$ m APS cells have lower dark currents of 30.6 mV/sec and 35.2 mV/sec at the reverse-biased voltage of 2 V and higher spectral response, as compared to the conventional structure and other photodiode structures.

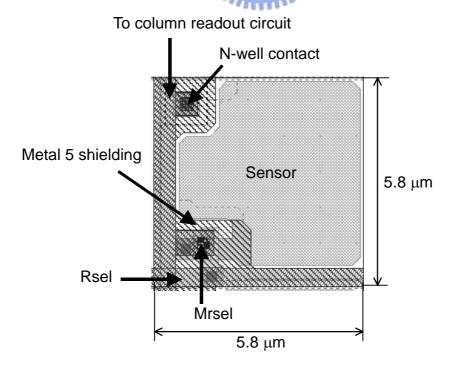

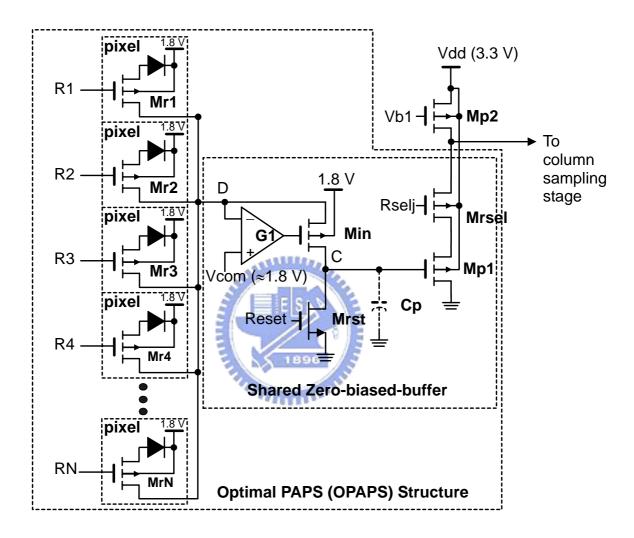

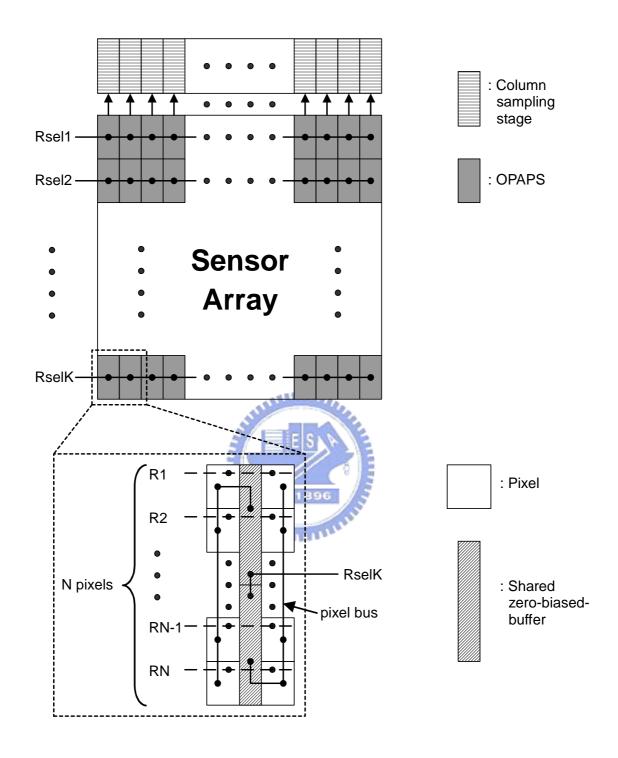

Secondly, based on the conventional APS pixel structure, a new pixel structure for still CMOS imager application called the pseudo active pixel sensor (PAPS) is proposed and analyzed. It has the advantages of low dark current, high signal-to-noise ratio (SNR), and high fill factor over the conventional passive pixel sensor (PPS) imager or APS imager. The readout circuit called the zero-bias column buffer-direct-injection (ZCBDI) structure is also proposed to suppress both dark current of photodiode and leakage current of row switches by keeping both biases of photodiode and parasitic pn junction in the column bus at or near zero voltage. The improved double delta sampling (DDS) circuits are also used to suppress fixed pattern noise, clock feedthrough noise, and channel charge injection. An experimental chip of the proposed PAPS CMOS imager with the format of 352 x 288 (CIF) has been fabricated by using 0.25 µm single-poly-five-level-metal (1P5M) N-well CMOS process. The pixel size is 5.8 µm x 5.8 µm. The pixel readout speed is from 100 kHz to 10 MHz, corresponding to the maximum frame rate above 30 frames/sec. The proposed still CMOS imager has a fill factor of 58%, chip size of 3110 µm x 2760 µm, and power dissipation of 24 mW under the power supply of 3.3 V. The experimental chip has successfully demonstrated the function of the proposed new PAPS structure. It can be applied in the design of large-array-size still CMOS imager systems with low dark current and high resolution.

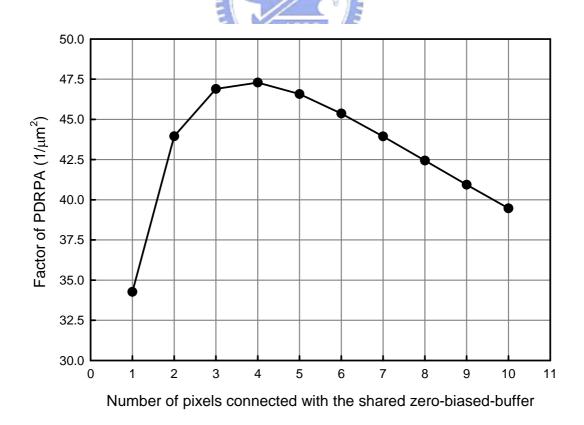

Finally, based on the proposed PAPS pixel structure, a pixel structure called the optimal pseudo active pixel sensor (OPAPS) is proposed, analyzed, and designed for the

applications of CMOS imagers. The shared zero-biased-buffer in the pixel is used to suppress both dark current of photodiode and leakage current of pixel switches by keeping both biases of photodiode and parasitic pn junctions in the pixel bus at zero voltage or near zero voltage. The factor of photocurrent-to-dark-current ratio per pixel area (PDRPA) is defined to characterize the performance of the OPAPS structure. It is found that a zero-biased-buffer shared by four pixels can achieve the highest PDRPA. In addition, the column sampling circuits and output correlated double sampling (CDS) circuits are also used to suppress fixed pattern noise, clock feedthrough noise, and channel charge injection. An experimental chip of the proposed OPAPS CMOS imager with the format of 352 x 288 (CIF) has been designed and fabricated by using 0.25 µm single-poly-five-level-metal (1P5M) N-well CMOS process. In the fabricated CMOS imager, one shared zero-biased-buffer is used for four pixels where the PDRPA is equal to 37.7 µm<sup>-2</sup>. The fabricated OPAPS CMOS imager has a pixel size of 8.2 µm x 8.2 µm, fill factor of 42%, and chip size of 3630 µm x 3390 µm. The measured maximum frame rate is 30 frames/sec and the dark current is 82 pA/cm<sup>2</sup>. The measured optical dynamic range is 65dB. It is found that the proposed OPAPS structure has lower dark current, higher fill factor, and higher optical dynamic range as compared with the APS structure and the conventional PPS structure.

From the above results, it is believed that the proposed new photodiode structures can be applied to CMOS imager systems with small pixel size, high resolution, and high quality. Moreover, with the advantageous characteristics of small pixel area, high fill factor, and low dark current, it is expected that the proposed new PAPS CMOS imager structure can be applied to the design of large-array-size still CMOS imagers. The proposed OPAPS CMOS imager has the smaller dark current than those of PAPS, APS, and PPS CMOS imagers and higher fill factor than that of APS CMOS imager. Thus the proposed OPAPS structure has high potential for the applications of high-quality CMOS imagers.

#### **ACKNOWLEDGMENTS**

首先我要感謝我的指導老師吳重雨教授多年來耐心的指導與鼓勵,使我能順利完成博士學業。在吳教授循序漸進的諄諄教誨下,讓我得以獲得許多積體電路設計的專業知識,更學習了挑戰困難及解決問題的態度與方法,沒有執著就沒有突破,雖然在過程倍感艱辛,但卻獲益良多。我還要感謝吳教授安排我到美國做短期研究的機會,不但增加我的國際視野廣度,而且也讓我對研究更加有興趣與信心。另外也要特別感謝充滿愛心,和藹可親的師母曾昭玲女士,謝謝她常常給予我關懷與打氣加油,讓我得以度過研究的低潮。

此外,我還要感謝汪重光教授、吳介琮教授、柯明道教授、劉濱達教授、盧志文教授、呂平幸處長以及藍正豐處長擔任口試委員,並提供寶貴的意見使得此論文可以更加完整與詳細。

在這段求學的過程中,積體電路與系統實驗室(307實驗室)日益成長茁壯,全靠歷代的學長姐及大家對 307實驗室的建立與運作所做的貢獻。另一方面我也要感謝姜信欽、顏文正、鄭秋宏、高宏鑫、廖以義、翁明鏟、徐研訓、徐建昌、周忠昀、黃冠勳、林俐如、徐國鈞、周儒明、傅昶綜、江政達、王文傑、范啟威、虞繼堯、蘇烜毅、徐新智等諸位學長同學及其他人員的努力,才使 307實驗室軟硬體設備一應俱全。在如此的環境下我的論文才得以順利完成。在此由衷感謝這些與我同在實驗室奮鬥的伙伴們,也希望積體電路與系統實驗室能越來越好。

我要感謝原相科技公司、工研院電通所及國科會晶片設計製作中心提供了晶片設計及製作之環境,使我能夠完成論文中積體電路之實驗印證。此外我還要謝謝原相科技的成員藍正豐、謝志成、呂志宏及黃建章等諸位學長及百力達公司的姜信欽經理在晶片設計上的協助與建議;感謝陳東暘、鄭秋宏、廖以義、周忠昀、黃冠勳、林俐如、陳厚柏、胡華珊、蘇紀豪、杜長慶、陳勝豪等在各項研究事務上的幫忙;感謝實驗室助理李婷媛及卓慧貞小姐在行政事務上的協助;感謝在美國約翰霍普金斯大學的Prof. Andreas G. Andreou 對我的指導;感謝實驗室的球友許振隆學長、陳厚柏、王文傑、陳勝豪以及交大電子桌球隊的所有成員,使我於課業繁忙之餘還可以藉由桌球來鍛鍊身體,數不清的大電盃、校長盃、系際盃、畢聯盃及大同中原盃的冠亞軍和痛宰梅竹賽代表選手永遠是我最美好的回憶;感謝所有關心我的師長與朋友。

最後,我要致上最深的感謝給我的父母親以及我的家庭,由於他們的支持與鼓勵,是我最大的精神支柱,使我能心無旁騖的完成學業。沒有你們無怨無悔、永無止境的付出、鼓勵、支持與照顧,就不會有今日的我。衷心的感謝你們,也感謝上蒼賜予我一個如此幸福和樂的家庭。

施育全 誌於 風城交大 九十三年秋

### **CONTENTS**

| ABSTRACT (              | CHINESE)                          | i                |

|-------------------------|-----------------------------------|------------------|

| ABSTRACT (              | ENGLISH)                          | iv               |

| ACKNOWLE                | DGEMENTS                          | vii              |

| CONTENTS                |                                   | viii             |

| TABLE CAPTIONS          |                                   |                  |

| FIGURE CAP              | TIONS                             | xiv              |

| 1.1 BACKG<br>1.2 MOTIVA | 1896                              | 1<br>3<br>5<br>8 |

| CHAPTER 2               | REVIEW OF PHOTODETECTORS AND      | D                |

|                         | PIXEL CIRCUITS IN CMOS IMAGE      |                  |

|                         | SENSORS                           |                  |

| 2.1 INTROI              | DUCTION                           | 9                |

| <b>2.2 PHOTO</b>        | DETECTORS FOR USE IN CMOS IMAGING |                  |

| SYSTEN                  | MS                                | 9                |

| 2.3 OVERA               | LL ARCHITECTURE AND OPERATIONAL   |                  |

| REQUIREMENTS OF CMOS IMAGE SENSORS                                                           | 11 |

|----------------------------------------------------------------------------------------------|----|

| 2.3.1 Overall Architecture                                                                   | 11 |

| 2.3.2 Operational Requirements of CMOS Image Sensors                                         | 12 |

| 2.4 PIXEL CIRCUITS OF CMOS IMAGE SENSORS                                                     | 18 |

| 2.4.1 Passive Pixel Circuit                                                                  | 19 |

| 2.4.2 Active Pixel Circuit                                                                   | 19 |

| 2.4.3 Logarithmic Pixel Circuit                                                              | 20 |

| 2.5 READOUT CIRCUITS OF CMOS IMAGE SENSORS                                                   | 20 |

| 2.5.1 Double Delta Sampling (DDS) Circuit                                                    | 20 |

| 2.6 SUMMARY                                                                                  | 21 |

| <b>Table 2.1</b>                                                                             | 22 |

| Figs. 2.1 – 2.5                                                                              | 23 |

| CHAPTER 3 DESIGN, OPTIMIZATION, AND PERFORMANCE ANALYSIS OF NEW PHOTODIODE STRUCTURES FOR CM | os |

| ACTIVE PIXEL SENSOR (APS) IMAGE                                                              | R  |

| APPLICATIONS                                                                                 |    |

| 3.1 INTRODUCTION                                                                             | 26 |

| 3.2 ANALYSIS OF NEW CMOS PHOTODIODE                                                          |    |

| STRUCTURES                                                                                   | 28 |

| 3.3 LAYOUT OPTIMIZATION OF NEW PHOTODIODE                                                    |    |

| STRUCTURES IN APS CELLS                                                                      | 33 |

| 3.4 EXPERIMENTAL RESULTS                                                                     |    |

| 3.4.1 Dark Current                                                                           | 37 |

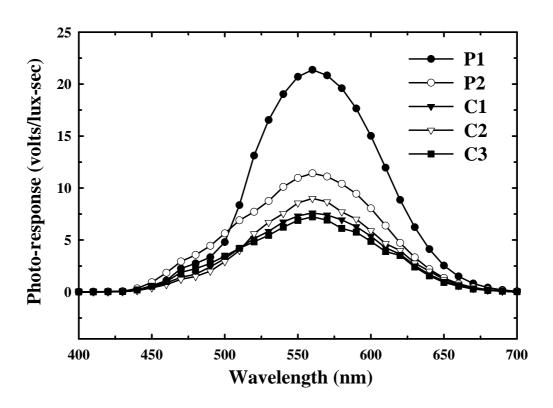

| 3.4.2 Spectral Response                                                                      | 39 |

| 3.5 SUMMA              | ARY                                                                                         | 41  |

|------------------------|---------------------------------------------------------------------------------------------|-----|

| <b>Table 3.1 – 3.2</b> |                                                                                             | 43  |

| Figs. 3.1 – 3.9        |                                                                                             | 45  |

| CHAPTER 4              | NEW CMOS PIXEL STRUCTURE FOR                                                                |     |

|                        | LOW-DARK-CURRENT AND                                                                        |     |

|                        | LARGE-ARRAY-SIZE STILL IMAGER                                                               |     |

|                        | APPLICATIONS                                                                                |     |

| 4.1 INTROI             | DUCTION                                                                                     | 56  |

| 4.2 PIXEL S            | STRUCTURE AND READOUT CIRCUITS                                                              | 58  |

| 4.2.1 Ps               | eudo Active Pixel Sensor (PAPS) Structure                                                   | 58  |

| Str                    | ero-Bias Column Buffer-Direct-Injection (ZCBDI) ructure aproved Double Delta Sampling (DDS) | 62  |

| $O_{J}$                | peration Circuit                                                                            | 66  |

| 4.3 CHIPA              | RCHITECTURE                                                                                 | 70  |

| 4.4 SIMULA             | ATION AND EXPERIMENTAL RESULTS                                                              | 71  |

| 4.5 SUMMA              | ARY                                                                                         | 74  |

| <b>Table 4.1 – 4.6</b> |                                                                                             | 76  |

| Figs. 4.1 – 4.16       | <b>i</b>                                                                                    | 78  |

| CHAPTER 5              | OPTIMAL DESIGN OF CMOS                                                                      |     |

|                        | PSEUDO ACTIVE PIXEL SENSOR (PAI                                                             | PS) |

|                        | STRUCTURE FOR LOW-DARK-CURRI                                                                | ENT |

## AND LARGE-ARRAY-SIZE IMAGER

### **APPLICATIONS**

| 5.1 INTRODUCTION                                                       | 87  |

|------------------------------------------------------------------------|-----|

| 5.2 OPTIMAL PSEUDO ACTIVE PIXEL SENSOR (OPAPS)                         | 88  |

| 5.3 CHIPARCHITECTURE AND SIMULATION RESULTS                            | 95  |

| 5.4 EXPERIMENTAL RESULTS                                               | 96  |

| 5.5 SUMMARY                                                            | 99  |

| <b>Table 5.1 – 5.4</b>                                                 | 101 |

| Figs. 5.1 – 5.15                                                       | 103 |

| CHAPTER 6 CONCLUSIONS AND FUTURE WORKS 6.1 MAIN RESULTS OF THIS THESIS | 2   |

| 6.1 MAIN RESULTS OF THIS THESIS 6.2 FUTURE WORKS                       | 2 5 |

| DEEEDENCES.                                                            | 7   |

| REFERENCES                                                             | 7   |

| VITA                                                                   | 2   |

| DIDI ICATIONI ICT                                                      |     |

| PUBLICATION LIST                                                       | 3   |

#### TABLE CAPATIONS

#### **CHAPTER 2**

Table 2.1 Comparisons of characteristics among photodetectors in CMOS imagers

#### **CHAPTER 3**

Table 3.1 All layers and their functions in the design of CMOS APS imager

#### **CHAPTER 4**

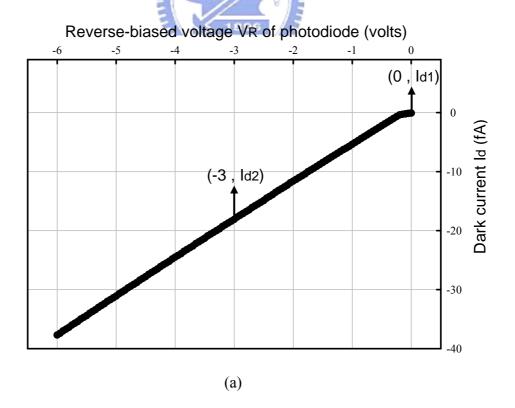

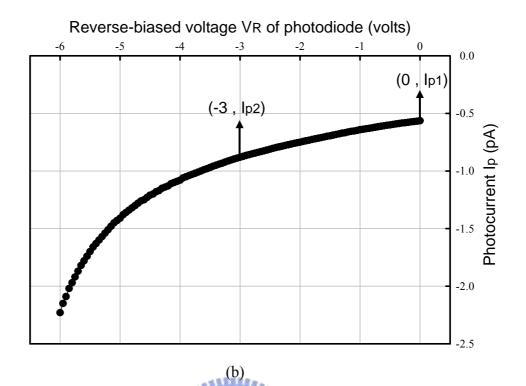

- Table 4.1 The values of Id1, Id2, Ip1, Ip2, Ip1/Id1, and Ip2/Id2

- Table 4.2 The values of Isp, Is1, Is2,  $\alpha$ , and width/length of Mrsel

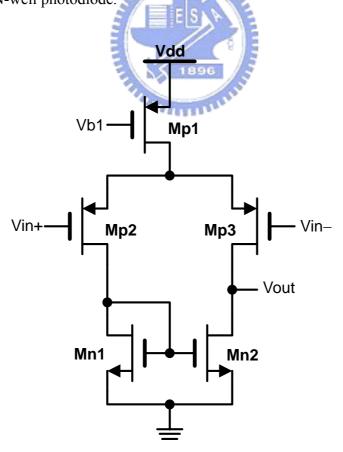

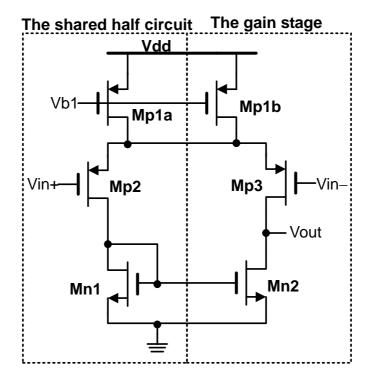

- Table 4.3 The device parameters in the circuit diagram of the gain stage.

- Table 4.4 The values of Chold, VILSB, GPGA, Ileak, and Tint

- Table 4.5 The depth of N+ diffusion, P+ diffusion, N-well, and Deep N-well in 0.25  $\mu m$  1P5M N-well CMOS process

- Table 4.6 The measurement results of the proposed PAPS CMOS imager with the value of Vcom equal to 1.79 V and its comparisons with that of APS CMOS imager [101]

- Table 5.1 The device parameters in the circuit diagram of the gain stage

- Table 5.2 The values of Isp, Is1, Is2, α, and width/length of Mri

- Table 5.3 The design parameters of Id1, Ip1, Abuf, Apsw, Apsw, D, Apsw, S, Apd, Asp, and

#### CR for 0.25 $\mu m$ 1P5M N-well CMOS process

Table 5.4 The measurement results of the proposed OPAPS CMOS imager with the value of Vcom equal to 1.79 V and its comparisons with that of PAPS [92] and APS CMOS imager [101]

#### FIGURE CAPATIONS

#### **CHAPTER 1**

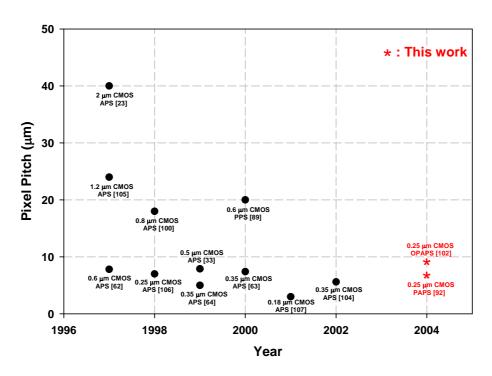

Fig. 1.1 The rate of pixel size decrease in CMOS imagers.

#### **CHAPTER 2**

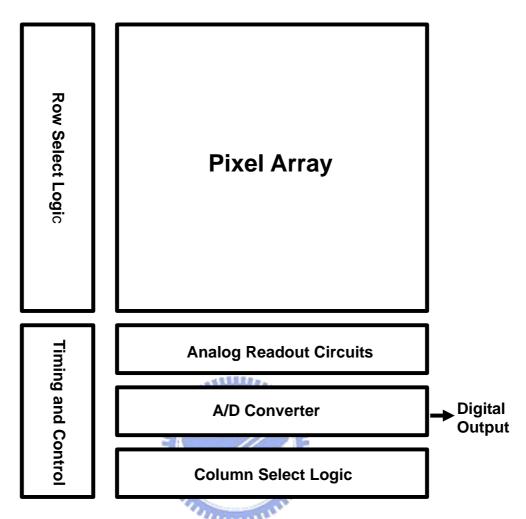

- Fig. 2.1 The overall architecture of a CMOS image sensor.

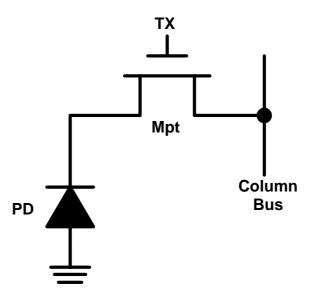

- Fig. 2.2 Passive pixel circuit.

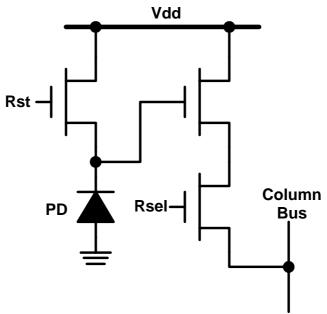

- Fig. 2.3 Active pixel circuit.

- Fig. 2.4 Logarithmic pixel circuit.

- Fig. 2.5 Double delta sampling (DDS) circuit.

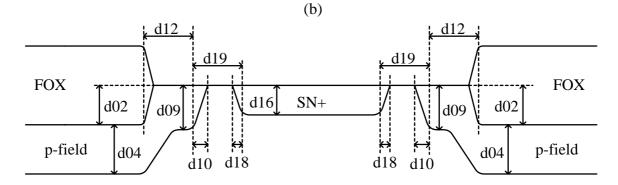

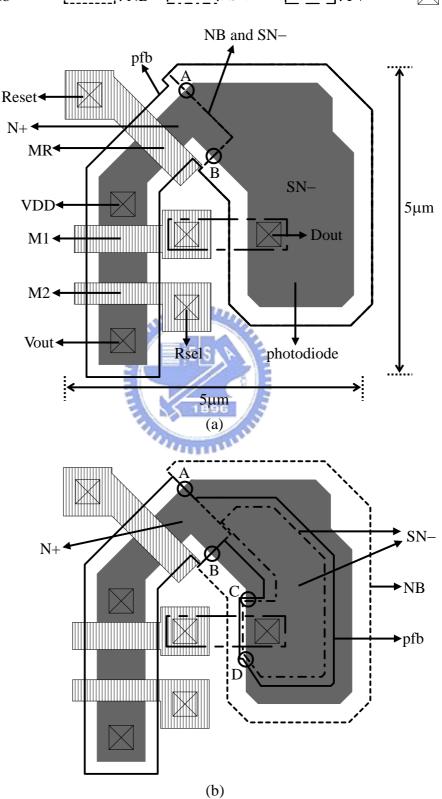

- Fig. 3.1 Two proposed new photodiode structures: (a) Type P1: photodiode is composed of p-substrate and SN- with its bird's beak embraced by SN-. (b) Type P2: photodiode is composed of p-substrate and SN- with its bird's beak embraced by p-field.

- Fig. 3.2 Four photodiode structures for comparisons: (a) Type C1: SN- is replaced by N+ in the structure of P1 (conventional structure in CMOS imager). (b) Type C2: SN- is replaced by SN+ in the structure of P1. (c) Type C3: SN- is replaced by SN+ in the structure of P2. (d) Type C4: P+ is added to embrace the bird's beak in the structure of P2.

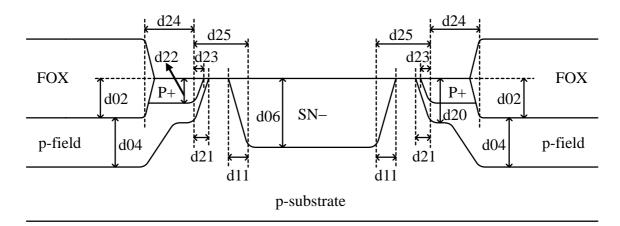

- Fig. 3.3 (a) Circuit diagram of APS cell. (b) Circuit diagram of APS cell with its Rsel and Vout connected to gnd and Vdd, respectively.

- Fig. 3.4 Layout of photodiode in 5 μm x 5 μm APS cell: (a) Type P1: fill factor = 32%.

(b) Type P2: fill factor = 15%. (c) Type C1: fill factor = 32%. (d) Type C4: fill factor = 15%.

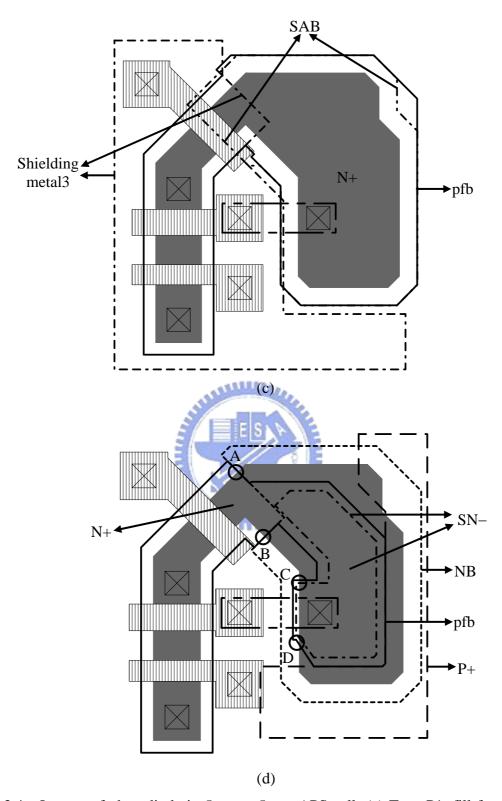

- Fig. 3.5 Photographs of (a) one photodiode structure in test chip and (b) overall test chip.

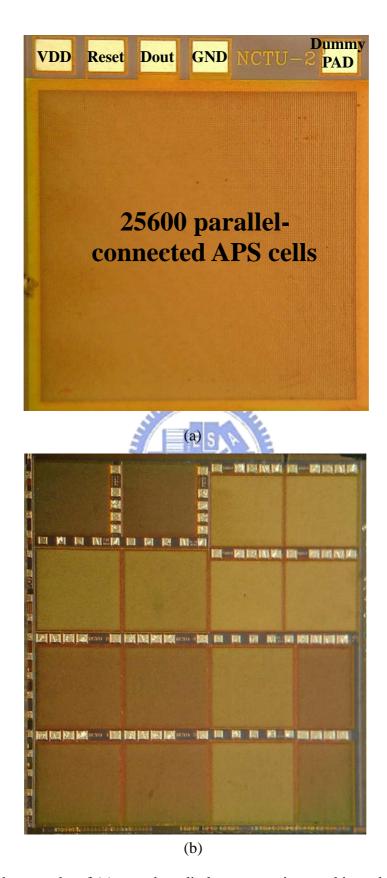

- Fig. 3.6 Dark current characteristics of photodiode in an APS cell with the photodiode of Type P1: (a) Current to voltage curve: I(V). (b) Capacitance to voltage curve: C(V).

- Fig. 3.7 Measurement results of dark current at the reverse-biased voltage of 2 V: (a) One photodiode. (b) One APS cell for imager applications.

- Fig. 3.8 Measurement results of dark current variations of Type P1 and P2 at the reverse-biased voltage of 2 V among seven different chips.

- Fig. 3.9 Spectral responses in the photodiode structures of Type P1, Type P2, Type C1, Type C2, and Type C3.

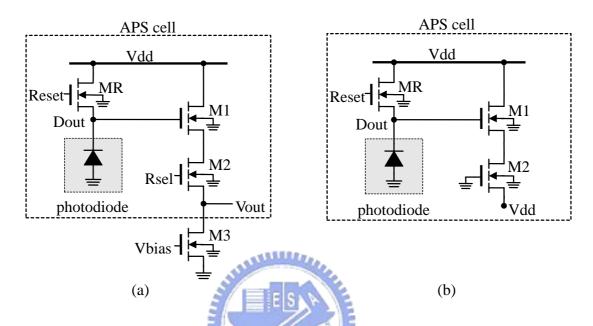

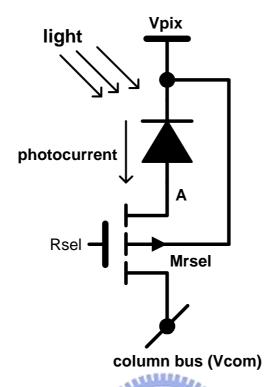

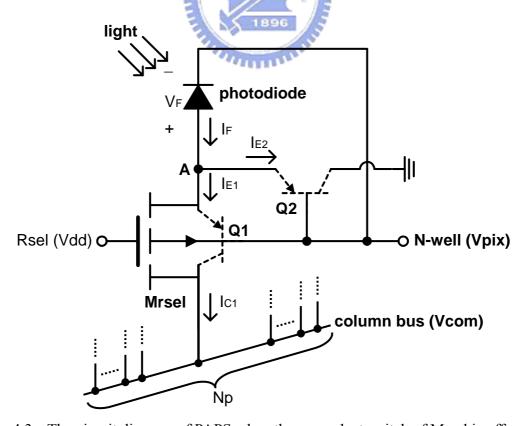

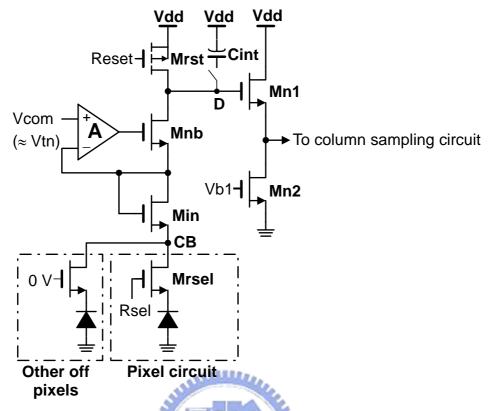

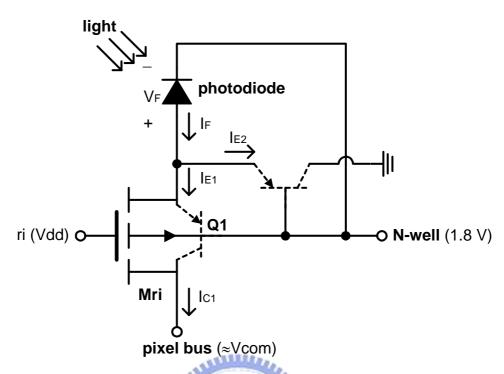

- Fig. 4.1 The circuit of the pseudo active pixel sensor (PAPS).

- Fig. 4.2 The measured (a) dark current Id and (b) photocurrent Ip of the fabricated P+/N-well photodiode.

- Fig. 4.3 The circuit diagram of PAPS when the row select switch of Mrsel is off.

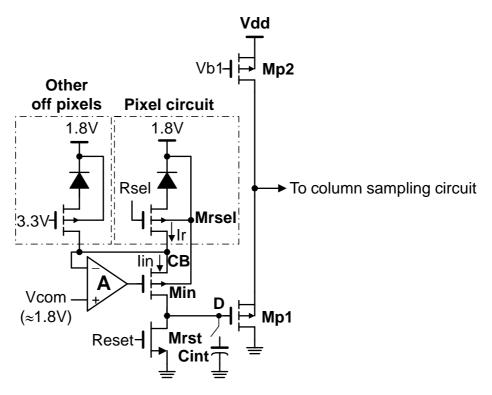

- Fig. 4.4 Zero-bias column buffer-direct-injection (ZCBDI) readout circuit with the P+/N-well photodiode.

- Fig. 4.5 The circuit diagram of the gain stage.

- Fig. 4.6 The modified ZCBDI readout circuit with the N+/P-substrate photodiode.

- Fig. 4.7 The PAPS structure with ZCBDI readout circuit and the improved DDS circuit.

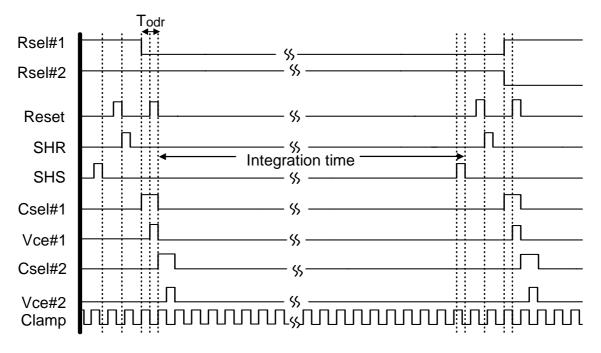

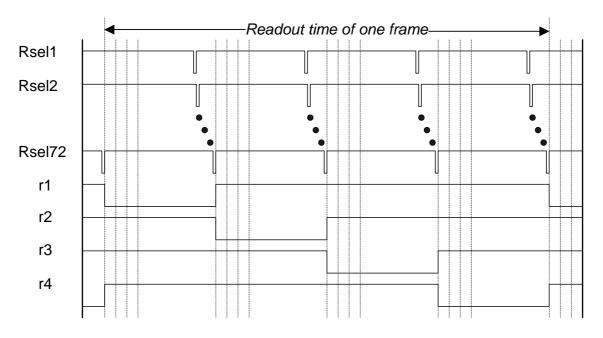

- Fig. 4.8 The major timing diagram of the column readout circuit and the output driver circuit.

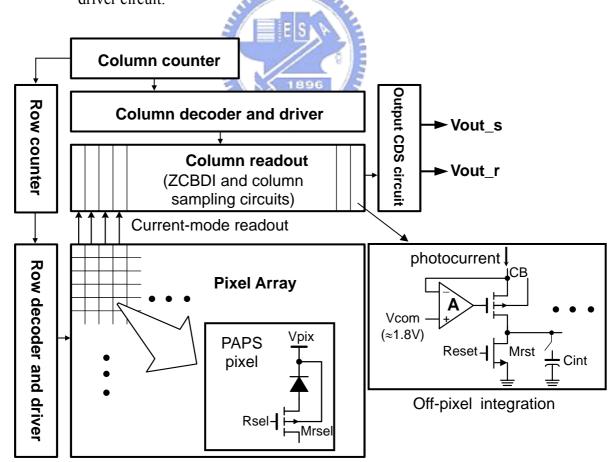

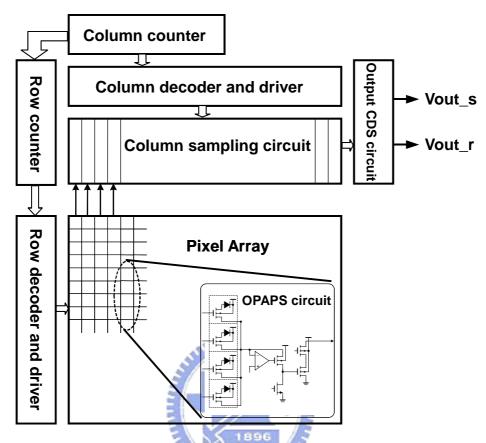

- Fig. 4.9 Block diagram of the proposed PAPS CMOS imager.

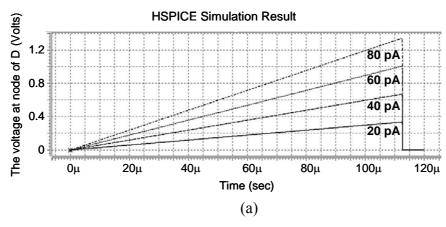

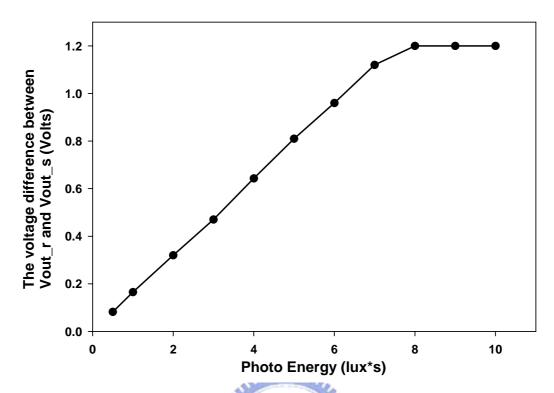

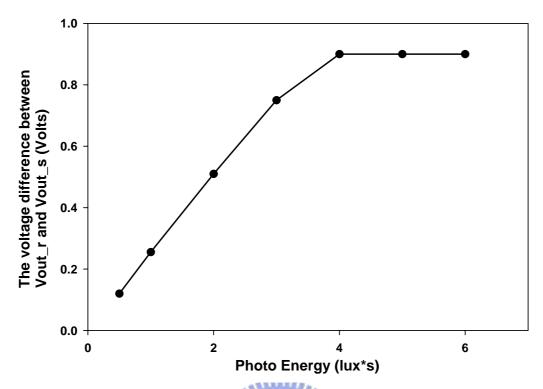

- Fig. 4.10 Simulation results of the voltage difference between Vout\_r and Vout\_s of Fig. 4.6 for the input photocurrent from 20 pA to 80 pA.

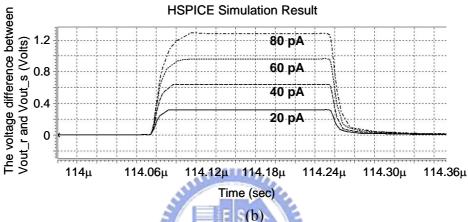

- Fig. 4.11 The layout of PAPS pixel.

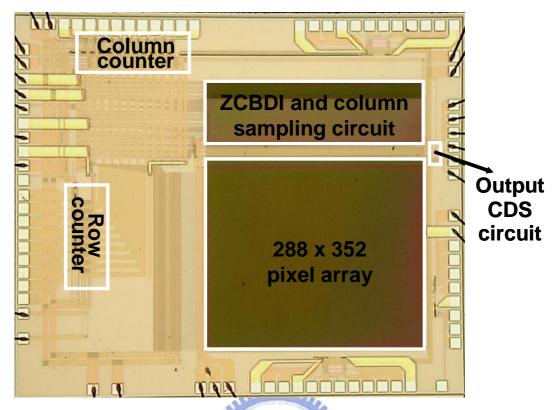

- Fig. 4.12 Die photograph of the test chip.

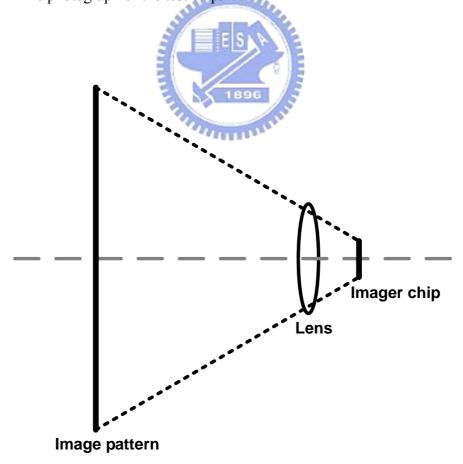

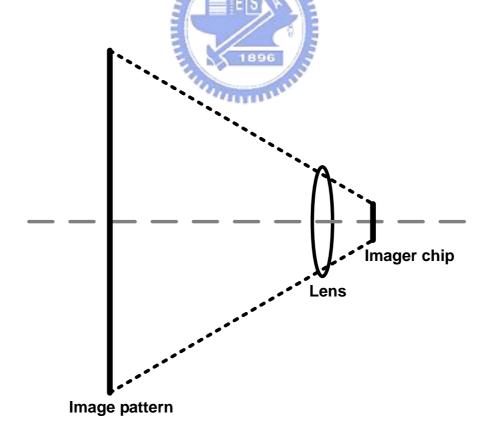

- Fig. 4.13 The measurement setup of image pattern, lens, and imager chip.

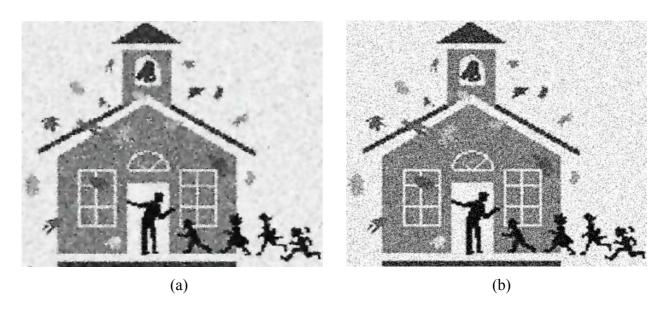

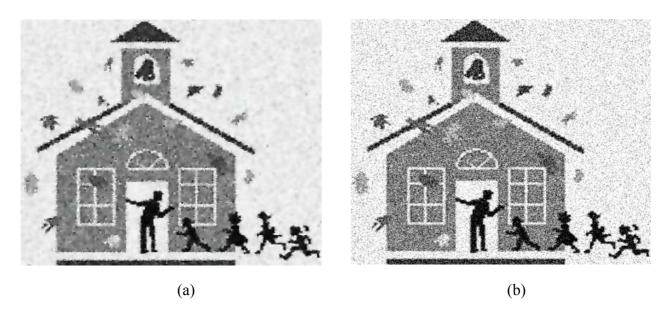

- Fig. 4.14 (a) Original image and (b) grayscale image captured by the test chip under the white light intensity of 24 lux and Vcom of 1.79 V.

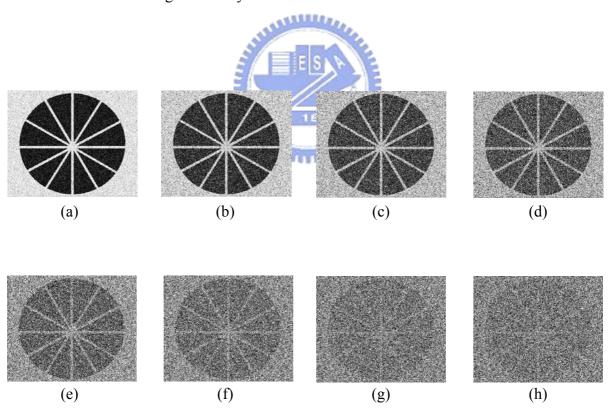

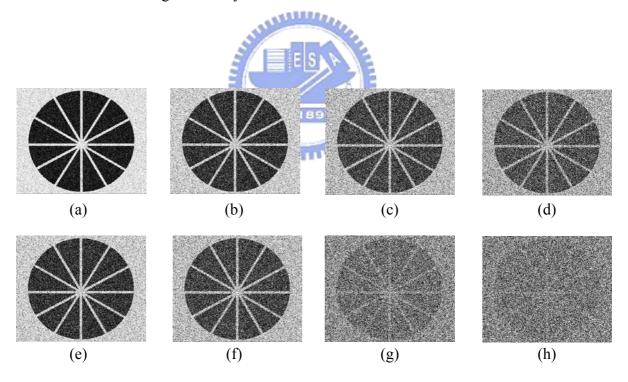

- Fig. 4.15 Image captured by the test chip under the white light intensity of 24 lux and Vcom of (a) 1.79 V, (b) 1.75 V, (c) 1.70 V, (d) 1.65 V, (e) 1.60 V, (f) 1.55 V, (g) 1.50 V, and (h) 1.45 V.

- Fig.4.16 Photo-sensitivity of PAPS CMOS imager.

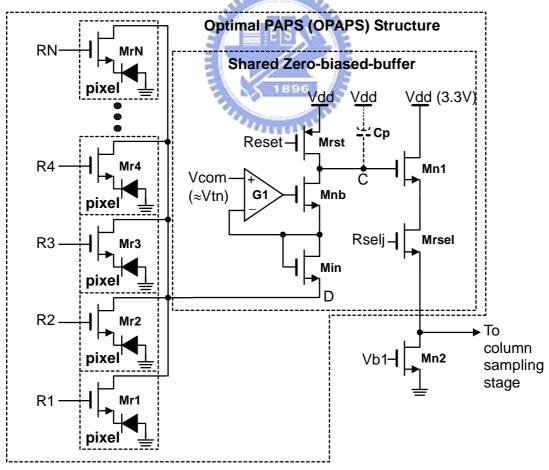

- Fig. 5.1 The optimal pseudo active pixel sensor (OPAPS) circuit with P+/N-well photodiode.

- Fig. 5.2 Interconnections of pixels, shared zero-biased-buffers, and column sampling stages in the OPAPS CMOS imager.

- Fig. 5.3 The circuit diagram of the gain stage.

- Fig. 5.4 The modified optimal pseudo active pixel sensor (OPAPS) circuit with N+/P-substrate photodiode.

- Fig. 5.5 The diagram of pixel circuit in OPAPS when the pixel select switch of Mri is off.

- Fig. 5.6 The factor of PDRPA in the OPAPS circuit.

- Fig. 5.7 Block diagram of the OPAPS CMOS imager.

- Fig. 5.8 The major timing diagram of the OPAPS circuit.

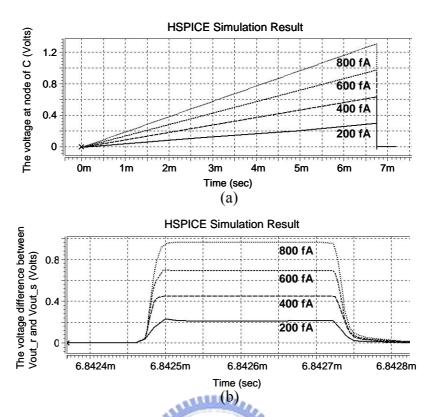

- Fig. 5.9 HSPICE simulation results of (a) the voltage at node C of Fig. 5.1 and (b) the voltage difference between Vout\_r and Vout\_s of Fig. 5.6 for the input photocurrent from 200 fA to 800 fA.

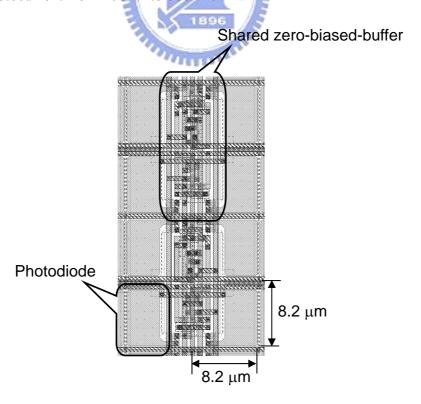

- Fig. 5.10 The layout of eight pixels in the OPAPS CMOS imager chip.

- Fig. 5.11 Die photograph of the test chip.

- Fig. 5.12 The measurement setup of image pattern, lens, and imager chip.

- Fig. 5.13 (a) Original image and (b) grayscale image captured by the test chip under under the white light intensity of 24 lux and Vcom of 1.79 V.

- Fig. 5.14 Images captured by the test chip of OPAPS structure under under the white light intensity of 24 lux and Vcom of (a) 1.75 V, (b) 1.65 V, (c) 1.50 V, and (d) 1.35 V and those captured by the test chip of PAPS structure under under the white light intensity of 24 lux and Vcom of (e) 1.79 V, (f) 1.65 V, (g) 1.50 V, and (h) 1.35 V

- Fig. 5.15 Photo-sensitivity of OPAPS CMOS imager.

#### INTRODUCTION

#### 1.1 BACKGROUND

Nowadays, the imaging system technology has been applied in various fields including camera [1]-[6], medical examination [7]-[9], surveillance systems [10]-[12], astronomy [13]-[15], military systems [16]-[18], and other strategic equipments [19]-[21]. The integration of commercial and military imaging systems has been recently developed and analyzed. Electronic imagers are one kind of popular imaging systems that have experienced continuing improvements over the past 10 years. The image quality is now approaching that of film.

Electronic imagers have come to dominate a wide range of markets. At the commercial end, electronic imagers are universally used for camcorders, scanners, digital still cameras, videophones, and recognition systems. At the high end, these devices are used in robotics, teleconferencing systems, and scientific applications. In addition, the medical industry often uses them for a variety of image scanning systems and applications.

Digital electronic cameras are the widest applications of electronic imagers, especially in computer peripherals for document capture and visual communications. The cost of the camera has been made sufficiently low, so that most personal computers almost have at least one camera peripheral. Even less expensive cameras will find entertainment applications. Wireless applications of cameras will require

ultra-low-power operation. Very small cameras will also permit new markets.

Due to the wide applications in our daily life, all digital electronic cameras have the same basic functions. These are 1) optical collection of photons, i.e., a lens; 2) wavelength discrimination of photons, i.e., filters; 3) detector for conversion of photons to electrons, e.g., a photodiode; 4) a method to readout the detectors, e.g., a CCD; 5) timing, control, and drive electronics for the sensor; 6) signal processing electronics for correlated double sampling, color processing, etc.; 7) analog-to-digital conversion; and 8) interface electronics [22]. In a CCD-based system, these functions often consume several watts of power and are therefore a major drain on a battery. The volume and mass of the electronics and power supply constraints the level of miniaturization of the system [22].

In imaging systems, integration of the image sensor with circuit for both driving the image sensor and performing on-chip signal processing is becoming increasingly important [23]. A high degree of electronics integration on the focal-plane can enable miniaturization of instrument systems and simplify system interfaces. In addition to good imaging performance with low noise, no lag, no smear, and good blooming control, it is desirable to have random access, simple clocks, and fast readout rates. The development of a CMOS-compatible image sensor technology is an important step for highly integrated imaging systems since CMOS technology is well suited for implementing on-chip signal processing circuits. CMOS technology is also a widely accessible and well-understood technology.

The main factor contributing to the recent activity in CMOS image sensors [24]-[30] is the steady, exponential improvement in CMOS technology. The rate of minimum feature size decrease has exceeded the similar improvements in CCD technology [22]. Over the past ten years, there has been a growing interest in CMOS image sensors. The major reason for this interest is customer demand for miniaturized,

low-power, and cost-effective imaging systems. CMOS-based image sensors offer the potential opportunity to integrate a significant amount of VLSI electronics on chip and reduce component and package costs. It is now straightforward to envision a single-chip camera that has integrated timing and control electronics, sensor array, signal processing electronics, analog-to-digital converter (ADC), and full digital interfaces. Such a camera-on-a-chip will operate with standard logic supply voltages and consume power measured in the tens of milliwatts [31]-[32].

With the rapid scaling down of CMOS technology, the design of multi-million-pixel high-resolution CMOS imagers [33]-[34] has become more and more challenging. Generally, small pixel size, low dark current, high fill factor, and high spectral response are required in the high-resolution CMOS imagers. The rate of pixel size decrease in CMOS imagers is shown in Fig.1.1. To achieve the optimal overall performance of CMOS imagers, a number of photodiode structures, pixel structures, and readout structures are developed for different system applications.

In this chapter, the background of CMOS image sensor is introduced first in Section 1.1. In Section 1.2, the design motivation of this thesis is described. Finally, the organization of this thesis is given in Section 1.3.

#### 1.2 MOTIVATION

The photodiode is a key component of CMOS imagers. To achieve a high-performance CMOS imager, the photodiode should be designed and optimized carefully. The two critical parameters in the design of photodiodes for imager applications are the dark current and the spectral response. Large dark current in the photodiode array of CMOS imagers can lead to non-uniformity, low scalability, and reduced dynamic range. The first source of dark current depends on doping

concentrations, bandgap, and temperature of the reverse-biased photodiode [35]. The second source is the defect-generated dark current determined by the shape of photodiode layout, the cross-sectional structure of the photodiode, and the fill factor [35]. The shape of photodiode layout can be designed to reduce the dark current [35]. Generally, the second source of dark current is mainly generated from the pn junction depletion region under bird's beak in LOCOS process [36] or in the interface isolation of STI (shallow trench isolation) as well as the surface damage caused by the implantation of high doping concentration. In addition, higher (lower) reverse-biased voltage of photodiode and parasitic pn junctions in the pixel leads to larger (smaller) dark current.

The spectral response is another important parameter considered in the design of photodiodes. The high spectral response of photodiodes can be generated by using shallow and deep depth of the pn junctions to absorb photons for light of short and long wavelengths, respectively.

In this thesis, both the operational requirements and structures of photodiode and pixel circuits are well studied and considered in detail. Two new photodiode structures for CMOS active pixel sensor (APS) imager applications are proposed and analyzed to reduce dark current and enhance the overall spectral response. In addition, a new pixel structure for still CMOS imager applications and its optimization is also proposed to have the advantages of lower dark current and higher fill factor over the conventional passive pixel sensor (PPS) imager or active pixel sensor (APS) imager. The proposed photodiode structures and pixel circuits can improve the overall performance of CMOS imager systems with innovative techniques and developments and can be applied to CMOS imagers with small pixel size, high resolution, and high quality. It is believed that the function and performance of CMOS imagers are well improved under our work.

#### 1.3 ORGANIZATION OF THIS THESIS

This thesis contains six chapters, which include design, optimization, and performance analysis of new photodiode structures for CMOS active pixel sensor (APS) imager applications, a new CMOS pixel structure called pseudo active pixel sensor (PAPS) for low-dark-current and large-array-size still imager applications, and optimization design of CMOS pseudo active pixel sensor (PAPS) structure.

Chapter 1 introduces the background, describes the research motivation, and explains the main topics of this thesis.

In Chapter 2, a brief description of photodetectors in CMOS image sensors is outlined and their developments are reported. Then, the structures and operational requirements of CMOS image sensor are discussed. Finally, we will discuss and review the pixel circuits in CMOS image sensors including the state-of-the-art structures.

In Chapter 3, two new photodiode structures with low dark current and high spectral response are proposed. The pn junction of p-substrate and the lightly-doped sensor implant SN— is used as a photodiode in both structures. The regions of bird's beak in the two proposed structures are completely embraced by the SN— implant and the p-field implant, thus not located in the pn junction depletion region. Both pn junction depletion located under the bird's beak and surface damage due to high doping concentration can be avoided and the generation of dark current can be suppressed. Furthermore, the use of shallow and deep pn junctions can increase the photo-sensitivity for light of short and long wavelengths, respectively. Thus the spectral response can be improved. Systematic comparisons on measurement results of dark currents and spectral responses among the proposed photodiode structures and

other structures in CMOS technology with reasonable process modifications are presented. From the experimental results, it has been verified that the two proposed structures in the 5  $\mu$ m x 5  $\mu$ m APS cell of the CMOS imager have low dark currents of 30.6 mV/sec and 35.2 mV/sec at the reverse-biased voltage of 2 V as well as good spectral response. The two proposed photodiode structures have lower dark current and higher spectral response as compared to the conventional structure and other photodiode structures.

In Chapter 4, a new pixel structure called the pseudo active pixel sensor (PAPS) for the large-array-size still CMOS imagers with low dark current and high fill factor is proposed. A new readout circuit is also proposed to readout the sensor current to the column bus and performs the outside-pixel integration using the APS-like structure. The new readout circuit keeps the biases of both photodiode and parasitic pn junctions in the column bus at or near zero bias to achieve low dark current, low column leakage current, and high linearity. The improved double delta sampling (DDS) circuit is used to reduce fixed pattern noise, clock feedthrough noise, and the noise from the effect of channel charge injection. An experimental chip of the proposed PAPS CMOS imager with the format of 352 x 288 (CIF) has been fabricated by using 0.25 µm single-poly-five-level-metal (1P5M) N-well CMOS process. The pixel size is 5.8 μm x 5.8 µm. The pixel readout speed is from 100 kHz to 10 MHz, corresponding to the maximum frame rate above 30 frames/sec. The proposed still CMOS imager has a fill factor of 58%, chip size of 3110 µm x 2760 µm, and power dissipation of 24 mW under the power supply of 3.3 V. The experimental chip has successfully demonstrated the function of the proposed new PAPS structure. It can be applied in the design of large-array-size still CMOS imager systems with low dark current and high resolution.

In Chapter 5, the optimal design of the structure of PAPS for the large-array-size

CMOS imagers with low dark current is presented and analyzed. In the proposed optimal PAPS (OPAPS) structure, a buffer circuit called the zero-biased buffer direct injection (ZBBDI) is shared by limited number of pixels to keep the photodiodes at zero or near zero bias and readout the selected pixel current [37]. Then the integration of readout current is performed by using an APS-like circuit. A new factor called the photocurrent-to-dark-current ratio per pixel area (PDRPA) is defined and optimized for the OPAPS structure. In the OPAPS design, both column sampling circuit and output correlated double sampling (CDS) circuit are used to reduce fixed pattern noise, clock feedthrough noise, and the noise from the effect of channel charge injection. An experimental chip of the proposed OPAPS CMOS imager with the format of 352 x 288 been designed and fabricated by using single-poly-five-level-metal (1P5M) N-well CMOS process. In the fabricated CMOS imager, one shared zero-biased-buffer is used for four pixels where the PDRPA is equal to 47.29 μm<sup>-2</sup>. The fabricated OPAPS CMOS imager has a pixel size of 8.2 μm x 8.2 µm, fill factor of 42%, and chip size of 3630 µm x 3390 µm. Moreover, the measured maximum frame rate is 30 frames/sec and the dark current is 82 pA/cm<sup>2</sup>. Additionally, the measured optical dynamic range is 6 5dB. It is found that the proposed OPAPS structure has lower dark current, higher fill factor, and higher optical dynamic range as compared with the active pixel sensor (APS) and the conventional passive pixel sensor (PPS). Thus the proposed OPAPS structure has high potential for the applications of high-quality and large-array-size CMOS imagers.

Finally, the main results and conclusions of this thesis are summarized in Chapter 6. Some suggestions for the future works about the implementations of photodiode structure, pixel circuits, and readout circuits are also addressed in this chapter.

Fig. 1.1 The rate of pixel size decrease in CMOS imagers.

# REVIEW OF PHOTODETECTORS, PIXEL CIRCUITS, AND READOUT CIRCUITS IN CMOS IMAGE SENSORS

#### 2.1 INTRODUCTION

In this chapter, the photodetectors and pixel circuits in CMOS image sensors are reviewed and discussed. The photodetectors for use in CMOS imaging systems are described in Section 2.2. In Section 2.3, the overall architectures and operational requirements of CMOS image sensors are discussed. In Section 2.4, the pixel circuits in CMOS image sensors are reviewed including the state-of-the-art structures. Finally, a summary is given in Section 2.5.

#### 2.2 PHOTODETECTORS CMOS IMAGING SYSTEMS

In Imaging systems, a pixel array transduces light to an electrical quantity (charge, current, or voltage) over a two-dimensional scene. Nearly all visible-light solit-state imagers are based on the principle of carrier photogeneration. Photons entering a semiconductor generate electron-hole pairs if the photon energy exceeds the bandgap energy. An electric field separates the holes and electrons typically and then they are collected in a potential well and the holes are discarded. The major differences between imager types are related to how the electrons are converted to an output signal and how the array is scanned out.

Considerable researches have been devoted to use silicon as a material for photodetection. The interest in silicon for such applications derives almost from its dominant position in the semiconductor industry, where its properties are well understood and its manufacturing processes well established. Furthermore, because of its relatively large bandgap, silicon has low leakage current at room temperature.

In the electromagnetic spectrum [38], visible light is one of many subsets of electromagnetic radiation that also include radio waves, microwave, infrared radiation, X-rays, and γ-rays. The different forms of radiations are distinguished by their wavelengths, which for visible light ranges from about 0.4 μm (violet) to about 0.8 μm (red). A variety of interactions can be occurred between visible light photons and silicon [39]. Some of these interactions result in the conversion of photons into electrical charges, while others convert impinging photons into entity without electronic charges and other photons.

Photodetectors is a very important component in OEIC (OptoElectronic integrated Circuit) [40]. The possible applications range from artificial retina (neuro-vision), pattern recognition, alert and control [41], CCD/CMOS imager [42]-[45], and front end receiver in optical communication [46], [47]. There are many kinds of photodetectors available, and each of them has its own merits and weaknesses for a given applications.

There are several commonly used photodetectors in CMOS imaging systems, namely, charge injection device (CID) [48], static induction transistor (SIT) [49], [50], base-store image sensor (BASIS) [51], and floating gate array device (FGA) [52]-[54]. Moreover, two most commonly used structures of photodetector, namely, photogate (PG) [22], [55]-[57] and photodiode (PD) [58]-[61], are often used in CMOS imagers. Some comparisons among these photodetectors in CMOS imagers are summarized in Table 2.1. As can be shown in Table 2.1, photodiode is chosen as the photodetector in

this thesis due to its good compatible with CMOS technology, high quantum efficiency, small pixel size, and random access. The medium fill factor can be improved by using microlens. In addition, the influence of noise can be improved by careful design of readout circuit.

There are many photodiode structures such as pinned photodiode [62], hole-accumulated photodiode [63], mixed P/N+ and P/N-well photodiode [64], and hollow photodiode [65]. The pinned photodiodes have small dark current, but the complex process may reduce yield and increase cost. It includes two junctions optimized independently of CMOS devices to improve the spectral response. Due to the same principle of the pinned photodiode and the distance of the sensor junction from the isolation region (LOCOS or STI region), the hole-accumulated photodiode structure has low dark current. It requires the same complex process as the pinned photodiode. The mixed P/N+ and P/N-well photodiode can absorb photons for light of short and long wavelengths by using P/N+ and P/N-well junctions, respectively. However, the structure is not scalable due to the large N-well width and space. The spectral response and quantum efficiency of the hollow photodiode are improved because of its extended depletion region. Controlling the uniformity of the hollow photodiode array is difficult due to the hollow shape of the photodiode.

## 2.3 OVERALL ARCHITECTURES AND OPERATIONAL REQUIREMENTS OF CMOS IMAGE SENSORS

#### 2.3.1 Overall Architectures

The overall architecture of a CMOS image sensor is shown in Fig. 2.1. The image sensor consists of an array of pixels that are typically selected a row at a time

by row select logic. This can be either a shift register or a decoder. The pixels are readout to vertical column busses that connect the selected row of pixels to a bank of analog readout circuits. These analog readout circuits perform functions such as charge integration, gain, sample and hold, correlated double sampling (CDS), and noise reduction.

More advanced CMOS image sensors contain on-chip ADC. The ADC can be column-parallel ADCs; that is, each column of pixels has its own ADC or a single ADC; that is, a single ADC is used in the overall CMOS imager sensor. The digital output of the ADC is readout to perform the off-chip digital signal processing. A timing and control logic block is also integrated on the same chip.

The CMOS image sensor architecture of Fig. 2.1 permits several modes of image readout. Progressive-scan readout of the entire array is the common readout mode. A window readout mode is implemented where only a smaller region of pixels is selected for readout. This increases access rates to windows of interest. A skip readout mode is also possible where every second (or third, etc.) pixel is readout, This mode allows for downsampling of the image to increase readout speed at the cost of resolution. Combinations of skip and window modes allow electronic pan, tilt, and room to be implemented.

#### 2.3.2 Operational Requirements of CMOS Image Sensors

In different applications of CMOS imaging systems, there exist certain specific requirements for the design of CMOS image sensors. In general, the requirements involve quantum efficiency, conversion gain, saturation level, image lag, smear, crosstalk, anti-blooming, noise, dynamic range, readout rate, array size, and pixel pitch. Some general discussions of these requirements are summarized below.

- 1) Quantum Efficiency: Quantum efficiency is the probability that a photon incident on the pixel creates a hole or electron that is collected in the pixel's potential well. Quantum efficiency depends on several parameters, including the reflection coefficient of the optical stack on the pixel, the fraction of the pixel area which is light-shielded, the fraction of the pixel area where photocharge goes elsewhere than the photosite, the photon wavelength, the bulk and surface carrier lifetimes, the depth of the potential well, and the volume and shape of the depletion regions. It is useful to think of quantum efficiency as the product of optical aperture, which is the fraction of pixel area which is optically active, optical stack transmission, which is the fraction of photons incident on optically active areas which reach the silicon surface, and collection efficiency, which is the fraction of photogenerated electrons that get collected.

- 2) Conversion Gain: The image data starts as charge and is usually converted to voltage. For an imager with a linear charge-to-voltage characteristic, the ratio of output signal to collected charge is a constant, referred to as the conversion gain. It is usually expressed in units of  $\mu V/e^-$  and is equal to the reciprocal of the charge sense capacitance, times any system gain.

- 3) Saturation Level: Pixel saturation occurs when the pixel stores the maximum amount of charge. If more charge is added, it simply spills into the substrate or adjacent pixels. It is usually expressed in terms of electrons, although it is sometimes referred to the output as a voltage. It can also be stated in terms of illumination required to produce the saturation charge. Depending on design, the output circuit can saturate before the pixel saturates. In this case, the saturation level is set by the output circuit.

- 4) *Image Lag*: Image lag refers to the persistence of one frame in successive frames. An imager demonstrates lag when, for example, a strong light is suddenly

turned off but the imager output does not immediately return to the black level. Lag is usually caused by incomplete charge reset. It is informally characterized by whether or not it is visible on a video display.

- 5) Smear: In a CMOS imager, a charge packet passing by a region of high illumination accumulates additional charge due to optical crosstalk, creating vertical stripes in the reconstructed image. A column line can easily collect stray charge from a highly illuminated pixel, corrupting the readout of all pixels in that column.

- 6) Crosstalk: Crosstalk is any contamination of one pixel's signal by another pixel's signal. Smear is an example of optical crosstalk. Examples of electrical crosstalk include ground bounce and capacitive coupling.

- 7) Anti-Blooming: Blooming is the spread of charge from saturated pixels into surrounding potential wells. It differs from optical crosstalk in that all photogenerated charge, not just a small fraction, spreads out into the surrounding pixels/shift registers. Most pixels contain some means for shunting excess charge to a drain in order to preserve the information in nearby non-saturated pixels. Anti-blooming characterizes the effectiveness of the technique used to drain excess charge. It is expressed as the ratio of the illumination required to produce blooming to the illumination required to saturate the pixel.

- 8) Noise: Noise in the imager sensor can be separated typically into two categories, random noise and pattern noise. Random noise varied temporally and is not constant from frame to frame in the imager. Pattern noise is divided into two components, one is fixed pattern noise (FPN) and the other is the photo-response nonuniformity (PRNU). The FPN comes from dimensions, doping concentration, and contamination of photo-detectors and the characteristics of threshold voltage, width, and length in MOSFETS. The PRNU noise comes from the thickness of layers on the top of photo-detectors and wavelength of illumination. These noise in the CMOS

imager sensor are briefly discussed below.

#### (i) Random Noise

An imager with a constant scene should produce identical output from frame to frame. In practice, the output from a given pixel will vary over time due to thermal noise, charge trapping, and 1/f noise in the devices which comprise the imager. Photonic shot noise is usually not included in this quantity, although this also contributes to noise at the output. Random noise is typically stated in terms of input-referred equivalent electrons, i.e., the root mean square (rms) output voltage noise divided by the conversion gain.

#### (ii) Fixed-Pattern Noise

Fixed-pattern noise (FPN) is the fixed (constant in time) variation between pixel outputs under spatially uniform illumination. Fixed-pattern noise is typically due to random or mask-induced mismatches in device parameters such as threshold voltage, trap density, and parasitic capacitance. FPN is usually a function of illumination, and can be written as the sum of a gain term and an offset term for an imager with a linear response characteristic. Offset FPN is constant over illumination, and gain FPN is proportional to illumination.

FPN consists of components that describe variation between columns, and variation between pixels in a single column. Column FPN is the standard deviation of the column-average pixel output values in a time-average, uniformly illuminated frame. The column FPN is expressed

as

FPN (column) =

$$\sqrt{\frac{\sum_{j} (\overline{P}_{j} - \overline{P})^{2}}{j-1}}$$

(2.1)

where  $\overline{P}_j$  is the average pixel value in column j and  $\overline{P}$  is the average pixel value in the frame. Since a column FPN calculation requires multiple columns, j>1. Pixel FPN is the standard deviation of pixel output values after column FPN has been removed. In order to calculate pixel FPN, multiple pixels are required. The pixel FPN is expressed as

FPN (pixel) =

$$\sqrt{\frac{\sum_{i,j} (\overline{P}_{i,j} - \overline{P}_{j})^{2}}{i \bullet j - 1}}$$

(2.2)

where  $i \bullet j > 1$ .

#### (iii) Reset Noise

If the diffusion of the photodiode is reset through a MOSFET, this is equivalent to a capacitance being charged through the resistance of the MOSFET channel. The rms (root-mean-square) noise voltage can be expressed as

$$\langle V_{\rm rms} \rangle = \sqrt{\frac{kT}{C}}$$

(2.3)

where k is the Boltzmann constant, T is temperature, and C is the capacitance of photodiode. The reset noise is generally called "KTC" noise. KTC noise can only be canceled by using the photogate-type active pixel sensor (APS). Currently, reset noise limits the read noise in photodiode-type APS [22].

#### (iv) Thermal Noise

Thermal noise is a white noise which means the noise power is constant over all frequencies. For a resistor, the thermal noise rms voltage can be expressed as

$$\langle V_{rms} \rangle = \sqrt{4kTBR}$$

(2.4)

where B is the noise bandwidth and R is the resistor. Since the thermal noise covers the entire frequency range, the bandwidth determines the actual amount measured.

#### (v) Shot Noise

Shot noise is another white noise that arises from the discrete nature of the electrons, for example, the random arrival of particles of charge. This is the result of the random generation of carriers such as thermal generation within a depletion region (i.e. shot noise of dark current) or the random generation of photon-electrons.

#### (vi) Flicker (1/f) Noise

The flicker noise occurs at any junction, including metal-to-metal, metal-to-semiconductor, semiconductor-to-semiconductor, and conductivity fluctuations. The flicker noise arises mainly in amplifier circuits where there are numerous such contacts. At low frequency, flicker noise can be the dominant component, but it drops below thermal noise at higher frequency.

- 9) Dynamic Range: The dynamic range is defined as the ratio of maximum charge capacity to noise floor. The required dynamic range of CMOS imagers is determined by the ratio of the brightest signal level to the weakest. Larger dynamic range is preferred but limited by storage capacitance, linearity, and noise level.

- 10) Readout Rate: The readout rate is chosen according to the specific imaging system requirements and limited by the allowable chip power dissipation as well as the circuit operation speed. Usually a higher readout rate is needed for multiple sampling applications in image compensation function. Higher readout rate is also

needed to avoid the saturation of the signal after integration.

11) Array Size and Pixel Pitch: Higher image resolution requires larger array size and smaller pixel pitch. However, a larger pixel size is needed to increase the fill factor, photo-senstivity, and dynamic range. Thus the optimal design trade-off should be made between the application flexibility and resolution performance.

It is important to determine the operational requirements in the design of CMOS imager for specific applications. A complete analysis of operational parameters like noise, spectral response, sensitivity, and resolution should be set before the design trade-off. Therefore, all the operational requirements discussed above have unique optimized orientations for CMOS imagers in different applications.

### 2.4 PIXEL CIRCUITS OF CMOS IMAGE SENSORS

In the development of CMOS imagers, the pixel circuit is the second major part next to the photodetectors. Pixel circuit is designed to support a good interface between photodetectors and the following signal processing stage. Different pixel circuit techniques have been developed for CMOS imagers with different applications.

Generally, the pixel pitch of CMOS imagers is reduced with the increasing array size and resolution. Moreover, the total power and noise of pixels are limited by the imaging system. These three major factors often put constraints on pixel circuit design space and complexity. Thus the design of pixel circuits requires a trade-off between circuit performance and complexity.

Some conventional pixel circuits such as passive pixel circuit [66], [67], active pixel circuit [68]-[74], and logarithmic pixel circuit [22] are still commonly used in CMOS imagers. More complex pixel circuits have been developed to provide

excellent bias control, high injection efficiency, high linearity, and low noise performance based on these conventional pixel circuits. In the following, these conventional pixel circuits used in CMOS imagers will be reviewed. The noise performance and dynamic range of these pixel circuits are also discussed.

#### 2.4.1 Passive Pixel Circuit [66], [67]

The photodiode-type passive pixel circuit consists of one photodiode PD and a pass transistor Mpt as shown in Fig. 2.2. When the pass transistor Mpt is on, the photodiode is connected to a column bus. A charge integrating amplifier (CIA) readout circuit at the bottom of the column bus keeps the voltage on the column bus constant and reduces KTC noise [68]. When the photodiode is accessed, the voltage on the photodiode is reset to the column bus voltage, and the charge proportional to the photosignal, is converted to a voltage by the CIA. This single-transistor pixel circuit allows the highest fill factor for a particular CMOS process. The quantum efficiency of the passive pixel can be quite high due to the large fill factor.

The disadvantages of the passive pixel circuit are its readout noise level and scalability. Readout noise of a passive pixel is typically of the order of 250 electrons r.m.s. [22]. The passive pixel also does not scale well to larger array sizes and faster pixel readout rates. This is because increased bus capacitance and faster readout speed both result in higher readout noise.

#### **2.4.2** Active Pixel Circuit [68]-[74]

After the invention of passive pixel circuit, the insertion of a buffer or an amplifier into the pixel can potentially improve the performance of pixel. A sensor

with an active amplifier within each pixel is referred as an active pixel sensor (APS). Each amplifier is only activated during readout, so power dissipation can be kept low. The photodiode-type APS consists of one photodiode and three transistor as shown in Fig. 2.3. The CMOS APS trades pixel fill factor for improved performance compared to passive pixels. Microlenses are commonly used to compensate the loss in optical signal [75], [76].

The read noise of photodiode-type APS pixel is limited by the reset noise on the photodiode, and is thus typically 75-100 electrons r.m.s [22]. The reset noise scales as  $1/C^{1/2}$  [22], where C is the photodiode capacitance. A trade-off can be made in pixel fill factor, dynamic range, and conversion gain. The photodiode APS is suitable for most mid to low performance applications.

#### 2.4.3 Logarithmic Pixel Circuit [22]

In some cases, nonlinear output of the sensor is required [77]-[81]. The logarithmic pixel circuit is shown in Fig. 2.4. As shown in Fig. 2.4, the photodiode voltage self-adjusts to a level such that the load transistor current is equal to the photocurrent collected by the photodiode. This results in a logarithmic transformation of the photosignal for typical light levels and wide dynamic range. The disadvantages of this logarithmic approach are slow response time due to low light levels, large fixed pattern noise (FPN), and small signal-to-noise ratio (SNR) due to FPN, temporal noise, and small voltage swings [22].

#### 2.5 READOUT CIRCUITS OF CMOS IMAGE SENSORS

#### 2.5.1 Double Delta Sampling (DDS) Circuit [99]

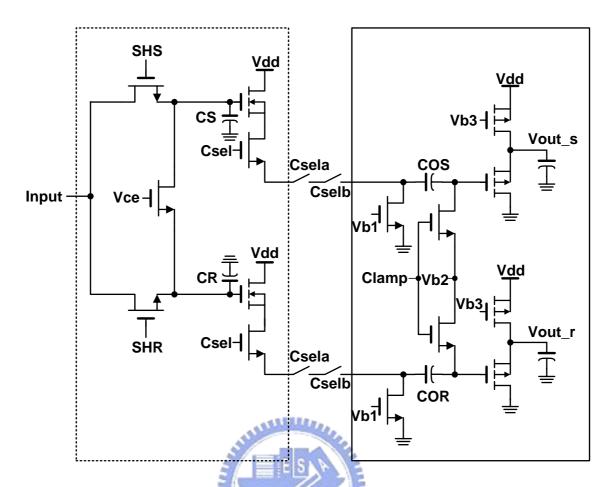

The most commonly used readout circuit in CMOS imagers is double delta sampling (DDS) circuit [99] as shown in Fig. 2.5. The DDS circuit is composed of column sampling circuit and output correlated double sampling circuit. The two branches in column sampling circuit are used to store the reset and signal voltage. Each branch consists of a sample and hold capacitor (CS or CR) with a sampling switch (SHS or SHR) and the first source follower with a column-selection switch (csel). The clamp switches, the coupling capacitors (COS and COR), and the output drivers are common to an entire column of pixels. The load transistors of the first set of source follower and the subsequent clamp circuits and output source followers are common to the entire array. The DDS circuit can be used to suppress fixed pattern noise (FPN) and clock feedthrough noise. The disadvantages of DDS circuit is the high noise due to channel charge injection.

#### 2.6 SUMMARY

In this chapter, the photodetectors and pixel circuits in CMOS image sensors are reviewed and discussed. All the structures and circuits discussed above have their uniqueness and features for different applications. Based on the developments of photodetectors and the fast advancement of CMOS technologies, high-performance and low-cost CMOS imagers will be developed through the inventions of new photodiode structures and pixel circuits. This will be driven by rapid developments and wide applications of multimedia systems. In the following chapters, the advanced developments of photodiode structures and pixel circuits are proposed. Under our work in this thesis, a new generation of CMOS imaging systems is highly expected.

Table 2.1 Comparisons of characteristics among photodetectors in CMOS imagers

| DEVICE<br>PARAMETERS | CID    | SIT    | BASIS  | FGA    | PG     | PD     |

|----------------------|--------|--------|--------|--------|--------|--------|

| CMOS Compatible      | Poor   | Medium | Medium | Medium | Medium | Good   |

| Fill Factor          | High   | Medium | Medium | High   | Medium | Medium |

| Quantum Efficiency   | Medium | Medium | Medium | Low    | Medium | High   |

| Noise                | Large  | Medium | Medium | Medium | Small  | Medium |

| Pixel Size           | Small  | Medium | Medium | Small  | Medium | Small  |

| Random Access        | Yes    | Yes    | Yes    | Yes    | Yes    | Yes    |

Fig. 2.1 The overall architecture of a CMOS image sensor.

Fig. 2.2 Passive pixel circuit.

Fig. 2.3 Active pixel circuit.

Vdd

Vdd

PD

Rsel

Column

Bus

Fig. 2.4 Logarithmic pixel circuit.

Fig. 2.5 Double delta sampling (DDS) circuit.

#### **CHAPTER 3**

# DESIGN, OPTIMIZATION, AND PERFORMANCE ANALYSIS OF NEW PHOTODIODE STRUCTURES FOR CMOS ACTIVE-PIXEL-SENSOR (APS) IMAGER APPLICATIONS

#### 3.1 INTRODUCTION

To achieve the performance requirements of CMOS imagers, one of the key elements is the photodiode array in which the photodiodes should be designed and optimized carefully. The two critical parameters in the design of photodiodes for imager applications are the dark current and the spectral response. Large dark current in the photodiode array of CMOS imagers can lead to non-uniformity, low scalability, and reduced dynamic range. The first source of dark current depends on doping concentrations, bandgap, and temperature of the reverse-biased photodiode [82]. The second source is the defect-generated dark current determined by the shape of photodiode layout, the cross-sectional structure of the photodiode, and the fill factor [82]. The shape of photodiode layout can be designed to reduce the dark current [82]. Generally, the second source of dark current is mainly generated from the pn junction depletion region under bird's beak in LOCOS process [83] or in the interface isolation of STI (shallow trench isolation) as well as the surface damage caused by the implantation of high doping concentration.

The spectral response is another important parameter considered in the design of

photodiodes. The high spectral response of photodiodes can be generated by using shallow and deep depth of the pn junctions to absorb photons for light of short and long wavelengths, respectively.

It is the aim of this chapter to propose two new photodiode structures with low dark current and high spectral response. The pn junction of p-substrate and the lightly-doped sensor implant SN- is used as a photodiode in both structures. The regions of bird's beak in the two proposed structures are completely embraced by the SN- implant and the p-field implant, thus not located in the pn junction depletion region. Both pn junction depletion located under the bird's beak and surface damage due to high doping concentration can be avoided and the generation of dark current can be suppressed. Furthermore, the use of shallow and deep pn junctions can increase the photo-sensitivity for light of short and long wavelengths, respectively. Thus the spectral response can be improved. Systematic comparisons on measurement results of dark currents and spectral responses among the proposed photodiode structures and other structures in CMOS technology with reasonable process modifications are presented. From the experimental results, it has been verified that the two proposed structures in the 5 µm x 5 µm APS cell of the CMOS imager have low dark currents of 30.6 mV/sec and 35.2 mV/sec at the reverse-biased voltage of 2 V as well as good spectral response.

The rest of this chapter is organized as follows. In Section 3.2, two new CMOS photodiode structures in 0.35 µm 1P3M 3.3 V CMOS technology with salicide process are described. Principles of reducing the dark current and improving the spectral response are also presented. Other photodiode structures for comparison purpose are also described. In Section 3.3, the layout consideration and optimization for the proposed photodiode structures and other structures for comparisons are described. In Section 3.4, experimental results of dark current and spectral responses

of the fabricated photodiodes are presented, analyzed, and compared to verify the advantageous performance of the proposed new photodiode structures. Summary are finally made in Section 3.5.

#### 3.2 ANALYSIS OF NEW CMOS PHOTODIODE STRUCTURES

Generally, it is difficult to accurately characterize and predict both dark current and spectral response of a pn-junction photodiode by using model equations. In this work, based on the analysis on the mechanisms for dark currents and spectral responses as well as the understanding of process technology, we proposed and designed two photodiode structures for low dark current and/or high spectral response. Several other structures were also designed. Through extensive experimental measurements on dark currents and spectral responses of all fabricated photodiode structure, the mechanism can be verified and the optimal structure can be confirmed.

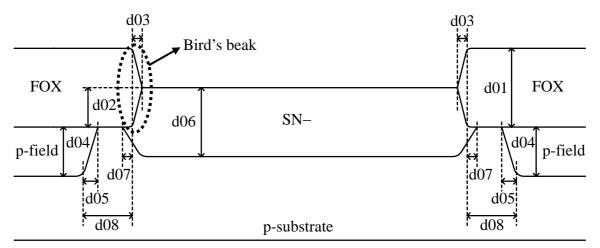

The cross-sectional views of the two proposed photodiode structures called Type P1 and Type P2 with the explanations of all dimension notations are shown in Figs. 3.1(a) and 3.1(b), respectively. The modified 0.35 µm single-poly-triple-metal (1P3M) CMOS process with a lightly-doped p-substrate and LOCOS structure is adopted to realize the two new structures. All the layers and their functions in the design of CMOS imager are summarized in Table 3.1. The p-well is defined by a mask that differs from the complement of the n-well mask in this modified CMOS process. The p-field implant is defined by another mask and is completed before the use of the mask defined by the thin oxide. Following the growth of SiO2 and SiN on the region defined by the thin oxide, the thick field oxide (FOX) is grown in areas where SiN is absent. Field oxide is grown in both vertical and lateral directions. The growth in the lateral direction results in the bird's beak. This technique of field oxide growth is so

called LOCOS (local oxidation of silicon). The planarization technique used to etch the field oxide to its final thickness is then completed. The regions of the p-field implant below the field oxide are pushed downward during the growth of the field oxide. The cross-sectional views of the bird's beak, FOX, and the p-field implant are shown in Figs. 3.1(a) and 3.1(b).

In the photodiode structures, all significant dimensions are mentioned in notations. These dimensions depend on different CMOS fabrication technologies, fabrication equipments, and different fabs. The real values for these dimensions should be carefully optimized for a certain technology or fabrication fab.

In the structure of the Type P1 photodiode, all regions of the thin oxide are implanted by the lightly-doped sensor implant SN- as shown in Fig. 3.1(a). Thus the pn junction of p-substrate and SN- is used as the photodiode. The length of d06 is longer than that of d02, so regions of the bird's beak are completely embraced by SN-.

Since the bird's-beak region has a high density of defects due to the high silicon/SiO2 stress, the dark current will be increased significantly if the depletion region of the pn junction photodiode is located in the bird's-beak region. In the Type P1 structure, the regions of bird's beak are not located in the depletion region of the pn junction photodiode formed by the p-field implant and SN- if the following equation is adopted.

$$d08 > d05 + d07 + \Delta d05 + \Delta d07 \tag{3.1}$$

where  $\Delta d05$  and  $\Delta d07$  represent the mask misalignments of the p-field implant and SN-, respectively. Thus the dark current that results from the bird's beak can be completely avoided in the Type P1 structure. Under these conditions, the depletion region of a photodiode is not located in the bird's-beak region. Too large d08 will decrease the fill factor. If d08 is equal to or smaller than the sum of d05 and d07, then

the depletion region of the p-field/SN- junction will be in the bird's-beak region to increase the dark current.

The dark current of the photodiode is also increased due to the surface damage generated by the sensor implant. The higher doping concentration of the sensor implant will result in greater surface damage causing larger dark current. The surface damage in the Type P1 structure is low due to the low doping concentration of SN–. This further decreases the dark current in P1.

In the Type P1 structure, p-well is replaced by p-substrate in the formation of the pn junction. Thus the depletion region of the photodiode becomes wider to absorb more photons due to the lower doping concentration of p-substrate than that of p-well. In the Type P1 structure, the depletion region of the p-substrate/SN- junction photodiode at the bottom plate is deep enough to absorb long wavelength photons. Thus the photo-sensitivity for the light of long wavelength can be improved. The depletion region of p-substrate and the side diffusion of SN- below FOX is effective in the absorption of short wavelength photons because this part of pn junction is shallow enough to absorb photons for the light of short wavelength. Absorption of photons is not affected by FOX because FOX is transparent.

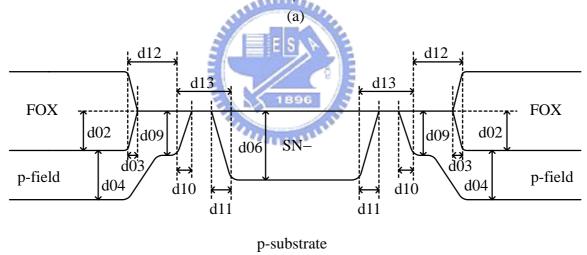

In the Type P2 structure, the pn junction of p-substrate and SN- is used as a photodiode where SN- has the same doping concentration as in the Type P1 structure. In the Type P2, only the central part of thin-oxide region is implanted by SN- as shown in Fig. 3.1(b). The mask of SN- is defined inside the regions of thin oxide. The length of d09 is slightly larger than that of d04 because the regions of p-field implant below the thin oxide are not pushed out by the field oxide during its growth. The length of d09 is larger than that of d02. In the Type P2, the regions of bird's beak are completely embraced by the p-field implant.

The regions of bird's beak in the Type P2 structure are not located in the

depletion region of pn junction photodiode formed by the p-field implant and SN- if the following two equations are adopted.

$$d03 < d10 + d12 + \Delta d10 \tag{3.2}$$

$$d13 > d10 + d11 + \Delta d10 + \Delta d11 \tag{3.3}$$

where  $\Delta d10$  and  $\Delta d11$  represent the mask misalignments of the p-field implant and SN-, respectively. If the sum of d10 and d12 is designed to be much larger than the length of d03, then the length of d13 can be designed to be shorter than the sum of d10 and d11. In this case, the p-field implant and SN- will be in contact together but the regions of bird's beak will not be located in the depletion region of p-field/SN-junction because the doping concentration of p-field implant is higher than that of SN-. However, the fill factor is small in this case. If the sum of d10 and d12 is designed to be shorter than the length of d03, then the length of d13 must be designed to be much longer than the sum of d10 and d11 to prevent the regions of bird's beak from being located in the depletion region of p-substrate/SN- junction. The fill factor is also small in this case.

The sum of d10 and d12 is designed to be slightly longer than the length of d03 and the length of d13 is designed to be slightly longer than the sum of d10 and d11 to protect the regions of bird's beak from being located in the depletion region of pn junction and keep the fill factor as large as possible. The regions of bird's beak in this optimal design are completely embraced by the p-field implant and are not located in the depletion region of p-field/SN– junction. Thus dark current from the bird's beak can be completely avoided in P2. The surface damage is also kept low in P2 due to the low doping concentration of both p-field implant and SN–.

In the performance of photo-sensitivity, the depletion region of the p-substrate/SN- junction at the bottom plate is deep enough and is therefore used to absorb photons for the light of long wavelength. Moreover, the depletion region of the

pn junction formed by the p-substrate and the side diffusion of SN- is used to absorb photons for the light of short wavelength.

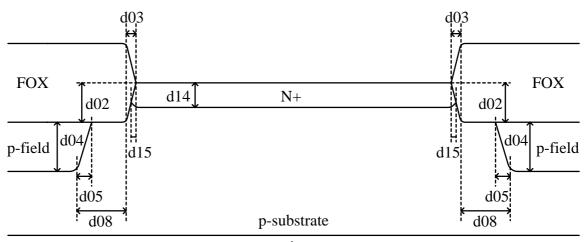

Four structures, C1, C2, C3, and C4 with the explanations of all dimension notations shown in Figs. 3.2(a), 3.2(b), 3.2(c), and 3.2(d), respectively, are analyzed to compare their performance with that of the two proposed new photodiode structures. In Fig. 3.2(a), the p-substrate and N+ implant are used as the pn junction photodiode. This structure is the same as Type P1 except that SN- is replaced by N+. Type C1 is the conventional photodiode structure used in the standard CMOS process. However, the bird's beak cannot be embraced completely by N+ because the length of d14 is shorter than that of d02. Thus, some bird's-beak regions are located in the depletion region of the p-substrate/N+ junction. In the performance of photo-sensitivity, the shallow p-substrate/N+ junction at the bottom plate can be used to absorb photons for light of short wavelength.

In Fig. 3.2(b), the p-substrate and the SN+ implant are used as the pn junction photodiode. SN+ is an extra sensor implant used in the modified CMOS process. The photodiode structure of Type C2 is the same as that of Type P1 except SN- is replaced by SN+. The length of d16 is shorter than that of d02, so SN+ still cannot be used to embrace completely the regions of bird's beak. Thus some bird's-beak regions are located in the depletion region of the p-substrate/SN+ junction. In the performance of photo-sensitivity, the shallow p-substrate/SN+ junction at the bottom plate can be used to absorb photons for light of short wavelength.

In Fig. 3.2(c), the p-substrate and SN+ are used as the pn junction photodiode. The photodiode structure of Type C3 is the same as that of Type P2 except that SN- is replaced by SN+. The bird's beak will be located in the depletion region of the p-field/SN+ junction if the length of d19 is equal to that of d13 in Fig. 3.1(b) because the doping concentration of SN+ is larger than that of the p-field implant. The

depletion region of the pn junction photodiode formed by the p-substrate and the side diffusion of SN+ can be used to absorb photons for light of short wavelength. Moreover, the shallow p-substrate/SN+ junction at the bottom plate can also be used to absorb photons for light of short wavelength.

In Fig. 3.2(d), the p-substrate and SN- are used as the pn junction photodiode. The photodiode structure of Type C4 is the same as that of Type P2 except that both P+ and p-field implant are used to embrace the bird's beak. The distance between the two edges of the P+ mask and the p-field mask is equal to zero. The regions of bird's beak are completely embraced by both of P+ and p-field implant if the lengths of d24 and d25 are equal to that of d12 and d13, respectively. The photo-sensitivity of Type C4 is the same as that of Type P2.

## 3.3 LAYOUT OPTIMIZATION OF NEW PHOTODIODE STRUCTURES IN APS CELLS

The circuit diagram of APS cell is shown in Fig. 3.3(a) where the NMOSFET of MR is used to reset the voltage of the photodiode. The two NMOSFETs of M1 and M2 are used as source follower and row selector, respectively. The layouts of the two proposed new photodiode structures applied to the 5 µm x 5 µm active-pixel-sensor (APS) cell are shown in Figs. 3.4(a) and 3.4(b), respectively. To show the layout of APS cell clearly, only masks of the thin oxide, poly, metal1, p-field block (pfb), N+ block (NB), SN-, P+ and contact are drawn in Figs. 3.4(a) and 3.4(b). Routing and interconnections of the APS cell are not shown in the layout diagrams. The placement of the three NMOSFETs is also shown in Figs. 3.4(a) and 3.4(b). The region of the p-field implant is defined outside the mask of pfb. The region of N+ is defined outside the mask of NB.