## 國立交通大學

# 光電工程研究所 碩士論文

高效能非晶系銦鎵鋅氧雙極性有機薄膜電晶體

High Performance Amorphous InGaZnO<sub>4</sub>/Organic Ambipolar Thin Film Transistors

研究生:朱益興

指導教授:謝漢萍 教授

中華民國九十八年六月

#### 高效能非晶系銦鎵鋅氧雙極性有機薄膜電晶體

## High Performance Amorphous InGaZnO<sub>4</sub>/Organic Ambipolar Thin Film Transistors

研究生:朱益興 Student:Yi-Hsing Chu

指導教授:謝漢萍 Advisor:Han-Ping D. Shieh

國立交通大學 電機學院

光電工程研究所

碩士論文

A Thesis

Submitted to Institute of Electro-Optical Engineering

College of Electrical and Computer Engineering

National Chiao Tung University

in Partial Fulfillment of the Requirements

for the Degree of Master

in

Electro-Optical Engineering

June 2009

Hsinchu, Taiwan, Republic of China

中華民國九十八年六月

#### 高效能非晶系銦鎵鋅氧雙極性有機薄膜電晶體

學生:朱益興 指導教授:謝漢萍

#### 國立交通大學光電工程研究所

## 摘ESA

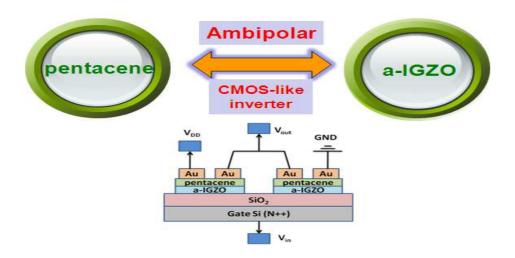

在矽基板上,運用了兩種主動層材料 pentacene / a-IGZO 做成的雙極性薄膜電晶體,可以在大氣環境下有穩定的特性展現。Pentacene 在雙極性薄膜電晶體中扮演著電洞傳輸的角色,相對的 a-IGZO 則是提供了電子傳輸。許多傳統的電子傳輸材料,在空氣中都會有不穩定的效果,必須藉由覆蓋一層修飾層來達到在空氣中量測的目的,但是 a-IGZO 卻可以直接在大氣環境下有穩定的特性。而且其具有透明的新穎性,遠高於非晶矽的載子遷移率等較佳電性,還同時保留了非晶系材料的高均勻性優點。而低製程溫度的需求更進一步的揭示使用便宜的玻璃基板,塑膠基板的可行性,也暗示著軟性電子的應用。成功結合 pentacene/a-IGZO 兩種半導體材料製作成雙極性薄膜電晶體(ambipolar TFTs),製作成 CMOS-like inverter circuit可應用並簡化顯示器上之驅動電路。且其在第一象限有高達70的電壓增益,亦可工作在第三象限。

High Performance Amorphous InGaZnO<sub>4</sub>/Organic **Ambipolar Thin Film Transistors**

**Student: Yi-Hsing Chu**

Advisor : Dr. Han-Ping D. Shieh

**Institute of Electro-Optical Engineering National Chiao Tung University**

**ABSTRACT**

Air-stable ambipolar thin-film transistors (TFTs) based on double active

layer of pentacene / a-IGZO (amorphous In<sub>2</sub>O<sub>3</sub>-Ga<sub>2</sub>O<sub>3</sub>-ZnO) have been

examined on SiO<sub>2</sub> /p-Si substrates. The a-IGZO exhibits n-channel behavior,

while pentacene presents p-channel characteristics. Most n-type organic

materials are easily affected by moisture and oxygen, thus measuring ambipolar

devices in ambience air is difficult. However, a-IGZO not only has outstanding

mobility but also has good stability while being measured in ambient air. In our

work, a CMOS-like inverter was constructed using two identical ambipolar

transistors and the voltage gain up to 70 was obtained. CMOS-like inverter

circuit was made to demonstrate the possibility for display applications. The

inverter can be operated in both the first and the third quadrants, simplifying

circuit design for active matrix flat panel display applications.

-ii-

#### 誌謝

首先,誠摯地感謝指導教授謝漢萍院長在我兩年的碩士班生涯中給予許多教誨、關懷與鼓勵。實驗室提供了良好的設備及實驗環境讓我們可以專心在研究上。此外實驗室注重英文能力等精神也讓我們培養國際化的視野,成為更全方位的人才。另一方面也感謝黃乙白教授的照顧,除了在研究方面對我們提供意見之外,平時也貼近同學,扮演著亦師亦友的角色,適時的給予照顧及關心。

兩年的碩士生活,感謝喬舜學長在實驗上的指導與照顧,常常為我解答一些實驗上的問題,給予我不同的思考方向。使我的研究能夠往正確的方向邁進。最感謝的人莫過於我的實驗夥伴-高銘,在漫長實驗中培養出來的默契和革命情感是無法用紙筆和言語形容,可以一起分擔實驗的壓力、可以一起分享實驗的成果,那種榮辱與共的精神,我想我一輩子都會記得,我曾經有個共患難的好兄弟。

最後,我要感謝我的家人,在我求學過程中給予我的支持跟鼓勵是我最大的支柱。家是永遠的的避風港,當遇到低潮時,總會在第一時間給予溫暖的關懷。在這兩年中,感謝所有幫助我的人,謝謝你們。因為有了你們當初的幫助,才能造就如今的我。

#### **Table of Content**

| Abstract (Chinese) | i    |

|--------------------|------|

| Abstract (English) | ii   |

| Acknowledgements   | iii  |

| Table of Content   | iv   |

| Figure Caption     | viii |

| List of Tables     |      |

| Chapter 1. Introduction                           | 1     |

|---------------------------------------------------|-------|

| 1.1. Ambipolar Thin Film Transistors              | 1     |

| 1.1.1 Introduction to Ambipolar Thin Film Transis | tors1 |

| 1.1.2 Issues of Ambipolar Thin FilmTransistors    | 3     |

| 1.2. Complementary-Metal-Oxide-Semiconductor Inve | rter4 |

| 1.3. Amorphous IGZO Thin Film Transistors         | 7     |

| 1.3.1 Introduction to Amorphous Oxide Semiconduc  | tor7  |

| 1.3.2 Introduction of a-IGZO                      | 9     |

| 1.4. Overview of Organic Thin Film Transistor     | 10    |

| 1.4.1 Introduction to OTFT                        | 10    |

| 1.4.2 Organic Materials- Pentacene                | 11    |

| 1.5. Motivation and Objective                     | 12    |

| 1.6. Organization of Thesis                       | 13    |

|                                                   |       |

| Chapter 2. Principles and Theories                | 14    |

| 2.1 Important Parameters of TFTs                  | 14    |

| 2.1.1 Mobility                                    | 14    |

| 2.1.2 Threshold Voltage                           | 16    |

| 2.1.3 Subthreshold Swing                          | 17    |

| 2.1.4 On-off Ratio                                           |

|--------------------------------------------------------------|

| 2.2 Important Parameters of CMOS Inverter18                  |

| 2.2.1 Voltage Gain18                                         |

| 2.2.2 Dynamic Behavior18                                     |

| 2.3 Principle of Sputter Deposition20                        |

| 2.4 Operational Basics of Field Effect Transistors23         |

| Chapter 3. Experimental Method26                             |

| 3.1 Experimental Steps26                                     |

| 3.1.1 Substrates Cleaning26                                  |

| 3.1.2 Inorganic Active Layer Deposition26                    |

| 3.1.3 Annealing Process                                      |

| 3.1.4 Organic Active Layer and Metal Electrodes Deposition28 |

| 3.2 The Fabrication Process of a-IGZO/Pentacene TFTs29       |

| 3.3 Electrical Measurement and Morphology analyses32         |

| 3.3.1 Film Morphology32                                      |

| 3.3.2 Electrical Characteristics of OTFT Device34            |

| Chapter 4 Decults and Discussion 35                          |

| 4.1Optimization of the Cha  | aracteristics of a-IGZO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Thin Film Transistors35 |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| 4.1.1. Discussions          | •••••••••••••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 36                      |

| 4.2 Characteristics of Pent | acene/a-IGZO Ambipo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | olar TFTs37             |

| <b>4.2.1. Discussions</b>   | •••••••••••••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 41                      |

| 4.3 Complementary Metal     | -Oxide- Semiconductor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -Like Inverter41        |

| <b>4.3.1. Discussions</b>   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 45                      |

|                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                         |

| Chapter 5. Conclusion.      | •••••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 48                      |

| 5.1 Conclusions             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 48                      |

| 5.2 Future Works            | ESA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 50                      |

|                             | 1896                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                         |

| References                  | The state of the s | 51                      |

## **Figures Captions**

| Fig. 1-1 (a) blend structure, (b) single-component structure, and (c) bilayer    |

|----------------------------------------------------------------------------------|

| structure3                                                                       |

| Fig. 1-2 (a) CMOS inverter circuit (b) standard symbol (c) operate region5       |

| Fig. 1-3 Schematic orbital drawing of electron pathway in convalent and ionic    |

| oxide semiconductors8                                                            |

| Fig.1-4 a-IGZO Transmittance in visible light10                                  |

| Fig. 1-5 Applications of organic transistors                                     |

| Fig. 1-6 Structure of n-type material pentacene11                                |

| Fig. 1-7 Ambipolar TFT and CMOS-like inverter diagram                            |

| Fig. 2-1 Threshold voltage and subthreshold swing diagram                        |

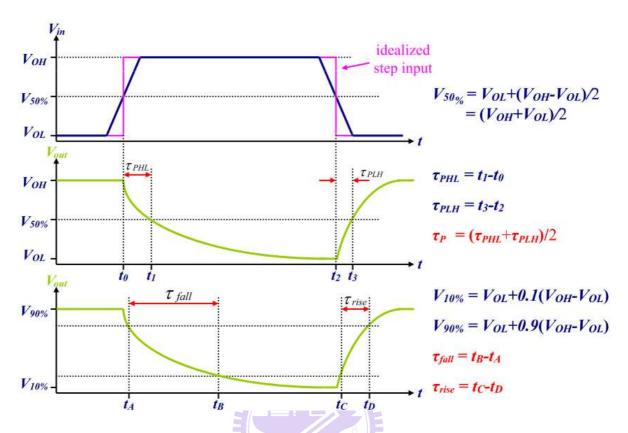

| Fig.2-2 Charging and discharging process                                         |

| Fig. 2-3 Graphical depiction for dynamic behavior20                              |

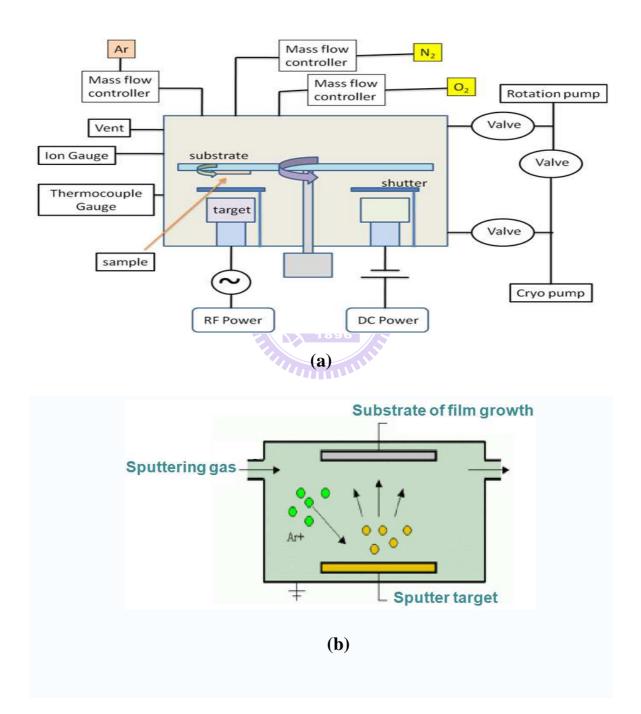

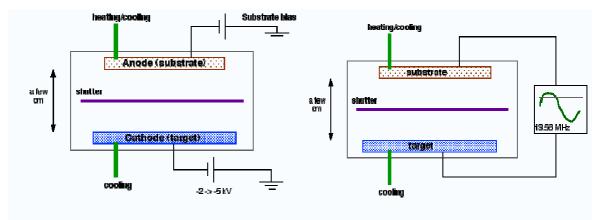

| Fig. 2-4 (a) Sputter system diagram and (b) Sputter mechanism diagram21          |

| Fig. 2-5 (a) DC mode of sputter system and (b) Radio-frequency mode of sputter   |

| system22                                                                         |

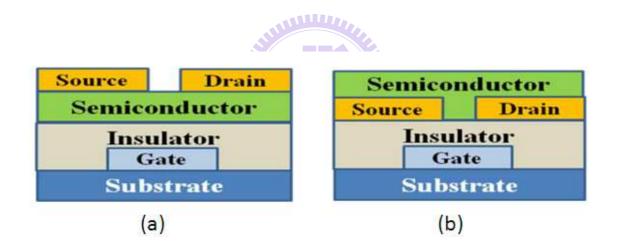

| Fig. 2-6 Schematic view of (a) top contact and (b) bottom contact TFTs23         |

| Fig. 2-7 Schematic of organic field-effect transistors operation in accumulation |

| mode: (a) $VD=VS=VG=0 V$ , (b) $VD=VS=0 V$ , $VG < 0$ , (c) $VS = VD = 0 V$ ,    |

| VG > 0, (d) $VS = 0$ V, $VG < VD < 0$ , and (e) $VS = 0$ V, $VD < VG < 0$ 25     |

| Fig. 3-1 Sputter system27                                                        |

| Fig. 3-2 Atmospheric anneal furnace                                              |

| Fig. 3-3(a) A thermal evaporation system and (b) the photo of the thermal        |

| evaporated facility29                                                            |

| Fig. 3-4 Process of ambipolar TFT flow chart (A), (B), (C), (D) and (E)31        |

| Fig.3-5 A schematic model of atomic force microscope33                                      |

|---------------------------------------------------------------------------------------------|

| Fig. 3-6 (from left to right) AFM images are 20, 30, 40 nm33                                |

| Fig.4-1 (a) $I_{DS}$ - $V_{GS}$ curves of a-IGZO TFT with different annealing time. (b)     |

| I <sub>DS</sub> -V <sub>DS</sub> curves of a-IGZO TFT after annealing36                     |

| Fig. 4-2 fixed a-IGZO thickness 40 nm, pentacene layer thickness (a) 20 (b) 30              |

| and (c) 40 nm                                                                               |

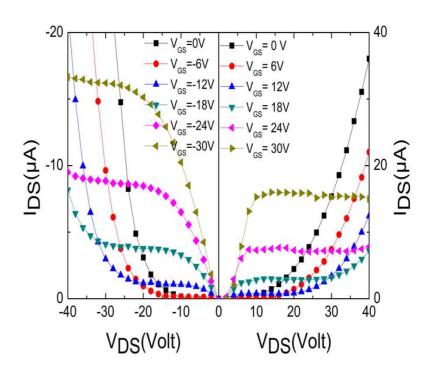

| Fig. 4-3 I <sub>DS</sub> -V <sub>DS</sub> curves (a-IGZO/pentacene 20nm/40nm)39             |

| Fig. 4-4 $I_{DS}\text{-}V_{GS}$ curve of optimized thicknesses of a-IGZO /pentacene layer40 |

| Fig. 4-5 CMOS-like inverter (a) planar structure diagram (b) simplified circuit             |

| diagram42                                                                                   |

| Fig. 4-6 Voltage transfer curve and their corresponding gains of ambipolar TFTs             |

| operated in the (a) first and (b) third quadrant                                            |

| Fig. 4-7 the dynamic behavior of CMOS-like inverter. The top diagram is at 1                |

| HZ. The bottom diagram is at 20 HZ44                                                        |

| Fig. 4-8 Voltage gain of CMOS-like inverter. Pentacene/a-IGZO film are both (a)             |

| 20nm (b) 40nm                                                                               |

| Fig. 4-9 power consumption issue from NMOS logic and CMOS-like inverter47                   |

| Fig. 5-1 CMOS-like inverter achievements                                                    |

### **List of Tables**

| Table 1-1 CMOS operate regin                                    | 6  |

|-----------------------------------------------------------------|----|

| Table 1-2 CMOS inverter characteristic                          | 6  |

| Table 2-1 Parameters of digital circuits                        | 19 |

| Table 5-1 Summary & comparison for ambipolar TFTs and inverters | 50 |

#### Chapter 1

#### Introduction

Pentacene and a-IGZO as active layer combined to make ambipolar TFTs. These devices show both p-type and n-type characteristic. Complementary-Metal-Oxide-Semiconductor-like inverter is composed of two ambipolar TFTs. In this chapter, ambipolar TFTs, CMOS-like inverter and the active layer material a-IGZO and pentacene, are presented, and the motivation and objective of the thesis will be given in the following. Final section is the organization of the thesis.

#### 1.1. Ambipolar Thin Film Transistors

#### 1.1.1 Introduction to Ambipolar Thin Film Transistors

An ambipolar thin film transistor is one in which both electrons and holes are accumulated depending on the applied voltages <sup>[1]</sup>. More recently, ambipolar organic field-effect transistors (OFETs) have been a focus of research due to their potential applications in organic integrated circuits (ICs). Such circuits

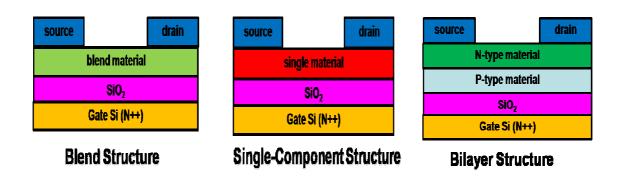

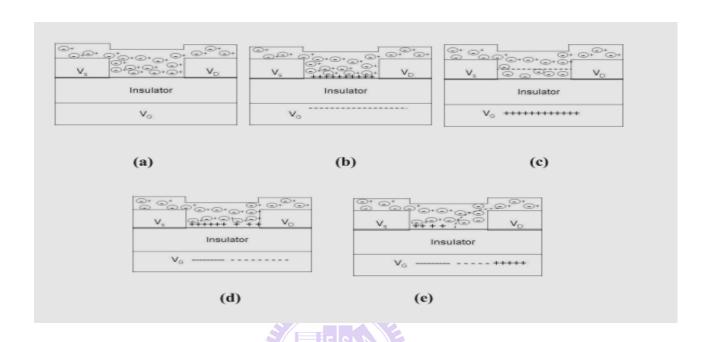

have many advantages, such as better immunity, lower power dissipation, simplifying fabrication and circuit design of ICs, etc. [2][3]. Ambipolar semiconductors are important for CMOS-like inverters that enable robust, low-power circuits with wide noise margins without using advanced patterning techniques to selectively deposit n- and p-channel materials. Currently there are three main structures of ambipolar OTFTs, shown in Figure 1-1, which are (a) blend structure, (b) single-component structure, and (c) bilayer structure. Blend structure is similar to single-component structure. However, the difference between blend structure and single-component structure is that blend structure is composed of 2 materials for respectively providing n-type and p-type characteristics while there is only one semiconductor material in single component structure. The active layer in bilayer structure is stacked of a p-type material and an n-type material for hole and electron transportation, respectively. Noticeable, it's not simple to find proper p-type material and n-type material because both the thickness and the junction properties affect the characteristics of OTFTs

Fig. 1-1 (a) blend structure, (b) single-component structure, and (c) bilayer structure.

#### 1.1.2 Issues of ambipolar thin film transistors

For n-type OTFTs, electron channel cannot be formed successfully in ambient air so that the TFTs show only p-type characteristics. The characteristic of ambipolar TFTs was measured in inert gas environment in most previous works [4-7]. Stability has always been an important issue for TFTs applications although some groups [8,9] had developed ambipolar OTFTs operable in ambient air. For example, Haibo Wang, et al. [9] reported the bilayer structure composed of BP2T (5, 5'-bis (4-biphenylyl)-2, 2'-bithiophene) and F16CuPc (Copper hexadecafluorophthalocyanine) in reference, the electron and hole mobility were up to 0.036 cm²/Vs and 0.04 cm²/Vs, respectively. Organic thin films such as pentacene are widely studied as active channel layers for the TFTs [10]. Like most

of the p-type organic semiconductors studied, pentacene exhibits inherent p-type conduction when grown on a SiO<sub>2</sub> gate oxide. On the other hand, metal oxide systems such as indium oxide (In<sub>2</sub>O<sub>3</sub>) were found to be promising materials for the n-channel TFTs <sup>[11], [12]</sup>. However in previous studies mentioned above, the voltage gain is small. Further, n-type material is unstable in air; the fabrication of stable ambipolar OTFTs is hence limited to few materials.

#### 1.2 Complementary-Metal-Oxide-Semiconductor Inverter

Complementary-metal-oxide-semiconductor (CMOS) inverter is a major class of integrated circuits. The words "complementary " refer to the fact that the typical digital design style with CMOS uses complementary and symmetrical pairs of p-type and n-type metal oxide semiconductor field effect transistors (MOSFETs) for logic functions. CMOS is a major class of integrated circuits. CMOS technology is used in microprocessors, microcontrollers, static RAM, and other digital logic circuits. Two important characteristics of CMOS devices are high voltage gain and low static power consumption. Significant power is only drawn when the transistors in the CMOS device are switching between on and off states. Consequently, CMOS devices do not produce as much waste heat

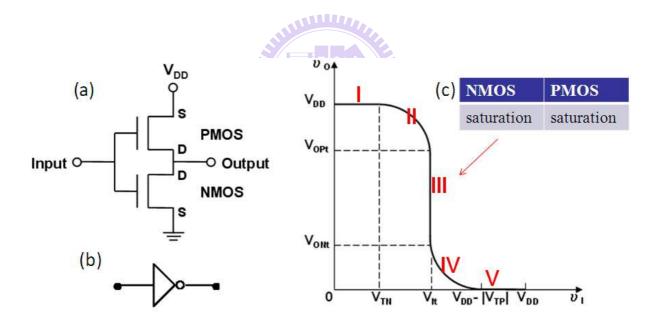

as other forms of logic, for example transistor-transistor logic (TTL) or NMOS logic, which uses all n-channel devices without p-channel devices. The inverter circuit and standard symbol are shown in Figs. 1-2 (a) and (b), respectively [13]. The transfer characteristic curve can be divided into 5 regions as shown in fig. 1-2(c) and the states are listed in table 1-1. Otherwise, when PMOS and CMOS both are saturation, CMOS can be an analog signal amplifier to amplify small signal. (Fig. 1-2 (c)).

Fig. 1-2 (a) CMOS inverter circuit (b) standard symbol (c) operate region

**Table 1-1 CMOS operate regin**

| V <sub>in</sub>                           | n-MOS      | p-MOS      | Vout                      |

|-------------------------------------------|------------|------------|---------------------------|

| 0                                         | cut-off    | linear     | $\mathbf{V}_{	extsf{DD}}$ |

| $V_{TN} < V_{in} < V_{DD}/2$              | saturation | linear     | $\sim$ $ m V_{DD}$        |

| $V_{\mathrm{DD}}/2$                       | saturation | saturation | $V_{DD}/2$                |

| $V_{DD}$ - $ V_{TP}  > V_{in} > V_{DD}/2$ | linear     | saturation | ~0                        |

| V <sub>DD</sub>                           | linear     | cut-off    | 0                         |

The function of CMOS inverter can be summarized by the following table:

**Table 1-2 CMOS inverter characteristic**

| Input | Output |

|-------|--------|

| High  | Low    |

| Low   | High   |

The output is the opposite of the input - this circuit inverts the input. Notice that always one of the transistors will be an open circuit and no current flows from the supply voltage to ground. Two important characteristics of CMOS devices are high noise immunity and low static power consumption. Significant power is only drawn when the transistors in the CMOS device are switching between on and off states. Consequently, CMOS devices do not produce as much waste heat as other forms of logic, for example transistor-transistor logic

(TTL) or NMOS logic, which uses all n-channel devices without p-channel devices. CMOS also allows a high density of logic functions on a chip.

#### 1.3 Amorphous IGZO Thin Film Transistors

#### 1.3.1 Introduction to amorphous oxide semiconductor

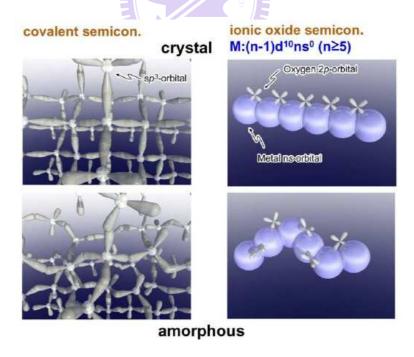

Recently, amorphous oxide semiconductors (AOSs) have attracted much attention because AOS TFTs exhibit large mobility with low-temperature or even room-temperature fabrication. [14-19] The conduction bands of the AOSs are derived from the ns orbital of heavy metal cations such as In<sup>3+</sup>, Ga<sup>3+</sup>, and Zn<sup>2+</sup> [19]. The electron transport path is very efficient because of the large radii and large overlap between adjacent ns orbital of spherical symmetry, which leads to insensitiveness to the distorted metal-oxygen-metal chemical bonds. However, metal oxide semiconductors such as zinc oxide (ZnO) are polycrystalline in nature. The grain boundaries of such metal oxides could affect device properties, uniformity and stability over large areas. To overcome this issue, a new ternary oxide material comprised of In, Ga, Zn and O has been proposed for use as the channel layer in TFTs. Figure 1-3 shows the differences in carrier transportation mechanism for covalent semiconductors, for example, silicon (Si), and ionic oxide semiconductors, in certain molecular orbital configuration, like a-IGZO. The spatial spread of this vacant s-orbital is so large that direct overlap between the s-orbitals of the neighboring cations is possible in heavy metal oxides, and therefore an effective mass of electron is small in these oxides. Electron transport path is also very efficient because of the large radii and large overlap between the adjacent ns orbitals of spherical symmetry, which is less sensitive to the arrangement of atoms. Oxide semiconductors have shown comparable mobilities both in crystalline and amorphous phases, while covalent semiconductors such as silicon shows at least two to three orders of magnitude smaller mobility in the amorphous phase. (Fig. 1-3)

Fig. 1-3 Schematic orbital drawing of electron pathway in covalent and ionic oxide semiconductors

#### 1.3.2 Introduction of a-IGZO

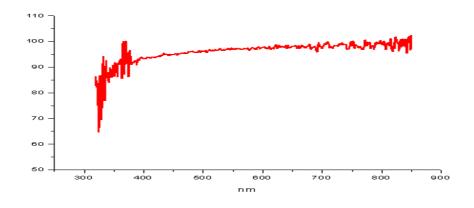

One of the most interesting oxide semiconductors for TFT application is a-IGZO. It was proposed by Hosono et al [20]. Amazingly, high mobility of 7 cm<sup>2</sup>/V s and high on/off ratio of more than five orders of magnitude were achieved even at room temperature process [20]. Incorporating Ga ions is crucial in a-IGZO for suppressing excessive carrier generation via oxygen vacancy. Ga3+ is supposed to attract the oxygen ions tightly due to its high ionic potential (+3 valence and small ionic radius), and thereby suppressing electron injection which is caused by oxygen ion escaping from the thin film. Amorphous IGZO semiconductor possesses three unique features in comparison with conventional a-Si semiconductor, that is, high performance, low process temperature and transparency. a-IGZO film is transparent in visible light range (300~800 nm) and near infrared range of the spectrum with transmittance greater than 80 percent. Without expensive laser apparatus like the poly-Si TFT process, depositing a-IGZO thin film by sputter at room temperature is feasible on the large area. Room temperature sputter makes the mass production on flexible plastic or cheap soda-lime glass viable.

Fig.1-4 Transmittance of a-IGZO in visible light

#### 1.4 Overview of Organic Thin Film Transistor (OTFT)

#### 1.4.1 Introduction to Organic Thin Film Transistor

Organic semiconductor was discovered in 1940s <sup>[21]</sup>. The possibility of fabricating OTFTs with small conjugated molecules was proposed in 1989 with sexithiophene. For a decade, their OTFT performance is improved continuously. Because of their unique properties, organic materials are suitable to be made on the flexible substrates. Many interesting applications such as flexible displays, smart cards, radio frequency identification tags, as well as light-emitting diodes (LEDs) and lasers have been demonstrated (Fig. 1-5).

Fig. 1-5 Applications of organic transistors

#### 1.4.2 Organic Materials- Pentacene

Pentacene,  $C_{22}H_{14}$ , a fused-ring polycyclic aromatic hydrocarbon, is one of the promising candidates of organic semiconductors. Its chemical structure is depicted in Fig. 1.6. There are ways to fabricate it as a continuous film such as the solution process, vapor phase deposition and thermal evaporation.

Fig. 1-6 Structure of n-type material pentacene

#### 1.5 Motivation and objective

There are few researches using metal-oxide semiconductors to act as the n-type material for ambipolar TFTs. Using a-IGZO for ambipolar TFT has not been reported yet. Furthermore, stability in ambient air, poor characteristic is the critical issue of conventional organic n-type material such as PTCDI-C8, F16CuPc, etc. We adopted a-IGZO for this study due to its high mobility and it is insentivity to oxygen and moisture in air. A novel ambipolar TFT composed of active layer material a-IGZO and pentacene is illustrated in Fig. 1-7. Unlike conventional CMOS inverter, our CMOS-like inverter can be operated in two quadrants since our ambipolar TFTs have both n-type and p-type behavior. This makes the circuit design simpler, and can be adopted for display circuit applications.

Fig. 1-7 Ambipolar TFT and CMOS-like inverter diagram

#### 1.6 Organization of Thesis

This thesis is organized as follows: The important parameters about transistors and CMOS inverter, the sputter systems, and fabrication method are presented in **Chapter 2**. In **Chapter 3**, the novel fabrication process of the ambipolar TFTs is described introduced in detail, important parameters such as mobility, threshold voltage, subthreshold swing and on-off ratio are also described. The experimental results, including the  $I_{DS}$ - $V_{DS}$  characteristic,  $I_{DS}$ - $V_{GS}$  characteristic, voltage gain, dynamic behaviors are discussed in **Chapter 4**. Finally, the conclusions of this thesis are presented in **Chapter 5**.

#### **Chapter 2**

#### **Principles and Theories**

Important parameters associated with transistor and CMOS inverter are presented in this chapter. Besides, the principle of sputter system is described detail. Finally the operational principle for TFTs is described.

#### 2.1. Important parameters of TFTs

The quality of a transistor can be examined through several parameters such as a high mobility, a threshold voltage  $(V_T)$  close to 0, and a small subthreshold swing (S.S).

#### 2.1.1. Mobility $(\mu)$

Under the external bias field, carriers can transport in the material. It is called mobility. The value of mobility can be defined in both linear and saturation regions.

(i) When the gate voltage  $(V_G)$  is low, the transistor works in linear region. The drain current  $(I_D)$  is linear to the  $V_G$ . The  $I_D$  can be expressed in terms of Eq. (2-1).

$$I_{D} = \mu C_{OX} \frac{W}{L} \left[ V_{G} - V_{T} - \frac{V_{D}}{2} \right] V_{D}$$

(2-1)

where

$C_{OX}$  is the gate oxide capacitance per unit area,

W is channel width,

L is channel length,

V<sub>T</sub> is the threshold voltage.

If  $V_D$  is much smaller than  $V_G - V_T$ ,  $I_D$  can be approximated as:

$$I_{D} = \mu C_{OX} \frac{W}{L} (V_{G} - V_{T}) V_{D}$$

(2-2)

The transconductance (g<sub>m</sub>) is defined as

$$g_{\rm m} = \frac{\partial I_{\rm D}}{\partial V_{\rm G}} |_{\rm VD=const.} = \frac{W}{L} \mu C_{\rm OX} V_{\rm D}$$

(2-3)

Therefore,  $\mu$  can be obtained by

$$\mu = \frac{L}{WC_{OX}V_{D}}g_{m} \tag{2-4}$$

(ii) When  $V_D$  is larger than  $V_G$ , the characteristic of TFTs is in saturation region.

The I<sub>D</sub> can be expressed as:

$$I_{D} = \mu C_{OX} \frac{W}{2L} (V_{G} - V_{T})^{2}$$

(2-5)

Followed by taking square of the I<sub>D</sub>, this term is taken differentiation to the

V<sub>G</sub>, which can be expressed as:

$$\frac{\partial \sqrt{I_D}}{\partial V_G} = \sqrt{\frac{WC_{OX}}{2L}} \ \mu \tag{2-6}$$

$\mu$  can be expressed in Eq. (2-7).

$$\mu = \sqrt{\frac{2L}{WC_{OX}}} \times \frac{\partial \sqrt{I_D}}{\partial V_G}$$

(2-7)

#### 2.1.2 Threshold voltage (V<sub>T</sub>)

The  $V_T$  of a MOSFET is defined as the  $V_G$  where an inversion layer forms at the interface between the insulating layer and the substrate of the transistor. Conventionally the  $V_G$  at which the electron density at the interface is the same as the hole density in the neutral bulk material is called the  $V_T$ . Practically speaking, the  $V_T$  is the voltage at which there are sufficient electrons in the inversion layer that provides a low resistance conducting path between source and drain of MOSFET. If the  $V_G$  is below the  $V_T$ , the transistor is turned off and ideally there is no current from the drain to the source of the transistor. As shown in Fig. 2-1, if the  $V_G$  is above the  $V_T$ , the transistor is turned on, due to there being many electrons in the channel at the oxide-silicon interface, creating a low-resistance channel where charges can flow from drain to source.

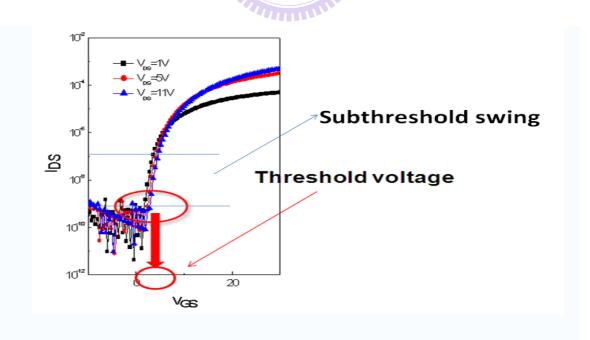

#### 2.1.3 Subthreshold swing (S.S)

Subthreshold swing (S.S in V/dec) is a typical parameter to describe the control ability of gate toward channel. It is defined as the amount of  $V_G$  required to increase/decrease  $I_D$  by one order of magnitude. Subthreshold swing, indicated in Fig.2-1, should be independent of  $V_D$  and  $V_G$ . However, in reality, S.S. might increase with drain voltage due to short-channel effects such as charge sharing, avalanche multiplication, and punchthrough-like effect. The S.S. is also related to  $V_G$  due to undesirable factors such as serial resistance and interface states.

Fig. 2-1 Threshold voltage and subthreshold swing diagram

#### 2.1.4 On-off ratio

On-current represents for the  $I_D$  when transistor is in on state. Contrary, off-current means the  $I_D$  when transistor is in off state. When the on/off current ratio is large, the leakage current can be regarded as negligible.

#### 2.2. Important Parameters of CMOS Inverter

#### 2.2.1. Voltage Gain

In electronics, gain is a measure of the ability of a circuit (often an amplifier) to increase the power or amplitude of a signal. It is usually defined as the mean ratio of the signal output of a system to the signal input of the same system.

Voltage gain can be expressed as in Eq. (2-8)

Voltage gain =

$$-\frac{dV_{out}}{dV_{in}}$$

(2-8)

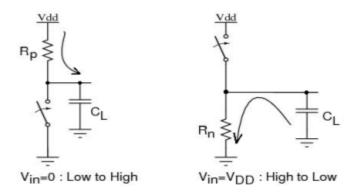

#### 2.2.2. Dynamic behavior

Dynamic behavior is an important parameter for CMOS inverter. Propagation delay and power dissipation are the key analysis in dynamic behavior. The delay of the CMOS inverter is a performance metric for how fast the circuit is. Fig.2-2 shows this delay is dependent upon the RC charging or discharging of the load

capacitor by the PMOS or NMOS devices respectively and provides a quantitative feel for the time that is taken by the output of the inverter to completely respond to a change at its input.

Fig.2-2 Charging and discharging process

Table 2-2 lists the definitions of temporal parameters of digital circuits. All percentages are of the steady state values.

**Table 2-2 Parameters of digital circuits**

| Rise Time t <sub>r</sub>                  | Time taken to rise from 10% to 90%             |

|-------------------------------------------|------------------------------------------------|

| Fall Time t <sub>f</sub>                  | Time taken to fall from 90% to 10%             |

| Edge Rate t <sub>rf</sub>                 | $(t_r + t_f) / 2$                              |

| H-to-L propagation delay t <sub>PHL</sub> | Time taken to fall from $V_{OH}$ to 50%        |

| L-to-H propagation delay t <sub>PLH</sub> | Time taken to rise from 50% to $V_{\text{OL}}$ |

| Propagation delay t <sub>p</sub>          | (t <sub>PHL</sub> + t <sub>PLH</sub> ) / 2     |

Graphical representation of dynamic behavior is shown in Fig. 2-3.

Fig. 2-3 Graphical depiction for dynamic behavior

WILLIAM STATE

#### 2.3 Principle of Sputter Deposition

Sputter deposition is a physical vapor deposition (PVD) method on their agglomerates thin films. Sputtering is a process whereby atoms are ejected from a solid target material due to strike of the target by energetic ions on target. Figure. 2-4 (a) shows the construction of a sputter system. The primary particles for the sputtering process can be supplied in a number of ways, for example by a plasma, an ion source, an accelerator or by a radioactive material emitting alpha

particles. As shown in Fig. 2-4(b), argon (Ar) was ionized under high electrical field. The target particle is deposited on the substrate by Ar<sup>+</sup> striking on the target.

Fig. 2-4 (a) Sputter system diagram and (b) Sputter mechanism diagram.

Sputter system has two operate modes, D.C. (direct current) and RF (radio frequency) mode. The common arrangement for a D.C. sputter coater is to make the target material in negative bias state, while the substrate is in anodic state. The desired operating pressure is achieved by using a suitable vacuum system, usually comprised rotary pump and a high vacuum pump such as turbo pump or cryo pump. An inert gas, such as argon, is admitted to the chamber by a fine control valve. The sputtered atoms are neutrally charged and so are unaffected by the magnetic trap. Charge build-up on insulating targets can be avoided with the use of RF sputtering where the sign of the anode-cathode bias is varied at a high rate. RF sputtering works well to produce highly insulating oxide films but only with the added expense of RF power supplies and impedance matching networks. Figs. 2-4(c) and (d) show DC sputter system and RF sputter system, respectively.

Fig. 2-4 (c) DC mode of sputter system and (d) Radio-frequency mode of sputter system.

#### 2.4 Operational Basics of Field Effect Transistors

Generally, thin film transistors (TFTs) are composed of four components: substrate, semiconductor (also called active layer), insulator and electrodes. The configuration of these elements with two different structures, one is top contact and the other is bottom contact TFTS, are depicted in Fig. 2-5. The electrical characteristics of TFTs can be adequately described by models developed for inorganic semiconductors.

Fig. 2-5 Schematic view of (a) top contact and (b) bottom contact TFTs

The TFTs could be divided into two parts, according to the type of charges transported by the semiconductor. In semiconductors with n-type channel, the charges transported are negative. On the other hand, in semiconductors with p-type channel, the charges transported are positive. When the gate electrode is

biased positively with respect to the grounded source electrode, they operate in the depletion mode, and the channel region is depleted of carriers resulting in high channel resistance. When the gate electrode is biased negatively, they operate in the accumulation mode and a large concentration of carriers is accumulated in the transistor channel, resulting in low channel resistance. For n-type TFT operation, the electrode polarity is reversed and the majority carriers are electrons instead of holes. For instance, a p-type semiconductor is shown in Fig. 2-6 (a) When  $V_D=V_S=V_G=0V$ , a negative bias is forced on the gate to form the ohmic current  $I_D$ . After that, when  $V_D = V_S = 0V$  and  $V_G < 0V$ , the gate current would across the insulator layer and some area of insulator-semiconductor interface would bend the band gap of the semiconductor. Then, the accumulation region is formed as shown in Fig. 2-6(b). The ohmic contact between source and drain electrodes leads to additional charges. When positive bias are applied on the gate electrode, an opposite curved band gap would occur in the insulator-semiconductor interface. This result conducts the depletion region of carriers. The higher bias on the gate electrode, the larger depletion the region expands. Finally, all of the semiconductor layer will be depleted. The voltage across the insulator and semiconductor layers depends on the position of the channel which is a functional relationship when drain voltage has strongly

negative bias effect as shown in Fig. 2-6 (d).

Fig. 2-6 Schematic of organic field-effect transistors operation in accumulation mode: (a) VD=VS=VG=0 V, (b) VD=VS=0 V, VG<0, (c) VS=VD=0 V, VG>0, (d) VS=0 V, VG<0, and (e) VS=0 V, VD<0.

# Chapter 3.

# **Experimental Method**

The device fabrication and processing parameters are described in detail. The method of fabrication process of CMOS-like inverter is also presented in this chapter.

## 3.1 Experimental Steps

## 3.1.1 Substrates Cleaning

The dimensions of substrate (si) are 2 cm x 2 cm. The substrate were cleaned by DI water for 5 minutes and HF solution (HF: H2O=1: 100) for 10 seconds, respectively. Sequentially, the cleaning was completed by blowing off the moisture and baking at 100°C for 2 hours.

## 3.1.2 Inorganic Active Layer Deposition

The sputter system with a background pressure  $< 8 \times 10^{-6}$  torr shown in Fig. 3-1 was employed to deposit a-IGZO thin films. The deposition was came out at

RF power = 80W, pressures working at  $8 \times 10$ -6 torr, oxygen and argon flow rate are equal to 0.6 sccm and 0.8 sccm, respectively.

Fig. 3-1 Sputter system

# **3.1.3** Annealing Process

Using atmospheric anneal furnace in nitrogen ambience to rearrange a-IGZO lattice again. After annealing process, the electrical characteristic of the device is better than the device without annealing. Fig. 3-2 shows the instrument of atmospheric anneal furnace.

Fig. 3-2 Tube furnace

# 3.1.4 Organic active layer and metal electrodes deposition

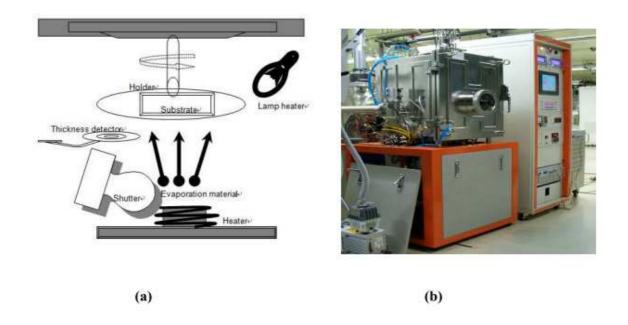

The thermal evaporation system with background pressure about 3 x  $10^{-6}$  shown in Fig. 3-3 was employed to deposit the pentacene layer and gold (Au) electrodes. The evaporation rate of pentacene was about  $0.3 \sim 0.4$  Å /sec. Subsequently, the Au electrodes were deposited onto the active layer with an evaporation rate of  $1 \sim 1.5$  Å/sec at a pressure of  $5 \times 10^{-6}$  torr.

Fig. 3-3(a) A thermal evaporation system and (b) the photo of the thermal evaporated facility.

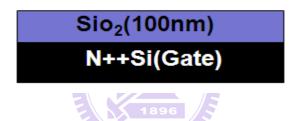

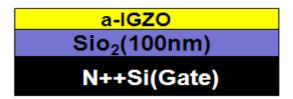

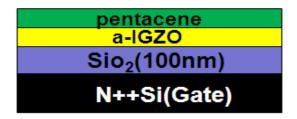

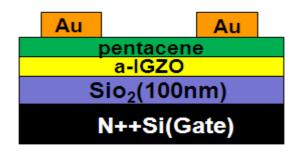

## 3.2 The fabrication process of a-IGZO/Pentacene TFTs

The bottom gate a-IGZO TFT structure was adopted in this study and the fabrication produces are depicted in Figure 3-4. The unit TFT was fabricated on heavily doped (n++) si wafer with 100-nm thick thermally grown oxide layer as the gate electrode and insulator, respectively. A 40-nm-thick a-IGZO film was deposited on to serve as the active channel (RT) by RF sputtering and the deposition was done in an oxygen atmosphere (~8 x 10<sup>-6</sup>) without any

intentional substrate heating. After deposited a-IGZO film, pentacene layer was deposited by thermal coater. Finally, the Au source/drain electrodes were patterned through a stencil mask by thermal evaporation. Finally, two identical transistors were interconnected with each other to complete the CMOS inverter. All of our device characterizations were carried out in the dark at RT by using a semiconductor parameter analyzer (Keithley 4200).

## (A)Start with n++Si / thermal oxide wafer & wafer clean

## (B)Deposit a-IGZO thin film with sputter, no intentional heat

#### (C) Deposit pentacene layer by thermal coater

(D)Thermal evaporation of Au source/drain electrode (40nm)

(E)Ambipolar TFT is Composed of 2 single devices

Fig. 3-4 Process of ambipolar TFT flow chart (A) Start with n++Si/t thermal oxide wafer & wafer clean, (B) Deposit a-IGZO thin film with sputter, no intentional heat, (C) Deposit pentacene layer by thermal coater,

- (D) Thermal evaporation of Au source/drain electrode (40nm) and

- (E) Ambipolar TFT is Composed of 2 single devices

## 3.3 Electical Measurement and Morphology analyses

## 3.3.1 Film Morphology

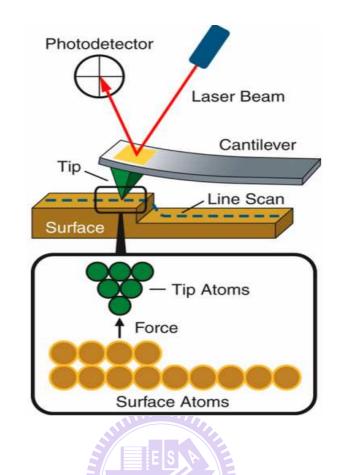

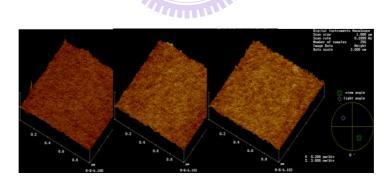

An atomic force microscope (AFM) shown in Fig. 3-5 was utilized to measure the morphology of deposited active layer. The AFM was set to tapping mode and the probe oscillation frequency was 300 Hz. The tapping mode overcame the limitations arose due to thin layer of the condensed phase that formed on most sample surfaces in an ambient imaging environment. The grain size and shape of pentacene are critical when the pentacene crystals deposited on the different insulator layers. Measurements of the grain morphology by AFM were operated in the atmospheric condition. As shown in Fig. 3-6, pentacene thin films with three kinds of thicknesses, 20, 30, 40 nm, were measured by atomic force microscope (AFM). The roughness of 20, 30, and 40nm thick films were 0.162 nm, 0.151 nm, 0.137 nm, respectively.

Fig.3-5 A schematic model of AFM.

Fig. 3-6 (from left to right) AFM images of 20, 30, 40 nm thick a-IGZO films.

## 3.3.2 Electrical characteristics of OTFT devices

The electrical characteristics of the devices, such as degradation and hysteresis, can be evaluated by Keithley 4200 semiconductor analyzer. In addition, the relationship between  $I_{DS}$ - $V_{GS}$  and  $I_{DS}$ - $V_{GS}$  curves can be extracted from measurement results.

The relationship between wafers surfaces and active layers will affect the **Subthreshold swing (S.S).** Annealing process will cause the **Threshold voltage** (**Vth**) shift.

# Chapter 4.

# **Results and Discussion**

## 4.1 Optimization of the Characteristics of a-IGZO Thin Film Transistors

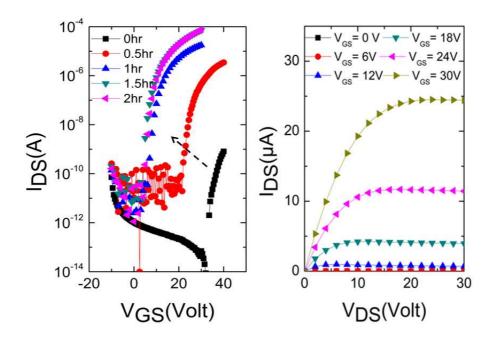

In order to control the electrical characteristics of a-IGZO film, TFT with the channel deposited by optimized deposition conditions (Ar /  $O_2$  flow rate =10 sccm/0.6 sccm) was fabricated. However, post annealing process strongly affects the electrical properties of a-IGZO film; it is one of the key parameter to control the characteristics of TFT behavior. As shown in Fig. 4-1(a), the threshold voltage (Vth) shifted negatively after annealing at 350 °C in  $N_2$  environment for 2 hours. Fig. 4-1(b) shows the  $I_{DS}$ - $V_{DS}$  characteristics of the a-IGZO TFT after annealing at 350 °C for 1 hour. According to Figs. 4-1(a) and (b), the transfer characteristics of a-IGZO TFTs were optimized by adjusting oxygen/argon ratios during RF sputter and varying different post-annealing conditions.

Fig.4-1 (a)  $I_{DS}$ - $V_{GS}$  curves of a-IGZO TFT with different annealing time.

(b)  $I_{DS}$ - $V_{DS}$  curves of a-IGZO TFT after annealing.

## 4.1.1. Discussions

In  $I_{DS}$ - $V_{GS}$  curves, the post annealing time from 0 to 2 hour in a half hour increment. It is noted that when the annealing time is over than 2 hour; TFTs do not exhibit an appreciable electrical characteristic and thus, are omitted from this plot. Consider the behavior of annealing time beyond 2 hour, the decrease of  $V_{TH}$  is possibly associated with crystallization (i.e., grain boundary-inhibited transport).

## 4.2 Characteristics of Pentacene/a-IGZO Ambipolar TFTs

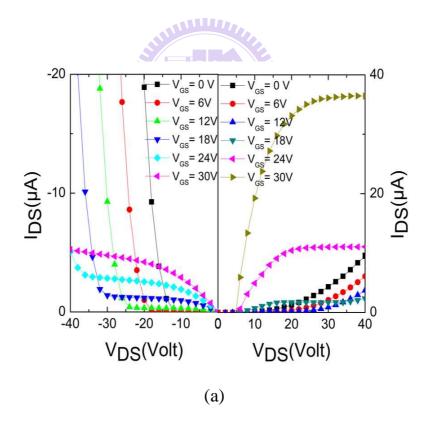

In order to optimize the electrical characteristics, several combinations of thicknesses were investigated. First, at by fixing a-IGZO thickness at 40 nm, change pentacene with thickness from 20 to 40 nm were fabricated and measured electrical property are shown in Figs. 4-2 (a) to (c). The reason for choosing a-IGZO thickness at 40 nm is that the thicker films can accumulate more carriers to attain high voltage gain.

Fig. 4-2 Thickness effect on devices (a) pentacene = 20 nm, IGZO = 40nm (b) pentacene = 30 nm, IGZO = 40nm and (c) pentacene and IGZO = 40 nm

When thicknesses of a-IGZO and pentacene films are 40 nm and 20 nm, respectively, a-IGZO layer will suppress pentacene layer's  $I_{DS}$ - $V_{DS}$  curves. Increasing pentacene layer to 40 nm, the current is not saturated at high  $V_{DS}$ . It is noted that at the thickness of pentacene layer of 40 nm and a-IGZO layer of 20 nm, p-type layer will also suppress the n-type's electrical characteristics. Fig. 4-3 shows the effect of  $I_{DS}$ - $V_{DS}$  curve.

Fig. 4-3 I<sub>DS</sub>-V<sub>DS</sub> curves (a-IGZO/pentacene 20nm/40nm)

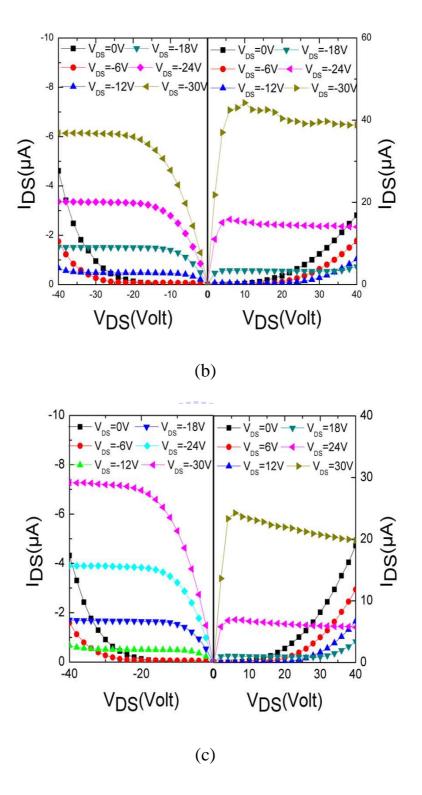

The optimal thicknesses of a-IGZO layer and pentacene layer were found to be 40nm and 30nm, respectively. The a-IGZO thin film (40nm) and pentacene

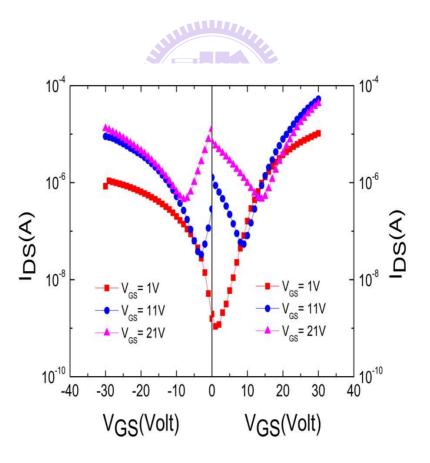

thin film (30nm) were deposited in order on the Si substrate with a thermally grown SiO<sub>2</sub> layer (100nm). Au was used as source and drain electrodes by thermal evaporation. Without any passivation layer, the TFT characteristics were successfully measured in ambient air.  $I_{DS}$ - $V_{GS}$  curves are shown in Fig. 4-4. On/off current ratio is decreased when  $V_{DS}$  is increased. Take n-type operation for example, when  $V_{DS} > V_{GS}$ , holes are induced and injected into active layer due to electric field between gate and drain electrode. Mobility of 0.02 and 4.57 cm<sup>2</sup> V/s were estimated for holes and electrons, respectively.

Fig. 4-4  $I_{DS}\text{-}V_{GS}$  curve of optimized thicknesses of a-IGZO /pentacene layer

#### 4.2.1. Discussions

There have several interesting phenomena observed during optimizing the thickness of a-IGZO/ pentacene. In the Figs. 4-2(a) and 4-3, at low  $V_{GS}$ , the current was not saturated at high  $V_{DS}$ , instead, it increased steeply. For example, when operated in n-type region,  $V_{GS}$  and  $V_{DS}$  are positively biased, when  $V_{DS}$ - $V_{GS}$ >0,  $V_{DS}$  can be treated as 0 while  $V_{GS}$  as negative. Thus, when the voltage difference becomes larger than the amount pentacene film can sustain, holes accumulate under the drain electrode. Both electrons in n-type region and holes in p-type region contribute to the current at this moment.

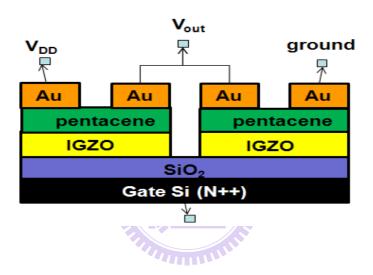

# 4.3 Complementary Metal-Oxide-Semiconductor-Like inverter

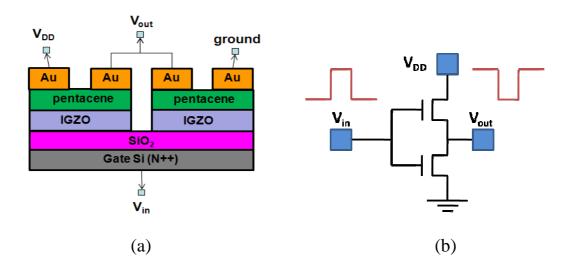

A CMOS-like inverter was fabricated combining two ambipolar TFTs containing a-IGZO/pentacene layers. The cross-sectional view of this CMOS-like inverter and equivalent circuit are shown in Figs. 4-5 (a) and (b).

Fig. 4-5 CMOS-like inverter (a) planar structure diagram (b) simplified circuit diagram

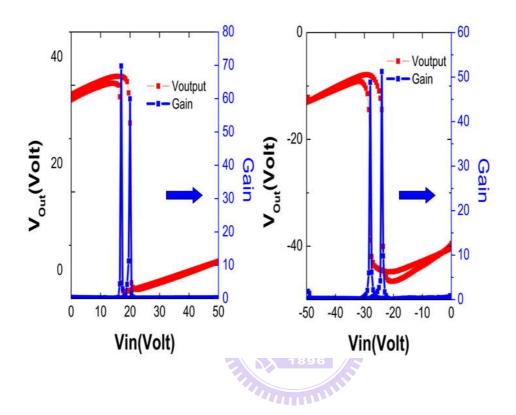

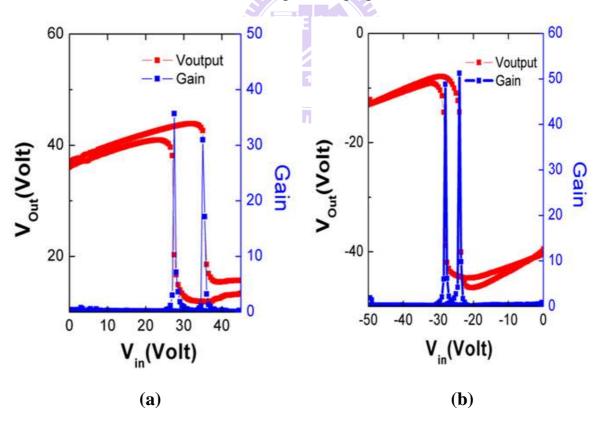

In the inverter circuit, the gate served as an input node and was shared by both transistors. The input voltage (Vin) range was  $0V \sim \pm 50V$  while  $V_{DD}$  was constantly biased at  $\pm 50V$ . Our inverter exhibits a high gain value ( $-dV_{out}/dV_{in}$ ) about 70. In Fig. 4-6, maximum gain up to 70 was obtained when operating the inverter in n-type region. In p-type region the maximum gain up to 53. Previous studies  $^{[22,23]}$  reported the voltage gain of devices about 10. Higher voltage gain for CMOS and small hysteresis were observed. Small hysteresis implies small grain boundary in the surface between active layer and insulator. Unlike conventional CMOS inverter, our CMOS-like inverter can be operated in 2 quadrants, because the ambipolar TFTs have both n-type and p-type behavior.

This makes the circuit design simpler, and can be adopted for display circuit applications.

Fig. 4-6 Voltage transfer curve and their corresponding gains of ambipolar TFTs operated in the (a) first and (b) third quadrant

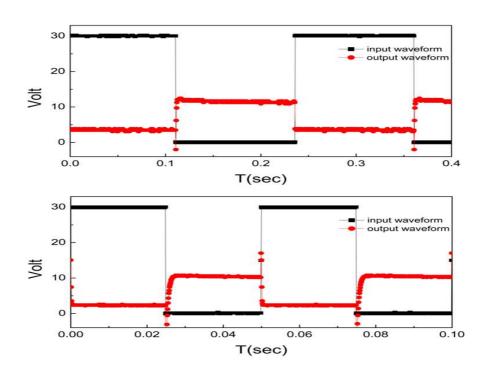

Dynamic response was performed by measuring the output signal  $V_{out}$  with respect to the input signal  $V_{in}$  using an oscilloscope with  $1M\Omega$  input impedance. At the frequency of 1 Hz, the input 30 V can invert to ~15 V. Until to the frequency of 20 Hz, the inverting action shows a little RC delay at on and off switching. Figure 4-7 shows the dynamic behavior of our inverter when

operating in the frequency range of 1Hz and 20 Hz. The rising  $(t_r)$  and falling times  $(t_f)$  at 20 Hz in our inverter was measured to be about ~2ms and 0.9 ms, respectively. Previous study published in APL <sup>[22]</sup> reported that the devices only can operate in the frequency less than 10 Hz. Our devices hence have the fastest frequency response in previous research. <sup>[22, 23]</sup>

Fig. 4-7 The dynamic behavior of CMOS-like inverter. The top diagram is at 1 HZ. The bottom diagram is at 20 HZ

#### 4.3.1. Discussions

In section 4.2, another interesting phenomenon observed during the optimization of thickness is the relationship between thickness and voltage gain. Figures. 4-8 (a) and (b) show the voltage gain diagrams. In Fig. 4-8 (a), pentacene layer and a-IGZO thin film are both at 20 nm. In Fig. 4-8 (b) pentacene layer and a-IGZO thin film are both both at 40 nm. Their I<sub>DS</sub>-V<sub>GS</sub> characteristic has no obviously different. However, the voltage gain is higher because the thicker active layers. The reason is that thicker films can accumulate more carriers to attain high voltage gain.

Fig. 4-8 Voltage gain of CMOS-like inverter. Pentacene/a-IGZO films are

(a) 20nm and (b) 40nm.

The other important parameters of CMOS inverter is dynamic behavior. To make a faster inverter (work at high frequency), Propagation delay (t<sub>P</sub>) is a key.

$$t_{pLH} = \frac{\Delta V}{I} C = \frac{C_{L} \cdot V_{dd}}{k_{p} \cdot \frac{W}{L} (V_{dd} - |V_{TP}|)^{2}} \approx \frac{C_{L}}{k_{p} \cdot \frac{W}{L} V_{dd}}$$

$$t_{pHL} = \frac{\Delta V}{I} C = \frac{C_{L} \cdot V_{dd}}{k_{n} \cdot \frac{W}{L} (V_{dd} - |V_{TN}|)^{2}} \approx \frac{C_{L}}{k_{n} \cdot \frac{W}{L} V_{dd}}$$

$$t_{p} \approx \frac{1}{2} (t_{pLH} + t_{pLH}) = \frac{C_{L}}{2 \cdot \frac{W}{L} V_{dd}} (\frac{1}{k_{n}} + \frac{1}{k_{p}})$$

So to reduce the propagation delay (t<sub>P</sub>), it is necessary increase  $k_n \cdot k_p \cdot W/L$  and  $V_{DD}$  and reduce the load capacitance (C<sub>L</sub>).

Another important issue of CMOS inverter is power consumption. The power consumption can be expressed in Eq. (4-2).

$$E = \text{Energy / transition} = \frac{1}{2} \times C_L \times V_{dd}^2$$

(4-1)

$$P = Power = 2 \times f \times E = f \times C_L \times V_{dd}^2$$

(4-2)

f: cycle / sec

The output is the opposite of the input is an ideal model of inverter. However, in order to make a low power consumption inverter, load capacitance ( $C_L$ ), work frequency and  $V_{DD}$  need to be reduced. However, the power is a function of frequency, as shown in Eq. (4-2). So considered the trade off of power

consumption and time delay, increase of W/L implies the larger size, and  $V_{\text{DD}}$  increase results in more power dissipation.

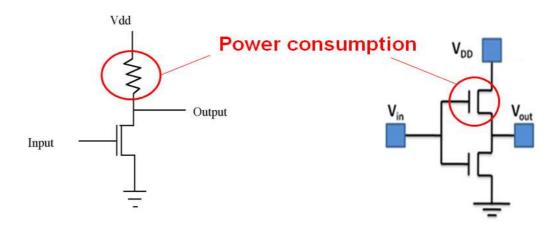

NMOS logic also can be the CMOS inverter. However, the resistance cause more power consumption when  $V_{dd}$  is high, as shown in Fig. 4-9. For our devices, increasing W/L of the ambipolar TFT near drain side can reduce the resistance achieve low power consumption.

Fig. 4-9 Power consumption issue from NMOS logic and CMOS-like inverter

# Chapter 5

# Conclusion And Future Works

#### **5.1 Conclusions**

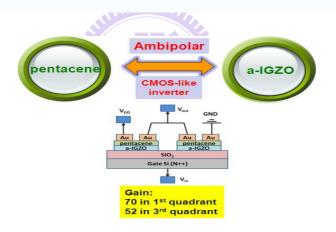

In this study, we fabricated ambipolar TFTs through a hybrid route by combining organic/oxide semiconductors. These ambipolar TFTs can be a CMOS-like inverter circuit. The contributions of this study are: (1) Largest gain and fastest operation frequency are achieved in CMOS-like inverter. (2) leading the researches regarding to the CMOS-like inverter composed of a-IGZO and pentacene.

First of all, in order to control the electrical characteristics of a-IGZO TFTs, optimization by adjusting oxygen/argon ratios during RF sputter and adjustment of post-annealing conditions were required. Annealing time over than 2 hour; TFTs do not exhibit an appreciable characteristic. One hour is the best time duration of annealing process for our device with 100-nm thick thermally grown oxide layer as the insulator. Both n channel and p channel behaviors of the ambipolar TFTs were analyzed together with their

corresponding inverter circuits. The optimal thicknesses of a-IGZO layer and pentacene layer were found to be 40nm and 30nm, respectively. The initial inverter showed a high voltage gain about 70 under the supply voltage ( $V_{DD}$ ) of 50V. Dynamic behavior of the inverter at 20 Hz rising ( $t_r$ ) time and falling times ( $t_f$ ) were measured to be about ~2ms and 0.9 ms, respectively. The largest gain and fastest dynamic behavior were achieved in our COMS-like inverter.

Fig. 5-1 CMOS-like inverter achievements

Overall, a-IGZO/pentacene TFTs exhibits an ambipolar behavior with balanced field effect mobility and qualifies themselves as promising candidates

for the applications in AMFPDs. Table 5-1 compares our latest results (the gain value of 70) and similar studies reported elsewhere. <sup>[12, 22]</sup>.

Table 5-1 Summary & comparison for ambipolar TFTs and inverters

| Inverter<br>Comparison                      | APL 2008<br>Vol. 93, 033306<br>NCKU | APL 2008<br>Vol. 93, 213505<br>U. of Tokyo | 2008<br>Submitted to SID09<br>NCTU |

|---------------------------------------------|-------------------------------------|--------------------------------------------|------------------------------------|

| TFT type                                    | Ambipolar                           | P-type + N-type                            | Ambipolar                          |

| Inverter                                    | CMOS-like                           | CMOS                                       | CMOS-like                          |

| P- type TFT                                 | pentacene                           | pentacene                                  | pentacene                          |

| N-type TFT                                  | In <sub>2</sub> O <sub>3</sub>      | a-IGZO                                     | a-IGZO                             |

| Gain (dV <sub>out</sub> /dV <sub>in</sub> ) | 9                                   | 56                                         | 70                                 |

| Operation quadrant                          | 1+3                                 | 1                                          | 1+3                                |

| Process                                     | Easy                                | Complex                                    | Easy                               |

#### **5.2 Future Works**

Using platinum (Pt) as the electrodes and buffer layer between active layer and insulator is a way to enhance hole's transport. Platinum enables both n-type and p-type characteristics for a-IGZO at the same time. The fabrication process can be simplified.

Operating voltage, output frequencies, and gain values of CMOS-like inverter will be further studied and optimized. These ambipolar TFTs open a viable way to fabricate high performance logic devices with mechanical flexibility and good reliability in air ambient.

# References

- [1] J.Zaumseil and H. Sirringhaus, Chem. Rev. 107, 1296 (2007)

- [2] E. J. Meijer, D. M. de Leeuw, S. Setayesh, E. van Veenendaal, B.-H. Huisman, P. W. M. Blom, J. C. Hummelen, U. Scherf, and T. M. Klapwijk, Nat. Mater. **2**, 678 \_2003\_.

- [3] T. D. Anthopoulos, D. M. de Leeuw, S. Setayesh, E. Cantatore, C. Tanase, P. W. M. Blom, and J. C. Hummelen, Mater. Res. Soc. Symp. Proc. **871E**, I11.9.1 \_2005\_.

- [4] S. J. Kang, Y. Yi, C. Y. Kim, K. Cho, J. H. Seo, M. Noh, K. Jeong, K.-H. Yoo, and C. N. Whang, "Ambipolar organic thin-film transistors using C60/pentacene structure: Characterization of electronic structure and device property." Appl. Phys. Lett. 87, 233502 (2005).

- [5] S. Cho, J. Yeun, J. Y. Kim, K. Lee, and A. J. Heeger, "Ambipolar organic field-effect transistors fabricated using a composite of semiconducting polymer and soluble fullerene." Appl. Phys. Lett. 89, 153505 (2006).

- [6] S. Hoshino, M. Yoshida, S. Uemura, T. Kodzasa, N. Takada, T. Kamata, and M. Muccini, Appl. Phys. Lett. 85, 1613 (2004).

- [7] C. Rost, S. Karg, W. Riess, M. A. Loi, M.Murgia, and M. Muccini, "Ambipolar light-emitting organic field-effect transistor." Appl. Phys. Lett. 85, 1613 (2004)

- [8] R. B. Ye, M. Bada, Y. Oishi, K. Mori, and K. Suzuki, "Air-stable ambipolar organic thin-film transistors based on an organic Homostructure." Appl. Phys. Lett. 86, 253505 (2005).

- [9] H. B. Wang, J. Wang, X. J. Yan, J. W. Shi, H. K. Tian, Y. H. Geng, and D.

- H. Yan, "Ambipolar organic field-effect transistors with air stability, high mobility, and balanced transport." Appl. Phys. Lett. 88, 133508 (2006).

- [10] T. Yasuda, T. Goto, K. Fujita, and T. Tsutsui, "Ambipolar pentacene field-effect transistors with calcium source-drain electrodes." Appl. Phys. Lett. 85, 2098 (2004)