# 國立交通大學

材料科學與工程學系奈米科技博士班

博士論文

可撓曲軟性電子元件之設計製造與電性分析

Design, Fabrication and Characterization of Soft Electrical

**Devices on Flexible Substrate**

研究生:孟杰新 Jagan Singh Meena

指導教授:柯富祥 Fu-Hsiang Ko

中華民國一百零一年二月

## 可撓曲軟性電子元件之設計製造與電性分析

### Design, Fabrication and Characterization of Soft Electrical

### **Devices on Flexible Substrate**

研究生: 孟杰新 Student: Jagan Singh Meena

指導教授:柯富祥 Advisor: Fu-Hsiang Ko

### 國交通大學

材料科學與工程學系奈米科技博士班

博士論文

A Dissertation

Submitted to

**Department of Materials Science and Engineering**

College of Engineering

National Chiao Tung University

in Partial Fulfillment of the Requirements

for the Degree of

### **Doctor of Philosophy**

in

Materials Science and Engineering

February, 2012

Hsinchu, Taiwan, Republic of China

### Acknowledgments

I am indeed delighted to write these final pages, I am pleased that my PhD graduation time has come to an end but my research could not have been done without the help of a lot of other people. Without them this experience abroad would definitely not have been as special and gratifying as it was. So, it is my pleasure to have the opportunity to express my thanks to those who have ever helped me.

I would like to thank my mentor Prof. Fu-Hsiang Ko. I will always be grateful to you for providing me this valuable opportunity to have worked in your lab in National Chiao Tung University as a PhD student, and for your guidance, constructive criticism, patience to guide me through my research and most of all your friendship. It has been excellent opportunity for me and I learned from you and, more importantly, some of the excellent tricks you taught me, which will make my own course very much better. Hopefully one day we can continue our collaboration in anyways. I really wish I could express my sincere thanks to you in Taiwan but after spending four years in this beautiful country, I am still unable to speak this beautiful language i.e., Chinese.

I owe a very big thanks to my friends Min-Ching Chu, Dr. Chung-Shu Wu, Srikanth Ravipati, Dr. Chia-Tien Wu, Dr. Yu-Cheng Chang, Chieh Cheng and Ching-Chang Lin. I am grateful for your kindness and constant readiness to help me. I will never forget the days when you enthusiastically taught Thermal-coater, SEM, AFM and Four-point-probe. Whenever I have any questions to seek help from you, you patiently and friendly helped me. I really thank you for the good times and "social support" throughout the four years in PhD. The financial support of my Ph.D. research work by a grant from the National Science Council (NSC), Taiwan, R.O.C., National Nano Device Laboratories (NDL) and NCTU, Taiwan, R.O.C. is grateful acknowledged.

To the colleague cum friends from Graduate Student Dormitory, Mr. Martin Hornansky, Dr. Kartik Sir and Dr. Dhananjya Patra, I thank you all for your help, encouragement and good time we had together. Everybody, in your way, has confronted me with situations that I never experienced and taught me something that what exactly the human behavior. I am grateful to my best friends for your support throughout my PhD endeavors even being away from me but always been very close, with a special note of thanks to my friends cum strength, Rajeev Gupta, Dr. Yogesh Sharma, Dr. Vikas Kaushal, Dr. Archana Shukla, Dr. Pushapraj Singh, Dr. Madhav Singh and Himanshu Varshney. Last but never should be least, I am heartily thankful to my friends Neha Beneda, Neeraj and Uncle-Aunty, Jaipur (Raj., India) for providing a solid source of merriment and relaxation; that's really exciting whenever be I talk with you all. It is so pleased to found you all as good and sincere friends and family ever.

Finally, my all time inspiration my beloved gentle parents, my sister Geeta, my both bhaiya's and bhabhi's, I thank you all for always being there for me, enabling me to be who I am and where I am today. And, my naughty family heroes, Lakshya, Suryansh; my sweet and cute nephews and my niece Vratika; have always been a source of innocent inspiration. You all have been the constant source of love, support and encouragement, which makes everything possible. There are not enough words to describe all the thanks you deserve, but perhaps these four words make me to come close: I love you all..! Not long ago but it's about loving and caring in the process to a sweet girl "Nishi"; my fiancé. Thank you for coming in my life.

Thanks again to everybody for having been there for me and making my "Taiwan adventure" so memorable and pleasurable.

### 可撓曲軟性電子元件之設計製造與電性分析

研究生:孟杰新 指導教授:柯富祥

#### 摘要

可撓曲式電子元件技術是目前各科技強國積極發展之領域,經由研究其材料基本特性,有系統地設計與製備可撓式電子產品將影響日常生活型態。本篇研究內容將針對各項可撓曲式電子元件進行探討,其中包括:金屬-絕緣層-金屬(MIM)與金屬-絕緣層-半導體 (MIS)電容以及有機薄膜電晶體 (OTFT)等。

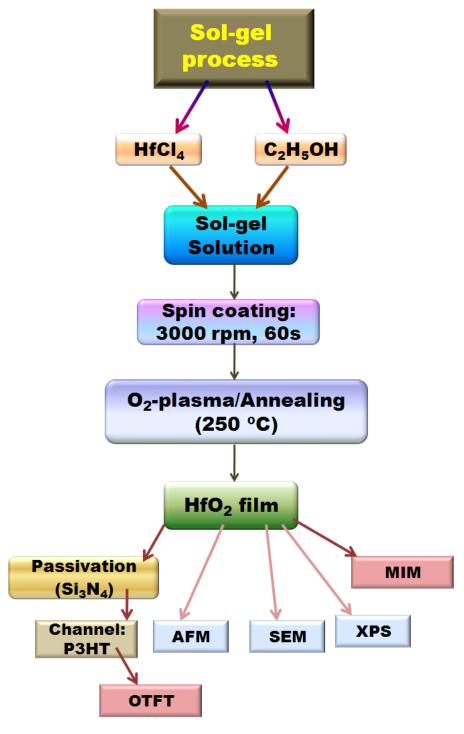

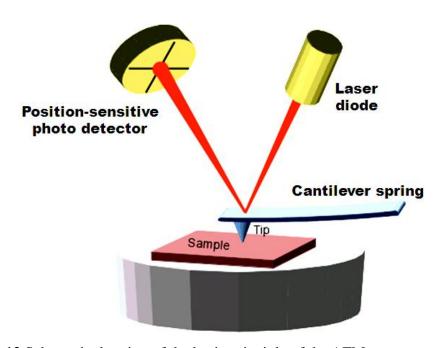

本篇論文第一部分,我們利用溶膠-凝膠(sol-gel)法旋轉塗佈高界電係數材料-HfO2於 polyimide(PI)基板,經由氧電漿(O2 plasma)處理此 sol-gel 薄膜製作膜厚為  $10 \text{ nm-HfO}_2$ 之 MIM 電容。此方法在低溫(250 C)製程之薄膜,利用原子力顯微鏡(AFM)與掃描式電子顯微鏡(SEM)實驗分析,得知此薄膜表面有良好的連續性和均勻性,在 x 射線光電子能譜(XPS)分析也指出此薄膜在經過 O2 plasma 處理後其化學特性與氧化程度有所改變。電性結果顯示此 MIM 電容具有低漏電流與高電容量之特性,且由於元件基板 PI 撓曲性高,經由 100,000次以上與將近 360° 折疊測試後,此元件仍可保持其電子特性。

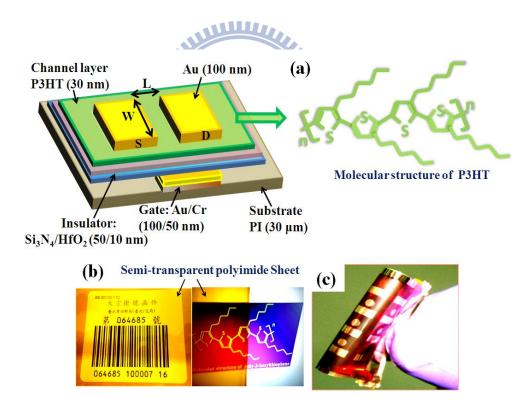

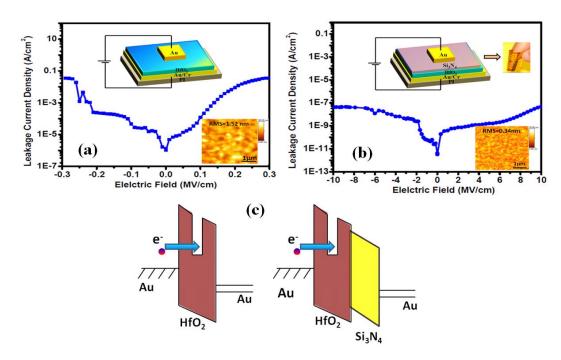

第二部分實驗,我們嘗試製作 p-type 之 poly-(3-hexylthiophene) (P3HT) 薄膜電晶體於 PI 基板上,並利用  $Si_3N_4$ -HfO<sub>2</sub> 為此電子元件之絕緣層。此薄膜電晶體製程步驟如下:1. 使用簡單、便宜 sol-gel 技術製作膜厚為  $10 \text{ nm-HfO}_2$  之介電層於 PI 基板;2. 堆疊 50 nm  $Si_3N_4$  於 HfO<sub>2</sub> 之上;3. 旋轉塗佈 30 nm P3HT 薄膜作為 channel layer。此製作過程,由於  $Si_4N_4$  之作用有效地改善原先 MIM 電容漏電流之情況,在電性量測方面(如:on-to-off ratio 及 saturation mobility 等),结果皆顯示其特性良好。此外,針對此電晶體之可撓性,我們也量測元件在不同曲度及折疊後之電性,詳細探討撓曲對元件所造成之影響。

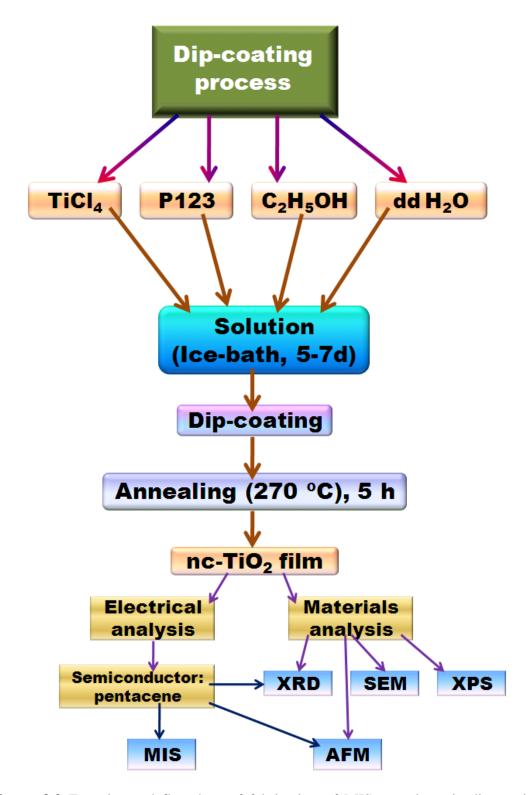

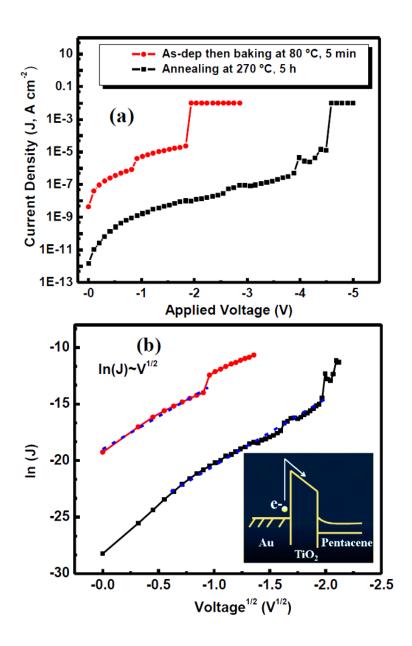

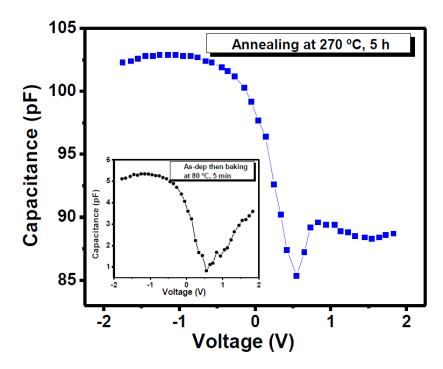

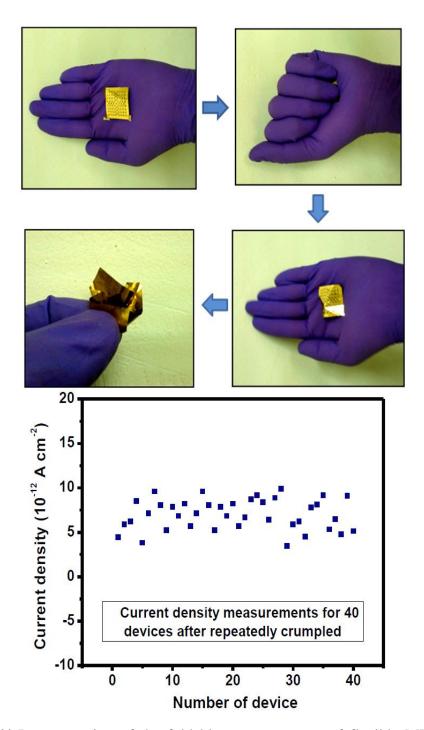

第三部分內容,我們使用聚合物(EO20-PO70-EO20; P123)當作表面活性劑備製二氧化鈦(nc-TiO2)薄膜,以旋轉塗佈技術將 P123-TiO2旋塗於 PI 基板製作成MIS 電容結構。經由 XRD、AFM 與 XPS 等分析在 270 °C 退火 5 小時後觀察 nc-TiO2表面形貌及化學組成等參數,實驗結果顯示薄膜經由 P123 的作用促使其表面結構平坦且均勻度良好,此外我們也針對半導體層(pentacene)表面進行探討,利用 AFM 與 XRD 實驗得知其表面為連續平面且均勻度高。在 I-V 特性量測分析方面,此 MIS 元件電性良好,在外加偏壓為 -5 V 時,漏電流密度值為  $8.7 \times 10^{-12} \, \text{A cm}^{-2}$ ,在  $1 \, \text{MHz}$  條件下,電容值為  $102.3 \, \text{pF}$ ,且介電常數值為  $28.8 \, \text{s}$  另外,針對此電子元件可撓性測試,我們量測元件在不同曲度的電性表現,發現經過  $30 \, \text{天置放後,此元件仍可保持其電子特性。}$

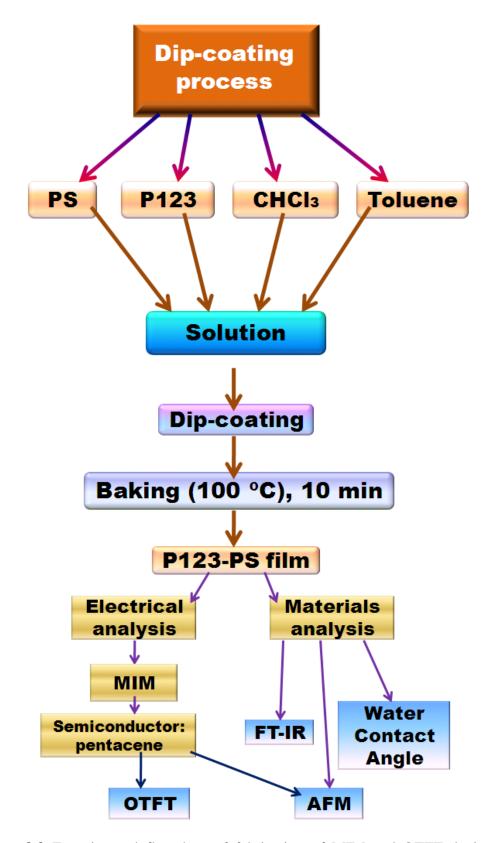

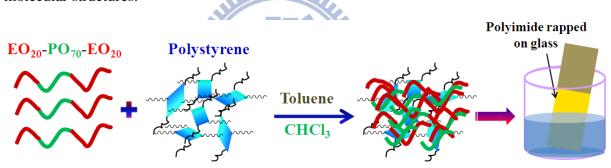

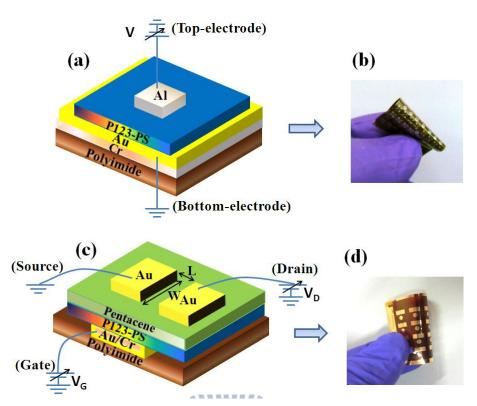

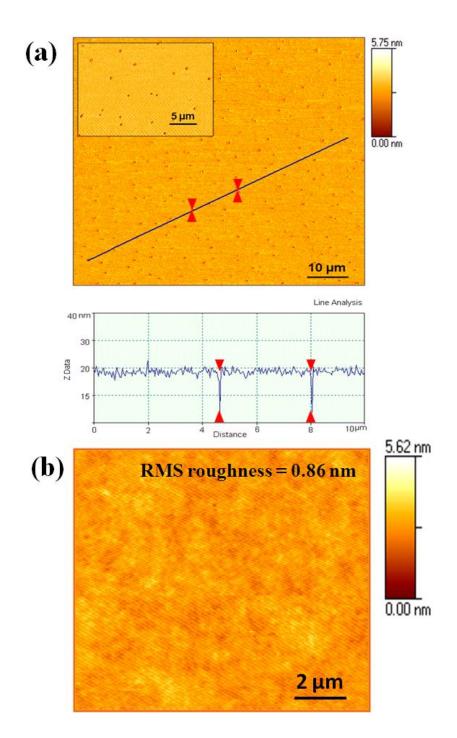

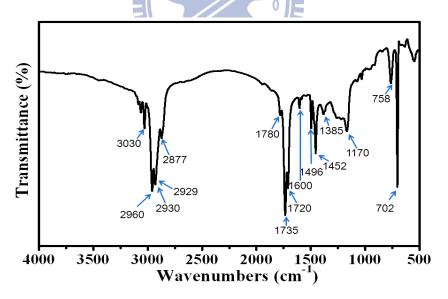

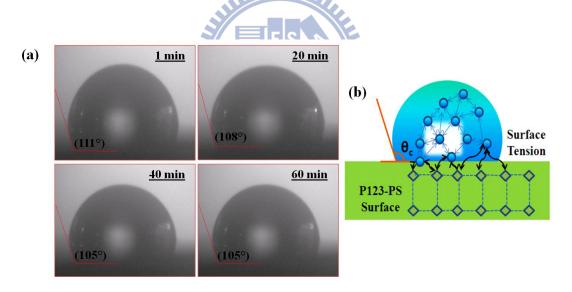

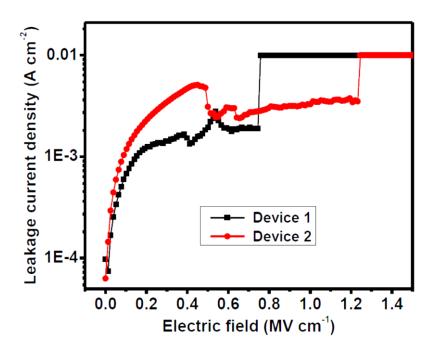

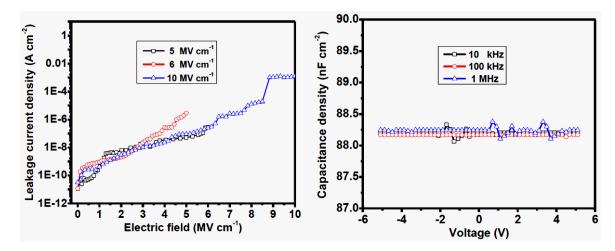

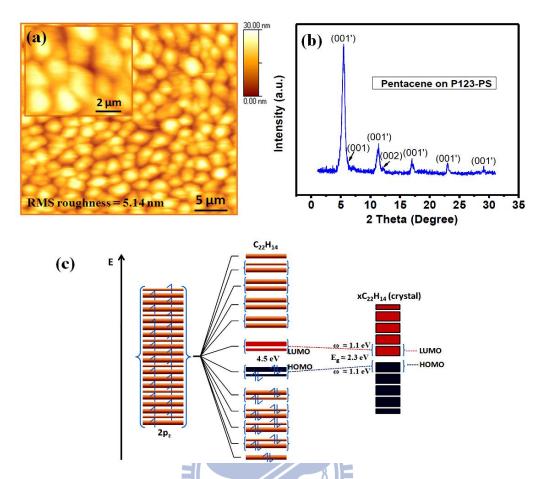

本論文最後一部分,我們將 P123 與聚苯乙烯(polystyrene; PS)兩種聚合物混合後當作製備有機薄膜層之材料(P123-PS),AFM 分析得知此薄膜表面均勻度高,且對於大氣水分有良好抵抗能力,利用接觸角量測儀實驗顯示,此平面為疏水表面,且表面自由能約為  $7.12~\text{mJ}~\text{m}^2$ 。之後我們嘗試利用此 P123-PS 薄膜製作成 MIM 結構之電子元件於 PI 基板,經由 I-V 特性量測分析結果得知,其漏電流密度值低於  $1.07\times10^{-11}~\text{A}~\text{cm}^{-2}$ ,電容值為  $88.2~\text{nF}~\text{cm}^{-2}$ ,而介電常數值為 2.7~e 此外,我們也利用此薄膜材料(P123-PS)當作絕緣層在 PI 基板上製作 OTFT,實驗結果顯示其電性參數值 saturation mobility:  $0.16~\text{cm}^2~\text{V}^{-1}~\text{s}^{-1}$ , on-to-off current ratio:  $5\times10^5$ ,且經過拉伸與壓縮測試,此元件亦維持良好電子特性,表示其可撓性良好。

Design, Fabrication and Characterization of Soft Electrical

**Devices on Flexible Substrate**

Student: Jagan Singh Meena

Advisor: Fu-Hsiang Ko

Department of Materials Science and Engineering

National Chiao Tung University

Flexible technology is rapidly exploding worldwide and it will revolutionize all

aspects of our everyday life, since it will lead to fundamental breakthroughs in the

way materials, devices and systems are understood, designed and manufactured. In

this thesis, the advances and prospects of nanotechnology in the fields of novel active

and functional thin films and nanocomposite-materials to be used for the production

of flexible electronic devices, such as flexible metal-insulator-metal (MIM),

metal-insulator-semiconductor (MIS) capacitors and organic thin-film transistor

(OTFT), will be described.

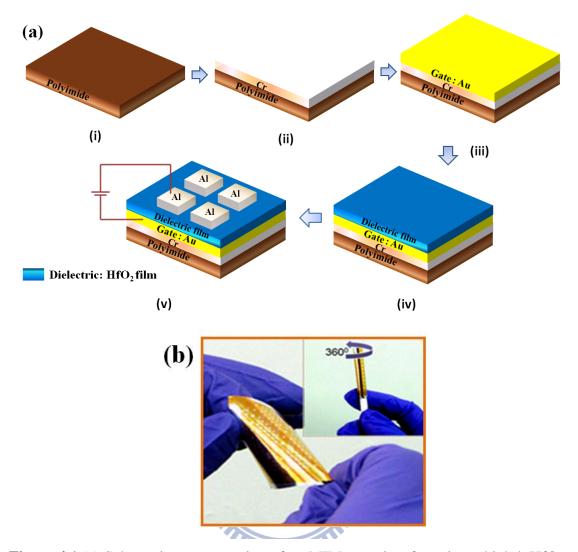

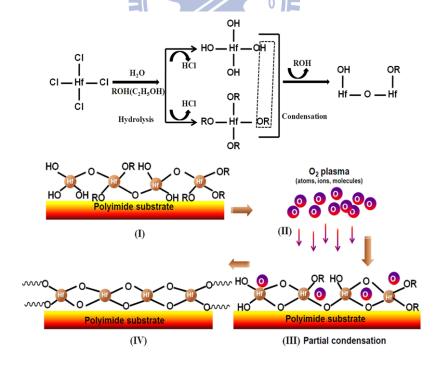

In first section, we focused on the oxygen (O2) plasma affected sol-gel

spin-coating process to fabricate a new MIM capacitor comprising a 10 nm-thick

high-k thin dielectric HfO<sub>2</sub> film on a flexible polyimide (PI) substrate. We observed

the as-deposited sol-gel film was completely oxidized when employing O2 plasma in

together annealing at a relatively low temperature (ca. 250 °C), thereby enhancing the

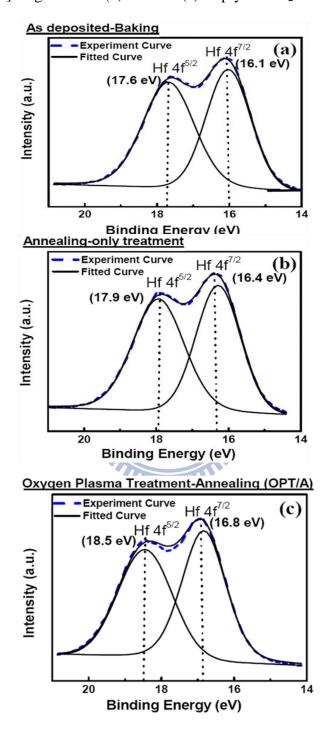

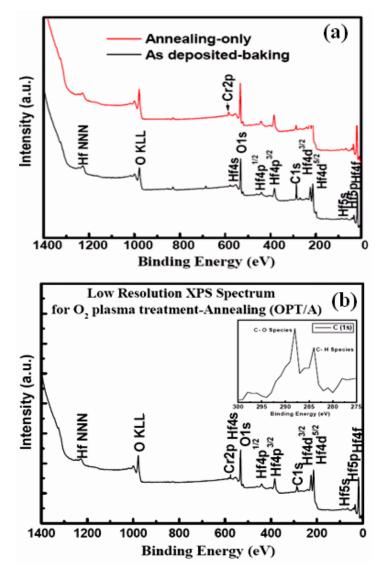

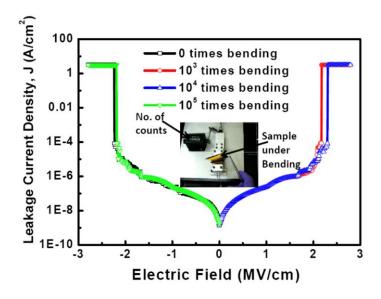

electrical performance. An O<sub>2</sub> plasma mechanism was proposed to explain the surface oxidation of the HfO<sub>2</sub> sol-gel film. The surface morphology of this HfO<sub>2</sub> film was investigated using atomic force microscopy (AFM) and scanning electron microscopy (SEM), which confirmed that continuous and crack-free film growth had occurred. We employed X-ray photoelectron spectroscopy (XPS) at both high and low resolution to examine the chemical composition of the film subjected to various treatment conditions. The shift of the XPS peaks towards higher binding energy revealed that O<sub>2</sub> plasma treatment was the most effective process for the complete oxidation of hafnium atoms at low temperature. To investigate the insulator properties of the HfO<sub>2</sub> film, we deployed it in sandwiched like cross sectional i.e., MIM structured capacitor, which exhibited a low leakage current density and a maximum capacitance density. The real-life flexibility study of the insulator properties indicated the excellent bendability of our MIM capacitor and the flexible PI substrate could be bent up to 100,000 times and folded to near 360° without any deterioration in its electrical performance.

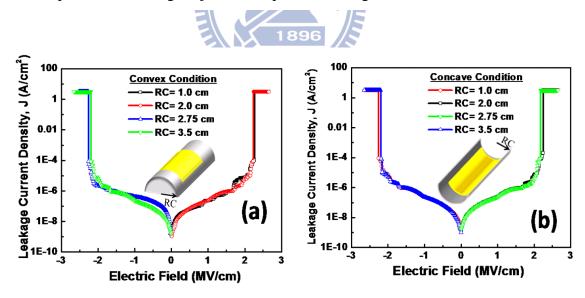

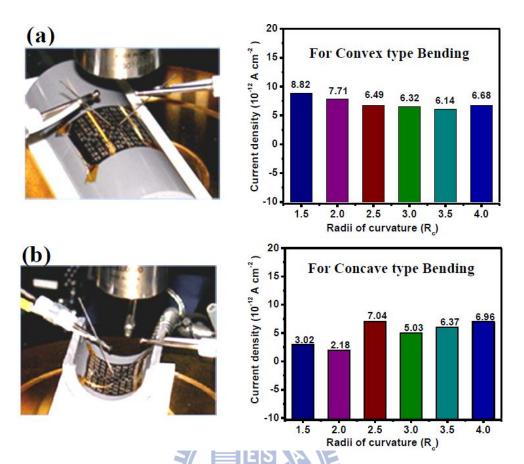

In second section, we demonstrated a new and fully flexible  $Si_3N_4$ -HfO<sub>2</sub> stacked poly-(3-hexylthiophene) p-type OTFT on PI substrate. The success of the TFT manufacturing adopts a very simple and cost-effective sol-gel spin-coating technique to obtain 10-nm high-k HfO<sub>2</sub> as dielectric layer over PI; 50-nm  $Si_3N_4$  as the most efficient passivation layer on top of HfO<sub>2</sub> film; and bendable 30-nm P3HT channel film by spin-coating method. The origin of unsatisfactory leakage current in MIM and TFT structures could be effectively suppressed by means of  $Si_3N_4$  film as the efficient passivation layer. The bottom-gate TFT demonstrated the on-to-off ratio  $2\times10^4$  for drain current and good saturation mobility (0.041 cm<sup>2</sup> V<sup>-1</sup>s<sup>-1</sup>). The proposed devices were examined in convex and concave types of various radii of curvature ( $R_c$ ) in order to explore the manufacturing feasibility and electrical reliability of the flexible TFT

for practical applications. Additionally, various folding times and environmental stability on aforementioned devices with respective to electrical performances were also evaluated.

In third section, we have synthesized triblock copolymer surfactant, EO<sub>20</sub>-PO<sub>70</sub>-EO<sub>20</sub> (i.e. P123)-based nanocrystalline (nc)-TiO<sub>2</sub> thin film on organic flexible PI sheet for their application in organic MIS device. The nc-TiO<sub>2</sub> film over PI was successfully deposited for the first time by a systematic solution proceeds dip-coating method and by the assistance of triblock copolymer surfactant. The effect of annealing temperature (270 °C, 5 h) on the texture, morphology and time-induced hydrophilicity was studied by XRD, AFM, and XPS, respectively, to examine the chemical composition of the film and the contact angle. The semiconductor-dielectric interface of pentacene and nc-TiO<sub>2</sub> films was characterized by current-voltage and capacitance-voltage measurements. This interface measurement in cross-link MIS structured device yielded a low leakage current density of 8.7×10<sup>-12</sup> A cm<sup>-2</sup> at -5 V, maximum capacitance of 102.3 pF at 1 MHz and estimated dielectric constant value of 28.8.

In last section, an organic–organic blend thin–film has been synthesized by solution deposition of triblock copolymer (Pluronic P123, EO<sub>20</sub>-PO<sub>70</sub>-EO<sub>20</sub>) and polystyrene (PS), hereafter named P123-PS for blend film. AFM result revealed that the optimized blend P123–PS film was uniform, crack-free, and highly resistant to moisture absorption. Time-induced contact angle measurements for P123–PS surface was also evaluated by using contact angle meter, which showed excellent hydrophobic surface with surface free energy to about 7.12 mJ m<sup>-2</sup>. The dielectric properties of P123–PS were characterized in cross linked MIM structured device over PI substrate showed a low leakage current density of 1.07×10<sup>-11</sup> A cm<sup>-2</sup>, large capacitance of 88.2 nF cm<sup>-2</sup> and dielectric constant of 2.7. In addition, we demonstrate

OTFT device on flexible PI substrate by using P123–PS as insulator layer and pentacene as channel layer. The OTFT showed good saturation mobility  $(0.16 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1})$  and on-to-off current ratio of  $5\times10^5$ . The OTFT should functions under bending condition; the flexibility tests for two types of bending modes (tensile and compressive) were also performed successfully.

# **Contents**

| Acknowledgments                                    | i    |

|----------------------------------------------------|------|

| Abstract (Chinese)                                 | iii  |

| Abstract (English)                                 | v    |

| Contents                                           | ix   |

| List of Tables                                     | xiii |

| List of Figures                                    | xiv  |

| List of Abbreviations                              | xxiv |

| Chapter 1: Overview                                | 1    |

| 1.1 Background                                     | 1    |

| 1.2 Motivation and Purpose of The Thesis           | 3    |

| 1.3 Thesis Organization                            |      |

| Chapter 2: Literature Survey                       | 8    |

| 2.1 Flexible Substrates                            |      |

| 2.1.1 Flexible Electronic Devices                  | 8    |

| 2.1.2 Highly Reliable and Mechanically Stable      | 12   |

| 2.1.3 Adding Features to Applications              | 14   |

| 2.2 High-k Gate Dielectrics                        | 17   |

| 2.3 Low-k Gate Dielectrics                         | 18   |

| 2.4 Oxygen-Plasma Surface Treatment                | 19   |

| 2.5 Metal-Insulator-Metal Capacitor                | 21   |

| 2.5.1 Introduction                                 | 21   |

| 2.5.2 Leakage Current Density                      | 22   |

| 2.5.3 Traps Influenced Current-Transport Mechanism | 24   |

| 2.5.4 Capacitance and Dielectric Constant          | 26   |

| 2.6 Metal-Insulator-Semiconductor Capacitor        | 27   |

| 2.7 Organic Thin-Film Transistor                   | 28   |

| 2.7.1 Introduction                                 | 28   |

| 2.7.2 On-to-Off Current Ratio and Carrier-Mobility | 29   |

| 2.7.3 Semiconductor Materials for Channel          | 32   |

| 2.7.4 Relation of Inorganic-Organic Semiconductor Materials                    | 35     |

|--------------------------------------------------------------------------------|--------|

| Chapter 3: Experimental Methods                                                | 38     |

| 3.1 General Introduction                                                       |        |

| 3.2 Materials Synthesis and Experimental Flowcharts                            | 38     |

| 3.3 Sol-Gel Spins Coating Techniques                                           |        |

| 3.4 Dip-Coating Techniques                                                     |        |

| 3.5 Harrick-Plasma System                                                      |        |

| 3.6 Thermal-Annealing System                                                   | 48     |

| 3.7 PECVD Deposition System                                                    | 49     |

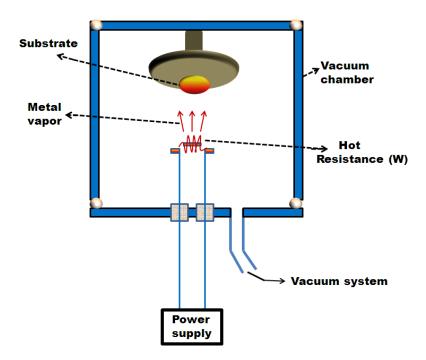

| 3.8 Thermal-Metal Coater                                                       | 51     |

| 3.9 Thin-Film Analysis Methods                                                 | 52     |

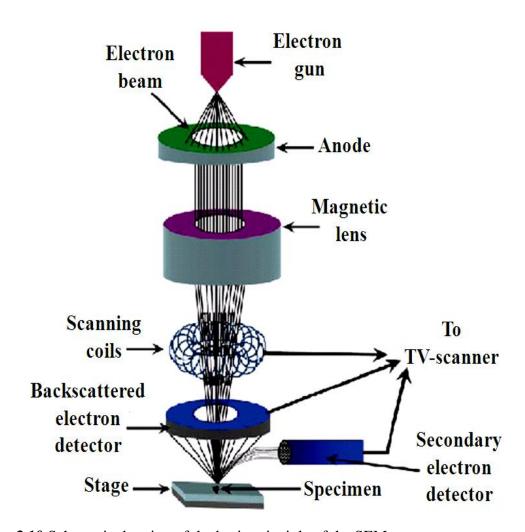

| 3.9.1 SEM                                                                      | 52     |

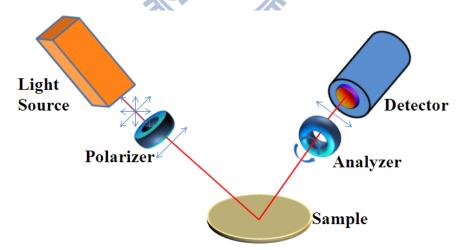

| 3.9.2 Ellipsometery                                                            | 54     |

| 3.9.2 Ellipsometery                                                            | 54     |

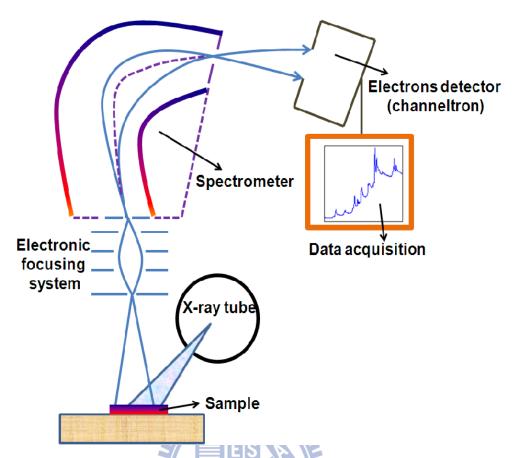

| 3.9.4 XPS                                                                      | 56     |

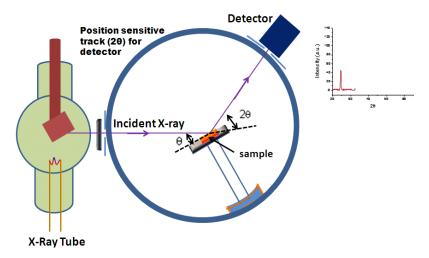

| 3.9.5 XRD                                                                      | 57     |

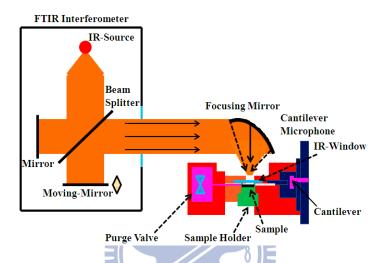

| 3.9.6 FT-IR                                                                    | 58     |

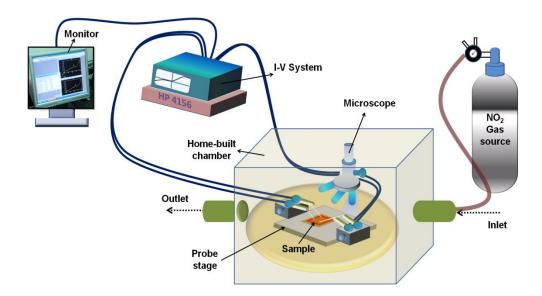

| 3.10 Electrical Measurements                                                   | 59     |

| 3.10.1 Four-Point Probe System                                                 | 59     |

|                                                                                |        |

| Chapter 4: Improved Reliability from a Plasma-As                               | sisted |

| Metal-Insulator-Metal Capacitor Comprising a High-k HfO <sub>2</sub> fi        | lm on  |

| a Flexible Polyimide Substrate                                                 | 61     |

| 4.1 Introduction                                                               | 61     |

| 4.2 Materials and Methods                                                      | 63     |

| 4.3 Results and Discussion                                                     | 66     |

| 4.3.1 Film Quality and Surface Roughness                                       | 66     |

| 4.3.2 Effect of O <sub>2</sub> -Plasma on HfO <sub>2</sub> Thin Film Formation | 66     |

| 4.3.3 Bending Treatment for Mechanical Flexability and Stability               | 77     |

| 4.4 Summary                                                                    | 79     |

| Chapter 5: Highly Reliable $Si_3N_4$ -HfO <sub>2</sub> Stacked Heteros                                       | tructure to  |

|--------------------------------------------------------------------------------------------------------------|--------------|

| Fully Flexible Poly-(3-hexylthiophene) Thin-Film Transiston                                                  | or81         |

| 5.1 Introduction                                                                                             | 81           |

| 5.2 Materials and Methods                                                                                    | 82           |

| 5.3 Results and Discussion                                                                                   | 85           |

| 5.3.1 Effect of Passivation Layer on Leakage-Current Density                                                 | 85           |

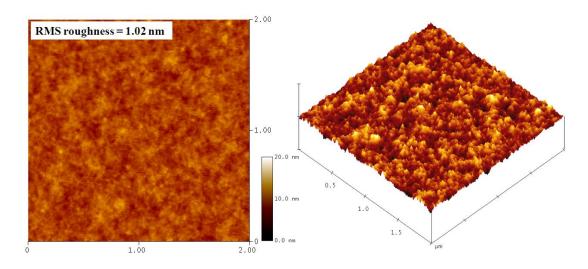

| 5.3.2 Surface Morphology of P3HT Film                                                                        | 88           |

| 5.3.3 Transfer and Output Characteristics                                                                    | 89           |

| 5.3.4 Bending Treatment to Three-Ponts Bending Conditions                                                    | 93           |

| 5.3.5 Improved Device Stability in Air                                                                       | 95           |

| 5.4 Summary                                                                                                  | 96           |

| Chapter 6: Facile Synthetic Route to Implement a Fully Organic Metal-Insulator-Semiconductor Device on Polyi | mide Sheet   |

| 6.1 Introduction                                                                                             | 97           |

| 6.2 Materials and Methods                                                                                    | 99           |

| 6.2 Materials and Methods  6.3 Results and Discussion                                                        | 104          |

| 6.3.1 Film Quality and Surface Roughness of nc-TiO <sub>2</sub>                                              |              |

| 6.3.2 XRD Analysis                                                                                           |              |

| 6.3.3 XPS Analysis                                                                                           | 108          |

| 6.3.4 Water Contact Angle Measurements for nc-TiO <sub>2</sub> film                                          | 110          |

| 6.3.5 Surface Analysis Study for Organic Pentacene Film                                                      | 113          |

| 6.3.6 Electrical Measurements from Pentace/TiO2-Au/Cr/PI Str                                                 | ructured MIS |

| Device                                                                                                       | 115          |

| 6.3.7 Real-Life Flexibility Test                                                                             | 120          |

| 6.4 Summary                                                                                                  | 123          |

| Chapter 7: Novel Chemical Route to Produce a New Poly                                                        | mer Blend    |

| Gate Dielectric for Flexible Low-Voltage Organic                                                             | Thin-Film    |

| Transistor                                                                                                   | 125          |

| 7.1 Introduction                                                                                             | 125          |

| 7.2 Materials and Methods                                                                                    | 127          |

| 7.3 Results and Discussion                                  | 132                      |

|-------------------------------------------------------------|--------------------------|

| 7.3.1 P123-PS Film Quality and Surface Roughness            | 132                      |

| 7.3.2 FT-IR Analysis                                        | 135                      |

| 7.3.3 Water Contact Angle Measurements for P123-PS Film     | 136                      |

| 7.3.4 Electrical Measurements from MIM Capacitor Device     | 139                      |

| 7.3.5 Pentacene: A Model for ordered Organic Semiconductors | 142                      |

| 7.3.6 Electrical Measurements from OTFT Device              | 146                      |

| 7.3.7 Flexibility Test for OTFT                             | 147                      |

| 7.4 Summary                                                 | 150                      |

|                                                             |                          |

| Chapter 8: Conclusions and Future Perspectives              | 151                      |

| Chapter 8: Conclusions and Future Perspectives              | 151                      |

| Chapter 8: Conclusions and Future Perspectives              | 151<br>151<br>153        |

| Chapter 8: Conclusions and Future Perspectives              | 151<br>151<br>153        |

| Chapter 8: Conclusions and Future Perspectives              | 151<br>151<br>153<br>155 |

# **List of Tables**

| Chapter 2                                                                           |

|-------------------------------------------------------------------------------------|

| Table 2-111                                                                         |

| List of typical properties of DuPont Kapton® polyimide film.                        |

|                                                                                     |

| Chapter 5                                                                           |

| Table 5-192                                                                         |

| Comparison of various dielectric layers and corresponding electrical performance of |

| Chapter 6  Table 6-1                                                                |

| leakage current, substrate type and growth temperature                              |

| Chapter 7                                                                           |

| Table 7-1142                                                                        |

| Comparison of electrical properties of various low-k dielectric materials           |

# **List of Figures**

| Chapter 1                                                                                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.1                                                                                                                                                            |

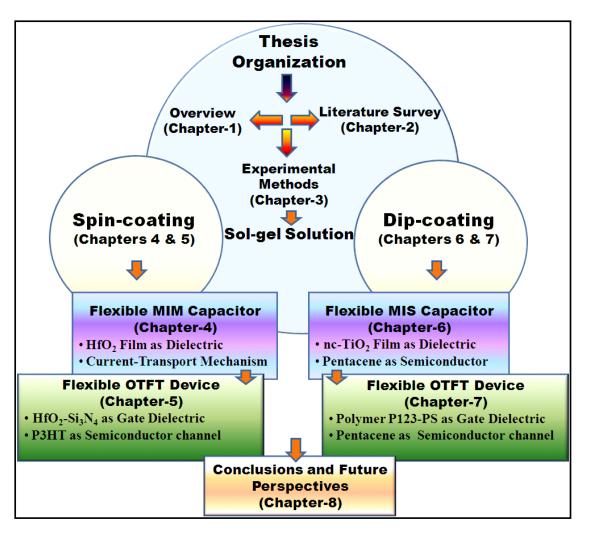

| Schematic representation of thesis organization showing eight chapters sequencly.                                                                                     |

| Chapter 2                                                                                                                                                             |

| Figure 2.19                                                                                                                                                           |

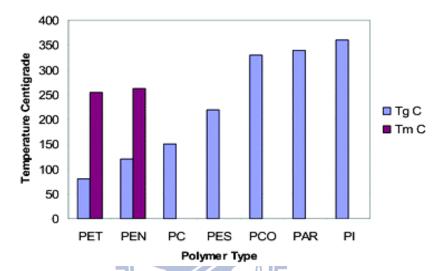

| The comparison of plastic substrates by $T_g$ of interest for applications in flexible electronics.                                                                   |

| Figure 2.210                                                                                                                                                          |

|                                                                                                                                                                       |

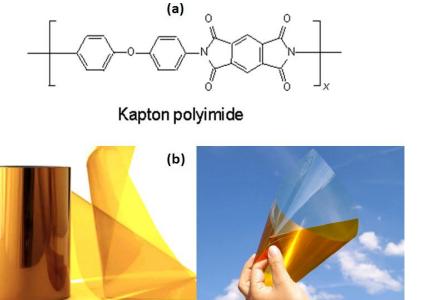

| (a) Molecular structure of polyimide Kapton® and (b) typically Kapton® films of                                                                                       |

| amber color near-transparent for applications in flexible electronics.                                                                                                |

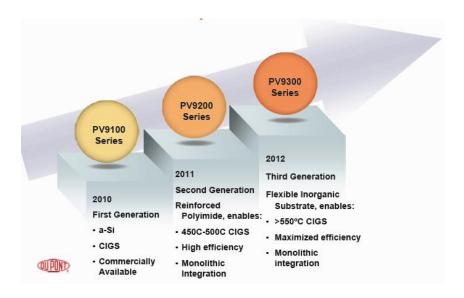

| Figure 2.3. 1896                                                                                                                                                      |

|                                                                                                                                                                       |

| Technology Roadmap: DuPont Kapton® polyimid films for flexible and thin-film                                                                                          |

| photovoltaic substrates.                                                                                                                                              |

| Figure 2.4                                                                                                                                                            |

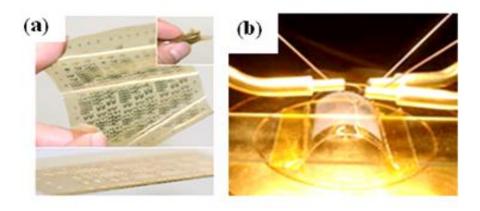

| (a) Photographs of a polyimide substrate with functional organic TFTs bending mode,                                                                                   |

| and (b) The device was bent at a radius of curvature 20 mm.                                                                                                           |

| Figure 2.5                                                                                                                                                            |

| Figure 2.5                                                                                                                                                            |

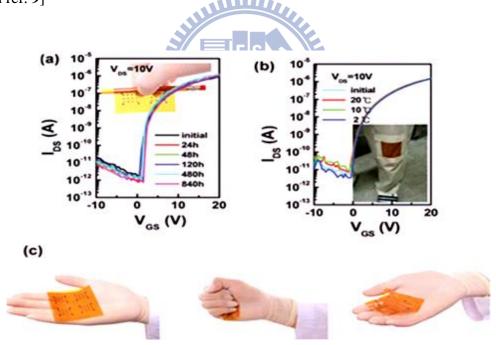

| Electrical characteristics and "real-life flexibility tests" of the ZnO-TFTs without                                                                                  |

| passivation, subjected to various bending conditions. (a) Variations in the transfer                                                                                  |

| charateristics over a long bending period (while wrapped around a pencil). Even<br>though the flexible device was mechanically stressed for approximately a month, no |

| electrical parameters changed. (b) One array of 48 TFTs on a flexible large-area                                                                                      |

| substrate was virtually characterized for "wearable applications" under different                                                                                     |

| temperatures and humidities (c) Demonstration of the foldable test. Flexible arrays                                                                                   |

| were repeatedly crumpled in the palm of the hand.                                                                                                                     |

| were repeatedry crumpied in the pann of the fland.                                                                                                                    |

| Figure 2.615                                                                                                                         |

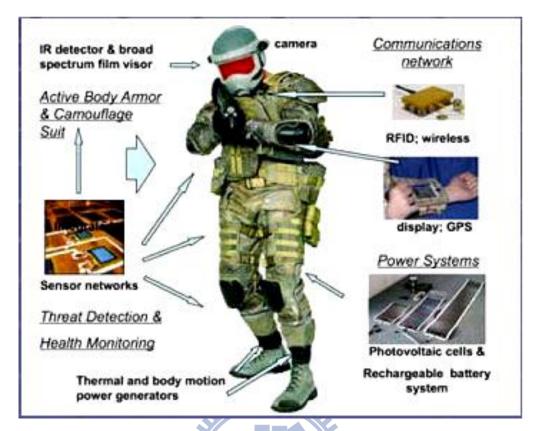

|--------------------------------------------------------------------------------------------------------------------------------------|

| The Paper flexible electronics: The soldiers to shed as much as 20 lbs of equipment.                                                 |

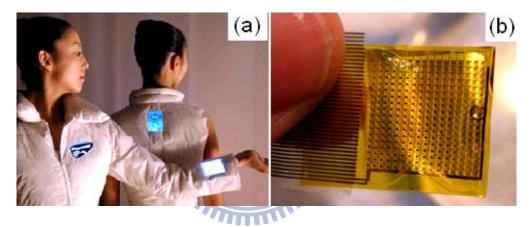

| Figure 2.716                                                                                                                         |

| (a) The Paper Phone prototype with flexible E-Ink display features bends gesture input recognition, (b) The Nokia 888 concept phone. |

| Figure 2.816                                                                                                                         |

| (a) Integrates electronic devices into textiles, like clothing and (b) Flexible heart sensor array.                                  |

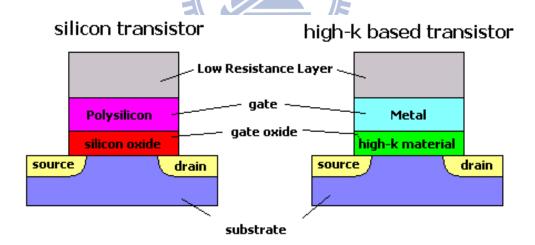

| Figure 2.9                                                                                                                           |

| High-k used in semiconductor manufacturing processes which replaces the $\mathrm{SiO}_2$ gate dielectric                             |

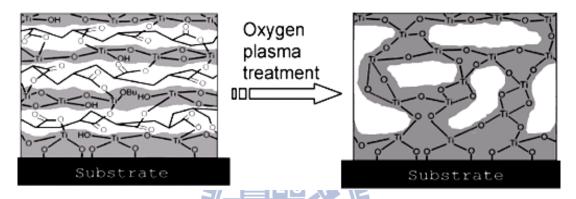

| Figure 2.10                                                                                                                          |

| Low-temperature oxygen plasma treatments on titania/PAA nanocomposite film.  Figure 2.11                                             |

| Figure 2.11                                                                                                                          |

| Schematic of metal-insulator-metal structured capacitor.                                                                             |

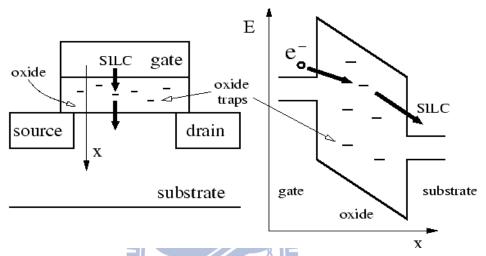

| Figure 2.1223                                                                                                                        |

| Schematic plots of the trap generation in the gate oxide. The presence of traps in the                                               |

| energy barrier yields the trap assisted tunneling mechanism.                                                                         |

| Figure 2.13                                                                                                                          |

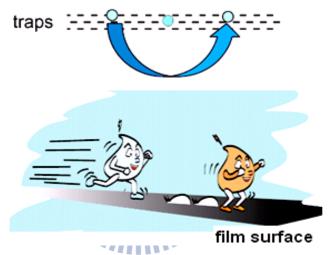

| Schematic pictures to represent the traps over film surface.                                                                         |

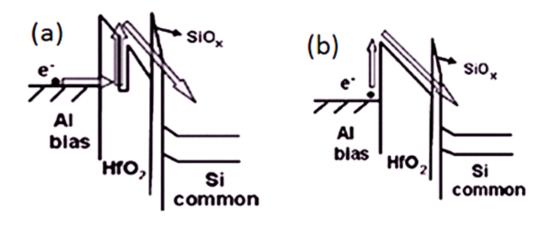

| Figure 2.14                                                                                                                          |

| (a) Schematic energy band diagram for HfO <sub>2</sub> film to explain Pool–Frenkel effect and                                       |

| (b) Schematic energy band diagram to explain the Schottky-Richardson emission.                                                       |

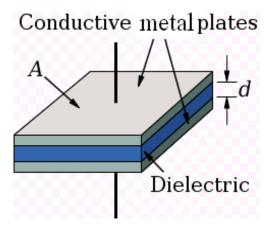

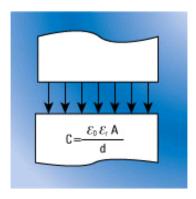

| Figure 2.15                                                                                                                          |

| The plates are metallic and they are separated by a distance $(d)$ .                                                                 |

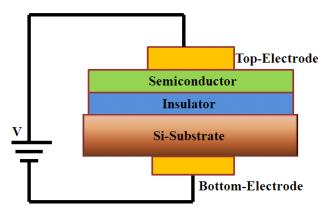

| Figure 2.16                                                                                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Schematic of metal-insulator-semiconductor structured capacitor.                                                                                                                                          |

| Figure 2.17                                                                                                                                                                                               |

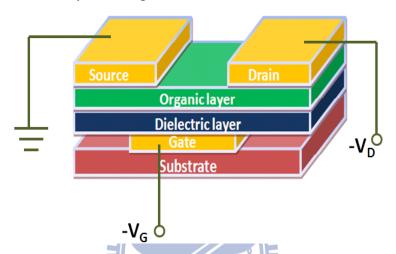

| Schematic structure of an organic thin-film transistor.                                                                                                                                                   |

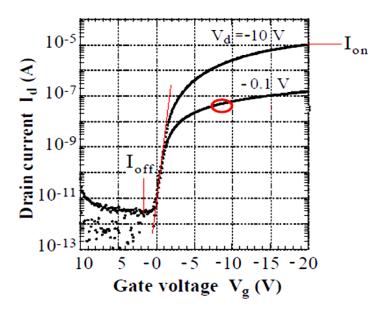

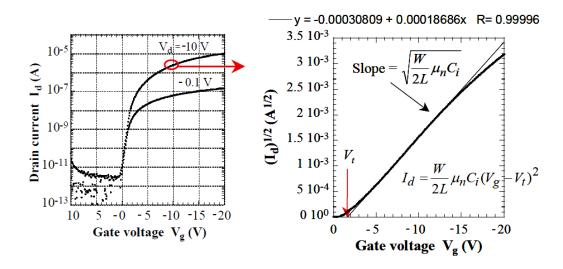

| Figure 2.1830                                                                                                                                                                                             |

| TFT transfer characteristics. ON current, OFF current, and sub-threshold form this plot.                                                                                                                  |

| Figure 2.1930                                                                                                                                                                                             |

| Drain current is plotted against gate voltage for the high drain voltage condition, $V_d$ = 10V. Threshold voltage ( $V_t$ ) and saturation mobility ( $\mu_{n,sat}$ ) can be extracted from such a plot. |

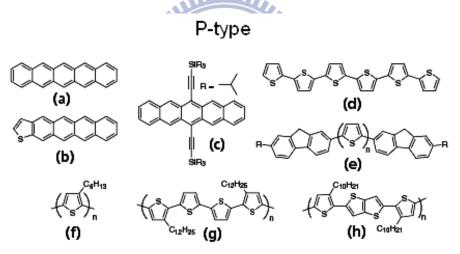

| Figure 2.20                                                                                                                                                                                               |

| Chemical structures of some representative p-channel organic semiconductors such as                                                                                                                       |

| (a) pentacene; (b) tetraceno[2,3-b]thiophene; (c) TIPS-pentacene; (d) a-sexithiophene                                                                                                                     |

| (e) oligothiophene-fluorene derivative; (f) regioregular(poly3-hexylthiophene); (g)                                                                                                                       |

| poly(3,3"'-didodecylquaterthiophene); (h) poly(2,5-bis(3-decylthiophen-2-yl)thieno                                                                                                                        |

| [3,2-b]thiophene).                                                                                                                                                                                        |

| Figure 2.2134                                                                                                                                                                                             |

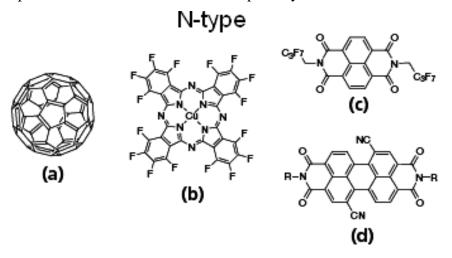

| Chemical structures of some representative n-channel organic semiconductors such as                                                                                                                       |

| (a) $C_{60}$ ; (b) hexadecafluoro copper phthalocyanine ( $F_{16}CuPc$ ); (c) naphthalene diimide                                                                                                         |

| derivative; (d) perylene diimide derivative.                                                                                                                                                              |

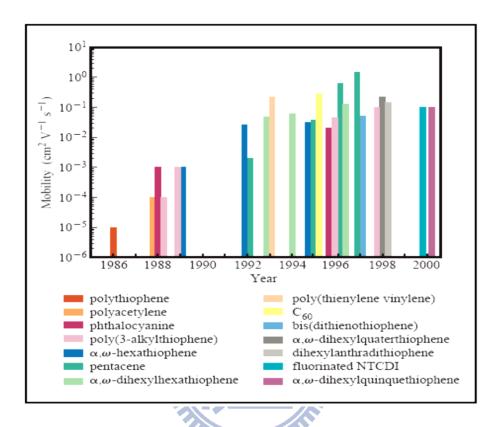

| Figure 2.2235                                                                                                                                                                                             |

| Chart showing different average electron mobility in commonly investigated                                                                                                                                |

| OTFT-semiconductor materials.                                                                                                                                                                             |

| Figure 2.23                                                                                                                                                                                               |

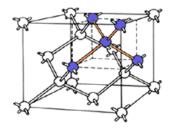

| Comparison between inorganic and organic semiconductor based material.                                                                                                                                    |

| Figure 2.24                                                                                                                                                                                               |

| Illustration of the highly ordered structures and arrangement may facilitate the                                                                                                                          |

| intermolecular hopping process.                                                                                                                                                                           |

| Chapter 3        |     |

|------------------|-----|

| Figure 3.1       | ••• |

| Experimental     | fl  |

| dielectrics of H | H(  |

|                  |     |

| Figure 3.140                                                                                 |

|----------------------------------------------------------------------------------------------|

| Experimental flowchart of fabrications of MIM capacitors using high-k gate                   |

| dielectrics of HfO2 film via surface sol-gel spin coating processes.                         |

|                                                                                              |

| Figure 3.2                                                                                   |

| Experimental flowchart of fabrication of MIS capacitor via dip-coating solution              |

| processes using nc-TiO <sub>2</sub> as gate dielectric and pentacene as semiconductor layer. |

| Figure 3.343                                                                                 |

| Experimental flowchart of fabrication of MIM and OTFT devices via dip-coating                |

| solution processes using P123-PS as gate dielectric and pentacene as semiconductor           |

| layer.                                                                                       |

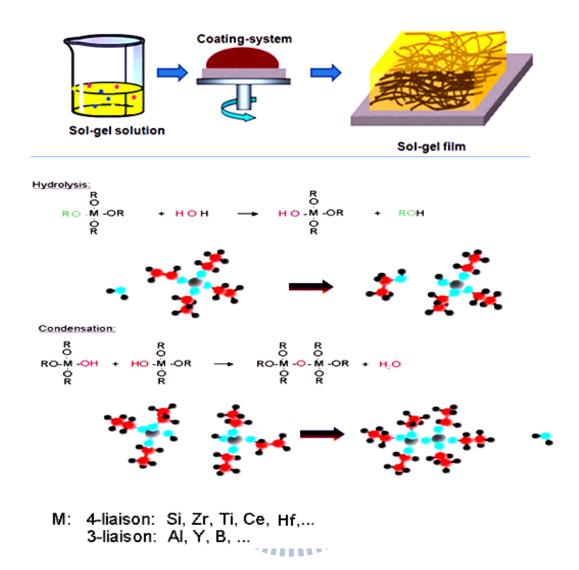

| Figure 3.445                                                                                 |

| The basic steps and the reaction of sol-gel process on substrate surface: Hydrolysis         |

| and condensation are influenced by partial substitutions of alcoolates groups with           |

| organic groups. 1896                                                                         |

| Figure 3.5                                                                                   |

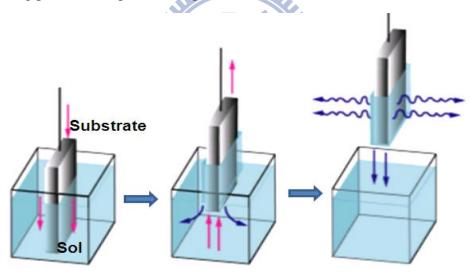

| The dip-coating process cycle.                                                               |

| Figure 3.648                                                                                 |

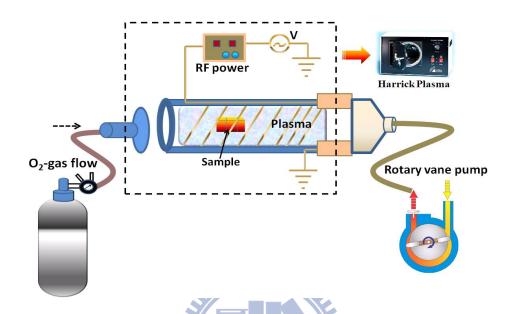

| The basic configuration of oxygen plasma system.                                             |

| The basic configuration of oxygen plasma system.                                             |

| Figure 3.7                                                                                   |

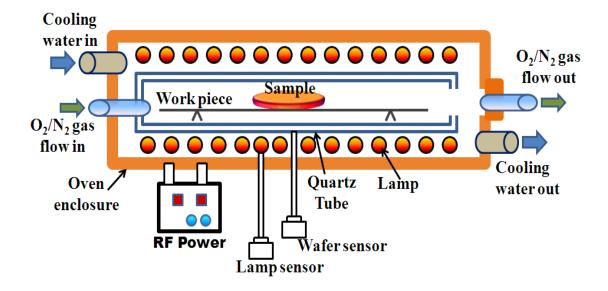

| Schematic configurations of thermal annealing system of quartz isolation tube with an        |

| oven enclosure and cooling system.                                                           |

| Figure 3.850                                                                                 |

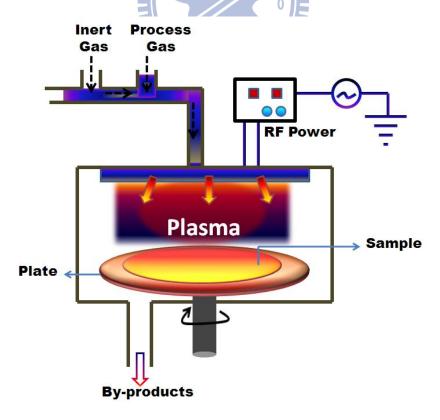

| Plasma Enhanced PECVD System.                                                                |

| •                                                                                            |

| Figure 3.9                                                                                   |

| General layouts for thermal evaporation method.                                              |

| Figure 3.1053                                                                                                                                                                                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Schematic drawing of the basic principle of the SEM.                                                                                                                                                                                                                               |

| Figure 3.1154                                                                                                                                                                                                                                                                      |

| The basic configuration of the ellipsometer                                                                                                                                                                                                                                        |

| Figure 3.1255                                                                                                                                                                                                                                                                      |

| Schematic drawing of the basic principle of the AFM.                                                                                                                                                                                                                               |

| Figure 3.1357                                                                                                                                                                                                                                                                      |

| General diagram of the basic principle of an XPS or ESCA setup.                                                                                                                                                                                                                    |

| Figure 3.1458                                                                                                                                                                                                                                                                      |

| General diagram of the basic principle of an XRD.                                                                                                                                                                                                                                  |

| Figure 3.15                                                                                                                                                                                                                                                                        |

| General diagram of the basic principle of an FT-IR                                                                                                                                                                                                                                 |

| Figure 3.16                                                                                                                                                                                                                                                                        |

| General layout of four-point probe station. 896  Chapter 4                                                                                                                                                                                                                         |

| Figure 4.165                                                                                                                                                                                                                                                                       |

| (a) Schematic representation of an MIM capacitor featuring a high-k $HfO_2$ thin film on a PI substrate in fabrication steps (i-v); (b) Photograph of our MIM capacitor on the flexible ultra-thin PI substrate; inset: unlimited bend test up to an angle of $360^{\circ}$ angle. |

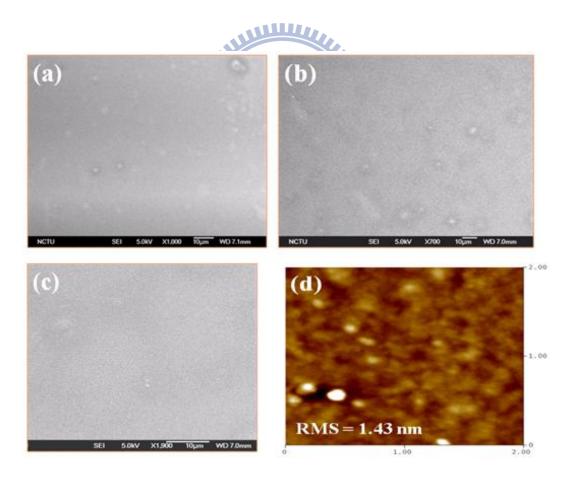

| Figure 4.267                                                                                                                                                                                                                                                                       |

| (a-c) Top-view SEM images of as-deposited $HfO_2$ films on $Cr/PI$ substrates after (a)                                                                                                                                                                                            |

| baking, (b) annealing at $250^{\circ}\text{C}$ for $12\ \text{h}$ , (c) sequential $O_2$ plasma treatment and                                                                                                                                                                      |

| annealing at 250°C for 12 h (OPT/A), (d) Tapping-mode AFM image of the film subject to OPT/A- treatment.                                                                                                                                                                           |

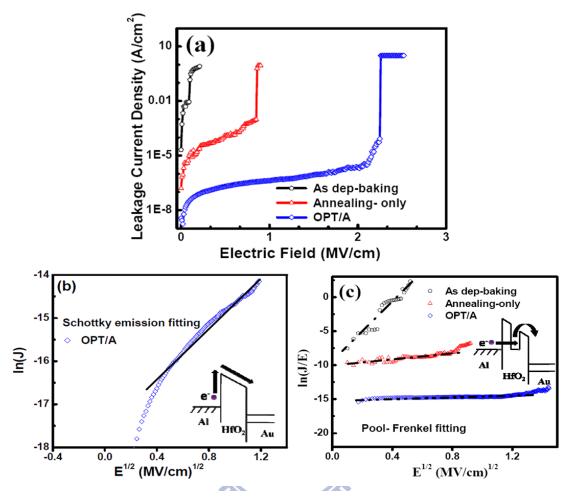

| Figure 4.369                                                                                                                                                                                                                                                                       |

| versus the square root of electric field ( $E^{1/2}$ ) for the OPT/A-treated sample. (c) Plot of $\ln(J/E)$ versus ( $E^{1/2}$ ) for the three samples. The corresponding schematic energy band diagram is presented to explain the S-R and P-F emissions.                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

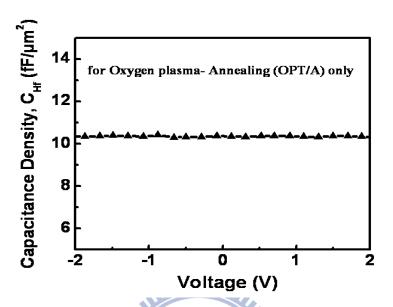

| Figure 4.4                                                                                                                                                                                                                                                                                      |

| Figure 4.5                                                                                                                                                                                                                                                                                      |

| Figure 4.6                                                                                                                                                                                                                                                                                      |

| (a) Low resolution XPS spectra of sol-gel deposited $HfO_2$ film on $Cr/PI$ substrate for as deposited-baking and annealing at 250 °C treated samples. (b) Low resolution XPS spectrum of the OPT/A-treated $HfO_2$ film on the PI substrate. Inset: XPS spectra in the BE regions of $C$ (1s). |

| Figure 4.8                                                                                                                                                                                                                                                                                      |

| Figure 4.9                                                                                                                                                                                                                                                                                      |

(a) Plots of leakage current density versus electric field under an applied positive voltage for samples prepared using all three treatment conditions. (b) Plot of ln(J)

**Chapter 5**

| Figure 5.184                                                                                                                                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (a) Schematic structure of P3HT-based OTFT with HfO <sub>2</sub> –Si <sub>3</sub> N <sub>4</sub> as a dielectric layer on                                                                                              |

| PI substrate; (b) the photograph of semi-transparent polyimide sheet; (c) photograph                                                                                                                                   |

| of proposed TFT device on a 30 µm-thick flexible PI substrate and under a large                                                                                                                                        |

| surface strain.                                                                                                                                                                                                        |

| Figure 5.287                                                                                                                                                                                                           |

|                                                                                                                                                                                                                        |

| (a) J-E Plot of leakage current density versus electric field for MIM-structural sample                                                                                                                                |

| prepared by using sol-gel HfO <sub>2</sub> film and inset of AFM image (surface roughness: 1.52                                                                                                                        |

| nm) from HfO <sub>2</sub> film; (b) <i>J-E</i> plot for MIM-structural sample prepared by using Si <sub>3</sub> N <sub>4</sub> -HfO <sub>2</sub> stacked film and inset of AFM image (surface roughness: 0.34 nm) from |

| Si <sub>3</sub> N <sub>4</sub> -HfO <sub>2</sub> stacked film; (c) schematic energy band diagrams to explain                                                                                                           |

| trap-dependent leakage and the passivation of traps.                                                                                                                                                                   |

| trup dependent reakage and the passivation of trups.                                                                                                                                                                   |

| Figure 5.389                                                                                                                                                                                                           |

| AFM image from P3HT thin film as channel area on $Si_3N_4$ – $HfO_2/Au/Cr/PI$ substrate                                                                                                                                |

| at a length scale of 2 µm (surface roughness: 1.02 nm).                                                                                                                                                                |

| Figure 5.4                                                                                                                                                                                                             |

| Figure 5.4                                                                                                                                                                                                             |

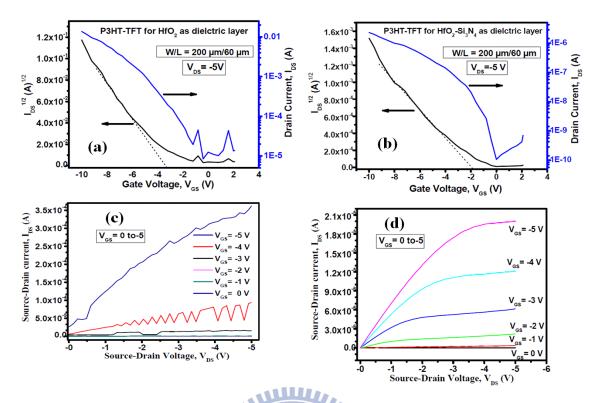

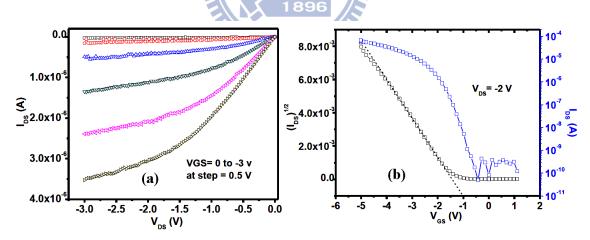

| (a) Plot of drain current and square root of drain current with respective to gate                                                                                                                                     |

| voltage (I <sub>DS</sub> -V <sub>GS</sub> ) for P3HT-OTFT on flexible PI substrate by using HfO <sub>2</sub> as gate                                                                                                   |

| dielectric under $V_{DS}$ =-5 V, and (b) output characteristic ( $I_{DS}$ - $V_{DS}$ ) as $V_{GS}$ ranging from                                                                                                        |

| 0 to -5.0 V at 1 V step for above device. (c) Plot of drain current and square root of                                                                                                                                 |

| drain current with respective to gate voltage ( $I_{DS}\text{-}V_{GS}$ ) for P3HT-OTFT on flexible P1                                                                                                                  |

| substrate by using $Si_3N_4$ -HfO $_2$ stacked film as gate dielectric under $V_{DS}$ =-5 V, and (d)                                                                                                                   |

| output characteristic ( $I_{DS}$ - $V_{DS}$ ) as $V_{GS}$ ranging from 0 to -5.0 V at 1 V step for above                                                                                                               |

| device.                                                                                                                                                                                                                |

| Et 5 5                                                                                                                                                                                                                 |

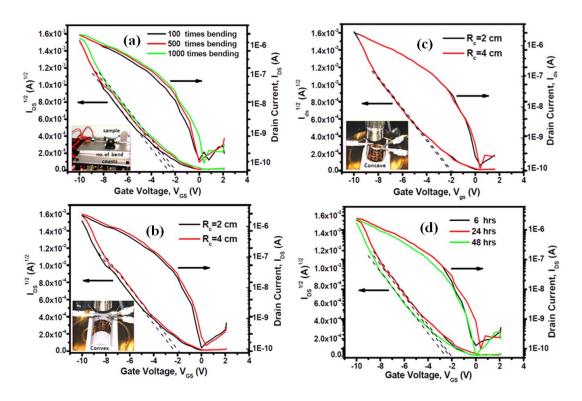

| Figure 5.5                                                                                                                                                                                                             |

| I <sub>DS</sub> -V <sub>GS</sub> plots for P3HT-OTFT by using Si <sub>3</sub> N <sub>4</sub> -HfO <sub>2</sub> stacked film as gate dielectric on                                                                      |

| flexible PI substrate: (a) bending time test and inset of customized-homemade                                                                                                                                          |

| bending system, (b) convex shape test and inset of convex setting, (c) concave shape test and inset of concave setting, and (d) time-dependent I <sub>DS</sub> -V <sub>GS</sub> characteristics over 6                 |

| hours, 1 day and 2 days.                                                                                                                                                                                               |

| nours, r day and 2 days.                                                                                                                                                                                               |

# Chapter 6

| Figure 6.1101                                                                                    |

|--------------------------------------------------------------------------------------------------|

| (a-e) Schematic illustration of the proposed synthetic solution proceeded                        |

| dip-coating approach for the preparation of the uniformed nc-TiO <sub>2</sub> film presented     |

| in this work.                                                                                    |

|                                                                                                  |

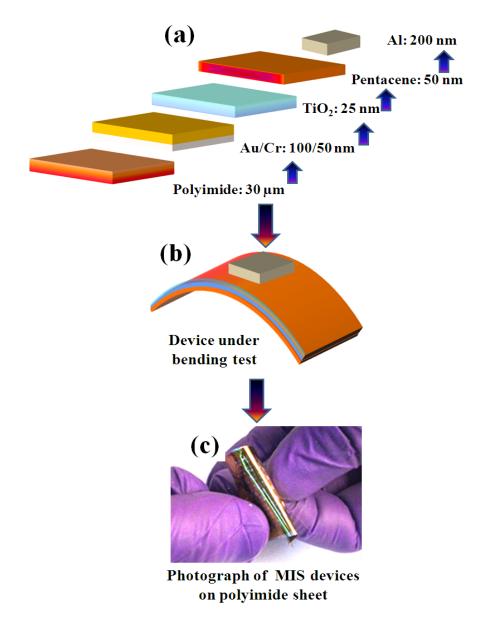

| Figure 6.2                                                                                       |

| (a) Schematic representation of an MIS device features a high-k TiO2 thin film and               |

| organic pentacene as semiconductor layer on a PI substrate in their fabrication                  |

| steps; (b) MIS device featuring a bend test. (c) Photograph of an array of MIS                   |

| devices on the flexible ultra-thin PI substrate.                                                 |

|                                                                                                  |

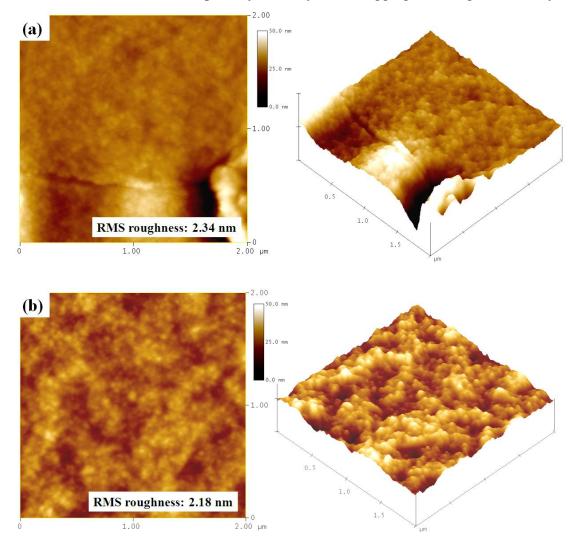

| Figure 6.3105                                                                                    |

| AFM images from thin film of nc-TiO <sub>2</sub> coated on Au/Cr/PI surface calcined at          |

| different temperatures conditions for (a) as-deposited then baking at $80  \text{C}$ , and (b)   |

| annealed in $O_2$ flow at 270 °C, 5 h.                                                           |

| Figure 6.4                                                                                       |

|                                                                                                  |

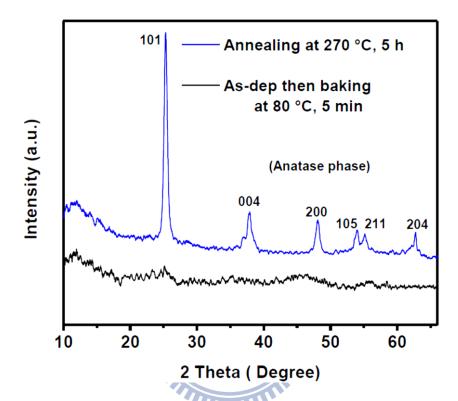

| XRD patterns from TiO <sub>2</sub> film surface sintered at baked at 80 °C, 5 min and annealed   |

| 270 °C, 5 h. I: intensity in arbitrary units, but the intensity scale is identical for both      |

| patterns.                                                                                        |

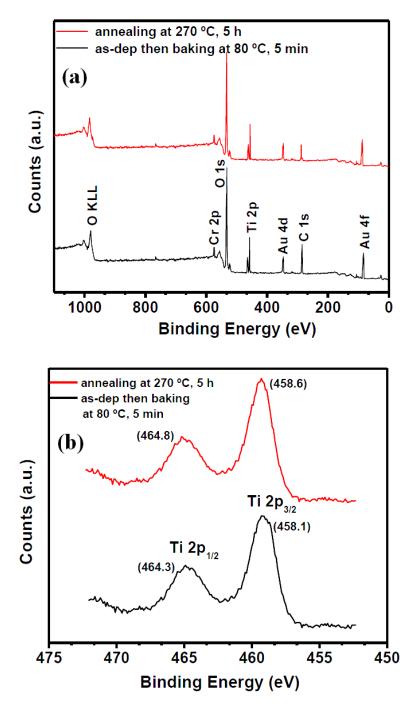

| Figure 6.5109                                                                                    |

|                                                                                                  |

| (a) Low resolution XPS spectra for dip-coated nc-TiO <sub>2</sub> film over Au/Cr/PI surface,    |

| and (b) high-resolution XPS spectra of the Ti 2p energy levels subjected to baking,              |

| and annealing at 270 $^{\circ}$ C, 5 h treatment conditions.                                     |

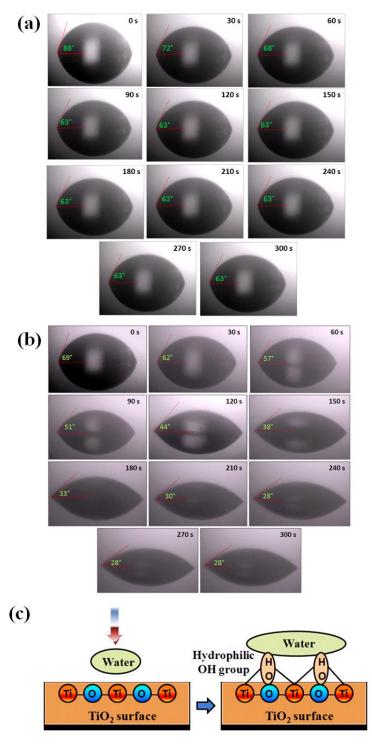

| Figure 6.6112                                                                                    |

| (a) Time-dependant change in contact angle of water droplet on a TiO <sub>2</sub> thin film      |

| dip-coated over Au/Cr/PI surface for 5 min, and (b) a schematic representation for the           |

| water drop exposed to the $TiO_2$ hydrophilic surface.                                           |

|                                                                                                  |

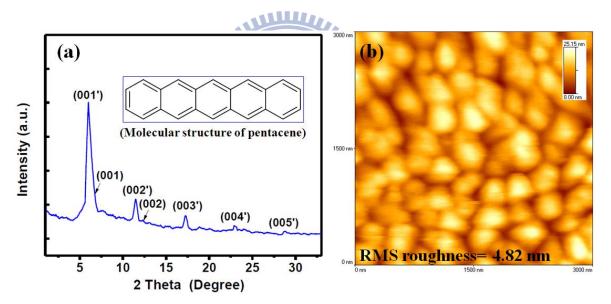

| Figure 6.7114                                                                                    |

| (a) X-ray diffraction pattern of the pentacene deposited over TiO <sub>2</sub> -Au/Cr/PI. Inset: |

| molecular structure of pentacene, (b) AFM image $(3\mu m \times 3\mu m)$ of the pentacene over   |

| TiO <sub>2</sub> -Au/Cr/PI.                                                                      |

|                                                                                                  |

| Figure 6.8117                                                                                    |

| (a) J-V characteristic when negative voltage applied, (b) Schottky emission $ln(J)$ versus the square root of the electric field $(V^{1/2})$ ; Inset: a schematic energy band diagram.                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 6.9                                                                                                                                                                                                            |

| Figure 6.10121                                                                                                                                                                                                        |

| Plots for J-R <sub>c</sub> measurement from out MIS device fabricated with nc-TiO <sub>2</sub> film; (a)                                                                                                              |

| convex shape test, (b) concave shape test.                                                                                                                                                                            |

| Figure 6.11                                                                                                                                                                                                           |

| Demonstration of the foldable test, one array of flexible MIS devices repeatedly                                                                                                                                      |

| Chapter 7  Figure 7.1                                                                                                                                                                                                 |

| structures.                                                                                                                                                                                                           |

| Figure 7.2129                                                                                                                                                                                                         |

| Schematic synthesis of triblock copolymer P123 and PS precursors mixed into toluene and chloroform employed for the fabrication of polymer P123-PS blend thin-film on a flexible PI substrate by dip-coating process. |

| <b>Figure 7.3</b>                                                                                                                                                                                                     |

| Figure 7.4                                                                                                                                                                                                            |

| (a) 11 11 mage from pure possessione from council of from the first substitute, where                                 |

|-----------------------------------------------------------------------------------------------------------------------|

| pinholes defective surface clearly viewed, and (b) AFM image from P123-PS blend film coated on flexible PI substrate. |

| Figure 7.5136                                                                                                         |

| FT-IR spectra from P123-PS thin film over flexible PI substrate.                                                      |

| r 1-1K spectra from F125-F5 tilli filli over flexible F1 substrate.                                                   |

| Figure 7.6137                                                                                                         |

| (a) The contact angle measurements for 0-60 min with the drop images at the point of                                  |

| contact on the P123-PS surface; (b) schematic representation of surface tension to                                    |

| calculate the surface energy for P123-PS surface.                                                                     |

| Figure 7.7140                                                                                                         |

| J-E plots from MIM structured device having PS film as gate insulator layer.                                          |

| Figure 7.8141                                                                                                         |

| (a) J-E and (b) C-V plots for MIM structured device fabricated with P123-PS blend                                     |

|                                                                                                                       |

| timi iiii as gate institator layet.                                                                                   |

| Figure 7.9                                                                                                            |

|                                                                                                                       |

| (a) AFM image (b) XRD pattern from pentacene film deposited on P123-PS film over                                      |

| Au/Cr/PI substrate, and (c) schematic representations of the orbital energies and the                                 |

| corresponding symmetries of molecular orbitals of a pentacene molecule in                                             |

| HOMO-LUMO states obtained from density-functional theory calculation.                                                 |

| Figure 7.10147                                                                                                        |

| Plots for OTFT (a) output characteristic ( $I_{DS}$ – $V_{DS}$ ), while $V_{GS}$ ranging from 0 to -5.0               |

| V at -1 V step, and (b) transfer characteristic ( $I_{DS}$ - $V_{GS}$ ), when $V_{DS}$ = -2 V.                        |

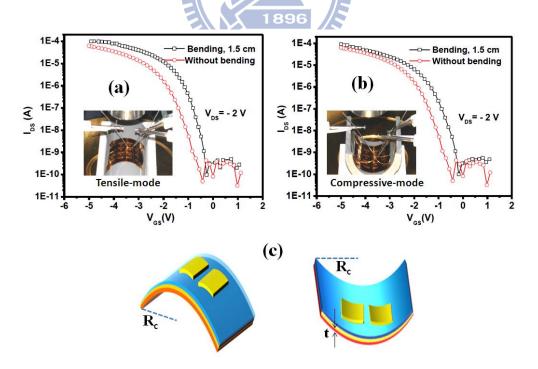

| Figure 7.11148                                                                                                        |

| $I_{DS}$ - $V_{GS}$ plots for OTFT, while device experiences (a) tensile mode for bending                             |

| deflection at 1.5 cm, (b) compressive mode at 1.5 cm; Inset: images show their                                        |

| respective actual images during measurement, (c) schematic geometries for flexible                                    |

| substrate, the thin film experiences tensile and compressive strain; $R_c$ : radius of                                |

| curvature, and t: thickness of substrate.                                                                             |

(a) AFM image from pure polystyrene film coated on flexible PI substrate, where

### List of Abbreviations

AFM Atomic Force Microscopy

ALD Atomic Layer Deposition

AMOLED Active Matrix Organic Light Emitting Display

ASTM American Society for Testing and Materials

BE Binding Energy

CA Contact Angle

DSSC Dye-Sensitized Solar Cell

ESCA Electron Spectroscopy for Chemical analysis

eV Electron Volt

GIDL Gate Induced Drain Leakage

GIXRD Grazing Incident X-ray Diffraction

HfO<sub>2</sub> Hafnium-Oxide

ITO Indium Tin Oxide

ITRS International Technology Roadmap for Semiconductors

LAE Large Area Electronics

LCD Liquid Crystal Display 1896

LED Light Emitting Diode

MIM Metal-Insulator-Metal

MIS Metal-Insulator-Semiconductor

MOCVD Metal Organic Chemical Vapor Deposition

MOS Metal Oxide Semiconductor

MOSFET Metal Oxide Semiconductor Field Effect Transistor

nc Nanocrystalline

OTFT Organic Thin-Film Transistor

OPT/A Oxygen Plasma Treatment then Annealing

P123-PS Pluronic P123-Polystyrene

Pa Pascal

PI Polyimide

PDMS Poly dimethylsiloxane

PECVD Plasma-Enhanced Chemical Vapor Deposition

PEN Poly-ether-sulfone

PET Polyethylene terephthalate

PVD Physical Vapor Deposition

RAM Random Access Memory

RF Radio Frequency

SEM Scanning Electron Microscopy

TEM Transmission Electron Microscopy

TiO<sub>2</sub> Titanium-Oxide

ULSI Ultra Large Scale Integrated

XRD X-ray Diffraction

XPS X-ray Photoelectron Spectroscopy

# **Chapter 1: Overview**

### 1.1Background

In recent years nanotechnology has become one of the most important and exciting forefront field in physics, chemistry, engineering and biology which the characteristic dimensions are below c.a. 1000 nm. It shows great promise for providing us in near future with many breakthroughs that will change the direction of technological advances in a wide range of applications. Advances in materials and processing techniques for silicon electronics continue to derive improvements in the speed and performance of a wide range of devices for consumer electronics. More recent research efforts seek to develop unconventional materials and processing techniques for completely new type of electronics systems. This class of circuitry will be important (at least initially) not because of its potential for high speed, density etc., but because it can be mechanically flexible, lightweight, durable and easy to manufacture over large areas. The use of plastic-based substrates coupled with recent developments in solution deposition and injects printing for laying down organic light emitting polymers and active matrix TFT arrays opens up the possibility of cost effective processing in high volumes by use of roll-to-roll processing. That complement the types of systems that conventional electronics supports well (microprocessors, high-density RAM etc.). This field is new (i.e., there are no entrenched technologies) and it has a strong materials content.

The rapid increase in the power of computers described by Moore's Law has relied essentially on the down-scaling of the planar MOSFET. The smallest dimension in this structure is the thickness of the gate dielectric. In the past, the dielectric of choice was SiO<sub>2</sub> but the scaling requirements described in the ITRS require the

thickness of the SiO<sub>2</sub> to go well below 1 nm. At this level, the leakage current due to tunneling rises unacceptably and atomic limitations come into play, as discussed by Muller et al. Since the gate capacitance is a key parameter, one approach to overcoming such problems is to use a dielectric with a higher permittivity, so that the same gate capacitance is achieved with a higher physical thickness is equally important. Moreover, silicon and silicon-based components require millions of gallons of water and temperatures of 500-800 °C to manufacture. Polymers are lighter and can cost much less to manufacture, although cost comparisons vary as well as create components at atmospheric pressure, and at temperatures of no more than 150 °C than silicon. As a result, there are considerable opportunities for innovation and basic scientific research into new types of electronics materials and methods for patterning them into large-area and low-cost circuits.

The semiconductor industry uses hundreds of thousands of gallons of highly toxic solvents annually. The technologies being developed for flexible electronic devices to enable this all revolve around these building devices using eco-friendly materials and processing techniques. A piece of silicon for a fingerprint recognition device, that one-square-centimeter piece of highly purified silicon; which is quite large in terms of ultrapure silicon usage will be very expensive. And, the promise with organics is related to the lower cost of the raw materials, in particular the substrate on which the device is built a silicon wafer is more expensive than a sheet of plastic. Recently, in terms of their superior bending, it was found that flexible organic transistors can perform better than flexible inorganic transistors. The bending and stretching properties of flexible devices designed for bio-medical applications such as accurate sensors for hydrogen or for integration into artificial muscles or biological tissues.

### 1.2 Motivation and Purpose of the Thesis

This thesis focuses on the requirements and achievements to date on the topic of flexible transparent conductors, where high transparency and high conductivity are required. Worldwide research and design efforts are presented, both from research institutes and companies that are developing the necessary materials and processes. Several technical solutions available are compared, and forecasts are given for the next 10 years. The importance of TCF increasingly more and more flexible devices are required, from flexible displays for e-readers, OLEDs and other types to flexible photovoltaics and beyond. These devices require a conductor to close the layers of active materials, but that conductor needs to be transparent in applications such as displays and photovoltaics to allow light through. Today, transparent conductive oxides are widely used for rigid devices but these will become more expensive due to rare materials used, and are inadequate for most flexible electronics applications where they can easily crack under little strain. Alternatives are sought.

The goal of this project was to investigate the layers and the interfaces by selected high-k and low-k polymer dielectrics in device applications with the aim of improving the basic understanding of the outcomes of the deposition and processing methods. Although the technology of such films was developed to an extent, some fundamental problems remain unclear and only their solution can result in wide-scale commercialization of high-k films with very low thickness, especially as the efficient current leakage for portable flexible devices. The most critical problem is the development of efficient processing techniques, which would provide the long-term (for several thousand hours) operation of flexible devices without sacrificing their characteristics.

The principal techniques used were those of sol-gel spins coatings and dip-coating of these techniques were integral to the work of the project. The composite high-k materials of interest were also prepared by sol-gel techniques in order to gain more insight into the materials themselves. For the first time, we developed the process to deposit low-k film on flexible PI substrate via surface dip-coating solution process. We developed a low-temperature O2 plasma-enhanced technique for preparing HfO<sub>2</sub> thin film-based MIM capacitors as well as a flexible Si<sub>3</sub>N<sub>4</sub>–HfO<sub>2</sub> stacked poly–(3–hexylthiophene i.e., P3HT) p-type TFT on PI substrate using surface sol-gel techniques. We also investigated the O<sub>2</sub> plasma oxidation growth mechanism in different kinetic regimes to understand the surface oxidation process. The insulator properties of the films were determined; which showed low leakage currents and good capacitances. A bending test revealed that the capacitors on the PI surface showed very stable performance after bending up to 100,000 times, minimum up to 1 or 2 cm radii of curvature for both convex and concave type settings even after period of time about one month. The device's electrical properties with respect to saturation mobility, on/off current ratio, and bending conditions (i.e., the number of bends and the bending radii) are also investigated to use for many practical applications. As detailed above, international sematech withdrew part way through the project. The particular systems to be studied and the areas to be concentrated on were specified and modified in the light of developments in the field by discussion at regular project meetings with these partners.

Further, we demonstrate an innovative and easy-to-follow synthesis approach for deposit a new polymer blend film on organic flexible polyimide substrate by a dip-coating technique at low temperature (c.a. 100 °C). This method is the most desirable to open up the way of preventing the problem of pin-hole defects in pure thin (<100 nm) polystyrene film. We have used dip-coating process to deposit

nanocrystalline-TiO<sub>2</sub> film for their application in electronic devices at processing low temperature ( $\sim 200$  °C). It should be emphasize that this novel synthesis dip-coating method provides a new way to investigate the surface of polymeric blend films (< 50 nm) and could be a promising approach for practical applications since it is a low-cost and low-temperature manufacturing technique. Moreover, the results of this research support the idea of sustainable and environment friendly as useful for flexible electronics technology. Their detailed knowledge of developments and thinking in the field of flexible electronics were central object in ensuring that the key areas requiring the development of fundamental understanding are pursued.

# 1.3 Thesis Organization