# 國立交通大學

電子工程學系 電子研究所碩士班

## 碩士論文

一個具正交相位和增益誤差校準之 5-GHz 直接 降頻射頻接收器

A 5-GHz Direct Conversion Receiver with I/Q Phase and Gain Error Calibration

研究生:李宗霖

指導教授:陳巍仁 博士

中華民國九十三年十月

# 一個具正交相位和增益誤差校準之 5-GHz 直接

## 降頻射頻接收器

# A 5-GHz Direct Conversion Receiver with I/Q Phase and Gain Error Calibration

研究生: 李宗霖Student : Tsorng-Lin Lee指導教授: 陳巍仁 博士Advisor : Wei-Zen Chen

國立交通大學 電子工程學系 電子研究所碩士班 碩士論文

## Submitted to Department of Electronics Engineering & Institute of

A Thesis

Electronics

College of Electrical Engineering and Computer Science

National Chiao Tung University

In Partial Fulfillment of the Requirements

for the Degree of

Master of Science

In

**Electronic Engineering**

July 2004

Hsin-Chu, Taiwan, Republic of China

中華民國九十三年十月

# 一個具正交相位和增益誤差校準之 5GHz 直接降頻射頻接收器

研究生: 李宗霖 指導教授: 陳巍仁 博士

國立交通大學

電子工程學系電子研究所碩士班

#### 摘要

近年來無線區域網路如 IEEE 802.11a 和 HIPER LAN 的發展,吸引許多相關 方面研究其傳送接收器。隨著系統晶片整合的時代來到,對低成本射頻傳送接收 器的需求更為強烈。而採用直接降頻架構的寬頻無線傳送接收器具有需求較少外 部元件的優勢,因此能達到低成本的目標。這架構因此吸引本篇論文研究。本篇 論文描述設計一個適用於無線區域網路應用之 5GHz,具可變增益直接降頻接收 器。而本地振盪器之頻率定為所欲接收射頻頻率之三分之二來避免功率放大器所 造成的拉起現象以及本地振盪器和射頻信號接收端的交互作用。此外,還提出增 益和相位誤差校準技巧來補償正交信號路徑上的不匹配情形。測量到用來評估正 交誤差之鏡像排拒比為 28.25 分貝。射頻前端電路之轉換增益根據輸入信號功率 具可切換高低來配合下一級之動態操作範圍。它可達到在高增益模式下具有轉換 增益 28.2 分貝而在低增益模式下具有轉換增益 11.6 分貝。整體雜訊指收為 9.4 分貝而線性度為-6.8dBm(在有輸出緩衝器情況下)。藉由所提出正交校準方法, 所測量到的相位誤差小於 0.6 度以及增益誤差小於 0.2 分貝。晶片面積為 1.64mm<sup>2</sup> 和在 1.8V 的供應電壓下功率消耗 37.25mW。 此外,還實現一個操作在所欲接收頻帶三分之二的頻率合成器。設計之重點 主要在於最佳化相位雜訊效能,和利用所提出的具電流匹配之電荷充放器有效地 降低參考信號雜頻。晶片面積為 1.06mm<sup>2</sup> 以及在 1.8V 的供應電壓下功率消耗 14.4mW。

# A 5-GHz Direct Conversion Receiver with I/Q Phase and Gain Error Calibration

Student: Tsorng-Lin Lee

Advisor: Wei-Zen Chen

Department of Electronics Engineering & Institute of Electronics

#### National Chiao-Tung University

Abstract

Wireless Local Area Networks (WLANs) based on IEEE 802.11a and HIPER LAN have drawn transceiver research efforts and turn widely deployed in recent years. With the coming of soc era, a low cost RF transceiver is in strong demand. For wide band wireless transceiver direct conversion architecture is a superior candidate for fewer external required components, thus low cost design goal can be achieved. This activates the research of this work. This thesis describes the design of a 5GHz, variable gain, and direct conversion receiver for wireless LNA application. The LO frequency is set to be 2/3 of required RF frequency to avoid PA pulling and LO-RF interaction. Furthermore, gain and phase error calibration techniques are proposed to compensate mismatches in the I/Q signal path. Measured image-rejection ratio for evaluating I/Q error is about 28.2dB. The conversion gain of the RF front-end is variable to slide the available dynamic range of the following stages based on the input power level. It performs a conversion gain of 28.2 dB in the high gain mode and 11.6 dB in the low gain mode. The overall noise figure (SSB) is 9.4dB and IIP3 is about -6.8dBm (with output buffer). By means of I/Q calibration techniques, the measured phase error is less than  $0.6^{\circ}$  and gain error is less than 0.2 dB. It consumes chip area of 1.64mm<sup>2</sup> and power of 37.25mW at 1.8V supply voltage.

Additionally, a frequency synthesizer operating at 2/3 of required RF frequency has been implemented. The design issue is to optimize the phase noise performance and effectively reduce reference spur from mismatches by employing proposed current-match charge pump. It consumes chip area of 1.06mm<sup>2</sup> and power of 14.4mW at 1.8V supply voltage.

### 誌謝

回顧快兩年的碩士求學生涯,在這段時光裡充滿了許多回憶,一點一滴在心 中,將是我這生中最珍貴的寶藏。

首先要感謝的是我的指導教授陳巍仁博士。老師對研究的執著,認真,以及 實事求是,深深影響我求學和做事的態度。能夠接受老師的指導,我覺得是非常 可貴的,在此也非常感謝老師對我的"發包"上的容忍,指導上的耐性,以及對我 的照顧,在此還是要再向老師說聲感謝。此外,能在 307 這個資源豐富的大家族 做研究,是非常幸福的,在此也要向 307 的每位老師和學長說聲謝謝。

接著要感謝的是一起打拼的同 group 戰友, 阿甘、家華、大新、騰毅、洪濤、 偉茗、冠勝、以及帥哥宗霖等, 大家一起做研究、打屁、互相切磋, 這段友誼和 發生的糗事將長存在我心中。還有學長姊們, 周忠昀(老大)、阿傑、小白、文蕙、 繼堯、奈良、仁鴻、傅昶綜、烜毅、陳榮昇、狗哥, 以及我認識幫助過我的人, 感謝你們在我論文研究的瓶頸或是晶片量測的疑難雜症上都給了我很多的方向 及幫助。

還有 527 的同學們,丁董、大頭、阿爛(嵐)、旻珓、雄霆、如琳、秉捷(精 王)、瑋仁、權哲、棋樺、聖文、阿瑞、秦豪哥、煒明、周政賢、蘇紀豪等,我 只想說一句話:那就是有你們真好,有你們陪伴,才會有那段回味無窮的回憶, 就算是時光也不能讓這段回憶消逝。除此外好友政良、宗良、鳥逸也是這條路上 的好伙伴。

學弟台佑、岱原、小幾九、小西西、諭哥、家熒、國慶、建文、啟賓、立龍、 弼嘉、淵文也感謝你們的支持和幫助,能有緣認識大家真好。

最後要感謝我的家人以及我的女友洪小易小姐。感謝他們多年來默默的關心 與支持,在我最需要的時候給予最大的幫助,使我能勇往向前,一路走來直至今 日。謹以此論文獻給我關心的人。

> 李宗霖 九十三年十月

V

## CONTENTS

| ABSTRACT (CHINESE)                                             | i         |

|----------------------------------------------------------------|-----------|

| ABSTRACT (ENGLISH)                                             |           |

| ACKNOWLEDGEMENT                                                |           |

|                                                                |           |

| CONTENTS                                                       |           |

| TABLE CAPTIONS                                                 |           |

| FIGURE CAPTIONS                                                | X         |

| Chapter 1 Introduction                                         | 1         |

| 1.1 Background                                                 | 1         |

| 1.1 Background<br>1.2 Motivation                               | 2         |

| <b>1.2.1</b> Optimum between gain, noise figure, and linearity | 2         |

| 1.2.2 Avoid VCO pulling for transceiver integration            | 3         |

| 1.2.3 Provide precise I/Q output                               |           |

| 1.3 Organization                                               |           |

| Chapter 2 Quadrature LO Generator with I/Q N                   | /lismatch |

| Calibration                               | 6  |

|-------------------------------------------|----|

| 2.1 Phase-calibrated LO Generator         | 6  |

| 2.2 Phase Calibration Verification        | 9  |

| 2.3 Gain-calibrated Down-conversion Mixer | 15 |

| 2.4 Circuit Realizations                  | 16 |

| 2.4.1 Complementary VCO                   | 16 |

| 2.4.2 Divide-by-2 divider                 | 17 |

| 2.4.3 Source Couple Pair Adder            |    |

| 2.5 Simulation result                     | 19 |

| 2.6 Measurements                          | 23 |

| 2.6.1 Measurement Setup                   | 23 |

| 2.6.2 Measurement Results                 |    |

# **Chapter 3 Front-End Receiver with I/Q Mismatch**

| Calibration                                                  | 32 |

|--------------------------------------------------------------|----|

| 3.1 Front-End Link Budget                                    |    |

| 3.2 Low Noise Amplifier Design                               |    |

| 3.2.1 Principle of the circuit design                        |    |

| 3.2.2 Input matching.                                        |    |

| 3.2.3 Optimum Noise Figure Analysis [13]                     |    |

| 3.2.4 Gain                                                   | 41 |

| 3.2.5 Shielded PAD (RF PAD)                                  |    |

| <b>3.2.6</b> LNA Simulation                                  | 42 |

| 3.3 Down-Conversion Mixer                                    | 45 |

| <b>3.3.1</b> Principle of the circuit design                 | 45 |

| 3.3.2 Noise Analysis                                         | 46 |

| 3.3.2 Mixer Simulation                                       |    |

| 3.4 Adaptive Biasing VCO                                     | 49 |

| 3.4.1 Principle of the circuit design                        | 50 |

| 3.4.2 Phase Noise Analysis                                   | 52 |

| <b>3.4.2</b> Phase Noise Analysis.     3.4.3 VCO Simulation. | 53 |

| 3.5 Receiver Simulation                                      | 54 |

| 3.6 Measurements                                             | 57 |

| 3.6.1 Measurement setup                                      | 57 |

| 3.6.2 Measurement Results                                    | 60 |

| Chapter 4 Low Spur Frequency Synthesizer                     | 72 |

| 4.1 Architecture and specification                           |    |

| 4.2 Phase Noise Consideration                                |    |

| 4.3 Circuit implementations                                  | 75 |

| <b>4.3.1</b> vco                                             |    |

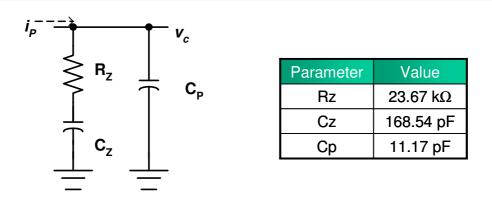

| 4.3.2 Loop filter                                            |    |

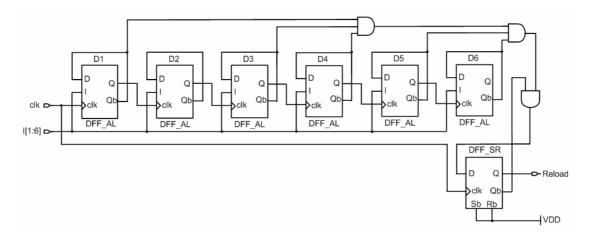

| 4.3.3 Programmable frequency divider                         | 76 |

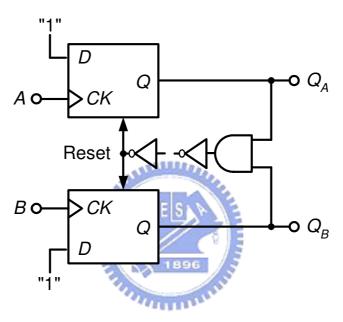

| <b>4.3.4</b> PFD                                             | 79 |

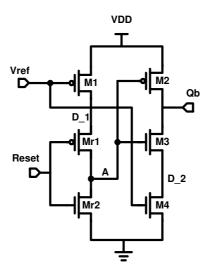

| 4.3.5 Charge pump                                            | 80 |

| 4.4 Simulation Results                                       | 80 |

| Chapter 5 Conclusions                                        | 85 |

| REFERENCES                                                   | 87 |

# **TABLE CAPTIONS**

| Table 1.1 Design target                                                    | 5  |

|----------------------------------------------------------------------------|----|

| Table 2.1 Performance summary                                              | 22 |

| Table 2.2 Measured performance summary                                     | 31 |

| Table 3.1 Estimated front-end link budget (High gain mode / Low gain mode) | 34 |

| Table 3.2 Summary of the LNA                                               | 44 |

| Table 3.3 Summary of the mixer                                             | 49 |

| Table 3.4 Summary of the VCO                                               | 54 |

| Table 3.5 Simulated summary of the receiver                                | 56 |

| Table 3.6 Measurement summary of the receiver                              | 71 |

| Table 4.1 Specification and design target                                  | 73 |

| Table 4.2 Allocated division number                                        | 77 |

| Table 4.3 Synthesizer performance summary                                  | 84 |

# **FIGURE CAPTIONS**

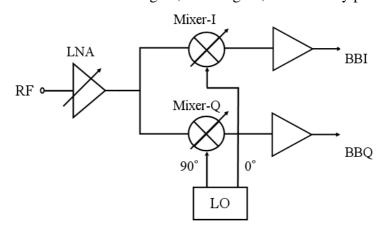

| Fig. 1.1 Programmable conversion gain in the front-end design                     | 2   |

|-----------------------------------------------------------------------------------|-----|

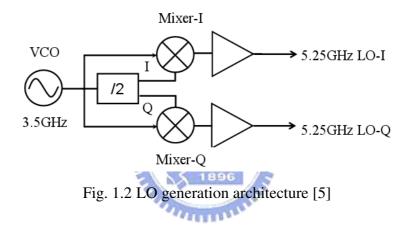

| Fig. 1.2 LO generation architecture [5]                                           | 3   |

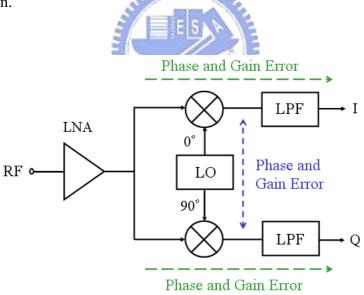

| Fig. 1.3 I/Q mismatch contributions by various stages                             | 4   |

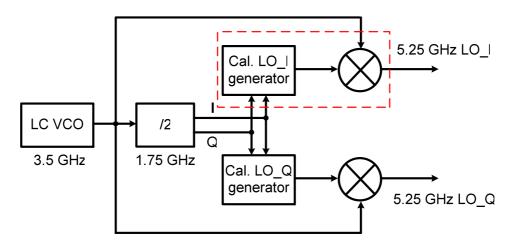

| Fig. 2.1 Calibrated LO generator architecture                                     | 7   |

| Fig. 2.2 Phase compensation concept                                               | 8   |

| Fig. 2.3 Phase-calibrated LO generator                                            | 8   |

| Fig. 2.4 Phase compensation concept                                               | 9   |

| Fig. 2.5 Relations between IRR, phase error, and magnitude error                  | 11  |

| Fig. 2.6 Relations between IRR, phase error, and magnitude error (3D)             | 11  |

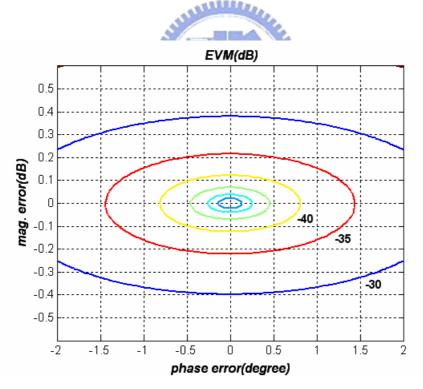

| Fig. 2.7 Relations between EVM, phase error, and magnitude error                  | 12  |

| Fig. 2.8 Monte Carlo simulations using Gaussian distribution                      | 13  |

| Fig. 2.9 Monte Carlo simulations using uniform distribution                       | 14  |

| Fig. 2.10 Monte Carlo simulations using Gaussian function                         | 14  |

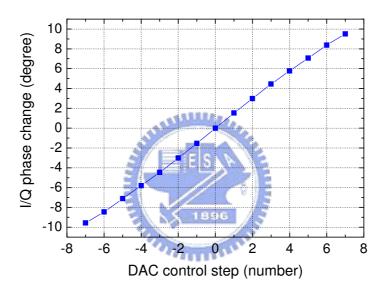

| Fig. 2.11 I/Q phase change versus DAC control step                                | 15  |

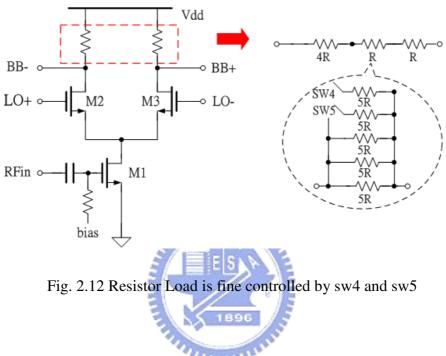

| Fig. 2.12 Resistor Load is fine controlled by sw4 and sw5                         | 16  |

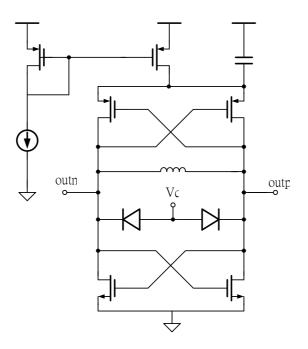

| Fig. 2.13 Complementary cross-coupled VCO                                         |     |

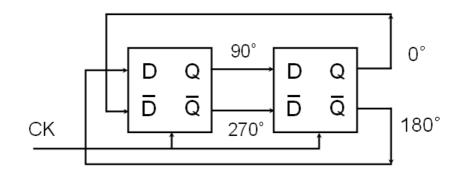

| Fig. 2.14 Divide-by-2 divider configuration                                       | 17  |

| Fig. 2.15 Divide-by-2 divider.                                                    | 18  |

| Fig. 2.16 Source couple pair adder                                                |     |

| Fig. 2.17 VCO differential output waveforms                                       | 19  |

| Fig. 2.18 Quadrature outputs of divide-by-2 divider                               | 19  |

| Fig. 2.19 Quadrature LO waveforms                                                 | 20  |

| Fig. 2.20 Down-conversion wanted signal                                           | 20  |

| Fig. 2.21 Down-conversion image signal                                            | 20  |

| Fig. 2.22 Spectrum of quadrature outputs of divide-by-2 divider                   | 21  |

| Fig. 2.23 Spectrum of down-conversion wanted signal                               | 21  |

| Fig. 2.24 Spectrum of down-conversion image signal                                | 22  |

| Fig. 2.25 Chip microphotograph of quadrature LO generator                         | 23  |

| Fig. 2.26 Bonding board                                                           | 24  |

| Fig. 2.27 Plugging DC board with bonding board                                    | 24  |

| Fig. 2.28 Measurement setup diagram of quadrature phase-calibrated LO generator   | r   |

| with image rejection mixers                                                       | 25  |

| Fig. 2.28 Quadrature hybrid (a) photograph (b) phase difference between port of R | F_I |

| and RFQ (c) gain error between port of RF_I and RF_Q                              | 26  |

| Fig. 2.29 I/Q port input matching                                                 | 27  |

| Fig. 2.30 Down-conversion signal from Q path                                      | 27  |

| Fig. 2.31 Down-conversion signal from I path                         | 28 |

|----------------------------------------------------------------------|----|

| Fig. 2.32 Down-conversion signal from Q path                         | 28 |

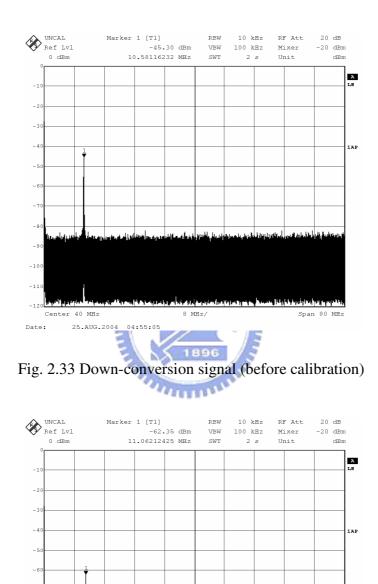

| Fig. 2.33 Down-conversion signal (before calibration)                | 29 |

| Fig. 2.34 Down-conversion image (before calibration)                 | 29 |

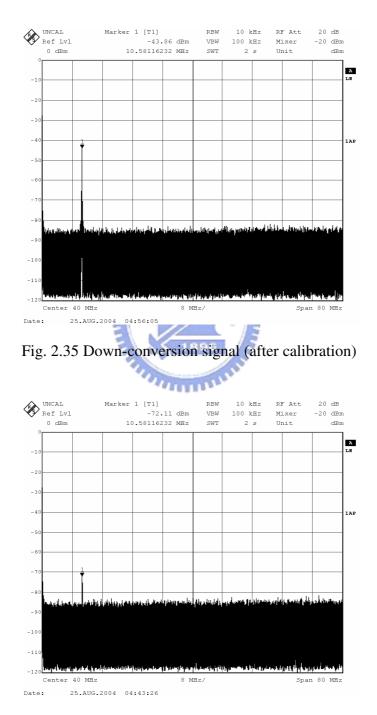

| Fig. 2.35 Down-conversion signal (after calibration)                 | 30 |

| Fig. 2.36 Down-conversion image (after calibration)                  | 30 |

| Fig. 3.1 Receiver block diagram                                      | 32 |

| Fig. 3.2 IEEE 802.11a lower frequency band of the channel allocation | 33 |

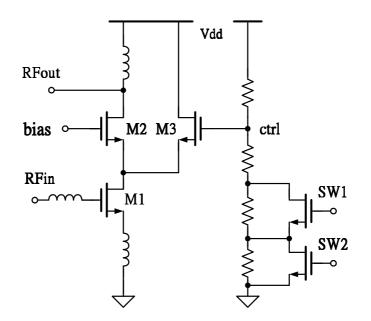

| Fig. 3.3 Current switch gain control LNA                             | 36 |

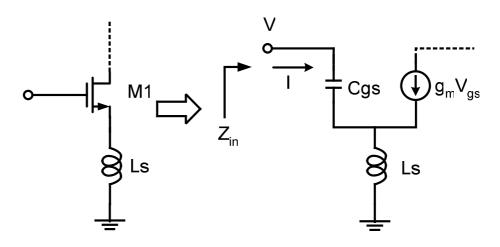

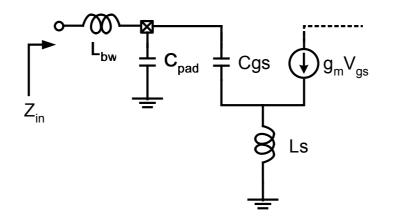

| Fig. 3.4 LNA Input matching                                          | 37 |

| Fig. 3.5 LNA input matching using pad and bondwire                   | 38 |

| Fig. 3.6 LNA input matching using pad and bondwire                   | 38 |

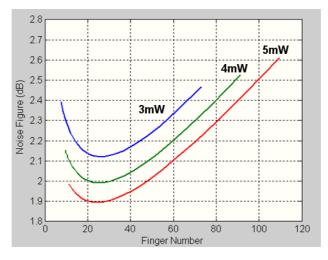

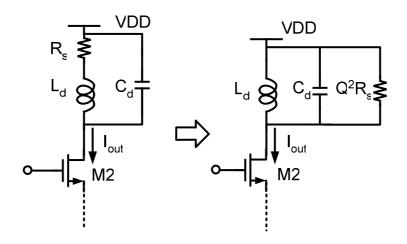

| Fig. 3.7 NF versus finger number of input stage                      | 40 |

| Fig. 3.8 Impedance transformation                                    | 41 |

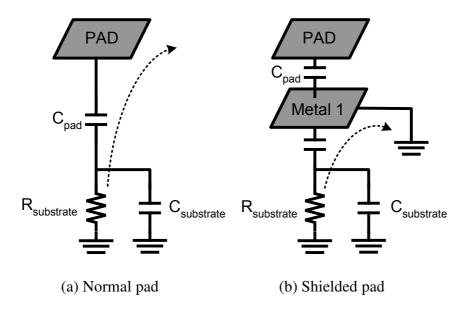

| Fig. 3.9 Normal pad and shielded pad                                 | 42 |

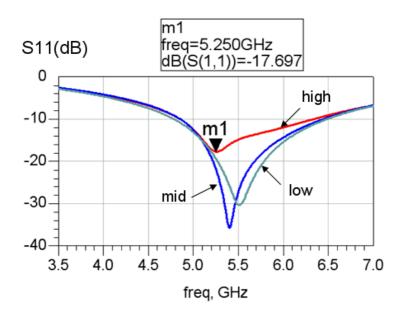

| Fig. 3.10 S11 of the LNA at different gain mode                      | 43 |

| Fig. 3.11 Noise figure of the LNA at high gain mode                  | 43 |

| Fig. 3.12 Voltage gain of the LNA at different gain mode             | 44 |

| Fig. 3.13 IIP3 of the LNA at high and low gain mode                  |    |

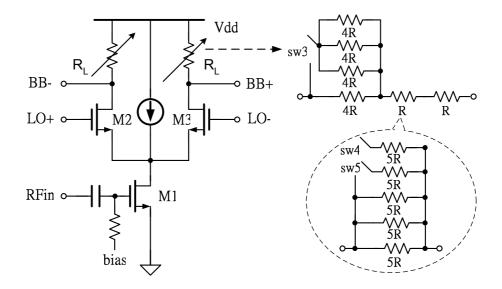

| Fig. 3.14 Mixer design                                               |    |

| Fig. 3.15 Mixer design and comparison                                | 46 |

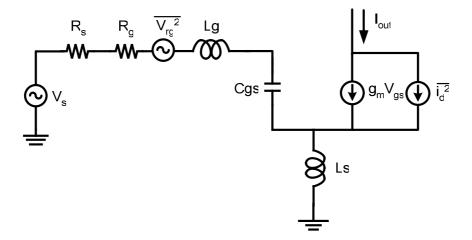

| Fig. 3.16 Noise analysis of used mixer                               | 47 |

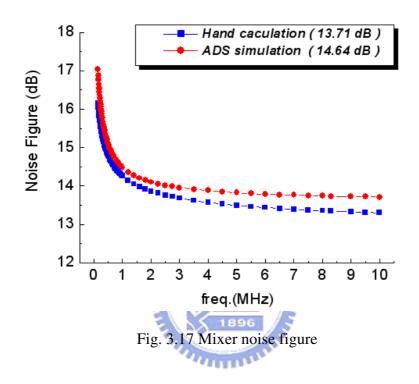

| Fig. 3.17 Mixer noise figure                                         | 48 |

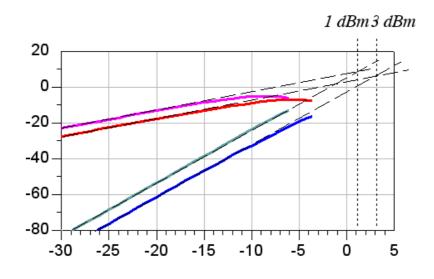

| Fig. 3.18 IIP3 of the mixer at high and low gain mode                |    |

| Fig. 3.19 Differential CMOS VCO [19]                                 | 50 |

| Fig. 3.20 Adaptive linear bias generation circuit [19]               | 51 |

| Fig. 3.21 DC simulation of VCO bias circuit                          | 53 |

| Fig. 3.22 Differential outputs of VCO at time domain                 | 53 |

| Fig. 3.23 Phase noise simulation using ADS simulator                 | 54 |

| Fig. 3.24 Phase noise simulation using ADS simulator                 | 55 |

| Fig. 3.25 Phase noise simulation using ADS simulator                 | 55 |

| Fig. 3.26 Down-conversion quadrature signals                         | 55 |

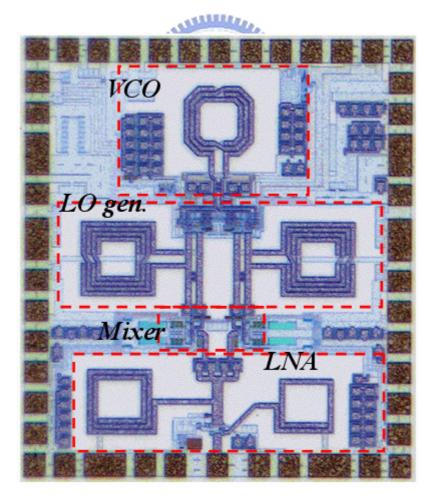

| Fig. 3.27 Chip microphotograph of the receiver                       | 57 |

| Fig. 3.28 Bonding board                                              | 58 |

| Fig. 3.29 Plugging DC board with bonding board                       | 58 |

| Fig. 3.30 Measurement setup diagram of receiver                      | 59 |

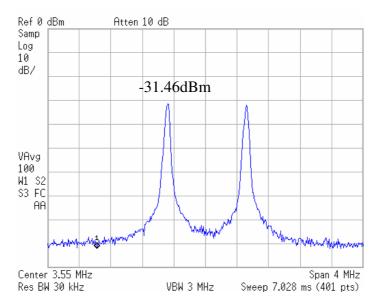

| Fig. 3.31 Measured down-conversion signal                            | 60 |

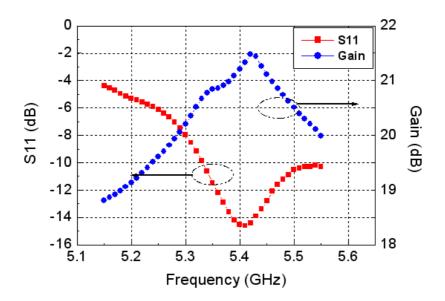

| Fig. 3.32 LNA gain and input matching (S11)                          | 60 |

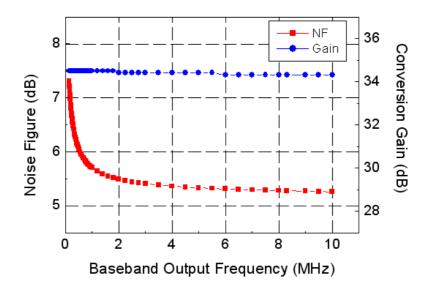

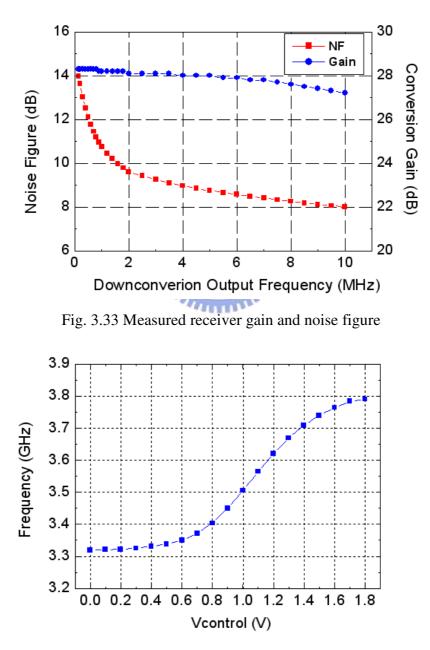

| Fig. 3.33 Measured receiver gain and noise figure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 61                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Fig. 3.34 Frequency tuning range versus frequency control voltage of VCO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 61                                                                                     |

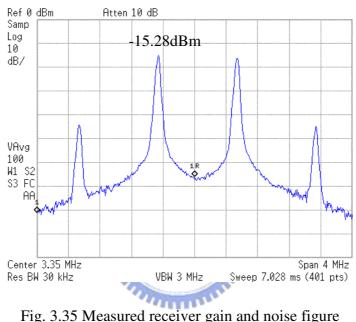

| Fig. 3.35 Measured receiver gain and noise figure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 62                                                                                     |

| Fig. 3.36 Measured receiver gain and noise figure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 62                                                                                     |

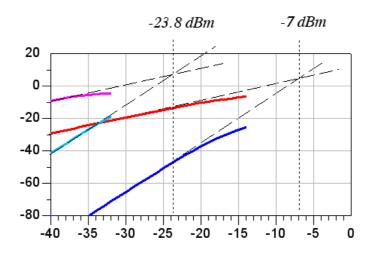

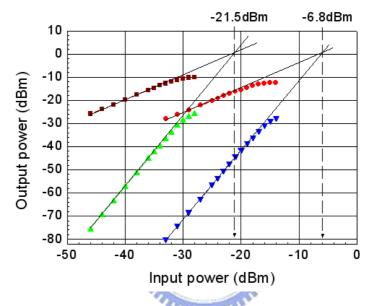

| Fig. 3.37 Two-tone test for IIP3 measurement at high/low gain mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 63                                                                                     |

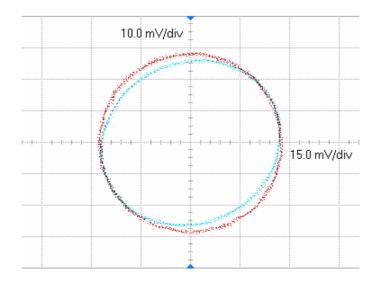

| Fig. 3.38 Measured I/Q down-conversion waveforms before calibration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 63                                                                                     |

| Fig. 3.39 Measured I/Q down-conversion waveforms after gain calibration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 64                                                                                     |

| Fig. 3.40 Measured I/Q down-conversion waveforms after gain and phase calibration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ions                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 64                                                                                     |

| Fig. 3.41 I/Q phase change of first positive step DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 65                                                                                     |

| Fig. 3.42 I/Q phase change of first negative step DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 65                                                                                     |

| Fig. 3.43 Measured maximum positive change of I/Q phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 66                                                                                     |

| Fig. 3.44 Measured maximum negative change of I/Q phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 66                                                                                     |

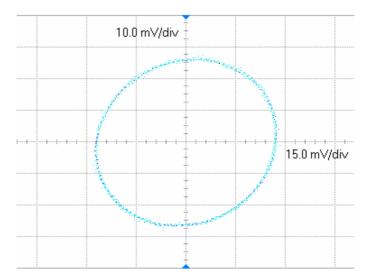

| Fig. 3.45 I/Q phase change through DAC control bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 67                                                                                     |

| Fig. 3.46 I-Q diagram (before calibration)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 67                                                                                     |

| Fig. 3.47 I-Q diagram (after calibration)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 68                                                                                     |

| Fig. 3.48 I-Q diagram comparison (calibration or not)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 68                                                                                     |

| Fig. 3.49 I/Q phase change through DAC control bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 69                                                                                     |

| Fig. 3.50 Measured input matching (S11) at different gain modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 69                                                                                     |

| - 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                        |

| Fig. 3.51 I/Q calibration and gain adjustment controlled by base band DSP using                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 70                                                                                     |

| Fig. 3.51 I/Q calibration and gain adjustment controlled by base band DSP using                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                        |

| Fig. 3.51 I/Q calibration and gain adjustment controlled by base band DSP using LMS algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 72                                                                                     |

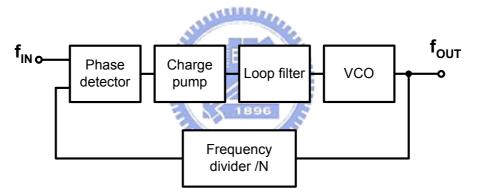

| <ul><li>Fig. 3.51 I/Q calibration and gain adjustment controlled by base band DSP using LMS algorithm</li><li>Fig. 4.1 Block diagram of the integer-N frequency synthesizer</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 72<br>72                                                                               |

| <ul> <li>Fig. 3.51 I/Q calibration and gain adjustment controlled by base band DSP using LMS algorithm.</li> <li>Fig. 4.1 Block diagram of the integer-N frequency synthesizer.</li> <li>Fig. 4.2 Synthesizer operation frequency transformation.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 72<br>72<br>se                                                                         |

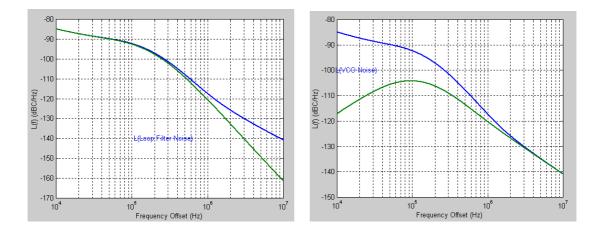

| <ul> <li>Fig. 3.51 I/Q calibration and gain adjustment controlled by base band DSP using LMS algorithm.</li> <li>Fig. 4.1 Block diagram of the integer-N frequency synthesizer.</li> <li>Fig. 4.2 Synthesizer operation frequency transformation.</li> <li>Fig. 4.3 (a) Phase noise of charge pump and loop filter compares with overall phase</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                          | 72<br>72<br>se<br>74                                                                   |

| <ul> <li>Fig. 3.51 I/Q calibration and gain adjustment controlled by base band DSP using LMS algorithm.</li> <li>Fig. 4.1 Block diagram of the integer-N frequency synthesizer.</li> <li>Fig. 4.2 Synthesizer operation frequency transformation.</li> <li>Fig. 4.3 (a) Phase noise of charge pump and loop filter compares with overall phase noise (b) VCO phase noise compares with overall phase noise.</li> </ul>                                                                                                                                                                                                                                                                                                                                                             | 72<br>72<br>74<br>74                                                                   |

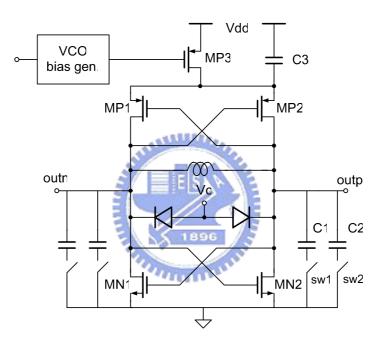

| <ul> <li>Fig. 3.51 I/Q calibration and gain adjustment controlled by base band DSP using LMS algorithm.</li> <li>Fig. 4.1 Block diagram of the integer-N frequency synthesizer.</li> <li>Fig. 4.2 Synthesizer operation frequency transformation.</li> <li>Fig. 4.3 (a) Phase noise of charge pump and loop filter compares with overall phase noise (b) VCO phase noise compares with overall phase noise.</li> <li>Fig. 4.4 Adaptive biasing VCO with switchable band.</li> </ul>                                                                                                                                                                                                                                                                                                | 72<br>72<br>74<br>74<br>75<br>76                                                       |

| <ul> <li>Fig. 3.51 I/Q calibration and gain adjustment controlled by base band DSP using LMS algorithm.</li> <li>Fig. 4.1 Block diagram of the integer-N frequency synthesizer.</li> <li>Fig. 4.2 Synthesizer operation frequency transformation.</li> <li>Fig. 4.3 (a) Phase noise of charge pump and loop filter compares with overall phase noise (b) VCO phase noise compares with overall phase noise.</li> <li>Fig. 4.4 Adaptive biasing VCO with switchable band.</li> <li>Fig. 4.5 Second-order loop filter.</li> </ul>                                                                                                                                                                                                                                                    | 72<br>72<br>74<br>75<br>76<br>76                                                       |

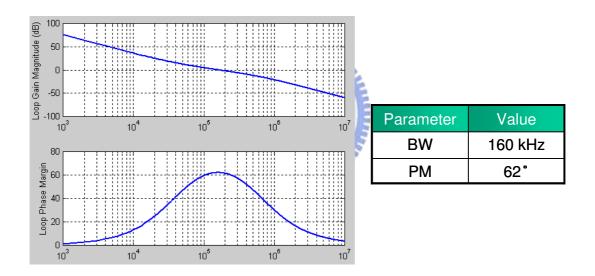

| <ul> <li>Fig. 3.51 I/Q calibration and gain adjustment controlled by base band DSP using LMS algorithm.</li> <li>Fig. 4.1 Block diagram of the integer-N frequency synthesizer.</li> <li>Fig. 4.2 Synthesizer operation frequency transformation.</li> <li>Fig. 4.3 (a) Phase noise of charge pump and loop filter compares with overall phase noise (b) VCO phase noise compares with overall phase noise.</li> <li>Fig. 4.4 Adaptive biasing VCO with switchable band.</li> <li>Fig. 4.5 Second-order loop filter.</li> <li>Fig. 4.6 Open-loop analysis.</li> </ul>                                                                                                                                                                                                              | 72<br>72<br>74<br>75<br>76<br>76<br>77                                                 |

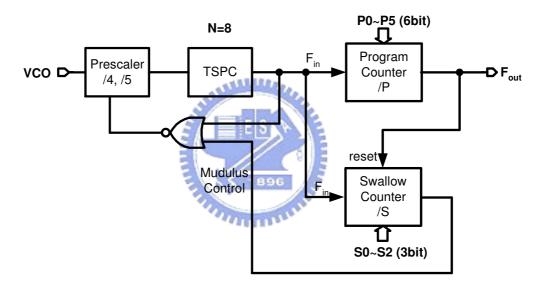

| <ul> <li>Fig. 3.51 I/Q calibration and gain adjustment controlled by base band DSP using LMS algorithm.</li> <li>Fig. 4.1 Block diagram of the integer-N frequency synthesizer.</li> <li>Fig. 4.2 Synthesizer operation frequency transformation.</li> <li>Fig. 4.3 (a) Phase noise of charge pump and loop filter compares with overall phase noise (b) VCO phase noise compares with overall phase noise.</li> <li>Fig. 4.4 Adaptive biasing VCO with switchable band.</li> <li>Fig. 4.5 Second-order loop filter.</li> <li>Fig. 4.6 Open-loop analysis.</li> <li>Fig. 4.7 Block diagram of frequency divider.</li> </ul>                                                                                                                                                        | 72<br>72<br>74<br>75<br>76<br>76<br>77<br>78                                           |

| <ul> <li>Fig. 3.51 I/Q calibration and gain adjustment controlled by base band DSP using LMS algorithm.</li> <li>Fig. 4.1 Block diagram of the integer-N frequency synthesizer.</li> <li>Fig. 4.2 Synthesizer operation frequency transformation.</li> <li>Fig. 4.3 (a) Phase noise of charge pump and loop filter compares with overall phase noise (b) VCO phase noise compares with overall phase noise.</li> <li>Fig. 4.4 Adaptive biasing VCO with switchable band.</li> <li>Fig. 4.5 Second-order loop filter.</li> <li>Fig. 4.6 Open-loop analysis.</li> <li>Fig. 4.7 Block diagram of frequency divider.</li> <li>Fig. 4.8 prescalar (/4 , /5)</li> </ul>                                                                                                                  | 72<br>72<br>we<br>74<br>75<br>76<br>76<br>77<br>78<br>78                               |

| <ul> <li>Fig. 3.51 I/Q calibration and gain adjustment controlled by base band DSP using LMS algorithm.</li> <li>Fig. 4.1 Block diagram of the integer-N frequency synthesizer.</li> <li>Fig. 4.2 Synthesizer operation frequency transformation.</li> <li>Fig. 4.3 (a) Phase noise of charge pump and loop filter compares with overall phase noise (b) VCO phase noise compares with overall phase noise.</li> <li>Fig. 4.4 Adaptive biasing VCO with switchable band.</li> <li>Fig. 4.5 Second-order loop filter.</li> <li>Fig. 4.6 Open-loop analysis.</li> <li>Fig. 4.7 Block diagram of frequency divider.</li> <li>Fig. 4.8 prescalar (/4 , /5)</li> <li>Fig. 4.9 Program counter.</li> </ul>                                                                               | 72<br>ae<br>74<br>75<br>76<br>76<br>77<br>78<br>78<br>78                               |

| <ul> <li>Fig. 3.51 I/Q calibration and gain adjustment controlled by base band DSP using LMS algorithm.</li> <li>Fig. 4.1 Block diagram of the integer-N frequency synthesizer.</li> <li>Fig. 4.2 Synthesizer operation frequency transformation.</li> <li>Fig. 4.3 (a) Phase noise of charge pump and loop filter compares with overall phase noise (b) VCO phase noise compares with overall phase noise.</li> <li>Fig. 4.4 Adaptive biasing VCO with switchable band.</li> <li>Fig. 4.5 Second-order loop filter.</li> <li>Fig. 4.6 Open-loop analysis.</li> <li>Fig. 4.7 Block diagram of frequency divider.</li> <li>Fig. 4.8 prescalar (/4 , /5)</li> <li>Fig. 4.9 Program counter.</li> <li>Fig. 4.10 Pulse swallow counter.</li> </ul>                                     | 72<br>ie<br>74<br>75<br>76<br>76<br>77<br>78<br>78<br>78<br>78                         |

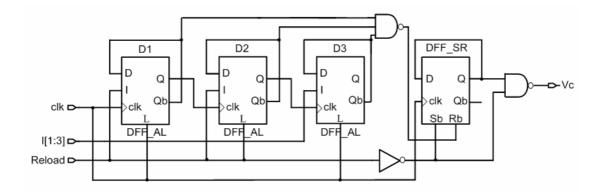

| <ul> <li>Fig. 3.51 I/Q calibration and gain adjustment controlled by base band DSP using LMS algorithm</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 72<br>se<br>74<br>75<br>76<br>76<br>76<br>77<br>78<br>78<br>78<br>79<br>79             |

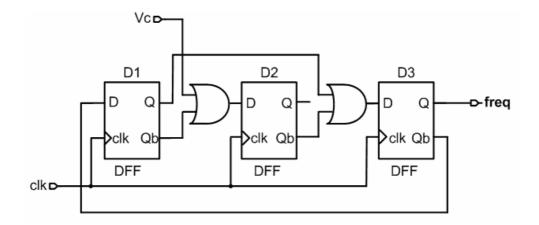

| <ul> <li>Fig. 3.51 I/Q calibration and gain adjustment controlled by base band DSP using LMS algorithm.</li> <li>Fig. 4.1 Block diagram of the integer-N frequency synthesizer.</li> <li>Fig. 4.2 Synthesizer operation frequency transformation.</li> <li>Fig. 4.3 (a) Phase noise of charge pump and loop filter compares with overall phase noise (b) VCO phase noise compares with overall phase noise.</li> <li>Fig. 4.4 Adaptive biasing VCO with switchable band.</li> <li>Fig. 4.5 Second-order loop filter.</li> <li>Fig. 4.6 Open-loop analysis.</li> <li>Fig. 4.7 Block diagram of frequency divider.</li> <li>Fig. 4.8 prescalar (/4 , /5)</li> <li>Fig. 4.9 Program counter.</li> <li>Fig. 4.10 Pulse swallow counter.</li> <li>Fig. 4.12 Simplified TSPC.</li> </ul> | 72<br>se<br>74<br>75<br>76<br>76<br>76<br>76<br>78<br>78<br>78<br>78<br>79<br>79<br>80 |

| <ul> <li>Fig. 3.51 I/Q calibration and gain adjustment controlled by base band DSP using LMS algorithm</li> <li>Fig. 4.1 Block diagram of the integer-N frequency synthesizer</li> <li>Fig. 4.2 Synthesizer operation frequency transformation</li> <li>Fig. 4.3 (a) Phase noise of charge pump and loop filter compares with overall phase noise (b) VCO phase noise compares with overall phase noise</li> <li>Fig. 4.4 Adaptive biasing VCO with switchable band</li> <li>Fig. 4.5 Second-order loop filter</li> <li>Fig. 4.6 Open-loop analysis</li> <li>Fig. 4.7 Block diagram of frequency divider</li></ul>                                                                                                                                                                 | 72<br>ae<br>74<br>75<br>76<br>76<br>76<br>77<br>78<br>78<br>78<br>79<br>79<br>80<br>81 |

| Fig. 4.17 Output waveform of dividing by 9                    | 82 |

|---------------------------------------------------------------|----|

| Fig. 4.18 Current pump current matching condition             | 83 |

| Fig. 4.19 Replica switching pair avoids charge sharing effect | 83 |

| Fig. 4.20 PFD dead zone simulation                            | 83 |

| Fig. 4.21 Close-loop response simulation                      | 84 |

# **Chapter 1**

## Introduction

### 1.1 Background

As increasing demand for high-speed wireless communication and high-quality multimedia application, wireless local-area network (WLAN) market has grown fast. The IEEE 802.11a standard [1], which operates in the 5-GHz unlicensed national infrastructure (UNII) band, supports higher data rates up to 54Mb/s compared with maximum data 11Mb/s offered by the 802.11b standard. It provides for orthogonal multiplexing (OFDM) modulation with 52 subcarriers in a channel bandwidth of 16.6MHz (channel spacing of 20MHz). The data is modulated with BPSK, QPSK, 16QAM, or 64QAM, and further mapped into 48 subcarriers (4 subcarriers are for pilot signals).

These advantages come at a cost, as OFDM-based systems pose significant implementation challenges requiring low in-band noise, high linearity, and accurate quadrature matching [2]. Besides, the use of 64QAM modulation requires a high SNR of 26dB, which is substantially greater than that required by the FSK modulation in Bluetooth and the QPSK modulation in 802.11b. This high SNR translates to more stringent phase noise requirement for the synthesizer and tight quadrature signal matching constraints for both the transmitter and receiver [3]. To realize the low-cost

implementation, the CMOS integrated receiver is desirable for its inexpensive price.

Implementation CMOS RF receiver using direct-conversion architecture has many advantages, such as fewer external filters (cost down), less internal components (reduce power dissipation), and highly integration (small form factor). However, this architecture accompanies with some problems, such as dc offset, I/Q mismatch, even-order distortion, flicker noise, and LO leakage , which described in detail in ref [4]. Therefore, in the past years, design issues in this architecture become popular and active researches.

#### **1.2 Motivation**

The drawbacks in direct conversion receiver architecture mentioned before can be alleviated and improved by the following design techniques.

#### 1.2.1 Optimum between gain, noise figure, and linearity

In the RF frond-end design (LNA + Mixer), providing high conversion gain will get better overall noise figure, but degrade whole linearity. Contrarily, providing low conversion gain will promote whole linearity, but increase overall noise figure. Therefore, if conversion gain of the frond-end is programmable, as shown in Fig1.1, it is able to alleviate tradeoff between gain, noise figure, and linearity performance.

Fig. 1.1 Programmable conversion gain in the front-end design

#### **1.2.2 Avoid VCO pulling for transceiver integration**

Combining direct-conversion receiver with direct-conversion transmitter accompanies some impairment, such as pulling effects by the on-chip PA, and large in-band LO leakage. Thus, design challenge in the direct conversion architecture is minimization of VCO pulling from on-chip PA and LO leakage. In order to alleviate these impairments, the VCO is operated at two-thirds of the required LO frequency to avoid VCO-pulling and reduce LO-RF interaction. The required LO generation is shown in Fig1.2 [5].

#### 1.2.3 Provide precise I/Q output

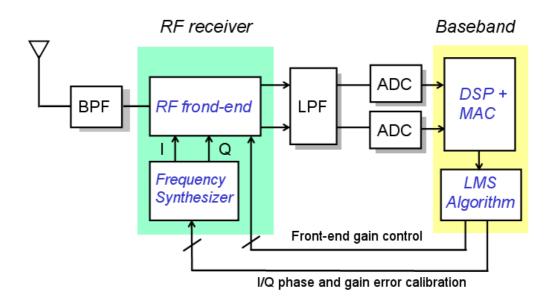

As shown in Fig1.1, for phase and frequency modulation schemes, a homodyne receiver has to incorporate quadrature mixing. The phase errors in qradrature LO generation, and mismatches between the amplitudes of the I/Q signals corrupt the down converted signal constellation, thereby raising the bit error rate. As shown in Fig1.3, all stages in the I/Q paths contribute gain and phase errors.

High order QAM-OFDM modulation requires tightly matched phase and gain in I/Q signal path to avoid degradation of the overall EVM. Thus, in order to get higher SNR in the receiving signals and better EVM (error vector magnitude) for transmitter, I/Q mismatch problem in the implementation of CMOS RF receiver must be

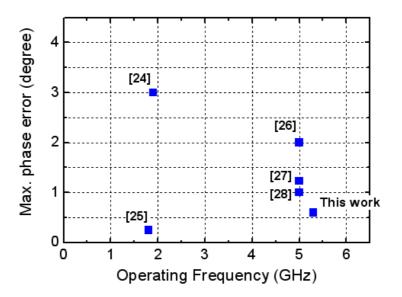

overcome. It comes from the process, voltage, temperature variations and transistors, passive components (L, C) mismatch. To compensate I/Q mismatch, some analog and digital calibration have been proposed [4]. Recently, a LC oscillator with poly-phase filter employing self-calibrated technique [6] and a quadrature LC oscillator using tail current source control for phase error calibration [7] have been presented. However, the calibrated I/Q phase error by their proposed mechanism is about less than 2°. However, system simulation shows that an I/Q mismatch of 1.5° / 0.2 dB and an integrated phase error of 1°rms are required [8]. Thus, phase and gain error calibration techniques are proposed to compensate gain and phase error in the receiving I/Q signal paths. By means of these techniques, the phase mismatched is reduced to less than 0.8° and gain error less than 0.2dB. Table 1.1 lists the design target of our receiver design.

Fig. 1.3 I/Q mismatch contributions by various stages

| Technology                       | TSMC 0.18 um CMOS  |  |

|----------------------------------|--------------------|--|

| Modulation / Data rates          | 64QAM / 54Mbps     |  |

| Supply Voltage                   | 1.8 V              |  |

| LNA gain                         | 10 ~ 22 dB         |  |

| LNA NF                           | < 2.5dB            |  |

| Mixer gain                       | 6 ~ 12 dB          |  |

| Mixer NF                         | < 15 dB            |  |

| Total noise figure               | < 7dB              |  |

| Max. gain                        | 34 dB              |  |

| 1dB point                        | -26dBm             |  |

| ШРЗ                              | - 16dBm            |  |

| I-Q path amplitude / phase error | < 0.2dB / < 0.8°   |  |

| Phase noise                      | -113 dBc/Hz @ 1MHz |  |

Table 1.1 Design target

## 1.3 Organization

In this thesis, chapter 2 describes how to realize the proposed I/Q calibration generator and LO generation architecture. The detail operation theory and improved performance are presented, and verified by chip implementation. Chapter 3 describes the direct-conversion front-end receiver design. The components employed in the receiver, such as LNA (low noise amplifier), down-conversion mixer, VCO, are also discussed. Chapter 4 describes the implementation of a frequency synthesizer chip with low phase noise and low reference spur. The design flow and performance optimum are presented. Finally, Chapter 5 describes the conclusions and future works.

## Chapter 2

# Quadrature LO Generator with I/Q Mismatch Calibration

Direct down-conversion from 5GHz requires quadrature LO generation at the RF carrier frequency, which may result in large gain and phase mismatches. Other significant problems include sensitivity to flicker noise and pulling of the VCO by the external or on-chip PA. In addition to these architecture-related nonidealities, higher order QAM-OFDM modulation requires tightly matched I/Q signal path on both transmit and receive side to avoid degradation of the overall EVM.

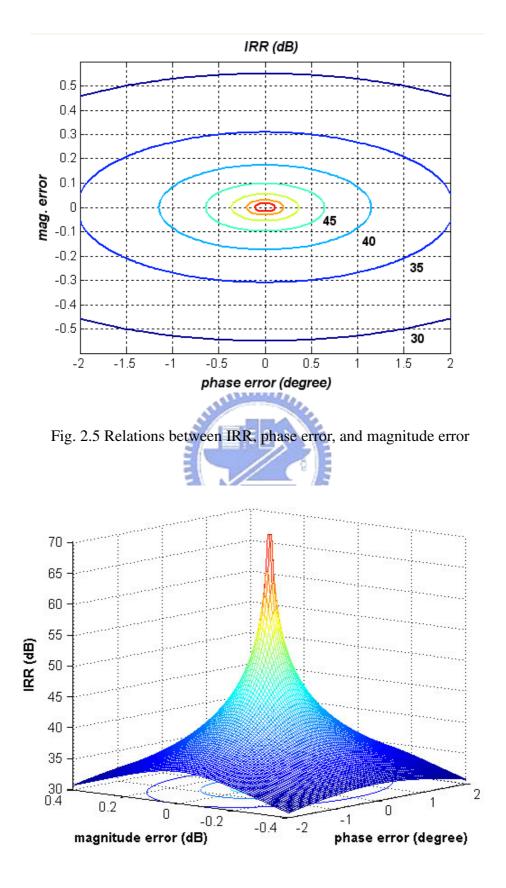

#### 2.1 Phase-calibrated LO Generator

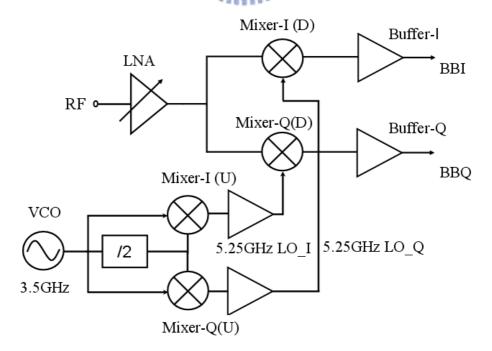

In this section, we present the phase-calibrated LO generator. In our frequency planning, a "fractional VCO" is adopted in which the desired RF frequency is 1.5 times higher than the VCO frequency [5]. Fig 2.1 reports an LO generation scheme that consists of a VCO operating at two-thirds of the LO frequency and a divide-by-2 divider generating quadrature outputs at one-third LO frequency. Besides, additional phase-calibrated LO generators are employed and combined with up-conversion mixers in LO I/Q path for phase error calibration.

Fig. 2.1 Calibrated LO generator architecture

As the VCO operates at two-thirds of the LO frequency (3.5GHz), this scheme can effectively avoid pulling and reduce LO-RF interaction. However, the generated LO signal has strong lower sideband at one-third of LO frequency, which is roughly 1.75GHz, a highly populated frequency band where high-power transmitters exist. To suppress the lower side band image at the LO I/Q output, the up conversion mixer utilizes LC tanks as the output load.

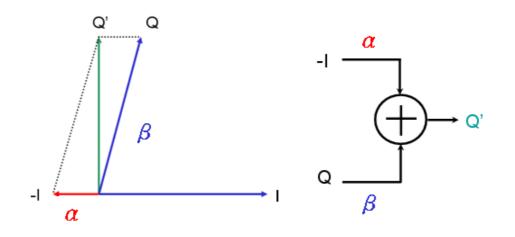

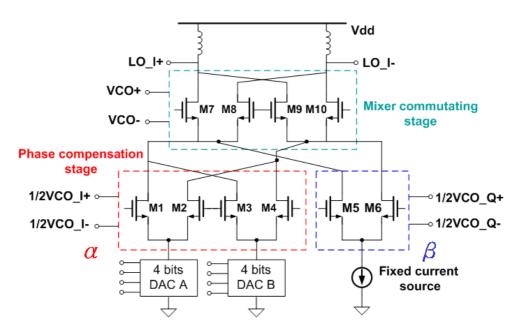

Assume vector I and Q are not orthogonal, as is illustrated in Fig 2.2, a modified quadrature phase Q' can be generated by summing up Q with a compensated vector –I. Once the polarity and weighting factor of the compensation can be digitally controlled, a precise I/Q signal can be generated by eliminating their phase error. Fig 2.3 depicts the phase-calibrated LO generator, which performs as an up conversion mixer with phase compensation capability. The divider output I/Q signals at 1/3  $f_{LO}$  are applied to the transconductance stages (M1-M6) of the mixer, while the VCO output at 1/3  $f_{LO}$  are applied to commutating stages (M7-M10) of the mixer. The vector compensation is achieved by I/Q phase current mixing.

Fig. 2.2 Phase compensation concept

Fig. 2.3 Phase-calibrated LO generator

Assume

$$\alpha I = (\alpha 1)I - (a2)I$$

The compensated quadrature vector (Q') can be derived as

$$Q' = \alpha I + \beta Q$$

Here  $\alpha 1$  and  $\alpha 2$  are controlled by 4 bits DAC A and B respectively. Thus the

polarity and magnitude of the compensated current can be digitally programmed to null out the phase error.

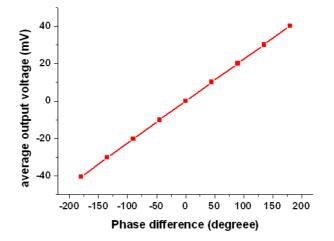

## 2.2 Phase Calibration Verification

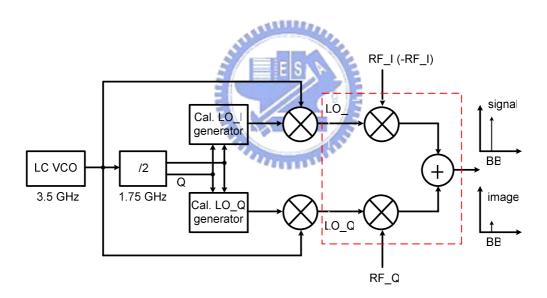

To evaluate the performance of the calibration LO I/Q generator, we must measure the phase and gain errors. But it is very hard to measure those parameters of quadrature phase outputs at such high frequency. To get information about phase error, we can use the image rejection down-conversion mixers to mix down LO I/Q signals with accurate quadrature RF I/Q signals and measure the image rejection ratio (IRR). Specific relations exist between gain error, phase error, and image rejection ratio.

Fig. 2.4 Phase compensation concept

Assume we generate and inject signals at two frequencies:  $\omega_{LO}$ ,  $\omega_{RF}$  respectively, then mix them together. Parameter  $\varepsilon$  represents the magnitude error of LO I/Q signals and  $\theta$  represents phase error of them.

$$RFI \times LOI + RFQ \times LOQ:$$

$$\cos(\omega_{RF}t) \times \cos(\omega_{LO}t) + \sin(\omega_{RF}t) \times (1+\varepsilon) \sin(\omega_{LO}t + \theta) \qquad (2.1)$$

$$\approx \frac{1}{2} [1 + (1+\varepsilon) \cos\theta] \times \cos(\omega_{RF} - \omega_{LO})t + \frac{1}{2} [1 - (1+\varepsilon) \cos\theta] \times \cos(\omega_{RF} + \omega_{LO})t$$

$$wanted signal$$

$$- RFI \times LOI + RFQ \times LOQ: \qquad (2.2)$$

$$- \cos(\omega_{RF}t) \times \cos(\omega_{LO}t) + \sin(\omega_{RF}t) \times (1+\varepsilon) \sin(\omega_{LO}t + \theta)$$

$$\approx -\frac{1}{2} (1 - (1+\varepsilon) \cos\theta) \times \cos(\omega_{RF} - \omega_{LO})t + \frac{1}{2} (1 + (1+\varepsilon) \cos\theta) \times \cos(\omega_{RF} + \omega_{LO})t$$

$$wanted signal$$

When we mix RFI and RFQ with LOI and LOQ respectively, we get down-conversion wanted signal at frequency of  $\omega_{RF} - \omega_{RF}$ , as indicated in equation (2.1). Inversely, when we mix –RFI and RFQ with LOI and LOQ respectively, we get down-conversion image signal at frequency of  $\omega_{RF} - \omega_{RF}$ , as indicated in equation (2.2). However, up-conversion signals at frequency of  $\omega_{RF} + \omega_{RF}$  after mixing will be filtered by the band-limited circuits, such as down conversion mixers, output buffers, and low pass filters. Image rejection ratio (IRR) is magnitude ratio between them, which is listed in equation (2.3).

$$IRR = 20Log \sqrt{\frac{(1+\varepsilon)^2 + 1 + 2\varepsilon \times \cos\theta}{(1+\varepsilon)^2 + 1 - 2\varepsilon \times \cos\theta}}$$

(2.3)

By using MATLAB, we can show relations between gain error, phase error, and image rejection ratio in Fig 2.5 and Fig 2.6.

Fig. 2.6 Relations between IRR, phase error, and magnitude error (3D)

From IEEE 802.11a specification, we get that EVM has to be less than -25dB for good data constellations. From hand calculation, EVM can be expressed as:

$$EVM \approx 20Log \frac{\sqrt{(1+\varepsilon)^2 + 1 - 2\varepsilon \times \cos\theta}}{\sqrt{2}} < -25dB$$

(2.4)

According to equation (2.3) and (2.4), it reveals that IRR has to be greater than 28dB to achieve specification. If I/Q mismatch of 0.8° and 0.2dB can be achieved by our proposed phase -calibrated mechanism, IRR will be greater than 37.4dB and EVM will be less than -34.3dB. By MATLAB, we can show relations between magnitude error, phase error, and EVM as shown in Fig 2.7.

Fig. 2.7 Relations between EVM, phase error, and magnitude error

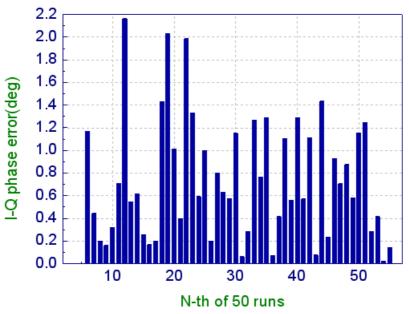

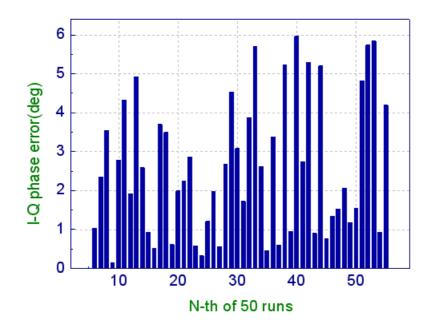

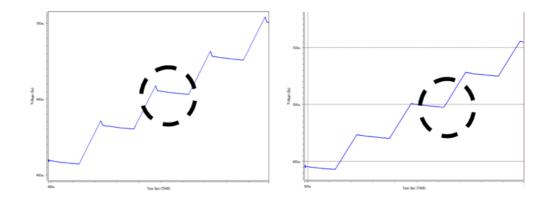

In order to determine the maximum phase compensation, Monte Carlo simulations have been employed for analyzing the maximum I/Q phase error from component mismatches. As shown in Fig 2.8, Monte Carlo simulations (50 times) using Gaussian distribution show that maximum phase error would achieve about 2.2° in the presence of 10% and 6-sigma device channel length mismatches. Furthermore, as shown in Fig 2.9, under more serious conditions, Monte Carlo simulations ( 50 times) using uniform distribution show that maximum phase error would achieve about 5.9° in the presence of 10% and 6-sigma device channel length mismatches. Thus, according to mention before, the calibrated LO I/Q generators have to be designed to have capability of compensating maximum phase error about 6°. In our phase compensation plan, I/Q phase error less than 10° can be compensated to less than 0.8°.

Fig. 2.8 Monte Carlo simulations using Gaussian distribution

Fig. 2.9 Monte Carlo simulations using uniform distribution

ATTILLES .

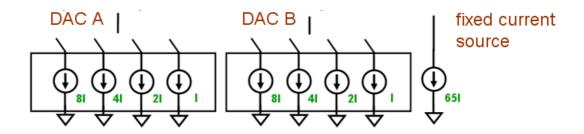

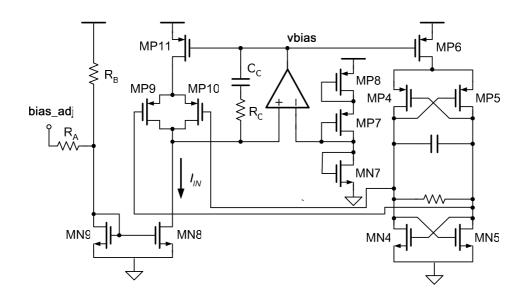

The DAC\_A and DAC\_B in Fig 2.3 are current-mode D/A converters and controlled by 4-bit binary-weighted current sources, as shown in Fig 2.10. The currents through DAC\_A and DAC\_B are proportional to their bit numbers respectively and total current through them are constant. In this work, the sum of bit numbers of DAC\_A and DAC\_B is a constant value, 16. By assigning bit number of DAC\_A and DAC\_B, I/Q phase compensation polarity and magnitude can be digitally controlled. As I/Q phase error is zero, DAC\_A and DAC\_B have the same current and

Fig. 2.10 Monte Carlo simulations using Gaussian function

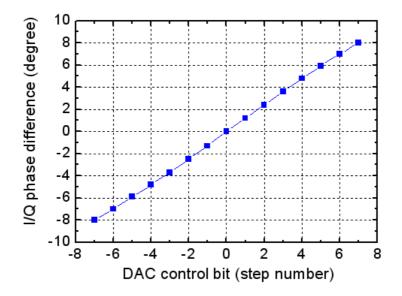

bit number, 8, so phase-I signals for compensation in Fig. 2.3 are canceled through cross couple pairs, M1-M4. And from roughly hand calculation and simulation result, current ratio under minimum DAC control is (2I / 65I), which results in I/Q phase variation about 1.54°. And current ratio under maximum DAC control is (15I / 65I), which results in I/Q phase variation about 9.58°. I/Q phase change versus DAC control step (the difference between bit number of DAC\_A and DAC\_B) is shown in Fig. 2.11.

Fig. 2.11 I/Q phase change versus DAC control step

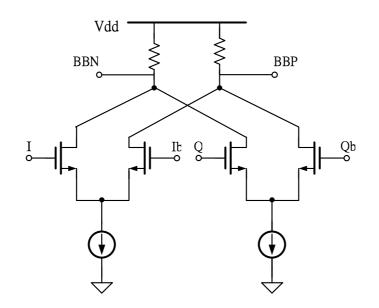

### 2.3 Gain-calibrated Down-conversion Mixer

To compensate the gain error at signal I/Q path, receiver frond-end (LNA + Mixer) is designed to provide fine gain control in I/Q paths conversion gain. However, the gain of LNA is the same for signal I/Q path. Therefore, the down-conversion mixers at signal I/Q path are suit to provide this function. The simplest way is to make changes in resistor load of mixers. Fig 2.12 shows that resistor load adjusted by switching sw4 and sw5. As sw4 and sw5 turn on, resistor load is "R + 5R". As sw4

turns off and sw5 turns on (or inversely), resistor load is "(5R/4) + 5R", mixer gain increases 0.4dB. As sw4 and sw5 turn off, resistor load is "(5R/3) + 5R", mixer gain increases about 0.7dB. Therefore, if signal I/Q path exists gain error less than 1dB, after gain error calibration, gain error will be less than 0.2dB.

## 2.4 Circuit Realizations

In this section, we will discuss other block designs in Fig 2.4, such as complementary VCO, divide-by-2 divider, and source couple pair adder.

#### 2.4.1 Complementary VCO

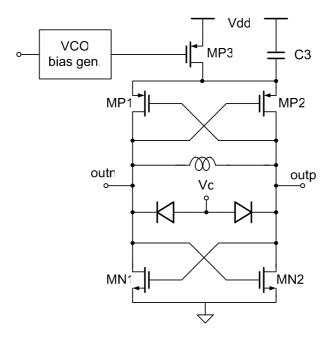

In this work, our VCO design adopted differential complementary cross-coupled LC oscillator architecture, as shown in Fig 2.13. Symmetric inductor and accumulation-mode varactor is used for inductor and capacitance of VCO. Complementary cross-coupled architecture saves more power than only nmos or pmos cross-coupled architecture because negative resistance becomes double. Also, its phase noise performance can be further improved by means of the complementary architecture thanks to symmetric output waveform [9].

Fig 2.13 Complementary cross-coupled VCO

## 2.4.2 Divide-by-2 divider

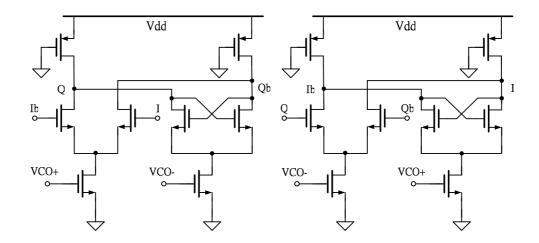

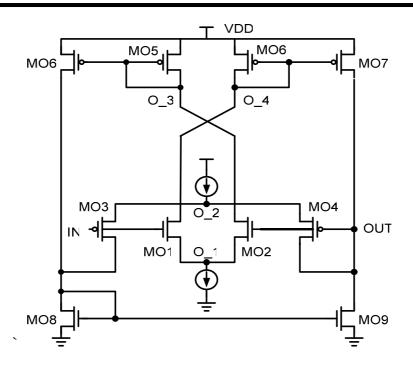

Fig 2.14 shows a divide-by-two divider schematic utilized to generate the quadrature LO signals. The circuit is realized as two master-slave D flip-flops configured in a negative feedback loop. Each flip-flop consists of a differential amplifier followed by a regenerative cross coupled pair. Thus dividing signals with I/Q phases can be derived at the divider outputs. The detailed schematic of MS-D-FF is shown in Fig 2.15. Typical device mismatches result in phase imbalances as large as  $5^{\circ}$  [10].

Fig. 2.14 Divide-by-2 divider configuration

Fig. 2.15 Divide-by-2 divider

#### 2.4.3 Source Couple Pair Adder

Fig 2.16 shows a source couple pair adder schematic. Since RF I/Q signals mix with LO I/Q signals respectively, then down convert to baseband signals (150k ~ 8.3MHz) and added up through source couple pair adder. If down-conversion signals were wanted signals, they would be sum up. However, if down-conversion signals were image signals, they would be canceled out.

Fig. 2.16 Source couple pair adder

### 2.5 Simulation result

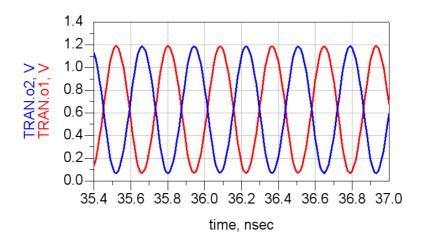

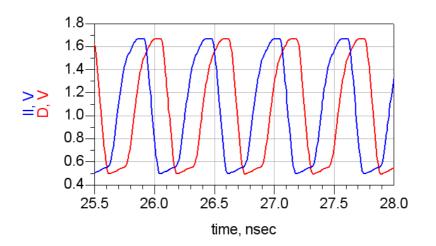

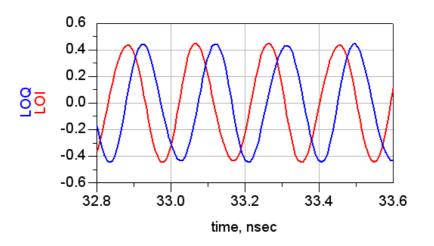

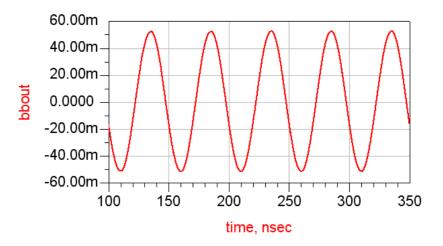

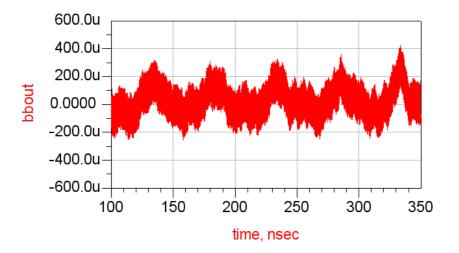

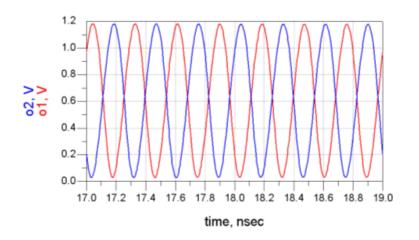

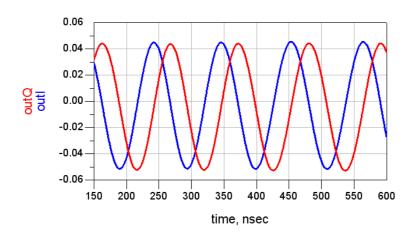

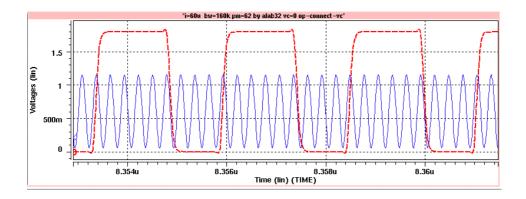

Transient response of each circuit block is shown in the following. The simulation results of VCO differential output waveforms are shown in Fig 2.17. Quadrature outputs of divide-by-2 divider are shown in Fig 2.18. The mixing up-conversion quadrature LO waveforms through phase-calibrated LO generator are shown in Fig 2.19. Fig 2.20 shows that simulation result of down-conversion wanted signal at 20MHz. On the other hand, Fig 2.21 shows that simulation result of down-conversion image signal at 20MHz.

Fig. 2.17 VCO differential output waveforms

Fig. 2.18 Quadrature outputs of divide-by-2 divider

Fig. 2.19 Quadrature LO waveforms

Fig. 2.20 Down-conversion wanted signal

Fig. 2.21 Down-conversion image signal

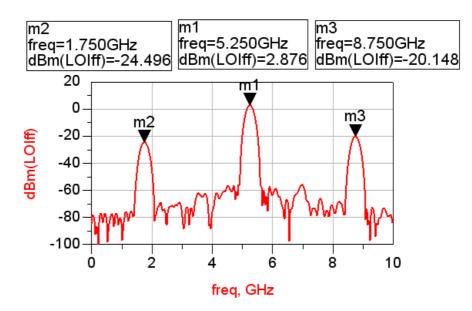

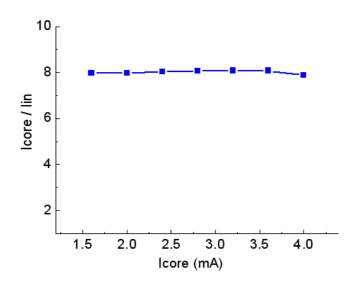

The spectrum of quadrature outputs of divide-by-2 divider is shown in Fig 2.22. As can be seen in Fig 2.21, LO signal power at 5.25GHz is higher than that of lower side band about 27dB. Fig 2.23 shows that spectrum of down-conversion wanted signal in Fig 2.20 and Fig 2.24 shows that spectrum of down-conversion image signal in Fig 2.21. As can be seen in Fig 2.23 and Fig 2.24, the simulated IRR is greater than 50dB under I/Q matching situation. In Table 2.1, it lists the performance summary of quadrature LO generator with I/Q mismatch calibration.

Fig. 2.22 Spectrum of quadrature outputs of divide-by-2 divider

Fig. 2.23 Spectrum of down-conversion wanted signal

Fig. 2.24 Spectrum of down-conversion image signal

| Technology              | Technology TSMC 0.18 um CMOS |          |

|-------------------------|------------------------------|----------|

| Supply Voltage          | 1.8 V                        |          |

| I/Q phase error         | 1896 < 0.8°                  |          |

| I/Q gain error          | < 0.2dB                      |          |

| Max. phase compensation | $\pm$ 9.58°                  |          |

| IRR                     | > 37.4 dB                    |          |

| VCO tuning range        | 3.18GHz ~ 3.74GHz            |          |

|                         | VCO                          | 3.56 mW  |

|                         | I/Q divider                  | 5.94 mW  |

| Power Consumptions      | LO generator                 | 5.86 mW  |

|                         | Mixer                        | 9.42 mW  |

|                         | Adder                        | 20.63 mW |

|                         | Overall                      | 45.41 mW |

Table 2.1 Performance summary

## 2.6 Measurements

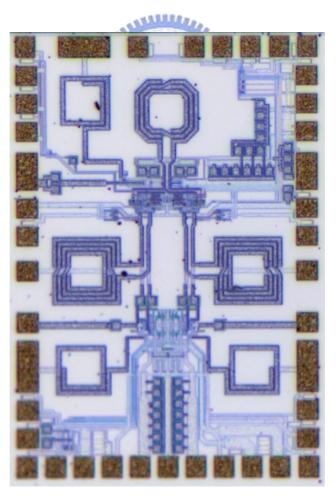

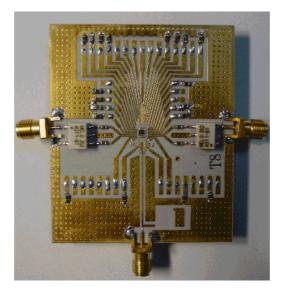

A Quadrature LO generator with I/Q mismatch calibration is designed and fabricated in TSMC  $0.18 \,\mu$  m technology. This section includes chip photograph, measurement setup and experimental results. Measured performances are taken into discussions.

## 2.6.1 Measurement Setup

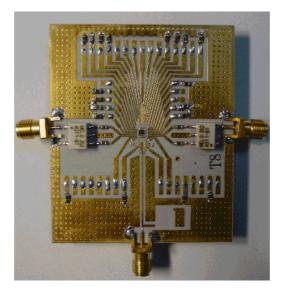

Dies for measurement are bare and required to be bonded on PCB board. Packages are excluded for complicated parasites. The chip microphotograph and bonding board for measurement test are shown in Fig 2.25 and Fig 2.26. The chip need quadrature RF inputs, and thereby quadrature generator is necessary.

Fig. 2.25 Chip microphotograph of quadrature LO generator

Fig. 2.26 Bonding board

DC board is used to provide the supply voltage, bias, and ground for bonding board. After plugging the DC board with the bonding board, test platform is completed as shown in Fig 2.27. SMD bypass capacitors are connected on the bonding board to filter out the high-frequency noise from supply and external components. The transformers with module number ADT1-6T are made by Mini-circuits. Signal attenuations caused by the matching network, transmission line,

Fig. 2.27 Plugging DC board with bonding board

coaxial line and transformer network are measured and compensated back to measurement results.

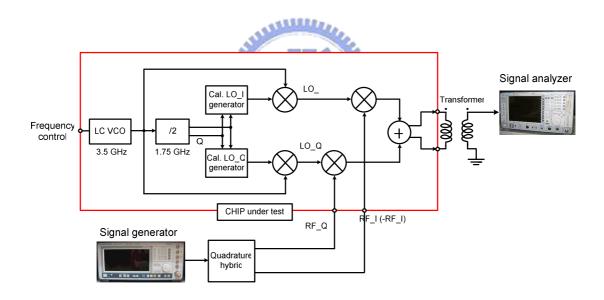

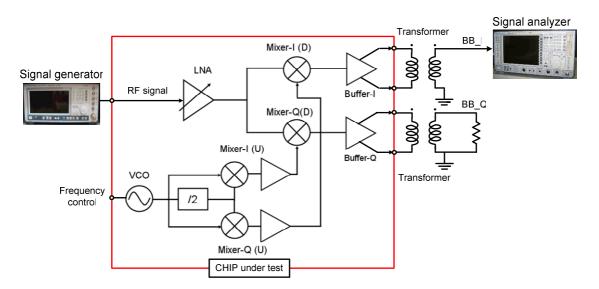

In Fig 2.28, it shows the measurement setup diagram of quadrature phase-calibrated LO generator with image rejection mixers. Input signal is provided from external signal generator and quadrature signals are generated through quadrature hybrid. By adjusting frequency control voltage of the VCO, we can down convert RF signals to frequency band of 150k ~ 8.3MHz. At the output terminals, a transformer converts differential outputs to single output and feeds this output to spectrum analyzer. By spectrum analyzer, we can measure image signal and wanted signal, thus IRR can be get.

Fig. 2.28 Measurement setup diagram of quadrature phase-calibrated LO generator

with image rejection mixers

## **2.6.2 Measurement Results**

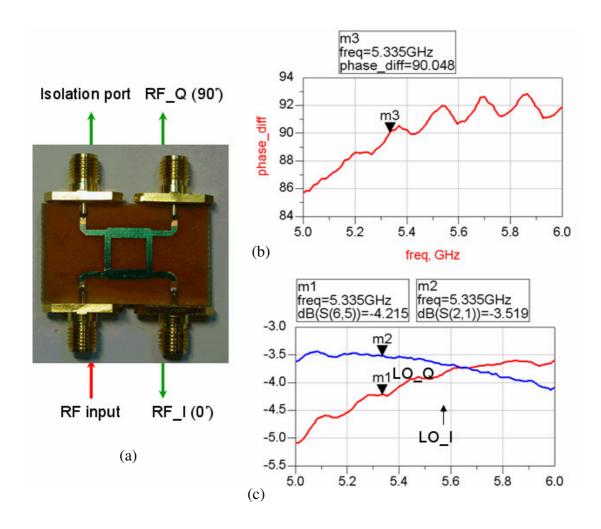

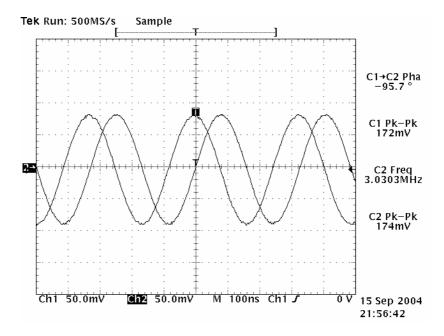

In Fig 2.28(a), it shows that photograph of quadrature hybrid. It is a four-port component. As RF signal inputs from one port, other two ports will generator RF I/Q signals at some frequency and the other port is isolated, i.e., the signal is cancelled at this port. In Fig 2.28(b), it shows that precise quadrature phase is at frequency of 5.335GHz. Fig 2.28(c), it shows that difference of S21 at 5.335GHz is about 0.7dB, a significant magnitude mismatch between port of RF\_I and port of RF\_Q.

Fig. 2.28 Quadrature hybrid (a) photograph (b) phase difference between port of RF\_I and RFQ (c) gain error between port of RF\_I and RF\_Q

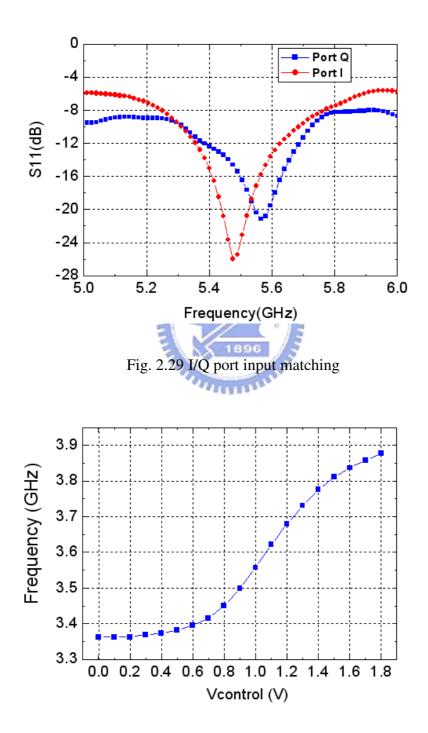

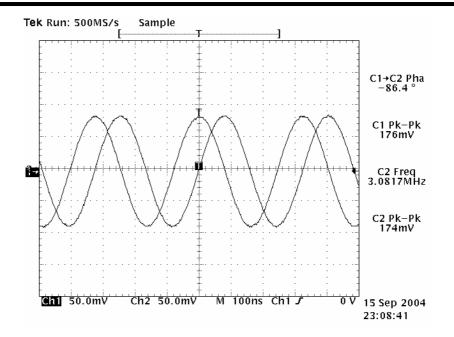

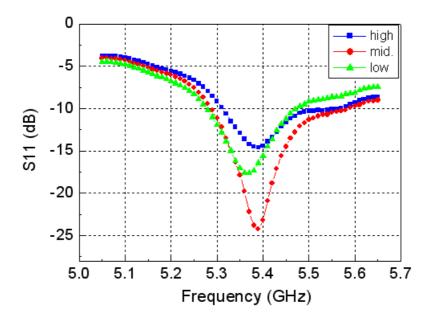

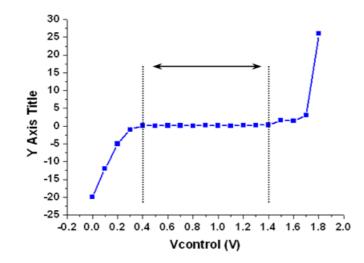

In Fig 2.29, it shows input matching condition at RF I/Q input ports. At frequency of 5.335GHz, I/Q input matching is similar, thus it is suitable for injecting RF test signal at 5.335GHz. In Fig 2.30, it shows operating frequency of VCO versus control voltage and reveals that desired frequency of 5.335GHz is achievable.

Fig. 2.30 Down-conversion signal from Q path

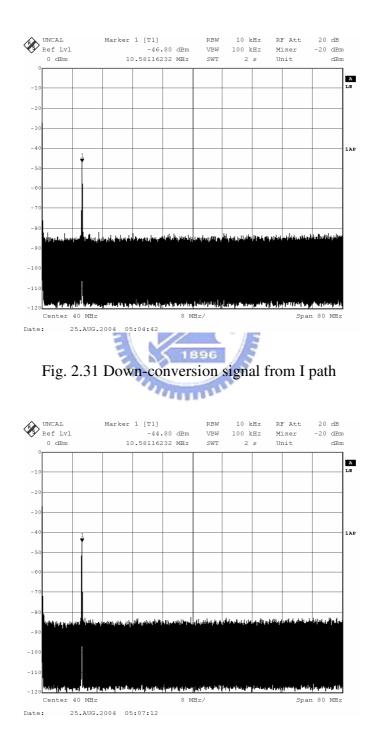

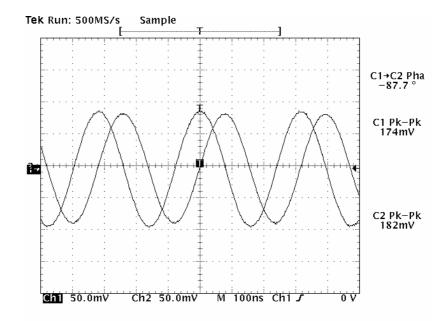

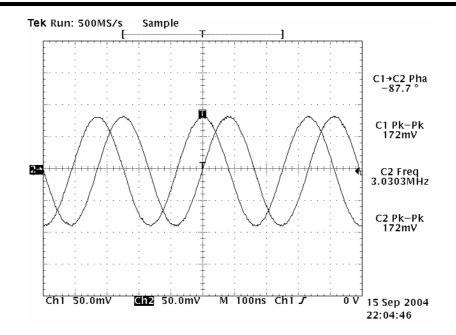

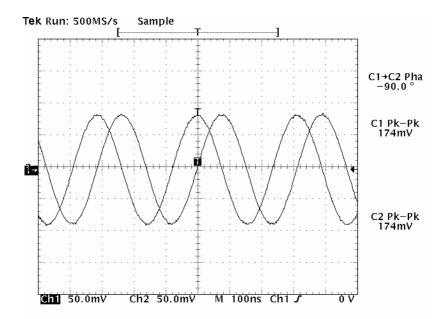

In Fig 2.31, it shows down-conversion signal by mixing of RFI and LOI. In Fig 2.32, it shows down-conversion signal by mixing of RFQ and LOQ. From Fig 2.31 and 2.32, it reveals that gain error about 2dB exists in I/Q path. However, our design is only able to calibrate gain error less than 1dB. This gain error exceeds our estimate.

Fig. 2.32 Down-conversion signal from Q path

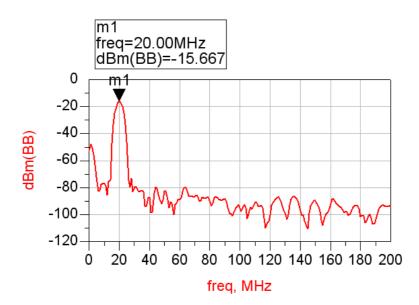

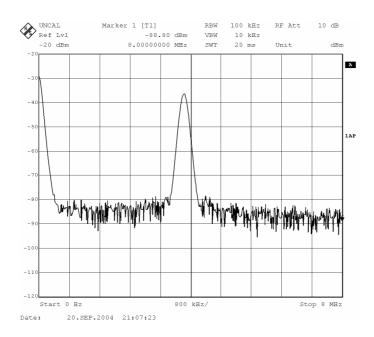

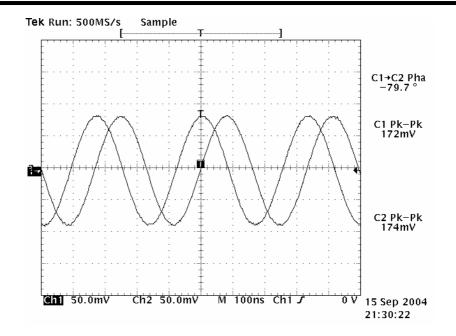

In Fig 2.33, it shows down-conversion signal is about -45.3dBm. In Fig 2.34, it shows down-conversion image is about -62.35dBm. From Fig 2.33 and 2.34, it reveals that IRR is about 17.05dB before calibration. And we can estimate that gain error is about 2dB and phase error is about 6°.

Fig. 2.34 Down-conversion image (before calibration)

8 MHz/

25.AUG.2004 03:10:55

Span 80 MHz

-100 -110 -120 **(1/41) \*\*\* 1\*\* 1\*\* 1\*\*** Center 40 MHz

Date:

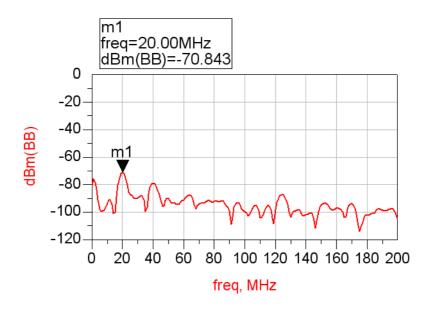

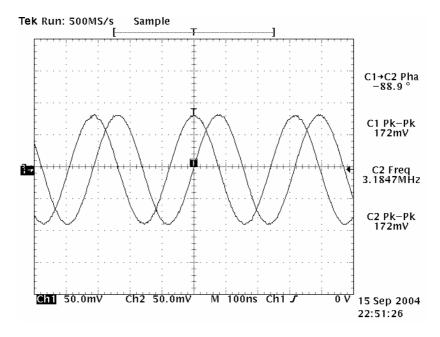

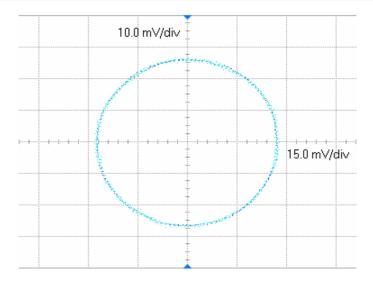

In Fig 2.35, it shows down-conversion signal is about -43.86dBm. In Fig 2.36, it shows down-conversion image is about -72.11dBm. From Fig 2.35 and 2.36, it reveals that IRR is about 28.25dB after calibration. And we can estimate that gain error is about 0.66dB and phase error is less than 1°.

Fig. 2.36 Down-conversion image (after calibration)

In Table 2.2, it lists the performance summary of quadrature LO generator with I/Q mismatch calibration. Measured IRR is underestimated because of gain mismatch in quadrature hybrid and devices mismatch in I/Q signal path.

| Technology         | TSMC 0.18    | um CMOS   |

|--------------------|--------------|-----------|

| Supply Voltage     | 1.8          | 3 V       |

| I/Q phase error    | <            | 1°        |

| I/Q gain error     | ≈ 0.6        | 66dB      |

| IRR                | 28.2         | 5 dB      |

| VCO tuning range   | 3.36GHz -    | ~ 3.87GHz |

| - HALLER           | VCO          | 3.64 mW   |

| E A III            | I/Q divider  | 5.56 mW   |

| Power Consumptions | LO generator | 6.97 mW   |

| STITUTE ST         | Mixer        | 9.05 mW   |

|                    | Adder        | 14.89 mW  |

|                    | Overall      | 40.11 mW  |

Table 2.2 Measured performance summary

## Chapter 3

# Front-End Receiver with I/Q Mismatch Calibration

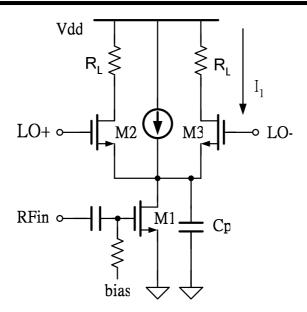

The function of our direct-conversion receiver is introduced in Chapter 1. In addition to the quadrature LO generator, the receiver requires the programmable front-end, including a variable-gain type LNA and a pair of gain-switch down-conversion mixer. Fig 3.1 gives an overall view of receiver block diagram. The quadrature LO generator is implemented by that mentioned in chapter 2. The LNA and mixer design will be introduced in the following.

Fig. 3.1 Receiver block diagram

## **3.1** Front-End Link Budget

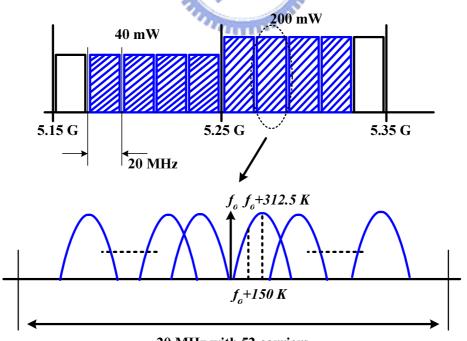

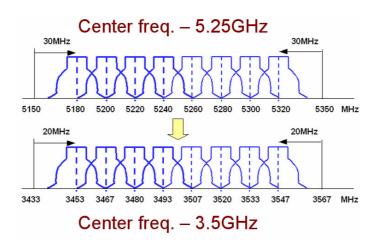

The IEEE 802.11a standard specifies over a generous 300-MHz allocation of spectrum for unlicensed operation in the 5-GHz block. Of that 300-MHz allowance, there is a contiguous 200-MHz portion extending from 5.15 to 5.35 GHz, and a separate 100-MHz segment from 5.725 to 5.825 GHz, whereas the output power cannot exceed 40 mW for channels from 5.15 to 5.25 GHz or 200 mW for channels from 5.25 to 5.35 GHz. Fig 3.2 shows a lower frequency band of the channel allocation [1]. To determine the precise target value, the specification sets frequency range, noise figure, maximum input signal level (input-referred 1-dB compression point). For frequency range, it is often acceptable to cover only the lower 200-MHz band. The upper 100-MHz domain is not contiguous with that allocation, so its coverage would complicate somewhat the design of the synthesizer. Furthermore, that upper 100-MHZ spectrum is not universally available, such as HIPERLAN. Hence,

20 MHz with 52 carriers

Fig. 3.2 IEEE 802.11a lower frequency band of the channel allocation

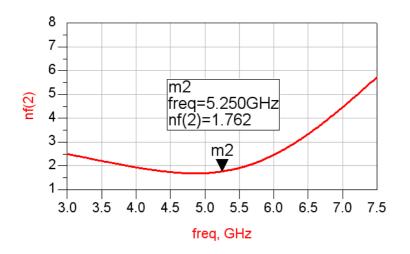

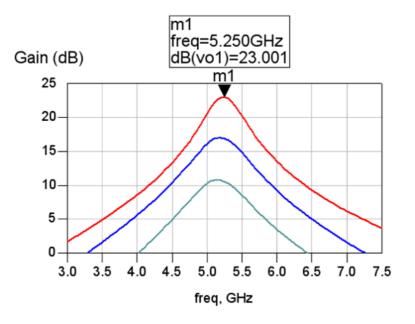

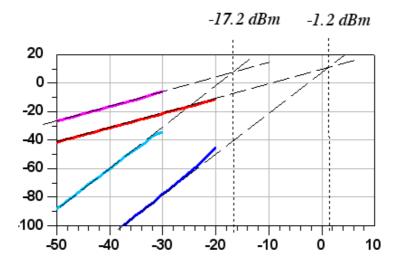

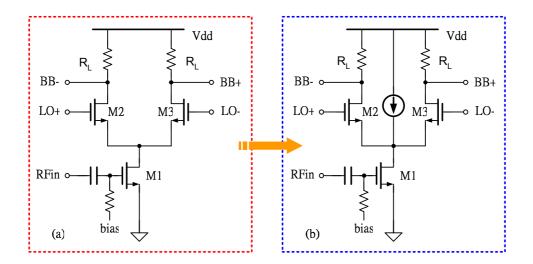

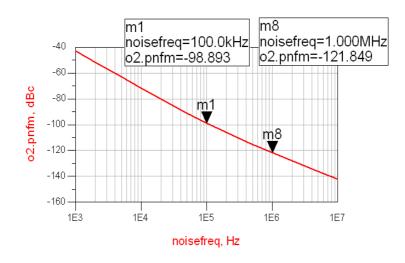

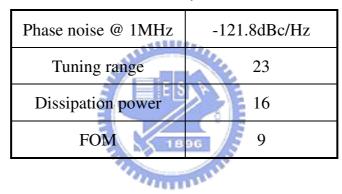

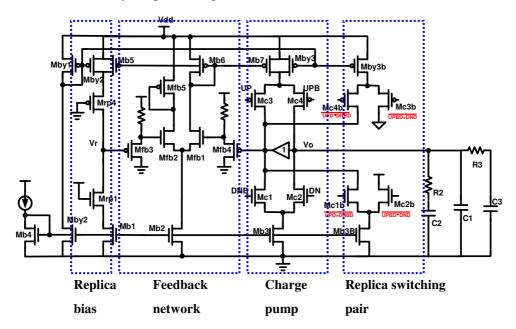

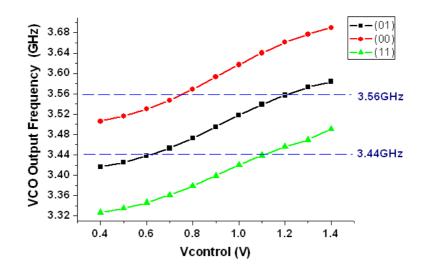

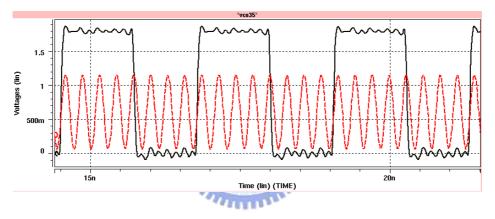

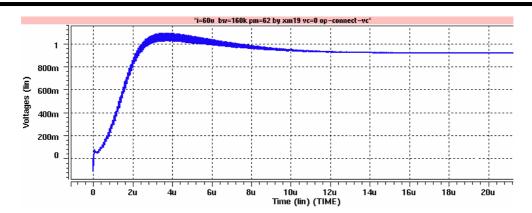

the receiver at the frequency band of 5.15-5.35GHz is our design goal. The specification simply recommends a noise figure of 10dB, with a 5-dB implementation margin. In order to accommodate the worst-case situation and gain more margins, maximum noise figure of 7dB is the design target for this receiver. The standard also specifies a value of -30 dBm as maximum input signal that a receiver must accommodate (for a 10% packet error rate). Converting this specification into a precise IIP3 target or 1-dB compression requirement is nontrivial. However, as a conservative rule of thumb, the 1-dB compression point of receiver should be about 4 dB above the maximum input signal power level that must be tolerated successfully. Based on this approximation, the target of input-referred 1-dB compression point has to be better than -26 dBm [11]. Furthermore, the IIP3 is about 9.6dB higher than the 1-dB compression point; therefore, the target of IIP3 is set to -16dBm.