## 國立交通大學

電子工程學系 電子研究所碩士班

## 碩士論文

互補式金氧半八位元 40MHz 取樣頻率管線化 類比至數位轉換器之設計與分析

## The Design and Analysis of a CMOS 8bit 40MS/s Pipelined Analog-to-Digital Converter

## 研 究 生:陳正瑞 指導教授:吳錦川 教授

中華民國九十三年五月

互補式金氧半八位元 40MHz 取樣頻率管線化 類比至數位轉換器之設計與分析

## The Design and Analysis of a CMOS 8bit 40MS/s Pipelined Analog-to-Digital Converter

研 究 生:陳正瑞 指導教授:吳錦川 教授 Student: Cheng-Jui Chen Advisor: Prof. Jiin-Chuan Wu

Submitted to Institute of Electronics College of Electrical Engineering and Computer Science National Chiao Tung University In Partial Fulfillment of the Requirements for the Degree of Master of Science in

**Electronic Engineering**

May 2004

Hsin-Chu, Taiwan, Republic of China

## 互補式金氧半八位元 40MHz 取樣頻率管線化 類比至數位轉換器之設計與分析

學生:陳正瑞

### 指導教授:吳錦川教授

國立交通大學電子工程學系 電子研究所碩士班

#### 摘要

本論文先對管線化類比至數位轉換器的架構加以描述,並同時將管線化 類比至數位轉換器所可能造成誤差的原因加以探討,並提出解決方法。

本論文描述一個 3.3V,8 位元,40M sample/s 管線化的類比至數位轉換 器。本設計採用每級 1.5 位元的架構並運用數位錯誤修正的技術。主要的 元件:餘數放大器 (residue amplifier),比較器 (comparator),正反 器 (D-flip-flop),加法器 (adder)和時脈產生器 (clock generator)。 整個電路是由七級加上一個前端輸入保持電路所組成,全差動輸入範圍為 -1V~+1V。餘數放大器的部分是以開闢加電容配合放大器來實現。比較器的 部分是以開闢加電容配合動態比較器來實現。本架構多加入了一個不同相 位的時脈,以減少比較器對餘數放大器的雜訊干擾,及確保比較器得到正確 的值。

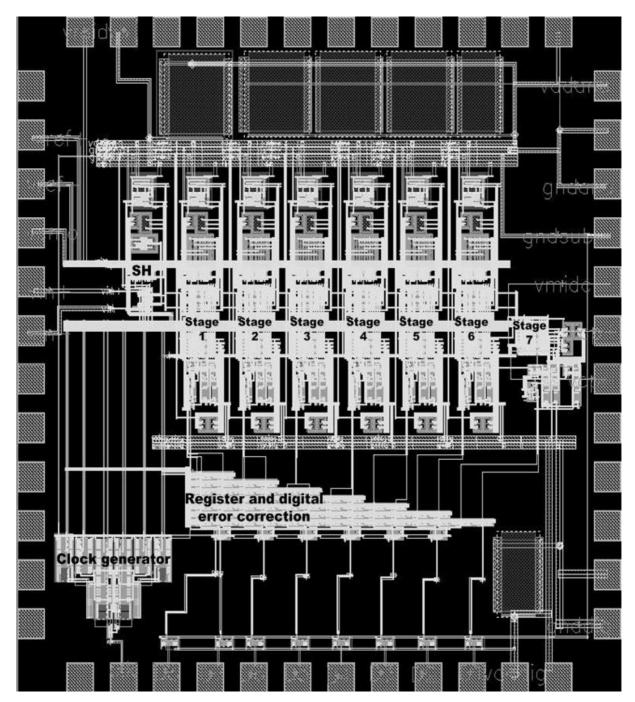

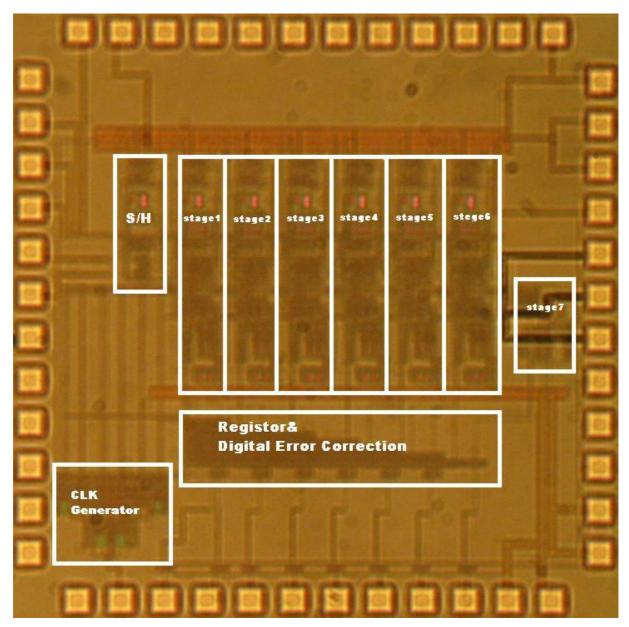

本架構使用台積電 0.35um 2P4M 互補式金氧半的製程,並以混合訊號全 客戶式佈局實現。整個晶片佈局面積 1.8mm x 1.8mm。以 HSPICE 作模擬, 模擬的結果符合 8 位元解析度, 40MHz 取樣頻率,總功率消耗約為 40mW。

## The Design and Analysis of a CMOS 8bit 40MS/s Pipelined Analog-to-Digital Converter

Student: Cheng-Jui Chen

Advisor: Prof. Jiin-Chuan Wu

Department of Electronics Engineering & Institute of Electronics National Chiao-Tung University

#### ABSTRACT

In this thesis, the advantage and the architecture of the pipelined analog-to-digital converter (ADC) is described. Furthermore, the error source of the pipelined ADC is shown and discussed. And there are some solutions to these problems in this thesis.

We also illustrate a 3.3V, 8-bit, 40M sample/s CMOS pipelined ADC. The 1.5b/stage architecture with digital error correction is used in this ADC. The component in the ADC is the residue amplifier, the comparator, the D flip-flop, the adder and the clock generator. The ADC has 7 stages and a front-end sample-and-hold(S/H). The input is a fully differential format, the input range is  $-1V \sim +1V$ . The residue amplifier is implemented by the switch capacitor circuit. The comparator is implemented by the switch and capacitor and dynamic comparator. We add a new phase of clock to reduce the noise in residue amplifier from comparator.

The ADC was designed using TSMC 0.35um 2P4M CMOS process and mixed-signal full custom layout is applied. The chip area is 1.8mm x 1.8mm. The simulation is done by HSPICE. The specification of the ADC is 8bit resolution, 40M sampling rate, less than 40mW power consumption.

誌 謝

首先要感謝指導教授吳錦川博士讓我有機會加入老師的研究群, 並對老師在我兩年研究所其間所提供的細心指導表示感謝。

感謝奈米電子與晶片系統實驗室裡所有的學長姐跟同學們這兩 年來的照顧。特別謝謝林子超,黃鈞正,范啟葳,廖以義,陳志 熒,王文傑,歐陽銘,范姜朝馨,蘇芳德學長在電路設計以及佈 局規劃上的指導,以及在晶片量測上所給予的寶貴意見,讓我可以 順利的完成這篇論文。除此之外,感謝同窗史周,權哲,棋樺, 聖文,瑋仁,阿嵐,在這兩年研究生的生涯中陪伴我一起成長並 給我許多幫助,感謝你們。

感謝我的女友淑惠,性人,小雞,阿胖,祥哥,芳吟,煒明, 馬亭,傑堯,耀中,在我最低潮的時候給我加油打氣,讓我能夠 有堅持下去的信念。

感謝我的家人,沒有你們的後盾,就沒有今日的我,謝謝你們。

謹以此篇論文獻給所有關心我的人

正瑞 於 新竹交大 筆

iii

### **CONTENTS**

| CHINESE ABSTRACT | i    |

|------------------|------|

| ENGLISH ABSTRACT | ii   |

| ACKNOWLEDGEMENTS | iii  |

| CONTENTS         | iv   |

| TABLE CAPTION    | vii  |

| FIGURE CAPTIONS  | viii |

### **CHAPTER 1 INTRODUCTION**

| 1.1 | Motivation and Goals1 |

|-----|-----------------------|

| 1.2 | Thesis Organization2  |

## CHAPTER 2 Fundamentals

| 2.1 Ov  | verview                         |    |

|---------|---------------------------------|----|

| 2.1.1   | Delta-Sigma Architecture        |    |

| 2.1.2   | SAR Architecture                |    |

| 2.1.3   | Flash Architecture              |    |

| 2.1.4   | Pipeline Architecture           | 7  |

| 2.1.5   | A Simple ADC Comparison Matrix  | 8  |

| 2.2 Pij | peline ADC versus Other ADCs    | 9  |

| 2.2.1   | Versus the Delta-Sigma          | 9  |

| 2.2.2   | Versus SAR                      | 9  |

| 2.2.3   | Versus Flash                    | 10 |

| 2.2.4   | Conclusion                      | 10 |

| 2.3 A1  | rchitecture for 8-bit 40MHz ADC | 11 |

| 2.3.1   | Architecture                    | 11 |

| 2.3.2   | Timing Strategy                 | 13 |

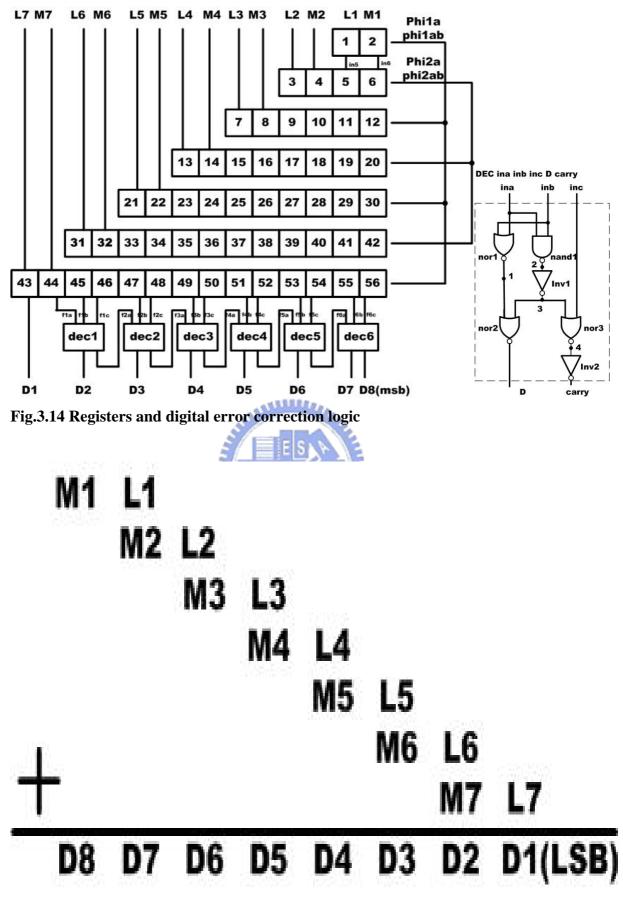

| 2.3.3   | Digital Error Correction        | 14 |

| 2.4 N   | on-ideality of Considerations   | 16 |

## **CHAPTER 3 Circuit Design**

| 3.1 | Sample-and-Hold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 17 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | .1 Capacitors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

| 3.1 | .2 Op-amp Gain Requirement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 19 |

| 3.1 | .3 Op-amp Bandwidth Requirement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 20 |

| 3.1 | .4 Switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 22 |

| 3.2 | Multiplying DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 22 |

| 3.3 | Op-amp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 25 |

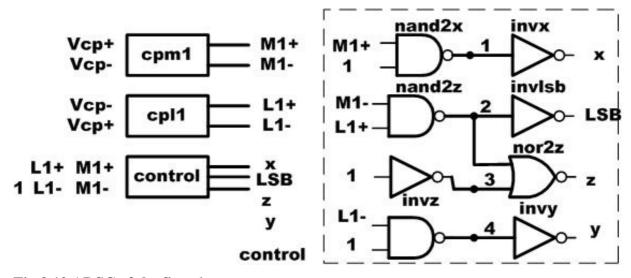

| 3.4 | Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 27 |

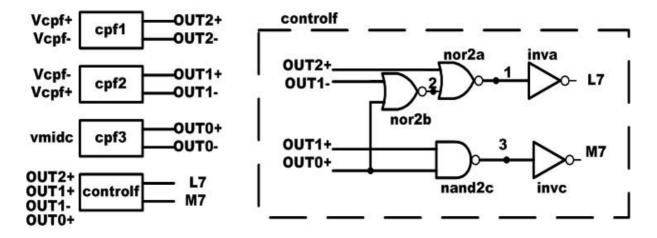

| 3.5 | Digital Error Correction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

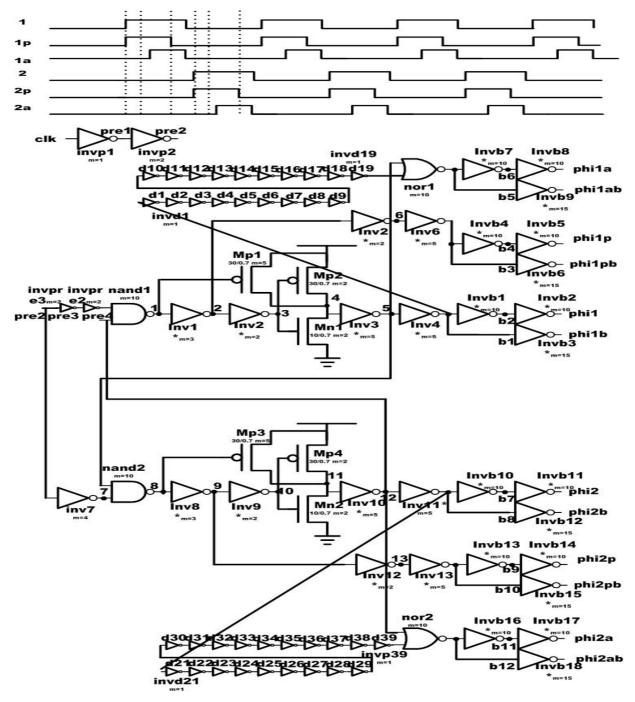

| 3.6 | Clock Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 32 |

| 3.7 | Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

| 3.7 | 7.1 Simulation results of op-amp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

| 3.7 | 7.2 Simulation results of S/H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

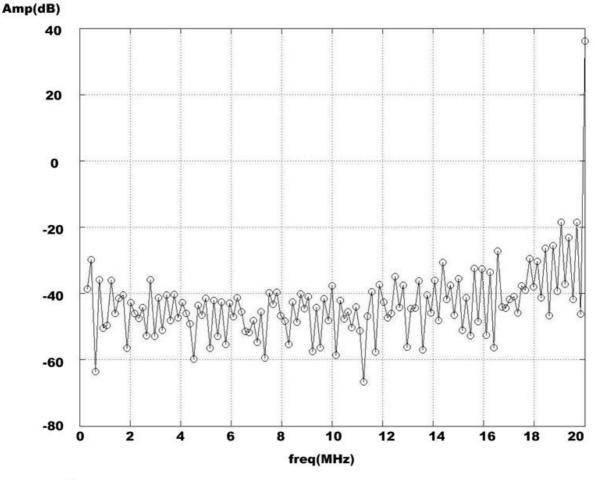

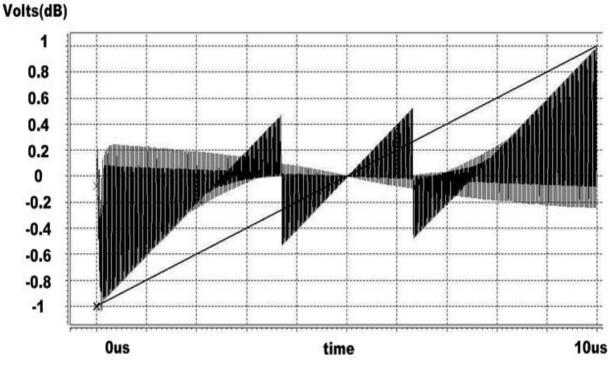

| 3.7 | 7.3 Simulation results of MDAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 34 |

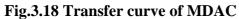

| 3.7 | 7.4 Simulation results of clock generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 35 |

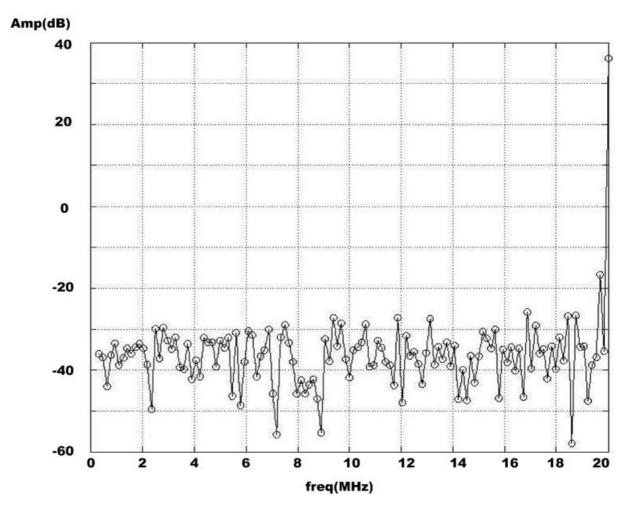

| 3.7 | 7.5 Simulation results of whole chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|     | The state of the s |    |

## **CHAPTER 4** Implementation and Results

| 4.1   | Layout consideration |    |

|-------|----------------------|----|

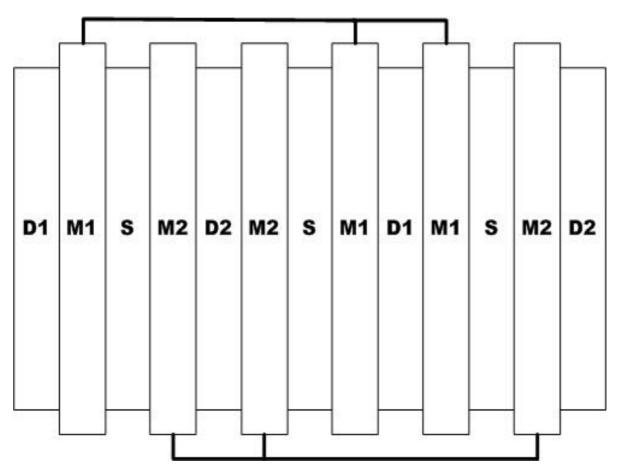

| 4.1.1 | Transistor matching  |    |

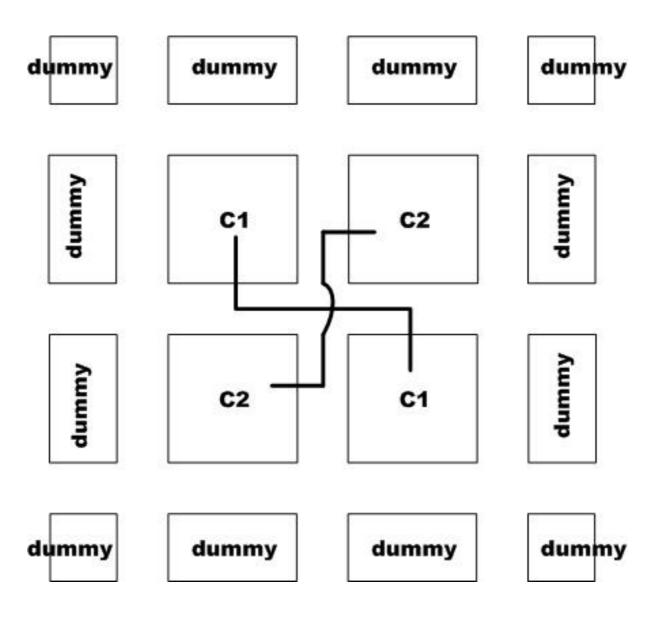

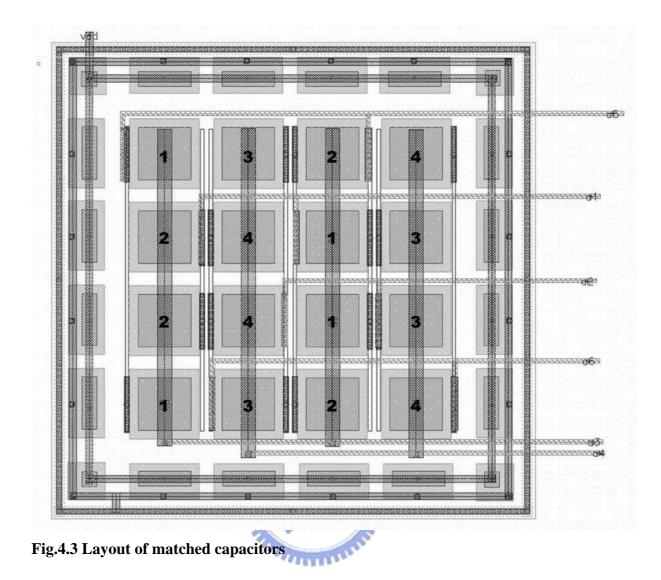

| 4.1.2 | Capacitor            |    |

| 4.1.3 | Floor Plan           |    |

| 4.2   | Performance          | 43 |

| 4.2.1 | Dynamic              |    |

| 4.2.2 | Static               | 44 |

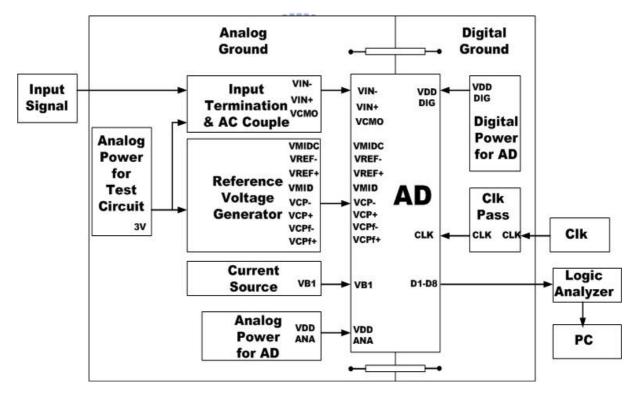

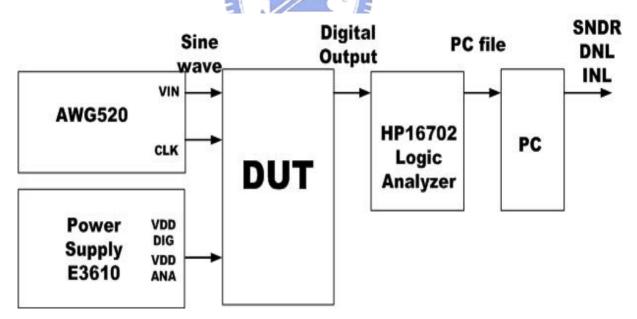

| 4.3   | Test setup           | 46 |

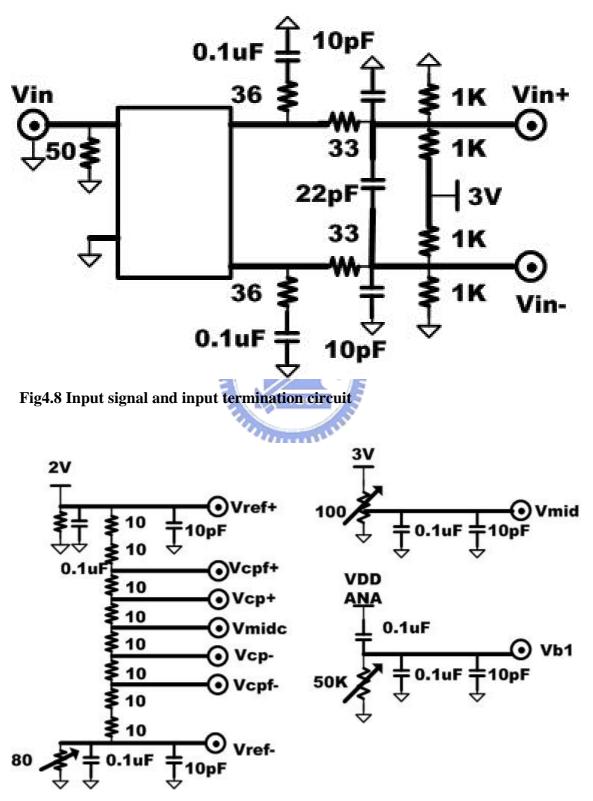

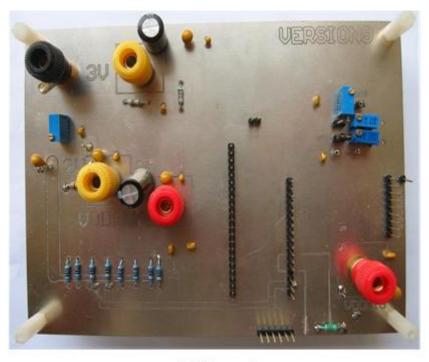

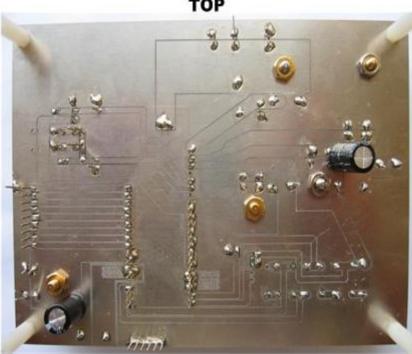

| 4.3.1 | PC board design      | 46 |

| 4.3.2 | Instrument setup     |    |

| 4.4   | Test result          |    |

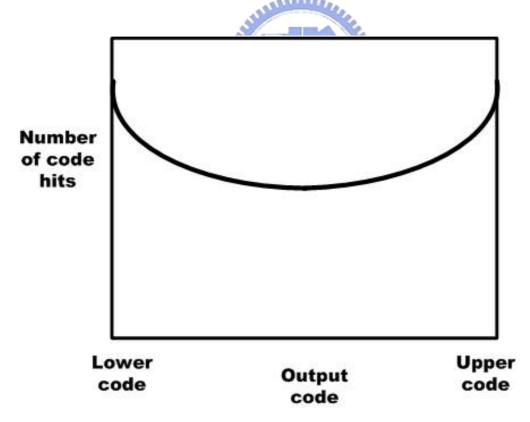

| 4     | .4.1 | DC measurement |    |

|-------|------|----------------|----|

| 4     | .4.2 | Discussion     |    |

| СНАРТ | ER S | 5 Conclusions  |    |

| 5.1   | Co   | onclusion      | 54 |

| 5.2   | Fu   | ture work      | 55 |

|       |      | CES            |    |

## **TABLE CAPTIONS**

| Table.2.1 | ADC Comparison Matrix                      | 8  |

|-----------|--------------------------------------------|----|

| Table.3.1 | The requirements of Op-amp in S/H and MDAC |    |

| Table.3.2 | Post-simulation results of op-amp          |    |

| Table.4.1 | Pin assignments                            | 42 |

| Table.4.2 | Codes distribution                         | 52 |

### **FIGURE CAPTIONS**

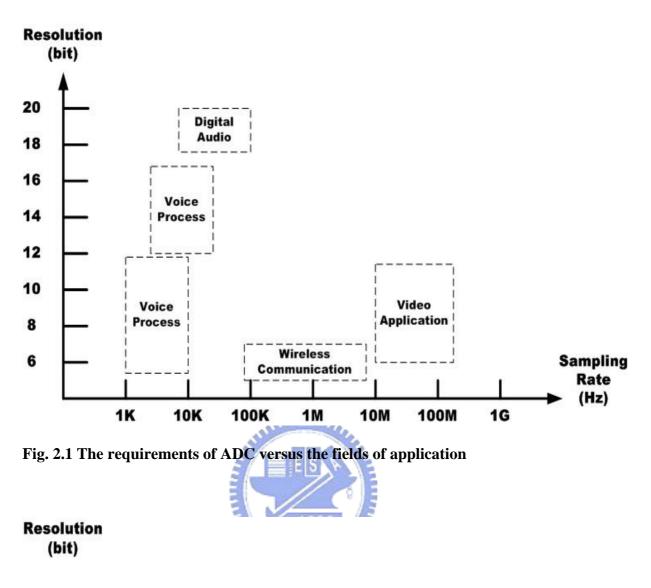

| Fig.2.1  | The requirements of ADC versus the fields of application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

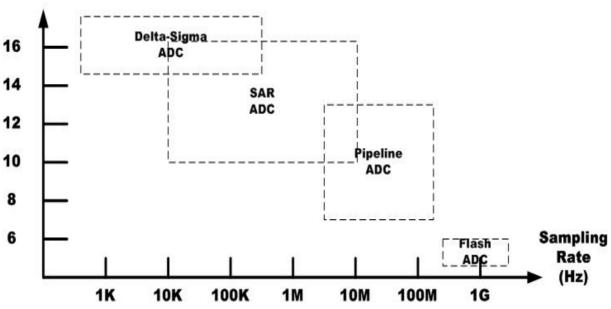

| Fig.2.2  | The properties of different architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

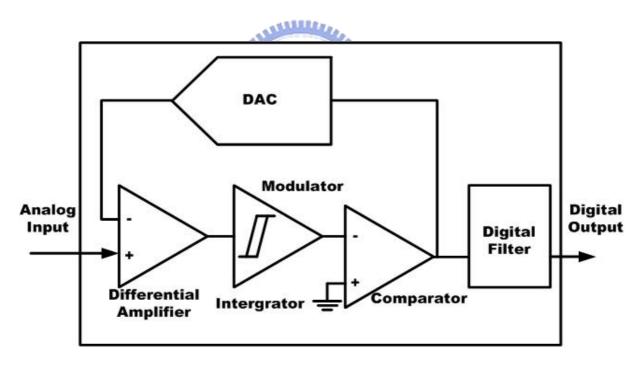

| Fig.2.3  | Delta-Sigma Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

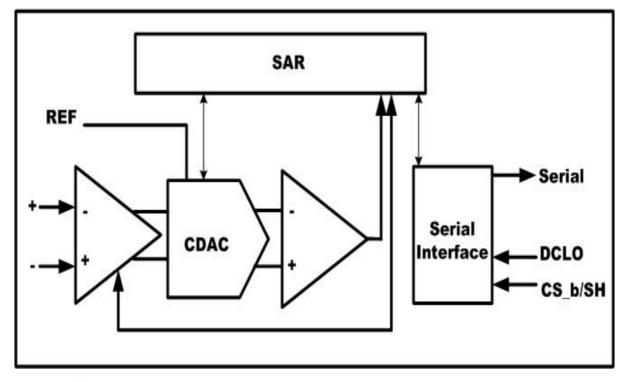

| Fig.2.4  | SAR Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6  |

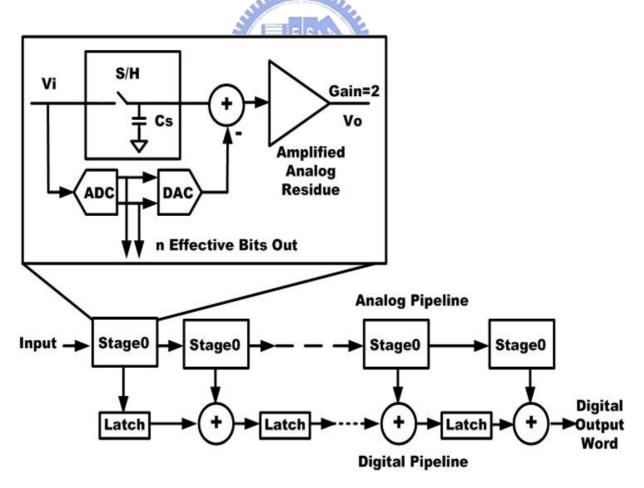

| Fig.2.5  | Pipeline Arechitecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7  |

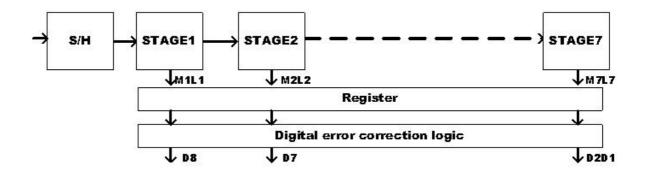

| Fig.2.6  | Architecture of 8-bit Pipeline ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 12 |

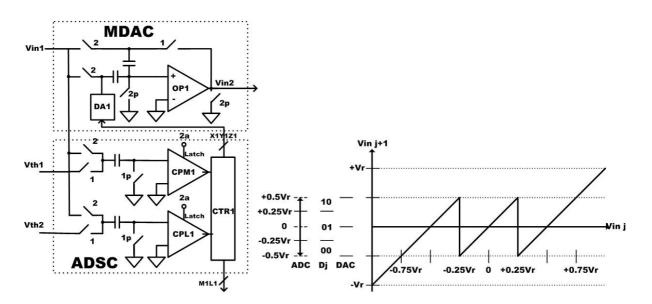

| Fig.2.7  | Main Stage Circuit and Transfer Curve                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

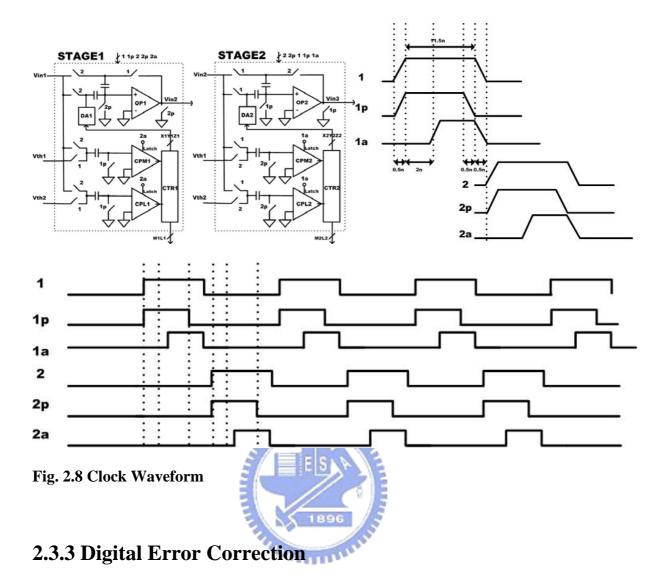

| Fig.2.8. | Clock Waveform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

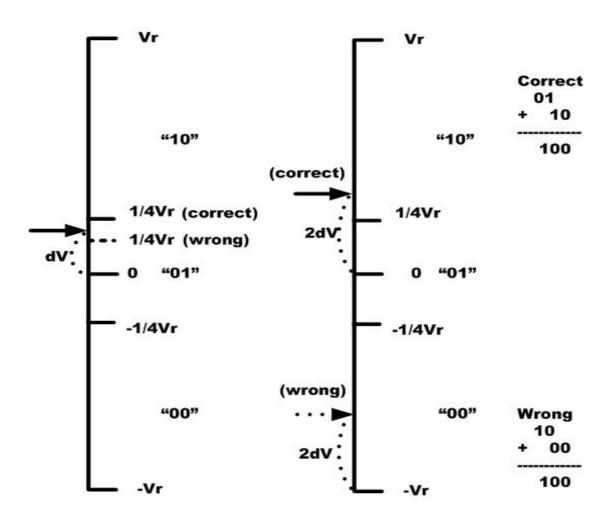

| Fig.2.9  | Example of Design Error Correction: First stage to Next Stage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15 |

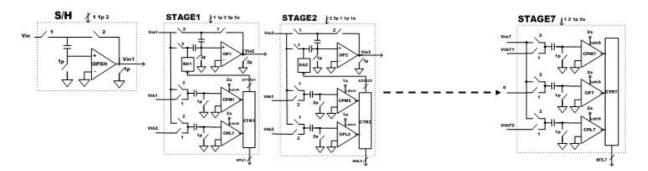

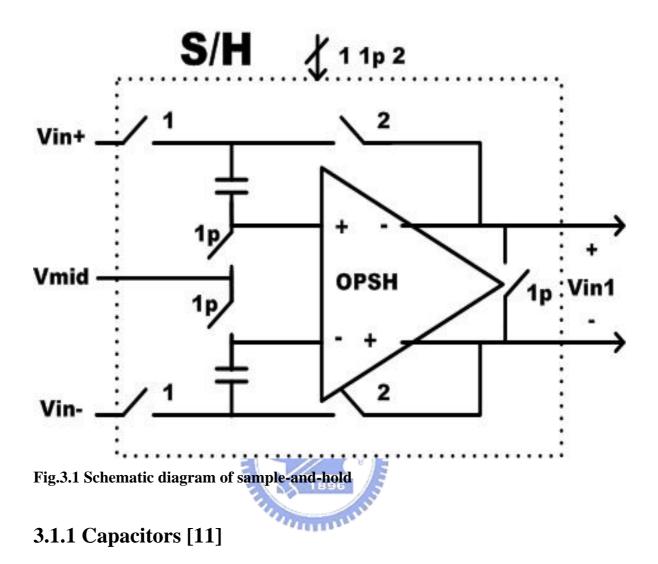

| Fig.3.1  | Schematic diagram of sample-and-hold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

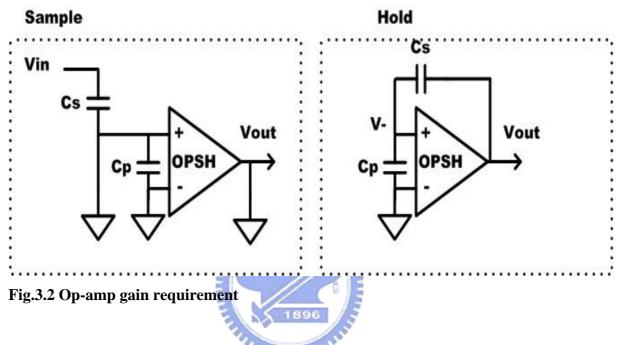

| Fig.3.2  | Op-amp gain requirement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

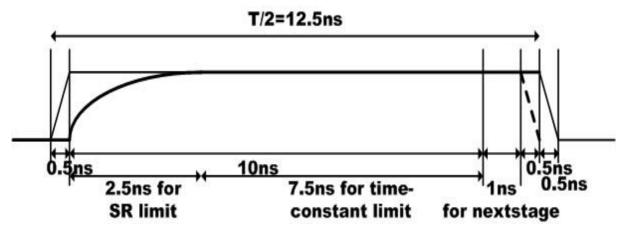

| Fig.3.3  | Settling time of S/H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

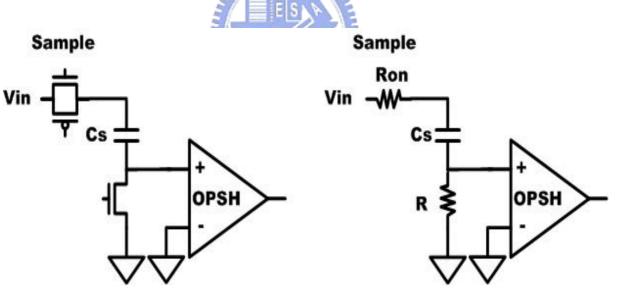

| Fig.3.4  | Switches of S/H in Sample mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

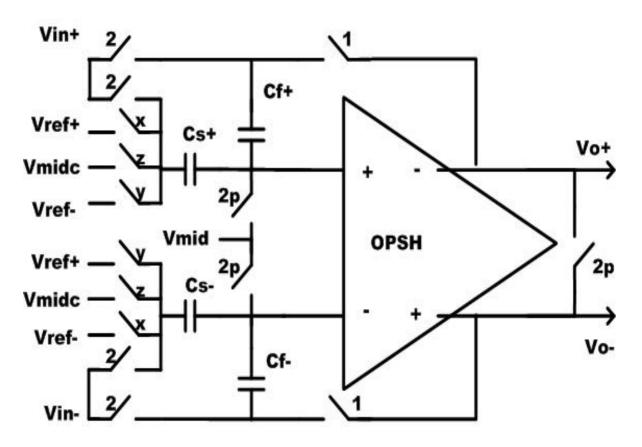

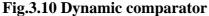

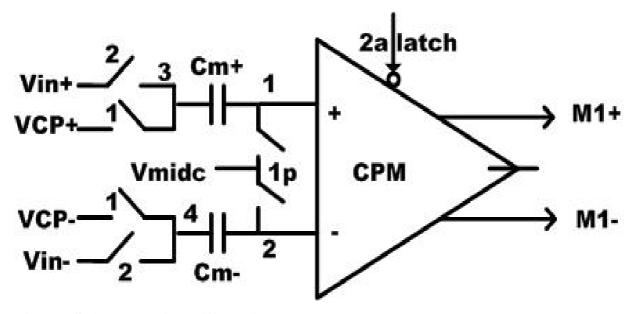

| Fig.3.5  | Schematic diagram of MDAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

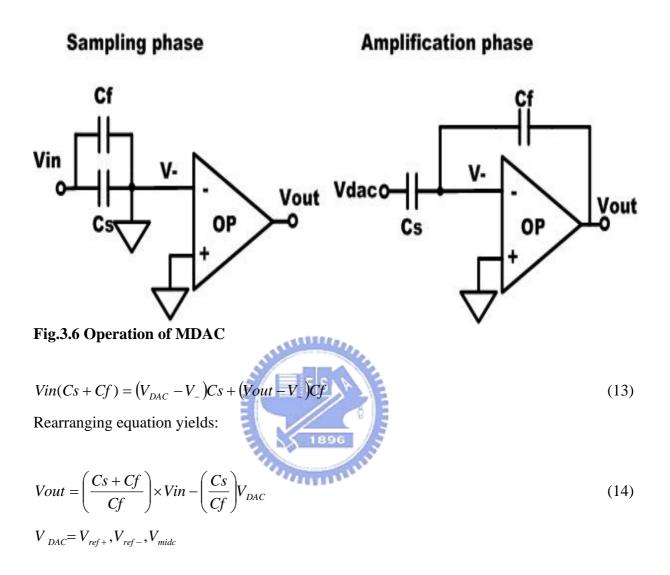

| Fig.3.6  | Operation of MDAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

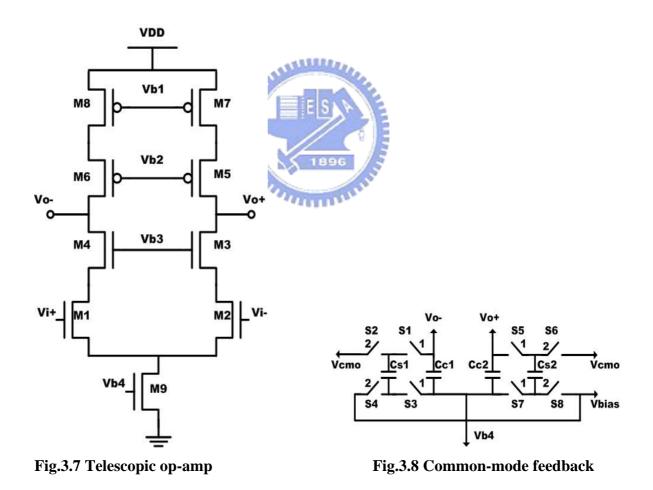

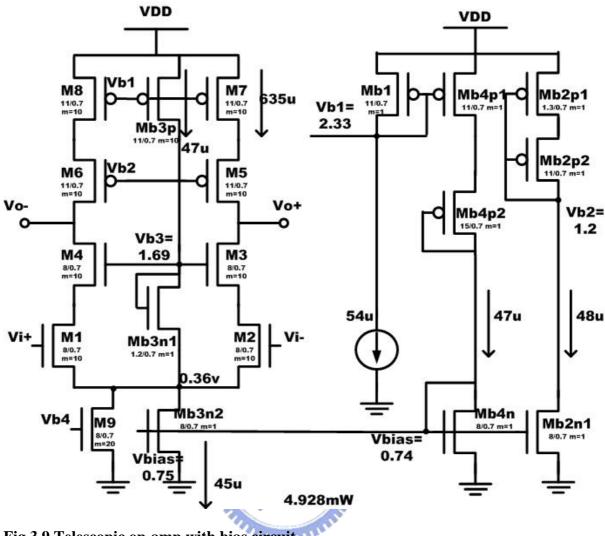

| Fig.3.7  | Telescopic op-amp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

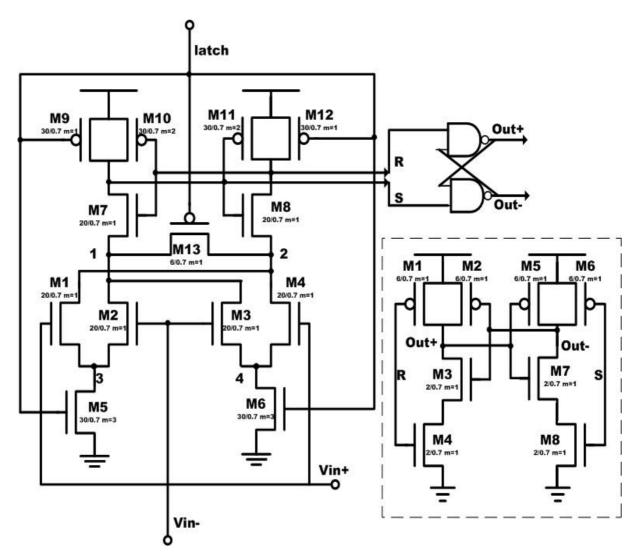

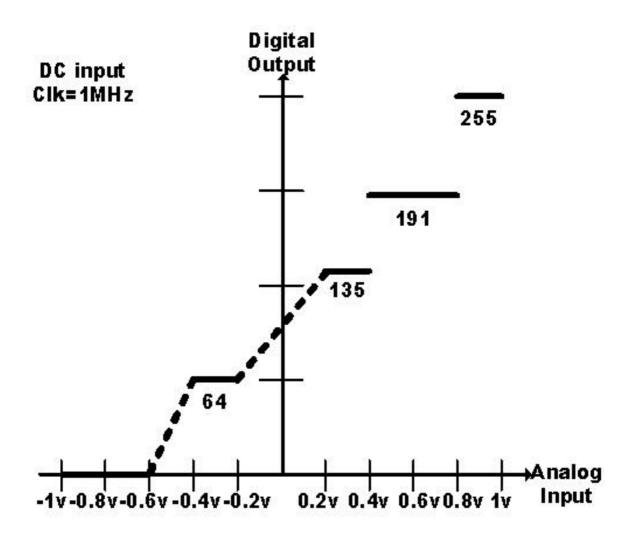

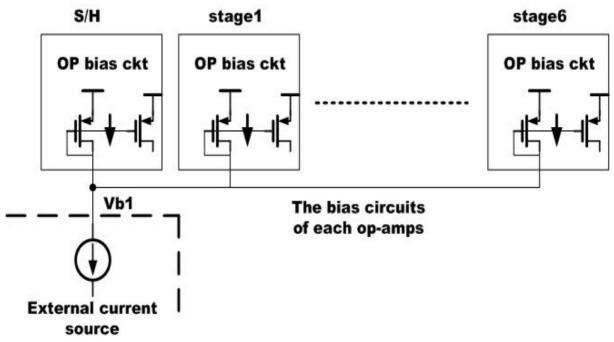

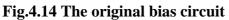

| Fig.3.8  | Common-mode feedback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |