### 國立交通大學

電子工程學系電子研究所

博士論文

應用於六百億赫茲通訊系統的毫米波 互補式金氧半電路分析與設計

The Analysis and Design of Millimeter-Wave CMOS Circuits for 60-GHz Communication Systems

研究生:陳旻珓 Min-Chiao Chen

指導教授 : 吳重雨 Chung-Yu Wu

中華民國九十七年十月

## 應用於六百億赫茲通訊系統的毫米波 互補式金氧半電路分析與設計

# The Analysis and Design of Millimeter-Wave CMOS Circuits for 60-GHz Communication Systems

研究生:陳旻珓 Student : Min-Chiao Chen

指導教授 :吳重雨 Advisor :Chung-Yu Wu

#### A Dissertation

Submitted to Department of Electronics Engineering and

Institute of Electronic

College of Electrical and Computer Engineering

Nation Chiao Tung University

in Partial Fulfillment of Requirements

for the Degree of

Doctor of Philosophy

in

Electronic Engineering

October 2008

Hsinchu, Taiwan, Republic of China 中華民國九十七年十月

## 應用於六百億赫茲通訊系統的毫米波 互補式金氧半電路分析與設計

學生: 陳旻珓 指導教授: 吳重雨博士

## 國立交通大學電子工程學系電子研究所

#### 摘 要

本篇論文主要闡述了適用於60GHz低功率通訊系統的毫米波互補式金氧半電路其設計方法及製作技術。論文中包含下列三個部分:(1)次諧波注入鎖住式三倍頻器的分析、模型建立與設計方法;(2)整合注入鎖住式頻率倍乘器的60GHz鎖相迴路電路分析及設計;(3)整合注入鎖住式三倍頻器的60GHz直接降頻接收機的設計。

首先,本論文提出以及分析一個具有差動輸出的互補式金氧半次諧波注入鎖住式三倍頻器,並且設計使其適用於K頻段和V頻段。根據所提出的次諧波注入鎖住式三倍頻器的架構,發展出鎖頻範圍及輸出相位雜訊的模型。K頻段的注入鎖住式三倍頻器採用了0.18微米互補式金氧半製程設計與製作。由量測結果可知:當功率消耗為0.45毫瓦特和輸入功率為4dBm時,鎖頻範圍為1092MHz;輸出的三階諧波對於一階、二階、四階及五階的諧波抑制比分別為22.65、30.58、29.29及40.35分貝;當使用可變電容及增加功率消耗到2.95毫瓦特時,K頻段的注入鎖住式三倍頻器鎖頻範圍可達到3915MHz。另外設計了採用0.13微米互補式金氧半製程的V頻段的注入鎖住式三倍頻器。量測結果顯示:當功率消耗為1.86毫瓦特和輸入功率為6dBm時,鎖頻範圍為1422MHz。可以發現到此次所提出的注入鎖住式三倍頻器,其鎖頻範圍與傳統利用可變電容來調整輸出頻率的壓控振盪器是相似的。

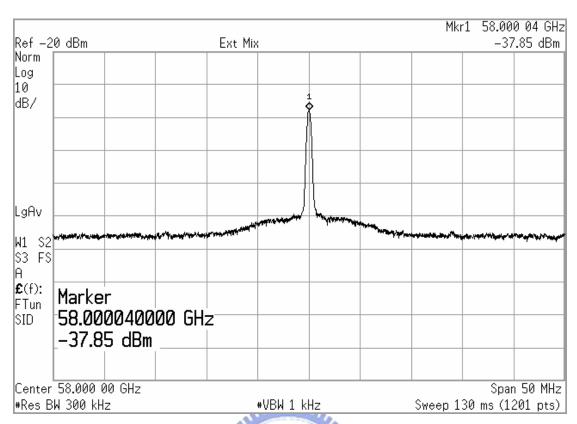

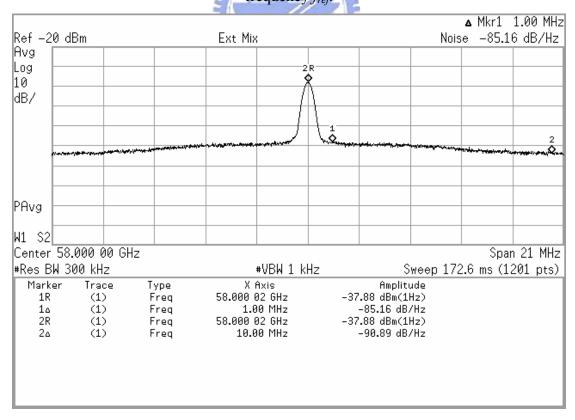

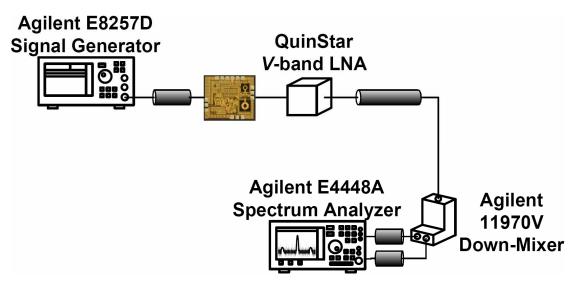

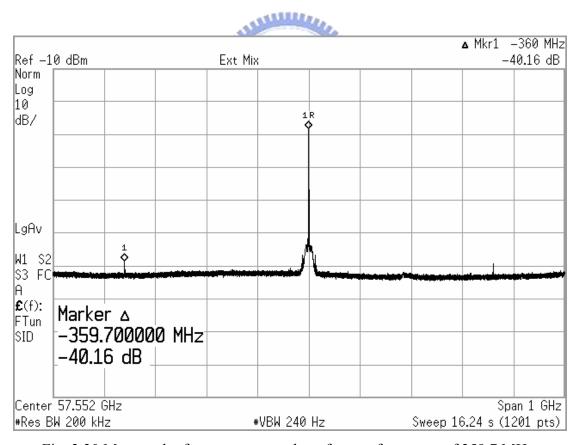

其次,本論文提出了一個能夠產生60GHz輸出的整合注入鎖住式頻率倍乘器之鎖相迴路。此60GHz鎖相迴路整合了壓控振盪器、注入鎖住式頻率倍乘器、除32的頻率除法器、相位頻率偵測器、電荷幫浦和迴路濾波器。因為所提出的注入鎖住式頻率倍乘器能夠產生壓控振盪器的五階諧波訊號,所以壓控振盪器僅需工作在所需要頻率的五分之一。此鎖相迴路採用了0.18微米互補式金氧半製程設計與製造。由量測結果可得:鎖相迴路輸出頻率為53.04到58.0GHz及輸出功率為-37.85dBm,相位雜訊在1MHz及10MHz偏移量下每赫茲分別較主訊號低85.2及90.9分貝,參考突波訊號較主訊號低65分貝。在1.8伏特的電壓工作下,其電路功率消耗為35.7毫瓦特。整個鎖相迴路的晶片面積為0.96×0.84平方毫米。

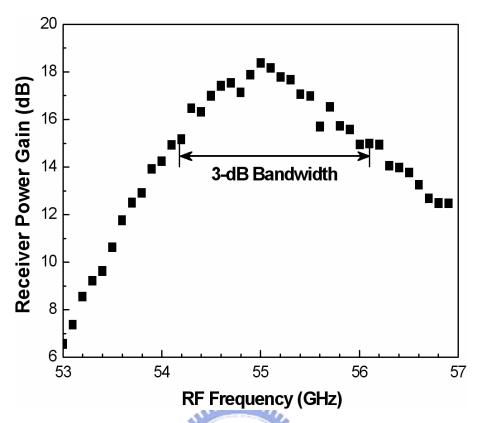

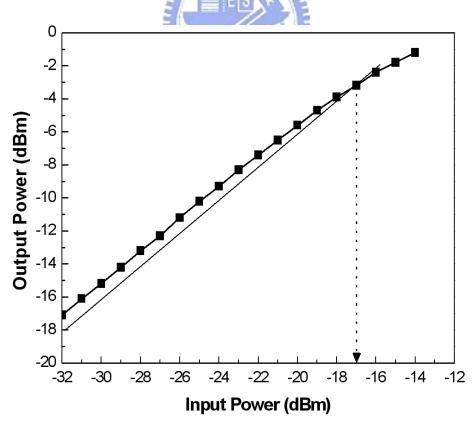

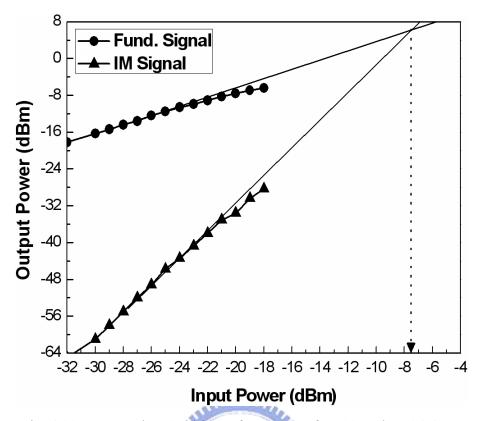

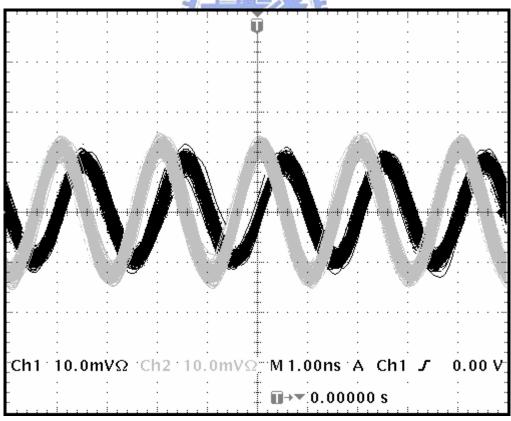

最後,本論文提出一個應用於60-GHz頻段且整合次諧波注入鎖住式三倍頻器的直接降頻接收機。本論文提出的直接降頻接收機包含了低雜訊放大器、四相位降頻混頻器、一個20-GHz的四相位壓控振盪器、兩個次諧波注入鎖住式三倍頻器、兩個中頻放大器以及兩個輸出緩衝級。在這個接收機中,本地振盪器的訊號是經由一個操作在三分之一載波的四相位壓控振盪器串接兩個次諧波注入鎖住式三倍頻器來提供。由於四相位壓控振盪器的頻率偏移,所以產生的本地振盪器訊號最高頻率只有55.03GHz。在以射頻訊號55.03GHz以及中頻訊號100MHz時的量測結果可知:接收機的增益為18.2分貝、雜訊指數16.96分貝、增益1分貝壓縮點在輸入端為-17.0dBm、三階互調失真點為-7.6dBm。本論文提出的接收機是使用0.13微米的互補式金氧半製程所製作。在供應電壓1.2伏特時的總功率消耗為31.0毫瓦特,整個直接降頻接收機的晶片面積為1.21×1.03平方毫米。

經由模擬以及量測結果可以證實,本論文所提出的注入鎖住式三倍頻器可適用於低功率高性能工作在毫米波頻段的收發機。在未來中,更進階的研究將可以整合低功率的單一晶片收發機以及頻率合成器。

The Analysis and Design of Millimeter-Wave CMOS Circuits for 60-GHz Communication Systems

Student: Min-Chiao Chen Advisor: Chung-Yu Wu

Department of Electronic Engineering Institute of Electronics National Chiao Tung University

#### **ABSTRACT**

In this thesis, the design methodologies and implementations of millimeter-wave CMOS circuit for 60-GHz low-power communication system are presented. There are three parts: (1) the analysis, modeling, and design of the subharmonic injection-locked frequency tripler (ILFT); (2) the analysis and design of 60-GHz phase-locked loop (PLL) integrated with injection-locked frequency multiplier (ILFM); and (3) the design of 60-GHz direct-conversion receiver integrated with ILFT.

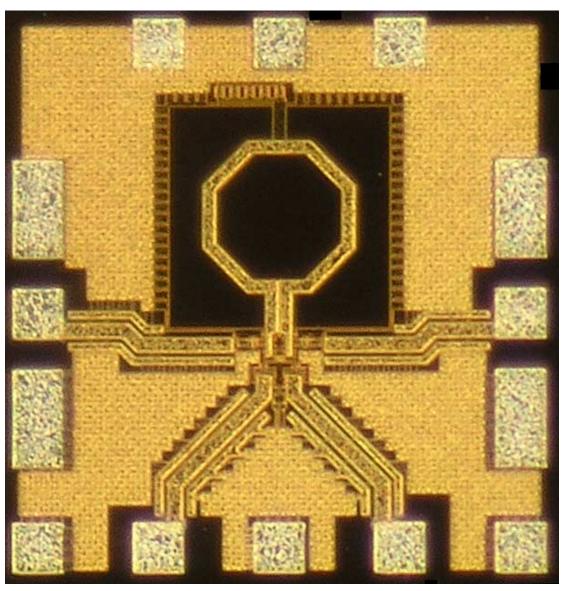

At first, *K*-band and *V*-band CMOS differential subharmonic ILFTs are proposed, analyzed, and designed. Based on the proposed ILFT structure, models for the locking range and the output phase noise are developed. A *K*-band ILFT is designed and fabricated using 0.18-μm CMOS technology. The measured locking range is 1092 MHz with a dc power consumption of 0.45 mW and an input power of 4 dBm. The harmonic rejection-ratios are 22.65, 30.58, 29.29, 40.35 dBc for the first, second, fourth, and fifth harmonics, respectively. The total locking range of the *K*-band ILFT can achieve 3915 MHz when the varactors are used and the dc power consumption is increased to 2.95

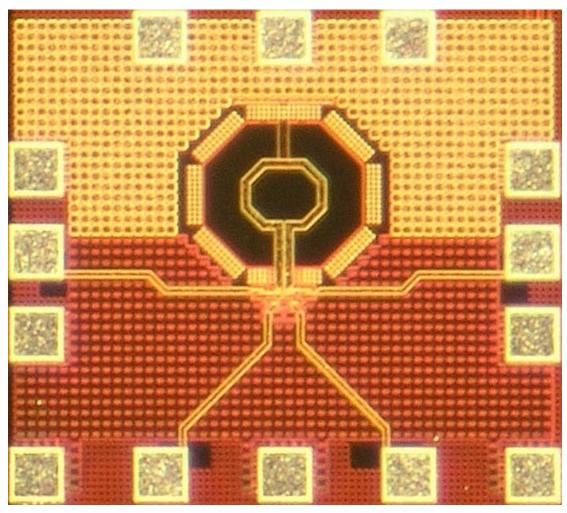

mW. A *V*-band ILFT is also designed and fabricated using 0.13-μm CMOS technology. The measured locking range is 1422 MHz with 1.86-mW dc power consumption and 6-dBm input power. It can be seen that the locking range of the proposed ILFT is similar to the tuning range of a conventional varactor-tuned bulk-CMOS voltage-controlled oscillator (VCO).

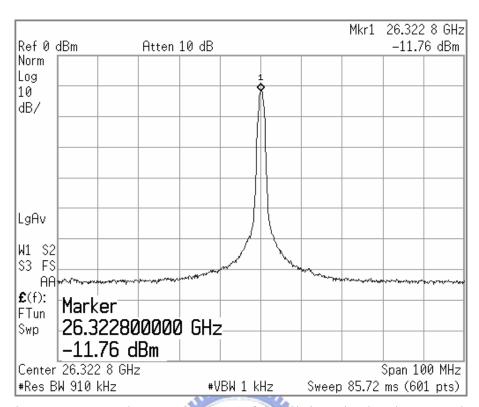

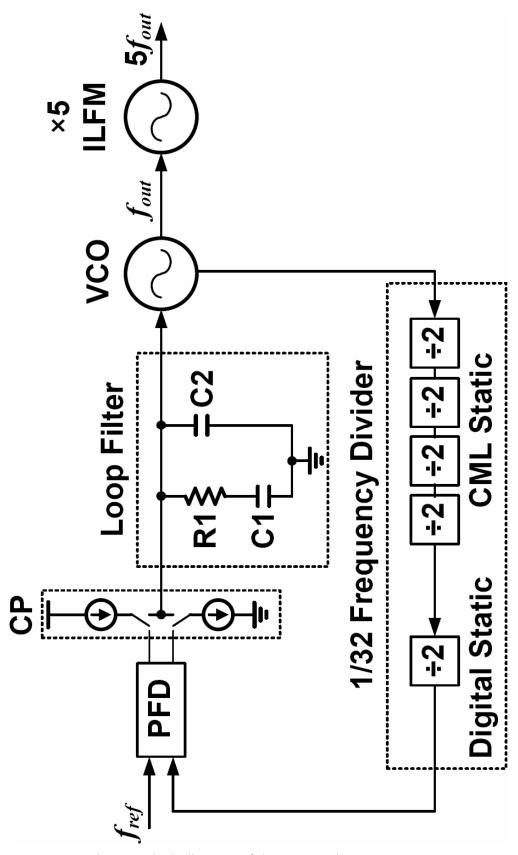

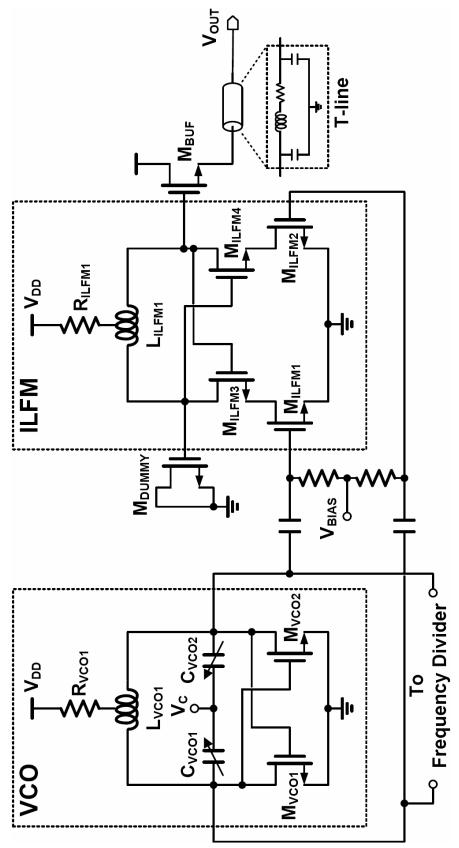

Secondly, a novel CMOS PLL integrated with ILFM that generates the 60-GHz output signal is proposed. The proposed 60-GHz PLL is composed of VCO, ILFM, 1/32 frequency divider, phase/frequency detector, charge pump, and loop filter. Because the proposed ILFM can generate the fifth-order harmonic frequency of VCO output, the operational frequency of the VCO can be reduced to only one-fifth of the desired frequency. The PLL is designed and fabricated in 0.18-μm CMOS technology. The output frequency range of the proposed PLL is from 53.04 GHz to 58.0 GHz with output power of –37.85 dBm. The measured phase noises at 1 MHz and 10 MHz offset from the carrier are –85.2 and –90.9 dBc/Hz, respectively. The reference spur level of –40.16 dBc is measured. The dc power dissipation of the fabricated PLL is 35.7 mW under a 1.8-V supply. The chip area including pads is 0.96 mm × 0.84 mm.

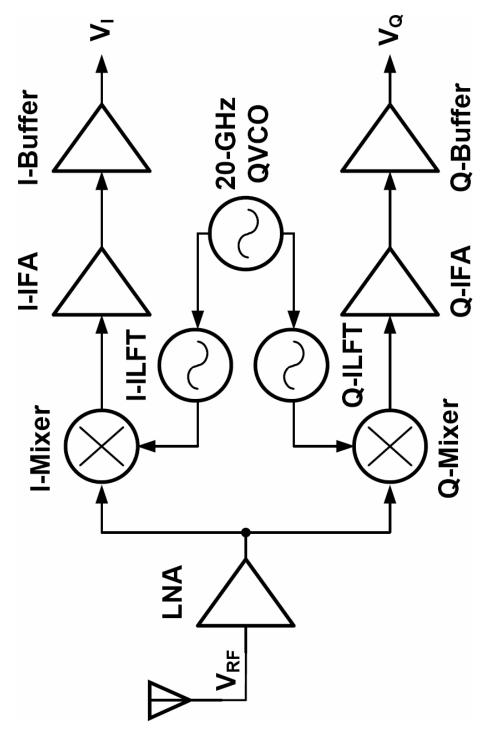

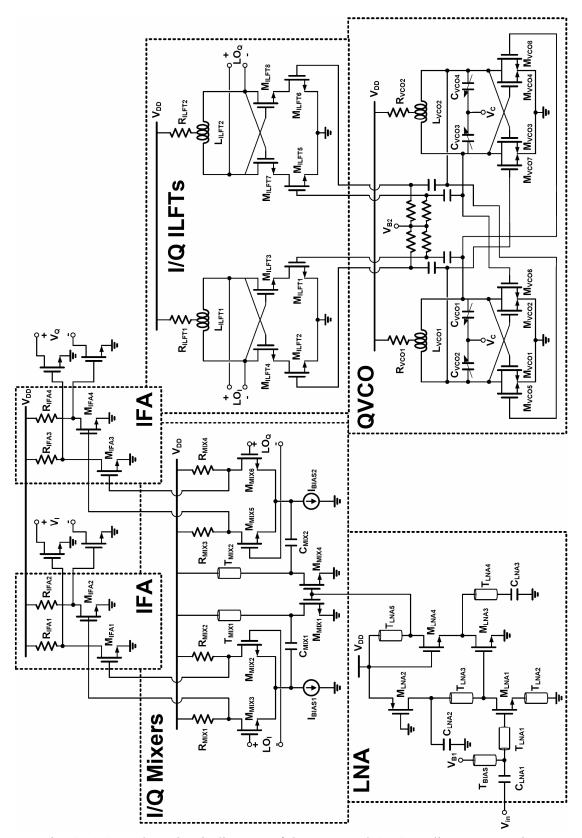

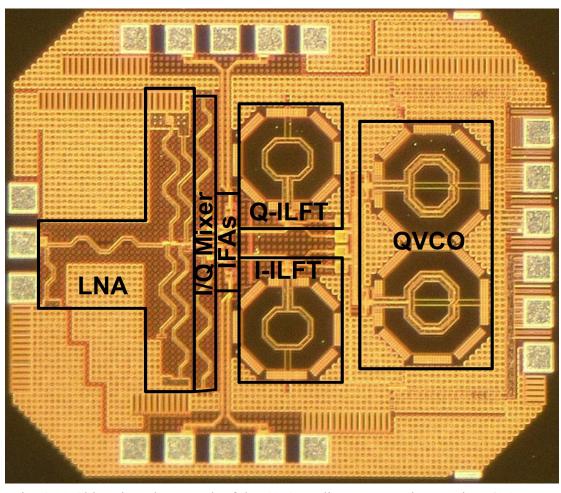

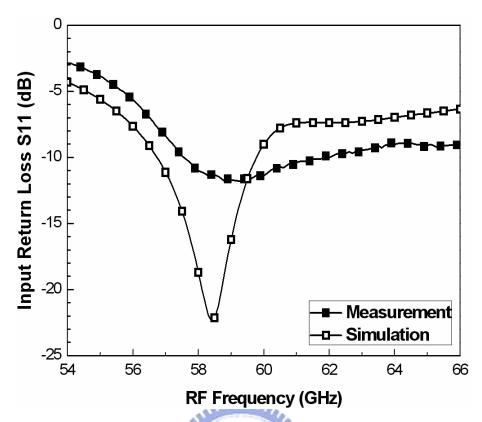

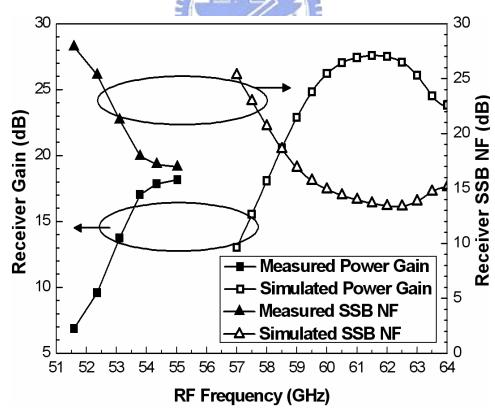

Finally, a 60-GHz direct-conversion receiver integrated with ILFT is proposed. The proposed direct-conversion receiver front-end is composed of a low-noise amplifier (LNA), I/Q quadrature down-conversion mixers, a 20-GHz QVCO, two ILFTs, two IF amplifiers, and two output buffers. In the proposed receiver, the local oscillator (LO) signals are generated by QVCO operated at only one-third of carrier frequency cascade with the two ILFTs. Due to the frequency shift of QVCO, the maximum RF frequency is only 55.03 GHz. The measured results show a receiver gain of 18.2 dB, a noise figure of 16.96 dB with RF frequency of 55.03 GHz and IF frequency of 100 MHz, channel bandwidth of 2 GHz with LO frequency of 55.02 GHz, an input-referred 1-dB compression point (P1dB) of -17.0 dBm, and input third-order inter-modulation intercept point (IIP3) of -7.6 dBm. The proposed receiver is implemented using

0.13- $\mu m$  CMOS technology and draws 25.84 mA from a 1.2-V supply. The total chip area, including testing pads, is only 1.21 mm  $\times$  1.03 mm.

It is believed that the proposed ILFT can be used in low-power high-performance transceiver design in the millimeter-wave band. Further research for low-power single chip transceiver and frequency synthesizer can be integrated in the future.

#### 致 謝

來到交大,一轉眼已經歷了十個寒暑,從進入大學部就讀時的懵懂,到如今取得博士學位,知識的浩瀚讓人逐漸體悟到不足而學會了謙虚。

首先要感謝吳重雨教授的啟蒙,在多年的指導下,我不僅學習到 了專業知識及培養面對問題、解決問題的態度與方法,更體會到與人 相處的態度及做事時該有的努力與堅持。另外也要特別感謝和藹的師 母曾昭玲女士,在我遭遇困難時所給予的鼓勵與關懷。感謝六位口試 委員:張志揚教授、孟慶宗教授、郭建男教授、詹益仁教授、蕭碩源 博士、高宏鑫博士,您的建議,讓我的論文更加完整。

在此我還要感謝蕭碩源、高宏鑫、周忠昀、王文傑四位學長,由 於你們過去在射頻電路累積的成果及經驗,讓我能有所依據並做更進 一步的發揮。此外研究群其他學長姊:鄭秋宏學長、廖以義學長、施 育全學長、黃冠勳學長及林俐如學姊帶著我進入了這間實驗室,以及 和我一起奮鬥的博士班、碩士班的同學;王仁傑、蘇烜毅、黃祖德、 蔡夙勇、丁彥、李宗霖、林韋霆、陳勝豪、楊文嘉、謝致遠,大夥曾 經一起在這間實驗室打拼,因為你們,讓研究過程多了許多的歡笑與 回憶。還要感謝實驗室其他研究群的學長姊和學弟妹,因為你們的對 實驗室的貢獻,提供了實驗室成為一個良好的研究環境,讓研究過程 更加順利。

最後,最重要的就是這些年來在我身後默默支持我的家人,致上 最深的感謝給我的父親、母親、大姊和二姊,感謝你們對我付出的一 切,讓我能夠完成學業。今日的成果,獻給我最親愛的家人。

> 陳 旻 珓 誌于風城交大 戊子 秋

#### **CONTENTS**

| ABSTRACT (      | CHINE  | SE)                                         | i   |

|-----------------|--------|---------------------------------------------|-----|

| ABSTRACT (      | ENGLIS | SH)                                         | iii |

| <b>ACKNOWLE</b> | DGEMI  | ENT                                         | vi  |

| CONTENTS        |        |                                             | vii |

| TABLE CAPT      | ΓIONS  |                                             | X   |

| FIGURE CAP      | TIONS  |                                             | xi  |

| CHAPTER 1       | INTRO  | ODUCTION                                    | 1   |

| 1.1             | BACK   | GROUND                                      | 1   |

| 1.2             | REVII  | EW ON CMOS CIRCUITS FOR                     | 3   |

|                 | 60-GH  | IZ APPLICATIONS                             |     |

|                 | 1.2.1  | Frequency Multiplier                        | 3   |

|                 | 1.2.2  | Phase-locked Loop and Frequency Synthesizer | 4   |

|                 | 1.2.3  | Receiver                                    | 6   |

| 1.3             | MOTI   | VATION AND MAIN RESULTS                     | 8   |

| 1.4             | ORGA   | ANIZATION OF THIS THESIS                    | 10  |

| CHAPTER 2       | CMOS   | SUBHARMONIC                                 |     |

|                 | INJEC  | CTION-LOCKED FREQUENCY                      |     |

|                 | TRIPI  | LERS                                        | 25  |

| 2.1             | THEO   | PRETICAL MODEL FOR                          | 26  |

|                 | INJEC  | CTION-LOCKED FREQUENCY                      |     |

|                 | TRIPI  | LER                                         |     |

| 2.2             | CIRC   | UIT REALIZATION                             | 33  |

|                 | 2.2.1  | The Circuit Design of Injection-locked      |     |

|                 |        | Frequency Triplers                          | 33  |

|                 | 2.2.2  | The Simulation Results of                   |     |

|                 |        | Injection-locked Frequency Triplers         | 35  |

|                 |        | 2.2.2.1 <i>K</i> -band ILFT                 | 35  |

|                 |        | 2.2.2.2 <i>V</i> -band ILFT                 | 36  |

|                 | 2.2.3  | Layout Consideration                        | 37  |

| 2.3             | EXPE   | RIMENTAL RESULTS                            | 38  |

|                 | 2.3.1  | <i>K</i> -band ILFT                         | 39  |

|                 | 2.3.2  | V-band IFLT                                 | 42  |

| 2.4              | SUMN  | MARY                                     | 45  |

|------------------|-------|------------------------------------------|-----|

| CHAPTER 3        | 60-GH | IZ CMOS PHASE-LOCKED LOOP                |     |

|                  | WITH  | I INJECTION-LOCKED FREQUENCY             |     |

|                  | MULT  | ΓIPLIER                                  | 73  |

| 3.1              | THEO  | ORETICAL MODEL FOR ODD-ORDER             |     |

|                  | INJEC | CTION-LOCKED FREQUENCY                   |     |

|                  | MULT  | ΓIPLIER                                  | 74  |

| 3.2              | THIR  | D ORDER PHASE-LOCKED LOOP                |     |

|                  | DESIG | GN CONSIDERATION                         | 77  |

| 3.3              | CIRC  | UIT REALIZATION                          | 81  |

|                  | 3.3.1 | VCO and Injection-locked Frequency       |     |

|                  |       | Multiplier                               | 81  |

|                  | 3.3.2 | Frequency Dividers                       | 83  |

|                  | 3.3.3 | Phase Frequency Detector, Charge         |     |

|                  |       | Pump, and Loop Filter                    | 84  |

|                  | 3.3.4 | Simulation Results of Phase-locked Loop  | 85  |

| 3.4              | EXPE  | RIMENTAL RESULTS                         | 87  |

| 3.5              | SUMN  | MARY                                     | 89  |

|                  |       |                                          |     |

| <b>CHAPTER 4</b> | 60-GH | IZ CMOS DIRECT-CONVERSION                |     |

|                  | RECE  | IVER FRONT-END WITH                      |     |

|                  | INJEC | CTION-LOCKED FREQUENCY                   |     |

|                  | TRIPI | LER                                      | 121 |

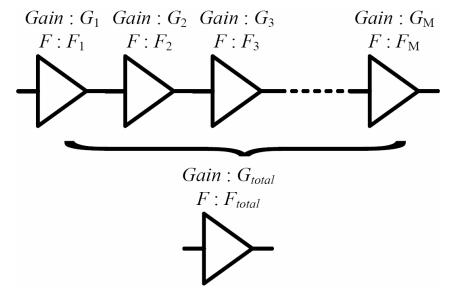

| 4.1              | SYSTI | EM DESIGN CONSIDERATION                  | 122 |

|                  | 4.1.1 | Noise Figure                             | 122 |

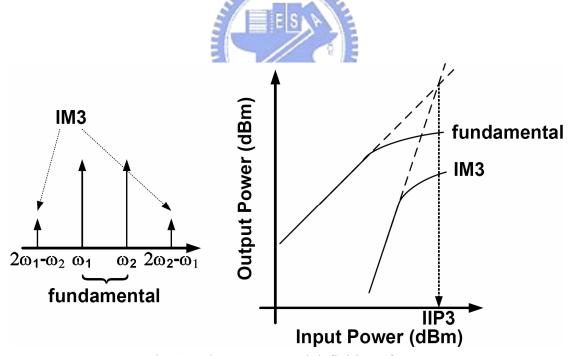

|                  | 4.1.2 | P1dB and IIP3                            | 124 |

|                  | 4.1.3 | Link Budget Analysis                     | 125 |

| 4.2              | ARCH  | IITECTURE AND OPERATIONAL                |     |

|                  | PRIN  | CIPLES                                   | 126 |

| 4.3              | CIRC  | UIT REALIZTION                           | 127 |

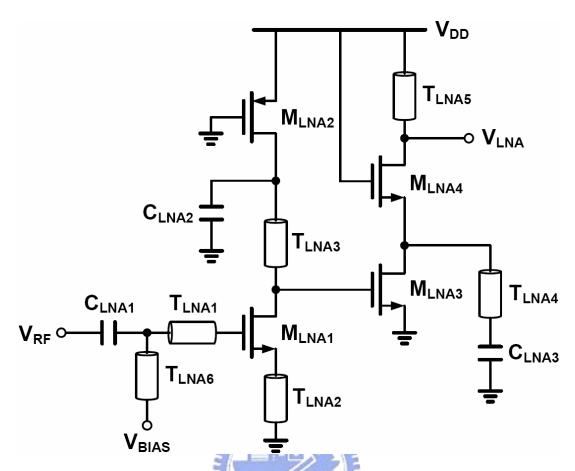

|                  | 4.3.1 | Low-noise Amplifier                      | 127 |

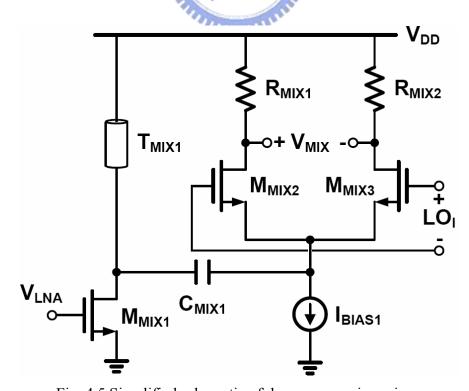

|                  | 4.3.2 | Down-conversion Mixer                    | 128 |

|                  | 4.3.3 | Quadrature Voltage-controlled Oscillator |     |

|                  |       | and Injection-locked Frequency Triplers  | 129 |

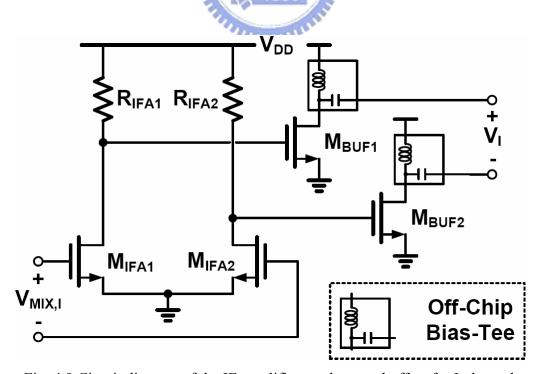

|                  | 4.3.4 | IF Amplifiers and Output Buffers         | 132 |

|                  | 4.3.5 | Overall Circuits                         | 132 |

| 4.4              | EXPE  | RIMENTAL RESULTS                         | 133 |

| 4.5        | SUMMARY                     | 137 |

|------------|-----------------------------|-----|

| CHAPTER 5  | CONCLUSIONS AND FUTURE WORK | 161 |

| 5.1        | MAIN RESULTS OF THIS THESIS | 161 |

| 5.2        | FUTURE WORK                 | 163 |

| REFERENCE  | S                           | 165 |

| VITA       |                             | 177 |

| PUBLICATIO | N LIST                      | 179 |

#### **Table Captions**

| Table 1.1 | Frequency plan for 60-GHz applications.                                   | 12   |

|-----------|---------------------------------------------------------------------------|------|

| Table 1.2 | Comparison of the FS architectures.                                       | 13   |

| Table 1.3 | Comparison of the receiver architectures.                                 | 14   |

| Table 2.1 | Dimensions of devices in (a) $K$ -band ILFT and (b) $V$ -band ILFT.       | 46   |

| Table 2.2 | Comparison with published subharmonic ILFMs.                              | 47   |

| Table 2.3 | Comparison with published bulk-CMOS VCOs.                                 | 48   |

| Table 3.1 | Dimensions of devices in VCO and ILFM.                                    | 91   |

| Table 3.2 | Dimensions of devices in four stage CML divide-by-two frequency dividers. | 92   |

| Table 3.3 | Summary of the post-simulation results.                                   | 93   |

| Table 3.4 | Comparison with recently published <i>V</i> -band CMOS Fs's and PLLs.     | 92   |

| Table 4.1 | Link budget analysis for 60-GHz wireless communication.                   | 139  |

| Table 4.2 | Design target of receiver front-end.                                      | 140  |

| Table 4.3 | Dimensions of devices in overall <i>V</i> -band receiver.                 | 140  |

| Table 4.4 | Comparison with recently published CMOS V-band receivers                  | 142  |

|           |                                                                           | 1 T4 |

#### Figure Captions

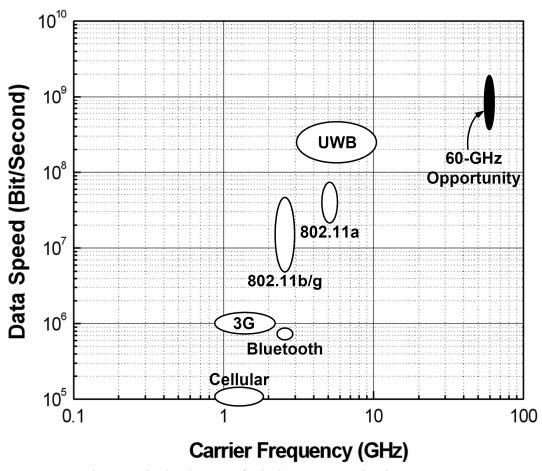

| Fig. 1.1  | The landscape of wireless communication systems.                                                       | 15       |

|-----------|--------------------------------------------------------------------------------------------------------|----------|

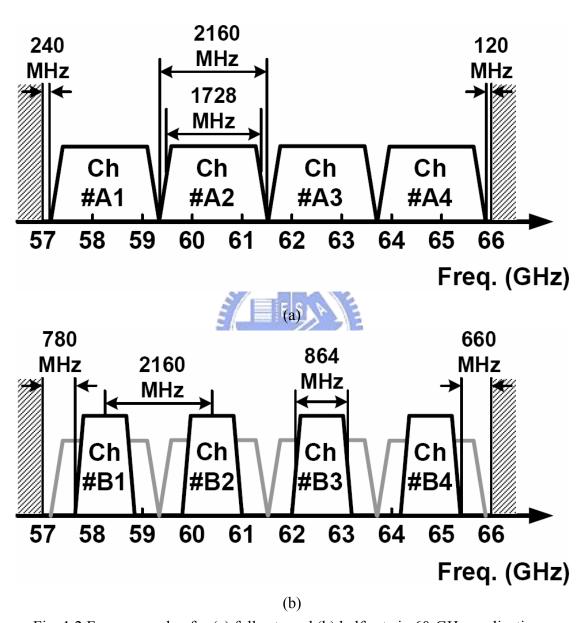

| Fig. 1.2  | Frequency plan for (a) full-rate and (b) half-rate in 60-GHz applications.                             | 16       |

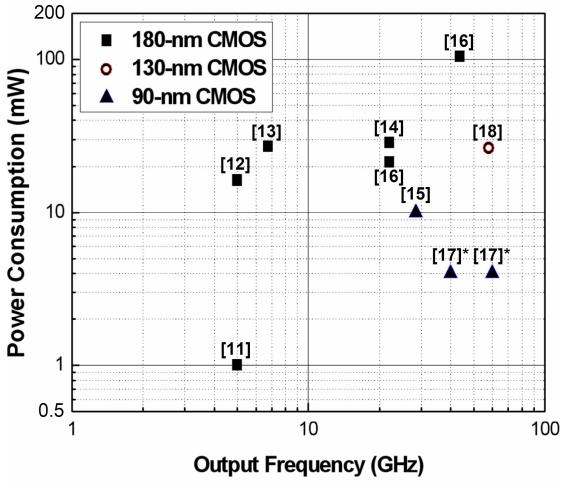

| Fig. 1.3  | Recently published CMOS frequency multipliers.                                                         | 17       |

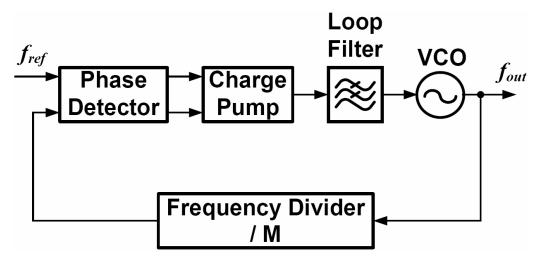

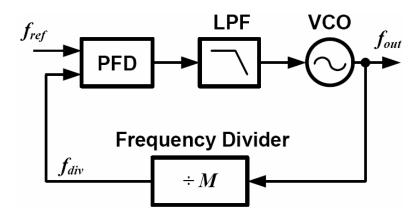

| Fig. 1.4  | Block diagram of the conventional frequency synthesizer.                                               | 18       |

| Fig. 1.5  | Recently published CMOS injection-locked frequency dividers.                                           | 18       |

| Fig. 1.6  | Recently published CMOS CML frequency dividers without inductor peaking.                               | 19       |

| Fig. 1.7  | Block diagram of frequency synthesizer with frequency multiplier.                                      | 20       |

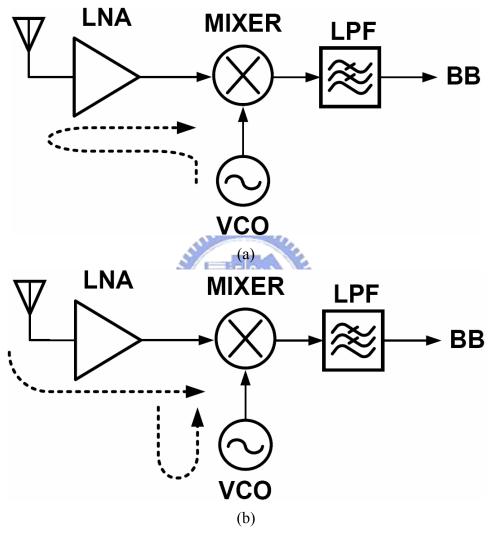

| Fig. 1.8  | Block diagram of the homodyne receiver.                                                                | 20       |

| Fig. 1.9  | The sources of dc offsets from (a) LO leaking to LNA input and (b) large interferers leaking to VCO.   | 21       |

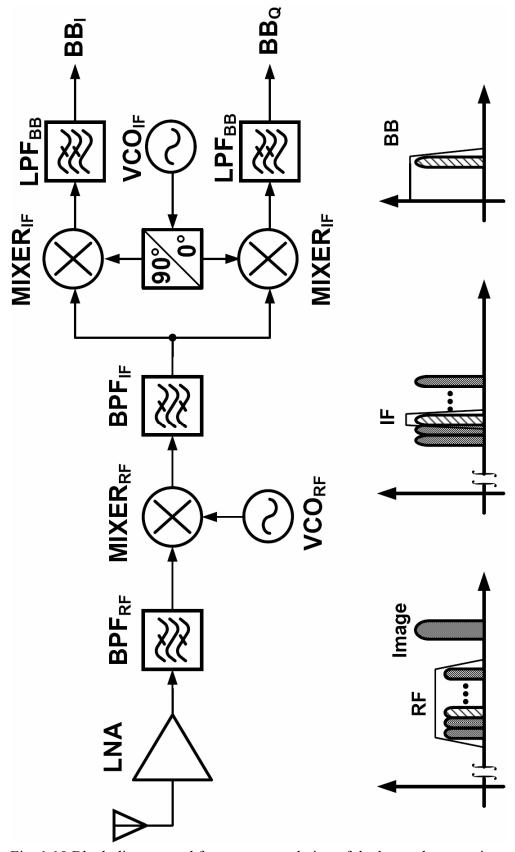

| Fig. 1.10 | Block diagram and frequency translation of the heterodyne receiver.                                    | 22       |

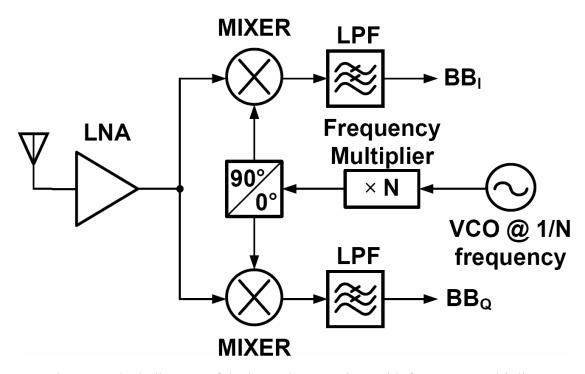

| Fig. 1.11 | Block diagram of the homodyne receiver with frequency multiplier.                                      | 23       |

| Fig. 2.1  | The model of the proposed ILFT.                                                                        | 49       |

| Fig. 2.2  | Simplified noise source model in the proposed ILFT.                                                    | 49       |

| Fig. 2.3  | The schematic of the proposed ILFT.                                                                    | 50       |

| Fig. 2.4  | HSPICE simulated coefficient of output harmonic current as a function of conduction angle.             | 51       |

| Fig. 2.5  | HSPICE simulated HRRs for various value of R1 for <i>K</i> -band ILFT                                  | 51       |

| Fig. 2.6  | Simulated locking range as a function of input bias $V_{\text{BIAS}}$ for $\emph{K}\text{-band ILFT}.$ |          |

| Fig. 2.7  | The transient simulation of the free-running <i>K</i> -band ILFT.                                      | 52<br>52 |

| Fig. 2.8  | Simulated output spectrum of the free-running <i>K</i> -band ILFT.                                     | 53<br>53 |

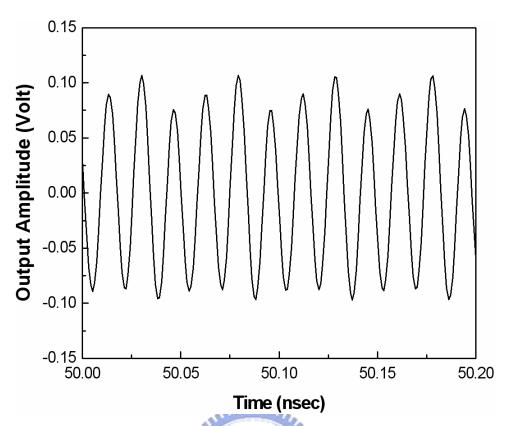

| Fig. 2.9  | The transient simulation of the locked $K$ -band ILFT with 4-dBm input power, 0.65-V $V_{\rm BIAS}$ , and 8.32-GHz input frequency.                                          | 54 |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 2.10 | Simulated output spectrum of the locked $\it K$ -band ILFT with 4-dBm input power, 0.65-V $\it V_{BIAS}$ , and 8.32-GHz input frequency.                                     | 54 |

| Fig. 2.11 | Simulated tuning voltage $V_{\text{TUNE}}$ versus output frequency with 0.65-V $V_{\text{BIAS}}$ and 4-dBm input power for $K$ -band ILFT.                                   | 55 |

| Fig. 2.12 | Simulated input power versus output frequency with 1.5-V $V_{\text{TUNE}}$ and 0.65-V $V_{\text{BIAS}}$ for K-band ILFT.                                                     | 55 |

| Fig. 2.13 | The transient simulation of the free-running $V$ -band ILFT.                                                                                                                 | 56 |

| Fig. 2.14 | Simulated output spectrum of the free-running $V$ -band ILFT.                                                                                                                | 56 |

| Fig. 2.15 | The transient simulation of the locked $\emph{V}$ -band ILFT with 6-dBm input power, 0.55-V $V_{BIAS}$ , and 20.3GHz input frequency.                                        | 57 |

| Fig. 2.16 | Simulated output spectrum of the locked $\emph{V}$ -band ILFT with 6-dBm input power, 0.55-V $V_{BIAS}$ , and 20.3-GHz input frequency.                                      | 57 |

| Fig. 2.17 | Simulated input power versus output frequency with 0.55-V $V_{\rm BIAS}$ for $V$ -band ILFT.                                                                                 | 58 |

| Fig. 2.18 | Simulated the phase noise of ILFT input and output for $V$ -band ILFT.                                                                                                       | 58 |

| Fig. 2.19 | Chip microphotograph of <i>K</i> -band ILFT (0.66 mm $\times$ 0.69 mm).                                                                                                      | 59 |

| Fig. 2.20 | Chip microphotograph of $V$ -band ILFT (0.59 mm $\times$ 0.66 mm).                                                                                                           | 60 |

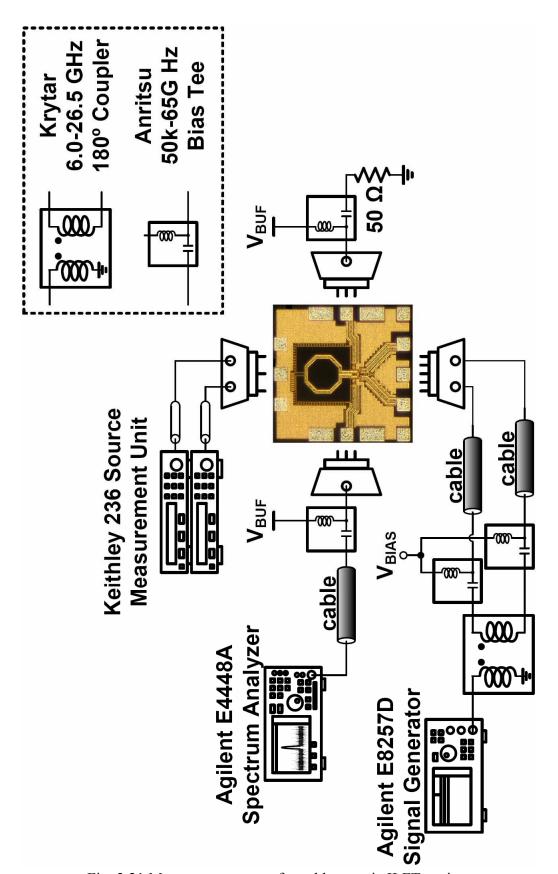

| Fig. 2.21 | Measurement setup for subharmonic ILFT testing.                                                                                                                              | 61 |

| Fig. 2.22 | Measured output spectrum of the fabricated $K$ -band ILFT under free-running condition with probe and cable losses and $V_{\rm BIAS}$ of 0.56 V.                             | 62 |

| Fig. 2.23 | Measured output spectrum of the fabricated $\textit{K}\text{-band}$ ILFT under locked condition with probe and cable losses, $V_{BIAS}$ of 0.56 V, and input power of 4 dBm. | 62 |

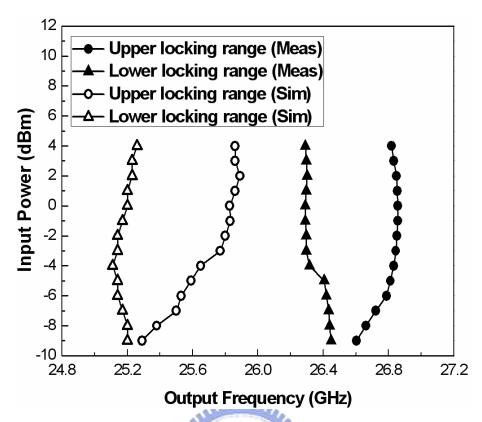

| Fig. 2.24 | Simulated and measured input powers versus output frequency with 1.5-V $V_{TUNE}$ and 0.56-V $V_{BIAS}$ for $K$ -band ILFT.                                                  | 63 |

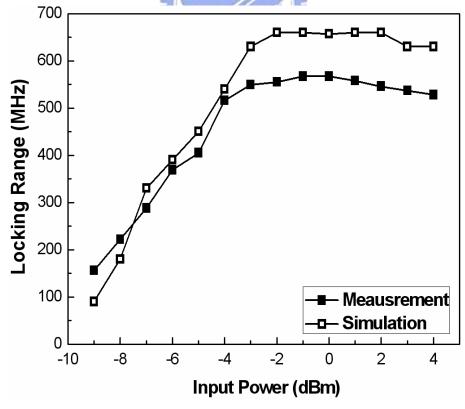

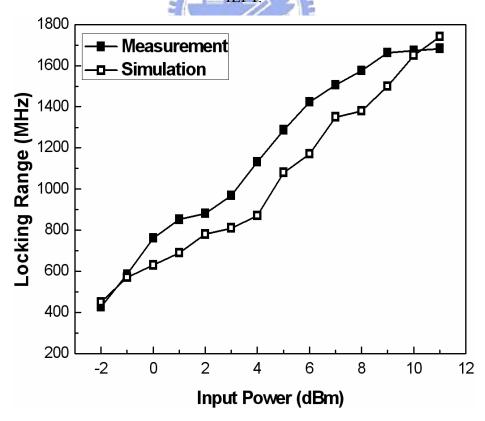

| Fig. 2.25 | Simulated and measured locking ranges versus input power with 1.5-V $V_{TUNE}$ and 0.56-V $V_{BIAS}$ for $K$ -band ILFT.                                                     | 63 |

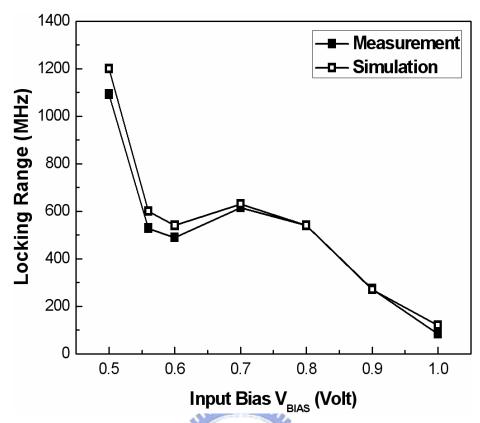

| Fig. 2.26 | Locking range as a function of input bias $V_{BIAS}$ with 4-dBm input power and 1.5-V $V_{TUNE}$ for $K$ -band ILFT.                                         | 64 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 2.27 | Measured tuning voltage $V_{\text{TUNE}}$ versus output frequency with 0.65-V $V_{\text{BIAS}}$ and 4-dBm input power for <i>K</i> -band ILFT.               | 64 |

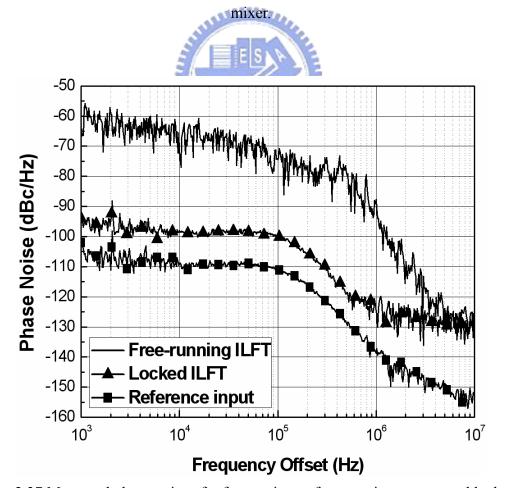

| Fig. 2.28 | Measured phase noise of reference input, free-running output, and locked output with 0.65-V $V_{\rm BIAS}$ and 4-dBm input power for $K$ -band ILFT.         | 65 |

| Fig. 2.29 | Measured phase noise characteristics of locked output as a function of input power with 0.65-V $V_{\rm BIAS}$ for $K$ -band ILFT.                            | 65 |

| Fig. 2.30 | Measured output power spectra of first, second, third, fourth, and fifth harmonics with 0.65-V $V_{\rm BIAS}$ and 4-dBm input power for <i>K</i> -band ILFT. | 66 |

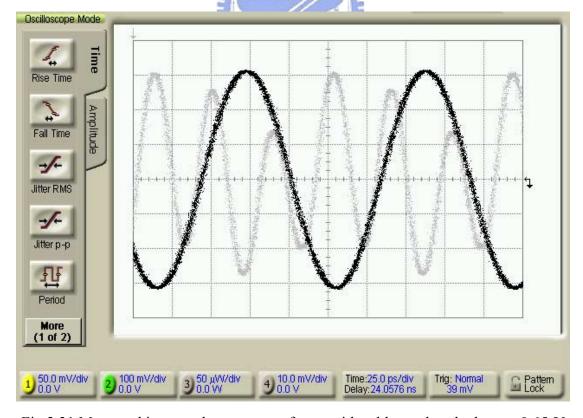

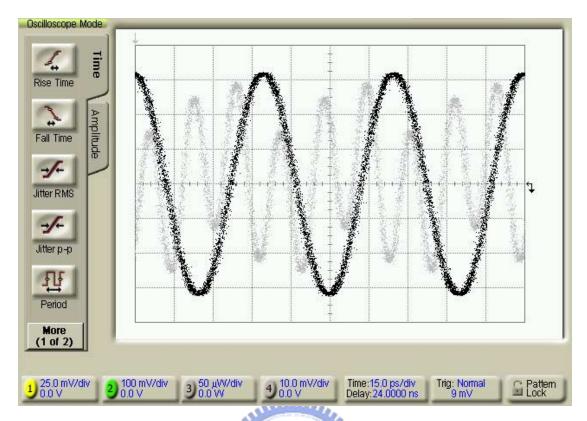

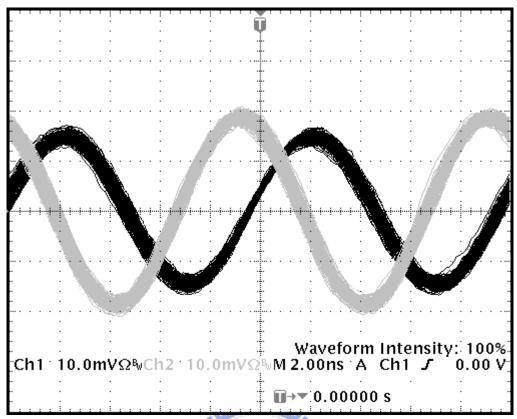

| Fig. 2.31 | Measured input and output waveforms with cables and probe losses, 0.65-V $V_{BIAS}$ , and 1.5-V $V_{TUNE}$ for $K$ -band ILFT.                               | 66 |

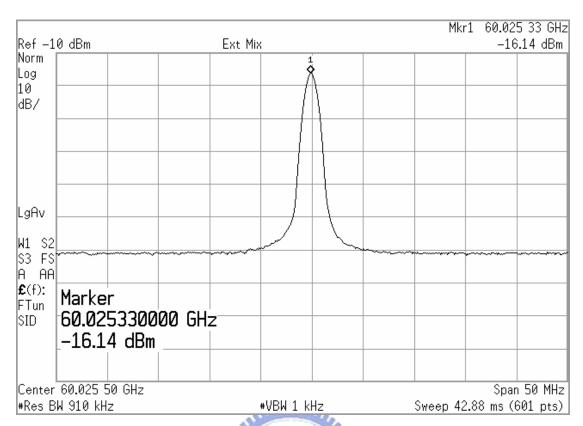

| Fig. 2.32 | Measured output spectrum of the fabricated <i>V</i> -band ILFT under free-running condition with probe and cable losses.                                     | 67 |

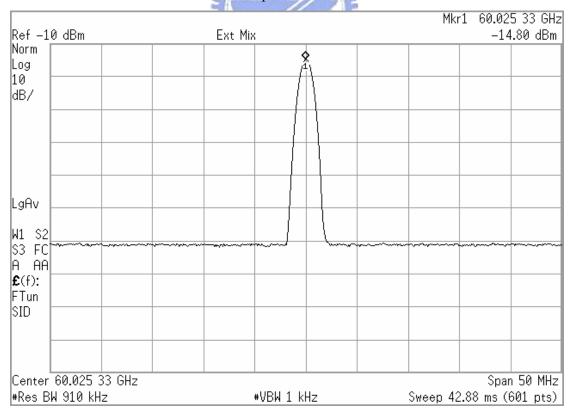

| Fig. 2.33 | Measured output spectrum of the fabricated <i>V</i> -band ILFT under locked condition with probe and cable losses and input power of 4 dBm.                  | 67 |

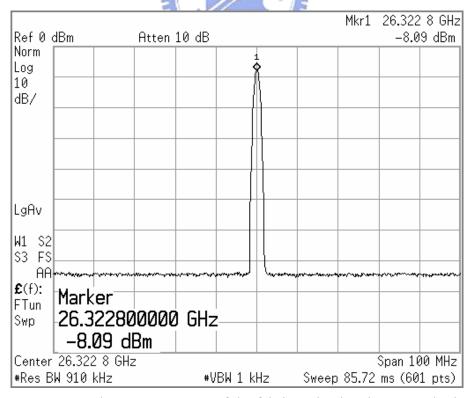

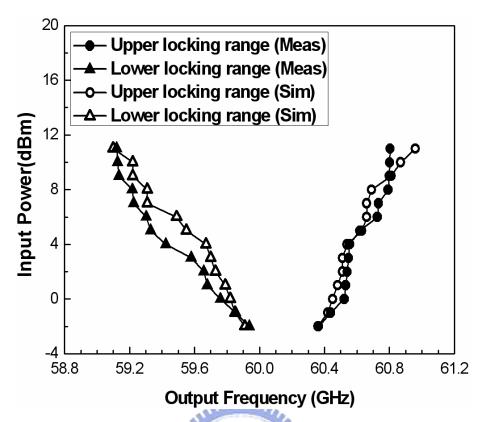

| Fig. 2.34 | Simulated and measured input powers versus output frequency for $V$ -band ILFT.                                                                              | 68 |

| Fig. 2.35 | Simulated and measured locking ranges versus input power for $V$ -band ILFT.                                                                                 | 68 |

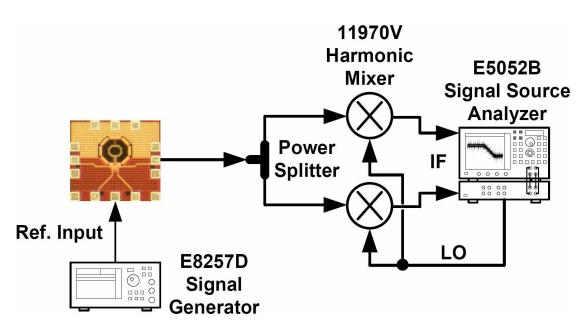

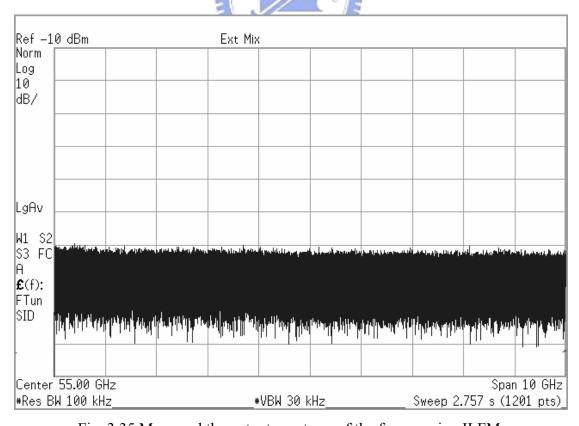

| Fig. 2.36 | Measurement setup for output phase noise with external down-conversion mixer.                                                                                | 69 |

| Fig. 2.37 | Measured phase noise of reference input, free-running output, and locked output with 6-dBm input power for <i>V</i> -band ILFT.                              | 69 |

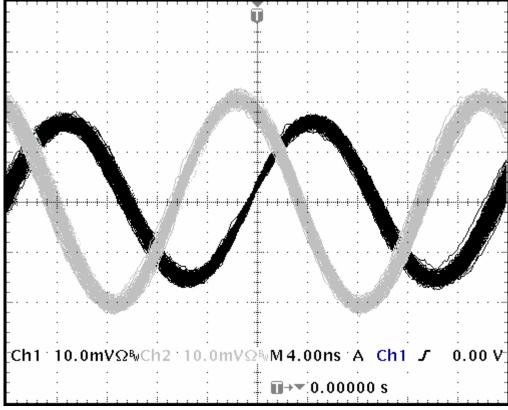

| Fig. 2.38 | Measured input and output waveforms with cables and probe losses for $V$ -band ILFT.                                                                         | 70 |

| Fig. 2.39 | Circuit diagram of the subharmonic ILFT in [23].                                                                                                             | 70 |

| Fig. 2.40 | Transformer-based ILFT.                                                                                                                                      | 71 |

| Fig. 3.1  | The general model of ILFM.                                                                                                                                   | 95 |

| Fig. 3.2  | Simplified noise source model for ILFM.                                                                                                                      | 95 |

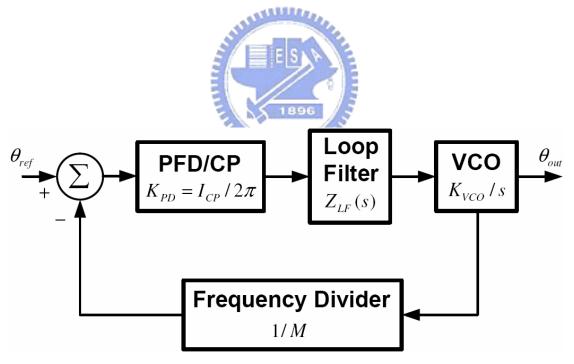

| Fig. 3.3  | Block diagram of a typical PLL.                                                                                                                              | 96 |

| Fig. 3.4  | The linear phase-domain PLL model.                                                                                                   | 96  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------|-----|

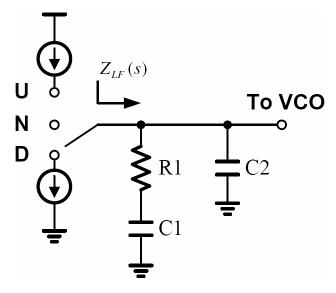

| Fig. 3.5  | Loop filter in a third-order PLL.                                                                                                    | 97  |

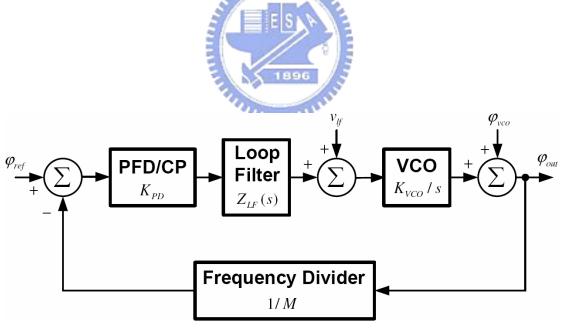

| Fig. 3.6  | PLL noise model.                                                                                                                     | 97  |

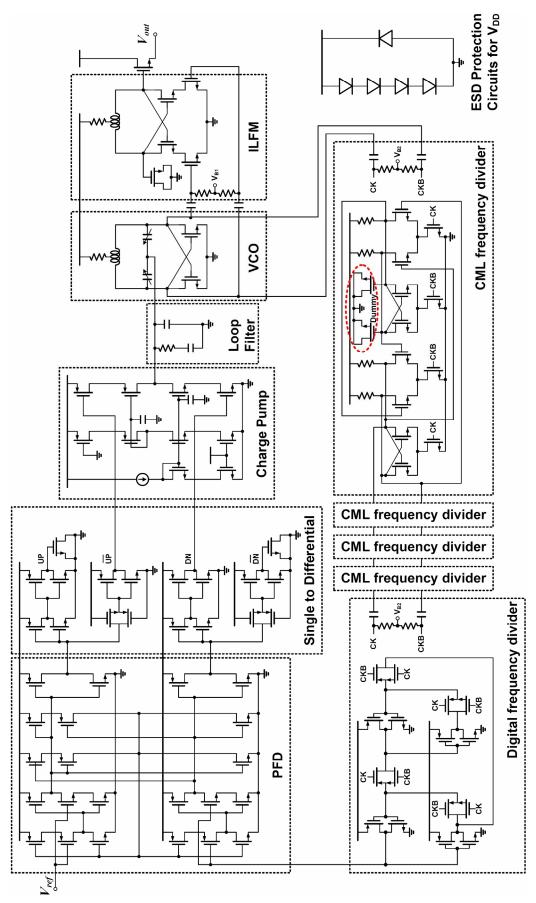

| Fig. 3.7  | Block diagram of the proposed 60-GHz PLL.                                                                                            | 98  |

| Fig. 3.8  | Circuit diagram of both VCO and ILFM.                                                                                                | 99  |

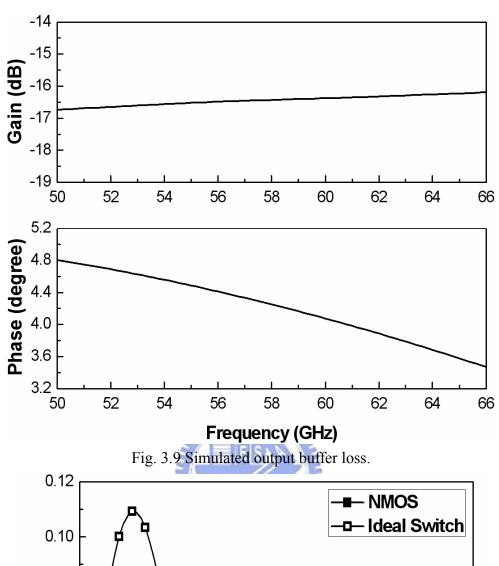

| Fig. 3.9  | Simulated output buffer loss.                                                                                                        | 100 |

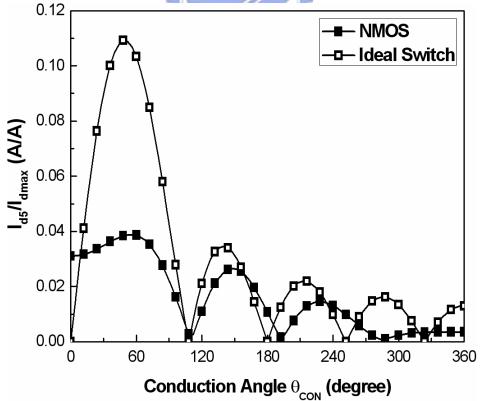

| Fig. 3.10 | HSPICE simulated coefficient of output harmonic current as a function of conduction angle.                                           | 100 |

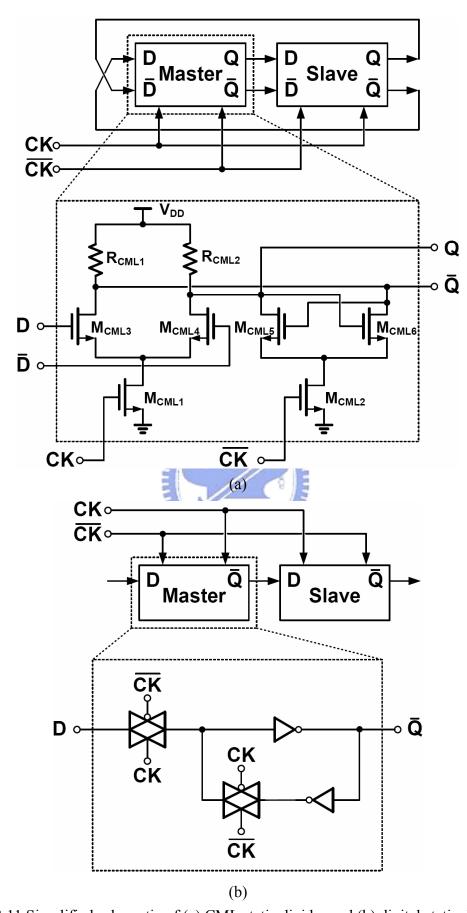

| Fig. 3.11 | Simplified schematic of (a) CML static divider and (b) digital static divider.                                                       | 101 |

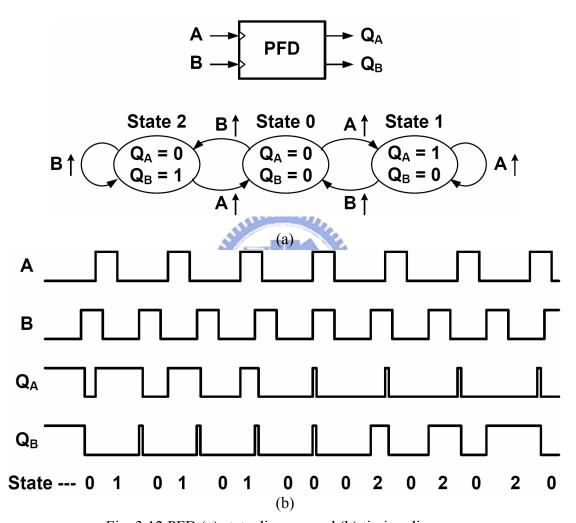

| Fig. 3.12 | PFD (a) state diagram and (b) timing diagram.                                                                                        | 102 |

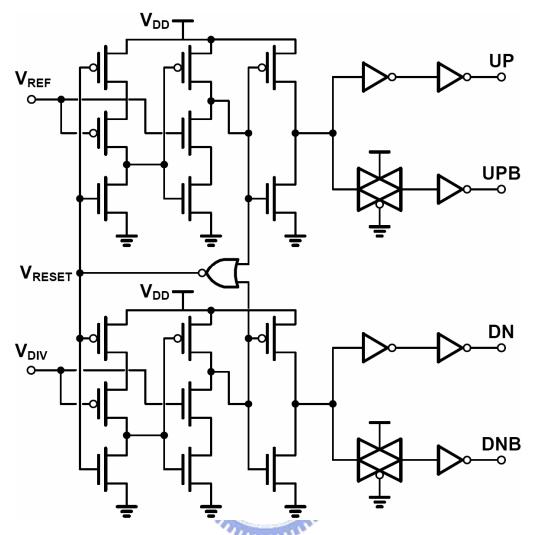

| Fig. 3.13 | Simplified schematic of the PFD.                                                                                                     | 103 |

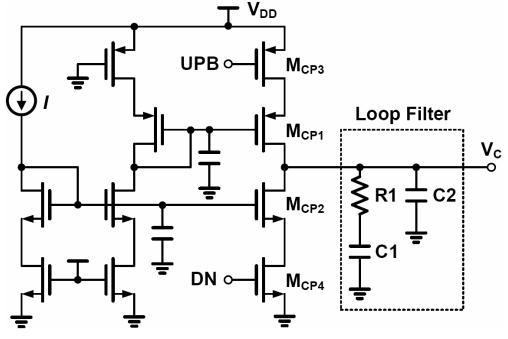

| Fig. 3.14 | Circuit diagram of the charge pump and loop filter.                                                                                  | 103 |

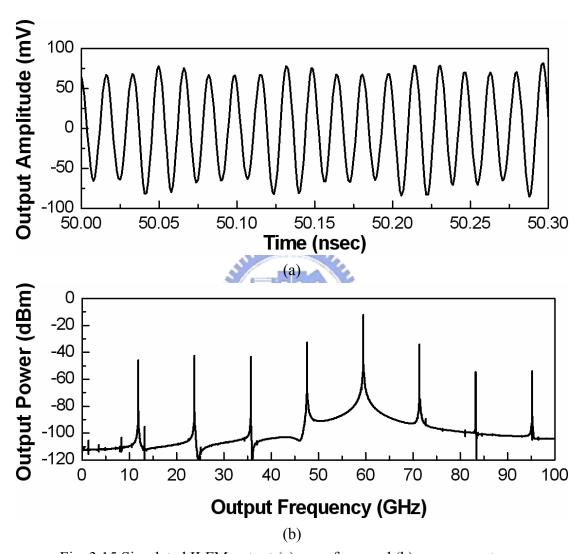

| Fig. 3.15 | Simulated ILFM output (a) waveform and (b) power spectrum.                                                                           | 104 |

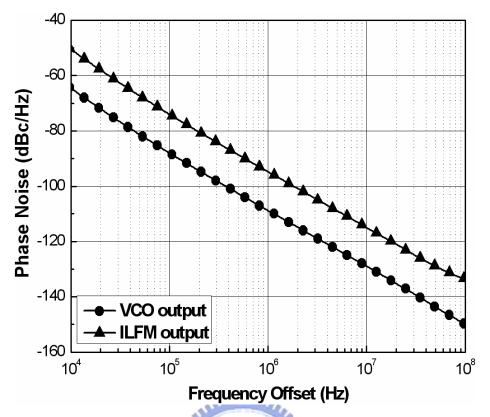

| Fig. 3.16 | Simulated output phase of VCO and ILFM.                                                                                              | 105 |

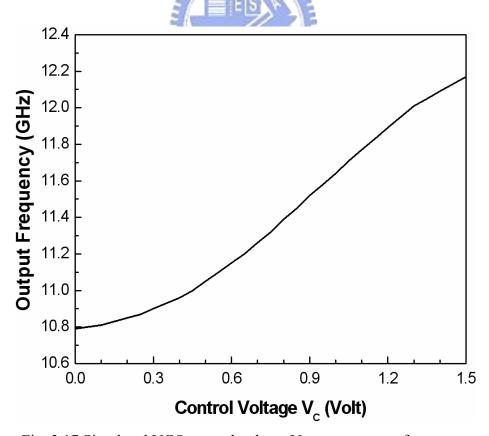

| Fig. 3.17 | Simulated VCO control voltage $V_{\rm C}$ versus output frequency.                                                                   | 105 |

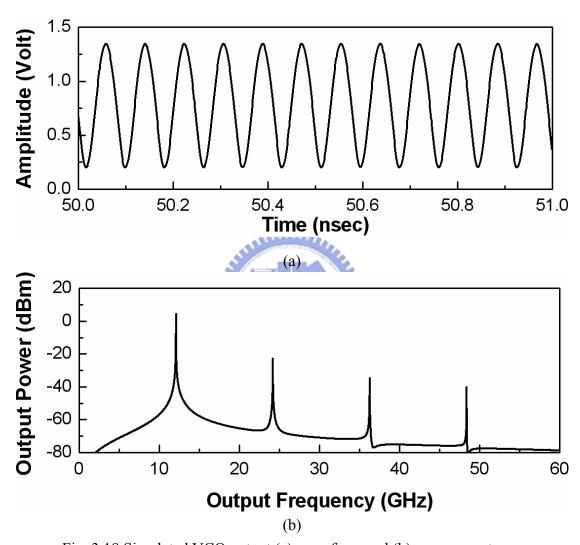

| Fig. 3.18 | Simulated VCO output (a) waveform and (b) power spectrum.                                                                            | 106 |

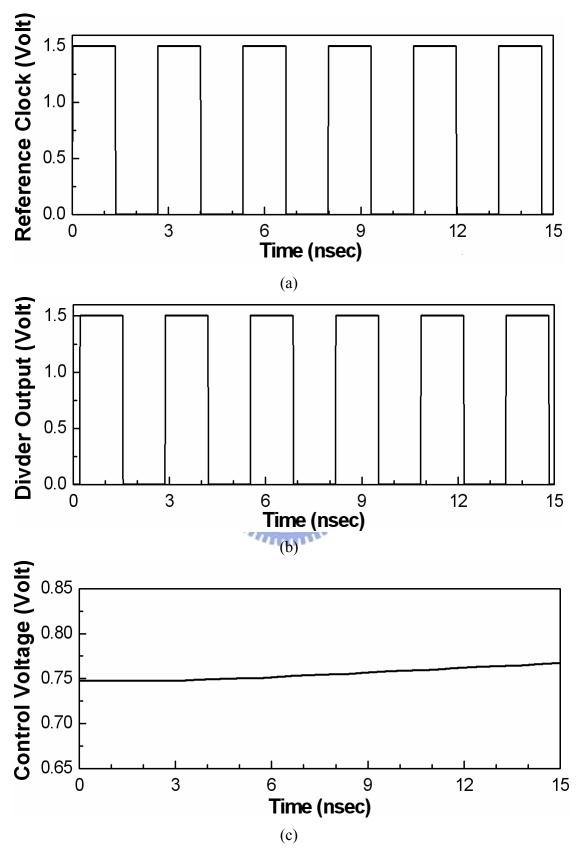

| Fig. 3.19 | Simulated waveforms of (a) reference clock, (b) divider output, and (c) control voltage of VCO with charging mode of charge pump.    | 107 |

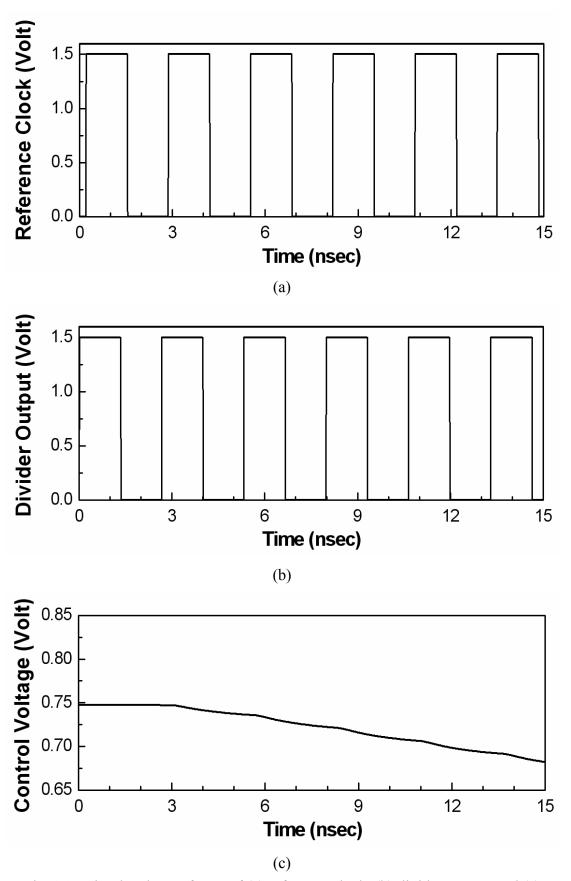

| Fig. 3.20 | Simulated waveforms of (a) reference clock, (b) divider output, and (c) control voltage of VCO with discharging mode of charge pump. | 108 |

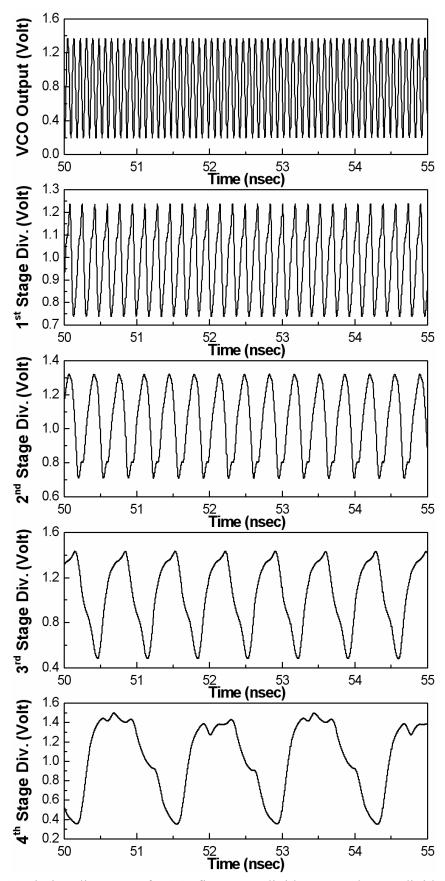

| Fig. 3.21 | Timing diagrams of VCO, first stage divider, second stage divider, third stage divider, and fourth stage divider.                    | 109 |

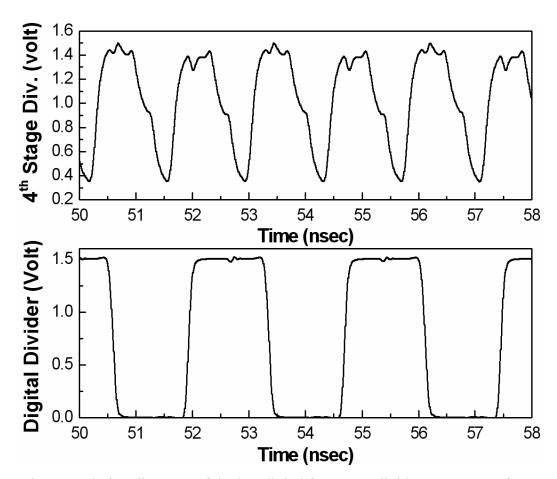

| Fig. 3.22 | Timing diagrams of the last digital frequency divider output waveform.                                                               | 110 |

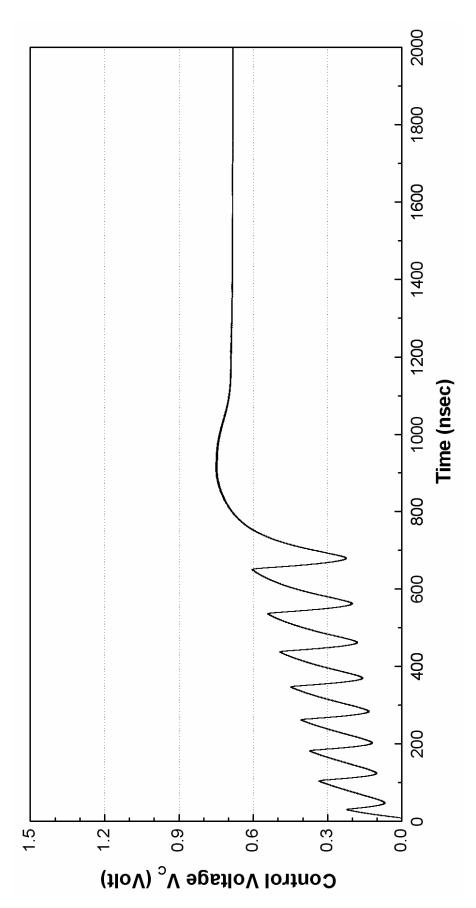

| Fig. 3.23 | Simulated waveform of control voltage $V_{\text{C}}$ in close-loop simulation.                                                       | 111 |

| Fig. 3.24 | Circuit diagram of the overall PLL.                                                                                                  | 112 |

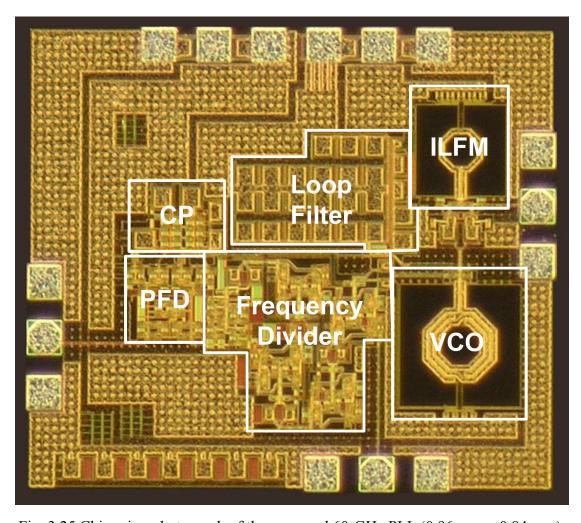

| Fig. 3.25 | Chip microphotograph of the proposed 60-GHz PLL (0.96 mm ×                                                          |     |

|-----------|---------------------------------------------------------------------------------------------------------------------|-----|

|           | 0.84 mm).                                                                                                           | 113 |

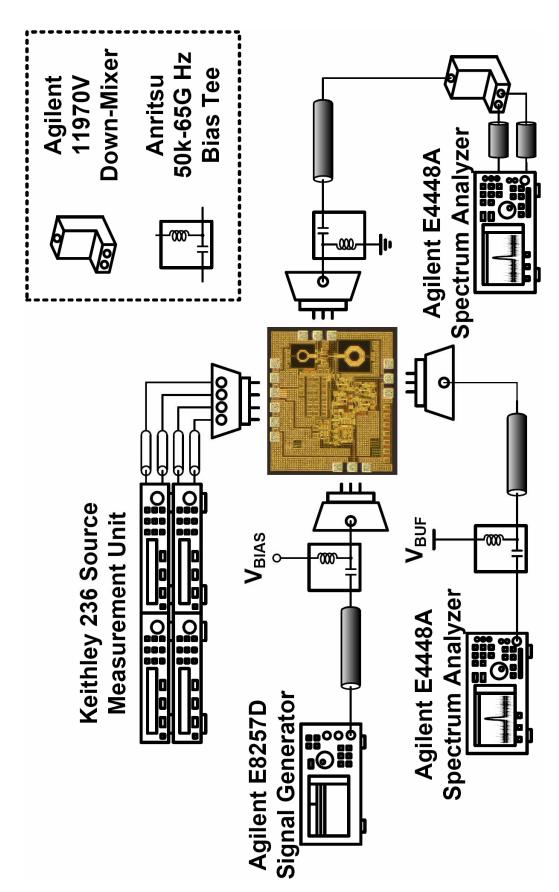

| Fig. 3.26 | Measurement setup for 60-GHz PLL testing.                                                                           | 114 |

| Fig. 3.27 | Measured Output spectrum of the 60-GHz PLL with 362.5-MHz reference frequency $f_{\it ref.}$                        | 115 |

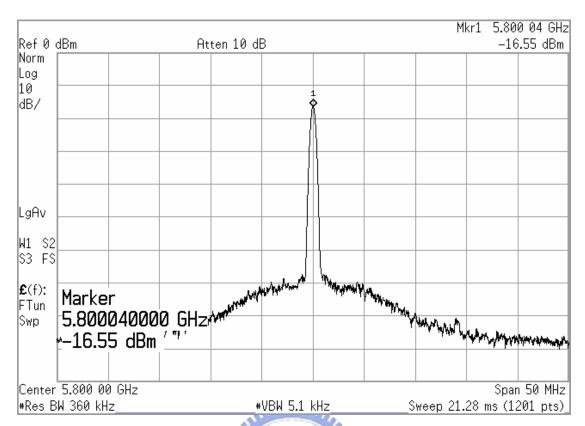

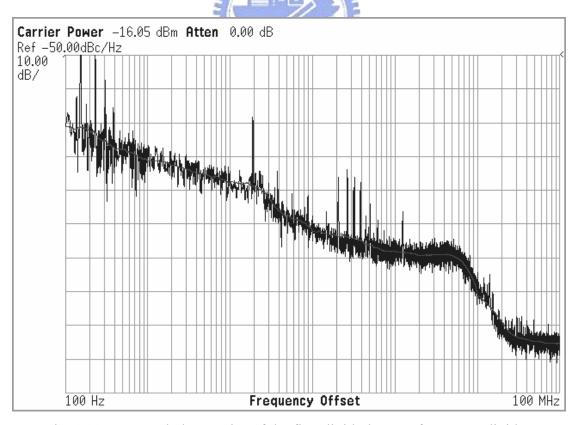

| Fig. 3.28 | Measured output phase noise marked at the offset frequency of 1MHz and 10 MHz.                                      | 115 |

| Fig. 3.29 | Measurement setup for the reference spurs testing.                                                                  | 116 |

| Fig. 3.30 | Measured reference spurs as the reference frequency of 359.7 MHz                                                    | 116 |

| Fig. 3.31 | Measured output spectrum of the first divide-by-two frequency divider.                                              | 117 |

| Fig. 3.32 | Measured phase noise of the first divide-by-two frequency divider.                                                  | 117 |

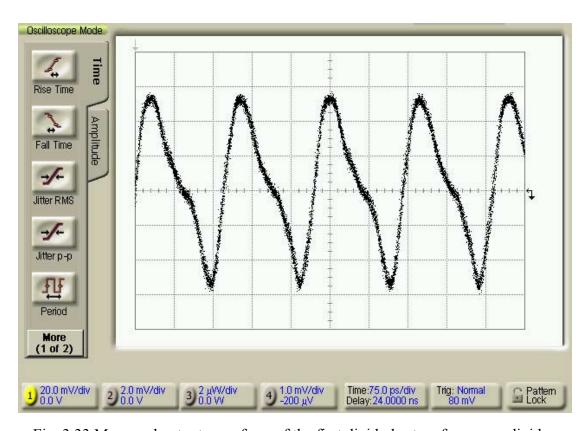

| Fig. 3.33 | Measured output waveform of the first divide-by-two frequency divider.                                              | 118 |

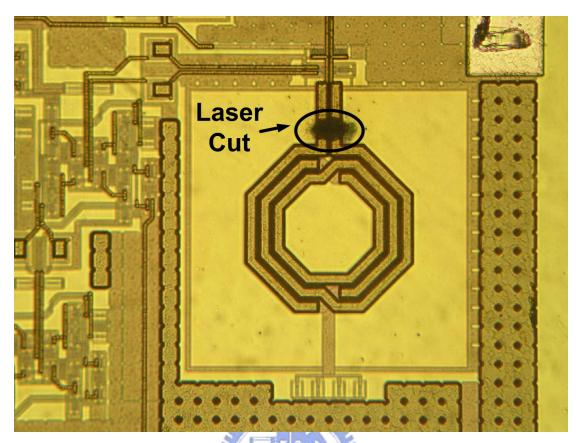

| Fig. 3.34 | The microphotograph of the laser cut position.                                                                      | 119 |

| Fig. 3.35 | Measured the output spectrum of the free-running ILFM.                                                              | 119 |

| Fig. 3.36 | Power consumption as a function of output frequency.                                                                | 120 |

| Fig. 3.37 | Output power as a function of output frequency.                                                                     | 120 |

| Fig. 4.1  | The equivalent system for multi-stage system.                                                                       | 143 |

| Fig. 4.2  | The property and definition of IIP3.                                                                                | 143 |

| Fig. 4.3  | Block diagram of the proposed direct-conversion receiver.                                                           | 144 |

| Fig. 4.4  | Circuit diagram of the two-stage 60-GHz LNA.                                                                        | 145 |

| Fig. 4.5  | Simplified schematic of down-conversion mixer.                                                                      | 145 |

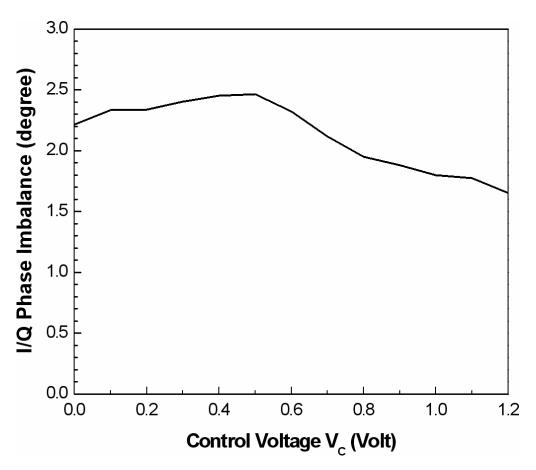

| Fig. 4.6  | Circuit diagram of the QVCO.                                                                                        | 146 |

| Fig. 4.7  | Simulated I/Q phase imbalance with 10-% channel width mismatch of the transistor in the even-stage ring oscillator. | 147 |

| Fig. 4.8  | Circuit diagram of the ILFT.                                                                                        | 148 |

| Fig. 4.9  | Circuit diagram of the IF amplifiers and output buffers for I-channel.                                              | 148 |

| Fig. 4.10 | Complete circuit diagram of the proposed 60-GHz direct-conversion receiver.                                                           | 149 |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 4.11 | Chip microphotograph of the 60-GHz direct-conversion receiver (1.21 mm $\times$ 1.03 mm).                                             | 150 |

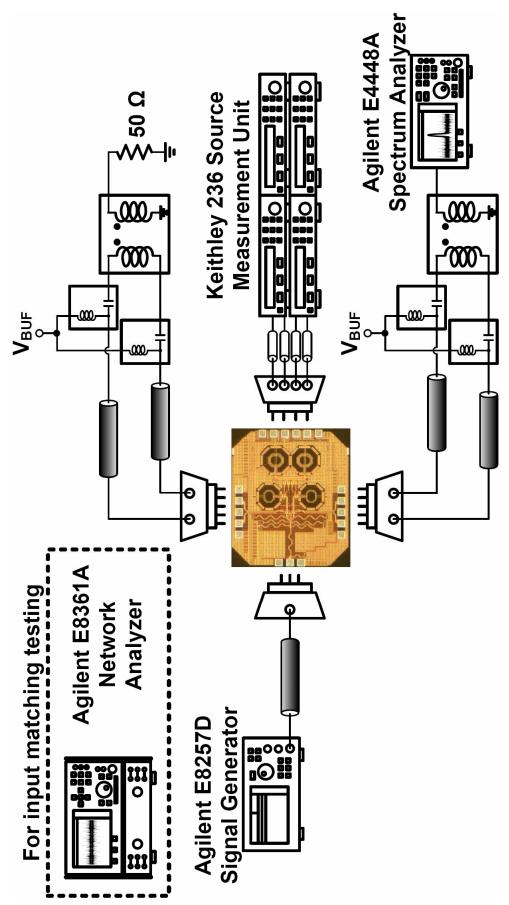

| Fig. 4.12 | Measurement setup for 60-GHz direct-conversion receiver testing.                                                                      | 151 |

| Fig. 4.13 | Simulated and measured input matching (S11) with frequency range from 54 to 66 GHz.                                                   | 152 |

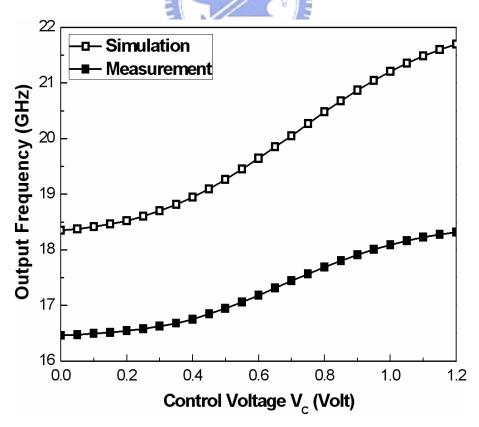

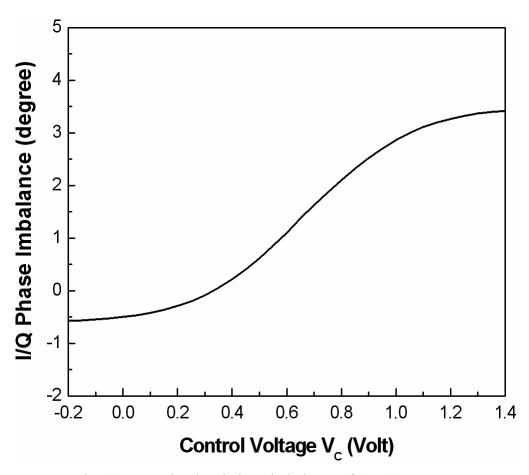

| Fig. 4.14 | Simulated and measured QVCO output frequency versus control voltage $V_{\text{C}}$ .                                                  | 152 |

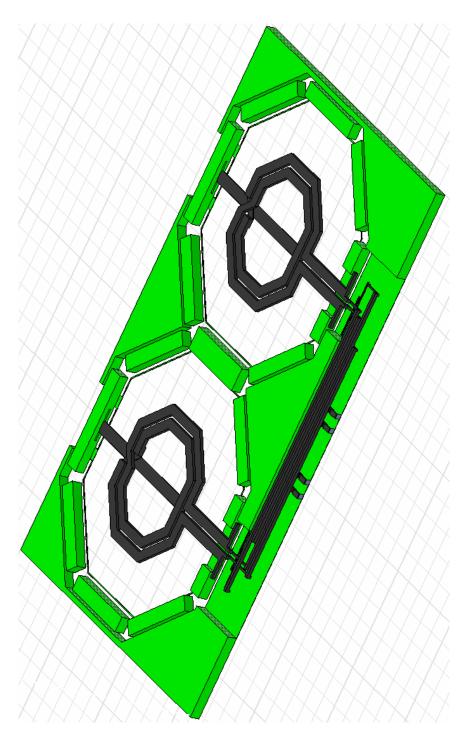

| Fig. 4.15 | 3D-view of the inductors and interconnection metals for EM simulation.                                                                | 153 |

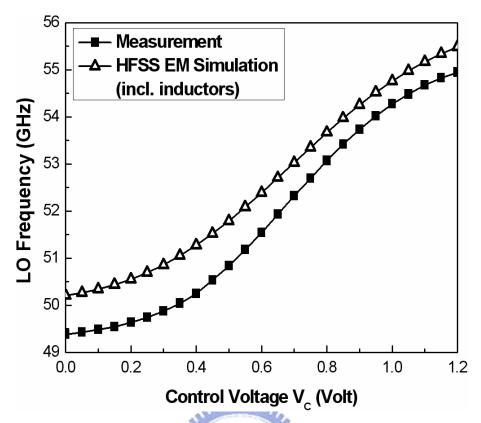

| Fig. 4.16 | Measured and EM simulated LO frequency versus control voltage $\ensuremath{V_{C}}.$                                                   | 154 |

| Fig. 4.17 | Simulated and measured receiver gain and SSB NF with IF frequency of 100 MHz.                                                         | 154 |

| Fig. 4.18 | Measured 3-dB channel bandwidth with LO frequency of 55.02 GHz.                                                                       | 155 |

| Fig. 4.19 | Measured P1dB with RF frequency of 55.03 GHz and IF frequency of 100 MHz.                                                             | 155 |

| Fig. 4.20 | Measured IIP3 with RF frequency of 55.03 and 55.04 GHz.                                                                               | 156 |

| Fig. 4.21 | Measured output waveforms with RF frequency of 55.07 GHz and IF frequency of 500 MHz.                                                 | 156 |

| Fig. 4.22 | Measured output waveforms with RF frequency of 55.03 GHz and IF frequency of 100 MHz.                                                 | 157 |

| Fig. 4.23 | Measured output waveforms with RF frequency of 55.025 GHz and IF frequency of 50 MHz.                                                 | 157 |

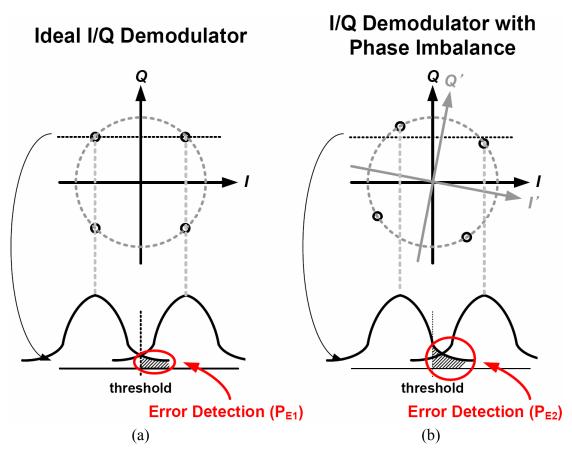

| Fig. 4.24 | The signal constellation and probability distribution of QPSK with (a) an ideal phase of I/Q channel and (b) a phase imbalance of I/Q |     |

|           | channel.                                                                                                                              | 158 |

| Fig. 4.25 | EM simulated phase imbalance of QVCO outputs.                                                                                         | 159 |

#### **CHAPTER 1**

#### INTRODUCTION

#### 1.1 BACKGROUND

Wireless communication system has been under significant development over the past few decades and it is closer to our daily life than ever before. Wireless communication products such as cellular phones, Personal Digital Assistants (PDAs), and Global Positioning System (GPS) greatly facilitate and enrich our life. Nowadays, the wireless system is continuing to surge under increasing demands of high data rate and lower power consumption. The early developed standards such as Bluetooth and IEEE 802.11 family fail to come to this end due to their maximum data rate merely up to 54 Mega-bit-per-second (Mbps).

Ultra-Wideband (UWB) is a new rapidly advancing technology targeting at this goal and specified in IEEE 802.15.3a. The IEEE 802.15 TG3a specifies the unlicensed 3.1–10.6 GHz UWB band for short-range and high data-rate wireless communications. The UWB system provides Wireless Person Area Networks (WPANs) with data communication capabilities up to 480 Mbps.

The 7-GHz unlicensed band around 60 GHz for short-range and high-speed communication is developed for new consumer applications such as wireless High-Definition Multimedia Interface (HDMI) for high-definition television (HDTV) video stream and wireless data bus for cable replacement in recent years. Presently available unlicensed frequency bands are 59.0–66.0 GHz in Japan, 57.05–64.0 GHz in USA and Canada, 57.0–64.0 GHz in Korea, 57.0–66.0 GHz in Europe, and 59.4–62.0

GHz in Australia.

The landscape of wireless communication systems is shown in Fig. 1.1. Obviously, multi-gigabit-per-second (Gbps) data transmission becomes a challenge for future wireless communication systems.

Although the 60-GHz band offers the same amount of spectrum as UWB system at 3 to 10 GHz, few interferences and up to 40 dBm of transmit power envision a link to support multi-Gbps communication. According to the recently convention record in November 2007, the possible carrier frequencies are 58.32, 60.48, 62.64, and 64.8 GHz. The channel plan for full-rate (2 GHz) and half-rate (1 GHz) are shown in Figs. 1.2(a) and (b), respectively. The detail frequency plan is listed in Table 1.1. The target data rate for single carrier is 50.2 and 1506.6 Mbps with common rate (CR) and mandatory low rate (MLR), respectively. The propositional modulation schemes are  $\pi/2$  binary phase shift keying (BPSK) and Gaussian minimum shifting keying (GMSK).

Historically, the implementation of 60-GHz integrated circuits are designed and fabricated by using Gallium Arsenide (GaAs) or advanced Silicon Germanium (SiGe) [1]–[3]. However, a low cost solution is necessary for consumer applications. Due to the continual scaling down of the CMOS technology, the transition frequency ( $f_T$ ) of the nanometer CMOS technology up to 400 GHz has been reported in [4]. The CMOS technology can become the potential choice for the implementation of the 60-GHz wireless transceiver. Moreover, advanced CMOS technology has the advantages of low cost and of high-level integration with digital VLSI section. Therefore, CMOS technology can be a viable option to address the millimeter-wave market [5].

It is a tough task to grasp the analog and high-frequency character in monolithic

microwave integrated circuit (MMIC) design especially by using low-cost CMOS technology. There are still many problems and issues that we are facing and even have experienced. Researchers are supposed to invest much time and efforts to make great advancement. Making a more comfortable and convenient world is our destination as well as the motivation of our endeavors.

#### 1.2 REVIEWS ON CMOS CIRCUITS FOR 60-GHZ

#### **APPLICATIONS**

#### 1.2.1 Frequency multiplier

There are two methods to generate local oscillator (LO) signals. In the first method, LO signals are generated directly by using fundamental frequency oscillators [6]–[10]. In the second one, they are generated by using lower frequency oscillators cascaded with frequency multipliers to obtain signals at the desired frequencies [11]–[19]. Because of the limited performance of active and passive devices at high frequency, it is easier to design high-performance voltage-controlled oscillators (VCOs) at low frequency rather than at high frequency. Moreover, high frequency dividers operated at the carrier frequency with a significant amount of power dissipation are not needed when using a low frequency VCO. Therefore, the second method is advantageous in low-power CMOS circuit implementation in the millimeter-wave band.

In general, a frequency multiplier can be divided into two stages: the harmonic generation stage and the LO amplification stage. The harmonic generation stage is designed to generate the signal at the desired harmonic and the LO amplification stage

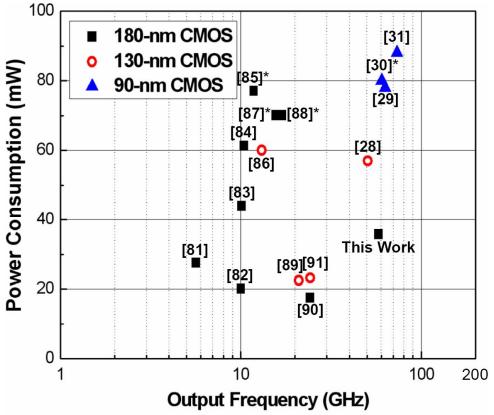

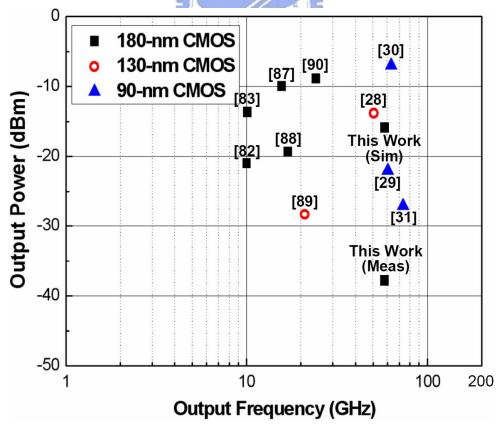

is designed to amplify the output amplitude at the desired frequency. Because large output amplitude is provided by the LO amplification stage, a large power consumption is required for driving output swing. Thus, a frequency multiplier with a significant amount of power dissipation is the main drawback [11]–[18]. It can be seen from Fig. 1.3, the power consumption of frequency multiplier is increased as the increase of output frequency of frequency multiplier. As a result, the key design requirement of the second method is to increase the frequency conversion gain of the frequency multipliers. In order to achieve this requirement, low input power and low dc power consumption are necessary to obtain the desired output power level.

Frequency multipliers integrated with injection-locked oscillators (ILOs) [20]–[25] can efficiently increase the conversion gain because ILOs have the superior properties of frequency stabilization and high conversion gain with a narrow bandwidth [26]. Such a frequency multiplier with ILO is called the subharmonic injection-locked frequency multiplier (ILFM). It offers great potential use with millimeter-wave frequency synthesizers because of its low input power and low dc power consumption. Even with low input power, the subharmonic ILFM [20]–[25] can provide the same performance as a conventional frequency multiplier [27].

#### 1.2.2 Phase-locked Loop and Frequency Synthesizer

Frequency synthesizer (FS) is a key building block of the radio-frequency integrated circuits (RFICs), which generates the carrier signal to convert transmission data up to the desired frequency band. The transmission and reception qualities in the wireless communication system are determined by the performance of LO that is generated by the FS.

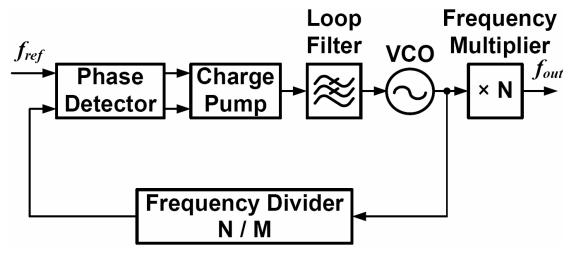

In the conventional FS [28]-[31], VCO is always operated at the highest

frequency to generate the LO signal as shown in Fig. 1.4. The output frequency  $f_{out}$  of VCO is M-times of input reference frequency  $f_{ref}$  under locked condition. Owing to the limited performance of the active and passive devices, the performance of the VCO is mainly determined by the device technology.

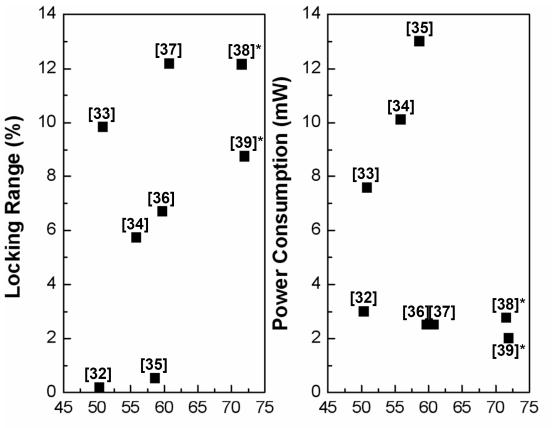

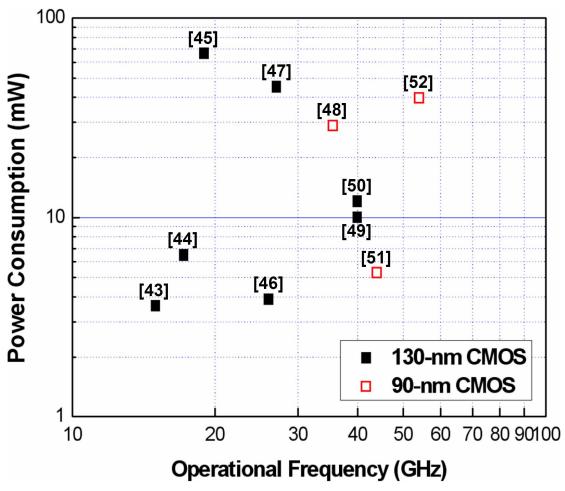

The implementation of the high-frequency divider is another important design issue in the conventional FS structure. The injection-locked frequency dividers (ILFDs) [32]–[39] or Miller divider [40]–[42] are the popular options for the high-frequency divider design. It can be seen from Fig. 1.5 that ILFDs can be operated under small power consumption but they are of narrow band characteristics. Any frequency shift in these dividers can cause the failure of the whole FS. Another high-speed frequency divider is current-mode logic (CML) divider [43]–[52]. The CMOS CML divider has been demonstrated to have high-speed operation with low power dissipation because the full swing for internal operation is not required. As can be seen from Fig. 1.6, the operational frequency of recently published CMOS CML divider without inductor is still lower than 60 GHz. Therefore, ILFD is the only one solution for 60-GHz frequency divider. Overdesign for locking range to avoid frequency shift is required. As a result, the output frequency range of conventional FS operated around 60 GHz can not be too large.

The other FS structure is composed of a low-frequency FS cascaded with a frequency multiplier to generate the desired output frequency as shown in Fig. 1.7. So far, there is no prior design with this FS structure in CMOS technology. In this FS structure, the low-frequency FS is operated at the subharmonic of the desired frequency and the target frequency is generated by the frequency multiplier after the low-frequency FS [53]–[55]. Obviously, it has the advantages of smaller division ratio and low power dissipation from the frequency divider. Therefore, the second FS

structure can be attractive for CMOS design in the millimeter-wave band if the high-frequency and low-power CMOS frequency multiplier can be developed.

The comparison of FS architectures is listed in Table 1.2. A high-performance and wide tuning range VCO can be designed in the subharmonic FS integrated with frequency multiplier due to lower operational frequency. Moreover, the division ratio of frequency divider can be lower than that of fundamental FS to reduce the power consumption. However, large power consumption is required as the operational frequency of frequency multiplier is high such as millimeter-wave band. Finally, because the last stage of the subharmonic FS structure is frequency multiplier, the output signal is usually mixed with the total harmonics of VCO output frequency. Hence, extra effort to suppress undesired harmonics is required.

As described in Section 1.2.1, the large power consumption from frequency multiplier can be reduced significantly by using ILO. ILO chain can become a possible solution to millimeter-wave MMIC synthesizers [53].

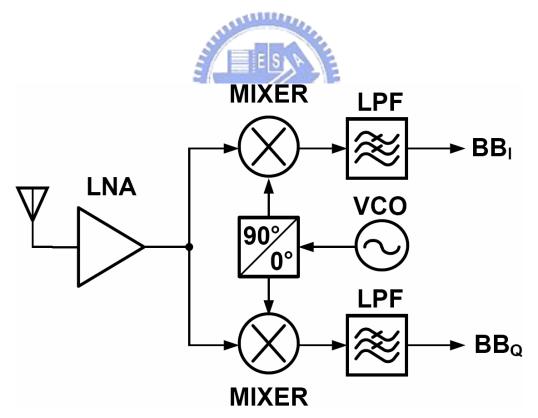

#### 1.2.3 Receiver

So far, some 60-GHz receivers have been demonstrated in CMOS technology [18]–[19], [56]–[64]. The homodyne receiver architecture is firstly implemented in the millimeter-wave receivers [56]–[59] because of its advantages of high integration and low system complication. The block diagram of the homodyne receiver is shown in Fig. 1.8. The radio-frequency (RF) signal is directly mixed with the local oscillator (LO) at the carrier frequency. Since the intermediate frequency (IF) is zero, the homodyne receiver is also called as zero-IF receiver or direct-conversion receiver.

Because the frequency of LO signal must be the same as the received frequency, the dc offset effect from the LO leakage by capacitive and substrate coupling [65] is serious. Two main sources of dc offsets are shown in Figs. 1.9 (a) and (b). The first source is the LO leaking to the low-noise amplifier (LNA) input and mixing with itself at the MIXER<sub>RF</sub>. The second source is the large nearby interferers leaking into VCO and then self-mixing.

Recently, a novel dc offset cancellation circuit has been proposed with simple Miller capacitor filter [66]. However, high-frequency synthesizer and high-frequency dividers with large power consumption are required. Due to large power consumption, the homodyne receiver structure is not suitable for consumer mobile applications.

The heterodyne receiver architecture is the one solution for the high-frequency synthesizer because the frequency of LO signals can be lower than received frequency as shown in Fig. 1.10 [60]–[64]. However, twice frequency translations make that the architecture of the receiver more complicated and image signal rejection is required for better signal-to-noise ratio (*SNR*). As compared with Fig. 1.8, the extra filters for frequency selection, BPF<sub>RF</sub> and BPF<sub>IF</sub>, are required. Therefore, the system complication is increased. Moreover, more inductors are required for system integration. Hence, total chip area is increased as compared with direct-conversion receiver.

Another solution for the high-frequency synthesizer is the frequency multiplier as shown in Fig. 1.11 [18]–[19]. The new CMOS frequency doubler [18] and frequency tripler [19] for the LO generation is proposed. Because of the even order frequency multiplier, the differential output can not be provided for the mixer operation. Thus, the extra effort is required for single to differential converter [18]. The first millimeter-wave CMOS frequency tripler is introduced in [19]. Due to its fully differential structure of frequency tripler, it is suitable for complex modulation schemes.

The comparison of receiver architectures is listed in Table 1.3. The homodyne receiver can achieve high-integration and low-power consumption, but the operational frequency of frequency synthesizer is the highest. The heterodyne receiver can be operated with lower operational frequency synthesizer but its system is too complex for millimeter-wave circuits. Finally, the homodyne receiver integrated with frequency multiplier is the best choice for high-frequency receiver design it has the advantages of homodyne receiver and the lower operational frequency of frequency synthesizer.

#### 1.3 MOTIVATION AND MAIN RESULTS

The performance of VCO in the millimeter-wave band strongly depends on the characteristics of active and passive devices. To design the high-performance of low-frequency VCO cascaded with frequency multiplier is a solution to generate the high-performance LO signals. However, the power consumption of frequency multiplier is large when the operational frequency is high. The design of CMOS subharmonic ILFMs becomes the new interesting research topic in the millimeter-wave band because of their low power consumption. In this dissertation, the novel CMOS subharmonic injection-locked frequency tripler (ILFT) is developed for millimeter-wave band applications. The proposed ILFT can provide the similar output power as a VCO with small power consumption. Moreover, the locking range of the proposed ILFT can be similar to the tuning range of a VCO. As a result, the proposed ILFT can offer great potential application in LO signal generators for frequency synthesizers in the millimeter-wave band.

The proposed CMOS subharmonic ILFMs are further verified by the integration

with phase-locked loop (PLL) and receiver. In the PLL design, the new CMOS PLL structure that is formed by a low-frequency PLL cascaded with subharmonice ILFM is designed to avoid the use of the conventional ILFDs and Miller dividers with narrow-band characteristics. In addition, the maximum operational frequency of frequency divider can be reduced. The low-power PLL without ILFDs or Miller dividers for 60-GHz applications is designed in CMOS technology. Finally, the direct-conversion receiver is also integrated with subharmonic ILFT.

The aim of this dissertation is to develop low-power 60-GHz CMOS millimeter-wave circuits including millimeter-wave CMOS ILFTs, a 60-GHz PLL and a 60-GHz direct-conversion receiver.

Firstly, a *K*-band ILFT is designed and fabricated using 0.18-μm CMOS technology. The total locking range of the *K*-band ILFT can achieve 3915 MHz with 4-dBm input power when the varactors are used and the dc power consumption is 2.95 mW. A *V*-band ILFT is also designed and fabricated using 0.13-μm CMOS technology. The measured injection-locking range is 1422 MHz with 1.86-mW dc power consumption and 6-dBm input power. The locking range of the proposed ILFT is similar to the tuning range of a conventional varactor-tuned bulk-CMOS VCO. Moreover, the output power of the proposed ILFT is also similar to that of a VCO.

Secondly, a novel CMOS PLL integrated with ILFM that generates the 60-GHz output signal is proposed and designed in 0.18-µm CMOS technology. The output frequency range of the proposed PLL is from 53.04 GHz to 58.0 GHz. The measured phase noises at 1 MHz and 10 MHz offset from the carrier are -85.2 and -90.9 dBc/Hz, respectively. The reference spur level of -40.16 dBc is measured. The dc power dissipation of the fabricated PLL is 35.7 mW under a 1.8-V supply. It can be seen that the performance of the proposed PLL is similar to previous woks and the

power dissipation of the proposed PLL is only two-third of previous works [28]–[31]. Therefore, the proposed PLL structure is suitable for low power and high performance millimeter-wave PLL in 60-GHz applications.

Finally, a novel 60-GHz CMOS direct-conversion receiver front-end integrated with ILFTs is described. In the proposed receiver, the LO signals are generated by the QVCO operated at only one-third of carrier frequency cascade with the two ILFTs. Because of the QVCO frequency shift, the maximum RF frequency is 55.03 GHz. The measured results show a receiver gain of 18.2 dB, a noise figure of 16.96 dB, and an input-referred 1-dB compression point of –17.0 dBm. The proposed receiver is implemented using 0.13-μm CMOS technology and draws 25.84 mA from a 1.2-V supply. The total chip area is 1.21 mm × 1.03 mm. From the measurement results, the proposed receiver architecture provides a potential choice for high-integration and low-power in 60-GHz transceiver design.

#### 1.4 ORGANIZATION OF THIS DISSERTATION

In Chapter 2, a novel CMOS ILFT is proposed and designed. The new concept for frequency tripler integrated with injection-locked oscillator (ILO) is introduced. In addition, the model and design methodology for the proposed ILFT are analyzed and developed. Finally, the performances of the proposed ILFTs are verified by experimental results at *K*-band and *V*-band. The experimental results show that the proposed ILFTs can provide large output power with low dc power dissipation.

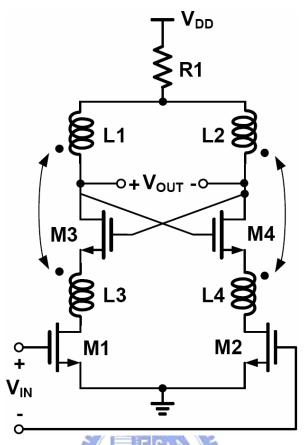

In Chapter 3, a 60-GHz CMOS PLL used for IEEE 802.15.3c applications is proposed and designed using 0.18-µm CMOS technology. The extension model from ILFT for fifth-order harmonic of ILFM is presented. The proposed ILFM worked

beyond device transition frequency ( $f_T$ ) is designed to generate the 60-GHz output signal. Because this design takes the advantage of low division ratio of frequency and low power consumption by using ILFM, the total power dissipation of the proposed PLL is significantly reduced as compared with published CMOS PLLs.

A 60-GHz CMOS direct-conversion receiver integrated with ILFT is described in Chapter 4. The proposed receiver is the first CMOS receiver design that integrates with ILFT. In addition, the maximum operation frequency of the frequency divider in a frequency synthesizer can be reduced to one-third by using the ILFT. Since it is feasible to design a high-performance VCO at low frequency and to save the large power consumption from full-speed frequency dividers, the proposed receiver can provide a solution to the wireless transceiver in the millimeter-wave band. Finally, conclusions and future work are given in Chapter 5.

Table 1.1 Frequency plan for 60-GHz applications.

|         | Channel Plan : Full-Rate (2 GHz) |                  |             |          |

|---------|----------------------------------|------------------|-------------|----------|

| Channel | Low Freq.                        | Center Freq.     | High Freq.  | Nyquist  |

| Number  | (GHz)                            | (GHz)            | (GHz)       | BW (MHz) |

| A1      | 57.24                            | 58.32            | 59.40       | 1728     |

| A2      | 59.40                            | 60.48            | 61.56       | 1728     |

| А3      | 61.56                            | 62.64            | 63.72       | 1728     |

| A4      | 63.72                            | 64.80            | 65.88       | 1728     |

|         | Channel                          | l Plan : Half-Ra | ate (1 GHz) |          |

| Channel | Low Freq.                        | Center Freq.     | High Freq.  | Nyquist  |

| Number  | (GHz)                            | (GHz)            | (GHz)       | BW (MHz) |

| B1      | 57.78                            | 58.32            | 58.86       | 864      |

| B2      | 59.94                            | 60.48            | 61.02       | 864      |

| В3      | 62.10                            | 62.64            | 63.18       | 864      |

| B4      | 64.26                            | 64.80            | 65.34       | 864      |

Table 1.2 Comparison of the FS architectures.

| Structure                                    | Fundamental FS<br>(Direct Generation) | Subharmonic FS with Frequency Multiplier          |

|----------------------------------------------|---------------------------------------|---------------------------------------------------|

| Output purity                                | Pure                                  | Mixed                                             |

| VCO performance                              | Poor                                  | Good                                              |

| Frequency divider division ratio             | High                                  | Low                                               |

| Frequency divider power consumption          | High                                  | Low                                               |

| Frequency divider bandwidth                  | Narrow<br>(ILFD or Miller<br>divider) | Wide<br>(if CML frequency<br>divider can be used) |

| Frequency<br>multiplier                      | Not Required                          | Yes                                               |

| Frequency<br>multiplier power<br>dissipation | None                                  | Large                                             |

|                                              | Manne                                 |                                                   |

Table 1.3 Comparison of the receiver architectures.

| Structure                   | Homodyne<br>Receiver                 | Heterodyne<br>Receiver | Homodyne<br>Receiver with<br>Frequency<br>Multiplier |

|-----------------------------|--------------------------------------|------------------------|------------------------------------------------------|

| Integration ability         | Good                                 | Poor                   | Good                                                 |

| Image rejection             | Not required                         | Required               | Not required                                         |

| dc-offset                   | Yes                                  | No                     | Yes                                                  |

| 1/f noise                   | Yes                                  | No                     | Yes                                                  |

| Operational frequency of FS | High<br>(Large power<br>consumption) | Mediate                | Low<br>(Small power<br>consumption)                  |

| Frequency multiplier        | Not required                         | Not required           | Required                                             |

Fig. 1.1 The landscape of wireless communication systems.

Fig. 1.2 Frequency plan for (a) full-rate and (b) half-rate in 60-GHz applications.

<sup>\*</sup> These values exclude the amplification stage with small output power for a fair comparsion.

Fig. 1.3 Recently published CMOS frequency multipliers.

Fig. 1.4 Block diagram of the conventional frequency synthesizer.

**Operational Frequency (GHz) Operational Frequency (GHz)**

Fig. 1.5 Recently published CMOS injection-locked frequency dividers.

<sup>\*</sup> Tuning Varactors are used for increasing locking range.

Fig. 1.6 Recently published CMOS CML frequency dividers without inductor peaking.

Fig. 1.7 Block diagram of frequency synthesizer with frequency multiplier.

Fig. 1.8 Block diagram of the homodyne receiver.

Fig. 1.9 The sources of dc offsets from (a) LO leaking to LNA input and (b) large interferers leaking to VCO.

Fig. 1.10 Block diagram and frequency translation of the heterodyne receiver.

Fig. 1.11 Block diagram of the homodyne receiver with frequency multiplier.

### **CHAPTER 2**

# CMOS SUBHARMONIC INJECTION-LOCKED FREQUENCY TRIPLERS

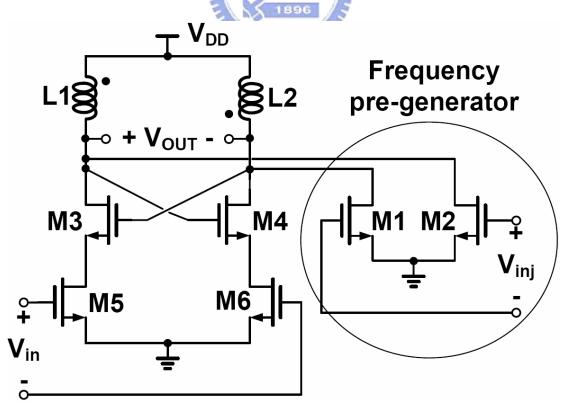

In this chapter, a new CMOS fully differential subharmonic injection-locked frequency tripler (ILFT) is proposed and analyzed. It is suitable for complex modulation schemes because of its fully differential structure. The locking range of the proposed ILFT is improved by inserting the frequency pre-generator circuit before the ILO. The main advantage of a frequency pre-generator is that the locking range can be maximized with little degradation of ILO output performance. An analytical model is developed to characterize both the locking range and the output phase noise of the proposed ILFT. The proposed *K*-band ILFT is fabricated using 0.18-μm CMOS technology. According to the measured results, it has an locking range of 1092-MHz wide with an input power of only 4-dBm and a dc power consumption of 0.45 mW. Moreover, the output power can achieve –9.4-dBm with 10.5-dB phase noise higher than that of the input signal. This chapter shows that the key design requirement can be achieved in the proposed ILFT. Finally, the theoretical results are verified by the experimental results.

In Section 2.1, the model for the proposed ILFT is derived. The CMOS circuit implementation is described in Section 2.2. The experimental results are presented in Section 2.3. Finally, the conclusion and summary are given in Section 2.4.

#### 2.1 THEORETICAL MODEL FOR INJECTION-LOCKED

#### FREQUENCY TRIPLER

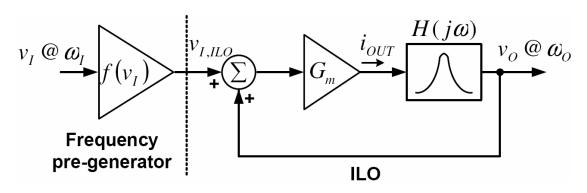

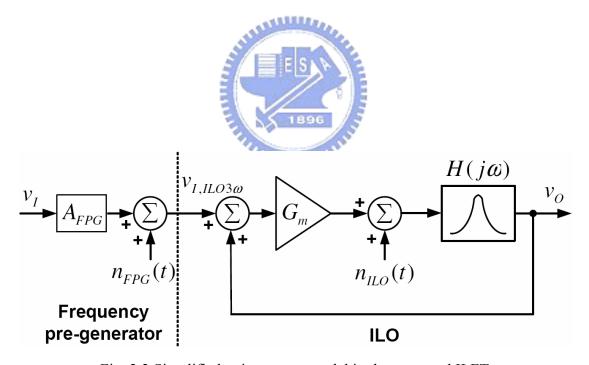

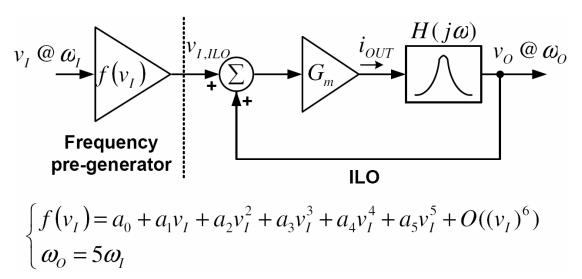

Based upon the locking mechanism for a small injection signal [26] and the simple ILO model [67], a physical representation of the proposed ILFT with a frequency pre-generator to generate the third-order harmonic signal connected to an ILO is shown in Fig. 2.1. In the ILO model,  $H(j\omega)$  is the transfer function of the band pass LC-tank filter used to eliminate undesired frequencies generated by the frequency pre-generator. The active devices of the ILO are modeled as the linear constant transconductance stage  $G_m$ . The frequency pre-generator is modeled as the nonlinear characteristic function  $f(v_I)$ . Both the  $G_m$  and  $H(j\omega)$  with a feedback path form the ILO. Without any input signal, the ILO has a steady output signal if the Barkhausen criterion is satisfied in the close-loop structure. An incident signal  $v_I(t)$  with input frequency  $\omega_I$  is injected into the oscillator via a frequency pre-generator. The output frequency  $\omega_O$  is the function of input frequency  $\omega_I$  while the oscillator is under the locked situation.

If the ILFT is under the locked condition, the following apply:

$$v_I(t) = V_i \cos(\omega_I t + \theta) \tag{2.1}$$

$$v_o(t) = V_o \cos(\omega_o t) \tag{2.2}$$

$$v_{I,ILO}(t) = f(v_I(t)) = f(V_i \cos(\omega_I t + \theta))$$

(2.3)

where  $v_I(t)$  is the incident signal with input frequency  $\omega_I$ , amplitude  $V_i$ , and phase  $\theta$ ;  $v_O(t)$  is the output signal with frequency  $\omega_O = 3\omega_I$  and amplitude  $V_o$ ; and  $v_{I,ILO}(t)$  is the output signal of the frequency pre-generator.

From [68],  $v_{I,ILO}(t)$  can be expressed as a polynomial series:

$$v_{I.ILO}(t) = f(v_I(t)) = \sum_{n=0}^{\infty} a_n (v_I(t))^n$$

$$= a_0 + a_1 v_I(t) + a_2 (v_I(t))^2 + a_3 (v_I(t))^3 + O((v_I(t))^4)$$

(2.4)

where  $a_n$  is the coefficient of polynomial f, and  $O((v_I(t))^4)$  is the terms of order higher than three. The coefficient  $a_3$  is proportional to the conversion gain of the third-order harmonic frequency generator. The output current of the transconductance stage  $G_m$  can been written as

$$i_{OUT} = G_m [f(v_I(t)) + v_O(t)]$$

$$= G_m [v_{I,ILO}(t) + v_O(t)].$$

$$E_{OUT} = G_m [v_{I,ILO}(t) + v_O(t)]$$

$$= G_m [v_{I,ILO}(t) + v_O(t)]$$

$$= G_m [f(V_I \cos(\omega_I t + \theta)) + V_O \cos(\omega_O t)].$$

(2.5)

By neglecting the  $O((v_I(t))^4)$  term in (2.4), by substituting other terms in (2.4) into (2.6), by assuming that any frequency not close to  $\omega_O$  is filtered out by the frequency selective load  $H(j\omega)$ , and by rearranging the terms, (2.6) can be rewritten as

$$i_{OUT} = \text{Re}\left\{e^{j\omega_O t} \left[G_m V_o + \frac{a_3 G_m V_i^3}{4} e^{j3\theta}\right]\right\}$$

$$= |i_{OUT}| \cos(\omega_O t + g(\theta))$$

(2.7)

where

$$\left|i_{OUT}\right| = \sqrt{\left[G_m V_o + \left(\frac{a_3 G_m V_i^3}{4}\right) \cos 3\theta\right]^2 + \left[\left(\frac{a_3 G_m V_i^3}{4}\right) \sin 3\theta\right]^2}$$

(2.8)

$$g(\theta) = \arctan\left\{\frac{a_3 G_m V_i^3 \sin 3\theta}{4 G_m V_o + a_3 G_m V_i^3 \cos 3\theta}\right\}$$

(2.9)

and  $a_3$  is the coefficient of cubic term in the nonlinear characteristic function of the frequency pre-generator.

The approximate transfer function of the band pass LC-tank filter  $H(j\omega)$  can be written as

$$H(j\omega) = \frac{H_0}{1 + j2Q\left(\frac{\omega - \omega_r}{\omega_r}\right)}$$

(2.10)

where  $\omega_r$  and Q are the resonant frequency and quality factor of the LC-tank, respectively.  $H_0$  is the impedance of the LC-tank at resonant frequency.

If the Barkhausen criterion is satisfied in the close-loop, the phase shift of the close-loop should be zero. Thus

$$-\arctan\left[\frac{2Q(\omega-\omega_r)}{\omega_r}\right] + g(\theta) = 0.$$

(2.11)

Combing (2.9) and (2.11), gives

$$\left[\frac{2Q(\omega - \omega_r)}{\omega_r}\right] = \left\{\frac{a_3 G_m V_i^3 \sin 3\theta}{4G_m V_o + a_3 G_m V_i^3 \cos 3\theta}\right\}.$$

(2.12)

By rearranging (2.12) and finding the solution for  $\theta$ , the following is derived

$$\sin(3\theta - \phi) = \frac{\frac{4V_o}{a_3V_i^3} \left[ \frac{2Q(\omega - \omega_r)}{\omega_r} \right]}{\sqrt{1 + \left[ \frac{2Q(\omega - \omega_r)}{\omega_r} \right]^2}}$$

(2.13)

where

$$\phi = \arcsin \left\{ \frac{\frac{2Q(\omega - \omega_r)}{\omega_r}}{\sqrt{1 + \left[\frac{2Q(\omega - \omega_r)}{\omega_r}\right]^2}} \right\}.$$

(2.14)

Since  $|\sin(3\theta - \phi)| \le 1$ , (2.13) can be rewritten as

$$\frac{\left|\omega - \omega_{r}\right|}{\omega_{r}} \le \frac{1}{2Q} \sqrt{\frac{\left(a_{3}V_{i}^{3}\right)^{2}}{\left(4V_{o}\right)^{2} - \left(a_{3}V_{i}^{3}\right)^{2}}} \approx \frac{1}{2Q} \left|\frac{a_{3}V_{i}^{3}}{4V_{o}}\right|. \tag{2.15}$$

If  $4V_o >> a_3V_i^3$ , the approximation in (2.15) is valid.

The output voltage amplitude can be written as

$$V_o = |i_{OUT}||H(j\omega)|$$

$$=G_m H_0 \sqrt{V_o + \left(\frac{a_3 V_i^3}{4}\right) \cos 3\theta}^2 . \tag{2.16}$$

By solving (2.16) and assuming  $V_o + (a_3V_i^3\cos 3\theta/4) > 0$ , the expression of the output amplitude can be rewritten as

$$V_o = \frac{a_3 G_m H_0 V_i^3 \cos 3\theta}{4(1 - G_m H_0)}. (2.17)$$

In general, the locking range is limited by failure of either the phase condition (2.15) or the gain condition (2.16) [67]. From (2.15), it can be seen that the locking

range increases with an increase in either the conversion gain of the frequency pre-generator or the incident amplitude  $V_i$ . The degradation of the LC-tank quality factor Q can also improve the locking range. However, the latter causes a decrease in the impedance of the LC-tank  $H_0$  and, thus, the output voltage amplitude also decreases (2.17). This result is consistent with the results in [26]. According to the proposed ILFT model, the design principle can be developed. It can be seen from (2.17) that the quality factor of the LC-tank can be maximized in order to obtain increased output amplitude. The resulting degradation of the locking range can be improved by increasing of the conversion gain of the frequency pre-generator (2.15).

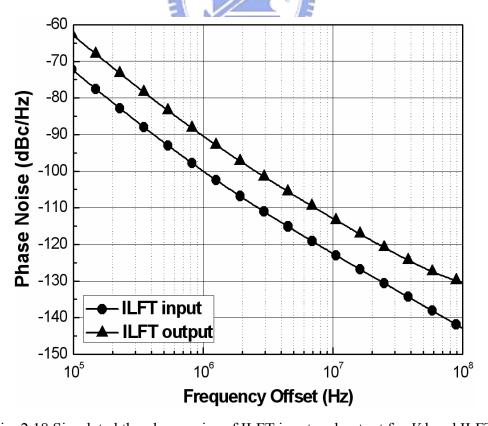

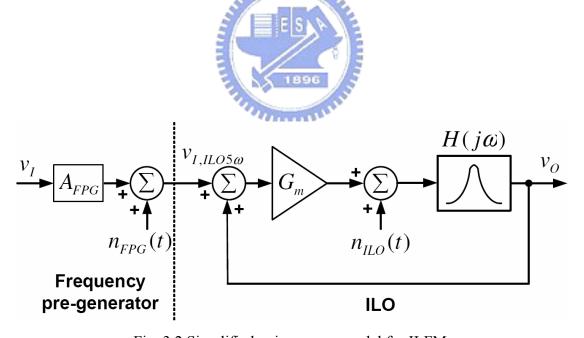

The overall ILO output phase noise is characterized by the noise contributions of all blocks in an ILO [69]. The simplified noise source model of the proposed ILFT is shown in Fig. 2.2 where the conversion gain of the third-order harmonic signal in the frequency pre-generator is simplified to be a constant value  $A_{FPG}$  and  $v_{I,ILO3\omega}$  is the signal with frequency  $3\omega_I$ . The noise contribution from the frequency pre-generator and the ILO are modeled as  $n_{FPG}(t)$  and  $n_{ILO}(t)$ , respectively. The linear phase-domain model [70] is adopted to calculate the output phase noise.

The simplified noise source model of the proposed ILFT, as shown in Fig. 2.2, can be divided into two parts. One part is the noise calculation of the frequency pre-generator and the other is the noise analysis of the ILO. First, the noise characteristic between  $v_I$  and  $v_{I,ILO3\omega}$  is considered. The phase noise spectral density  $S_{IN,ILO}(\omega_m)$  at  $v_{I,ILO3\omega}$  node can be expressed as [69]

$$S_{IN,IIO}(\omega_m) = 3^2 \cdot S_{INI}(\omega_m) + S_{EPG}(\omega_m)$$

(2.18)

where  $S_{INJ}(\omega_m)$  and  $S_{FPG}(\omega_m)$  are phase noise spectral densities of the injection signal and frequency pre-generator, respectively.  $\omega_m$  is the offset frequency from output

frequency  $\omega_O$ .

The noise relation between  $v_{I,ILO3\omega}$  and  $v_O$  can be written as [69]

$$S_{OUT}(\omega_m) = \frac{1}{1 + \left(\frac{\omega_m}{\omega_p}\right)^2} S_{IN,ILO}(\omega_m) + \frac{\left(\frac{\omega_m}{\omega_p}\right)^2}{1 + \left(\frac{\omega_m}{\omega_p}\right)^2} S_{FreeRun}(\omega_m)$$

(2.19)

where the corner frequency of the ILFT noise transfer function  $\omega_p$  can be written as

$$\omega_p = \frac{\omega_r}{2Q} \frac{\eta}{1+\eta} \tag{2.20}$$

$$\eta = \frac{A_{FPG}V_i}{V_o}. (2.21)$$

In the above equations,  $S_{OUT}(\omega_m)$  and  $S_{FreeRun}(\omega_m)$  are phase noise spectral densities of output and internal circuits, respectively;  $A_{FPG}$  is the conversion gain of the third-order harmonic signal in the frequency pre-generator;  $\omega_r$  and Q are the resonant frequency and the quality factor of LC-tank in the band pass filter, respectively;  $H_0$  is the impedance of the LC-tank at resonant frequency; and  $V_i$  and  $V_o$  indicate the amplitudes of input and output, respectively.

The combination of (2.18) and (2.19) results in the following:

$$S_{OUT}(\omega_m) = \frac{3^2}{1 + \left(\frac{\omega_m}{\omega_p}\right)^2} S_{INJ}(\omega_m) + \frac{1}{1 + \left(\frac{\omega_m}{\omega_p}\right)^2} S_{FPG}(\omega_m) + \frac{\left(\frac{\omega_m}{\omega_p}\right)^2}{1 + \left(\frac{\omega_m}{\omega_p}\right)^2} S_{FreeRun}(\omega_m) \quad (2.22)$$

As may be seen from the first and the second terms in (2.22), the noise from the input signal and frequency pre-generator are passed through the low-pass filter so that their noise transfer functions have low-pass transfer characteristics. Thus, the output

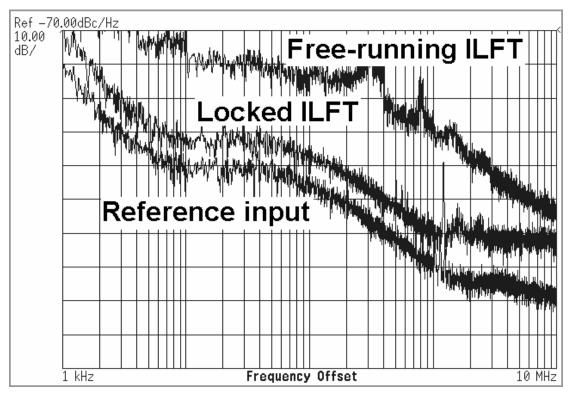

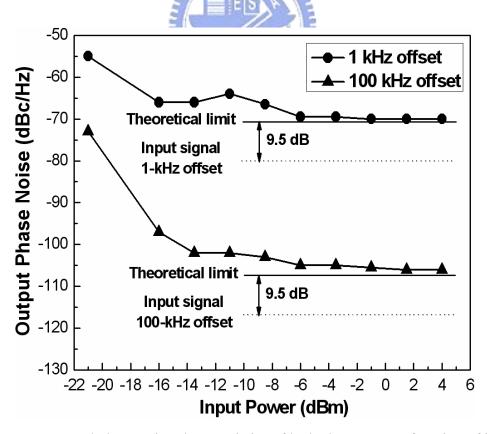

phase noise is dominated by these two noise sources at small offset frequency  $\omega_m$ . If the noise contribution from the frequency pre-generator is negligible, the output phase noise is 9.5 dB [=10log (3<sup>2</sup>)] higher than that from the input signal with a small offset frequency. The noise from internal circuits as given in the third term of (2.22) has a high-pass transfer characteristic. At large offset frequency  $\omega_m$ , the output phase noise is dominated by this noise and has a high-pass shape. To minimize the output phase noise, the corner frequency  $\omega_p$  can be increased to filter out the internal noise. As may be seen from (2.20) and (2.21),  $\omega_p$  can be increased by either degradation of the *LC*-tank quality factor Q or the high incident amplitude  $V_i$ .

A summary of the proposed ILFT can be developed from (2.6)–(2.11). The quality factor Q of the LC-tank is maximized for a large output voltage swing and for low-power consumption. The degradation of the locking range and the output phase noise from the increase in quality factor Q can be compensated for by increasing the conversion gain of the frequency pre-generator.

If the frequency pre-generator is removed from ILFT, the nonlinear characteristic function is performed by ILO. Thus, the locking range can be derived as

$$\frac{\left|\omega - \omega_{r}\right|}{\omega_{r}} \leq \frac{1}{2Q} \sqrt{\frac{\left(a_{3}V_{i}^{3}\right)^{2}}{\left(4a_{1}V_{o} + 6a_{3}V_{i}^{2}V_{o} + 3a_{3}V_{o}^{3}\right)^{2} - \left(a_{3}V_{i}^{3}\right)^{2}}}$$

$$\approx \frac{1}{2Q} \left|\frac{a_{3}V_{i}^{3}}{4a_{1}V_{o} + 6a_{3}V_{i}^{2}V_{o} + 3a_{3}V_{o}^{3}}\right|.$$

(2.23)

Whereas the output amplitude is represented as

$$V_o = G_m H_0 \sqrt{\left[a_1 V_o + \left(\frac{a_3 V_i^3}{4}\right) \cos 3\theta + \frac{3}{2} a_3 V_i^2 V_o + \frac{3}{4} a_3 V_o^3\right]^2}$$

(2.24)

It can be seen from (2.23) that the locking range can be increased by increasing  $|a_3|$ . In general, the value of  $a_3$  is negative, and an  $|a_3|$  which is too large would degrade the output amplitude of the ILFT in (2.24) significantly. Obviously, if an ILFT works without the frequency pre-generator, the extra power consumption is required for both a large locking range and large output amplitude.

#### 2.2 CIRCUIT REALIZATION

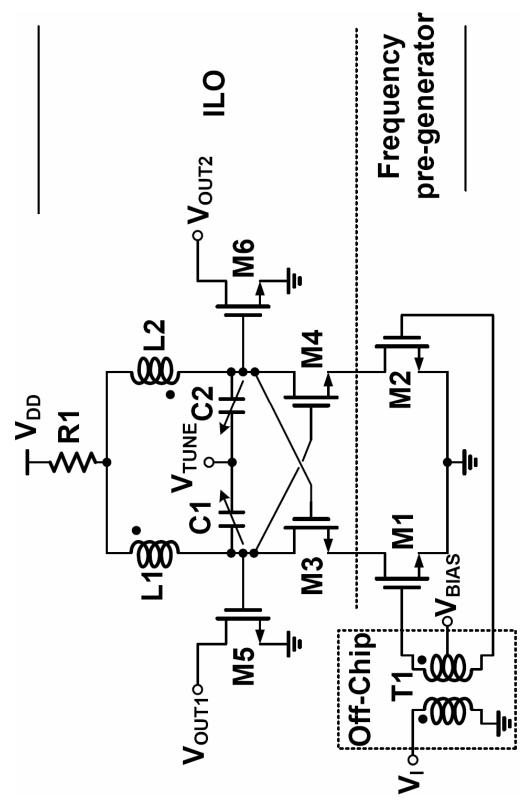

#### 2.2.1 The Circuit Design of Injection-locked Frequency Triplers

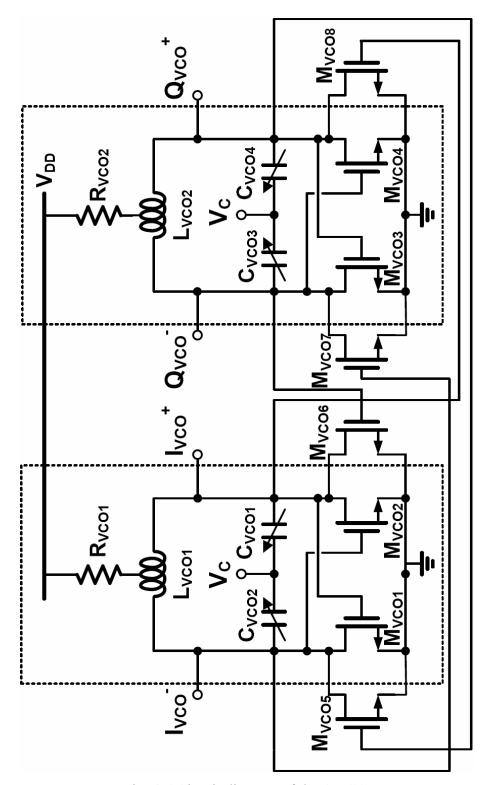

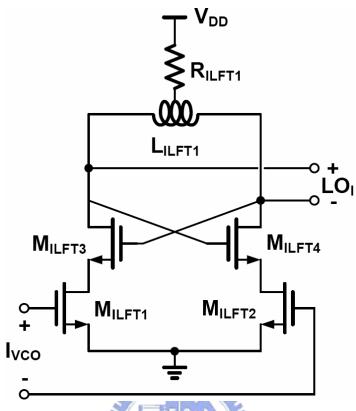

Based on the model developed in Section 2.1, the K-band and V-band CMOS ILFTs are designed. The proposed CMOS ILFT circuit is shown in Fig. 2.3. The off-chip transformer T1 is designed to generate the differential input signal. The function of the frequency pre-generator is implemented by M1 and M2. The design guideline of M1 and M2 is the same as for the conventional frequency multipliers in [71]. The gate bias V<sub>BIAS</sub> of M1 and M2 is fed from the input off-chip transformer T1 and the conversion gain of the frequency pre-generator can be maximized with an appropriate V<sub>BIAS</sub> value. The tripled-frequency signal generated by the frequency pre-generator is injected into the ILO formed by M3, M4, C1, C2, L1, and L2. The selected values of inductors L1/L2 and varactors C1/C2 are chosen so that their resonant frequency is close to the third-order harmonic frequency of the input signal. According to the design guideline in Section 2.1, the quality factor of the LC-tank is maximized for a large output swing and low power consumption.  $V_{\text{TUNE}}$  is the external controlled signal used to increase the locking range. M3 and M4 are used to generate the negative resistance to compensate for the loss of the LC-tank. R1 is designed for the improvement of the harmonic rejection-ratios (HRRs). Finally, the output signals are taken from the open-drain buffers for test purposes. The proposed ILFT has a current-reuse structure between the frequency pre-generator and the ILO for low power operation.

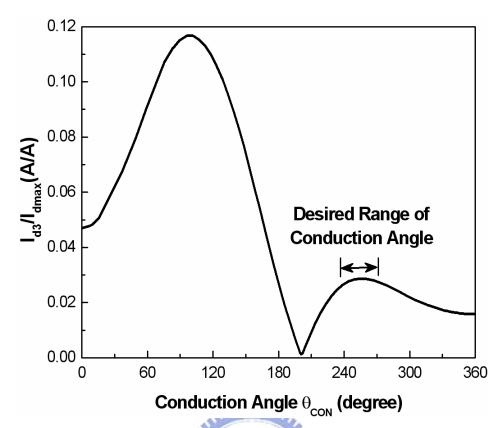

Fig. 2.4 shows the HSPICE simulated normalized third-order harmonic currents I<sub>d3</sub>/I<sub>dmax</sub> of the frequency pre-generator M1/M2 as a function of conduction angle  $(\theta_{\text{CON}})$  where  $I_{\text{d3}}$  is the output amplitude of the drain current at the third-order harmonic frequency, I<sub>dmax</sub> is defined as the maximum peak-to-peak output drain current, and conduction angle is the device turn-on angle within one period of input signal. The simulation condition involves an 8-GHz input signal with 4-dBm input power and a MOS device with dimensions of W/L =  $18 \mu m/0.18 \mu m$  with gate-source bias voltage changing from 0.03 V to 1.03 V. Because of the parasitic capacitance of the device, the ac current between the gate and drain is included in the output drain current I<sub>dmax</sub>. Thus, the normalized harmonic current curve in Fig. 2.4 is not the same as the ideal switch condition in [71]. The maximum output third-order harmonic current occurs when the conduction angle is 100°. With this conduction angle, the devices M1/M2 must be biased at the weak-inversion region. Under this condition, the ILO circuits may not satisfy the oscillation condition with such a small dc current. In the proposed ILFT, the frequency tripled function devices (M1 and M2) are biased at a conduction angle of 250° for higher frequency conversion efficiency while maintaining oscillation. The V<sub>BIAS</sub> can be calculated by a given input power, a device threshold voltage, and a suitable conduction angle [71].

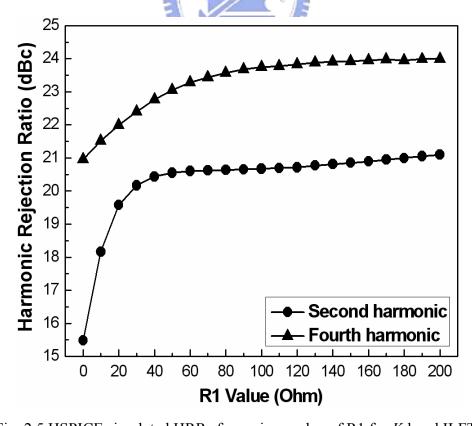

Because the even harmonic signals are common-mode signals, an appropriate value for resistor R1 is set to eliminate the undesired even harmonic signals. To verify the effect of R1, Fig. 2.5 shows the HSPICE simulation results of the second-order and forth-order HRRs for various values of R1 in the *K*-band ILFT design. It can be

seen that the HRR can be improved with a small R1 value. When the R1 value is 90 ohm, the HRRs improve with only a small voltage drop for the K-band ILFT. However, for the V-band ILFT, the R1 value needs only to be 55 ohm because of the low nominal power supply voltage in 0.13- $\mu$ m CMOS technology.

#### 2.2.2 The Simulation Results of Injection-locked Frequency Triplers

#### **2.2.2.1** *K*-band ILFT

Based on the model development in Section 2.1 and the circuit description in Section 2.2.1, the device dimension for K-band ILFT in 0.18- $\mu$ m CMOS technology is shown in Table 2.1 (a). The locking range as a function of input bias  $V_{BIAS}$  is shown in Fig.2.6. Small dc current is allowed through M3/M4 as the input bias  $V_{BIAS}$  is decreased, the negative-resistance generated by M3/M4 becomes weaker. Therefore, the locking range is increased due to the small effective quality factor of LC tank. Due to a large third-order harmonic current is generated by M1/M2 at the  $V_{BIAS}$  of 0.65 V, it exists a peak locking range. As a results, the input bias value  $V_{BIAS}$  of 0.65 V is suggested in the K-band ILFT.

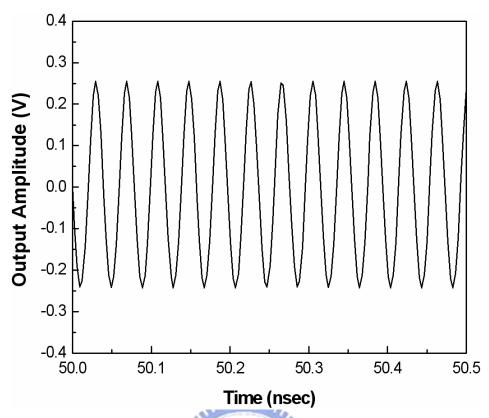

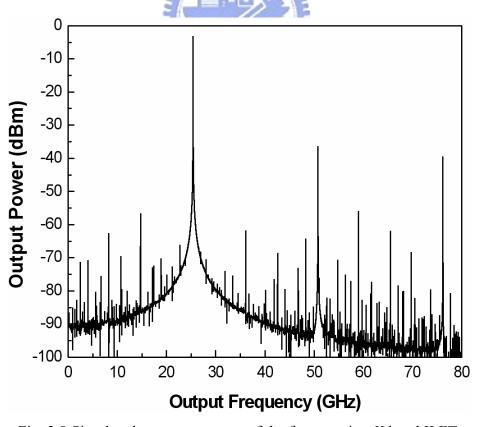

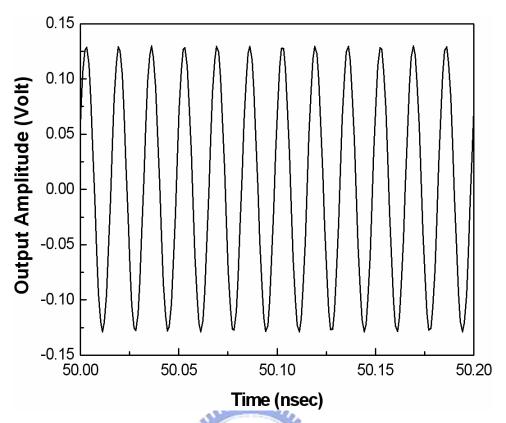

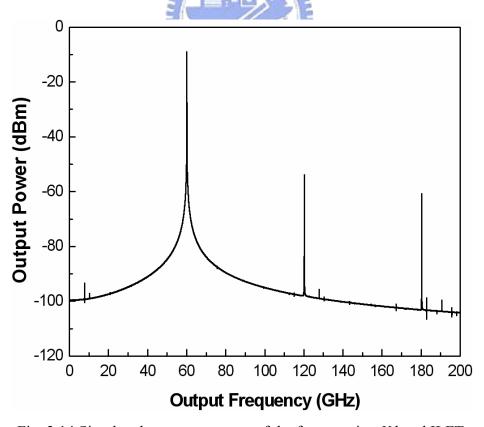

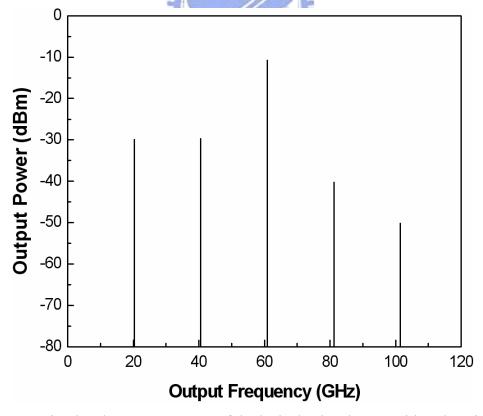

The simulated power consumption of the *K*-band ILFT is 2.95 mW at a power supply of 1.5 V. The SPECTRE RF simulated free-running *K*-band ILFT output after output buffer at time-domain and frequency-domain analysis are shown in Figs. 2.7 and 2.8, respectively. The free-running *K*-band ILFT provides the output amplitude of 250 mV as can be seen from transient simulation and output power of –2.04 dBm at 25.39 GHz as shown in the Fast-Fourier Transform (FFT) results. The simulated locked *K*-band ILFT output after output buffer with input power of 4 dBm, input frequency of 8.48 GHz, and V<sub>BIAS</sub> of 0.65 at time-domain and frequency-domain are shown in Figs. 2.9 and 2.10, respectively. It can be seen from Fig. 2.9 that the fundamental signal is existed in the output waveform. The simulated output spectrum

of locked *K*-band ILFT is shown in Fig. 2.10 where the HRRs compared to the desired third-order harmonic are 24.21, 16.56, 25.49, 40.40 dBc for the first, second, forth, and fifth harmonics, respectively. Due to the parasitic capacitance of resistor R1, the HRRs can not reach to the ideal case in Fig. 2.5.

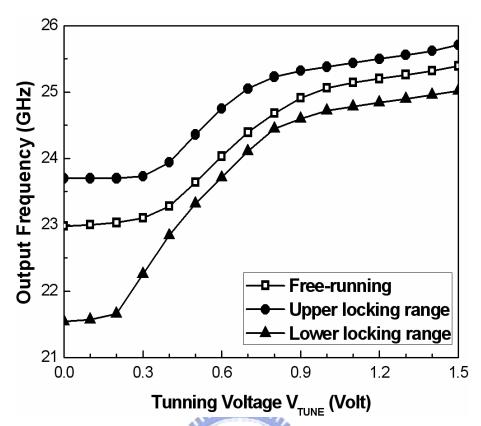

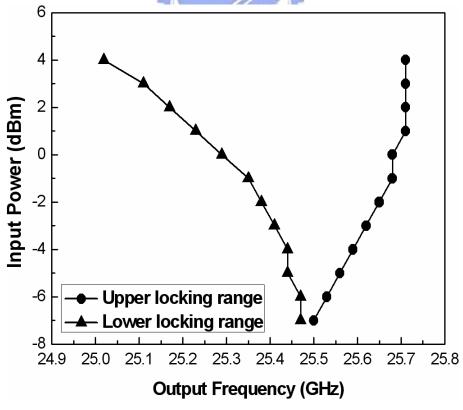

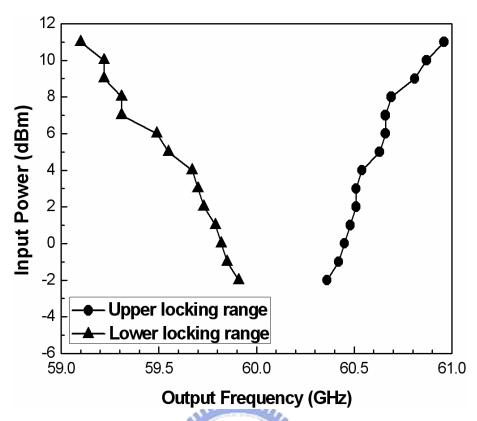

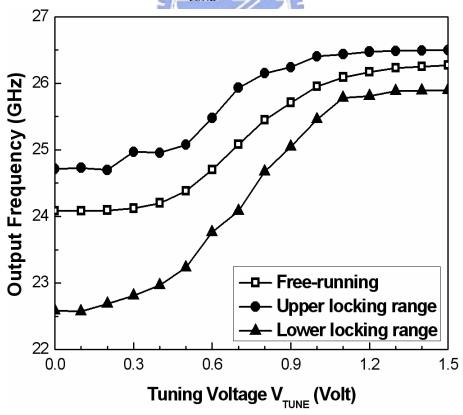

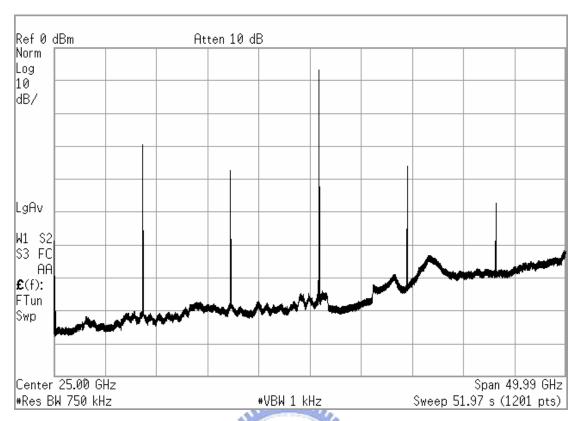

The SPECTRE RF simulated output frequency under locked condition as the varactors tuning voltage V<sub>TUNE</sub> varies from 0 to 1.5 V is shown in Fig. 2.11. Because the quality factor of the varactor decreases as the tuning voltage V<sub>TUNE</sub> decreases, the locking range at lower tuning voltage is larger than that at higher tuning voltage. The output frequency range of the *K*-band ILFT under free-running condition is from 22.98 GHz to 25.39 GHz. With a 4-dBm input signal, the output frequency range of the *K*-band ILFT under locked condition is from 21.54 GHz to 25.71 GHz. Therefore, the output frequency range extends from 2410 MHz to 4170 MHz. The simulated input power versus the output frequency when the input bias V<sub>BIAS</sub> is set at 0.65 V is shown in Fig. 2.12. The upper and lower locking ranges are labeled as the maximum and minimum output frequencies under locked condition, respectively. The locking range is from 30 to 690 MHz while the input power varies from –7 to 4 dBm.

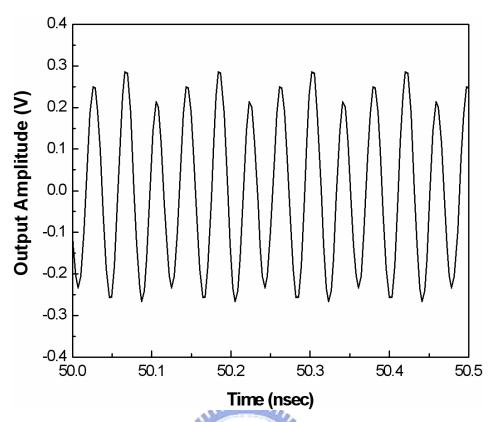

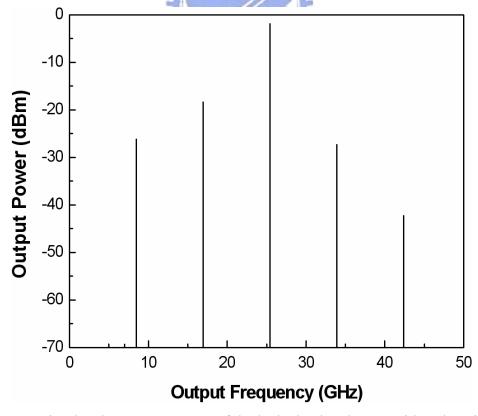

#### **2.2.2.2** *V*-band ILFT