# 國立交通大學

# 理學院應用科技學程 碩士論文

發展奈米探針與被動電壓對比技術 應用到 MOSFET 故障分析

DEVELOPMENT OF NANO PROBING AND PASSIVE

VOLTAGE CONTRAST TECHNIQUES FOR THE FAILURE

ANALYSIS OF MOSFET

研 究 生: 林定弘

指導教授:柯富祥 教授

中華民國九十九年九月

# 發展奈米探針與被動電壓對比技術應用到MOSFET故障分析

#### DEVELOPMENT OF NANO PROBING AND PASSIVE

#### VOLTAGE CONTRAST TECHNIQUES FOR THE FAILURE

#### ANALYSIS OF MOSFET

研究生:林定弘 Student: Ding-Hong Lin

指導教授:柯富祥 Advisor: Fu-Hsiang Ko

國立交通大學

理學院應用科技學程

碩士論文

1896

A Thesis

Submitted to Degree Program of Applied Science and Technology

College of Science

National Chiao Tung University

in partial Fulfillment of the Requirements

for the Degree of

Master

in

Degree Program of Applied Science and Technology

June 2010

Hsinchu, Taiwan

中華民國九十九年九月

發展奈米探針與被動電壓對比技術 應用到 M O S F E T 故障分析

學生: 林定弘 指導教授: 柯富祥 教授

#### 摘要

本文研究奈米探針(Nano probe)與被動電壓對比技術並對MOSFET 之故障分析(failure analysis)進行應用,我們開發一種最適流程去進行奈米定位(localization),並發現某些在奈米級積體電路(IC)中對良率(yield)有影響的微缺陷(defect)。此流程有能力將MOSFET 為結構的故障元件適當隔離(isolation)並且正確測定出。根據研究結果我們瞭解製程中之故障機制(failure mechanism)與產生的原因(root cause)。為了將缺陷視覺化,電晶體級的電性量測結果也提供了後續物性故障分析尋找故障區塊之依據。

關鍵詞:故障分析、奈米探針量測、被動電壓對比。

# DEVELOPMENT OF NANO PROBING AND PASSIVE VOLTAGE CONTRAST TECHNIQUES FOR THE FAILURE ANALYSIS OF MOSFET

Student: Ding-Hong Lin Advisor: Fu-Hsiang Ko

#### **ABSTRACT**

This study pays more attention to understand the reason of defect deterioration on device performance. The state-of-the-art nano probing and passive voltage contrast techniques are established for the failure analysis of MOSFET. We successfully address some of the subtle defects of which seriously influencing the yield of integrated circuits. The developed technique equipped with the nano probing and electrical capability can effectively isolate and characterize the actual site of failed transistors of the malfunctioned devices. As a result, the proposed identification process can identify the failure mechanisms and the root cause. In addition, the electrical characterization at the

transistor level also offers an appropriate solution for the following physical analysis to "visualize" the defects. Our study provides a feasible way for the semiconductor manufacturing to target the unpredictable defect site by means of nano probing and passive voltage contrast techniques in the future.

Keywords: failure analysis, nano probing, passive voltage contrast.

# 誌謝

光陰似箭,三年很快就過去了,我也完成了碩士班的學業 及夢想。在這段日子裡,首當感謝指導教授柯富祥老師於實 驗、研究與論文上給予充分且詳實的指導與教誨鼓勵,老師嚴 謹認真的研究態度、條理分明的思考模式及廣博的知識,令學 生受益匪淺。另外也要感謝小朱學長研究上給我的建議及鼓 勵。

要特別感謝我的太太湘妍,以及我的一對可愛的寶貝詠婕、毅鈞謝謝家人對我的全力支持及默默付出,使我得以全心投入學業,完成碩士學位,感恩。

定弘 謹誌於 交通大學理學院 2010 年 9 月

# **B** 錄

| 中文摘要 |                                           | i    |

|------|-------------------------------------------|------|

| 英文摘要 |                                           | ii   |

| 致謝   |                                           | iv   |

| 目錄   |                                           | V    |

| 表目錄  |                                           | .vii |

| 圖目錄  |                                           | viii |

| 第一章  | 緒論                                        | 1    |

|      | 1-1 前言                                    | 1    |

|      | 1-2 MOSFET 在電子電路上應用的優勢                    | 2    |

|      | 1-3 本文架構 CMOS 的優點                         | 3    |

|      | 1-4 研究背景. ES. C.                          | 4    |

|      | 1-5 研究動機及大綱                               | 6    |

|      | 1-5.1 研究動機                                |      |

|      | 1-5.2 研究大綱                                | 7    |

|      |                                           |      |

| 第二章  | 原理與文獻                                     | .14  |

|      | 2-1 金氧半場效電晶體(MOSFET)簡介                    | 14   |

|      | 2-1.1 MOSFET 的操作原理                        | .15  |

|      | 2-1.2 MOSFET 的結構                          | .16  |

|      | 2-1.3 MOSFET 的操作模式                        | .17  |

|      | 2-2 被動電壓對比(Passive Voltage Contrast, PVC) |      |

|      | 2-2.1 被動電壓對比(PVC)技術原理                     |      |

|      | 2-2.2 被動電壓對比(PVC)技術應用實例                   |      |

|      | 2-3 導電式原子力顯微鏡(Conductive Atomic For       |      |

|      |                                           |      |

|   |    |     | Microscopy, C-AFM)原理與架構       | 23 |

|---|----|-----|-------------------------------|----|

|   |    |     | 2-3.1 機台原理與架構                 | 23 |

|   |    |     | 2-3.2 C-AFM 試片處理方式            | 24 |

|   |    |     | 2-3.3 導電式原子力顯微鏡的應用實例          | 24 |

|   |    |     | 2-4 奈米探針量測(Nano-Probing)原理與應用 | 26 |

|   |    |     | 2-4.1 奈米探針量測原理                | 26 |

|   |    |     | 2-4.2 Nano-probing 的種類        | 27 |

|   |    |     | 2-4.3 Nano-probing 的應用方式      | 29 |

|   |    |     | 2-4.4 Nano-probing 的應用實例      | 29 |

|   |    |     |                               |    |

| 第 | 三  | 章   | 實驗流程設計                        |    |

|   |    |     | 3-1 實驗步驟                      |    |

|   |    |     | 3-2 樣品前置作業   E S              | 46 |

| 第 | 四  | 章   | 實驗結果與討論 1896                  | 52 |

|   |    |     | 4-1 被動電壓對比技術之實驗結果             | 52 |

|   |    |     | 4-2 導電式原子力顯微鏡(CAFM)實驗結果       | 53 |

|   |    |     | 4-3 奈米探針量測的實驗結果               | 55 |

|   |    |     | 4-4 討論                        | 56 |

|   |    |     | 4-4.1 被動電壓對比技術之實驗結果之討論        | 56 |

|   |    |     | 4-4.2 導電式原子力顯微鏡(CAFM)實驗結果討論   | 58 |

|   |    |     | 4-4.3 奈米探針量測的實驗結果討論           | 60 |

| 第 | 五  | 章   | 結論                            | 79 |

| 杂 | 老文 | r 件 |                               | 80 |

# 表目錄

## 第四章

| 表 | 1-1 | 研究動機對照表          | .40 |

|---|-----|------------------|-----|

| 表 | 3-1 | 被動電壓對比技術實驗設計表    | .50 |

| 表 | 3-2 | 導電是原子力顯微鏡量測實驗設計表 | .51 |

| 表 | 3-3 | 奈米探針量測實驗設計表      | .51 |

# 圖目錄

| 第一章                                                              |

|------------------------------------------------------------------|

| 圖 1-1 微處理器之發展與摩爾定律(Moore's Law)之關係                               |

| 圖 1-2 MOSFET 的基本應用8                                              |

| 圖 1-3 與故障分析有關的半導體相關的關係圖                                          |

| 圖 1-4 半導體製造流程10                                                  |

| 圖 1.5 CMOS 示意圖 11                                                |

| 圖 1.6 CMOS 輸入輸出特性曲線11                                            |

| 圖 1-7 半導體之電性與物性故障分析技術分類圖 12                                      |

| 圖 1-8 發展奈米探針與電壓對比技術應用於 MOSFET 的故障分析                              |

| 流程圖                                                              |

| 第二章                                                              |

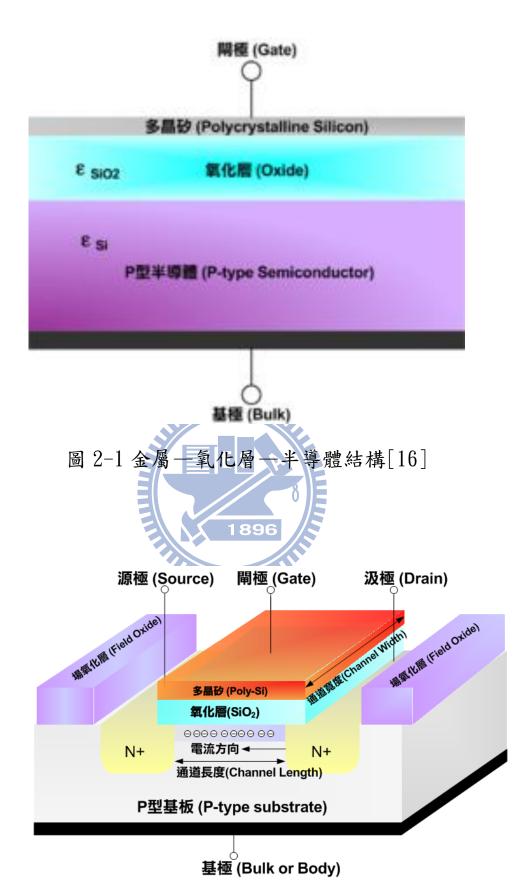

| 圖 2-1 金屬—氧化層—半導體結構應31                                            |

| 圖 2-2 NMOS 電晶體的立體截面圖31                                           |

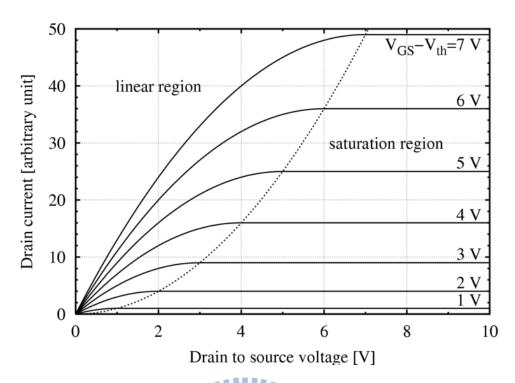

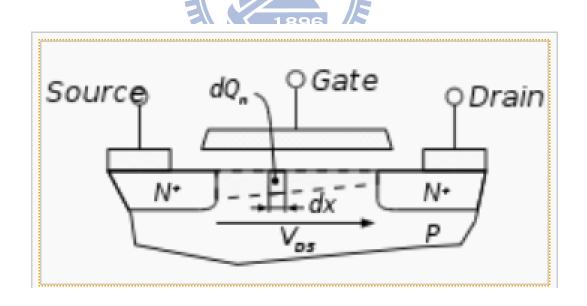

| 圖 2-3 NMOS 的汲極電流與汲極電壓之間在不同 $V_{gs}$ - $V_{th}$ 的關係32             |

| 圖 2-4 MOSFET 在線性區操作的截面圖32                                        |

| 圖 2-5 MOSFET 在飽和區操作的截面圖33                                        |

| 圖 2-6 電壓對比機制的示意圖33                                               |

| 圖 2-7 為接觸窗(Contact)層 N <sup>+</sup> /P-Well 的佈局圖與 1 keV PVC 影像34 |

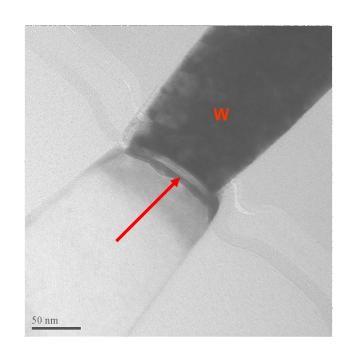

| 圖 | 2-8  | TEM 觀察到 W spike                                          | 34 |

|---|------|----------------------------------------------------------|----|

| 圖 | 2-9  | 調高加速電壓可觀察底層的層次,用來保護現場方便真因判斷                              | 35 |

| 圖 | 2-10 | 為金屬層(Metal layer)的佈局圖                                    | 35 |

| 圖 | 2-11 | SEM High keV PVC 影像                                      | 36 |

| 圖 | 2-12 | TEM 觀察發現是接觸窗開路(contact open)                             | 36 |

| 圖 | 2-13 | C-AFM 的架構示意圖                                             | 37 |

| 圖 | 2-14 | N <sup>+</sup> contact bias +1V current map 影像           | 37 |

|   |      | 相同試片的(-1V) P+ contact 之 C-AFM current mapping 影像         |    |

|   |      | 異常 SRAM contact 之 layout                                 |    |

| 圖 | 2-17 | 異常 contact 之 1-V curve                                   | 39 |

| 圖 | 2-18 | TEM 顯示 contact 與 poly 有短路(short)現象                       | 39 |

| 圖 | 2-19 | 圖中黯淡之黃點為異常 contact 所在                                    | 40 |

| 圖 | 2-20 | 異常的 N <sup>+</sup> diffusion contact 的 I-V curve         | 40 |

| 邑 | 2-21 | TEM 顯示 Contact 與 salicide 之間有異常之界面                       | 41 |

| 圖 | 2-22 | 架設在 SEM 裡的模組,可安裝四至六個探針                                   | 41 |

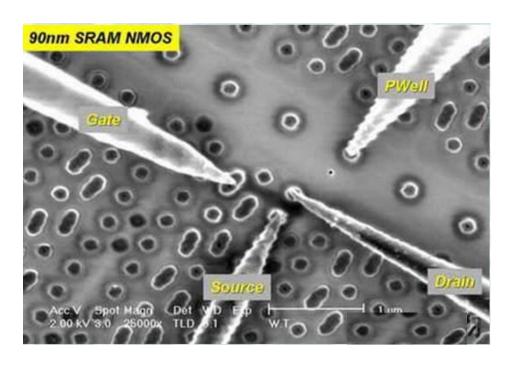

| 圖 | 2-23 | 90-nm SRAM 點針情形                                          | 42 |

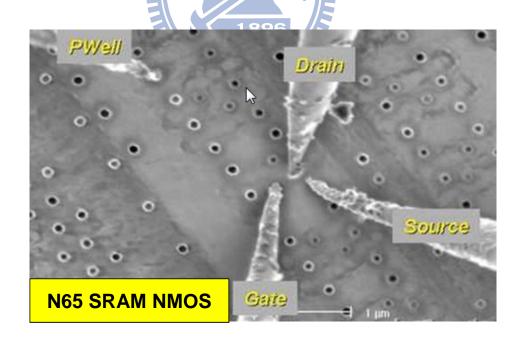

| 圖 | 2-24 | 65-nm SRAM 點針情形                                          | 42 |

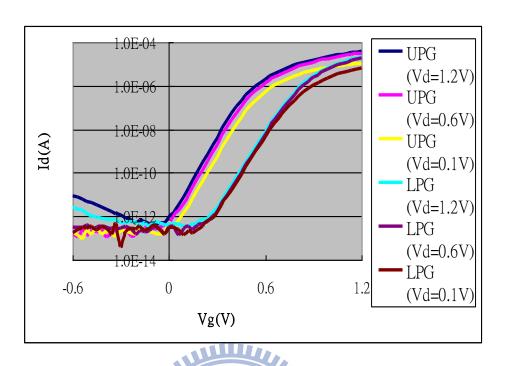

| 圖 | 2-25 | Nano-probing 可量測元件的 I <sub>d</sub> -V <sub>g</sub> 特性曲線圖 | 43 |

| 圖 | 2-26 | Nano-probing 可量測元件的 la-Va 特性曲線圖                          | 43 |

| 圖 2-2 | 27 Nano-probing 可量測元件的電流組合             | 44 |

|-------|----------------------------------------|----|

| 圖 2-2 | 28 SEM Internal Probing 架針             | 44 |

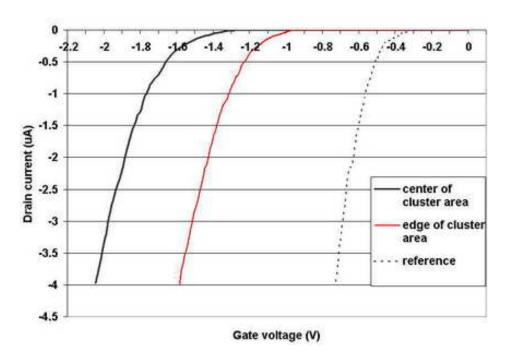

| 圖 2-2 | 29 好壞元件的比較證明異常 cell 有較低的飽和電流           | 45 |

| 圖 2-3 | 30 TEM 確認是 S/D 的離子佈植異常所致               | 45 |

| 第三章   | <del>7.</del>                          |    |

| 圖 3-1 | 實驗組的晶圓二位碼分類圖(wafer map)                | 49 |

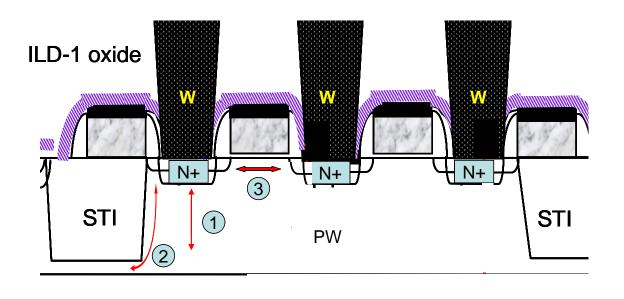

| 圖 3-2 | 2 為本實驗觀察與量測 MOSFET 的示意圖                | 49 |

| 圖 3-3 | 3 立體截面圖                                | 50 |

| 第四章   | 1896                                   |    |

| 圖 4-1 | 實驗組的 1keV 的 PVC 影像                     | 65 |

| 圖 4-2 | 2 對照組的 1keV 的 PVC 影像                   | 65 |

| 圖 4-3 | 3 實驗組的 30keV 的 PVC 影像                  | 66 |

| 圖 4-4 | I Low keV 的 PVC 示意圖                    | 66 |

| 圖 4-5 | 5 編號 1 的 contact 之 PN 接面電流(I)-電壓(V)曲線圖 | 67 |

| 圖 4-6 | 6 編號 2 的 contact 之 PN 接面電流(I)-電壓(V)曲線圖 | 67 |

| 圖 4-7 | 7 編號 3 的 contact 之 PN 接面電流(I)-電壓(V)曲線圖 | 68 |

| 圖 4-8 | 3 編號 4 的 contact 之 PN 接面電流(I)-電壓(V)曲線圖 | 68 |

| 圖 4-9 | 9 編號 5 的 contact 之 PN 接面電流(I)-電壓(V)曲線圖 | 69 |

| 昌 | 4-10 | TEM 示意圖, X-TEM 表示 TEM 取樣的位置69                     | 9 |

|---|------|---------------------------------------------------|---|

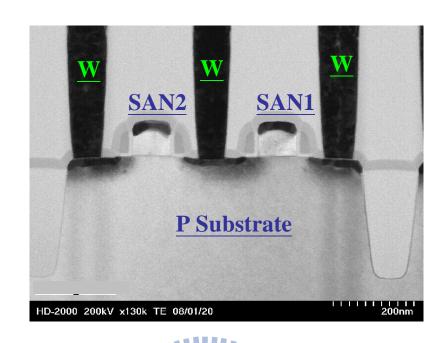

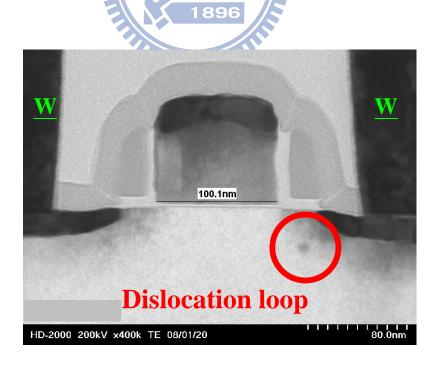

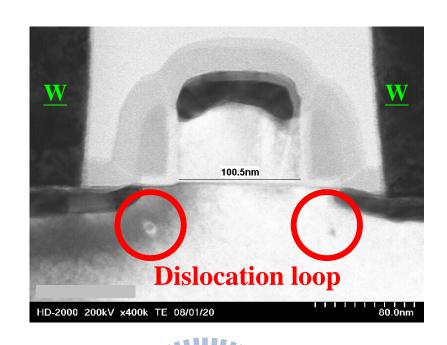

| 圖 | 4-11 | 實驗組 SAN1 與 SAN2 之 TEM 影像70                        | 0 |

| 圖 | 4-12 | 實驗組 SAN1 TEM 放大圖,紅圈指出 Dislocation defect70        | 0 |

| 圖 | 4-13 | 實驗組 SAN1 TEM 放大圖,紅圈指出 Dislocation defect7         | 1 |

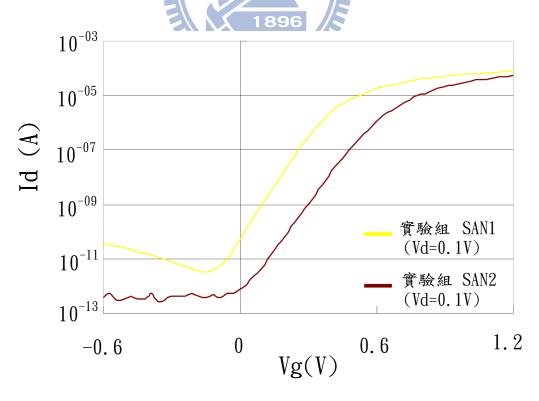

| 圖 | 4-14 | 實驗組 SAN1/SAN2,Vd=0.1V 轉移特性曲線比較圖7                  | 1 |

| 圖 | 4-15 | 對照組 SAN1/SAN2,Vd=0.1V 轉移特性曲線比較圖72                 | 2 |

| 圖 | 4-16 | 實驗組 SAN1/SAN2,Vd=1.2V 轉移特性曲線比較圖72                 | 2 |

| 圖 | 4-17 | 對照組 SAN1/SAN2,Vd=1.2V 轉移特性曲線比較圖7                  | 3 |

| 圖 | 4-18 | SEM 在不同低/高加速電壓下(1keV)/(30keV),電子東穿透鎢(W) 深度與寬度的示意圖 | 4 |

| 圖 | 4-19 | 深度與寬度的示意圖       74         MOSFET 主要漏電途徑          | 4 |

|   |      | 實驗後而且製程經過改善之後的晶圓測試二位碼分類圖7                         |   |

| 圖 | 4-21 | 功能正常晶粒的 TEM 影像75                                  | 5 |

| 圖 | 4-22 | 顯示 DRAM 胞(Cell)與其資料讀寫相關之電路圖70                     | 6 |

| 圖 | 4-23 | 本實驗觀察與量測 MOSFET 的示意圖70                            | 6 |

| 圖 | 4-24 | 顯示 DRAM 胞運作時的波形(waveform)7                        | 7 |

| 圖 | 4-25 | 整體實驗步驟之流圖                                         | 8 |

# 第一章 緒論

#### 1-1 前言

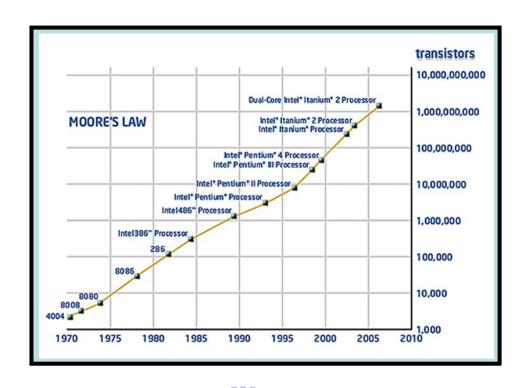

台灣經過近三十多年來的努力,在全球半導體產業及IT產業鏈中,佔有關鍵性的地位,晶圓代工及後段封測產值,均位居全球第一。圖 1-1 所示為摩爾定律(Moore's Law)每十八個月矽晶板上積體電路的密度會增加一倍,確立了積體電路設計製造的複雜度呈現定期級數成長的時代走向,也造就許多製造及設計的困難度[1]。

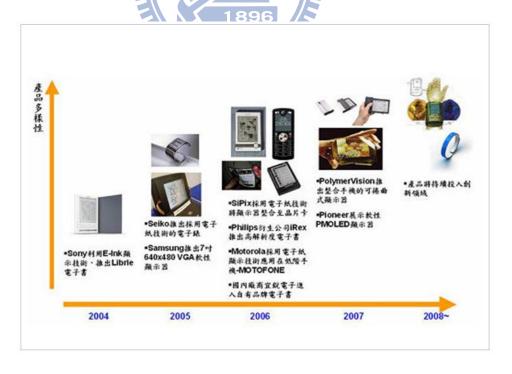

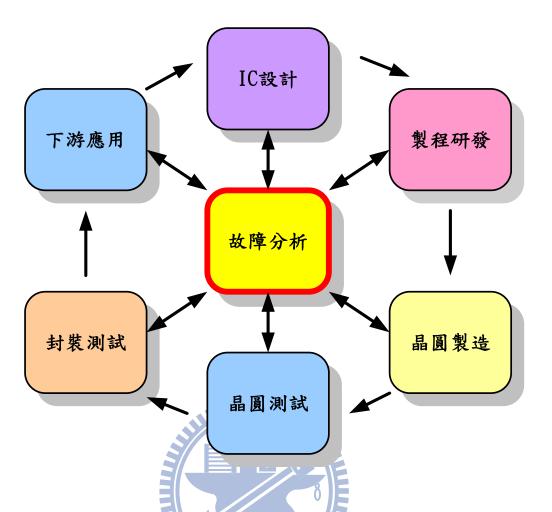

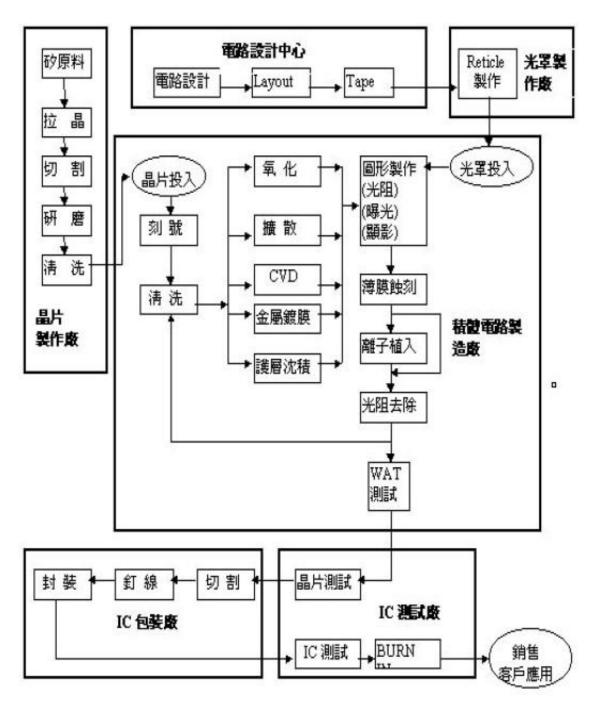

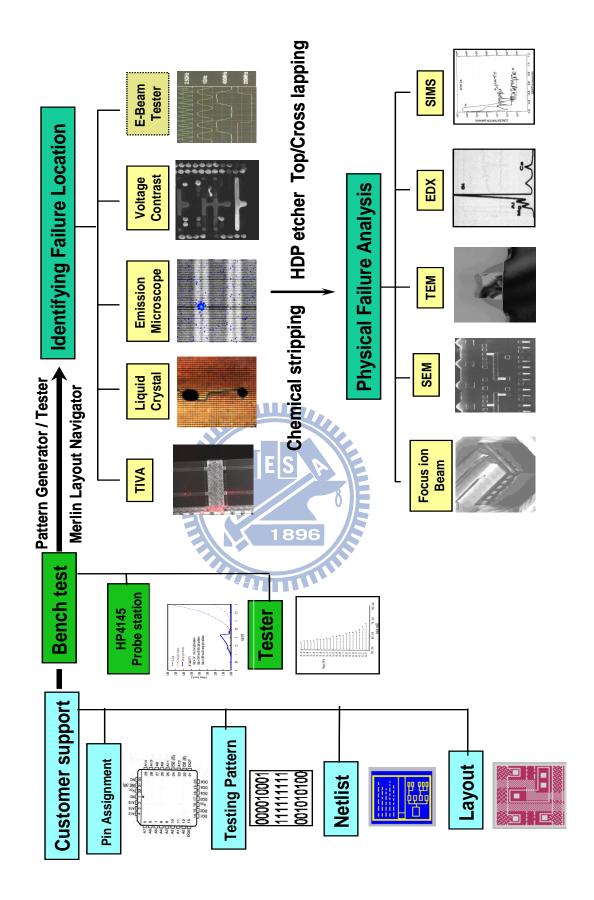

而目前業界已由 110 奈米、90 奈米製程持續發展至 65 奈米、45 奈米,甚至最新報導晶圓代工龍頭台積電已經朝向 20 奈米製程發展。當製程技術不斷地進步,如圖 1-3 所示為與故障分析有關的半導體相關的關係圖,不論是 IC 設計、製程研發、晶圓製造、晶圓測試、封裝測試,還是可靠度分析等等半導體垂直分工細緻的產業如圖 1-4,都需要半導體故障分析(Failure Analysis, FA)的支援與協助,以釐清故障問題之所在,並且針對問題,擬定實驗及對策,以期改善。目前全世界的各大晶圓廠內也都設有故障分析部門來提升產品品質與良率,增加公司與產品的競爭力。

# 1-2 MOSFET 在電子電路上應用的優勢[15]

MOSFET 在 1960 年由貝爾實驗室 (Bell Lab.) 的 D. Kahng 和 Martin Atalla 首次實作成功,這種元件的操作原理和 1947 年蕭克利 (William Shockley)等人發明的雙載子接面電晶體 (Bipolar Junction Transistor, BJT) 截然不同,且因為製造成本低廉與使用面積較小、高整合度的優勢,在大型積體電路 (Large-Scale Integrated Circuits, LSI)或是超大型積體電路 (Very Large-Scale Integrated Circuits, VLSI) 的領域裡,重要性遠超過 BJT。

近年來由於 MOSFET 元件的性能逐漸提升,除了傳統上應用

於諸如微處理器、微控制器等數位訊號處理的場合上,也有越來越多類比訊號處理的積體電路 可以用 MOSFET 來實現,以下分別介紹這些應用。

### 1-3 CMOS 的優點[16]

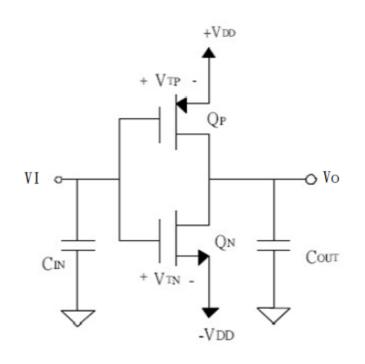

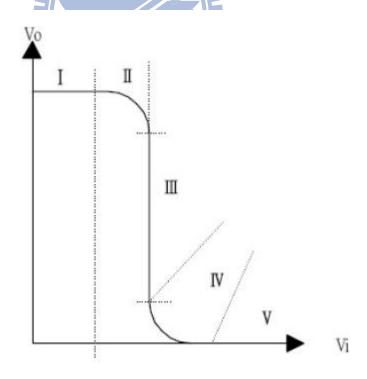

性氧化金屬半導 體 互 ( Complementary Metal-Oxide-Semiconductor, CMOS) 是一種積體電路型態,它是 利用 NMOS 及 PMOS 在電路中電壓極性對電流導通的互補特性來 設計電路圖 1-5,其輸入輸出特性曲線圖 1-6 共分為五區。第一區 是當 VI < VTN 時, VO = VDD,此時 QN 在截止區, QP 在三極 體區 (圖 1-6 的 I 部分)。第二區是當 VI>VTN 時,此時曲線是 二次曲線, QN 在飽和區, QP 在三極體區(圖 1-6 的Ⅱ部分)。 第三區時(圖 1-6 的Ⅲ部分) QN 和 QP 均在飽和區,第四區是當 VI>VDD/2 時, QN 在三極體區, QP 在飽和區,此時曲線也是 二次曲,(圖 1-6 的IV部分)。第五區是當 VI>(VDD-Vt)時, VO = 0,此時 QN 在三極體區, QP 在截止區(圖 1-6 的 V 部分)。 這樣的工作特性使得電路在導通與截止之間更為省電,而且有著 較高的抗雜訊能力,目前常看到的微處理器(microprocessor),微控 制器 (microcontroller), 靜態隨機存取記憶體 (SRAM) 與其他數 位邏輯電路,大多是利用 CMOS 所製作,因為只有在電晶體需要切換開啟關閉時才需耗能的優點,因此非常省電且發熱少,可大大提升產品的續航能力,也因此 COMS 技術大量被運用在ULSI(Ultra Large Scale Integration)的製造。由於現在的半導體製程相當進步,通道長度 65nm 的製程已經大量量產,也因為尺寸越做越小,所以可以將更多的邏輯電路整合進更小的晶片裡,使得晶片功能更加強大更加完善。

#### 1-4 研究背景

當積體電路產業步入奈米技術範疇以下,相關的分析量測技術亦面臨了前所未有的極限,由於積體電路(IC)製程技術不斷的微縮,故障缺陷變得越來越小,也越來越難被發現及觀察到,這些不可見的缺陷一直增加,也使得良率不斷地下降。甚至有些所謂的軟性故障(soft fail)的問題,長期下來也會影響到元件的可靠性品質。一個優良且嚴格的晶圓廠所生產製造出來元件必定是經過優越的製程控制過程,這個控制過程是元件良率與品質的保證,因為一個非常微小的製程變動會造成 MOSFET 電性參數的偏移,就造成元件的故障,而為了捕捉到這個細微的 MOSFET 電性參數的偏移,就需要電性故障分析的技術來幫忙解決問題[2]。傳統的電

性故障分析手法過度倚賴所謂的被動電壓對比(Passive Voltage Contrast, PVC)的方式來確認故障點位置。但是在 100nm 以下,這些技術已經無法長期滿足這些先進製程技術了。

目前,在故障點的故障機制判斷上遇到了瓶頸,必須發展新的故障分析流程,將傳統的故障分析流程中,無法將缺陷視覺化的缺點,導向為可視覺化的方向,也就是將故障區域的故障機制用更詳盡的電性故障分析來完成它。此外,半導體故障分析時,常因為無法得到足夠且有效技術支援的情形下,產生故障真因的誤判,導致晶圓廠的良率無法有效提升和改善,浪費時間與成本,因此,如何改善以上所述的情況就顯得急需且更為重要了。

圖 1-7 為半導體之電性與物性故障分析技術分類圖,一般來說,目前半導體故障分析系統(Failure Analysis System, FA)之主要技術可分為下列幾種:(1)電性故障分析技術(Electrical Failure Analysis, EFA),(2)物性故障分析技術(Physical Failure Analysis, PFA),這些是傳統的故障分析技術流程的分類。電性故障分析技術與物性故障分析技術之間,還有所謂的確認故障點位置的步驟。本論文是著重在於確認故障點位置之後,電性分析流程的發展與說明。同時也會應用到穿透式電子顯微鏡(Transmission Electron Microscopy, TEM)。[3][4]

#### 1-5 研究動機及大綱

#### 1-5.1 研究動機

藉由關於 65 奈米製程的動態隨機存取記憶體(Dynamic Random-Access-Memory, DRAM),經過測試過程研判為位元線 (Bit Line)故障的實驗中,說明如何將發展奈米探針與電壓對比技術應用於 MOSFET 的故障分析,可以將不可見的元件故障缺陷成為可視覺化,將晶圓製造良率遲遲無法提升的問題,提供正確的故障真因,解決問題。

發展奈米探針與被動電壓對比技術當中整合有

- (一) 導電式原子力顯微鏡(Conductive Atomic Force Microscopy, CAFM)。

- (二) 奈米探針量測(Nano probing)。

- (三)被動電壓對比技術(Passive Voltage Contrast, PVC)。

在傳統的手法上加上新的元素,就可以在區隔與檢測故障點的故障分析方法上,建立新的階段。而就在許多有關 MOSFET 的故障分析報告中,大多只是說明使用何種儀器設備發現何種缺陷,只流於單一說明,今天這個研究發展,就是整合並且介紹此新穎的流程分析步驟。如表 1-1

本文的目的是希望提高以 MOSFET 為電子元件之主要結構的 故障分析流程可以藉由有效的技術發展流程,可以在故障點定位 完成之後,應用此流程 圖 1-8,提升觀察到故障點的真正成因的 機會,並提高故障分析命中率的能力。

#### 1-5.2 研究大綱

#### 本論文的大綱如下:

- 一、第一章簡介 MOSFET 元件的研究背景,包含了 MOSFET 的發展與應用介紹以及近況,並闡述研究動機與目的。

- 二、第二章說明 MOSFET 的操作原理、結構、操作模式,被 1896 動電壓對比、導電式原子力顯微鏡、奈米探針量測的原 理與應用。

- 三、 第三章介紹在本論文實驗流程設計。

- 四、第四章為實驗結果與討論分析。

- 五、 第五章為結論。

圖 1-1 微處理器之發展與摩爾定律(Moore's Law)之關係 資料來源:http://www.intel.com/technology/mooreslaw

圖 1-2 MOSFET 的基本應用

資料來源:工研院 IEK(2007/06)

圖 1-3 與故障分析有關的半導體相關的關係圖

圖 1-4 半導體製造流程 資料來源:半導體學院

圖 1-5 CMOS 示意圖

資料來源:新電子雜誌 2001,8 月號 第 185 期

圖1-6 CMOS 輸入輸出特性曲線

資料來源:新電子雜誌 2001,8 月號 第 185 期

圖 1-7 半導體之電性與物性故障分析技術分類圖

圖 1-8 發展奈米探針與電壓對比技術應用於 MOSFET 的故障分析流程圖

表 1-1 研究動機對照表

#### 傳統故障分析手法 發展最適故障分析流程

- (一)被動電壓對比(Passive Voltage Contrast, PVC) (二)研磨去層次(delayer)的方 式來判斷故障點。

- (一) 導電式原子力顯微鏡 (Conductive Atomic Force Microscopy, CAFM) •

- (二) 奈米探針量測(Nano probing) •

- (三)被動電壓對比技術( Passive Voltage Contrast, PVC) •

由於積體電路(IC)製程技術 不斷的微縮,故障缺陷變得越來 可以在故障點定位完成之後,應 越小,也越來越難被發現及觀察 用此流程,提升觀察到故障點 到,這些不可見的缺陷一直增加的機會,並提高故障分析命中率 有些所謂的軟性故障(soft fail)的 障缺陷成為可視覺化,將晶圓製 問題,長期下來也會影響到元件 造良率遲遲無法提升的問題,提 的可靠性品質。

藉由有效的技術發展流程, ,也使得良率不斷地下降。甚至 的能力。可以將不可見的元件故 供正確的故障真因,解決問題。

# 第二章 原理與文獻

#### 2-1 金氧半場效電晶體(MOSFET)簡介[14]

金屬氧化物半導體場效電晶體,簡稱金氧半場效電晶體 (Metal-Oxide-Semiconductor Field-Effect Transistor, MOSFET)是一種可以廣泛使用在模擬電路與數位電路的場效電晶體 (field-effect transistor)。MOSFET 依照其「通道」的極性不同,可分為 n-type 與 p-type 的 MOSFET,通常又稱為 NMOSFET 與 PMOSFET。

MOSFET 裡的氧化層位於其通道上方,依照其操作電壓的不同,這層氧化物的厚度僅有數十至數百埃 (Å) 不等,通常材料是二氧化矽  $(silicon\ dioxide,\ SiO_2)$ ,不過有些新的進階製程已經可以使用如氮氧化矽  $(silicon\ oxynitride,\ SiON)$  做為氧化層之用。

當一個夠大的電位差施於 MOSFET 閘極(gate)與源極(source) 之間時,電場會在氧化層下方的半導體表面形成感應電荷,而這 時所謂的「反轉通道」(inversion channel)就會形成。通道的極性 與其汲極(drain)與源極相同,假設汲極和源極是 n-type,那麼 通道也會是 n-type。通道形成 後,MOSFET 即可讓電流通過,而 依據施於閘極的電壓值不同,可由 MOSFET 的通道流過的電流大 小亦會受其控制而改變。

#### 2-1.1 MOSFET 的操作原理

MOSFET 在結構上以一個金屬(Metal)—氧化層(Oxide)—半導體(Semiconductor)的電容為核心,氧化層的材料多半是二氧化矽,其下是作為基極的矽,而其上則是作為閘極的多晶矽。這樣子的結構正好等於一個電容器(capacitor),氧化層扮演電容器中介電質(dielectric material)的角色,而電容值由氧化層的厚度與二氧化矽的介電常數(dielectric constant)來決定。閘極多晶矽與基極(base)的矽則成為 MOS 電容的兩個端點。

當一個電壓施加在 MOS 電容的兩端時,半導體的電荷分佈也會跟著改變。考慮一個 p-type 的半導體(電洞濃度為 NA)形成的 MOS 電容,當一個正的電壓 VGB 施 加在閘極與基極端如圖 2-1時,電洞的濃度會減少,電子的濃度會增加。當 VGB 夠強時,接近閘極端的電子濃度會超過 電洞。這個在 p-type 半導體中,電子濃度(帶負電荷)超過電洞(帶正電荷)濃度的區域,便是所謂的反轉層(inversion layer)。

MOS 電容的特性決定了 MOSFET 的操作特性,但是一個完整的 MOSFET 結構還需要一個提供多數載子(majority carrier)的源極以及接受這些多數載子的汲極。

#### 2-1.2 MOSFET 的結構

圖 2-2 是一個 n-type MOSFET (以下簡稱 NMOS)的截面圖。如前所述,MOSFET 的核心是位於中央的 MOS 電容,而左右兩側則是它的源極與汲極。源極與汲極的特性必須 同為 n-type (即 NMOS)或是同為 p-type (即 PMOS)。圖 2-2 NMOS 的源極與汲極上標示的「N+」代表著兩個意義:(1)N 代表摻雜 (doped) 在源極與汲極區域的雜質極性為 N;(2)「+」代表這個區域為高摻雜濃度區域(heavily doped region),也就是此區的電子濃度遠高於其他區域。在源極與汲極之間被一個極性相反的區域隔開,也就是所謂的基極(或稱基體)區域(substrate)。如果是 NMOS,那麼其基體區的摻雜就是 p-type。基體的摻雜濃度不需要如源極或汲極那麼高,故在圖 2-2 中沒有「+」。

對這個 NMOS 而言,真正用來作為通道、讓載子通過的只有 MOS 電容正下方半導體的表面區域。當一個正電壓施加在閘極上,帶負電的電子就會被吸引至表面,形成通道,讓 n-type 半導體的多數載子—電子可以從源極流向汲極。如果這個電壓被移除,或是放上一個負電壓,那麼通道就無法形成,載子也無法在 源極與汲極之間流動。

假設操作的對象換成 PMOS,那麼源極與汲極為 p-type、基體則是 n-type。在 PMOS 的閘極上施加負電壓,則半導體上的電洞會被吸引到表面形成通道,半導體的多數載子—電洞則可以從源極流向汲極。假設這個負電壓被移除,或是加上正電壓,那麼通道無法形成,無法讓載子在源極和汲極間流動。

特別要說明的是,源極在 MOSFET 裡的意思是「提供多數載子的來源」。對 NMOS 而言,多數載子是電子;對 PMOS 而言,多數載子就是電洞。相對的,汲極就是接受多數載子的端點。

# 2-1.3 MOSFET 的操作模式

1896

依照在 MOSFET 的閘極、源極、與汲極等三個端點施加的「偏壓」(bias)不同,一個常見的加強型 (enhancement mode) n-type MOSFET 有下列三種操作區間如圖 2-3,2-4,2-5:

1. 線性區(三極區)(linear or triode region)

當  $V_{GS}$ > $V_{th}$ 、且  $V_{DS}$ < $V_{GS}$ - $V_{th}$ , 此處  $V_{DS}$ 為 NMOS 汲極至源極的電壓,則這顆 NMOS 為導通的狀況,在氧化層下方的通道也已形成。 此時這顆 NMOS 的行為類似一個壓控電阻(voltage-controlled resistor),而由汲極流出的電流大小為:

$$I_D = \mu_n C_{ox} \frac{W}{L} \left( (V_{GS} - V_{th}) V_{DS} - \frac{V_{DS}^2}{2} \right)$$

μn 是載子遷移率 (carrier mobility)、W 是 MOSFET 的閘極寬度、L 是 MOSFET 的閘極長度,而 C<sub>ox</sub> 則 是閘極氧化層的單位電容大小。在這個區域內,MOSFET 的電流—電壓關係有如一個線性方程式,因而稱為線性區如圖 2-3。

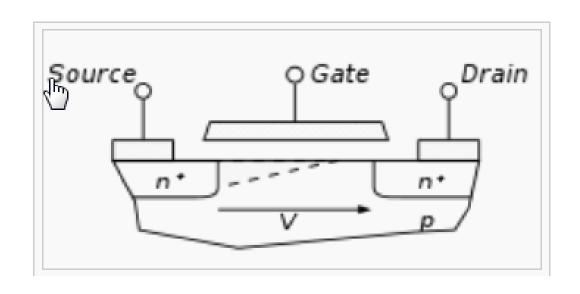

#### 2. 飽和區 (saturation region)

當 V<sub>GS</sub>>V<sub>th</sub>、且 V<sub>DS</sub>>V<sub>GS</sub>-V<sub>th</sub>,這類 MOSFET 為導通的狀況, 也形成了通道讓電流通過。但是隨著汲極電壓增加,超過閘極電 壓時,會使得接近汲極區的反轉層電荷為零,此處的通道消失如, 這種狀況稱之為「夾止」(pinch-off)。在這種狀況下,由源極出發 的載子經由通道到達夾止點時,會被注入汲極周圍的空間電荷區 (space charge region),再被電場掃入汲極。此時通過 MOSFET 的電流與其汲極—源極間的電壓且 V<sub>DS</sub> 無關,只與閘極電壓有 關,關係式如下:

$$I_D = \frac{\mu_n C_{ox}}{2} \frac{W}{L} (V_{GS} - V_{th})^2$$

#### 3. 截止區 (次臨界區) (cut-off or sub-threshold region)

當閘極和源極之間的電壓  $V_{GS}(G$  代表閘極,S 代表源極)小於一個稱為臨界電壓(threshold voltage, Vth) 的值時,這個 MOSFET 是處在「截止」(cut-off)的狀態,電流無法流過這個 MOSFET,也就是這個 MOSFET 不導通。

但事實上當  $V_{GS} < V_{th}$ 、MOSFET 無電流通過的敘述和現 實有些微小的差異。雖然當  $V_{GS} < V_{th}$  的狀 況下,MOSFET 的通道沒有形成,但仍然有些具有較高能量的載子可以從半導體表面流至汲極。而若是  $V_{GS}$  略高於 0,但小於  $V_{th}$  的情況下,還會有一個稱為「弱反轉層」(weak inversion layer)的區域在半導體表面出現,讓更多載子流過。透過弱反轉而從源極流至汲極的載子數量與  $V_{GS}$  的大小之間呈 指數的關係,此電流又稱為次臨界電流(subthreshold current)。

在一些擁有大量 MOSFET 的積體電路產品,如 DRAM,次臨 限電流往往會造成額外的能量或功率消耗。 2-2 被動電壓對比(Passive Voltage Contrast, PVC)

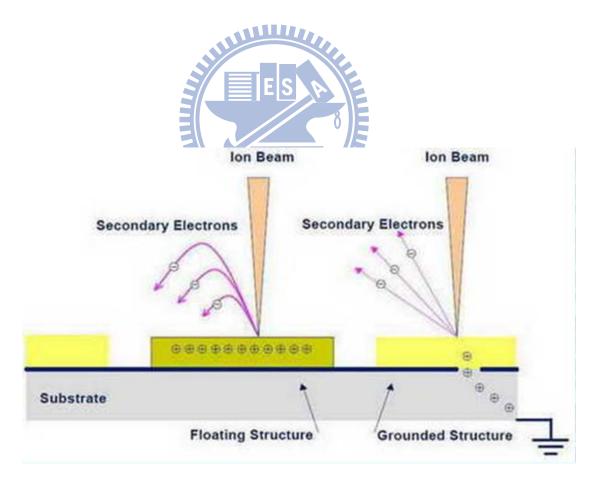

#### 2-2.1 被動電壓對比(PVC)技術原理

被動電壓對比技術(passive voltage contrast, PVC)[5][6]對於半 導體故障分析領域來說是非常重要且基礎的技術,通常應用在確 認故障位置上,有初步的功用。被動電壓對比在不外加偏壓的情 況下,以電子束(electron beam)或離子束(ion beam)打在試片上,此 時試片各區域所被激發出來的二次電子數量的多寡決定了試片影 像的明亮度,而二次電子數量的多寡則取決於試片本身有無路徑 導通,或試片本身有無堆積電荷,這樣的技巧便稱為被動式電壓 對比(Passive Voltage Contrast, PVC) 圖 2-6 ,以在 FIB 下的 VC 為 例,FIB 成像的來源為離子束,是一正電荷,若觀察點為浮接狀態, 則正電荷累積在觀察點內,造成被激發出的、帶有負電荷的二次 電子因為正負相吸而偏離了原有正常的路線,因而影響了偵測器 的偵測量,自然此觀察點就會呈現暗的對比,相反的,觀察點若 是導通或有漏電路徑,則此觀察點的淨電荷不再是正的,則呈現 亮的對比。原則上,該暗未暗,則是有漏電狀況,該亮未亮,則 是有 open 情形。

至於在 SEM 下的 PVC 也是相同的原理,不過成像來源為電

子束,而且情況變得稍微複雜一點。為避免電子束損壞試片,造成誤判的情形,使用的加速電壓會比正常操作來得低,比如 lkeV,但試片本身就會積聚一些正電荷,此時低能量的電子束仍無法有效地中和浮接 layer 內的正電荷,也就是淨電荷仍是正的,所以浮接的 layer 會在 SEM 內呈現暗的對比,如果觀察的 layer 是導通的,則淨電荷為負的,則有明亮的影像。

但如果加速電壓稍微高一點,比如 2 keV 或 5 keV,則變成相反的情況,此時電子東已經有效地中和浮接 layer 內的正電荷,即淨電荷是負的,所以浮接 layer 反而是亮的,而有導通路徑的 layer 因為淨電荷仍是正的,故呈現的卻是暗色的。以上 SEM VC 的判斷為大體上的分辨方式,但觀察點的明暗仍需看 SEM 的機型、觀察層次上是否還有 oxide 殘留、加速電壓的大小以及電子東電流的大小而定,不管這些條件如何,在 SEM 內判斷 VC 明暗的最佳方式就是比較觀察點周遭確定為正常的 layer,如果同為明亮或同為暗的,則觀察點判定為未發現到異常,如果一明一暗,則觀察點判定為異常,並開始後續的試片處理。

#### 2-2.2 被動電壓對比(PVC)技術應用實例

在 SEM 常利用 PVC 觀察的 MOSFET 元件是否有開路

(Open)、短路(Short)、漏電(Leakage)或是高阻值(high Rc)的故障問題。接下來就將上述之故障實例做說明。

#### 1. 漏電(Leakage)觀察

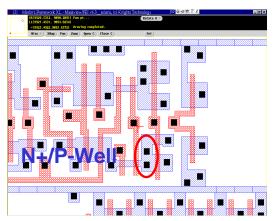

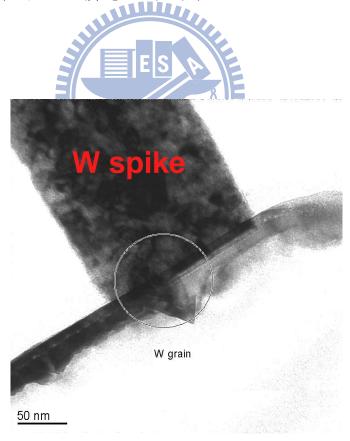

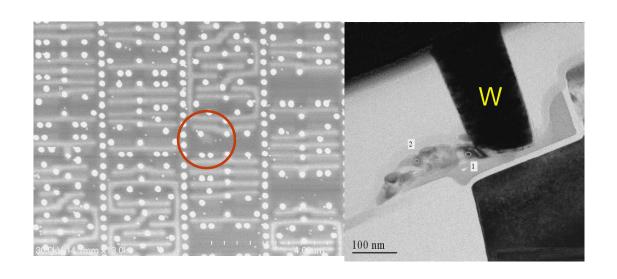

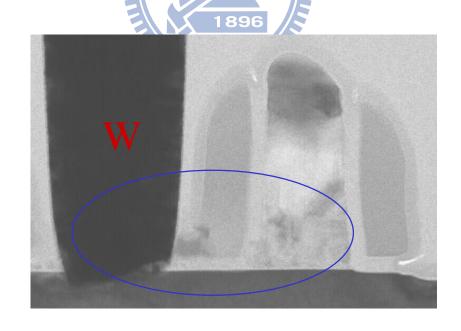

圖 2-7 為接觸窗(Contact)層 N+/P-Well 的佈局圖(layout)與 1 keV PVC 影像,圖中下方的 contact 正常應該是呈現暗的為對比,而在觀察後卻發現呈現亮的對比,表示這個 contact 應該有漏電的路徑,圖 2-8 TEM 觀察發現是鎢突出(tungsten spike)。

## 2 高壓(High KV)觀察

有些 SEM 機台並未附有背向散射電子偵測器,因此無法用此功能來觀察較深層的 layer,雖然無法像背向散射電子影像那麼的清楚確定,但我們可以提高加速電壓來彌補這項不足。圖 2-8 左圖是把加速電壓從一般的 1 keV 提升至 30 keV 所觀察到的 contact PVC 影像,試片本身處理到 contact,透過高壓 30 keV,可以稍微看到隱藏在 contact 底下的模糊影子,更加確認 contact 有異常,圖 2-9 右圖則是經由 TEM 確認為 contact open。

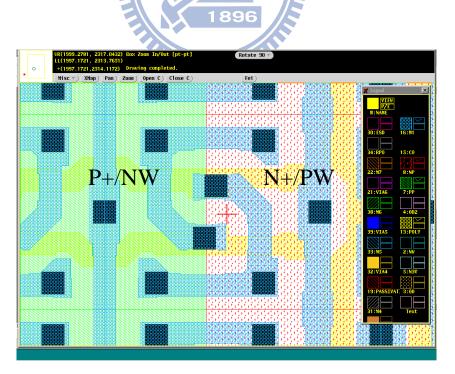

### 3 開路(Open)觀察

圖 2-10 為金屬層(Metal layer)的佈局圖(layout)與(圖 2-11) high keV PVC 影像,圖中央的金屬層正常應該是呈現暗的為對比,而在觀察後卻發現呈現亮的對比,表示這個金屬層以下的電路應該有開路(open)的可能,圖 2-12 TEM 觀察發現是接觸窗開路(contact open)。

- 2-3 導電式原子力顯微鏡(Conductive Atomic Force Microscopy, C-AFM)原理與架構

- 2-3.1 機台原理與架構

1896

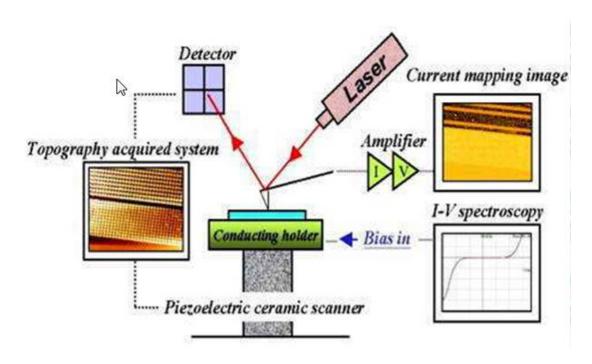

C-AFM 是 SPM 的一種,也就是利用探針量取試片表面的性質。如(圖 2-13)[10],試片放置於基座之上,基座本身是接地或給予一定電壓,C-AFM 用一探針直接接觸試片表面,而探針也給予一定電壓或接地,並量取探針掃過表面的任何一點的電流值,就像一般的電性量測儀器一樣。其電流解析度可低到 60fA[11],試片上每點的電流值量出之後,依照各點電流大小,會依顏色深淺標示在各點上,就可得出試片表面的電流分布圖(current mapping),對照電路佈局圖或正常試片的掃描結果,如此我們就可

以知道試片上的哪一點可能會有漏電或高阻值。

在確定某一點有異常之後,我們也可以把探針移至此點做 IV 曲線的量測,以確認此點電流異常是否為真,並確定電性故障的機制,以推敲出此點的缺陷型態為何,方便決定之後的試片處理方式[12]。

當然量取電流值之外,試片表面起伏的偵測,也就是 AFM 影像,也是必備的功能,試片的 AFM 影像與電流分布圖的比對讓操作者可確知所掃描區域是否為觀測目標。

# 2-3.2 C-AFM 試片處理方式

1896

C-AFM 觀察結果已可概知試片的觀察方向可以是俯視,也可以是橫切面的檢視方式,端看可能的缺陷型態而定,在俯視觀察方面,試片需研磨至接觸洞孔(via)或接觸窗(contact)裸露出來,即可進行觀察,而橫切面的試片則需 FIB 蝕刻或手動研磨。

2-3.3 導電式原子力顯微鏡(Conductive Atomic Force Microscopy, CAFM)的應用實例

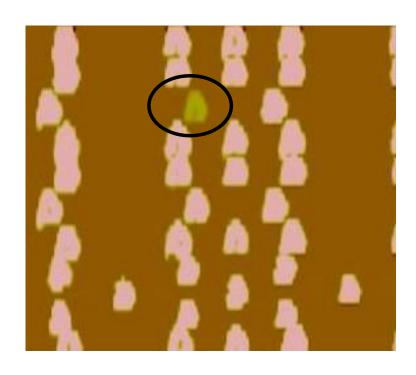

1 Poly short to contact 實例

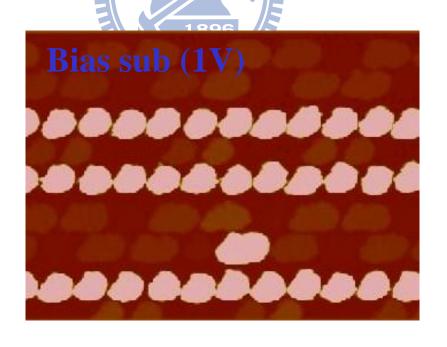

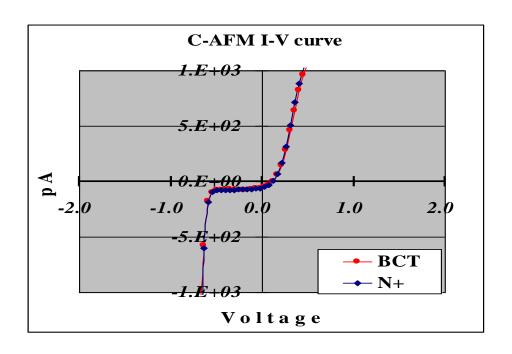

圖 2-14,2-15 為一試片的 C-AFM 的電流分布圖,圖中的亮點與暗點是 contact 位置,此時探針與基座電壓分別設定為 1V 及 -1V,可以明顯的看到,規律排列的白色的亮點為  $N^+$  diffusion contact,因為基座是設定為 1V,故  $N^+$  diffusion contact 是處於順向偏壓的狀態,有量測到大電流,故在著色上以白色顯示之,但是在圖中下方位置非常突兀的出現了一個白色亮點,對照圖 2-16 layout 發現此為一 budded contact,理論上是不該有電流的,故判斷 poly 有漏電路徑,為了確認此漏電是否為真,我們再把探針點到此 poly contact 量取 IV 曲線,並和  $N^+$  diffusion contact 做以較,如圖 2-17,發現  $N^+$  diffusion contact 與 budded contact 的曲線重疊,而根據這些電性量測結果,判斷 poly 應該與  $N^+$  diffusion contact 有短路現象,而此假設由 TEM 得到了證明,如圖 2-18。

### 2 High resistive contact 實例

C-AFM 也可用來尋找高阻值的問題,圖 2-19 為 contact 的電流分布圖,探針與基座電壓分別施予 0V 和 1V,圖中有白色亮點的即為有量測電流存在,黑色圓圈為  $N^+$  diffusion contact,處於順

向偏壓,所以應該有電流,但它所顯示的白色卻比較黯淡,說明了此 contact 應有高阻值以致電流變小,使得對應到的白色飽和度也變小了,為了確認此高阻值是否為真,我們再把探針移到此異常的  $N^+$  diffusion contact 量取 IV 曲線,並和附近正常的  $N^+$  diffusion contact 做以較,如圖 2-20,發現異常的  $N^+$  diffusion contact 的曲線在基座電壓為正的時候,比起正常的異常的  $N^+$  diffusion contact 就有晚 turn on 的現象產生,根據這些電性量測結果,判斷異常的  $N^+$  diffusion contact 應該有高阻值現象,而此假設由 TEM 得到了證明,如圖 2-21。經由 TEM 觀察,發現在 contact 底部有一不正常的界面,以致產生高阻值。

1896

### 2-4 奈米探針量測(Nano-Probing)原理與應用

#### 2-4.1 奈米探針量測原理

隨著半導體製程愈趨先進,IC對缺陷大小的容忍度也越來越低,傳統的故障分析工具或手法可能無法有效地找出微小的製程或設計缺陷,例如奈米大小的粒子或元件特性飄移,即便是用高解析度的電子顯微鏡也難在一開始觀察出個端倪,為了縮小檢查的故障區域,我們偶而會用FIB進行電路修補,以拉出PAD做電性量測上的確認,但此法受限於拉線阻值、繞線的方便性、量測

干擾或者是製作花費等,使得電路修補無法成為有效的故障分析解決方案,尤其當 metal 間距愈趨縮小和 metal 層數越多之後,用電路修補來量測電路或元件特性更成為不可能的任務,因此要怎麼直接量取奈米級元件特性就成為一項有趣的課題[11]。

當80年代成功開發出奈米級大小的探針以做些元件表面的物性量測之後,直觀的想,為何不能善用這樣的探針直接點在元件上做電性量測呢?因此近幾年來,一個嶄新的技術叫做nano-probing 誕生了,它就是用直徑可小到幾十 nm 的探針直接點在 contact 或 metal 上做基本的電性量測,諸如電晶體、二極體或阻值等等,之後從變異的特性上去判斷可能的問題點,在缺陷改善上,可用適當的觀察工具進一步找出一般情況可能會忽略掉的缺陷,而在電路或製程改良上,則提供改進的方向,相較於傳統的電性定位工具,nano-probing 有一針見血的功能。

### 2-4.2 Nano-probing 的種類

利用探針來量取元件特性首先就是得看到探針下針的位置, 既然要看到,那就需選擇『看到』的工具,也就是探針需要架設 在哪一種電子顯微鏡底下,基本上有兩大主流,一是架設在 SEM 下的 nano-probing,叫做 SEM internal probing,另一則是以 AFM 為架構,稱為AFP(Atomic Force Probing)。

#### 1. SEM internal probing

在現有的 SEM 機台下,如果 SEM chamber 的空間夠大,足以塞進架設 nano-probing 的儀器,那麼就可請廠商來評估架設的流程,而不需要另外添購 SEM,這些評估項目除了包含架設空間,還有架設後的影像品質,因為 nano-probing 架設完成後多少還是會影響 SEM 的工作距離,但 nano-probing 又需在低加速電壓下操作,以免產生的累積電荷影響了元件特性,所以安裝 nano-probing 後的 SEM 的影像解析度已經沒有一般 SEM 來得清楚了。

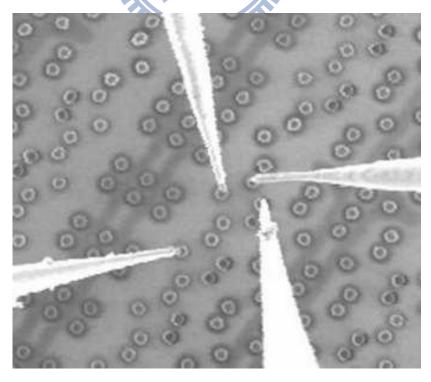

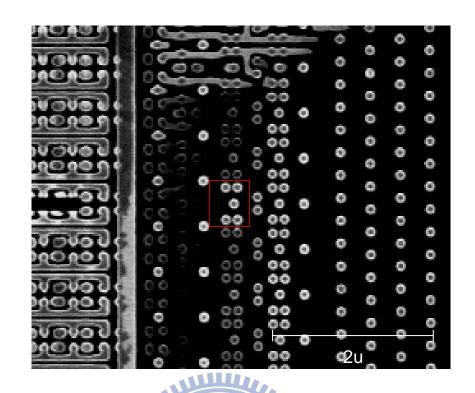

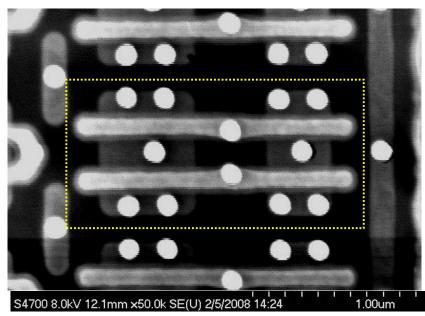

架設在 SEM 裡的 nano-probing 可安裝四至六個針座,如圖 2-22,探針是用鷂來製作,直徑可小到 40nm,因此目前量測到 65nm SRAM bit cell 都沒有問題,圖 2-23,2-24 是量測 90nm SRAM 以及 65nm SRAM 輸入級 buffer 電路的點針實況,試片需先處理至接觸 窗(contact)或金屬連線(metal)層。

探針的移動是用外部的系統來控制,必須小心謹慎的慢慢移動探針,這是需要花時間的,若是移動距離過大,一個控制不好,可能會傷及試片或探針,探針點到定位之後,就可利用電性量測系統進行基本的量測,這部份跟一般的量測儀器沒有二致。

### 2-4.3 Nano-probing 的應用方式

Nano-probing 的主要功能是用來量取元件特性,因此就必須 先行知道量取元件的位置,所以 nano-probing 的前置工作就是定 位,可能是用電性定位工具,如 Bit-Power 來得知,也可能是測試 機台抓取的故障 bit cell 位址。

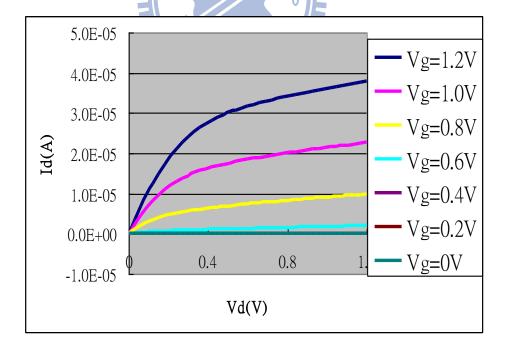

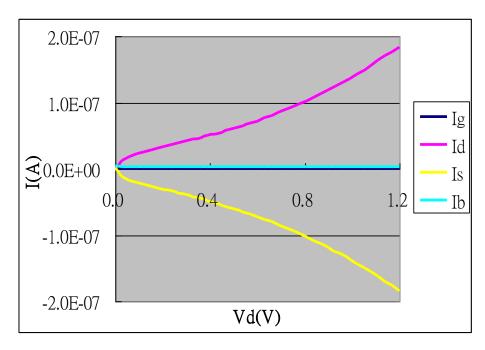

因為 nano-probing 可針對特定的元件量取電流特性,因此它不僅是用來找出微小缺陷可能座落的位置,也可應用在製程開發上,以得知製程參數與元件特性的關係。如圖  $2-25\sim2-27$ ,分別為  $I_d\text{-}V_g$  圖、 $I_d\text{-}V_d$  圖、Current component 圖,

在良率改善上,既然它是應用在微小缺陷的尋找上,因此後 1896 續的工作也就必須搭配能夠觀察微小缺陷的顯微鏡工具上,如 TEM、C-AFM,唯有這些工具彼此的搭配才能看到以往傳統故障 工具所不能觀察到的問題。

## 2-4.4 Nano-probing 的應用實例

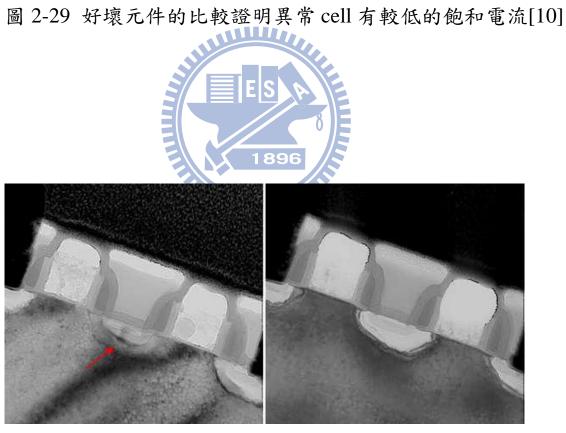

#### 90-nm SRAM soft fail [10]

先藉由記憶體測試機台抓出故障位址之後,直接使用 SEM nano probing 直接點在有問題的 SRAM bit cell 圖 2-28,共六個電

晶體,發現其中 PMOS 的 臨界電壓有降低趨勢,使得其飽和電流變小如圖 2-29,之後再利用化學藥劑對試片做選擇性的蝕刻,並用 TEM 觀察,結果發現 S/D 區域因為在進行離子佈植的動作有受到阻隔而使得此區域濃度變小如圖 2-30。

圖 2-2 NMOS 電晶體的立體截面圖[16]

圖 2-3 NMOS 的汲極電流與汲極電壓之間在不同 VGS- Vth 的關係[17]

圖 2-4 MOSFET 在線性區操作的截面圖[17]

圖 2-5 MOSFET 在飽和區操作的截面圖[17]

圖 2-6 電壓對比機制的示意圖

資料來源:國立中興大學研發處貴重儀器中心

圖 2-7 為接觸窗(Contact)層 N<sup>+</sup>/P-Well 的佈局圖(layout)與 lkeV PVC 影像

圖 2-8 TEM 觀察到 W spike

圖 2-9 調高加速電壓可觀察較底層的層次,可用來保護現場以方 便真因判斷

圖 2-10 為金屬層(Metal layer)的佈局圖(layout)

圖 2-11 SEM high keV PVC 影像

圖 2-12 TEM 觀察發現是接觸窗開路(contact open)

圖 2-13 C-AFM 的架構示意圖

資料來源:國立中興大學研發處貴重儀器中心

圖 2-14 N<sup>+</sup> contact bias +1V current map 影像 資料來源:台積電內部訓練網站

圖 2-15 相同試片的(-1V) P<sup>+</sup> contact 之 C-AFM currentmapping 影像

圖 2-16 異常 SRAM contact 之 layout

圖 2-17 異常 contact ≥ I-V curve

圖 2-18 TEM 顯示 contact 與 poly 有短路(short)現象

圖 2-19 圖中黯淡之黃點為異常 contact 所在

圖 2-20 異常的 N<sup>+</sup> diffusion contact 的 I-V curve

圖 2-21 TEM 顯示 Contact 與 salicide 之間有異常之界面

圖 2-22 架設在 SEM 裡的模組,可安裝四至六個探針

圖 2-23 90-nm SRAM 點針情形

圖 2-24 65-nm SRAM 點針情形

圖 2-25 nano-probing 可量測元件的  $I_d$ - $V_g$  特性曲線圖 資料來源:台積電內部訓練網站

圖 2-26 nano-probing 可量測元件的  $I_d$ - $V_d$  特性曲線圖 資料來源:台積電內部訓練網站

圖 2-27 nano-probing 可量測元件的電流組合

(current component)特性曲線圖

資料來源:台積電內部訓練網站

1896

圖 2-28 SEM Internal Probing 架針[10]

圖 2-30 TEM 確認是 S/D 的離子佈植異常所致[10]

# 第三章 實驗流程設計

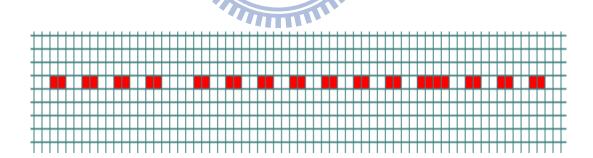

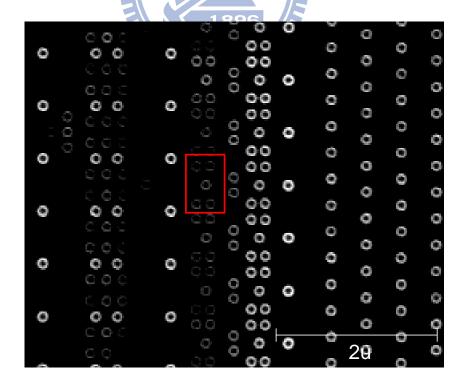

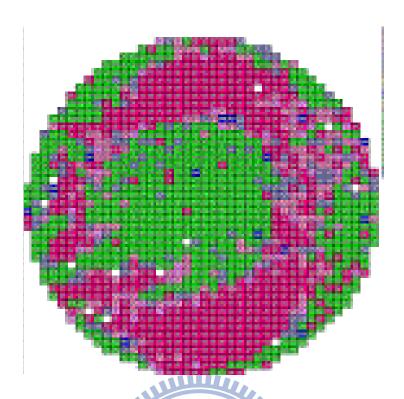

本實驗使用的樣品晶片是 65 奈米製程的動態隨機存取記憶體 (Dynamic Random-Access-Memory, DRAM),經測試機台測試後,發現故障型態為位元線(Bit Line, BL)故障。圖 3-1 為實驗組的晶圓二位碼分類圖(wafer map),圖 3-2 為 BL fail 的示意圖。由圖 3-1 中紅色的晶粒分佈型態像是甜甜圈型,圖 3-2 中紅色的 Cell 排成一列,視為 BL 故障。

## 3-1 樣品前置作業

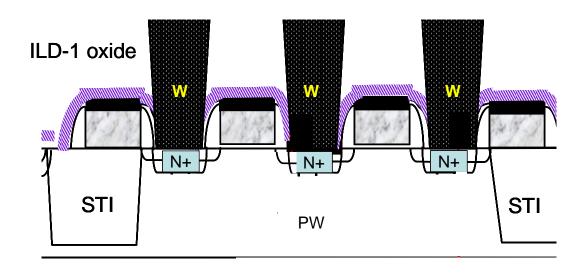

必須先使用磨台,將樣品晶片逐層處理到 MOSFET 結構中的 ILD1 接觸窗層(Contact)如圖 3-1,並且應用 Focus Ion Beam 之離 子束在樣品晶片上做記號。以及將樣品表面務必清理乾淨,不得 有殘存的灰塵顆粒留置在觀察樣品,以免汙染機台,或是造成觀察時誤判的可能,之後才可再進行實驗步驟。

#### 3-2 實驗步驟

本論文實驗主要分成三個部分:

- (1) 使用掃描式電子顯微鏡(Scanning Electron Microscopy, SEM) 儀器下應用被動電壓對比(passive voltage contrast, PVC)技術,本實驗設定溫度為室溫,加速電壓設定為 1keV、30 keV,觀察實驗組與對照組區域範圍內,有無異常之電壓對比影像,如表 3-1。

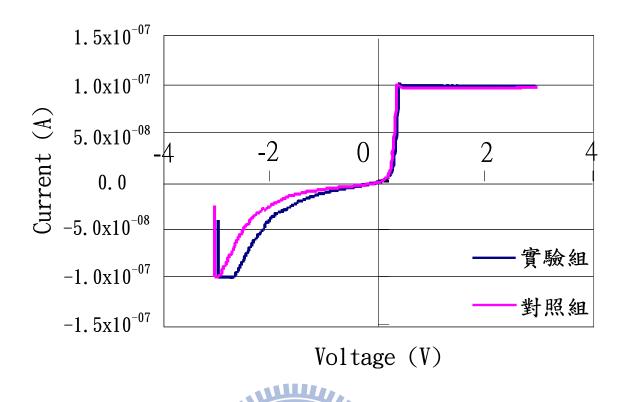

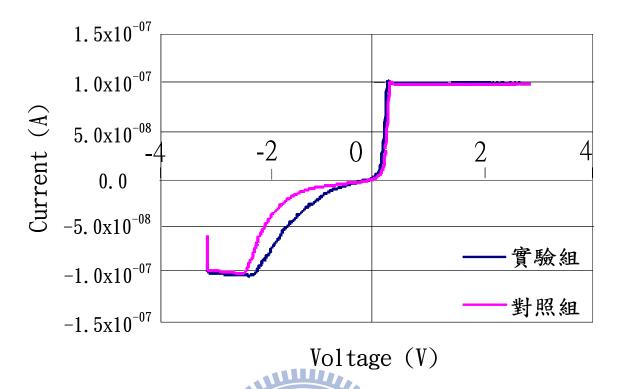

- (2) 使用 Veeco Innova 導電式原子力顯微鏡(Conductive Atomic Force Microscopy, C-AFM), 觀察實驗組與對照組二極體接面 (N<sup>+</sup>/Pwell)的電流(I)-電壓(V)特性曲線做比較。本實驗設定溫 度為室溫,偏壓設定範圍由負 3V~ 正 3V, 電流限定為 -0.1uA~+0.1uA,實驗分成五組,如表 3-2。

- (一)編號 1 之實驗組與對照組的二極體接面(N<sup>+</sup>/Pwell)的電流(I)-電壓(V)特性曲線圖。

- (二)編號2之實驗組與對照組的二極體接面(N<sup>+</sup>/Pwell)的電流(I)-電壓(V)特性曲線圖。

- (三)編號 3 之實驗組與對照組的二極體接面(N<sup>+</sup>/Pwell)的電流(I)-電壓(V)特性曲線圖。

- (四)編號 4 之實驗組與對照組的二極體接面(N<sup>+</sup>/Pwell)的電流(I)-電壓(V)特性曲線圖。

- (五) 編號 5 之實驗組與對照組的二極體接面(N<sup>+</sup>/Pwell)的電

#### 流(I)-電壓(V)特性曲線圖。

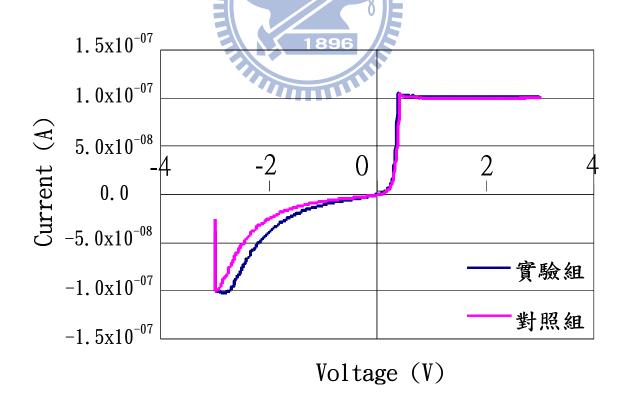

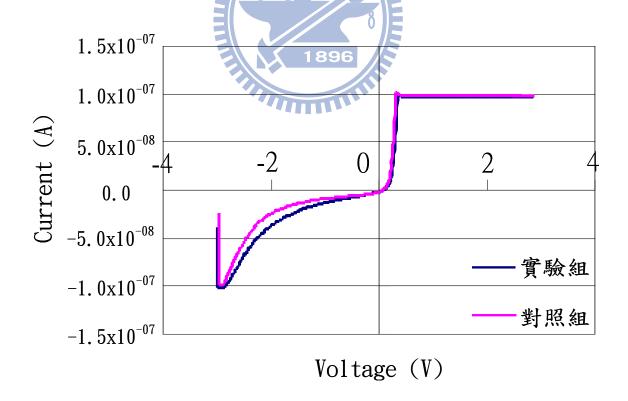

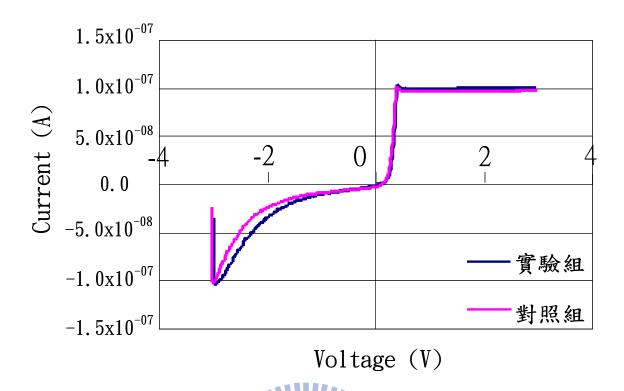

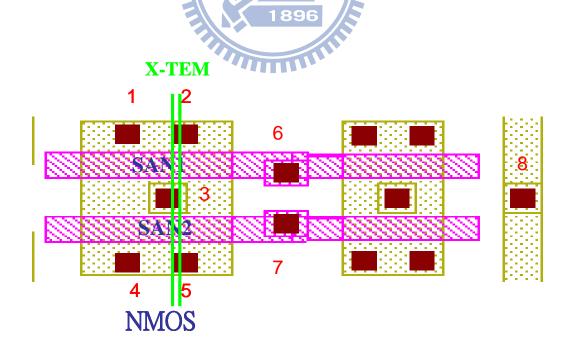

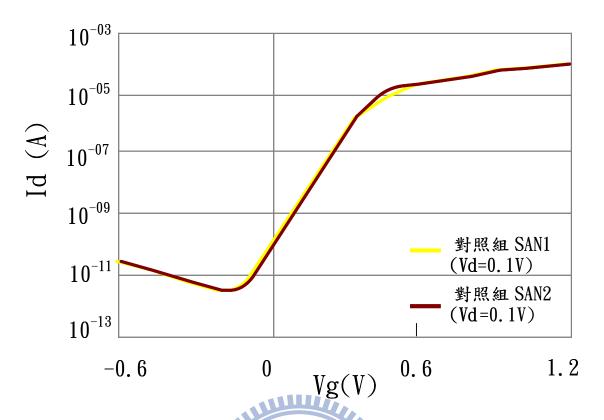

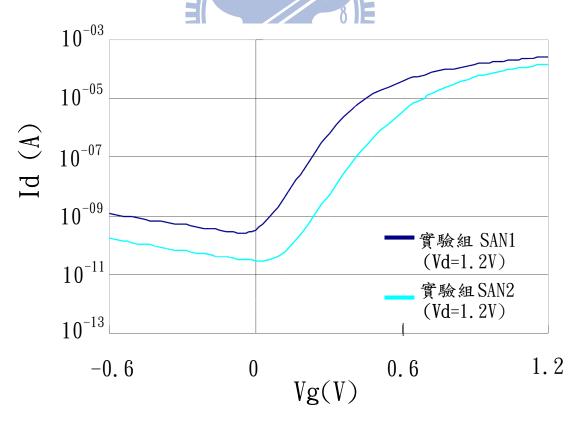

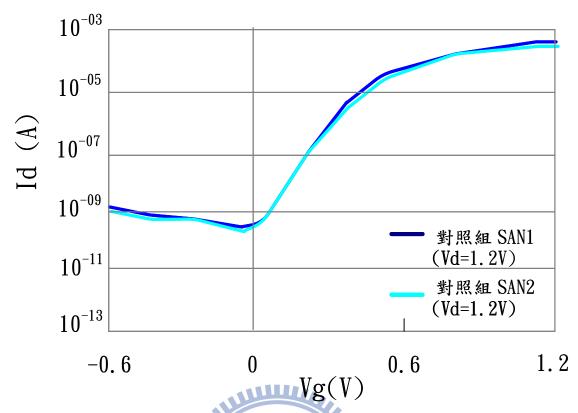

- (3) 使用 SEM N6000 與 Keithley 4200 組成之奈米探針量測 (Nano-Probing)儀器,觀察實驗組 NMOSFET SAN1 SAN2 的轉移特性(transfer characteristics)  $I_d$ - $V_g$  與對照組做比較。將汲極電流  $I_d$ (為輸出 output)對閘極偏壓  $V_g$ (為輸入 input)的作圖。本實驗設定溫度為室溫, $V_g$  設定範圍為-0.6V~1.2V, $V_s$ = $V_b$ =0V,編號 1、 4 的 contact 為 nMOSFET 電晶體的汲極(drain),編號 3 為源極(source),編號 6、7 為閘極(gate),編號 8 為基極(Bulk),實驗分成四組,如表 3-3。

- (一) 實驗組 SAN1 SAN2  $V_d$ =0.1V 時之轉移特性曲線。

- (二) 對照組 SAN1 SAN2 Va=0.1V 時之轉移特性曲線。

- (三) 實驗組 SAN1 SAN2  $V_d$ =1.2V 時之轉移特性曲線。

- (四) 對照組 SAN1 SAN2  $V_d$ =1.2V 時之轉移特性曲線。

圖 3-1 實驗組的晶圓二位碼分類圖(wafer map)

1896

圖 3-2 實驗組的 Bit Line 故障示意圖

圖 3-3 立體截面圖(cross layout)

表 3-1 被動電壓對比技術實驗設計表

|        | 被動電壓對比技術實驗設計     |               |  |  |  |

|--------|------------------|---------------|--|--|--|

| 實驗組別   | 1                | 1             |  |  |  |

| 實驗儀器   | Hitachi SEM 4700 |               |  |  |  |

| 實驗溫度   | 室溫               |               |  |  |  |

| 實驗組別   | 實驗組/對照組          | 實驗組/對照組       |  |  |  |

| 加速電壓設定 | 1 KV 30KV        |               |  |  |  |

| 主要觀察重點 | PVC影像是否有異常       | CT 與Poly間有無異常 |  |  |  |

表 3-2 導電是原子力顯微鏡量測實驗設計表

|        | <b>導電式原子力顯微鏡量測實驗設計</b>                 |     |     |     |     |  |

|--------|----------------------------------------|-----|-----|-----|-----|--|

| 實驗組別   | 1                                      | 11  | 三   | 四   | 五   |  |

| 實驗儀器   | Veeco Innova                           |     |     |     |     |  |

| 實驗溫度   | 室溫                                     |     |     |     |     |  |

| 電壓設定範圍 | (-3V~+3V)                              |     |     |     |     |  |

| 限電流範圍  | (−0. 1uA~+0. 1uA)                      |     |     |     |     |  |

| 實驗設定   | 實驗組/對照組                                |     |     |     |     |  |

| 量測位置   | 編號1                                    | 編號2 | 編號3 | 編號4 | 編號5 |  |

| 主要觀察重點 | 實驗組與對照組二極體接面(N+/Pwell)的電流(I)-電壓(V)特性曲線 |     |     |     |     |  |

表 3-3 奈米探針量測實驗設計表

|          | 奈米探針量測實驗設計                                                           |     |      |     |  |  |

|----------|----------------------------------------------------------------------|-----|------|-----|--|--|

| 實驗組別     | -1                                                                   | 五   | 11]  | 四   |  |  |

| 實驗儀器     | Hitachi SEM N6000 與 Keithley 4200 示波器                                |     |      |     |  |  |

| 實驗溫度     | 室溫                                                                   |     |      |     |  |  |

| 限電流範圍    | $(-100 \text{mA} \sim +100 \text{mA})$                               |     |      |     |  |  |

| Vg電壓設定範圍 | $(-0.6V \sim +1.2V)$                                                 |     |      |     |  |  |

| 量測位置     | SAN1/SAN2                                                            |     |      |     |  |  |

| Vd電壓設定   | 0. 1V                                                                |     | 1.2V |     |  |  |

| 實驗設定     | 實驗組                                                                  | 對照組 | 實驗組  | 對照組 |  |  |

|          | 編號1、4的contact 為nMOSFET電晶體的汲極(drain)                                  |     |      |     |  |  |

| 附註       | 編號3為源極(source)                                                       |     |      |     |  |  |

|          | 編號6、7為閘極(gate)                                                       |     |      |     |  |  |

|          | 編號8為基極(Bulk)                                                         |     |      |     |  |  |

| 主要觀察重點   | NMOSFET <b>SAN1 SAN2</b> 的轉移特性(transfer characteristics) Id-Vg曲線之比較。 |     |      |     |  |  |

# 第四章 實驗結果與討論

#### 4-1 被動電壓對比技術之實驗結果

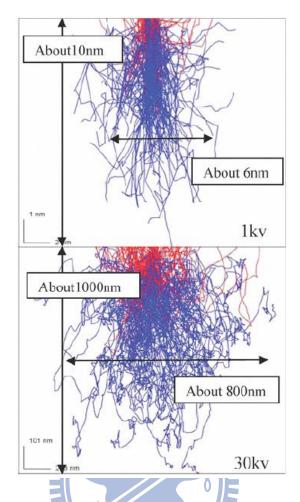

本實驗是在掃描式電子顯微鏡(Scanning Electron Microscopy, SEM)下應用 PVC 技術,設定加速電壓為 1keV 與 30keV 下的 PVC 影像實驗結果。

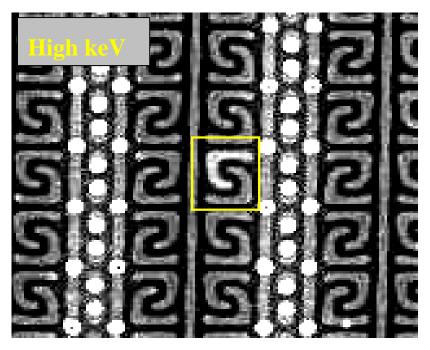

- (一) 圖 4-1 為實驗組的 1keV 的 PVC 影像,圖 4-2 為對照組的 1keV 下的 PVC 影像 。觀察兩組 1keV 的 PVC 影像後,發現實驗組的 NMOS 的影像比對照組的影像為亮。

- NMOS 在加速電壓為 1keV 的情形下 PVC 影像應該如圖 4-2,是呈現暗點才是正常的 PVC 影像,也就是應該暗未暗,因此判斷 NMOS 有漏電路徑的可能性。

- (二) 圖 4-3 為實驗組的 30keV 下的 PVC 影像,觀察圖中灰白色的 Poly gate 與接觸窗(Contact)之間,並沒有任何異常影像,此觀察目的在檢查 Poly gate 是否與 contact 有短路的可能,經由 30keV 下的 PVC 觀察之後,確定 NMOS contact 沒有與 poly gate short 的可能,綜合以上的觀察,推測故障點可能位於 Contact 下方。

- (三) 圖 4-1 中,在 SEM 低加速電壓 1keV 下,正電荷會聚集

在氧化層上,對正電荷來說,NMOSFET之 N<sup>+</sup>/P well 的結構為剛好是處在逆向偏壓的情況,因此正電荷無法被導引而被保留在 contact 表面上,所以呈現暗的 PVC 影像。如圖 4-4 所示。

## 4-2 導電式原子力顯微鏡(CAFM)實驗結果

本實驗是在應用導電式原子力顯微鏡(CAFM),觀察實驗組與對照組二極體接面(N<sup>+</sup>/Pwell)的電流(I)-電壓(V)特性曲線做比較。實驗分為五組,圖 4-5~4-9 為第一組至第五組之實驗組與對照組的 NMOSFET contact 之 PN 二極體接面(junction) 1896 電壓(V)與電流(I)關係 I-V 特性曲線比較圖,分析如下:

- (一) 觀察圖 4-5 為第一組的 I-V 特性曲線,在正向偏壓(forward bias)的部分,實驗組與對照組沒有明顯差別,在 0.3V 時電流都達到飽和,切入電壓(cut in voltage) 也沒有偏移。

- (二) 逆向偏壓(reverse bias)的部分,可以發現實驗組的電流增加速度比對照組來的快,也就是相同的逆向偏壓下,實驗組有較大的漏電電流。同時,實驗組比起對照組較快達到限電流 0.1μA

- (三) 圖 4-6~圖 4-9 為編號 2-5 的 contact 之 I-V 曲線, 觀察之

- 後,發現這些 contact 上的 PN 二極體接面(junction)之 I-V 曲線,在正向偏壓的部分,實驗組與對照組沒有差別。

- (四)但在逆向偏壓的部分,也可以發現實驗組的電流增加速度比對照組來的快,也就是相同的反向偏壓下,實驗組有較大的漏電電流。

- (五) 因此,此五點的 CAFM 的 PN 二極體接面(junction)之 I-V 曲線都顯示有 junction leak 的情形。

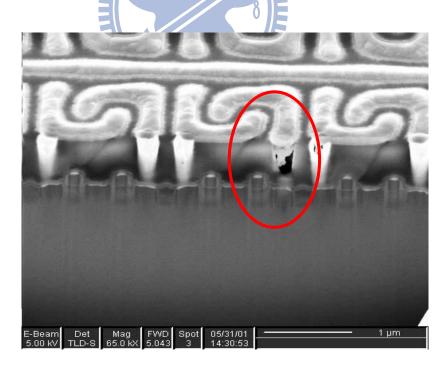

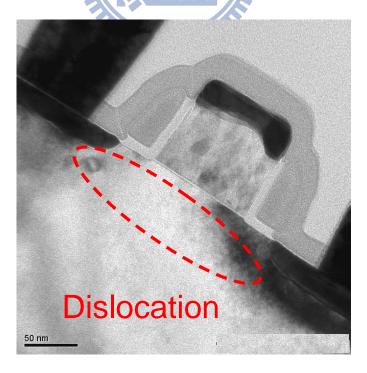

- (七) 結合實驗4-1與本實驗之電性行為結果,更加確認contact 下方有故障缺陷存在,圖4-10~圖4-13為示意圖以及TEM 的影像,由圖4-10的 X-TEM 為表是TEM切的位置,圖 4-11是SAN1與SAN2的TEM影像,圖4-12,4-13中可以清 楚見到,在 salicide 下方,發現有 dislocation的現象產生(紅圈處)。

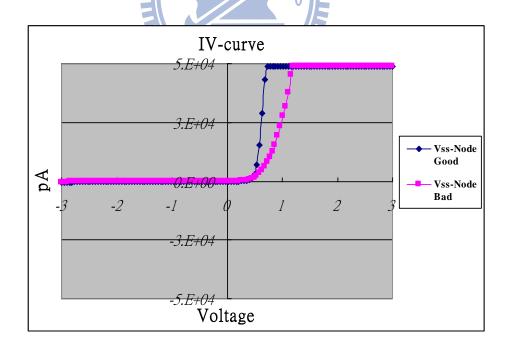

#### 4-3 奈米探針量測的實驗結果

本實驗是在應用奈米探針量測(Nano probing),實驗分成六

- 組。圖 4-14~4-17 為第一組至第四組實驗之轉移特性曲線比較圖,分析如下:

- (一) 觀察圖 4-14 為第一組實驗組的轉移特性曲線比較 圖,發現 SAN1 與 SAN2 在 Id 電流值為  $0.1\mu A$  時,  $V_g$  電壓值不同,SAN1 的  $I_d$ = $0.1\mu A$  時,  $V_g$ = $V_{tlin}$ =250mV;SAN2 的  $I_d$ = $0.1\mu A$  時, $V_g$ = $V_{tlin}$ =500mV。同時也發現 SAN1 與 SAN2 在  $V_g$ =0V 時, $I_d$  電流值不同,SAN1 的  $V_g$ =0V 時, $I_d$ =0.1 nA,而 SAN2 的  $I_d$  電流值近似於 0.001 nA。

- (二) 觀察圖 4-15 為第二組對照組的轉移特性曲線比較圖,發現 SAN1 與 SAN2 在  $I_d$  電流值為  $0.1\mu A$  時的  $V_g$  電壓值相近,沒有明顯差別,SAN1 與 SAN2 在  $I_d$ = $0.1\mu A$  時, $V_g$  電壓值均接近 250 mV。同時也發現 SAN1 與 SAN2 在  $V_g$ =0V 時, $I_d$  電流值相近,也沒有明顯差別。

- (三) 觀察圖 4-16 為第三組實驗組的轉移特性曲線比較 圖,發現 SAN1 與 SAN2 在 Id 電流值為  $0.1\mu A$  時,  $V_g$  電壓值不同,SAN1 的  $Id=0.1\mu A$  時,  $V_g=V_{tsat}=250mV$ ;SAN2 的  $I_d=0.1\mu A$  時,  $V_g=$

(四) 觀察圖 4-17 為第二組對照組的轉移特性曲線比較圖,發現 SAN1 與 SAN2 在  $I_d$  電流值為  $0.1\mu A$  時的  $V_g$  電壓值相近,沒有明顯差別,SAN1 與 SAN2 在  $I_d$ = $0.1\mu A$  時, $V_g$  電壓值均接近 220mV。同時也發現 SAN1 與 SAN2 在  $V_g$ =0V 時, $I_d$  電流值相近,也沒有明顯差別。

### 4-4 討論

### 4-4.1被動電壓對比技術之實驗結果之討論

電壓對比技術應用在半導體故障分析上已經很多年,同時也是在判斷電路是否開路(open)、短路(short)或是漏電的機制上,有相當強大的威力[18][19]。而新的應用方法也有將 PVC 影像與佈局圖結合在一起使用,將節省下許多時間,可提升效率[20]。並且,PVC在確認故障位置上也具有關鍵的方法,這個方法的工作原理是利用在 SEM 影像下,對比的不同,來加

以判斷。在 2002,Z. G. Song 和 J. Y. Dai 等人,將 PVC 的原理機制,用圖像的方法來說明 [21],我們現在用表 4-1 來做整理,方便說明。我們從表 4-1 中可以應用到我們的實驗中,在4-1 實驗中,使用的樣品為 N<sup>+</sup>/P-well 結構,對應表中的說明,實驗組 PVC 影像應呈現為暗態,如對照組之對比影像,但比較之後,發現實驗組的影像卻是呈現亮態,表示 contact 有漏電路徑,但是 Low keV 的影像無法判斷 contact 側邊是否有異常,所以需要 High keV 來幫助確認。從圖 4-3 我們可以觀察High keV 影像下 contact 側邊附近有沒有與 poly 短路或是橋接(bridge)的狀況,contact 側邊是清楚可見沒有異常,如此我們才可以進行 4-2 的實驗。1896

此外,在2009年,May Yang和 Sanan Liang 等人在SEM High keV 電子束穿透鎢(W) Contact 的實驗中提到[22], Low/High keV 電子束的穿透鎢(W) Contact 的深度與寬度如圖 4-18,或許我們是應用 High keV,檢驗 contact 是否有 open 或是 short 的問題。

### 4-4.2 導電式原子力顯微鏡(CAFM)實驗結果討論

我們知道電晶體漏電途徑有二如圖 4-19:一是順著電晶體的電極(source)與 P 井(P Well)或是 P 型矽底材的接合處;第二則是沿著 NMOS 的通道而漏失。針對第一個問題,就是所謂的接面漏電,我們了解到,半導體接面間的接面電流在順向偏壓時較高,在逆向偏壓時較低,如果能夠讓電晶體的汲極(drain)與源極(source),時時處於逆向偏壓之下,就可以降低電晶體接合處的漏電電流[1]。圖 4-5~圖 4-9 二極體接面(N<sup>+</sup>/Pwell)的電流(I)-電壓(V)特性曲線中,實驗組的曲線並非是直接通過原點的歐姆接觸,表示 contact 與 salicide 有很好的接合。[30]

從圖 4-12,圖 4-13 中可以清楚看到,在 salicide 底部的地方,有兩個與其他區域不一樣的影像,這就是所謂差排缺陷 (dislocation defect),在半導體的領域中,這種缺陷以被大家熟知很久了,特別是這種缺陷造成漏電機制,也是許多人都知道的[23][24]。有關造成 dislocation 為主要因素,以經確認製程過程是最大主因[25][26],也就是為了形成 CMOS 元件的源極 (source)、汲極(drain)、閘極(gate)時的離子佈質過程中造成點缺陷(point defect),不幸的是,這些點缺陷導致晶粒(crystal)損壞 [27]。接著利用回火(annealing)步驟來修復這些被損壞的晶粒,

但是過程中,損壞的晶粒還是有機會殘留在一些對於元件特性非常敏感的區域。此外應力(stress)也是形成此缺陷的原因 [28]。這裡要討論的,差排缺陷在N型半導體的行為好比是 "受體",如果在P型半導體的行為好比是 "施體"[29],隨著這個缺陷的延伸會型成漏電路徑,因此,如圖 4-12,圖 4-13 中的差排缺陷進入 MOSFET 的 PN 二極體接面中[30],會造成漏電流的增加,甚至於導致整個元件的電性故障[31]。

二極體接面(N+/Pwell)的電流(I)-電壓(V)特性曲線如圖 4-5~圖 4-9 以及 TEM 影像,還有漏電機制,整理告訴製程設備人員,經過製程改善後,應該將問題已解決,但是事實不是如此,圖 4-20 所示是實驗後而且製程經過改善之後的晶圓測試二位碼分類圖,我們可以發現圖中紫色的故障晶粒,仍然有著有類似甜甜圈的故障分佈型態,再接著與圖 3-1 之實驗組的晶圓測試二位碼分類圖比較後,發現故障分佈型態極為類似,最後由圖 4-21 功能正常晶粒的 TEM 影像中,發現與故障晶粒的TEM 影像中,都有差排缺陷(Dislocation)現象產生,表示差排缺陷(Dislocation)並非真正的故障真因。必定有其他真因,導致問題無法解決。

## 4-4.3 奈米探針量測的實驗結果討論

本實驗量測的結果告訴我們實驗組的 SAN1 與 SAN2 的臨界 電壓  $(V_{th})$  ,  $V_{tlin}$  與  $V_{tsat}$  都是有 200 mV 不匹配 (mis-match) 現象。

我們對於感應放大器的研究大部分假定為完美對稱,也就是電路的兩端都顯示相同特性和偏壓電流。然而實際上,名義上相同的元件會遇到因為而製成步驟中每一個步驟的不確定性所產生的有現不匹配(mis-match)現象。例如本實驗中的臨界電壓(V<sub>th</sub>)不匹配,會導致三個重要的現象: 直流偏移、訊號失真和較低的共模排斥現象[32]。

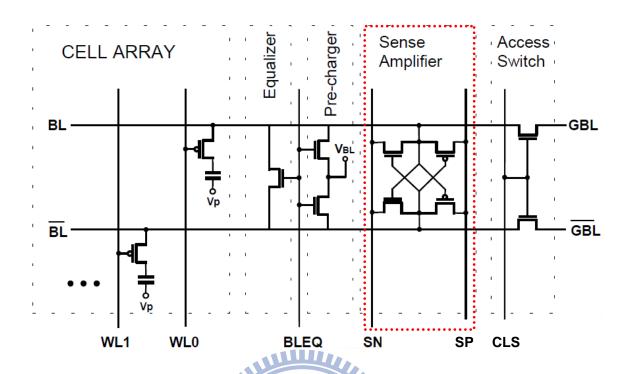

圖 4-22 顯示 DRAM 胞(Cell)與其資料讀寫相關之電路圖示。 其中,等化器(Equilizer)用以將兩條位元線的電壓加以均等化;紅虛線所圈的範圍即是感應放大器(Sense Amplifier, S/A),用以確定儲存於 DRAM cell 內的訊號是 "1"或是"0";而右區的選擇器(CLS),用以隔離出適當區域的 DRAM cell 以方便進行資料的讀或寫,或是再存入(Refresh)。本實驗所要觀察與量測的區域就是圖4-22 紅虛線所圈的範圍即是感應放大器(Sense Amplifier, SA)。

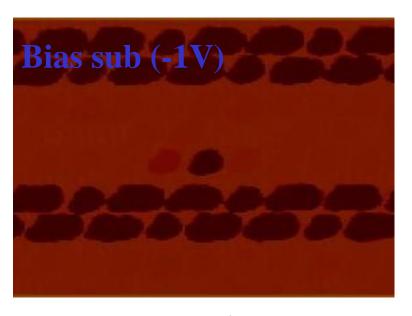

圖 4-23 為本實驗觀察與量測 MOSFET 的示意圖,此為 CMOS的結構,共有四個 MOSFET,分別為兩個 NMOS(n<sup>+</sup>/p well)與兩個 PMOS,圖中左邊兩個 NMOS SAN1、SAN2 為實驗中使用的觀察

樣品,數字 1~8 是這兩個 NMOS 之接觸窗(Contact)的編號,也是本實驗所要觀察及量測的範圍區域。同時本實驗分為實驗組與對照組,方便觀察與說明。

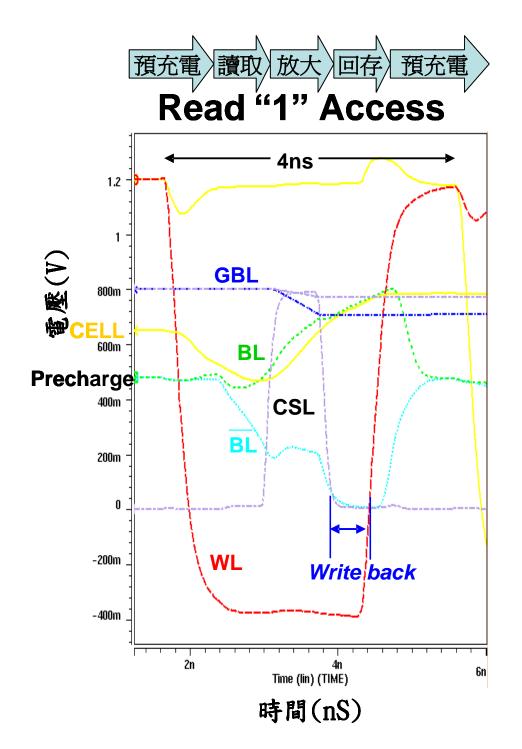

該圖的縱軸代表電壓大小,而橫軸則代表時間,但是其時間單位非常的短,僅僅只有 nS 的等級。圖 4-24 的波形圖,主要是說明胞內的資料,從"被讀出然後再被寫回"的這段過程中,主要幾個訊號隨時間的變化情形。其主要參與的訊號計有:字元線(WL)、兩條互相互補的位元線(BL 及 BL )及 DRAM 胞(cell)內的電容器。但是為了簡化內容得以單純化,選定的幾條最重要參與此動作的訊號線為代表,來解釋圖 4-24 的運作。

幾個資料的讀取款至回存的動作循環,我們可以圖 4-24 的波形圖來加以說明。基本上,這個動作的循環,分成四個主要的動作區間:預充電、讀取、放大、及回存。首先在 WL(紅線表示)還沒有開啟之前,整個圖 4-22 內的迴路都是處於預充電的階段。這時,圖 4-22 中的等化器將開啟使得 BL、 $\overline{BL}$  (分別以綠線及藍線來表示)兩條相互補的位元線的電壓值相同,且等於  $V_{BL}$  (亦即等於  $1/2V_{CC}$ );同時,DRAM 胞的電容器的電壓值(以黃線表示)也處於接近其滿載的情況(即~ $V_{CC}$ ),如圖 4-24 最左邊的波形圖示。

一旦 WL 開啟,整個 DRAM 的資料讀取動作便開始展開,電容器內所儲存的電荷將送入 BL,使得 BL 與 BL 的電壓值開始產生 些微的差異,此電壓值差異的大小約在 30~40 mV 之間。這時圖 4-22 的電路正在進行所謂的"讀取"的動作,而這期間內的幾個主要訊號線的波形變化如圖 4-24 所示(本圖以儲存的訊號為"1"做例子)。一旦這個 BL 與 BL 的電壓差異值 ΔV 隨著 S/A 的啟動而加速拉大之後呢,圖 4-22 的迴路便開始進入圖 4-24 的"放大"階段,這時 BL 的電壓將被提升到等於 V<sub>CC</sub>,而 BL 則被拉低到 V<sub>SS</sub>,至此,圖 4-22 的 S/A 已完成該 DRAM 胞(cell)所儲存的資料讀取[1]。 從另一角度來分析此電路,BL 電壓值若從一開始就較 BL 小的情形下,則 S/A 將無法判斷並放大"1"的訊號,導致 BL 整條訊號出現異常,測試程式就會出現 BL 故障的情形。

本實驗中 SAN1 與 SAN2 的臨界電壓不匹配,會造成直流偏移、訊號失真,導致圖 4-20 的 BL 與 BL 無法讀取及寫入 cell 內的資料,因此造成 DRAM 的 BL 故障,因此故障真因確定為感應放大器中的 NMOS 臨界電壓不匹配,造成 DRAM 的 BL 故障。

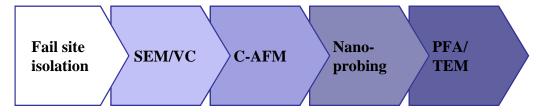

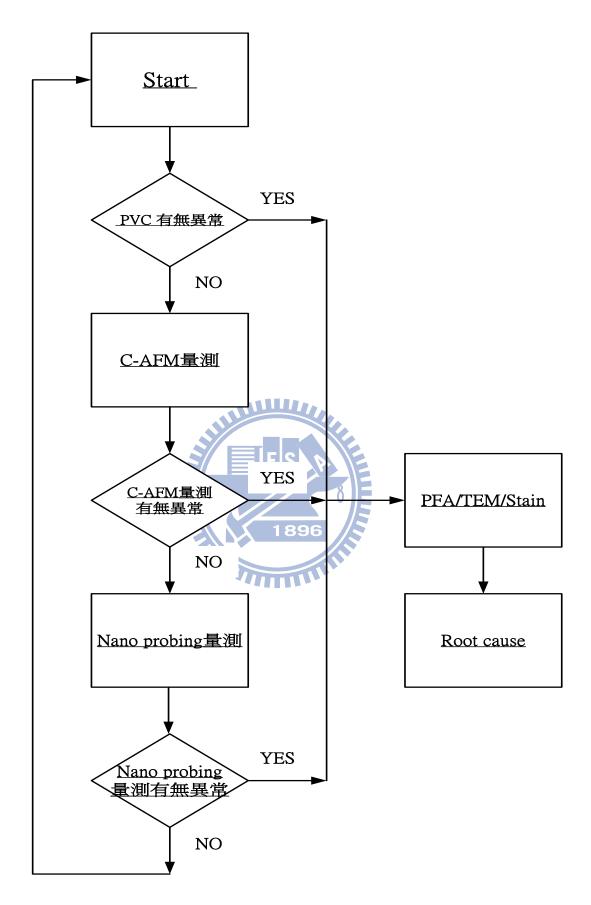

綜合以上的實驗結果與討論,我們可將發展奈米探針與被動電壓對比技術歸納如圖 4-25,當我們開始一個故障分析時,先使用 PVC 的技術來確認故障點的位置,並且確認 PVC 行為是否有

異常,若無異常行為,進行 CAFM 量測,分析比較 MOSFET 的 PN 二極體接面電流(I)-電壓(V)關係圖,觀察是否有異常,若是沒有異常,再進行 nano probing 量測,利用 nano probing 取得 MOSFET 的完整電性特徵,以方便接下來的 PFA 進行。若是 PVC、CAFM、Nano probing 中有任何的異常,都可以進行 PFA 的步驟,當然,若是想得到更多詳細的電性資料,是可以將所有的程序執行完成,只是會花時間與成本的考量,當然最重要是查出真正的故障真因為第一考量。

此外,PVC對於故障分析中的 open、short、leakage 與高阻值有絕佳的判斷能力,但因為 PVC 影像只有亮,灰,暗,黑等的灰階,常對於極小缺陷(tiny defect)無法作更進一步的分析,會有誤判的機會。CAFM 就彌補 PVC 的不足的部分,也就是說 CAFM對極小缺陷(tiny defect)有電性及 current map 可以讓這些缺陷無所遁形,但是 MOSFET 是立體結構的開關,CAFM 對於垂直方向的故障偵測有較 PVC 技術更加精準的優點,但對於水平方向的問題,就束手無策,無計可施,如此一來就需要使用到 Nano probing的工具,將 MOSFET 的所有電性特徵量測完成,搭配半導體物理與製程的知識,結合電路設計的概念與 TEM 影像,解釋故障機制的可能性,最後完成一件故障分析報告,提供前段製程做為擬訂

製程改善實驗的重要依據,故障缺陷排除後,良率也自然提升。 因此發展奈米探針與被動電壓對比技術以三維示意的話,PVC可 說是一維(One Dimension, 1D), CAFM 是二維(Two Dimension, 2D), Nano probing 就是三維(Three Dimension)。

圖 4-1 實驗組的 1keV 的 PVC 影像,紅框標示就是 PVC 異常的 Contact

圖 4-2 對照組的 1keV 的 PVC 影像

圖 4-4 Low keV 的 PVC 示意圖

圖 4-5 編號 1 的 contact 之 PN 接面電流(I)-電壓(V)曲線圖

圖 4-6 編號 2 的 contact 之 PN 接面電流(I)-電壓(V)曲線圖

圖 4-7 編號 3 的 contact 之 PN 接面電流(I)-電壓(V)曲線圖

圖 4-8 編號 4 的 contact 之 PN 接面電流(I)-電壓(V)曲線圖

圖 4-9 編號 5 的 contact 之 PN 接面電流(I)-電壓(V)曲線圖

圖 4-10 TEM 示意圖, X-TEM 表示 TEM 取樣的位置

圖 4-11 實驗組 SAN1 與 SAN2 之 TEM 影像

圖 4-12 實驗組 SAN1 TEM 放大圖,紅圈指出 Dislocation defect

圖 4-13 實驗組 SAN1 TEM 放大圖,紅圈指出 Dislocation defect

圖 4-14 實驗組 SAN1/SAN2,Vd=0.1V 轉移特性曲線比較圖

圖 4-15 對照組 SAN1/SAN2,V<sub>d</sub>=0.1V 轉移特性曲線比較圖

圖 4-16 實驗組 SAN1/SAN2,V<sub>d</sub>=1.2V 轉移特性曲線比較圖

圖 4-17 對照組 SAN1/SAN2,V<sub>d</sub>=1.2V 轉移特性曲線比較圖

表 4-1 被動電壓對比技術行為對照表,共分成三種製程部分 1. 鋁銅製程。 2. 銅製程。 3. 後段製程。

| Al-Cu         | N+/ P<br>Well    | P+/N<br>Well   |                   | Poly<br>Gate | Well     |

|---------------|------------------|----------------|-------------------|--------------|----------|

| Low KV        | Dark             | Bright         |                   | Dark         | Bright   |

| High KV       | Dark             | Bright         |                   | Bright       | Dark     |

| Cu<br>process | N+/ P<br>Well    | P+ / N<br>Well |                   | Poly<br>Gate | Well     |

| Low KV        | Dark             | Bright         |                   | Dark         | Bright   |

| High KV       | Bright           | Dark           |                   | Dark         | Dark     |

| Back-<br>end  | Connected to S/D |                | Connected to gate |              | Floating |

| Low KV        | Bright           |                | Gray              |              | Black    |

| High KV       | Dark             |                | Bright            |              | Bright   |

圖 4-18 SEM 不同低/高加速電壓下(1keV)/(30 keV),電子東穿透 鎢(W)深度與寬度的示意圖

圖 4-19 MOSFET 主要漏電途徑: 1. PN 接面; 2. 隔離; 3.通道

圖 4-20 實驗後而且製程經過改善之後的晶圓 測試二位碼分類圖

1896

圖 4-21 功能正常晶粒的 TEM 影像

圖 4-22 顯示 DRAM 胞(Cell)與其資料讀寫相關之電路圖

1 2 6 8 8 8 4 5 NMOS

圖 4-23 本實驗觀察與量測 MOSFET 的示意圖

圖 4-24 顯示 DRAM 胞運作時,自預充電(Pre-charge)至資料回存 (Restore)整個循環中,各個主要訊號線於不同時間點的電壓大小與波形(waveform)。其中 WL 指字元線,BL 指位元線,而 VBL 為位元線電壓,通常為 1/2Vcc。

圖 4-25 整體實驗步驟之流程圖

## 第五章 結論

發展奈米探針與被動電壓對比技術對於 MOSFET 之故障分析,乃是一個新的嘗試,我們的目標是希望提高以 MOSFET 為電子元件之主要結構的故障分析流程可以因為這一個有效的發展流程,可以在故障點定位完成之後,應用此流程,有增進觀察到故障分析的命中率的能力。藉由本研究所進行的一系列實驗來檢驗發展奈米探針與被動電壓對比技術的偵測能力。

這個發展的方法流程已經證實有效的,利用元件上的電性特徵,來幫助工程人員能夠更方便找到故障原因並且提供前段製程設備人員有效的預防機制,幫助晶圓廠提升良率並節省時間成 1896 本,同時此發展技術也需要訓練優良的操作人員及專業的工程判 讀知識,這些都有賴後續相關故障分析的人員共同努力及發展。

## 參考文獻

- 1. 莊達人 , <u>VLSI 製造技術</u> , 五版 , 台北 , 高立出版社, 民國九十四年。

- M.F. Bailon, P.F.F. Salinas, J.P.S. Arboleda, "Application of conductive AFM on the electrical characterization of single-bit marginal failure", IEEE Trans. Device Mater.

Reliab, v6(2), pp. 282-284 (2006)

- 3. Michael Quirk, Julian Serda, <u>Semiconductor manufacturing</u>

technology metrology and defect inspection, Prentice Hall

(2001).

- 4. Stefan Mogck, <u>Transmission electron microscopy studies of interfaces in multi-component systems</u>, Groningen

University (2004).

- 5. Y. C. Yong, J. T. L. Thong, J. C. H. Phang, "Determination of secondary electron yield from insulators due to a low KV electron beam" J. Appl. Phys., v84(8), pp. 4543-4548 (1998).

- 6. Jone C. Lee, C.H. Chen, David Su, J.H. Chuang,

- "Investigation of sensitivity improvement on passive voltage contrast for defect isolation", Microelectron. Reliab., V42(9-11), pp. 1707-1710 (2002).

- 7. K. Lin, H. Zhang, S.S. Lu, "Conductive atomic force microscopy application for semiconductor failure analysis in advanced nanometer process", International Symposium for Testing and Failure Analysis, pp. 178-181, San Jose, USA (2006).

- 8. C.S. Liu, C.R. Chen, Y.F. Hsieh, "Identification of processing defects by focused ion beam (FIB) induced voltage contrast" IPFA 1999 Proceedings, pp. 128–131, IEEE (1999).

- H. Yamashita, H. Nanatsue, Y. Hata, S. Mayuml, "Open contact analysis of single bit failure in 0.18 μm technology", Microelectron. Reliab., v42(12), pp. 1997-2001 (2002).

- 10. C.C. Wu, J.C. Lee, J.H. Chuang, T.T. Li, "Single device characterization by nano-probing to identify failure root cause", International Symposium for Testing and Failure Analysis, p183-185, San Jose, USA (2005).

- 11. G. Zimmermann, S. Mueller, "90nm technology SRAM soft fail analysis using nanoprobing and junction stain TEM", International Symposium for Testing and Failure Analysis, pp. 512-516, San Jose, USA (2006).

- 12. M. Mahanpour, "Emission microscope and passive voltage contrast: Solving a problem quickly" III-Vs Review, v9(6), pp. 46-49 (1996).

- 13. O.C. Khiam, B.J. Hua, S. Redkar, "Electrochemical Wet Etching in KOH:H2O Solution and Secondary/Ion Image Passive Voltage Contrast as a Complementary Technique in Failure Analysis", Microelectronics Reliability, v40(8), pp. 1455-1459 (2000).

- 14. S. M. Sze, Physics of Semiconductor Devices 2nd ed. New York: Wiley (1981).

- 15. A. Donald Neamen, Semiconductor Physics & Devices, 3rd ed. McGraw Hill (2003).

- 16. Behzad Razavi, Design of Analog CMOS Integrated Circuits,1st ed. McGraw Hill (2002).

- 17. Adel. S. Sedra and Kenneth. C. Smith, Microelectronics

- Circuits, 5th ed., Oxford (2003).

- 18. Tctsuya Sakai, Noriaki Oda, Takashi Yokoyama, "Defect Isolation and Characterization in Contact Array-Chain Structures by using Voltage Contrast Effect", Proceeding IEEE International Symposium (1999).

- 19. H.P. Kuan, X. M. Zhang, "Physical Analysis of TiSi2 bridging (gate-to-S/D) failure in IC", IPFA 2005Proceedings, pp. 7803-9301, IEEE, Singapore (2005).

- W. Ng, S. Jacobson, D. Nguyen, "Configurable PVC Checking for Fault Identification", IPFA 2009 Proceedings, pp. 4240-4244, IEEE, China (2009).

- 21. Z. G. Song, J. Y. Dai, S. Ansari, C. K. Oh, S. Redkar, " Front-end Processing Defect Localization by Contact-level Passive Voltage Contrast Technique and Root Cause Analysis", IPFA 2002 Proceedings, pp. 7416-7419, IEEE, Singapore (2002).

- 22. May Yang, Sanan Liang, Linfeng Wu, Lilung Lai, Jie Su, Chomg Niou, Yoyo Wen, Yvonne Zhu, "Application of Passive Voltage Contrast Fault Isolation on 65nm SRAM

- Single Bit Failure", IPFA 2009 Proceedings, pp. 3912-3916, IEEE, China (2009).

- 23. M.Whelan, "Leakage currents of n/p silicon diodes with different amount of dislocations", Solid-State Electronics, v12, pp. 963-968 (1969).

- 24. B. O. Kolbesen, H. P. Strunk, "Analysis Electrical Effects and Prevention of Process Induced Defects in Silicon Integrated Circuits." VLSI Electronics Microstructure Science, pp. 143-222, Academic Press (1985).

- 25. M. Dellith, G. Booker, B. Kolbesen, W. Berholz, "A dislocation formation model of trench-induced dislocations in dynamic random access memories", J. Electrochem. Soc., v143(1), pp. 210-215 (1996).

- 26. K.S. Garth, Y.H. Chen, "Effects of Dislocation and Bulk Micro Defects on Device Leakage", SEMICON, Taiwan (2001).

- 27. M. Miyake, M. Takahashi, "Defects Induced by Deep Preamorphization and Their Effects on Metal Oxide Semiconductor Device Characteristics", J. Electrochem.

- Soc., v144(3), pp. 1020-1024 (1997).

- 28. P. Fahey, S. Mader, "Stress- Induced dislocations in silicon integration circuits", IBM Journal of Research and Development, v36(2), pp. 158-182 (1992).

- 29. J. Li, K.S. Jones, "311 defect in silicon: The source of the loops", Appl. Phys. Lett., v73(25), pp. 3478-3750, (1998).

- 30. J.R. Patel, L.R. Testardi, P.E. Freeland, "Electronic effects on dislocation velocities in heavily doped silicon", Phys. Rec. B., v13(8), pp. 3548-3557 (1976).

- 31. Frank Siegelin, Anton Stuffer. "Dislocation related Leakage in Advanced CMOS device." International Symposium for Testing and Failure Analysis, pp. 59-63, San Jose, USA (2005).

- 32. 劉傳璽,陳進來,<u>半導體物理與製程</u>,二版,台北,五 南出版社,民國九十五年。