# 國立交通大學

電子工程學系電子研究所碩士班

# 碩士論文

標準 CMOS 製程之單光子偵測器

Single-Photon Avalanche Photodiode Fabricated with Standard

CMOS Technology

研究生: 戴嘉邑

指導教授:林聖迪 教授

中華民國九十九年八月

#### 標準 CMOS 製程之單光子偵測器

# Single-Photon Avalanche Photodiode Fabricated with Standard CMOS Technology

研 究 生:戴嘉邑 Student : Chia-ie Dai

指導教授:林聖迪 Advisor : Dr. Sheng-Di Lin

國立交通大學電子工程學系電子研究所碩士班碩士論文

#### A Thesis

Submitted to Department of Electronics Engineering and Institute of Electronics

College of Electrical and Computer Engineering

National Chiao Tung University

In partial Fulfillment of the Requirements

For Degree of

Master

In

**Electronics Engineering**

August 2010

Hsinchu, Taiwan, Republic of China

中華民國九十九年八月

#### 標準 CMOS 製程之單光子偵測器

學生: 戴嘉邑 指導教授: 林聖迪 博士

# 國立交通大學 電子工程學系電子研究所碩士班

#### 摘要

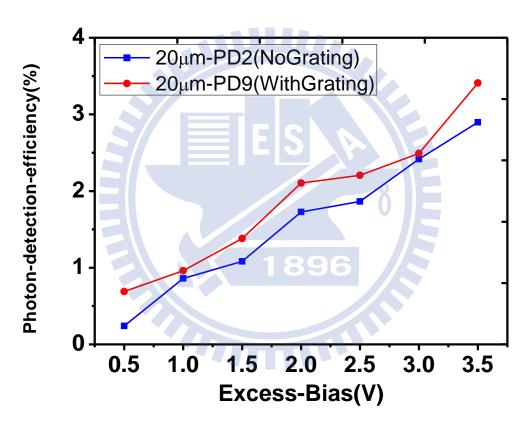

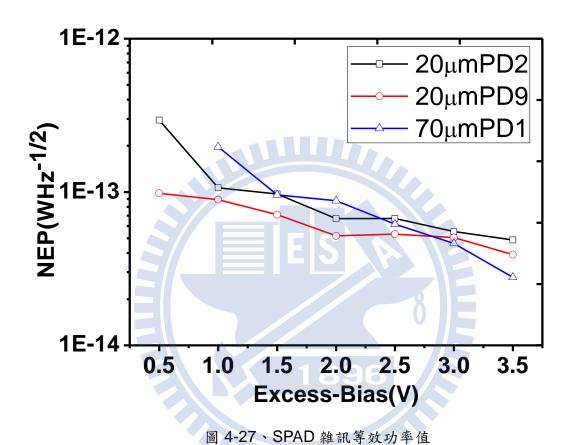

本論文主要為利用標準  $0.18~\mu m$  CMOS 製程技術,設計出均勻內建電場以形成光偵測區域,並利用金屬光柵結構,來提升單光子偵測器之偵測效率。由於現今利用單光子偵測器的影像陣列在進行影像擷取時,係利用脈衝式藍光二極體,所以我們將偵測光波長設定在 550~n m 以下之藍光可見光波長範圍,藉以提升單光子偵測器在此偵測波段的偵測效率,在此我們利用 Pwell 形成 guard-ring 的方法,來避免元件的 corner breakdown 造成元件的提前崩潰。設計晶片面積約  $851 \times 851 \mu m^2$ ,崩潰電壓約為-9.9V。在直流響應的量測上,我們比較了不同面積及光柵結構下的響應率並且得到在藍光波段  $400nm \times 465nm$  分別因為光柵結構而提升 1.04~e 居及 1.53~e 。暫態響應上,我們藉由 400nm 及 780nm 脈衝雷射,得到預期中不同波長下吸收係數對元件操作速度之影響。最後我們藉由 Passive quenching 電路,將元件操作至崩潰電壓之上,設定  $R_L$  在  $250k\Omega$ ,得到元件暗計數為  $1.3MHz(0.5V \times 25°C)$ ,並且經由元件死亡時間 (Dead time)校正入射光子數,量測出最高之單光子偵測效率為 6%,單光子偵測效率因利用光栅結構提升約 1.2~e ,雜訊等效功率在 $1\times 10^{-13}~WHz^{-1/2}$ 。

Single-Photon Avalanche Photodiode Fabricated with Standard CMOS

**Technology**

Student: Chia-ie Dai

Advisors: Dr. Sheng-Di Lin

Department of Electronics Engineering & Institute of Electronics Engineering

**National Chiao Tung University**

**Abstract**

In this thesis, by using standard 0.18µm CMOS technology, we design a single-photon

avalanche photodiode (SPAD) with uniform built-in electric field in light detection region.

The metal grating structure is used to enhance the photon detection efficiency. Because

the imaging system with SPAD array uses pulsed blue LED as lighting source, we aim at

enhancement of detection efficiency below 550nm. We use P-well guard-ring to avoid the

corner breakdown and, to enhance photon detection, the metal layers are used to

implement grating structure in the active region. As a result, we can enhance detection

efficiency and, at the same time, keep the response speed. We design 15 devices with a

chip size of about 851×851 µm<sup>2</sup> and the low breakdown voltage of -9.9V is obtained as

expected. In DC response measurement, we compare responsivity between devices with

different grating structures and, with one of the devices, a 50% enhancement of

photo-responsivity measured with a 465nm blue-LED is achieved. The pulsed lasers of 400

nm and 780 nm are used to study the transient response of our SPADs and the results are

consistent with the simulation. Finally, with a passive quenching method, we bias the

SPADs above breakdown voltage with a load resistor ( $R_L$ ) of 250 k $\Omega$ . At an excess bias of 0.5

V, the dark count rate is about 1.3MHz at  $25^{\circ}$ C. By considering the dead time of SPADs, we

get the effective incident photon numbers and obtain a peak photon detection efficiency

(PDE) of about 6%. Most importantly, by using the metal grating, we improve the PDE by

20% and achieve a noise equivalent power of 1x10<sup>-13</sup> WHz<sup>-1/2</sup>.

ii

#### 致謝

兩年的碩士生涯即將在完成這篇論文時畫下句點,一路走來,歷經種種低潮與失 敗。然而,由於許多人的幫忙於鼓勵,才可使我更加成長茁壯,突破瓶頸。即使最後 的成果尚有努力的空間,也希望能對得起自己、家人、及幫助我的教授、同學們。

過程中,最感激的便是我的指導教授-林聖迪博士,感謝他收留我這個備取生,因為我知道,以我的大學成績在這實驗室中是不及格的,並且鼓勵我要比別人更加的努力認真。在遭遇困難卡關時,老師總是耐心且細心的幫助我的思緒釐清,以不至於多走了許多冤枉路。下線的成功也多虧於老師用心的給予許多意見並幫助修改報告,在此我表達萬分的謝意。另外,我要特別感謝旭傑及朝陽學長在架設量測系統上的幫忙。並謝謝、建宏、大鈞、依珊、英哲、小豪、KB、學長學姐們在研究及實驗上的協助與解析。而與我同屆的柏仰、柏存、庭聿、雅婷,你們都很棒,在各自畢業的未來期許我們大家都有個美好的明天。學弟政儒、宏任也非常謝謝你們在量測上的幫忙,記得,在成功的路上難免有挫折和瓶頸,堅持到底、莫忘初衷,你們一定會做得比我更好。其他學弟妹們,加油,我相信你們都做得到。

最後我要感謝我的家人和朋友,我的父母辛苦的養育教育我,使我能勇敢的成長,放心的念書。也謝謝哥哥在每次遇到難關時給我的鼓勵與打氣。我一群中興的死黨們,加油,你們一定都能順利畢業的。在最後的最後,我要非常用力的感謝我可愛的女朋友壹婷,任何研究的狀況妳一定掌握著最前線的消息,雖然妳不懂什麼是半導體,卻代表著妳對我有多重要,妳的鼓勵與笑容,常使得我在低潮時恢復戰鬥的勇氣,有妳真好。

僅以此論文獻給我最愛的家人以及關心我的師友們。

戴嘉邑 2010/8/25

# 目錄

| 中文摘要 |      |           |              | i   |

|------|------|-----------|--------------|-----|

| 英文摘要 |      |           |              | ii  |

| 致謝   |      |           |              | iii |

| 目錄   |      |           |              | iv  |

| 表目錄  |      |           |              | vi  |

| 圖目錄  |      |           |              | vii |

| 第一章  | 簡介   |           | 111111111    |     |

|      | 1.1  | 研究背景      |              | 1   |

|      | 1.2  | 論文架構      |              | 2   |

| 第二章  | СМС  | OS 單光子崩   | 清二極體(SPAD)   |     |

|      | 2. 1 | 光偵測原理     | T X E        | 3   |

|      | 2.2  | 單光子崩潰     | 貴二極體基本特性     | 7   |

|      |      | 2. 2. 1   | 暗計數(DCs) 896 | 10  |

|      |      | 2. 2. 2   | 單光子偵測效率(PDE) | 12  |

|      |      | 2. 2. 3   | 雜訊等效功率(NEP)  | 13  |

|      |      | 2. 2. 4   | 時間解析度        | 15  |

|      | 2.3  | CMOS 單光   | 子偵測器         | 16  |

| 第三章  | TCA  | D 元件模擬    | 與模型建立        |     |

|      | 3. 1 | Sentaurus | 電性模擬         | 19  |

|      | 3. 2 | EMW 光性核   | 莫擬           | 23  |

|      |      | 3. 2. 1   | 吸收係數效應       | 24  |

|      |      | 3. 2. 2   | 入射光強度與波長相關性  | 25  |

|      |      | 3. 2. 3   | 反射率與響應率      | 26  |

|      |      | 3. 2. 4   | 光栅結構效應       | 28  |

|      | 3.3  | 元件暫態特性模擬                   | 32 |

|------|------|----------------------------|----|

|      |      | 3.3.1 暫態響應                 | 32 |

|      |      | 3.3.2 Passive-Quenching 電路 | 34 |

|      | 3.4  | 元件佈局與設計                    | 39 |

| 第四章  | 實驗   | 結果與討論                      |    |

|      | 4. 1 | 晶片佈局結果討論                   | 41 |

|      | 4. 2 | Linear-mode 量測結果           | 43 |

|      |      | 4.2.1 量測技巧與環境              | 43 |

|      |      | 4.2.2 直流響應                 | 46 |

|      |      | 4.2.3 暫態響應                 | 52 |

|      | 4.3  | Geiger-mode 量測結果           | 56 |

|      |      | 4.3.1 量測技巧與環境              | 56 |

|      |      | 4.3.2 Passive-Quenching 電路 | 59 |

| 第五章  | 結論   | 與未來展望                      | 64 |

| 參考文獻 |      | 1896                       | 65 |

| 簡歷   |      |                            | 67 |

|      |      |                            |    |

# 表目錄

| 表 3-1 | 預計製作光栅結構表    | 31 |

|-------|--------------|----|

| 表 4-1 | 量測電容與計算電容比較表 | 48 |

# 圖目錄

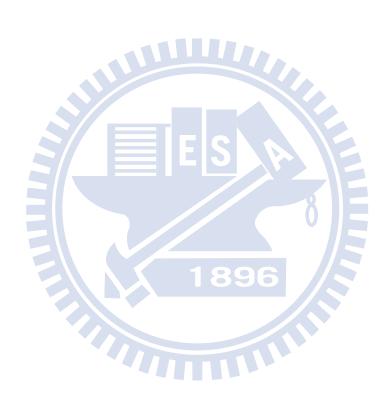

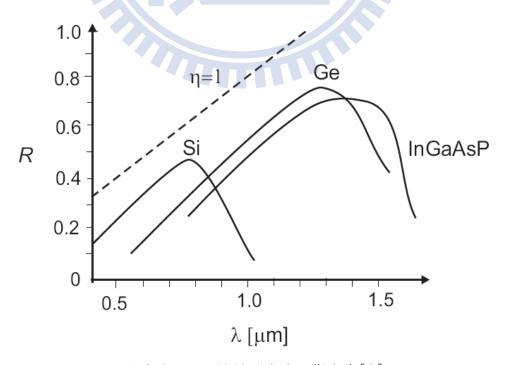

| 啚 | 2-1  | 不同材料吸收係數與光波長之關係                       | 4  |

|---|------|---------------------------------------|----|

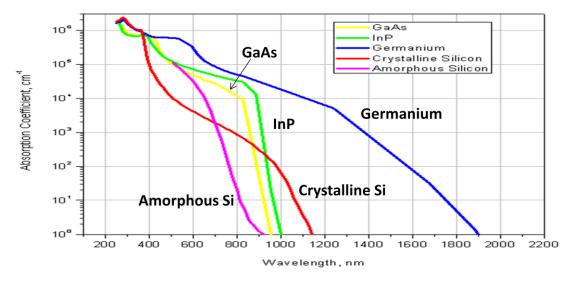

| 邑 | 2-2  | 矽光偵測器入射光波長與吸收係數                       | 4  |

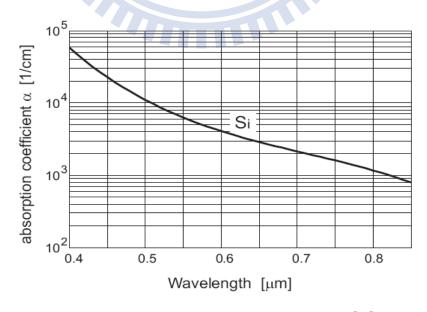

| 邑 | 2-3  | CMOS 光偵測器元件結構與入射光吸收之深度                | 5  |

| 邑 | 2-4  | 不同材料對波長之響應率                           | 6  |

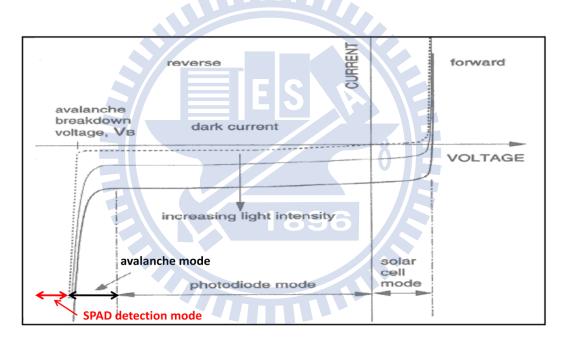

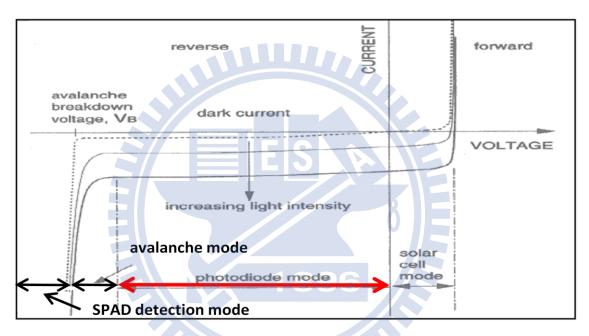

| 昌 | 2-5  | Diode 操作在各種偏壓時的 DC 輸出曲線               | 7  |

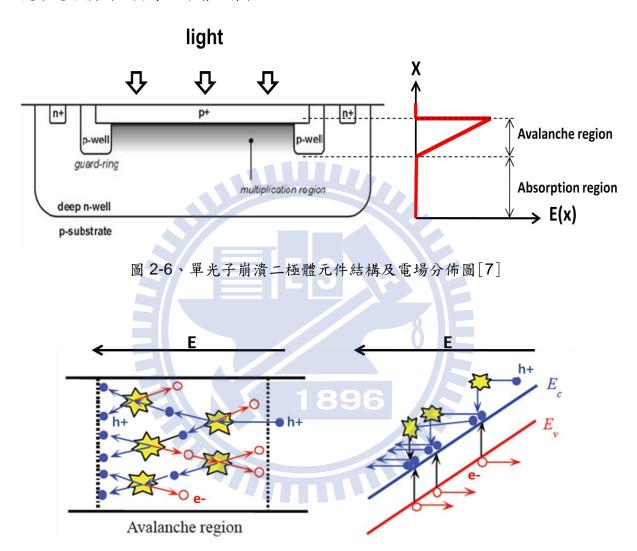

| 昌 | 2-6  | 單光子崩潰二極體元件結構及電場分佈圖                    | 8  |

| 邑 | 2-7  | 圖形表示離子化效應、載子發生碰撞產生電子電洞對               | 8  |

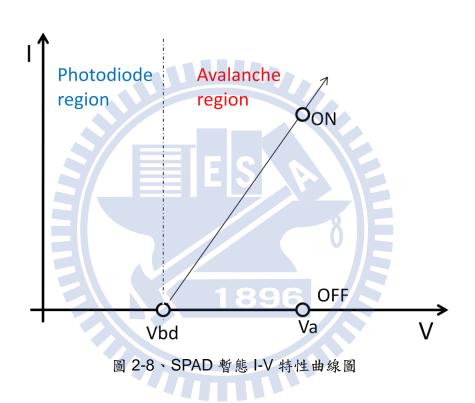

| 置 | 2-8  | SPAD 暫態 I-V 特性曲線圖                     | 9  |

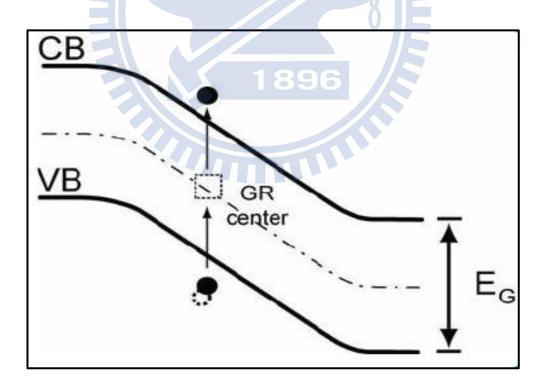

| 邑 | 2-9  | 熱雜訊示意圖                                | 10 |

| 昌 | 2-10 | Trap release 效應                       | 11 |

| 邑 | 2-11 | 偵測面積與暗計數關係圖(Vex=4V、25℃)               | 12 |

| 邑 | 2-12 | 極化係數與電場關係圖                            | 13 |

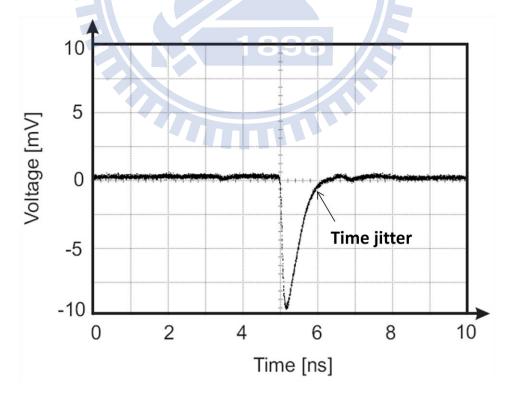

| 邑 | 2-13 | 元件暫態響應圖形 1896                         | 15 |

| 邑 | 2-14 | 早期矽單光子偵測器元件結構                         | 16 |

| 邑 | 2-15 | CMOS 共容技術單光子偵測器元件結構                   | 17 |

| 邑 | 2-16 | CMOS-STI 單光子偵測器元件結構                   | 18 |

| 昌 | 2-17 | CMOS 單光子偵測器整合電路佈局與陣列                  | 18 |

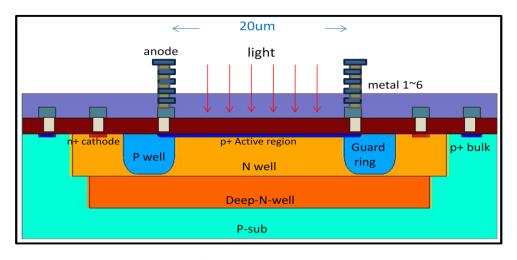

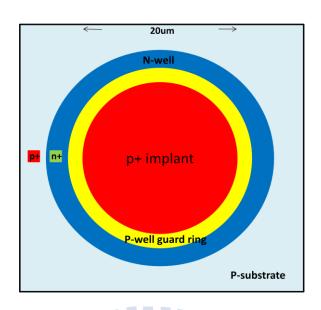

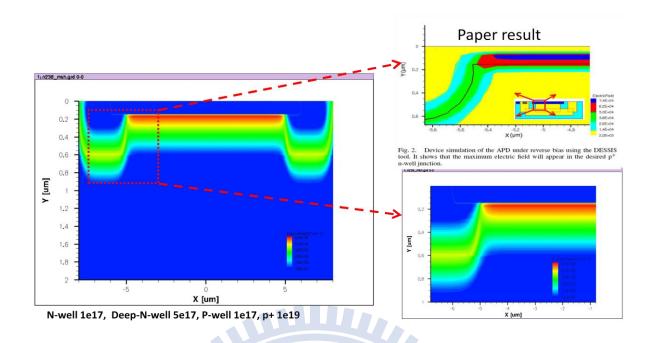

| 昌 | 3-1  | CMOS 單光子崩潰二極體模擬結構(Cross-section view) | 19 |

| 昌 | 3-2  | CMOS 單光子崩潰二極體模擬結構(Plan view)          | 20 |

| 置 | 3-3  | SPAD 元件模擬電場分佈圖                        | 21 |

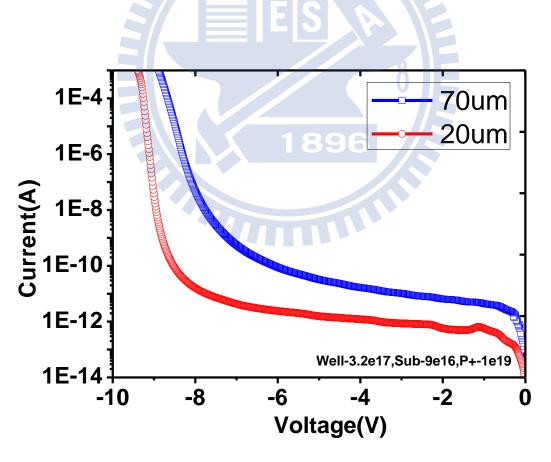

| 置 | 3-4  | SPAD 元件模擬 I-V 特性曲線                    | 21 |

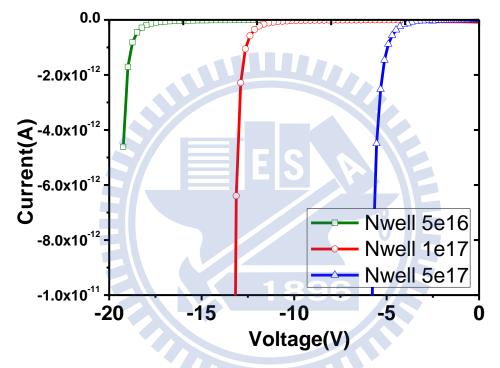

| 圖 | 3-5  | 崩潰電壓隨 Nwell 摻雜濃度變異圖                   | 22 |

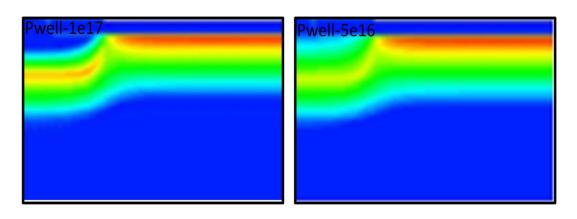

| 昌 | 3-6  | Pwell 摻雜濃度對電場均勻度影響圖                   | 22 |

| 圖 3-7  | 接面深度製程變異模擬                | 23 |

|--------|---------------------------|----|

| 圖 3-8  | Silicon 在不同入射光波長下之吸收圖形    | 24 |

| 圖 3-9  | 光電流與入射光強度及波長關係圖           | 25 |

| 圖 3-10 | 光電流與 Nwell 摻雜濃度及波長關係圖     | 26 |

| 圖 3-11 | SPAD反射率模擬圖                | 27 |

| 圖 3-12 | SPAD 響應率隨光波長變化圖           | 27 |

| 圖 3-13 | 光柵結構與光子入射載子吸收路徑示意圖        | 28 |

| 圖 3-14 | 光柵繞射示意圖                   | 29 |

| 圖 3-15 | 理想光柵繞射階數圖                 | 29 |

| 圖 3-16 | 400nm、470nm 金屬光柵響應率提升比較圖  | 30 |

| 圖 3-17 | 脈衝雷射訊號模擬圖                 | 32 |

| 圖 3-18 | 400nm 脈衝雷射暫態響應模擬結果        | 33 |

| 圖 3-19 | 780nm 脈衝雷射暫態響應模擬結果        | 33 |

| 圖 3-20 | 超額偏壓 0.5V 下元件暫態響應模擬圖      | 34 |

| 圖 3-21 | Passive-Quenching 電路示意圖   | 35 |

| 圖 3-22 | 模擬 Passive-quenching 崩潰機制 | 35 |

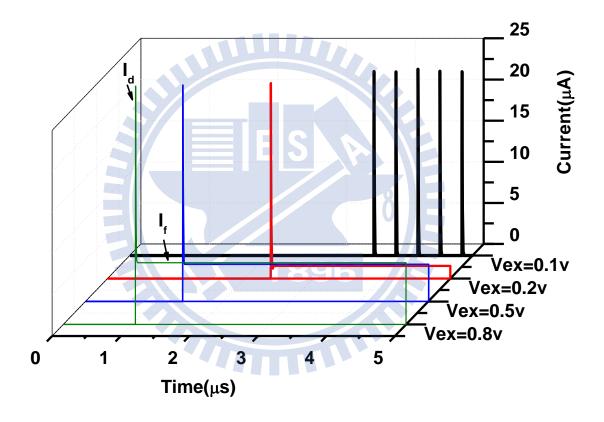

| 圖 3-23 | 模擬改變超額偏壓下 SPAD 暫態電流大小     | 36 |

| 圖 3-24 | 模擬改變 RL電阻下 SPAD 重複崩潰電壓變化  | 37 |

| 圖 3-25 | 模擬改變寄生電容 Cs 下 SPAD 電壓電流變化 | 38 |

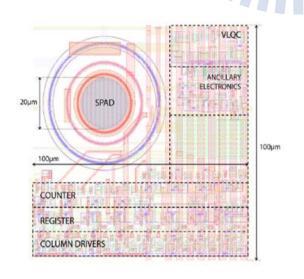

| 圖 3-26 | SPAD 元件設計結構圖              | 40 |

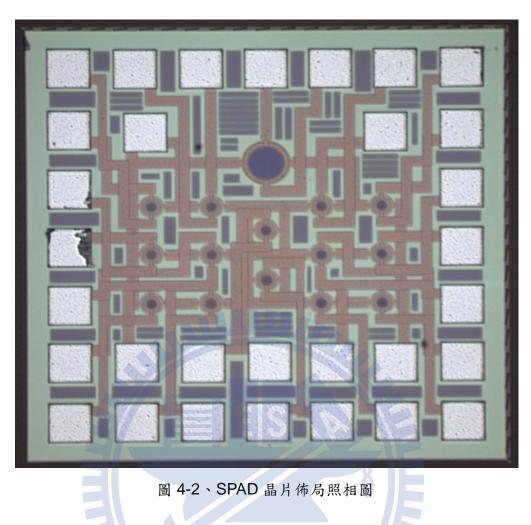

| 圖 3-27 | SPAD 晶片佈局圖(851µm×851µm)   | 40 |

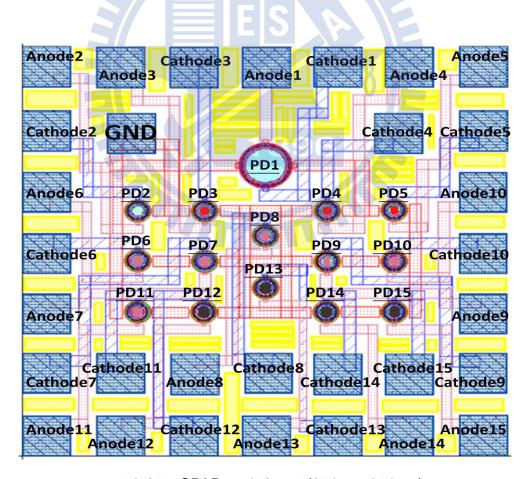

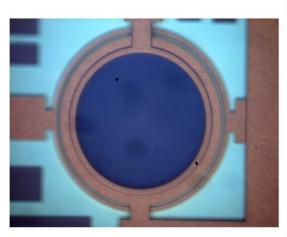

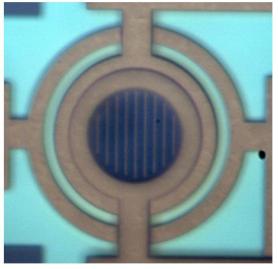

| 圖 4-1  | SPAD 元件結構照相圖              | 41 |

| 圖 4-2  | SPAD 晶片佈局照相圖              | 42 |

| 圖 4-3  | Linear-mode IV 曲線示意圖      | 43 |

| 圖 4-4  | IV、CV 量測系統                | 44 |

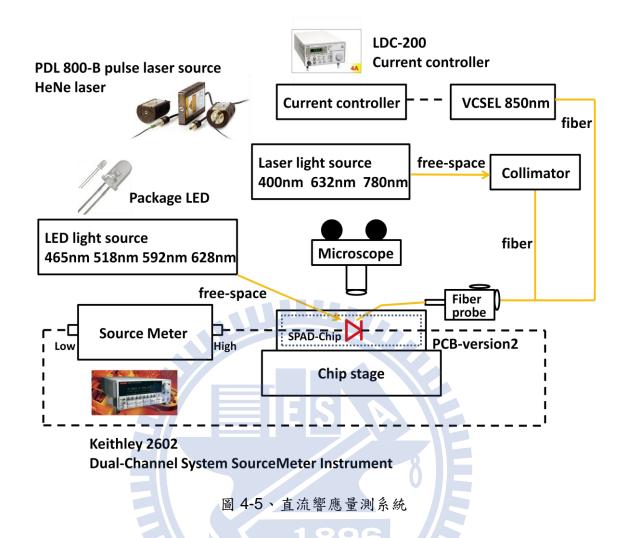

| 圖 4-5  | 直流響應量測系統                  | 45 |

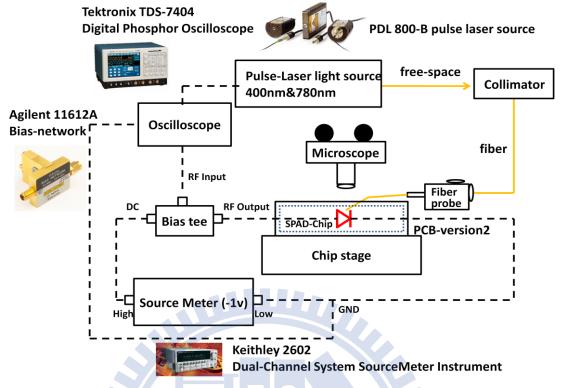

| 圖 4-6  | 暫態響應量測系統                              | 46 |

|--------|---------------------------------------|----|

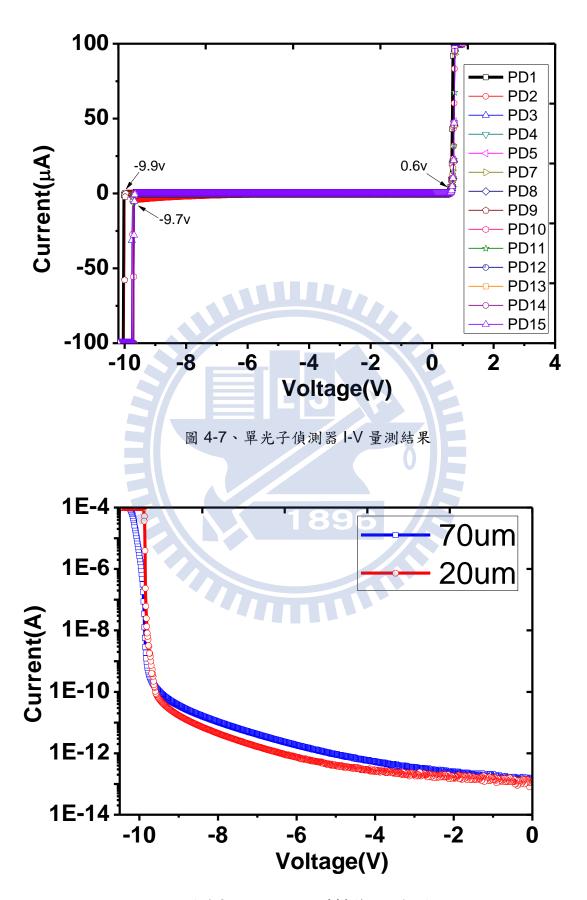

| 圖 4-7  | 單光子偵測器 I-V 量測結果                       | 47 |

| 圖 4-8  | 不同面積下 I-V 特性比較圖                       | 47 |

| 圖 4-9  | 單光子偵測器 C-V 量測結果                       | 48 |

| 圖 4-10 | 雷射光源下直流響應曲線                           | 49 |

| 圖 4-11 | LED 光源下直流響應 I-V 曲線                    | 49 |

| 圖 4-12 | SPAD 直流響應隨波長變化圖量測與模擬比較                | 50 |

| 圖 4-13 | 400nm 雷射光源金屬光柵響應比較圖                   | 51 |

| 圖 4-14 | 465nm LED 光源金屬光柵響應比較圖                 | 51 |

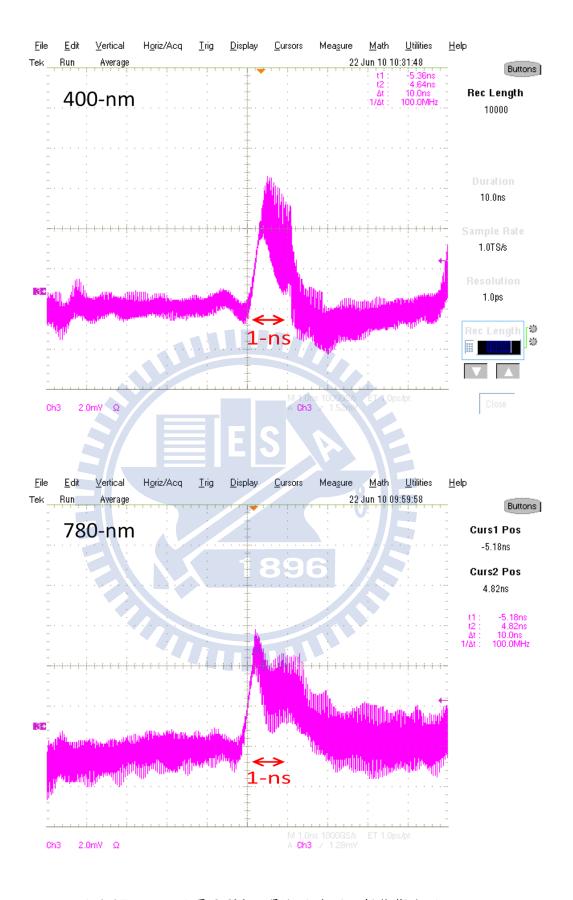

| 圖 4-15 | 400nm 脈衝雷射暫態響應量測圖形                    | 53 |

| 圖 4-16 | 780nm 脈衝雷射暫態響應量測圖形                    | 54 |

| 圖 4-17 | 超額偏壓 0.2V 下單光子偵測器暫態響應圖                | 55 |

| 圖 4-18 | Geiger-mode IV 曲線示意圖                  | 56 |

| 圖 4-19 | 單光子偵測器量測系統(Passive-quenching)         | 57 |

| 圖 4-20 | PCB板設計圖 1896                          | 58 |

| 圖 4-21 | Passive-quenching 電路示意圖               | 58 |

| 圖 4-22 | Passive-quenching 電路 RL電流與 Rs 電壓相對關係圖 | 59 |

| 圖 4-23 | 不同顆 SPAD 量測暗計數隨超額偏壓改變情形               | 60 |

| 圖 4-24 | 量測不同直徑大小 SPAD 暗計數比較圖                  | 61 |

| 圖 4-25 | 量測不同直徑大小 SPAD 單光子偵測效率比較圖              | 61 |

| 圖 4-26 | 量測有金屬光柵下 SPAD 單光子偵測效率比較圖              | 62 |

| 圖 4-27 | SPAD 雜訊等效功率值                          | 63 |

## 第一章 簡介

#### 1.1 研究背景

近年來由於量子密碼(Quantum Cryptography),時間解析的光激光量測(Time Resolved Photoluminescence),3D影像處理,生命科學及天文探測方面的應用需求,大量刺激著影像技術的提升,因此具有高偵測度及快速響應的單光子偵測器迅速發展。

早期關於單光子偵測器方面的研究,較偏向使用光電倍增管(Photomultiplier Tube),但是隨著微型化及輕便化的目標,光電倍增管需要太大的體積及相當高的操作電壓(~1700V Hamamatsu),而且使用真空管既昂貴又易碎。近年來隨著 IC 製程技術的不斷進步,電荷耦合元件(CCD)與主動像素感測器(APS)亦朝著提升偵測速度及靈敏度的目標邁進,然而在微量光子計算上,CCD 在吸收光之後,電荷從 CCD 中釋放的時間過長(約2 ms),使得重複速度過慢。或是必須操作在非常低溫及高度最佳化下的外部電路,以避免雜訊過大導致無法偵測。此外量子點也可用於偵測單光子,但目前仍停留在學術研究階段,因為量子點本身的面積太小而導致探測光的難度增加,偵測效率大約只有 1%,且同樣的因為面積過小的問題大大增加了讀取訊號的困難度。

相較之下 CMOS 單光子崩潰二極體偵測器有著小體積[1]、低操作電壓、低功耗、耐用性佳、及與外部電路整合成單一晶片的優勢,若能在維持低雜訊下有效提升矽單光子偵測器的偵測效率,對於其在 2D 或 3D 光偵測器、影像感測器與其他應用上的發展必有相當大的助益。所以,本論文目標在利用 CMOS 標準製程實現單光子偵測器,並且利用金屬光柵結構有效提升載子吸收效率,達到操作在 Geiger mode 時[2],增加單光子偵測效率的目的。

### 1.2 論文架構

本論文由五個章節架構而成。第二章將介紹光偵測基本原理,並探討材料吸收係數造成的影響,接著討論二極體累增崩潰基本理論、操作特性及單光子偵測器主要參數,最後切入本篇論文重點,CMOS單光子偵測器,比較製程間差異及元件結構所造成的影響。第三章利用 Sentaurus-TCAD 元件模擬軟體進行元件模型的建立與製程變異預測,並模擬二極體在入射雷射光後的各項特性及光柵結構最佳化。最後計算元件暫態響應及外部電路連接,完成元件的佈局與設計。第四章講述量測的方法及環境,並以二極體不同操作區域及量測模式,分別討論實驗的量測結果。第五章為結論與未來的展望。

## 第二章 CMOS 單光子崩潰二極體

材料吸收係數的差異,直接影響著光偵測器的使用波段。然而,設計一個兼具速度與高響應的光偵測器必須在元件結構、製程難易度及外部電路影響下做取捨。在本章中將就光偵測基本原理,探討材料吸收係數造成的影響,並討論二極體累增崩潰基本理論、操作特性及單光子偵測主要參數。最後就本篇論文的重點,CMOS單光子偵測器,做深入的探討與比較。

#### 2.1 光偵測原理

- 一種能將光能量轉換成電能量的半導體感測器我們即稱為半導體光偵測器。因此, 如何有效率的在光電轉換的過程中減少損失與消耗,便為設計光偵測器的主要訴求。 對於現今半導體光偵測器,有著四個主要因素影響著最後的光偵測效能:

- (1)光穿透率,(2)材料吸收,(3)量子效率,(4)電荷傳輸效率。[3]

- (1)光穿透率即為光在入射後至偵測器結構吸收前因為不同材料所造成的表面反射。一般來說,反射率皆可經由表面鍍上抗反射層(Anti-Reflection-Coating)達到相當程度的減少,然而此結構無法於 CMOS 標準製程中達成。

- (2)當光打入光偵測器後,在光能量大於材料能隙 (Bandgap) 的條件下,位於價帶的電子將躍升至傳導帶產生電子電洞對,決定電子電洞對數量的因子便為材料吸收係數  $\alpha$  (Absorption Coefficient)其倒數定義為入射深度(Penetration Depth)。此外由於吸收係數的影響,入射光的強度會隨著入射深度成指數的衰減,  $I \propto e^{-\alpha x}$  ,對特定波長而言,吸收係數為一定值,如圖 2-1 所示。

圖 2-1、不同材料吸收係數與光波長之關係[4]

然而對 CMOS 製程而言,矽的吸收係數可由方程式(2-1)近似(λ為入射光波長(μm)),而得到圖 2-2 之相對關係。圖中我們可以了解,矽吸收係數隨著波長減少呈指數增加,在入射光大於 0.95 μm 時因吸收過低而無法產生載子,小於 0.4 μm 因大量載子產生過於靠近表面而使表面復合率相當高。因此,CMOS 光偵測器操作範圍約在 0.4-0.85 μm。

### 1896

$$\alpha = 10^{13.2131 - 36.7985\lambda + 48.1893\lambda^2 - 22.5562\lambda^3} \quad 1/[cm]$$

(2-1)

圖 2-2、矽光偵測器入射光波長與吸收係數[3]

- (3)量子效率(Quantum Yield)定義為每吸收一個光子可激發電子電洞對的機率。 理想上一顆光子可產生一組電子電洞對。

- (4)電荷收集效率(Charge Collection Efficiency)決定了光偵測器的速度與響應率。為了使光偵測器有最好的特性,若能使大部分光子在空乏區內吸收,利用較快的飄移(drift)機制傳輸少數載子,避免少數載子在通過空乏區前復合,就能達到高速度、高響應的效果。在空乏區外的載子則由較慢的擴散(Diffusion)機制傳輸,光電流即為此兩種機制收集到的載子總和。然而緩慢的擴散載子在暫態響應上產生的尾狀響應(Tail Response),限制了光偵測器的速度,距離空乏區過遠的吸收甚至無法貢獻響應率。因此,在圖 2-3 中顯示 CMOS 光偵測器元件結構與入射光吸收之深度,並可發現波長為 400nm 在深度大於 0.5µm 時以幾乎完全被吸收,而 850nm 在大於 10µm 時仍有一半的光未被吸收。因此,如何在 CMOS 製程下利用最有效的接面深度在最適當的吸收波段達到最好的偵測效能與頻寬便是設計光偵測器上的一大課題。

圖 2-3、CMOS 光偵測器元件結構與入射光吸收之深度[3]

最後,根據以上四個主要因素,我們定義兩個重要的參數[5]:

$$\eta_{ph}(\text{Quantum Efficiency}) = \frac{I_{ph}/q}{P_{inc}/h\nu} = \frac{\text{Number of induced electrons}}{\text{Number of photons}}$$

(2-2)

$$R(Responsivity) = \frac{I_{ph}}{P_{inc}} = \frac{\eta_{ph}e}{h\nu} = \frac{Photocurrent}{Incident power}$$

(2-3)

量子效率(Quantum Efficiency)代表平均每入射一顆光子可產生多少電子電洞對被收集到。也就是一顆光子經過有可能的損失與消耗後,最後產生載子被偵測到的機率。

響應率(Responsivity)則代表每單位入射光能量所能產生的電流比例。若我們假設量子效率最理想為 1 時,對波長  $0.4~\mu m\sim 0.85~\mu m$  入射光而言,其響應率約為  $0.32\sim 0.68$  A/W。圖 2-4 為不同材料對光波長的響應率,矽材料響應率最大值約在  $0.78~\mu m$ 。

圖 2-4、不同材料對波長之響應率[3]

#### 2.2 單光子崩潰二極體基本特性

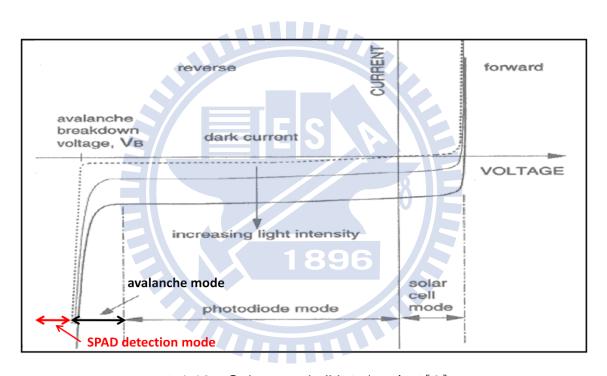

一般二極體的操作電壓因應用的不同大致分成三種不同的操作區,分別為 solar cell 區、photodiode 區與 avalanche 區如圖 2-5 所示。光偵測器通常使用後兩區,而兩區間差異可以用其增益係數來區別,photodiode 的增益係數為 1,而 avalanche 區的增益係數通常大於 1,介於 10-100 之間,然而,單光子崩潰二極體偵測器運作時,有別於傳統光偵測器操作在 photodiode 區,或是一般光崩潰二極體操作在低於崩潰電壓(約 1~2V)的 avalanche 區,而是操作在高於元件崩潰電壓(約 0.5~5 V)區域[6]。

圖 2-5、Diode 操作在各種偏壓時的 DC 輸出曲線[6]

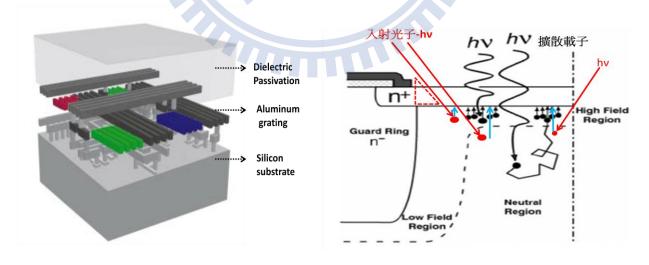

有別於傳統光偵測器,單光子偵測器在操作電壓區域或元件結構上有著截然不同的呈現,單光子崩潰二極體的基本結構,與 avalanche diode 相似,而相較於 pn 接面光二極體來說多了一層摻雜量較吸收層高的 p+層如圖 2-6 所示,因此當元件操作在高負偏壓下 p+層與 n-well 接面形成空乏區並同時承受很大的電場,此區域即為 SPAD 特有的累增層(Avalanche Region),當光進入偵測器且被吸收層吸收產生光載子,即被內建電場掃進累增層中,累增層內部的大電位差會對載子加速且同時增加載子所具

有的能量,當載子能量超過活化能(Activation Energy)時,便會藉由碰撞而產生新的電子電洞對,此程序持續的進行下便會形成所謂的累增離子化效應如圖 2-7 所示。在此效應下,當一個電子進入偵測器的累增層後,會產生大量的電子輸出,於是可知此層使單光子偵測器具有內部增益存在。

圖 2-7、圖形表示離子化效應、載子發生碰撞產生電子電洞對[6]

與 avalanche photodiode 不同的是,對於單光子偵測器來說,在偵測光子時利用的是高於崩潰電壓的暫態特性,當偵測器操作在高於崩潰電壓時,會具有的兩種暫態 I-V 特性如圖 2-8 所示,ON 曲線代表著操作在崩潰電壓之上且有發生崩潰電流,而 OFF 曲線代表著操作在崩潰電壓之上時但並沒有發生崩潰效應所代表的 I-V 特性,此

一OFF特性曲線是在DC的量測結果中不會發現的。當元件電壓高於崩潰電壓的瞬間,需要一段時間(約數 ns 至數μs)產生崩潰電流,如果光子在此期間進入元件產生光電流,就會造成元件崩潰而據以判定已偵測到光子,透過以上機制的了解,可以將單光子崩潰二極體在光偵測過程分為光吸收與累增崩潰效應兩個部分,對於傳統光偵測器與單光子偵測器來說,吸收光產生載子的機制並沒有不同,但在累增效應的差異性,決定了單光子偵測器是否可以偵測單光子的關鍵能力。

介紹完光偵測基本原理並了解單光子崩潰二極體在 DC 與暫態下有著不同的操作特性後,接下來將針對決定單光子偵測器特性好壞的主要參數分別做介紹,進一步了解單光子偵測器操作時的物理特性。

#### 2.2.1 暗計數(DCs)

單光子偵測器雖然與一般光偵測器的操作不同,但運作在崩潰電壓之上的單光子 偵測器仍須克服的一項重要特性便是雜訊,而影響著單光子偵測器的主要雜訊參數便 是暗計數(Dark counts)。單光子偵測系統經由計數器累計偵測訊號,然而系統使用時 無法區分單一次累增崩潰效應是由光子或暗載子所產生,因此必須先計算在無光子下 所產生的偵測訊號,此訊號即為暗計數(Dark counts)。

暗計數的大小由下列兩個現象所主導[6]:

- (1) 熱雜訊,(2) Trap release 效應。

- (1)熱雜訊是由於在高溫時,電子因熱能導致由價帶被激發到導帶上形成電流,因 此我們可以透過降溫的方式來降低熱雜訊的發生如圖 2-9。

圖 2-9、熱雜訊示意圖[6]

(2)Trap release 效又稱為 After Pulsing 效應如圖 2-10。在累增崩潰期間大電流流經元件內部時填滿了元件內部的 Trap Center,使 SPAD 再度探測時有一定的機率計算到從 Trap Center 中釋放出來的載子而形成重複的計數。

圖 2-10、Trap release 效應[6]

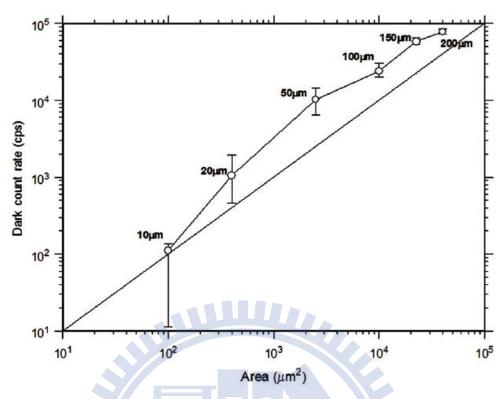

Trap center 的數量與材料本身的缺陷數量有關,對於III-V族材料來說,磊晶所造成的晶格不匹配,均勻度相對較差及陡變接面的存在,勢必會造成天生缺陷較多的問題。然而對於 Silicon SPAD 來說,矽材料本身缺陷數較少,因此本身受到捕捉釋放的影響較少,After Pulsing 效應相對較低。而不論是何種材料,偵測面積越大意謂著材料缺陷的數量越多,因此單光子偵測器直徑越大, After Pulsing 效應將越嚴重,暗計數越高。圖 2-11 中顯示暗計數隨著偵測面積等比例的增加。

圖 2-11、偵測面積與暗計數關係圖(Vex=4V、25℃) [8]

無論是降低材料的缺陷、減少偵測器面積或是低溫下操作,如何減少暗計數的數量是現今致力於增進單光子偵測器能力的一大方向。因此在元件設計上,如何降低單光子偵測器雜訊便是一大課題。

#### 2.2.2 單光子偵測效率(PDE)

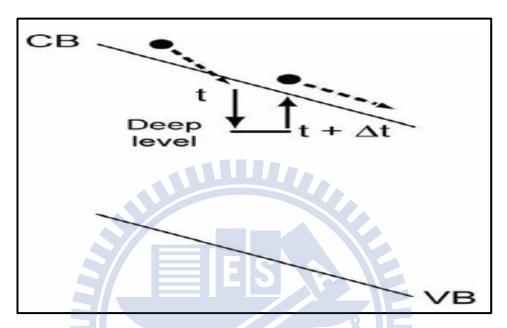

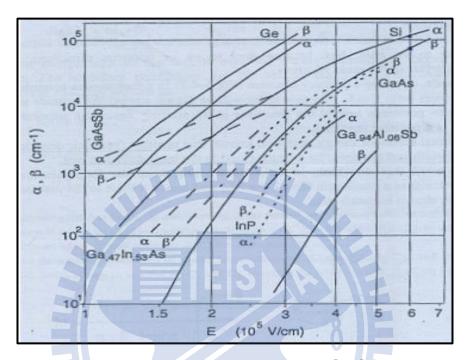

在2.1節中我們提到了量子效率(Quantum Efficiency)代表平均每入射一顆光子可產生多少電子電洞對被收集到的機率,然而單光子崩潰二極體操作在崩潰區以上時,代表光偵測能力的指標將由量子效率再乘上 Trigger Probability 所組成。Trigger-Probability 代表著光子所產生的電子電洞對在進入高電場的累增層後有多少的機率可以產生可自我維持的累增崩潰機制[9]。影響 Trigger Probability 的因子便是材料游離

係數(Ionization coefficient)。 $\alpha$ 、 $\beta$ 各代表著電子及電洞每單位距離下可產生多少新的電子電洞對,倒數則代表每產生一個新的電子電洞對,電子及電洞各所需要的平均自由路徑如圖 2-12 所示。

圖 2-12、極化係數與電場關係圖[10]

## 1896

最後我們定義單光子偵測效率為每入射一顆光子是否可產生累增崩潰電流並由計數器量測到的機率(公式 2-4),其中  $\eta_{QE}$  為量子效率, $\eta_{Trig}$  為 Trigger Probability。

PDE =

$$\eta_{QE} \cdot \eta_{Trig} = \frac{Count_{signal} \cdot h\nu \cdot e}{P_{incident}} \times 100\%$$

(2-4)

### 2.2.3 雜訊等效功率(NEP)

雜訊等效功率(NEP)是對於判別光偵測器好壞一個最重要的特性指標,並可藉由 比較 NEP 的值來分辨兩者之間好壞,其定義為需要多少光的能量產生光電流使得與 雜訊電流相同。又可定義為需要多少光量才可以使 SPAD 的 SNR 值等於一。 單光子偵測器的訊號輸出分佈是遵照 Poisson distribution 的理論,Poisson distribution 的輸出平均值為 M,標準差則為 $\sqrt{M}$ ,在了解 Poisson distribution 的平均值與標準差之後,即可代入討論單光子偵測器的 SNR 與 NEP。

單光子偵測器 SNR 與 NEP 公式推導[6]:

有光環境下1秒鐘積分時間內的訊號總合=光計數+暗計數

$$S_{S+D} = (N_S + N_D) \pm (N_S + N_D)^{1/2}$$

無光環境下1秒鐘積分時間內訊號總合=暗計數

$$S_D = (N_D) \pm (N_D)^{1/2}$$

將上述兩項相減可得光訊號造成的計數值

$$S_S = (N_S) \pm (N_S + 2N_D)^{1/2}$$

經由 SNR 公式將光訊號平均值除與標準差即可得到 SNR 值

$$SNR = \frac{s_S}{\Delta s_S} = N_S / (N_S + 2N_D)$$

因此當 SNR=1 時 N<sub>S</sub>=N<sub>S</sub>+2N<sub>D</sub> ,且從單光子偵測效率中我們可以得到

$$PDE = \frac{N_{s} \cdot h\nu \cdot e}{P_{in}} \qquad \Longrightarrow \qquad P_{in} = \frac{h\nu \cdot e}{PDE} \sqrt{N_{S+} 2N_{D}}$$

且因 N<sub>D</sub>>>>N<sub>S</sub> ,最後我們得到雜訊等效功率 (公式 2-5)

$$NEP = \frac{h\nu \cdot e}{PDE} \sqrt{2N_D}$$

(2-5)

PDE 為單光子偵測效率, $N_D$ 是暗計數,h 是浦郎克常數,U 是光的頻率。

#### 2.2.4 時間解析度

在單光子偵測器中,提升偵測效率與抑制雜訊固然為做為偵測器的一大重點。然而對於 SPAD,偵測速度的快慢同樣也決定了可以偵測訊號的多寡,因此時間解析度 (Timing resolution)的減少代表著元件操作速度的提升。藉由 time jitter 我們可以得知單光子偵測器的時間解析度,定義為光子入射時間與最後得到電流訊號的時間差。

在元件中高速的飄移載子擁有最快的響應速度。然而,緩慢的擴散載子才是造成元件 time jitter 拉長與頻寬下降的主因。因此,偵測器材料對光吸收深度的不同與元件空乏區與吸收區的深淺長短便是造成單光子偵測器時間解析度強弱的關鍵因素。

我們可以藉由入射不同波長的 picosecond laser pulse 來得到 SPAD 在不同光波長下 time jitter 的多寡,也就是暫態響應(Transient response)如圖 2-13 所示,另外 Time Correlated Single Photon Counting(TCSPC)及量測元件頻率響應,同樣的也可以得知元件操作速度的快慢。

圖 2-13、元件暫態響應圖形[3]

#### 2.3 CMOS 單光子偵測器

單光子崩潰二極體(Single-Photon-Avalanche-Diode)發展至今,由於材料吸收係數的差異,操作在 Geiger-Mode 的單光子崩潰二極體對於 1.3 μm 與 1.55 μm 等通訊波段的光源探測必須使用 InGaAs/InP 等材料製成的單光子崩潰二極體來偵測,雖然InGaAs/InP 單光子崩潰二極體有著相當高的偵測效率,但無法偵測可見光以及外部電路整合一直是其兩大問題。而利用 CMOS 製程所製作的矽單光子崩潰二極體偵測器,具有能夠偵測可見光範圍及易與外部電路整合成單一晶片的優勢,雖然因為製程的限制及矽材料吸收係數的偏低造成偵測效率普遍不高,然而由於 CMOS 製程技術不斷的進步,矽單光子偵測器近年來發展備受關注。

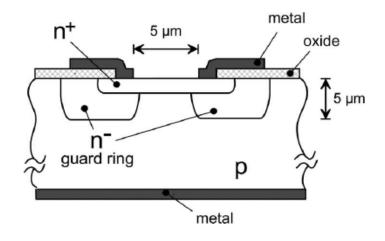

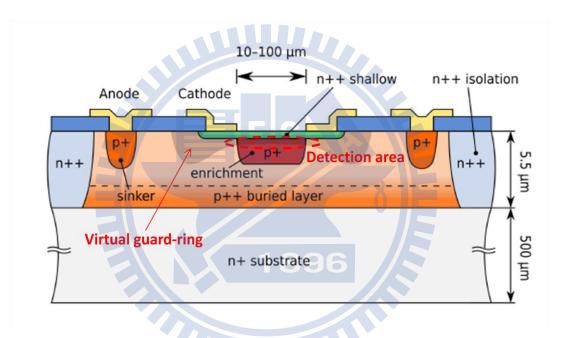

矽單光子偵測器的發展由早期簡單的 p-n 接面搭配 guard-ring 漸漸形成兩大主流如圖 2-14 所示[11],其一為由磊晶技術製作的矽基板相容在 CMOS 製程中如圖 2-15,提升矽晶圓品質,對於表面缺陷相當敏感的單光子偵測器有著很好的特性提升,並且使用電子做為少數載子提升元件崩潰機率,然而此一製程並無法相容於 CMOS 標準製程中。相較之下由 CMOS 標準製程所發展的單光子偵測器如圖 2-6,雖然沒有較好的矽晶圓品質且使用電洞為少數載子做為主要崩潰機制,但減少元件崩潰機率同時也降低了雜訊的產生,且因為使用標準製程的方便性及有效的節省成本,進展尤其快速。

圖 2-14、早期矽單光子偵測器元件結構[11]

無論是 CMOS 共容技術或 CMOS 標準製程技術,單光子崩潰二極體在操作時皆需要維持著均勻的大電場,並且避免接面的角落有著較宰的空乏區形成較高的峰值電場而導致電流集中在邊緣,此種效應導致元件的提前崩潰,崩潰機制不再由主要偵測區主導而是由接面的邊緣效應所控制。Guard-ring 的設計便是邊緣消除峰值電場的功用,無論是 p-well、STI 或共容技術中的虛擬 guard-ring[12],皆能有效減少元件角落電場大小,然而 CMOS 共容技術所使用之虛擬 guard-ring 並無法相容在標準製程中因此我們不多加描述。

圖 2-15、CMOS 共容技術單光子偵測器元件結構[12]

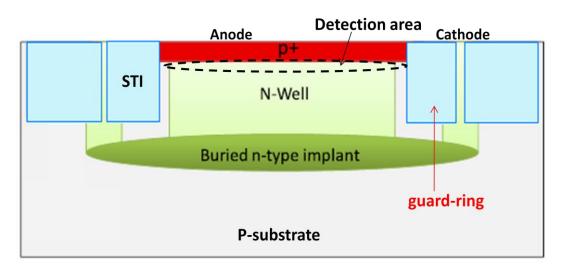

現今 CMOS 標準製程單光子偵測器,朝著提升速度、減少雜訊、以及應用上的發展。已經有人使用 STI(Shallow Trench Isolation)做為 guard-ring 結構有效將元件速度提升至 27 ps (Full-width-half-maximum)如圖 2-16,偵測器直徑縮小至 5 µm 以下[13],以及利用較低濃度的 N-well 掺雜,將 DCR(Dark count rate)降低至 0.22 kHz[14、15]。然而,使用 STI 雖有效避免元件的提前崩潰並縮小偵測器直徑,但因為減少熱退火製程使得 STI 表面缺陷大量增加,導致於非常高的 dark counts。較低濃度的掺雜雖有效降低元件雜訊,但卻造成崩潰電壓較高及內部電場降低使得載子速度的下降。

圖 2-16、CMOS-STI 單光子偵測器元件結構[13]

在應用的發展上,使用 CMOS 標準製程將 Passive or Active quenching circuit 與單光子崩潰二極體整合進單一晶片中如圖 2-17 左所示,減少電路中訊號的損耗,藉以達到快速精準的偵測(約 30 ns) [16]。此外,將單光子崩潰二極體製作成陣列的方式如圖 2-17 右所示,進行 2D 和 3D 影像的處理,都是十分重要的方向。因此,在製作陣列時如何避免偵測器元件間訊號互相干擾、整合成單一晶片電路的匹配性、及解決使用標準製程下欠缺靈活性抑制元件的最佳化設計,都是目前單光子崩潰二極體偵測器主要發展的目標。

圖 2-17、CMOS 單光子偵測器整合電路佈局與陣列[1]

## 第三章 TCAD 元件模擬與模型建立

利用 CMOS 標準製程雖然有著低成本、低功耗、小體積、耐用性佳等種種優勢,然而在元件設計時我們並無法得知製程上確切的相關參數,如摻雜濃度、接面深度、材料參數等。因此,我們必須使用 Technology Computer Aided Design(TCAD)模擬軟體,將 CIC 所提供之製程檔及相關參考論文之參數設定,利用元件模擬來確認我們的設計無誤,並且建立單光子偵測器模型。在本章中我們將使用 Sentaurus TCAD 模擬軟體,分別使用其中之子軟體,完成元件電性上的各項模擬及元件照光後光性上的計算,最後預測元件之暫態響應及 Passive-quenching 電路特性,完成元件之佈局與設計。

### 3.1 Sentaurus 電性模擬

在模擬單光子崩潰二極體的電性時,我們使用如圖 3-1 之結構,並且設定偵測面積直徑約為 20µm。其中我們使用標準 CMOS 製程技術中 source/drain implant P+-Nwell 形成主要偵測接面,也就是放大區。然而一個正常的 P+-Nwell 二極體在崩潰時的電流

圖 3-1、CMOS 單光子崩潰二極體模擬結構(Cross-section view)

圖 3-2、CMOS 單光子崩潰二極體模擬結構(Plan view)

並不均勻分佈在 P<sup>+</sup>區,反倒是因為在接面的角落有著較窄的空乏區形成較高的峰值電場而導致電流集中在邊緣,此種效應導致元件的提前崩潰,崩潰機制不再由 P<sup>+</sup>-Nwell 空乏區主導而是由接面的邊緣效應所控制。然而對於單光子崩潰二極體偵測器而言,需要的是將崩潰區域延伸在整個 P<sup>+</sup>-Nwell 接面上,因此我們使用 Pwell 當成 guard-ring 環繞在整個 P<sup>+</sup>邊緣上,如此將使得元件邊緣上擁有較低電場,藉此大量減少元件邊緣效應避免二極體的提前崩潰。此外為了有效的隔絕元件間的訊號干擾,使用 Deep-Nwell 結構搭配 Nwell 藉此達到有效的隔絕,亦可以避免因 Pwell 與 Nwell 產生之空乏區過大,使得載子擴散長度過長而減低元件的操作速度。

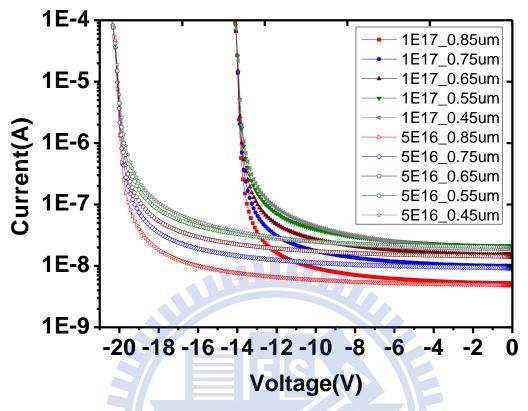

圖 3-3 中顯示元件模擬電場分佈圖,並且可以清楚看到最大電場均勻分佈在主要 偵測區中(紅色部分),達到與其他參考論文中之模擬一致的結果,Pwell 所形成的 guard-ring 成功的降低元件邊緣效應。由模擬計算出的 I-V 特性曲線中如圖 3-4 所示, 我們預測崩潰電壓介於-9~-10V,暗電流值約在10<sup>-12</sup> A,而暗電流值與偵測器面積成 正比關係,圖中可得知直徑 70μm 與 20μm 面積差約 12 倍,暗電流差亦是如此。

接下來我們將考慮 CMOS 標準製程下可能的製程變異,利用元件模擬推估可能對 元件造成的影響。首先針對摻雜濃度對元件的影響,接著確認元件在不同接面深度下 都能維持電場的均勻度。

圖 3-3、SPAD 元件模擬電場分佈圖[16]

圖 3-4、SPAD 元件模擬 I-V 特性曲線

元件的摻雜濃度,影響著單光子崩潰二極體的崩潰機制。若我們改變 Nwell 的摻雜濃度並且固定其他摻雜濃度,將會觀察到崩潰電壓隨著 Nwell 摻雜濃度下降而提升如圖 3-5 所示,此時元件的崩潰機制皆由 P<sup>+</sup>-Nwell 接面所主導。若我們將 Pwell 摻雜濃度降低至 5e+16,Nwell 摻雜濃度一樣做改變,將會發現邊緣的電場因為 guard-ring 摻雜濃度的減少而降低,使得電場更加均勻分布於偵測區如圖 3-6 所示,崩潰電壓則隨著 Nwell 濃度上升而減少。

圖 3-5、崩潰電壓隨 Nwell 摻雜濃度變異圖

圖 3-6、Pwell 摻雜濃度對電場均勻度影響圖

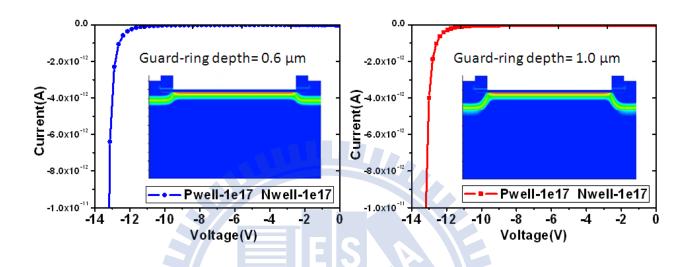

由於 CMOS 標準製程中,無法確切得知接面深度,因此我們改變 Nwell 與 Pwell 的接面深度 0.6µm 及 1.0µm,確認元件在不同接面深度下,仍有很好的表現如圖 3-7 所示。

圖 3-7、接面深度製程變異模擬

經由製程變異模擬,我們可以得知元件 well 的掺雜濃度主導著崩潰電壓及邊緣效應,並且確定在摻雜濃度合理的變異範圍內,皆有良好的元件特性。此外接面的深度改變並不影響元件崩潰電壓,電場的均勻度仍然維持得很好,邊緣效應並不顯著。

#### 3.2 EMW 光性模擬

在確認單光子崩潰二極體元件結構模型後,為了瞭解光打入 SPAD 後不同波長造成的影響,我們首先須定義 TCAD-EMW 模擬入射光的光電場強度為 E(V/m),藉由下面簡單的計算可以得到入射光的能量(Power), 因此可以得知我們在模擬時使用的光量及在計算元件響應率時入射光能量的大小。

$${\rm Incident\ power}(W) = {\rm Power\ density}(W/_{m^2}) \times {\rm Area}(m^2)$$

Power density

$$(W/_{m^2}) = \frac{1}{2} \cdot c \cdot \epsilon_0 \cdot n \cdot E^2$$

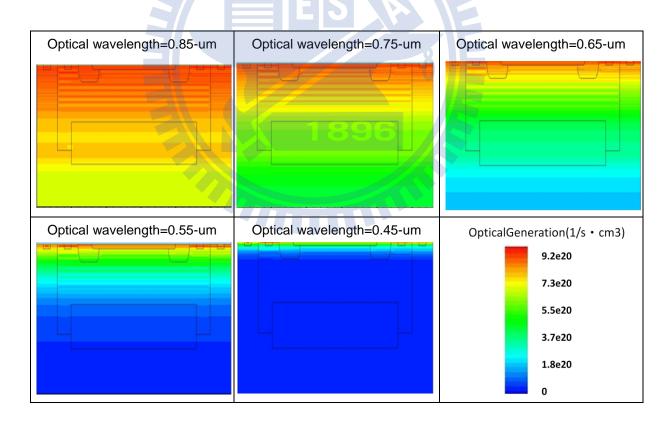

#### 3.2.1 吸收係數效應

由於矽材料對不同波長的光吸收係數的不同,造成光穿透進矽晶圓後強度有著不同的指數性衰減,由圖 3-8 可觀察到,當入射光波長由 0.85µm 減少至 0.45µm,吸收速度增加越快,光穿透路徑快速縮短。

圖 3-8、Silicon 在不同入射光波長下之吸收圖形

#### 3.2.2 入射光強度與波長相關性

入射光強度的不同,影響二極體產生載子的多寡,入射光波長改變,造成不同強度的吸收亦會影響載子的濃度,光電流因此隨之變化。圖 3-9 中我們可以經由模擬證實,當入射光波長越短吸收越強,產生之光電流則些微提升,光強度越大光電流便之變大。另一方面主要崩潰區域(Nwell)的摻雜濃度只影響著崩潰電壓大小,對於光電流則沒有改變如圖 3-10 所示。

圖 3-9、光電流與入射光強度及波長關係圖

圖 3-10、光電流與 Nwell 摻雜濃度及波長關係圖

1896

## 3.2.3 反射率與響應率

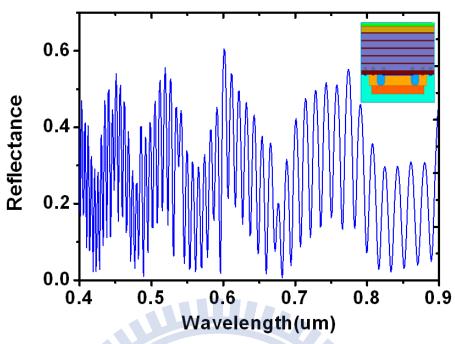

我們首先使用光學計算軟體(Rsoft),利用嚴格耦合波分析(Rigorous Coupled Wave Analysis, RCWA)方法計算 CMOS 標準製程結構下元件之反射率。然而從圖 3-11 結果中可以發現,反射率隨著波長有著非常大的震盪,經由模擬我們推測此原因 可能為 CMOS 製程中之絕緣層及鈍化層所造成如圖 3-11 右上方所示,因此當入射光波長若是稍微改變反射率將會有很大的變化。

圖 3-11、SPAD 反射率模擬圖

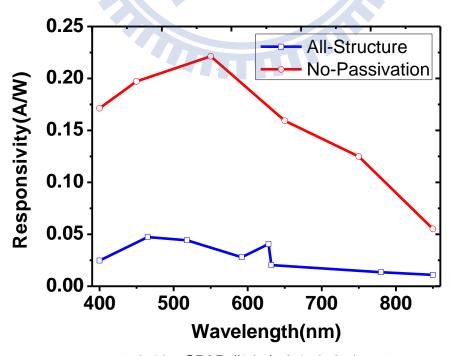

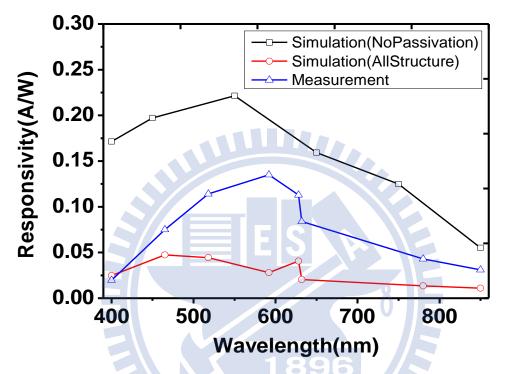

接著由模擬出的光電流,我們可以計算出元件的響應率,圖 3-12 中我們可以得知在真實的單光子崩潰二極體元件中,改變響應率的因素不只是光強度和光頻率,在製程的過程中必須製作的絕緣層以及鈍化層,導致反射率的震盪,使得響應率的下降及改變亦是一大因素。

圖 3-12、SPAD 響應率隨光波長變化圖

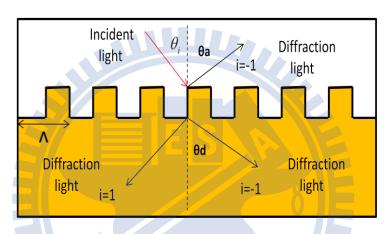

#### 3.2.4 光栅結構效應

在先前的討論中我們有提到,SPAD 在光偵測過程分為光吸收與累增崩潰效應兩個部分,然而對於光吸收部分,由於材料對於不同波長吸收係數的差異,光入射至半導體時,其強度會隨入射深度指數的衰減  $I \propto e^{-\alpha x}$ ,其中 $\alpha$  即為吸收係數,若要增加吸收率通常使用 SOI(Silicon on Insulator)結構在 buried oxide 上鍍 DBR(Distributed Bragg Reflector)結構藉以反射入射光子增加一倍的光吸收路徑,或是在表面鍍上抗反射層(Anti-Reflection coating)減少光子的反射率,然而這些結構皆無法於 CMOS 標準製程中製作。

因此,若我們利用標準 CMOS 製程中的金屬層,適當地設計金屬光柵,使得當光子垂直入射偵測器時產生繞射效應,導致光子等效地以傾斜一個角度入射進矽表面並增加光子穿透率如圖 3-13 所示,此舉不但增加了光子吸收的路徑,且載子擴散路徑並沒有因此增加,藉此在不降低元件偵測速度下增加元件的響應率最終使得光子偵測效率提升。

# 1896

圖 3-13、光栅結構與光子入射載子吸收路徑示意圖[17]

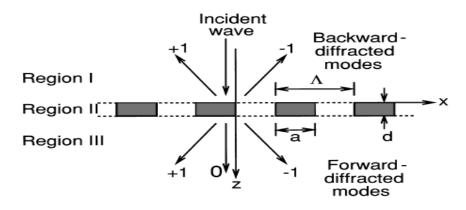

在此我們先介紹光柵繞射基本理論。廣義上,具有週期性的空間結構皆稱為光柵, 而光柵的基本結構,如圖 3-14 所示。當有一道單色光傾斜以一個 θi 角度入射到週期 為Λ的光柵,會因為光柵週期的影響而產生有反射繞射角 θa 的繞射光和透射繞射角 θo 的繞射光。在一般光偵測或影像使用時,光係以近似平行光入射至光柵,如圖 3-15 所示,同樣會因繞射而產生不同方向的反射與透射光。透過傳統光學的遠場分析,可 以得到第 0 階,正負第 1 階等光束,其原因係來自平行光源經光柵後,入射光與繞射 光產生的光程差導致建設性干涉的結果。

圖 3-14、光柵繞射示意圖

然而,在單光子偵測器元件中,金屬光柵與吸收層的距離僅有數百奈米至數微米, 傳統的遠場分析並不一定適用,所以我們採用 EMW-FDTD 的電磁波套件進行計算, 該方法係從基本的 Maxwell 方程式出發,所以適用於近場與遠場分析。

圖 3-15、理想光柵繞射階數圖[18]

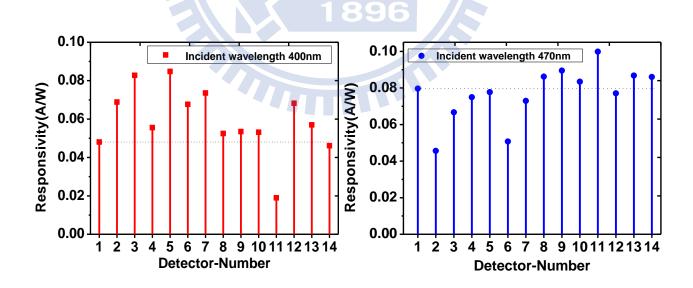

在 CMOS 標準製程中,我們盡量以製程下所能設計的最小線寬為主,並應用 6 層的金屬層來模擬光柵結構,然而因為第 6 層的金屬線寬限制過大,因此我們選擇使用第 1、3 及 5 層的金屬來設計理想的光柵結構,並且將入射光波長設定至藍光波段,模擬光在 400nm 與 470nm 波長下,光柵在不同週期及線寬下元件對於兩種不同入射光波長的響應率,最後得到 13 種理論上光響應較佳的光柵結構。圖 3-16 中代表兩種不同入射光下響應率大小,並以偵測器編號"1"做為單光子偵測器在沒有金屬光柵下做為比較,最後得到表 3-1 中響應率提升倍數。表 3-1 中表示 2~15 顆偵測器對應到偵測器編號的光柵結構,並對照上圖響應率做分析。

從模擬的結果中,我們可以發現在 13 種光柵結構下,單光子偵測器在最少一種入射光波長下響應率有著明顯的提升,並且在偵測器編號 6,入射光波長為 400nm 上有著最大的提升,約 1.77 倍。在其他光柵結構中至少也有大約 1.1 倍的提升。對於單光子偵測器,響應率的增加意味著在偵測效率上必定也隨之提升,這便是我們所需要的,在不降低元件的偵測速度下提升單光子偵測器的偵測效率,增加單光子偵測器應用上的可能性。

圖 3-16、400nm、470nm 金屬光柵響應率提升比較圖

| 偵測器編號<br>(Number) | 週期<br>(period) | 金屬寬度<br>(width) | 金屬間距<br>(spacing) | 填充係數<br>(fill-factor) | 金屬層<br>(metal layer) | 響應率提升 倍數 |  |

|-------------------|----------------|-----------------|-------------------|-----------------------|----------------------|----------|--|

| 1                 | (I             | 1               |                   |                       |                      |          |  |

| 2                 |                | 1               |                   |                       |                      |          |  |

| 3                 | 0.58           | 0.23            | 0.35              | 0.4                   | Metal1               | 1.43     |  |

| 4                 | 0.68           | 0.23            | 0.45              | 0.34                  | Metal1               | 1.72     |  |

| 5                 | 2.0            | 0.35            | 1.65              | 0.18                  | Metal1               | 1.16     |  |

| 6                 | 0.56           | 0.28            | 0.28              | 0.5                   | Metal3               | 1.77     |  |

| 7                 | 0.7            | 0.28            | 0.42              | 0.4                   | Metal3               | 1.41     |  |

| 8                 | 1.1            | 0.28            | 0.82              | 0.25                  | Metal3               | 1.53     |  |

| 9                 | 2.0            | 0.35            | 1.65              | 0.18                  | Metal3               | 1.07     |  |

| 10                | 1.8            | 0.28            | 1.52              | 0.16                  | Metal3               | 1.21     |  |

| 11                | 2.0            | 0.28            | 1.72              | 0.14                  | Metal3               | 1.09     |  |

| 12                | 0.67           | 0.28            | 0.39              | 0.42                  | Metal5               | 1.25     |  |

| 13                | 0.9            | 0.28            | 0.62              | 0.31                  | Metal5               | 1.42     |  |

| 14                | 1.8            | 0.35            | 1.45              | 0.19                  | Metal5               | 1.22     |  |

| 15                | 1.7            | 0.28            | 1.42              | 0.16                  | Metal5               | 1.08     |  |

| 長度單位:μm           |                |                 |                   |                       |                      |          |  |

表 3-1、預計製作光柵結構表

### 3.3 元件暫態特性模擬

#### 3.3.1 暫態響應

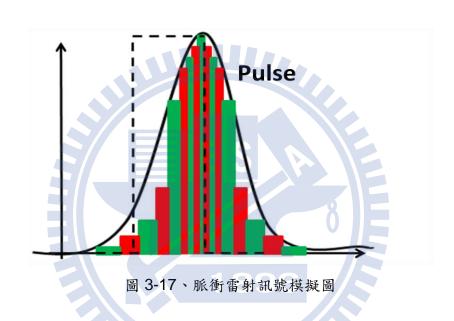

利用 TCAD 暫態元件模擬,我們可以經由模擬入射不同波長脈衝雷射得到元件之 暫態響應。在此我們利用片段堆疊的方式模擬一個脈衝雷射訊號如圖 3-17 所示。

由於實驗室中現有 400nm 與 780nm 脈衝雷射,因此我們選用此兩種波段做為模擬脈衝雷射主要的入射波長,並且將脈衝訊號半高寬設定約為 75ps,最後改變單光子 偵測器操作電壓由-1V 至超過崩潰電壓約 0.5V。

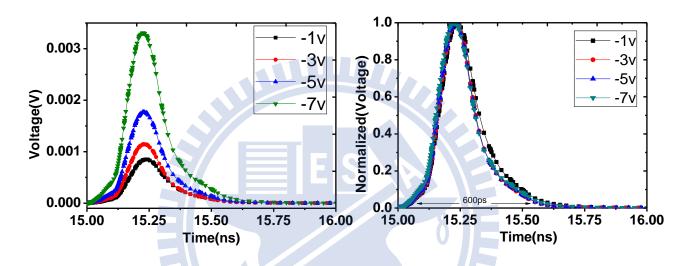

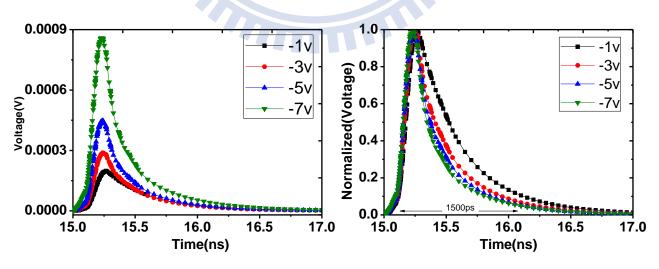

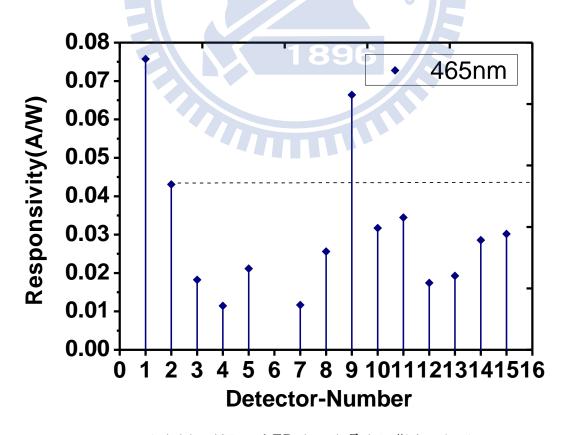

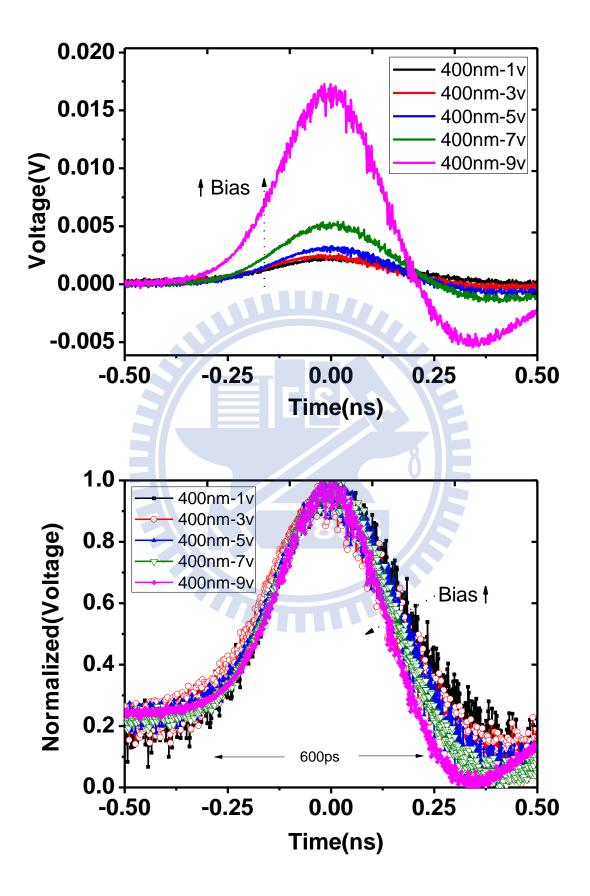

圖 3-18 及 3-19 中,我們模擬出 400nm 及 780nm 脈衝雷射暫態響應圖,左圖為產生之電壓波形與時間關係,並經由歸一化後得到右圖之關係。我們可以發現當元件負偏壓上升時,空乏區加大引發暫態響應提升,並由右圖我們可以了解隨著元件負偏壓上升,電場的加大將導致載子擴散及飄移速度加快,元件響應時間縮短。400nm下元件暫態響應因為吸收較淺,元件響應時間變化較不明顯,在長波長 780nm 下因吸收較深元件響應時間變化較明顯如圖 3-19 右,對照兩種波長下之響應時間 400nm

約 600ps,780nm 約 1500ps,顯示出長波長下因吸收較深,擴散載子需花較多時間至空乏區,也就是所謂 time jitter 效應,是導致元件暫態響應延遲的主要原因。

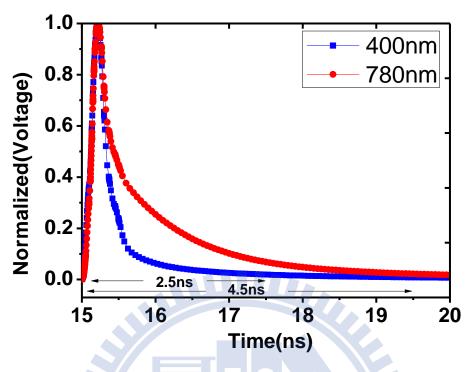

此外,由圖 3-20 我們模擬超過崩潰電壓以上的暫態響應,並且得到 400nm 脈衝雷射下元件暫態響應時間由 0.6ns 增加至 2.5ns,780nm 由 1.5ns 增加至 4.5ns,因此我們再次證明當元件操作至崩潰電壓以上時,發生累增崩潰效應,導致載子不斷崩潰產生,響應時間因而增加,此時便需要外部電路將崩潰電流關閉。

圖 3-18、400nm 脈衝雷射暫態響應模擬結果

圖 3-19、780nm 脈衝雷射暫態響應模擬結果

圖 3-20、超額偏壓 0.5V 下元件暫態響應模擬圖

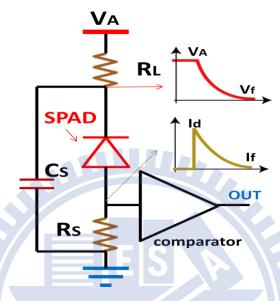

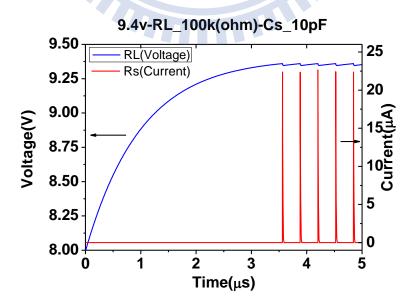

## 3.3.2 Passive-Quenching 電路

SPAD 真正在操作時,需要有外部電路將崩潰電壓拉回並且重複崩潰的機制,要使 SPAD 可重複崩潰,便需要特殊的電路設計使 SPAD 被觸發後透過抑制偵測器內部電流的方式來關閉 SPAD,使得 SPAD 可以重複偵測以計算光量的變化,此種電路設計便統稱為 Quenching 電路。根據不同的偵測機制,現今約有三種,分別為Gated-mode、Passive-quenching與 Active-quenching。利用 TCAD 暫態元件模擬,我們嘗試預測單光子偵測器操作在 Passive-quenching 時,元件重複崩潰的機制與電路關係。

當 SPAD 操作在崩潰之上時,就其特性而言,便是一個電壓主宰輸出電流的電性元件,操作電壓越高,崩潰機率也就越高。Passive-quenching 電路便是用於抑制 SPAD 的崩潰電流如圖 3-21 所示,利用一個大電阻 R<sub>L</sub>(k-ohm)與 SPAD 串聯,當 SPAD 關

閉時電阻相當大,因此外加電壓跨於 SPAD 兩端,迴路中並沒有電流存在,當 SPAD 經載子觸發後,電阻驟降至極低,使得迴路中電流流經 RL,造成 SPAD 上電壓降低,若適當的設計 RL 大小,使得 SPAD 上的壓降降低至電流約 20µA 以下,便有相當程度的機率使 SPAD 自行關閉[2]。

圖 3-21、Passive-Quenching 電路示意圖

圖 3-22 顯示當 SPAD 操作在 Passive-quenching 時,超額電壓 0.1V 下,透過大電阻  $R_L$ ,SPAD 可以成功的重複崩潰。

圖 3-22、模擬 Passive-quenching 崩潰機制

經由公式(3-1)搭配圖 3-21 之 Passive-quenching 電路圖, $R_d$ 為崩潰時元件內阻,  $V_{ex}$  為元件超額偏壓, $V_A$  為元件偏壓,可得到當元件超額偏壓越大時,電流訊號隨之變大( $I_d$ ),偏壓越大可能使得元件崩潰後電流  $I_f$  越大,造成 SPAD 無法自行關閉,因而無法重複崩潰。並經由元件暫態模擬驗證得到如圖 3-23。

$$I_{d}(t) = \frac{V_{ex}(t)}{R_{d}}$$

,  $I_{f} = \frac{V_{A}}{R_{L}}$  (3-1)

圖 3-23、模擬改變超額偏壓下 SPAD 暫態電流大小

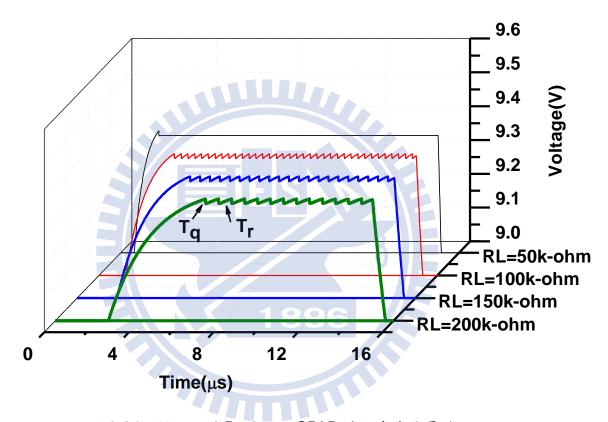

由 2.2.2 節中我們理解 SPAD 光子偵測效率隨著超額偏壓上升而提升。因此,為了使 SPAD 操作至更高的超額偏壓,我們必須將  $R_L$ 加大,使得 SPAD 可自行關閉,並且由公式(3-2)得知, $R_L$ 越大元件充電時間越長( $T_r$ ),當  $R_L$ 足夠大時 SPAD 關閉時間( $T_q$ )與元件內阻  $R_d$ 成正比, $R_L$ 決定了 SPAD 是否可自行關閉的電流大小但對關閉時間影響則可以忽略,其中  $C_S$ 為元件寄生電容、 $C_d$ 代表 SPAD 空乏區等效電容值。

$$T_r = R_L(C_d + C_s)$$

,  $T_q = \frac{R_d \cdot R_L}{R_d + R_L}(C_d + C_s) \approx R_d(C_d + C_s)$  (3-2)

圖 3-24 中,我們固定元件超額偏壓為 0.5V, 改變 RL電阻值大小,模擬出元件充電時間隨 RL加大而上升,當 RL大於 100k 歐姆時 SPAD 開始可自行關閉達到重複的崩潰。

圖 3-24、模擬改變 Ri 電阻下 SPAD 重複崩潰電壓變化

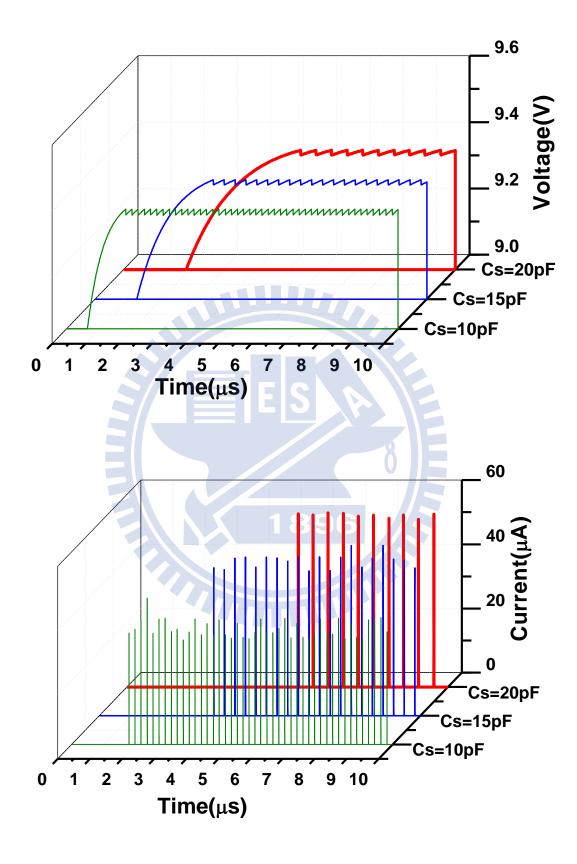

此外,從公式(3-2)中同樣可以預測無論是元件寄生電容或是空乏區等效電容值上升,皆會造成 SPAD 操作時間增加。若我們固定元件空乏區等效電容將寄生電容 Cs加大模擬 SPAD 的暫態崩潰,便可得到圖 3-25,驗證出當寄生電容越大時 SPAD 操作時間隨之增加,且崩潰電流值因電流寄生效應而些微的提升。

圖 3-25、模擬改變寄生電容 Cs 下 SPAD 電壓電流變化

### 3.4 元件佈局與設計

現今單光子偵測器直徑可從 4~200 μm,但因應用上及製程結構上的不同,大於直徑 100 μm 以上的單光子偵測器,必須使用特殊 CMOS 製程以確保元件在大偵測面積上仍有均勻的電場以達到崩潰,及減少雜質在偵測的面積上以降低暗電流及 afterpulsing 影響。另外製作 10 μm 以下的單光子偵測器主要是因為使用 STI 結構當作 guard-ring,有效的維持均勻且大的電場並且在製作成陣列時增加約九倍的 fill factor 達到提升偵測器像素的目的。

在先前電性模擬上我們證明使用 Pwell guard-ring 結構成功消除元件邊緣效應,並且在直徑縮小至接近 10 µm 及製程變異下仍然有很好的操作特性。光性模擬上得到 SPAD 對可見光波長下之響應度,並模擬推測光柵結構在藍光波段的可行性。此外經由元件暫態特性模擬推估 SPAD 在不同脈衝雷射光波長下的響應速度及偵測器外部 Passive-quenching 電路對 SPAD 操作機制的影響。

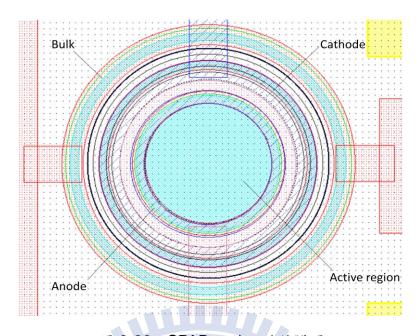

然而為了完整將光耦合進偵測器中,避免在單光子訊號量測中訊號過小導致偵測失敗,以及使得加入光栅結構的效果能夠更明顯,我們最終選定以直徑 20μm 製作單光子偵測器,並且搭配一個直徑 70μm 單光子偵測器做為響應率校正使用。而在元件 layout 的部分如圖 3-26 所示,採用圓形取代傳統的正方形或八角形,盡量減少元件可能產生的邊緣效應,使得電場均勻分佈在偵測區域上,並將元件陰極及接地之金屬加寬,使得偵測器只有在主要偵測區能夠有光進入,減少元件間的相互干擾。圖 3-27 SPAD 晶片佈局圖中共有 15 顆單光子偵測器,每一顆單光子偵測器共有三個電極,將 15 顆偵測器利用 bulk 共同接地,另外每一顆偵測器皆有獨立的陰極及陽極,因此共有 31 個 PAD,最後根據光栅模擬結果表 3-1 之偵測器標號及結構依序佈局。

圖 3-26、SPAD 元件設計結構圖

圖 3-27、SPAD 晶片佈局圖(851μm×851μm)

# 第四章 實驗結果與討論

本章中首先將介紹晶片佈局結果,介紹經由 CMOS 標準製程製作出的單光子偵測器結構。接著說明偵測器操作在 Linear-mode 時量測的環境及技巧,並分析直流響應與暫態響應的量測結果。最後針對單光子偵測器主要操作模式 Geiger-mode 介紹當元件操作在 Passive-quenching 時量測的方法與計算,並討論 Passive-quenching 量測之結果。

## 4.1 晶片佈局結果討論

圖 4-1 中,左圖為 70µm 單光子偵測器,右圖為有光柵結構下 20µm 單光子偵測器,深藍色部分為主要偵測區,淺藍色部分為絕緣層,褐色為 1~3 層的金屬層,並由內向外的金屬環形依序為陽極、陰極、及接地。圖 4-2 則為晶片照相圖。在這次元件的佈局中,由於 20µm 單光子偵測器在設計時的疏忽,導致陽極金屬第二層至第三層斷路,第三層金屬層 floating,因此在量測前我們必須先利用 FIB(Focus Ion Beam)將金屬層打通,然而在接下來的量測結果中我們發現,此一程序勢必對偵測器特性造成一定的影響。

圖 4-1、SPAD 元件結構照相圖

圖 4-2、SPAD 晶片佈局照相圖

### 4.2 Linear-mode 量測結果

元件操作在 Linear-mode 時,如圖 4-3,便是將元件操作在反偏以下且在累增崩潰發生之前。經由此模式,可以確認元件在照光之後 I-V 曲線是否維持正常,響應率的量測可以分析光柵結構是否有增強光吸收的效果,利用不同的脈衝雷射我們便可推測 SPAD 在不同光波長下暫態響應的速度。

圖 4-3、Linear-mode IV 曲線示意圖[6]

## 4.2.1 量測技巧與環境

Linear-mode 的量測中,主要分為直流響應與暫態響應,在量測光電流響應之前 必須先量測元件 I-V 與 C-V 特性,確認元件崩潰電壓與空乏區電容之大小是否符合先 前模擬之預測,以定義元件操作電壓的大小。因此我們利用 Agilent 4156b 半導體參 數分析儀(Semiconductor parameter analyzer),使用探針量測尚未打線晶片,確定元 件 I-V 曲線並定義崩潰電壓的大小及計算崩潰時 SPAD 內阻大小如圖 4-4 所示,另外使用 Agilent 4284a 電感電容電阻測量計(LCR meter),量測改變負偏電壓下空乏區電容隨電壓變化情形,以了解元件崩潰下空乏區電容值大小。

### Agilent 4156b Semiconductor Parameter Analyzers

直流響應量測部分如圖 4-5 所示,我們利用 Keithley2602 直接監看 SPAD 電流 大小,以確定光纖射出光量完整進入主要偵測區,待確定光量後再量測電流曲線。因 為光源的不同我們採用兩種模式入光,雷射光源部分有 400nm、780nm 脈衝雷射及 632nm HeNe 雷射、850nm VCSEL,並利用準直儀連接光纖傳導的方式入射至 SPAD, LED 光源則分別有 465nm、518nm、592nm、628nm 四種波長,並且在自由空間下 直接入射至 SPAD。此外,為了確認入射光量大小,在入射前我們利用積分球(Power meter)校正入射光量,用以確定響應率的真實度。

暫態響應部分如圖 4-6 所示,由於必須將直流雜訊過濾,因此我們使用 Agilent 11612A bias network 過濾直流使得在高頻示波器上只顯示暫態訊號,並且利用 Keithley2602 固定將 SPAD 操作在負偏下,光源部分由於暫態響應需要高速的脈衝雷射,因此使用我們現有 400nm、780nm 脈衝雷射,同樣經由準直儀連接光纖傳導的方式入射至 SPAD。此外,量測時為了避免雷射訊號因光能量過大而半高寬過長及可能造成光波長的位移,我們盡量將脈衝雷射能量調降至示波器可讀之極限進行量測,最後利用 Tektronix TDS7404 示波器紀錄暫態訊號波形。

圖 4-6、暫態響應量測系統

#### 4.2.2 直流響應

經由 I-V 與 C-V 量測我們可以得到二極體的 turn on 電壓、崩潰電壓、暗電流值及 SPAD 電容值、電阻值的大小。由圖 4-7 可得知我們所設計的單光子崩潰二極體 turn on 電壓約在 0.6V 附近,崩潰電壓則約在-9.9V ,此值與先前模擬預測崩潰電壓約為-10V 非常接近。然而因為製程的變異,不同顆晶片上之崩潰電壓會有些微的差異,如PD1 與 PD9 崩潰因為與其他二極體在不同顆晶片進行之量測,因此崩潰電壓落在-9.7V,產生了 0.2V 的差異。另外,直徑 70μm 暗電流值的大小隨著電壓加大約從10<sup>-13</sup>~10<sup>-11</sup>A 如圖 4-8 所示與直徑 20μm 差距相當小,理想上,暗電流值的大小越小越好且與偵測器面積成正比的差距,這和我們所預期的相距甚遠,因此我們推測,由於直徑 20μm 偵測器須經過 FIB 導通金屬,然而在導通金屬的過程中可能造成陽極與陰極間部分的漏電,這是無法避免的,卻也造成元件永久的損害。量測 I-V 時我們將限流設定在 1mA,計算元件崩潰後的電阻值,我們得到崩潰時內阻約為 20~30Ω。

圖 4-8、不同面積下 I-V 特性比較圖

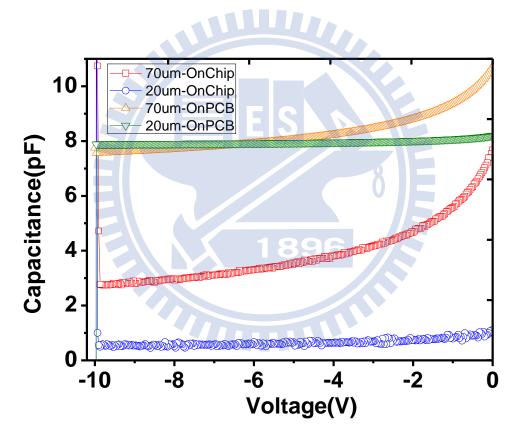

電容值的大小如圖 4-9 所示, 我們藉由探針直接量測晶片及 PCB 板打線後分別量測,得到在經由 PCB 量測時電容值皆提高許多,因此我們推測 PCB 板電容值約在數個 pF,而在藉由探針直接量測下,我們可得知二極體中空乏區電容隨反偏電壓加高而漸漸降低,偏壓 0V 時 70µm 電容值為 7.39pF,20µm 電容值為 1.11pF,偏壓在接近崩潰電壓時,70µm 電容值降低為 2.75pF,20µm 電容值則降低為 0.49pF。表 4-1中,我們比較量測與計算之電容值,發現量測值皆些微大於計算值,造成此現象主要為晶片中電路導線與接地線以及 PAD 間皆有電容值並聯造成元件電容值的提高,然而此值並不屬於空乏區之電容因此不隨偏壓而變化。

圖 4-9、單光子偵測器 C-V 量測結果

| SPAD 直徑\偏壓 | 0V(量測) | 0V(計算) | -10V(量測) | -10V(計算) |

|------------|--------|--------|----------|----------|

| 20µm       | 1.11pF | 0.39pF | 0.49pF   | 0.12pF   |

| 70µm       | 7.39pF | 3.69pF | 2.75pF   | 1.11pF   |

表 4-1、量測電容與計算電容比較表

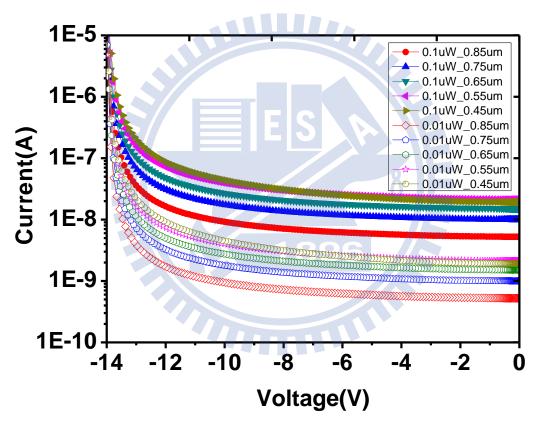

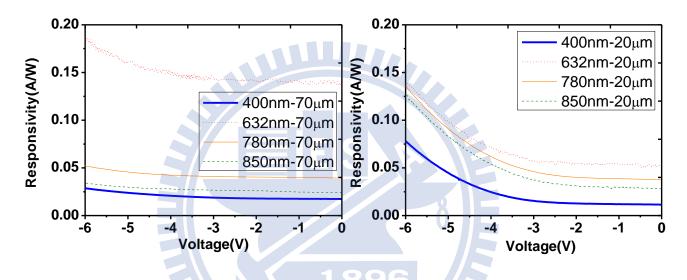

在入射固定的光能量下,量測光電流,經由公式(2-3)我們便可求出偵測器響應率。 圖 4-10、4-11 分別為量測雷射及 LED 光源下不同波長的直流響應曲線,左圖為直徑 70μm 偵測器,右圖則為 20μm 偵測器,我們可以發現在無論在雷射或 LED 光源下 70μm 偵測器響應率皆較高,推測此原因可能為量測雷射光源時光纖在 70μm 下幾乎 可完全入射至主要偵測區而 20μm 無法完全入射,另外 20μm 偵測器在 FIB 製作過程 中打入之 Tungsten 遮住部分主要偵測區也可能為造成 20μm 響應率較低之原因,此 外在 LED 光源下綠光及紅光因響應率相當接近而使得有交叉之情形。

圖 4-10、雷射光源下直流響應曲線

圖 4-11、LED 光源下直流響應 I-V 曲線

經由圖 4-12 我們比較量測與模擬直流響應隨波長變化情形,得到量測之響應率除了 400nm 光源以外皆大於模擬值,且皆由短波長漸漸上升在超過 600nm 後,響應率緩慢下降,比較無絕緣層的模擬結果,我們可以得知製程中需製作的鈍化層及絕緣層對單光子偵測器響應率造成了一定程度的影響。

圖 4-12、SPAD 直流響應隨波長變化圖量測與模擬比較

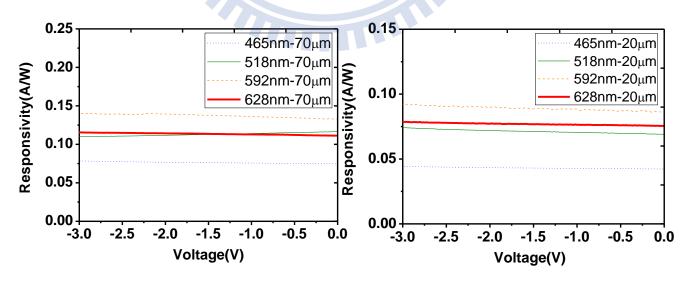

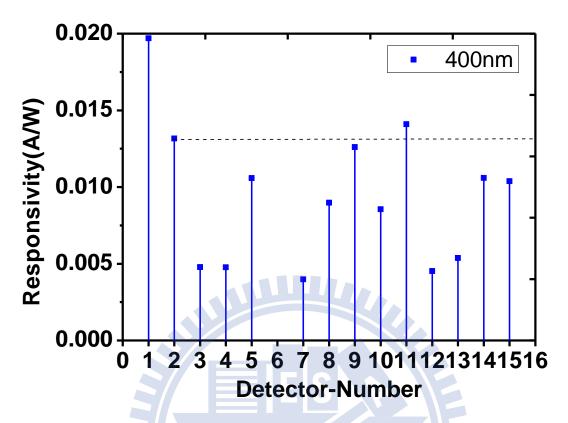

量測金屬光柵結構 SPAD 響應率時,我們將入射光波長設定至藍光波段,因此我們利用 400nm 雷射及 465nm LED 光源分別量測,並且與先前模擬 400nm 與 470nm 波長作對應,圖 4-13、4-14 量測結果中我們發現有金屬光柵結構下各只有一顆單光子偵測器響應率的提升,與先前模擬相差許多,且 70µm 與 20µm 無光柵結構下響應率並不一致。推測造成響應率不一致原因可能為 FIB 所造成,且由於模擬與製作出的結構接面深度的差異造成吸收的不同導致於模擬失準以及先前模擬之反射率震盪造成響應率的跳動,都是造成大部分光柵結構響應率無法提升之原因。而在比較無光柵結構(PD2)與有提升響應率之光柵結構(PD11、PD9)後,我們得到 400nm 響應率提升 1.04倍、465nm 響應率提升 1.53 倍。

圖 4-13、400nm 雷射光源金屬光柵響應比較圖

圖 4-14、465nm LED 光源金屬光柵響應比較圖

#### 4.2.3 暫態響應

暫態響應的量測在於元件中垂直結構的吸收造成飄移及擴散載子移動時間的不同,因此對於晶片中不同直徑大小的偵測器較無關係。在此我們選用直徑 70µm 偵測器進行量測,以便於產生較大光電流而減少入射光能量之大小,以及在經由光纖量測時較容易將大部分光入射至偵測器主要偵測區。

圖 4-15、4-16 為量測元件在 400nm 及 780nm 脈衝雷射下暫態響應結果,上圖分別為產生之電壓波形與時間之關係,下圖則為規一化後結果,由先前 3.3.1 節暫態響應模擬我們可以得知,400nm 雷射光因為吸收較淺將造成約 600ps 的暫態波形,由圖 4-15 我們發現響應大小隨偏壓上升漸漸提高,且訊號寬度因電場加大而漸漸縮短約 600ps,此現象與模擬預測完全一致,並且得到暫態響應的時間同樣相當吻合。此外,從圖 4-16,780nm 雷射光量測的結果我們可以再次驗證,因為長波長所造成元件內較深處的吸收導致暫態波形約 1500ps 的寬度,響應的大小與寬度同樣的隨偏壓提高且縮短,此值與模擬同樣一致。

在量測完元件操作在負偏壓下之暫態響應後,我們將偏壓操作於崩潰電壓之上, 試圖得到與先前模擬圖 3-20 一樣的結果,也就是元件不斷的累增崩潰造成響應圖形半 高寬急遽的加大,從圖 4-17 得到兩種波長下的量測結果我們發現,400nm 響應時間 已超過 1ns,780nm 則超過 2ns,此現象符合模擬中預期,代表著累增崩潰的發生使 得暫態響應延長幾倍的時間之後才結束,而此時暫態響應的速度不再是由光波長所決 定,而是累增崩潰效應所控制。

圖 4-15、400nm 脈衝雷射暫態響應量測圖形

圖 4-16、780nm 脈衝雷射暫態響應量測圖形

圖 4-17、超額偏壓 0.2V 下單光子偵測器暫態響應圖

## 4.3 Geiger-mode 量測結果

在前一章的暫態電路模擬中我們了解,在 Geiger-mode 操作模式下,單光子偵測器實際運作時需將電壓操作在高於崩潰電壓之上如圖 4-18 所示,並且需有將崩潰中止並拉回的外部電路機制。因此在此階段的量測,我們將外部電路相容在 PCB 板中,試圖將外部電路可能對偵測器元件造成的影響降至最低,並且針對 465nm LED 光源做單光子偵測效率計算。

圖 4-18、Geiger-mode IV 曲線示意圖[6]

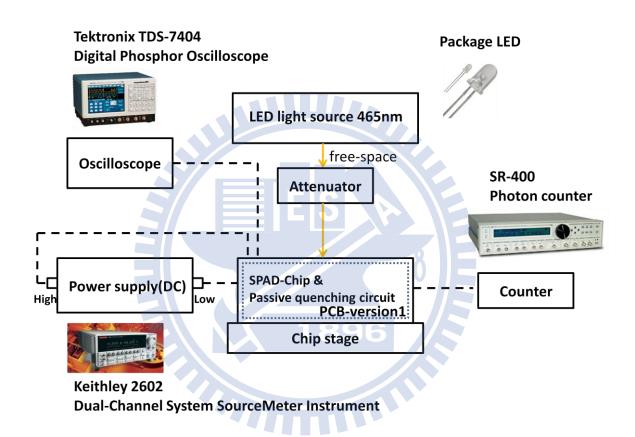

### 4.3.1 量測技巧與環境

利用 Passive-quenching 機制量測單光子偵測器之系統如圖 4-19 所示,我們採用 465nm LED 光源,利用衰減片將光衰減至約  $10^{-9}$  W,並使用積分球校正光量,換算積分球面積與偵測器面積倍數,使得入射光進入主要偵測面積約 $10^{-13}$  W,固定每

秒約10<sup>6</sup>個光子數。操作時我們使用 Keithley2602 固定超額偏壓大小,並且在計算暗計數與光子數前先利用 Tektronix TDS7404 觀察崩潰電壓及電流相關性是否正確,並讀出電流輸出訊號可辨識之位準,此位準用於在計算暗計數與光子數時 SR-400 計數器設定。使用計數器計算時,我們設定計算時間為一秒並計算十次做平均使得在量測上能夠更為精確。

圖 4-19、單光子偵測器量測系統(Passive-quenching)

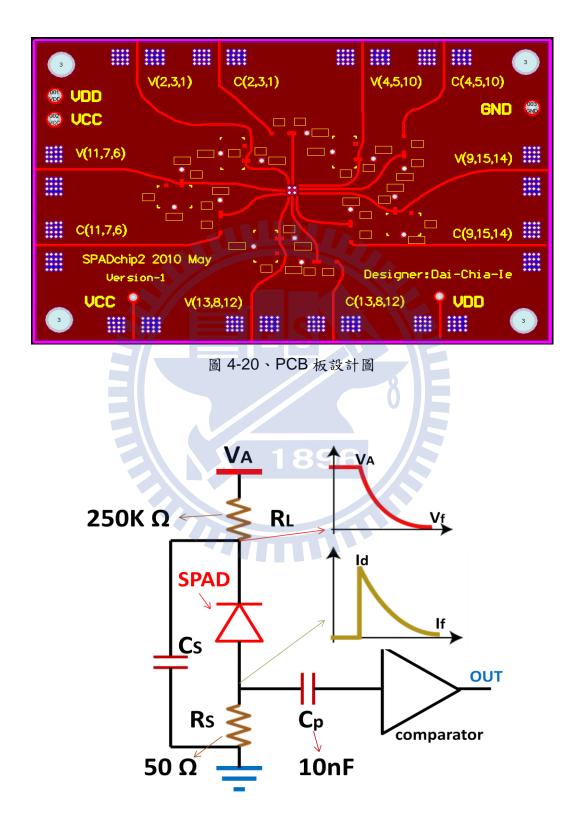

PCB 板之設計如圖 4-20 所示,由於一顆晶片中有共有 15 顆偵測器,為了將 Passive-quenching 電路置於 PCB 板中以減少外部電路所造成之雜訊,我們設計一片 PCB 板中只量測 5 顆偵測器,並分別獨立 5 顆偵測器下 Passive-quenching 電路所輸 出之崩潰電壓及電流。Passive-quenching 電路設計如圖 4-21 所示,我們先從公式(3-1) 中可以了解為了避免崩潰時 SPAD 電流過高導致元件損壞,我們必須使用適當大小的  $R_L$ 電阻,在此我們使用可變電阻將  $R_L$ 固定為 250 $k\Omega$ ,  $R_S$ 使用定電阻固定為 50 $\Omega$  以

利於與外部機器連接時阻抗匹配,另外利用定電阻  $C_P$  過濾直流雜訊約 10nF,完成 Passive-quenching 電路設定。

圖 4-21、Passive-quenching 電路示意圖

#### 4.3.2 Passive-Quenching 電路

經由先前章節量測的結果,我們得到了 SPAD 崩潰電壓、不同光波長下的響應率及響應速度,在接下來的量測中我們將針對單光子偵測器主要操作模式 Passive-quenching,量測 SPAD 的暗計數、465nm 藍光 LED 下之單光子偵測效率及雜訊等效功率。

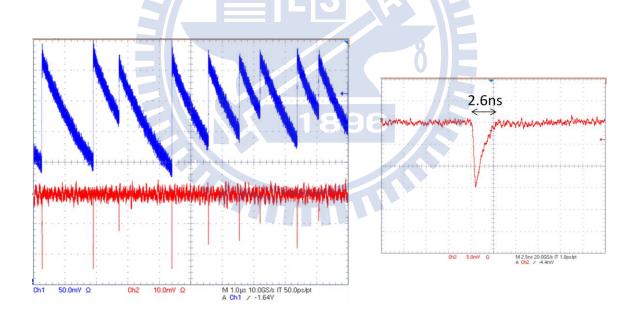

圖 4-22 中顯示 SPAD 操作在崩潰電壓之上時,RL電阻上電壓充放電及 Rs電阻上之崩潰電流訊號,代表著 Passive-quenching 電路成功的將單光子偵測器關閉並開啟,進行重複的偵測,與先前模擬預測圖 3-22 相同,此外為了降低雜訊將電路相容至 PCB 板中,我們得到的電流訊號相當清晰,右圖中顯示崩潰電流突然變大接著被 PQC 關閉的情形,時間約 2.6ns。

圖 4-22、Passive-quenching 電路 RL 電流與 Rs 電壓相對關係圖

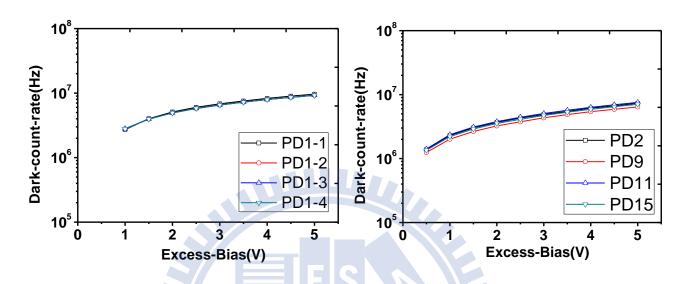

暗計數的量測我們可從圖 4-23 中得到, 左圖為直徑 70µm 偵測器(PD1)不同顆的量測比較, 右圖則為 20µm 偵測器不同光柵結構比較, 可以發現暗計數在超額偏壓 0.5V以上時皆已超過 1MHz, 此值在 70µm 偵測器上由於面積相當大可能造成材料中缺陷偏多是合理的, 然而 20µm 偵測器暗計數應比 70µm 小約 12 倍卻仍然高於 1MHz,

且在圖 4-23 中顯示同樣元件結構下 70μm 暗計數相當穩定而 20μm 則有些微的不同,因此我們合理的推測 FIB 所造成直徑 20μm 偵測器暗電流偏高的情形同樣的也造成在暗計數的提高。

圖 4-23、不同顆 SPAD 量測暗計數隨超額偏壓改變情形

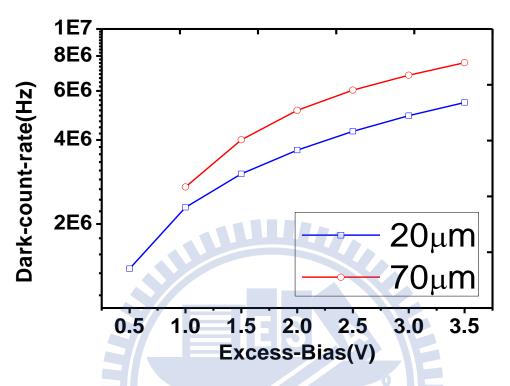

此外由於暗計數的偏高,在量測單光子偵測效率前我們必須先把雜訊的影響扣除,如此才可得到正確的偵測效率,圖 4-23 中我們比較不同直徑 SPAD 量測暗計數與單光子偵測效率,由於暗計數的偏高,使得絕大部分的暗計數在充電未完成前發生,如此先前公式(3.2)推測元件死亡時間(Dead time)由 RL電阻及元件電容值所決定的機制將無法成立,取而代之的我們藉由量測暗計數大小隨電壓上升的情形推測元件所能操作的最快速度來決定死亡時間。

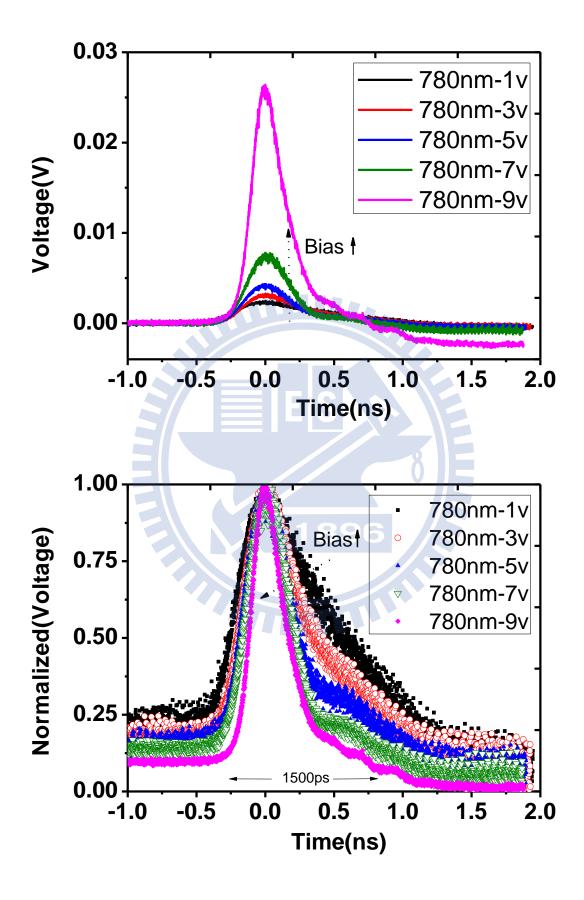

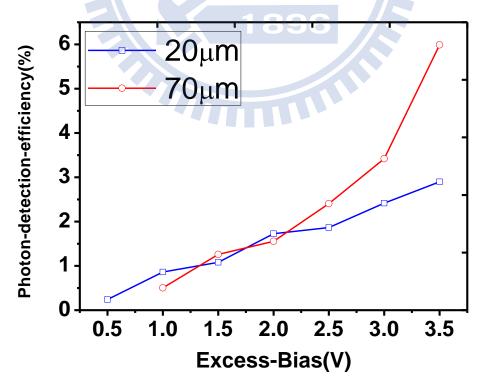

因此我們經由圖 4-23 中推測 70μm 及 20μm 偵測器死亡時間平均約為 100ns 與 125ns,如此我們藉由公式(4-1)可得知偵測器每秒實際可偵測光的時間。因此在量測時我們得到圖 4-24 中暗計數的結果後,代入公式(2-10)便可計算出單光子偵測效率。在此我們將入射光子數固定約每秒7×10<sup>6</sup>,因此在經過公式(4-1)校正後光子數將減少一半以上,藉此得出單光子偵測效率圖 4-25,最高在超額偏壓 3.5V 時 70μm(PD1)約有 6%,20μm(PD2)約有 2.8%的偵測效率。

圖 4-24、量測不同直徑大小 SPAD 暗計數比較圖

圖 4-25、量測不同直徑大小 SPAD 單光子偵測效率比較圖

經由先前直流響應的量測我們得到在 465nm LED 光源下 PD9 響應率有著 1.5 倍的增加,因此圖 4-26 中我們量測比較在 PD9 光栅結構下單光子偵測效率是否有提升,圖中我們明顯的發現 PD9 隨著超額偏壓加大皆略大於無光栅結構 PD2 約 1.2 倍,此值與先前直流響應略有不同,推測可能因為元件暗計數的偏高導致於偵測效率並不明顯,因而相對使得單光子偵測效率降低,提升倍數隨之較低。但我們可經由此結果得到,經由直流響應量測結果可以預測單光子偵測效率是否有提升,然而提升之倍數將會因為元件雜訊的大小而有所改變。

圖 4-26、量測有金屬光柵下 SPAD 單光子偵測效率比較圖

在量測出單光子偵測器暗計數及單光子偵測效率後,由公式(2-5)可以計算出 SPAD 雜訊等效功率值,圖 4-27 中計算 PD1、PD2、PD9 之雜訊等效功率值約在  $1\times 10^{-13}$  WHz<sup>-1/2</sup> 隨著超額偏壓加高漸漸降低,PD9 表現則最好維持在 $1\times 10^{-13}$  WHz<sup>-1/2</sup>以下,而  $70\mu$ m(PD1)則是在超額偏壓超過 3V 時有最好的雜訊等效功率。

63

# 第五章 結論與未來展望

在實驗中,我們利用 Sentaurus TCAD 元件模擬軟體預測單光子偵測器元件結構的可行性,避免操作於崩潰電壓時元件提前的崩潰,另外利用光性的模擬設計出不同金屬光栅結構的單光子偵測器。在暫態模擬上理解元件吸收深度與操作速度之關係,並模擬單光子偵測器操作在 Passive-quenching 時電路機制,充分了解 RL 電阻與元件電容之對應關係。

在得出適當的元件結構模型後,我們利用 CMOS 0.18μm 標準製程,設計元件並佈局結構,製作直徑 70μm、20μm 及 13 種金屬光柵結構,共 15 顆單光子偵測器,總晶片面積約 851×851μm<sup>2</sup>。

量測上,我們根據光偵測器不同的操作區間分別進行量測分析,並先經由 I-V 及 C-V 量測得知元件崩潰電壓為-9.9V 及崩潰時內阻及電容值各為  $20\sim30\Omega$  及 0.49pF,接著量測直流響應在藍光波段 400nm、465nm 分別因為光柵結構而提升 1.04 倍及 1.53 倍,並且在暫態響應量測上完全符合模擬預測。在單光子偵測器主要操作模式 Passive-quenching 我們藉由設定  $R_L$ 在  $250k\Omega$ ,量測元件暗計數在超額偏壓  $0.5V(25^{\circ}C)$ 時約 1.3MHz、並且經由元件死亡時間(Dead time)校正入射光子數,量測出單光子 偵測效率最高為 6%,並利用光柵結構提升單光子偵測效率 1.2 倍,雜訊等效功率則 維持在 $1\times10^{-13}$  WHz<sup>-1/2</sup>。

然而由於佈局時的疏忽造成 20µm 偵測器必須先以 FIB 修補,造成暗電流、直流響應的偏低及暗計數的偏高,暗電流的過高使得元件無法操作在 Gated mode 量測,都是往後可以加以改進之處。

未來我們可以藉由更適當的元件佈局及 PCB 板設計,降低量測時電容值大小及減少單光子偵測器暗計數值,使得元件死亡時間更短、操作速度更快,並且將外部電路整合至單一晶片中減少電路中訊號的損耗並且有著更佳的電路匹配性,都是使得單光子偵測器性能更進一步的目標。

## 参考文獻

- [1] F. Zappa, A. Tosi, A. D. Mora, F. Guerrieri, S. Tisa, "Single-photon avalanche diode arrays and CMOS microelectronics for counting, timing, and imaging quantum events," *Proc. of SPIE.* **7608**, 70682C, (2010)

- [2] S. Cova, M. Ghioni, A. Lacaita, C. Samori, F. Zappa, "Avalanche photodiodes and quenching circuits for single-photon detection, "Applied Optics. **35**, 12, (1996)

- [3] S. Radovanovic', High-Speed Photodiodes in Standard CMOS Technology, (2004)

- [4] http://www.tf.uni-kiel.de/matwis/amat/semi\_en/kap\_5/backbone/r5\_2\_2.html

- [5] S. O. Kasap, Optoelectronics and Photonics: Principles and Practices, (2001)

- [6] H.T.Yen, "InGaAs Avalanche Photodiode for Single-Photon-Detector Application," *Master thesis,* National Chaio Tung University, Taiwan (2007)

- [7] C. Niclass, M. Sergio, E. Charbon, "A Single Photon Avalanche Diode Array Fabricated in Deep-Submicron CMOS Technology," *IEEE Design Automation and Test in Europe.* **1**, 1 (2006)

- [8] A. G. Stewart, L. Wall, J. C. Jackson, "Properties of silicon photon counting detectors and silicon photomultipliers," *International Journal of Optics.* **56**, 2, (2009)

- [9] W. G. Oldham, R. R. Samuelson, P. Antognetti, Triggering Phenomena in Avalanche Diodes, *IEEE Trans. on Electron Devices.* **19**, 9, (1972)

- [10] S. Donati, Photodetectors Devices Circuit and Applications, (2000)

- [11] M. Ghioni, A. Gulinatti, I. Rech, F. Zappa, S. Cova, Progress in Silicon Single-Photon Avalanche Diodes, *IEEE J. Selected. Topics in Quantum Electronics*. **13**, 4, (2007)

- [12] I. Rech, A. Ingargiola, R. Spinelli, I. Labanca, S. Marangoni, M. Ghioni, S. Cova, "A New Approach to Optical Crosstalk Modeling in Single-Photon Avalanche

- Diodes, " IEEE Photonics Technology Lett. 20, 5 (2008)

- [13] M. J. Hsu, H. Finkelstein, and S. C. Esener, A CMOS STI-Bound Single-Photon Avalanche Diode With 27-ps Timing Resolution and a Reduced Diffusion Tail, *IEEE Electron Device Lett.* **30**, 6 (2009)

- [14] M. Gersbach, J. Richardson, E. Mazaleyrat, S. Hardillier, C. Niclass, "A low-noise single-photon detector implemented in a 130 nm CMOS imaging process," *Solid-State Electronics*. **53**,7 (2009)

- [15] J. A. Richardson, L. A. Grant, R. K. Henderson, Low Dark Count Single-Photon Avalanche Diode Structure Compatible With Standard Nanometer Scale CMOS Technology, IEEE Photonics Technology Lett. 21, 14 (2009)

- [16] N. Faramarzpour, M. J. Deen, S. Shirani, Q. Fang, Fully Integrated Single Photon Avalanche Diode Detector in Standard CMOS 0.18-µm Technology, *IEEE Trans. on Electron Devices.* **55**, 3, (2008)

- [17] P. B. Catrysse, B. A. Wandell, "Integrated color pixels in 0.18-μm complementary metal oxide semiconductor technology, " *J. Opt. Soc. Am.* **20**, 12, (2003)

- [18] J. J. Kuta, H. M. Driel, D. Landheer, Y. Feng, "Coupled-wave analysis of lamellar metal transmission gratings for the visible and the infrared," J. Opt. Soc. Am. 12, 5, (1995)

- [19] M. A. Marwick, A. G. Andreou, "Fabrication and Testing of Single Photon

Avalanche Detectors in the TSMC 0.18µm CMOS Technology," *IEEE Information*Sciences and Systems . 741, (2007)

# 簡歷(vita)

姓名: 戴嘉邑 (Chia-Ie Dai)

性別: 男

出生年月日:民國75年4月19日

籍貫:台灣省南投縣

學歷:

國立花蓮高級中學 (2001.9 - 2004.6)

國立中興大學電機工程系學士 (2004.9 - 2008.6)

國立交通大學電子工程系碩士 (2008.9 - 2010.8)

碩士論文題目:

標準CMOS製程之單光子偵測器

Single-Photon Avalanche Photodiode Fabricated with Standard CMOS

Technology