# 國立交通大學

電子工程學系 電子研究所碩士班

# 碩士論文

具有低電壓之金屬-氧化層-氮化層-氧化層-矽 結構非揮發性記憶體之製程技術應用與研究

# Process and Technology For Low Voltage MONOS Non-Volatile Memory

研究生:李宗翰

指導教授:荊鳳德 教授

中華民國九十九年七月

# 具有低電壓之金屬-氧化層-氮化層-氧化層-矽 結構非揮發性記憶體之製程技術應用與研究

# Process and Technology For Low Voltage MONOS Non-Volatile Memory

研究生:李宗翰 Student: Tsung-Han Lee

指導教授:荊鳳德 博士 Advisor: Dr. Albert Chin

國立交通大學

電子工程學系 電子研究所碩士班

碩士論文

A Thesis

Submitted to Department of Electrical Engineering & Institute of Electronics

College of Electrical and Computer Engineering

National Chiao Tung University

In partial Fulfillment of the Requirements

For the Degree of Master

In

**Electronics Engineering**

July 2010

Hsinchu, Taiwan, Republic of China

中華民國九十九年七月

具有低電壓之金屬-氧化層-氮化層-氧化層-矽結 構非揮發性記憶體之製程技術應用與研究 研究生:李宗翰 指導教授:荊鳳德教授

# 國立交通大學 電子工程學系 電子研究所碩士班

#### 摘要

近年來,在半導體產業中,記憶體元件的發展已成為另一主流。其中,屬於非揮發性型態的快閃式記憶體因其具有高密度特性、良好的資料保存能力和重複抹寫功能而被廣泛的使用在個人行動電子產品,例如手機或數位相機。隨著這些電子產品的普及化,對快閃式記憶體的需求也快速增加。因此,快閃式記憶體的發展和技術已成為重要的研究之一。

隨著元件尺寸持續縮微,快閃式記憶體主要的製程技術關鍵為其具有導電性的多晶矽浮停閘。基於非揮發性記憶體基本的需求,以多晶矽材料當作電荷儲存層的快閃式記憶體需要厚度至少約6-7奈米的穿遂氧化層來防止儲存電荷遺以增加資料儲存能力。其主要原因為反覆的編碼和抹除過程將會對穿遂氧化層造成應力而產生缺陷,這些缺陷可能形成漏電路徑而導致多晶矽全面性的漏電。然而,較厚的穿遂氧化層不僅需要較大的操作電壓也增加元件製程縮微的困難度。為了解決此問題,多晶矽材料將被氮化矽所取代。由氮化矽電荷儲存層所形成的多晶矽或金屬閘極-氧化矽-氮化矽-氧化矽-矽結構記憶體元件可以解決平面微縮的問題且同時具有良好電荷儲存能力、低工作電壓特性和符合目前互補式金氧半場效電晶體元件的製程,因此已開始受到大家的關注。

在此論文中,我們使用全新的高介電係數介電質材料氧化鉿(介電係數約25) 和氧化鋯(介電係數約35)形成交錯層取代傳統的氮化矽電荷捕獲層。高介電係 數介電質的使用,不僅可以有效降低操作電壓,同時也可以將電壓有效的跨在薄二氧化矽穿遂層以增加編碼和抹寫速度。此外,應用具高功函數的金屬閘極氮化 銀替代傳統多晶矽閘極可以防止在抹除狀態時電荷從閘極端注入並增加抹除效 率。

Process and Technology For Low Voltage

MONOS Non-Volatile Memory

Student: T. H. Lee Advisor:

**Advisor: Dr. Albert Chin**

**Department of Electronics Engineering**

& Institute of Electronics

**National Chiao Tung University**

Abstract

Recently, the Flash memory is commonly used in portable electronic products, such as cell phone, MP3 player and USB Flash. However, with the increase in requirements for products, the technology and process must be still improved.

The key issue for poly-Si floating gate non-volatile memory is the electrically conductive charge storage layer, where the programmed electrons will leak out through the single oxide defect. Such oxide defects are generated by the program and erase stress operation. In order to maintain the data retention, the thick tunnel oxide (6-7 nm) is required. That is opposite to the VLSI scaling trend. In addition, the memory device with thick tunnel oxide requires a higher operation voltage. To overcome this problem, the conductive poly-Si is replaced by discrete trapping nitride to form the [poly-Si or metal gate]-SiO<sub>2</sub>-Si<sub>3</sub>N<sub>4</sub>-SiO<sub>2</sub>-Si SONOS or MONOS memory. The isolated charges stored in discrete traps can prevent complete charge leakage. Therefore, a thinner tunnel oxide can be used. This in turn yields lower voltage and faster speed for program and erase.

In this dissertation, we demonstrated a low voltage, fast speed and good data retention MONOS memory device with high work function MoN metal gate, novel

iii

interactive high- $\kappa$  HfO<sub>2</sub>-ZrO<sub>2</sub> structure for trapping layer substituted conventional Si<sub>3</sub>N<sub>4</sub> trapping layer.

#### 誌謝

两年忙碌的碩士班生活,也隨著論文的完成而進入尾聲,首先,要感謝我的指導老師-荊鳳德博士對我耐心的指導,讓我在這兩年中學習到做研究的態度和方法,也培養出我面對問題時的解決能力,並告訴我們第一手的世界級科技新知讓我們做的研究能跟上世界的腳步,讓我們碩班兩年所學足以應付未來工作。

我首要感謝博士班 蔡竣揚學長的耐心指導,從機台訓練、學業指導、量測方式、到結果討論全都傾囊相授,讓我受用無窮;真的很慶幸能有你這樣的學長,伴隨我這兩年碩士生活。還有我要感謝博士班 陳維邦學長、周坤億學長以及博士後研究 鄭淳護學長,你們的經驗傳授,讓我克服了許多大大小小問題。另外也感謝我的同屆同學們-明倫、佳芸、智偉以及柏君,一起討論不好意思詢問學長的簡單問題,一起分享研究的酸甜苦辣,你們是碩士班這段旅途裡不可或缺的夥伴,謝謝你們。我必須感謝我的學弟 廷瑜,不僅努力跟隨我學習也陪伴我做實驗,讓空虛的無塵室有一點笑聲。

接著,我要感謝國家奈米元件實驗室與交大奈米中心提供優良的製程環境。

最後,我要感謝我的母親鄭香梅女士和我的兄長宗憲,謝謝他們一路上的栽培 與耐心的陪伴,在我遭受挫折或沮喪時給我安慰與能量,使我有勇氣面對困境並 得以順利突破,你們是我心靈最後的歸宿,謝謝你們。

李宗翰

99年7月

### **Contents**

| 摘要                                                                                                             | i      |

|----------------------------------------------------------------------------------------------------------------|--------|

| Abstract                                                                                                       | iii    |

| 誌謝                                                                                                             | v      |

| Contents                                                                                                       | vi     |

| Figure Caption                                                                                                 | viii   |

| Chapter 1 Introduction                                                                                         | 1      |

| 1-1 Motivation to study high-κ dielectrics                                                                     | 1      |

| 1-2 Motivation to study metal gate                                                                             | 2      |

| 1-3 The measurement of the devices                                                                             | 4      |

| Chapter 2 General Background of Flash Memory                                                                   | 9      |

| 2-1 Evolution of Non-volatile Memory                                                                           | 9      |

| 2-1.1 Overview of Non-volatile Memory Development                                                              | 10     |

| 2-1.2 Floating Gate and SONOS Memory Device physics                                                            | 10     |

| 2-1.3 Charge-tapping type is More Competitive to Floating Gate Str                                             | acture |

|                                                                                                                | 14     |

| 2-2 Motivation to study MONOS Flash memory                                                                     | 14     |

| Chapter 3 A Novel Program-erasable High-κ HfO <sub>2</sub> -ZrO <sub>2</sub> /Si MIS Capacito                  | or21   |

| 3-1 Introduction                                                                                               | 21     |

| 3-2 Experimental                                                                                               | 21     |

| 3-3 Results and discussion                                                                                     | 22     |

| Chapter 4 Low Voltage SiO <sub>2</sub> /HfO <sub>2</sub> -ZrO <sub>2</sub> /SiO <sub>2</sub> /MoN MONOS Memory | 40     |

| 4-1 Introduction                                                                                               | 40     |

| 4-2 Experimental                                                                                               | 41     |

| 4_3 Results and discussion                                                                                     | /11    |

| Chapter 5 Conclusions |    |

|-----------------------|----|

| References            | 50 |

| Chapter 1:            | 50 |

| Chapter 2:            | 54 |

| Chapter 3:            | 56 |

| Chapter 4:            | 59 |

### **Figure Caption**

| Chapter 1 Introduction                                                                   |

|------------------------------------------------------------------------------------------|

| Fig.1-1 The evolution of MOS technology requirement. 5                                   |

| Fig.1-2 The value of high-κ materials6                                                   |

| Fig.1-3 The band offset of popular high-κ materials6                                     |

| Fig.1-4 The advantages and requirements of metal gate technology7                        |

| Fig.1-5 The values of work function for different metal materials                        |

| Chapter 2 General Background of Flash Memory                                             |

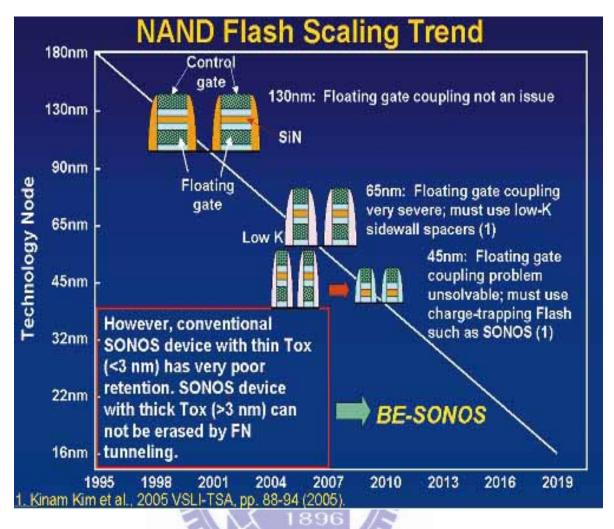

| Fig.2-1 Scaling trend for flash memory device development                                |

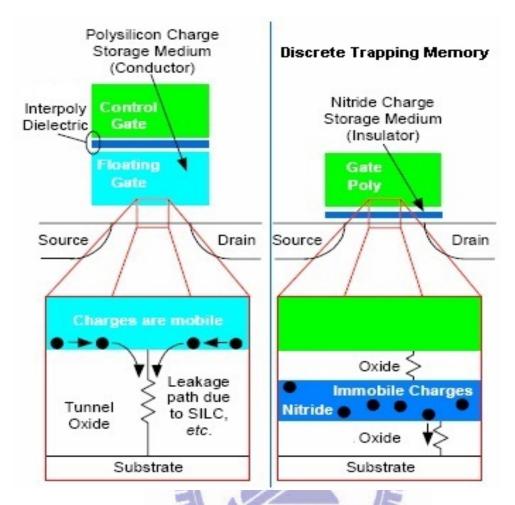

| Fig.2-2 Diagrams illustrating physical structures of floating-gate and discrete trapping |

| (SONOS) devices [2.6]                                                                    |

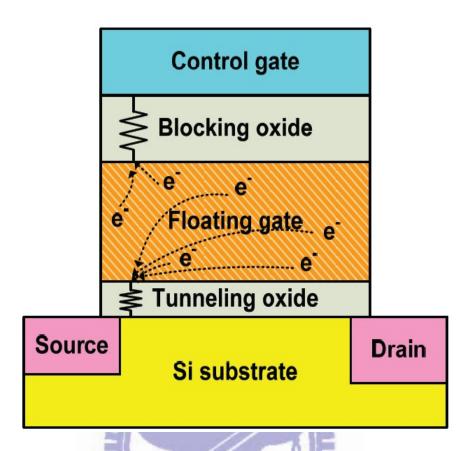

| Fig.2-3 Basic concept of floating gate (FG) non-volatile memory                          |

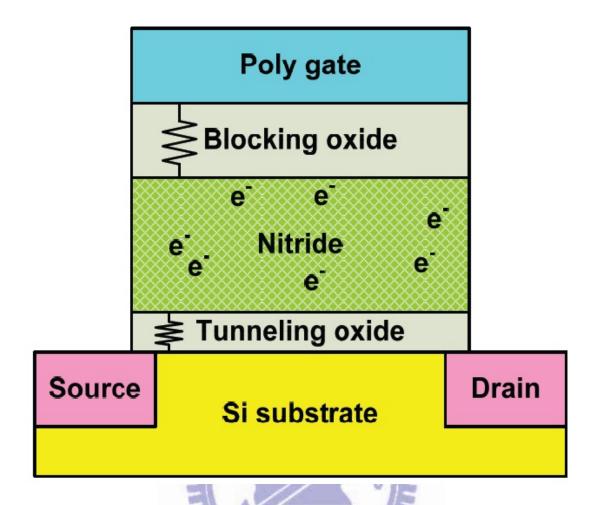

| Fig.2-4 Basic concept of SONOS non-volatile memory                                       |

| Fig.2-5 The requirements for NV memory (the international technology roadmap for         |

| semiconductors: 2006 update)20                                                           |

| Chapter 3 A Novel Program-erasable High-κ HfO <sub>2</sub> -ZrO <sub>2</sub> /Si MIS     |

| Capacitor                                                                                |

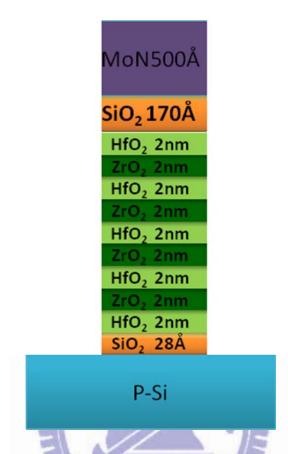

| Fig.3-1 Cross section view of novel program-erasable interactive structure               |

| high-κ HfO <sub>2</sub> -ZrO <sub>2</sub> MIS capacitors                                 |

| Fig.3-2 Cross section view of novel program-erasable high-к HfO <sub>2</sub> MIS         |

| capacitors27                                                                             |

| Fig.3-3 The measured C-V hysteresis of high-κ HfO <sub>2</sub> MIS capacitors after      |

Post-deposition annealing (PDA) in  $N_2$  ambient at  $600^{\circ}\text{C}$  for 5

| barrier without a field. The dashed line shows the effect of an electric field                             |

|------------------------------------------------------------------------------------------------------------|

| on the barrier. The slope of the dash-dot line is proportional to the applied                              |

| field                                                                                                      |

| Fig.3-5 The $ln(J)-E^{1/2}$ and $ln(J/T^2)-E^{1/2}$ plots, using the measured J-V of a                     |

| MoN/HfO <sub>2</sub> /Si MIS device, where the electron injection is from the Si.(a)                       |

| Calculated data using Schottky Emission (SE) and (b) Frenkel-Poole (FP)                                    |

| conduction models are included                                                                             |

| Fig.3-6 (a) The retention characteristics of $V_{FB}$ from the C-V curves programmed or                    |

| erased at $\pm 10V$ or $\pm 10$ V,(b) The P/E characteristics for HfO <sub>2</sub> MIS                     |

| capacitor31                                                                                                |

| Fig.3-7 The measured C-V hysteresis of interactive structure high-κ HfO <sub>2</sub> -ZrO <sub>2</sub> MIS |

| capacitors after Post-deposition annealing (PDA) in O2 ambient at                                          |

| 600°C for 5 min                                                                                            |

| Fig.3-8 The measured C-V hysteresis of interactive structure high-κ HfO <sub>2</sub> -ZrO <sub>2</sub> MIS |

| capacitors after Post-deposition annealing (PDA) in N2 ambient at                                          |

| 600°C for 5 min                                                                                            |

| Fig.3-9 The schematic band diagram of the MoN metal gate/high-κ HfO <sub>2</sub> -ZrO <sub>2</sub> /Si     |

| MIS capacitor34                                                                                            |

| Fig.3-10 The schematic band diagram of the metal-gate/high-κ dielectric/Si MIS                             |

| capacitor in erase state                                                                                   |

| Fig.3-11 The $ln(J)-E^{1/2}$ and $ln(J/T^2)-E^{1/2}$ plots, using the measured J-V of a                    |

| MoN/HfO <sub>2</sub> -ZrO <sub>2</sub> /Si MIS processed PDA in O <sub>2</sub> ambient at 600°C for 5      |

| min, where the electron injection is from the Si.(a) Calculated data using                                 |

| Schottky Emission (SE) and (b) Frenkel-Poole (FP) conduction models are                                    |

| included36                                                                                                 |

| Fig.3-12 The $ln(J)$ - $E^{1/2}$ and $ln(J/T^2)$ - $E^{1/2}$ plots, using the measured J-V of a ix         |

| MoN/HfO <sub>2</sub> -ZrO <sub>2</sub> /Si MIS processed PDA in N <sub>2</sub> ambient at 600°C for 5                                |

|--------------------------------------------------------------------------------------------------------------------------------------|

| min, where the electron injection is from the Si.(a) Calculated data using                                                           |

| Schottky Emission (SE) and (b) Frenkel-Poole (FP) conduction models are                                                              |

| included37                                                                                                                           |

| Fig.3-13 (a) The retention characteristics of $V_{FB}$ from the C-V curves programmed or                                             |

| erased at $\pm 10V$ or $\pm 10V$ (b) The P/E characteristics of                                                                      |

| MoN/HfO <sub>2</sub> -ZrO <sub>2</sub> /Si MIS processed PDA in O <sub>2</sub> ambient at 600°C for 5                                |

| min                                                                                                                                  |

| Fig.3-14 (a) The retention characteristics of $V_{FB}$ from the C-V curves programmed or                                             |

| erased at $\pm 10V$ or $\pm 10V$ (b) The P/E characteristics of                                                                      |

| MoN/HfO <sub>2</sub> -ZrO <sub>2</sub> /Si MIS processed PDA in N <sub>2</sub> ambient at 600°C for 5                                |

| min39                                                                                                                                |

| Chapter 4 Low Voltage SiO <sub>2</sub> /HfO <sub>2</sub> -ZrO <sub>2</sub> /SiO <sub>2</sub> /MoN MONOS                              |

| Memory                                                                                                                               |

| Fig.4-1 Cross section view of MoN/SiO <sub>2</sub> /HfO <sub>2</sub> -ZrO <sub>2</sub> /SiO <sub>2</sub> /Si structure which was not |

| patterned43                                                                                                                          |

| Fig.4-2 Cross section view of MoN/SiO <sub>2</sub> /HfO <sub>2</sub> -ZrO <sub>2</sub> /SiO <sub>2</sub> /Si MONOS44                 |

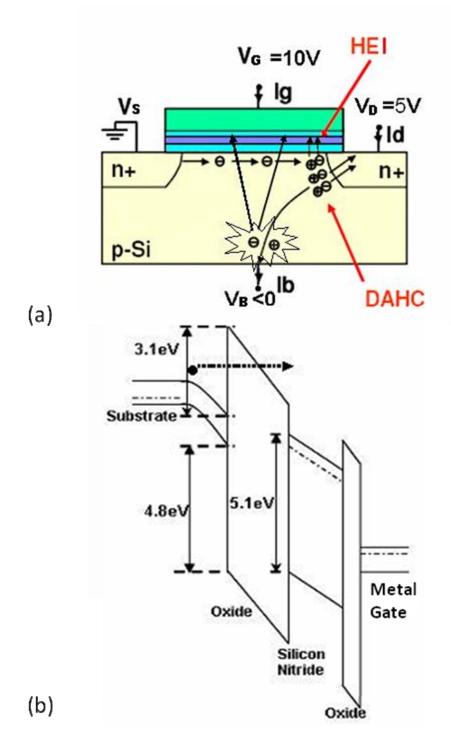

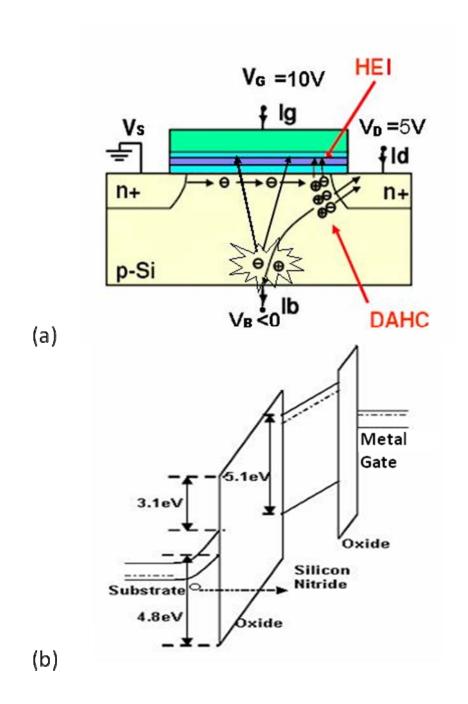

| Fig.4-3 Channel-initiated secondary electron (CHISEL) programming mechanism for                                                      |

| n-channel MONOS memory device. (a) Programming conditions and related                                                                |

| events inside the substrate. (b) Band gap diagram for the programming45                                                              |

| Fig.4-4 Hot holes injection (HHI) erasing characteristics of N channel MONOS                                                         |

| memory device. (a) Erasing conditions and mechanisms. (b) Erasing band                                                               |

| gap diagram46                                                                                                                        |

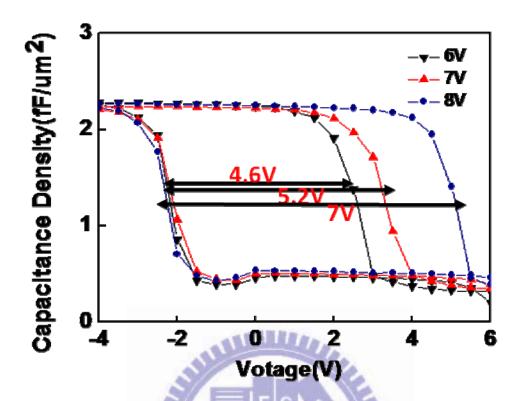

| Fig.4-5 The measured C-V hysteresis of high-κ HfO <sub>2</sub> -ZrO <sub>2</sub> interactive trapping                                |

| MONOS capacitor                                                                                                                      |

| Fig.4-6 The measured J-V characteristics of high-κ HfO <sub>2</sub> -ZrO <sub>2</sub> interactive trapping                           |

## **Chapter 1**

### Introduction

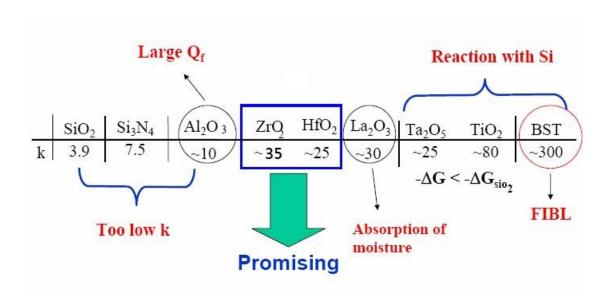

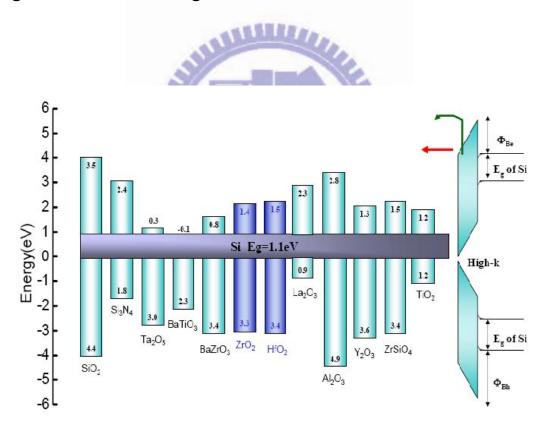

#### 1-1 Motivation to study high-κ dielectrics

Along of the improvement of the semiconductor processing technology, the scaling trend of MOSFETs devices will produce the large gate leakage current due to thinner gate oxide [1.1]-[1.2]. The MOSFETs exhibit significant leakage current more than 1 A/cm<sup>2</sup> when the thickness of ultra-thin silicon gate oxide (SiO<sub>2</sub>) is less than 2 nm. To reduce the leakage current related higher power consumption in highly integrated circuit and overcome the physical thickness limitation of silicon dioxide, the conventional SiO<sub>2</sub> will be replaced with high dielectric constant (high-κ) materials as the gate dielectrics beyond the 0.1µm technology node [1.3]-[1.8]. Therefore, the engineering of high-κ gate dielectrics have attracted great attention and played an important role in technology pull for VLSI. Although high-κ materials often exhibit smaller bandgap and higher defect density than conventional silicon dioxide, using the high-k gate dielectric can increase efficiently the physical thickness in the same effective oxide thickness (EOT) that shows lower leakage characteristics than silicon dioxide by several orders without the reduction of capacitance density [1.4]-[1.7]. Recently, some high-κ materials have been widely studied and successfully intergraded in advanced MOSFETs or semiconductor devices, such as DRAMs or Flash memory and RF metal-insulator-metal (MIM) capacitors [1.9]-[1.10]. According to the ITRS (International Technology Roadmap for Semiconductor), the suitable gate dielectrics must have κ value more than 8 for 50-70 nm technology nodes and that must be more than 15 when the technology dimension less than 50

nm.

- Fig. 1-1 shows the evolution of MOSFET technology requirement. Moreover, the useful gate dielectrics should meet the following fundamental requirements:

- Thermodynamic stability on silicon with respect to formation of SiO<sub>2</sub> and MSi<sub>x</sub>.

- Amorphous after device integration, implies that the dielectrics should remain amorphous after S/D or elevated temperature activation.

- Low conduction for low leakage and low power consumption. For metal oxides

(MOx), it is well known that bandgap is inversely related to κ value (the aluminum

oxide as an exception). Low leakage current implies large band-offset for

electrons and holes.

- High carrier mobility at the dielectric/Si interface. Therefore, the low Dit and lowbulk charges (low effective fixed charges) are requirements.

- High breakdown strength and acceptable reliability. The breakdown strength is inversely related to  $\kappa$  value for metal oxides.

The most popular high- $\kappa$  materials which are studied extensively nowadays are metal oxides (MOx), such as Ta<sub>2</sub>O<sub>5</sub>, TiO<sub>2</sub>,HfO<sub>2</sub>, ZrO<sub>2</sub>,Al<sub>2</sub>O<sub>3</sub> and La<sub>2</sub>O<sub>3</sub> which have the higher  $\kappa$  values ranging from 9 to 80. However, the most metal oxides will have the characteristics of crystallization at elevated temperature which cause devices generate non-uniform leakage distribution and give large statistical variation for nano-meter devices across the chip. Therefore, replacement gate strategies have been proposed to prevent crystallization and deleterious effects of mass and electrical transport along grain boundaries. Figs.1-2 and 1-3 summarize the  $\kappa$  value and band offset for popular high- $\kappa$  dielectric candidates.

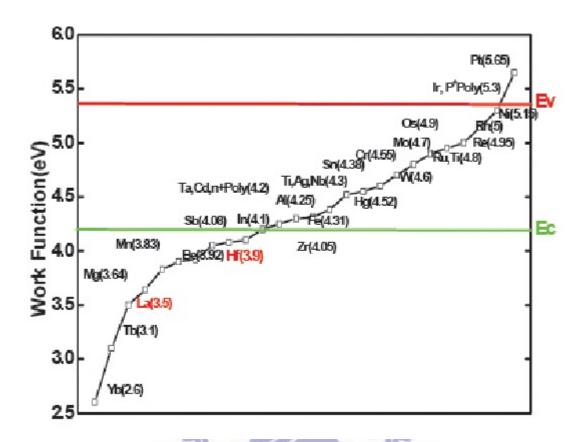

#### 1-2 Motivation to study metal gate

Metal gate is required for advanced CMOS transistors to eliminate poly gate

depletion [1.11]-[1.18]. Since the EOT target prescribed by the ITRS roadmap in years 2018 is only 0.5 nm for 7 nm CMOS, any depletion of the poly-Si gate electrode will be unacceptable. To overcome this problem, the metal gate electrode will be required to make poly-depletion free due to the poly depletion will reduce the capacitance and contribute a degradation to EOT in inversion state [1.11]-[1.23], is shown in Fig. 1-4. The work function ( $\Phi_B$ ) of metal (in Fig. 1-5) play an important role for metal-gate/high-κ MOSFET. The preferred work function of the metals are ~5.1 eV for p-MOSFETs and ~4.2 eV for n-MOSFETs. However, one of the difficult challenges for metal-gate/high-k CMOS devices is large threshold voltage (Vth) due to Fermi-level pinning effect. This is especially difficult for pMOSFET [1.11] since only Ni (5.15 eV), Ir (5.27 eV) and Pt (5.65 eV) in the Periodic Table have work function close to the desired 5.2 eV used in conventional p<sup>+</sup> poly-Si gated p<sup>-</sup>MOS (in Fig.1-5). In addition, thermal stability of the effective metal electrode and metal diffusion are also important considerations. Recently, lots of metal or metal-nitride materials have been widely researched and successfully intergraded in advanced CMOSFET's, such as TiN, TaN, Pt, Mo, MoN and Ir [1.11]-[1.23]. Molybdenum (Mo) has a work-function close to n<sup>+</sup> poly-Si. Molybdenum nitride (MoN) is quite stable (to maintain thermal stability up to a 1000°C RTA) because the activation energy of metal and nitrogen is relatively low. Molybdenum is bonded tightly within nitride and no obvious diffuse was observed in fabricated devices. However, MoN gate on high-k HfO2 shows a significant shift of flat band voltage (VFB) toward the mid-gap of Si due to the interface reaction between the MoN and HfO<sub>2</sub> at the high temperature. This is called the "Fermi-level pinning effect." Therefore, the Fermi-level pinning effect needs to be avoided by selecting suitable metal gate and high-κ materials for advanced MOSFETs.

For MONOS structured non-volatile memory device, the metal electrode with high

work function is needed. The metal gate with higher work-function can prevent the electron injection from electrode in erase operation [1.24]. That improves efficiently erase speed.

#### 1-3 The measurement of the devices

To investigate the electrical characteristics of devices, we measured the  $I_g$ - $V_g$  curves for gate leakage current by using HP4156A semiconductor parameter analyzer. Besides, HP4284A precision LCR meter was used to evaluate the gate capacitance and the conductance ranging from 100 kHz to 1 MHz. For memory measurement, the fabricated MONOS devices were characterized by program/erase measurements.

|                                           |               | 2003 | 2005 | 2007 | 2009 | 2012 | 2015 | 2018 |

|-------------------------------------------|---------------|------|------|------|------|------|------|------|

| Gate Length (nm)                          |               | 107  | 80   | 65   | 50   | 30   | 25   | 18   |

| EOT<br>(nm)                               | High<br>Speed | 1.3  | 1.2  | 0.9  | 0.8  | 0.7  | 0.6  | 0.5  |

|                                           | Low Power     | 1.6  | 1.4  | 1.2  | 1.0  | 0.9  | 0.8  | 0.7  |

| S/D Junction Depth (X <sub>j</sub> , nm)* |               | 49.5 | 35.2 | 27.5 | NA   | NA   | NA   | NA   |

| Interconnect Levels                       |               | 9    | 11   | 11   | 12   | 12   | 13   | 14   |

| Logic<br>V <sub>DD</sub> (V)              | High<br>Speed | 1.2  | 1.1  | 1.1  | 1.0  | 0.9  | 0.8  | 0.7  |

|                                           | Low Power     | 1.0  | 0.9  | 0.8  | 0.8  | 0.7  | 0.6  | 0.5  |

Source: International Technology Roadmap for Semiconductor (ITRS 2003)

Fig.1-1 The evolution of MOS technology requirement.

Fig.1-2 The value of high- $\kappa$  materials.

Fig.1-3 The band offset of popular high- $\kappa$  materials.

- · Advantages:

- no GDE, low sheet resistance

- Requirements:

- Appropriate F<sub>M</sub> (~4.1eV for NMOS; ~5.2eV for PMOS)

- High  $T_m$  (>1000°C), stable interface w/ gate dielectric

- Compatible with Si processing (deposition, etch)

- Candidate materials:

- High- $T_m$  metals (Ti (Ir, Ta), Mo, Ru, W, Pt) and alloys

Fig.1-4 The advantages and requirements of metal gate technology.

Fig.1-5 The values of work function for different metal materials.

# Chapter 2

## **General Background of Flash Memory**

#### 2-1 Evolution of Non-volatile Memory

Since the millennium, people's daily life habit has been changed by various kinds of portable electronic products, such as notebook computer, digital camera, MP3 player, personal digital assistant (PDA), USB, iPod...and so on. The memory devices need to be adopted into all of these electronic products to make them work for different functions. These memories can be divided into volatile memory and non-volatile memory. The use of non-volatile memory (NVM) is to remain the storage data for a long time without power supply, and then portable electronic products can work just by battery due to low power consumption of non-volatile memory.

Non-volatile memories are mainly classified into non-charge-based memory and charge-based memory. The typical charge-based memory is the so called flash memory. There are three types of flash memory including the floating gate (FG) type, SONOS (Silicon/Oxide/Nitride/Oxide/Silicon) type, and nano-crystal type. The mainstream of NVM nowadays is floating gate (FG) type. Some non-charge-based memories have been in small volume production, such as magnetroresistive random access memory (MRAM). The production technologies of ferroelectric random access memory (FeRAM) and phase change random access memory (PCRAM) are still under development. A novel resistive random access memory (RRAM) attracts much more attention recently. All types of flash memories and non-charge-based memories are introduced in detail in the following section.

Smart system must have larger brains which include both sophisticated functions

(code storage) and more memory capacity (data storage). These characteristics can be served by two types of flash memories. The NOR-type memory has fast and random access capability for the code storage, and the NAND-type memory has the page access architecture for date storage [2.1].

#### 2-1.1 Overview of Non-volatile Memory Development

After decades of development with device scaling, several technologies have been employed for product manufacturing, including earlier metal-nitride-oxide-semiconductor (MNOS), electrical programmable read-only-memory (EPROM), and more recently Flash [2.2][2.3].

Because of mass data storage requirement in electronic products, Flash device has become the mainstream in non-volatile semiconductor memory products nowadays [2.4]. An indispensable trend for technology development is to shrink the channel length for a higher storage capacity. Moreover, lowering the voltage for writing/erasing operations is essential for lower power consumption, while high speed access is required to shorten mass data storage time.

#### 2-1.2 Floating Gate and SONOS Memory Device physics

Fig. 2-1 shows that it is necessary to extend the actual flash memory device technology lifetime as much as possible. Through decades of development, flash devices are categorized into two types of structures, namely, FG [2.5] and charge trapping structures, as illustrated in Fig. 2-2. For FG devices, owing to the high topography of the gate structure, the interference between neighboring cells by gate coupling becomes an almost unsolvable issue beyond 45nm-node. As a consequence charge trapping flash memory devices such as SONOS is revisited as the succeeding technology to avert interference between neighboring cells.

Before the floating gate (FG) non-volatile memory, the magnetic-core memory[2.7] has a lot of issues, such as large volume, high power consumption, and high cost. Therefore, new kind of memory needs to be invented to replace the magnetic-core memory. In 1967, the first floating gate non-volatile memory was invented by D. Kahng and S. M Sze at Bell Labs [2.8]. FG structure is composed of a POLY1 floating gate inserted between an underlying tunnel oxide and a blocking oxide layer. A POLY2 layer is deposited on top of the blocking oxide layer to serve as the control gate, as shown in Fig. 2-3. In SONOS structure, in Fig. 2-4, a carrier-trapping layer made up of nitride is inserted between two silicon oxide layers to prevent charge loss. Such flash cells resemble a standard MOS transistor except that the gate oxide is replaced by an oxide-nitride-oxide dielectric stack [2.9].

The storage material is typically a degenerately doped poly-Si for floating-gate devices and a nitride layer for SONOS devices. The mechanisms of charge storage are different between the two types of devices due to the different storage materials. Since the floating gate is made up of a conducting material, the stored electrons flow freely inside the floating gate. This raises a reliability issue in that if certain paths for stress induce leakage current (SILC) are created in the tunnel oxide during operation, the stored charges may easily find the path to leak out which in turn lead to poor retention and endurance characteristics. On the other hand, the nitride storage layer in SONOS device contains discrete traps serving as the charge storage sites. The injected electrons are trapped in deep level of the nitride layer and become immobile, so the aforementioned SILC issue can be avoided and better retention and endurance are expected [2.10].

Programming operation can be achieved by injecting charges into the storage layer, a nitride for the SONOS or a poly layer for the FG type. Channel or substrate hot carrier injections are usually employed for this purpose. On the other hand, erasing

mechanism could be implemented via band-to-band hot holes injection from drain side. For efficiency, both programming and erasing operations need high biases on the gate and drain. The high electric field may provoke potential reliability concerns such as oxide breakdown and generation of excessive SILC. Moreover, high power consumption while the devices are under programming and erasing operations is inevitable [2.11].

The difference between FG and SONOS-type devices lies in the method of charge storage, which is fundamental to issues such as scaling and radiation hardness. The concept of nonvolatile data storage based on a shift in the threshold voltage of the nonvolatile semiconductor memory (NVSM). The threshold voltage has the following expression [2.12]

$$V_{th} = \Phi_{gs} + 2\Phi_{F} - \frac{Q_{ss} + Q_{s}}{c_{t}} + \frac{Q_{T}}{\varepsilon_{t}}$$

(Eq.2-1)

where Qss is the fixed charge at Si-SiO<sub>2</sub> interface,  $Q_{\rm g}$  is the charge in silicon semiconductor, QT is the charge stored in the gate insulator, C<sub>I</sub> and  $\varepsilon_{\rm I}$  are the capacitance per unit area and dielectric constant of the gate insulator layer, respectively. Based on Eq.2-1, threshold voltage increases when more electrons are trapped. On the contrary, threshold will be decreased, if Q<sub>S</sub> quantities are reduced. Therefore we can control Q<sub>S</sub> by means of varying the substrate doping concentration to adjust the threshold voltage of flash devices. The threshold voltage window (Program V<sub>th</sub> – Erase V<sub>th</sub>) should be maintained at least 1.5V to easily distinguish between "1" and "0" states by peripheral sense amplifier circuits [2.13]. The storage charges will gradually leak away as the storage time progresses because of the existence of different leakage mechanisms. The capability of preserving the charge

storage is directly related to the data retention and device life time. Therefore the FG device has added a thick oxide layer or ONO (oxide-nitride-oxide) layer above POLY1 to reduce charge loss through the top side while keeping the gate coupling ratio. On the other hand, SONOS must maintain a tunneling oxide thickness of around 2nm or above to prevent the excessive direct tunneling of charges from nitride layer to substrate. When thickness of oxide is smaller than 25Å or extreme big electric field across on the thin oxide, it is easier to happen direct tunneling which is hopeless for ONO structure and it could be eliminate retention. High temperature data retention analysis is usually performed to monitor the variation of programmed threshold voltage as a function of the elapsing time. The measurements are typically performed between 150°C and 250°C to ensure 10-year data retention time. Both programmed and erased operations affect the endurance capability of flash devices. These procedures should thus be carefully designed and optimized to improve the endurance characteristics. Conventionally for floating-gate devices, channel hot electron injection (CHEI) and hot hole injection (HHI) mechanism are employed to program and erase the device, respectively. CHEI has better speed performance. Nevertheless, the hot electrons are injected into POLY1 layer from the channel region near the drain, and may cause defects like trapped charges in the oxide and interface states, so the threshold voltage window narrows with program/erase (P/E) cycles. For SONOS devices, channel induced secondary electron injection (CHISEL) can be an alternative approach for programming, while HHI is used for erasing. CHISEL programming method proceeds by negatively biasing the substrate. As a result, more hot electrons and secondary electrons are generated and the programming speed is effectively improved. CHISEL thus provides better programming efficiency than CHEI. However, CHISEL will also result in interface state damage, so that subthreshold swing (SS) and mobility (Gm) are degraded after P/E cycling.

# 2-1.3 Charge-tapping type is More Competitive to Floating Gate Structure

Charge-tapping type is superior to floating gate structure in the following aspect:

- Tunneling oxide

- Thickness can not be thinner than 8nm.

- Defects generated in oxide

- SILC causes poor reliability

- Blocking oxide

- Thickness is non-scalable

- Gate electron injection if too thin

- Poor coupling ratio if too thick

- Worse erase efficiency

- Lateral scaling limit

- Floating gate coupling

Charge-trapping type is the solution for Floating Gate Memory, stored charges in trapping layer spatially isolated within insulator which avoiding charges leakage with individual leak path. For vertical and horizontal direction, charge-trapping type has good scalability compatible to ITRS of NVM (in Fig.2-5).

### 2-2 Motivation to study MONOS Flash memory

In general, poly-Si as top electrode is widespread applied in ONO charge trapping type of non-volatile memory because poly gate is used in a lot of mature process technology node. Poly-Si is utilized in these roles because of its compatibility with subsequent high temperature processing (temperature from 250-1100°C), its excellent interface with thermal SiO<sub>2</sub> (low concentration of interface states). On the other hand, poly gate have poly gate depletion, and polysilicon exhibits significantly higher

resistivity than single-crystal silicon (except at very high dopant concentrations, where the resistivity is only slightly greater). This is primarily due to two mechanisms:

- Under heat treatment some of the dopant atoms segregate to the grain boundaries, where they do not effectively produce free carriers.

- The grain boundaries are rich in incomplete bonds, and these cause some free carriers to be trapped at the grain boundaries.

The influence of various types of metal nitride gate electrodes, i.e., tantalum nitride, molybdenum nitride, and tungsten nitride, on electrical characteristics of metal-oxide-semiconductor capacitors with hafnium oxide as the gate dielectric material has been studied. The result shows that both the physical and electrical properties of the high-κ gate stack are influenced by the gate electrode materials and the post-metal-annealing temperature. Both the physical thickness and equivalent oxide thickness of the gate stack These metal nitride electrodes are suitable for n-channel metal-oxide-semiconductor device applications increased after the high-temperature N<sub>2</sub> annealing step. The interface state density and oxide trap density of the high-  $\!\kappa$  gate stack were also reduced by the high-temperature  $N_2$  annealing step. Molybdenum nitride (MoN) is quite stable (to maintain thermal stability up to a 1000°C RTA) because the activation energy of metal and nitrogen is relatively low. Molybdenum is bonded tightly within nitride and no obvious diffuse was observed in fabricated devices. However, MoN gate on high-κ HfO<sub>2</sub> shows a significant shift of flat band voltage (V<sub>FB</sub>) toward the mid-gap of Si due to the interface reaction between the MoN and HfO<sub>2</sub> at the high temperature. Therefore, we study on MONOS rather than SONOS.

Fig.2-1 Scaling trend for flash memory device development.

Fig.2-2 Diagrams illustrating physical structures of floating-gate and discrete trapping (SONOS) devices [2.6].

Fig.2-3 Basic concept of floating gate (FG) non-volatile memory.

Fig.2-4 Basic concept of SONOS non-volatile memory.

| Year of Production                                                                | 2014     | 2015     | 2016     | 2017     | 2018     | 2019     | 2020     |

|-----------------------------------------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|

| SONOS/NROM technology - F (nm) [34]                                               | 32       | 28       | 25       | 23       | 20       | 19       | 18       |

| SONOS/NROM cell size – area factor a in multiples of F <sup>2</sup> [35]          | 6.5      | 6.5      | 7        | 7        | 7        | 7        | 7        |

| SONOS/NROM typical cell size (µm²) [36]                                           | 0.007    | 0.005    | 0.004    | 0.0037   | 0.003    | 0.0025   | 0.002    |

| SONOS/NROM maximum number of bits per cell ((physical 2-<br>bit/cell) x MLC) [37] | 4        | 4        | 4        | 4        | 4        | 4        | 4        |

| SONOS/NROM area per bit (µm²) [38]                                                | 0.0018   | 0.0013   | 0.0011   | 0.0009   | 0.0007   | 0.0006   | 0.0005   |

| SONOS Lg-stack (physical – µm) [39]                                               | 0.15     | 0.15     | 0.14     | 0.14     | 0.14     | 0.13     | 0.13     |

| SONOS highest W/E voltage (V) [40]                                                | 5.0-5.5  | 5.0-5.5  | 4.5-5.0  | 4.5-5.0  | 4.0-4.5  | 4.0-4.5  | 4.0-4.5  |

| SONOS/NROM I <sub>read</sub> (µA) [41]                                            | 23-33    | 22-32    | 21-31    | 21-31    | 20-30    | 20-30    | 20-30    |

| DRAM ½ Pitch (nm) (contacted)                                                     | 28       | 25       | 22       | 20       | 18       | 16       | 14       |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)(contacted)                                     | 28       | 25       | 22       | 20       | 18       | 16       | 14       |

| MPU Physical Gate Length (nm)                                                     | 11       | 10       | 9        | 8        | 7        | 6        | 6        |

| SONOS/NROM tunnel oxide thickness (nm) [42]                                       | 3        | 3        | 2.5      | 2.5      | 2.5      | 2        | 2        |

| SONOS/NROM nitride dielectric thickness (nm) [43]                                 | 4        | 4        | 4        | 4        | 4        | 4        | 4        |

| SONOS/NROM blocking (top) oxide or dielectric thickness (nm)<br>[44]              | 6        | 6        | 5        | 5        | 5        | 5        | 5        |

| SONOS/NROM endurance (erase/write cycles) [45]                                    | 1.00E+08 | 1.00E+08 | 1.00E+09 | 1.00E+09 | 1.00E+09 | 1.00E+09 | 1.00E+09 |

| SONOS/NROM nonvolatile data retention (years) [46]                                | 10-20    | 10-20    | 10-20    | 10-20    | 10-20    | 10-20    | 10-20    |

Fig.2-5 The requirements for NV memory (the international technology roadmap for semiconductors: 2006 update).

## Chapter 3

# A Novel Program-erasable High-κ HfO<sub>2</sub>-ZrO<sub>2</sub>/Si MIS Capacitor

#### 3-1 Introduction

Capacitors are essential devices for various analog, RF and DRAM functions [3.1]-[3.8] in circuits. It is also desirable to have a program-erasable capability. This is especially important for RF ICs where process variations can shift the resonance frequency of LC tank away from designed values, creating impedance mismatches and bandpass frequency differences [3.9]. Program-erasable capacitors can also extend the data retention for DRAMs leading to less frequent re-flashing cycles. In this dissertation, we propose and demonstrate a MIS capacitor on Si using interactive high-κ materials of Hafnium oxide (HfO<sub>2</sub>) and Zirconium oxide (ZrO<sub>2</sub>) as dielectric, as Fig3.1, which exhibits the program-erase function as well as good data retention. The structure has a programmable and erasable C-V character. In contrast, we execute and demonstrate a MIS capacitor on Si using a single layer of high-κ HfO<sub>2</sub> as dielectric(in Fig.3-2), which shows the program-erase function. The single layer high-κ capacitor has a and erasable C-V character.

#### **3-2 Experimental**

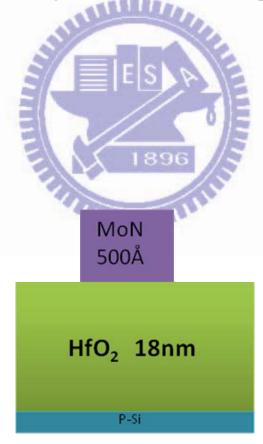

The MIS devices were formed by sputter-depositing a  $\sim$ 18 nm thick single layer  $HfO_2$  on Si substrate which is processed RCA clean. Then, the dielectric layer suffered suffered post-deposition annealed at  $600^{\circ}$ C for 5 min in a furnace under  $N_2$  ambient. Eventually, I sticked shallow mask on wafer tightly, metal electrode was deposited by

PVD and patterned after removing shallow mask. (in Fig.3-2)

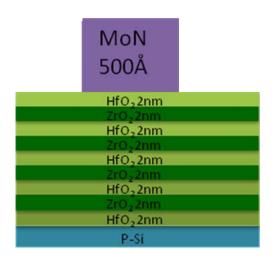

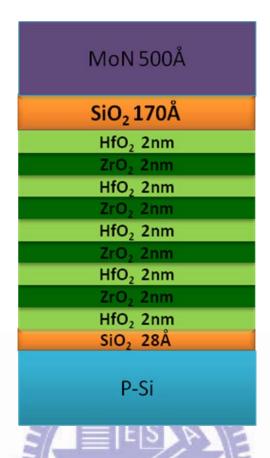

For comparison, the MIS capacitors were fabricated using high- $\kappa$  dielectric process on 4-in 1-10 $\Omega$ -cm p-type Si wafer. After standard pre-gate clean, moving some particles and native oxide on the surface away, the interactive layer (in Fig.3-1) of 18 nm was deposited by physical vapor deposition (PVD) system. This layer first deposits HfO<sub>2</sub> of 2nm then deposits ZrO<sub>2</sub> of 2nm, repeats it with four cycles, eventually deposits HfO<sub>2</sub> of 2nm. And then separate into two classifications. One is post-deposition annealed (PDA) at  $600^{\circ}$ C for 5 min in a furnace under O<sub>2</sub> ambient, another is post-deposition annealed (PDA) at  $600^{\circ}$ C for 5 min in a furnace under N<sub>2</sub> ambient. Finally, MoN metal was deposited by PVD and then patterned by shallow mask to form top electrode with capacitor area of circle with 140 $\mu$ m diameter.

All the C-V characteristics were measured by HP4284A at 1 MHz.

#### 3-3 Results and discussion

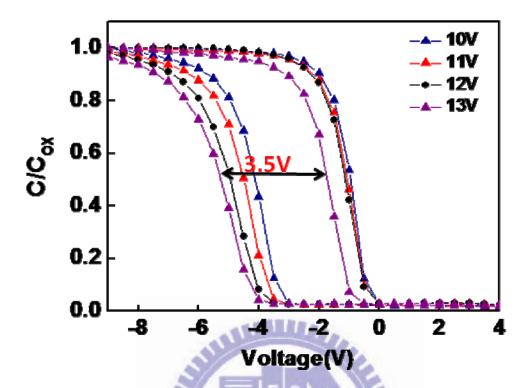

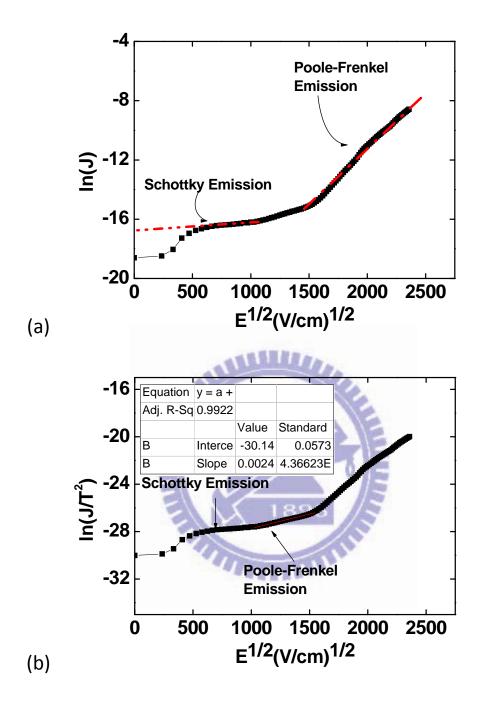

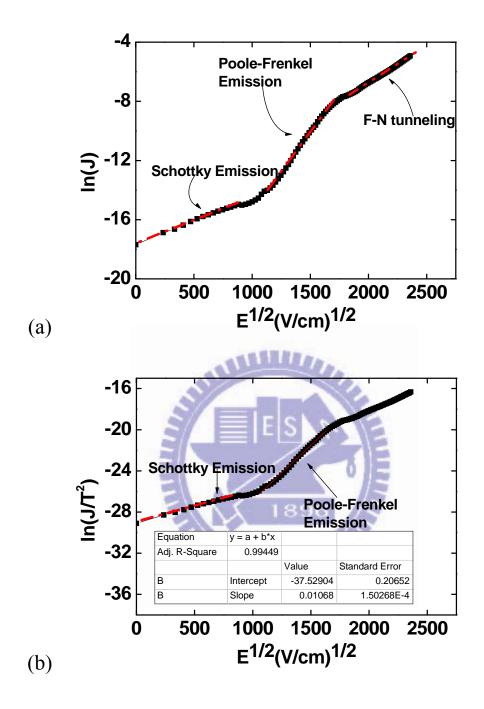

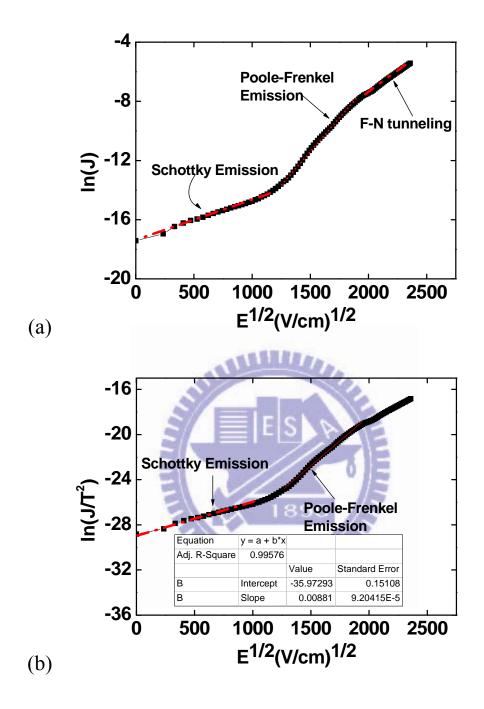

Fig.3-3 show the C-V characteristics of the single high- $\kappa$  HfO<sub>2</sub> layer MIS capacitors processed by PDA at  $600^{\circ}$ C flowed in N<sub>2</sub> ambient. We apply voltage on MoN electrode and erase the high- $\kappa$  HfO<sub>2</sub> /Si MIS capacitors from -13V to 13 Volt, and program the high- $\kappa$  HfO<sub>2</sub>-ZrO<sub>2</sub>/Si MIS capacitors from 13V to -13 V, and it just has 3.5V memory window. the holes tunnel in HfO<sub>2</sub> layer to recombine electrons and eliminate the V<sub>FB</sub> in erase operation, On the contrary, the electrons tunnel in HfO<sub>2</sub> layer and V<sub>FB</sub> elevate. The value of capacitance density is 9.3 fF/ $\mu$ m<sup>2</sup>, we can calculate the  $\kappa$  value is 19. There are three kind of leakage mechanism. MoN metal Gate has large work function so that electron will suffer a high barrier when the external voltage is small. In this way, electrons can not transport to dielectric film, called Schottky Emission. We can use following equation to represent.

$$J\alpha \exp\left[\frac{\gamma E^{1/2} - \nu_b}{kT}\right]$$

(Eq.3-1)

$$\ln(J)\alpha \frac{\gamma}{kT} E^{1/2} - \frac{V_b}{kT}$$

(Eq.3-2)

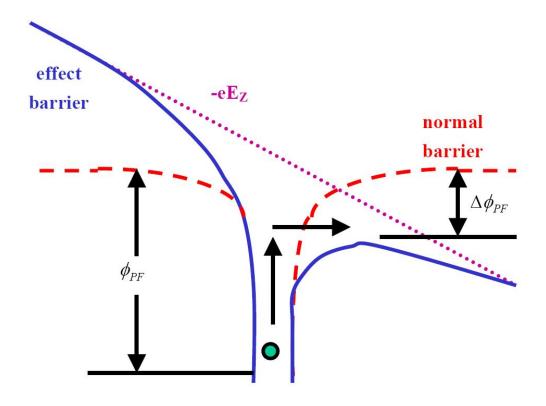

Poole-Frenkel Effect, it means there have charges be trapped in dielectric layer. The Poole-Frenkel effect is the lowering of a Coulombic potential barrier when it interacts with an electric field, and is usually associated with the lowering of a trap barrier in the bulk of an insulator, as shown in Fig.3-4. We can use following equation to represent.

$$\frac{J}{T^2}\alpha \exp\left[\frac{\gamma E^{1/2} - \nu_b}{kT}\right] \tag{Eq.3-3}$$

$$\ln\left(\frac{J}{T^2}\right)\alpha \frac{\gamma}{kT}E^{1/2} - \frac{\nu_b}{kT} \tag{Eq.3-4}$$

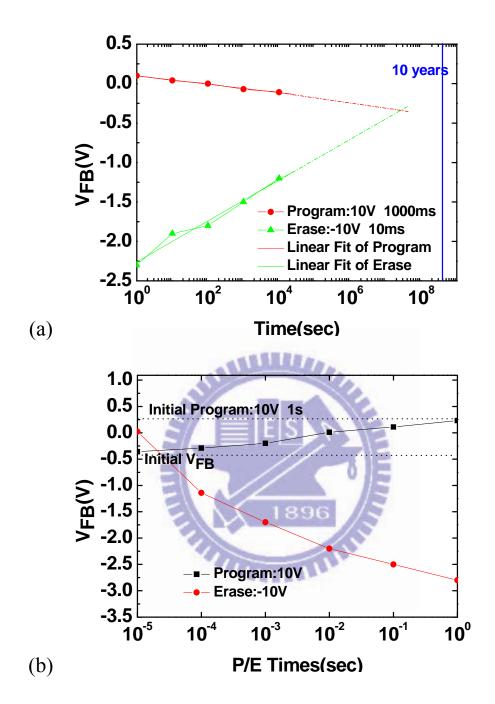

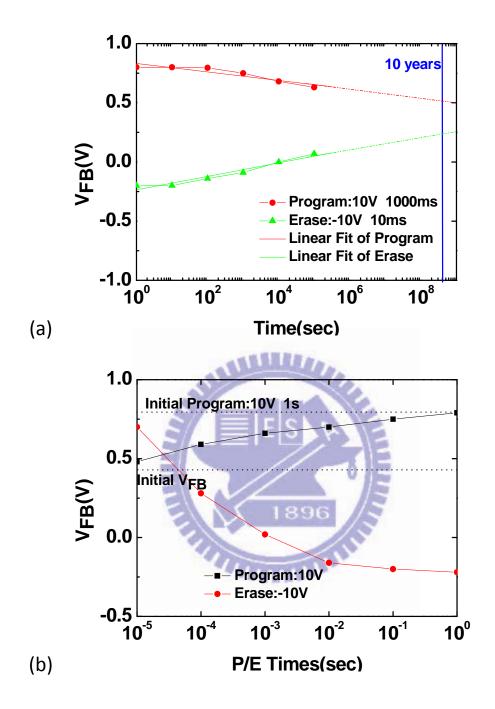

If the external bias is big enough, F-N tunneling will decide the leakage mechanism. We can draw  $\ln(J)$ - $E^{1/2}$  and  $\ln(J/T^2)$ - $E^{1/2}$  relation, and calculate the value of  $\nu_b$  is -0.78 (the intercept of y-axis in Fig.3-5(b) multiplied kT), knowing that the charges was not catch to deep level. To measure retention, I triggered a constant voltage of +10V for program during the pulse length of 1s to the MoN electrode, then, I measured the C-V curves and extracted  $V_{FB}$  shift pass through times. Repeat the same action for erase, the  $V_{FB}$  became larger. Figs.3-6(a) and (b) show poor retention for HfO<sub>2</sub> single layer, therefore, improving the trapping layer by interactive structure.

HfO<sub>2</sub> and ZrO<sub>2</sub> these two materials can't endure temperature more than 35°C when programming process. If depositing them by E-Gun system, temperature is hard to control and the dielectric film may be destroyed. Therefore, I deposit them by sputter system.

Due to the  $\kappa$  value of Hafnium oxide (HfO<sub>2</sub>) is 25 and Zirconium oxide (ZrO<sub>2</sub>) is

35, we can elementarily count up ideal capacitance density. In Eq.3-5,  $\epsilon_0$  is permittivity, A is the capacitor area and t is the thickness of capacitor.

$$\mathbf{C} = \frac{\mathbf{k} \times \mathbf{e}_{p} \times \mathbf{A}}{\mathbf{t}}$$

(Eq.3-5)

Calculation of ideal capacitance density of interactive structure in the following equations:

$$C = \left\{ \left\{ \left( \frac{8.851 \times 10^{-14} \times 25}{20 \times 10^{-8}} \right)^{-1} \times 5 + \left( \frac{8.851 \times 10^{-14} \times 35}{20 \times 10^{-8}} \right)^{-1} \times 4 \right\} \right\}^{-1}$$

(Eq.3-6)

$$= 1.4 \times 10^{-6} \left( \frac{F}{cm^2} \right) = 14 \left( \frac{fF}{\mu m^2} \right)$$

(Eq.3-7)

$$= \frac{6.651 \times 10^{-14} \times 5.9}{\text{EOT}}$$

(Eq.3-8)

By Eqs.3-6 and 3-7, EOT is 2.4nm for MIS which mix up Zirconium oxide (ZrO<sub>2</sub>) to Hafnium oxide (HfO<sub>2</sub>), it is obviously increasing the EOT.

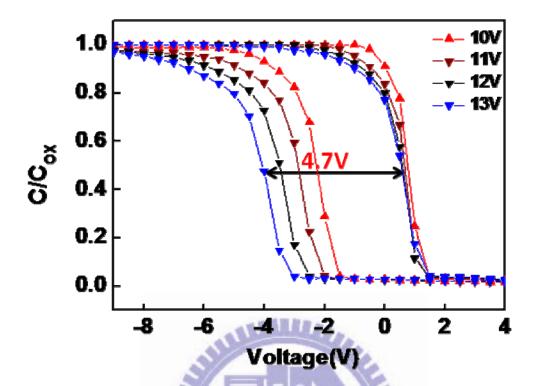

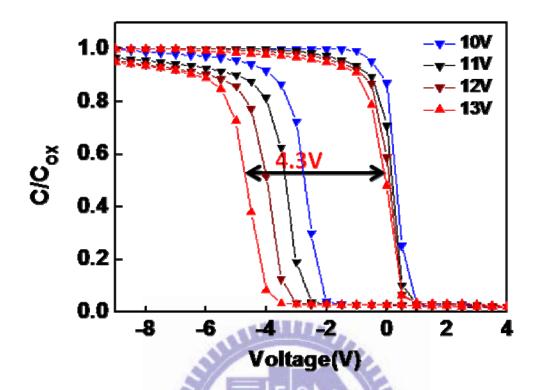

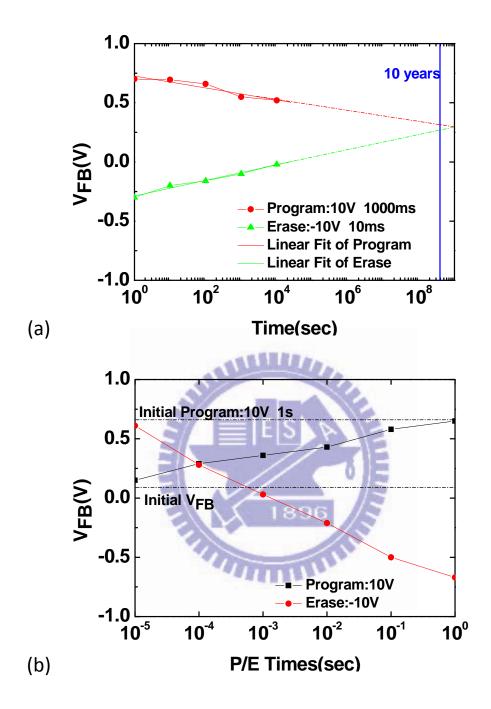

Figs.3-7 and 3-8 show the measured C-V hysteresis of interactive dielectric MoN/HfO<sub>2</sub>-ZrO<sub>2</sub>/Si capacitors measuring by HP4284. We apply voltage on MoN electrode and erase the high-κ HfO<sub>2</sub>-ZrO<sub>2</sub>/Si MIS capacitors from -13V to 13 Volt, and and program the high-κ HfO<sub>2</sub>-ZrO<sub>2</sub>/Si MIS capacitors from 13V to -13 V. It shows large memory window character of 4.7V and the value of capacitance density is 12.2 fF/μm<sup>2</sup> whose dielectric is post-deposition annealed in O<sub>2</sub> ambient at 600°C for 5 min. The interactive dielectric HfO<sub>2</sub>-ZrO<sub>2</sub> after post-deposition annealed in N<sub>2</sub> ambient at 600°C for 5 min shows 4.3V memory window and the value of capacitance density is 11.5 fF/μm<sup>2</sup>. The value of capacitance density elevates. Memory window increasing may be due to increasing charges trapped in dielectric. Single layer has small memory window, the recipes of going through PDA at 600°C flowed N<sub>2</sub> ambient just exhibit 3.5V P/E shift by contrast. Double-layer

Double-layer structure lattice was recombined by PDA process and two high- $\kappa$  materials could be mix together. Although HfO<sub>2</sub> and ZrO<sub>2</sub> have similar band-gap and band-diagram, ZrO<sub>2</sub> in HfO<sub>2</sub> increase the  $\kappa$  value (the  $\kappa$  value of ZrO<sub>2</sub> and HfO<sub>2</sub> is 35 and 25 respectively) and decrease effective oxide thickness. The high capacitor density density is especially important for backend capacitor due to the very thick equivalent-oxide thickness (EOT) > 5 nm and hence the low leakage current. On the other hand, low leakage current is one of the most important factors for high- $\kappa$  gate dielectric with typical EOT  $\leq$ 2 nm[3.10]-[3.16].

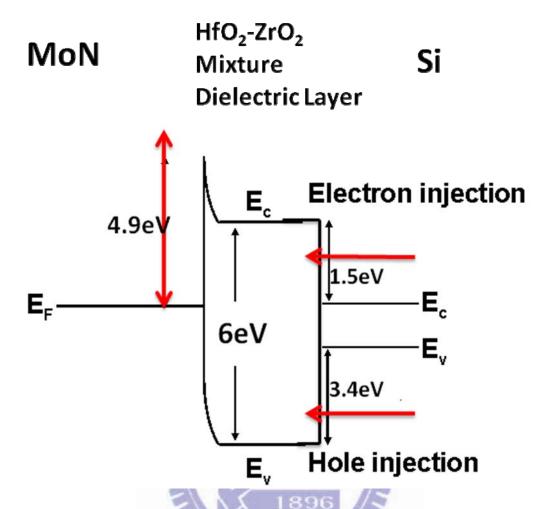

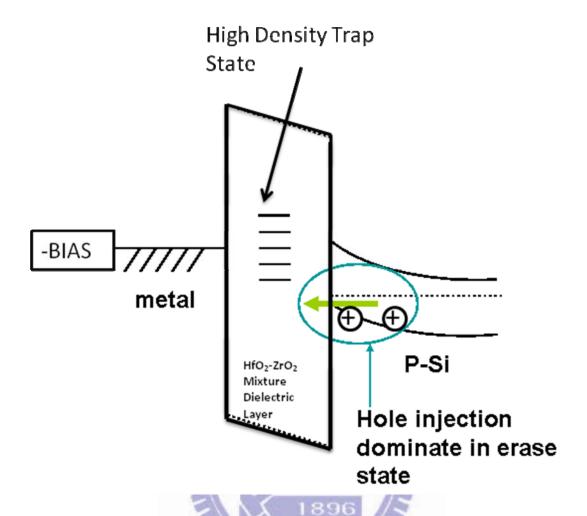

Fig.3-9 shows the schematic band diagram of metal-gate/HfO<sub>2</sub>-ZrO<sub>2</sub>/Si capacitor. The possible erase mechanism may arise from the smaller bandgap (EG  $\sim$ 6.0 eV), small bandgap has more probabilities to catch electrons. This could permit hole injection or electron tunneling out from the high density of trap states, electrons tunnel from Si-sub to trapping layer when metal gate applied positive bias, and hole injection recombines electron trapped deeply in dielectric as metal applied negative bias (Fig.3-10).

In Fig.3-11(b), the value of  $v_b$  PDA in  $O_2$  ambient at  $600^{\circ}$ C for 5 min in Poole-Frenkel Effect is -0.971, and the value of  $v_b$  PDA in  $N_2$  ambient at  $600^{\circ}$ C for 5 min in Poole-Frenkel Effect is -0.931 calculated by intercept of Fig.3-12(b) multiply to the value of kT. Compare modulus of  $v_b$ , PDA in  $O_2$  ambient has excellent ability to catch charges in deep position of trapping layer.

In addition to trapping position, retention is one of the important issue for discuss interactive HfO<sub>2</sub>-ZrO<sub>2</sub> layer. On the whole, a device revealing good retention should have slow velocity to P/E. Figs. 3-13 and 3-14 exhibit the research of interactive HfO<sub>2</sub>-ZrO<sub>2</sub>. It says that processed PDA in O<sub>2</sub> ambient at 600°C for 5 min shows shows good retention for ten years and has excellent speed in erase

operation. PDA in  $N_2$  ambient at  $600^{\circ}C$  for 5 min revealed inferior retention for ten years and the P/E speed is slow because saturation need more time.

Fig.3-1 Cross section view of novel program-erasable interactive structure high- $\kappa$  HfO<sub>2</sub>-ZrO<sub>2</sub> MIS capacitors.

Fig.3-2 Cross section view of novel program-erasable high- $\kappa$  HfO<sub>2</sub> MIS capacitors.

Fig.3-3 The measured C-V hysteresis of high- $\kappa$  HfO<sub>2</sub> MIS capacitors after Post-deposition annealing (PDA) in N<sub>2</sub> ambient at  $600^{\circ}$ C for 5 min.

Fig.3-4 Mechanism of Poole-Frenkel effect. The solid line represents the Coulombic barrier without a field. The dashed line shows the effect of an electric field on the barrier. The slope of the dash-dot line is proportional to the applied field.

Fig.3-5 The ln(J)-E<sup>1/2</sup> and ln(J/T<sup>2</sup>)-E<sup>1/2</sup> plots, using the measured J-V of a MoN/HfO<sub>2</sub>/Si MIS device, where the electron injection is from the Si.(a) Calculated data using Schottky Emission (SE) and (b) Frenkel-Poole (FP) conduction models are included.

Fig.3-6 (a) The retention characteristics of  $V_{FB}$  from the C-V curves programmed or erased at +10V or -10 V,(b) The P/E characteristics for HfO<sub>2</sub> MIS capacitor.

Fig.3-7 The measured C-V hysteresis of interactive structure high- $\kappa$  HfO<sub>2</sub>-ZrO<sub>2</sub> MIS capacitors after Post-deposition annealing (PDA) in O<sub>2</sub> ambient at  $600^{\circ}$ C for 5 min.

Fig.3-8 The measured C-V hysteresis of interactive structure high- $\kappa$  HfO<sub>2</sub>-ZrO<sub>2</sub> MIS capacitors after Post-deposition annealing (PDA) in N<sub>2</sub> ambient at  $600^{\circ}$ C for 5 min.

Fig.3-9 The schematic band diagram of the MoN metal gate/high- $\kappa$  HfO<sub>2</sub>-ZrO<sub>2</sub>/Si MIS capacitor.

Fig.3-10 The schematic band diagram of the metal-gate/high-κ dielectric/Si MIS capacitor in erase state.

Fig.3-11 The  $ln(J)-E^{1/2}$  and  $ln(J/T^2)-E^{1/2}$  plots, using the measured J-V of a MoN/HfO<sub>2</sub>-ZrO<sub>2</sub>/Si MIS processed PDA in O<sub>2</sub> ambient at 600°C for 5 min, where the electron injection is from the Si.(a) Calculated data using Schottky Emission (SE) and (b) Frenkel-Poole (FP) conduction models are included.

Fig.3-12 The  $ln(J)-E^{1/2}$  and  $ln(J/T^2)-E^{1/2}$  plots, using the measured J-V of a MoN/HfO<sub>2</sub>-ZrO<sub>2</sub>/Si MIS processed PDA in N<sub>2</sub> ambient at 600°C for 5 min, where the electron injection is from the Si.(a) Calculated data using Schottky Emission (SE) and (b) Frenkel-Poole (FP) conduction models are included.

Fig.3-13 (a) The retention characteristics of  $V_{FB}$  from the C-V curves programmed or erased at +10V or -10 V (b) The P/E characteristics of MoN/HfO<sub>2</sub>-ZrO<sub>2</sub>/Si MIS processed PDA in  $O_2$  ambient at  $600^{\circ}$ C for 5 min.

Fig.3-14 (a) The retention characteristics of  $V_{FB}$  from the C-V curves programmed or erased at +10V or -10 V (b) The P/E characteristics of MoN/HfO<sub>2</sub>-ZrO<sub>2</sub>/Si MIS processed PDA in  $N_2$  ambient at  $600^{\circ}$ C for 5 min.

## Chapter 4

# Low Voltage SiO<sub>2</sub>/HfO<sub>2</sub>-ZrO<sub>2</sub>/SiO<sub>2</sub>/MoN MONOS Memory

#### **4-1 Introduction**

Poly-Si/SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub>/Si (SONOS) devices are promising for non-volatile memory applications as scaling decreases below 50 nm. This is because of the merit of charge storage in discrete traps within the Si<sub>3</sub>N<sub>4</sub>, which prevents charge leakage through a single oxide defect, as compared with the conventional poly-Si floating gate memory case. By replacing the poly-Si in SONOS with a high work-function metal-gate (MONOS), further improvements of the erase performance can be achieved by decreasing the electron injection over the gate. However, one difficulty in SONOS or MONOS is the small conduction band discontinuity ( $\Delta E_C$ ) of only 1.1 eV at the Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub> interface [4.1], which causes charge leak out from shallow trap levels near E<sub>C</sub> of Si<sub>3</sub>N<sub>4</sub>. In contract, a conventional poly-Si floating gate device has a much deeper energy of ~3.15 eV for storage of charge. Therefore, the high temperature retention is a serious concern for a shallow trap energy MONOS device that uses a Si<sub>3</sub>N<sub>4</sub>. To address this requires the use of a thick SiO<sub>2</sub> tunnel layer to improve the charge storage, but unfortunately this leads to a performance degradation of increased program/erase (P/E) voltage and write speed. This is contrary to the scaling trend indicated in the International Technology Roadmap for Semiconductors (ITRS). To overcome this problem, we have previously proposed using a novel Hafnium oxide (HfO<sub>2</sub>) and Zirconium oxide (ZrO<sub>2</sub>) interactive layer which has deeper  $\Delta E_C$  than Si<sub>3</sub>N<sub>4</sub>. This improved the P/E voltage, and write speeds in such

deep-trap MONOS devices.

## **4-2 Experimental**

The fabrication process of the MoN/SiO<sub>2</sub>/HfO<sub>2</sub>-ZrO<sub>2</sub>/SiO<sub>2</sub>/Si MONOS devices was similar to previous work. First, a 2.8 nm thick thermal SiO<sub>2</sub> was grown on a standard p-Si substrate. Then a 18 nm the interactive layer was deposited by physical vapor deposition (PVD) system. This layer first deposits HfO<sub>2</sub> of 2nm then deposits ZrO<sub>2</sub> of 2nm, repeats it with four cycles, eventually deposits HfO<sub>2</sub> of 2nm. And the dielectric layer suffered post-deposition annealed (PDA) at 600°C for 5 min in a furnace under O<sub>2</sub> ambient. A 17 nm SiO<sub>2</sub> blocking oxide was formed by TEOS, included because of its good thermal stability at 1000°C. Pull the wafer to PDA at 500°C for 5 min in a furnace under O<sub>2</sub> ambient. A 50 nm MoN layer was added by sputtering and processed it by rapid thermal anneal at 450°C in N<sub>2</sub> flow for 15 sec. After standard processing, the structure is as Fig.4-1. To pattern the MONOS, then photo-resist deposition and exposure by mask. The MoN top layer was etched by a high density plasma reactive ion etch (HDP-RIE) system using the gas mixture of BCl<sub>3</sub> and Cl<sub>2</sub> as the etchant source, and then remove photo-resist in acetone, showed in Fig.4-2.

#### 4-3 Results and discussion

To promote the injection efficiency of electrons, the feasibility of using channel-initiated secondary electron (CHISEL) programming has been demonstrated in the MONOS devices [4.2]. CHISEL programming conditions and mechanisms are shown in Fig.4-3(a). The hot holes generated near the drain mainly drift toward the substrate and contribute to the substrate current (I<sub>B</sub>). Some of these hot holes create electron-hole pairs by secondary impact ionization, which are greatly enhanced under a a high electric field by the applying of a reverse substrate bias ( $V_B < 0$ ). As a result,

the hot electrons caused by the secondary impact ionization tend to be injected into the MONOS structure and result in a wide distribution of trapped electrons, compared with the case of channel hot electron injection (CHEI) [4.3]. Fig.4-3(b) illustrates the energy band diagram for CHISEL programming operation. Owing to the reverse substrate bias, the conduction band (E<sub>C</sub>) of the substrate is raised, and the substrate hot electrons can more easily tunnel through the oxide energy barrier (i.e., 3.1eV). Discrete charge storage memories (e.g., SONOS and nanocrystal) are typically erased using hot holes injection (HHI) [4.4], generated by band-to-band tunneling (BBT) in the channel and drain side overlap region. The HHI erasing conditions and mechanisms are shown in Fig.4-4(a). During the HHI erasing operation, the n-type SONOS device is turned off while maintaining a negative gate bias with positive drain and substrate biases. The energy band diagram [4.5] during the HHI erasing operation is shown in Fig.4-4(b). The increased positive bias in substrate causes a downward shift of valance band of the substrate and also helps promote charge trapping efficiency of the nitride layer [4.6]. My discussion replaced the Si<sub>3</sub>N<sub>4</sub> to HfO<sub>2</sub>-ZrO<sub>2</sub> layer own the same program and erase mechanism to above-mentioned.

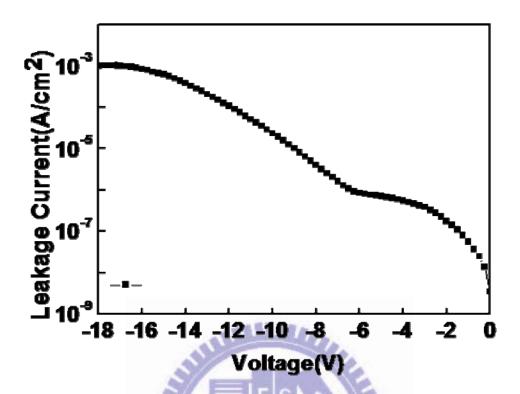

We apply low voltage on MoN electrode and erase the MONOS capacitors from -6Volt to 6 Volt, and program the MONOS capacitors from 6Volt to -6Volt, and then raise the external voltage to erase the MONOS capacitors from -7Volt to 7 Volt, and program the MONOS capacitors from 7Volt to -7Volt, continuously to 8Volt. In Fig.4-5, the *C-V* hysteresis window of 4.6V, 5.2V and 7 V was measured respectively. Low leakage current exhibits the blocking oxide has good quality to isolate electrons as Fig.4-6.

Fig.4-1 Cross section view of MoN/SiO<sub>2</sub>/HfO<sub>2</sub>-ZrO<sub>2</sub>/SiO<sub>2</sub>/Si structure which was not patterned.

Fig.4-2 Cross section view of MoN/SiO<sub>2</sub>/HfO<sub>2</sub>-ZrO<sub>2</sub>/SiO<sub>2</sub>/Si MONOS.

Fig.4-3 Channel-initiated secondary electron (CHISEL) programming mechanism for n-channel MONOS memory device. (a) Programming conditions and related events inside the substrate. (b) Band gap diagram for the programming.

Fig.4-4 Hot holes injection (HHI) erasing characteristics of N channel MONOS memory device. (a) Erasing conditions and mechanisms. (b) Erasing band gap diagram.

Fig.4-5 The measured C-V hysteresis of high- $\kappa$  HfO<sub>2</sub>-ZrO<sub>2</sub> interactive trapping MONOS capacitor.

Fig.4-6 The measured J-V characteristics of high-κ HfO<sub>2</sub>-ZrO<sub>2</sub> interactive trapping MONOS capacitor.

# Chapter 5

## **Conclusions**

Semiconductor flash memory device technology will continue to play an important role in the electronics industry, although its development has been facing a lot of challenges. Conventional FG structure suffers from serious coupling issues that degrade the device characteristics and may eventually limit further device scaling. It thus faces fierce competition from a number of new types of devices, including the MONOS.

In this dissertation, we emphasize on improvement of the trapping layer. If the trapping layer can efficiently catch more charges in a thin film, storage capability may become outstanding. High-κ material of Hafnium oxide (HfO<sub>2</sub>) and Zirconium oxide (ZrO<sub>2</sub>) mix together by post-deposition annealing (PDA) process, in chaper3 and chapter4, we see that the interactive structure reveals big memory window, good retention and program-erase function by charge trapping or de-trapping in the high trap density HfO<sub>2</sub>-ZrO<sub>2</sub>.

## **References**

## Chapter 1:

- [1.1] Wang Bin, J. S. Suehle, E. M. Vogel and J. B. Bernstein, "Time-dependent breakdown of ultra-thin SiO<sub>2</sub> gate dielectrics under pulsed biased stress," *IEEE Electron Device Lett.* 22, pp. 224-226, 2001.

- [1.2] J. H. Stathis, A. Vayshenker, P. R. Varekamp, E. Y. Wu, C. Montrose, J. McKenna, D. J. DiMaria, L. -K. Han, E. Cartier, R. A. Wachnik and B. P. Linder, "Breakdown measurements of ultra-thin SiO<sub>2</sub> at low voltage," in *IEDM Tech. Dig.*, pp. 94-95, 2000.

- [1.3] M. Koyama, K. Suguro, M. Yoshiki, Y. Kamimuta, M. Koike, M. Ohse, C. Hongo and A. Nishiyama, "Thermally stable ultra-thin nitrogen incorporated ZrO<sub>2</sub> gate dielectric prepared by low temperature oxidation of ZrN," in *IEDM Tech. Dig.*, pp. 20.3.1-20.3.4, 2001.

- [1.4] E. P. Gusev, D. A. Buchanan, E. Cartier, A. Kumar, D. DiMaria, S. Guha, A. Callegari, S. Zafar, P. C. Jamison, D. A. Neumayer, M. Copel, M. A. Gribelyuk, H. Okorn-Schmidt, C. D Emic, P. Kozlowski, K. Chan, N. Bojarczuk, L. -A. Ragnarsson and Rons, "Ultrathin high-κ gate stacks for advanced CMOS devices," in *IEDM Tech. Dig.*, pp. 20.1.1-20.1.4, 2001.

- [1.5] W. Zhu, T. P. Ma, T. Tamagawa, Y. Di, J. Kim, R. Carruthers, M. Gibson and T. Furukawa, "HfO<sub>2</sub> and HfAlO for CMOS: thermal stability and current transport," in *IEDM Tech. Dig.*, pp. 20.4.1-20.4.4, 2001.

- [1.6] L. Kang, K. Onishi, Y. Jeon, Byoung Hun Lee, C. Kang, Wen-Jie Qi, R. Nieh, S. Gopalan, R Choi and J. C. Lee, "MOSFET devices with polysilicon on single-layer HfO<sub>2</sub> high-κ dielectrics," in *IEDM Tech. Dig.*, pp. 35-38, 2000.

- [1.7] Rino Choi, Chang Seok Kang, Byoung Hun Lee, K. Onishi, R. Nieh, S. Gopalan,

- E. Dharmarajan and J. C. Lee, "High-quality ultra-thin HfO<sub>2</sub> gate dielectric MOSFETs with TaN electrode and nitridation surface preparation," in *IEDM Tech. Dig.*, pp. 15-16, 2001.

- [1.8] Z. J. Luo, T. P. Ma, E. Cartier, M. Copel, T. Tamagawa and B. Halpern, "Ultra-thin ZrO<sub>2</sub> (or silicate) with high thermal stability for CMOS gate applications," in *Symp. on VLSI Technology*, pp. 135-136, 2001.

- [1.9] K. C. Chiang, C. H. Lai, Albert Chin, T. J. Wang, H. F. Chiu, J. R. Chen, S. P. McAlister, and C. C. Chi, "Very High-Density (23 fF/μm²) RF MIM Capacitors Using high-κ TaTiO as the Dielectric," *IEEE Electron Device Lett.* 26, no. 10, pp. 728-730, 2005.

- [1.10] K. C. Chiang, Albert Chin, C. H. Lai, W. J. Chen, C. F. Cheng, B. F. Hung, and C. C. Liao, "Very High-κ and High Density TiTaO MIM Capacitors for Analog and RF applications," *Symp. on VLSI Technology*, pp. 62-63, Japan, June 2005.

- [1.11] J. K. Schaeffer, C. Capasso, L. R. C. Fonseca, S. Samavedam, D. C. Gilmer, Y. Liang, S. Kalpat, B. Adetutu, H.-H. Tseng, Y. Shiho, A. Demkov, R. Hegde, W. J. Taylor, R. Gregory, J. Jiang, E. Luckowski, M. V. Raymond, K. Moore, D. Triyoso, D. Roan, B. E. White Jr, and P. J. Tobin, "Challenges for the integration of metal gate electrodes," in *IEDM Tech. Dig.*, pp. 287-290, 2004.

- [1.12] W. P. Maszara, Z. Krivokapic, P. King, J. S. Goollgweon, and M. R. Lin, "Transistors with dual work function metal gate by single full silicidation (FUSI) of polysilicon gates," in *IEDM Tech. Dig.*, pp.367–370, 2002.

- [1.13] H.-H. Tseng, C. C. Capasso, J. K. Schaeffer, E. A. Hebert, P. J. Tobin, D. C. Gilmer, D. Triyoso, M. E. Ramón, S. Kalpat, E. Luckowski, W. J. Taylor, Y. Jeon, O. Adetutu, R. I. Hegde, R. Noble, M. Jahanbani, C. El Chemali, and B. E. White, "Improved short channel device characteristics with stress relieved

- pre-oxide (SRPO) and a novel tantalum carbon alloy metal gate/HfO<sub>2</sub> stack," in *IEDM Tech. Dig.*, pp. 821-824, 2004.

- [1.14] H. -J. Cho, C. S. Kang, K. Onishi, S. Gopalan, R. Nieh, R. Choi, E. Dharmarajan and J.C. Lee, "Novel nitrogen profile engineering for improved TaN/HfO<sub>2</sub> Si MOSFET performance," in *IEDM Tech. Dig.*, pp. 30.2.1-30.2.4, 2001.

- [1.15] Y. T. Hou, M. F. Li, T. Low, and D. L. Kwong, "Impact of metal gate work function on gate leakage of MOSFETs," in *DRC Symp.*, pp. 154-155, 2003.

- [1.16] Dae-Gyu Park, Kwan-Yong Lim, Heung-Jae Cho, Tae-Ho Cha, Joong-Jung Kim, Jung-Kyu Ko, Ins-Seok Yeo and Jin Won Park, "Novel damage-free direct metal gate process using atomic layer deposition," in *Symp. on VLSI Technology*, pp. 65-66, 2001.

- [1.17] C. Cabral Jr., J. Kedzierski, B. Linder, S. Zafar, V. Narayanan, S. Fang, A. Steegen, P. Kozlowski, R. Carruthers, and R. Jammy," Dual work-function fully silicided metal gates," in *Symp. on VLSI Technology*, pp. 184-185, 2004.

- [1.18] S. B. Samavedam, L. B. La, J. Smith, S. Dakshina-Murthy, E. Luckowski, J. Schaeffer, M. Zavala, R. Martin, V. Dhandapani, D. Triyoso, H. H. Tseng, P. J. Tobin, D. C. Gilmer, C. Hobbs, W. J. Taylor, J. M. Grant, R. I. Hegde, J. Mogab, C. Thomas, P. Abramowitz, M. Moosa, J. Conner, J. Jiang, V. Arunachalarn, M. Sadd, B.-Y. Nguyen, and B. White," Dual-metal gate CMOS with HfO<sub>2</sub> gate dielectric," in *IEDM Tech. Dig.*, pp. 433-436, 2002.

- [1.19] D. S. Yu, A. Chin, C. C. Laio, C. F. Lee, C. F. Cheng, W. J. Chen, C. Zhu, M.-F.Li, S. P. McAlister, and D. L. Kwong, "3D GOI CMOSFETs with novel IrO<sub>2</sub> (Hf) dual gates and high-κ dielectric on 1P6M-0.18 μm-CMOS," in *IEDM Tech. Dig.*, pp. 181-184, 2004.

- [1.20] D. S. Yu, A. Chin, C. C. Liao, C. F. Lee, C. F. Cheng, M. F. Li, Won Jong

- Yoo, and S. P. McAlister, "3D Metal-Gate/High-κ/GOI CMOSFETs on 1-Poly-6-Metal 0.18-μm Si Devices," *IEEE Electron Device Lett.* 26, pp. 118-120, Feb. 2005.

- [1.21] X. P. Wang, C. Shen, Ming-Fu Li, H.Y. Yu, Yiyang Sun, Y. P. Feng, Andy Lim, Hwang Wan Sik, Albert Chin, Y. C. Yeo, Patrick Lo, and D.L. Kwong," Dual Metal Gates with Band-Edge Work Functions on Novel HfLaO High-κ Gate Dielectric," in *Symp. on VLSI Technology*, pp. 12-13, 2006.

- [1.22] J. H. Lee, H. Zhong, Y.-S. Suh, G. Heuss, J. Gurganus, B. Chen, and V. Misra,"Tunable work function dual metal gate technology for bulk and non-bulk CMOS," in *IEDM Tech. Dig.*, pp. 359-362, 2002.

- [1.23] H. Y. Yu, M. F. Li, and D.L. Kwong," Thermally Robust HfN Metal as a Promising Gate Electrode for Advanced MOS Device Application," *IEEE Transactions on Electron Devices*, vol. 51, Apr., 2004.

- [1.24] C. H. Lee, K. I. Choi, M. K. Cho, Y. H. Song, K. C. Park, and K. Kim, "A novel SONOS structure of SiO<sub>2</sub>/SiN/Al<sub>2</sub>O<sub>3</sub> with TaN metal gate for multi-giga bit flash memories," in *IEDM Tech. Dig.*, pp. 613-616, 2003.

### Chapter 2:

- [2.1] C. Y. Lu, T. C. Lu, and R. Liu, "Non-volatile memory technology-today and tomorrow," in Proc. IEEE-IPFA, 2006, pp. 18-23.

- [2.2] YunSeung Shin, "Non-volatile Memory Technologies for Beyond 2010," Symposium on VLSI circuits digest of Technical, no. 10-2, pp. 156-159, 2005.

- [2.3] R. Koval, V. Bhachawat, C. Chang, M. Hajra, D. Kencke, Y. Kim, C. Kuo, T. Parent, M. Wei, B. J. Woo, and A. Fazio, "Flash ETOX Virtual Ground Architecture: A Future Scaling Direction," *Symposium on VLSI circuits digest of Technical*, no. 11B-1, pp.204-205, 2005.

- [2.4] Brian Dipert and Lou Hebert, "Flash Memory Goes Mainstream," IEEE SPECTRUM, pp.48-52, October 1993.

- [2.5] Greg Atwood, "Future Directions and Challenges for ETox Flash Memory Scaling," *IEEE Trans. on Device and Materials Reliability*, Vol. 4, No. 3, pp.301-305, September 2004.

- [2.6] Barbara De Salvo, Cosimo Gerardi, Rob van Schaijk, Savatore A.Lombardo, Domenico Corso, Cristina Plantamura, Stella Serafino, Giuseppe Ammendola, Michiel van Duuren, Pierre Goarin, Wan Yuet Mei, Kees van der Jeugd, Thierry Baron, Marc Gely, Pierre Mur, and Simon Deleonibus, "Performance and Reliability Features of Advanced Nonvolatile Memories Based on Discrete Traps (Silicon Nanocrystals, SONOS)," IEEE Transactions on Device and Materials Reliability, Vol.4, No. 3, pp.377-389, September 2004.

- [2.7] W. N. Papian, "The MIT magnetic-core memory," in *Proc. Eastern Joint Comp. Conf.*, Dec. 1953, pp. 37-42.

- [2.8] D. Kahng and S. M. Sze, "A floating gate and its application to memory devices," *Bell Syst. Tech. J.*, vol. 46, no. 4, pp. 1288-1295, 1967.

- [2.9] Tung-Sheng Chen, Kuo-Hong Wu, Hsien Chung, and Chin-Hsing

- Kao, "Performance Improvement of SONOS Memory by Bandgap Engineering of Charge-Trapping Layer," *IEEE Electron Device Letters*, Vol. 25, No. 4, pp.205-207, April 2004.

- [2.10] Barbara De Salvo, Cosimo Gerardi, Rob van Schaijk, Savatore A.Lombardo, Domenico Corso, Cristina Plantamura, Stella Serafino, Giuseppe Ammendola, Michiel van Duuren, Pierre Goarin, Wan Yuet Mei, Kees van der Jeugd, Thierry Baron, Marc Gely, Pierre Mur, and Simon Deleonibus, "Performance and Reliability Features of Advanced Nonvolatile Memories Based on Discrete Traps (Silicon Nanocrystals, SONOS)," *IEEE Transactions on Device and Materials Reliability*, Vol. 4, No. 3, pp.377-389, September 2004.

- [2.11] Stefan Lai, "Flash Memories: Where We Were and Where We are Going," *IEDM Tech. Dig.*, pp.971-973, 1998.

- [2.12] Marvin H. White, Dennis A. Adams, and Jiankang Bu, "On the go with SONOS," *IEEE Circuit and Device*, pp.22-31, July 2000.

- [2.13] Roberto Bez, Emilio Camerlenghi, Alberto Modelli, and Angelo Visconti, "Introduction to Flash Memory," *Proceedings of The IEEE*, Vol. 91, No. 4, pp.489-502, April 2003.

### Chapter 3:

- [3.1] C.-M. Hung, Y.-C. Ho, I.-C. Wu, and K. O, "High-Q capacitors implemented in a CMOS process for low-power wireless applications," *in IEEE MTT-S Int. Microwave Symp. Dig.*, 1998, pp. 505-511.

- [3.2] J. A. Babcock, S. G. Balster, A. Pinto, C. Dirnecker, P. Steinmann, R. Jumpertz, and B. El-Kareh, "Analog characteristics of metal-insulator-metal capacitors using PECVD nitride dielectrics," *IEEE Electron Device Lett.*, vol.22, pp. 230-232, May 2001.

- [3.3] C. H. Ng, K. W. Chew, J. X. Li, T. T. Tioa, L. N. Goh, and S. F. Chu," Characterization and comparison of two metal-insulator-metal capacitor schemes in 0.13μm copper dual damascene metallization process for mixed-mode and RF application", in *IEDM Tech. Dig.*, 2002, pp.241-244.

- [3.4] T. Ishikawa, D. Kodama, Y. Matsui, M. Hiratani, T. Furusawa, and D. Hisamoto," High-capacitance Cu/Ta<sub>2</sub>O<sub>5</sub>/Cu MIM structure for SoC applications featuring a single-mask add-on process, in *IEDM Tech. Dig.*, 2002, p. 940-942.

- [3.5] H. Hu, S. J. Ding, H. F. Lim, C. Zhu, M.F. Li, S.J. Kim, X. F. Yu, J. H. Chen, Y. F. Yong, B. J. Cho, D.S.H. Chan, S. C. Rustagi, M. B. Yu, C. H. Tung, A. Du, D. My, P. D. Fu, A. Chin, and D. L. Kwong, "High performance HfO<sub>2</sub>-Al<sub>2</sub>O<sub>3</sub> laminate MIM capacitors by ALD for RF and mixed signal IC applications," in *IEDM Tech. Dig.*, 2003, pp. 379-382.

- [3.6] K. C. Chiang, Albert Chin, C. H. Lai, W. J. Chen, C. F. Cheng, B. F. Hung, and C. C. Liao, "Very high-κ and high density TiTaO MIM capacitors for analog and RF applications," in *Symp. on VLSI Tech. Dig.*, 2005, pp. 62-63.

- [3.7] K. C. Chiang, C. C. Huang, Albert Chin, W. J. Chen, H. L. Kao, M. Hong, and J. Kwo, "High performance micro-crystallized TaN/SrTiO<sub>3</sub>/TaN capacitors for

- analog and RF applications," in Symp. on VLSI Tech. Dig., 2006, pp. 126-127.

- [3.8] K. C. Chiang, C. C. Huang, Albert Chin, G. L. Chen, W. J. Chen, Y. H. Wu, Albert Chin, S. P. McAlister, "High performance SrTiO<sub>3</sub> metal-insulator-metal capacitors for analog applications," *IEEE Trans. Electron Devices*, vol. 53, pp. 2312-2319, September 2006.

- [3.9] C. Zhu, H. Hu, X. Yu, A. Chin, M. F. Li, and D. L. Kwong, "Voltage temperature dependence of capacitance of high-κ HfO<sub>2</sub> MIM capacitors: A unified understanding and prediction," in *IEDM Tech. Dig.*, pp. 379-382, 2003.

- [3.10] D. S. Yu, Albert Chin, C. C. Laio, C. F. Lee, C. F. Cheng, W. J. Chen, C. Zhu, M.-F. Li, S. P. McAlister, and D. L. Kwong, "3D GOI CMOSFETs with novel IrO2 (Hf) dual gates and high-κ dielectric on 1P6M-0.18 μm-CMOS," in *IEDM Tech. Dig.*, CMOS-Section, San Francisco, USA, 2004.

- [3.11] D. S. Yu, K. C. Chiang, C. F. Cheng, A. Chin, C. Zhu, M. F. Li, and D. L. Kwong, "Fully silicided NiSi:Hf/LaAlO<sub>3</sub>/smart-cut-Ge-on-insulator n-MOSFETs with high electron mobility" *IEEE Electron Device Lett.* 25, no. 8, pp. 559-561, 2004.

- [3.12] C. H. Huang, D. S. Yu, A. Chin, W. J. Chen, C. X. Zhu, M.-F. Li, B. J. Cho, and D. L. Kwong, "Fully silicided NiSi and germanided NiGe dual gates on SiO2/Si and Al<sub>2</sub>O<sub>3</sub>/Ge-on-insulator MOSFETs," in IEDM Tech. Dig., pp. 319-322, 2003.

- [3.13] C. H. Huang, M. Y. Yang, A. Chin, W. J. Chen, C. X. Zhu, B. J. Cho, M.-F. Li, and D. L. Kwong, "Very low defects and high performance Ge-on-insulator p-MOSFETs with Al<sub>2</sub>O<sub>3</sub> gate dielectrics," in *Symp. on VLSI Tech.*, pp. 119-120,2003.

- [3.14] H. Iwai, S. Ohmi, S. Akama, C. Ohshima, A. Kikuchi, I. Kashiwagi, J. Taguchi, H. Yamamoto, J. Tonotani, Y. Kim, I. Ueda, A. Kuriyama, and Y.

- Yoshihara, "Advanced gate dielectric materials for sub-100nm CMOS," *in IEDM Tech. Dig.*, pp. 625-628, 2002.

- [3.15] A. Chin, Y. H. Wu, S. B. Chen, C. C. Liao, W. J. Chen, "High quality La<sub>2</sub>O<sub>3</sub>and Al<sub>2</sub>O<sub>3</sub> gate dielectrics with equivalent oxide thickness 5-10 Å," in *Symp. on VLSI Tech. Dig.*, pp. 16-17, 2000.

- [3.16] A. Chin, C. C. Liao, C. H. Lu, W. J. Chen, and C. Tsai, "Device and reliability of high-κ Al<sub>2</sub>O<sub>3</sub> gate dielectric with good mobility and low D<sub>it</sub>," in *Symp. On VLSI Tech. Dig.*, pp. 135-136, 1999.

### Chapter 4:

- [4.1] S. H. Gu, T. Wang, W. P. Lu, Y. H. Ku, and C. Y. Lu, "Extraction of nitride trap density from stress induced leakage current in silicon-oxide-nitride-oxide-silicon flash memory," *Appl. Phys. Lett.*, vol. 89, pp. 163514-163516, 2006.

- [4.2] Souvik Mahapatra, S. Shukuri, and Jeff Bude, "CHISEL Flash EEPROM-Part I: Performance and Scaling," *IEEE Trans. on Electron Devices*, Vol. 49, No. 7, pp.1296-1301, July 2002.

- [4.3] Souvik Mahapatra, S. Shukuri, and Jeff Bude, "CHISEL Flash EEPROM-Part II: Reliability," *IEEE Trans. on Electron Devices*, Vol. 49, No. 7, pp.1302-1307, July 2002.

- [4.4] Y. Wang, Y. Zhao, B. M. Khan, C. L. Doherty, J. D. Krayer, M. H. White, "A novel SONOS Nonvolatile Flash Memory Device Using Substrate Hot-hole Injection for Write and Gate Tunneling for Erase," Semiconductor Device Research Symposium, Vol. 10-12, pp.228-229, December 2003.

- [4.5] Luca Larcher, Paolo Pavan and Boaz Eitan, "On the Physical Mechanism of the NROM Memory Erase," *IEEE Trans. on Electron Device*, Vol. 51, No. 10, pp.1593-1599,October 2004.

- [4.6] Gowrishankar L. Chindalore, Craig T. Swift, and David Burnett, "A New Combination-Erase Technique for Erasing Nitride Based (SONOS) Nonvolatile Memories," *IEEE Electron Device Letters*, Vol. 24, No. 4, pp.257-259, April 2003.