# 國立交通大學

## 電子工程學系 電子研究所

### 碩士論文

應用於微瓦特動態電壓與頻率調節系統設計中近/次 臨界電壓具製程電壓溫度能力之感測器

Near-/Sub-threshold PVT Sensors for Micro-Watt DVFS System Design

> 研究生:陳璽文 指導教授:黃 威 教授 中華民國九十九年七月

應用於微瓦特動態電壓與頻率調節系統設計中近/次

# 臨界電壓具製程電壓溫度能力之感測器 Near-/Sub-threshold PVT Sensors for Micro-Watt DVFS System Design

研究生:陳璽文 Student: Shi-Wen Chen

指導教授:黃 威 教授 Advisor: Prof. Wei Hwang

Submitted to Department of Electronics Engineering & Institute of Electronics College of Electrical Engineering and Computer Engineering National Chiao Tung University in partial Fulfillment of the Requirements

for the Degree of

Master

in

**Electronics Engineering**

June 2009

Hsinchu, Taiwan, Republic of China

中華民國九十九年七月

應用於微瓦特動態電壓與頻率調節系統設計中近/次

臨界電壓具製程電壓溫度能力之感測器

教授

### 學生:陳璽文 指導教授:黃 威

#### 國立交通大學電子工程學系電子研究所

在本篇論文中,我們將目標放在設計並實現一個應用於微瓦特動態電壓與頻率 調節系統設計中具製程電壓溫度能力之感測器。其中包含自動補償全數位之製程 電壓溫度感測器、多臨界電壓互補式金屬氧化層半導體(MTCMOS)之交換式電容 直流-直流轉換器、具數位溫度補償之低電壓鎖相迴路頻率產生器、動態電壓與 頻率調節系統。主要的研究成果如下:

- 提出了一個可以操作在近臨界/次臨界電壓的全數位溫度感測器,具備有 高精準度、電壓小、耗電低、自動補償等優點。

- 提出了一個利用可調性脈衝寬度產生器去自動補償溫度感測器受電壓製 程影響且可以操作在近臨界/次臨界電壓的數位溫度感測器,具備有高精 準度、電壓小、耗電低等優點。

- 在本篇論文中提出了一個可應用於微瓦特系統中具製程電壓溫度感知的 動態電壓與頻率調節系統。本系統透過交換式電容直流-直流轉換器可以 提供非常穩定直流電源,產生不同的電壓位準透過動態電壓轉換電路做電

壓調節。並且透過溫度感測器在不同溫度下選擇不一樣的電壓,可有效的 減少功率消耗和維持系統運作的穩定度。

- 一個新的架構用於提升交換式電容直流-直流轉換器在低負載時的能量效益和電壓穩定度被提出。

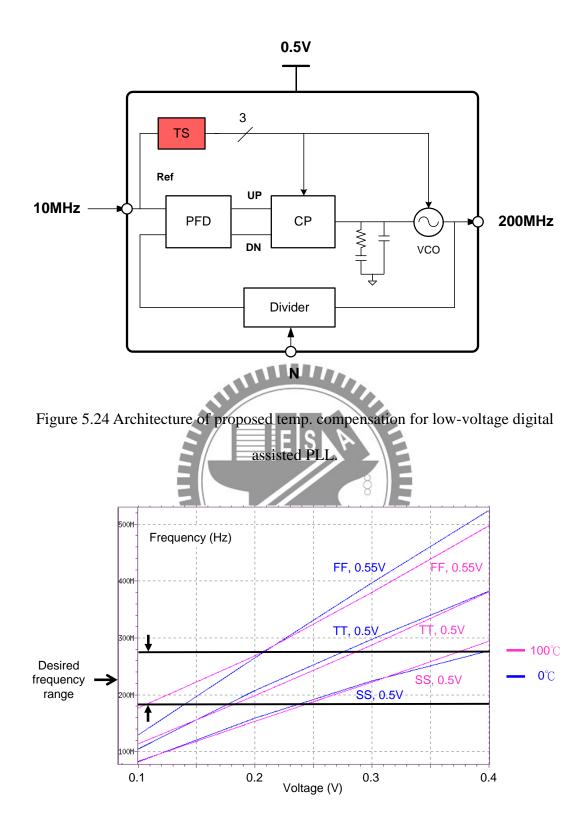

- 在本篇論文中提出一個具數位溫度補償之低電壓鎖相迴路頻率產生器,可 以透過除頻器去調節輸出頻率,以及用溫度去補償最壞情況下頻率無法鎖 住的問題。

## Near-/Sub-threshold PVT Sensors for Micro-Watt DVFS System Design

Student : Shi-Wen Chen

Advisors : Prof. Wei Hwang

Department of Electronics Engineering & Institute of Electronics National Chiao-Tung University

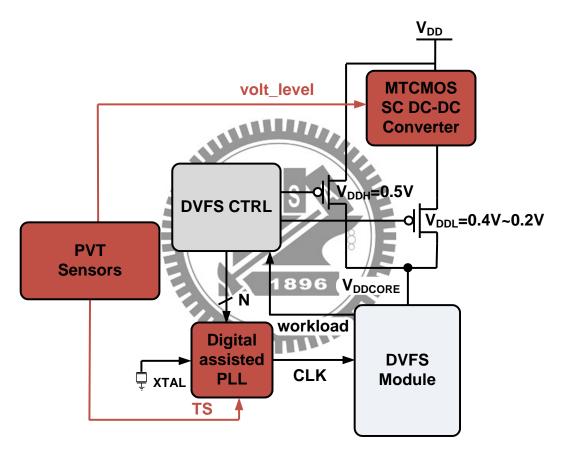

The goal of this research is to design and implement PVT sensors for micro-watt DVFS system design. It includes the design of self-calibration all-digital PVT sensors, MTCMOS switched capacitor (SC) DC-DC converter, temperature compensation for low-voltage digital assist PLL, and dynamic voltage and frequency scaling system. The major contributions are as below:

- 1. A near-/sub-threshold all-digital process, voltage, and temperature sensor is proposed and integrated to the DVFS control for micro-watt system applications. The sensor is proposed for high accuracy, ultra-low voltage, low power, and self-calibration portable applications.

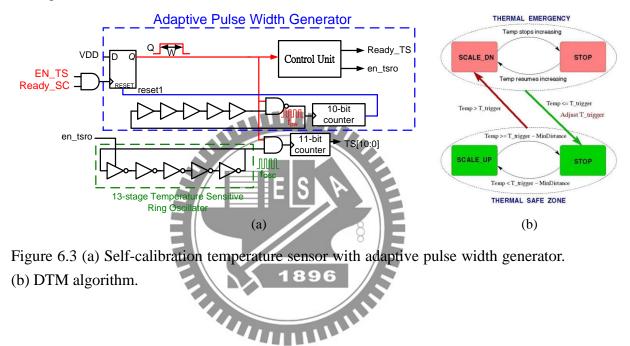

- 2. A self-calibration near-/sub-threshold all-digital temperature sensor with adaptive pulse width generator is proposed. The sensor is proposed for high accuracy, ultra-low voltage, low power, and self-calibration portable applications.

- 3. A PVT-aware DVFS for micro-watt system is proposed. The system through the switched capacitor (SC) DC-DC converter can provide a very stable DC power supply. It generates different voltage levels which are suitable for SoC integrated regulator applications.

- 4. A novel connect scheme for improving power efficiency and reducing voltage variation of switched capacitor (SC) DC-DC converter which generates ultra low voltage is proposed.

- Proposed a temperature compensation for low voltage digital assist PLL can modulate output frequency via divider. Use the temperature sensor to compensate the frequency can not lock in the worth case.

# Content

| 摘    | 要                                                                        | i |

|------|--------------------------------------------------------------------------|---|

| ABS  | <b>TRACT</b> ii                                                          | i |

| Con  | tent                                                                     | v |

| List | of Figures                                                               | i |

| List | of Tables                                                                | X |

| Cha  | pter 1 Introduction1                                                     | 1 |

|      | 1.1 Motivation of the Thesis1                                            | 1 |

|      | 1.2 Research Goals and Major Contributions                               | 3 |

|      | 1.3 Thesis Organization                                                  | 4 |

| Cha  | pter 2 Previous of Process, Voltage, and Temperature sensors             | б |

|      | 2.1 Conventional Process Sensor                                          | 6 |

|      | 2.2 Voltage Sensor Circuit Evolution                                     | 9 |

|      | 2.3 Temperature Sensor Circuit Evolution                                 | 5 |

|      | 2.3 Temperature Sensor Circuit Evolution                                 | 9 |

|      | 2.5 Summary                                                              | 5 |

| Cha  | pter 3 Fully On-Chip Process, Voltage, and Temperature Sensors           | б |

|      | 3.1 Time to Digital Converter (TDC) Architecture 3'                      | 7 |

|      | 3.2 Frequency to Digital Converter (FDC)                                 | 8 |

|      | 3.2 Frequency to Digital Converter (FDC)                                 | 9 |

|      | 3.4 Zero Temperature Coefficient Point Application – Process Sensor4     | 1 |

|      | 3.5 A Fully Digital Voltage Sensor Using A New Delay Element             | 5 |

|      | 3.6 Fully On Chip Ultra-Low Voltage Temperature Sensor4                  | 6 |

|      | 3.7 1-point Calibration Method of Proposed Temperature Sensor            | 0 |

|      | 3.8 Conclusion and Simulation Results                                    | 2 |

|      | 3.9 Summary                                                              | 4 |

| Cha  | pter 4 Self-Calibration Method for Subthreshold All-Digital PVT Sensors5 | 5 |

|      | 4.1 Previous TDC Calibration Method5                                     | 5 |

|      | 4.2 Proposed Self-Calibration Method for Subthreshold All-Digital PVT    |   |

|      | Sensors                                                                  | 0 |

|      | 4.3 Ultra-Low Voltage All-Digital Temperature Sensor with Adaptive Pulse |   |

|      | Width Compensation                                                       | 7 |

|      | 4.4 Summary                                                              | 4 |

| Cha  | pter 5 PVT Sensors for Micro-Watt DVFS System Design7                    | 5 |

|      | 5.1 PVT Sensors for Micro-Watt DVFS System Design                        | 6 |

|      | 5.2 Switched Capacitor DC-DC Converter                                   | 7 |

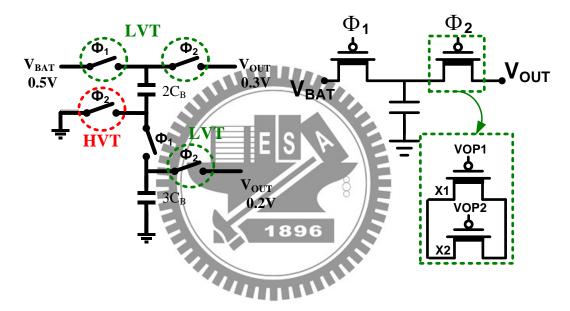

|      | 5.3 Multi-threshold CMOS SC DC-DC Converter                              | 7 |

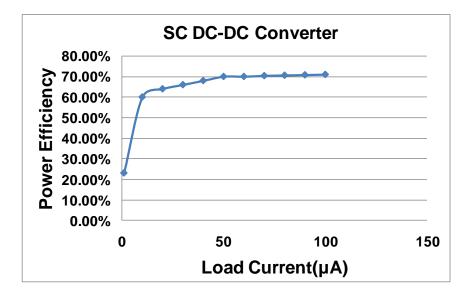

| 5.4 Post-Layout Simulation Results                          | 96  |

|-------------------------------------------------------------|-----|

| 5.5 Temp. Compensation for Low-voltage Digital Assisted PLL |     |

| 5.6 Summary                                                 |     |

| Chapter 6 Concludions and Future Work                       |     |

| 6.1 Conclusions                                             |     |

| 6.2 Future Work                                             |     |

| Bibliography                                                | 111 |

# **List of Figures**

| Figure 2.28. (a) Temperature monitoring circuit. (b) Process monitoring circuit                | 35    |

|------------------------------------------------------------------------------------------------|-------|

| Figure 3.1 A basic TDC architecture.                                                           | 37    |

| Figure 3.2 A vernier delay line TDC.                                                           | 38    |

| Figure 3.3 Frequency-to-digital converter (FDC) Architecture                                   | 39    |

| Figure 3.4 Fixed pulse generator block diagram and wave form                                   | 40    |

| Figure 3.5 simulation result of fixed pulse generator.                                         | 40    |

| Figure 3.6 MOS current equation in saturation mode                                             | 41    |

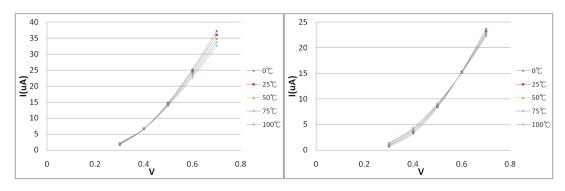

| Figure 3.7 UMC90 NMOS and PMOS I <sub>D</sub> - T plot at supply voltage 0.3~0.7V              | 42    |

| Figure 3.8 ZTC points of UMC90 NMOS and PMOS transistor are at about 0.4V                      | and   |

| 0.6V                                                                                           | 43    |

| Figure 3.9 At 0.5V, NMOS I <sub>D</sub> decreases with T, PMOS I <sub>D</sub> increases with T | 44    |

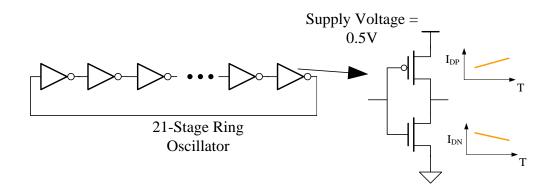

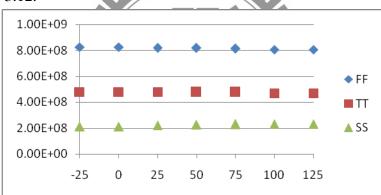

| Figure 3.10 Ring oscillator's frequency – temperature plot in corners FF, TT, SS               | 44    |

| Figure 3.11 Process Monitor circuit                                                            | 44    |

| Figure 3.12 Ring oscillator's frequency with process variation.                                | 45    |

| Figure 3.13 A fully digital voltage sensor.                                                    | 46    |

| Figure 3.14 Proposed fully on chip temperature sensor                                          | 49    |

| Figure 3.15 Bias current generator.                                                            | 49    |

| Figure 3.16 (a) Simulation result of temperature sensor with voltage variation.                |       |

| Simulation result of temperature sensor with process variation                                 | 50    |

| Figure 3.17 (a) Simulation result of temperature sensor with voltage variation                 | 52    |

| Figure 3.18 1-point Calibration Method of Temperature Sensor.                                  | 52    |

| Figure 4.1 (a) Typical setup for direct calibration of an arbitrator.                          | 56    |

| Figure 4.2 (a) Portion of a conventional VDL-based TDC. (b) Equivalent cir                     | rcuit |

| containing a single delay line with an added AND gate for calibration                          | 58    |

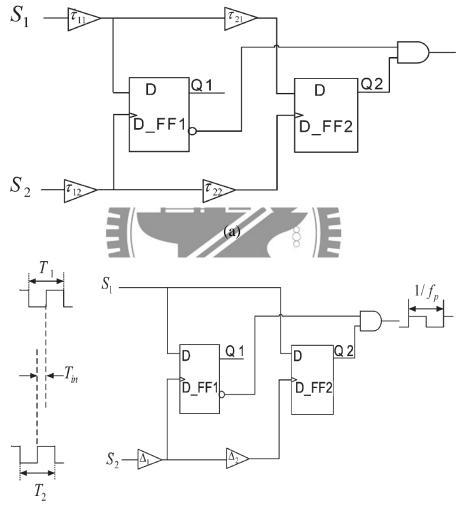

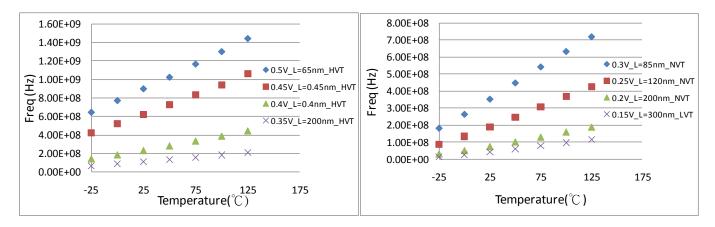

| Figure 4.3 Proposed all-digital temperature sensor                                             | 61    |

| Figure 4.4 Simulation result of proposed temperature sensor in different sup                   | pply  |

| voltage                                                                                        | 63    |

| Figure 4.5 Simulation result of temperature sensor in different process corner                 | 63    |

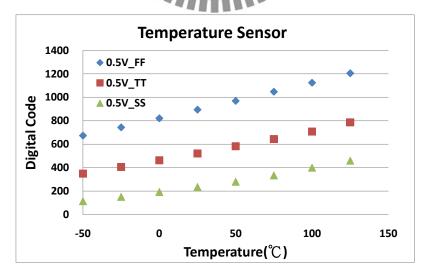

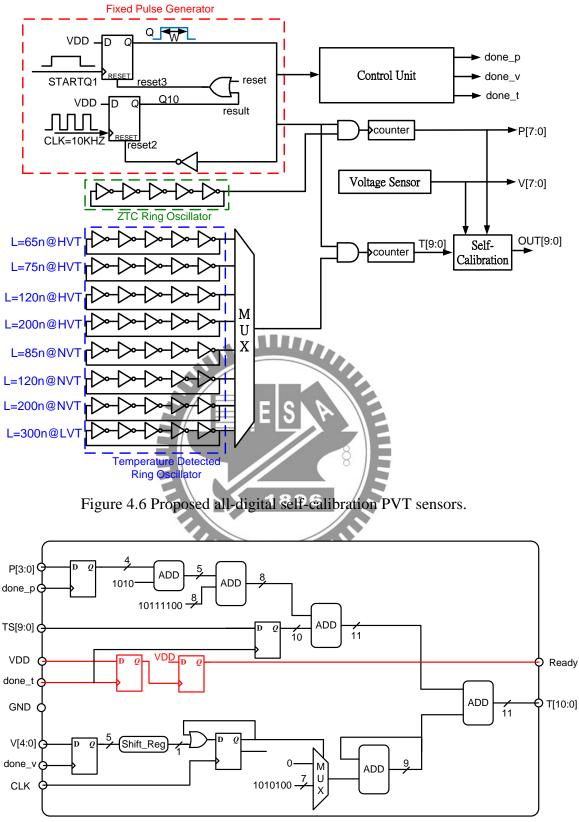

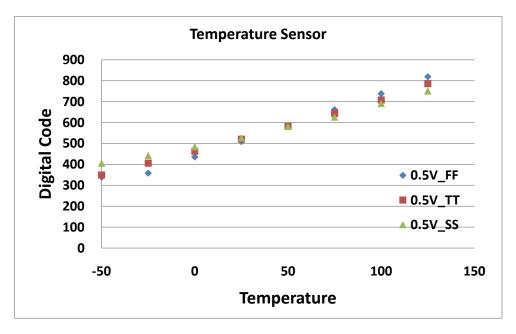

| Figure 4.6 Proposed all-digital self-calibration PVT sensors.                                  | 63    |

| Figure 4.7 Self- Calibration circuit of all-digital PVT Sensors.                               | 63    |

| Figure 4.8 Simulation results of calibration of temperature sensor in different pro            | cess  |

| corner                                                                                         | 65    |

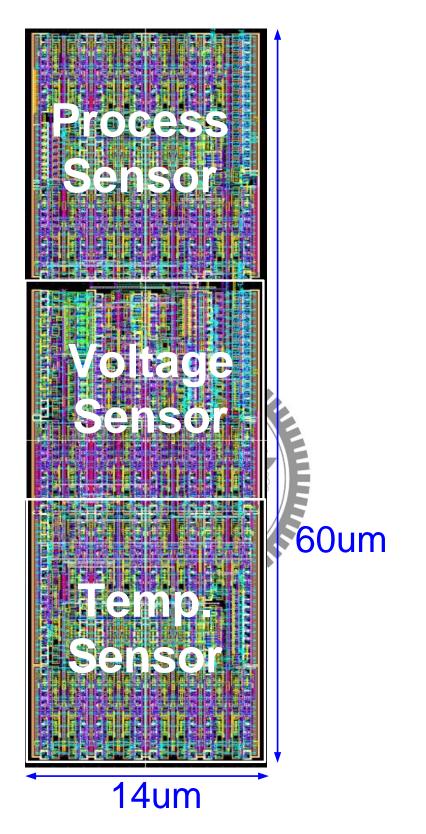

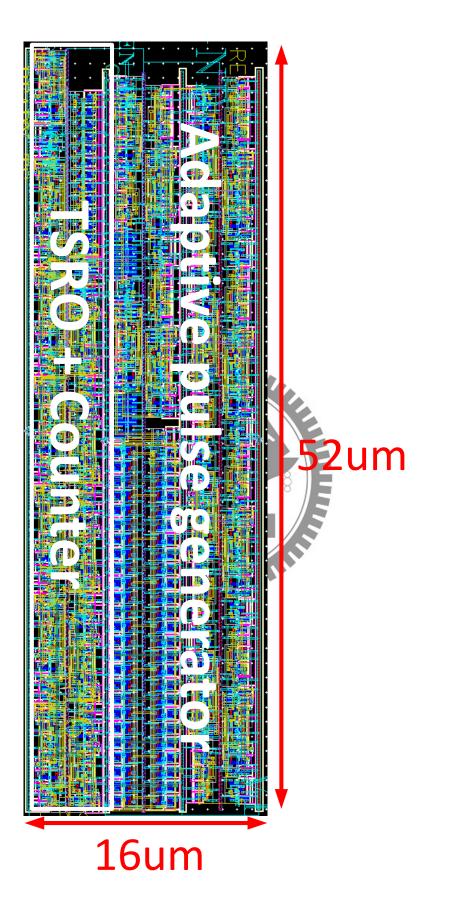

| Figure 4.9 Layout views of the all-digital PVT Sensors                                         | 63    |

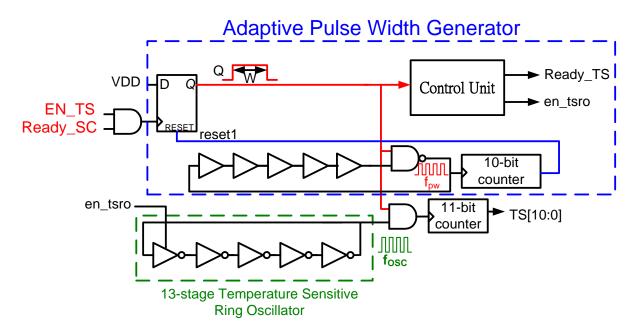

| Figure 4.10 Architecture of FDC-based CMOS all-digital temperature sensor                      | 63    |

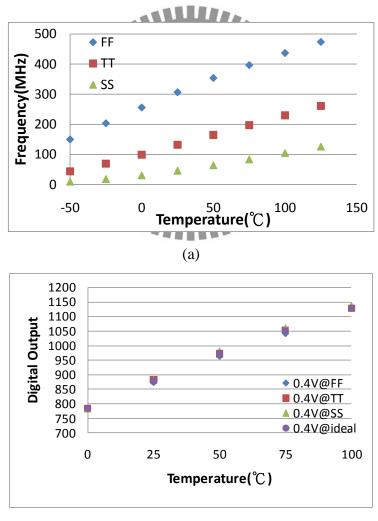

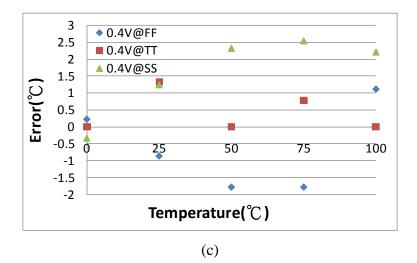

| Figure 4.11 (a) Simulated frequency of ring oscillator in different process corner             | . (b) |

| Digital output of sensor after self-calibration method. (c) Simulated output error f           | for 0 |

| °C ~100°C                                                                                      | 72    |

|                                                                                                |       |

Figure 4.12 Layout views of the all-digital temperature sensor with adaptive pulse

| width compensation                                                                         |

|--------------------------------------------------------------------------------------------|

| Figure 5.1 PVT sensors for micro-watt DVFS system                                          |

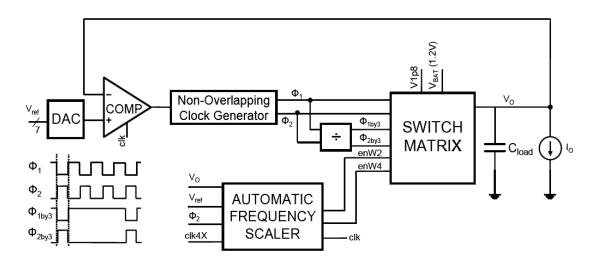

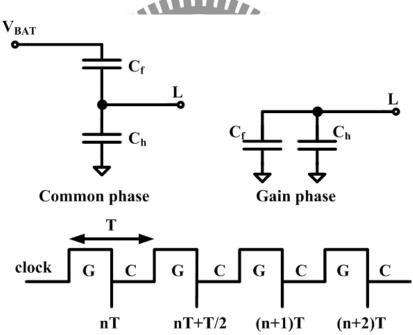

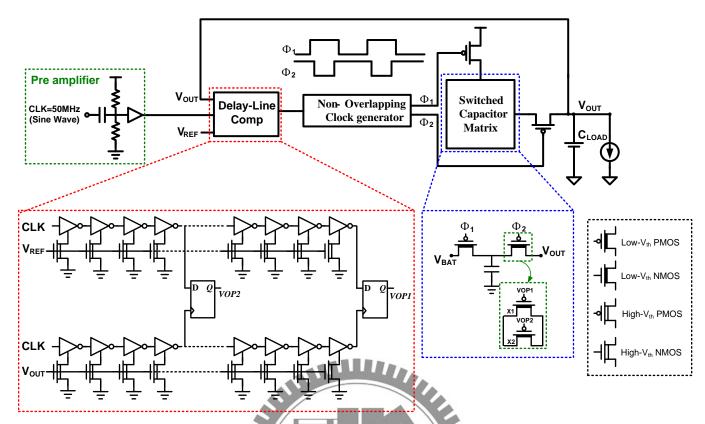

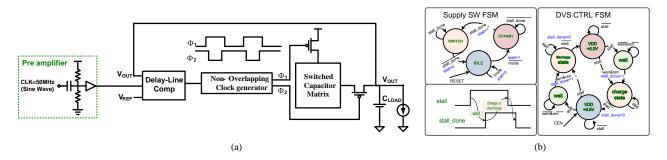

| Figure 5.2 Architecture of the switched capacitor DC-DC converter system78                 |

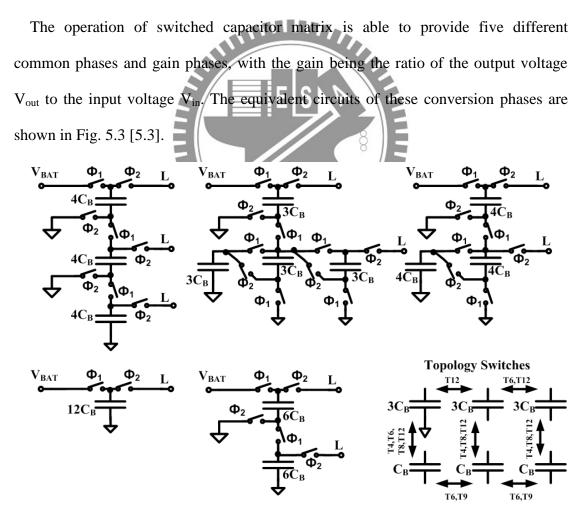

| Figure 5.3 Topologies used to generate a wide range of load voltages from a 1.2V           |

| supply                                                                                     |

| Figure 5.4 Equivalent circuit of the gain configuration with gain of 1/279                 |

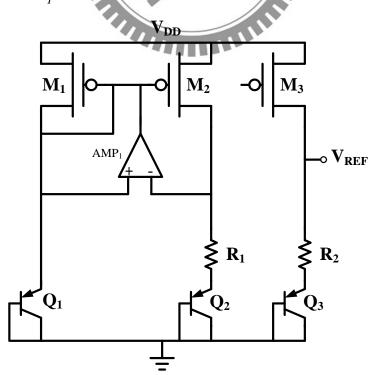

| Figure 5.5 Conventional CMOS bandgap voltage reference                                     |

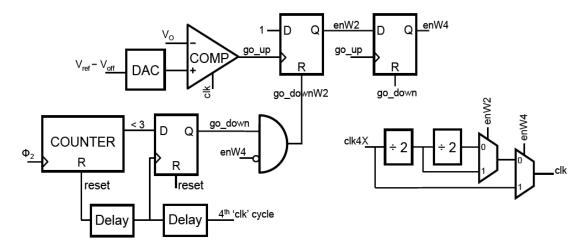

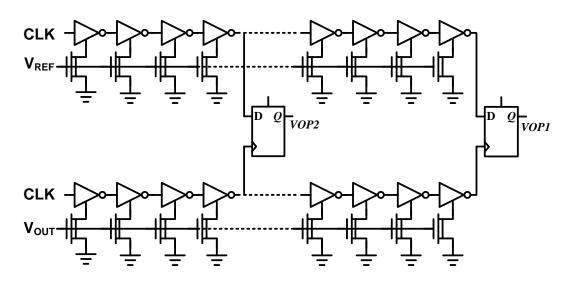

| Figure 5.6 Automatic frequency scaling circuit                                             |

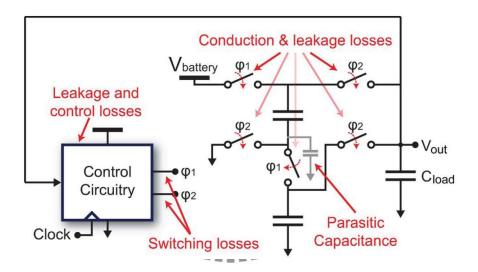

| Figure 5.7 Energy loss mechanisms in a switched capacitor DC–DC converter85                |

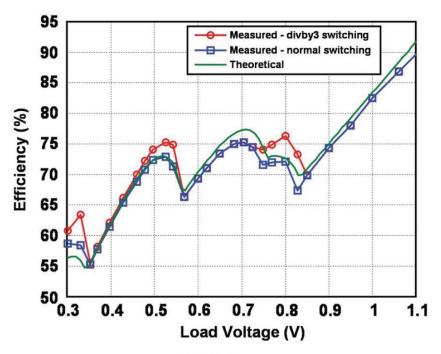

| Figure 5.8 Efficiency plot with change in load voltage                                     |

| Figure 5.9 Architecture of switched capacitor DC-DC converter                              |

| Figure 5.10. Switch matrix and simplified representation of the switch size control89      |

| Figure 5.11. DC-DC converter efficiency while delivering 300 mV90                          |

| Figure 5.12. Delay line comparator                                                         |

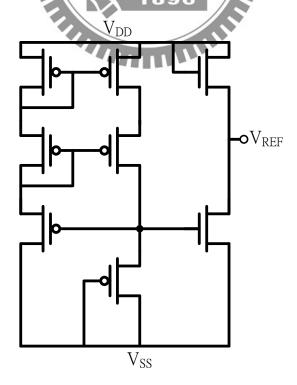

| Figure 5.13. Proposed Bandgap Voltage Reference (BVR)                                      |

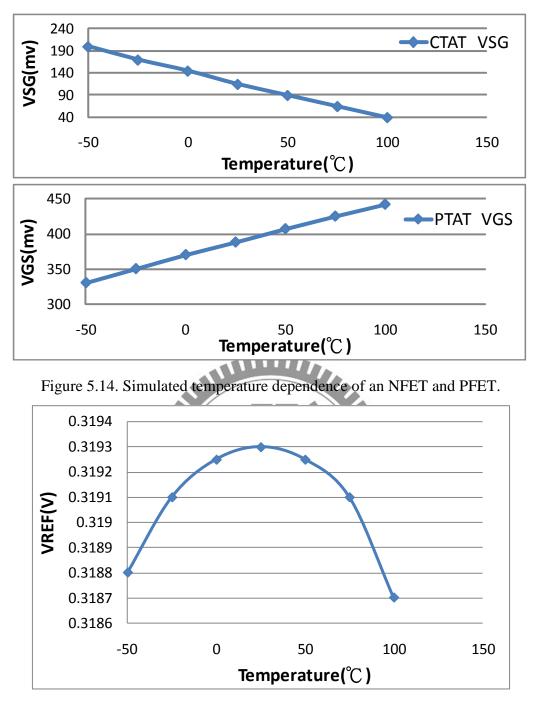

| Figure 5.14. Simulated temperature dependence of an NFET and PFET94                        |

| Figure 5.15. Simulated V <sub>REF</sub> versus temperature94                               |

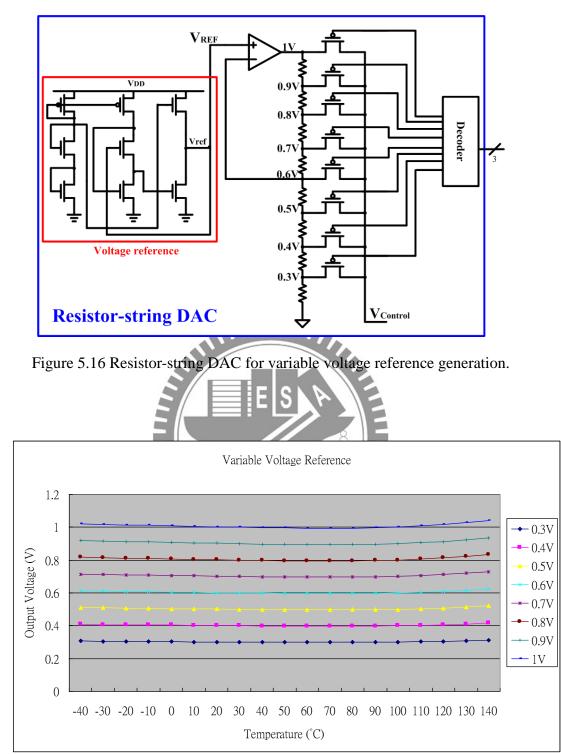

| Figure 5.16 Resistor-string DAC for variable voltage reference generation95                |

| Figure 5.17 Variable voltage reference generation with temperature variation95             |

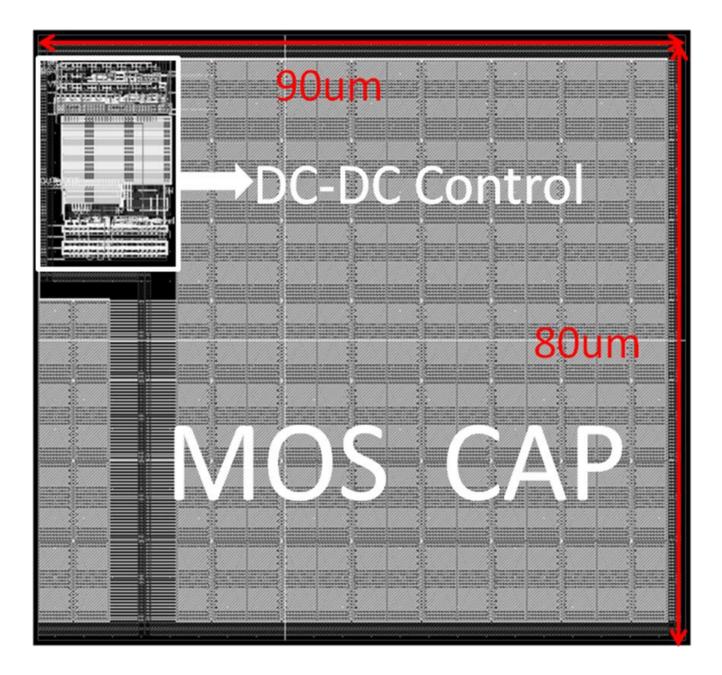

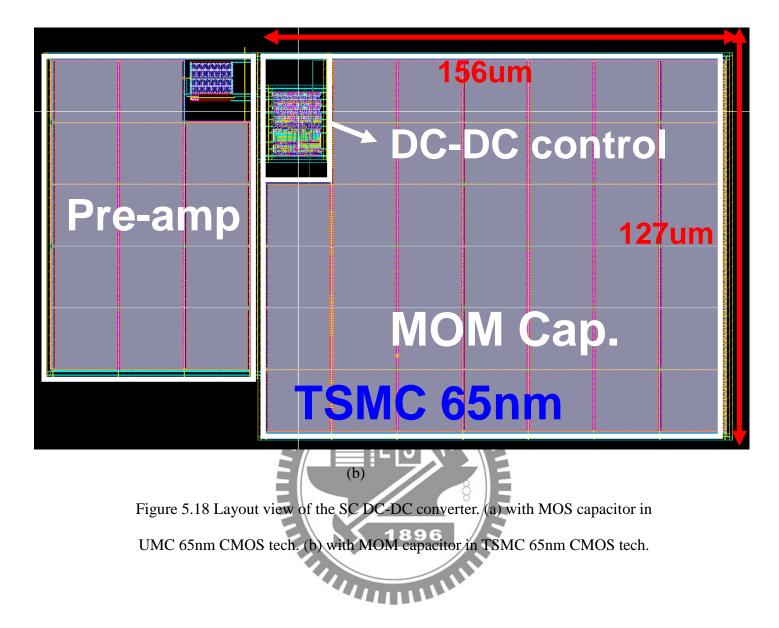

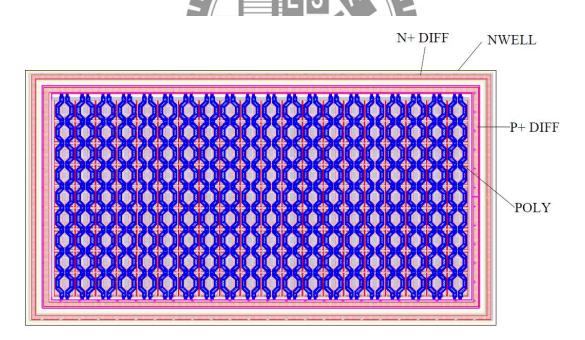

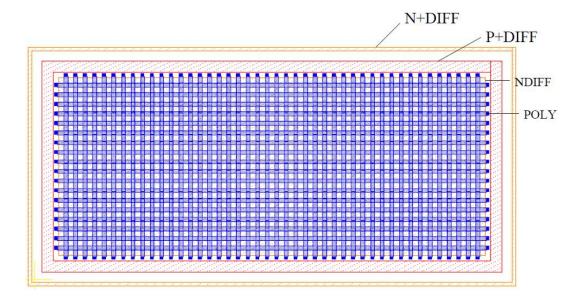

| Figure 5.18 Layout view of the SC DC-DC converter. (a) with MOS capacitor in               |

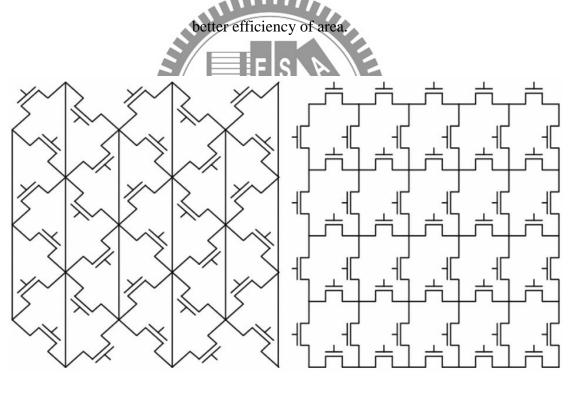

| UMC 65nm CMOS tech. (b) with MOM capacitor in TSMC 65nm CMOS tech98                        |

| Figure 5.19 The layout of the Power MOS <sup>(a)</sup> with better ESD protection (b) with |

| better efficiency of area100                                                               |

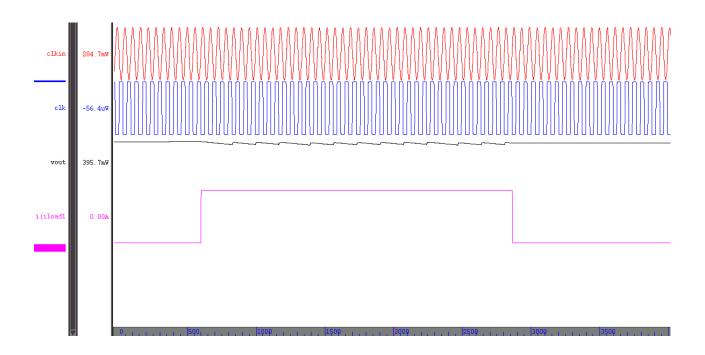

| Figure 5.20 The equivalent MOS of layout in Fig. 5.18(a) and(b)100                         |

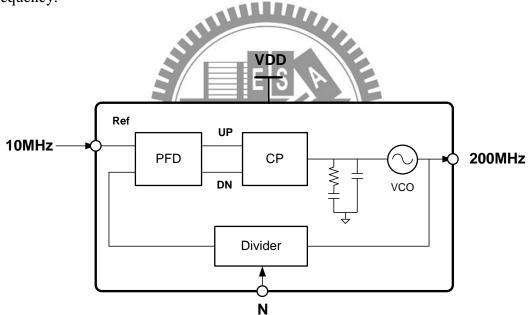

| Figure 5.21 The transient response of SC DC-DC converter100                                |

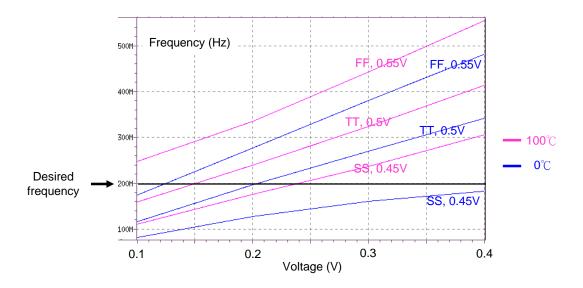

| Figure 5.22 Architecture of phase lock loop (PLL)100                                       |

| Figure 5.23 Simulation results of VCO output frequency in different environment            |

| condition                                                                                  |

| Figure 5.24 Architecture of proposed temp. compensation for low-voltage digital            |

| assisted PLL                                                                               |

| Figure 5.25 Simulation results of VCO output frequency in different environment            |

| condition with temperature compensation100                                                 |

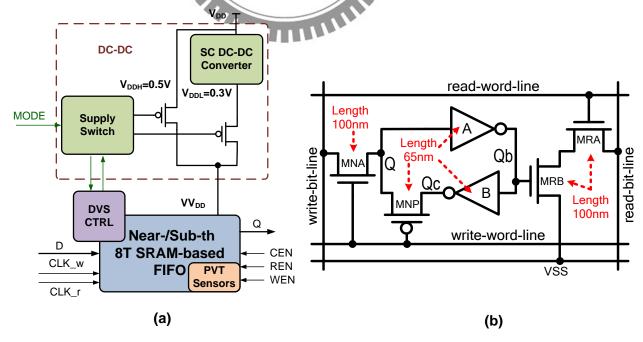

| Figure 6.1 (a) Block diagram of Near/Sub- threshold FIFO memory. (b) Proposed 8T           |

| Near/Sub-threshold SRAM cell                                                               |

| Figure 6.2 (a) ULV MTCMOS SC DC-DC converter. (b) Smart dynamic voltage                    |

| scaling converter                                                                          |

| Figure 6.3 (a) Self-calibration temperature sensor with adaptive pulse width generator.    |

| (b) DTM algorithm 100                                                                      |

# **List of Tables**

| Table 2.1 The output of voltage-to-time conversion ADC             | 14  |

|--------------------------------------------------------------------|-----|

| $(T_{D1} > T_{D2} > T_{D3} > T_{D4} > T_{D5}) \dots$               | 14  |

| Table 3.1 Voltage Sensor Digital Code Table                        | 46  |

| Table 3.2   Temperature sensor comparisons                         | 54  |

| Table 4.1 Temperature sensor comparisons                           | 74  |

| Table 5.1 Temperature variation                                    | 96  |

| Table 5.2 Comparison of [36], [39] and proposed voltage regulator. | 102 |

### **Chapter 1 Introduction**

#### **1.1 Motivation of the Thesis**

Wireless microsensor network (WSN) technology creates enormous possibility to have a positive impact on our near future life [1.1]-[1.2]. Advances in ultra-low voltage (ULV) circuit design have recently demonstrated capabilities compatible with wireless body area sensor networks (WBASNs) needs. An important application of WBAN is the vital sensor network shown in Fig1.1. Sensor nodes that measure biomedical signals such as electrocardiogram, blood pressure, and etc, are small pieces either attached on or implanted into a human body. They use a battery with as thin and light characteristics as possible. Most of them do not have the ability to last for a long time. As a result, the demand for low power has been critical in a WBAN. For the health-care purpose, it makes sense when the observation period could last for days to weeks. Therefore, the ultra-low power wireless sensor node (WSN) is the most crucial design target to achieve.

Figure 1.1. Sensor network of WBAN.

The power reduction is an important design issue for the WBAN. For ultra-low power circuit design, transistors will operate in near/sub-threshold region [1.3]. Lowering the supply voltage and frequency is one of the attractive approaches to reduce power consumption.

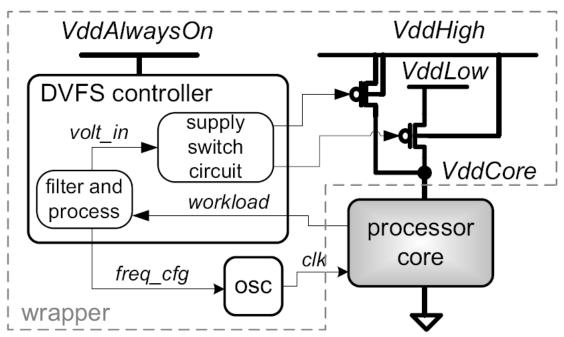

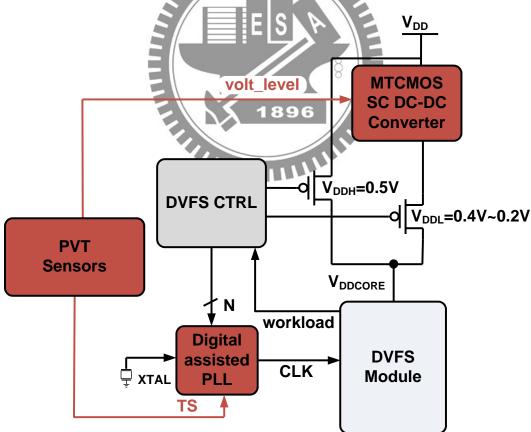

Furthermore, dynamic voltage and frequency scaling (DVFS) shown in Fig.1.2, achieves extremely efficient energy saving by adjusting system supply voltage and frequency depending on workload monitor [1.4]. Because if this reason, there are many previous researches about DVFS power management for digital systems such as RISC, DSP and Video Code.

Figure 1.2 Dynamic voltage and frequency scaling systems.

As we continue to reduce the voltage until the transistor get into the near/sub-threshold voltage, circuits will become more sensitive to PVT variations than super threshold. Thus, minimizing energy dissipation and improving variation immunity are far more important rather than operating frequency. Thus, a process, voltage, and temperature (PVT) aware subthreshold clocking design is essential to solve the one last puzzle in ULV circuits.

Since wearable sensors are intended to be worn on the body, miniaturization and minimal weight are important [1.5], [1.6]. Energy harvesting and 3D integration have the potential to solve above mentioned challenges. Energy harvesting [1.7] can exploit the external environment as a source of energy for sensor nodes operating over a full lifetime; while 3D integration [1.8], [1.9] can stack more die connected with a very high packing density of one chip. Through-silicon via (TSV) technology, however, led to higher power density that is much worse hot spot issues. Thus, a PVT-aware micro-watt DVFS system for energy harvesting is also essential.

### **1.2 Research Goals and Major Contributions**

The goal of this research is to design and implement PVT sensors for micro-watt DVFS system shown in Fig.1.3. It includes the design of self-calibration all-digital PVT sensors, MTCMOS switched capacitor (SC) DC-DC converter, temperature compensation for low-voltage digital assist PLL, and dynamic voltage and frequency scaling system.

The major contributions of this thesis are list as follow:

- 1. A near-/sub-threshold all-digital process, voltage, and temperature sensor is proposed and integrated to the micro-watt DVFS system. The sensor is proposed for high accuracy, ultra-low voltage, low power, and self-calibration portable applications.

- 2. A self-calibration near-/sub-threshold all-digital temperature sensor with adaptive pulse width generator is proposed. The sensor is proposed for high accuracy, ultra-low voltage, low power, and self-calibration portable applications.

- A novel connect scheme for improving power efficiency and reducing voltage variation of switched capacitor(SC) DC-DC converter which generates ultra low voltage is proposed.

- 4. To proposed a temperature compensation for low voltage digital assist PLL can modulate output frequency via divider. Use the temperature sensor to compensate the frequency can not lock in the worth case.

Figure 1.3 Proposed PVT sensors for micro-watt DVFS system.

### **1.3 Thesis Organization**

The organization of the thesis is as bellow: Previous of conventional process, voltage, and temperature sensors are introduced in the Chapter 2. The detail circuits of conventional process, voltage, and temperature sensors are introduced. The

shortcomings of conventional PVT sensors are introduced. The applications of PVT sensors are also introduced.

The organization of the thesis is as below. The Chapter 1 is an introduction and motivations for research. Then, in chapter 2, introduces an overview of conventional process, voltage, and temperature sensors. The detail circuits of conventional process, voltage, and temperature sensors are introduced in this chapter and which also includes the shortages of conventional PVT sensors and the applications of PVT sensors.

In chapter 3, we have as following ideas. First, proposed fully on chip and fully digital PVT sensors. Second, we presented novel FDC technique for PVT sensors, and it can reduce power and area. Also at the same time, it improves temperature linearity in near/sub-threshold region. The self-calibration all-digital PVT sensors and the self-calibration temperature sensor with adaptive pulse width compensation are proposed in Chapter 4. We use all-digital circuit to replace the traditional PVT sensors which can reduce power consumption and area. And to propose self-calibration technology does not require additional circuitry to achieve high accuracy.

PVT sensors for micro-watt DVFS system is introduced in the final chapter. We combine with previous proposed PVT sensors and DVFS system to control the output voltage of SC DC-DC converter for achieving the reduction of power consumption in different PVT variation. And use PVT sensors to compensate the output frequency of low voltage PLL can not lock in the worth case.

# Chapter 2 Previous of Process, Voltage, and Temperature sensors

This chapter introduces the overview of PVT sensors in power management system. The conventional process sensor design would be demonstrated in Section 2.1. The conventional voltage sensor circuit evolution would be introduced in Section 2.2. Section 2.3 introduces the temperature sensor circuit evolution. Section 2.4 introduces the power management system for PVT sensors applications. Finally, Section 2.5 is the summary.

### 2.1 Conventional Process Sensor

Technology scaling beyond 90 nm is causing higher level of process variations, which changes the design paradigm from deterministic to probabilistic.

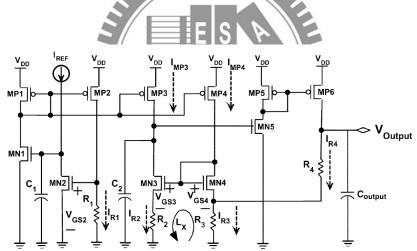

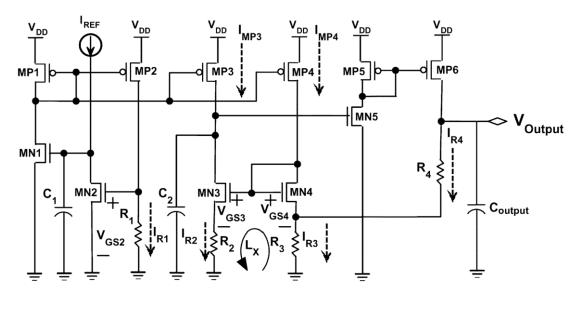

Fig. 2.1 shows a process monitor circuit [2.1]. The circuit consists of a current reference circuit,  $I_{R1}$  generator, and circuits to generate temperature insensitive  $V_{Output}$ . The current  $I_{R1}$  in Fig. 2.1 is given by

$$I_{R1} = \frac{V_{GS1}}{R_1}$$

(2.1)

The current  $I_{MP4}$  is determined by the  $I_{R1}$  and the ratio of the transistor MP2 and MP4. Therefore,  $V_{Output}$  is given by

$$V_{Output} = R_4 I_{R4} + V_{R3} = R_4 \left(\frac{V_{R3}}{R_3} - I_{R2} \frac{\beta_{MP4}}{\beta_{MP2}}\right) + V_{R3}$$

(2.2)

Where  $\beta$  is the transistor aspect ratio.

From the loop "Lx" in Fig. 2.1

$$V_{R2} + V_{GS3} = V_{R3} + V_{GS4}$$

(2.3)

$$\frac{\beta_{MP3}}{\beta_{MP2}}R_2 + V_{GS3} = V_{R3} + V_{GS4}$$

(2.4)

If transistor MN3 and MN4 are in subthreshold region,  $V_{R3}$  is obtained by solving the (2.4) using the current mirror relationships among  $I_{R1}$ ,  $I_{MP3}$ , and  $I_{MP4}$ , and it is given by

$$V_{R3} = \frac{\beta_{MP3}}{\beta_{MP2}} \frac{R_2}{R_1} V_{GS1} + V_T \ln(\frac{\beta_{MN4}}{\beta_{MN3}} \frac{\beta_{MP3}}{\beta_{MP4}})$$

(2.5)

By substituting (2.1) and (2.5) in (2.2), V<sub>Output</sub> is obtained as follows:

$$V_{Output} = C_1 V_{GS1} + C_2 V_T$$

(2.6)

where

$$C_{1} = \left(\frac{R_{4}}{R_{3}} + 1\right) \frac{R_{2}}{R_{1}} \frac{\beta_{MP3}}{\beta_{MP2}} \frac{R_{2}}{R_{1}} \frac{\beta_{MP4}}{\beta_{MP2}}$$

(2.7)

$$C_{2} = \left(\frac{R_{4}}{R_{3}} + 1\right) \ln\left(\frac{\beta_{MN4}}{\beta_{MN3}} \frac{\beta_{MP3}}{\beta_{MP2}}\right)$$

(2.8)

In [2.2], V<sub>GS1</sub> is given by

$$V_{GS1} \approx V_{GS1}(T_{0}) + K_{G}\left(\frac{T}{T_{0}} - 1\right)$$

(2.9)

where

$$K_G = K_T + V_{GS}(T_0) - V_{th}(T_0)$$

(2.10)

where  $V_T$  is the thermal voltage,  $K_T$  is the temperature coefficient for threshold voltage (typical value is 0.3 V), and  $T_0$  is the room temperature.

Substituting (2.10) in (2.6) to find temperature independent  $V_{Output}$ , taking partial derivative with respect to temperature, and setting it zero

$$\frac{\partial V_{Output}}{\partial T} = 0 \tag{2.11}$$

Solving (2.11), the condition nullifying the temperature coefficient  $V_{Output}$  of is given by

$$\frac{C_1}{C_2} = -\frac{V_T(T_0)}{K_G}$$

(2.12)

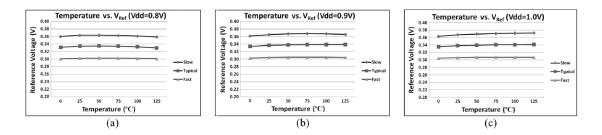

However, from (2.12), the temperature coefficient is affected by the large [threshold-voltage variation in different process corner and it leads significant variation of reference voltage. Therefore, the circuit is not suitable for a voltage-reference circuit but is suitable for a process-variation monitoring circuit. Fig. 2.2 demonstrates linear variation of the reference voltage according to process corner conditions. The reference voltage is not affected by temperature and supply voltage variations as shown in Fig. 2.2.

Figure 2.1. Process monitoring circuit.

Figure 2.2. Process dependence of reference voltage (output) in different temperatures and supply voltages: (a)  $V_{DD} = 0.8 \text{ V}$ ; (b)  $V_{DD} = 0.9 \text{ V}$ ; (c)  $V_{DD} = 1.0 \text{ V}$ .

#### 2.2 Voltage Sensor Circuit Evolution

Advanced systems (automobiles, medical and other electronic devices) have come to use multiple sensors in recent years, and the number is expected to increase even more in the future. The basic structure of the sensors includes a sensing element and electronic circuits. User requirements for sensors have become more and more demanding, including the need for high performance and lower cost.

Therefore, there are four major problems in predicting the analog type sensors of the near future. The first issue, from an economic perspective, is the difficulty of shrinkage due to loss of accuracy. The second problem involves greater sophistication of, for example, self-correction and self-diagnostics. The third issue is environmental durability. The fourth problem relates to improving reliability.

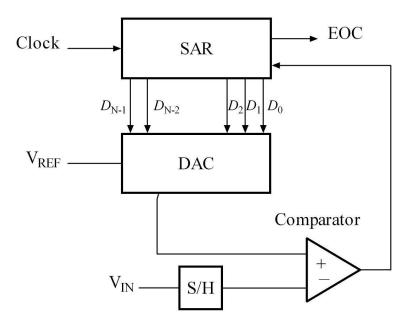

Research on digitalization of sensor circuits has become energized as efforts are made to resolve these problems. To realize digital sensing, the weak signal from the element must be analog-to-digital (A/D) converted at an early stage within the sensor chip, so an A/D converter (ADC) is required. A successive approximation ADC is a type of analog-to-digital converter that converts a continuous analog waveform into a discrete digital representation via a binary search through all possible quantization levels before finally converging upon a digital output for each conversion.

#### 2.2.1 Successive Approximation Analog-to-Digital Converter

The successive-approximation (SA) ADC is one of the most popular architectures for data-acquisition applications, especially when high-resolution, low power and medium speed are required. In some applications such as wireless sensor nodes, designing low power and low energy ADC is one of the major challenges. For SAADC, the dominant power dissipation sources are the comparator and the switching in the DAC capacitor array. Traditional successive-approximation ADC architecture is shown in Fig2.3.

The successive approximation ADC circuit typically consists of four chief subcircuits:

- 1. A sample and hold circuit (S/H) to acquire the input voltage  $(V_{in})$ .

- An analog voltage comparator that compares V<sub>in</sub> to the output of the internal DAC and outputs the result of the comparison to the successive approximation register (SAR).

- A successive approximation register subcircuit designed to supply an approximate digital code of V<sub>in</sub> to the internal DAC.

- 4. An internal reference DAC that supplies the comparator with an analog voltage equivalent of the digital code output of the SAR for comparison with  $V_{in}$ .

The successive approximation register is initialized so that the most significant bit (MSB) is equal to a digital 1. This code is fed into the DAC which then supplies the analog equivalent of this digital code ( $V_{ref}/2$ ) into the comparator circuit for comparison with the sampled input voltage. If this analog voltage exceeds  $V_{in}$  the comparator causes the SAR to reset this bit; otherwise, the bit is left a 1. Then the next bit is set to 1 and do the same test, continuing this binary search until every bit in the SAR has been tested. The resulting code is the digital approximation of the sampled input voltage and is finally output by the DAC at the end of the conversion (EOC).

Figure 2.3 Successive Approximation ADC Block Diagram

### 2.2.2 All-Digital Analog-to-Digital Converter

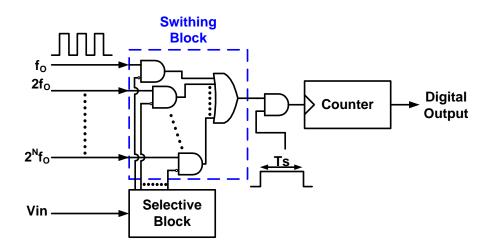

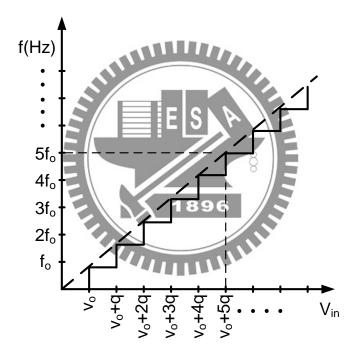

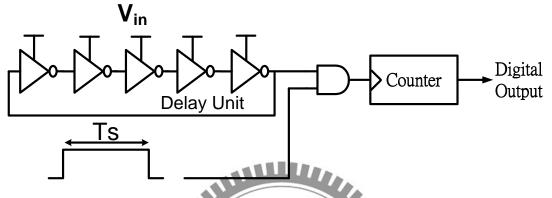

The general schematic of all-digital ADC is shown in Fig 2.4. The multi oscillators  $(f_0, 2f_0, ...., 2^N f_0)$  are employed to be corresponding to the quantization levels (q, 2q,  $2^N q$ ) in the conventional ADC, Fig2.5. According to the input voltage, one of these oscillators is selected and pass through constant time pulse ( $T_S=l/f_0$ ) to the counter. The switching block is a combinational logic circuit as shown in Fig 2.4, which is used to pass the equivalent frequency required. The input voltage controls the selective block.

Figure 2.4 The general all-digital ADC.

Figure 2.5 Quantization levels of ADC.

In the last approach, the number of gates will be dramatically high. Therefore, to minimize the hardware complexity, a new circuit was presented [2.3] as shown in Fig2.6. In the circuit, the input voltage is converted to frequency (voltage controlled oscillator) using only one oscillator. This clock signal is passing through constant duration pulse (Ts) to count, as shown in Fig2.6. In this circuit, if the supply voltage (control terminal) is changed from  $V_0$  to  $V_0$ +q, where q is the quantization voltage,

the output frequency of the VCO will be less or equal  $f_0$ . (fo=l/Ts, where T, is time of conversion). Therefore, the counter will count 0's, (no positive/negative edge will be counted). At the second quantization level (2q), the frequency output must be 2fo. Only two pulses will be memorized in the counter during the Ts pulse. The relation between the input voltage and its equivalent frequency is shown in Fig 2.5.

Figure 2.6 All-digital voltage to frequency converter ADC.

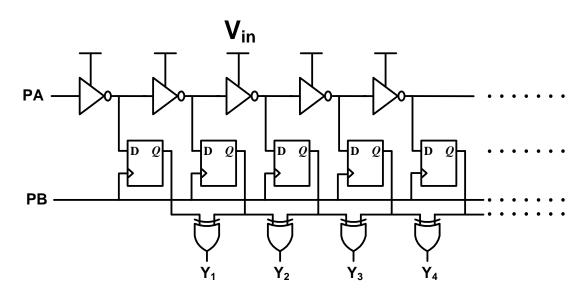

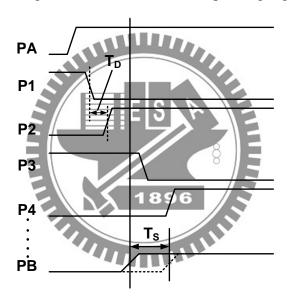

The digital voltage-to-time conversion technique, can be employed as controlled circuit. The basic block and timing diagram of this controlled circuit are shown in Fig2.7. The inverter steps within the gate delay pulse group are P1, P2, P3,..., which are steady states (1,0,1,...). Measurement process starts with the rise of pulse PA, then the P1, P2, P3, ... are going to invert. Due to the propagation delay time, there is an overlap between two 1's or 0's as shown in Fig 2.8. When pulse PB starts to rise, the number of inverters in which its outputs have changed due to PA is equal the measurement time. Table 2.1 illustrates the XOR gate outputs for 4-stage delay line, the 0's output logic means that position of the overlap between two 1's logic. This 0's logic will be cached at  $Y_1$  at level  $V_1$  of the input, at  $Y_2$  at level  $V_2$ , and so on, where  $(V_1 < V_2 < V_3 < V_4 < V_5)$ .

Figure 2.7 Voltage to time conversion concept using digital circuit.

Figure 2.8 Voltage to time conversion wave signals.

| $\label{eq:table} \begin{array}{c} Table \ 2.1 \ The \ output \ of \ voltage-to-time \ conversion \ ADC \\ (T_{D1} \! > \! T_{D2} \! > \! T_{D3} \! > \! T_{D4} \! > \! T_{D5}) \end{array}$ |                 |                |                |                |                |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------|----------------|----------------|----------------|--|--|--|--|

| • •                                                                                                                                                                                          | Delay           |                | 0              | utput          |                |  |  |  |  |

| $\mathbf{V}_{\mathbf{in}}$                                                                                                                                                                   | Time            | Y <sub>1</sub> | Y <sub>2</sub> | Y <sub>3</sub> | Y <sub>4</sub> |  |  |  |  |

| <b>V</b> <sub>1</sub>                                                                                                                                                                        | T <sub>D1</sub> | 0              | 1              | 1              | 1              |  |  |  |  |

| $V_2$                                                                                                                                                                                        | T <sub>D2</sub> | 1              | 0              | 1              | 1              |  |  |  |  |

| V <sub>3</sub>                                                                                                                                                                               | T <sub>D3</sub> | 1              | 1              | 0              | 1              |  |  |  |  |

| $V_4$                                                                                                                                                                                        | T <sub>D4</sub> | 1              | 1              | 1              | 0              |  |  |  |  |

| $V_5$                                                                                                                                                                                        | T <sub>D5</sub> | 1              | 1              | 1              | 1              |  |  |  |  |

#### **2.3 Temperature Sensor Circuit Evolution**

In recent years, numerous portable electronic products have been launched to the market with considerable market growth. With process scaling down continuously, this high level of integration also introduces the problem of self-heating, which is the result of increased power density. Low cost, low power, high-performance temperature sensors are therefore becoming increasingly important for applications from power consumption control to thermal monitoring, so as to enhance performance and reliability. The important applications of smart temperature sensors include:

1) The power consumption control in VLSI chips, such as CPU and chip sets.

2) The thermal compensation in single-chip systems and micro systems with built-in sensors.

- 3) The environment temperature monitors in automatic fabrication factories.

- 4) The temperature control of consumer electronics, such as automobiles and home electronics. Kim et al. [2.4] use temperature Sensor for Mobile DRAM Self-refresh Control.

#### 2.3.1 Analog Temperature Sensor

Several different implementations of on-chip temperature sensors have been reported in the last ten years. With the use of bipolar transistors for temperature sensing, and advanced techniques including chopping circuit, dynamic element matching and sigma-delta ADC for noise suppression and cancellation, Pertijs et al. [2.5] developed an on-chip temperature sensor with a  $3\sigma$  inaccuracy of  $\pm 1^{\circ}C$  at the expense of increased circuit complexity.

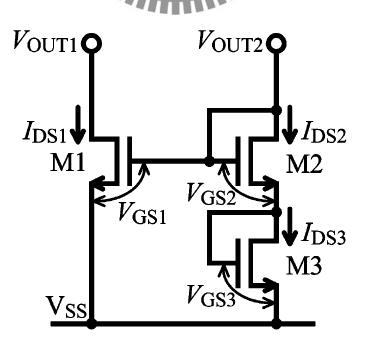

With the use of three CMOS transistors for temperature sensor was presented in [2.6]. The three-transistor temperature sensor shows in Fig. 2.9, which utilizes the

temperature characteristic of the threshold voltage, shows highly linear characteristics at a power supply voltage of 1.8 V. The conditions of this temperature sensor are defined as follows.

- 1) All transistors operate in the saturation region.

- 2) The output voltages of each node are equal.

- 3) The sinking currents at each node are equal.

The temperature is obtained by measuring  $V_{OUT}$ , where the two currents,  $I_{OUT1}$  and  $I_{OUT2}$ , have the same value. When the substrate bias effect of the transistor M2 is neglected to simplify the calculation, their  $I_{DS}$ - $V_{GS}$  characteristics and the operating conditions are

$$I_{DS1} = \frac{\beta_1}{2} (V_{GS1} - V_{T_1})^2$$

$$\beta_1 = \mu_{eff1} C_{OX} \frac{W_1}{L_1}$$

$$I_{DS2} = \frac{\beta_2}{2} (V_{GS2} - V_{T_2})^2$$

$$(2.13)$$

$$(2.14)$$

$$(2.14)$$

$$(2.15)$$

$$\beta_2 = \mu_{eff\,2} C_{OX} \, \frac{W_2}{L_2} \tag{2.16}$$

$$I_{DS3} = \frac{\beta_3}{2} (V_{GS3} - V_{T3})^2$$

(2.17)

$$\beta_3 = \mu_{ef\,3} C_{OX} \, \frac{W_3}{L_3} \tag{2.18}$$

$$I_{DS1} = I_{DS2} = I_{DS3}$$

(2.19)

$$V_{OUT1} = V_{GS1}$$

,  $V_{OUT2} = V_{GS2} + V_{GS3}$  (2.20)

$$V_{OUT1} = V_{OUT2} \tag{2.21}$$

After solving (2.16) - (2.18) for each transistor's respective  $V_{GS}$ , the results are applied to  $V_{GS2}$  and  $V_{GS3}$  in (2.20). Then,  $I_{DS2}$  and  $I_{DS3}$  are also substituted for (2.13)&(2.14) using (2.19). Finally, (2.21) is solved against  $V_{GS1}$  and we get

$$V_{OUT1} = V_{GS1} = \frac{V_{T2} + V_{T3} - (\sqrt{\beta_1 / \beta_2} + \sqrt{\beta_1 / \beta_3})V_{T1}}{1 - (\sqrt{\beta_1 / \beta_2} + \sqrt{\beta_1 / \beta_3})} \propto T$$

(2.22)

$$\frac{dV_{OUT1}}{dT} = a(\frac{dV_{T2}}{dT} + \frac{dV_{T3}}{dT}) - b\frac{dV_{T1}}{dT}$$

(2.23)

Where

$$a = \frac{1}{1 - (\sqrt{\beta_1 / \beta_2} + \sqrt{\beta_1 / \beta_3})}$$

$$b = \frac{\sqrt{\beta_1 / \beta_2} + \sqrt{\beta_1 / \beta_3}}{1 - (\sqrt{\beta_1 / \beta_2} + \sqrt{\beta_1 / \beta_3})}$$

Since  $\sqrt{\beta_1 / \beta_2} + \sqrt{\beta_1 / \beta_3}$  can be assumed as constant, the variables and in (2.23)

also become constant. Therefore, the output voltage corresponds to the temperature **1896** coefficients of the transistor threshold voltages.

Figure 2.9 Conventional three-transistor temperature sensor.

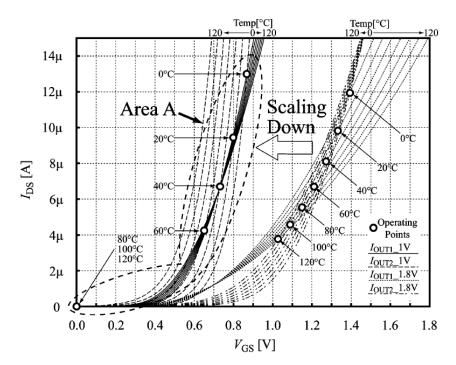

Fig. 2.10 shows the characteristics at 1.8V and 1V supply voltages, where the intersections of and correspond to the operating points of this sensor. This method shows highly linear characteristics at a power supply voltage of 1.8V or more, which enables us to define the operating conditions well above twice the threshold voltage. But the linearity diminishes after scaling down the supply voltage to 1V using a 90-nm CMOS process. Because the temperature coefficient of the operating point's current at a 1V supply voltage is steeper than the coefficient at a 1.8V supply voltage, the operating point's current at high temperature becomes quite small and the output voltage goes into the subthreshold region or the cutoff region.

Figure 2.10 Operating-point comparison of three-transistor temperature sensor on  $I_{DS}$ -V<sub>GS</sub> curves at 1.8- and 1.0-V supply voltage.

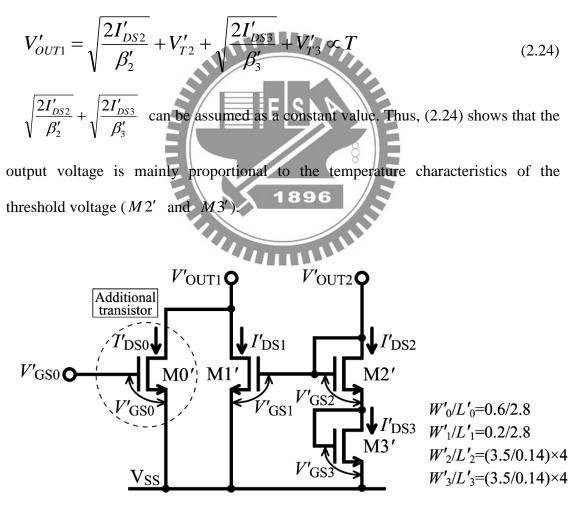

To improve linearity at a 1V supply voltage, an accurate four-transistor temperature sensor was designed in [2.7] shows in Fig. 2.11, and developed for thermal testing and monitoring circuits in deep submicron technologies. Note that to operate the additional transistor in the saturation region, an extra bias voltage  $V'_{GS0}$  is required.

Of course, the bias voltage generation circuit must not possess temperature dependency, and, in some cases, this circuit becomes larger than the temperature sensor itself.

In addition, the W/L ratio of the transistors M0' and M1' should be as small as possible so that the current  $I'_{OUT1}$  remains small. However, the smaller W/L ratio requires a longer channel, so it occupies larger chip area. Consequently, there is a tradeoff between the current consumption and the chip area.

The  $I'_{DS} - V'_{GS}$  characteristics and the operating conditions of both the proposed four-transistor sensor is the following:

Figure 2.11 Four-transistor, voltage output, temperature sensor.

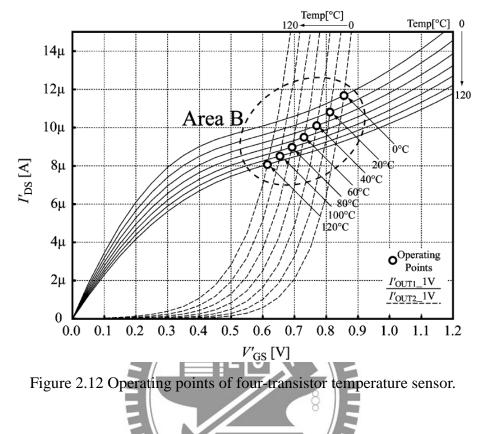

The output current of four- transistor temperature sensor is more high linearity with high temperature than conventional three-transistor circuit shows in Fig 2.12.

### 2.3.2 Time-to-Digital Based Temperature Sensors

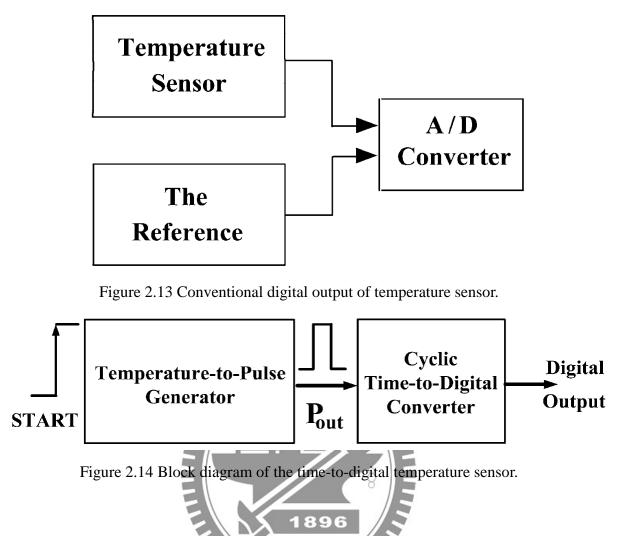

In the late 20th century, analog-to-digital converters (ADCs) were gradually integrated into analog thermal sensors by IC designers to compose the so-called intelligent or smart temperature sensors. The typical block diagram of the conventional smart temperature sensor is depicted in Fig. 2.13 [2.8]. The sensor consumes more power, and large area, so another version of all-digital temperature sensor which is based on time-to-digital converters instead of ADCs was presented in [2.9]-[2.15].

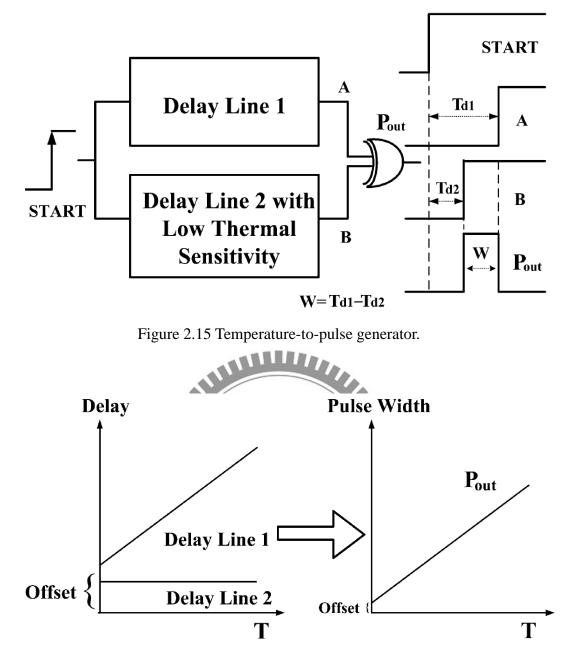

The temperature sensor composed of temperature-to-pulse generator and cyclic time-to-digital converter, shows in Fig 2.14. Temperature-to-pulse generator, it can generate a pulse width is linear to temperature variation. A simple circuit utilizing gate delays to generate the thermally sensitive pulse is shown in Fig. 2.15. The START signal is delayed a certain amount of time by the delay line composed of even number of inverter. The high-to-low and low-to-high propagation delay time for an inverter can be expressed as [2.16]

$$t_{PHL} = \frac{2C_L V_{TN}}{K_N (V_{DD} - V_{TN})^2} + \frac{C_L}{K_N (V_{DD} - V_{TN})} \cdot \ln(\frac{1.5V_{DD} - 2V_{TN}}{0.5V_{DD}}) \quad (2.25)$$

$$t_{PHL} = \frac{-2C_L V_{TP}}{K_P (V_{DD} + V_{TP})^2} + \frac{C_L}{K_P (V_{DD} + V_{TP})} \cdot \ln(\frac{1.5V_{DD} + 2V_{TP}}{0.5V_{DD}}) \quad (2.26)$$

Where  $k_N = \mu_N C_{OX} (W/L)_N$ ,  $k_P = \mu_P C_{OX} (W/L)_P$  and  $C_L$  are the transconductance parameters and effective load capacitance of the inverter. Note that we assume square-law behavior for the CMOS devices and thereby ignore the effects of velocity saturation. For an inverter with equivalent NMOS and PMOS, the propagation delay can be derived as

$$t_{P} = \frac{t_{PLH} + t_{PHL}}{2} = \frac{(L/W)C_{L}}{\mu C_{OX}(V_{DD} - V_{T})} \ln(\frac{1.5V_{DD} - 2V_{T}}{0.5V_{DD}})$$

(2.27)

Where

$$\mu = \mu_0 \left(\frac{T}{T_0}\right)^{km} , \quad km = -1.2 \sim -2.0 \tag{2.28}$$

$$V_T(T) = V_T(T_0) + \alpha(T - T_0)$$

,  $E \alpha = -0.5 - -3.0 mv / ^{\circ}k$  (2.29)

As the temperature increases, the mobility  $(\mu)$  and the threshold voltage  $(V_T)$  will both decrease. In the case of  $V_{DD}$  much larger than  $V_T$ , the thermal effect of the propagation delay will be dominated by the mobility. That is, the thermal coefficient of the propagation delay will become positive. The major problem of the simple temperature-to-pulse generator is that the width of the output pulse at the lower bound of the measurement range is usually much larger than zero. This will cause a large DC offset at the smart temperature sensor output. The second delay line with thermal compensation for temperature sensitivity reduction is inserted in the lower transmission path of the START signal to reduce the width offset of the output pulse, which is shown in Fig. 2.16. The width offset of the output can be easily reduced by adjusting the number of delay cells in delay line 2.

Figure 2.16 Width offset reduction accomplished by delay line 2.

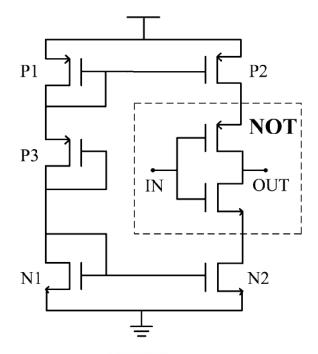

As shown in Fig. 2.17, a simple thermal compensation circuit is used to reduce the sensitivity of the inverter in delay line2. The diode connected transistors P1, N1, and P3 serve as the core of the thermal compensation circuit. Since P1, P3, and N1 are all diode connected, they will operate in saturation if bias current is flowing. Thus, we have

Figure 2.17 Delay cell is used in delay line 2.

$$I_{DP3} = \frac{1}{2} \mu C_{OX} \left(\frac{W}{L}\right) \left(V_{GSP3} - V_{T}\right)^{2} \left(1 + \lambda V_{GSP3}\right)$$

(2.30)

By substituting (2.28) and (2.29) into (2.30), the equation becomes

$$I_{DP3} = \frac{1}{2} \mu_{0} C_{OX} \left(\frac{W}{L}\right) \left(\frac{T}{T_{0}}\right)^{kn} \left[V_{GSP3} - V_{T}(T_{0}) - \alpha(T - T_{0})\right]^{2} \left(1 + \lambda V_{GSP3}\right) (2.31)$$

When the temperature is higher than 200K, a significant plateau effect can be observed for the difference between mask channel length and effective channel length. The thermal sensitivity of channel length modulation term  $(1 + \lambda V_{GSP3})$  will be neglected in the following deviations since it is much smaller than those of mobility and threshold voltage over the temperature range we are interested.

To get the minimum thermal sensitivity, let  $\frac{\partial I_{DP3}}{\partial T} = 0$

$$\frac{\mu_0 \cdot C_{OX} \cdot km}{2T_0} (\frac{W}{L}) (\frac{T}{T_0})^{km-1} \left[ V_{GSP3} - V_T(T_0) - \alpha(T - T_0) \right]^2 (1 + \lambda V_{GSP3})$$

=  $\alpha \cdot \mu_0 \cdot C_{OX} (\frac{W}{L}) (\frac{T}{T_0})^{km} \left[ V_{GSP3} - V_T(T_0) - \alpha(T - T_0) \right] (1 + \lambda V_{GSP3})$

After simplification, we have

$$V_{GSP3} = V_T(T_0) + \alpha (T - T_0) + 2 \frac{\alpha \cdot T}{km}$$

(2.32)

The sizes of transistors P1 and N1 are adjusted to make the gate-to-source voltage of P3 fit the requirement stated in (2.32) as closely as possible. The conduction current of transistor P3 can be found by substituting (2.32) back into (2.31) to yield

$$I_{DP3} = \frac{1}{2} \mu_0 C_{OX} \left(\frac{W}{L}\right) \left(\frac{T}{T_0}\right)^{km} \left[\frac{2\alpha T}{km}\right]^2 \left(1 + \lambda V_{GSP3}\right)$$

(2.33)

When km = -2, the drain current will become totally thermal independent

$$I_{DP3} = \frac{1}{2} \mu_0 C_{OX} \left(\frac{W}{L}\right) (\alpha T_0)^2 (1 + \lambda V_{GSP3})$$

Through the help of the current mirrors (P1, P2) and (N1, N2), the drain current of the inverter will be kept thermally insensitive as well, as will the propagation delay of delay line 2. This greatly reduces the design difficulty and enhances the tolerance to process variation.

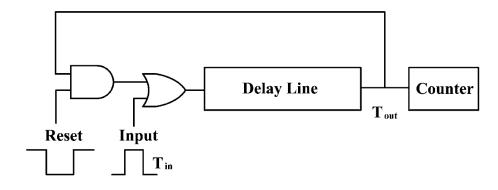

Finally, the cyclic time-to-digital converter, shows in Fig 2.18, it convert the pulse width of temperature-to-pulse generator to digital output code.

Figure 2.18 Block diagram of the cyclic TDC.

### **2.3.3 Dual-DLL-Based All-Digital Temperature Sensors**

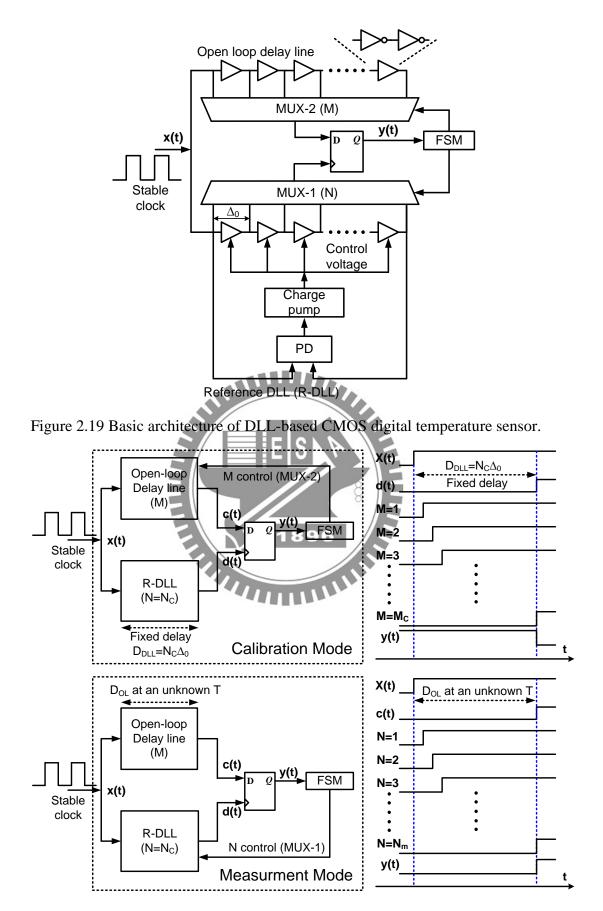

With process scaling down continuously, PVT variation will be a big problem about Time-to-digital based temperature sensors. A new type DLL-based all-digital temperature sensor [2.17] was presented. It has two improvements. First, it removes the effect of process variation on inverter delays via calibration at one temperature point, thus, reducing high volume production cost. Second, we used two fine-precision DLLs, one to synthesize a set of temperature-independent delay references in a closed loop, the other as a TDC to compare temperature-dependent inverter delays to the references. The use of DLLs simplifies sensor operation and yields a high measurement bandwidth (5kS/s) at 7bit resolution, which could enable fast temperature tracking.

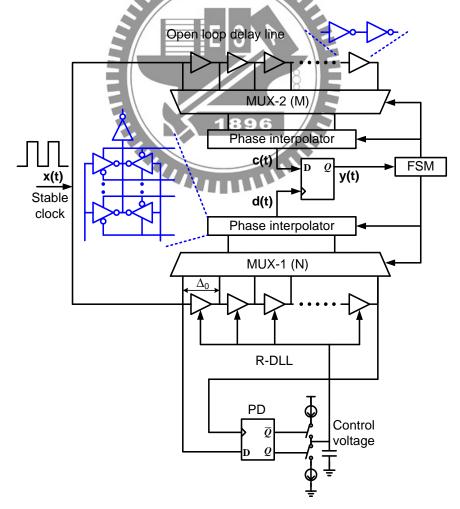

We execute calibration and delay normalization using the circuit of Fig. 2.19. It line, open-loop delay DLL contains and that an a synthesizes temperature-independent-delay references. This reference-DLL (R-DLL) is locked to a crystal oscillator x(t): each delay cell in the R-DLL has constant delay  $\Delta 0$ . MUX-1 taps a node in the R-DLL delay line: if the N-th cell's output is tapped, the delay from input x(t) to output d(t) of the R-DLL is  $D_{DLL} = N\Delta_0$ . This is our delay reference independent of temperature and process. N can be altered to produce different reference delays. In the open-loop line, if the M-th cell's output is tapped by MUX-2, the delay between input x(t) and output c(t) is varies with temperature and process.

Figure 2.20 Calibration mode (top) and measurement mode (bottom).

In calibration mode at temperature  $T_C$ , we set  $N = N_C$  to fix the reference delay at  $D_{DLL} = N_C \Delta_0$ . We then increase M (MUX-2 setting) until  $D_{OL}$  equals  $D_{DLL}$  at  $M = M_C$ . This comparison of  $D_{OL}$  to  $D_{DLL}$  to find their lock at  $M = M_C$  is done via the bang-bang phase detector in the middle of Fig. 2.19. Then the  $M_C$  value is corresponding to process corner.

Once 1-point calibration is complete, the sensor enters measurement mode. Temperature T is unknown, thus,  $D_{OL}$  of the hardwired open-loop line is an unknown delay, which the M-DLL measures by varying the reference delay  $D_{DLL}$  of the R-DLL (bottom of Fig. 2.20). MUX-1 setting N is varied until DDLL equals  $D_{OL}$  at N = Nm. Nm is a digital output that faithfully represents T. Nm corresponds to the normalized delay seen earlier. Fig. 2.21 shows the implemented architecture.

Figure 2.21 DLL-based CMOS all-digital temperature sensor.

# **2.4 PVT Sensors Applications**

The important applications of temperature sensors include:

1) The temperature control of consumer electronics, such as automobiles and home electronics.

2) The power consumption control in VLSI chips, such as CPU and chip sets;

3) The environment temperature monitor in automatic fabrication factories;

4) The temperature control of 3D-ICs.

5) The temperature compensation of clock skew in synchronous digital circuit.

# 2.4.1 CMOS Temperature Sensor with Ring Oscillator for Mobile DRAM Self-refresh Control

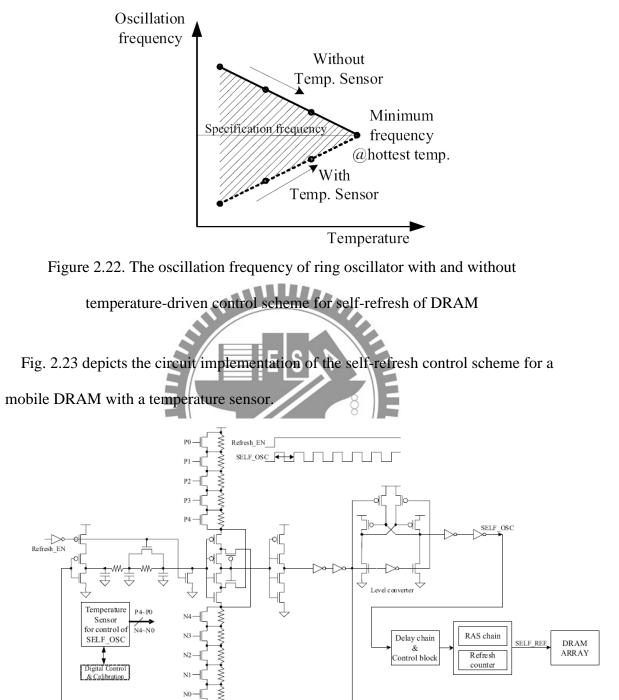

Low-power mobile DRAM can adjust its self refresh period according to internal temperature to minimize data retention current during power-down mode [2.4]. Usually, the leakage characteristic of a DRAM cell becomes worse at high temperature than at low temperature. Hence, for a conventional DRAM with no self-refresh control scheme, the interval for self-refresh operation must be determined by the hottest temperature condition. This means that data retention current is wasted at low temperature due to too early refresh of memory cells. Moreover, if a local clock signal to determine the self-refresh interval is generated by a ring oscillator as conventional DRAMs do, the wasted data retention current tends to be further increased at low temperature because the oscillation frequency of the oscillator increases as temperature decreases. This situation is described by the upper curve in Fig. 2.22 showing the dependency of the oscillation frequency of a ring oscillator on temperature variation. On the other hand, if we can measure the temperature using a temperature sensor, the self-refresh period can be adjusted adaptively based on this

measured temperature. That is, the period can be set long at low temperature and short at high temperature, as seen by the lower curve in Fig. 2.22

Figure 2.23. Circuit diagram of DRAM self-refresh control scheme with temperature

5-stage inverters ring

sensor

## 2.4.2 Thermally Robust Clocking Schemes for 3D Integrated Circuits

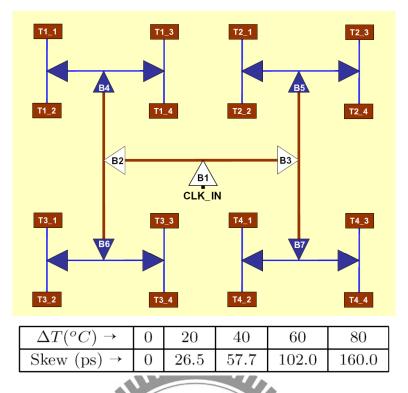

3D integration of multiple active layers into a single chip is a viable technique that greatly reduces the length of global wires by providing vertical connections between layers. However, dissipating the heat generated in the 3D chips possesses a major challenge to the success of the technology and is the subject of active current research. Since the generated heat degrades the performance of the chip, thermally insensitive/adaptive circuit design techniques are required for better overall system performance. A thermally adaptive 3D clocking scheme that dynamically adjusts the driving strengths of the clock buffers to reduce the clock skew between terminals [2.18].

For the synchronous part of a 3D chip, which may be distributed across layers, skewless clock signal is of utmost importance for the accuracy and speed of operation of a design. Since the clock network spans over most parts of the chip and thereby gets exposed to as diverse temperature range as occurs across the chip, the effect of temperature is very pronounced in clock trees. Fig. 2.24 shows an H-tree for a single layer of a 3D chip where we can see that for a number of physically close terminals the clock signals traverse through entirely different temperature zones to reach the terminals which can lead to significant skew between these terminals.

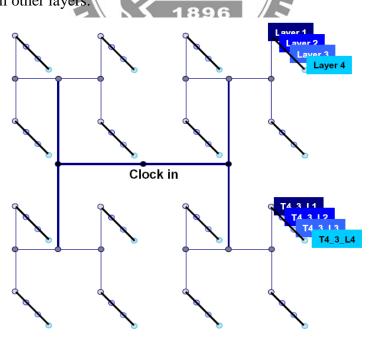

Figure 2.24.Temperature effect on rising edge skew between buffers T3\_4 and T4\_2. Fig. 2.25 implements the via topology clock tree with the clock buffers on a single layer and using interlayer vias the clock signals from the terminals of the clock tree are passed to all other layers.

Figure 2.25. 3D clock tree with via.

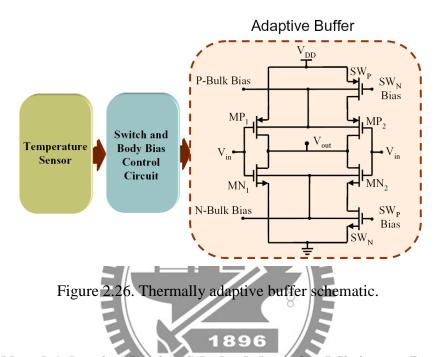

An adaptive circuit scheme was presented to reduce the variation of the clock skew with temperature gradient in the 3D design in Fig. 2.26. The temperature sensors sense the ambient temperatures and convert the temperatures to voltages that are processed by a wave shaping circuitry and finally used for dynamically changing the driving strengths of the clock buffers to reduce the overall skew.

# 2.4.3 A Novel Adaptive Design Methodology for Minimum Leakage Power Considering PVT Variations on VLSI Systems

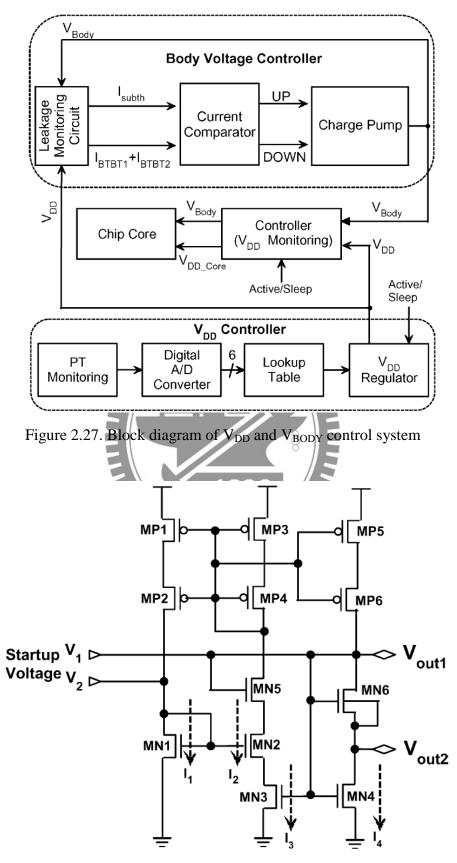

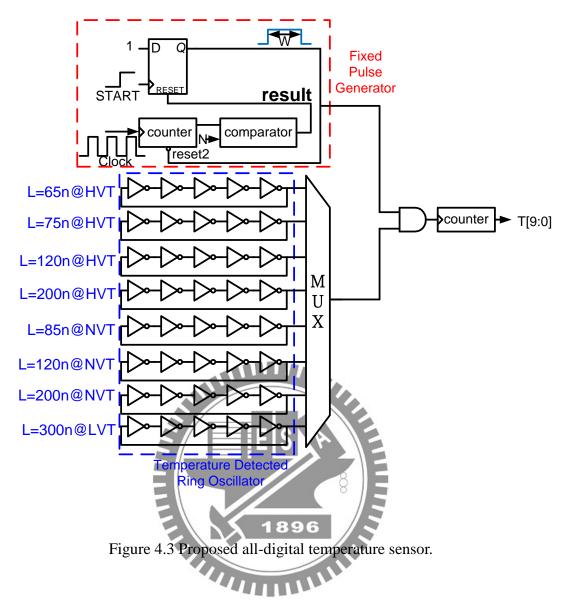

A novel design method to minimize the leakage power during standby mode using a novel adaptive supply voltage and body-bias voltage generating technique for nanoscale VLSI systems [2.19]. The minimum level of V<sub>DD</sub> and the optimum body-bias voltage are generated for different temperature and process conditions adaptively using a lookup table method based on the PVT monitoring and controlling systems shows in Fig 2.27. The process, voltage, and temperature (PVT) variations are monitored and controlled independently by their own dedicated systems shows in Fig 2.28. The subthreshold current as well as gate-tunneling and band-to-band-tunneling currents are monitored and minimized adaptively by the

optimally generated body-bias voltage.

(a)

34

(b)

Figure 2.28. (a) Temperature monitoring circuit. (b) Process monitoring circuit.

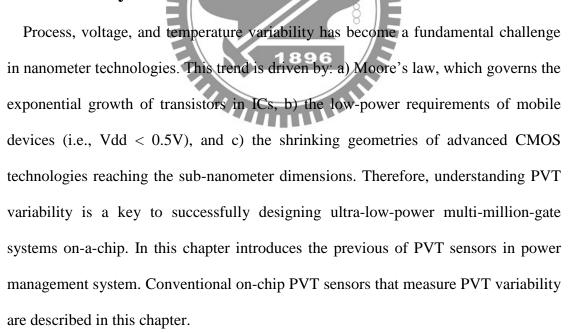

# 2.5 Summary

# **Chapter 3 Fully On-Chip Process, Voltage, and Temperature Sensors**

The past 20 years have seen enormous growth in the capability and ubiquity of digital integrated circuits. Today, it sometimes seems difficult to buy any product without them—even greeting cards have chips in them. In a short review paper like this, it is unfortunately impossible to mention (let alone describe) all of the great work that was done and published in the VLSI Circuits Symposium during this period. Time-to-Digital-Converter (TDC) is usually used to replace analog circuit. Its applications are gradually expanding such as a phase comparator of all-digital-PLL [3.1], [3.2], PVT sensors circuit [2:9]-[2.14], jitter measurement [3.3], modulation circuit and demodulation circuit as well as a TDC-based ADC [3.4]. The TDC will play more important role in nano-CMOS era because it is well-matched to implement with fine digital CMOS process; it consists of mostly digital circuits and as the switching speed increases, its performance is improved.

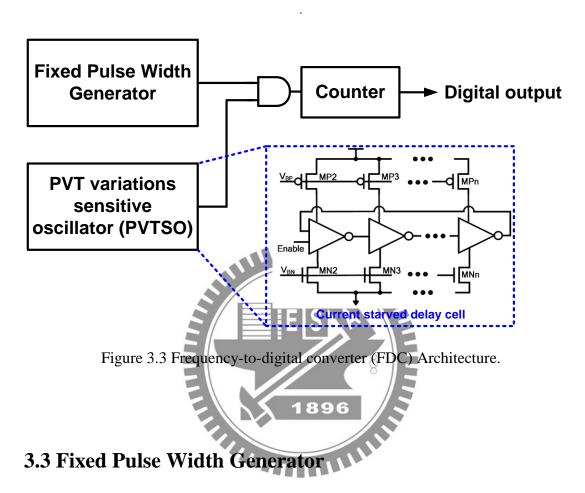

However, TDC converters are adopted in [3.5]. As a result, hundreds of inverters were required to obtain enough pulse delay to achieve sufficient temperature resolution. A DLL based temperature sensor has problems of occupying large area, consuming high power. In order to solve these problems, the frequency-to-digital converter (FDC) based smart PVT sensors are proposed in this chapter. The proposed FDC exhibits simple and efficient feature in the process of measuring PVT variation and converting it to digital value. Compared to previous work, the proposed PVT sensors are small-area, low-power, and high performance.

## **3.1 Time to Digital Converter (TDC) Architecture**

A Time-to-Digital-Converter (TDC) is to measure the interval time between two signals, and its time resolution of several pico seconds is achieved when it is implemented with advanced CMOS process. The next will introduce two types of TDC architecture.

## 3.1.1 Basic TDC Architecture

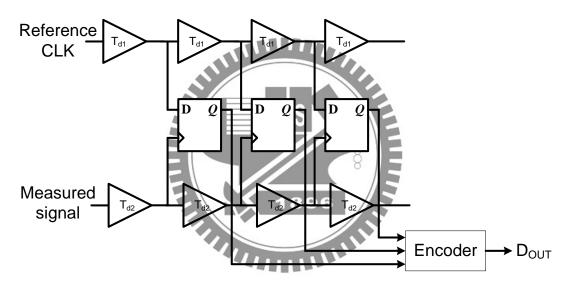

Fig. 3.1 shows configuration of a basic TDC, where the reference CLK passes through a buffer line which consists of an inverter chain, and the delayed reference CLK signals are fed into Flip-Flops as their data input. Also the measured signal is fed into Flip-Flops as their clock signal. We obtain the outputs of the Flip-Flops as a thermometer code, according to the rise-edge-timing interval between the reference CLK and the measured signal, and the encoder transforms it into a binary code. Its time resolution is given as the gate delay  $T_d$ . 1896 Reference CLK D D 0 Q Measured signal Encoder ► D<sub>OUT</sub>

Figure 3.1 A basic TDC architecture.

### **3.1.2 Vernier Delay Line TDC Architecture**

Fig. 3.2 shows a vernier delay line TDC which uses two delay lines: one is for the reference CLK with the buffer delay of  $T_{d1}$  and the other is for the measured signal

with the buffer delay of  $T_{d2}$ . Its time resolution is given by  $T_{d1}$ –  $T_{d2}$  (gate delay difference) which can be smaller than the basic TDC, but note that it uses 2N buffers (N buffers of  $T_{d1}$  and N buffers of  $T_{d2}$ ) for the input range from 0 to  $N(T_{d1} - T_{d2})$ . A new calibration method for a Vernier-based time-to-digital converter (TDC) was presented [3.6]. The method eliminates the need for accurate external sources typically used for TDC calibration. Simulation and experimental results using a field programmable gate array platform indicate that the method can successfully be employed to calibrate high-resolution TDCs with reasonable accuracy.

Figure 3.2 A vernier delay line TDC.

# **3.2 Frequency to Digital Converter (FDC)**

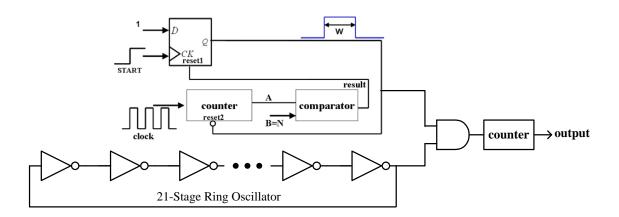

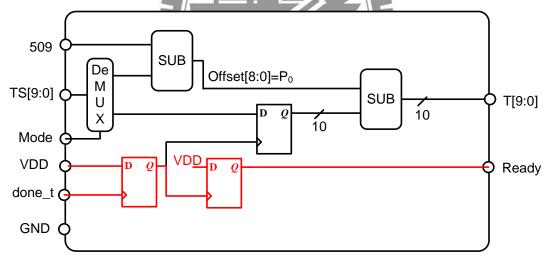

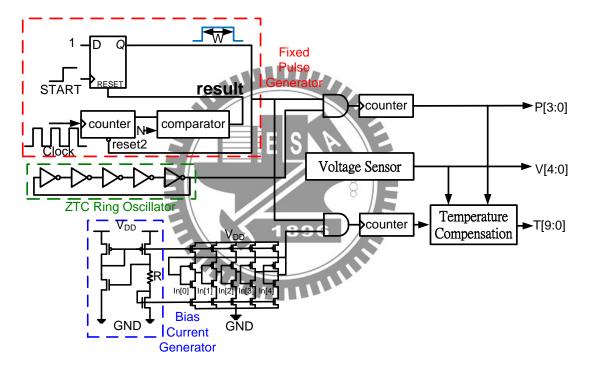

A TDC based PVT sensors have problems of occupying large area, consuming high power. In this thesis, we propose frequency-to-digital converter (FDC) based PVT sensors with small area, low-power, and high-resolution. Fig. 3.3 shows the proposed frequency-to-digital converter (FDC) exhibits simple and efficient feature in the process of measuring PVT variations and converting it to digital value. PVT variations are measured by the frequency difference between the PVT variations sensitive oscillator (PVTSO). The PVTSO are constructed from ring oscillators using a current starved delay cell.

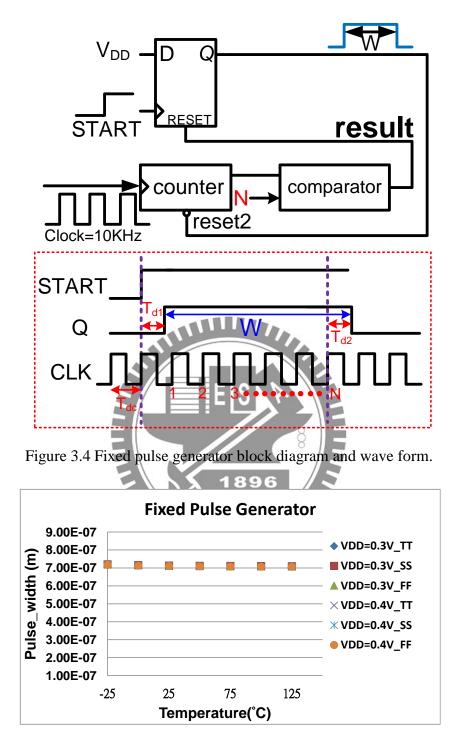

The proposed fixed pulse generator generates a pulse signal width independent of PVT variation. The detail schematic of the fixed pulse generator is drawn in Fig. 3.4. It is composed of D-type flip-flop, counter and comparator. When START signal rises, over a delay time (Td1), the output of D-type flip-flop also rises. When "result" signal rises, over a delay time (Td2), the output of D-type flip-flop will be reset to 0. The delay time Td1 and Td2 both affected by similar PVT variation, so it can be removed. From the above description, the output pulse signal width (W) is invariant from PVT variation. The simulation result of fixed pulse generator shows in Fig. 3.5. The circuit output pulse width is independent of PVT variation.

Figure 3.5 simulation result of fixed pulse generator.

# 3.4 Zero Temperature Coefficient Point Application – Process Sensor

A low power all-digital FDC-based process sensor circuit is proposed, and the circuit used ZTC characteristic to design. Section 3.4.1 introduces the effect of PVT variation in CMOS circuits. Section 3.4.2 introduces ZTC bias point of a MOS transistor. The architecture of all-digital process sensor and simulation results are presented in section 3.4.3.

## 3.4.1 PVT variation effects in CMOS circuits

In deeper submicron CMOS circuits design, PVT variations problem is more and more critical. In this section, the PVT variation effects are revealed.

$$MOS \text{ Current Equation in saturation mode}$$

$$I_{DSAT} = I_{D0} \left( \frac{V_{GS} - V_T}{V_{DD} - V_T} \right)^{\alpha};$$

$$I_{D0} = (W/L) \frac{\mu_0}{[1 + \theta(V_{GS} - V_T)][1 + V_{DSSAT}/(E_CL)]} CoxV_{D0}[V_{DD} - V_T - (\eta/2)V_{D0}];$$

$$\alpha = \frac{1}{\ln(2)} \ln \left( \frac{2V_{D0}[V_{DD} - V_T - (\eta/2)V_{D0}]}{V_{Da}[V_{DD} - V_T - \eta V_{Da}]} \right);$$

$$V_{DSSAT} = E_{CL} \left\{ \sqrt{1 + \frac{2}{E_{CL}} \left( \frac{V_{GS} - V_T}{\eta} \right)} - 1 \right\};$$

$$V_{D0} = V_{DSSAT} \mid v_{GS} = v_{DD}; \quad V_{Da} = V_{DSSAT} \mid v_{GS} = (V_{DD} + V_T)/2;$$

#### Figure 3.6 MOS current equation in saturation mode

MOS current varied with temperature, process, and voltage. Fig. 3.6 shows MOS current equations in saturation mode [3.7]. In the equations,  $I_{DSAT}$  is varied with

supply voltage (for  $V_{DD}$ ), temperature (for mobility and  $V_T$ ), and process (for W, L,  $C_{OX}$  and  $V_T$ ). In different PVT situations,  $I_{DSAT}$  makes gate delay an inconstant value.

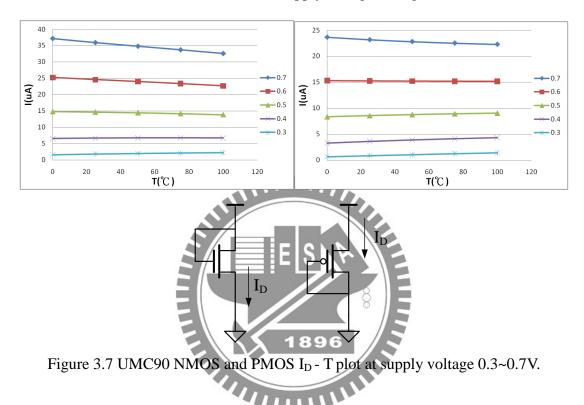

Fig. 3.7 is  $I_D$  – Temperature plot with supply voltage 0.5V, 0.4V, 0.3V. The current variation caused by temperature gets 26.5% difference at 0.3V. Temperature variation should be taken care while low supply voltage configurations are used.

### 3.4.2 Zero Temperature Coefficient Point

Mutual compensation of mobility and threshold voltage temperature variations may result in a zero temperature coefficient (ZTC) bias point of a MOS transistor. The ZTC effect has been used in many applications, for instance, voltage reference circuits and temperature sensor.

The n-channel transistor drain current equation

$$I_d = \frac{\mu_n C_{ox}}{2} \left(\frac{W}{L}\right) (V_{gs} - V_T)^2$$

(3.1)

The carrier mobility and the threshold voltage decrease with temperature. Make a partial differential on both side of (3.1) equation, and at the ZTC point  $(\partial I_d)/(\partial T) = 0$ .

We can find the bias voltage such that the drain current  $I_d$  would not vary with temperature T

$$V_{GS} = V_T (T_1) + \left[ 2 \mu_n \frac{\partial V_T / \partial T}{\partial \mu_n / \partial T} \right] |_{T = T_1}$$

(3.2)

Figure 3.8 ZTC points of UMC90 NMOS and PMOS transistor are at about 0.4V and

<u>0.6V.</u>

In Fig. 3.8, in UMC90 process, the ZTC points of NMOS and PMOS are at about 0.4V and 0.6V respectively. With the ZTC point, one may be able to create a logic gate with almost constant delay at a specific voltage point. The application of ZTC point is in the next section that a ring oscillator's period varies less with temperature.

### **3.4.3 ZTC Point Application – Process Sensor**

A ZTC application is shown in this section. Although the NMOS and PMOS's ZTC point are at different  $V_{GS}$ , with proper sizing, there is a  $V_{GS}$  point that the ring oscillator's period would vary less with temperature in process corners FF, TT, SS. In Fig. 3.9, at 0.5V, NMOS I<sub>D</sub> decreases with T, PMOS I<sub>D</sub> increases with T. The PMOS and NMOS mutual current compensation results in a ring oscillator's period are constant.

Figure 3.9 At 0.5V, NMOS  $I_D$  decreases with T, PMOS  $I_D$  increases with T.

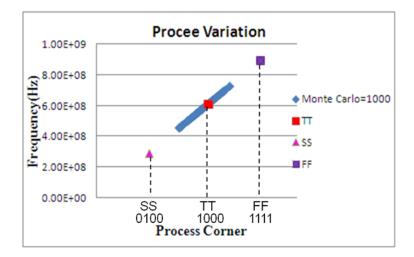

Fig. 3.10 is the testing result of a ring oscillator's frequency, at 0.5V, in process corners FF, TT, and SS. The NMOS and PMOS's width/length both are 120nm/90nm. Fig. 3.11 is the process monitor circuit, it can detect process variation in different corner. Finally, I use counter to convert the ring oscillator's frequency to 4-bit digital output. The output value will change with process variation, and the simulation result shows in Fig. 3.12.

Figure 3.10 Ring oscillator's frequency – temperature plot in corners FF, TT, SS.

Figure 3.11 Process Monitor circuit.

Figure 3.12 Ring oscillator's frequency with process variation.

# 3.5 A Fully Digital Voltage Sensor Using A New Delay Element

The conventional ADC, however, consists of conventional op amplifier. Cascode architecture of conventional op amplifier did not have enough headroom, so it is difficult to design at sub-1V.

One way to overcome the challenge of the low-power and low-voltage design is to process the signal in time-domain. In time-based ADC converter, the input analog voltage is converted to time or phase information. Thus, digital ADC circuit was presented in [2.3]. The circuit can replace conventional analog ADCs, and it can reach low-power, low-voltage, and small area. However, the digital ADC is not accuracy with PVT variation. Therefore, a novel fully digital ultra-low voltage sensor using a new delay element circuit is proposed to improve accuracy.

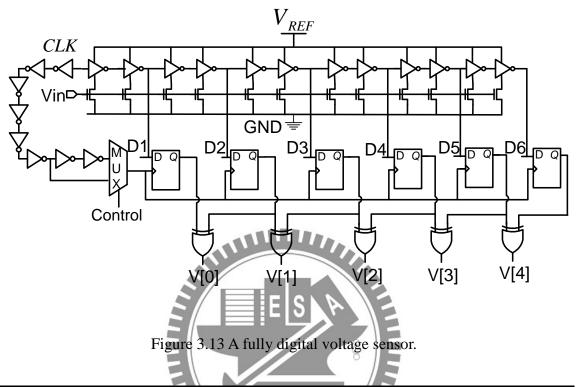

The proposed voltage sensor with 0.5V voltage reference is presented in this paper, shows in Fig. 3.13. It converts input voltage to 5-bit digital code V[4:0]. The proposed voltage sensor consists of current starved inverters, flip-flops, and XOR gate. The

control bit is from process monitor, and it can reduce the voltage sensor output error. The control bit can compensate process variation, and Table 3.1 represents the V[4:0] with different voltage. The quantization step of voltage sensor is about 50mv.

| Table 3.1 Voltage Sensor Digital Code Table |              |      |      |             |              |  |  |  |  |

|---------------------------------------------|--------------|------|------|-------------|--------------|--|--|--|--|

| $\mathbf{V}_{\mathbf{in}}$                  | Digital Code |      |      |             |              |  |  |  |  |

|                                             | <b>V[0]</b>  | V[1] | V[2] | <b>V[3]</b> | <b>V</b> [4] |  |  |  |  |

| 0.3                                         | 1            | 0    | 0    | 0           | 0            |  |  |  |  |

| 0.35                                        | 0            | 1    | 0    | 0           | 0            |  |  |  |  |

| 0.4                                         | 0            | 0    | 1    | 0           | 0            |  |  |  |  |

| 0.45                                        | 0            | 0    | 0    | 1           | 0            |  |  |  |  |

| 0.5                                         | 0            | 0    | 0    | 0           | 1            |  |  |  |  |

# 3.6 Fully On Chip Ultra-Low Voltage Temperature Sensor

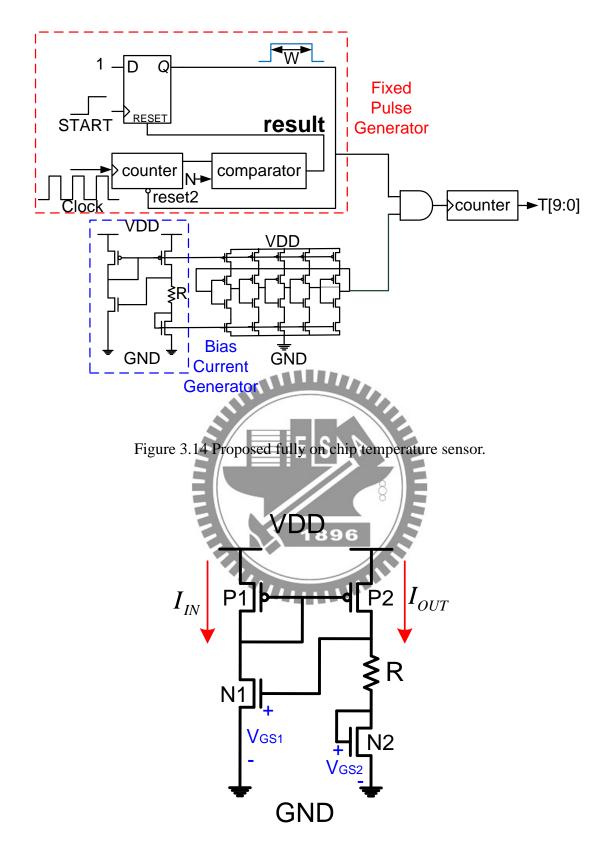

The proposed temperature sensor, it shows in Fig. 3.14. The bias current generator shows in Fig. 3.15, and N1, N2 transistors operate in weak inversion region. Alpha-power subthreshold drain current ( $I_{D_{-SUB}}$ ) [3.7] can be expressed as follows:

$$I_{D_{SUB}} = \mu_0 C_{OX} \frac{W}{L} (m-1) (V_T)^2 \times e^{(V_{GS} - V_{th})/mV_T} \times (1 - e^{-V_{DS}/V_T})$$

(3.3)

Assume V<sub>DS</sub>>>V<sub>T</sub>, The term of  $(1 - e^{-V_{DS}/V_T})$  can be ignored. Simplification of the formula can be expressed based on the following:

$$I_{IN} = \mu_0 C_{OX} \frac{W}{L} (m-1) (V_T)^2 \times e^{(V_{GS1} - V_{th})/mV_T}$$

(3.4)

$$I_{OUT} = \mu_0 C_{OX} \frac{W}{L} (m-1) (V_T)^2 \times e^{(V_{GS2} - V_{th})/mV_T}$$

(3.5)

Assume

$$I_{o} = \mu_{0} C_{oX} \frac{W}{L} (m-1)$$

(3.6)

$P_1$  and  $P_2$  are current mirror.

$$\frac{I_{P1}}{I_{P2}} = \frac{W_{P1}/L_{P1}}{W_{P2}/L_{P2}} = \frac{I_{IN}}{I_{OUT}}$$

(3.7)

Simplification (3.4) and (3.5) into (3.8) and (3.9), the equation becomes

$$V_{GS1} = mV_T \times \ln\left(\frac{I_{IN}}{I_{ON1}}\right) + V_{th}$$

$$(3.8)$$

$$V_{GS2} = mV_T \times \ln\left(\frac{I_{OUT}}{I_T}\right) + V_{th}$$

$$(3.9)$$

$$I_{GS2} = mV_T \times \ln\left(\frac{OUT}{I_{ON2}}\right) + V_{th}$$

And

$$\frac{I_{ON1}}{I_{ON2}} = \frac{W_{N1}/L_{N1}}{W_{N2}/L_{N2}}$$

(3.10)

Combine (5)-(8) into (9), the equation becomes

$$I_{OUT} = \frac{V_{GS1} - V_{GS2}}{R}$$

=  $\frac{mV_T \times \ln\left(\frac{I_{IN} \times I_{ON2}}{I_{OUT} \times I_{ON1}}\right)}{R} = \frac{mV_T}{R} \times \ln\left(\frac{W_{p1}W_{N2} / L_{p1}L_{N2}}{W_{p2}W_{N1} / L_{p2}L_{N1}}\right)$  (3.11)

If,

$$L_{P1} = L_{P2} = L_{N1} = L_{N2}$$

$$I_{OUT} = \frac{mV_T}{R} \times \ln\left(\frac{W_{p1}W_{N2}}{W_{p2}W_{N1}}\right)$$

(3.12)

The output current of the bias current generator is proportional to temperature, as described in equation (3.12). The output current is used to charge the inverters, so the frequency of ring oscillator is also proportional to temperature. All of above mentioned characteristics have perfect linearity. The fixed pulse generator generates a pulse signal width independent of PVT variation. The ring oscillator output and fixed pulse through 2-AND gate, and the output frequency digital code connects to "clock" pin of counter, and the counter can be positive edge triggered generating the corresponding digital output T[9:0]. The output T[9:0] represents the corresponding environmental temperature, and T[9:0] will be adjusted by proposed PV sensor to reduce the error caused by PV variation.

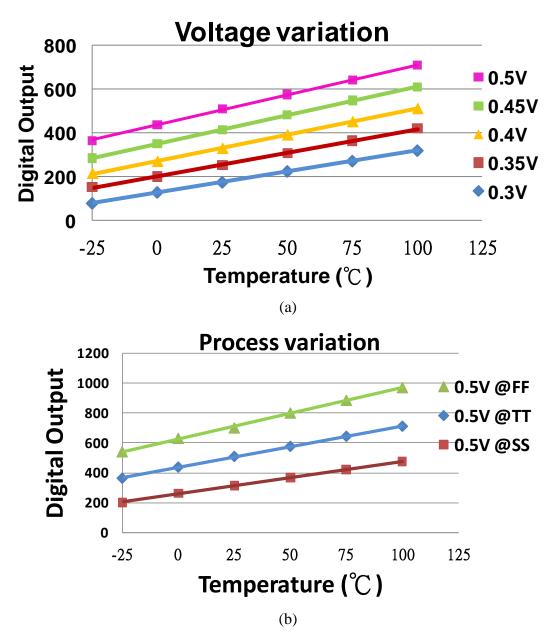

When the supply voltage is  $0.5V \sim 1V$ , a voltage regulator was presented to generate output voltage below 0.5V. Thus, the output of voltage reference provides a voltage source to temperature sensor. The simulation result with process and voltage variation is shows in Fig. 3.16.

Figure 3.15 Bias current generator.

Figure 3.16 (a) Simulation result of temperature sensor with voltage variation. (b) Simulation result of temperature sensor with process variation.

# 3.7 1-point Calibration Method of Proposed Temperature Sensor

Fig. 3.16 shows the simulation result of temperature sensor with process and voltage variation. We choose 1-point calibration (a.k.a linear calibration) method to compensate the output of this sensor. The calibration selects one point in the range of

a data logger or chart recorder and setting it to give an identical reading as the same point.

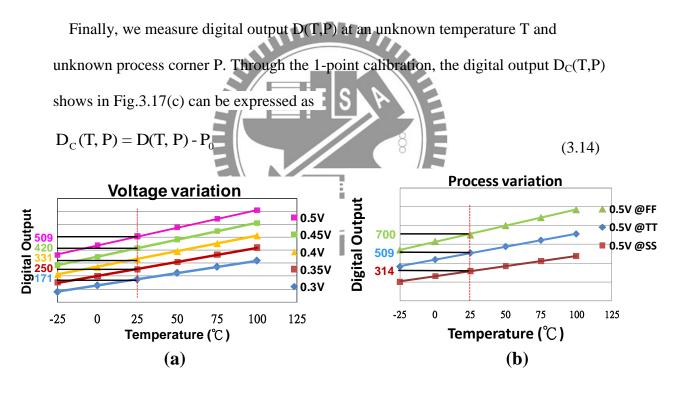

Frequency of ring oscillator varies with both voltage and process shows in Fig 3.17(a)-(b). Proposed sensor calibrates out the process dependency with a frequency measurement at one temperature. First, we record the digital output  $D(25^{\circ}C,TT)=509$  at 25°C and TT corner from Fig 3.17. Then we measure digital output  $D(25^{\circ}C,P)$  at 25°C and unknown process corner P. Then we record the difference P<sub>0</sub> between  $D(25^{\circ}C,P)$  and  $D(25^{\circ}C,TT)$ .

$$P_0 = D(25^{\circ}C, P) - D(25^{\circ}C, TT) = D(25^{\circ}C, P) - 509$$

(3.13)

Figure 3.17 (a) Simulation result of temperature sensor with voltage variation.

(b) Simulation result of temperature sensor with process variation.

(c) 1-point calibration method of proposed temperature sensor.

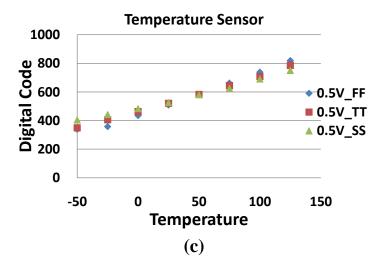

1-point calibration method hardware implementation of the proposed scheme is introduced to compensate for the voltage and process variations on the impact of temperature. The proposed calibration circuit is shown in Fig. 3.18.

Figure 3.18 1-point Calibration Method of Temperature Sensor.

# **3.8** Conclusion and Simulation Results

From the previous section, we proposed a fully on chip ultra-low power PVT sensors in Fig. 3.19. The sensor without analog-to-digital converter (ADC) or bandgap reference is proposed for high accuracy, ultra-low power, and wide voltage

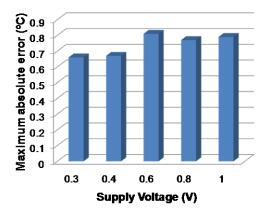

range portable applications. Conventional temperature sensors rely on ADCs for digital output code conversion. The proposed temperature sensor generates a clock frequency proportional to the measured temperature, and converts the frequency into a corresponding digital code T[9:0]. A voltage sensor and process sensor are proposed to compensate temperature sensor. The sensor was designed in a 65nm CMOS technology. It operate over a wide voltage range from  $0.3V\sim1V$ . The power consumption is under  $3.7\mu$ W at 0.3V and a sample rate of 10k samples/sec. The temperature error is merely -0.8 $\circ$ 0.8 $\circ$ C shows in Fig. 3.20.

Figure 3.19 Proposed fully on chip PVT sensors

Figure 3.20 Maximum absolute error of proposed temperature sensor.

# **3.9 Summary**

A process, voltage, and temperature (PVT) sensor without a voltage/current analog-to-digital converter (ADC) or bandgap reference is proposed for high accuracy, low power, and wide voltage range portable applications. Conventional temperature sensors rely on voltage/current ADC for digital output code conversion. The proposed temperature sensor generates a clock frequency proportional to the measured temperature, and converts the frequency into a corresponding digital code. The generated digital code is still under the influence of PVT variations. Two distinct sensors for voltage and process monitoring are also proposed to enhance temperature coefficient (ZTC) bias point is used to remove temperature effect. It is capable of operating over a wide voltage range within 0.3V+1V. The power consumption is no more than 3.7W at 0.3V supply voltage and a high sample rate of 10k samples/sec. The temperature error is merely -0.8+0.8°C.

A comparison chart between this work and previously presented temperature sensors is shown in Table 3.2. In Table 3.2, the main characteristics, such as operation supply voltage, power, error, temperature range, sensor type, process technology, and conversion rate are compared.

| Table 3.2         Temperature sensor comparisons |           |           |           |                |            |                 |  |  |  |  |

|--------------------------------------------------|-----------|-----------|-----------|----------------|------------|-----------------|--|--|--|--|

| Sensor                                           | Supply(V) | Power(µW) | Error(°C) | Sensor Type    | CMOS       | Conversion rate |  |  |  |  |

|                                                  |           |           |           | Sensor Type    | Technology | (samples/s)     |  |  |  |  |

| [2.7]                                            | 3.0       | 4.5       | -0.6~+0.6 | Temp-to-Pulse  | 0.35um     | 10              |  |  |  |  |

| [2.9]                                            | 3.0       | 10        | -0.7~+0.9 | Temp-to-Pulse  | 0.35um     | 10k             |  |  |  |  |

| [2.10]                                           | 1.0       | 25        | -1.0~+0.8 | Analog Voltage | 90nm       | 4               |  |  |  |  |

| Fully on chip                                    | 0.3~1     | 3.7@0.3V  | -0.8~+0.8 | Temp-to        | 65nm       | 10k             |  |  |  |  |

| <b>PVT sensors</b>                               |           |           |           | frequency      |            |                 |  |  |  |  |

# **Chapter 4 Self-Calibration Method for Subthreshold All-Digital PVT Sensors**

## **4.1 Previous TDC Calibration Method**

To calibrate a TDC, first, the duration of each quantization level is determined. Then, the actual characteristic curve representing the TDC is constructed based on the estimated size of each quantization level. The measurement error of the TDC is determined from its characteristic curve and compensated accordingly. Various TDC calibration methods have been proposed in the literature; the dominant methods are given here.

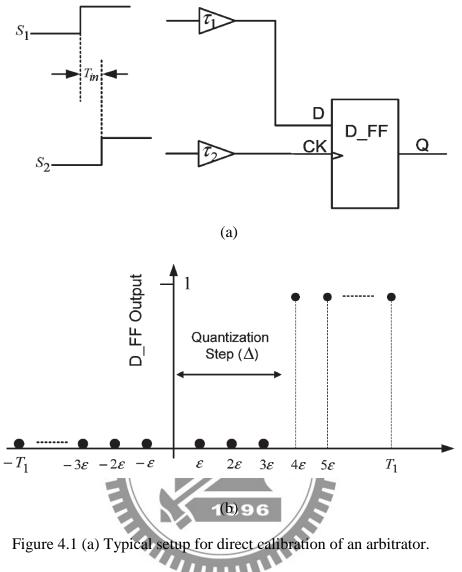

## 4.1.1 Direct Calibration

The concept of direct calibration is shown in Fig. 4.1, in which two signals with a precise delay difference of  $T_{in}$  are externally generated and applied to one stage of a Vernier-based TDC containing two buffers with delays of  $\tau_1$  and  $\tau_2$  and a D flip flop. If the input time interval T in is increased in small steps  $\varepsilon$  over a sufficiently long interval of  $(-T_1,+T_1)$ , the output of the flip-flop generates a stream of "0"s and "1"s. Assuming an ideal D flip-flop, the difference between the total number of "0"s and "1"s divided by two determines the size of the quantization step, which is equal to  $\Delta = \tau_2 - \tau_1$ , where  $\tau_2 > \tau_1$ . The accuracy of this calibration method is highly dependent on the size and precision of  $\varepsilon$ .

(b) Calibration result for an arbitrator with a quantization step of  $\Delta = 4\varepsilon$ .

## 4.1.2 Improved Direct Calibration Based on Added Noise

To ensure proper calibration of modern TDCs using the direct calibration method,  $\Delta T$  has to be in the range of femtoseconds. This requirement can be alleviated to some extend by adding noise with a standard deviation of  $\sigma_{noise}$  to  $\Delta T$ . Assuming that the standard deviation of the TDC delay elements are much lower than  $\sigma_{noise}$ , the sum of  $\Delta T$  and the noise creates a set of time events that follow Gaussian distribution with a mean value of  $\Delta T$  and a standard deviation of  $\sigma_{noise}$ . The addition of noise in this method increases the standard deviation of the quantization step and facilitates its measurement. Using additive temporal noise, Levine and Roberts [4.1] reported TDC calibration down to 5 ps. This method requires an on-chip noise source with a relatively large standard deviation, which may not be easy to implement.

## **4.1.3 Indirect Calibration**