# 國立交通大學

# 電子工程學系電子研究所

## 碩士論文

6T 靜態隨機存取記憶體的設計與特性分析

Design and characterization of 6T SRAM

研究生:林宜緯

指導教授:莊景德

中華民國九十九年十一月

# 6T 静態隨機存取記憶體的設計與特性分析 Design and characterization of 6T SRAM

研究生:林宜緯 Student:Yi-Wei Lin

指導教授: 莊景德 Advisor: Prof. Ching-Te Chuang

國立交通大學電子工程學系電子研究所碩士班

Submitted to Department of Electronics Engineering & Institute of Electronics

College of Electrical and Computer Engineering

National Chiao Tung University

in Partial Fulfillment of the Requirements

for the Degree of

Master of Science

In

Electronics Engineering

September 2010

Hsinchu, Taiwan, Republic of China

中華民國 九十九 年 十一 月

## 6T 静態隨機存取記憶體的設計與特性分析

學生:林宜緯 指導教授:莊景德教授

#### 國立交通大學電子工程學系電子研究所

#### 摘要

對於幾乎現今所有的電子設備都必須要用到記憶體來當作儲存媒介,於是記憶體的操作效能變掌握了整個系統的操作速度。而因為靜態隨機存取記憶體有著比其他記憶體種類更高的操作速度,靜態隨機存取記憶體通常會被嵌入到系統當中做為儲存媒介或者是快取記憶體。過去 20 年當中,6T 靜態隨機存取記憶體因為有比較緊密的面積以及較高的操作速度而變成靜態隨機存取記憶體設計的主流。然而當製程進行到一百奈米等級之後,製程變異讓6T 靜態隨機存取記憶體變得很難存活。先進製程中,6T 靜態隨機存取記憶體的讀取和寫入能力都遭受到很大的退化。特別是低壓操作,6T 靜態隨機存取記憶體的資取和寫入能力都遭受到很大的退化。特別是低壓操作,6T 靜態隨機存取記憶體的資取和寫入能力都遭受到很大的退化。特別是低壓操作,6T 靜態隨機存取記憶體的

為了要使 6T 靜態隨機存取記憶體能夠正常的在先進製程下工作,我們提出了兩個電路技巧: WL 降壓以及資料依存性寫入幫助電路來幫助讀寫能力。而讀寫的雜訊限度都會得到提升。即使在低壓操作,128k 位元的 6T 靜態隨機存取記憶體測試晶片依然能夠操作。此外,我們另外實現了一個監測電路來對 6T 靜態隨機存取記憶體的變異以及雜訊限度來做特性化。512 位元的測試陣列可以提供我們足夠的資料量來分析其統計上的分佈。而陣列的實現方式可以使得到的資訊能夠很接近真實的 6T 靜態隨機存取記憶體陣列而不是僅僅從模擬上得到。而配合特別設計的的量測方法,可以是我們的解析度達到某個程度,也可以自動化的量測。

١

Design and characterization of 6T SRAM

Student: Yi-Wei Lin

Advisor: Ching-Te Chuang

Department of Electronics Engineering & Institute of Electronics

National Chiao-Tung University

**ABSTRACT**

Almost the modern electronic devices need memory as its storage media, and the performance

of memory always dominant the overall performance of one system. Since SRAM has highest

operating speed than other memory family, it is usually embedded into system to storage data or to be a

cache. From past decades, standard 6T cell becomes the main stream of SRAM design due to its

compact area and high speed. However, as the technology goes beyond 100 nm, variation issue makes

6T SRAM cell hard to survive. The Read/Write ability suffers a serious degradation in advanced

technology node. Especially at low voltage, 6T SRAM seem has smaller probability to work.

In order to successfully allow 6T SRAM work at advanced process, we proposed two circuit

techniques: Word-Line Under-Drive and Data-Aware Write-Assist to increase the read and write ability.

Both Read Static Noise Margin and Write Margin would be improved. Even at low voltage operation,

the test chip of one 128kb 6T SRAM still function work. Besides, we implement a monitoring structure

to characterize the variation factors and noise margin of 6T cells. The test Array has 512kb cells could

provide us a sufficient amount sample to analysis the statistical distribution. The Array Based

implementation could allow us to get the information about Noise Margin quite close to real SRAM

macro rather than get it just from simulation. And with a special designed measure scheme, the

measurement resolution could be guaranteed and the measurement could be automatic.

I

## 誌 謝

本論文能順利完成,首先誠摯的感謝指導教授莊景德教授。在這兩年多的研究生涯裡,莊老師以他豐富的學識內容來指導我們,使得我很快就搭上最先端的研究,而省去懵懵懂摸索的歷程。莊老師為人和藹可親的態度,讓我在研究過程中遇到問題,都能夠找到一個很好討論以及指點方向的對象。而莊老師的處事不苟且嚴謹的態度,讓我也除了在專業知識以外也學得了許多。

另外感謝楊皓義學長,在研究過程中給了許多的幫助。皓義學長對於研究 經驗充足,也在許多方面給了我指導與建議,讓我能夠很快的就對於研究方面上 手。至於實驗室的同學以及學弟學妹們,也感謝你們能夠和我一起討論,也讓整 個研究室的氣氛相當歡愉,讓我來到實驗室不會有壓力,能夠開心的在這個空間 快樂做研究。

#### 1896

最後,謹以此文獻給我摯愛的雙親,感謝你們能夠構將我扶養成人,在我 跌跌撞撞的生涯裡給予最適時的幫助與鼓勵。

林宜緯

于新竹交大

2010.09.15

# **Content**

| CHAPTER | 1 INTRODUCTION                                                       | 1  |

|---------|----------------------------------------------------------------------|----|

| 1.1     | BACKGROUND                                                           | 1  |

| 1.2     | MOTIVATION AND GOALS                                                 | 1  |

| 1.3     | THESIS ORGANIZATION                                                  | 2  |

| CHAPTER | OVERVIEW OF THE OPERATION AND THE DESIGN OF 6T SRAM                  | 3  |

| 2.1     | MEMORY FAMILY AND SRAM                                               | 3  |

| 2.2     | 6T SRAM                                                              | 4  |

| 2.2.1   | Introduction of 6T SRAM                                              | 4  |

| 2.2.2   | Read Operation and read disturb voltage of 6T SRAM                   | 5  |

| 2.2.3   | Write Operation of 6T SRAM                                           | 6  |

| 2.2.4   | Read Static Noise Margin (RSNM) and Write Static Noise Margin (WSNM) | 6  |

| 2.2.5   | Write margin                                                         | 9  |

| 2.2.6   | The size of 6T SRAM                                                  | 10 |

| 2.3     | SRAM ARRAY ARCHITECTURE                                              | 10 |

| 2.3.1   | Memory Array and half-select problem  Decoder                        | 10 |

| 2.3.2   | Decoder 0 5                                                          | 13 |

| 2.3.3   | Sense scheme and column architecture                                 | 15 |

| 2.4     | VARIATION ISSUE                                                      | 18 |

| 2.4.1   | Global variation and Local variation                                 | 18 |

| 2.4.2   | Variation to 6T SRAM                                                 | 20 |

| 2.5     | DESIGN METHODOLOGY OF MODERN 6T SRAM                                 | 22 |

| 2.5.1   | Dual Supply Voltage                                                  | 22 |

| 2.5.2   | Dynamic Word-Line voltage                                            | 24 |

| 2.5.3   | Negative Bit-Line Level                                              | 26 |

| 2.6     | RELIABILITY ISSUE AND MONITORING STRUCTURE OF SRAM ARRAY             | 27 |

| 2.6.1   | BTI effect                                                           | 27 |

| 2.6.2   | Monitoring Structures                                                | 30 |

| CHAPTER | 23 DESIGN OF ONE 128KB TRADITIONAL 6T SRAM WITH WORD-LIN             | E  |

| UNDER-D | RIVE SKILL AND DATA-AWARE WRITE ASSIST SKILL                         | 32 |

| 3.1     | INTRODUCTION                                                         | 32 |

| 3.2     | CONCEPT OF WORD-LINE UNDER-DRIVE                                     | 35 |

| 3.3     | PREVIOUS WORK OF WORD-LINE UNDER-DRIVE                               | 35 |

| 3.1     | DDODOSED WODD-I INE LINDED-DDIVE SKILI                               | 40 |

| 3.4.1   | RSNM improvement and WM decrease with word-line under-drive | 40 |

|---------|-------------------------------------------------------------|----|

| 3.4.2   | Prior-art comparison                                        | 42 |

| 3.4.3   | Proposed Word-Line Under Drive (WLUD) Scheme                | 44 |

| 3.4.4   | The chosen of WL voltage                                    | 48 |

| 3.5     | PREVIOUS WORK OF WRITE ABILITY IMPROVEMENT                  | 49 |

| 3.6     | DATA-AWARE WRITE ASSIST CIRCUIT                             | 52 |

| 3.6.1   | Proposed Data-Aware Write-Assist Circuits                   | 53 |

| 3.6.2   | Write current and Column Half-Selected problems             | 54 |

| 3.6.3   | Asymmetric Hold SNM                                         | 56 |

| 3.6.4   | Leakage Issue                                               | 57 |

| 3.6.5   | Keeper Design                                               | 57 |

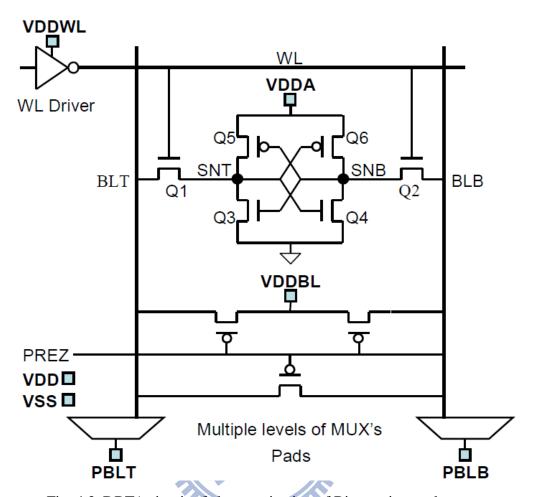

| 3.7     | IMPLEMENTATION OF ONE 128KB 6T SRAM                         | 63 |

|         | EMENT CIRCUIT                                               |    |

| 4.1     | Introduction                                                | 68 |

| 4.2     | INTRODUCTION PREVIOUS WORK                                  | 70 |

| 4.2.1   | Array Based measurement structure                           | 70 |

| 4.2.2   | All Digital measurement scheme. E.S.                        | 76 |

| 4.3     | MODIFIED CELL FOR RSNM MEASUREMENT                          | 78 |

| 4.4     | WM MEASUREMENT METHODOLOGY                                  | 81 |

| 4.5     | ARRAY IMPLEMENTATION 1896                                   |    |

| 4.6     | MEASUREMENT METHODOLOGY AND CIRCUIT BLOCKS                  |    |

| 4.7     | CALIBRATION                                                 |    |

| 4.8     | TEST CHIP IMPLEMENTATION                                    | 93 |

| CHAPTER | conclusions                                                 | 95 |

| REFEREN | CE OF CHAPTER 2                                             | 1  |

| REFEREN | CE OF CHAPTER 3                                             | 1  |

| REFEREN | CE OF CHAPTER 4                                             | 1  |

# **List of Figures**

| Fig. 2-1    | Traditional 6T SRAM                                                                 | 5    |

|-------------|-------------------------------------------------------------------------------------|------|

| Fig. 2-2    | Voltage Transfer Curve (VTC) of CMOS inverter [2-1]                                 | 6    |

| Fig. 2-3    | Butterfly curve of HSNM                                                             | 7    |

| Fig. 2-4    | The RSNM butterfly curve                                                            | 7    |

| Fig. 2-5    | The WSNM butterfly curve                                                            | 7    |

| Fig. 2-6    | Write trip voltage and Write Margin (WM)[2-3]                                       | 9    |

| Fig. 2-7    | Transistor size ratio in 6T SRAM                                                    | 10   |

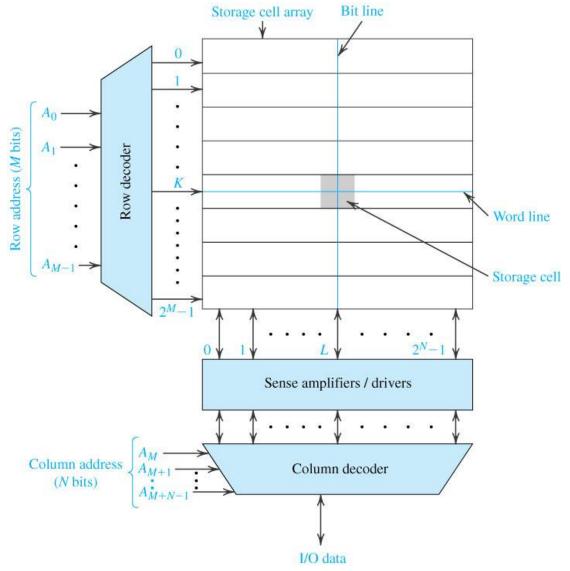

| Fig. 2-8    | Array architecture of an 2 <sup>N</sup> x2 <sup>M</sup> memory array[2-1]           | 11   |

| Fig. 2-9    | SRAM critical path [2-5]                                                            | 12   |

| Fig. 2-10   | Half-selected Read Disturb Voltage [2-4]                                            | 12   |

| Fig. 2-11   | Stability ratio [2-4]                                                               | 13   |

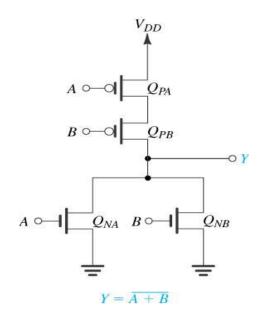

| Fig. 2-12   | CMOS Logic Circuits [2-1]                                                           |      |

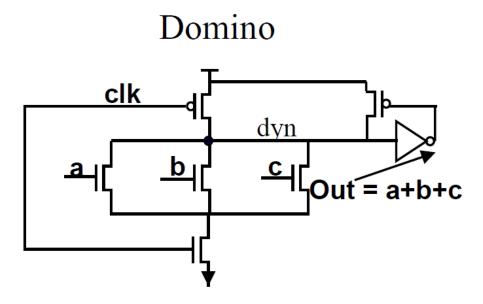

| Fig. 2-13   | Domino Logics [2-6]                                                                 | 14   |

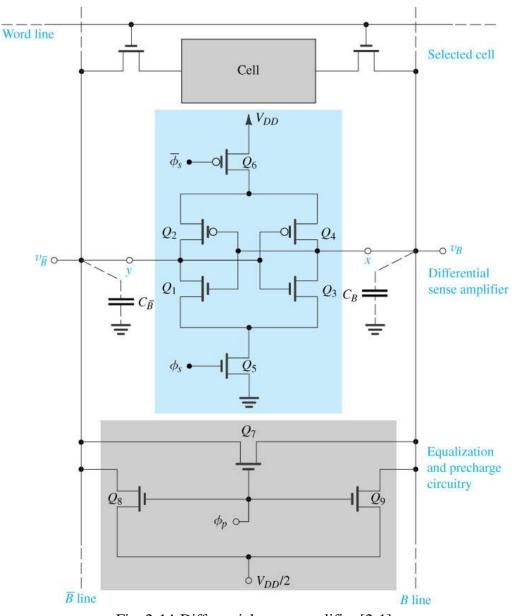

| Fig. 2-14   | Differential sense amplifier [2-1]                                                  | 16   |

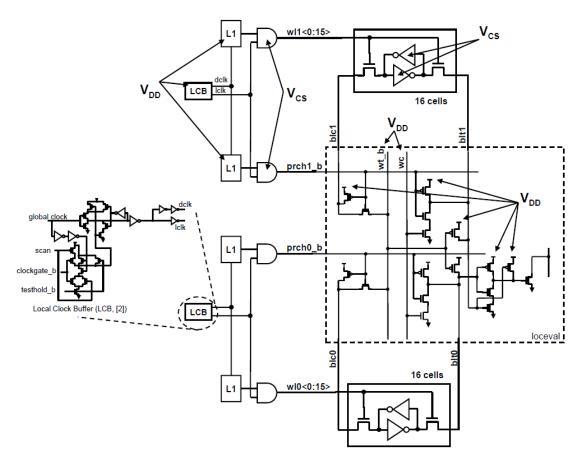

| Fig. 2-15   | Large signal sensing scheme of IBM Cell processor [2-7]                             | 17   |

| Fig. 2-16   | Global variation and Local variation of threshold voltage [2-6]                     | 19   |

| Fig. 2-17   | Static Noise Margin definition and the applied noise or variation that makes the SN | M    |

| equals zero | [9] 1896                                                                            | 20   |

| Fig. 2-18   | The effect of the inter-die Vt variation [2-8]                                      | 21   |

| Fig. 2-19   | The effect of local variation, (a) Write mode worse case, and (b) Read mode worse   | case |

|             | 22                                                                                  |      |

| Fig. 2-20   | Dual VCC Design of [2-10]                                                           | 23   |

| Fig. 2-21   | Negative VSS scheme [2-11]                                                          | 23   |

| Fig. 2-22   | RSNM improvement with lower $V_{WL}$ , (b)WSNM decade with lower $V_{WL}$ [12]      | 25   |

| Fig. 2-23   | Traditional method of word-line under-drive [2-12]                                  | 26   |

| Fig. 2-24   | Constant Negative Bit-line of [2-13]                                                | 27   |

| Fig. 2-25   | The generation of interface traps a PMOS transistor is biased in inversion.[2-20]   | 28   |

| Fig. 2-26   | Schematic description of the reaction-diffusion model [2-15]                        | 28   |

| Fig. 2-27   | Time dependent effect of stress and relaxation mechanism [2-15]                     | 29   |

| Fig. 2-28   | NBTI and PBTI impact to traditional 6T cell                                         | 30   |

| Fig. 2-29   | RSNM degradation due to NBTI                                                        | 30   |

| Fig. 3-1    | "Level Programmable Word-Line Driver and Dynamic Array Supply Control in            |      |

| Dual-Suppl  | y SRAM scheme [3-13]"                                                               | 35   |

| Fig. 3-2    | Adaptive Word-Line Under-Drive (WLUD) Scheme                                        | 36   |

| Fig. 3-3    | Conventional version (b) resistor added version                                     | 37   |

| Fig. 3-4  | Simulated word-line voltage of Fig. 3-3                                                      | 38 |

|-----------|----------------------------------------------------------------------------------------------|----|

| Fig. 3-5  | The I-V curve of two RACs, and shows the temperature dependence                              | 38 |

| Fig. 3-6  | Single-Supply WLUD using Replica Discharging Transistor                                      | 39 |

| Fig. 3-7  | Standard 6T SRAM in Read Mode                                                                | 40 |

| Fig. 3-8  | RSNM increase with word-line voltage decrease                                                | 41 |

| Fig. 3-9  | WSNM decrease with word-line voltage decrease                                                | 42 |

| Fig. 3-10 | Prior art of word-line under-drive circuits                                                  | 43 |

| Fig. 3-11 | Proposed word-line under-drive circuit                                                       | 44 |

| Fig. 3-12 | I-V <sub>WL</sub> curve of proposed WLUD circuit                                             | 46 |

| Fig. 3-13 | $V_{\text{WL}}$ comparison across process corners with different temperature of the proposed |    |

| WLUD circ | uit                                                                                          | 46 |

| Fig. 3-14 | Word-line rising time comparison of this work and prior art                                  | 47 |

| Fig. 3-15 | RSNM and WM versus WL voltage level                                                          | 48 |

| Fig. 3-16 | Column based dynamic V <sub>CC</sub> .                                                       | 49 |

| Fig. 3-17 | Floating Power Line Write                                                                    | 50 |

| Fig. 3-18 | Differential Data-Aware V <sub>DD</sub> scheme                                               |    |

| Fig. 3-19 | Differential Data-Aware V <sub>SS</sub> scheme                                               | 51 |

| Fig. 3-20 | Differential Data-Aware Power-supplied (D2AP) 8T cell                                        |    |

| Fig. 3-21 | Proposed word-line under-drive scheme                                                        | 53 |

| Fig. 3-22 | Proposed word-line under-drive circuit                                                       | 53 |

| Fig. 3-23 | Column Arrangement of DAWA and WLUD                                                          | 55 |

| Fig. 3-24 | equivalent circuit of column half-selected cells                                             | 56 |

| Fig. 3-25 | Hold SNM with Asymmetric supply voltages                                                     | 56 |

| Fig. 3-26 | Leakage drop waveform                                                                        | 57 |

| Fig. 3-27 | corner tracing keeper control                                                                | 58 |

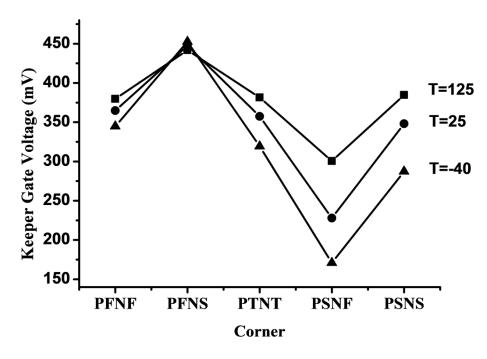

| Fig. 3-28 | gate voltage of keeper at different corner                                                   | 59 |

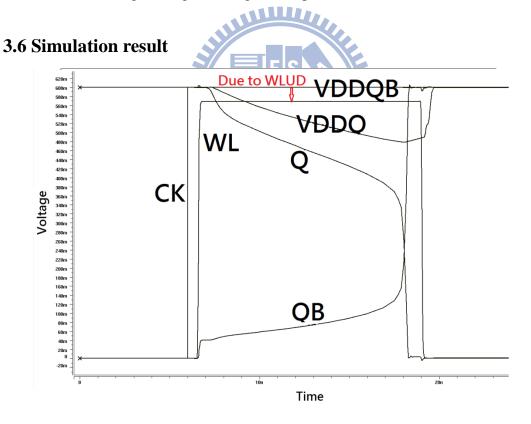

| Fig. 3-29 | Write waveform                                                                               | 59 |

| Fig. 3-30 | Read waveform                                                                                | 60 |

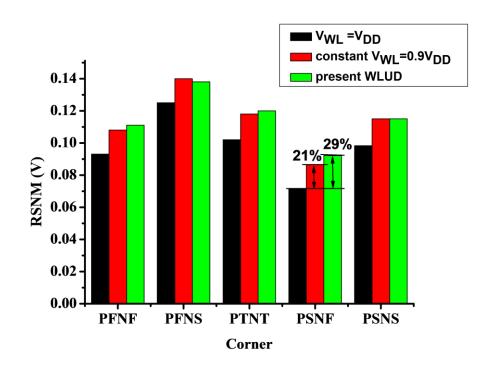

| Fig. 3-31 | RSNM improvement of constant V <sub>WL</sub> and WLUD                                        | 61 |

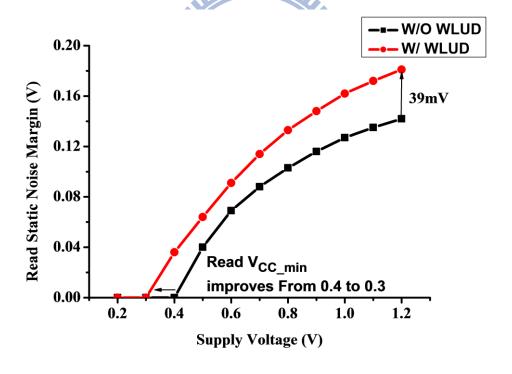

| Fig. 3-32 | Read margin and read V <sub>CC_min</sub> improvement                                         | 61 |

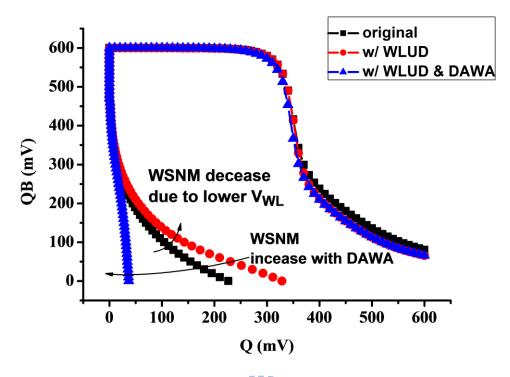

| Fig. 3-33 | WSNM improvement with DAWA                                                                   | 62 |

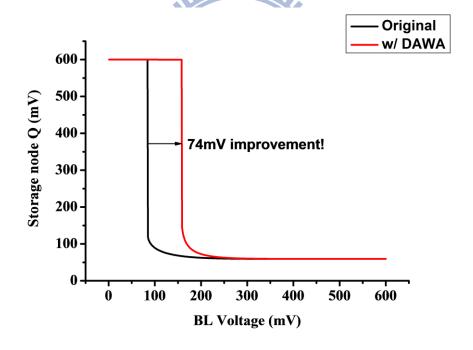

| Fig. 3-34 | Write Trip Voltage (write margin) improvement with DAWA                                      | 62 |

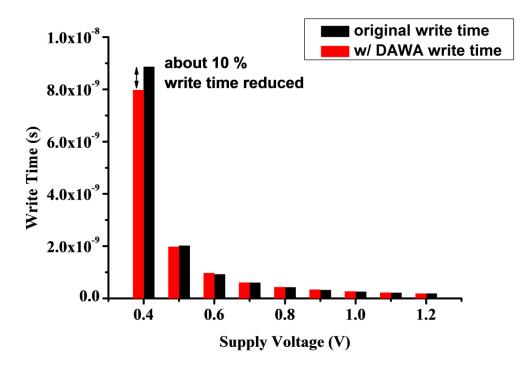

| Fig. 3-35 | Write Time and write V <sub>CC_min</sub> Improvement                                         | 63 |

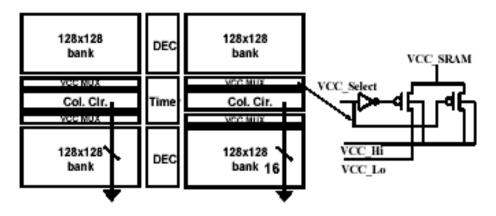

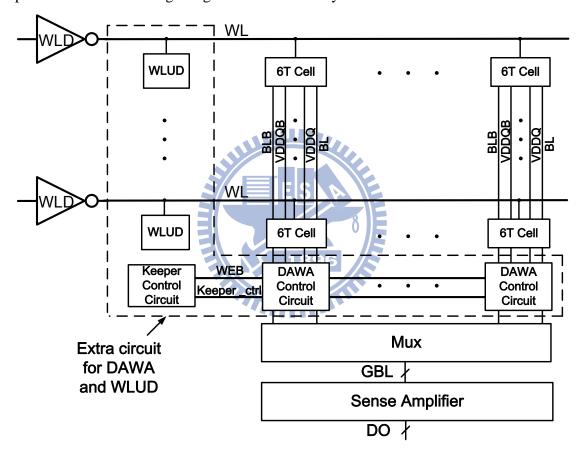

| Fig. 3-36 | Test Array Architecture                                                                      | 64 |

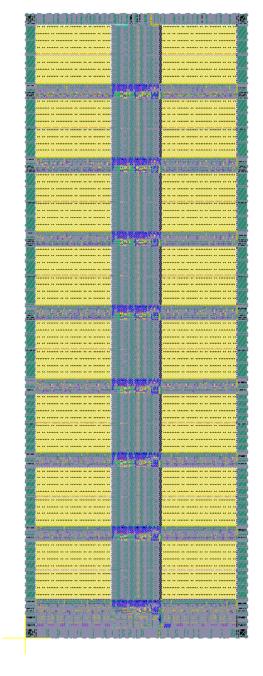

| Fig. 3-37 | Layout view of 128kb 6T SRAM Macro                                                           | 66 |

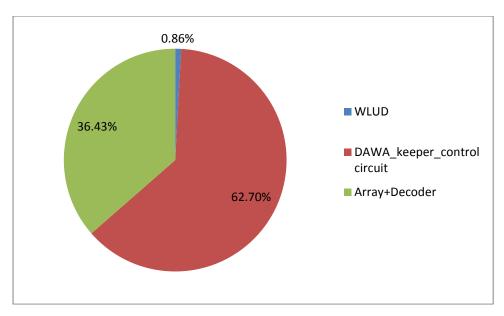

| Fig. 3-38 | Power Distribution                                                                           | 67 |

| Fig. 4.1  | Finding Vwrite structure with LYA (Low Yield Analysis) DFT                                   | 70 |

| Fig. 4.2  | DBTA circuit of characterization of Bit transistor scheme                                    | 71 |

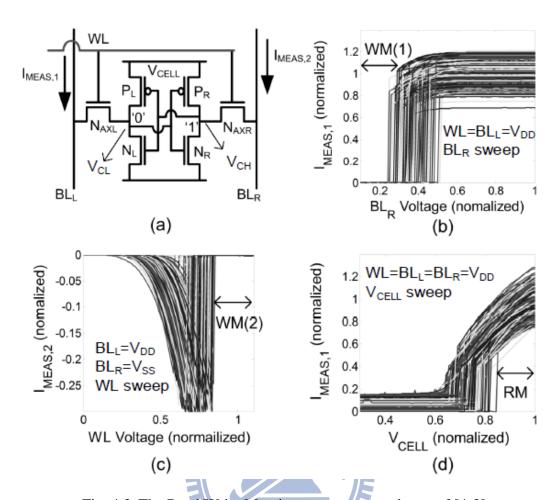

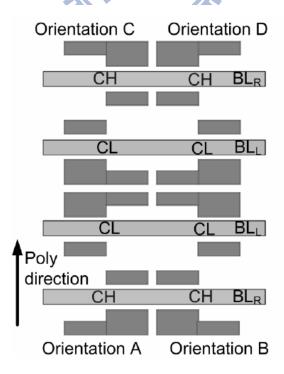

| Fig. 4.3   | The Read/Write Margin measurement scheme of [4-3]                                        | 72    |

|------------|------------------------------------------------------------------------------------------|-------|

| Fig. 4.4   | The storage node wired-out SRAM cell layout of [4-3]                                     | 72    |

| Fig. 4.5   | Read SNM, Butterfly curve WNM and I <sub>W</sub> measurement of [4-3]                    | 73    |

| Fig. 4.6   | 1-M bit SRAM transistor NBTI test structure of [4-4]                                     | 74    |

| Fig. 4.7   | Modified cells of [4-4]                                                                  | 74    |

| Fig. 4.8   | Fast stability analysis of large-scale SRAM arrays and the impact of NBTI degradati      | on.   |

|            | 75                                                                                       |       |

| Fig. 4.9   | measurement of read current and impact of NBTI                                           | 75    |

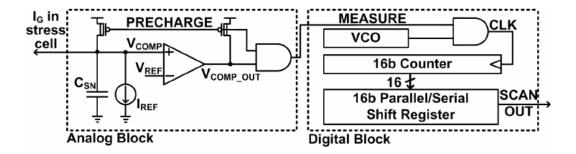

| Fig. 4.10  | Block diagram of measurement structure                                                   | 76    |

| Fig. 4.11  | current sensing scheme                                                                   | 77    |

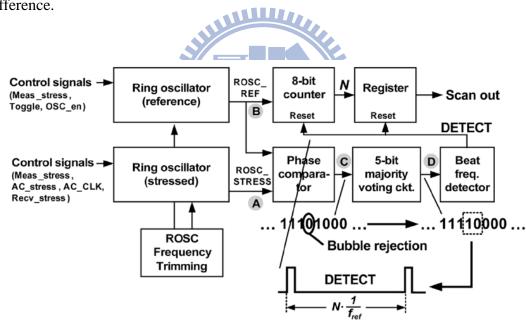

| Fig. 4.12  | Shows another frequency difference detection circuit                                     | 77    |

| Fig. 4.13  | traditional standard 6T SRAM cell                                                        | 78    |

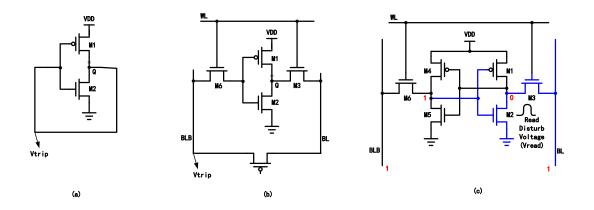

| Fig. 4.14  | (a) Basic concept to get Vtrip of inverter (b) Concept of Vtrip equivalent circuit in 6T | •     |

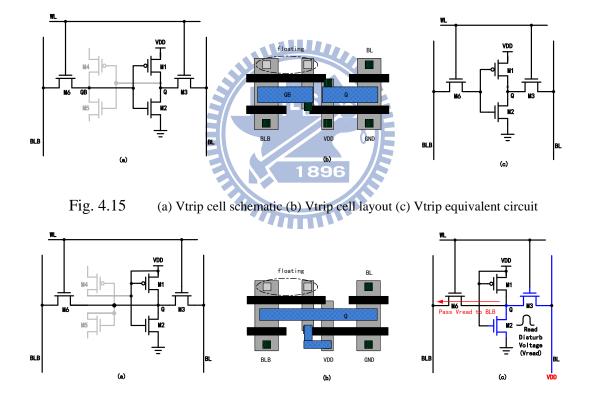

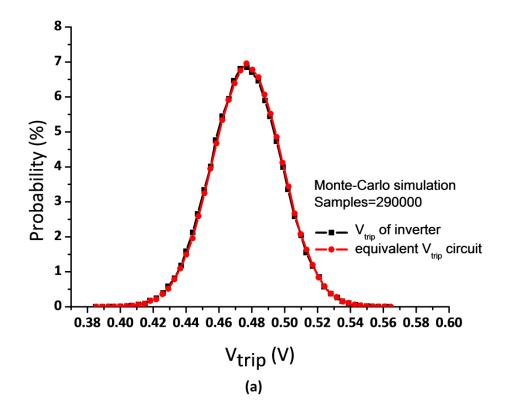

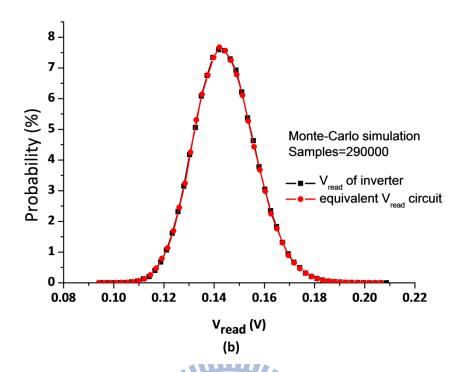

| SRAM (c) V | read Disturb Concept                                                                     | 79    |

| Fig. 4.15  | (a) Vtrip cell schematic (b) Vtrip cell layout (c) Vtrip equivalent circuit              | 79    |

| Fig. 4.16  | (a) Vread cell schematic (b) Vread cell layout (c) Vread equivalent circuit              | 79    |

| Fig. 4.17  | (a) Vread cell schematic (b) Vread cell layout (c) Vread equivalent circuit              | 81    |

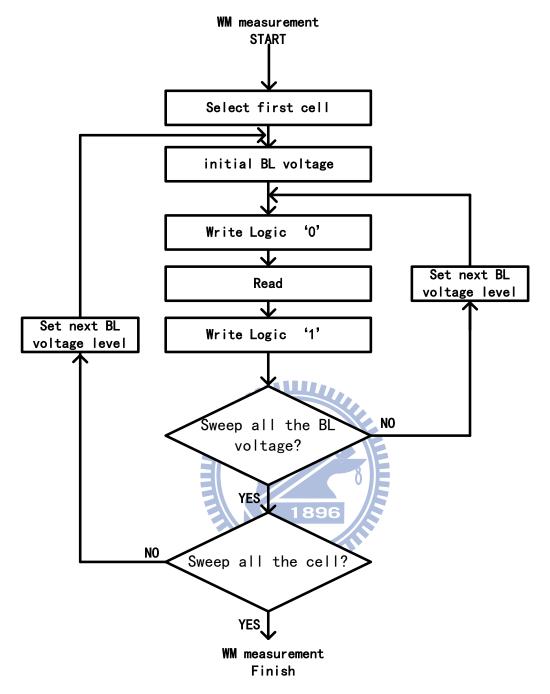

| Fig. 4.18  | Write Margin measurement flow                                                            | 82    |

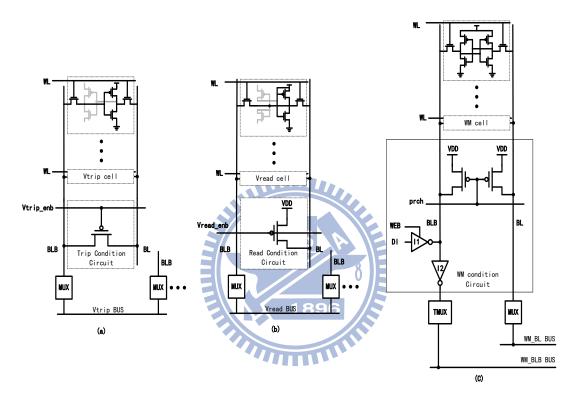

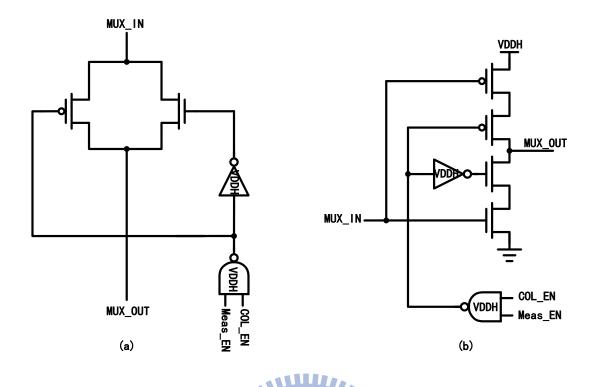

| Fig. 4.19  | (a) Vtrip column and trip condition circuit (b) Vread column and read condition circu    | uit   |

| (c) WM col | umn and WM condition                                                                     | 83    |

| Fig. 4.20  | (a) Vtrip column and trip condition circuit (b) Vread column and read condition circu    | uit   |

| (c) WM col | umn and WM condition                                                                     | 85    |

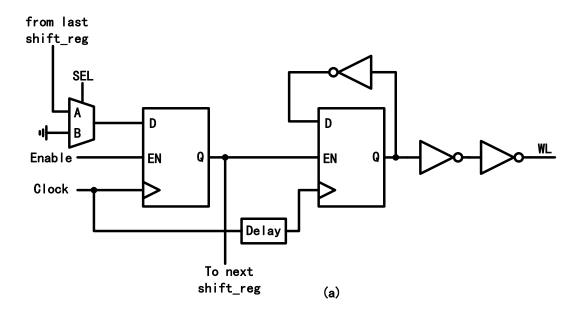

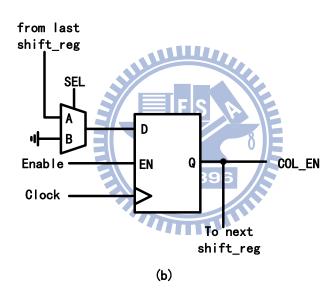

| Fig. 4.21  | (a) Modified Row direction shift register (b) Modified Column direction shift register   | er 86 |

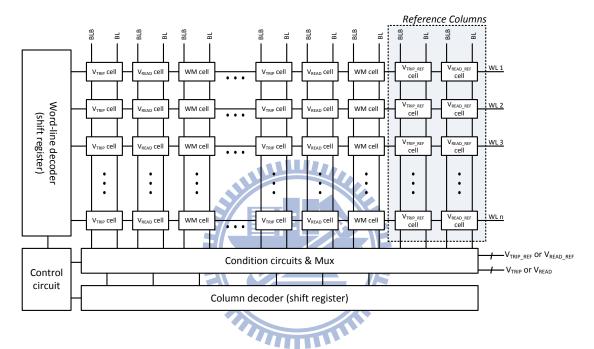

| Fig. 4.22  | Measurement Array Architecture                                                           | 87    |

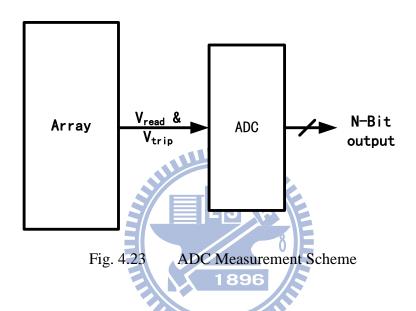

| Fig. 4.23  | ADC Measurement Scheme                                                                   | 88    |

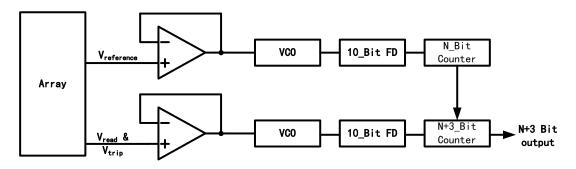

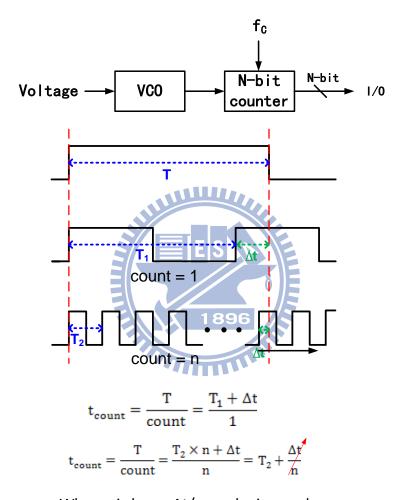

| Fig. 4.24  | VCO + Counter Based scheme                                                               | 89    |

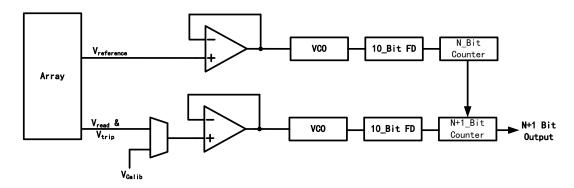

| Fig. 4.25  | Building blocks of voltage measurement scheme                                            | 90    |

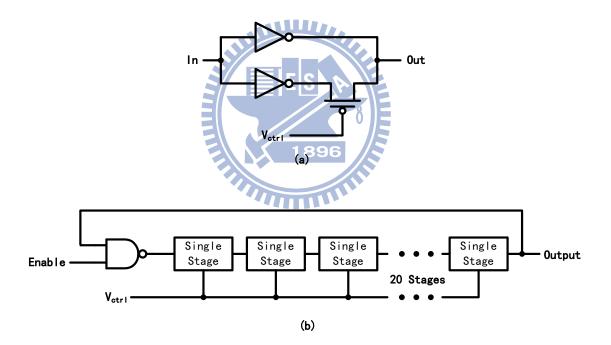

| Fig. 4.26  | (a) Single stage of VCO (b) 21 stages VCO                                                | 90    |

| Fig. 4.27  | VCO with counter based measurement scheme concept                                        | 91    |

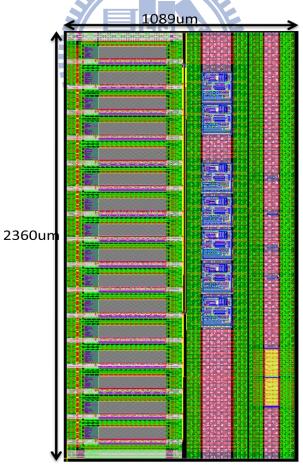

| Fig. 4.28  | Layout of present 512k Test Macro                                                        | 93    |

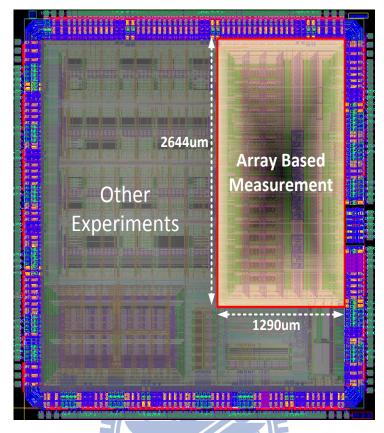

| Fig. 4.29  | Test Macro Location in Test Chip                                                         | 94    |

## Chapter 1

## Introduction

#### 1.1 Background

From the past decades, the trend of IC development perfectly fit the Moor's law: the density of the chip capacity is doubled per 18 month. The performance, complexity, and cost to a chip are promoted with the advanced technology. However, the size of device becomes very small at nano-scaled technology, variation is the major obstacle to chip design. The fabricated out transistor may be different to previous designed value and lead to system functional failure. This could result the degradation to the yield during chip manufacture.

From the predicting of ITRS Roadmap, memory area will be the largest portion to SOC. Static Random Access Memory (SRAM) would dominate the performance, power and area. In recent years, multi-core system and clouding computing gradually occupies an important role to the electronic application. These systems usually need high speed and large volume SRAM to do data processing. This makes the design to high speed SRAM an important issue.

#### 1.2 Motivation and Goals

Nowadays, the Static Random Access Memory (SRAM) occupies an important role to current SOC. However, with the shrinking process and reducing supply voltage, regular SRAM design no longer easily survived at advanced technology node. The most crucial issue is the degradation of the read/write ability to 6T SRAM. Since it is

hard to be fixed at the process phase, we would like to sue for the circuit technique solution. For SRAM, the read/write ability are contradictory conditions. So we must use different circuit technique to separately solve the read and write problem. In thesis, we focus on the circuit technique which could improve the functionality to 6T SRAM. Even at low supply voltage, we wish 6T SRAM could also have good yield with these circuit technique. Besides, we also want to investigate the real characteristic to 6T SRAM Array to provide more actual information rather than only from simulation. We also focus on the implementation of measurement circuit. With this implemented measurement structure, we can more precisely characterize several effects to the 6T SRAM cell.

## 1.3 Thesis Organization

In the following of the thesis, Chapter 2 discuss the basic operation to traditional 6T SRAM and its design issue. The reliability issue would be also mentioned in this chapter. Chapter 3 demonstrates "55nm 6T SRAM with Variation Tolerant Word-Line Under-Drive (WLUD) and Data-Aware Write Assist (DAWA)" design. In this Chapter, Variation Tolerant WLUD is proposed to improve the read stability of 6T SRAM. Data-Aware Write-Assist circuit skill is proposed to improve the 6T cell write ability. The design issue would be also discussed in Chapter 3. Chapter 3 shows an "An array-based all-digital on-chip circuit for 6T SRAM Stability measurement" design to characterize the static noise margin to 6T SRAM. 6T cell is modified to perform trip voltage to 6T cell (V<sub>trip</sub>) and read-disturb voltage (V<sub>read</sub>) measurement. Write margin measurement scheme is also implemented in this design. For analog voltage measurement, a VCO based measurement scheme is modified to fit our measurement scheme. Chapter 5 makes a conclusion to this thesis.

## Chapter 2

# Overview of the operation and the design of 6T SRAM

#### 2.1 Memory Family and SRAM

For current System on Chip (SOC), memory always account for the majority of transistors. As a result, memory always dominates the overall performance of one system. For current CMOS chips, Random Access Memory (RAM) array always be build in the integrated system (IC) as the storage media. RAMs is always associated with volatile memory which the storage data would loss if the power turn off. In contrast, there are several nonvolatile types of memory that are ROM, flash, DISK, etc. In the recent years, flash memory has a great growth at the market share and its application.

RAM is often applied to the Embedded System due to its higher access speed than other memory family. Volatile RAM could roughly divided into two categories: Dynamic RAM (DRAM) and Static RAM (SRAM). DRAM has slightly slower access speed than SRAM, but it has more compact density to save data with much smaller area. DRAM is currently the major storage device of most SOC. SRAM has the highest operation speed which could reach several hundred Mega Hertz or even Giga Hertz, so it is always embedded into system as cache memory. For the past decade, 6-transistor (6T) SRAM is always the main stream to the cache memories.

However, as the technology node goes the nano-scaled, the design of 6T SRAM

array faces several challenges. Process variation and leakage issue may cover the designed margin that may fail the read/write operation. This means we need to use extra circuit technique to counter the process variation and the leakage. In order to properly apply the circuit technique to 6T SRAM, we have to first discuss the basic operation of it.

#### **2.2 6T SRAM**

#### 2.2.1Introduction of 6T SRAM

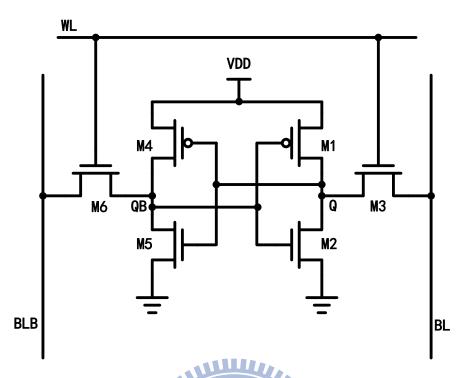

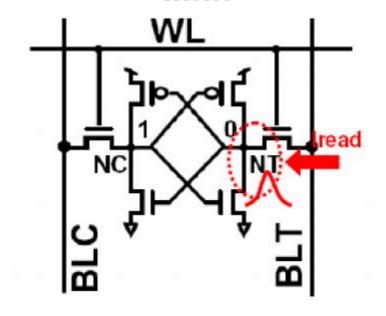

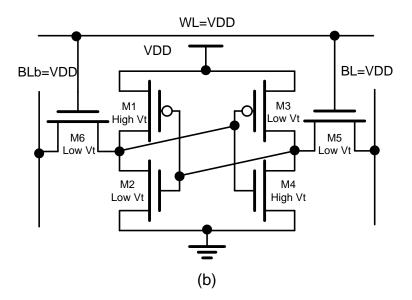

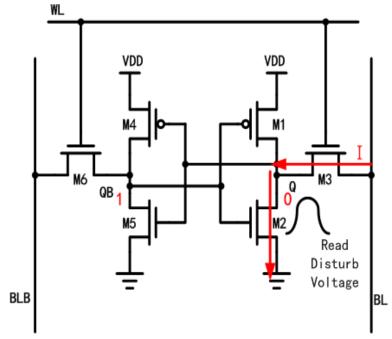

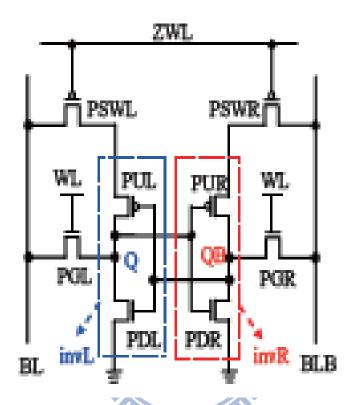

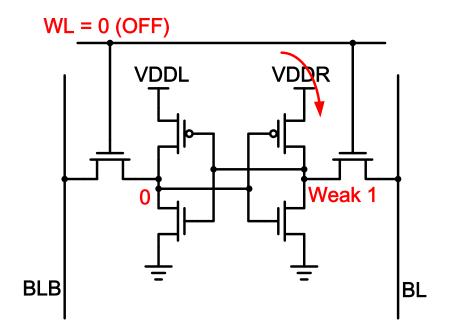

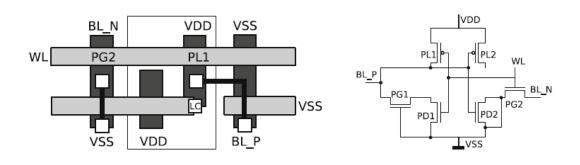

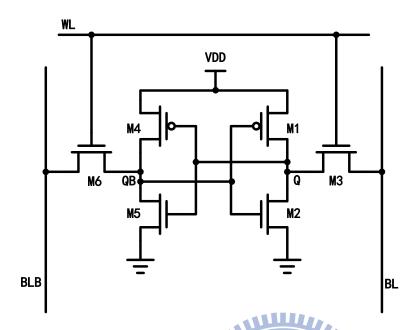

The most common used cell for SRAM is traditional 6T cell (show in Fig.2-1). Basically, this cell contains six transistors →two pull-up PMOS (M1&M4), two pull-down NMOS (M2&M5), and two pass-gate NMOS (M3&M6), so this cell is called 6"T" (Transistor) cell. In this cell, two inverter (M1-M2 and M4-M5) forms a cross couple pair latch that could strongly lock the storage value at logic "0" or "1", because the Voltage Transfer Curve (VTC) of this cell has only two stable point (actually there are 3 cross point, but one is the meta-stable point and hard to be exist) (Fig.2-3). And NMOS M3 and M6 could be seen as port to access the storage data of this cell. And one pair of Bit-lines (BL & BLB) are connected to the source node of pass-gate NMOS. This Bit-Line pair is used to pass in or pass out data. And one signal Word-Line (WL) is the activation signal of this cell.

Fig. 2-1 Traditional 6T SRAM

1896

#### 2.2.2Read Operation and read disturb voltage of 6T SRAM

Actually, all of the BL of 6T cell are pre-charged to VDD at standby mode which means there is no operation. Both of BL and BLB are held at high voltage before the read operation. Once the WL is activate, the pass-gate of this cell is turn on for accessing storage value. The BL of storage "0" side will be pulled close to the ground level however the storage "1" side will still keep at high level. Because of this operation, the storage value of this cell is passed to the BL. And we just need extra read circuit to get the value on the BL that we can get exact storage value.

However, for 6T cell, there is a disturb that could destroy the original storage value. From Fig.1, we assume Q is originally storage "0". Once the WL goes high, Q would be a divided voltage of M3 and M2 rather than ground voltage. This non-zero read-disturb voltage at storage node is close to the trip voltage of the other side inverter. If this read-disturb voltage is higher than the trip voltage of the opposite side

inverter, than destructive read operation is performed and the cell storage value would be flipped.

#### 2.2.3Write Operation of 6T SRAM

Write is an opposite operation to read for a 6T traditional cell. Before WL is selected to perform write operation, the Data-In should be prepared at the BL & BLB. For example, we want to write logic "0" into a cell, we must set the BL at ground voltage and BLB at high voltage before WL goes high. Once the WL goes to the high level, the storage value Q will quickly drop below the trip voltage of the opposite inverter that would flip the original storage value. And the regenerative process of the central latch would again hold the Q at strong ground voltage.

But there is also write fail problem for write operation. If the voltage at Q when the WL turns on is not lower than the trig voltage of opposite inverter, then write fail.

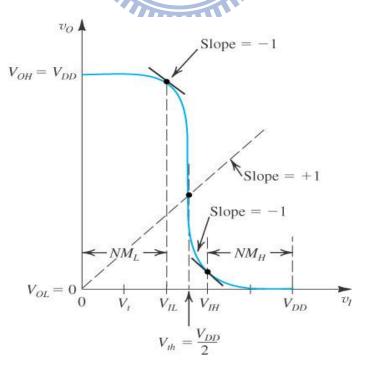

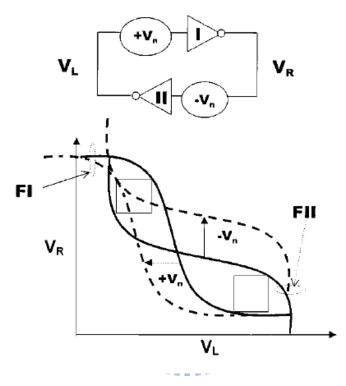

# 2.2.4Read Static Noise Margin (RSNM) and Write Static Noise Margin (WSNM)

Fig. 2-2 Voltage Transfer Curve (VTC) of CMOS inverter [2-1]

Fig. 2-3 Butterfly curve of HSNM

Fig. 2-4 The RSNM butterfly curve

Fig. 2-5 The WSNM butterfly curve

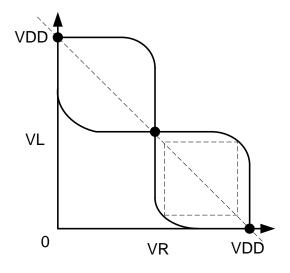

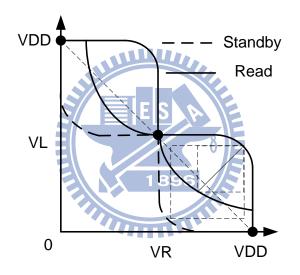

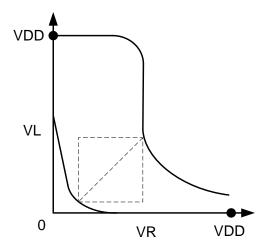

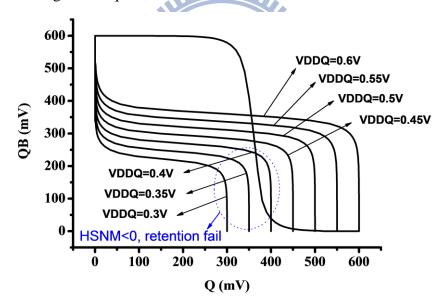

To evaluate the read ability or write ability, the static noise margin is usually a good approach. And static noise margin could be get from the Voltage Transfer Curve (VTC) which we always called as "butterfly curve". For an inverter, as the input voltage arises, the output won't decrease as the increased input voltage (Fig. 2-2). Instead, the output voltage would have a sharp transition at a specific voltage which we always called as trig-voltage of this inverter. (Actually, in definition, the trig-voltage is the input voltage that result the output voltage at half of the supply voltage.). However, to a cross pair latch, the output of one inverter is the input of the other. So we can get another VTC from this relationship but switch the axis. We can overlap these two curves to get a "butterfly-like" curve. Fig2-3 shows the butterfly curve of HSNM or cross coupled pair latch, because the hold mode operation of 6T SRAM is exactly a cross coupled pair latch. In this butterfly curve, we can see it has two "wings". The common used definition of SNM is the largest tolerable square at the either wing and takes the smaller one.

For read operation, both of the pass-gate NMOS are turn-on for accessing data. However, the high voltage level BLs and the turn-on pass-gate will decrease the VTC slope of the inverter of the storage "0" side. But the VTC of the other side remains. As shown in Fig 2-4, the Butterfly curve of read mode is smaller than the read mode, and the largest square in either wing that is the RSNM is smaller than the Hold mode or Standby mode. As mentioned before, there exist the read disturb voltage that decrease the noise margin. So, the minimum RSNM could directly defined as the voltage difference from trig voltage to read disturb voltage. Once the RSNM equals to 0 or less than zero which in other words that there is no any square could locate at each wing, that the destructive read operation occurs and read fail.

Fig 2-5 shows the butterfly curve of write operation. Since one BL would be set at ground and the other BL would be set at high voltage, the butterfly curve would be

wide open and only have one intersect point. This means we can successfully write in a data because we have only one stable point. And these two VTC should be get more farer. By definition, like Read and Hold SNM does, we also fine a largest square in this curve. But rather than find it in wings, we locate a largest square to define how much voltage distance between it which is called WSNM. If the butterfly curve of write mode of 6T cell has no WSNM that means there is more than one interest point, write operation will fail.

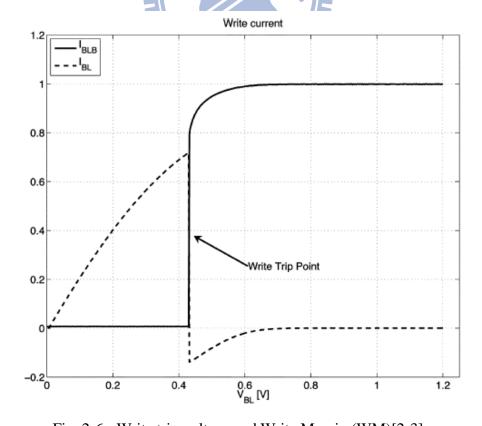

#### 2.2.5Write margin

There is another definition which we called as Write Margin (WM) to evaluate the write performance of write ability rather than WSNM. First we both set the BLs are at high level, and sweep down one BL form VDD to ground. At some BL voltage the cell storage value will be suddenly flip, and the BL voltage at this moment is defined as WM. (Fig.2-6)

Fig. 2-6 Write trip voltage and Write Margin (WM)[2-3]

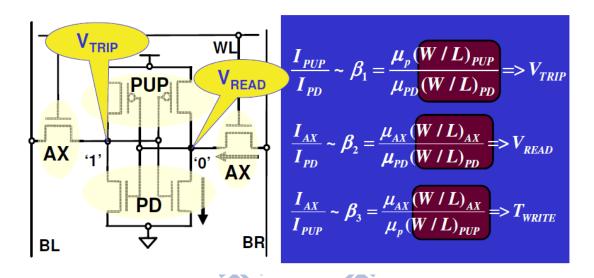

#### 2.2.6The size of 6T SRAM

In order to keep the read stability, the pull-down NMOS should be stronger than the pass-gate NMOS. To maintain the write ability, the pass-gate NMOS should be stronger than pull-up PMOS. However to ensure the stability at standby mode, the pull-up PMOS cannot be too weak compares to pull-down NMOS. As a result, the size of each transistor in 6T SRAM cell is specific designed to maximize the read, hold stability and the write ability.

Fig. 2-7 Transistor size ratio in 6T SRAM

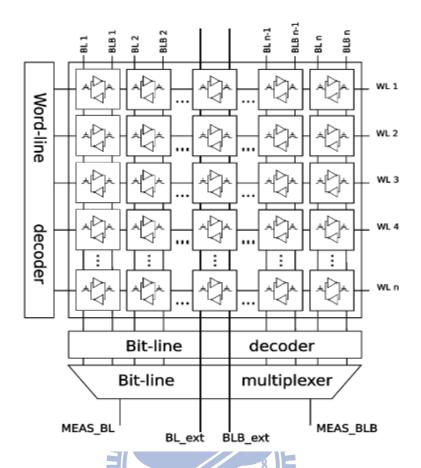

### 2.3 SRAM Array architecture

#### 2.3.1Memory Array and half-select problem

Because we always need a large volume memory, so we have to have a large amount of memory cells. However, these cells are usually formed into an array to save the area and to easy access. Traditionally, all of the SRAM cell are put together which we called SRAM array and the peripheral circuit such as decoder and Sense Amplifier are placed next to the SRAM to control those operation. For a 6T SRAM array, Word-Line (WL) is usually a row direction signal that control pass-gate of all the row direction cells. And Bit-Line (BL) is column direction signal line that could

pass in or out the data. So if we want to select one cell for operation, both the WL and BL must active. The intersect cell is the selected one, and the operation is depend on the BL.

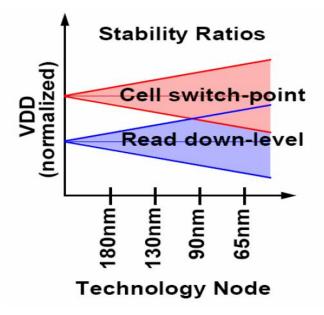

Fig. 2-8 Array architecture of an 2<sup>N</sup>x2<sup>M</sup> memory array[2-1]

However, due to the array formation, there would have the half-selected problem. The most common seem problem to 6T SRAM Array is the half-selected read disturb problem. Since the word-line is row-based, all the pass-gate along this direction would be turn-on even those un-selected cells. The BL of these unselected cells are held at high because there are in hold mode, so all of the half-selected cells are performing the half-selected read operation. But this half-selected problem is

unwanted, because this means all of the other standby cells of this row would suffer disturb that would affect the storage value.

Fig. 2-9 SRAM critical path [2-5]

Fig. 2-10 Half-selected Read Disturb Voltage [2-4]

Fig. 2-11 Stability ratio [2-4]

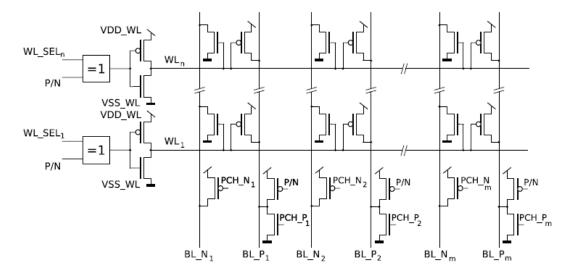

#### 2.3.2Decoder

For a memory, the address pins are usually the input which is used to select the specific cell to read/write data. So the decoder circuit is needed to get the address information. Decoder can be divided into Row Decoder and Column Decoder. Row Decoder (Which is also called X-Decoder or WL Decoder) is used to decode the selected WL. The Column Decoder is used to decode the select column to perform operation.

Fig. 2-12 CMOS Logic Circuits [2-1]

The decoder always composed by simple logics. But the decoding time occupies a not small portion of the overall performance of SRAM, so the decoder must as fast as possible. However, decoder always has a large amount branches because we usually has more than hundred BLs and WLs, loadings of parasitic capacitance usually the main factor that slow down the decoding time. So the solution form architecture is to divide the decoder into the Pre-decoder and decoders. The operation Pre-decoders could be overlap at the last operation cycle to save the time. So the result of the Pre-decoder could be get at the early cycle stage. Once the clock triggered, decoder could process to save time.

Another method to boost the decoding time is to use variety logic family. The most common used logic family is CMOS, but the parasitic capacitance always slow down the speed. Domino or Dynamic logic family could reduce the parasitic capacitance to increase operation speed. And the pre-charge operation of one-side could allow one signal transmission path is almost 0. But the design of these dynamic circuits must be careful to their margin and secondary effect issue such as charge sharing, etc. Pass-Transistor Logic family is also favored in decoder design.

Fig. 2-13 Domino Logics [2-6]

#### 2.3.3Sense scheme and column architecture

Since we have pass the storage value on the BL at read operation, we need to extra circuit to sense whether the storage value is "1" or "0". Basically, there are two kind of sensing scheme: one is differential sensing and the other one is large signal sensing.

Differential sensing or small signal sensing is the traditional sensing scheme. The basic idea of small signal is to sense the voltage difference between BLs than amplify it, so that we can get the logic "0" or "1" from the amplified signal of differential sense amplifier. The traditional differential sense amplifier is a cross-coupled latch with two access transistor that is quite like a 6T SRAM cell. But the size tuning and design issue is different from 6T cell. During read operation, WL is active and the storage value start to pass to the Bit-Line, either BL or BLB will start to go low. Once the voltage difference of BLs reaches a value that differential sense amplifier could operate, then a sense amplifier enable (SAE) signal would be activated to turn on the sense amplifier. Then the low going Bit-Line would be amplified to fully ground voltage and the logic "0" or "1" could be get.

Fig. 2-14 Differential sense amplifier [2-1]

The differential sensing scheme usually adopt with long bit-line structure which means there are many cells along the Bit-line (usually more than hundred cells). Because large number of cells result heavy loading, the storage value fully pass to BLs is a slow process in the long Bit-line structure. The Differential Sense Amplifier is to sense the small difference of BLs, so the use small signal scheme could arise the operation speed greatly.

As the process scales down, however, leakage becomes a crucial issue. Long Bit-line structure first faces the problems because there are large amount devices

along Bit-line. Even the WL is turn off, the large amount leakage current may flip the standby cells that would result retention fail. And the small signal sensing scheme also may fail to sense the data at Bit-line due to the un-neglectable leakage current. So the Bit-Line length must be decreased or adopt the short Bit-line Structure. For the Short Bit-Line scheme, the Bit-Line length is about 8, 16, or 32 cells which is quite smaller than long Bit-Line scheme. Because the lesser cell, the total leakage current could be reduced.

Fig. 2-15 Large signal sensing scheme of IBM Cell processor [2-7]

Rather than adopt the differential sensing scheme, large signal sensing scheme is usually used with short Bit-Line structure. Large signal sensing is directly use one transistor or one inverter to detect the logic signal on the BLs. Once the Bit-line goes lower than the trig voltage of the sensing transistor or sensing inverter, the logic signal would be passed out to the other circuit. And the shorter Bit-Line length reduces the

BL loading, so the signal pass to the BL is faster. Since the large sensing is almost single ended sensing, so the leakage impaction is almost half to the differential sensing scheme where both the Bit-line are connect to the Sense Amplifier. And the implementation of single transistor or inverter is much simple than the Sense Amplifier which is always exhausted time to find the optimized gain. But the short Bit-line structure may have much more area overhead than the long Bit-line structure. Because the long Bit-line structure may only need one Sense Amplifier per each column, short Bit-line structure needs several sensing devices in each column.

#### 2.4 Variation Issue

# 2.4.1 Global variation and Local variation

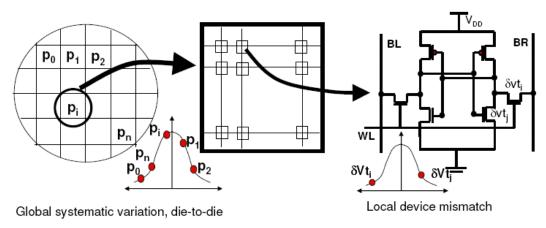

For the real chip implementation, there must exist the variation factor that makes the real outcome device is different from that we the original designed. For CMOS process, these variations can be totally reflected on the threshold voltage  $V_T$ . Since the VT is different from the designed value, the current drive ability of transistors would deviate and the leakage may be larger. These could even result the functional fail or more power consumption. The existence of variation is various. The most common reason are the lithography variation at each process, the dopant number fluctuation, and the line edge roughness, etc. In a deeper sight to view the variation formation, we can separate the variation into the Global and Local. Global variation which is also called the inter-die variation means the variation between die to die. And the Local variation that also called intra-die variation means the variation of transistors at the same die. The total variation to one transistor could be the superposition of Global variation and Local variation. 2-16 shows the case for threshold voltage variation  $(\delta V_t)$ , the variation can be expressed as [8]:

$$\delta V_t = \Delta V_{t-GLOBAL} + \delta V_{t-LOCAL}$$

Fig. 2-16 Global variation and Local variation of threshold voltage [2-6]

The Global variation is also the corner variation. At each time we make the real chip, the lithography, machine settings, temperature, doping concentration would be different. Different die may suffer the different process condition, so the characteristic would vary inter dies. And due to the formation reason, the Global variation is systematic and predictable.

But for the two same transistors in the same die but different location, the dopant number may fluctuate. This would result the VT of transistor with the same size in the same die not the same. This we called local variation. However, the dopant number is random and follows the statistical Gaussian distribution, Local variation is unpredictable and hard to be controlled.

For the current nanometer technology, the channel length is short and the dopant number is a few. Variation becomes a most critical issue at the design phase. Shorter channel length makes the Line Edge Roughness variation become more serious. And a few number dopant let one missing dopant result a large percent dopant concentration change. Random Dopant Fluctuation is almost the main factor of Local variation and become more serious at modern process.

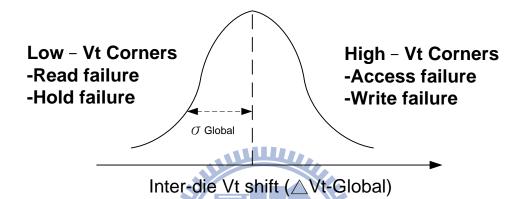

#### 2.4.2 Variation to 6T SRAM

The variation issue also affects the characteristic of 6T SRAM. Due to the condense and compact environment, 6T SRAM cell may suffer much serious variation than logic devices. Both of the Global and Local variation would greatly affect cells

Fig. 2-17 Static Noise Margin definition and the applied noise or variation that makes the SNM equals zero [2-9]

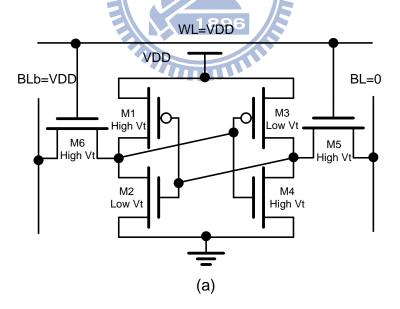

We first discuss the read operation. The Global variation locate at PSNF corner would make the 6T SRAM has the smallest RSNM. At PSNF, the trig voltage of inverter would be lower than normal, so that the noise margin between trig voltage and read disturb voltage would be smaller. However, there would be also the Local variation that is random. The variation of each transistor would be random and independent. From the Fig. we can get that the worst case cell of read operation. High VT M4 and Low VT M5 forms higher read-disturb voltage and High VT M1 and Low VT M2 forms smaller trig voltage of inverter. The existence of Local variation could result a worst case for read.

And for the write operation, the worst case of Global corner is at PFNS corner. Since the pass-gate NMOS is weak, the write trip voltage is much higher than nominal. Consider the Local variation, the worst case cell of write is shown in Fig. Low VT M3 and High VT M5 result higher write trip voltage and High VT M1 and Low VT M2 make a lower trig voltage. So that the WM would be lesser if we both consider these variation issues.

Fig. 2-18 The effect of the inter-die Vt variation [2-8]

Fig. 2-19 The effect of local variation, (a) Write mode worse case, and (b) Read mode worse case

ALLILLY,

## 2.5 Design methodology of modern 6T SRAM

So far we have discuss several critical issue of 6T SRAM such as read-disturb voltage, half selected problem, leakage, variation, and SNM issue, etc. Unfortunately, these critical issues become more serious than before, and the read/write ability of 6T SRAM has greatly degraded. In order to increase the read/write ability, we need extra circuits to improve. In fact, the most common methodology to improve the read/write ability is three: 1) Dual Supply voltage 2) Lower Bit-Line level 3) Negative Bit-Lin. These issues would be discussed below.

#### 2.5.1 **Dual Supply Voltage**

Fig. 2-20 Dual VCC Design of [2-10]

In order to improve the read/write ability, one straight forward concept is to change the supply voltage. If we want to increase the read ability or the noise margin, we could raise the supply voltage of the cell supply or reduce the cell ground voltage to a negative voltage. Or if we want to increase the write ability, we can reduce the supply of the cell. In order to achieve these, the simplest method is to use the second supply voltage directly, so that the supply voltage of cell and logic circuit are separated. However, the implementation of second power supply is expensive. For a general embedded system, the second supply voltage means we have to use another set of power converter, power regulator, and battery, etc. This will greatly increase the cost of chip. So the much practical method is still use single supply, but generates second supply voltage with circuits.

Fig. 2-21 Negative VSS scheme [2-11]

The most common circuit technique of adjusting the voltage is to use the boost

capacitance. By using the capacitance which is previously precharged, we can "add or subtract" amount of voltage on the original voltage. So that, this "pseudo second supply" could achieve almost the same effect of using second supply. For example, we could only boost the cell supply voltage higher during read cycle or boost the GND to a negative voltage to increase the read ability. This implementation is just need to realize capacitance and has precise timing control.

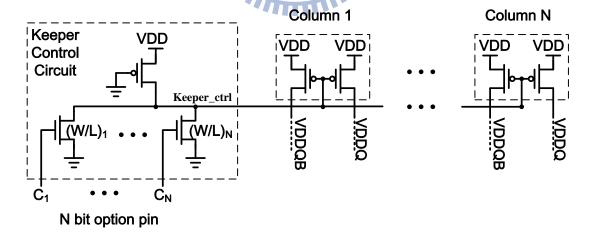

In order to increase the write ability, we would like to reduce the cell supply voltage. But it is difficult to reduce the cell supply voltage with the boost skill. The alternative method is to float cell supply voltage during write. Since the cell power is floating during write cycle, the write ability would increase with the decreasing floating power. Basically the write ability would be greatly improved. However, the floating cell supply would affect the stability of cell and reduce the regenerative process speed of the cross-coupled latch. One compromised method is only floating once side power during write. This could greatly improve the stability and strengthen the regenerative process speed. Another approach is to use keeper. Rather than directly floating supply node, a weak keeper is added to replace the strong power supply. The write ability could also be improved because of the weaker supply. But the keeper size has to be fine tuned to maximize the write ability improvement.

#### 2.5.2 Dynamic Word-Line voltage

Another method is to control the WL voltage. If we raise the WL voltage, the pass-gate would be strengthened. The write ability and read speed would be improved. However, higher WL voltage would increase the read disturb voltage of 6T cell which would decrease the RSNM. More important, all of the cells along the selected WL except of the selected one are performing half-selected read operation. Insufficient RSNM could result a serious retention fail to those half-selected cells.

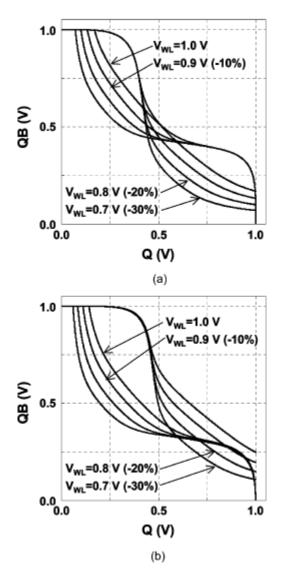

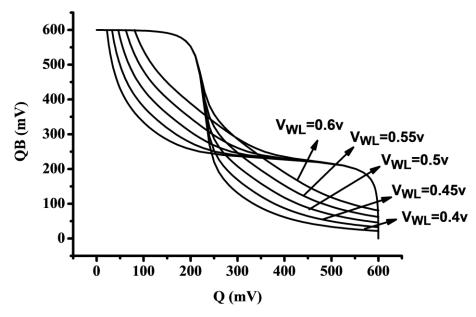

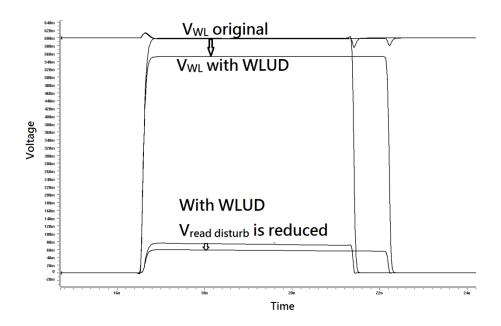

Fig. 2-22 RSNM improvement with lower  $V_{WL}$  (b)WSNM decade with lower  $V_{WL}$ [2-12]

Another direction is to reduce the WL voltage or also called word-line under drive. Although the lower WL voltage weakened the pass-gate and read speed and write ability are weakened. But with this word-line under drive skill, RSNM of all cells are improved. This could at least prevent the destructive read problem of insufficient RSNM. Moreover, we can mix the skill of the dynamic supply skill to improve the read speed and write ability. The mix use of word-line under drive and dynamic supply skill has no contradiction and could improve RSNM, read speed, write ability at the same time. So many benefit could be get by the mix use, we the

word-line under drive has more and more become the main stream.

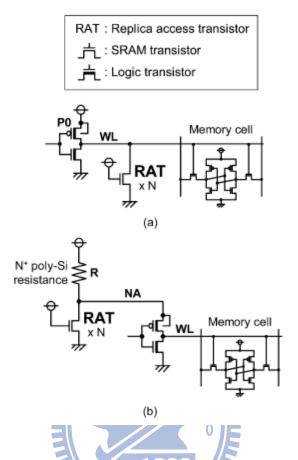

RAT : Replica access transistor

: SRAM transistor

: Logic transistor

Fig. 2-23 Traditional method of word-line under-drive [2-12]

#### 2.5.3 Negative Bit-Line Level

Negative Bit-Line (NBL) is a skill to improve the write ability. The basic idea is to generate a negative voltage on Bit-Line with the boosting skill we mention previously pass into the cell storage node to improve write performance. Much lower voltage could help trigger the cross coupled pair latch to flip its value of cells which have insufficient write margin. And the stability could also maintain if the NBL is used. From many previous works, NBL could greatly improve the write ability and write margin. However, it is necessary to implementation a large capacitance if we want to use NBL skill. A large and good performance capacitance is difficult to get if we use the MOS capacitance. The large area overhead would be a serious problem of NBL. Besides, NBL circuit needs a quite precise timing control to maximize the improvement of write. Basically, the negative voltage should be generated before WL turned on. But the timing is quite hard to be controlled and to be a crucial issue to NBL.

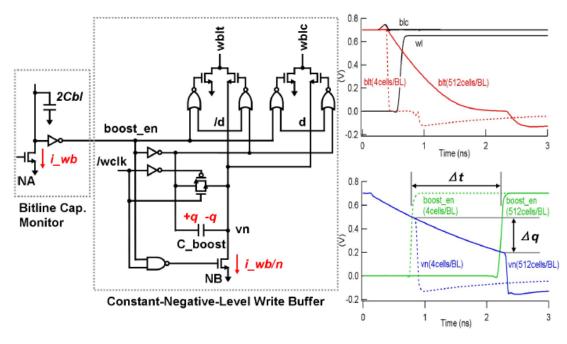

$\Delta q = \Delta t^*i_wb/n = (\Delta Cbl^*Vdd/i_wb)^*(i_wb/n) \propto \Delta Cbl$

Fig. 2-24 Constant Negative Bit-line of [2-13]

# 2.6 Reliability issue and monitoring structure of SRAM

Array

1896

#### 2.6.1 BTI effect

As the supply voltage decrease with the scaled down technology, the Hot Carrier Injection (HCI) has become a minor effect to MOSFET degradation. However, the Bias Temperature Instability (BTI, especially the Negative Bias Temperature Instability, NBTI) rules the major effect that degrades the MOSFET reliability. Several works has done deep investigation to NBTI mechanism and its impact to digital circuits [15]-[22].

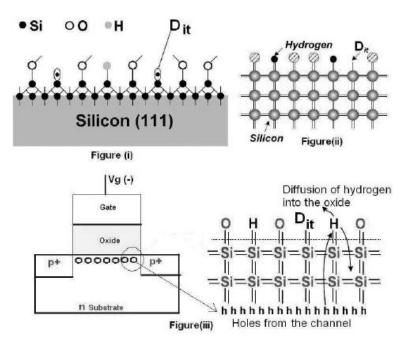

Fig. 2-25 The generation of interface traps a PMOS transistor is biased in

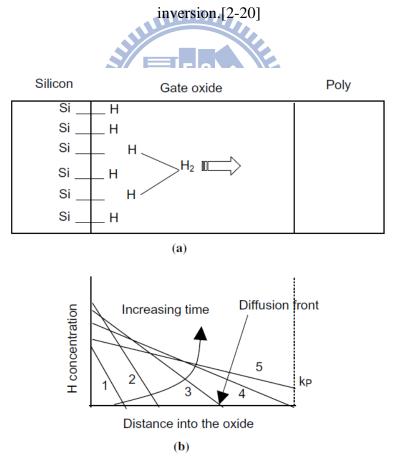

Fig. 2-26 Schematic description of the reaction-diffusion model [2-15]

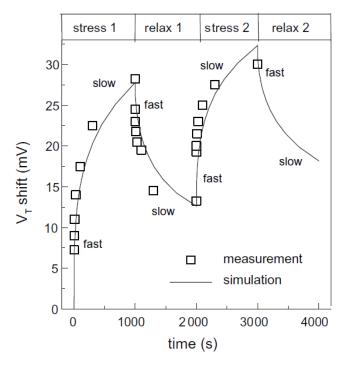

Fig. 2-27 Time dependent effect of stress and relaxation mechanism [2-15]

Several formation mechanism of NBTI is proposed, and the most acceptable one is the Reaction-Diffusion (R-D) model (Fig.2-25 & Fig.2-26). For standard silicon MOSFET process, especially PMOS, there would generate the Si-H bond at the interface between bulk silicon and oxide. Once the PMOS suffers the Negative-Bias, the interface Si-H bond would break and format traps and the formation H<sub>2</sub>, D<sub>it</sub>, etc would diffusion away from the interface of bulk silicon and oxide. As a result, the effective threshold voltage (V<sub>T</sub>) would degrade according this process. This NBTI effect is an time-dependent effect and getting worse especially at high temperature, so we called NB"T"I. Due to the time-dependent characteristic to NBTI, it would result the CMOS Digital Circuit has the finite lifetime. Fortunately, there is a recovery mechanism to NBTI effect only if we induce the positive-bias. Besides, the recovery mechanism is also time-dependent (Fig. 2-27).

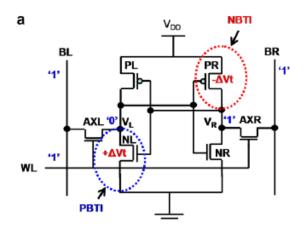

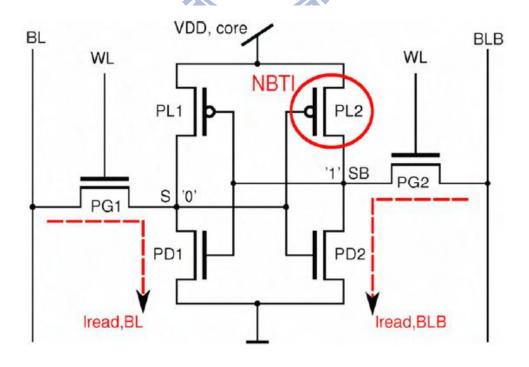

Fig. 2-28 NBTI and PBTI impact to traditional 6T cell

Fig. 2-29 RSNM degradation due to NBTI

NBTI would be also happened to the traditional cell (PBTI would be also happened to High-K metal gate NMOS) (Fig.2-28). Due to NBTI, the absolute  $V_T$  to PMOS becomes larger than nominal value. This could result a lower  $V_{trip}$  voltage to cell inverter. As a result, the RSNM would be getting smaller with time that degrades the read stability to traditional 6T SRAM cell. Due to the half select read problem, the NBTI degradation would be a critical issue that affects the reliability and lifetime to 6T SRAM.

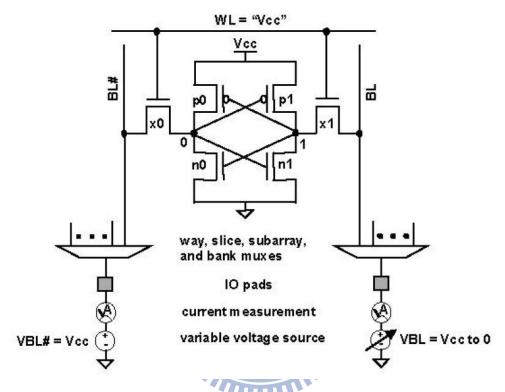

### 2.6.2 Monitoring Structures

Reliability is an important issue as the speed, and power. For electronic devices, the characteristic of transistor would change with time due to some specific physical phenomenon such HCI, NBTI, etc. This would result the performance degradation or

even function fail, and every chips has a finite life time. From a view point of circuit designer, to understand and characterize the formation of degradation and realize the quality and quantity of physical phenomenon is necessary. If designer can get the information about the transistor characteristic and the degradation from the real chip, it would be a great help to understand real physical phenomenon and add some reliability improvement circuit at early design stage.

The simplest and most straight forward way is to build a monitoring structure on chip to get the information what we want. The monitoring circuit could be designed for measure variety characteristics, like statistical distribution and degradation of transistor VT, the NBTI and PBTI degradation to transistor, HCI of transistor, etc. For a SRAM, we could build circuit to measure the SNM or the PBI impaction to SRAM cell. By analyzing the collected data, we can find out the statistical distribution of these parameters. The means value, standard deviation of it could tell us the real information about the real chip.

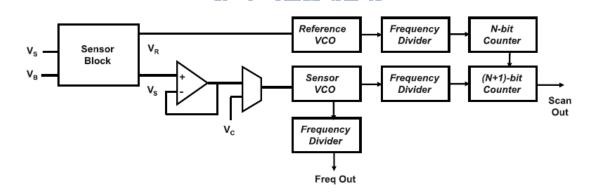

Several types monitoring structure has been proposed to measure different parameters. Some previous work would be noticed in Chapter 4. Besides, An Array Based monitoring structure to measure the static noise margin is proposed and would be discussed in Chapter 4 in this essay. An "Embedded SRAM Ring Oscillator for BTI Measurement" is also proposed at the work [2-23].

# **Chapter 3**

# Design of one 128kb traditional 6T SRAM with Word-line Under-Drive skill and Data-Aware Write Assist skill

#### 3.1 Introduction

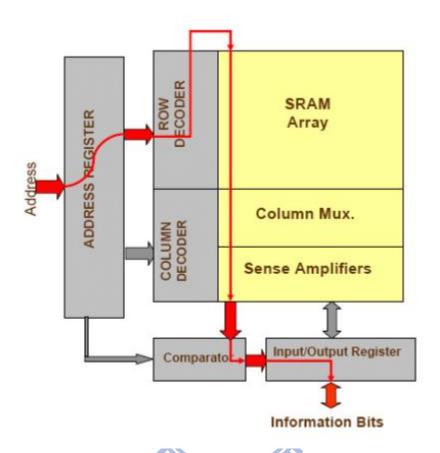

High-performance Static Random Access Memory (SRAM) is one of the most crucial components in processors and SoC. Due to the large transistor counts and areas occupied by embedded SRAM macros in today's systems, the performance of SRAMs dominates the speed, yield, and the power consumption of SoC's. With technology scaling, leakage (subthreshold leakage and gate leakage), variation (systematic global variation and local random variations due to microscopic effects such as Random Dopant Fluctuation (RDF) and Line Edge Roughness (LER)), and long term degradation (e.g. hot carrier effect, and Bias Temperature Instability (BTI)) have become major challenges for SRAM design in deep sub-100nm technologies. Furthermore, as the supply voltage is lowered to reduce power consumption, the variability becomes worse and the design/noise margin deteriorates [3-1~3-2].

For conventional 6T SRAM, The cell stability, Static Noise Margin (SNM), and  $V_{min}$  are limited by leakage, variation, and supply voltage in the physical domain; and

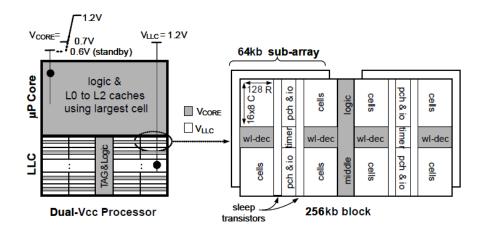

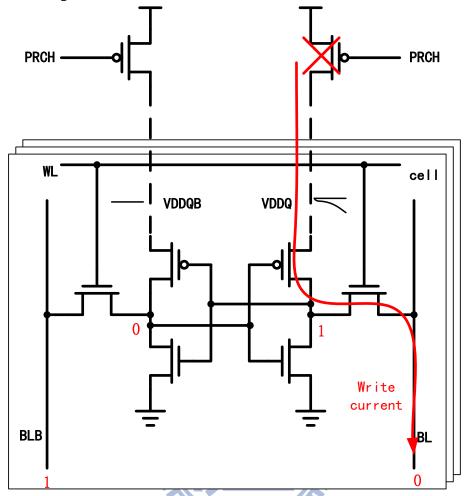

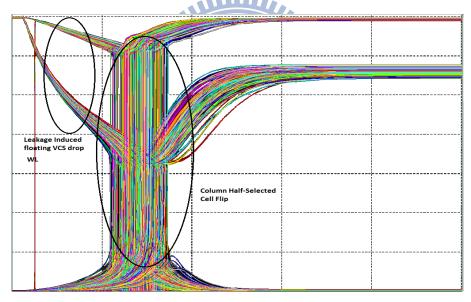

by the conflicting Read/Write requirements and cell disturbs in the design domain. In the design and optimization of 6T SRAM, the procedure typically starts by reducing Read-disturb to maintain adequate RSNM to make sure the cell won't flip during Read operation. Circuit techniques such as "unclamped" or "weakly-clamped" Local Bit-Lines (LBL) where all LBL's are released ("unclamped" or "wealy clamped" by a diode drop) in active mode have been widely adopted to reduce Half-Select disturb. In high-end systems which can afford dual supply, higher supply voltage (VCS) can be used for cell array to enhance cell stability and Read performance, while BL is precharged to the lower (VDD) supply to reduce Read/Half-Select disturb. For cost-performance applications and portable/ handheld devices where the cost, form factor, and weight considerations dictate the use of single supply, scheme such as Word-Line Under-Drive (WLUD) ( also called Suppressed Word-Line (SWL)) can be employed to mitigate Read disturb and Half-Select disturb[3-4]~[3-10]. Notice that the WLUD scheme is essentially a "Poor Man's Dual Supply" scheme to generate a lower supply level. With WLUD, the Read performance and Write-ability degrade. The Read performance can be recovered by circuit techniques such as transient negative cell VGND [3-12]. The Write-ability, Write Margin (WM), and Write performance are typically recovered/enhanced by Floating power-line Write (where the cell supply is left floating during Write) [3-15]~[3-20], dynamic Read/Write supply (where the cell supply is lowered during Write), or Negative Bit-Line (NBL, where the low-going BL is transiently pulled down below GND during Write) techniques [3-11]~[3-14].

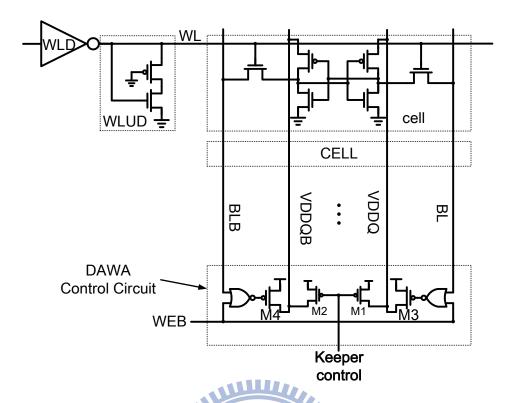

In this work, we proposed a variation-tolerant Word-Line Under-Drive (WLUD) circuit technique to improve the RSNM. Each word-line has one WLUD circuit and the level of the selected word-line is lowered. Our WLUD circuit comprises of one PMOS which tracks the WL driver pull-up PMOS, and one NMOS which tracks the

cell access NMOS. This resistor-less implementation reduces the area overhead, and eliminates the variation due to the sheet resistance variation of the resistor which can easily be  $\pm 30\%$  in sub-100nm technologies [3-11]~[3-16].

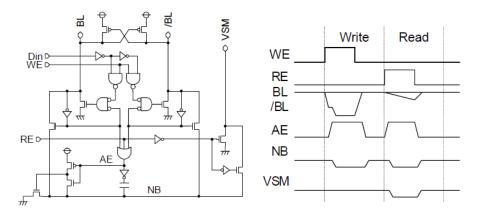

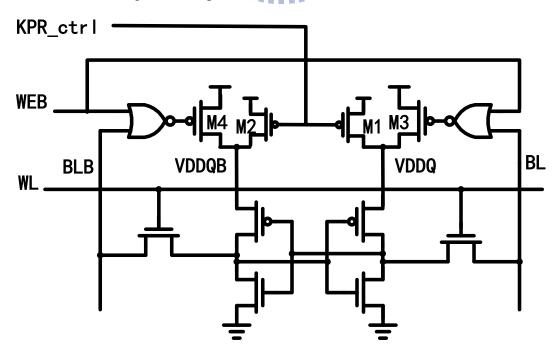

The proposed WLUD scheme provides excellent tracking capability across process corners. The Write-ability and Write performance are enhanced by a novel variation-tolerant Data-Aware Write-Assist (DAWA) scheme where the virtual cell supply nodes for the left- and right-half cells on a column are control by separate power-switch/keeper pairs. The power-switch on the low-going BL side for the selected column is turned off to allow the corresponding virtual supply node voltage to go down to enhance Write-ability, Write Margin, and Write performance. The keeper remains "On" to maintain a proper (low) virtual cell supply level, thus ensuring adequate Hold SNM for half-selected cells on the selected column. Switching only the half-cell virtual supply improves the supply switching speed and reduces the switching power/noise by half. The scheme also offers fast WL rise time as the WL drivers is driven by full VDD [3-4], and die-to-die programming capability can be easily implemented if desired. The power-switch control logic is simple, and thus requires much smaller area overhead compared with Negative Bit-Line (NBL) Write-assist scheme which requires large boosting capacitor and more complicated timing control [3-4][3-17]~[3-20]. The half-cell virtual supply switching is controlled/initiated by the low-going BL during Write operation, thus tolerant to PVT variation and V<sub>T</sub> scatter. The DAWA scheme adds minimum loading to the BL (only 1 C<sub>gate</sub> per BL), hence no degradation to the BL sensing speed. Implemented in a 55nm 128Kb 6T SRAM, the WLUD and DAWA schemes together require 18% area overhead compared with the base 6T SRAM design. The chip can operate across wide voltage range from 1.2V to 0.6V, with operating frequency of 940MHz@1.0V and 25°C.

#### 3.2 Concept of word-line under-drive

Just as said previously, word-line under-drive could increase the RSNM of 6T SRAM cells. Due to every half-selected cells along row direction are performing a read operation once some word-line is activated, the increase of read stability could do great help to resist the variations which could result function fail. The detail of how the word-line under-drive skill increase the RSNM we will be discussed later. Many previous works has proposed to achieve the requirement of word-line under-drive, however, they always has some drawbacks when implementation. We propose a simple word-line under-drive circuit which uses full CMOS transistor. And the proposed circuit has better corner tracking ability and previous works.

# 3.3 Previous work of word-line under-drive

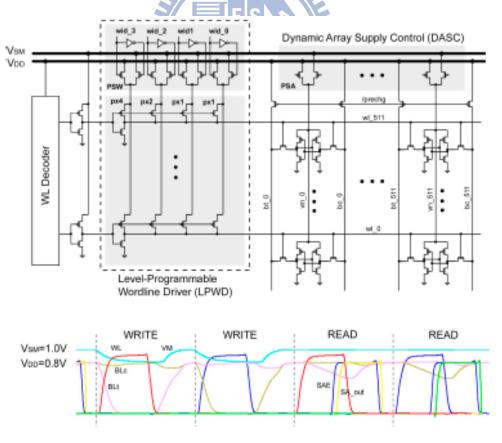

Fig. 3-1 "Level Programmable Word-Line Driver and Dynamic Array Supply Control in Dual-Supply SRAM scheme [3-13]"

Fig. 3-1 shows previous work of "Level Programmable Word-Line Driver and Dynamic Array Supply Control in Dual-Supply SRAM scheme". In this scheme, VSM is higher than VDD, so the programmable word-line level would determined by the ratio of PMOS of VSM and PMOS VDD. And we can either switch cell supply higher to improve read or switch cell supply lower to improve write. But this method needs dual supply which is an expensive cost when realization. And there is nothing mechanism to prevent the process variation.

Fig. 3-2 Adaptive Word-Line Under-Drive (WLUD) Scheme

Fig. 3-2 shows the "Adaptive Word-Line Under-Drive Scheme" method. This scheme eliminates the high cost of dual supply. By controlling the gate voltage of PMOS, word-line level would be separated into two levels. But this implementation is quite complicate and needs a lot of extra component such as operational amplifier (OPA). The area cost of this scheme is considerable. The much practical implementation method to under drive the word-line level is the Read-Assist Circuit

(RAC) in [3-14].

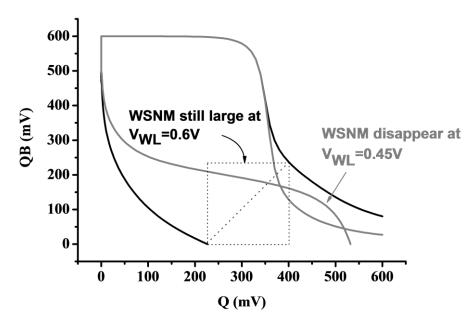

Fig. 3-3 Conventional version (b) resistor added version

Fig. 3-3 [3-16] shows two version of this simple word-line under drive circuits. Both of these two are single supply design. Fig.3-3 (a) is the conventional version and only use single transistor. One NMOS is used with drain connect to the word-line and gate connect to the supply. This allows the word-line voltage to be lower when word-line is active by the forming divide voltage between P0 and RAT NMOS. This implementation is quite simple and even without other control signal. The RAT NMOS can track the pass-gate NMOS to adjust the word-line level around corners.

Fig. 3-4 Simulated word-line voltage of Fig. 3-3

But as shows in Fig. 3-4, this single NMOS implementation encounters large temperate variations. Especially at NFPS corner, we can see that from Fig. 3-4 that the word-line voltage drops to a quite low level. In order to fix this, previous work of Fig. 3-3 (a) is proposed to fix temperature variation. Fig. 3-3 (b) shows the circuits of the resistor added implementation. Rather than directly connect to the word-line, this method controls the supply by using resistor and NMOS to form divide voltage.

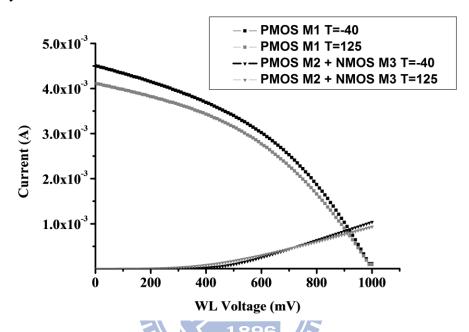

Fig. 3-5 The I-V curve of two RACs, and shows the temperature dependence

From the I-V curve shows in Fig. 3-5, we can get that this implementation could reduce the temperature dependence due to the current-voltage relationship of resistor is stable to temperature. Fig. 3-4 also shows this method could achieve stable word-line level around temperature. However there exists the resistor variation that would lead the variation to the divided voltage. And the result word-line level would also suffer this fluctuation. Besides, the decrease of the word-line driver supply would decrease the rising time of word-line activation. This could lead the performance degradation.

Fig. 3-6 Single-Supply WLUD using Replica Discharging Transistor

Fig. 3-6 [3-4] shows another word-line under-drive scheme proposed from Toshiba. A simple PMOS and resistor is series connected to the WL. And the PMOS is used to track the PU and the POLY resistor is used to suppress the temperature variation. From the simulation result of this work, we can see that the WL rising time

has great improvement than the previous works. And the WL level variation could be suppressed at certain level. However, the resistor may have variation that will cause extra deviation to the WL voltage.

#### 3.4 Proposed word-line under-drive skill

# 3.4.1RSNM improvement and WM decrease with word-line under-drive

Fig. 3-7 Standard 6T SRAM in Read Mode

For a 6T SRAM cell shown in Fig.3-7, a read disturb voltage would be generated at the storage node once the word-line is turn-on for read. This read disturb voltage would decrease the noise margin of cell during read and even result a destructive read failure if the read static noise margin is smaller than zero. According to the architecture of memory array, if one column is selected to do read/write operation, the other half selected cells in the row direction is performing a read operation. Those half-selected cells may fail to retain its storage value due to this disturbed read. With the unsystematic local variation, the RSNM of cells may degrade more, and the half-selected problem would become more seriously. As a result, we have to have

higher priority to fix this read failure than write failure if we want to achieve higher yield chip.

The simplest method to alleviate this read failure is to reduce the read disturb voltage. This read disturb voltage can be seem as the divided voltage between pass-gate (M3) and pull-down NMOS (M2), and we can decrease the read disturb voltage by decreasing the current drive ability of pass-gate (M3). As a result, the lower current drive ability is similar to a larger resistance which will force the divided voltage smaller. Fig.3-8 shows the RSNM increase with the low-going WL voltage.

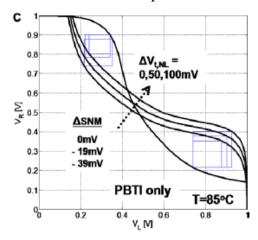

Fig. 3-8 RSNM increase with word-line voltage decrease

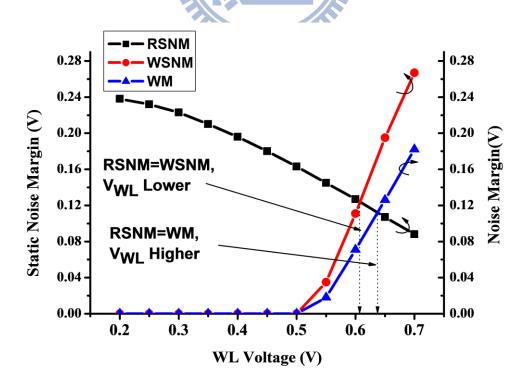

However, word-line under-drive increases the RSNM but reduce the write ability. Because the current drive ability of pass-gate is weakened, cell will become harder to pull the storage node into another state. As shown in Fig.3-9, WSNM reduces with WL decrease. Once the WL drop to a certain value, the butterfly curve of cell no longer has only one root. More than one root of butterfly curve means the cell will write fail. So, we must keep certain write ability when we increase RSNM with word-line under-drive.

Besides, the weaker strength of pass-gate will also degrade the read speed. The

chosen of WL voltage is an important issue.

Fig. 3-9 WSNM decrease with word-line voltage decrease

#### 3.4.2Prior-art comparison

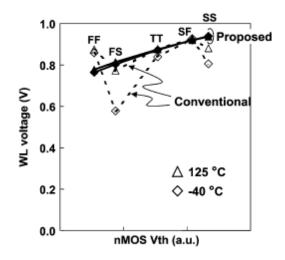

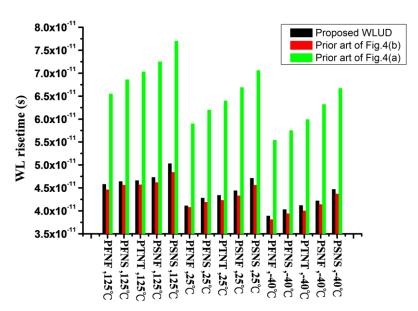

Fig. 3-10(a) [3-17] shows a further improved version utilizes the tracking NMOS and series feedback resistor to control the virtual supply node of the WL driver. Notice that in Fig. 3-10(a), the virtual supply node of the WL driver taps the poly-resistor somewhere in the middle to minimum the sensitivity of WL level to poly sheet-resistance variation, which can be easily ±30% in deep sub-100nm technology. However, due to the presence of resistor in the virtual supply path and the lowered virtual supply for the WL driver, the scheme suffers severe degradation of WL rise time. Another scheme, depicted in Fig. 3-10(b), uses PMOS and series feedback resistor to lower the WL level [4]. This method could prevent the degradation of WL rise time and provide a stable WL level across process corners and temperature, but still suffers from the poly sheet-resistance variation and the large area needed to implement the resistor.

Fig. 3-10 Prior art of word-line under-drive circuits

Fig. 3-10(c) shows the simulated WL levels of the schemes in Fig. 3-10(a) and 3-10(b). The scheme of Fig. 3-10(a) exhibits larger temperature dependence, especially at high temperature. At high-T and PFNF corner, the WL voltage drops significantly more than other cases due to the large temperature dependence of NMOS.

The scheme of Fig. 3-10(b) has smaller temperature dependence, yet exhibits large corner-to-corner variations. Moreover, the level control deteriorates significantly when poly sheet-resistance variation is taken into account. Finally, the scheme in Fig. 3-10(a) only tracks the cell access NMOS, and that in Fig. 3-10(b) only tracks the WL driver pull-up PMOS. As such, they do not fully track the corner variations, and the WL level is not optimally adjusted across process corners.

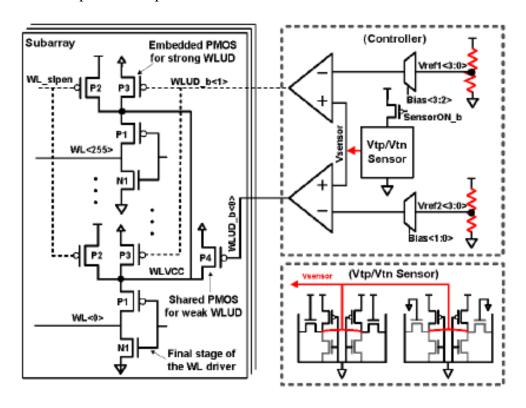

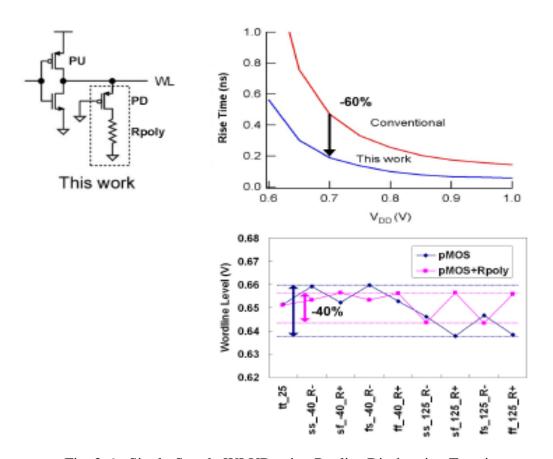

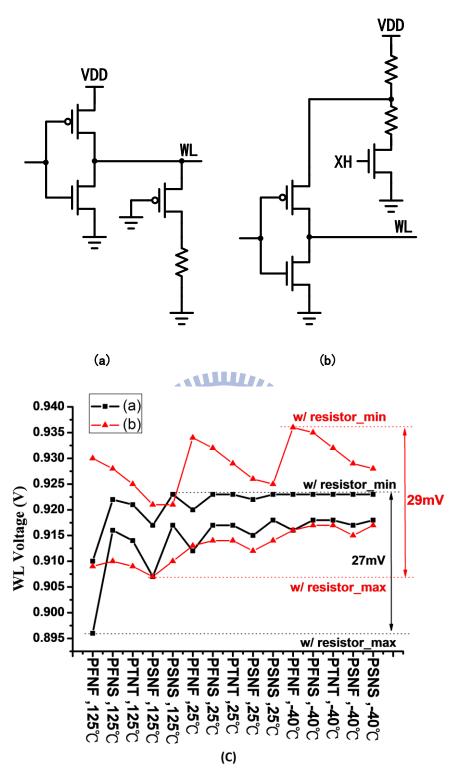

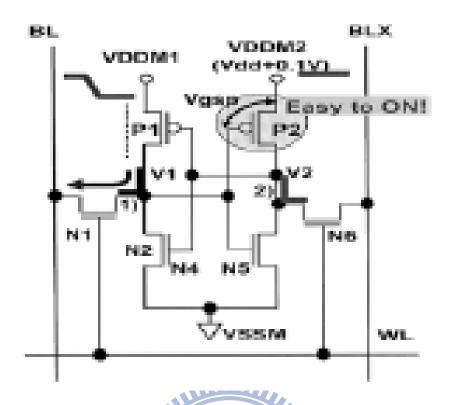

#### 3.4.3Proposed Word-Line Under Drive (WLUD) Scheme

Fig. 3-11 Proposed word-line under-drive circuit

Fig. 3-11 (a) shows the schematic of the proposed word-line under-drive (WLUD) circuit. One NMOS (M3) and one PMOS (M2) form a series connection. The gate of M3 is connected to the word-line and the gate of M2 is connected to ground. M3 is

turn on when the word-line voltage goes high, so the WLUD circuit is activated only when the word-line is selected. PMOS M2 tracks WL driver pull-up PMOS M1, while NMOS M3 tracks the cell access NMOS (M3/M6 in Fig. 3-7). In essence, PMOS M2 serves as the feedback "resistor" for NMOS M3, and NMOS M3 serves as the feedback "resistor" for PMOS M2. This resistor-less feedback for WL discharging circuit mitigates the WL level sensitivity to process corners and temperature, eliminates sensitivity to poly sheet-resistance variation, and can be easily implemented with minimum device/area overhead. The scheme also offers fast WL rise time, as the WL driver is driven by full VDD, and the WL is pulled up by PMOS M1 with no resistor in the pull-up path. Notice that as the WL voltage goes low, the channel resistance of M3 increases and the current through M3 decreases. This helps to stabilize the WL voltage at a certain level. The tracking of both cell access NMOS and WL driver pull-up PMOS offers the capability to optimally place/adjust WL level across process corners. For example, at PSNF corner, if there is no M2 to track M1 (i.e. if M2 is replaced by a poly-resistor), the WL level would be pulled-down too low by the strong NMOS. With M2, to track M1, the channel resistance of M2 increases and its current decreases, thus limiting the WL pull-down current to maintain a proper WL level, Similarly, at PFNS corner, the slow NMOS M3 allows the WL level to stay higher, thus compensating for the slow (weak) cell access NMOS. Notice that the WL driver pull-up PMOS M1 works at triode (linear) region, and M2-M3 forms a diode like I-V characteristics (Fig. 3-12). The diode like I-V curve of M2-M3 intersects the PMOS M1 I-V curve in triode (linear) region where the transistors behave like resistors and have small temperature sensitivity. As a result, the resulting WL level has small sensitivity to temperature.

As illustrated in Fig. 3-11(b), the gate of PMOS M2 can be connected to the input of the WL driver. Functionally, it is the same as that in Fig. 3-11(a), with the

difference in the layout and possibly area overhead. Fig. 3-11(c) depicts another scheme where the discharging NMOS M3 is shared among WL drivers to further reduce device and area overhead. Notice that the gate of the shared discharging NMOS can be connected to a "Control Voltage" to offer Die-to-Die programming capability.

Fig. 3-12 I-V<sub>WL</sub> curve of proposed WLUD circuit

Fig. 3-13  $\,V_{WL}$  comparison across process corners with different temperature of the proposed WLUD circuit.

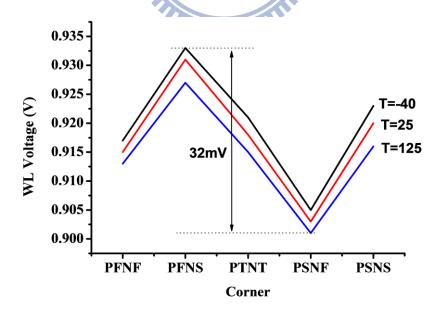

Fig. 3-13 shows the simulated WL voltage level for the proposed scheme. We can see that the proposed WLUD circuit results in about 32mV variation across process corners and temperature. The temperature sensitivity is very small due to the dual-tracking capability and the triode-operated resistor-like device behavior discussed above. Furthermore, the WL level is optimally adjusted/placed across process corners. For example, the WL level is the highest at PFNS corner (which would compensate for the slow cell access NMOS), and the lowest at PSNF corner (which would compensate for the fast cell access NMOS). The scheme also reduces/confines the WL level difference between PFNF and PSNF corners. Fig. 3-14 compares the WL rise time for the schemes in Fig. 3-10(a),(b), and the proposed scheme in Fig. 3-11(a) across various process corners at different temperature. The scheme in Fig. 3-10(a) can be seen to have slow WL rise time, as the WL driver is driven by a lower voltage, and poly-resistor is present in the WL virtual supply path. Our proposed scheme and the scheme in Fig. 3-11(b) have significantly better WL rise times than that in Fig. 3-11(a) as the WL driver is driven by full VDD and there is no resistor in the WL pull-up path.

Fig. 3-14 Word-line rising time comparison of this work and prior art.

#### 3.4.4The chosen of WL voltage

With WLUD, the RSNM improves while WSNM degrades as shown in Fig. 9. If we choose the  $V_{WL\_WLUD'}$  which makes WSNM equals RSNM, we can strike to a balance point that read/write margin are equal. However, this  $V_{WL\_WLUD'}$  is lower and the read performance and write ability suffers more. In our methodology, we choose the WL voltage level  $V_{WL\_WLUD2}$  where the RSNM equals to WM as Write-assist can be applied to improve the Write-ability, WSNM, WM, and Write performance. This  $V_{WL\_WLUD}$  is higher than  $V_{WL\_WLUD'}$  to prevent read performance and write-ability degrades too much. The WL voltage level  $V_{WL\_WLUD}$  is chosen based on PSNF corner, which needs the most RSNM improvement and thus the lowest WL level among all corners. The WL levels of other corners would be higher to prevent too much Write-ability degradation, especially at PFNS corner which has the worst Write-ability.

Fig. 3-15 RSNM and WM versus WL voltage level.

# 3.5 Previous work of write ability improvement

As the technology node goes to nanometer scale, write performance has become a critical issue. Especially with the supply voltage is reduced, write ability and write margin (WM) of traditional 6T-SRAM face a severely degradation. There are several ways to improve write ability: 1) Higher WL voltage, 2) Negative Bit Line (NBL), 3) Lower cell supply. Higher WL voltage could help write ability because the word-line voltage is arisen higher that makes the pass-gate stronger. But this would let the half-select disturb problem more serious because other cells in the row direction are performing half-selected read operation. Since the RSNM is reduced due to the higher word-line voltage, these half-selected cells may loss their storage value. [3-3] Negative Bit Line (NBL) skill is to pass a negative voltage in to cell rather than a ground voltage during write operation. This could improve write ability without losing noise margin. However, negative voltage is hard to pass into the cell and a large capacitor is always needed to maximize the coupling ability. But the implementation of large capacitor cost lots of area. [3-10]~[3-14] Besides, the timing of capacitor boosting mechanism should be precisely controlled. This timing control issue makes the NBL design much harder. Another good method to improve write ability is the lower cell supply write.

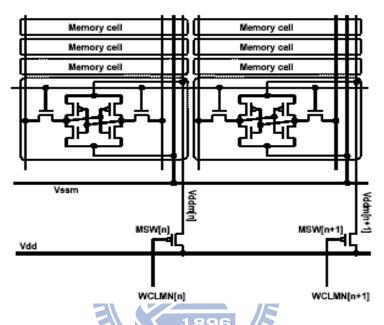

Fig. 3-16 Column based dynamic  $V_{CC}$ .

Lower cell supply is another direction to improve write ability. Fig. 3-16 shows a traditional method with column based dynamic  $V_{CC}$ . The  $V_{CC}$  would be switch to the lower one during read cycle. However, two supplies are needed in this implementation, and the power switching of whole chip is a slow process.

Fig. 3-17 Floating Power Line Write

Rather than directly use the second power, Floating Power Line Write demonstrates another idea to improve the write ability. Because the power line is floating during the write cycle, the floating power line will continuous go low due to the write current. This means the write margin would increase with the low going supply voltage. And column direction switch could prevent large carrier movement that cause the slow switching time. But this scheme floats the both side power line of cell. This would degrade the latch regenerate process which could result slow settle time. And the floating drop too low would degrade the SNM, cause the stability problem of other column direction half-selected cells.

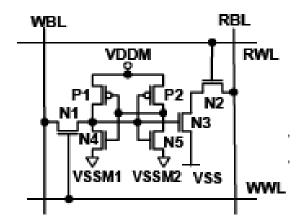

Fig. 3-18 Differential Data-Aware V<sub>DD</sub> scheme

Fig. 3-18 shows the differential Data-Aware  $V_{DD}$  circuit. This scheme only weaken the power of write "0" side with a diode drop. The power line of the opposite half cell is kept to enhance the latch regenerative effect. And the SNM has a better improvement than previous work. But the diode drop limit the granularity of supply tuning with poor level-setting capability. The SNM of column direction half-selected cells is still degraded.

Fig. 3-19 Differential Data-Aware  $V_{SS}$  scheme

Besides, we can also control the  $V_{SS}$  with the data-aware scheme rather than control the  $V_{DD.}$  (As shown in Fig. 3-19)

Fig. 3-20 Differential Data-Aware Power-supplied (D2AP) 8T cell

The column control of power line could result the SNM problem of those column half-selected cells, the Differential Data-Aware Power-supplied (D2AP) 8T cell directly add 2 transistors into original 6T cell to control the power with the Data-Aware scheme. But extra 2 transistors of each cell add extra area and performance overhead. Cell supply for unselected rows cut-off during read/write still degrades the SNM. BL suffer 2 time pass-gate loading that would degrade the sensing margin, performance, and density.

#### 3.6 Data-Aware Write Assist circuit

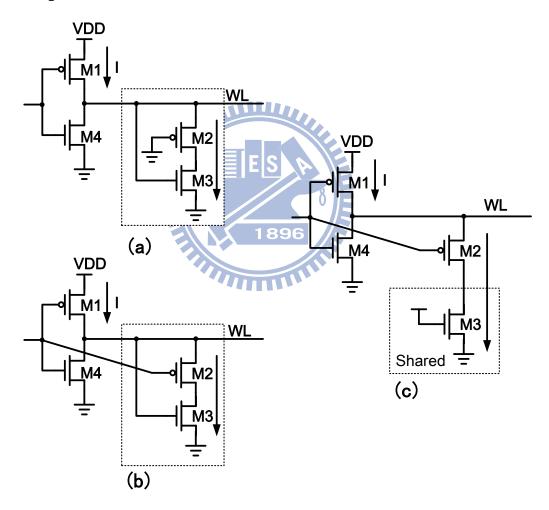

# 3.6.1 Proposed Data-Aware Write-Assist Circuits

Fig. 3-21 Proposed word-line under-drive scheme

Fig. 3-22 Proposed word-line under-drive circuit