# 國立交通大學

電子工程學系電子研究所

博士論文

以電流模式操作之低功率和高速率的靜態隨機 存取記憶體

Low Power and High Speed SRAM with Current-Mode Techniques

研究生:王上銘

指導教授 : 吳 慶 源 博士

中華民國九十三年六月

## 以電流模式操作之低功率和高速率的靜態隨機 存取記憶體

# Low Power and High Speed SRAM with Current-Mode Techniques

研究生: 王上銘 Student: Shang-Ming Wang

指導教授: 吳 慶 源 博士 Advisor: Dr. Ching-Yuan Wu

#### A Thesis

Submitted to Institute of Electronics

College of Electrical Engineering and Computer Science

National Chiao-Tung University

in Partial Fulfillment of the Requirements

for the Degree of

Doctor of Philosophy

in

Electronic Engineering

June 2004

Hsinchu, Taiwan, Republic of China

中華民國九十三年六月

# 以電流模式操作之低功率和高速率的 隨機靜態存取記憶體

學 生: 王上銘 指導教授: 吳慶源

#### 國立交通大學電子研究所

#### 摘要

本論文主要針對低功率消耗的靜態隨機存取記憶體的設計與分析。靜態隨機 存取記憶體的存取路徑可分為三部分:一為寫入路徑,從位元址輸入到列位元線 端;另一為讀取路徑,從列位元線到資料輸出端;最後為記憶細胞元。

藍達雙極性電晶體是利用金氧半場效電晶體與其寄生的雙極性電晶體所合成的一種電壓控制負微分電阻電晶體,可應用於記憶的元件。本文提出新的藍達 雙極性電晶體結構,並以簡單的電路模式與元件物理來探討其工作原理。利用所 提的藍達雙極性電晶體,設計完成新型單邊讀寫記憶細胞元。

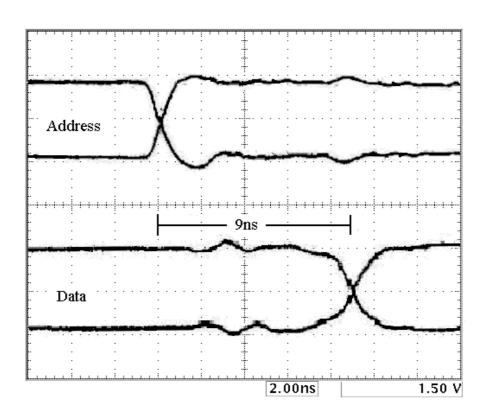

設計一個低功率且高效能的靜態隨機存取記憶體,常常著重於減少工作時的 工率及被用狀態的直流電流與漏電流。為減少讀寫操作時所消耗的功率,我們提 出電流模式讀寫操作的機制以取代傳統的電壓模式。本論文提出電流模式操作感 測放大器,當位元線的電壓僅需少許的變化,此感測放大器便能順利的讀取,並 且能降低雜訊。另外,提出以電流模式操作的寫入驅動器,其寫入時僅需將位元 線的電壓作少許的變化,不僅可降低功率的消耗並可加速寫入的動作。利用電流 模式的讀寫技術,讀取速度與寫入的脈衝寬度幾乎與位元線和資料元線的電容負 載無關。根據此電流模式,提出一個可操作於高速低功率的細胞元。此細胞元的 存取電晶體和反向器電晶體的尺寸幾乎相同,並可經由位元線的微小電壓差而驅 動。 為評估此電流模式技術,使用 0.35 微米一層複晶矽兩層金屬製程,製作一個 32Kx8 的靜態隨機存取記憶體。此記憶體在 3 伏特供壓下其存取時間為 9 奈秒,動態電流在 100 百萬赫茲頻率工作時為 28 毫安培。

# Low Power and High Speed SRAM with Current-Mode Techniques

Student: Shang-Ming Wang Advisor: Dr. Ching-Yuan Wu

Institute of Electronics

National Chiao-Tung University

#### **Abstracts**

This thesis explores the design and analysis of Static Random Access Memories (SRAMs) and focuses on low power operation. The SRAM access path is split into three portions: from address input to word line rise (the write operation), from word line rise to data output (the read path) and memory cell. The techniques to optimize both of these paths are investigated.

The voltage-controlled negative-differential-resistance device by using a merged integrated circuit of n-channel MOSFET and parasitic NPN bipolar transistor, called Lambda bipolar transistor (LBT), is known for its memory application. In this thesis, a new LBT structure is developed and its characteristics are derived by simple circuit model and device physics. A novel single-sided memory cell based on the proposed LBT's is presented.

High performance and low power SRAM design always focuses on reducing dynamic power dissipation at the operating state and decreasing DC current and leakage current at the standby state. To reduce operation

power without decreasing read/write speed, we propose special current-mode read/write mechanism instead of conventional voltage-mode circuits. In this thesis, a new current-mode sense amplifier is proposed to sense the bit-line signal even though the voltage swing of the bit-line is small, and the non-floating design reduces noise produced during sensing in the standby mode. The current-mode write driver can reduce the bit-line swing when data write in, not only decreasing power consumption but also speeding up writing access time. Using new current-mode techniques for read and write operation, the sensing speed and write pulse width are insensitive to the bit-line and data-line capacitances and a separated positive feedback technique is used to enable the circuit to operate at high-speed and low-power. These techniques always keep the voltage swing of the bit-line and data-line quite small. Based on current-mode operation, a memory cell that operates at low-power current-mode is developed. The memory cell has almost equally sized access and inverter transistors, which can be toggled using a small differential bit-line voltage.

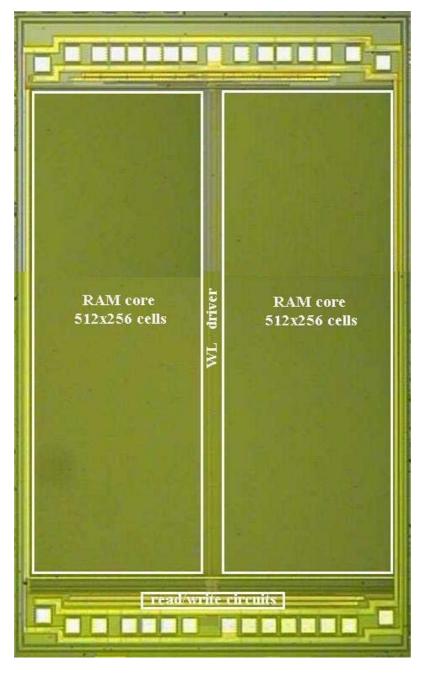

The presented techniques were demonstrated to be useful by evaluating an experimental 32Kx8 SRAM chip using 0.35um 1P2M CMOS process technology. An experimental 32Kx8 CMOS SRAM with a 9ns access time at a supply voltage of 3V is described to evaluate the new current-mode techniques. The active current is 28mA at 100MHz and 25°C.

#### Acknowledgements

I thank my advisor Prof. Ching-Yuan Wu for his invaluable guidance throughout the course of this thesis. His insights and wisdom have been a great source of inspiration for this work. He not only encourages me to pursue this degree but also provides me the best research environment with generous support. Special thanks are given to Silicon-Based Technology Corp. for financial support, especially chip implementation.

Thanks to my many friends on campus and outside, I have had many memorable moments outside my work. I would especially like to thank Prof. Bill Tai and the members of Silicon-Based Technology Corp.

Furthermore, I would like to thank the members of the Advanced Semiconductor Device Lab. for their valuable suggestions, interesting discussions, and their friendship.

I am grateful to my sisters and brother for being such a wonderful family. I thank my wife, Hsiao-Mei, for her love and patience during the final stages of my dissertation. Last but not the least, I am eternally indebted to by my parents for their love, encouragement and support. This dissertation is dedicated to them.

## **Contents**

| Abstract(Chinese)                                | 1    |

|--------------------------------------------------|------|

| Abstract(English)                                | iii  |

| Acknowledgments                                  | v    |

| Contents                                         | vi   |

| Figure Captions                                  | viii |

| Table Captions                                   | xi   |

| Chapter 1 Introduction                           | 1    |

| Chapter 2 Overview of CMOS SRAM                  | 6    |

| 2.1 SRAM Partitioning                            | 6    |

| 2.2 Circuit Techniques in SRAMs                  | 8    |

| Chapter 3 Lambda Bipolar Transistor Memory Cell  | 16   |

| 3.1 New Lambda Bipolar Transistor                | 18   |

| 3.2 Description of New Memory Cell               | 23   |

| 3.3 Performance of New Memory Cell               | 28   |

| 3.3.1 Write Operation                            | 28   |

| 3.3.2 Read Operation                             | 29   |

| 3.3.3 Comparisons                                | 31   |

| Chapter 4 New Current-Mode Sense Amplifier       | 33   |

| 4.1 Introduction                                 | 33   |

| 4.2 Voltage Sensing and Current Sensing          | 35   |

| 4.2.1 Theoretical Model                          | 35   |

| 4.2.2 Voltage-Mode and Current-Mode Signal Delay | 38   |

| 4.3 Voltage-Mode Sense Amplifier                 | 43   |

| 4.4 Clamped Bit-Line Sense Amplifier             | 45   |

| 4.5 New Current-Mode Sense Amplifier             | 48   |

| 4.5.1 Circuit Description and Operation          | 48   |

| 4.5.2 Simulation Results                         | 52   |

| Chapter 5 New Current-Mode Write Driver          | 57   |

| 5.1 Conventional Voltage Writing Mechanism       | 58   |

| 5.2 Current Writing with Equalization Transistor      | 59   |

|-------------------------------------------------------|------|

| 5.3 New Current Writing Mechanism                     | 62   |

| 5.3.1 Current-Mode Write Driver                       | . 62 |

| 5.3.2 New Memory Cell for Current-Mode Operation      | 64   |

| 5.3.3 Simulation Results and Comparisons              | 66   |

| Chapter 6 Low Power and High Speed SRAM               | 69   |

| 6.1 Low Power SRAM Architecture                       | . 69 |

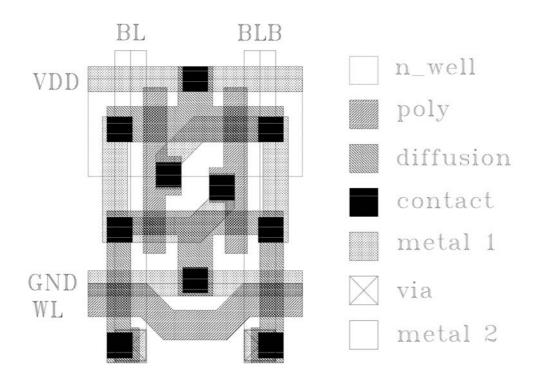

| 6.2 Cell Design and Layout                            | . 71 |

| 6.3 Process Variation Effects on Current-Mode Circuit | 73   |

| 6.4 Experimental Results                              | . 76 |

| Chapter 7 Conclusions                                 | . 80 |

| References                                            | 82   |

## **List of Figures**

Elementary SRAM structure

Fig. 1

| Fig. 2  | Divided Word Line (DWL) Architecture                                                    |

|---------|-----------------------------------------------------------------------------------------|

| Fig. 3  | Schematic of a two-level 8 to 256 decoder                                               |

| Fig. 4  | <ul><li>a) Conventional static NAND gate</li><li>b) Nakamura's NAND gate [35]</li></ul> |

| Fig. 5  | Skewed NAND gate                                                                        |

| Fig. 6  | Bit-line mux hierarchies in a 512 row block                                             |

| Fig. 7  | Two common types of sense amplifiers                                                    |

| Fig. 8  | A vertical Lambda bipolar transistor structure                                          |

| Fig. 9  | An equivalent circuit of a vertical Lambda bipolar transistor                           |

| Fig. 10 | The I-V characteristics of a vertical Lambda bipolar transistor                         |

| Fig. 11 | General configuration of a new memory cell                                              |

| •       | The I-V characteristics of a new memory cell with current and resistive load            |

| Fig. 13 | A new SRAM memory cell circuit                                                          |

| Fig. 14 | The static transfer characteristics of the memory cells                                 |

| Fig. 15 | Write "0" operation                                                                     |

| Fig. 16 | Write "1" operation                                                                     |

| Fig. 17 | Read "0" operation                                                                      |

| Fig. 18 | Read "1" operation                                                                      |

| Fig. 19 | Sensing delay versus bit-line capacitance                                               |

| Fig. 20 | Typical use of a sense amplifier                                                        |

| Fig. 21 | Theoretical voltage-mode signal model                                                   |

| Fig. 22 | Theoretical current-mode signal model                                                   |

| Fig. 23 | CMOS representation for a voltage-mode signal model                                     |

| Fig. 24 | CMOS representation for a current-mode signal mode                                      |

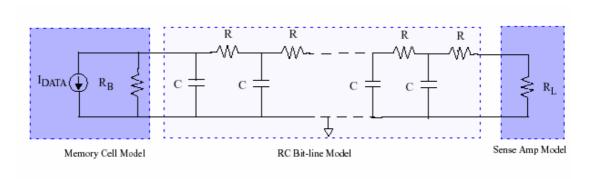

| Fig. 25 | A long interconnect model                                                               |

|         |                                                                                         |

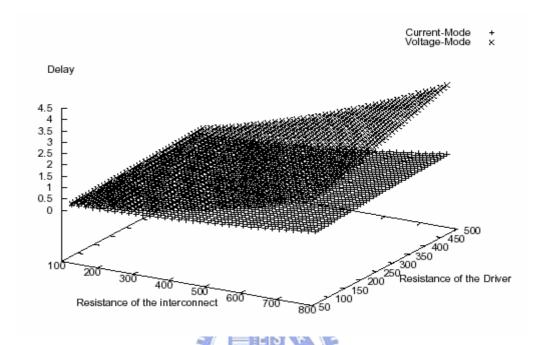

- Fig. 26 Comparison of voltage sensing and current sensing

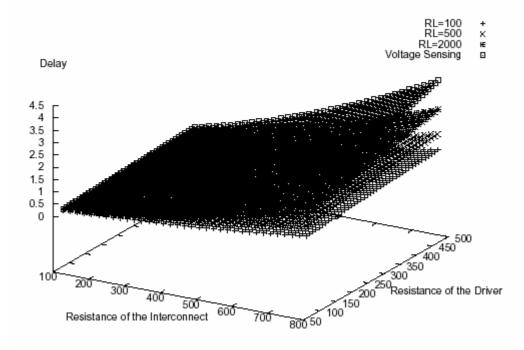

- Fig. 27 Comparison of voltage sensing and current sensing with different values of load resistance

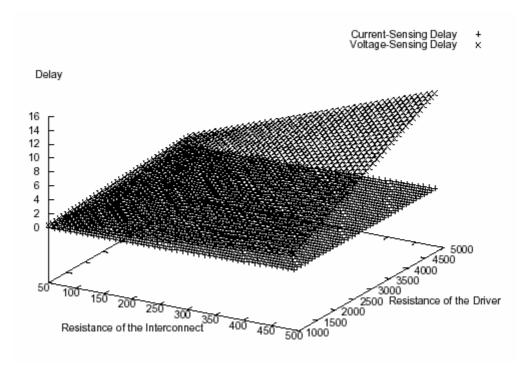

- Fig. 28 Comparison of voltage-sensing and current-sensing with approximations

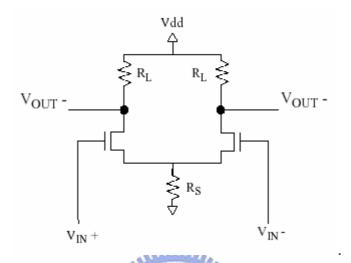

- Fig. 29 Simple differential couple schematic

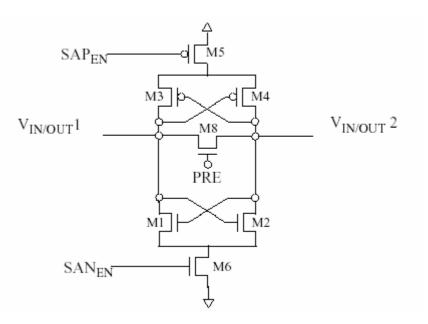

- Fig. 30 Full complementary positive feedback amplifier schematic

- Fig. 31 Clamped bit-line sense amplifier

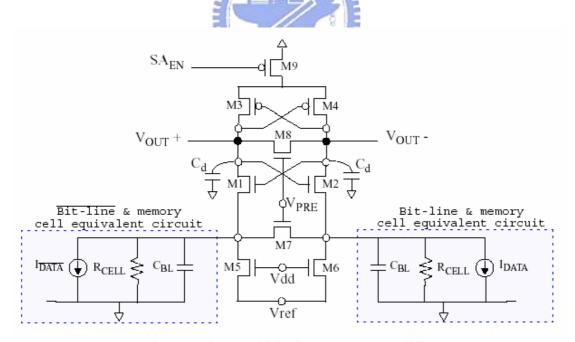

- Fig. 32 A current-mode sense amplifier and a simplified data path circuit

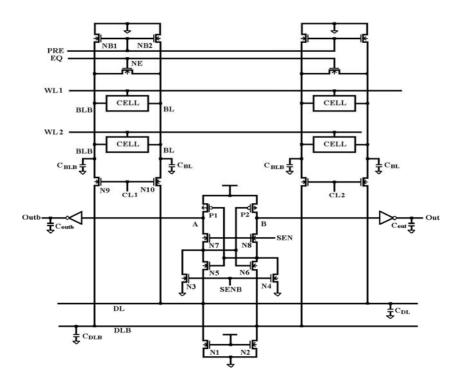

- Fig. 33 Simulated current waveforms of the new current-sensing data path circuit

- Fig. 34 Simulated waveforms of the new current-sensing data path circuit

- Fig. 35 Sensing delay and average power dissipation versus bit-lines capacitance

- Fig. 36 Sensing delay and average power dissipation versus data-lines capacitance

- Fig. 37 Bit-line model during write access cycle

- Fig. 38 7T-memory cell

- Fig. 39 A current-mode write driver and a simplified data path circuit

- Fig. 40 Schematic of the memory cell

- Fig. 41 The static transfer characteristics of the memory cell

- Fig. 42 Simulated waveforms of the new current-writing data path circuit

- Fig. 43 Write pulse width and average power dissipation versus data-lines capacitance

- Fig. 44 Architecture of low power memory chip

- Fig. 45 The layout of memory cell

- Fig. 46 Layout placement of same-size transistor

- Fig. 47 Sensing delay and average power dissipation with process variations versus bit-lines capacitance

- Fig. 48 Write pulse width and average power dissipation with process

#### variations versus data-lines capacitance

- Fig. 49 A photomicrograph of 32Kx8 SRAM

- Fig. 50 Typical address and output waveforms

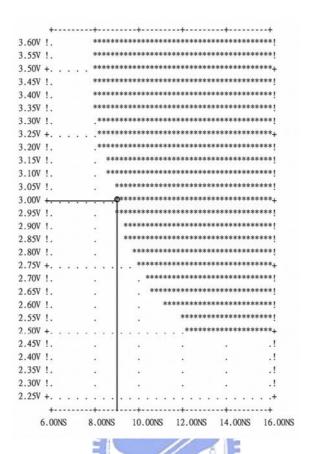

- Fig. 51 Shmoo plot of address time versus power supply voltage

## **List of Tables**

Table 1. Comparison to conventional SRAM cell

Table 2. Process and SRAM characteristics

## **Chapter 1**

#### Introduction

High-speed and low-power SRAMs have become a critical component of many VLSI chips. This is especially true for microprocessors, wherein the on-chip cache sizes are growing with each generation to bridge the increasing divergence in the speeds of the processor and the main memory [1-2]. Simultaneously, power dissipation has become an important consideration both due to the increased integration and operating speeds, as well as due to the explosive growth of battery operated appliances [3]. This thesis explores the design of SRAMs and focuses on reducing the operating power. While process scaling [4-5] remains the biggest drivers of low power design, this thesis investigates some circuit techniques which can be used in conjunction to scaling to achieve low power operation.

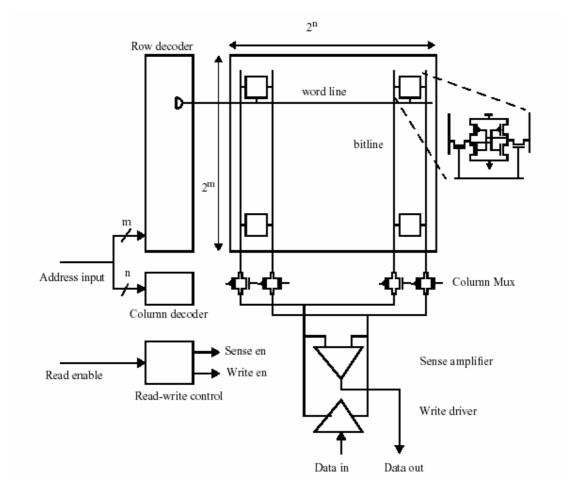

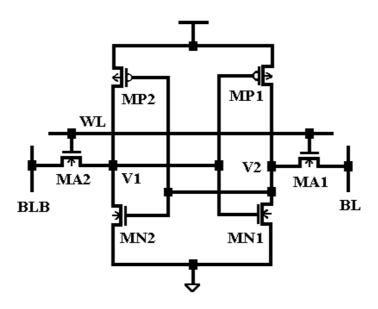

Conceptually, a SRAM has the structure shown in Fig.1. It consists of a matrix of 2<sup>m</sup> rows by 2<sup>n</sup> columns of memory cells. Each memory cell in a SRAM contains a pair of cross-coupled inverters which form a bi-stable element. These inverters are connected to a pair of bit-lines through NMOS pass transistors which provide differential read and write access. A SRAM also contains some column and row circuitries to access these cells. The m+n bits of address input, which identify the cell to be accessed, are split into m row address bits and n column address bits. The row decoder activates one of the 2<sup>m</sup> word lines, which connects the memory cells of that row to their respective word line. The column

decoder sets a pair of column switches, which connects one of 2<sup>n</sup> bit-lines to the peripheral circuits.

Fig.1 Elementary SRAM structure

In a read operation, the bit-lines start precharged to a reference voltage usually close to the positive supply. When the word line turns high, the access NMOS connected to the cell node being stored a data '0' starts discharging the bit-line, while the complementary bit-line remains in its precharged state, thus resulting in a differential voltage being developed across the bit-line pair. Each SRAM cell is optimized to minimize the cell area, and hence its cell current is very small, resulting

in a slow bit-line discharge rate. To speed up the RAM access, each sense amplifier is used to amplify the small bit-line signal and eventually drives the signal to the external world.

During a write operation, the write data is transferred to the desired columns by driving the data onto the bit-line pairs by grounding either the bit-line or its complementary. If the cell data is different from the write data, then the data '1' node is discharged when the access NMOS connects to the discharged bit-line, thus causing the cell to be written with the bit-line value.

The next chapter introduces the various techniques which are used in practical SRAMs. For the purpose of design and optimization, the access path can be divided into two portions: the read path- the portion from the memory cell ports to the SRAM I/O ports and the write path- the portion from the I/O ports to the memory cell.

In most SRAM cell design, the basic flip-flop circuit structure is the most frequently used. However, a full CMOS cell usually occupies twice larger area as compared with high-resistance poly load and poly-PMOS TFT load cells. On the other hand, a high-resistance poly load cell consumes relatively high standby power. Therefore, several earlier works [6-11] on single-sided memory cells had been conducted for both power and area reduction. In this thesis, we proposed new single-sided memory cells based on new Lambda bipolar transistor (LBT). In Chapter 3, we report the new LBT, and the new LBT is developed based on the original LBT structure with a modification for low power purpose. The operation principle of the device is derived by simple circuit model and device physics. In Chapter 3, we also present the new single-sided memory cells

based on our LBT. Some comparisons between the reported memory cells and the single-sided CMOS cell are made.

For many years, the design of SRAM circuits has focused on improving the operation speed. For example, the capacity of SRAM quadruples every three years, and various voltage-mode sense amplifiers have been used in many generations of SRAM. As the bit-line and data-line capacitances get larger and larger as SRAM evolves, memory access time using voltage-mode sense amplifier will become quite long. Meanwhile, power supply voltage should be reduced in the future VLSI design for the sake of power reduction and device reliability. In order to overcome these problems, several papers [12-17] had proposed to use current-mode sense amplifiers for the future. However, the DC current through the sense amplifier would not be eliminated. To solve this DC power consumption in sense amplifier, a new current-mode sense amplifier is proposed. The new structure not only reduces DC power consumption of sense amplifier but also senses the bit-line differential signal in a very short time. The new n-type separated flip-flop current-mode sense amplifier will be described in Chapter 4.

Chapter 5 discusses the new current-mode write driver circuit. The power consumption of writing data into memory always dominates for a large percentage of whole chip during the writing access cycle. In the past, the voltage-mode writing circuit was used. Using this mechanism, the voltage swing at the bit-line always needs almost full supply voltage swing. Therefore, the dynamic power consumption at the bit-line will increase as large as voltage swing at the bit-line variation. This large voltage swing not only consumes large power when writing data, but also

increases the memory cycle time. The cycle time is long because the bit-line level must be pulled up back to supply voltage after write operation, preparing for next read or write operation. So the operation speed of SRAM is not only determined by the access time but also by the cycle time. Some design concepts [18] using the current-mode technique in write operation have been proposed to reduce the large voltage swing at the bit-line. However, these methods increase the transistor number in memory cell, making the memory size larger. Moreover, the decoder of control signal and timing control become more complicated. The new current writing mechanism is proposed to reduce the large voltage swing at the bit-line without increasing transistor number in memory cell. The decoder architecture and timing control signal are as simple as the conventional technique.

In Chapter 6, 32Kx8 SRAM chip is implemented. At the architecture level design, the key goals are localizing on operation signal to reduce active capacitance and switch, reduce signal swings, and eliminate any DC power consumption of system. We finally summarize the main conclusions of this thesis in Chapter 7.

### **Chapter 2**

#### **Overview of CMOS SRAM**

The delay and power of practical SRAMs have been reduced over the years via innovations in the array organization and circuit design. This chapter discusses both these topics and highlights the issues addressed by this thesis. We will first explore the various partitioning strategies in Section 2.1 and then point out the main circuit techniques which have been presented in the literature to improve speed and power in Section 2.2.

### 2.1 SRAM Partitioning

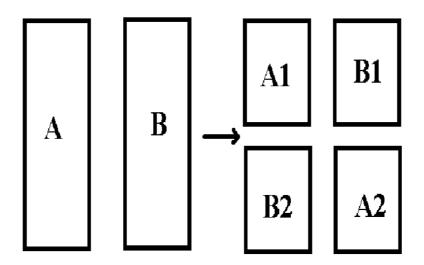

For large SRAMs, significant improvement on delay and power can be achieved by partitioning the cell array into smaller subarrays, rather than having a single monolithic array as shown in Fig.1. Typically, a large array is partitioned into a number of identically sized subarray (commonly referred to as macros), each of which stores a part of the accessed word, called the subword, and all of which are activated simultaneously to access the complete word [19-21]. The macros can be thought of as independent RAMs, except that they might share parts of the decoder.

Each macro conceptually looks like the basic structure shown in Fig.1. During an access to a certain row, the word line activates all the

cells in that row and the desired subword is accessed via the column multiplexers. This arrangement has two drawbacks for macros that have a very large number of columns; the word line RC delay grows as the square of the number of cells in the row, and bit line power grows linearly with the number of columns. Both these drawbacks can be overcome by

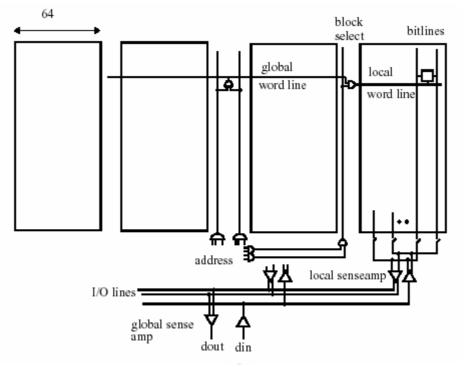

Fig.2 Divided Word Line (DWL) Architecture

further subdividing the macros into smaller blocks of cells using the Divided Word Line (DWL) technique as first proposed by [22]. In the DWL technique, the long word line of a conventional array is broken up into k sections, which each section is activated independently thus reducing the word line length by k and hence reducing its RC delay by  $k^2$ . Fig.2 shows the DWL architecture where a macro of 256 columns is partitioned into 4 blocks and each block has only 64 columns. The row selection is now done in two stages, first a global word line is activated which is then transmitted into the desired block by a block select signal to

activate the desired local word line. Since the local word line is shorter (only 64 columns wide), it has a lower RC delay. Though the global word line is nearly as long as the width of the macro, it has a lower RC delay than a full length word line since its capacitive loading is smaller. It sees only the input loading of the four word line drivers instead of the loading of all the 256 cells. In addition, its resistance can be lowered as it could use wider wires on a higher level metal layer. The word line RC delay is reduced by another factor of four by keeping the word-line drivers in the center of the word line segments thus halving the length of each segment. Since 64 cells within the block are activated as opposed to all the 256 cells in the undivided array, the column current is also reduced by a factor of 4. The concept of dividing the word line can be carried out recursively on the global word line (and the block select line) for larger RAMs, and is called the Hierarchical Word Decoding (HWD) technique [23]. Partitioning can also be done to reduce the bit-line height.

Partitioning of the RAM incurs area overhead at the boundaries of the partitions. For example, a partition which dissects the word lines requires the use of word-line drivers at the boundary. Since the RAM area determines the lengths of the global wires in the decoder and the data path, it directly influences their delay and energy.

## 2.2 Circuit Techniques in SRAMs

The SRAM access path can be broken down into two components: the decoder and the data path. The decoder encompasses the circuits from the address input to the word line. The data path encompasses the circuits

from the cells to the I/O ports.

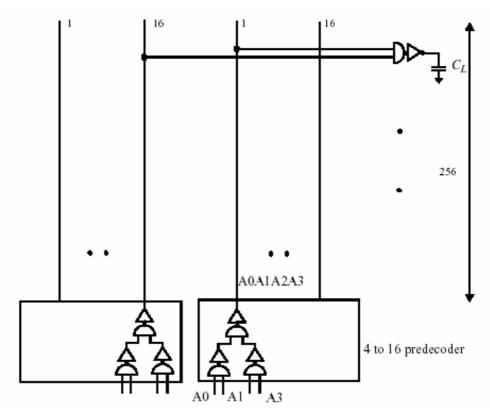

The logical function of the decoder is equivalent to 2<sup>n</sup> -input AND gates, where the large fan-in AND operation is implemented in a hierarchical structure. The schematic of a two-level 8 to 256 decoder is shown in Fig.3. The first level is the predecoder where two groups of four address inputs and their complements (A0, A0, A1, A1, ...) are first decoded to activate one of the 16 predecoder output wires respectively to form the partially decoded products (A0A1A2A3, A0A1A2A3, ...). The predecoder outputs are combined at the next level to activate the

Fig.3 Schematic of a two-level 8 to 256 decoder

word line. The decoder delay consists of the gate delay in the critical path and the interconnect delay of the predecoder and word line wires. As the wire RC delay grows as the square of the wire length, the wire delay within the decoder structure, especially of the word line, becomes significant in large SRAMs. Sizing of gates in the decoder allows for trade off between the delay and the power. Transistor sizing had been studied by a number of researchers for both high speed [24-26] and low power [27-28]. The decoder sizing problem is complicated slightly due to the presence of intermediate interconnect from the predecoder wires.

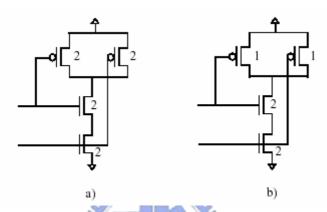

Fig.4 a) Conventional static NAND gate b) Nakamura's NAND gate [35]

The decoder delay can be greatly improved by optimizing the circuit style used to construct the decoder gates. Older designs implemented the decoder logic function in a simple combinational style using static CMOS circuit style (Fig.4a) [29-31]. In such a design, one of the 2<sup>m</sup> word lines will be active at any time. If in any access, the new row address differs from the previous one, then the old word line is deasserted and the new word line is asserted. Thus, the decoder gate delay in such a design is the maximum of the delay to deassert the old word line and the delay to assert a new word line, and it is minimized when each gate in the decode path is designed to have equal rising and falling delays. The decoder gate delay can be significantly reduced by using pulsed circuit techniques [32-34], where the word line is not a combinational signal but a pulse

which stays active for a certain minimum duration and then shuts off. Thus, before any access all the word lines are off and the decoder just needs to activate the word line for the new row address. Since only one kind of transition needs to propagate through the decoder logic chain, the transistor sizes in the gates can be skewed to speed up this transition and minimize the decoder delay. Fig.4b shows an instance of this technique [35], where the PMOS in the NAND gates are sized to be a half that in a regular NAND structure. In the pulsed design, the PMOS sizes can be reduced by a factor of two and still result in the same rising delay since it is guaranteed that both the inputs will deassert, thus reducing the loading of the previous stage and hence reducing the overall decoder delay. This concept is extended further in [32], where the deassertion of the gate is completely decoupled from its assertion. Fig.5 shows an example of such a gate where the transistor size in the logic chain is skewed heavily to speed up the output assertion once the inputs are activated. The gate is then reset by some additional devices and made ready for the next access. By decoupling the assert and deassert paths, the former can be optimized to reduce the decoder delay.

Fig.5 Skewed NAND gate

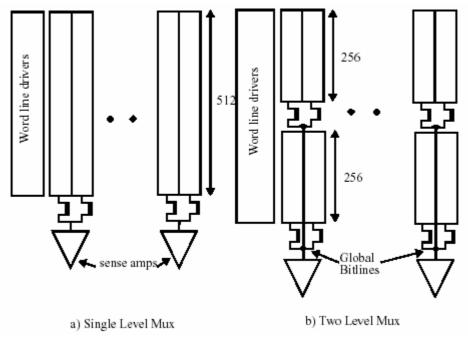

The SRAM data path logically implements a multiplexer for reads (and a demultiplexer for writes). In the simplest implementation, the multiplexer has only two levels: at the lowest level, the memory cells in a column are all connected together to a bit line and in the next level, a small number of these bit lines are multiplexed together through column pass transistors (Fig.1). When the bit-line height is very large, it can be further partitioned to form multi-level bit line hierarchies, by using additional layers of metal [36]. In general, the multiplexer hierarchy can be constructed in a large number of ways (2<sup>r-1</sup>\*2<sup>c</sup> mux designs are possible for a 2<sup>r</sup> \* 2<sup>c+k</sup> block with 2r number of rows, 2<sup>c</sup> number of columns and an access width of 2<sup>k</sup> bits). Fig.6 shows two possible designs for a block with 512 rows. The schematic shows only the NMOS pass gates for a single-ended bit line to reduce the clutter in the figure, while the real multiplexer would use CMOS pass gates for differential bit-lines, to allow for reads and writes. Fig.6a shows the single level mux design, where two adjacent columns with 512 cells are multiplexed into a single sense amplifier. Fig.6b shows a two level structure in which the first level multiplexes two 256 high columns, the output of which are multiplexed in the second level to form the global bit lines, feeding into sense amplifiers. Similarly, hierarchical muxing can also be done in the I/O lines which connect the outputs of all the sense amplifiers to the I/O ports [37].

Due to its small size, a memory cell is very weak and limits the bit-line slew rate during reads. Hence sense amplifiers are used to amplify the bit-line signal so signals as small as 100mV can be detected. In a conventional design, even after the sense amplifier senses the bit lines,

they continue to slew to eventually create a large voltage differential. This leads to a significant waste in power since the bit lines have a large capacitance. By limiting the word-line pulse width, we can control the amount of charges pulled down by the bit lines and hence limit power dissipation [38-41]. In this thesis, we use a scheme to control the word line pulse width to be just wide enough, over a wide range of operating conditions, for the sense amplifiers to reliably sense, and prevent the bit lines from slewing further.

Fig.6 Bit-line mux hierarchies in a 512 row block

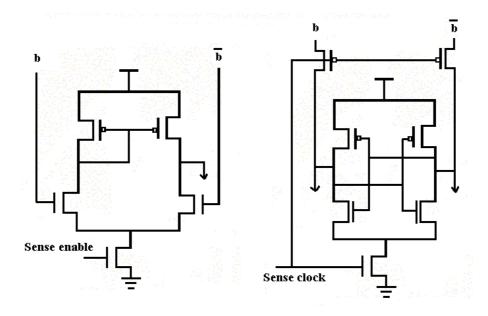

A number of different sense amplifier circuits have been proposed in the past and they essentially fall into two categories: the linear amplifier type [42-43] and the latch type [19-21]. Fig.7 illustrates a simple prototype of each type. In the linear amplifier type (Fig.7a), the amplifier needs a DC bias current to set it up in the high gain region prior to the arrival of the bit-line signal. To convert the small swing bit-line signal into a full swing CMOS signal, a number of stages of amplification are

required. These kinds of amplifiers are typically used in very high performance designs. Because they consume biasing power and they operate over a limited supply voltage, they are not preferred for low power and low voltage designs. In these designs, the latch-type designs are used (Fig.7b). They consist of a pair of cross-coupled gain stages which are turned on with the aid of a sense clock when an adequate input differential is set up. The positive feedback in the latch leads to a full amplification of the input signal to a full digital level. While this type consumes the least amount of power due to the absence of any biasing power, they could potentially be slower since a timing margin is needed in the generation of the sense clock. If the sense clock arrives before enough input differential is set up, it could lead to a wrong output value. Typically, the sense clock timing needs to be adjusted for the worst case operating and process condition, which in turn slows it down for the typical conditions due to the excess timing margins. In this thesis, we will look at some timing circuits which track the bit-line delay and which are used to generate a sense clock with a reduced timing overhead.

In large SRAMs, another level is added to the data path hierarchy by connecting the outputs of the sense amplifiers onto the I/O lines (Fig.2). The I/O lines transport the signal between the RAM I/O ports to the memory blocks. In large access width SRAMs, the power dissipation of these lines can also be significant and hence the signaling on these is also via small swings [44]. In Chapter 4, we will apply the low swing bit-line technique to the I/O lines too, to reduce the I/O line power.

- a) current mirror amplifier

- b) latch-type amplifier

Fig.7 Two common types of sense amplifiers

### **Chapter 3**

## Lambda Bipolar Transistor Memory Cell

Negative differential resistance semiconductor devices have been known for their memory application. The negative differential resistance or the folded I-V characteristics of devices makes it possible to have the multiple stable states with good margins in a simple circuit consisting of just a few devices. This fact was recognized by several researchers and several compact multiple-valued storage functions had been described in the literature. For example, Thomas et al. [45] had described a voltage-controlled negative differential resistance device (NEGIT) made by a bipolar transistor and an extended field plate over the emitter-base junction. The operation of NEGIT depends on some uncontrollable parameters such as surface recombination velocity and surface state. Wu et al. [46~47] had presented another voltage-controlled negative differential resistance device, called Lambda bipolar transistor (LBT), which merges a NMOS with a bipolar transistor. The LBT's, in particular, had shown clear voltage-controlled negative differential resistance characteristics, which functional circuit applications. advantageous for Moreover, planar-structure LBT's has also been realized to meet the demand for high-level integration. In recent years, quantum devices with carrier transport of resonant tunneling (RT) had been developed, several attempts were made on the RT structures to obtain multiple negative differential resistance characteristics [48]. Based on the multiple negative differential

resistance concepts, many resonant tunneling devices had been developed and fabricated to implement a memory cell [49-51]. However, these structures need the external bias source to separate the peaks and are difficult to incorporate into a bipolar transistor to exploit the additional advantages of high gain and good input-output isolation. Also, they will be difficult to fabricate over million-transistor circuit in III-V technology, and one of the shortcomings is the absence of a reasonable density low-power on-chip memory.

In the past, several earlier works on single-side memory cells had been conducted for both power and area reduction. Among these, Takagi et al. [6] proposed Dual Depletion CMOS memory cell; Schrader et al. [7] proposed a static memory based Schmitt trigger circuit; Elmasry et al. [8] proposed double-Lambda diode (DOL) memory cells, and they also proposed SDW MOSFET memory cell [9] by using single-device well MOSFET's. To our knowledge, none of them has been implemented far for practical applications. Besides, as the advance of submicrometer device fabrication technology, the area of memory cells is continuously scaled down, leading to fine metal bit-line problems. The fine metal bit-lines in a high-resistance poly load or ploy-PMOS load cell will induce large signal delays, or high current density could cause reliability degradation. For these reasons, several new works on single-bit line SRAM's were proposed. Sasaki et al. [10] had proposed a high-density 16-Mb SRAM, and a CMOS flip-flop circuit is acted as the storage element with only one access transistor. However, the noise margin is small based on this structure. Ukita et al. [11] had proposed an ultra-low power SRAM. They used the same CMOS flip-flop as the

storage element but with two serial-connected access transistors at one side: one is for X address selection and the other is for Y address selection. This structure can achieve very low power requirement. However, as the driver to load ratio is small, the delay time becomes significant.

Fig.8 A vertical Lambda bipolar transistor structure

The proposed new memory cell is based on Wu's Lambda bipolar transistor (LBT) developed in 1980's. The LBT is a highly integrated device characterized by its voltage-controlled negative differential resistance, and has been used successful in many applications [52-53]. If the LBT is to be used in static random access memory cell, the standby current in one of its storage states is relatively high. For this reason, a new LBT is proposed for low power applications.

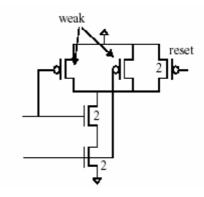

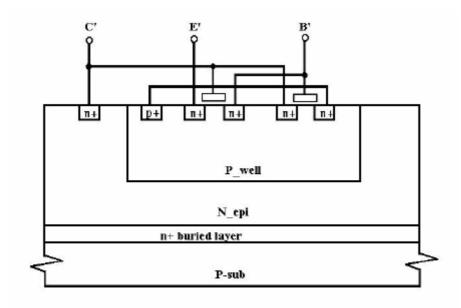

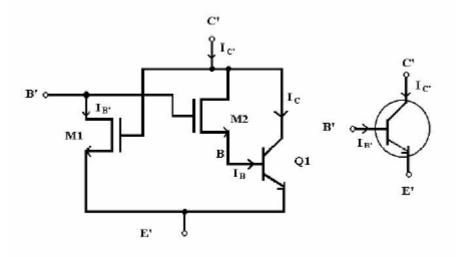

#### 3.1 New Lambda Bipolar Transistor

The basic structure of the new Lambda bipolar transistor and its electrical equivalent circuit connection are shown in Fig.8 and Fig.9, respectively. From Fig.8, the n-channel enhancement-mode MOSFET's are fabricated upon the base region of a vertical NPN bipolar transistor, which is called the vertical Lambda bipolar transistor (VLBT). The source of one of the MOSFET's (labeled as E') is utilized as the emitter of the vertical NPN bipolar transistor, while the p-type diffusion well and the n-type epi-layer act as the base and the collector, respectively. The equivalent circuit is shown in Fig.9 and their interconnections can be clearly seen. It could be noted that, in ordinary circuit applications, E' is biased at a voltage level lower than B' and C'. Therefore, E' is the only possibly turned-on PN junction, i.e. the other three sources/drains other than E' have no chance to act as the emitter of the vertical bipolar transistor.

Fig.9 An equivalent circuit of a vertical Lambda bipolar transistor

The vertical Lambda bipolar transistor is operated in the same way as

the conventional bipolar transistor with a fixed external base current. From the terminal characteristics of the separate devices, the general equations for the proposed VLBT, according to the circuit model of Fig.9, can be written as

$$I_{B'} = \begin{cases} K_1 \left[ \left( V_{C'E'} - V_{T1} \right) V_{B'E'} - \frac{V_{B'E'}^2}{2} \right] & if \left( V_{C'E'} - V_{T1} \right) > V_{B'E'} \\ \frac{K_1}{2} \left( V_{C'E'} - V_{T1} \right)^2 & if \left( V_{C'E'} - V_{T1} \right) < V_{B'E'}, \end{cases}$$

$$(1)$$

where  $K_1 = C_{ox} \mu_n W_1 / L_1$  and  $V_{T1}$  is the threshold voltage of  $M_1$ .

$$I_{C'} = I_C + I_B \tag{2}$$

$$I_{B} = \begin{cases} K_{2} \left[ (V_{B'E'} - V_{T'})(V_{C'E'} - V_{BE'}) - \frac{(V_{C'E'} - V_{BE'})^{2}}{2} \right] & if (V_{B'E'} - V_{T2}) > V_{C'E'} \\ \frac{K_{2}}{2} (V_{B'E'} - V_{T'})^{2} & if (V_{B'E'} - V_{T2}) < V_{C'E'}, \end{cases}$$

$$(3)$$

where  $K_2 = C_{ox} \mu_n W_2 / L_2$ ,  $V_{T2}$  is the threshold voltage of  $M_2$ , and

$$V_{T'} = V_{T2} + V_{BE'}$$

.

$$I_C = \beta I_B + I_{CO} (1 + \beta) \tag{4}$$

where  $\beta$  is the dc common-emitter current gain of the NPN bipolar transistor, and  $I_{CEO}=I_{CO}(1+\beta)$  is the common-emitter collector reverse saturation current.

A certain current source load  $M_3$  operated in saturation region is chosen for derivation. The current equation can be written as

$$I_{B'} = \frac{K_3}{2} (V_{GG} - V_{B'E'} - V_{T3})^2 \qquad for \quad V_{GG} > (V_{B'E'} + V_{T3})$$

(5)

where  $K_3 = C_{ox} \mu_n W_3 / L_3$ ,  $V_{T3}$  is the threshold voltage of  $M_3$  and the  $V_{GG}$ is the power supply connected to the drain of the  $M_3$ .

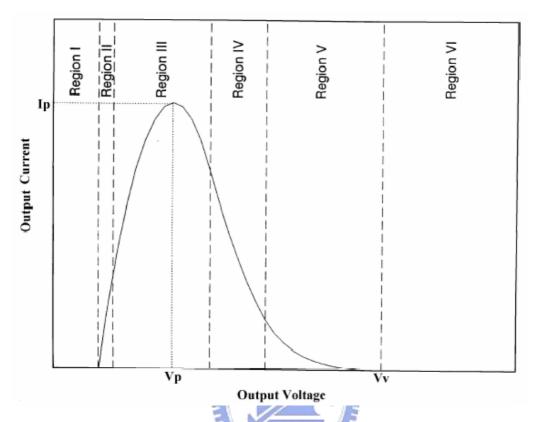

In order to get analytical expressions, the body effects are assumed to be negligible. To see the quantitative operational principles of a VLBT shown in Fig. 10, the six-region analyses are given as follow:

#### Region I:

If  $V_{C'E'} < V_{BE'(on)} < V_{T1}$ , ,  $M_1$  is off,  $M_2$  is operated in linear region, and  $Q_1$  is off. In this region,  $I_B=0$ , thus  $I_{C'}=I_{CO}(1+\beta)$ .

Region II:

from II:

If

$$V_{BE'(on)} < V_{C'E'} < V_{T1}$$

and  $V_{B'E'} = V_{GG} - V_{T3} - K \left[ \sqrt{2\phi_{fp} + V_{B'E'}} - \sqrt{2\phi_{fp}} \right] > V_{T'}$

(where K is the modifying substrate factor), M<sub>1</sub> is off, M<sub>2</sub> is kept in linear region, and  $Q_1$  is operated in forward-active region. By solving  $V_{B'E'}$ , i.e.

$$V_{B'E'} = \left(V_{GG} - V_T + K\sqrt{2\phi_{fp}} + \frac{K^2}{2}\right) + K\left(V_{GG} - V_T + K\sqrt{2\phi_{fp}} + \frac{K^2}{4} + 2\phi_{fp}\right)^{1/2}$$

(6)

we get the output current in this region:

$$I_{C'} = \left(1 + \beta\right) \left[ K_2 \left[ \left( \left( V_{GG} - V_T + K \sqrt{2\phi_{fp}} + \frac{K^2}{2} \right) + K \sqrt{\left( V_{GG} - V_T + K \sqrt{2\phi_{fp}} + \frac{K^2}{4} + 2\phi_{fp} \right)} - V_{T'} \right] \left( V_{C'E'} - V_{BE'} \right) - \frac{\left( V_{CE'} - V_{BE'} \right)^2}{2} + I_{CO} \right]$$

$$(7)$$

Region III:

If  $V_{T1} < V_{C'E'} < V_{B'E'} - V_{T2}$  and assuming that  $V_{B'E'} > V_{T'}$ ,  $M_1$  is operated in saturation region,  $M_2$  is kept in linear region, and  $Q_1$  is still in forward-active region. Solving  $V_{B'E'}$  by equating (1) and (5), we obtain

$$V_{B'E'} = V_{GG} - \sqrt{\frac{K_1}{K_3}} (V_{C'E'} - V_{T1}) - V_{T3}$$

(8)

and the output current in this region is

$$I_{C'} = (1 + \beta) \left[ K_2 \left[ V_{GG} - \sqrt{\frac{K_1}{K_3}} (V_{C'E'} - V_{T1}) - V_{T3} - V_{T'} \right] (V_{C'E'} - V_{BE'}) - \frac{(V_{C'E'} - V_{BE'})^2}{2} + I_{CO} \right]$$

$$(9)$$

The peak current is  $I_P = I_{C'|V_{B'E'}=V_P}$ , where the peak voltage  $V_P$  can be derived by letting  $\frac{\partial I_{C'}}{\partial V_{C'E'}} = 0$ , i.e.

$$V_{P} = \frac{K_{3}(V_{GG} - V_{T2} + V_{T3}) + \sqrt{K_{1}K_{3}}(V_{BE'} + V_{T1})}{K_{3} + 2\sqrt{K_{1}K_{3}}}$$

(10)

ion IV: If  $V_{B'E'} - V_{T2} < V_{C'E'} < V_{B'E'} + V_{T1}$  and  $V_{B'E'} > V_{T'}$ ,  $M_1$  and  $M_2$  are both operated in saturation region, and  $Q_1$  is operated in forward-active region. Using equations (1),(2),(4), and (8), we obtain

$$I_{C'} = \left(1 + \beta\right) \left[ \frac{K^2}{2} \left( V_{GG} - \sqrt{\frac{K_1}{K_3}} \left( V_{C'E'} - V_{T1} \right) - V_{T3} - V_{T'} \right)^2 + I_{CO} \right]$$

(11)

By differentiating (11) with respect to  $V_{C'E'}$ , the output resistance in this region can be written as

$$R_{O} = \frac{-1}{(1+\beta)K_{2}\sqrt{\frac{K_{1}}{K_{3}}} \left[V_{GG} - \sqrt{\frac{K_{3}}{K_{1}}} (V_{C'E'} - V_{T1}) - V_{T3} - V_{T'}\right]}$$

(12)

Region V:

When  $V_{C'E'} > V_{B'E'} + V_{T1}$ ,  $M_1$  is operated in linear region and  $M_2$  is operated in saturation region.

Assuming  $V_{B'E'} > V_T$ ,  $Q_1$  is operated in forward-active region. The output

current is

$$I_{C'} = (1 + \beta) \left[ \frac{K_2}{2} (V_{B'E'} - V_{T'})^2 + I_{CO} \right]$$

. Solving (1) and (5), gives

$$V_{B'E'} = \frac{K_1 (V_{C'E'} - V_{T1}) + K_3 (V_{GG} - V_{T3})}{K_1 + K_3}$$

$$-\frac{\left[\left[K_{1}\left(V_{C'E'}-V_{T1}\right)+K_{3}\left(V_{GG}-V_{T3}\right)\right]^{2}-K_{3}\left(K_{1}+K_{3}\right)\left(V_{GG}-V_{T3}\right)^{2}\right]^{\frac{1}{2}}}{K_{1}+K_{3}}$$

(13)

By a chain rule, we have the output resistance

$$R_{O} = \frac{1}{\frac{\partial I_{C'}}{\partial V_{B'E'}}} \frac{\partial I_{B'E'}}{\partial V_{C'E'}}$$

$$= \frac{1}{(1+\beta)K_{2}(V_{B'E'}-V_{T'})(K_{1}+K_{3})} \times \left[K_{1} - \frac{2K_{1}[K_{1}(V_{C'E'}-V_{T1})+K_{3}(V_{GG}-V_{T3})]}{2[[K_{1}(V_{C'E'}-V_{T1})+K_{3}(V_{GG}-V_{T3})]^{2}-K_{3}(K_{1}+K_{3})(V_{GG}-V_{T3})^{2}]^{\frac{1}{2}}}\right]$$

(14)

The valley voltage  $V_v$  can be obtained by solving  $V_{B'E'}(V_{C'E'}) = V_{T'}$ , i.e.

$$V_{V} = \frac{K_{3}(V_{GG} - V_{T'} + V_{T3})^{2} + K_{1}(V_{T'}^{2} + 2V_{T'}V_{T1})}{2K_{1}V_{T'}}$$

(15)

Region VI:

When  $V_{C'E'} > V_V$ ,  $M_1$  is still operated in linear region,  $M_2$  and  $Q_1$  are both off. Thus,  $I_B = 0$  and  $I_{C'} = I_{CO}(1 + \beta)$ .

The output dc characteristic of the new VLBT is shown in Fig. 3-3.

#### 3.2 Description of the New Memory Cell

The performance of a SRAM strongly depends on the design of its memory cell. Generally, a full CMOS cell is suitable for low power design with acceptable speed. However, it has a significant area penalty over a high-resistance poly load or poly-PMOS load cell. On the contrary,

the fine metal bit-lines in a high-resistance poly load or poly-PMOS load cell will induce large signal delay or high current density, causing reliability

Fig. 10 The I-V characteristics of a vertical Lambda bipolar transistor

degradation. In our thesis, a new single-sided memory cell is proposed to solve these problems.

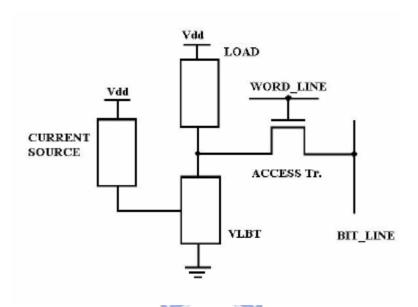

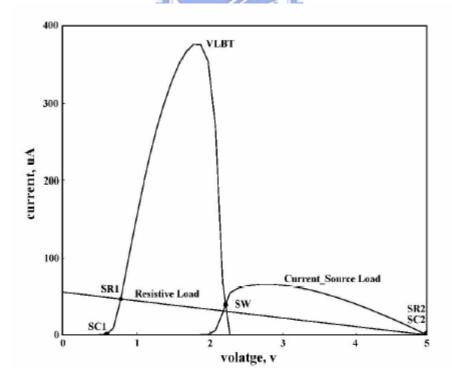

The general configuration of the proposed static random access memory cell is shown in Fig.11, which consists of a VLBT, a load element, a current source device, and an access transistor. Owing to the negative differential resistance of VLBT, the storage node SN has two dc static points (See Fig.12). Two kinds of load elements, current source-like and resistance-like, can be selected for different applications. For a current source-like load, the current flow at the static points  $S_{C1}$  and  $S_{C2}$  can be both small if the circuit is well-configured. On the contrary, a

resistance-like load memory cell generally suffers dc current flow at the lower static state  $S_{R2}$ . However, it occupies a relative smaller area as compared with a current source-like load one.

Fig.11 General configuration of a new memory cell

Fig.12 The I-V characteristics of a new memory cell with current and resistive load

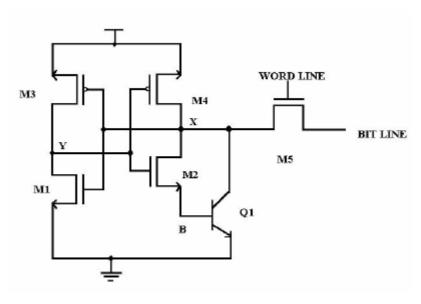

The new memory cell based on the proposed VLBT is presented in Fig.13. In memory cell configuration,  $M_1$ ,  $M_2$  and  $Q_1$  operate as a VLBT storage element,  $M_3$  acts as a current source,  $M_4$  acts as the load element, and  $M_5$  is the access transistor. When Vx is in the low stable-state  $S_{C1}$ , any positive noise causes Vx to increase slightly. At this moment,  $I_{C^\circ}$  is larger than  $I_{DS4}$  so that Vx discharges to  $S_{C1}$ . If any negative noise causes Vx to reduce a little, the fact that  $I_{DS4}$  is larger than  $I_{C^\circ}$  will cause Vx to be charged to  $S_{C1}$ . Previous description demonstrates why this state is stable. The same argument can apply to the state  $S_{C2}$  to verify this state to be stable.

Fig. 13 A new SRAM memory cell circuit

If any positive noise is introduced as Vx in the switching state  $S_W$ , the positive differential current  $I_{DS4}$ - $I_{C'}$  will charge the node X to the high stable state  $S_{C2}$ . The memory cell no longer stays in the state  $S_W$ . On the other hand, if negative noise is introduced as the memory cell is in the state  $S_W$ , a negative differential current  $I_{DS4}$ - $I_{C'}$  makes the node X to be discharged to  $S_{C1}$ . Both types of noise (positive and negative) cause a

transition from the state  $S_W$  to either the stable state  $S_{C1}$  or  $S_{C2}$ . The stored voltage levels are CMOS like, i.e., a full swing between ground and supply voltage is obtained.

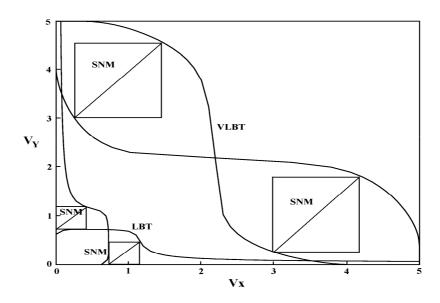

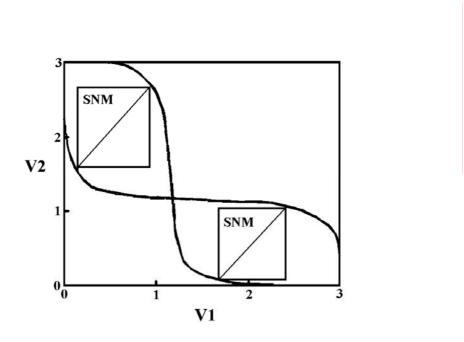

Fig.14 shows the static noise margin (SNM) comparison between our new memory cell and [48] proposed, which is referred as a LBT configuration. The voltage of storage node at any instant is the base-emitter voltage in the LBT configuration, hence is always less than 1V. The SNM of the new memory cell (VLBT) and the LBT configuration are about 1.2V and 0.4V, respectively. The new memory cell has the larger SNM than LBT configuration. It also shows that the LBT configuration requires adequate circuit to sense the state of the cell, because the switch point of the LBT configuration is less than 1V.

Fig. 14 The static transfer characteristics of the memory cells

## 3.3 Performance of the New Memory Cell

Extensive circuit simulations have been carried out to verify the circuit operation and the characteristics of performance. The performance of the proposed circuit is evaluated based on 5V, 0.5um BiCMOS technology. The simulation results are based on 1ns rise and fall time.

#### 3.3.1 Write Operation

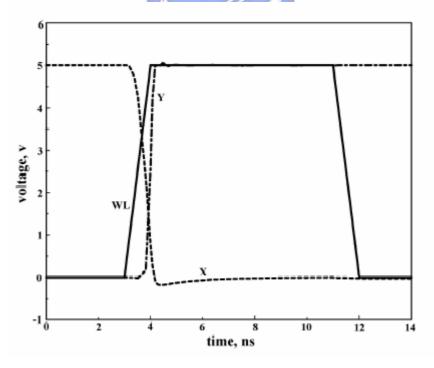

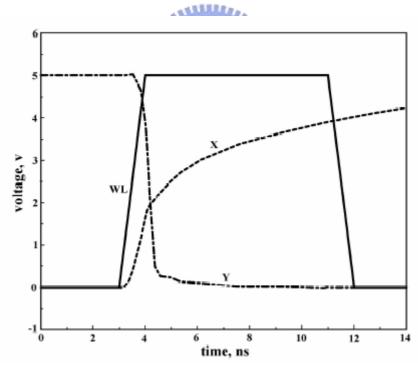

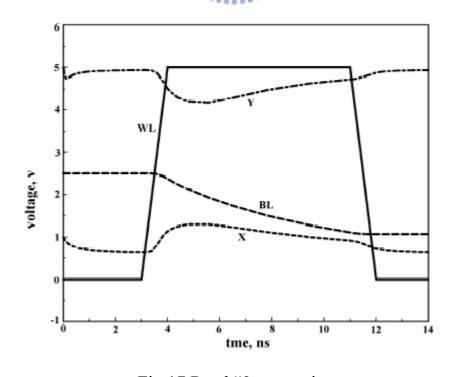

In the static memory cell, the write operation is performed by forcing high and low voltage to the bit-line. The operation cycles start at 3ns, turning on the access transistor M<sub>5</sub> by a word-line pulse with 1ns rise time.

Fig.15 Write "0" operation

When changing the binary state of the memory circuit from 1 to 0, the voltage level of node X rapidly decreases. Because the transistor  $M_1$

is turned off and the transistor  $M_2$  and  $Q_1$  are turned on, the internal capacitor of node Y is charged very fast via the transistor  $M_3$ . The simulation result is shown in Fig.15. Changing the binary state from 1 to 0 just takes about 0.5ns.

When changing the binary state from 0 to 1, the voltage level of node X increases very fast due to the fact that the current through the transistor  $M_4$  is increased. But with increasing the node voltage Vx, the access transistor as well as the transistor  $M_3$  is turned off. Now, the internal capacitor of node X is charged more slowly via the load transistor  $M_4$ . The simulation result is shown in Fig.16. Changing the binary state from 1 to 0 just takes about 1.5ns.

Fig.16 Write "1" operation

## 3.3.2 Read Operation

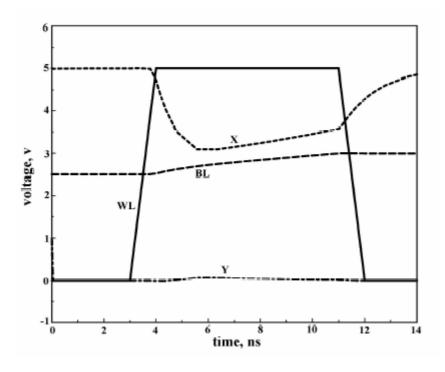

The stored data of a memory cell selected by the word-line and the

column decoder has to be read nondestructively. For the read operation, the bit-line capacitor  $C_{BL}$  is precharged to the reference voltage level  $V_{ref}$  and then is left floating. The bit-line voltage versus time during the reading cycle is calculated by assuming that the memory cell has to charge a bit-line capacitor  $C_{BL}$  of 1pF.

Reading a binary 0, the bit-line capacitor has to be discharged via the transistor Q<sub>1</sub>. The current flowing from the bit-line into the circuit should be low enough so that the voltage level of node X does not cross the switching point S<sub>W</sub>. This current will increase with an increasing precharge voltage level on the bit-line. It means that the precharge voltage has an upper limiting voltage. For a precharge voltage level higher than the upper limiting voltage, the circuit becomes unstable and switches into the opposite binary state. The information in the memory cell will then be destroyed during readout. The reading "0" operation is shown in Fig.17.

Fig.17 Read "0" operation

Reading a binary 1, the bit-line capacitor is charged via the transistor  $M_4$ , and the load current will cause the node voltage Vx to full. To avoid the voltage level of node X crossing the switching point  $S_W$ , the load current level should be higher. Therefore, during reading a binary 1, the precharge voltage level has a lower limiting voltage. The reading "1" operation is shown in Fig.18.

Fig.18 Read "1" operation

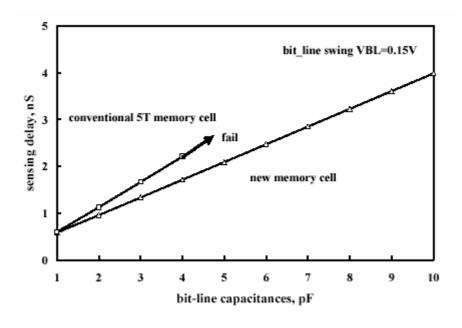

## 3.3.3 Comparisons

Fig.19 shows comparisons of the transient analysis of read "0" operation with respect to different load capacitances on the bit-line. Since the bipolar transistor is operated from cut-in to forward-active region, the proposed memory cell does not make too much difference on the delay time from conventional single-side CMOS memory cell for a small

bit-line capacitance. However, for a large bit-line capacitance, the proposed memory cell is superior to the conventional one because it owns large cell current. What can be noted is that for a heavily-loaded bit-line, the conventional memory is destructively read, i.e. its storage state is changed from "0" to "1" after read operation. On the contrary, the proposed memory cell maintains its trend on delay time toward a bit-line capacitance. Because the charges required for changing the state of the proposed cell from "0" to "1" are relatively large as compared with the conventional one, which are important for nondestructive read operation.

Fig. 19 Sensing delay versus bit-line capacitance

## **Chapter 4**

## **New Current-Mode Sense Amplifier**

During the reading access cycle, the sense amplifier is one of the most critical element of memory circuit. The conventional sense amplifier is based on the voltage-mode technique, but its sensing time increases as the bit-line capacitance increases and its AC operation power consumption is very large. Several design techniques had been proposed to reduce the power dissipation of static RAM [54] in the past. On the other hand, several current-mode sensing circuits [55-57] had been proposed to overcome the problem of possible speed degradation due to larger bit-line or data-line capacitances.

#### 4.1 Introduction

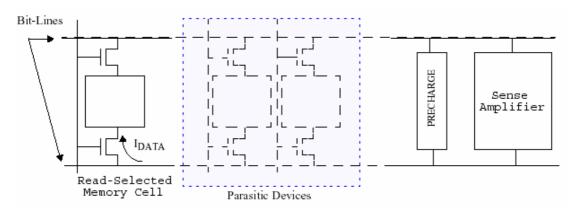

Due to their great importance in memory performance, sense amplifiers have become a very large class of circuits. Their main function is to sense or detect stored data from a read selected memory cell. Fig.20 shows a typical use of a sense amplifier.

Fig.20 Typical use of a sense amplifier

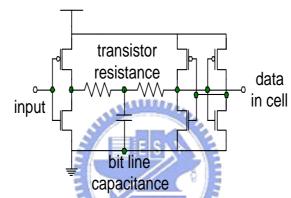

The memory cell being read produces a current " $I_{DATA}$ " that removes some of the charge (dQ) stored on the pre-charged bit-lines. Since the bit-lines are very long and are shared by other similar cells, the parasitic resistance " $R_{BL}$ " and capacitance " $C_{BL}$ " are large. Thus, the resulting bit-line voltage swing (d $V_{BL}$ ) caused by the removal of "dQ" from the bit line is very small, i.e.,  $dV_{BL}$ = $dQ/C_{BL}$ . Sense amplifiers are used to translate this small voltage signal to a full logic signal that can be further used by digital logic.

The need for increased memory capacity, higher speed, and lower power consumption has defined a new operating environment for future sense amplifiers. Below are some of the effects of increased memory capacity and decreased supply voltage:

- 1) Increasing the number of memory cells per bit-line increases  $C_{\rm BL}$ , while an increase in length of the bit-line increases  $R_{\rm BL}$ .

- 2) Decreasing memory cell area to integrate more memory cells in a single chip reduces the current  $I_{DATA}$  that is driving the heavily loaded bit-line. This coupled with increased  $C_{BL}$  causes an even smaller voltage swing on the bit-line.

- 3) Decreasing supply voltage results in smaller noise margins which in turn affect sense amplifier reliability.

In this Chapter, new current-mode sense amplifiers will be presented and its ability to deal with these newly imposed operating conditions examined.

### 4.2 Voltage Sensing and Current Sensing

Current-sensing or current-mode as the name suggests is the sensing technique which determines the logic value present on a wire based on the current through the wire. The difference between current-sensing and voltage sensing is very subtle for conventional CMOS. As for MOS transistors, there is no current-threshold but they have a voltage threshold and hence, conventionally they determine the signal state by sensing the voltage.

#### **4.2.1** Theoretical Model

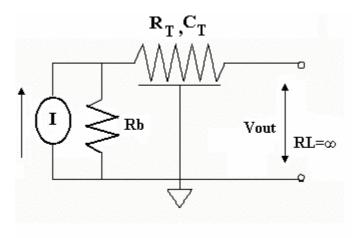

Theoretically, a voltage-mode signaling can be modeled as shown in Fig.21. In the voltage mode, the driver drives interconnect and is terminated with an open circuit ( $R_{L} \approx \infty$ ). This allows the voltage at the destination to change based on the input voltage. The sensing circuit at the destination has to then figure out the signal state using this voltage value.

Fig.21 Theoretical voltage-mode signal model

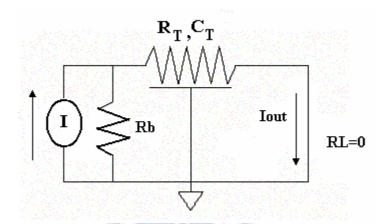

However, in the case of current-sensing the signal is transmitted by a current pulse. The theoretical representation for current sensing would be shown in Fig.22. In a current-sensing, the driver drives a line which is terminated by a short ( $R_L \approx 0$ ). Hence, there exists a path for the current to flow and the sensing circuit at the end of the line has to detect this current to determine the signal value.

Fig.22 Theoretical current-mode signal model

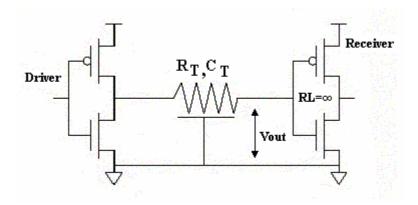

As shown in Fig.23, the conventional way of signaling is voltage-mode. An inverter acting as a driver drives interconnect which builds up a voltage at the end of the line. Since the line ends in the gates of the transistors,  $R_L \approx \infty$ . The voltage sensing circuit is another inverter and since the MOS transistors have voltage thresholds to turn them on or off, the output of the inverter depends on the voltage at its gate. The biggest challenge in current-mode signaling is to design an efficient sensing circuitry, which detects the change in current. A normal driver can be used to drive interconnect and to drive current instead of voltage,

Fig.23 CMOS representation for a voltage-mode signal model

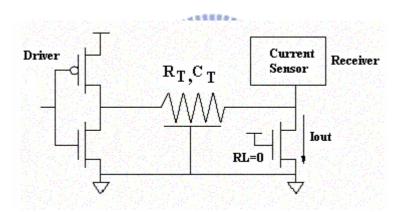

and the end of the line should provide a path to ground. Thus, a current-mode sensing setup would look like the one in Fig.24.

Fig.24 CMOS representation for a current-mode signal model

The main difference between the current-mode and voltage-mode signaling is the termination of interconnect. In the case of current-mode, the termination resistance is very small; while in the case of voltage-mode, it is very large. Since current is used as a mode of signaling in current-mode and there should be a path to ground from driver, static power dissipation is expected in current-mode signaling. Also the receiving (sensing) circuit is complex in current-mode as MOS

transistors don't have a current threshold.

Also since there is a low impedance path to the ground at the end of the line, the capacitance of interconnect is not charged to Vdd but to an intermediate value. Since the sensing current in MOS is not very trivial, most of the current-mode sensing is done differentially. This may require some synchronizing (precharging or pre-equalizing) signal.

#### 4.2.2 Voltage-Mode and Current-Mode Signal Delay

The use of current sensing amplifiers has a number of benefits over voltage sensing amplifiers. The most important ones are significant reductions in bit-line voltage swing and major reductions in sensing delays [58]. These benefits translate to lower dynamic power consumption and increased sensing speed. The key to these improvements lies in the low input resistance of the current sensing amplifier. This becomes evident when examining the equivalent sensing circuit in Fig.25.

Fig.25 A long interconnect model

In this model, we assumed that the output current is a linear-ramp signal as shown in Eq. (4-1), i.e.,

$$i_o = p_o(t - \delta t) \tag{4-1}$$

where  $i_o$  is the output current,  $p_o$  is the constant slope, and  $\delta t$  is the delay.

The analysis shows that the delay for a line is given by the following equation:

$$\delta t = \frac{\left(R_T \cdot C_T\right)}{2} \cdot \left(\frac{R_B + \frac{R_T}{3} + R_L}{R_B + R_T + R_L}\right) + R_B C_T \cdot \left(\frac{R_L}{R_B + R_T + R_L}\right)$$

(4-2)

where  $R_T$  and  $C_T$  are the total bit-line resistance and capacitance.

A voltage mode signal path, the RC line modeled in the above circuit is open circuit, it means that the resistor  $R_L$  is extremely large. When  $R_L$  >>  $R_B$ , it can be assumed to be infinite in the above equation. Therefore, the time constant can be given by:

$$\delta t = \frac{(R_T \cdot C_T)}{2} \cdot \left(1 + \frac{2R_B}{R_T}\right)$$

(4-3)

When we consider a current mode signal path behavior, the output loading of the long interconnect line is always a low resistance (ideally zero). Therefore, the  $R_L$  modeled in Eq. (4-1) can be ignored, so the time constant can be given by :

$$\delta t = \frac{(R_T \cdot C_T)}{2} \cdot \left( \frac{R_B + \frac{R_T}{3}}{R_B + R_T} \right)$$

(4-4)

Fig.26 shows a comparison of voltage-sensing and current-sensing, Eq. (4-3) and Eq. (4-4). The figure shows that the current-sensing has less delay as compared to the voltage sensing. Actually, the load resistance for

current-sensing is not zero and so the effect of non zero load resistance should be studied. Fig.27 shows a comparison of the current-sensing with different load resistances.

Fig.26 Comparison of voltage sensing and current sensing

Fig.27 Comparison of voltage sensing and current sensing with different values of load resistance

As expected, an increase in load resistance increases the delay in the current-sensing technique, but the increase is not very significant for low resistance of interconnect and/or low resistance of the driver. The plots show that the delay in both current-sensing and voltage-sensing technique increases quadratically with respect to the length of the line (represented by the resistance of the line in the plots).

When we consider the long interconnect line signal path delay, we assume the source resistance is  $1k\Omega$ , and total capacitance distributed in the line is 1pF, and the total resistance of the line is  $100\Omega$ . The time constant of voltage mode signal path is 1.05ns. For the same assumption in current mode signal path, the time constant can be estimated to be 0.047ns.

We makes another approximation, since  $R_B >> R_T$ , the delay for voltage-mode can be approximated as  $R_B C_T$ . Also, the delay for current-mode can be approximated as  $R_T C_T / 2$  and since  $R_B >> R_T$  current-mode is faster than voltage mode.

A plot for comparing the voltage-mode and current-mode delay is shown in Fig.28.

Based on the above analysis, if the capacitance loading is independent, the time constant of long interconnection line can be reduced by reducing the loading resistance  $R_L$ . When the next stage is a voltage-mode circuit, it is always working as a capacitance loading. Therefore, the loading resistance is much larger than resistance in line. This method will make long delay time in signal transportation. In order to shorten the time constant in long interconnect line, we can make

Fig.28 Comparison of voltage-sensing and current-sensing with approximations

next stage to be a current mode circuit. By this way, the loading  $R_L$  can be reduced to lower than the line resistance. Even they are the same order; the delay time in long line can be shorten to one order or more little. Hence, this low resistance input node for next stage can speed up the signal delay time, which pass through the long interconnects line.

#### 4.3 Voltage-Mode Sense Amplifier

Voltage-mode sense amplifiers have been known for a long time, the simplest voltage sensing amplifier is the differential couple [2]. Fig.29 shows a schematic diagram of a simple differential couple with its inputs and outputs labeled. During a read, the input nodes ( $V_{IN+}$  and  $V_{IN-}$ ) would be pre-charged to  $V_{PRE}$ , causing the output nodes ( $V_{OUT+}$  and  $V_{OUT-}$ ) to

stay at the same level. The read-selected cell would then be asserted and a small voltage swing would appear on the bit-lines. This small voltage swing would then be amplified by the differential couple and later used to drive digital logic

Fig.29 Simple differential couple schematic

Another version of a voltage sense amplifier which has enjoyed a wide usage is the full complementary positive feedback differential sense amplifier. This voltage sense amplifier has a very large differential gain and the added ability to automatically rewrite destructive read data [59]. Fig.30 shows the schematic diagram of the full complementary positive feedback amplifier.

The positive feedback amplifier has two data nodes  $V_{IN/OUT1}$  and  $V_{IN/OUT2}$  and three control nodes  $SAN_{EN}$ ,  $SAP_{EN}$  and PRE. Nodes  $V_{IN/OUT1}$  and  $V_{IN/OUT2}$  act as both input and output to the sense amplifier. Its operation is as follows: 1) the data nodes are equalized using PRE; 2)the memory cell being read is asserted and a small voltage difference forms on nodes  $V_{IN/OUT1}$  and  $V_{IN/OUT2}$ ; 3) while MN1 and MN2 are biased to be operated

Fig.30 Full complementary positive feedback amplifier schematic

in the saturation region, MN6 is turned on by  $SAN_{EN}$ ; 4)as both  $V_{IN/OUT1}$  and  $V_{IN/OUT2}$  are decreased in voltage, so is the difference between them; 5) one of them decreases much faster than the other and causes MN(1or2) to enter cutoff while the other starts operating in triode; 6) at this point MP5 is turned on by  $SAP_{EN}$  which pulls the signals rapidly apart; 7) at this point since  $V_{IN/OUT1}$  and  $V_{IN/OUT2}$  are directly connected to the bit-lines, the data is automatically written to the destructively read memory cell. Due to its positive feedback, this voltage sensing amplifier achieves a very high differential gain. This high gain minimizes sensing time by being able to sense small voltage swings on the bit-line. However, since the bit-line capacitance is growing along with memory capacity, the bit-line voltage swing is becoming smaller and more power expensive to produce. There also exists a practical limit to this decreasing voltage swing. When the bit-line voltage swing reaches the same magnitude as bit-line noise, the voltage sense amplifier will become unusable.

Therefore, to achieve the preset objectives of large memory capacity, high speed, and low power, a new type of sense amplifier is needed.

## 4.4 Clamped Bit-Line Sense Amplifier

A commonly used current mode sensing amplifier is the clamped bit-line sense amplifier [58] shown in Fig.31. By clamping the voltage on the bit-line to a stable voltage ( $V_{REF}$ ), the signal current produced by the cell can be transferred to an internal sense amp node without charging/discharging the large bit-line capacitance. As a result, both sensing delay and dynamic power consumption are significantly decreased.

Fig.31 Clamped bit-line sense amplifier

This sense amplifier uses three pre-charge and equalization transistors (M7, M8 and M9), two current sensing transistors (M5 and M6)

and four back to back inverter configuration transistors for the voltage output stage (M1, M2, M3, M4). Its operation follows two stages pre-charge/equalization and sensing. The following is the timing schedule:

1) transistors M7, M8, and M9 are turned on to pre-charge and equalize the sensing nodes; 2) transistors M7 and M8 are turned off and the memory cell accessed; 3) the current from the cell starts being sourced by one of the transistors M1 and M2 and a voltage difference starts forming on one of the output nodes; 4) this voltage is further amplified by the positive feedback amplifier until it reaches the latched state.

It has been shown that the time response of a latch formed by cross-coupled inverters is directly related to the AC small signal gain bandwidth (GBW) product of the inverters. Maximizing GBW product maximizes the speed of the sense amplifier. By examining both small signal models for the positive feedback cross-coupled voltage sense amplifier and the clamped bit-line current sensing amplifier, we can derive the following GWBs:(a) voltage sensing and (b) current sensing GWB:

a)

$$GBW_{VS} = \frac{g_m}{C_{RL}}$$

b)  $GBW_{CS} = \frac{g_m}{C_d}$

Since  $C_d \ll C_{BL}$ , it can be easily seen that the current mode sense amplifier enjoys a much higher speed. Another observation is that this amplifier is bit-line capacitance insensitive maintaining a constant speed over increased bit-line capacitance.

To recognize the power savings associated with the switch to current sensing amplifiers, we need to examine the dynamic power dissipation of the voltage sensing amplifier. In voltage sensing, the bit-line are discharged and charged by  $dV_{BL}$ (close to 400mV) for every read operation. When this  $dV_{BL}$  is combined with both increasingly large bit-line capacitance  $C_{BL}$  and read frequency " $f_{read}$ ", the energy following below equation becomes large [60]:

$$P = f_{read} * C_{BL} * V_{BL}^2$$

.

The current sensing amplifier on the other hand has a very negligible voltage swing, thus nearly eliminating dynamic power dissipation. Furthermore, this bit-line voltage inactivity significantly decreases cross talk between bit-lines, and supply voltage drop associated with bit-line charge-up.

# 4.5 New Current-Mode Sense Amplifier

The sensing speed of the current mode sense amplifier is faster than conventional voltage sense amplifier and is independent of the bit-line and data-line capacitances. For conventional sense amplifier, because the input nodes connect the bit line or data line, the reading access speed is always dependent of the bit-line and data-line capacitance. This will be a difficult problem to solve due to the more and more cells parallel connect in bit line that always makes a large bit line loading. As the store capability in memory grows up, the number of cell increased in the memory can not be avoided. If we need reading data of cell in a short time, the number of switch that selects the current column can not be increased, it means that the column number must be reduced, at this time, the cells parallelly connected in the bit-line increase. Loading a large bit-line capacitance makes the RC time constant delay extremely larger and the speed of sense

amplifier pulls down as capacitance increases. Due to the low impedance of current-mode sense amplifier, the signal from the memory cell can be injected into the sense amplifier with only minimal charging or discharging of the bit-line capacitance. As a consequence, the voltage change in the bit line during the sense portion of a cell read access is extremely low, eliminating the source of most voltage noise coupling problems and minimizing power supply bounce during sensing.

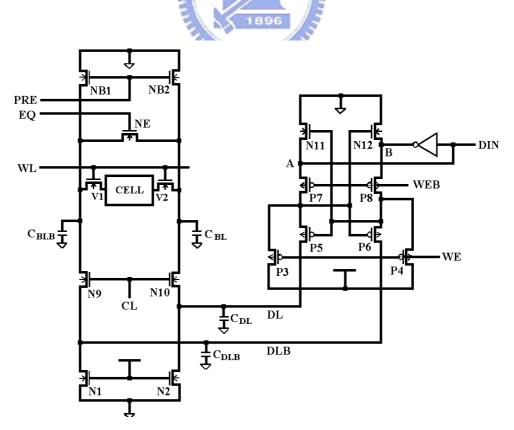

## 4.5.1 Circuit Description and Operation

In this section, the new current-mode sense amplifier is proposed. The operation power of reading access cycle is less than that of conventional current-mode sense amplifier and the speed is extremely high. Fig.32 presents the read data path of an n-type separated flip-flop current-mode sense amplifier. The N5-N6 and P1-P2 are made in a manner similar to positive feedback latches. N1 and N2 connect the input nodes and pull down the data-lines close to the ground level. The transistors N7 and N8 are the separating transistors, and the transistors N3 and N4 are the equalization transistors. The bit-line and data-line capacitances are represented by C<sub>BL</sub> and C<sub>DL</sub>, respectively, and WL and CL are the word-line and column-line selector signals, respectively. The inputs to the current-mode cross-coupled latch are at the sources of the transistors N5 and N6. The low impedance at the input nodes causes the current signals at the data-lines to be injected into the cross-coupled latch without charging or discharging the data-line capacitances. Hence, the sensing speed is insensitive to both the bit-line and the data-line capacitances.

Fig.32 A current-mode sense amplifier and a simplified data path circuit

1896

Before beginning the sensing operation, the same as the conventional sense amplifier, the bit-lines need to be equalized to the same voltage level. In this design, we pull down the bit-line voltage to the ground level, which is different from the conventional SRAM's.

When the sense amplifier is in the standby state, the signal "SENB" is at high-level and the signal "SEN" is at low-level. Under this condition, N3 and N4 are on, so they pull down the drains of the N5 and N6 to low-level. Hence, N5 and N6 are in the cut-off state, and P1 and P2 operate in the linear region, since their gate voltages are at low-level. The "SEN" is at low-level, so N7 and N8 are in the cut-off state, therefore, no current flows through N7 and N8. At the time, the voltage at the output nodes of the sense amplifier (node A and node B) are equal to the power supply voltage, the input nodes are at zero volts, and the latch nodes (the

drains of N5 and N6) are discharged to low-level. Hence, in the standby state, no DC current flows in the sense amplifier.

During the read operation, both WL and CL lines are activated. The "SENB" is at low-level, and so turns off N3 and N4; and the "SEN" is at high-level, the separated flip-flop is turned on. When a particular memory cell is accessed, a differential current signal appears at the DL and DLB of the common data-lines. N5 has a lower V<sub>GS</sub> than N6, so the voltage at node A exceeds the voltage at node B. Moreover, the amplifier with cross-coupled configuration implies that the source to gate voltage of P2 is less than that of P1. The current that flows into node A will therefore be much higher than the current that flows into node B. The voltage at node A then increases further and the voltage at node B decreases. The separated flip-flop is a positive feedback loop, which regenerates the voltage to full swing and latches the voltage, and the response time of the flip-flop is very short, since the capacitance of the output node is very small.

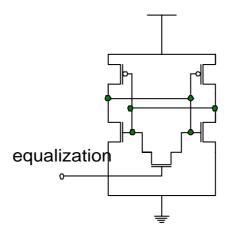

Besides, the different points from conventional current sense amplifier are the equalization transistors N3, N4, and the special positive latch structure with separated transistor N7, N8. In conventional design, for example, CBLSA or hybrid mode sense amplifier always uses only one NMOS transistor which connects the two output nodes as an equalization transistor. For this method, when equalizing signal rise high, the NMOS turns on to equalize the charge between the two output nodes. Assume the beginning voltage levels of the output nodes are supply voltage and ground level. After the equalization stops, the voltage is the half of the supply voltage. In this condition, the transistors that combine the positive feedback latch always turn on due to their gate-source voltage is larger than their threshold voltage. Hence, there is a static current flow through from power supply node to the ground. This static current makes

the power consumption at the operation state increase as the equalization time increases. Moreover, use only one NMOS for equalization transistor, the operation of output nodes charges redistribution like two same size capacitance, so that NMOS must be large to speed up the equalization time. Not only it will slow down the equalizing state, but also the loading in the equalizing signal increases.

To avoid the static current flow through and speed up the equalizing time, N7 and N8 separate the latch nodes and output nodes. And the N3, N4 are used to substitute for only one transistor. During equalizing situation, N7 and N8 turn off to cut the current flow down from P1 and P2. N3 and N4 open to pull down the latch nodes to ground. Because the capacitance of ground is larger than the capacitance of the latch nodes, the equalizing time can be reduced, and the sizes of N3 and MN4 are much smaller than conventional transistor. The voltages of latch nodes are zero volts, so the transistors N5 and N6 are all at cut off region. Hence, the current flow through P1 and P2 is stopped. Transistor N7 and N8 separate the output nodes and latch nodes, the output capacitance won't affect the latch node. Although the output capacitance is large, the capacitance in the latch nodes is still very small due to only one gate load connects, so that the latch operation is insensitive to output capacitance, and the smaller latch capacitance makes the latch time short.

When the sense amplifier equalizes, the latch nodes connect to ground, the output nodes connect to supply voltage, and the input nodes connect to ground. In this circuit structure, every node is connected to constant voltage, so that there is no floating node at the sense amplifier at standby state. This no floating node condition will make the noise inject reduced.

As discussed above, the new current mode sense amplifier can reduce the operation power consumption by the separate transistor and equalize the latch nodes to ground. And the voltage gain of the output nodes can be increased by exponential function to achieve high-speed reading access cycle.

#### 4.5.2 Simulation Results

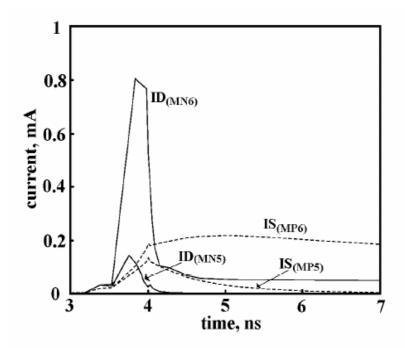

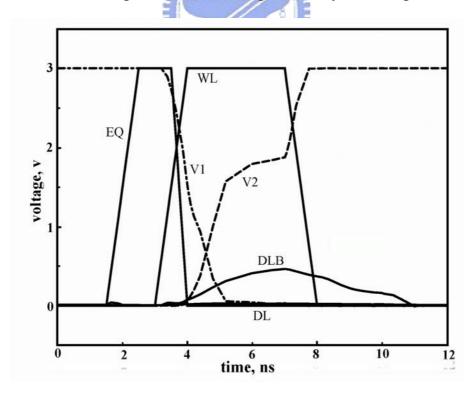

Extensive circuit simulations, using HSPICE, were performed to confirm the operation of circuit and characterize its performance. The simulation results are based on rise and fall times of 1ns. During the read cycle, differential current signals appear at the common bit-lines, as shown in Fig.33. Since no differential capacitance discharging is required to sense the cell data, these currents are almost transported instantaneously to the data-lines. The data-line voltages are kept low and equal by N1 and N2, and this eliminates the need for data-line equalization during the read access. Owing to the small capacitances at node A and B, the response speed of the new current-mode sense amplifier is very fast.

The key voltages during the read operation are shown in Fig.34. When the sense amplifier is equalized, the two outputs are pulled up to supply voltage because the latch nodes are in ground level. The voltage differences at the bit-lines and data-lines are indeed very small (about 50mV) and close to the ground level, thus reducing the power dissipation. The positive feedback effect of the proposed current-mode sense amplifier very rapidly amplifies the differential voltage between nodes A and B to the CMOS logic level.

Fig.33 Simulated current waveforms of the new current-sensing data path circuit

Fig.34 Simulated waveforms of the new current-sensing data path circuit

From the simulation results, the new current mode sense amplifier can reduce the operation power by two concepts. First is to use the current mode sensing to substitute for voltage mode sensing, and second is to use the separation transistor to reduce current flow during equalization state of sense amplifier. Due to positive feedback characteristic of the cross-couple pair in the sense amplifier, the sensing speed can be very fast. Hence, the low operation power and high speed sense amplifier can be implemented.

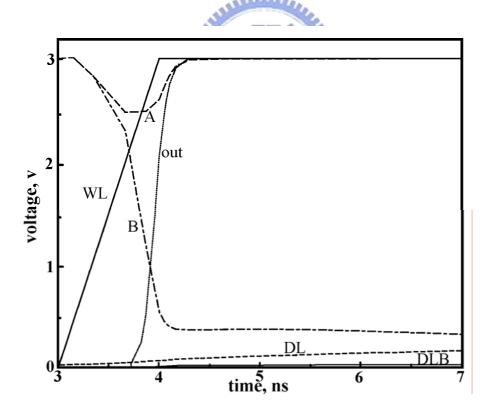

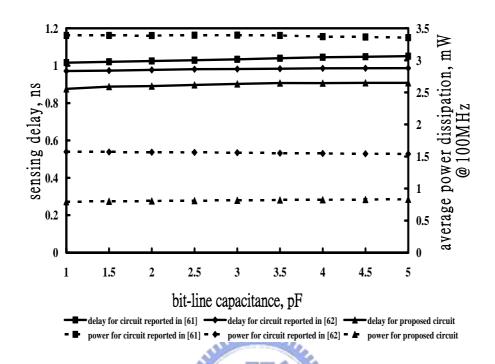

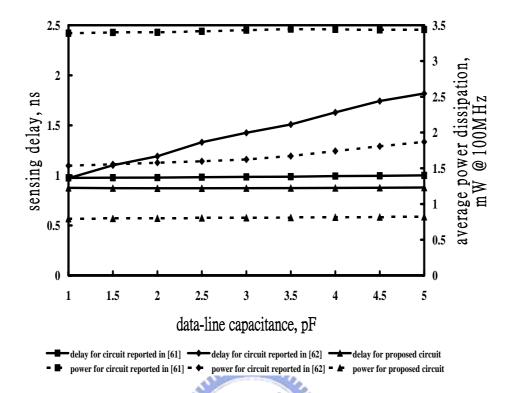

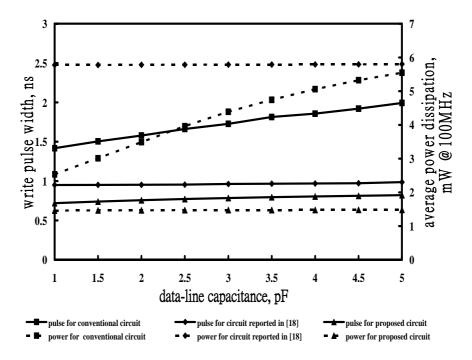

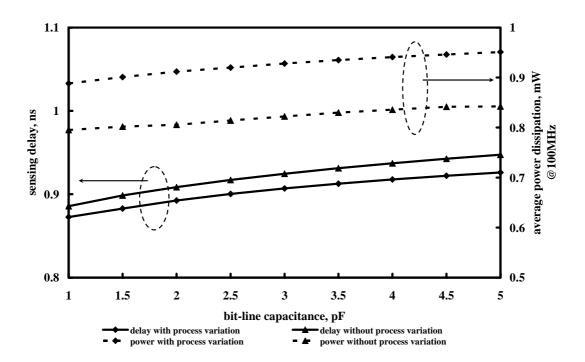

The performance of the proposed circuit is evaluated and compared with that of the hybrid current-mode sense amplifier [61] and the cross-coupled current-mirror sense amplifier [62] based on 3V, 0.35um technology. The simulations were carried out on the proposed current sense amplifier circuit, by sizing the transistor compared to the previous circuits. Fig.35 shows the effect of bit-line capacitances on both sensing delay and average power consumption at a frequency of 100 MHz and data-line capacitances of 1pF. Here, the sensing delay is the interval between the time when a word line becomes high and the time when the memory cell data is read and amplified to the CMOS level. All the circuits are insensitive to the bit-line capacitances, but the proposed circuit senses more quickly. The power consumption is determined from the current drawn by the read data path circuit. The average power consumption of the proposed circuit during a read operation is also less than that of the circuits in [61] and [62]. Before the read operation, the sense amplifier is in the standby state, and the transistors of the flip-flop in [61] and [62] are all turned on, increasing power dissipation. However, N7 and N8 of the proposed sense amplifier isolate the flip-flop, so no DC

current path exists.

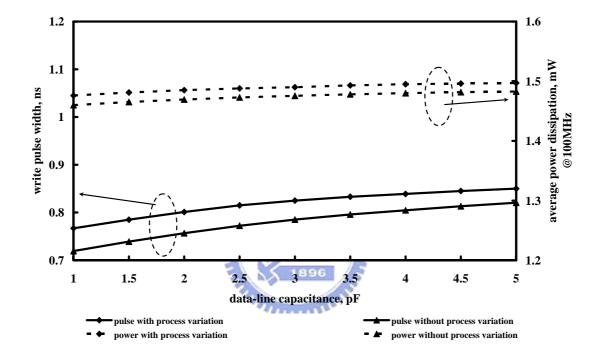

Fig.35 Sensing delay and average power dissipation versus bit-lines capacitance