## Chapter 4

# Reliability Study of Poly-Si TFTs with Multiple Nanowire Channels under DC and AC Hot-Carrier Stress

#### 4.1 Introduction

In recent years, polycrystalline silicon thin-film transistors (poly-Si TFTs) have drawn much attention because of their widely applications on active matrix liquid crystal displays (AMLCDs) [1], and organic light-emitting diodes (OLEDs) [2]. Except large area displays, poly-Si TFTs also have been applied for memory devices such as dynamic random access memory (DRAM) [3], static random access memory (SRAM) [4]. However, reliability of ploy-Si TFT is one of the main constraints toward this direction. In comparison with single-crystalline silicon, granular structure of poly-Si is rich in grain boundary defects arising from lattice discontinuities between different oriented grains as well as intra-grain defects. Moreover, a low process temperature, i.e. less than 600 °C, also produces numerous defects at the poly-Si\SiO<sub>2</sub> interface and poly-silicon boundaries. Under the operation of high drain voltage and a relatively high gate voltage (hot-carrier condition), the defects acting as trapping centers lead to hot-carrier injection that generates trap states. Thus, those generated trap states are strongly influenced the performance of poly-TFTs and causes severe device characteristics degradation, such as threshold voltage (Vth), subthreshold swing (SS), ON current (Ion), and transconductance (Gm). The Gm degradation and Vth variation during stress application which results in improper operation and circuit failure is of great importance for circuit designers in order to integrate TFTs in flat-panel displays or VLSI circuits. In AMLCD application, unlike pixel TFTs, TFTs in the driver circuits are subject to high-frequency voltage pulses [5]. The degradation behavior under dynamic stress is closer to real operation condition than the static stress. Therefore, improvement of TFTs degradation under dynamic stress is most important requirements in realization of system-on-panel (SOP).

Accordingly, the reliability of poly-Si TFTs under dc [6]-[9], and ac [10]-[12] stress has been investigated. However, to our knowledge, improvement of poly-Si TFT degradation under ac stress by device structure modulation has not been addressed. Therefore, in this work, we develop a poly-Si TFT with ten nanowire channels and LDD structure to study the degradation mechanism; also a single-channel poly-Si was fabricated for comparison.

## 4.2 Poly-Si TFTs Hot-Carrier Stress effect theory background

#### **4.2.1 Static Hot-Carrier Stress**

According to the operation of poly-TFTs with grain boundary defects and intra-grain defects in Poly-Si film and a large number of interface states at the poor

SiO<sub>2</sub>/poly-Si interface, most of the applied voltage drops across the grain boundaries since they have much larger resistances than the grains. The lateral electric field in the grain boundaries will be much higher than in the grains, and at large drain voltages, impact ionization may occur. Thus, unlike to the hot-carrier effect in MOSFETs, the poly-Si TFT electrical parameters such as threshold voltage (V<sub>th</sub>), maximum transconductance (G<sub>m.max</sub>), ON current (I<sub>on</sub>), and subthreshold slope (SS) could depend on grain, grain boundaries, and/or interface properties. The deep traps existing in grain boundaries have been demonstrated to affect mainly threshold voltage and much less G<sub>m,max</sub> [13], [14]. On the other hand, tail states from grain regions in the interface and/or from grain boundaries mainly contribute to the decrease of gm max [15]. The subthreshold slope depends mainly on intra-grain traps distributed uniformly inside the poly-Si film and also on the deep interface states [16]. Therefore, it is obvious that depending on the nature of state generation after stress, electrical parameters can provide useful information in order to clarify poly-Si TFTs degradation under hot carrier stress conditions. These points are systemically summarized on the Table I [8].

Moreover, the poly-TFTs' non-ideal effect, Kink effect, which is due to the holes injected and stored in a floating body to cause the reduction of the threshold voltage and a parasitic bipolar element is resulting in positive-feedback effect to enhance the

generation of the hot-carriers [16]. This kink effect associated with float-body is especially dramatic for n-channel devices, because of the higher impact-ionization rate of electrons.

#### **4.2.2 Dynamic Hot-carrier Stress**

Dynamic stress is closer to real operation condition than the static stress. It is reported that the reliability evaluation method proposed under the static stress conditions may not be suitable for the reliability evaluation under the dynamic stress [10]. According the pervious reports, the dynamic stress degradation mainly depends on the stress frequency (f), stress temperature, and falling time (Tf) [10]-[12], [17]. The dynamic stress degrades the poly-Si TFT more seriously than the static stress. The impact ionization generation hot electrons and hot holes near drain at ON state. However, as the device is changed from ON state to OFF state, the drain avalanche hot carrier will occur to cause serious degradation and generate more hot electrons and hot holes near drain [10]. At the switching period, a transient current (I = C dV/dt) can be observed to damage the device, and degradation is mainly dependent on falling time rather than rising time [17].

#### 4.3 Device structure and fabrication

The single-channel and ten-nanowire channel poly-Si TFT structure and theirs fabrications are the same as described in chapter 3.2.

## 4.4 Results and discussion

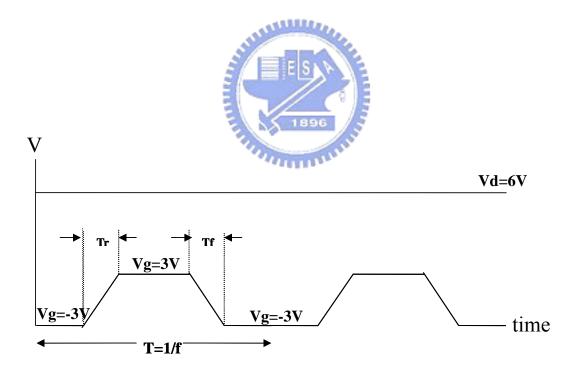

The static hot carrier stress condition is determined at kink-effect occurrence, Vd = 6 V and Vg = 3 V, and the source potential is common. The dynamic pulse train stress is defined at constant Vd = 6 V and dynamic Vg = 3 V (ON), -3 V (OFF) with the duty cycle of 50%, and the source potential is grounded. The waveform of the pulse train is shown in Fig. 4-1. In this section, we discuss the device reliability after a series of stress frequency (f), rising time (tr), falling time (tf) and substrate temperature (T) conditions.

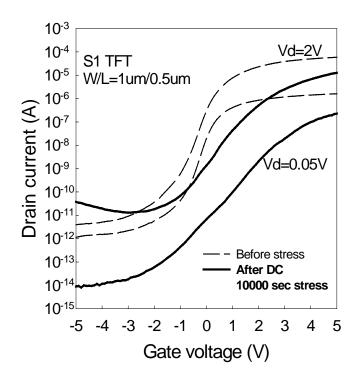

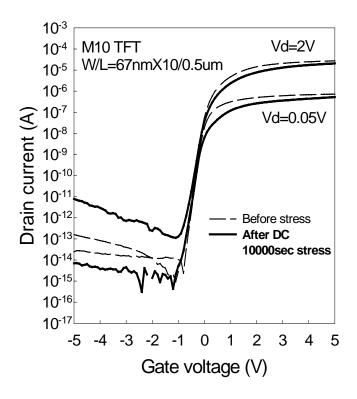

Fig. 4-2 (a) depicts typical M10 poly-Si TFT  $I_d$ - $V_g$  curves before and after dc hot carrier stress at 10000 second. Fig.4-2 (b) depicts typical S1 poly-Si TFT  $I_d$ - $V_g$  curves before and after dc hot carrier stress at 10000 second.

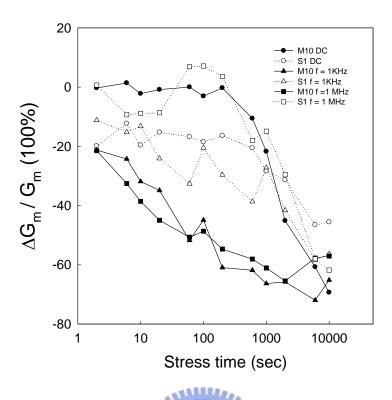

Figure 4-3 depicts maximum conductance (Gm,max) degradation of S1 and M10 TFT as a function of the stress time with different frequencies (dc, f = 1K Hz, and f = 1M Hz). The S1 and M10 TFT show the similar Gm degradation. These results reveal that the S1 and M10 have similar tail state generation.

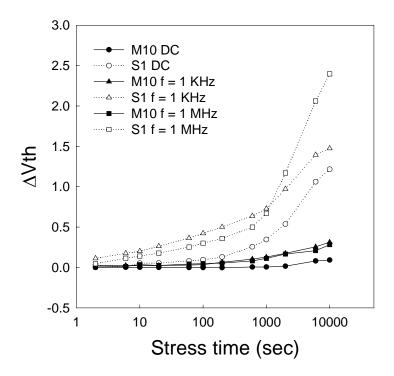

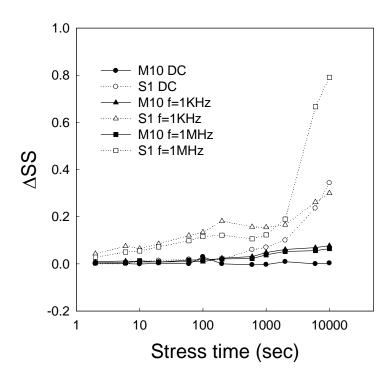

Figure 4-4 and 4-5 depict the threshold voltage and subthreshold swing variation of S1 and M10 TFT as a function of the stress time with different frequencies, respectively. For M10 TFT the Vth and SS variation is much lower than the S1 TFT. According to table I, these results indicate that the M10 TFT has less deep states

generation after dc and ac stress. Firstly, the M10 TFT has more effective NH<sub>3</sub> plasma passivation than that of S1 TFT due to the ten split nanowire channels of M10 TFT has wide NH<sub>3</sub> plasma passivation area. Secondly, M10 TFT has robust tri-gate control, thus the additional two side-gate surface scattering (Fig. 3b) reduce the hot carrier effect. Therefore, the deep-states generation of M10 TFT by the hot carrier impaction is lower than which of S1 TFT. Notably, for S1 TFT, the Vth and SS variation increase with the frequency increasing from 1 K Hz to 1 MHz. These results reveal that the device reliability is strongly dependent on the transient current Id (displace current).

$$I_d = C_{ox} \cdot \frac{dV_g}{dt} \approx C_{ox} \cdot f \cdot \overline{V_g}$$

where f is frequency,  $\overline{V_g}$  is average gate voltage.

Thus, the transient current induced hot carrier is dependent on the frequency.

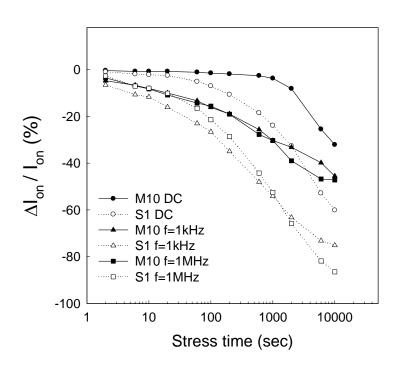

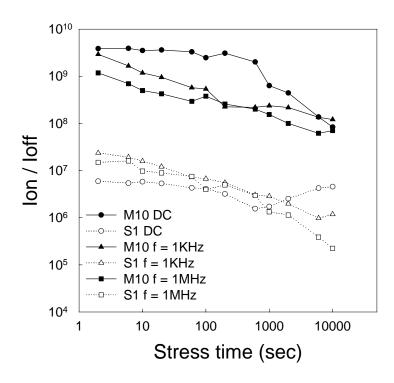

Figure 4-6 and 4-7 depict the ON current (I<sub>ON</sub>) variation and ON/OFF ratio of S1 and M10 TFT as a function of the stress time with different frequencies, respectively. The M10 TFT shows lower  $I_{\text{ON}}$  variation than S1 TFT. These results reveal that the S1 TFT has high Vth variation and increase with the frequency increasing. Thus, the I<sub>ON</sub> of S1 TFT is much lowering than that of M10 TFT. For the ON/OFF ratio, although the S1 and M10 TFT have the similar degradation behavior, the ON/OFF ratio of M10 still remains exceed 10<sup>8</sup>, under different frequencies.

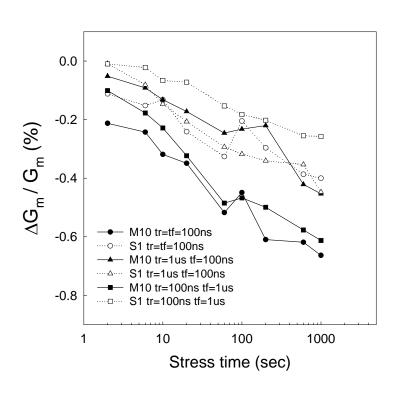

Figure 4-8 depicts Gm degradation of S1 and M10 TFT as a function of the stress time with different rising time (Tr) and falling time (Tf) under the frequency of 1 KHz.

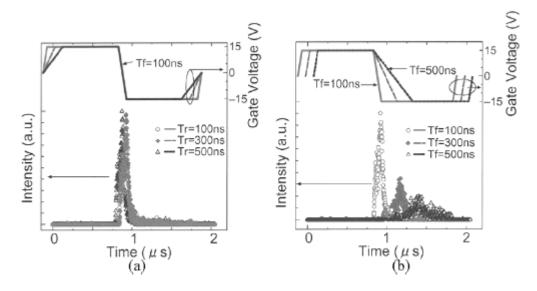

For S1 TFT (dash-line) with the same falling time of 100 ns, the S1 TFT has the similar Gm degradation. However, for the same rising time of 100 ns, as the falling time increasing from 100 ns to 1 us, the Gm degradation is reduced from 40% to 20% at the stress time at 1000 second. These results reveal that the device reliability is strongly dependent on the transient current. According to the Uraoka et al. report [17], only the transient current induced by the falling period would cause more damage near the drain. Figure 4-9 indicates clearly that the amount of the hot carriers generated depends on the pulse falling time. Therefore, using the dynamic stress with longer falling time will be helpful for the reliability improvement in the poly-Si TFTs. On the other hand, for M10 TFT, however the Gm degradation dependent on falling time is not significant. These results indicate that M10 TFT has highly effective NH<sub>3</sub> plasma passivation and robust tri-gate control to screen the transient current hot carrier effect, which induced by the falling period.

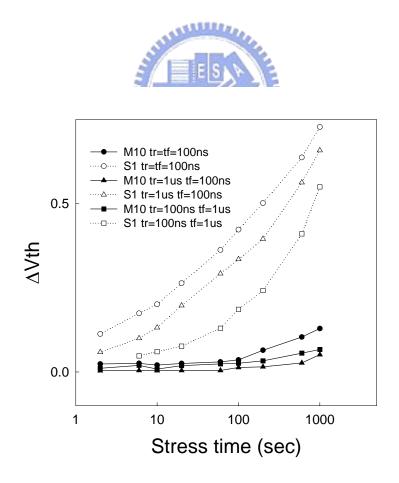

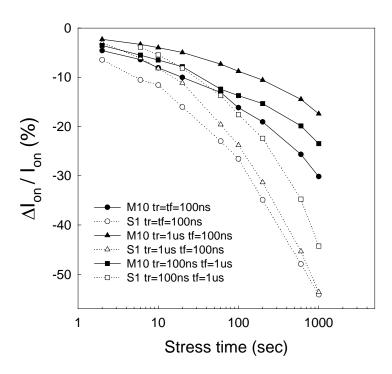

Figure 4-10 and 4-11 depicts Vth variation and ON current (Ion) degradation of S1 and M10 TFT as a function of the stress time with different rising time (Tr) and falling time (Tf) under the frequency of 1 KHz. For the same reason, the Vth variation and ON current (Ion) degradation of S1 TFT (dash-line) is highly dependent on the falling time rather than rising time. As the falling time increasing from 100 ns to 1 us, the Vth variation and ON current (Ion) degradation are reduced. Again, M10 TFT has

highly effective NH<sub>3</sub> plasma passivation and robust tri-gate control to screen the transient current hot carrier effect, which induced by the falling period.

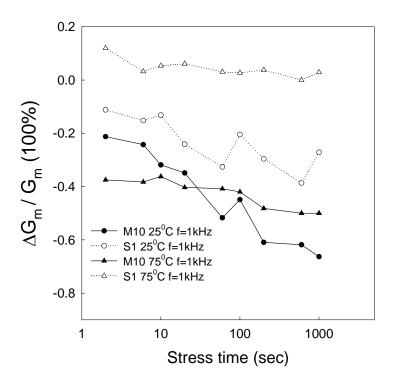

Figure 4-12 depicts Gm degradation of S1 and M10 TFT as a function of the stress time with different subtract temperature with  $25^{\circ}$ C, and  $75^{\circ}$ C under the same frequency of 1 KHz, and the same Tr = Tf =100 ns. For both S1 and M10 TFT, the Gm degradation is reduced with the temperature increasing from  $25^{\circ}$ C to  $75^{\circ}$ C. These results reveal that hot carrier effect is reduced with the temperature increasing. As the temperature increasing, the mean free path ( $\lambda$ ) [18] is decreasing.

$$\lambda = \lambda_0 \cdot \tanh(\frac{E_P}{2kT})$$

Thus, that hot carrier energy is reduced as the mean free path ( $\lambda$ ) is decreasing.

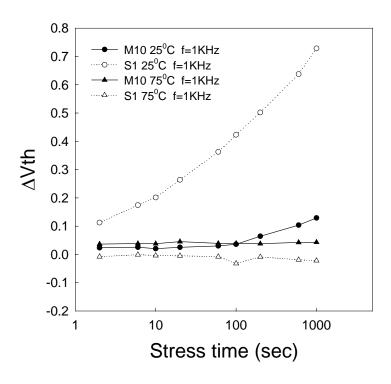

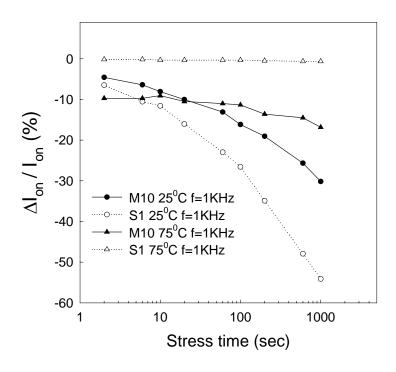

Figure 4-13 and 4-14 depicts Vth variation and ON current (Ion) degradation of S1 and M10 TFT as a function of the stress time with  $25^{\circ}$ C, and  $75^{\circ}$ C under the same frequency of 1 KHz, and the same Tr = Tf =100 ns. For both S1 and M10 TFT, the Vth variation and ON current (Ion) degradation is reduced with the temperature increasing from  $25^{\circ}$ C to  $75^{\circ}$ C. For the same reason, hot carrier effect is reduced with the temperature increasing as the mean free path ( $\lambda$ ) decreasing.

### 4.5 Conclusion

The performance and ac and dc reliability of multiple nanowire poly-Si TFTs are investigated. The experiment results reveal that the multiple nanowire poly-Si TFTs

has higher performance than single-channel TFT, including a high ON/OFF current ratio, a low subthreshold slope, an absence of DIBL and favorable output characteristics. In static and dynamic hot-carrier stress experiments, the multiple nanowire poly-Si TFTs reduces the degradation of Vth, SS, Ion, On/OFF ratio and DIBL, for all kind of frequency, rising time, falling time and temperature, compared to single-channel TFT. These high reliability results of multiple nanowire poly-Si TFTs can be explained by its robust tri-gate control and its superior channel NH<sub>3</sub> passivation on the poly-Si grain boundary. The fabrication of this novel multiple nanowire channels structure TFTs is easy and involves no additional processes. Such TFTs are thus highly promising for use in future high-performance poly-Si TFT applications.

#### **References:**

- [1] H. Oshima and S. Morozumi, "Future trends for TFT integrated circuits on glass substrates," IEDM Tech. Dig., 157, 1989.

- [2] M. Stewart, R. S. Howell, L. Pires, and M. K. Hatalis, "Polysilicon TFT technology for active matrix OLED displays," IEEE Trans. Electron Devices, vol. 48, pp. 845-851, 2001.

- [3] H. Kuriyama et al., "An asymmetric memory cell using a C-TFT for ULSI SRAM," Symp. On VLSI Tech., p.38, 1992.

- [4] T. Yamanaka, T. Hashimoto, N. Hasegawa, T. Tanala, N. Hashimoto, A. Shimizu, N. Ohki, K. Ishibashi, K. Sasaki, T. Nishida, T. Mine, E. Takeda, and T. Nagano, "Advanced TFT SRAM cell technology using a phase-shift lithography," IEEE Trans. Electron Devices, Vol. 42, pp.1305-1313, 1995.

- [5] Y. Uraoka, T. Hatayama, T. Fuyuki, T. Kawamura, Y. Tsuchihashi, "Reliability of low temperature poly-silicon TFTs under inverter operation," IEEE Trans. Electron Devices, Vol. 48, pp.2370-2374, 2001.

- [6] S. Inoue and T. Shimoda, "Investigation of the relationship between hot-carrier degradation and kink-effect in low-temperature poly-Si TFTs," in SID Tech. Dig., pp. 452-455, 1999.

- [7] I. W. Wu, W. B. Jackson, T. Y. Huang, A. G. Lewis, and A. Chiang, "Mechanism of device degradation in n- and p-channel polysilicon TFTs by electrical stressing," IEEE Trans. Electron Device Lett, vol. 11, pp. 167-169, 1990.

- [8] F. V. Farmakis, J. Brini, G. Kamarinos, and C. A. Dimitradis, "Anomalous turn-on voltage degradation during hot-carrier stress in polycrystalline silicon thin-film transistors," IEEE Electron Device Lett, vol. 22, pp. 74-76, 2001.

- [9] F. V. Farmakis, C. A. Dimitradis, J. Brini, G. Kamarinos, V. K. Gueorguiev,

- and T. E. Ivanov, "Interface state generation during electrical stress in n-channel undoped hydrogenated polysilicon thin-film transistors," Electron Lett., vol. 34, pp. 2356-57, 2001.

- [10] K. M. Chang, Y. H. Chung, G. M. Lin, C. G. Deng, and J. H. Lin, "Enhanced degradation in polycrystalline silicon thin-film transistors under dynamic hot-carrier stress," IEEE Electron Device Lett, vol. 22, pp. 475-477, 2001.

- [11] Y. Toyota, T. Shiba, and M. Ohkura, "Mechanism of device degradation under AC stress in low-temperature polycrystalline silicon TFTs," Proc. IEEE IRPS, pp. 278-282, 2002.

- [12] Y. Toyota, T. Shiba, and M. Ohkura, "A new model for device degradation in low-temperature N-channel polycrystalline silicon TFTs under AC stress," IEEE Electron Device Lett, vol. 51, pp. 927-932, 2004.

- [13] G. A. Armstrong, S. Uppal, S. D. Brotherton, and J. R. Ayres, "Differentitation of effects due to grain and grain boundary traps in laser annealed poly-Si thin film transistors," Jpn. J. Appl. Phys., vol. 37, pp. 1721-1726, 1998.

- [14] F. V. Farmakis, J. Brini, G. Kamarinos, C. T. Angelis, C. A. Dimitriadis, M. Miyasaka, and T. Ouisse, "Grain and grain-boundary control of the transfer characteristics of large-grain polycrystalline silicon thin-film transistors," SOLID-STATE ELECTRON. Vol. 44, no. 6, pp. 913-916. 2000.

- [15] G. A. Armstrong, S. Uppal, S. D. Brotherton, and J. R. Ayres, "Modeling of laser-annealed polysilicon TFT characteristics," IEEE Electron Device Lett., vol. 18, pp. 315-318, 1997.

- [16] S. Inoue nad T. Shimoda, "Investigation of Relationship between Hot Carrier Degradation and Kink Effect in Low Temperature Poly-Si TFTs," in Proc. SID, pp. 452-455, 1999.

- [17] Y. Uraoka, N. Hirai, H. Yano, T. Hatayama, and T Fuyuki, "Hot Carrier

- Analysis in Low-Temperature Poly-Si TFTs Using Picosecond Emission Microscope," IEEE Trans. Electron Devices, Vol. 51, pp.28-34, 2004.

- [18] S.M. Sze "Semiconductor Devices Physics and Technology," second edition, pp. 47-48, Wiley, New York, 2002.

Table 4-1. Variation of experimental electronic parameters and corresponding possible degradation mechanics.

| Electrical parameters   | Mainly depending on                                   |

|-------------------------|-------------------------------------------------------|

| after stressing         |                                                       |

| $\Delta g_{	ext{mmax}}$ | Interface state generation                            |

|                         | State generation in the grain boundaries (tail state) |

| $\Delta 	ext{Von}$      | Charge injected into the gate oxide                   |

|                         | Interface state generation (deep states)              |

|                         | State generation in the grain boundaries(deep states) |

| ΔS (subthreshold swing) | Intra-grain defect density generation (bulk state)    |

|                         | Interface state generation (deep states)              |

|                         |                                                       |

Fig. 4-1. The dynamic pulse train stress is defined at constant Vd = 6 V and dynamic Vg = 3V (ON), -3V (OFF) with the duty cycle of 50%, and the source potential is common.

Fig. 4-2a Typical M10 poly-Si TFT  $I_d$ - $V_g$  curves before and after DC hot carrier stress at 10000 second.

Fig. 4-2b Typical S1 poly-Si TFT  $I_d$ - $V_g$  curves before and after DC hot carrier stress at 10000 second.

Fig. 4-3 Maximum conductance (Gm,max) degradation of S1 and M10 TFT as a function of the stress time with different frequencies (DC, f = 1K Hz, and f = 1M Hz).

Fig. 4-4. Threshold voltage of S1 and M10 TFT as a function of the stress time with different frequencies.

Fig. 4-5. Subthreshold swing variation of S1 and M10 TFT as a function of the stress time with different frequencies.

Fig. 4-6. ON current ( $I_{\rm ON}$ ) variation of S1 and M10 TFT as a function of the stress time with different frequencies.

Fig 4-7. ON/OFF ratio of S1 and M10 TFT as a function of the stress time with different frequencies.

Fig. 4-8. Gm degradation of S1 and M10 TFT as a function of the stress time with different rising time (Tr) and falling time (Tf) under the frequency of 1 KHz.

Fig. 4-9. Dependence of emission intensity on (a) pulse rise time and (b) pulse fall time. Emission intensity is independent of the pulse rise time. However, we have found that it strongly depends on the fall time [17].

Fig. 4-10. Vth variation of S1 and M10 TFT as a function of the stress time with different rising time (Tr) and falling time (Tf) under the frequency of 1 KHz.

Fig 4-11. ON current (Ion) degradation of S1 and M10 TFT as a function of the stress time with different rising time (Tr) and falling time (Tf) under the frequency of 1 KHz.

Fig. 4-12. Gm degradation of S1 and M10 TFT as a function of the stress time with different subtract temperature with 25<sup>o</sup>C, and 75<sup>o</sup>C under the same frequency of 1 KHz.

Fig. 4-13. Vth variation of S1 and M10 TFT as a function of the stress time with  $25^{\circ}$ C, and  $75^{\circ}$ C under the same frequency of 1 KHz

Fig 4-14. ON current (Ion) degradation of S1 and M10 TFT as a function of the stress time with 25°C, and 75°C under the same frequency of 1 KHz