Empirical constants of the electron

mobility in the inversion layer of

Abstract-An analytic I-V model for lightly doped drain (LDD)

MOSFET devices is presented. In this model, the n- region is consid-

# An Analytic *I–V* Model for Lightly Doped Drain (LDD) MOSFET Devices

GWO-SHENG HUANG, STUDENT MEMBER, IEEE, AND CHING-YUAN WU, MEMBER, IEEE

α, η

| ered to be a modified bur<br>region is considered to<br>device. Combining the n<br>in the linear/saturation of<br>culated directly from the<br>ters used in the channel<br>square fittings. According | ied-channel MOSFET device, and the channel be an intrinsic enhancement-mode MOSFET models of these two regions, the drain current regions and the saturation voltage can be calterminal voltages. In addition, the parameterion can be extracted by a series of leasting to comparisons between the experimental | $egin{aligned} V_{sl} \ E_c \ V_T(V_{T0}) \end{aligned}$ | the active channel device.  Saturation velocity.  Critical electric field $(E_c = l/\beta = V_{sl}/\mu_n)$ .  Threshold voltage for biased conditions (at zero drain voltage). |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                       | test transistors and the theoretical calcula-<br>model is shown to be valid for wide ranges of                                                                                                                                                                                                                   | $\mu_n$                                                  | Maximum electron mobility in the inversion layer of the active channel device.                                                                                                 |

|                                                                                                                                                                                                       | Nomenclature                                                                                                                                                                                                                                                                                                     | $\mu_b(\mu_s)$                                           | Effective electron mobility of the conducting charge in the bulk                                                                                                               |

| $V_{gs}(V_{ds})$                                                                                                                                                                                      | External gate (drain) to source volt-                                                                                                                                                                                                                                                                            |                                                          | (surface) of the n <sup>-</sup> region.                                                                                                                                        |

| $V_{BG}$                                                                                                                                                                                              | age.<br>Substrate bias.                                                                                                                                                                                                                                                                                          | $Q_b(Q_s)$                                               | Conducting charge density in the bulk (surface) of the n region.                                                                                                               |

| $V_d'(V_s') \ V_d''(V_s'')$                                                                                                                                                                           | Intrinsic drain (source) voltage.<br>n <sup>-</sup> -n <sup>+</sup> junction voltage in the drain                                                                                                                                                                                                                | $\mu_{	ext{eff}}$                                        | Effective electron mobility in the channel region.                                                                                                                             |

| $V_{g1} (= V_g - V_s')$                                                                                                                                                                               | (source) side. Intrinsic gate-source voltage.                                                                                                                                                                                                                                                                    | $N_d$                                                    | Doping concentration of the n <sup>-</sup> region.                                                                                                                             |

| $V_{d1}^{g1} (= V_{d}^{g} - V_{s}^{g})$                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                  |                                                          | ~                                                                                                                                                                              |

| $V_{d2}^{a1}(=V_d^{"}-V_d^{"})$                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                  | $r_n$                                                    | Junction depth of the n region.                                                                                                                                                |

| 'd2( 'd 'd)                                                                                                                                                                                           | the drain side.                                                                                                                                                                                                                                                                                                  | $l_1$                                                    | Effective length of the spacer.                                                                                                                                                |

| $V_{g2}(=V_g-V_d')$                                                                                                                                                                                   | Voltage across the gate and the intrinsic drain.                                                                                                                                                                                                                                                                 | $l_2$                                                    | Effective overlapped length of the n region with respect to the gate.                                                                                                          |

| $V_{d3}(=V_d''-V_s)$                                                                                                                                                                                  | Voltage across the n <sup>+</sup> source and the n <sup>-</sup> -n <sup>+</sup> junction.                                                                                                                                                                                                                        | $\overline{C}(C(x))$                                     | Average (effective) capacitance per unit area of the surface charge                                                                                                            |

| $V_{d4} = V_d' - V_s$                                                                                                                                                                                 | Voltage across the n <sup>+</sup> source and the intrinsic drain.                                                                                                                                                                                                                                                | A ( A )                                                  | layer in the n region.                                                                                                                                                         |

| $I_{ds}$                                                                                                                                                                                              | Drain current in the linear region.                                                                                                                                                                                                                                                                              | $\Delta r_n(\Delta r_{ne})$                              | (Effective) depletion depth of the                                                                                                                                             |

| $L(W_1)$                                                                                                                                                                                              | Effective channel length (width).                                                                                                                                                                                                                                                                                |                                                          | bulk in the n <sup>-</sup> region with respect to the substrate.                                                                                                               |

| $L_{ m mask}$                                                                                                                                                                                         | Mask channel length.                                                                                                                                                                                                                                                                                             | $N_a$                                                    | Effective substrate concentration.                                                                                                                                             |

| $V_{FB}(V_{FBn})$                                                                                                                                                                                     | Flat-band voltage of the active channel (n region) device.                                                                                                                                                                                                                                                       | $V_{\rm bi}$                                             | Built-in voltage of the n <sup>-</sup> -substrate junction.                                                                                                                    |

| $oldsymbol{\phi}_{s,	ext{inv}}$                                                                                                                                                                       | Surface potential at strong inversion condition.                                                                                                                                                                                                                                                                 | $W_d$                                                    | Effective depletion depth of the substrate with respect to the n                                                                                                               |

| + (C)                                                                                                                                                                                                 | Omide Abidenses (constitutions                                                                                                                                                                                                                                                                                   |                                                          | *                                                                                                                                                                              |

Manuscript received July 11, 1986; revised December 5, 1986. This work was supported by grants from the Electronics Research and Service Organization (ERSO) and the Industrial Technology Research Institute (ITRI), Taiwan, Republic of China.

Oxide thickness (capacitance per

Dielectric permittivity of the bulk

semiconductor (oxide).

The authors are with the Institute of Electronics, College of Engineering, National Chiao-Tung University, Taiwan, Republic of China.

IEEE Log Number 8613903.

$t_{\rm ox}(C_{\rm ox})$

$\epsilon_{\rm si}(\epsilon_{\rm ox})$

pletion edge due to the  $n^-$  region in the drain side.  $V_{DSAT}(V_{dsat})$  Saturation source-drain voltage for

region.

region).

Geometrical factor of the bulk in

tions (at zero drain voltage).

Depletion length at the channel de-

the n region for biased condi-

the whole device (in the channel

$f_b(f_{b0})$

$\Delta L_d$

| $\Delta L_1(\Delta L_2)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Channel-length-modulation facto in the channel (n <sup>-</sup> ) region |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| $I_{DSAT}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Drain current in the saturation re gion.                                |

| $I_{d\mathrm{sat}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Drain current at the onset of the saturation condition.                 |

| $Y_d$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Depletion width in the channel region.                                  |

| $R_{nd}\left(R_{ns}\right)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Resistance of the n region near the drain-source side.                  |

| $R_d(R_s)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Parasitic resistance of the drain-<br>source.                           |

| and the second s |                                                                         |

#### I. INTRODUCTION

THE LIGHTLY DOPED drain (LDD) structure can reduce the high-field effects in scaled down devices by introducing n<sup>-</sup> regions between the channel and the n<sup>+</sup> source-drain [1]. Since part of the high electric field can be absorbed into the n<sup>-</sup> regions, the LDD MOSFET devices exhibit higher breakdown voltage, flatter threshold voltage versus channel-length relation, lower substrate and gate currents, and lower channel-length modulation effect [1], [2]. However, the n<sup>-</sup> regions give large parasitic resistances that can cause the reduction of device transconductance and the increase of saturation voltage [2]. These large parasitic resistances are bias-controlled and share the appreciable voltage drop, especially when the channel length is short and the drain voltage is large.

In general, the behavior of the LDD structure can be characterized by the two-dimensional numerical method [3]. However, it consumes much longer computational time and is very difficult and impractical for circuit analysis use in a CAD system. Therefore, the analytic model is necessary to avoid the complicated computation. Recently, Duvvury *et al.* [4] have proposed an analytic *I-V* model in which the parasitic resistances of the n<sup>-</sup> regions

In this paper, an analytic I-V model is proposed, in which the drain current can be calculated directly from the terminal voltages and the parasitic resistances of the n regions are bias/structure-dependent. In Section II, the mobility and I-V models in the channel region developed by Wu and Daih [6] are adopted. These models are well established and have good agreement with the experimental results. The parasitic resistance of the n region is derived based on a buried-channel MOSFET model with a modified charge-sharing scheme and an effective capacitance. Combining these two models, the analytic expressions in the linear region can be obtained. Moreover, the analytical forms for the terminal saturation voltage and the saturation current considering the effect of channellength modulation are also derived from the above models. In Section III, we demonstrate that the parameters used in the active channel region can be obtained from a series of extraction techniques. In Section IV, comparisons between the experimental results and the theoretical calculations are made and satisfactory agreements are obtained. In Section V, conclusions are given.

#### II. THE I-V MODEL

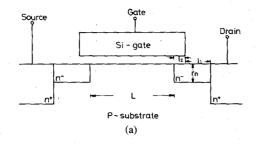

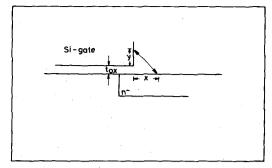

The schematic diagram and the equivalent circuit of a MOSFET device with an LDD structure are shown in Fig. 1(a) and (b), respectively. It is shown that an intrinsic enhancement-mode MOSFET is placed in the middle and both of the  $n^-$  regions are taken to be buried-channel MOSFET's. Note that  $R_s$  and  $R_d$  are the parasitic resistances including  $n^+$  diffusion, contact, and wiring series resistances, which are considered to have constant values.

### A. The I-V Characteristics in the Linear Region

The current equation for the intrinsic enhancement-mode MOSFET in the linear region can be written as [6], [10]

$$I_{ds} = \frac{\mu_n C_{\text{ox}} W \left[ V_{g1} - V_T (V_{d1}) - \frac{1}{2} V_{d1} \right] V_{d1}}{L \left\{ 1 + \frac{\alpha C_{\text{ox}}}{2\epsilon_{\text{si}}} \left[ V_{g1} + V_T (V_{d1}) - 2(V_{FB} + \phi_{s, \text{inv}}) - \frac{1}{2} V_{d1} \right] + \left( \eta + \frac{\beta}{L} \right) V_{d1} \right\}}$$

(1)

are considered to have constant values. However, this model is not valid for the I-V characteristics with different applied gate and substrate biases. More recently, Lai and Sun [5] have also proposed an analytic I-V model, in which the drain current cannot be calculated directly from the terminal voltages. This model is not suitable for cir-

where  $V_T(V_{d1})$  is the threshold voltage that is a function of  $V_{d1}$ ; all other notations have been defined in [6].

In the linear region, the drain-source voltage is small. Therefore, we may linearize the threshold voltage with respect to  $V_{d1}$  and the drain current can be expressed in [10]

$$I_{ds} = \frac{\mu_n C_{\text{ox}} W(V_{g1} - V_{T0} - aV_{d1}) V_{d1}}{L \left\{ 1 + \frac{\alpha C_{\text{ox}}}{2\epsilon_{\text{si}}} \left[ V_{g1} + V_{T0} - 2(V_{FB} + \phi_{s, \text{inv}}) - bV_{d1} \right] + \left( \eta + \frac{\beta}{L} \right) V_{d1} \right\}}$$

(2)

cuit simulation. In addition, the parasitic resistance of the  $n^-$  region near the source is assumed to have a constant value.

where  $a = \frac{1}{2} - k$ ;  $b = \frac{1}{2} + k$ , and k is the slope of the threshold voltage with respect to  $V_{d1}$  at zero drain bias. The parameters used above can be obtained from a series

Fig. 1. (a) The schematic diagram of the LDD structure; (b) the equivalent circuit of the LDD MOSFET.

of extraction techniques as will be discussed in Section III.

Taking the n region to be a buried-channel MOSFET, the drain current can be expressed as

$$I_{ds} = W(\mu_b Q_b + \mu_s Q_s) \frac{dV(x)}{dx}$$

(3)

where  $Q_b$  and  $Q_s$  are the conducting charge densities in the bulk and the surface, respectively.

It's assumed that the drain voltage is small and the depleted charges in the bulk of the  $n^-$  region are caused by the substrate. Then,  $Q_b$  and  $Q_s$  in the drain side can be expressed as

$$Q_b = qN_d(r_n - \Delta r_n) \tag{4}$$

$$Q_s = C(x) [V_{g2} - V_{FBn} - V(x)]$$

(5)

where C(x) is the effective capacitance per unit area of the surface charge layer and is a function of position (see Appendix A);  $\Delta r_n$  is the depletion depth of the bulk in the  $n^-$  region with respect to the substrate and is a function of the potential;  $N_d$  is the average doping concentration in the  $n^-$  region.

Taking  $N_a$  as the effective substrate concentration,  $\Delta r_n$  can be expressed by

$$\Delta r_n = \left\{ \frac{2\epsilon_{si} N_a [V_{bi} + V_{BG} + V_{d4} + V_{(x)}]}{qN_d (N_a + N_d)} \right\}^{1/2}$$

(6)

where  $V_{\rm bi}$  is the built-in voltage of the n<sup>-</sup>-substrate junction and  $V_{BG}$  is the substrate bias.

Integrating (3) across the two ends of the n<sup>-</sup> region near the drain, the result is (see Appendix B)

$$I_{ds}(l_1 + l_2) = W[\mu_b q N_d (r_n - \Delta r_{ne}) V_{d2} + \mu_s \overline{C} (V_{g2} - V_{FBn} - \frac{1}{2} V_{d2}) V_{d2}]$$

(7)

where  $\overline{C}$  is the average capacitance per unit area of the surface charge layer and depends on the structure of the  $n^-$  region;  $\Delta r_{ne}$  is the effective depletion depth of the bulk in the  $n^-$  region with respect to the substrate. Note that

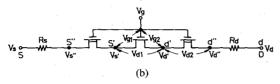

Fig. 2. The schematic structure for calculating the geometrical factor of the bulk in the  $n^-$  region.

the effective depletion depth of the substrate with respect to the n<sup>-</sup> region  $(W_d)$  can be obtained by multiplying the factor  $N_d/N_a$  to  $\Delta r_{ne}$ . The result can be expressed as

$$W_{d} = \left[\frac{2\epsilon_{si}N_{d}(V_{bi} + V_{BG} + V_{ds})}{qN_{a}(N_{d} + N_{a})}\right]^{1/2}.$$

(8)

As the drain voltage is large, the depleted charges exist not only in the n<sup>-</sup>/substrate junction but also in the n<sup>-</sup>/channel junction. From the concept of the charge-sharing scheme as shown in Fig. 2, the depleted charges in the bulk of the n<sup>-</sup> region have the same amount of charges depleted in the substrate and channel regions (which are plotted as the shaded region). Based on this geometrical consideration, the conducting charge density in the bulk of the n<sup>-</sup> region expressed in (7) should be modified as [7], [8]

$$qN_d(r_n - \Delta r_{ne}) \to qN_d r_n f_b \tag{9}$$

where  $f_b$  is the geometrical factor of the bulk in the n<sup>-</sup> region and can be expressed as

$$f_b = 1 - \frac{N_a \left\{ W_d(l_1 + l_2) + \frac{\Delta L_d}{2} \left[ 2(W_d + r_n) - Y_d \right] \right\}}{N_d r_n (l_1 + l_2)}$$

(10)

where

$$\Delta L_d = r_n \bigg[ \bigg( 1 + \frac{2W_d}{r_n} \bigg)^{1/2} - 1 \bigg]. \tag{11}$$

Using the following relations:

$$V_{d2} = I_{ds}R_{nd} \tag{12}$$

and

$$V_{g2}-V_{FBn}-\tfrac{1}{2}V_{d2}$$

$$= V_{gs} - V_{ds} - V_{FBn} + I_{ds} (R_d + \frac{1}{2} R_{nd}) \quad (13)$$

we can get a quadratic equation for  $R_{nd}$  that is

$$A_1 R_{nd}^2 + B_1 R_{nd} + C_1 = 0 (14)$$

where

$$A_1 = \frac{1}{2} W \mu_s \overline{C} I_{ds} \tag{15}$$

$$B_1 = W \left[ \mu_b q N_d r_n f_b + \mu_s \overline{C} \left( V_{gs} - V_{ds} - V_{FBn} + R_d I_{cs} \right) \right]$$

(16)

$$C_1 = -(l_1 + l_2). (17)$$

In general,  $B_1^2 >> 4A_1C_1$ , and  $R_{nd}$  can be approximated by

$$R_{nd} = \frac{l_1 + l_2}{W[\mu_b q N_d r_n f_b + \mu_s \overline{C} (V_{gs} - V_{ds} - V_{FBn} + R_d I_{ds})]}.$$

(18)

Note that the term  $R_d I_{ds}$  cannot be neglected in the high-current condition and can be approximated as

$$R_d I_{ds} = \frac{\mu_n C_{ox} W}{I} (V_{gs} - V_{T0}) V_{ds} R_d.$$

(19)

As expressed in (10),  $f_b$  is a function of the bias conditions. By linearizing the geometrical factor at the zero drain bias as the same method used for the threshold voltage [6], the result is

$$f_b = f_{b0} - SV_{ds} \tag{20}$$

where

$$f_{b0} = f_b(V_{ds} = 0) (21)$$

and

$$S = \left| \frac{df_b}{dV_{ds}} \right|_{V_{ds} = 0} \tag{22}$$

Putting (19) and (20) into (18), the resistance of the n region in the drain side can be expressed as

$$R_{nd} = \frac{l_1 + l_2}{W[\mu_b q N_d r_n f_{b0} + \mu_s \overline{C} (V_{gs} - V_{FBn}) - G V_{ds}]}$$

(23)

where

$$G = \mu_b q N_d r_n S + \mu_s \overline{C} \left[ 1 - R_d \frac{\mu_n C_{\text{ox}} W}{L} (V_{\text{gs}} - V_{T0}) \right].$$

(24)

The resistance of the n<sup>-</sup> region near the source side can be derived by the same method. In the general case,  $V_{g,s}$  –  $V_{FBn}$  is much greater than  $I_{ds}R_s$ . Therefore, the  $I_{ds}R_s$  term can be neglected, and the result can be expressed as

$$R_{ns} = \frac{l_1 + l_2}{W[\mu_b q N_d r_n f_{b0} + \mu_s \overline{C} (V_{gs} - V_{FBn})]}.$$

(25)

Using the following terminal relations:

$$V_{g1} = V_{gs} - I_{ds}(R_{ns} + R_s) = V_{gs} - I_{ds}R_{st}$$

(26)

and

$$V_{d1} = V_{ds} - I_{ds}(R_{ns} + R_s + R_{nd} + R_d)$$

=  $V_{ds} - I_{ds}R_t$  (27)

the  $I_{ds}$  can be calculated from the following equations:

$$A_2 I_{ds}^2 + B_2 I_{ds} + C_2 = 0 (28)$$

and the solution is

$$I_{ds} = \frac{-B_2 + (B_2^2 - 4A_2C_2)^{1/2}}{2A_2}$$

(29)

where

$$A_{2} = \frac{\alpha C_{\text{ox}}}{2\epsilon_{\text{si}}} \left( bR_{t} - R_{\text{st}} \right) - \left( \eta + \frac{\beta}{L} \right) R_{t}$$

$$+ \frac{R_{t}}{L} \mu_{n} C_{\text{ox}} W(aR_{t} - R_{\text{st}})$$

(30)

$$B_{2} = 1 + \frac{\alpha C_{\text{ox}}}{2\epsilon_{\text{si}}} \left[ V_{gs} + V_{T0} - 2(V_{FB} + \phi_{s, \text{inv}}) - bV_{ds} \right] + \left( \eta + \frac{\beta}{I} \right) V_{ds} + \frac{R_{t}}{I} \mu_{n} W C_{\text{ox}} (V_{gs} - V_{T0})$$

$$-\frac{V_{ds}}{L}\mu_n C_{ox}W(2aR_t - R_{st})$$

(31)

$$C_2 = -\frac{\mu_n C_{ox} W}{L} (V_{gs} - V_{T0} - aV_{ds}) V_{ds}$$

(32)

and  $R_{st} = R_{ns} + R_s$  and  $R_t = R_{ns} + R_s + R_{nd} + R_d$  since  $A_2$ ,  $B_2$ , and  $C_2$  are expressed in terms of the terminal voltages. Therefore, the  $I_{ds}$  can be obtained directly if the external bias conditions are given.

#### B. The Saturation Voltage

As the drain voltage is increased, the electric field in the channel region near the drain will reach the critical electric field  $E_c$  and will result in the saturation velocity  $V_{sl}$  for electrons. The saturation current at the saturation voltage can be expressed as

$$I_{dsat} = W \mu_{eff} C_{ox} [V_{g1} - V_{T0} - (1 - k) V_{dsat}] E_c$$

(33)

where  $V_{dsat}$  and  $\mu_{eff}$  are the saturation voltage and the effective mobility in the channel region. Using  $V_{g1} = V_{gs} - I_{dsat}(R_s + R_{ns})$ , the  $I_{dsat}$  term that includes the effects of the parasitic resistance of the source can be expressed by

$$I_{dsat} = W\mu_{eff}C_{ox} \frac{[V_{gs} - V_{T0} - (1 - k)V_{dsat}]E_c}{1 + W\mu_{eff}C_{ox}(R_c + R_{rs})E_c}.$$

(34)

From (2),  $I_{dsat}$  can also be expressed as

$$I_{dsat} = W \mu_{eff} C_{ox} \frac{(V_{gs} - V_{T0} - aV_{dsat}) V_{dsat}}{L + W \mu_{eff} C_{ox} (R_s + R_{ns}) V_{dsat}}.$$

(35)

Equating (34) and (35), the saturation voltage in the channel region can be solved by the following equation:

$$A_3 V_{dsat}^2 + B_3 V_{dsat} + C_3 = 0 (36)$$

where

$$A_3 = (k - \frac{1}{2}) + \frac{1}{2}E_c W \mu_{\text{eff}} C_{\text{ox}} (R_{ns} + R_s)$$

(37)

$$B_3 = (1 - k)E_cL + (V_{gs} - V_{T0}) \tag{38}$$

$$C_3 = -(V_{gs} - V_{T0})E_cL. (39)$$

The solution for (36) can be expressed by

$$V_{dsat} = \frac{-B_3 + (B_3^2 - 4A_3C_3)^{1/2}}{2A_3}.$$

(40)

Note that  $V_{dsat}$  is calculated from the terminal voltage. Putting (40) into (2), the saturation current ( $I_{dsat}$ ) can be obtained.

The saturation voltage in the terminal end  $(V_{DSAT})$  can be expressed as

$$V_{DSAT} = V_{dsat} + I_{dsat}(R_{ns} + R_s + R_{nd} + R_d).$$

(41)

Putting (23), (25), and (40) into (41), the  $V_{DSAT}$  can be solved by the following equation:

$$A_4 V_{DSAT}^2 + B_4 V_{DSAT} = C_4 = 0 (42)$$

where

$$A_4 = -WG \tag{43}$$

$$B_{4} = W \left\{ \mu_{b}qN_{d}r_{n}f_{b0} + \mu_{s}\overline{C}(V_{gs} - V_{FBn}) + G[V_{dsat} + I_{dsat}(R_{s} + R_{ns} + R_{d})] \right\}$$

$$C_{4} = -W[\mu_{b}qN_{d}r_{n}f_{b0} + \mu_{s}\overline{C}(V_{gs} - V_{FBn})]$$

$$(44)$$

$$[V_{dsat} + I_{dsat}(R_s + R_{ns} + R_d)] - I_{dsat}(l_1 + l_2).$$

(45)

Note that G in (43) and (44) has been given in (24). The solution for (42) can be expressed by

$$V_{DSAT} = \frac{-B_4 + (B_4^2 - 4A_4C_4)^{1/2}}{2A_4}.$$

(46)

From (46), it is clearly seen that the saturation voltage  $(V_{DSAT})$  is also expressed in an analytic form and can be calculated from the terminal voltages.

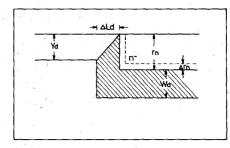

# C. Channel-Length Modulation

In the saturation region, the pinchoff point will move toward the source side as the drain voltage is increased. Therefore, the effective conducting length of the inversion layer in the channel region becomes shorter. This phenomenon increases the slope of the saturation current, especially for the short-channel devices. Due to the n region, the space-charge region may extend into the n region near the drain, then, part of the voltage is shared by this region. Therefore, the channel-length-modulation effect should be less pronounced as compared to that of the conventional devices. The diagram showing the pinchoff point is shown in Fig. 3.

The current in the saturation region, considering the effect of channel-length modulation, can be expressed as

$$I_{DSAT} = \frac{I_{dsat}}{1 - \frac{\Delta L_1}{L}} \tag{47}$$

Fig. 3. The schematic diagram for showing the channel-length-modulation effect.

where  $I_{DSAT}$  is the saturation current in the saturation region;  $\Delta L_1$  can be calculated directly from the terminal voltage and is shown in Appendix C. Note that  $\Delta L_1$  is equal to zero at the onset of saturation condition.

# III. EXPERIMENTS AND PARAMETER EXTRACTION TECHNIQUES

#### A. Fabrication Data and Measurements

Experimental Si-gate n-channel MOSFET's with LDD structures were fabricated by using a set of test structures with the mask channel length varied from 2 to 12  $\mu$ m and a mask channel width of 55  $\mu$ m. The silicon substrates used were of  $\langle 1, 0, 0 \rangle$  orientation and the resistivity range was about 15-25  $\Omega$  cm. The device fabrications were carried out in a production line of the Electronics Research and Service Organization (ERSO), Industrial Technology Research Institute (ITRI), and the process sequence was quite standard. The double-channel-boron implantations were performed by using the shallow implantation with an energy of 25 keV and a dose of 7.5  $\times$ 10<sup>11</sup>/cm<sup>2</sup> and the deep implantation with an energy of 150 keV and a dose of  $4 \times 10^{11}/\text{cm}^2$ , all through the gate oxide with a thickness of 250 Å. The over-etching technique for the polysilicon gate was taken to obtain the submicrometer-channel-length devices. The n regions of the LDD structure were formed by implanting the phosphorus ions with an energy of 30 keV and a dose of  $1 \times 10^{13}$ /cm<sup>2</sup>. After depositing the CVD oxide on the polysilicon gate, the sidewall spacers were formed by using directional RIE. Then, the source-drain n<sup>+</sup> regions were implanted with an energy of 60 keV and a dose of  $6 \times 10^{15} / \text{cm}^2$ .

The gate oxide thickness (250 Å) of the fabricated LDD devices was measured by the controlled sample after the gate oxide growth using an ellipsometer and checked by the fabricated MOS capacitor using the C-V measurement. The junction depths of  $n^-$  and  $n^+$  regions and the width of the spacer were measured by the auto-spreading resistance probe and SEM cross section analyses. The junction depth in the  $n^-$  region  $(r_n)$  is 0.25  $\mu$ m and that in the  $n^+$  region  $(R_j)$  is 0.35  $\mu$ m. The spacer width  $(l_1)$  is about 0.45  $\mu$ m and the lateral  $n^-$  diffusion depth  $(l_2)$  is about 0.2  $\mu$ m. The threshold voltages and I-V characteristics of the fabricated LDD devices were measured by

| T <sub>OX</sub> (Å) | N <sub>AB</sub> (cm <sup>-3</sup> ) | $N_{AS}(cm^{-3})$       | N <sub>AD</sub> (cm <sup>-3</sup> ) | Υ <sub>s</sub> (μm) | M <sup>p</sup> (hw) | R <sub>j</sub> (µm) | v <sub>fb</sub> (v) |

|---------------------|-------------------------------------|-------------------------|-------------------------------------|---------------------|---------------------|---------------------|---------------------|

| 250                 | 9 x 10 <sup>14</sup>                | 4.77 x 10 <sup>16</sup> | 8.33 x 10 <sup>15</sup>             | 0.155               | 0.48                | 0.35                | -0.745              |

using a microcomputer-controlled HP-4140B picoampere meter.

#### B. Parameter Extraction Techniques

1) Parameters in the Threshold Voltage: The threshold voltage  $(V_{T0})$  of the fabricated LDD devices was determined by the extrapolation of the linear conductance with respect to different applied gate voltages with a low source-drain voltage (50 mV). Using the threshold voltage model developed by Wu et al. [8], the parameters in the threshold voltage model including  $V_{FR}$  and the channel doping profile with the step profile approximation for the double-channel-boron implantations can be easily extracted from the fabricated long-channel MOSFET by using the measured threshold voltages under different substrate biases, as described in [8]. The extracted parameters are listed in Table I. From Table I, the extracted  $N_{AS}Y_{S}$ product is  $7.394 \times 10^{11}/\text{cm}^2$ , which is quite close to the implanted boron dose of  $7.5 \times 10^{11}/\text{cm}^2$  for the shallow implantation through the 250-Å gate oxide. Similarly, the extracted  $N_{AD}W_B$  product is 3.998  $\times$  10<sup>11</sup>/cm<sup>2</sup>, which is in excellent agreement with the implanted boron dose of  $4 \times 10^{11} / \text{cm}^2$  for the deep implantation. Based on the extracted parameters,  $\phi_{s,inv}$  can be computed by the model in [8].

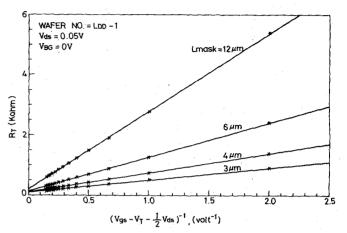

2) Other Parameters in the Channel Region: In order to extract the parameters in the channel region, the biascontrolled effects of the n region must be eliminated. Therefore, the parameters in the channel region must be extracted from the fabricated long-channel MOSFET devices with a lower gate voltage and a low source-drain voltage, for example,  $0.5 \le V_{gs} - V_{T0} - \frac{1}{2}V_{ds} \le 7 \text{ V}$ and  $V_{ds} = 0.05$  V. In this case, the resistance in the channel region is much larger than that in the n<sup>-</sup> regions, and the parasitic resistances can be considered to have average values. At lower source-drain voltage ( $V_{ds} = 0.05 \text{ V}$ ), the source-drain current is about in the microampere range and the voltage drop across the n regions can be neglected, i.e.,  $V_{g1} \cong V_{gs}$ ,  $V_{d1} \cong V_{ds}$ . Under the above conditions, the total resistance can be obtained from (1) and is written as

$$R_{T} = R_{ns}^{0} + R_{s} + R_{nd}^{0} + R_{d} + \frac{L\alpha}{2W\mu_{n}\epsilon_{si}} + \frac{L}{W\mu_{n}C_{ox}}$$

$$\cdot \left\{ \frac{1 + \frac{\alpha C_{ox}}{\epsilon_{si}} \left[ V_{T0} - \left( V_{FB} + \phi_{s,inv} \right) \right]}{V_{gs} - V_{T0} - \frac{1}{2}V_{ds}} \right\}$$

(48)

Fig. 4. The  $R_T$  versus  $(V_{gs} - V_{T0} - 1/2 V_{ds})^{-1}$  relation for different mask lengths.

where  $R_{ns}^0$  and  $R_{nd}^0$  are the resistances of the n<sup>-</sup> regions at zero drain voltage, and  $V_{T0}$ ,  $V_{FB}$ , and  $\phi_{s,inv}$  have been determined from the threshold voltages.

Plotting  $R_T$  versus  $(V_{gs} - V_{T0} - \frac{1}{2}V_{ds})^{-1}$  for different mask lengths with the same channel width  $(W = 55 \,\mu\text{m})$ , a set of the straight lines can be obtained by the least squares method as shown in Fig. 4. The slope (named SLOPE1) and the intercept in the vertical coordinate (named CUT1) can be expressed as

SLOPE1 =

$$\frac{L}{W\mu_n C_{\text{ox}}} \left\{ 1 + \frac{\alpha C_{\text{ox}}}{\alpha_{\text{si}}} \left[ V_{T0} - \left( V_{FB} + \phi_{s, \text{inv}} \right) \right] \right\}$$

(49)

CUT1 =

$$R_{ns}^0 + R_s + R_{nd}^0 + R_d + \frac{L\alpha}{2W\mu_n\epsilon_{si}}$$

(50)

where  $L = L_{\text{mask}} - \Delta L$  is the effective channel length;  $L_{\text{mask}}$  is the mask length.

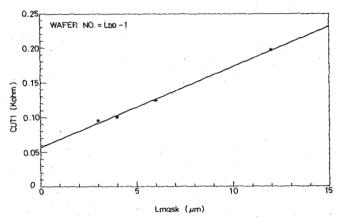

Using the same method for the CUT1 versus  $L_{\rm mask}$  relation as shown in Fig. 5, the slope (named SLOPE2) and the intercept in the vertical coordinate (named CUT2) can be written as

$$SLOPE2 = \frac{\alpha}{2Wu_n\epsilon_{ci}} \tag{51}$$

CUT2 =

$$R_{ns}^0 + R_s + R_{nd}^0 + R_d - \frac{\alpha \Delta L}{2W\mu_n \epsilon_{ci}}$$

. (52)

**Taking**

$$a = \frac{1}{W\mu_n C_{\text{ox}}} - \frac{\alpha}{W\mu_n \epsilon_{\text{si}}} (V_{FB} + \phi_{s, \text{inv}})$$

(53)

|                   | TABLE II       |                        |

|-------------------|----------------|------------------------|

| THE EXTRACTED AND | AFTER-ADJUSTED | PARAMETERS USED IN THE |

|                   | CHANNEL REGIO  | ON .                   |

|                              | μ <sub>n</sub> (cm <sup>-2</sup> /v-s) | α(cm/v)                 | ΔΓ (huu) | η (1/v)                 | β(cm/v)                 | R <sub>s</sub> ,R <sub>d</sub> (Ω) | μ <sub>eff</sub> (cm <sup>2</sup> /v-s) |

|------------------------------|----------------------------------------|-------------------------|----------|-------------------------|-------------------------|------------------------------------|-----------------------------------------|

| From Parameter<br>Extraction | 593.05                                 | 8.00 x 10 <sup>-7</sup> | 1.32     | 2.05 x 10 <sup>-2</sup> | 4.51 x 10 <sup>-5</sup> | 13                                 | 550                                     |

| After<br>Adjustments         | 570.00                                 | 8.00 x 10 <sup>-7</sup> | 1.32     | 2.05 x 10 <sup>-2</sup> | 4.90 x 10 <sup>-5</sup> | -13                                | 550                                     |

Fig. 5. The CUT1 versus  $L_{\text{mask}}$  relation to obtain CUT2 and SLOPE2.

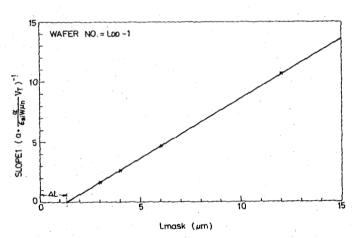

Fig. 6. The SLOPE1  $(a + \alpha/\epsilon_{si} w \mu_n V_{70})^{-1}$  versus  $L_{\text{mask}}$  relation.  $\Delta L$  can be obtained from the intercept in the horizontal coordinate.

and applying the least squares method again to the SLOPE1 versus  $(a + \alpha V_{T0}/W\mu_n\epsilon_{\rm si}) \cdot L_{\rm mask}$  relation,  $\Delta L$  and a can be determined by the iterative calculations and the SLOPE1  $\cdot$   $(a + \alpha V_{T0}/W\mu_n\epsilon_{\rm si})^{-1}$  versus  $L_{\rm mask}$  relation is plotted in Fig. 6. Using (51) and (52),  $\mu_n$ ,  $\alpha$ ,  $\Delta L$ ,  $R_p$  (=  $R_{ns}^0 + R_s + R_{nd}^0 + R_d$ ) can be solved. The extracted parameters are given in the second row of Table II.

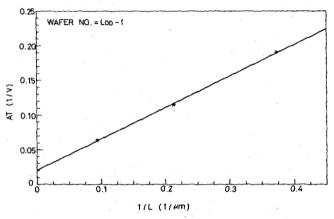

For long-channel devices, the major part of the voltage drop is in the channel region and the resistances of the n regions near the source-drain can be assumed to be the same, i.e.,  $R_{ns}^0 + R_s = R_{nd}^0 + R_d = R_p/2$ . To determine the parameters  $\eta$  and  $\beta$ , the drain current is measured for

Fig. 7. The AT versus  $L^{-1}$  relation to obtain  $\eta$  and  $\beta$ .

each of the long-channel devices ( $L_{\text{mask}} \ge 4 \, \mu\text{m}$ ) at the drain voltage less than the saturation voltage. Using (2), (26), and (27), we can obtain the value of  $AT(=\eta + \beta/L)$  for each device with different channel lengths. Plotting the AT versus 1/L relation as shown in Fig. 7,  $\eta$  and  $\beta$  can be obtained from the slope and the intercept in the vertical coordinate. Therefore, the critical field and saturation velocity can be determined by  $E_c = \beta^{-1}$  and  $V_{sl} = \mu_n/\beta$ .

The sum of contact resistance and spreading resistance due to the  $n^+$  diffusion islands  $(R_s + R_d)$  was extracted from the fabricated devices without  $n^-$  spacers by using the extrapolation method as shown in 2) for  $R_{ns}^0 = R_{nd}^0 = 0$  and the extracted  $R_s(=R_d)$  is listed in Table II. The effective mobility ( $\mu_{\rm eff}$ ) used in (35) was obtained by using the average value of the effective mobility with the extracted parameters for the gate voltage changed from 0 to 5 V.

3) Parameters in the  $n^-$  Region: Since the parameters  $r_n$ ,  $l_1$ , and  $l_2$  were determined by the SEM cross section and spreading analyses, the average doping concentration in the  $n^-$  region can be estimated by the measured doping profile and the average value for a step profile approximation is  $N_d \cong 2.5 \times 10^{17}/\text{cm}^3$  as shown in Table III. The calculated effective dose in the  $n^-$  region  $(N_d r_n)$  is  $0.625 \times 10^{13}/\text{cm}^2$ , which is in reasonable agreement with the total phosphorus dose of  $10^{13}/\text{cm}^2$  implanted across the gate oxide with an energy of 30 keV. Based on the known  $N_d$  value, the average mobility in the bulk  $n^-$  region  $(\mu_b)$  can be obtained from the following empirical expression [11]:

|            | TABLE   | $\mathbf{III}$ |        |

|------------|---------|----------------|--------|

| PARAMETERS | USED IN | THE n          | REGION |

| $\mu_{\rm b}({\rm cm}^2/{\rm v-s})$ | μ <sub>s</sub> (cm <sup>2</sup> /v-s) | N <sub>a</sub> (cm <sup>-3</sup> ) | r <sub>n</sub> (μ <sub>m</sub> ) | 1 <sub>1</sub> (µ <sub>m</sub> ) | 1 <sub>2</sub> (μ <sub>m</sub> ) | V <sub>FBn</sub> (V) |

|-------------------------------------|---------------------------------------|------------------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------|

| 542.74                              | 542.74                                | 2.5 x 10 <sup>17</sup>             | 0.25                             | 0.45                             | 0.2                              | -0.5                 |

$$\mu_b = \frac{1360 - 92}{1 + \left(\frac{N_d}{1.3 \times 10^{17}}\right)^{0.91}} + 92.$$

(54)

The calculated  $\mu_b$  is 542.74 cm<sup>2</sup>/V · s, which is shown in Table III. For simplicity, the surface mobility in the accumulation layer of the n<sup>-</sup> region ( $\mu_s$ ) is assumed to be the same as the calculated  $\mu_b$ . The average doping concentration in the channel region  $(N_a)$  is chosen to be  $N_{AS}$ +  $N_{AB}$ , which is equal to the average doping concentration in the channel for shallow boron implantation. However, the average doping concentration  $(N_a)$  under the n region is chosen to be  $N_{AD} + N_{AB}$ , which is equal to the average doping concentration under the gate for deep boron implantation when  $r_n + W_d < Y_s + W_b$ ; when  $W_d >$  $Y_s + W_b - r_n$ , the average doping concentration under the  $n^-$  region can be calculated by  $N_a = [N_{AD}(Y_s + W_b (r_n) + N_{AB}W_d$   $/W_d$ , which may occur as the backgate is large. The flat-band voltage in the n region  $(V_{FBn})$  is determined by the best fitting in the low drain current and is found to be equal to -0.5 V. The major contribution of  $V_{FBn}$  is found to add an offset current at low gate voltage for the I-V characteristics.

# IV. Comparisons Between Experimental Results AND SIMULATIONS

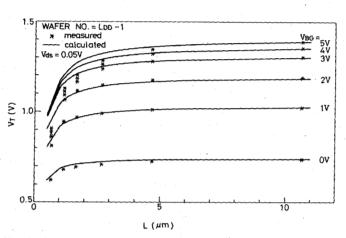

As described in Section III, the parameters in the threshold-voltage model [8] for double-channel-boron implantations have been extracted from the fabricated longchannel MOSFET's. Similarly, the threshold-voltage model developed in [8] for short-channel devices can be used to simulate the threshold voltages of the fabricated short-channel LDD devices. Using the parameters listed in Table I, comparisons between the measured threshold voltages and the simulation results are shown in Fig. 8, in which the shortest effective channel length is  $0.68 \mu m$ . It is clearly seen that satisfactory agreement has been obtained for wide ranges of channel lengths and applied substrate biases and the discrepancy for shorter channellength devices operated at higher substrate biases is mainly due to the simplified charge-sharing scheme used in the threshold-voltage model.

In order to simulate the I-V characteristics of the fabricated LDD devices, the extracted parameters shown in Tables II and III should be used. However, two parameters ( $\mu_n$  and  $\beta$ ) listed in Table II have been slightly adjusted in order to have the best fittings for the I-V characteristics of shorter channel-length devices, and the adjusted parameter values are given in the third row of Table II. The slight adjustments for  $\mu_n$  and  $\beta$  are under-

Fig. 8. Comparisons between the measured threshold voltages and the theoretical calculations at  $V_{ds} = 0.05 \text{ V}$ .

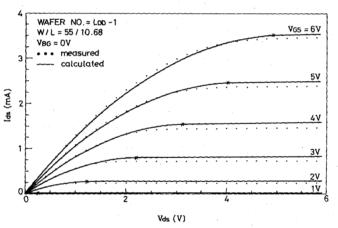

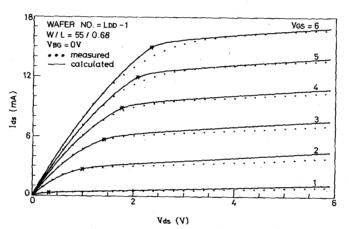

Fig. 9. Comparisons between the measured and calculated I-V characteristics for  $L=10.68~\mu\mathrm{m}$  with  $V_{BG}=0~\mathrm{V}$ .

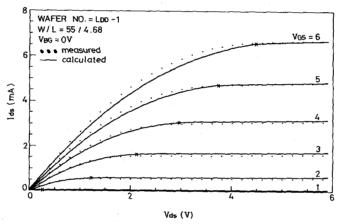

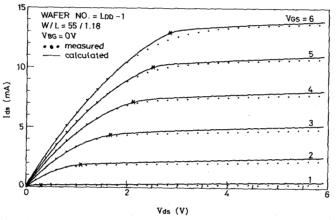

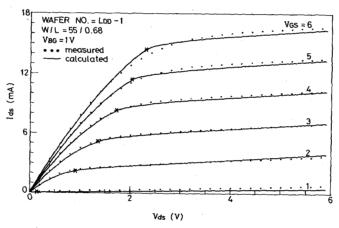

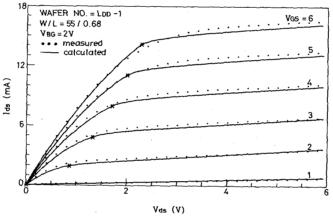

standable because the original  $\mu_n$  and  $\beta$  values have been extracted from the fabricated long-channel devices and the hyperbolic mobility model used has been known to overestimate the scattering-limited velocity ( $V_{sl} = \mu_{n/\beta}$ ) for shorter channel-length devices if the extracted  $\mu_n$  and  $\beta$ values are used. Therefore, the slight adjustments for  $\mu_n$ and  $\beta$  will slightly sacrifice the simulation accuracy for long-channel devices but will produce better simulation results for shorter channel devices. Figs. 9 and 10 show comparisons of the I-V characteristics between the expermental data and the developed model for longer channel lengths  $(L > 4 \mu m)$ , in which the asterisks shown in the figures indicate the calculated saturation voltages for the corresponding gate voltages. Similarly, comparisons for shorter channel lengths (L = 1.18 and 0.64  $\mu$ m) are shown in Figs. 11 and 12. It is clearly seen that agreement

Fig. 10. Comparisons between the measured and calculated I-V characteristics for  $L=4.68~\mu\mathrm{m}$  with  $V_{BG}=0~\mathrm{V}$ .

Fig. 11. Comparisons between the measured and calculated I-V characteristics for  $L=1.18~\mu m$  with  $V_{BG}=0~V$ .

Fig. 12. Comparisons between the measured and calculated I-V characteristics for  $L=0.68~\mu \mathrm{m}$  with  $V_{BG}=0~\mathrm{V}$ .

between the experimental data and the simulation results becomes better as the channel length is reduced, as expected from the adjusted  $\beta$  and  $\mu_n$  values. Note that for all simulated channel lengths, the maximum error is no more than 9 percent and the global error is less than 5 percent (only 3 percent for  $L=0.68~\mu m$ ). In order to show the effects of substrate bias on the I-V characteris

Fig. 13. Comparisons between the measured and calculated I-V characteristics for  $L=0.68~\mu m$  with  $V_{BG}=1~V$ .

Fig. 14. Comparisons between the measured and calculated I-V characteristics for  $L=0.68~\mu\mathrm{m}$  with  $V_{BG}=2~\mathrm{V}$ .

tics, comparisons for an effective channel length of 0.64  $\mu$ m with different applied substrate biases ( $V_{BG}=1$  and 2 V) are shown in Figs. 13 and 14. Similarly, satisfactory agreement between the experimental data and the simulation results is obtained for different applied substrate biases. The global error for  $V_{BG}=1.0$  V is 2 percent and that for  $V_{BG}=2.0$  V is 3.5 percent.

# V. CONCLUSIONS

In this paper, an analytic *I-V* model for MOSFET's with an LDD structure has been developed by considering the n<sup>-</sup> region as a modified buried-channel MOS device and the channel region as an intrinsic enhancement-mode MOSFET. Although the developed model looks complicated, it is a structure/process-oriented model. Moreover, the drain current is explicitly expressed in terms of terminal voltages and, therefore, the drain in the linear/saturation regions and the saturation voltage can be directly calculated from the known terminal voltages. In order to verify the accuracy of the developed *I-V* model, the test devices with the LDD structure fabricated by a standard process have been measured and the methods for extracting the model parameters are presented. It has been shown that satisfactory agreement between the experimental *I-V*

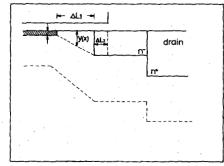

Fig. 15. The schematic diagram for calculating the effective capacitance (C(x)) for the surface charge layer in the  $n^-$  region.

characteristics and the simulation results has been obtained for wide ranges of channel lengths and applied biases by using a set of parameters. Therefore, the developed model can be used for device design and circuit analysis in a CAD system.

#### APPENDIX A

Assuming that the line of the electric field is straight as shown in Fig. 15, the normal electric field at the surface of the n<sup>-</sup> region with respect to the gate can be expressed by

$$E_N(x, y) = \frac{\epsilon_{ox}(y + t_{ox})}{x^2 + (y + t_{ox})^2} [V_{g2} - V_{FBn} - V(x)].$$

(A1)

It is assumed that the effective capacitance is defined at the condition of the maximum electric field with respect to y. Using

$$\left. \frac{dE_N}{dy} \right|_{y=-\infty} = 0 \tag{A.2}$$

and

$$y_0 = x - t_{\rm ox} \tag{A3}$$

and

$$\max E_N(x) = \frac{\epsilon_{ox}}{2x} \left[ V_{g2} - V_{FBn} - V(x) \right]$$

$$= C(x) \left[ V_{g2} - V_{FBn} - V(x) \right] \quad (A4)$$

where C(x) is the effective capacitance per unit area for  $t_{ox} \le x \le l_1$ . For  $0 \le x \le t_{ox}$ , the maximum electric field is obtained by  $y_0 = t_{ox}$ . For  $-l_2 \le x \le 0$ , the electric field is assumed to be uniform along the n region. Then, the effective capacitance per unit area can be expressed as

$$C(x) = \begin{cases} \frac{\epsilon_{\text{ox}}}{t_{\text{ox}}}, & -l_2 \le x \le 0\\ \frac{\epsilon_{\text{ox}}t_{\text{ox}}}{x^2 + t_{\text{ox}}^2}, & 0 \le x \le t_{\text{ox}} \end{cases}$$

$$(A5)$$

$$\frac{\epsilon_{\text{ox}}}{2x}, & t_{\text{ox}} \le x \le l_1.$$

#### APPENDIX B

From (3)–(6), we can get the following results:

$$I_{ds}(l_1 + l_2) = W \left[ \mu_b q N_d \left( r_n V_{d2} - \int_0^{V_{d2}} \Delta r_n dV \right) + \mu_s \overline{C} \left( V_{g2} - V_{FBn} - \frac{1}{2} V_{d2} \right) V_{d2} \right]$$

(B1)

where

$$\int_{0}^{V_{d2}} \Delta r_{n} dV = \frac{2}{3} \left( \frac{2\epsilon_{si} N_{a}}{q N_{d} (N_{a} + N_{d})} \right)^{1/2} \left[ (V_{bi} + V_{BG} + V_{d3})^{3/2} - (V_{bi} + V_{BG} + V_{d4})^{3/2} \right]$$

$$\approx \left( \frac{2\epsilon_{si} N_{a}}{q N_{d} (N_{a} + N_{d})} \right)^{1/2} (V_{bi} + V_{BG} + V_{ds})^{1/2} V_{d2}$$

$$= \Delta r_{ne} V_{d2}$$

(B2)

$$\overline{C} = \frac{\int_{0}^{V_{d2}} C(x) \left[ V_{g2} - V_{FBn} - V(x) \right] dV}{\int_{0}^{V_{d2}} \left[ V_{g2} - V_{FBn} - V(x) \right] dV}$$

$$\approx \frac{\int_{-l_{2}}^{l_{1}} C(x) (x + l_{2}) dx}{\int_{-l_{2}}^{l_{1}} (x + l_{2}) dx}$$

$$= \frac{\epsilon_{ox}}{t_{ox}} l_{2}^{2} + \epsilon_{ox} t_{ox} \left[ \ln(2) + \frac{\pi}{8} \frac{l_{2}}{t_{ox}} \right] + \epsilon_{ox} \left[ (l_{1} - t_{ox}) + l_{2} \ln\left(\frac{l_{1}}{t_{ox}}\right) \right]}{(l_{1} + l_{2})^{2}}.$$

(B3)

Note that (B3) is derived by considering the case that the  $n^-$  region is partially overlapped by the Si gate. For the extreme case that the  $n^-$  region is just outside the silicon gate, (B3) is still valid and the result can be obtained by setting  $l_2$  equal to zero. For the case of  $l_1 = 0$ , the average capacitance is equal to the gate-oxide capacitance.

#### APPENDIX C

Referring to Fig. 3, the one-dimensional Poisson's equation in the pinchoff region can be expressed as follows [9]. For  $-\Delta L_1 \le x < 0$ , we have

$$\frac{d^2V(x)}{dx^2} = \frac{1}{\epsilon_{si}} \left[ qN_{AB} + \frac{J(x)}{V_{si}} \right]$$

(C1)

$$J(x) = \frac{I_{dsat}}{W_{V}(x)} \tag{C2}$$

$$y(x) = \frac{r_n - d}{\Delta L_1} x + r_n.$$

(C3)

For  $0 < x \le \Delta L_2$ , we have

$$\frac{d^2V}{dx^2} = \frac{1}{\epsilon_{\rm si}} \left[ -qN_d + \frac{J(x)}{V_{sl}} \right]$$

(C4)

$$J(x) = \frac{I_{dsat}}{Wr_n} \tag{C5}$$

where d is the thickness of the inversion layer that can be calculated by

$$d = \frac{k_B T}{q|E_s|} \tag{C6}$$

where the surface electric field  $(E_s)$  can be calculated from [8].

The boundary conditions can be written by

$$V(x)\Big|_{x=-\Delta L_1} = V_{dsat} \frac{dV}{dx}\Big|_{x=-\Delta L_1} = E_c$$

$$V(x)\Big|_{x=0} = V_{d1} \frac{dV}{dx}\Big|_{x=0^-} = \frac{dV}{dx}\Big|_{x=0^+}$$

$$V(x)\Big|_{x=\Delta L_2} = V_{d0} \frac{dV}{dx}\Big|_{x=\Delta L_2} = E_c.$$

(C7)

Using the boundary conditions in (C7), Poisson's equation can be solved and the result is

$$V_{d0} - V_{dsat} = E_c \left( 1 - \frac{A}{B} \right) \Delta L_1 + \frac{1}{\epsilon_{si}} \left( C - \frac{A^2}{2B} \right) \Delta L_1^2$$

(C8)

where

$$A = qN_{AB} + \frac{I_{dsat}}{WV_{sl}(r_n - d)} \ln\left(\frac{r_n}{d}\right)$$

(C9)

$$B = -qN_d + \frac{I_{dsat}}{WV_{sl}r_n} \tag{C10}$$

$$C = \frac{qN_{AB}}{2} + \frac{I_{dsat}r_n}{WV_{sl}(r_n - d)^2} \left[ \ln\left(\frac{r_n}{d}\right) - \left(1 - \frac{d}{r_n}\right) \right].$$

(C11)

It is assumed that the resistance of the  $n^-$  region near the drain where the electric field does not reach the critical field  $E_c$  can be approximated by

$$R'_{nd} = R_{nd} \frac{l_1 + l_2 - \Delta L_2}{l_1 + l_2}$$

(C12)

where  $R_{nd}$  is equal to the resistance at the saturation voltage.

Using  $V_{d0} = V_{ds} - I_{dsat}(R_s + R_{ns} + R_d + R'_{nd})$ ,  $\Delta L_1$  can be solved from the following equation:

$$V_{ds} - I_{dsat}(R_s + R_{ns} + R_d + R_{nd}) - V_{dsat}$$

$$= \frac{I_{dsat}R_{nd}A}{(l_1 + l_2)B} \Delta L_1 + E_c \left(1 - \frac{A}{B}\right) \Delta L_1$$

$$+ \frac{1}{\epsilon_{ci}} \left(C - \frac{A^2}{2B}\right) \Delta L_1^2. \tag{C13}$$

#### ACKNOWLEDGMENT

The authors would like to express their sincere thanks to Dr. C.-T. Shih and Dr. C.-C. Chang of ERSO for helpful discussions and encouragement.

#### REFERENCES

- [1] S. Ogura, P. J. Tsang, W. W. Walker, D. L. Critchlow, and J. F. Shepard, "Design and characteristics of the lightly doped drain-source (LDD) insulated gate field-effect transistor," *IEEE Trans. Electron Devices*, vol. ED-27, no. 8, pp. 1359, 1980.

- [2] D. A. Baglee, C. Duvvury, M. C. Smayling, and M. P. Duane, "Lightly doped drain transistors for advanced VLSI circuit," *IEEE Trans. Electron Devices*, vol. ED-32, no. 5, pp. 896, 1985.

- [3] A. Schutz and C. Werner, "State-of-the-art of MOS modeling," in IEDM Tech. Dig., pp. 766, 1984.

- [4] C. Duvvury, D. Baglee, M. Duane, A. Hyslop, M. Smayling, and M. Maekawa, "An analytical method for determining intrinsic drain/ source resistance of lightly doped drain (LDD) devices," Solid-State Electron., vol. 27, no. 1, pp. 89, 1984.

- Electron., vol. 27, no. 1, pp. 89, 1984.

[5] F. S. J. Lai and J. Y. C. Sun, "An analytical one-dimensional model for lightly doped drain (LDD) MOSFET devices," IEEE Trans. Electron Devices, vol. ED-32, no. 12, pp. 2803, 1985.

- [6] C. Y. Wu and Y. W. Daih, "An accurate mobility model for the I-V characteristics of n-channel enhancement-mode MOSFET's with single-channel boron implantation," Solid-State Electron., vol. 28, no. 12, pp. 1271, 1985.

- [7] C. Y. Wu and K. C. Hsu, "A new threshold-voltage model for small geometry buried-channel MOSFET's," Solid-State Electron., vol. 28, no. 12, pp. 1283, 1985.

- [8] C. Y. Wu, G. S. Huang, and H. H. Chen, "An analytical threshold-voltage model for short-channel enhancement mode n-channel MOS-FET's with double boron channel implantation," Solid-State Electron., vol. 29, no. 4, pp. 387, 1986.

[9] G. Merckel, J. Borel, and N. Z. Cupcea, "An accurate large-signal

- [9] G. Merckel, J. Borel, and N. Z. Cupcea, "An accurate large-signal MOS transistor model for use in computer-aided design," *IEEE Trans. Electron Devices*, vol. ED-19, no. 5, pp. 681, 1972.

- [10] C. Y. Wu, Y. W. Daih, and H. H. Chen, "A structure- and process-oriented model for the I-V characteristics of small-geometry n-channel enhancement mode MOSFET with single-channel boron implantation," in Proc. Nat. Sci. Council, Republic of China, Part A: Phys. Sci. Eng., vol. 10, no. 4, pp. 335, 1986.

[11] G. Baccarani and P. Ostoja, "Electron mobility empirically related

- [11] G. Baccarani and P. Ostoja, "Electron mobility empirically related to the phosphorus concentration in silicon," Solid-State Electron., vol. 18, pp. 579, 1975.

Gwo-Sheng Huang (S'85) was born in Chiayi, Taiwan, Republic of China, on November 4, 1959. He received the B.S. degree from National Cheng-Kung University and the M.S. degree from Chiao-Tung University, Taiwan, Republic of China, in 1982 and 1984, respectively, both in electrical engineering. He is currently working toward the Ph.D. degree at the Institute of Electronics, National Chiao-Tung University. His research area has been device modeling for submicrometer MOS structures.

Ching-Yuan Wu (S'72-M'75) was born in Taiwan, Republic of China, on March 18, 1946. He received the B.S. degree from the Department of Electrical Engineering, National Taiwan University, Taiwan, Republic of China, in 1968, and the M.S. and Ph.D. degrees from the State University of New York (SUNY) at Stony Brook, in 1970 and 1972, respectively.

During the 1968-1969 academic year, he served in the Chinese Air Forces as a Second Lieutenant. During the 1972-1973 academic year,

he was appointed as a Lecturer at the Department of Electrical Sciences,

SUNY, Stony Brook. During the 1973-1975 academic years, he was a Visiting Associated Professor at National Chiao-Tung University (NCTU), Taiwan, Republic of China. In 1976, he became a Full Professor in the Department of Electronics and the Institute of Electronics, NCTU. During 1974-1980, he was the Director of Engineering Laboratories and Semiconductor Research Center, NCTU. He was a principal investigator of the National Electronics Mass Plan-Semiconductor Devices and Integrated-Circuit Technologies, during 1976-1979. He was the Director of the Institute of Electronics, NCTU, during 1978-1984. Since 1984, he has been the Dean, College of Engineering, NCTU. He has also been the Research Consultant of the Electronics Research and Service Organization (ERSO). ITRI, and the Academic Advisory Member of the Ministry of Education, Republic of China. He has been the Coordinator of Microelectronics Research and Development Committee, National Science Council (NSC), Republic of China. His research activities have been in semiconductor device physics and modeling, integrated-circuit designs, and technologies. His present research interests focus on small-geometry devices in VLSI, CMOS latchup, new devices, and technologies. He has published over 120 papers in the semiconductor field.

Dr. Wu is a member of Phi Tau Phi and an Editor of the Journal of the Chinese Institute of Engineers in Electrical Engineering. He received the Academic Research Award in Engineering from the Ministry of Education (MOE) in 1979 and the Outstanding Scholar award from the Chinese Educational and Cultural Foundation, Republic of China, in 1985, and has received the Outstanding Research Professor fellowship from the MOE and the National Science Council (NSC), Republic of China, during 1982-1986.