# A New Structure-Oriented Model for Well Resistance in CMOS Latchup Structures

MING-JER CHEN, MEMBER, IEEE, SONG-CHENG SZE, HSING-HAI CHEN, AND CHING-YUAN WU, MEMBER, IEEE

Abstract-A new analytical model has been developed to deal with the parasitic well resistance in CMOS structures. This model also provides a closed-form expression for the induced potential drop in the well due to the action of an emitter in the substrate, and is expressed in terms of the structure parameters in the well, the well sheet resistance, and the current density across the well-substrate junction. Based on the developed model, the calculated potential drops for various structures have been compared with the experimental results and good agreement has been obtained. Furthermore, the steady-state collector current of an active parasitic lateral bipolar transistor, which is used to trigger the parasitic vertical bipolar transistor into the latchup, has been calculated using the developed model. The calculated triggering currents in excess of 1 mA have a maximum error of 20 percent when compared with the experimental results measured from various structures. This error may be improved by taking into account the accurate position-dependent well sheet resistance. Therefore, the developed model becomes an efficient design tool for protecting the devices in the well from being disturbed by an active emitter in the substrate.

### I. Introduction

N A CMOS circuit, the majority-carrier current in he Levell injected by an active emitter in the substrate can produce a resistive potential drop in the well. This potential drop may trigger the CMOS circuit into the latchup state and causes permanent damage on the related devices. Even if this potential drop is not sufficient to trigger the latchup, it may result in the malfunction of the circuit such as the leakage current discharging a charge-storage node located within the well. Therefore, it is valuable to develop a model to calculate the majority-carrier current required to induce a given potential drop in the well. Pinto and Dutton [1] have presented the accurate analysis in this respect using full two-dimensional numerical simulation. To greatly improve the computational efficiency, however, it is desirable to use a simple method with considerable accuracy. Traditionally, such a method has been presented with the well sheet resistances multiplied by the corresponding numbers of squares in the pinched well 2]. The accuracy of this method in the prediction of the steady-state triggering current for latchup has been verified experimentally [3]. However, this method is not applicable for the case of the topside well contact placed close to the well edge, i.e., the guard ring in the well. In

Manuscript received August 11, 1986; revised October 24, 1986.

The authors are with the Institute of Electronics, College of Engineering, National Chiao-Tung University, Hsin-Chu, Taiwan, Republic of China.

IEEE Log Number 8612475.

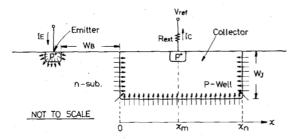

Fig. 1. Cross-sectional view of a parasitic p-n-p transistor in the p-well CMOS circuits. The holes are injected from the active emitter into the substrate, some of which are collected by the p-well.

this paper, a new analytical model is presented to perform the work in a more accurate manner. Based on the developed model, calculated results such as the induced potential drop in the well and the steady-state triggering current for latchup are compared with the experimental data measured from various fabricated structures.

### II. MODEL

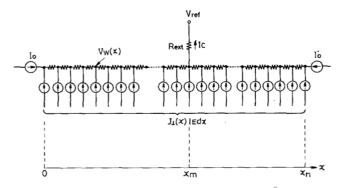

Fig. 1 shows a cross section of a lateral p-n-p transistor that is used to represent a parasitic bipolar device in the p-well CMOS circuits. Moreover, this transistor uses a long-stripe shape geometry with the stripe length denoted as  $l_E$ . As this transistor is operated in the active regime, its p<sup>+</sup>-emitter injects the holes into the substrate, some of which are collected by the well-substrate junction and become the majority carriers in the well. Fig. 1 also shows that not only the sidewall of the well-substrate junction but also the bottom side of the well-substrate junction contribute to the collection of the holes. This feature is included in the proposed model shown in Fig. 2 where the position-dependent current source labeled  $J_{\perp}(x) l_E dx$  accounts for the total collector current across the bottom area of  $l_E dx$  and the current sources labeled  $I_0$  and  $I'_0$  represent the collector currents across the left-hand and right-hand sides of the well-substrate junction, respectively. Note that  $J_{\perp}(x)$  is the position-dependent collector current density per unit area across the bottom side and dx is the incremental length in the x-direction. The model uses a one-dimensional distributed network to appropriately represent the parallel flow lines of the majority-carrier current in the pinched well. In addition, the resistance labeled  $R_{\rm ext}$  in Fig. 2 represents the contact resistance.

Using the superposition principle, the potential drop in the well based on Fig. 2 can be shown to be

Fig. 2. The new model used to calculate the induced potential drop or equivalently the well resistance.

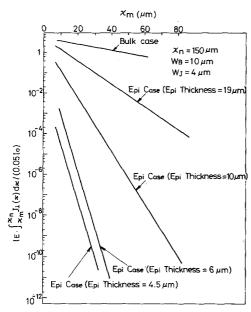

in the bulk case, while for the epi case the lightly doped epitaxial layer uses a doping of  $10^{15}$  cm<sup>-3</sup> and the heavily doped substrate uses a doping of  $4 \times 10^{19}$  cm<sup>-3</sup>. It has been found [5] through this numerical procedure that the greatly suppressed  $J_{\perp}(x)$  for the epi case as shown in Fig. 3 is mainly due to Auger recombination inherent in the heavily doped substrate rather than the consequence of reflection action at the high-low junction. From Fig. 3, it is observed that  $l_E J_{\perp}(x)$  can be appropriately represented by  $be^{-ax}I_0$  where a and b are the positive constants. In a similar way, we make  $I_0' = cI_0$  where c is a positive constant. Consequently, the well transfer resistance can be expressed in a more compact manner by

$$V_{w}(x) - V_{\text{ref}} = \begin{cases} \left(I_{0} + \int_{0}^{x} l_{E}J_{\perp}(x') dx'\right) R_{T1}(x) + \int_{x}^{x_{m}} l_{E}J_{\perp}(x') R_{T1}(x') dx' + I_{c}R_{\text{ext}}, \\ \text{for } 0 \leq x \leq x_{m} \\ \left(I'_{0} + \int_{x}^{x_{n}} l_{E}J_{\perp}(x') dx'\right) R_{T2}(x) + \int_{x_{m}}^{x} l_{E}J_{\perp}(x') R_{T2}(x') dx' + I_{c}R_{\text{ext}}, \end{cases}$$

$$\text{for } x_{m} \leq x \leq x_{n}$$

$$(1)$$

where the voltage  $V_w(x)$  minus  $V_{ref}$  is the position-dependent potential drop in the well. Note that  $R_{T1}$  and  $R_{T2}$  in the above equations are expressed by

$$R_{T1}(x) = \int_{x}^{x_m} \rho_{\square} \frac{dx'}{l_E}$$

and

$$R_{T2}(x) = \int_{x_m}^x \rho_{\square} \frac{dx'}{l_E} \tag{2}$$

where  $\rho_{\square}$  is the position-dependent well sheet resistance and  $dx'/l_E$  represents the incremental number of squares. Furthermore, the total collector current  $I_c$  can be expressed by

$$I_c = I_0 + \int_0^{x_n} l_E J_{\perp}(x) \ dx + I_0'. \tag{3}$$

Therefore, the transfer resistance [4] denoted as  $R_w(x)$  in the well can be obtained by using (1) divided by (3). Note that the special case of  $J_{\perp}(x) = 0$  and  $I'_0 = 0$  in the above expressions for  $0 \le x \le x_m$  represents the traditional method for calculating the well resistance.

A two-dimensional numerical procedure [5] has been performed on the structure shown in Fig. 1 and the calculated result for the integral of  $J_{\perp}(x)$  is shown in Fig. 3. This numerical procedure primarily includes 1) the solution of the low-level minority-carrier injection equation in the substrate with the appropriate boundary conditions; 2) the effects of Auger recombination, Shockley-Read-Hall recombinations, and energy-gap shrinkage; and 3) the effects of the reflection action at the high-low junction of the epi case. A substrate doping of  $10^{15}$  cm<sup>-3</sup> is used

$$R_{w}(x) = \begin{cases} \rho_{\square} \left\{ \left( 1 + \frac{b}{a} \right) (x_{m} - x) + \frac{b}{a^{2}} (e^{-ax_{m}} - e^{-ax}) \right\} \\ l_{E} \left\{ 1 + \frac{b}{a} (1 - e^{-ax_{n}}) + c \right\} \\ \text{for } 0 \le x \le x_{m} \text{ and} \\ \rho_{\square} \left\{ \left( c - \frac{b}{a} e^{-ax_{n}} \right) (x - x_{m}) + \frac{b}{a^{2}} (e^{-ax_{m}} - e^{-ax}) \right\} \\ l_{E} \left\{ 1 + \frac{b}{a} (1 - e^{-ax_{n}}) + c \right\} \\ \text{for } x_{m} \le x \le x_{n} \end{cases}$$

$$(4)$$

Note that (4) has been developed using a constant  $\rho_{\square}$  throughout the well. In a similar way, an analytical expression more complex than (4) can be easily derived for the case of position-dependent sheet resistance along the well.

#### III. RESULTS AND DISCUSSION

To judge the validity of the proposed model, several fabricated structures based on standard p-well CMOS technology are presented. These structures are formed on the same bulk wafer with a well sheet resistance of about  $11 \text{ k}\Omega/\Box$  determined by an auto-spreading resistance probe. Moreover, these structures use long-stripe-shape geometries with a stripe length  $(l_E)$  of  $150 \mu m$  so that the present two-dimensional simulation space is allowed to appropriately represent the actual three-dimensional case.

Fig. 3. The calculated  $J_{\perp}(x)$  in the integral form as a function of  $x_{i,j}$  for the structure shown in Fig. 1 [5].

The experimental results for these structures and the simulated results based on the developed model are presented as follows.

## A. Resistance Potential Drop

One of the fabricated structures used to investigate the induced potential drop in the well is shown in Fig. 4 where the values of relevant dimensions are indicated in details. There are three different definitions for terminal connections shown in Fig. 4: 1) the terminal  $V_{cl}$  is floating and the terminal  $V_{c2}$  is connected to the collector terminal; (2) the terminal  $V_{c2}$  is floating and the terminal  $V_{c1}$  is connected to the collector terminal; and (3) both the terminals  $V_{c1}$  and  $V_{c2}$  are connected to the identical collector terminal. The potential drop in the first terminal connection is defined as the voltage  $V_{c1}$  minus  $V_{c2}$  due to the current  $I_{c2}$ , while in the second terminal connection the potent al drop is the voltage  $V_{c2}$  minus  $V_{c1}$  due to the current  $I_{c1}$ . Furthermore, the third terminal connection is used to verify the model on the correlation between  $I_{c1}$  and  $I_{c2}$  under the condition of  $V_{c1} = V_{c2}$ .

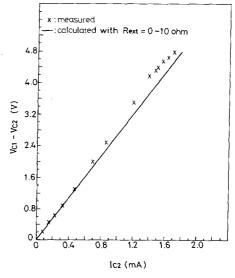

By fitting the integral of  $be^{-ax}$   $I_0$  to the numerical results of the bulk case in Fig. 3, we obtain  $a=0.03~\mu\text{m}^{-1}$  and  $b=0.006~\mu\text{m}^{-1}$  for  $j_{\perp}(x)$ , and in a similar way we have c=0.006 for  $I_0'$  [5]. These numerically fitted data are used throughout the paper. The case of the first terminal connection has been calculated using (4) with  $x=1~\mu\text{m}$ ,  $x_m=39.5~\mu\text{m}$ , and  $x_n=43~\mu\text{m}$  for  $R_{\text{ext}}=0$  and  $10~\Omega$ . The calculated results are shown in Fig. 5 where the experimental results are also shown for comparisons. From Fig. 5, it can be seen that the model has yielded results that are in good agreement with the experimental data. The case of the second terminal connection is shown

Fig. 4. The fabricated structure with the detailed relevant dimensions in order to verify the model.

Fig. 5. The calculated and measured  $V_{c1}$  with respect to  $V_{c2}$  as a function of  $I_{c2}$  for Fig. 4 with  $I_{c1}=0$ .

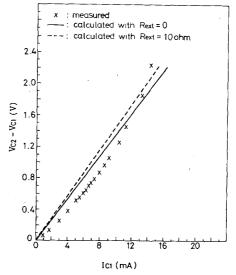

Fig. 6. The calculated and measured  $V_{c2}$  with respect to  $V_{c1}$  as a function of  $I_{c1}$  for Fig. 4 with  $I_{c2}=0$ .

in Fig. 6 where the calculated results have been obtained using (4) with  $x=42 \mu m$ ,  $x_m=3.5 \mu m$ , and  $x_n=43 \mu m$  for  $R_{\rm ext}=0$  and 10  $\Omega$ . As can be seen from Fig. 6, the

Fig. 7. The calculated and measured  $I_{c1}$  as a function of  $I_{c2}$  for Fig. 4 with

calculated results agree closely with the experimental data. Comparisons between Figs. 5 and 6 show that the spacing between the topside well contact and the emitter in the substrate should be less than that between the emitter in the well and the emitter in the substrate so that the induced potential drop under the emitter in the well can be greatly reduced for a given majority-carrier current. Furthermore, Fig. 7 shows the case of the third terminal connection where the calculated results have a maximum error of 30 percent when compared with the experimental data. The calculated results in Fig. 7 are based on the determination of a point labeled  $x_{eff}$  between the two topside well contacts by solving the following equation:

$$V_w(x_{\text{eff}}^-) - V_{c1} = V_w(x_{\text{eff}}^+) - V_{c2}$$

(5)

where

$$I_{c1} = I_0 + \int_0^{x_{\text{eff}}} l_E J_{\perp}(x) dx$$

and

$$I_{c2} = \int_{x_{c0}}^{x_3} l_E J_{\perp}(x) dx + I_0'.$$

(6)

By substituting  $l_E J_{\perp}(x) = be^{-ax} I_0$  and  $I'_0 = cI_0$  into (5) and (6), and using a constant  $\rho_{\square}$ , we have

the determination of a point labeled

$$x_{\text{eff}}$$

between poside well contacts by solving the following

$$V_{w}(x_{\text{eff}}^{-}) - V_{c1} = V_{w}(x_{\text{eff}}^{+}) - V_{c2}$$

$$(5) \begin{cases} \rho_{\square}(x_{2} - x_{1}) + 2 R_{\text{ext}} l_{E} \\ \rho_{\square} \frac{1}{a} (e^{-ax_{1}} - e^{-ax_{2}}) + \left(1 + \frac{a}{b} - \frac{ac}{b} + e^{-ax_{3}}\right) R_{\text{ext}} l_{E} \end{cases}$$

$$(7)$$

$$V_{w}(x) = \begin{cases} \left[ \int_{x}^{x_{\text{eff}}} l_{E}J_{\perp}(x') dx' \right] \int_{x_{1}}^{x} \rho_{\square} \frac{dx'}{l_{E}} + \int_{x_{1}}^{x} l_{E}J_{\perp}(x') \left[ \int_{x_{1}}^{x'} \rho_{\square} \frac{dx''}{l_{E}} \right] dx' + I_{c1}R_{\text{ext}} + V_{c1}, \\ \text{for } x_{1} \leq x \leq x_{\text{eff}}^{-} \\ \left[ \int_{x_{\text{eff}}}^{x} l_{E}J_{\perp}(x') dx' \right] \int_{x}^{x_{2}} \rho_{\square} \frac{dx'}{l_{E}} + \int_{x}^{x_{2}} l_{E}J_{\perp}(x') \left[ \int_{x'}^{x_{2}} \rho_{\square} \frac{dx''}{l_{E}} \right] dx' + I_{c2}R_{\text{ext}} + V_{c2}, \\ \text{for } x_{\text{eff}}^{+} \leq x \leq x_{2}. \end{cases}$$

Equation (5) states that the potential drop at the point  $x_{\text{eff}}$ is unique under  $V_{c1} = V_{c2}$ . Furthermore, the collector current density for  $x < x_{\text{eff}}$  contributes to  $I_{c1}$  and the collector current density for  $x > x_{\text{eff}}$  contributes to  $I_{c2}$ , i.e.

$$I_{c1} = I_0 \left\{ 1 + \frac{b}{a} \left( 1 - e^{-ax_{\text{eff}}} \right) \right\}$$

(8)

$$I_{c2} = I_0 \left\{ \frac{b}{a} \left( e^{-ax_{\text{eff}}} - e^{-ax_3} \right) + c \right\}$$

(9)

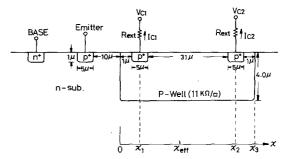

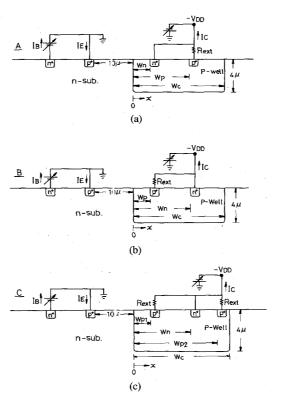

Fig. 8. The fabricated structures used to verify the accuracy of the model with respect to the steady-state triggering current. The relevant dimensions are shown in Table I.

and

$$R_{w}(x) = \begin{cases} \rho_{\square} \frac{b}{a} \left( x_{1} e^{-ax_{\text{eff}}} - x e^{-ax_{\text{eff}}} + \frac{1}{a} e^{-ax_{1}} - \frac{1}{a} e^{-ax} \right) + \left[ 1 + \frac{b}{a} \left( 1 - e^{-ax_{\text{eff}}} \right) \right] R_{\text{ext}} l_{E}}{l_{E} \left\{ 1 + \frac{b}{a} \left( 1 - e^{-ax_{3}} \right) + c \right\}}, \\ for \quad x_{1} \leq x \leq x_{\text{eff}} \\ \rho_{\square} \frac{b}{a} \left( x_{2} e^{-ax_{\text{eff}}} - x e^{-ax_{\text{eff}}} + \frac{1}{a} e^{-ax_{2}} - \frac{1}{a} e^{-ax} \right) + \left[ \frac{b}{a} \left( e^{-ax_{\text{eff}}} - e^{-ax_{3}} \right) + c \right] R_{\text{ext}} l_{E}}{l_{E} \left\{ 1 + \frac{b}{a} \left( 1 - e^{-ax_{3}} \right) + c \right\}}, \end{cases}$$

$$for \quad x_{\text{eff}} \leq x \leq x_{2}, \end{cases}$$

where  $R_w(x)$  is defined as the potential drop  $(V_w(x) - V_{c1}(=V_{c2}))$  divided by the sum of  $I_{c1}$  and  $I_{c2}$ . Note that the calculated results in Fig. 7 have been obtained using  $x_1 = 3.5 \ \mu m$ ,  $x_2 = 39.5 \ \mu m$ , and  $x_3 = 43 \ \mu m$ . Moreover, an analytical model more complex than (7)–(10) can be easily derived in a similar way for the case of position-dependent sheet resistance along the well. Based on the above results, it is concluded that the developed model is capable of yielding design rules for locating the devices on the appropriate regime within the well, so that the induced potential drop due to an active emitter in the substrate is too small to cause the malfunction of the devices.

# B. Steady-State Triggering Current

Several structures like those shown in Fig. 8 have been characterized with respect to the steady-state triggering current. This current is defined as the collector current of the lateral p-n-p transistor to initiate the latchup. The measured triggering current labeled  $I_{\rm c\parallel, ug}$  for each structure is listed in Table I where the corresponding structure parameters are also shown. Note that the structure labeled C-1 in Table I has the guard ring in the well and has the largest triggering current among the illustrated structures. Based on the developed model, the corresponding

| TABLE I                                                     |  |  |  |  |  |  |  |

|-------------------------------------------------------------|--|--|--|--|--|--|--|

| THE STRUCTURE PARAMETERS FOR FIG. 8 AND THE CALCULATED WELL |  |  |  |  |  |  |  |

| RESISTANCES AND MEASURED STEADY-STATE TRIGGERING CURRENTS   |  |  |  |  |  |  |  |

| Structure Notation | W <sub>P</sub> 1* |      |    |     |    |       | R <sub>W</sub> (ohm) <sup>++</sup> | Icu,trg(mA) |

|--------------------|-------------------|------|----|-----|----|-------|------------------------------------|-------------|

| A - I              | 37                | 37   | 18 | 43  | 18 | 1526  | 1536                               | 0.44        |

| A - 2              | 37                | 37   | 9  | 43  | 9  | 2137  | 2147                               | 0.28        |

| A - 3              | 156               | 156  | 1  | 171 | 1  | 11113 | 11123                              | 0.064       |

| B - 1              | 1                 | 1    | 18 | 43  | 23 | 108   | 118                                | 4.0         |

| B - 2              | 1                 | 1    | 22 | 43  | 27 | 120   | 130                                | 4.8         |

| C - 1              | 1                 | 37 , | 18 | 43  | 18 | 33    | 39                                 | 10.6        |

<sup>\*:</sup>  $W_{p1} = W_{p2}$  represents the case shown in Fig. 8(a) and Fig. 8(b).

well resistances have been calculated and are shown in Table I. To calculate the steady-state triggering current, the following expression has been used [3]:

$$I_{c\parallel, \text{trg}} = V_{BE\perp, \text{on}}/R_w \tag{11}$$

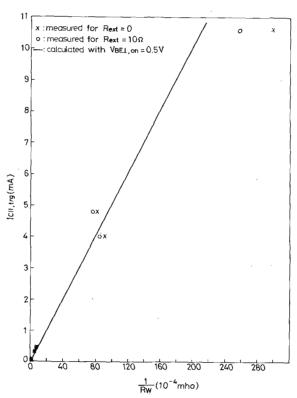

where  $V_{BE\perp, on}$  represents not only the induced potential drop in the well but also the turn-on voltage across the base-emitter junction of the vertical n-p-n transistor. The correlations between the measured triggering current and the inverse of the calculated  $R_w$  for each structure in Table I are established in Fig. 9. The calculated results using (11) are shown in Fig. 9 with  $V_{BE\perp, on} = 0.5$  V. It can be seen from this figure that there is a maximum error of 20 percent between model result and experimental data for the structure labeled C-1. This error may be due to 1) the assumed constant sheet resistance  $\rho_{\square}$  when using (7)-(10), and 2) the fluctuations of the well sheet resistance of the fabricated devices. Usually the sheet resistance under the emitter in the well is greater than that elsewhere in the well. Moreover, according to Troutman and Hargrove [4], the insertion of an emitter in the substrate can drastically alter the substrate transfer resistance. Therefore, the application of (7)-(10) using a constant sheet resistance determined outside the emitter in the well may overestimate the triggering current as shown in Fig. 9 for the structure labeled C-1. However, a constant sheet resistance determined under the emitter in the well may lead to the underestimation of the triggering current and in this respect the simple model may be useful for the worst case design. Nevertheless, it is very helpful to use the general expressions shown in this paper as long as the

Fig. 9. The calculated and measured steady-state triggering currents  $I_{c\parallel, \rm trg}$  versus  $1/R_w$  for the structures in Table I.

position-dependent well sheet resistance has been accurately determined. Note that the choice of  $V_{BE\perp, \text{on}} = 0.5$  V in (11) is based on the fact that, as the emitter current of the vertical n-p-n transistor is negligibly small with re-

<sup>\*\*:</sup> x denotes the position where the emitter edge locates and is used to calculate  $\mathbf{R}_{\mathbf{W}}$  .

<sup>+:</sup> The calculated result under Rext=0.

<sup>++:</sup> The calculated result under  $R_{\text{ext}}=10$  ohm.

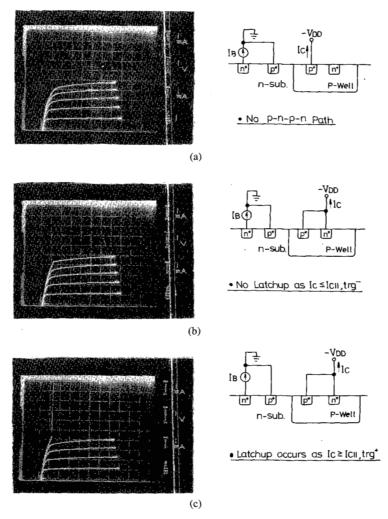

Fig. 10. The measured collector *I-V* characteristics of the lateral p-n-p transistor for the structure labeled B-2 with the absence of the vertical n-p-n transistor for (a) and with the presence of the vertical n-p-n transistor for (b) and (c).

spect to  $I_{c\parallel, \rm trg}$ , its base-emitter voltage is smaller than  $V_{BE\perp, on}$  of about 0.5 V. This is verified by Fig. 10, which shows the measured collector I-V characteristics of the lateral p-n-p transistor for the structure labeled B-2 with different terminal connections. Fig. 10(a) shows the operating regime of the independent lateral p-n-p transistor while Fig. 10(b) and 10(c) shows the behavior of the lateral transistor that is located in a complete p-n-p-n path. Fig. 10(b) is obtained for the collector current ranging between 0 and  $I_{c\parallel,\text{trg}}$  above which the latchup will occur. The curves in Fig. 10(b) are nearly identical to those in Fig. 10(a), irrespective of the connection of the n<sup>+</sup> enitter to the  $-V_{DD}$  terminal. Now as a very small current is added to the original base current of Fig. 10(b) in order to make the uppermost curve slightly approach a critical value of  $I_{c\parallel, \text{trg}}$ , latchup occurs as shown in Fig. 10(c). Note that the curves in Fig. 10(a) and (b) are nearly identical to those in Fig. 10(c) for a collector current less than  $I_{c\parallel,\mathrm{trg}}$  since the corresponding base currents are nearly identical between Fig. 10(a), (b), and (c). Therefore, the accuracy of the proposed model has been confirmed despite of its simplicity.

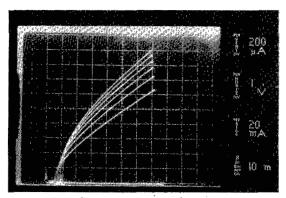

Finally, a fabricated structure like Fig. 8(b) with  $W_p =$ 156  $\mu$ m,  $W_n = 165 \mu$ m, and  $W_c = 171 \mu$ m is used to illustrate the application of the model and to establish design rules that provide normal operation for the devices in the well under the action of an emitter in the substrate. The well resistance for this structure has been calculated to be 14.4  $\Omega$  for  $R_{\rm ext} = 10 \Omega$ ; as a result, the collector current of the lateral p-n-p transistor to trigger the latchup is 35 mA using (11) with  $V_{BE\perp, on} = 0.5$  V. Therefore, the corresponding emitter current of the lateral p-n-p transistor is greater than 3.5 A since the common-emitter current gain of the lateral p-n-p transistor has been empirically estimated to be less than 0.01 (see Fig. 11). Such a large current may damage the devices prior to latchup. It has been verified experimentally that this structure is free from latchup due to the strong forward-biased emitter in the substrate, as shown in Fig. 11. In addition, this structure has been experimentally found to burn out as the emitter current of the lateral p-n-p transistor exceeds about 200 mA. Note that to preclude the latchup under the action of an emitter in the substrate, a large value of  $W_p$  is required for the bulk structure in Fig. 8(b) while this value may be

Fig. 11. The measured collector I-V characteristics of the lateral p-n-p transistor with the presence of the vertical n-p-n transistor for the structure in Fig. 8(b) with  $W_p=156~\mu\mathrm{m}$ ,  $W_n=165~\mu\mathrm{m}$ , and  $W_c=171~\mu\mathrm{m}$ . No latchup is observed.

significantly reduced for the same structure based on the epi wafer. This can be seen from Fig. 3 that the current density  $J_{\perp}(x)$  across the bottom side of well-substrate junction is greatly suppressed for the epi case.

#### IV. CONCLUSION

A new structure-oriented model has been presented to calculate the resistance potential drop in the well of CMOS structures due to the action of an emitter in the substrate. In a step-by-step manner, the simulated results using the developed model for various structures have been found to be in good agreement with the experimental data of the induced potential drop in the well and the steady-state triggering current for latchup. Moreover, the model is capable of yielding design rules in order to prevent the devices in the well from being disturbed by an active emitter in the substrate.

## REFERENCES

- M. R Pinto and R. W. Dutton, "Accurate trigger condition analysis for CMOS latchup," *IEEE Electron Device Lett.*, vol. EDL-6, pp. 100-102, Feb. 1985.

- [2] D. B. Estreich, "The physics and modeling of latch-up and CMOS integrated circuits," Ph.D. dissertation, Stanford Electronics Labs. Tech. Rep. G-201-9, 1980.

- [3] M. J. Chen and C. Y. Wu, "An efficient method for calculating the dc triggering currents in CMOS latch-up," Solid-State Electron., vol. 29, no. 5, pp. 551-554, May 1986.

- [4] R. R. Troutman and M. J. Hargove, "Transmission line modeling of substrate resistances and CMOS latchup," *IEEE Trans. Electron Devices*, vol. ED-33, no. 7, pp. 945-954, July 1986.

- [5] M. J. Chen, "Modeling and prediction of SCR latch-up in CMOS/ VLSI," Ph.D. dissertation, National Chiao-Tung University, June 1985.

Ming-Jer Chen (S'77-M'86) was born in Taiwan, Republic of China, on April 1, 1954. He received the B.S. degree with highest honors from National Cheng-Kung University in 1977, and the M.S. and Ph.D. degrees from National Chiao-Tung University in 1979 and 1985, respectively, all in electrical engineering. His doctoral work involved the modeling and prediction of CMOS latchung.

From 1979 to 1980, he worked for Telecommunication Labs., Taiwan, where he was respon-

sible for the design of a multiprocessor distributed system. From 1985 to 1986, he conducted post-doctoral research on CMOS latchup at National Chiao-Tung University where he was also a part-time Associate Professor. He recently became an Associate Professor in the Department of Electronics and the Institute of Electronics, National Chiao-Tung University. His primary research interests are on the modeling and optimization of semi-conductor devices and integrated circuits with enhanced performance and improved reliability.

Song-Cheng Sze was born in Taiwan, Republic of China, on June 2, 1962. He received the B.S. degree in electrical engineering from the Tatung Institute of Technology in 1984 and the M.S. degree in electronics engineering from National Chiao-Tung University in 1986.

Hsing-Hai Chen was born in Taiwan, Republic of China, in 1952. He received the B.S. degree in electrophysics from National Chiao-Tung University in 1976 and the M.S. degree in applied physics from National Tsing Hua University in 1978. He is working toward the Ph.D. degree at the Institute of Electronics, National Chiao-Tung University, Republic of China.

Since 1980, he has worked with the Electronics Research and Service Organization (ERSO), ITRI. His research area has been in semiconductor de-

vices and process development for MOS, and he is currently involved in the development of CMOS/VLSI process.

Ching-Yuan Wu (S'69-M'72) was born in Taiwan, Republic of China, on March 18, 1946. He received the B.S. degree from the Department of Electrical Engineering, National Taiwan University, Taiwan, Republic of China, in 1968, and the M.S. and Ph.D. degrees from the State University of New York (SUNY) at Stony Brook, in 1970 and 1972, respectively.

During the 1968-1969 academic year, he served in the Chinese Air Forces as a Second Lieutenant. During the 1972-1973 academic year,

he was appointed as a Lecturer at the Department of Electrical Sciences, SUNY, Stony Brook. During the 1973-1975 academic years, he was a Visiting Associate Professor at National Chiao-Tung University (NCTU), Taiwan, Republic of China. In 1976, he became a Full Professor in the Department of Electronics and the Institute of Electronics, NCTU, During 1974-1980, he was the Director of the Engineering Laboratories and Semiconductor Research Center, NCTU. He was a principal investigator of the National Electronics Mass Plan-Semiconductor Devices and Integrated-Circuit Technologies during 1976-1979. He was the Director of the Institute of Electronics, NCTU, during 1978-1984. Since 1984, he has been the Dean, College of Engineering, NCTU. He has also been the Research Consultant of the Electronics Research and Service Organization (ERSO), ITRI, and the Academic Advisory Member of the Ministry of Education, Republic of China. He has been the Coordinator of Microelectronics Research and Development Committee, National Science Council (NSC), Republic of China. His research activities have been in semiconductor device physics and modeling and integrated-circuit design and technology. His present research interest is focused on small-geometry devices in VLSI, CMOS latchup, and new devices and technologies. He has published over 120 papers in the semiconductor field.

Dr. Wu is a member of Phi Tau Phi and an Editor of the Journal of the Chinese Institute of Engineers in Electrical Engineering. He received the Academic Research Award in Engineering from the Ministry of Education (MOE) in 1979, and the Outstanding Scholar award from the Chinese Educational and Cultural Foundation, Republic of China, in 1985. He has received the outstanding research Professor fellowship from the MOE and the National Science Council (NSC), Republic of China, during 1982–1986.