# 國立交通大學

電信工程研究所

碩士論文

擁有寬捕獲範圍之全數位 鎖相迴路電路設計

A Wide Capture Range PLL based on All-Digital Design

研 究 生:謝進益

指導教授:高銘盛 教授

中華民國一百年七月

# 擁有寬捕獲範圍之全數位鎖相迴路電路設計 A Wide Capture Range PLL based on All-Digital Design

研究生:謝進益 Student: Chin-Yi Hsieh

指導教授:高銘盛 Advisor:Ming-Seng Kao

國立交通大學電信工程研究所 碩士論文

Submitted to Institute of Communication Engineering

College of Electrical and Computer Engineering

National Chiao Tung University

in partial Fulfillment of the Requirements

for the Degree of

Master

in

Communication Engineering

July 2011

Hsinchu, Taiwan, Republic of China

中華民國一百年七月

# 擁有寬捕獲範圍之全數位鎖相迴路 電路設計

學生:謝進益 指導教授:高銘盛 教授

國立交通大學 電信工程研究所

# 摘要

本論文設計一個擁有極寬捕捉頻帶的全數位鎖相迴路,其鎖定頻率範圍從 1kHz 到 1MHz。此鎖相迴路的最高頻率與最低頻率的倍率為 1000,並且使用者不需知道輸入頻率的範圍,只要工作頻率位於此區間的應用,皆可使用此電路。為了能夠適用於充滿雜訊的環境,所設計的電路擁有良好的抗雜訊能力,即使在 SNR=0dB 的惡劣環境中,它依然可以正常的運作。

在設計時,我們著重於三個效能參數:頻率鎖定的正確率、鎖定效率與抗頻率漂移能力。為了能在各個面向都有良好的表現,我們設計三種不同的工作模式及對應的演算法,其中包含捕獲模式、追蹤模式與相位修正模式,並且在實際電路中選擇使用雙迴路的方式,以完成一個全數位雙迴路鎖相電路。最後,我們利用硬體描述語言實現此鎖相迴路,以驗證其可行性。

# A Wide Capture Range PLL based on All-Digital Design

Student: Chin-Yi Hsieh Advisor: Prof. Ming-Seng Kao

Institute of Communication Engineering

National Chaio Tung University

<u>Abstract</u>

In this thesis we design an all-digital phase-locked loop (PLL) with ultra-wide capture range which spans from 1kHz to 1MHz. The ratio of the highest frequency to the lowest frequency is 1000 and there is no need for prior information of the input frequency. With this PLL, all applications whose working frequency is within this frequency range could use it to implement the corresponding system. Also, for applying it in noisy environment, the PLL is asked to have good noise immunity. It is designed to work efficiently when SNR=0dB.

On designing this PLL, we focus on three aspects: the frequency locked rate, the lock efficiency and the capability of anti-frequency drift. For good efficiency in every aspect within wide capture range under noisy environment, we design three different states which include the acquisition state, the tracking state and the phase-fixing state. Moreover, we introduce the dual-loop system to further improve the performance. Finally, to verify the feasibility of our approach, we implement this PLL by Hardware Description Language based on all-digital design.

ii

### 誌謝

當我需要寫到個段落時,也代表著我的交大生涯已在開始倒數,謹以此篇文章以表兩年來給予我幫助的人獻上深深的敬意。

首先在我研究所期間影響最深的當屬我的指導教授高銘盛老師,除了專門學問之外, 老師給予我最大的學習就是何謂研究的態度,或許在未來我所扮演的角色會變,研究的學問也會不斷的更新,但是這份學習精神卻是不容遺忘的。此外還有多虧兩位大學長,兩位中學長和兩位小學弟,讓我兩年來在研究上不至於孤軍奮門,也充實我碩士生活的回憶。 最後當然也要感謝我的家人父母,讓我可以在這段時間安心的做好學生的本分,以本身的 辛勞來換取我學習的資源,就是這份支持才足以支撐我在求學期間所遭遇到的總總挫折與 困難,讓我最後能成功的獲得交大碩士的肯定,謝謝你們。

# **Contents**

| Abs  | trac | t        |                                        | i    |

|------|------|----------|----------------------------------------|------|

| Ack  | now  | ledgem   | nent                                   | iii  |

| Con  | tent | s        |                                        | iv   |

| List | of   | Tables   |                                        | vii  |

| List | of I | Figures  |                                        | viii |

| 1    | Intı | roductio | on                                     | 1    |

|      | 1.1  | PLL C    | Overview                               | 1    |

|      |      | 1.1.1    | History and Application                | 1    |

|      |      | 1.1.2    | All-Digital Phase-Locked Loop          | 2    |

|      | 1.2  | Resear   | rch Motivation                         |      |

|      |      | 1.2.1    | Motivations and Purpose of Research    | 2    |

|      |      | 1.2.2    | Research Approaches                    | 4    |

|      | 1.3  | Thesis   | s Organization                         | 4    |

| 2    | Pha  | ise-Loc  | ked Loop Basics                        | 5    |

|      | 2.1  | Linear   | r Model of PLL                         | 5    |

|      |      | 2.1.1    | Phase Detector Characteristics         | 6    |

|      |      | 2.1.2    | VCO Characteristics                    | 6    |

|      |      | 2.1.3    | Frequency Response of Linear PLL Model | 7    |

|      |      | 2.1.4    | Loop Filter Characteristics            | 9    |

|      | 22   | Traditi  | ional PLL Circuit Design               | 11   |

|   |       | 2.2.1  | Analog PLL12                              |

|---|-------|--------|-------------------------------------------|

|   |       | 2.2.2  | Digital PLL                               |

|   |       | 2.2.3  | All-Digital PLL15                         |

|   | 2.3   | An AI  | DPLL Circuit Model16                      |

|   |       | 2.3.1  | Phase Frequency Detector                  |

|   |       | 2.3.2  | Time to Digital Converter                 |

|   |       | 2.3.3  | Digital Integrator                        |

|   |       | 2.3.4  | Digital-Controlled Oscillator             |

|   | 2.4   | Desig  | n Challenges20                            |

| 3 | Creat | tom An | echitecture 23                            |

| ) | •     |        | ALLIEN.                                   |

|   | 3.1   | Acqui  | sition State23                            |

|   | 3.2   | Tracki | ing State30                               |

|   |       |        | -Fixing State                             |

|   | 3.4   | Noise  | Problem                                   |

|   |       | 3.4.1  | Noise Effect                              |

|   |       | 3.4.2  | Conversion of Noise                       |

|   |       | 3.4.3  | Improvement in Acquisition State44        |

|   |       | 3.4.4  | Improvement in Tracking State45           |

|   |       | 3.4.5  | Improvement in Phase-Fixing State47       |

|   | 3.5   | Summ   | nary                                      |

|   | 3.6   | Dual-  | Loop PLL System49                         |

|   |       | 3.6.1  | The Primary Loop and the Secondary Loop50 |

|   |       | 3.6.2  | Improvement of Dual-Loop System           |

| ļ | Svsi  | tem Im | aplementation by Digital Hardware 55      |

|   |       |        | m Module                                  |

|   | 4 1   | Syster | n woone )                                 |

|     |       | 4.1.1   | Phase Frequency Detector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 56 |

|-----|-------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     |       | 4.1.2   | Time to Digital Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 57 |

|     |       | 4.1.3   | Digital Loop Filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 58 |

|     |       | 4.1.4   | Digital-Controlled Oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 60 |

|     |       | 4.1.5   | State Control Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 62 |

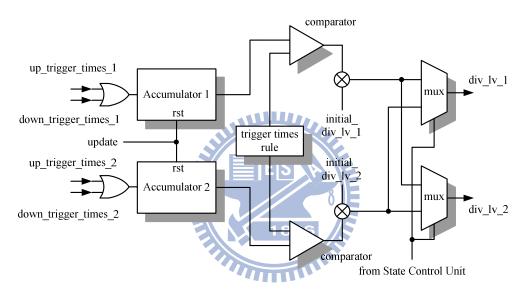

|     |       | 4.1.6   | Divider Control Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 62 |

| 5   | Sim   | ulation | Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 64 |

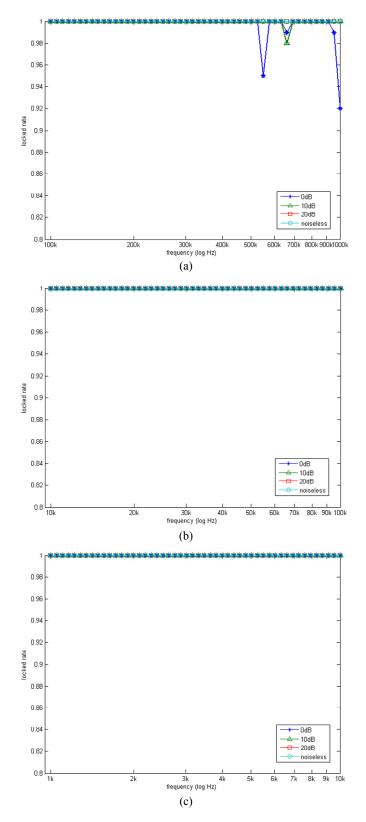

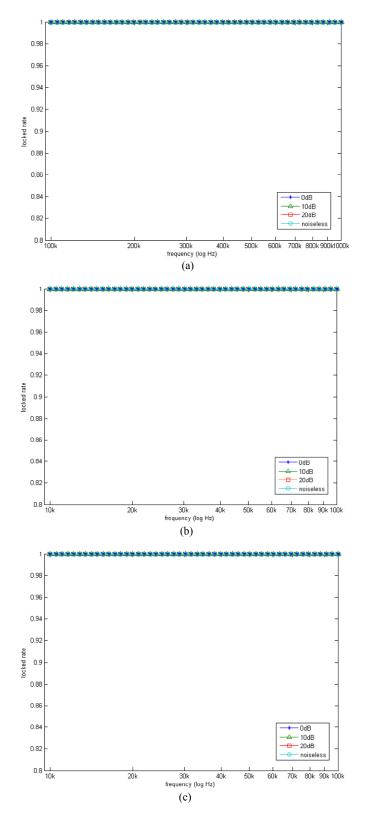

|     | 5.1   | Freque  | ency Locked Rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 64 |

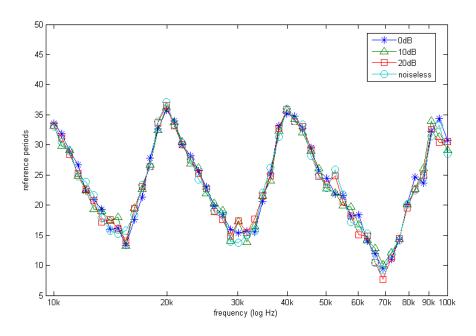

|     | 5.2   | Lock E  | Efficiency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 67 |

|     | 5.3   | Capabi  | ility of Anti-Frequency Draft                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 72 |

| 6   | Con   | clusion | ES A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 75 |

| Ref | erenc | ees     | 1896                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 77 |

|     |       |         | The state of the s |    |

# **List of Tables**

| 1.1 | Performance parameters about several PLL systems                                                | 3  |

|-----|-------------------------------------------------------------------------------------------------|----|

| 3.1 | Trigger times for several m                                                                     | 28 |

| 3.2 | Decision rule of band change                                                                    | 28 |

| 3.3 | $N_{Tref}$ and $R_{\Delta f}$ by the end of acquisition state with different noise environments | 45 |

| 5.1 | The reference period required for different cases in single-loop system                         | 70 |

| 5.2 | The reference period required for different cases in dual-loop system                           | 71 |

# **List of Figures**

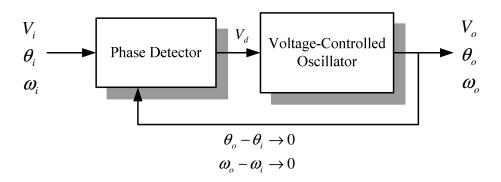

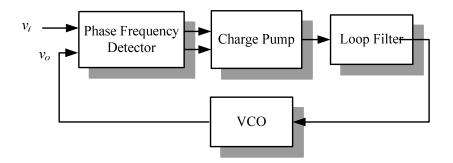

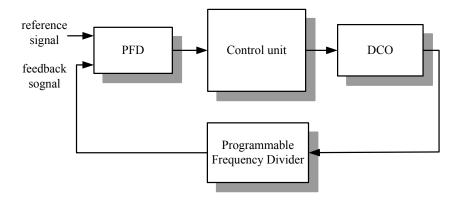

| 2.1  | The general function block of PLL                             | 5   |

|------|---------------------------------------------------------------|-----|

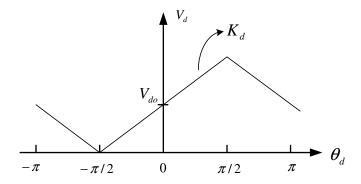

| 2.2  | Phase detector characteristic                                 | .6  |

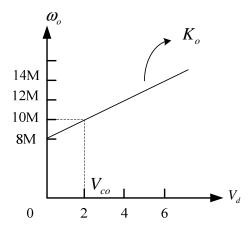

| 2.3  | Voltage-controlled oscillator characteristic                  | 7   |

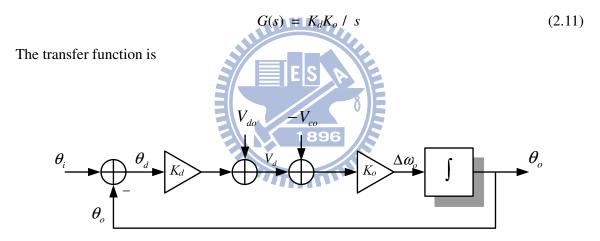

| 2.4  | Linear model with PD and VCO                                  | 8   |

| 2.5  | The AC model with PD and VCO                                  | .8  |

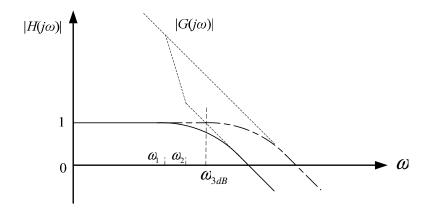

| 2.6  | Frequency response and bandwidth of linear PLL model          | .9  |

| 2.7  | A RRC low pass filter                                         | 10  |

| 2.8  | Frequency response of RRC low pass filter S.                  | 10  |

|      | Frequency response and bandwidth of complete linear PLL model |     |

| 2.10 | The complete linear PLL model 1896                            | 11  |

| 2.11 | The multiplier PD characteristic                              | 12  |

| 2.12 | PI filter circuit                                             | 13  |

| 2.13 | Block structure diagram of DPLL                               | 13  |

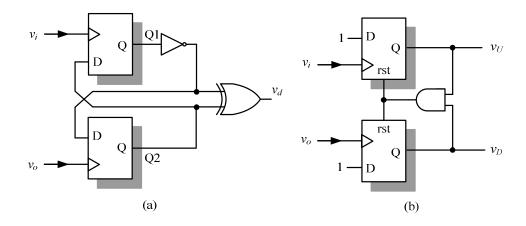

| 2.14 | (a) Two-state PFD structure (b) three-state structure         | 14  |

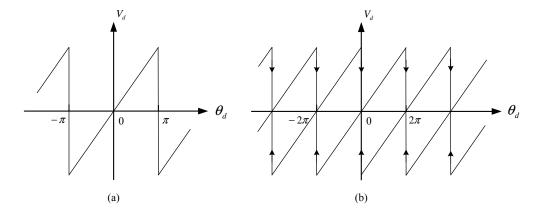

| 2.15 | PFD characteristic of (a) two-state PFD (b) three-state PFD   | 14  |

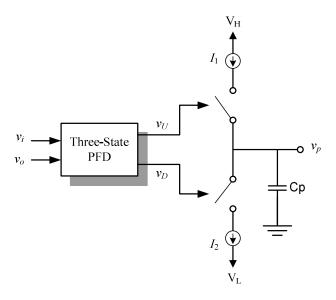

| 2.16 | Charge pump structure                                         | 15  |

| 2.17 | Function block diagram of ADPLL                               | 16  |

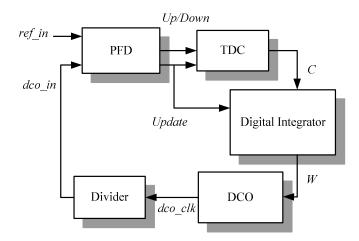

| 2.18 | An ADPLL model                                                | 17  |

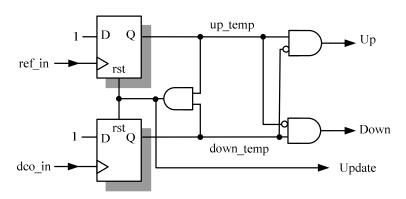

| 2.19 | The improved structure of three-state PFD                     | 17  |

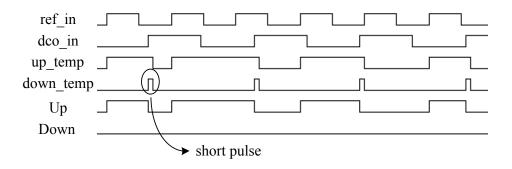

| 2.20 | Timing diagram of new three-state PFD                         | 18  |

| 2 21 | TDC structure                                                 | 1 Q |

| 2.22 | Timing diagram of TDC                                                            | 18  |

|------|----------------------------------------------------------------------------------|-----|

| 2.23 | Digital integrator structure                                                     | 19  |

| 2.24 | DCO constituted by parallel tri-state inverter                                   | 20  |

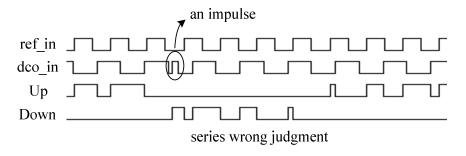

| 2.25 | A series wrong judgment caused by an impulse                                     | 21  |

| 3.1  | Two cases with large frequency difference                                        | 24  |

| 3.2  | The trigger positions                                                            | 24  |

| 3.3  | The divided bands                                                                | 25  |

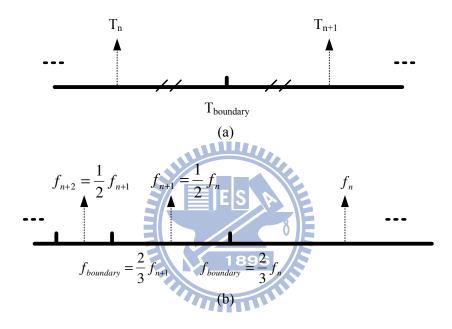

| 3.4  | (a) Boundary in unit of period (b) boundary in unit of frequency                 | 25  |

| 3.5  | Relation between triggers and phase differences                                  | 26  |

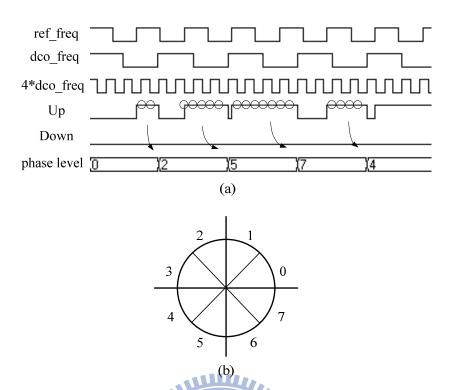

| 3.6  | (a) Use quadruple DCO frequency to count the phase difference (b) phase differen | ice |

|      | level                                                                            | 29  |

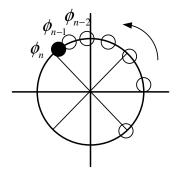

| 3.7  | Phase difference converges to the same level                                     | 30  |

| 3.8  | The superfluous behavior of DCO frequency                                        | 31  |

|      | Phase difference converges to the same level <i>N</i> tines                      |     |

| 3.10 | Constant phase difference                                                        | 33  |

|      | The process of fixing phase                                                      |     |

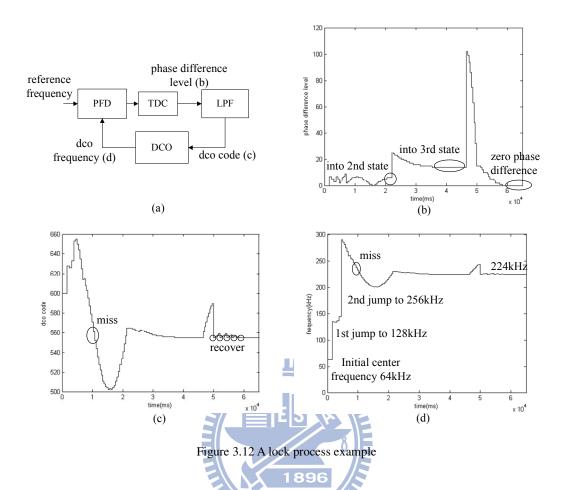

| 3.12 | A lock process example                                                           | 36  |

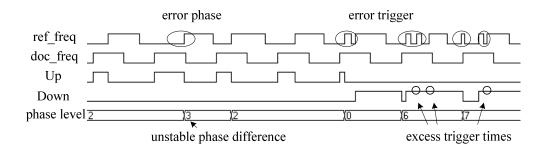

| 3.13 | Error phase and error trigger                                                    | 37  |

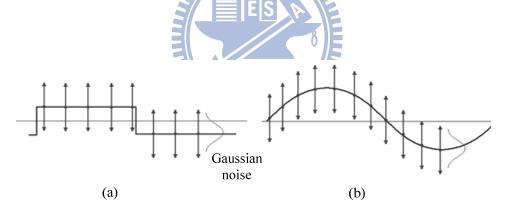

| 3.14 | Noise effect for different signals                                               | 38  |

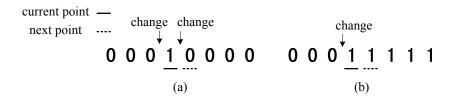

| 3.15 | (a) Adjacent changes appeared (b) the separate change                            | 38  |

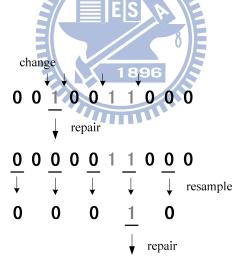

| 3.16 | Cascade approach to repair consecutive points                                    | 39  |

| 3.17 | Observing more points to repair consecutive points                               | 39  |

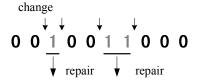

| 3.18 | Comparison between two approaches of repairing two consecutive points            | 40  |

| 3.19 | (a) Wrong repairment with correct points (b) phase resolution problem            | 40  |

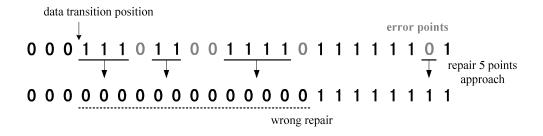

| 3.20 | Wrong repairment with multiple points approach                                   | 41  |

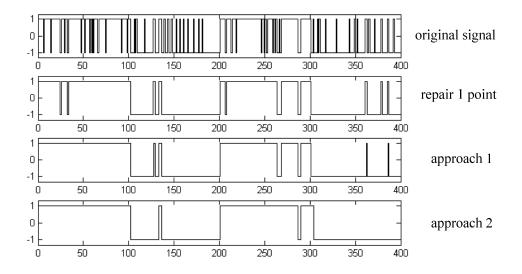

| 3 21 | Comparison between renairing multiple points                                     | 41  |

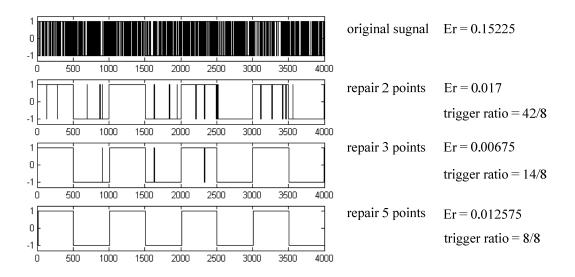

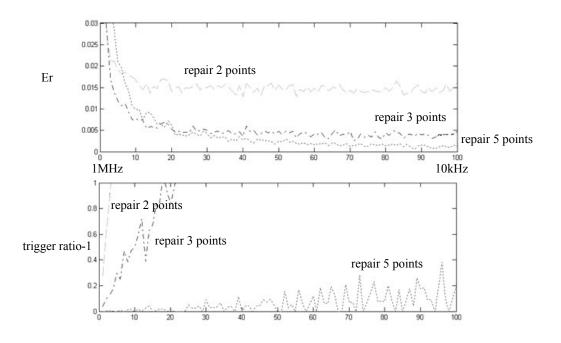

| 3.22 | The error probability and ratio for repairing different points42                        |

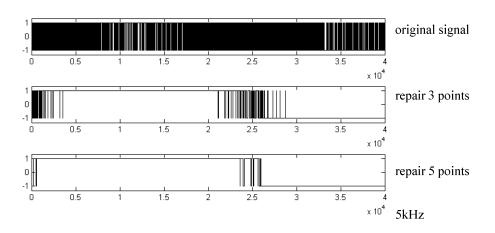

|------|-----------------------------------------------------------------------------------------|

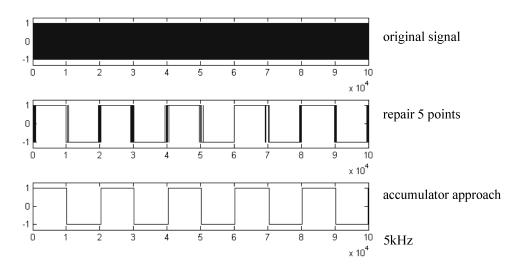

| 3.23 | Weak repair capability in 5kHz reference frequency                                      |

| 3.24 | The performance comparison between repairing 5 points and accumulator                   |

|      | approach44                                                                              |

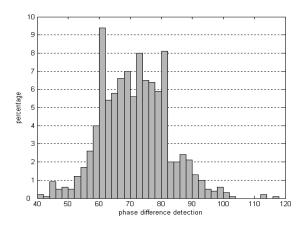

| 3.25 | Phase difference detection with SNR=0dB in the acquisition state                        |

| 3.26 | Phase difference detection with SNR=0dB in the tracking state                           |

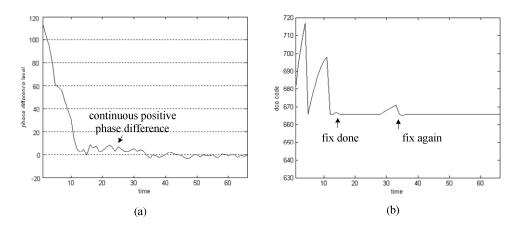

| 3.27 | The phase difference leads to the oscillating DCO code                                  |

| 3.28 | Phase difference detection with averaging (a) two points (b) four points (c) eight      |

|      | points                                                                                  |

| 3.29 | Phase difference detection with SNR=0dB in the phase-fixing state                       |

| 3.30 | The accumulator technique against noise effect in phase-fixing state                    |

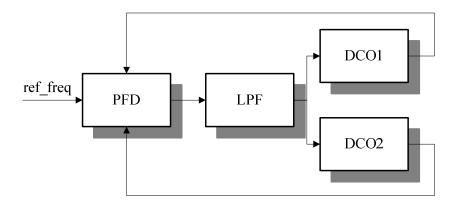

| 3.31 | Block diagram of dual-loop system                                                       |

| 3.32 | Frequency variation phenomenon on DCO code of (a) original system (b) the primary       |

|      | loop of dual system (c) the secondary loop of dual system                               |

| 3.33 | Two inefficient processes on selecting appropriate center frequency52                   |

| 3.34 | The efficient hopping process of dual center frequencies                                |

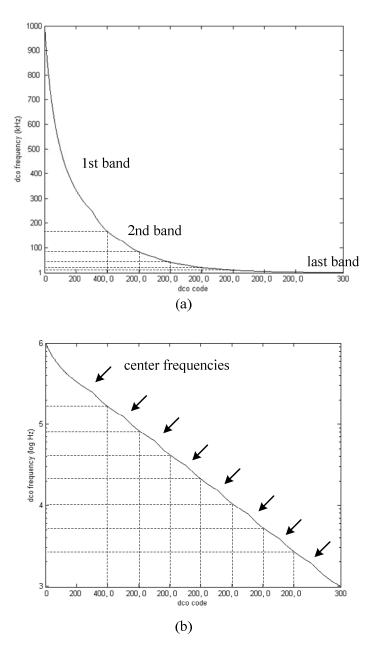

| 4.1  | The architecture of the dual-loop PLL system55                                          |

| 4.2  | The noise treatment of PFD56                                                            |

| 4.3  | Phase frequency detection of PFD                                                        |

| 4.4  | Structure of Time to Digital Converter                                                  |

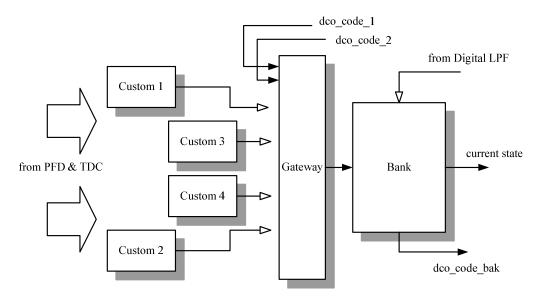

| 4.5  | Overview of Digital Loop Filter structure59                                             |

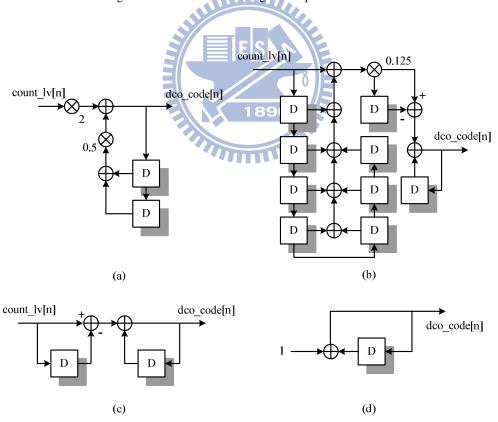

| 4.6  | Structure of several integrators (a) Integrator 1 and Integrator 2 (b) Integrator 3 (c) |

|      | Integrator 4 (d) Integrator 5                                                           |

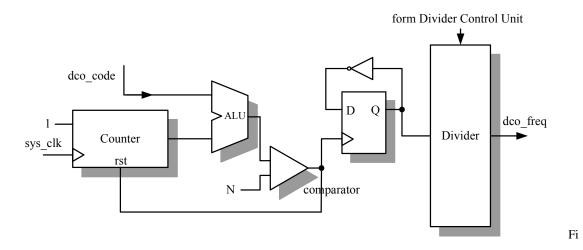

| 4.7  | Structure of Digital-Controlled Oscillator60                                            |

| 4.8  | DCO characteristic on (a) linear scale (b) logarithmic scale61                          |

| 49   | Overview of State Control Unit                                                          |

| 4.10 | Overview of Divider Control Unit63                                                       |

|------|------------------------------------------------------------------------------------------|

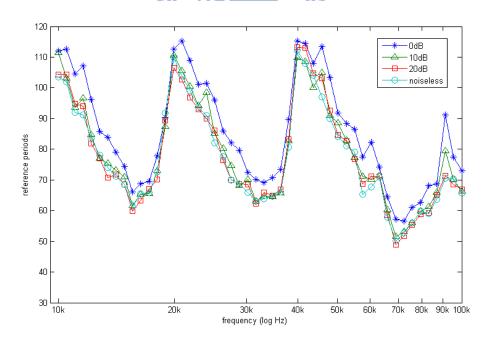

| 5.1  | Locked rate of single-loop system in (a) 100kHz-1MHz (b) 10kHz-100kHz (c)                |

|      | 1kHz-10kHz65                                                                             |

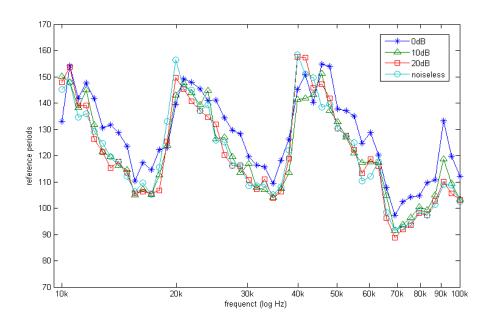

| 5.2  | Locked rate of dual-loop system in (a) 100kHz-1MHz (b) 10kHz-100kHz (c)                  |

|      | 1kHz-10kHz66                                                                             |

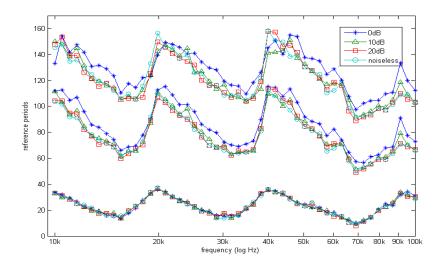

| 5.3  | The reference periods required in the acquisition stat for 10kHz-100kHz67                |

| 5.4  | The reference periods required in the tracking stat for 10kHz-100kHz68                   |

| 5.5  | The reference periods required in the phase-fixing stat for 10kHz-100kHz69               |

| 5.6  | The total reference periods required for 10kHz-100kHz69                                  |

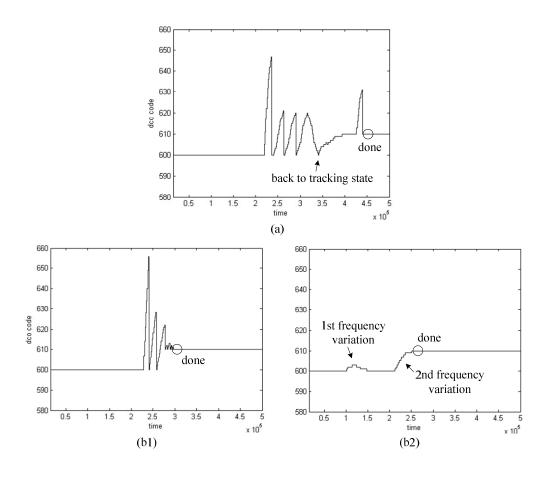

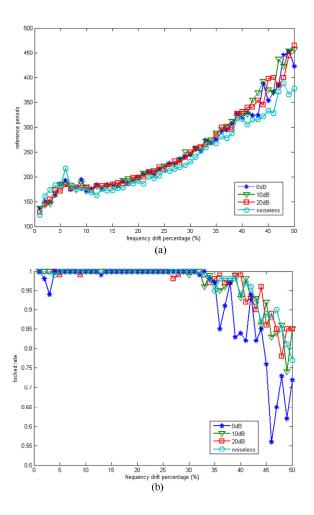

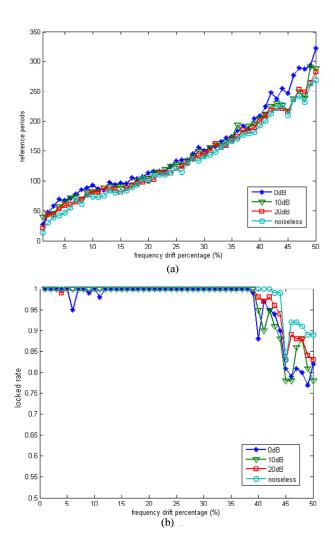

| 5.7  | (a)The required periods and (b) locked rate for reference frequency drift in single-loop |

|      | system                                                                                   |

| 5.8  | (a)The required periods and (b) locked rate for reference frequency drift in dual-loop   |

|      | system                                                                                   |

|      |                                                                                          |

## Chapter 1

### Introduction

#### 1.1 PLL Overview

The phase-locked loop (PLL) is a very critical component in modern electronic circuits [1]. It is able to generate a stable output signal whose phase and frequency are the same as those of the input. The PLL is also a feedback system, whose output is directly connected to the input. Therefore the system will adjust its output signal constantly until the phase/frequency difference between input and output is near to zero.

#### 1.1.1 History and Application

The history of PLL can be traced back to 80 years ago. Originally it had been used for the synchronous detection of radio in the 1930s. During the 1950s, it was used for television broadcasting and satellite tracking. Because of the high cost, the application of PLL was rather limited at that time. In recent years, thanks to the progress of the manufacturing technology of VLSI and the system on a chip (SoC) design, the scope of application is increased significantly. Until now, the role of PLL in system design is more and more important, which has become a versatile multi-function integrated circuit after the operational amplifier [2].

The phase-locked loop is widely used in the televisions, telecommunications, computers, and other electronic applications [3], [4]. It is able to generate or synthesize stable frequencies to select broadcasting stations or channels, synchronize the carrier frequency from noisy channel to demodulate the communication signals coherently, track the unknown frequencies

in wireless system, or recover clock pulses in digital logics. Therefore, the wide application range of PLL leads to continuous research on PLL circuits.

#### 1.1.2 All-Digital Phase-Locked Loop

Although the PLL is applied ubiquitously, there are still some problems with integration of traditional PLL at the current trend. In the traditional designs, most of them use analog components to build the PLL. That is, all the circuits are implemented with the resistances, capacitances, or inductances. But the area of these passive components in IC manufacturing is relatively large and the exact values of them are not easy to be grasped. Moreover, in today's single-chip system, merging analog circuits and digital logic on the same chip is inevitable, but it may cause many electrical problems such as noise interference, signal mask, power supply stability, etc [5], [6]. These will increase the difficulty in circuit verification and enlarge the risks of research and development.

Instead of analog approach, we could design the PLL by all-digital circuits to replace analog designs for avoiding above troubles. This PLL is called the "all-digital phase-locked loop (ADPLL)". By this way, many of the problems mentioned above can be removed between the integration of analog and digital. Furthermore, in contrast to the analog PLL, the adaptability of ADPLL is rather high. Due to the programmable capability, it is easy to change the parameters for satisfying different system requirements, and then reducing the cost and time of development [7]-[9]. This is also the main reason why we choose the all-digital structure as our research topic.

#### 1.2 Research Motivation

#### 1.2.1 Motivations and Purposes of this Research

For most PLL, their capture ranges are narrow usually. With a narrow capture range, the

PLL can only work within a narrow frequency band; therefore we intend to design a PLL with ultra-wide capture range. This PLL is designed to work for the input frequency which spans from 1kHz to 1MHz, and we don't have any prior information about the signal frequency. In this case, the ratio of the highest input frequency to the lowest input frequency is up to 1000. Moreover, we hope to have a good lock-in range and lock time to increase the application range. As displayed in Table 1.1, there are several researches about the PLL whose capture range ratios are over 3 at least. The lock time of analog PLL is larger in general such as the PLL in [5]. Although the PLL in [10], [11] have pretty good lock time, their phase resolutions, which isn't shown in this table, are very poor. In other words, they have worse jitter performance even if they are in the locked-state. Therefore, in contrast to [7], [8], [12], we hope the lock time could be less than 100 cycles in our design. We don't want to pay too much price for wide capture range.

Furthermore, there are other researches about ultra-wide capture range of PLL so far, but all of them have to work in the noiseless environment [7], [11], [13]-[15]. This is obviously not suitable for practical applications; it is necessary that the PLL is required to have good noise immunity.

Table 1.1 The performance parameters about several PLL systems

| Performance parameter        | Ref [5]   | Ref [7]     | Ref [8]     | Ref [10]  | Ref [11]    | Ref [12]    |

|------------------------------|-----------|-------------|-------------|-----------|-------------|-------------|

| Circuit type                 | Analog    | All-Digital | All-Digital | Digital   | All-Digital | All-Digital |

| Capture range (Hz)           | 8.5M-660M | 2M-500M     | 87M-250M    | 0.3G-0.8G | 50M-550M    | 500M-1.5G   |

| Lock time (reference cycles) | 720       | 63          | 72          | 16        | 50          | 96          |

#### 1.2.2 Research Approaches

Because of the ultra-wide capture range, it is difficult to use only one control algorithm to handle all the status such as capturing the unknown signal or tracking the signal which is under control. Thus we classify the process of our system into multiple states [10], [11], [16]. Here we design three states for our system: the acquisition state, tracking state and phase-fixing state. Each state uses different control rule for different purposes. For example, we adopt comparatively wide loop bandwidth in acquisition state for capturing the input frequency quickly, but a narrow bandwidth phase-fixing state for fine-tuning.

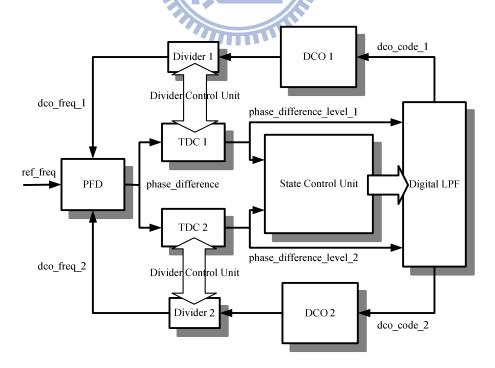

Additionally, we intend to combine two loops together to get better performance. The PLL which has dual-loop is helpful in various aspects. For example, it uses the dual cascaded PLL to increase the capture range in [17], [18], and in [19] it could also enhance the phase resolution due to two loops. With dual-loop, we can get shorter lock time and wider lock range in our system. Finally, we will implement the PLL system by the digital Hardware Description Language (HDL) to verify the feasibility of our design.

# **1.3 Thesis Organization**

This thesis is organized as following: In Chapter one, we introduce the background of PLL briefly. Next, we describe the structure of traditional PLL to understand its behavior in Chapter two. Chapter three will present all the details of our design concept, including the system architecture and the control algorithm. In Chapter four, we show the hardware circuit architecture of all the designed modules and summarize the operation of this system. Then, in Chapter five we show the simulation results, and make conclusions of this research in Chapter six finally.

# **Chapter 2**

# **Phase-Locked Loop Basics**

In this chapter, we will review some critical concepts about PLL and introduce three types of them: analog PLL (APLL), digital PLL (DPLL) and all-digital PLL (ADPLL). At first, we use a linear model to express the PLL system. Although most PLL are not linear, we can assume the input of PLL is a pure sinusoid and the system already in the lock-state. Then it can be represented as a linear system [1], [2].

# 2.1 Linear Model of PLL

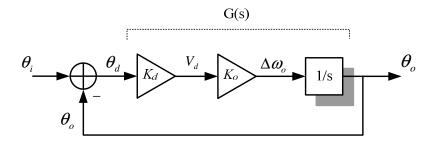

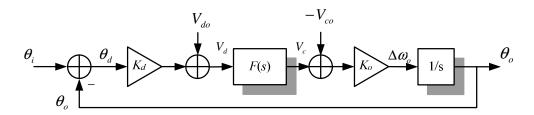

The function block of PLL is shown in Figure 2.1. The phase detector (PD) is responsible for detecting the differences of frequency and phase between two input signals. Then the output voltage  $v_d$  is entered into the voltage-controlled oscillator (VCO). The VCO will send a new signal back to the phase detector accordingly. Usually, the objective of PLL is to generate a pure sinusoidal and merely two components PD and VCO are necessary to achieve it easily.

Figure 2.1 The general function block of PLL

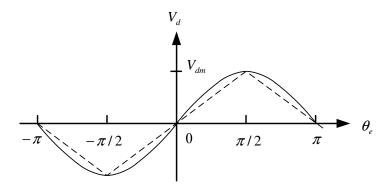

Figure 2.2 The phase detector characteristic

#### 2.1.1 Phase Detector Characteristics

Because frequency is the time derivative of phase, we can use the phase difference  $\theta_d$  to represent both phase and frequency differences between two inputs as below:

$$\theta_d = \theta_i - \theta_o \tag{2.1}$$

The voltage  $v_d$  is produced in response to  $\theta_d$ . The relationship between  $v_d$  and  $\theta_d$  is shown in Figure 2.2, which is normally a linear curve. In this figure,  $K_d$  is the PD gain and it is a constant in the range  $-\pi/2 \le \theta_d \le \pi/2$ , which is also the effective detection range of PD. The  $V_{do}$  corresponds to  $\theta_d = 0$ , which means there is no difference between input phase and VCO phase. Next, we can model the phase detector as

$$v_d = K_d \theta_d + V_{do} \tag{2.2}$$

#### 2.1.2 VCO Characteristics

The voltage-controlled oscillator, as its name implies, can generate an output signal whose frequency is controlled by the input voltage. The I/O relationship of VCO is shown in Figure 2.3, where  $v_c$  and  $\omega_o$  represent the input voltage and output frequency, respectively, and the slope  $K_o$  is assumed to be constant for simplifying the analysis. When the PLL is in lock, the frequency deviation  $\Delta\omega_o$  is zero, where

$$\Delta\omega_o = \omega_o - \omega_i \tag{2.3}$$

Figure 2.3 The Voltage-Controlled Oscillator characteristic

As shown in the Figure 2.3, in which  $\omega_i = 10$  MHz, and  $v_c = V_{co} = 2$  is corresponding to  $\omega_o = \omega_i$ . Beware that  $V_{co}$  is not a property of the VCO; it depends on the input frequency  $\omega_i$ . The frequency deviation of VCO can be modeled as

$$\Delta\omega_o = K_o(v_c - V_{co}) \tag{2.4}$$

#### 2.1.3 Frequency Response of Linear PLL Model

As mentioned above, we assume the input and output signals are pure sinusoids, that is:

$$v_i = \sin(\omega_i t + \theta_i) \tag{2.5}$$

$$v_o = \sin(\omega_o t) \tag{2.6}$$

where the  $\theta_i$  is the exact phase difference between  $v_i$  and  $v_o$ . But for phase detector, it supposes that the frequency of  $v_i$  and  $v_o$  is the same. In other words, the phase detector believes that all differences between  $v_i$  and  $v_o$  are made by both phases. Hence we can rewrite  $v_o$  as

$$v_o = \sin(\omega_i t + \theta_o) \tag{2.7}$$

Then, the output frequency of VCO can be expressed as

$$\omega_o = d(\omega_i t + \theta_o)/dt = \omega_i + d\theta_o/dt$$

(2.8)

We define  $\Delta \omega_o = \omega_o - \omega_i$ , thus

$$\Delta\omega_o = d\theta_o/dt \tag{2.9}$$

or

$$\theta_o = \int \Delta \omega_o \, dt \tag{2.10}$$

Now we combine above equations with PD and VCO, and the resulting linear model of PLL is shown in Figure 2.4.

Next, we discuss the frequency response of this model. From the frequency response we can observe if  $\omega_o$  can reasonably follow  $\omega_i$  which may vary temperately. We form an AC model by ignoring the DC parameters from Figure 2.4, and the result is shown in Figure 2.5, where 1/s represents the Laplace transform of integration. Let the open loop gain of the model in Figure 2.5 is G(s), then

Figure 2.4 The linear model with PD and VCO

Figure 2.5 The AC model with PD and VCO

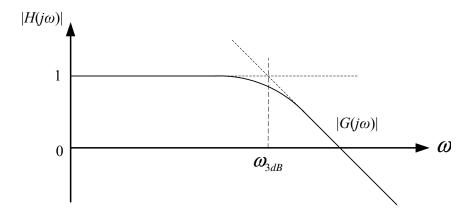

Figure 2.6 The frequency response and bandwidth of linear PLL model

$$H(s) = \frac{\theta_o(s)}{\theta_i(s)} = \frac{G(s)}{1 + G(s)} = \frac{1}{1 + s/K_d K_o}$$

(2.12)

For describing the frequency response, we replace s by  $j\omega$ , and the response  $|H(j\omega)|$  is shown in Figure 2.6. When  $\omega$  is low,  $|H(j\omega)|$  is about equal to unity. On the other hand, when  $\omega$  is high,  $|H(j\omega)|$  approaches  $|G(j\omega)|$ . Notice that the meaning of  $\omega$  here is not the same as  $\omega_i$  or  $\omega_o$ , which represents the varying rate of frequency. Concerning frequency response, we can see that the bandwidth  $\omega_{3dB}$  occurs when  $|G(j\omega)| = 1$ . That is

$$\omega_{3dB} = K_d K_o \tag{2.13}$$

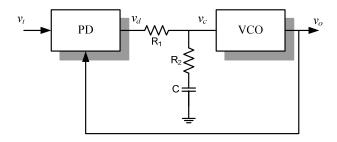

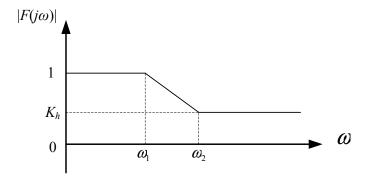

#### 2.1.4 Loop Filter Characteristic

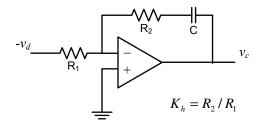

Now suppose we want to reduce the bandwidth but keep PD and VCO unchanged, we can put a voltage attenuator between PD and VCO. The objective of voltage attenuator is to decrease the gain so as to reduce the bandwidth, but we intend to decrease the AC gain only and don't limit the DC voltage. The solution is to use the RRC low pass filter which is also called the loop filter (LPF) as shown in Figure 2.7. This filter acts as an attenuator at high frequencies but with unity gain at DC. The transfer function of the LPF is

$$F(s) = K_h \frac{s + \omega_2}{s + \omega_1} \tag{2.14}$$

Figure 2.7 A RRC low pass filter

where

$$K_h = \frac{R_2}{R_1 + R_2}$$

$$\omega_1 = \frac{1}{(R_1 + R_2)C}$$

$$\omega_2 = \frac{1}{R_2C}$$

(2.15)

The frequency response of  $|F(j\omega)|$  is plotted in Figure 2.8. The gain |F(0)| = 1 at DC and  $|F(j\omega)| = K_h$  at high frequencies. After including F(s), the open loop gain of PLL is modified as

$$G(s) = K_d F(s) K_o / s (2.16)$$

The new frequency response of  $|H(j\omega)|$  is shown in Figure 2.9, and the 3dB bandwidth becomes

$$\omega_{3dB} = K_d K_h K_o = K \tag{2.17}$$

Figure 2.8 The frequency response of RRC low pass filter

Figure 2.9 The frequency response and bandwidth of complete linear PLL model

Finally, a complete linear model with the LPF is shown in Figure 2.10, and the transfer function is

$$H(s) = \frac{\theta_{o}(s)}{\theta_{i}(s)} = \frac{Ks + K\omega_{2}}{s^{2} + (K + \omega_{1}) + K\omega_{2}}$$

(2.18)

Because the denominator of this transfer function is a second-order polynomial in *s*, it is called a second-order PLL. The different loop filter affects the order of PLL, which may affect the different characteristic or stability of the system loop. Therefore, for simplifying analysis, the PLL design could follow the linear model usually.

Figure 2.10 The complete linear PLL model

### 2.2 Traditional PLL Circuit Design

This section we introduce various types of PLL which are classified according to the

circuit structure. As mentioned above, the APLL is constituted by analog components only, the DPLL combines analog circuits with digital, and the ADPLL has the all-digital implementation.

#### 2.2.1 Analog PLL (APLL)

The analog PLL consists of the PD, the LPF, and the VCO as mentioned in Section 2.1. A four-quadrant multiplier is used as the PD for detecting frequency deviation at the earliest. Let two inputs of the multiplier be

$$v_i = \cos(\omega_i t) \tag{2.19}$$

$$v_o = \sin(\omega_i t + \theta_e) \tag{2.20}$$

Suppose the gain of multiplier is  $K_m$ , and the output of multiplier is given as

$$v_d = v_i v_o = \frac{K_m}{2} (\sin(\theta_e) + \sin(2w_i t + \theta_e))$$

(2.21)

Because of the LPF, the high frequency part is removed. Thus

$$v_d = 0.5K_m \sin(\theta_e) \tag{2.22}$$

The relationship between  $\theta_e$  and  $v_d$  is shown in Figure 2.11. Comparing with Figure 2.1, the linear range of PD is very narrow unless the value of  $\theta_e$  is small, and the effective detection range is also  $[-\pi/2, \pi/2]$ .

Figure 2.11 The multiplier PD characteristic

Figure 2.12 The PI filter circuit

For the LPF, instead of the RRC low pass filter, the proportional integrator filter (PI filter) is also a good choice as shown in Figure 2.12, which has the better loop bandwidth than the RRC. However, comparing with the DPLL and ADPLL, the lock time of APLL is rather slow relatively.

#### 2.2.2 Digital PLL (DPLL)

As shown in Figure 2.13, the main difference between DPLL and APLL is that the DPLL uses the digital phase frequency detector (PFD) and the charge pump (CP) to replace the analog PD.

The DPLL usually uses the Exclusive-OR gate (XOR) or Flip-Flop as the PFD. Since the behavior of XOR mimics the multiplier, we can't get too many advantages. Two PFDs constituted with D-Flip-Flops are depicted in Figure 2.14, where the inputs  $v_i$  and  $v_o$  are square waves.

Figure 2.13 The block structure diagram of DPLL

Figure 2.14 (a) The two-state PFD structure (b) the three-state PFD structure

The PFD of Figure 2.14a has two states, where  $v_i$  and  $v_o$  act as clock input of the two D-Flip-Flops, respectively. In the beginning, assume Q1 and Q2 both are low, and  $v_d$  is high. When positive edge of  $v_o$  is coming, Q2 becomes high and then makes  $v_d$  low. When positive edge of  $v_i$  comes, Q1 becomes high and then make the  $v_d$  high. In contrast to Figure 2.14a, the circuit of Figure 2.14b replaces  $v_d$  with two outputs  $v_U$  and  $v_D$  to has more states than the former. The I/O relationships of them are shown in Figure 2.15 below. We find that the effective detection range of two-state PFD is  $\pm \pi$ , and the three-state PFD is up to  $\pm 2\pi$ . It is more useful than the PD of APLL.

Figure 2.15 The PFD characteristic of (a) two-state PFD (b) three-state PFD

Figure 2.16 The charge pump structure

Additionally, the charge pump can transfer the logic signal to be voltage. The structure of charge pump with three-state PFD is given in Figure 2.16. As shown, the capacitor  $C_p$  charges when  $v_U$  is high and  $v_D$  is low, discharges when  $v_U$  is low and  $v_D$  is high, and keeps the status unchanged when both  $v_U$  and  $v_D$  are low.

A disadvantage with DPLL is that the output voltage  $v_p$  of CP may be unstable when the capacitor  $C_p$  charges and discharges inconsistently or the charge currents  $I_1$  and  $I_2$  don't match with each other. The self-generated noise is capable of destroying the VCO phase, so that additional components are necessary for eliminating the noise disturbance.

#### 2.2.3 All-Digital PLL (ADPLL)

From the above discussion, we find that maintaining the stability of APLL or DPLL is usually complicated, but most analog components have low tolerance for noise. Therefore we may apply the algorithm of behavior description to replace the operation of circuit components. That is the ADPLL, whose function block diagram is shown as Figure 2.17.

The PFD, which is similar to the DPLL's, is connected to the control unit. The control unit is a general block; any helpful control blocks about the system can be included inside this

Figure 2.17 The function block diagram of ADPLL

unit, and it isn't confined to only the loop filter. Usually we use the time-to-digital converter (TDC) and the digital recursive filter (or named digital LPF) as the core of control unit, because they can exactly replace the CP and LPF of DPLL, respectively. The TDC translates the PFD output into digital codes, and then the digital recursive filter decodes these codes and generates another digital code to adjust the DCO.

The DCO is the digital-controlled oscillator. Obviously, the difference between DCO and VCO is that the output of DCO is controlled by digital codes, but not voltage. The main advantage with DCO is that voltage is more sensitive than digital code, so that DCO can generate a comparably stable output frequency. But there is the resolution problem for DCO since the number of digital codes is limited. In other words, the VCO is able to generate more accurate output frequency than DCO.

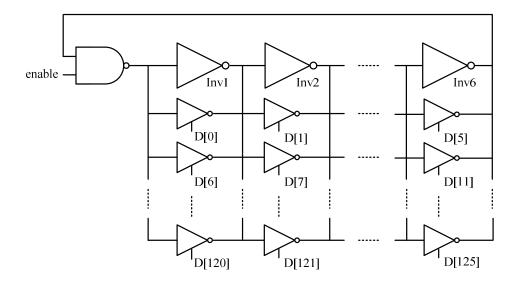

#### 2.3 An ADPLL Circuit Model

Here we will analyze the ADPLL in details [14], [20]. Figure 2.18 shows the block diagram of ADPLL [14]. The PFD produces series pulses Up and Down with lengths represent the phase differences, and the Update is used to clock the registers and reset the TDC between measurements. The TDC translates the lengths of Up and Down into digital

Figure 2.18 An ADPLL model

code C as mentioned above. Then the digital integrator determines the digital word W according to C. Finally, the DCO generates the output  $dco\_clk$  which is compared with the reference  $ref\_in$  in the PFD after frequency division by the divider.

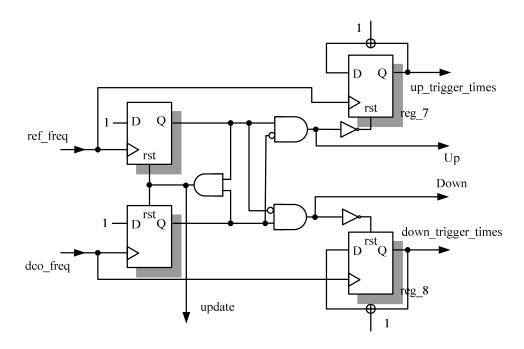

#### 2.3.1 Phase Frequency Detector (PFD)

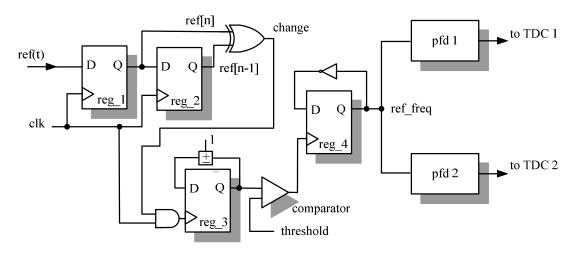

The PFD also uses the three-state PFD but we make some improvements as illustrated in Figure 2.19. In the original PFD, if the *ref\_in* leads the *dco\_in*, the *Down* output still has short pulse. This is not desirable so that we add two inverters and two AND gates. In this way, the *Up* output is high when *ref\_in* leads the *dco\_in* and the *Down* output is high when *ref\_in* lags the *dco\_in*, as shown in Figure 2.20.

Figure 2.19 The improved structure of three-state PFD

Figure 2.20 The timing diagram of new three-state PFD

The short *Update* output is necessary. Because the system is controlled in digital manner, the *Update* is a good trigger to be the time unit of system.

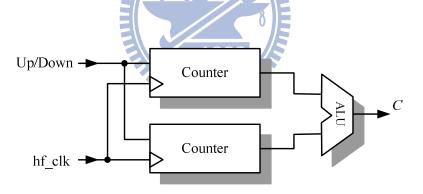

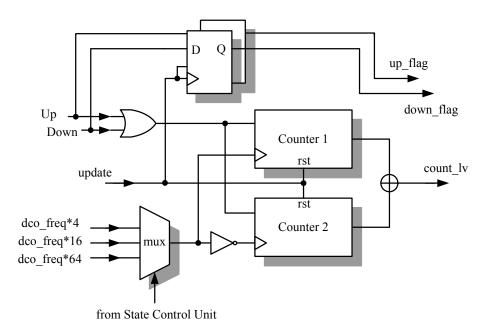

#### 2.3.2 Time to Digital Converter (TDC)

The TDC could be complicated, but we can use the counters to simplify it, as shown in Figure 2.21. Intuitively, the longer Up/Down stands for the larger phase difference. We use

Figure 2.21 The TDC structure

Figure 2.22 The timing diagram of TDC

high frequency signal *hf\_clk* as the clock of counter; we can even combine both positive and negative edges to double the precision. The timing diagram is shown in Figure 2.22.

When the *Up* or *Down* output is high, the counters will start to work. Until the positive edge of *Update* is detected, the counters send results to the ALU and go to zeros afterwards. Then, the code *C* will represent the phase difference in this round.

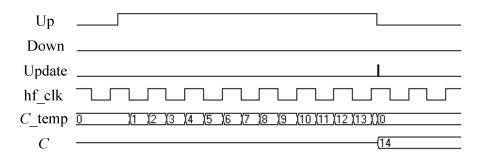

#### 2.3.3 Digital Integrator

The digital integrator, the recursive filter or the digital loop filter, which is essentially the same. In order to approximate the second-order loop filter as mentioned above, we let the transfer function of integrator be

$$F(z) = \frac{1}{1 - 0.5z^{-1} - 0.5z^{-2}}$$

(2.24)

For simplicity, we only use the number 1 or 0.5 as constant, which can be expressed correctly by limited bits. Converting to digital domain, we get

$$y[n] = x[n] + 0.5y[n-1] + 0.5y[n-2]$$

(2.25)

This is just the behavior of the integrator. The input x[n] and output y[n] are C and W, respectively; W[n] is the function of C[n], W[n-1], and W[n-2]. The structure is shown as Figure 2.23. The *Update* is the delay clock, and *Up/Down* is helpful to decide the sign of C.

Figure 2.23 The digital integrator structure

Figure 2.24 DCO constituted by parallel tri-state inverter

When Up is high, W increases with the positive C. Oppositely, W decreases with the negative C when the signal Down is high. Additionally, W has the initial value; this value can cause the DCO to generate the initial frequency.

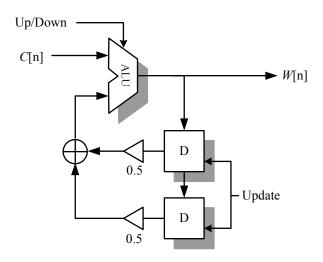

#### 2.3.4 Digital-Controlled Oscillator (DCO)

A DCO is shown in Figure 2.24. It is an evolution from the ring oscillator, which consists of 126 tri-state inverters controlled by a 126-bit digital code D, and D is decoded from the 7-bit word W. When W = 0, all the inverters are off and the charge efficiency of the MOS should be lower. Otherwise, when W = 126 or 127, all the inverters are on and the DCO can generate higher frequency.

### 2.4 Design Challenges

From above descriptions, we have preliminary knowledge about the operation of ADPLL. However, for working with the wide capture range under noisy environment, the above system is not sufficient. There are some challenges to be overcome:

#### Challenge 1:

Although the effective detection range of three-state PFD is up to  $\pm 2\pi$ , it is still difficult to handle the capture range which has 1000 times between the highest frequency and the lowest frequency. Moreover, in order to reduce the lock time, it may be unrealistic to have a long observation time. How can the PFD detect correct phase difference from the ultra-wide frequency range?

#### **Challenge 2:**

Under noisy environment, the three-state PFD is easily affected by noise. As shown in Figure 2.25, a small pulse can cause series wrong judgment of the phase, let alone under serious noise environment. How can the PLL determine if the trigger is caused by noise or by signal?

#### Challenge 3:

Because the input code length of DCO is limited, the wider range causes the lower resolution. In our DCO, the lowest frequency and the highest frequency are respectively 1kHz and 1MkHz. Even if the codeword *W* is 10-bit, it only generates 1024 different frequencies. How can the DCO get fine resolution under limited bits?

#### Challenge 4:

As mentioned earlier, the LPF bandwidth is the key of system stability. With wide capture range, it is possible that the difference between reference frequency and center

Figure 2.25 A series wrong judgment caused by an impulse

frequency is quite large, and we can't use a very narrow loop bandwidth to avoid the high frequency interference. How can the LPF get the balance between the efficiency in large frequency difference and the stability in small frequency difference?

## **Chapter 3**

# **System Architecture**

As mentioned above, we classify the process of our system into three states: the acquisition state, the tracking state and the phase-fixing state. In this chapter, we will describe the algorithm and the architecture about the proposed PLL system and present how to combine the three states against the difficulties encountered under serious noise environment.

#### 3.1 Acquisition State

The acquisition state is the initial state in our PLL design, whose purpose is to find the possible region of reference frequency from 1kHz to 1MHz quickly. Because there is no prior information about this frequency, we have to get useful information from the PFD and handle the information adequately.

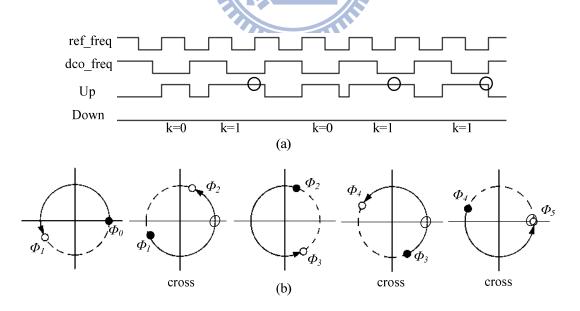

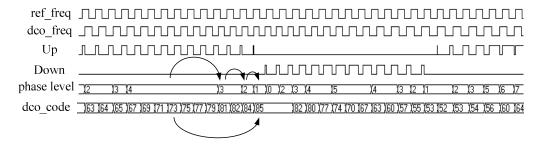

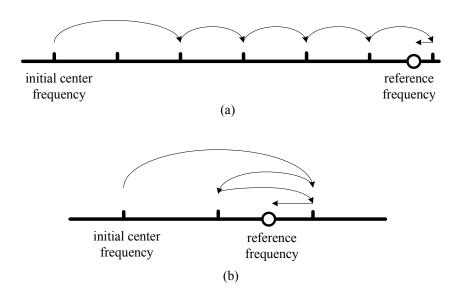

The traditional three-state PFD only provides the *Up* and *Down* outputs as shown in Section 2.3.1. It is not enough for the requirement of wide capture range. An example is given as Figure 3.1, where we only get the information that the difference between two frequencies is very large from the exaggerated length of *Up/Down*, but can't distinguish the difference between these two cases. A PFD which can make an accurate judgment when there is a huge difference between the reference frequency and DCO frequency is necessary.

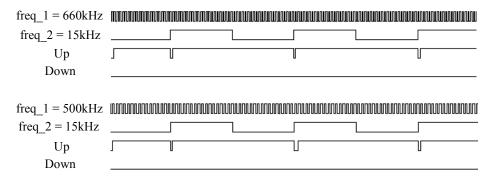

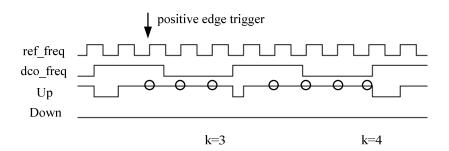

After some observation, we find it is possible to count the trigger times of positive edge continuously when the Up/Down is determined already. The concept is equivalent to use the reference frequency as the sampling frequency to sample the DCO signal. If one DCO period

Figure 3.1 Two cases with large frequency difference

is sampled k times, the trigger times should be k-l, as shown in Figure 3.2. The trigger times can also represent the cycles which the leader exceeds. Although we can't identify the precise reference frequency according to the trigger times, we know the ratio of the reference frequency with respect to DCO frequency approximately.

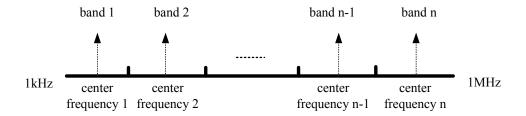

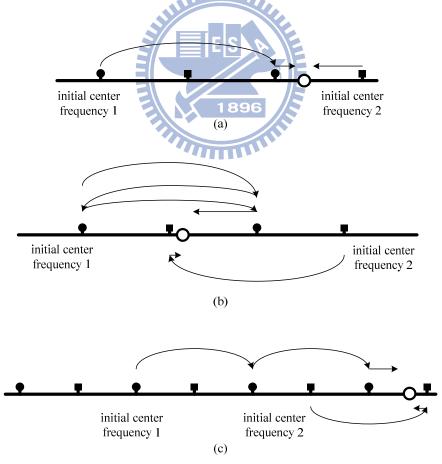

On the other hand, we divide the 1kHz-1MHz into multiple bands (Figure 3.3). Each band has its own center frequency, and the difference between adjacent center frequencies is double as frequency increases. Then, we use a Divider that can control the DCO to shift its center frequency from one band to the others. Combining above ideas, we can spend only several DCO signal periods to count the trigger times and then shift the DCO signal to the appropriate center frequency closest to the reference frequency.

Figure 3.2 The trigger positions

Figure 3.3 The divided bands

Figure 3.4: (a) The boundary in unit of period (b) The boundary in unit of frequency

The decision rule of trigger times is closely related to the approach of dividing bands. For simplify, we use the Divider to divide bands, which helps us to use a simple decision rule for selecting the right band according to the trigger times. As shown in Figure 3.4a, the most intuitive approach in dividing bands is to select the middle of two adjacent center frequencies as the boundary. But our design is based on digital circuits, therefore we replace the frequency with the period as time unit, given as

$$T_{boundary} = \frac{T_n + T_{n+1}}{2} = \frac{T_n + 2T_n}{2} = \frac{3}{2}T_n$$

(3.1)

where  $T_n$  and  $T_{n+1}$  are any two adjacent center periods, and  $T_{n+1}$  is twice of  $T_n$ . Then

$$f_{boundary} = \frac{2}{3} f_n = \frac{4}{3} f_{n+1}$$

(3.2)

As shown in Figure 3.4b, when the reference frequency is over 4/3 times or under 2/3 times than the current DCO center frequency, it jumps to other band.

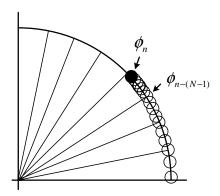

For the decision rule of trigger times, we have to know the relationship between trigger times and reference frequency. Suppose the initial phase difference between the DCO frequency and the reference frequency is zero for simplifying the problem, and let the reference frequency be 1.6 times of the DCO frequency. This example is shown in Figure 3.5, where (a) shows the phase difference detected by PFD, and (b) shows them on the unit circle. We could find that the trigger happens when the phase difference is beyond a cycle. Therefore, we can use a simple equation to calculate the number of trigger times.

When the reference frequency is m times of the DCO frequency, the phase difference  $\phi$  will be

Figure 3.5 The relation between triggers and phase differences

$$\phi_1 = \frac{f_{ref} - f_{dco}}{f_{dco}} \times 2\pi + \phi_0 = (m - 1)2\pi + \phi_0$$

(3.3)

where  $\phi_0$  is assumed to be zero. Then

$$\phi_{2} = (m-1)2\pi + \phi_{1} = 2 \times (m-1)2\pi$$

$$\phi_{3} = (m-1)2\pi + \phi_{2} = 3 \times (m-1)2\pi$$

$$\vdots$$

$$\phi_{n} = (m-1)2\pi + \phi_{n-1} = n \times (m-1)2\pi$$

(3.4)

Thus the total number of trigger times  $N_{tri\_total}$  is

$$N_{tri\_total(n)} = \left| \frac{\phi_n}{2\pi} \right| = \lfloor n(m-1) \rfloor$$

(3.5)

But in our plan, the trigger times have to recount once again per cycle, and we turn the  $N_{tri}$  as following:

$$N_{tri(n)} = N_{tri\_total(n)} - N_{tri\_total(n-1)} = \lfloor n(m-1) \rfloor - N_{tri\_total(n-1)}$$

(3.6)

Finally, we build a table with different *m* for observing the trend about trigger times, as shown in Table 3.1.

According to Table 3.1, we find that it is almost 3 rounds per cycle about the boundary trigger times because of our way of dividing bands. For example, at m=4/3 if we observe the sum of any three adjacent  $N_{tri}$  that is over 1 (0+0+1), the reference frequency is over 4/3 times of the DCO frequency at least and then double the DCO frequency. Moreover, our purpose is to judge whether the reference frequency is over the boundary or not, therefore we just have to observe two rounds. We take the maximum sum of any two adjacent k points as a threshold and show it in Table 3.2. If the sum of two trigger times is over the threshold, the DCO frequency band will be changed immediately.

Table 3.1 The trigger times for several m

| multiples | trigger times k |   |   |   |   |   |   |   |   |   |  |

|-----------|-----------------|---|---|---|---|---|---|---|---|---|--|

| m=16/3    | 4               | 4 | 5 | 4 | 4 | 5 | 4 | 4 | 5 | 4 |  |

| m=4       | 3               | 3 | 3 | 3 | 3 | 3 | 3 | 3 | 3 | 3 |  |

| m=8/3     | 1               | 2 | 2 | 1 | 2 | 2 | 1 | 2 | 2 | 1 |  |

| m=2.5     | 1               | 2 | 1 | 2 | 1 | 2 | 1 | 2 | 1 | 2 |  |

| m=2       | 1               | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |  |

| m=1.6     | 0               | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 1 |  |

| m=4/3     | 0               | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |  |

Table 3.2 The decision rule of band change

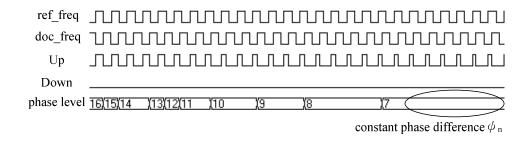

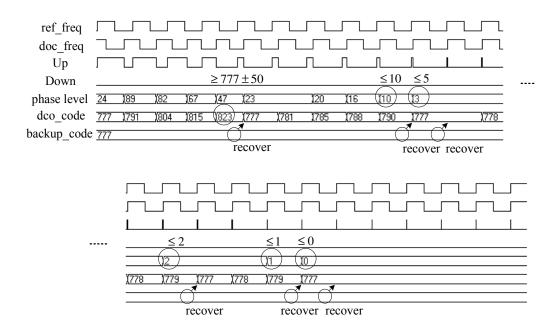

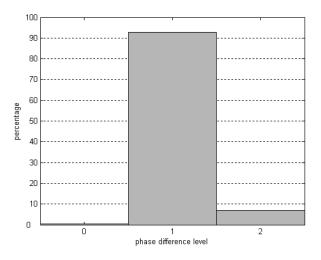

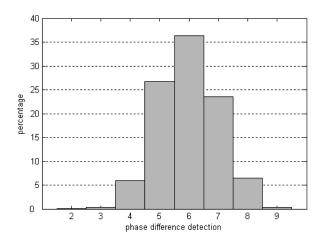

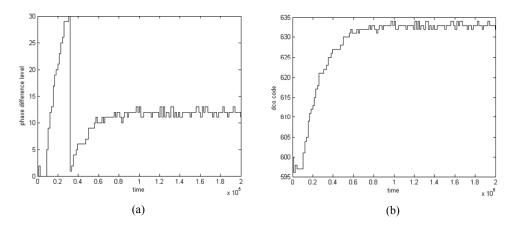

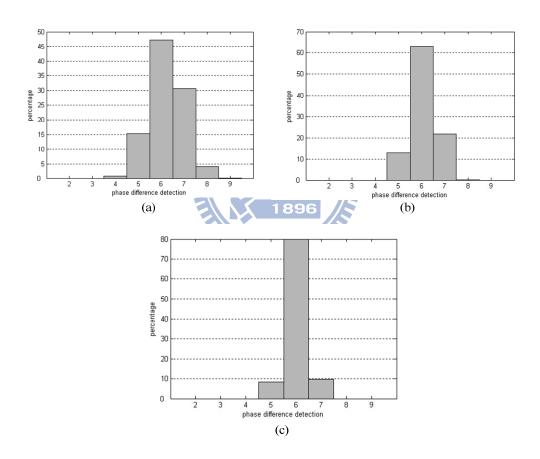

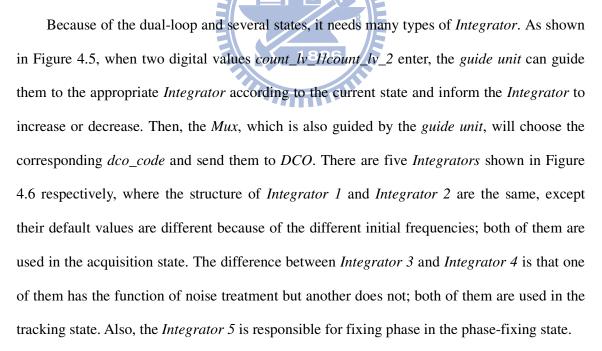

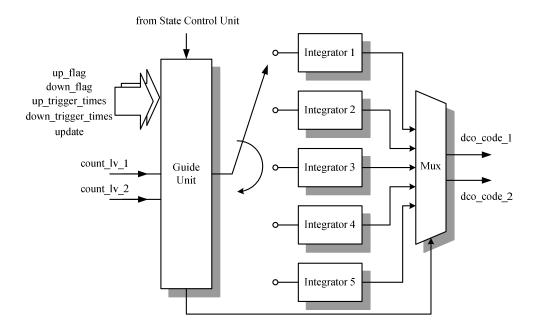

| multiples | thresholds                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | change level |