國 立 交 通 大 學

電子工程學系電子研究所

碩 士 論 文

砷化銦量子點在蕭基二極體

與場效電晶體上之效應

Effects of InAs Quantum Dots on Schottky Diodes

and Field Effect Transistors

1896

研究生：王 參 豪

指導教授：林 聖 迪 教 授

中華民國一〇二年四月

國 立 交 通 大 學

電子工程學系

電子研究所碩士班

碩 士 論 文

砷化銦量子點在蕭基二極體

與場效電晶體上之效應

Effects of InAs Quantum Dots on Schottky Diodes

and Field Effect Transistors

1896

研究生：王 參 豪

指導教授：林 聖 迪 教 授

中華民國一〇二年四月二十九日

# 砷化銦量子點在蕭基二極體 與場效電晶體上之效應

研究生：王參豪 指導教授：林聖迪 博士

國立交通大學

電子工程學系 電子研究所碩士班

## 中文摘要

本論文呈獻蕭基二極體與場效電晶體內之量子點層捕捉/釋放電荷對量測電性特徵所造成影響之探討。蕭基二極體在低溫環境下之電流-電壓曲線中，可發現具量子點與無量子點之元件展現不同的導通行為，此差異可藉由將量子點層以等效電阻之模型取代解釋之。而在頻率相依之電容-電壓曲線量測結果中，也可觀察到由量子點層所導致之明顯特徵。根據實驗分析，能將此電容之特徵歸究於量子點內第一與第二能階對電荷之充-放電行為所造成。而量測所擷取出之載子捕捉/釋放速率則會隨溫度提高而上升。在場效電晶體元件上，則著重於兩種不同結構之研究。其中當二維電子氣通道位於量子點下方之結構，可能因為通道與閘極間之距離，致使閘極無法有效空乏通道內之載子。對於二維電子氣通道位於量子點上方之結構而言，雖說能空乏二維電子氣通道內之載子，但無論是在電流-電壓或電容-電壓量測中，都無法觀察到量子點下之能態充放電行為所造成之影響。為了能在將來實現以量子點為電荷儲存處之記憶元件，尚還需要更多之研究與探討。

# **Effects of InAs Quantum Dots on Schottky Diodes and Field Effect Transistors**

**Student : Tsan-Hao Wang**

**Advisor : Dr. Sheng-Di Lin**

**Department of Electronics Engineering and Institute of Electronics

National Chiao Tung University**

## **Abstract**

This thesis present the study on how charge capturing/escaping of quantum dot (QD) layers affects measured the electrical characteristics of Schottky diodes and field effect transistors (FETs). For the Schottky diodes with QDs, the current-voltage (I-V) curves measured at low temperature exhibit different turn-on behavior from those without QDs, which can be explained by effective resistance model of QD layers. Clear features from QDs are observed with the frequency-dependent capacitance-voltage (C-V) results. According to our analysis, the C-V features can be attributed to the charging/discharging of QDs' inter first and second energy levels. The extracted carrier capture/escape rate increases with increasing temperatures. For FETs, two sample structures are studied. The 2-D channel under the QD layers cannot be depleted by gate probably due to the distant gate metal. The other structure, although the 2-D channel can be well depleted, the charging states in the underneath QDs cannot be revealed either by I-V or C-V measurements. Further studies are needed to realize the QD-based memory device in the future.

# 致謝

在研讀碩士的這三年來，充滿著各種酸甜苦辣的記憶。對研究的茫然、對實驗的挫折、對結果之困頓，更是主要充斥在我生活上的所有情感。值得慶幸的是對這樣無助的我，實驗室的教授以及不少學長姐與學弟妹們都給予了我不少的幫助，我衷心誠意的感謝你們。如果沒有你們的教導和幫助的話，我真的不敢想像會是怎麼樣可怕的生活。感謝林聖迪教授在我學業上的指導也謝謝老師對我的包容，相較於實驗室其它同仁能獨立思考研究而言，只會像機器人般說一項做一項的我真的給老師平添不少麻煩，由衷感謝老師的耐心指導縮減了我在研究上枉走冤路的時間。此外也要特別感謝林仕偉學長，謝謝學長花費了不少保貴的時間為我長晶結構樣品。謝謝巫朝陽學長、傅英哲學長、林岳民學長、張家豪學長、李宗霖學長、徐偉程學長、賴國瑋學長、以及戴文長學長教會了我不少量測以及製程機台並有時願意花時間和我討論所遭遇到的困難。感謝李依珊學姐、鄭濬學長以及張胤傑學弟在光學量測機台上的教導和幫助。

最後要感謝我的父母，謝謝你們的支持和體貼。在我最封閉最無奈的日子中陪伴著我、開導著我。你們的堅強以及辛勤的生活態度讓我能完完全全沒有後顧之憂地去專注於自身之研究和實驗項目之上，也因為這樣的環境給了我能好好的思考著未來方向的機會，對不起讓你們操心和擔心了。還有我那光說不練的老哥，一次次的說可以抽空幫我看看問題所在，也一次次地放我鴿子讓我恨的牙癢癢的，不過我還是很感謝你和我之間的爭吵和互酸，因為在你面前我能完全沒有顧慮地去做自己，在你面前我能回復自己的開朗和快樂，也謝謝你那一頓頓美味昂貴的料理。

# 目 錄

|                        | 頁次  |

|------------------------|-----|

| 中文摘要 .....             | i   |

| 英文摘要 .....             | ii  |

| 致謝 .....               | iii |

| 目錄 .....               | iv  |

| 圖目錄 .....              | vi  |

| 表目錄 .....              | vii |

| 第一章 簡介 .....           | 1   |

| 1.1 基礎背景 .....         | 1   |

| 1.2 量子點非揮發性記憶體元件 ..... | 2   |

| 1.3 論文架構 .....         | 4   |

| 第二章 負微分電容之基礎理論 .....   | 5   |

| 2.1 負微分電容數學模型 .....    | 5   |

| 2.2 負微分電容之頻率反應模型 ..... | 7   |

| 第三章 元件製作與量測系統 .....    | 14  |

| 3.1 薦基二極體製程 .....      | 14  |

| 3.1.1 光罩設計 .....       | 15  |

| 3.1.2 製程步驟 .....       | 15  |

## 頁次

|                             |    |

|-----------------------------|----|

| 3.2 場效電晶體元件製程 .....         | 17 |

| 3.2.1 光罩設計 .....            | 18 |

| 3.2.2 製程步驟 .....            | 19 |

| 3.3 量測系統 .....              | 22 |

| 3.3.1 光激發螢光量測系統 .....       | 22 |

| 3.3.2 室溫環境下之電性量測系統 .....    | 24 |

| 3.3.3 可變溫環境下之電性量測系統 .....   | 25 |

| 第四章 實驗結果與討論 .....           | 26 |

| 4.1 蕭基二極體之實驗結果 .....        | 26 |

| 4.1.1 蕭基二極體之光激螢光頻譜 .....    | 27 |

| 4.1.2 蕭基二極體之 I-V 電性量測 ..... | 27 |

| 4.1.3 蕭基二極體之 C-V 電性量測 ..... | 30 |

| 4.1.4 實驗結果與討論 .....         | 42 |

| 4.2 場效電晶體元件之實驗結果 .....      | 43 |

| 4.2.1 場效電晶體元件之光激螢光頻譜 .....  | 43 |

| 4.2.2 場效電晶體元件之電性量測 .....    | 44 |

| 4.2.3 實驗結果與討論 .....         | 51 |

| 第五章 總結與未來研究 .....           | 52 |

| 參考文獻 .....                  | 53 |

# 圖 目 錄

頁次

|                                                                                                |    |

|------------------------------------------------------------------------------------------------|----|

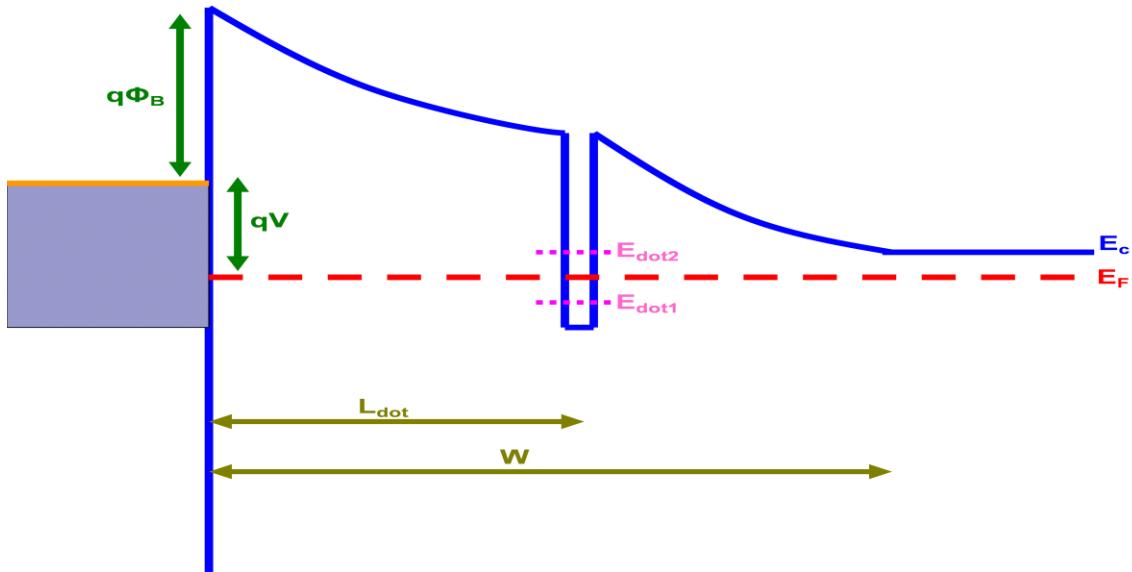

| 圖 2.1、單層量子點雙能階之蕭基二極體之能帶圖示意圖 .....                                                              | 7  |

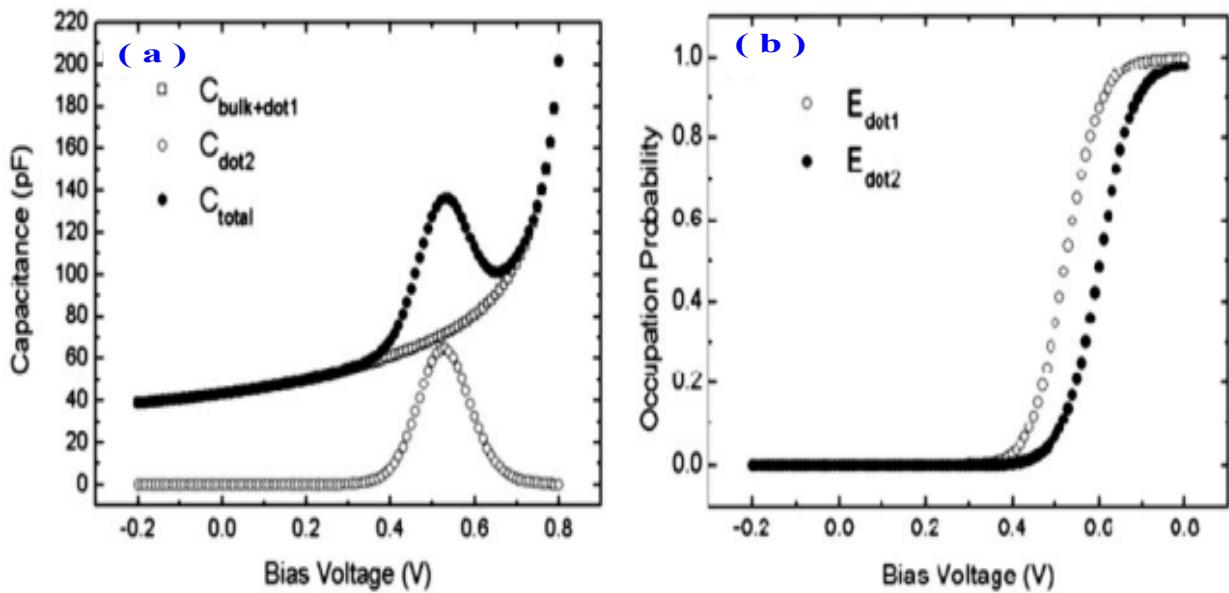

| 圖 2.2、(a)計算後的電容-電壓相依關係。(b) $E_{dot1}$ 、 $E_{dot2}$ 佔有率 .....                                   | 6  |

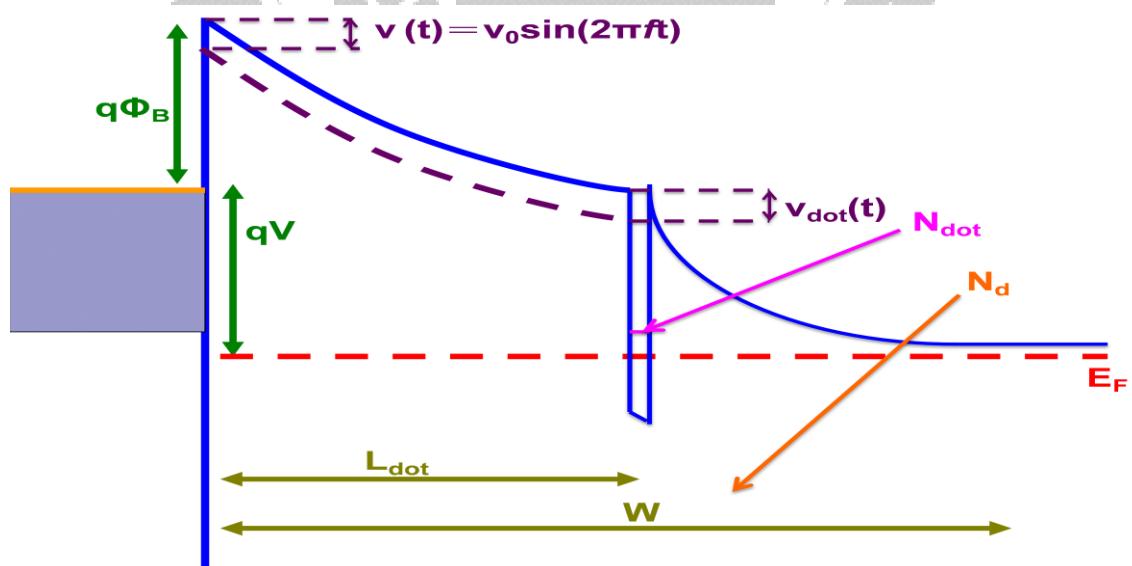

| 圖 2.3、單層量子點單能階之蕭基二極體之能帶圖示意圖 .....                                                              | 10 |

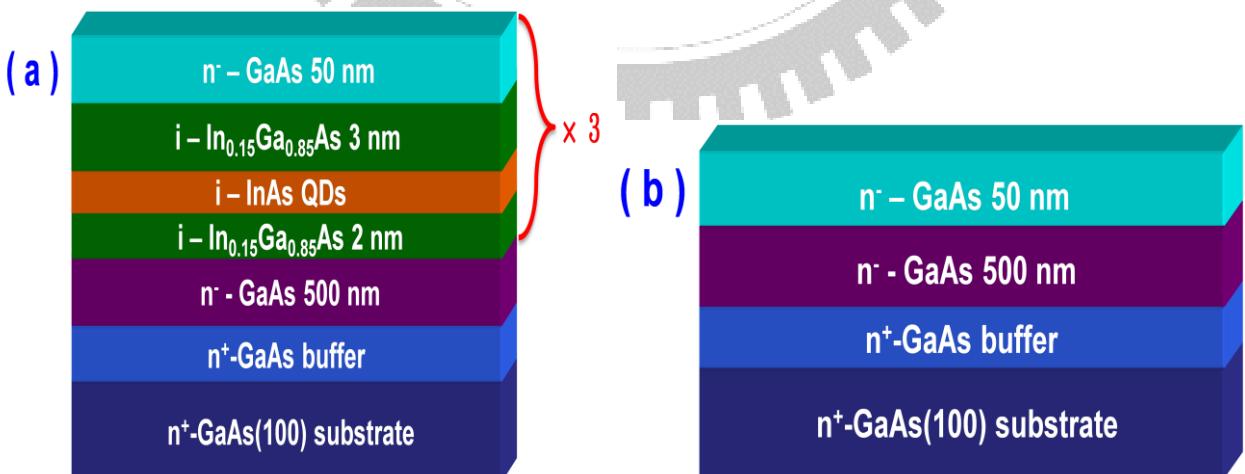

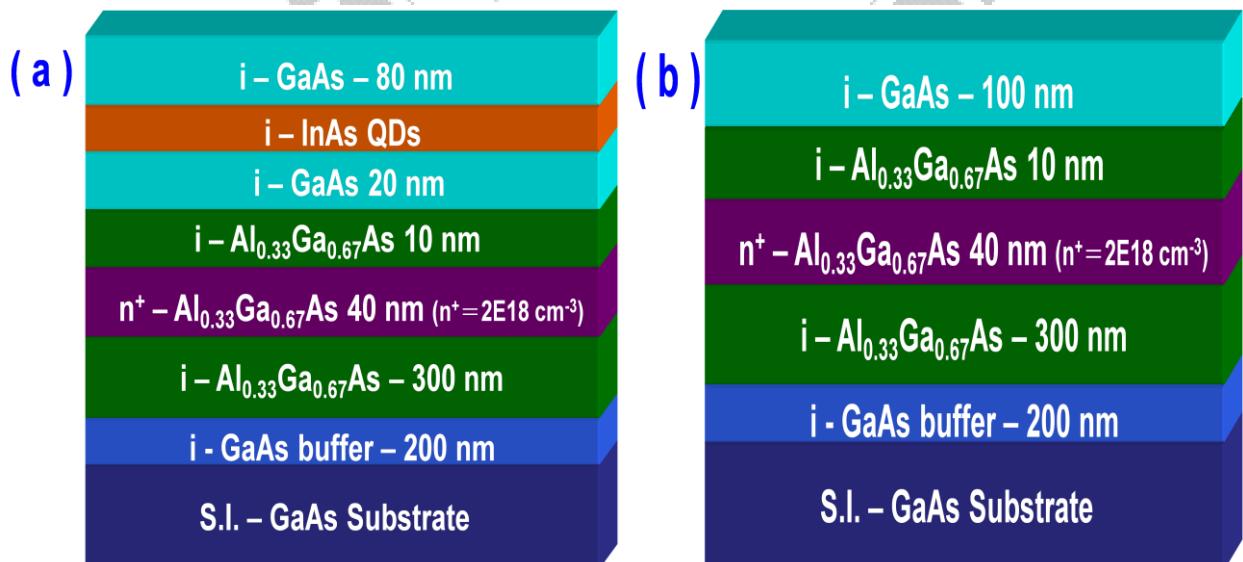

| 圖 3.1、(a)樣品 A 結構圖。(b)樣品 B 結構圖。.....                                                            | 14 |

| 圖 3.2、樣品磊晶結構圖(a)樣品 C、(b)樣品 D。.....                                                             | 17 |

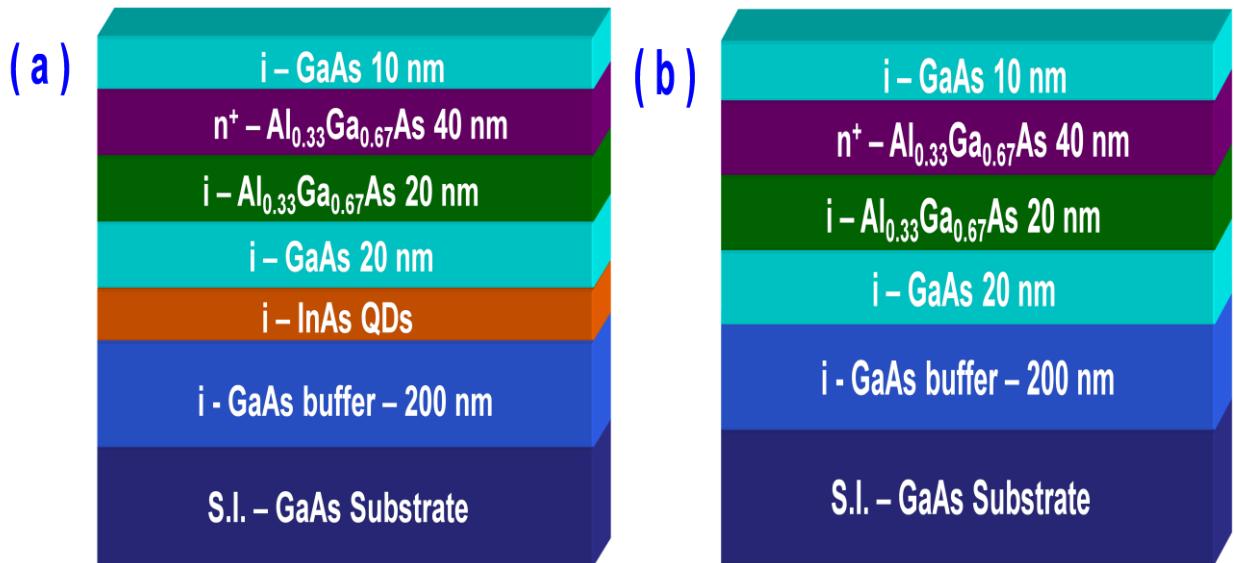

| 圖 3.3、樣品磊晶結構圖(a)樣品 E、(b)樣品 F。.....                                                             | 18 |

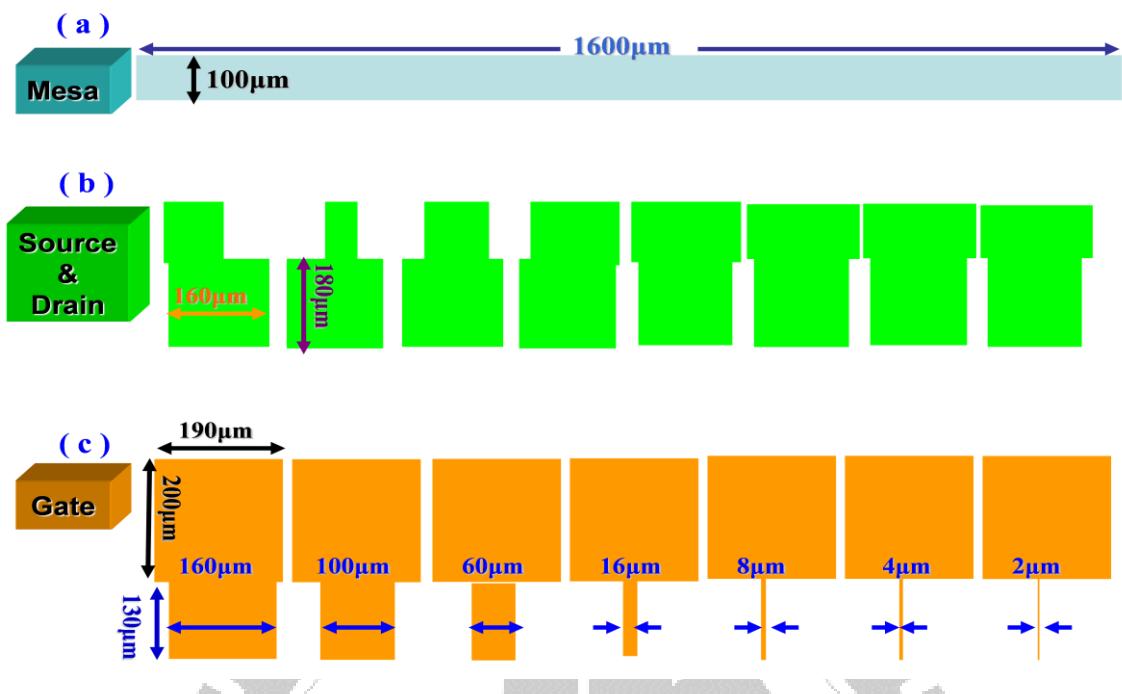

| 圖 3.4、場效電晶體所使用的三道光罩圖案。(a)Mesa 光罩。(b)源/汲極光罩。(c)閘極光罩。.....                                       | 19 |

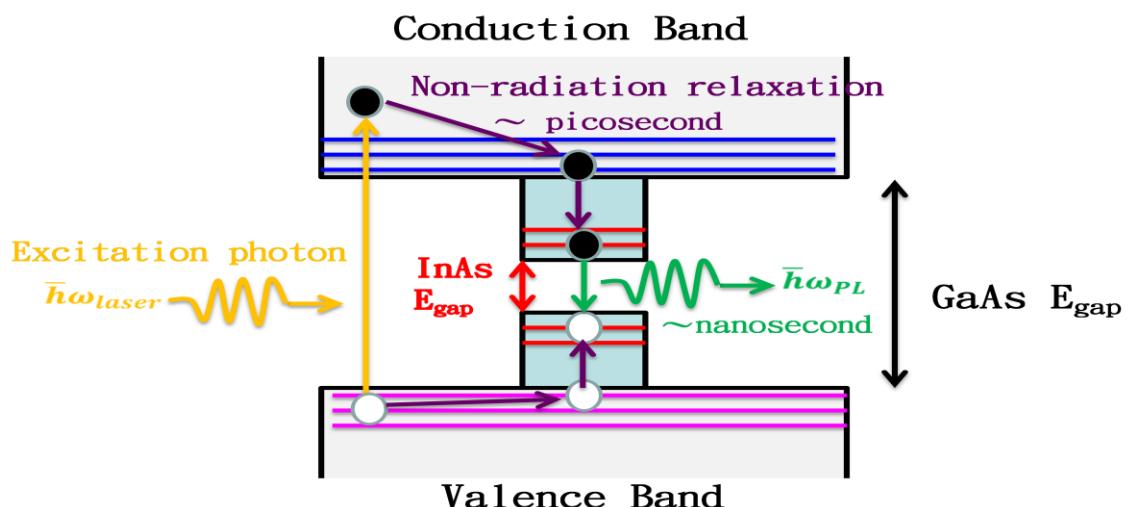

| 圖 3.5、光激螢光量測發光機制 .....                                                                         | 22 |

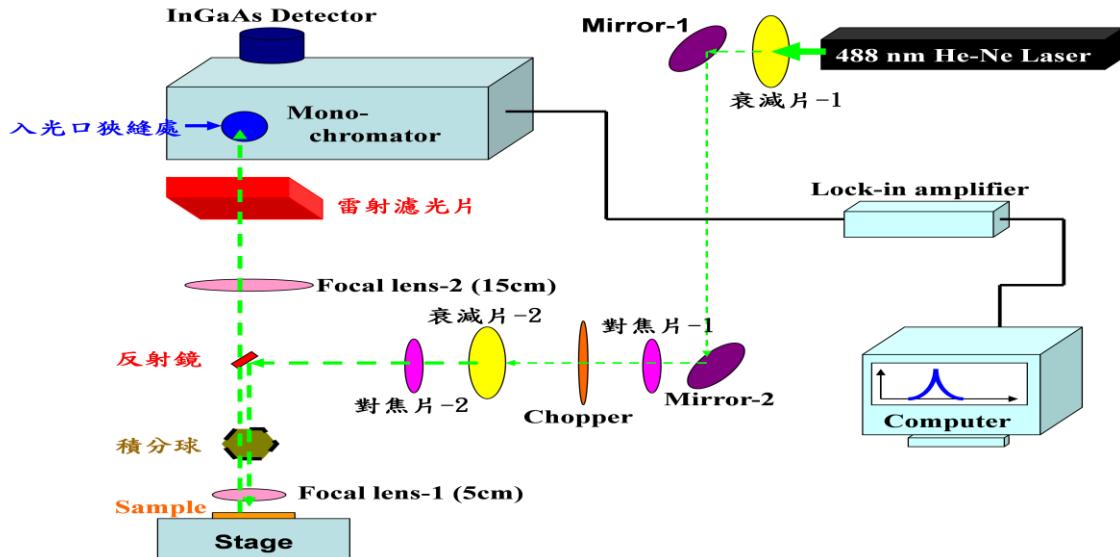

| 圖 3.6、光激螢光量測系統示意圖 .....                                                                        | 23 |

| 圖 3.7、室溫電性量測系統示意圖 .....                                                                        | 24 |

| 圖 3.8、可變溫之環境電性量測系統示意圖 .....                                                                    | 25 |

| 圖 4.1、樣品 A 在室溫及低溫下之光激螢光量測結果。(a)室溫、(b)低溫 .....                                                  | 27 |

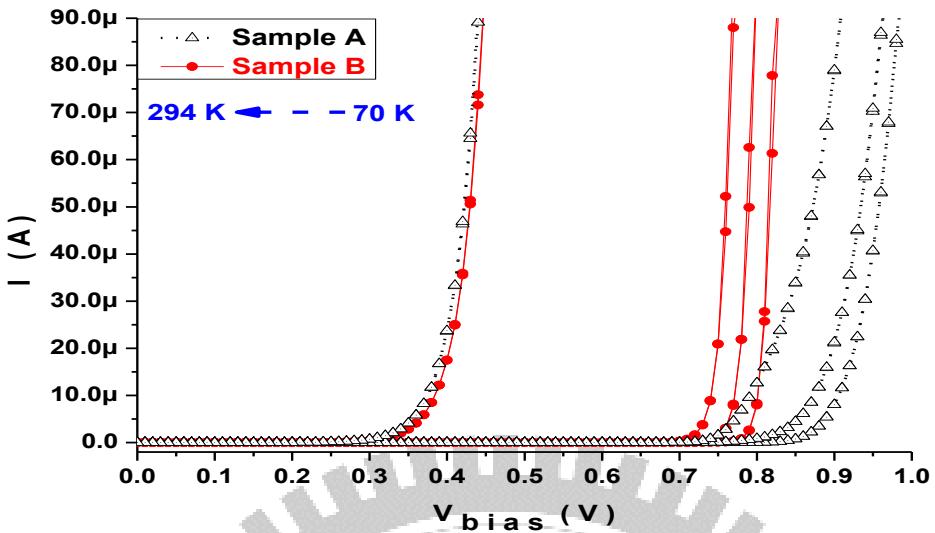

| 圖 4.2、樣品 A、B 於 70、90、110、294 K 溫度下的 I-V 曲線結果 .....                                             | 28 |

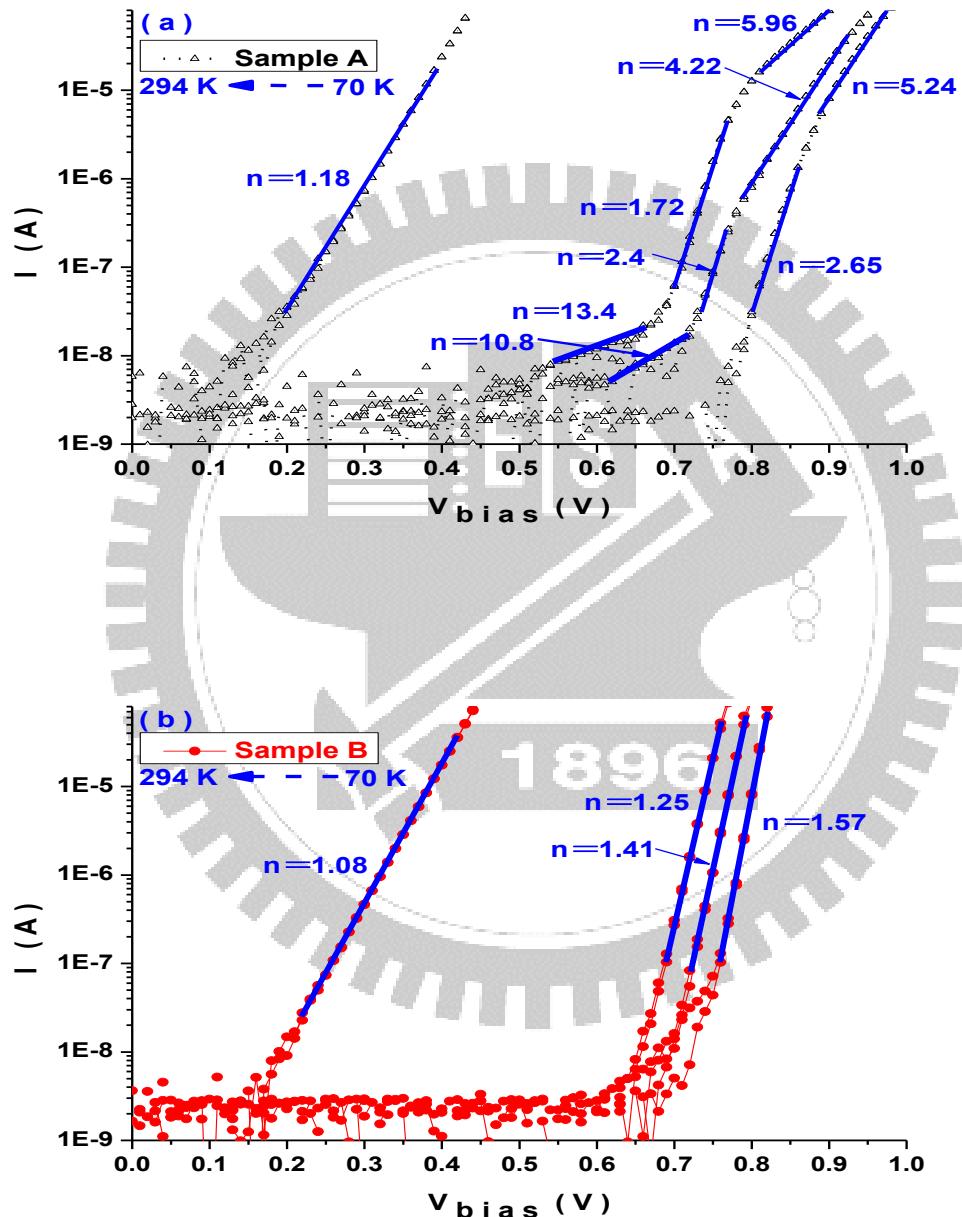

| 圖 4.3、樣品 A、B 於 70、90、110、294 K 溫度下的(log I)-V 曲線結果 .....                                        | 29 |

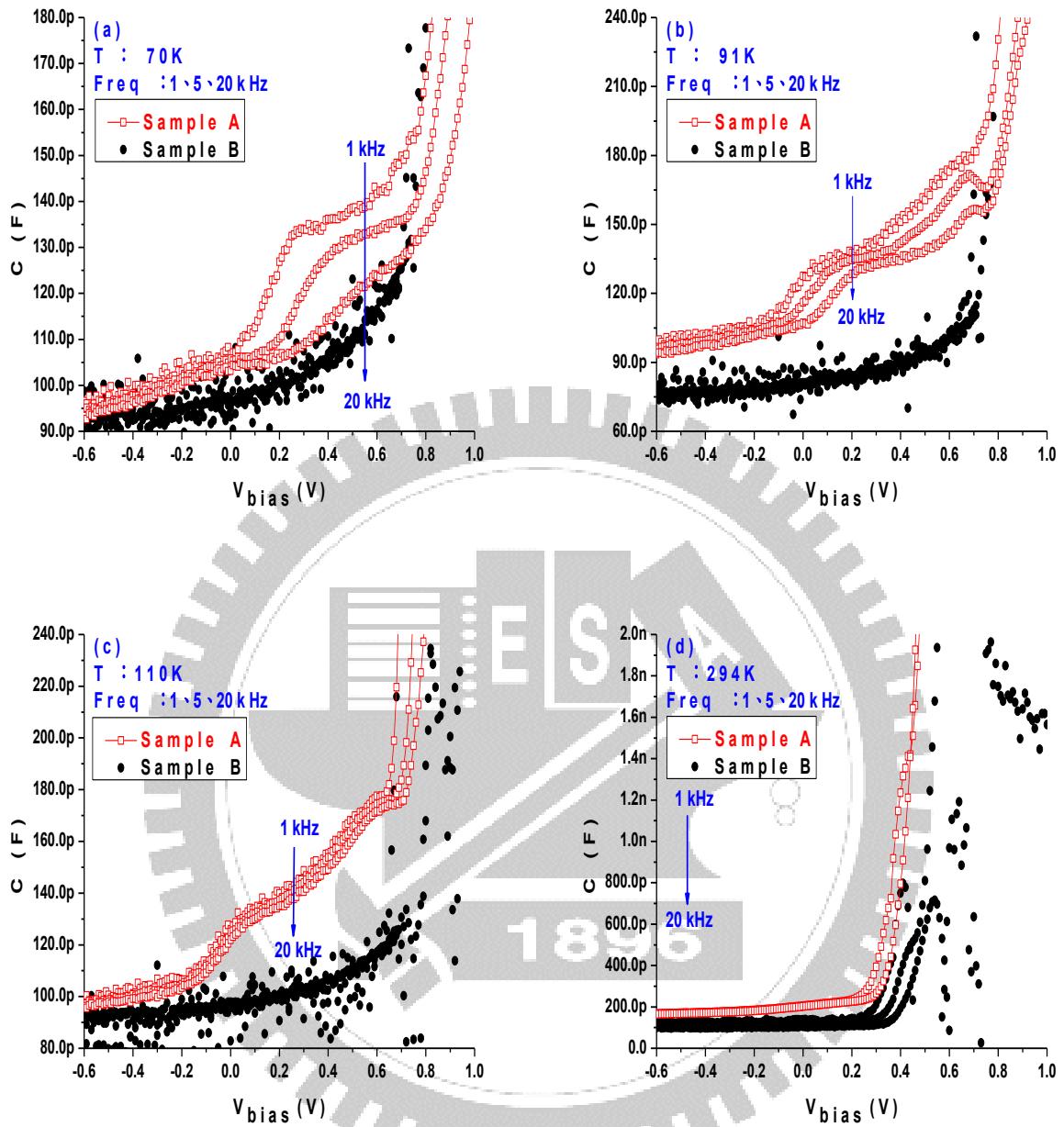

| 圖 4.4、樣品 A、B 在(a) 70K、(b) 91K、(c) 110K、(d) 294K，溫度下之 C-V 電性比較 .....                            | 31 |

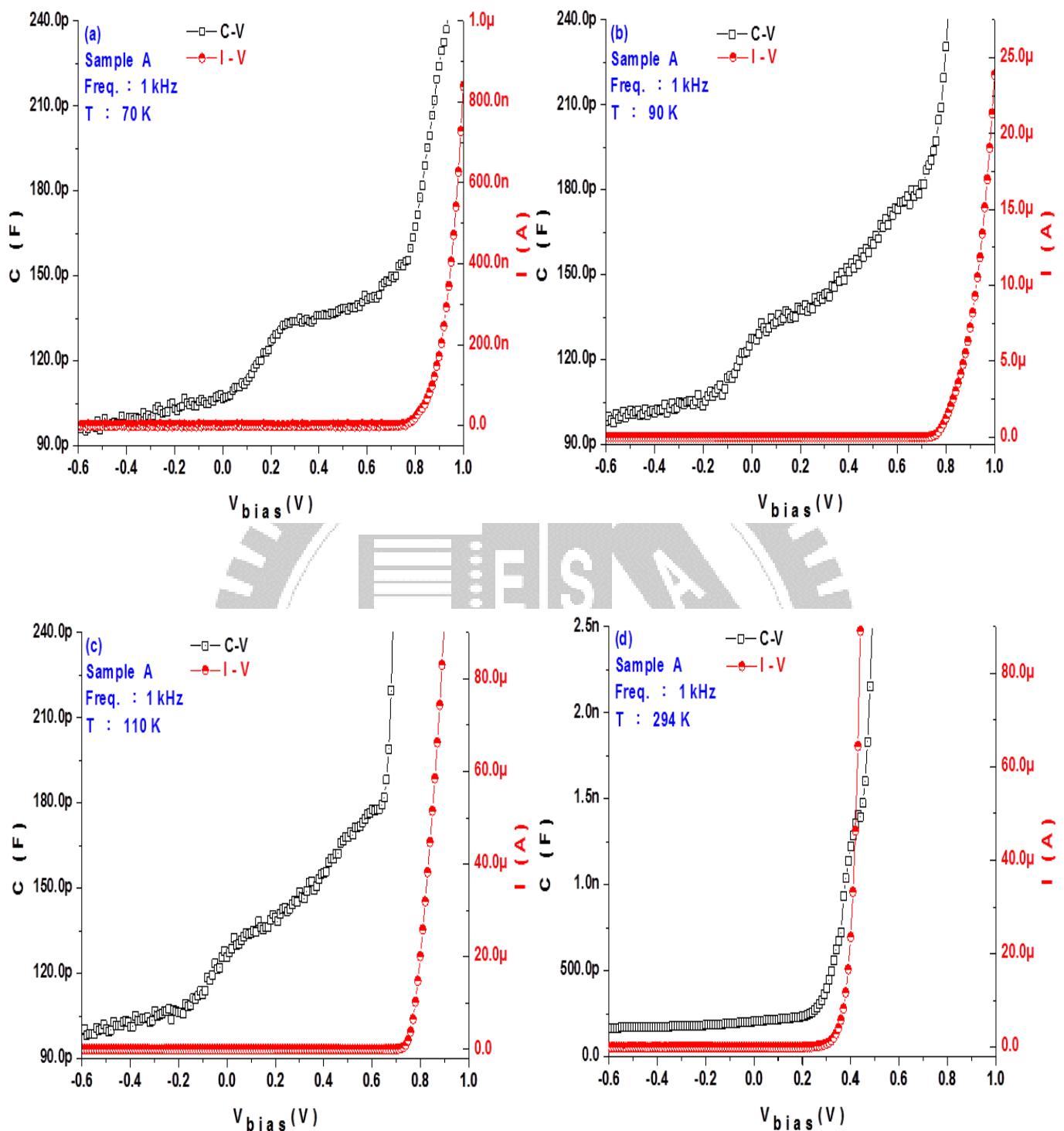

| 圖 4.5、樣品 A 在(a) : 70 K、(b) : 90 K、(c) : 110 K、(d) : 294 K、下 C-V 及 I-V 曲線結合圖 .....              | 32 |

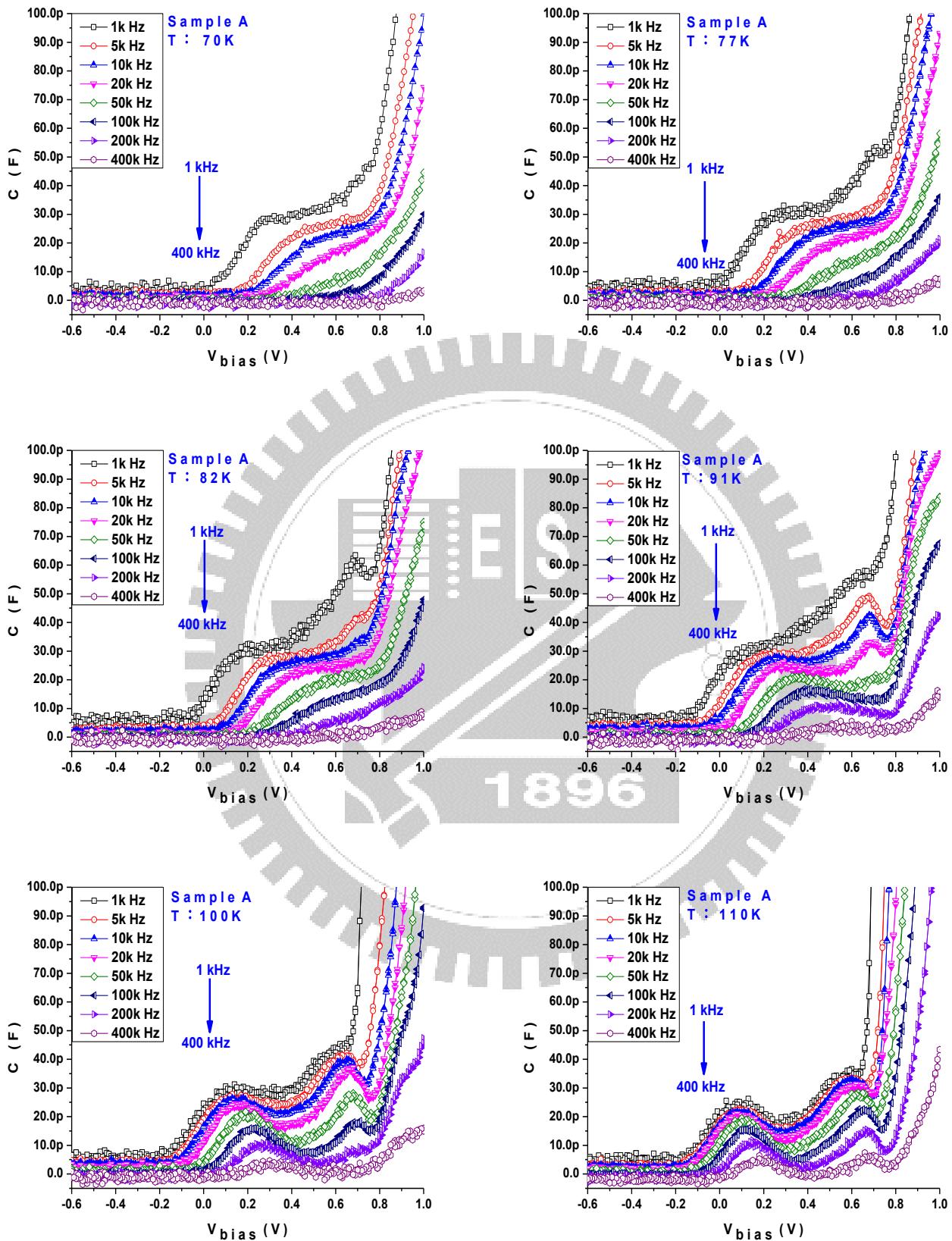

| 圖 4.6、樣品 A 在中溫度下的 C-V 曲線 .....                                                                 | 34 |

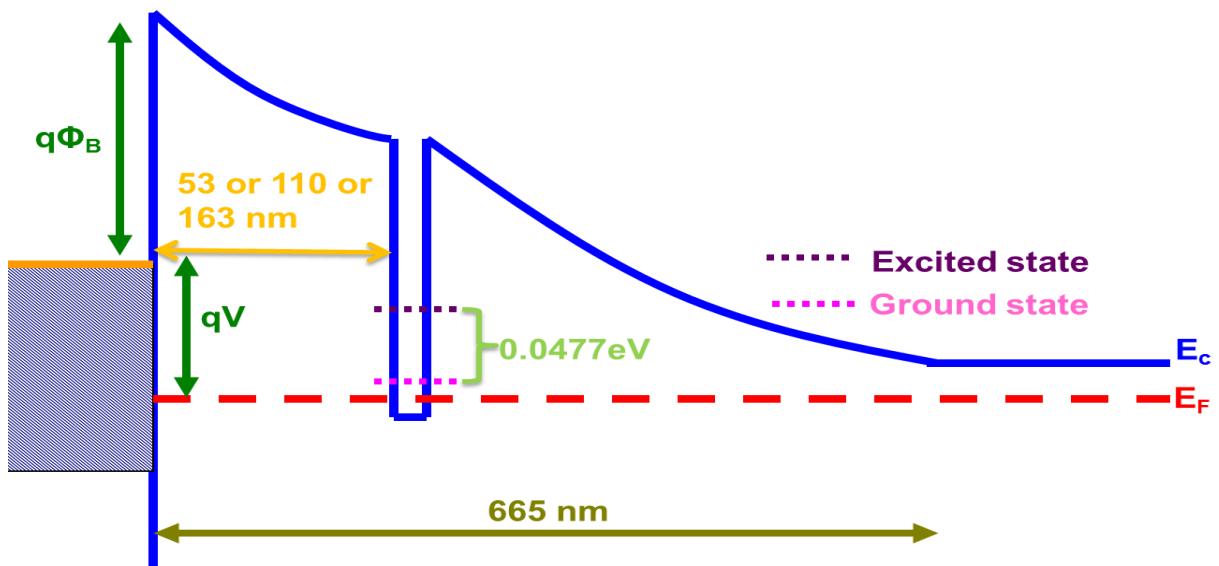

| 圖 4.7、樣品 A 之單量子點層基態與激發態能階模型 .....                                                              | 36 |

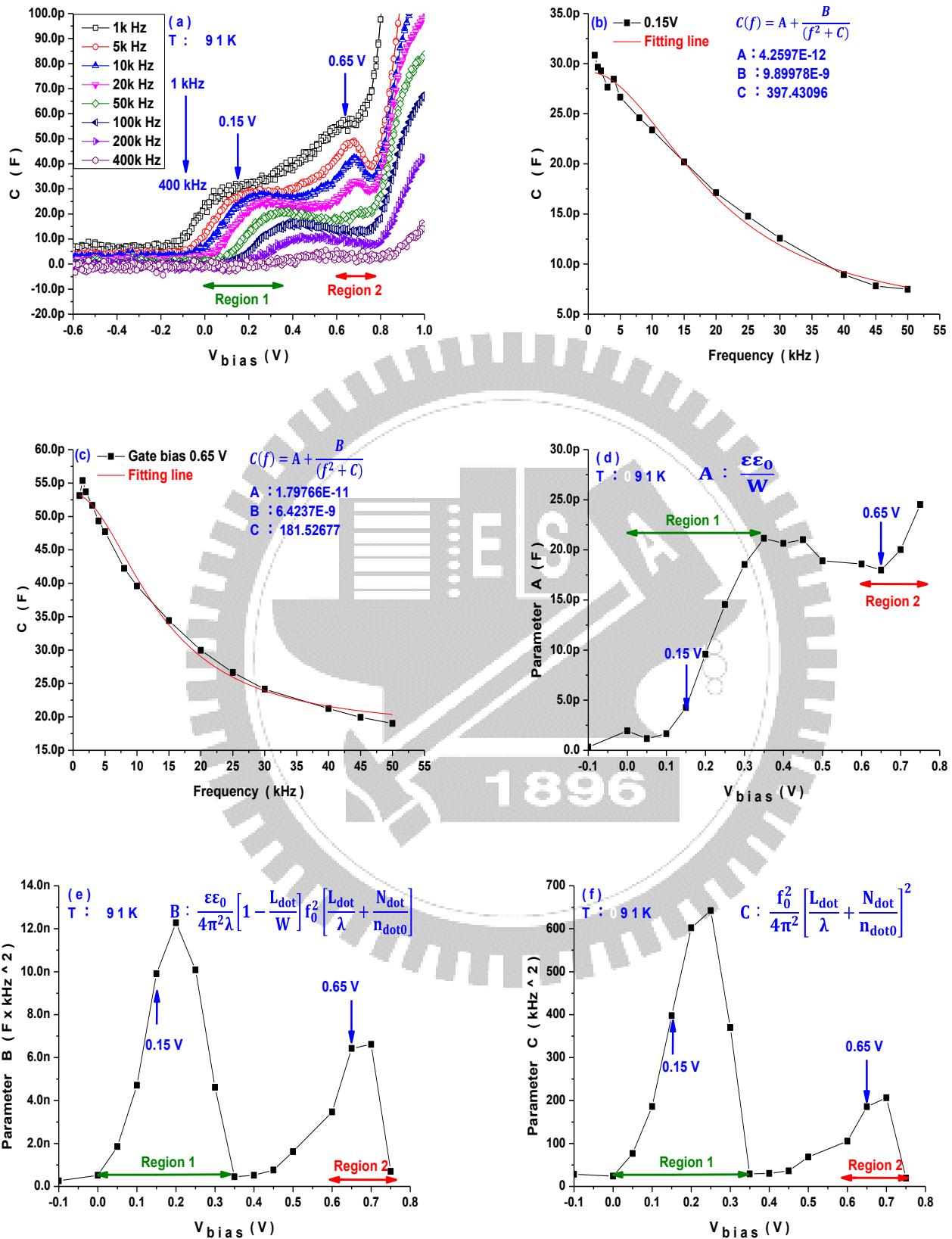

| 圖 4.8、樣品 A 在 91 K 下(a)電容-電壓圖、(b)0.15 V 下電容-頻率圖、(c)0.65 V 下電容-頻率圖、(d)參數 A、(e)參數 B、(f)參數 C ..... | 37 |

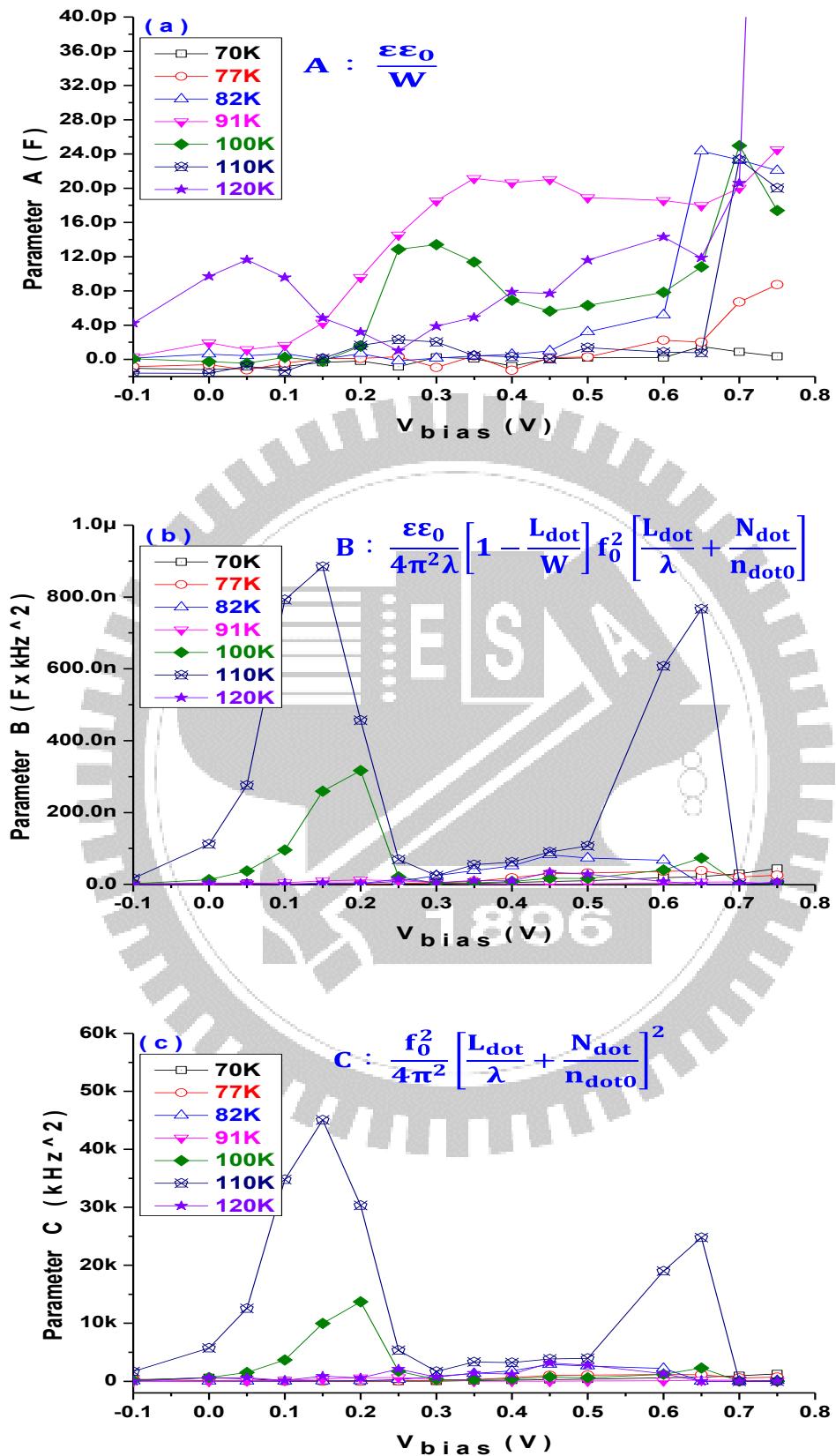

| 圖 4.9、樣品 A 在不同溫度影響下(a)參數 A。(b)參數 B。(c)參數 C 之改變 .....                                           | 38 |

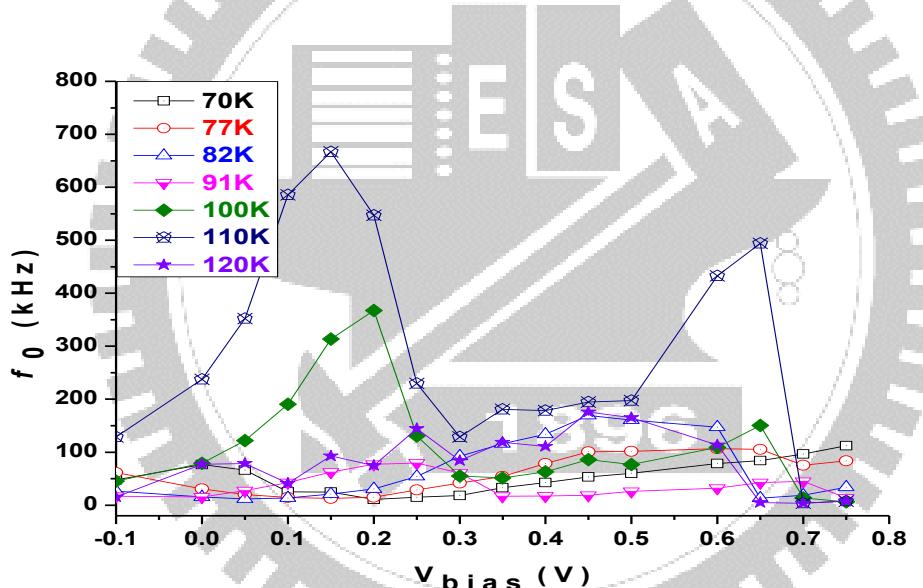

| 圖 4.10、 $f_0$ 在不同溫度環境下，隨電壓變化之趨勢圖 .....                                                         | 40 |

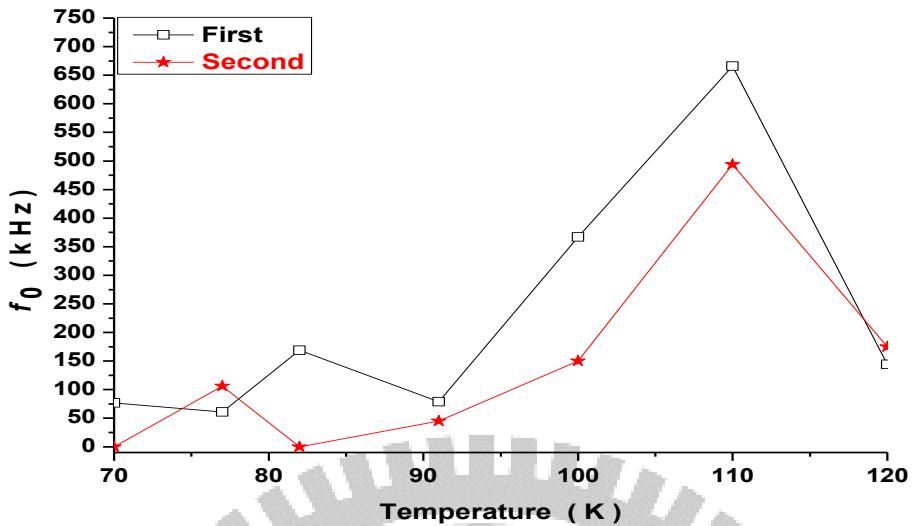

| 圖 4.11、溫度和電荷捕捉率 $f_0$ 之關係。.....                                                                | 41 |

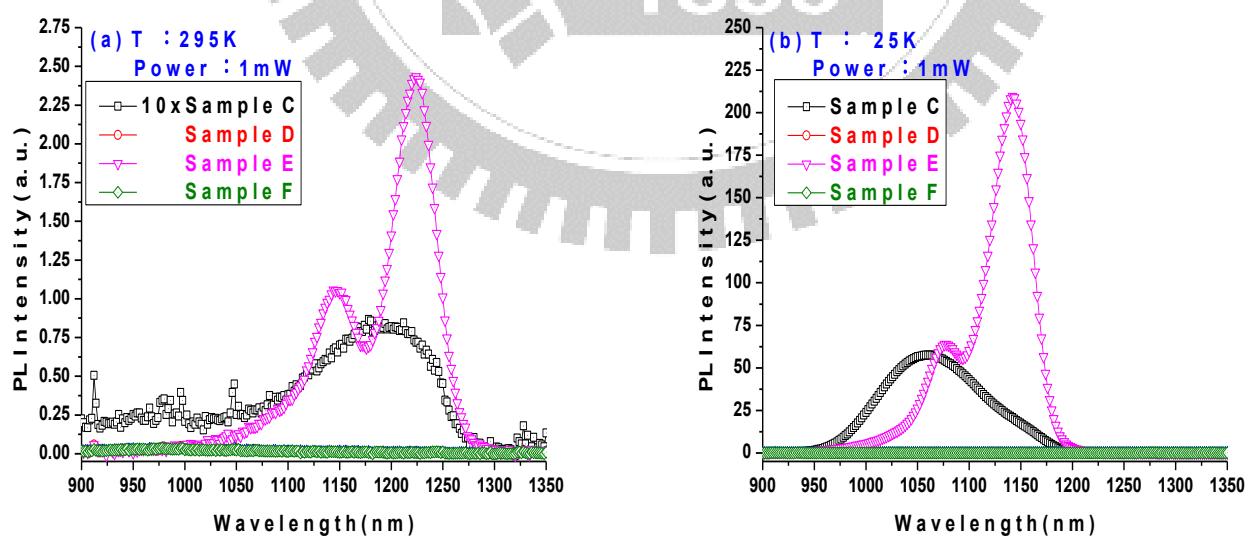

| 圖 4.12、樣品 C、D、E、F 在 1 mW 功率下之(a)室溫(b)低溫的 PL 結果。.....                                           | 43 |

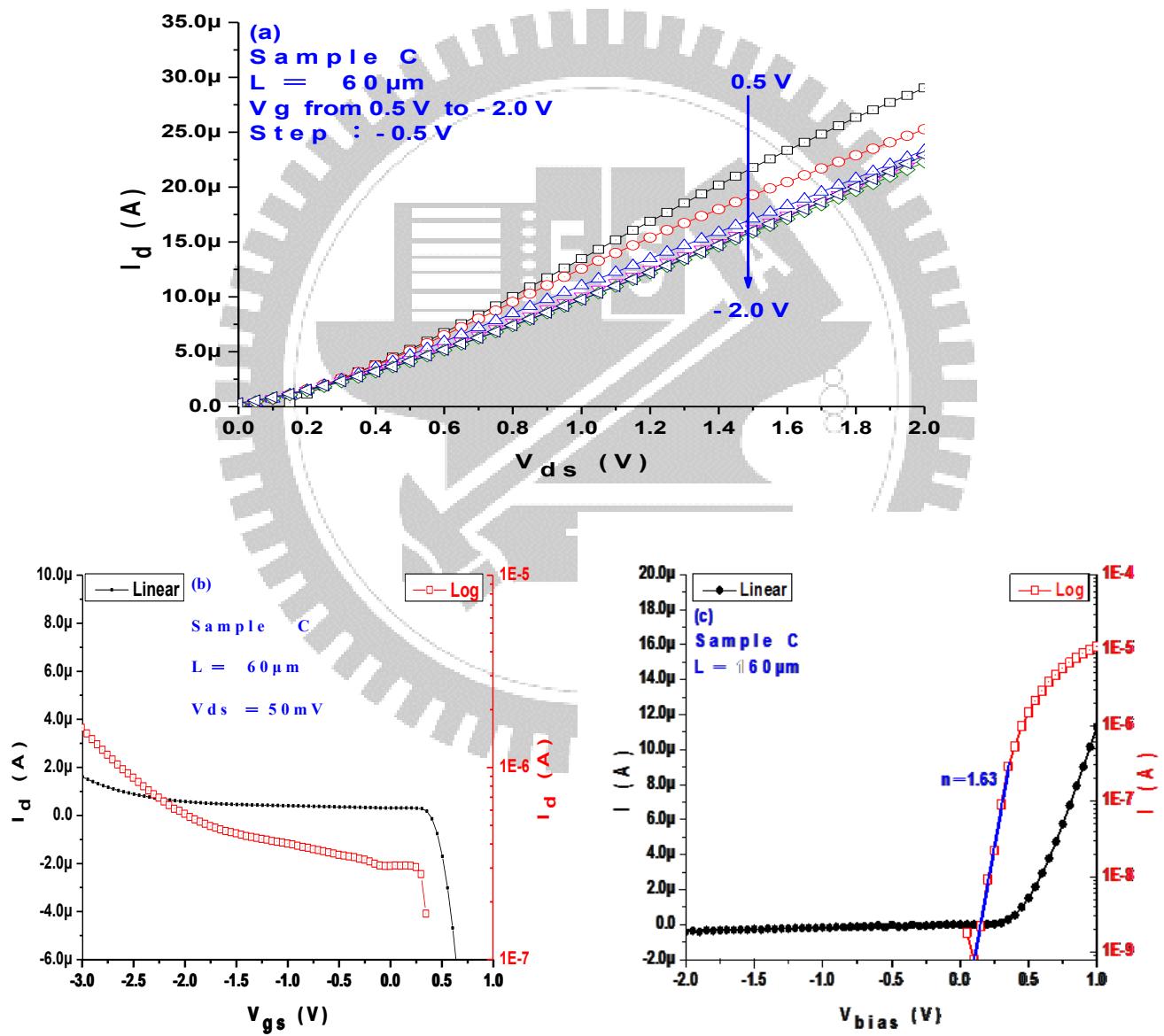

| 圖 4.13、樣品 C 在線寬 $100 \mu\text{m}$ 下之電性圖。.....                                                  | 45 |

頁次

|                                                            |    |

|------------------------------------------------------------|----|

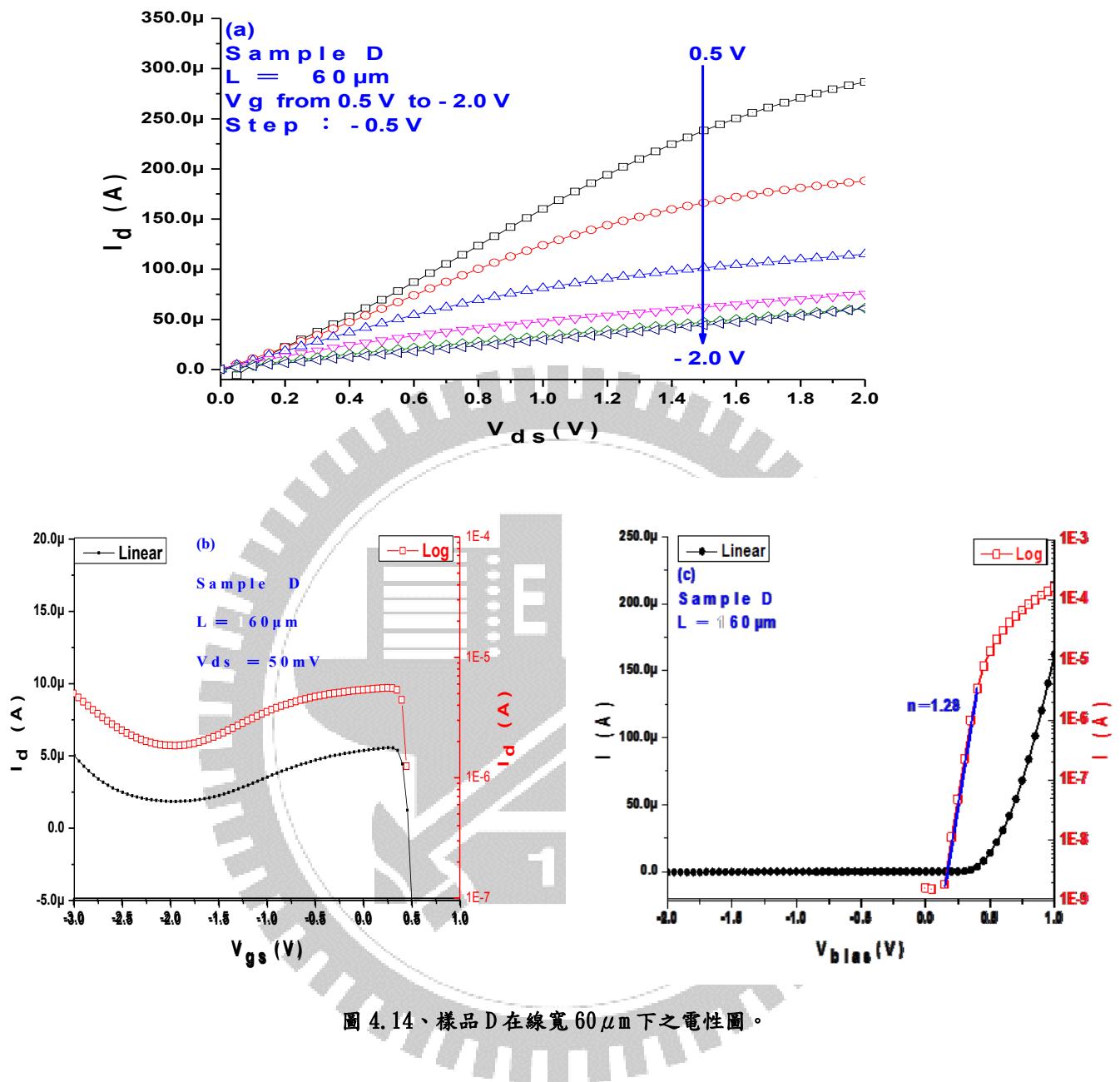

| 圖 4.14、樣品 D 在線寬 $100 \mu\text{m}$ 下之電性圖。                   | 46 |

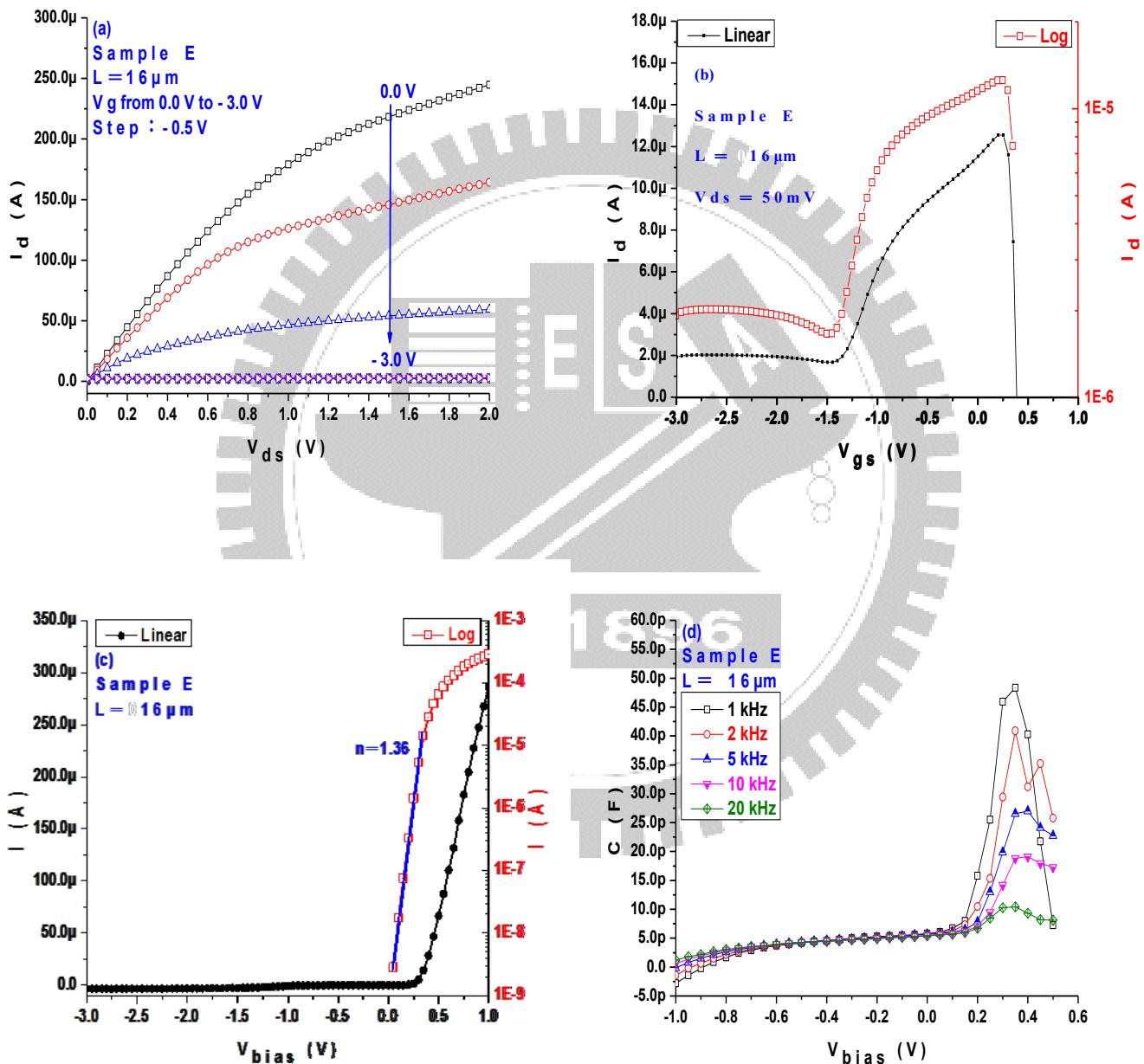

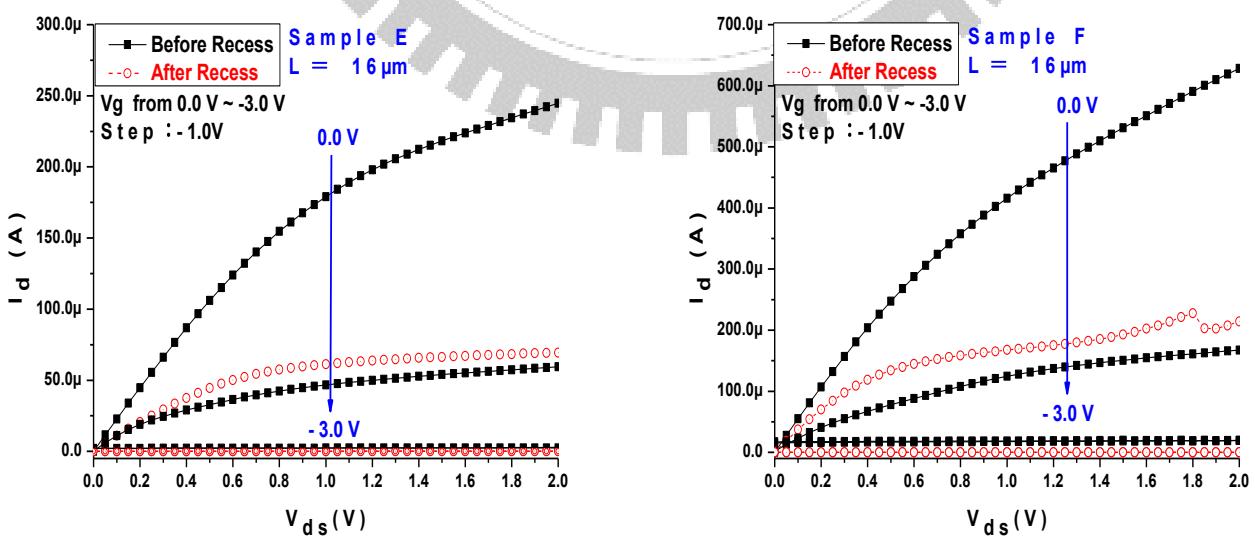

| 圖 4.15、樣品 E 在 $16 \mu\text{m}$ 線寬下的電性量測。                   | 47 |

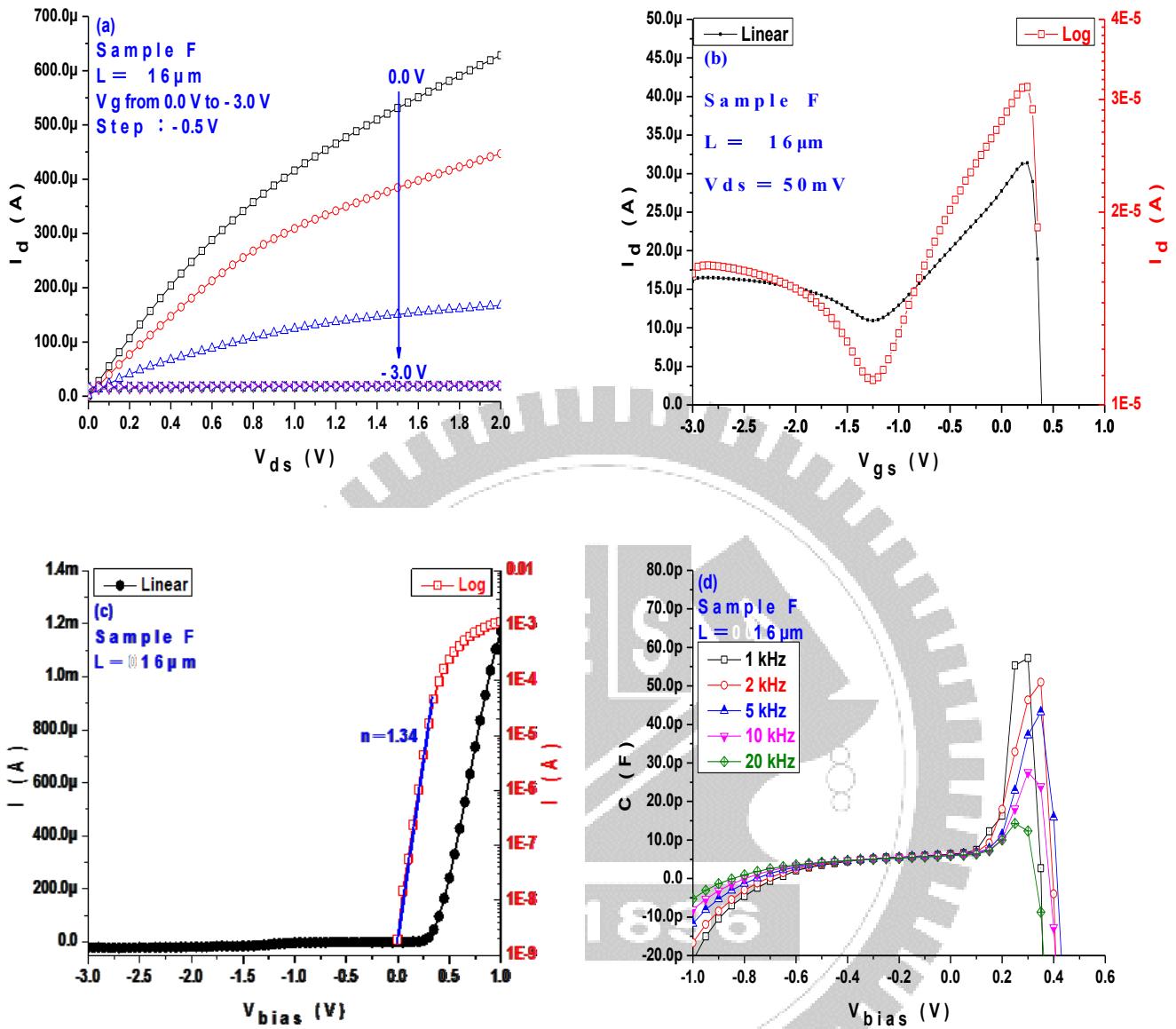

| 圖 4.16、樣品 F 在 $16 \mu\text{m}$ 線寬下的電性量測。                   | 48 |

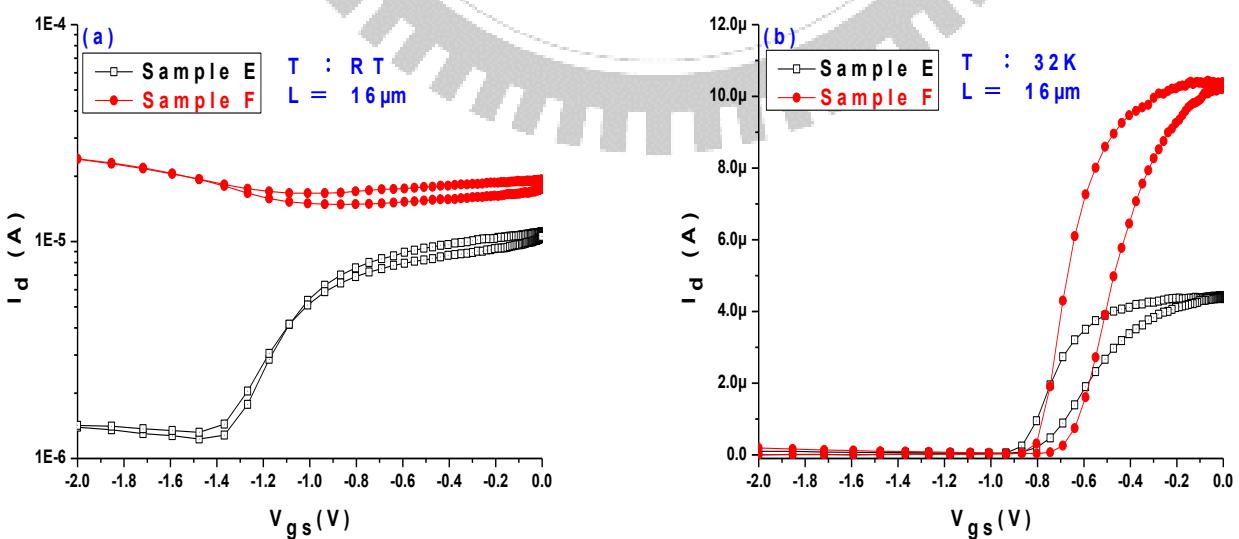

| 圖 4.17、樣品 E、F 在 $16 \mu\text{m}$ 線寬下之(a)室溫、(b)低溫環境下記憶體特性量測 | 49 |

| 圖 4.18、樣品 E、F 在 Recess 前後之 $16 \mu\text{m}$ I-V 曲線比較圖。     | 50 |

表目錄

頁次

|                                                                                                      |    |

|------------------------------------------------------------------------------------------------------|----|

| 表 4.1、樣品 A、樣品 B 於 $70 \text{ K}$ 、 $90 \text{ K}$ 、 $110 \text{ K}$ 、 $294 \text{ K}$ 下之理想因子 $n$ 之值。 | 30 |

|------------------------------------------------------------------------------------------------------|----|

# Chapter 1

## 簡介

### 1.1 基礎背景

在 1967 年，D.Kahng 和 S.M.Sze 在貝爾實驗室中發明了浮閘( floating-gate、FG)非揮發性半導體記憶體或者稱作為快閃記憶體(flash memory)[1]。其結構相似於一般常見的場效電晶體，但不同之處在於將閘極改變成為由控制閘(control gate)、阻擋層(blocking oxide)、浮閘和穿隧層(tunneling oxide)四個部份所組成。其中浮閘就是元件中主要儲存電荷形成記憶體功能與應用處。浮閘記憶體元件結構最重要的一項限制就是由穿隧層厚度所影響的縮放限制(scaling limit)。當穿隧層厚度愈薄，我們就可以擁有更小的操作電壓和更快的操作速度。但隨著記憶體元件的反覆操作使用，橫跨在絕緣體上的高電場愈可能在薄的穿隧層中造成缺陷(defect)，一旦缺陷形成了漏電途徑，那所有儲存在浮閘中的電荷都將回到通道而消失。因此如何作取捨來達到本身對於記憶體元件要求的最佳化，便成為研究之重點所在[2]。一般最常採用 poly-Si/oxide/nitride/oxide/Si(SONOS)[3~5] 以及奈米晶(nano-crystal)[6~8]之離散電荷儲存處的結構，來解決元件的縮放限制，相較於傳統浮閘，在離散節點(discrete nodes)中的電荷較不易受缺陷影響而重新分佈(redistribute)。因此當缺陷產生時，只有少部份在缺陷附近的離散節點會受到影響。而這種缺陷附近的少部份電荷損失，相較於整體儲存電荷而言並不會造成記憶值的完全喪失，所以是一種值得研究的方向。

## 1.2 量子點非揮發性記憶體元件

相比於傳統浮閘記憶體結構將電荷儲存在單一連續的節點(浮閘)上，一旦當穿隧層產生漏電途徑就會使所有資料消失而言，以各自分散獨立且週遭被介電質(dielectric)包圍之量子點為電荷儲存處的非揮發性記憶元件，可以突破傳統浮閘的縮放限制，其物理原因在於以離散的節點來儲存區域性電荷，每一個節點間都被閘極介電質所覆蓋而減少了節點間相互影響的情況，進而限制住節點間的側向電荷遷移。在 1990 年代，由 IBM 研究者首次使用矽奈米量子點為材料製作的顆粒狀浮閘 [9]，奈米量子點顧名思義就是在奈米尺度下的晶體結構，一般典型的奈米量子點非揮發性記憶體，彼此間的奈米量子點們是互相獨立地存在於閘極介電質中，由於三維量子侷限(quantum confinement)效應，能態呈現離散化的現象，因此每一個奈米量子點通常只能儲存少數的電子於其中，而這些儲存在點(dot)中的電子會共同決定記憶電晶體中通道的電導率。

除了改善縮放限制的優點之外，奈米量子點非揮發性記憶體結構還有下述的優點。

(1) 使用奈米尺度等級的量子點來做電荷儲存處，其量子侷限效應會使能隙變寬(band gap widening)和能量量化(energy quantization)進而增強記憶體的表現。(2) 相較於傳統浮閘非揮發性記憶體需要用到複雜且高成本的雙聚(dual-poly)製程程序，奈米量子點非揮發性記憶體的製程程序較為簡易。(3) 由於缺少了浮閘和汲極(drain)之間的耦合(coupling)效應，奈米量子點記憶體承受較少的汲極引致能障降低(drain-induced-barrier-lowering、DIBL)，因此我們可以在記憶體讀取時加高汲極偏壓並改善存取時間(access time)，更可以使用更短的通道來達到高密度的標準。(4) 由於使用離散分佈的奈米量子點來當作電荷儲存的地方，使元件免於受到 stress-induced-leakage-current(SILC)和氧化層缺陷的影響。雖說使用量子點的優點很多，但離散分佈的量子點同樣使得外接閘極控制源和量子點分佈儲存層之間的電容耦合變低，這使得我們需用到更高的操作電壓來操作因此抵消了之前降低穿隧層所造成的低操作電壓，這同樣使我們失去了一個設計元件最佳化的重要參數耦合率(coupling ratio)。

奈米量子點非揮發性記憶體的性能和運作良好與否，是很大程度的依據在 (A) 製程對薄膜穿隧氧化層的均勻性(uniform)和重製性(reproducible)的可靠度。(B) 奈米等級電荷儲存點的特性如：結晶度(crystallinity)、尺寸(size)、空間分佈(spatial distribution)…等等，這些特性都會影響到被捕捉到電子的位能(potential energy)和庫侖阻擋能(coulomb blockade energy)，進而控制住在奈米晶電荷儲存點中的電子數目。大尺寸的量子點排列由於會有較小的量化侷限和庫侖阻擋效應，而使得奈米晶記憶體元件可提供更高的編寫/抹除(programming/erasing、P/E)效率。但較小的量子點可以提高在通道上量子點密度藉此來達到元件的均勻性。因此瞭解量子點的物理特性，如電子的捕捉與逃逸…等，是發展其記憶元件的第一步。

相較於矽量子點記憶體中較無變化能隙之缺點，如以 III-V 族化合物來當量子點之組成材料，則可擁有更多元之能障設計、更少介面缺隙……等等優點[10]，在 III-V 族化合物研究中有不少文獻所採用的就是 InAs 量子點結構。有研究著重於觀察 InAs 量子點充放電荷在 I-V 曲線上形成臨界電壓偏移之記憶窗口，並觀察在溫度的變化下之差異來分析和量子點內能階的關係[11]。也有研究著重在於 InAs 量子點密度和偏移電壓的關係[12]。有研究則是比較了 InAs 量子點磊晶於超晶格或塊材 GaAs 下，對電荷之侷限能力和抗熱擾動之能力[13]。除了以電性之方式操作 InAs 量子點記憶體外，有研究則是利用了波長在電信通訊範圍之光源去控制單電子之 InAs 記憶行為[14]。本實驗室則著重於探討 InAs 量子點層內能階之充放電行為隨頻率之變化，在 C-V 曲線上所形成之負微分電容的現象，並藉由分析此負微分電容之原理，來加深對量子點內之能階電荷對電性影響的理解。最終希望用 InAs 之量子點層為場效電晶體之記憶中心，觀察其記憶效應。

### 1.3 論文架構

在此篇論文中，將著重於對量子點內部能階之電荷儲存以及釋放之行為所造成的電性結果，包括其電流--電壓關係與電容--電壓關係。

在本篇論文的第二章開始，主要是介紹已發表之文獻中對於含量子點之蕭基二極體之電性量測觀察，此章將利用簡易的元件模型以及數學推導來解釋其電容--電壓關係中觀察到獨特『負微分電容』之物理現象。

第三章則是簡介本研究之二種元件之製作，包含『蕭基二極體』以及『場效電晶體』。對於所需要注意之事項和製程的全部內容都仔細地記錄在此章節之中，以及所使用之光罩、製程之條件以求能讓各位能對每一道之製程內容與結果可擁有較為清楚之概念。最後則是實驗中所使用到之量測系統，包含『光激發螢光系統』以及『室溫及可變溫環境下之電性量測系統』這兩項之架設以及使用。

第四章就量測之結果進行討論，首先利用光激發螢光之光量測結果，對樣品中量子點層之磊晶結果作出評估，再對蕭基二極體之電流--電壓曲線量測，觀測元件之導通電壓並計算元件之理想因子  $n$ 。接著就是利用樣品 A、樣品 B 來在電容--電壓曲線中的差異來判別量子點層所導致之負微分電容之現象，接著便是針對樣品 A 去觀察量子點層之電容--電壓訊號在不同溫度以及頻率下的改變。針對場效電晶體的部份則是著重於觀察量子點層位於二維電子氣上方之樣品 C，以及下方之樣品 E 元件結構，彼此之間的相對位置對電流--電壓曲線之影響，並以相似結構卻無量子點層之樣品 D、F 為比較元件。

第五章則是總結，根據目前進行到之研究結果以簡短之敘述作出結論。並針對將來可進行之研究方向作出可行性之建議。

# Chapter 2

## 負微分電容之基礎理論

### 2.1 負微分電容之數學模型

一般對量子點的物理特性的研究著重以光學方法，如光激發螢光(photoluminescence) [15]。但為了達到奈米量子點之記憶功能和其它更多元的應用，對於量子點的電性研究也是不可或缺的。在電性研究中可看到隨著量子點對電荷之捕捉/釋放，在 C-V 曲線圖中顯示出不同的特徵[16~21]，而負微分電容也可在對量子點的電性研究中被看到。在此章節中將提及所謂的負微分電容在零維效應下，離散能態間電荷的行為影響結果，也以簡單的假設模型和算式來驗証實驗量測之結果中所觀察到的現象。在接下來的將會把所使用的模型以及數學公式做更為清楚的解說，以方便更深入地瞭解負微分電容概念。為了解釋造成負微分電容現象的原理，已有研究提出利用兩個能階( $E_{dot1}$ 、 $E_{dot2}$ )的量子點模型去解釋[22~25]。概念是利用一固定電壓  $V$  和一測試頻率為  $\omega$  之測試訊號電壓  $V(\omega)$  外加到蕭基二極體上，便可利用定電壓操控所在量子點附近的準費米能階(quasi-fermi level)  $E_F$  去接近不同的能階，由於能階間擁有不同的對電荷捕捉/釋放時間，故可藉由每個能階間電荷捕捉/釋放時間和測試訊號電壓  $V(\omega)$  反應與否，來決定是否要在計算中加入此電容值。在此先簡單以一個單層量子點層之蕭基二極體元件來當作電容--電壓相依性量測結果之初始模型，模型中量子點層和表面閘極金屬觸點的距離為  $L_{dot}$  如圖 2.1 所示，在此能帶圖中我們先忽略了量子點層的寬度以簡化模型之計算。

圖 2.1、單層量子點雙能階之蕭基二極體之能帶圖示意圖。

為了進行數學上的運算，採以用 delta 函數來近似忽略寬度下量子點之表示式。並採用 Poisson's 方程式如式子(2.1)所示以及邊界條件如式子(2.2)所示去解。

$$\text{Poisson's equation} : \frac{\partial^2 \varphi}{\partial x^2} = -\frac{eN_d}{\varepsilon_0} + \frac{en_{dot}}{\varepsilon_0} \delta(x - L_{dot}) \quad (2.1)$$

$$\text{B.C. } \varphi(W) = 0 \quad \& \quad \left. \frac{\partial \varphi}{\partial x} \right|_{x=W} = 0 \quad (2.2)$$

在式子(2.1)中 Poisson's 方程式右邊項的電荷密度包含了兩個部份，其中  $N_d$  代表了離子化摻雜物之電荷密度常數，而  $n_{dot}$  代表了在量子點中的累積電荷密度。如把邊界條件帶入 Poisson's 方程式中可得解如式子(2.3)所示。在式子(2.3)中  $\varepsilon$  代表的是砷化鎵(GaAs)的介電係數 13.1。

$$\varphi(x) = -\frac{eN_d}{2\varepsilon_0} (x - W)^2 + \{0\} \quad \text{if } x > L_{dot}.$$

$$\varphi(x) = -\frac{eN_d}{2\varepsilon_0} (x - W)^2 + \left\{ \frac{en_{dot}}{\varepsilon_0} (L_{dot} - x) \right\} \quad \text{if } x < L_{dot}. \quad (2.3)$$

從實驗中可得知當以逆向偏壓加於閘極金屬極時，由於量子點內的能階遠在準費米能階之上，故量子點內部沒有任何能階被電荷佔據住，因此量子點此時對電性量測結果於圖型不會有的影響，也就是說在逆向偏壓的情況下  $n_{dot}$  趨近於零，故此時式子(2.3)也會變為常見之古典方程式。而當慢慢增加外接電壓往正向電壓移動時，就會使準費米能階  $E_F$  逐漸接近量子點中的第一個能階  $E_{dot}$  而使電子填入量子點的基態中，此時量子點中累積電荷密度  $n_{dot}$  也想當然而會逐漸增，對於量子點中的電荷密度可利用式子(2.4)來作計算。在式子(2.4)中， $N_{dot}$  表示量子點的有效密度以及  $\eta_1$  表示每一個量子點中基態( $E_{dot}$ )能階所能捕捉到的最大電子數。

$$n_{dot}(V_{dot}) = N_{dot} \frac{\eta_1}{1 + \exp((E_F - E_{dot} - eV_{dot})/kT)} \quad (2.4)$$

從圖 2.1 中可得知當  $V$  趨近 0 時邊界條件會如式子(2.5)所示，其中  $\Phi_B$  為蕭基能障高度(schottky barrier height)，將其和式子(2.3)結合後便可得到式子(2.6)所示。接著將式子(2.4)代入式子(2.6)中便可得式子(2.7)。最後就可以藉由式子(2.7)之計算來得到此蕭極二極體元件的空乏區寬度  $W$ 。

$$\phi(0) = -\Phi_B + V \quad (2.5)$$

$$-\Phi_B + V = -\frac{eN_d}{2\epsilon_0}W^2 + \frac{en_{dot}}{\epsilon_0}L_{dot} \quad (2.6)$$

$$W^2 - \frac{2\epsilon_0}{eN_d}(\Phi_B - V) - \frac{2N_{dot}}{N_d} \times \frac{\eta_1}{1 + \exp\left(\left(E_F - E_{dot} - \left(\frac{e^2 N_d}{2\epsilon_0}\right)(L_{dot} - W)^2\right)/kT\right)} \times L_{dot} = 0 \quad (2.7)$$

上式(2.7)可以用數值運算的方式求解，此章節至目前為止已將塊狀(bulk)電容和量子點內基態電荷存取作了完整的數學計算，而對量子點內激發態之電荷存取也可以用同樣之方式運算。

在此模型中假設量子點的基態  $E_{dot1}$  由於擁有較長地捕捉/釋放時間，因此累積在基態的負電荷較不易隨測試頻率改變，反之，處在激發態  $E_{dot2}$  中的電荷由於捕捉/釋放時間較短，故激發態能階  $E_{dot2}$  之內部電子較易跟隨到測試頻率  $V(\omega)$ 。因此可將整個蕭基二極體的總電容表示成不隨測試頻率變化的塊狀電容  $C_{Bulk+dot1}$  以及充電--放電電容  $C_{dot2}$  之總和，如式子(2.8)所示。

$$C = C_{Bulk+dot1} + C_{dot2} \quad (2.8)$$

對於式子(2.8)中不隨測試頻率變化之塊狀電容  $C_{Bulk+dot1}$  值的計算可利用式子(2.7)解之值代入式子(2.9)中求解。

$$C_{Bulk+dot1} = \frac{\epsilon_0}{W} \quad (2.9)$$

而對於式子(2.8)中充電--放電電容  $C_{dot2}$  值之計算，由於  $C_{dot2}$  主要來自隨偏壓改變下的量子點內電荷的變化量，故可將此變化量影響之電容用式子(2.10)所示來計算。在此計算中假設激發態能階  $E_{dot2}$  上之所有電子都會隨測試頻率  $V(\omega)$  反應，故對量子點內累積電荷密度  $n_{dot2}$  之計算可利用式子(2.4)求得。

$$C_{dot2} = e \frac{\partial n_{dot2}}{\partial V} \quad (2.10)$$

圖 2.2(a)秀出了經計算後所得到塊狀電容  $C_{Bulk+dot1}$  以及充電--放電電容  $C_{dot2}$  之值，很明顯地負微分電容主要來自於充電--放電電容  $C_{dot2}$ ，也就是說造成 NDC 的主要原因就是量子點中激發態能階的快速充放電荷的過程。如果再以佔有率(occupation probability)和電壓作圖的話更容易理解 NDC 的成因，如圖 2.2(b)所示，

圖 2.2、(a) 計算後的電容-電壓相依關係。(b)  $E_{dot1}$ 、 $E_{dot2}$  佔有率。From [ Ref 22 ]

從式子(2.10)中可以看出充電-放電電容  $C_{dot2}$  的峰值會出現在能階  $E_{dot2}$  有半數被佔據的情況下。而且由於量子點量化所造成的離散能態密度之原因，所以隨著佔有率的提昇會使其值趨近於 1。故  $C_{dot2}$  之值一開始會隨佔有率提升而上升，到半佔滿情況下時達到峰值，最後則會隨著佔有率上升而下降，這符合之後在蕭基二極體量測中所觀察到的現象。因此便可以總結一下所謂的負微分電容現象就是在零維效應下，離散能態間的快速電荷捕捉釋放下所觀察到的結果。

## 2.2 負微分電容之頻率反應模型

在此節中將探討負微分電容和頻率的數學關係，因此將模型再簡化為單量子點能階之情況，如圖 2.3 所示。並要把 2.1 節算式中的  $V$  改為定電壓源  $V_0$  以及和時間相關的弦波訊號源  $v(t)$ ，如式子(2.11)所示。在式子(2.11)中  $v_0$  表示弦波訊號源的振幅大小，而  $f$  表示其頻率。

$$V = V_0 + v(t) = V_0 + v_0 \sin(2\pi f t) \quad (2.11)$$

當將時間相依的弦波訊號源  $v(t)$  考慮進元件之中時，除了明顯可以知道它會影響到量子點內的累積電荷情況外，也勢必會影響到元件內空乏區的寬度  $W$ 。將(2.11)式代入(2.4)、(2.7)中同樣可看出考慮測試弦波訊號源時，會使量子點內電荷密度  $n_{dot}$  以及元件空乏區寬度  $W$  變為時間相關的函數。故最後藉由對  $\Delta W(t)$  和  $\Delta n_{dot}(t)$  的計算以及利用公式(2.9)、(2.10)就可得到電容--電壓的關係。

圖 2.3、單層量子點單能階之肖特基二極體之能帶圖示意圖。

為了得到 NDC 模型中電容和頻率的關係式，就必須先要知道  $\Delta n_{dot}(t)$  和  $\Delta W(t)$  之變化量所造成的電荷  $\Delta q_{dot}(t)$  和  $\Delta q_w(t)$  之改變，並藉由對時間  $t$  的微分來取得電流  $I(t)$ ，如式子(2.12)所示。

$$I(t) = \frac{\partial[\Delta q_{dot}(t)]}{\partial t} + \frac{\partial[\Delta q_w(t)]}{\partial t} = -e \frac{\partial[\Delta n_{dot}(t)]}{\partial t} + eN_d \frac{\partial[\Delta W(t)]}{\partial t} \quad (2.12)$$

式子(2.12)中右式的第一項就是量子點內部的充放電行為之電荷變化量。而第二項就是來自於空乏區寬度的變動所造成的影響，其值可利用式子(2.1)來求解並利用  $(V_0 > > \nu_0)$  之特性，最後就可得到式子(2.13)。

$$v_{dot}(t) = \frac{eN_d}{\epsilon_0} (W - L_{dot}) \Delta W(t) = \left(1 - \frac{L}{W}\right) \left[ v(t) + \frac{eL}{\epsilon_0} \Delta n_{dot} \right] \quad (2.13)$$

上式中  $v_{dot}(t)$  表示的是在距離金屬表面  $L_{dot}$  處量子點內部隨時間變化之電壓。藉由算式(2.13)可求得  $\Delta W(t)$  的值。因此對(2.12)中的電流  $I(t)$  而言，只剩下  $\Delta n_{dot}(t)$  項還未知其解，為了求得  $\Delta n_{dot}(t)$  之解必須考量到電荷在量子點捕捉/釋放過程中的動能程序如式子(2.14)。

$$\frac{\partial \Delta n_{dot}(t)}{\partial t} = \sigma_n \bar{v}_n n(t) [N_{dot} - n_{dot}(t)] - e_n n_{dot}(t) \quad (2.14)$$

在上式中  $\sigma_n$  代表在量子點中的捕捉截面積尺寸、 $\bar{v}_n$  表電子在導帶中的熱速度、 $n(t)$  表示在導帶中量子點附近的電子密度、 $e_n$  表示量子點中的電子發射率(emission rate) [40~41]。要計算量子點中的電子發射率  $e_n$  的值，可以利用沒有外接測試訊號的情況來獲得，此時  $\partial \Delta n_{dot}(t) / \partial t$  之值會為零因此式子(2.14)會變為式(2.15)：

$$e_n n_{dot}(t) = \sigma_n \bar{v}_n n(t) [N_{dot} - n_{dot}(t)] \quad (2.15)$$

另外如將量子點內隨時間變化的電子量  $n_{dot}(t)$  以一個定量  $n_{dot0}$  和一變量  $\Delta n_{dot}(t)$  替代，並同樣將導帶中量子點附近的電子密度  $n(t)$  以一個定量值  $n_0$  以及一變量值  $\Delta n(t)$  取代之，如式子(2.16)、(2.17)所示。將(2.16)、(2.17)式代入(2.14)式中並忽略掉高次項便可得到(2.18)式。

$$n_{dot}(t) = n_{dot0} + \Delta n_{dot}(t) \quad (2.16)$$

$$n(t) = n_0 + \Delta n(t) \quad (2.17)$$

$$\frac{\partial n_{dot}(t)}{\partial t} = \sigma_n \bar{v}_n n_0 \left[ \frac{(N_{dot} - n_{dot0})}{n_0} \Delta n(t) - \frac{N_{dot}}{n_{dot0}} \Delta n_{dot}(t) \right] \quad (2.18)$$

將時間相依弦波訊號考慮進式子中，即以量子點附近的電壓變化量為  $v_{dot}(t)$  之情況代入算式中，可以想像導帶中的電子密度變化  $\Delta n(t)$  可以用式子(2.19)表示之。在式子(2.19)中，如果當  $v_{dot}(t)$  的振幅遠小於  $e/kT$  時便可以用式子(2.20)來近似之。

$$\Delta n(t) = n_0 \left( \exp \left[ \frac{ev_{dot}(t)}{kT} \right] - 1 \right) \quad (2.19)$$

$$\Delta n(t) \approx -n_0 \left[ \frac{ev_{dot}(t)}{kT} \right] \quad (2.20)$$

將式子(2.20)代入式子(2.18)中並以式子(2.13)取代其中的  $v_{dot}(t)$ ，並假設量子點內的累積電荷隨頻率之變化量如式子(2.21)所示，便可求得以  $v(t)$  的型式表示的  $\Delta n_{dot}(t)$  之解。

$$\Delta n_{dot}(t) = \frac{\alpha \epsilon_0 f_0}{e \lambda} \frac{v(t)}{i 2 \pi f + f_0 \left( \frac{L}{\lambda} + \frac{N_{dot}}{n_{dot0}} \right)} \quad (2.21)$$

還記得式子(2.12)中，將電流  $I$  分成由空乏區寬度變化所貢獻的  $I_w$  以及量子點內部累積電荷變化量所造成的  $I_{dot}$  這兩部份。以及之前所提到的所謂負微分電容就是量子點內部電子隨頻率之動態行為變化，再藉由前面算式中對  $\Delta W(t)$  和  $\Delta n_{dot}(t)$  所得的數學方程式。便可以將式子(2.12)表示成如式子(2.22)的型式。

$$\frac{I(t)}{v(t)} = G(f) + i2\pi f C(f) \quad (2.22)$$

因此最後便可將式子(2.12)整理成如下式(2.23)來獲取對負微分電容而言，不可或缺的電容和頻率的關係式。

$$C(f) = \frac{\varepsilon_0}{4\pi^2 \lambda} \left(1 - \frac{L_{dot}}{W}\right) \frac{f_0^2 \left( \frac{L_{dot}}{\lambda} + \frac{N_{dot}}{n_{dot0}} \right)}{f^2 + \frac{f_0^2}{4\pi^2} \left( \frac{L_{dot}}{\lambda} + \frac{N_{dot}}{n_{dot0}} \right)^2} + \frac{\varepsilon_0}{W} \quad (2.23)$$

在式子(2.23)中  $f_0 = \sigma_n \bar{v}_n n_0$ ，而  $\lambda^{-1} = e^2 N_{dot0} / kT \varepsilon_0 (1 - L/W)(1 - n_{dot0}/N_{dot0})$ 。因

此只要知道元件穩態狀況下之資訊，就可以利用式子(2.23)來獲得我們所需要的電容和頻率的關係下之值。甚至可以獲得元件中在特定出現負微分電容現象之偏壓下，量子點對電荷的捕捉速率  $f_0$ 。對  $f_0$  之計算首先要在 C-V 曲線下將電壓固定於 NDC 出現電容峰值處，並將不同頻率影響下之峰值電容和頻率關係作圖。並將(2.23)式簡化成如(2.24)式。最後利用 Fitting 所得之 A、B、C 三項數值，就可以求得所需知曉量子點對電荷的捕捉速率  $f_0$  之值。

$$C(f) = A + B / (f^2 + C) \quad (2.24)$$

其中  $A = \varepsilon_0 / W$ 、 $B = \frac{\varepsilon_0}{4\pi^2 \lambda} \left(1 - \frac{L_{dot}}{W}\right) f_0^2 \left( \frac{L_{dot}}{\lambda} + \frac{N_{dot}}{n_{dot0}} \right)$ 、 $C = \frac{f_0^2}{4\pi^2} \left( \frac{L_{dot}}{\lambda} + \frac{N_{dot}}{n_{dot0}} \right)^2$ 。

# Chapter 3

## 元件製作與量測系統

本章節主要介紹實驗中所使用到的兩項元件製程的內容。其一就是利用金屬-半導體的蕭基二極體製程。其次是場效電晶體製程。最後則是簡介實驗中所使用到的量測系統包含光激發螢光系統、室溫電性量測系統以及可變溫環境之電性量測系統三項。

### 3.1 蕭基二極體元件製程

本實驗目的在於用有摻雜的  $n^+$ -GaAs 基底上以分子束磊晶 (Molecular beam epitaxy、MBE) 成長出所需量子點結構。目前在此實驗中採用之結構有樣品 A-Lm3677、樣品 B-Lm3368。其結構如圖 3.1(a)、(b) 所示。樣品 A 之磊晶結構為三層之  $In_{0.15}Ga_{0.85}As$  /  $InAs$  /  $In_{0.15}Ga_{0.85}As$  量子井結構，而層與層之間以厚度 50 奈米之 GaAs 作為間隔。而樣品 B 則是無量子點層之相似結構。樣品 A 量子點層之磊晶條件如下:  $520^\circ\text{C}$ 、 $0.033 \text{ ML/sec.}$ 、砷通量  $\text{As}_2 = 1.5(\text{E}-5) \text{ torr}$  以及量子點的面積密度約為  $1(\text{E}+10) \text{ cm}^2$ 。

圖 3.1、(a)樣品 A 結構圖。(b)樣品 B 結構圖。

### 3.1.1 光罩設計

蕭基二極體製程最主要的部份就是樣品正反兩面的金屬電極之製作。由於背電極在之後的量測系統中要和 LCC 板整面結合，因此無需特別設計光罩。所以在蕭基二極體製程中唯一的光罩使用便是表面閘極之設計，其主要圖案為長  $480\mu\text{m}$  和寬  $325\mu\text{m}$  的長方型圖案，且每一個長方型圖案之間隔為  $100\mu\text{m}$ 。

### 3.1.2 製程步驟

製程主要可區分為以下三個步驟，包括(1)樣品的清洗。(2)表面金屬閘極之顯影沉積。(3)背面銅焊膜。以下將會詳細敘述蕭基二極體製程上，主要五道製程步驟以及每一道的製程條件和所需注意的事項。

#### (一) 晶圓樣品清洗

由於蕭基二極體並沒有蝕刻的製程步驟，所謂的金屬接觸也就是直接在樣品表面上沉積金屬形成電極，因此在製程中對樣品表面的潔淨度要求較高，任何灰塵微粒或有機物的存在，都可能造成金屬電極的接觸不良，影響後續之電極量測。常用晶圓清洗的方式為先將樣品放置到丙酮內來清除表面地有機物，接著以 D. I. Water 清洗殘餘丙酮溶劑並利用氮氣槍吹乾樣品後，將樣品放入烤箱中做預烤的動作，時間約二至三分鐘，最後將樣品放置於室溫下回溫就可以使用了。

#### (二) 樣品正面閘極顯影

使用 AZ-5214E 當負光阻來進行顯影，首先將清洗完的樣品放入旋轉塗佈機中以 1000 轉 10 秒、6100 轉 45 秒兩階段轉速完成光阻覆蓋，接著以  $90^\circ\text{C}$  Hot Plate 軟烤 30 秒，並以 ACE 和刷子去除邊緣光阻後再軟烤 60 秒。用 DUV 曝光 2.5 秒後，放置入  $120^\circ\text{C}$  烤箱中反轉烤約 2 分鐘後，再放到室溫下回溫約 1~3 分鐘，接著以 DUV 全曝 14 秒後就可以用 FHD-5 顯影。顯影時間以肉眼觀察為準一般而言約  $25\sim30$  秒，最後以 D. I. Water 清洗和  $\text{N}_2$  吹乾後，便可用顯微鏡觀察光阻上的轉移圖型。如最後出來的轉移圖型

的誤差在可接受的範圍內，則進行下一道『表面閘極金屬沉積』製程程序，反之則再次進行『晶圓清洗』和重複『正面閘極顯影』製程。

### (三) 閘極金屬沉積

為了避免在『樣品正面閘極顯影』製程後，因為肉眼看不到的殘餘光阻影響到之後金屬和樣品表面的接觸，會先使用  $100^{\circ}\text{C}$  的 UV Ozone 進行兩分鐘的清潔殘餘光阻程序，接著以  $(\text{HCl} : \text{H}_2\text{O}) = (1 : 10)$  的 Dip 溶液去除樣品表面生成之氧化物後，再以 D. I. Water 清洗和  $\text{N}_2$  吹乾後便可置入 E-Gun 中進行閘極( $\text{Ti}/\text{Au} = (20/300\text{ nm})$ )金屬沉積。比較要注意的是如鍍金屬時，腔體內溫度太高會使之後 lift-off 變得困難，所以一般而言，不會使腔體溫度高過  $60^{\circ}\text{C}$ 。鍍完金屬後便可將樣品放入丙酮中進行 lift-off 去除覆蓋光阻後，最後再以 D. I. Water 清洗和  $\text{N}_2$  吹乾。

### (四) 背面銻焊膜

由於樣品的基底是  $n^+ \text{-GaAs}$ ，因此只需在樣品的背面製作歐姆金屬後便可進行量測，在此使用銻當背電極金屬。主要的作法是利用焊槍熔銻線後，將其均勻地塗佈在樣品背面，比較要注意的地方在於焊槍槍頭之潔淨度，會影響到熔銻線以及將銻塗佈到樣品背面的難易度。此外也要避免以手碰觸銻線，因為油脂轉移到銻線後也同樣會增加此道製程的難易度。

### (五) LCC 接觸

在上述背面銻焊膜製程中已提到，銻焊膜的不平坦度會影響到量測結果，再考慮到低溫量測系統的架設結構，因此在 LCC 基板和樣品背電極的接觸中，同樣以金屬銻來當作接觸媒介。做法是先將銻線壓成足以覆蓋樣品但小於 LCC 板面積的薄膜，將此銻薄膜放置於 LCC 板和樣品背面之間，利用  $100^{\circ}\text{C}$  烤箱高溫溶融銻使其內聚，這樣不但可以緊實地將樣品和 LCC 板連結在一起，還能製造出更為平滑的背面銻電極，接著利用鎢線機將樣品閘極和背電極以金線連結到 LCC 板內部接點上，便可放入低溫量測系統中進行量測。

### 3.2 場效電晶體元件製程

由於本實驗是想利用鄰近二維電子氣之量子點，藉由閘極偏壓的改變來使量子點捕捉或釋放二維電子氣中的電荷，並藉由電流-電壓曲線和電容-電壓曲線之改變來觀察量子點的充放電特性。為了達到實驗目的，在 S. I. GaAs 晶圓上利用分子束磊晶成長實驗所需要之結構。長晶的結構主要可分為三個部份，(1) InAs 在 GaAs 夾層間所形成的量子點。(2) GaAs 和  $Al_xGa_{1-x}As$  的異質接面所形成的二維電子氣通道。(3)  $n^+$  摻雜的  $Al_xGa_{1-x}As$  層來提供主要的載子。實驗中所用到的樣品又可以區分為量子點層位於二維電子氣之上結構的樣品 C-Rn0632 以及量子點層在二維電子氣之下結構的樣品 E-Lm5264 這兩種主要結構，加上相同結構下無量子點層之對照樣品 D-Rn0633、樣品 F-Lm5266 等共計四個樣品。圖 3.2 與圖 3.3 展示此四種樣品的結構參數。樣品 C 結構中包含 200 nm GaAs 緩衝層、300 nm  $Al_{0.33}Ga_{0.67}As$ 、40 nm 砷摻雜為  $2(E+18) cm^{-3}$   $Al_{0.33}Ga_{0.67}As$ 、10 nm  $Al_{0.33}Ga_{0.67}As$ 、20 nm GaAs、InAs 量子點層以及 80 nm GaAs。而樣品 E 結構則包含 200 nm GaAs 緩衝層、InAs 量子點層、20 nm GaAs、20 nm  $Al_{0.33}Ga_{0.67}As$ 、40 nm 砷摻雜為  $2E10^{18} cm^{-3}$   $Al_{0.33}Ga_{0.67}As$  以及 10 nm GaAs。樣品 C、E 量子點層磊晶條件為  $533^{\circ}C$ 、0.056 ML/sec.、砷通量  $As_2 = 7.1(E-6)$  torr。

圖 3.2、樣品磊晶結構圖(a)樣品 C、(b)樣品 D。

圖 3.3、樣品磊晶結構圖(a)樣品 E、(b)樣品 F。

### 3.2.1 光罩設計

場效電晶體的製程光罩有三道，分別為(1)：Mesa 光罩。(2)：源極/汲極光罩。(3)：閘極光罩。Mesa 光罩為一個長  $1600\ \mu\text{m}$  和寬  $100\ \mu\text{m}$  的長方形圖案，如圖 3.4(a)所示。第二道光罩源極/汲極光罩則如圖 3.4(b)所示，以長  $180\ \mu\text{m}$ 、寬  $160\ \mu\text{m}$  的長方形放置在 Mesa 側面做外接的觸點，而在 Mesa 上則分別以  $180\ \mu\text{m}$ 、 $120\ \mu\text{m}$ 、 $80\ \mu\text{m}$ 、 $30\ \mu\text{m}$ 、 $20\ \mu\text{m}$ 、 $12\ \mu\text{m}$ 、 $8\ \mu\text{m}$  的距離間隔，來當之後不同閘極長度的區域元件。最後一道閘極光罩如圖 3.4(c)所示，則是以長  $200\ \mu\text{m}$ 、寬  $190\ \mu\text{m}$  的長方形做外接的接觸點，而其閘極長度分別為  $160\ \mu\text{m}$ 、 $100\ \mu\text{m}$ 、 $60\ \mu\text{m}$ 、 $16\ \mu\text{m}$ 、 $8\ \mu\text{m}$ 、 $4\ \mu\text{m}$ 、 $2\ \mu\text{m}$ 。

圖 3.4、場效電晶體所使用的三道光罩圖案。

(a)Mesa 光罩。(b)源/汲極光罩。(c)閘極光罩。

### 3.2.2 製程步驟

對於場效電晶體的製程，主要也分為三個部份，(1)Mesa 蝕刻。(2)源極/汲極顯影沉積。(3)閘極顯影沉積。以下將會詳細敘述場效電晶體製程中四道步驟和製程條件。

#### (一) 製程前準備工作

由於所使用的光罩中，閘極長度範圍從  $160\text{ }\mu\text{m}$  至  $2\text{ }\mu\text{m}$ ，因此相較於蕭基二極體製程而言更需做好一些製程前的準備工作，來減少外加因素對製程的干擾，包括以下幾點：

- (1)清洗容器：採用的作法是先以 D. I. Water 沖洗容器約五分鐘，接著以氮氣槍吹散出大部份的水份，再將容器放置入烤箱之中蒸乾殘餘的水份，最後將容器放置在室溫下回溫後便可以使用了。

- (2)晶圓清洗：其程序同蕭基二極體晶圓清洗步驟。

(3) 蝕刻液配製：蝕刻溶液配製比例為硫酸：雙氧水：水=(1：8：80)的比例混合。由於蝕刻溶液的均勻性會嚴重影響到對樣品的蝕刻速率，為了能夠確認樣品蝕刻的深度，在製程開始前六十分鐘便配製溶液，讓蝕刻溶液有足夠的時間去反應。最後在蝕刻前再以攪拌棒攪拌後，便可開始進行蝕刻速率的測試。

## (二) Mesa 蝕刻

使用正光阻(AZ 6112)將前置作業中已清洗完的樣品，以兩段轉速 1000 轉 10 秒、4500 轉 25 秒來塗佈光阻。之後以 90°C 的 Hot Plate 完成軟烤和去邊光程序，回溫後以經過測試得到之曝光時間 2.5 秒曝光，接著顯影、定影、吹乾後，以顯微鏡檢視圖案之線寬和邊緣，便可將樣品置入蝕刻溶液(硫酸：雙氧水：水)=(3ml：24ml：240ml)中進行蝕刻，蝕刻速率約每秒 9 nm，樣品 C、D 蝕刻的深度約 100 nm 以上，而樣品 E、F 蝕刻的深度約 70 nm 以上。最後將蝕刻後之樣品放入薄膜測厚儀中，以固定方式抽取元件來量測實際蝕刻深度。如不符則再進行蝕刻的動作，如符合所需蝕刻深度，則同樣重複『清洗晶圓』步驟來移除殘存光阻。

## (三) 源極/汲極製程

將光阻 AZ 5214E 以兩階段轉速 1000 轉 10 秒、6100 轉 45 秒來完成光阻之塗佈，接著同以 90°C 之 Hot Plate 完成軟烤和去邊光後，以 DUV 進行第一階段曝光，時間為 2.5 秒，接著以 120°C 烤箱中做反轉烤約兩分鐘，回溫後便可進行全面性的反轉曝光，曝光時間 14 秒，最後顯影定影吹乾後就可以放置在顯微鏡上進行檢視後完成。在鍍金屬電極前，同樣以 100°C 的 UV Ozone 進行兩分鐘的清潔殘餘光阻程序後，以 Dip 溶液清除表面生成氧化物，就進 E-Gun 中鍍 N-Type 金屬(Ni/Ge/Au)=(30/50/200 nm)。接著則進行 lift-off 和以 D. I. Water 清洗、N<sub>2</sub>吹乾便可進行下一道退火製程了。退火的主要目的在於將源極/汲極金屬和樣品表面之接觸從蕭基接觸變為歐姆接觸，退火條件如下：在通氮氣與氬氣的環境下，395°C-35 秒。

#### (四) 閘極製程

閘極顯影之製程步驟其實和源極/汲極顯影步驟十分相似，同樣採用反轉 AZ 5214E 光阻的製程，因此將不再重述閘極顯影的流程內容。比較要特別注意的是邊緣光阻影響對準的問題，此問題雖說在其它製程也會發生，但由於閘極線寬僅有  $2\mu\text{m}$  的小線寬，且此線寬和源極/汲極間隔只相距  $1\mu\text{m}$ ，因此四周殘餘邊緣光阻在樣品和光罩接觸時，即便只產生微小的偏斜也會使閘極碰觸到源極或汲極，進而造成元件失效。金屬沉積部份，同源極/汲極金屬沉積製程流程，首先將做完閘極顯影的樣品進行 UV Ozone 與(HCl :  $\text{H}_2\text{O} = (1 : 10)$ )之溶液 Dip 後，放進 E-Gun 中，蒸鍍金屬(  $\text{Ti}/\text{Au} = 20/200\text{ nm}$  )。鍍完金屬後再 lift-off 移除不需要光阻和金屬的區域，再以 D. I Water 清洗殘餘丙酮並以  $\text{N}_2$  吹乾樣品便完成了我們場效電晶體元件製程了。

### 3.3 量測系統

這個章節主要是在介紹實驗中主要用到的三個量測系統的架設，其中包含(1)光激螢光量測系統。(2)室溫環境下電性量測系統。(3)可變溫環境下之電性量測系統。以下將各別詳述此三項量測系統。

#### 3.3.1 光激發螢光量測系統

藉由光激發螢光量測系統分析光激發螢光之資料，可得知樣品量子點層之情況。因此在每一片樣品磊晶結構完成後，都會先使用 PL 系統去確認量子點磊晶結果，再去進行蕭基二極體或場效電晶體製程。簡易來說所謂的螢光就是物質接收能量後放出電磁輻射的一種機制。故光激發螢光系統，是將一道能量大於材料能隙之雷射光入射於樣品表面之上。對本研究中使用的實驗樣品而言，GaAs 層會在吸收了此入射光源的能量後，激發價電帶中的電子躍遷到導電帶之中，並在價電帶中遺留下一電洞，形成了電子-電洞對，但此時的狀態並不穩定，因此當趨近於熱平衡時，導電帶中的激發電子必會順著最小能隙，即量子點層掉回到價電帶之中，期間也將以光子或聲子之方式釋放出能量，如圖 3.5 所示。最後藉由觀察樣品激發後所發出特定波長強度便可判定量子點的磊晶結果 [26~32]。

圖 3.5、光激螢光量測發光機制。

圖 3.6、光激發螢光量測系統示意圖。

本實驗室的光激發螢光系統架構如圖 3.6 所示，一開始利用波長為 488 nm 的氦氖雷射來當激發樣品之光源，並先藉由衰減片 1、2 來調降雷射之出光功率，接著以 Mirror-1、Mirror-2 來改變雷射行進之方向使整體光激發螢光量測系統能更符合在有限面積之光學桌上的布置。並利用對焦片-1、對焦片-2 上可開閉之圓孔來精確操控雷射行進之方向，以便我們能更有效率地將雷射光入射到小面積的反射鏡上，此小面積的反射鏡會將雷射反射到樣品上去激發樣品光出來。在此其間利用 Chopper 擋除如日光燈之雜訊以提高訊雜比以及積分球去量測入射至樣品之雷射功率之大小。再來利用 Focal lens-1、2 來聚焦樣品光以及雷射濾光片讓樣品光成為唯一進入分光儀之光源，最後利用偵測波長為 1~1.5  $\mu\text{m}$  的 InGaAs detector 以及將電流訊號轉為電壓訊號的 Lock-in amplifier，就可以在電腦上觀看到量子點之發光波長以及強度。

### 3.3.2 室溫環境下之電性量測系統

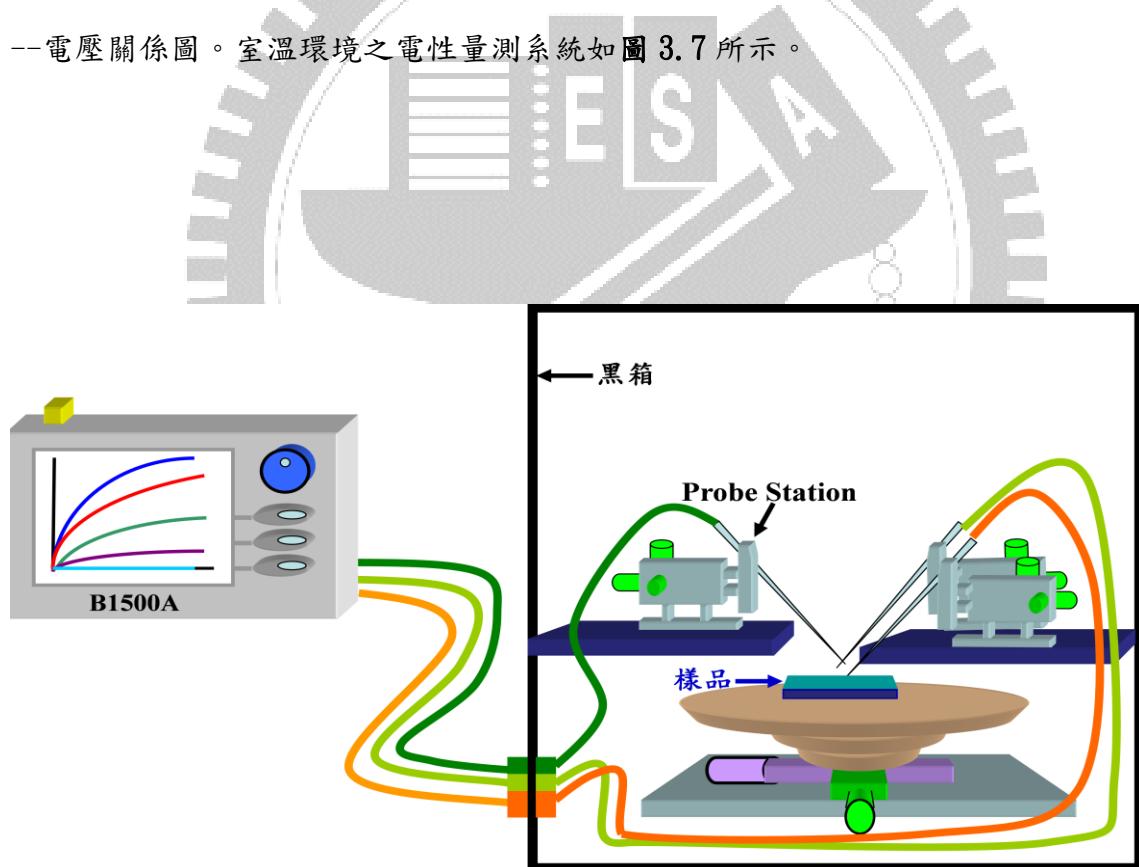

實驗中對於電性量測都採用 Agilent B1500A 當作實驗電源供應器及量測機台，此機台在電流-電壓量測中，提供了 $\pm 200$  V 之功率電源 SMU1、SMU2 以及 $\pm 100$  V 之功率電源 SMU3、SMU4 等四個通道接點。在電容-電壓量測中則提供了 $\pm 25$  V 之直流源，以及 $0\sim 250$  mV 且頻率範圍  $1\text{ k}\sim 5\text{ MHz}$  交流電源之 CMU 接點。量測中使用黑箱來隔絕外界光源的影響，量測方式首先將 Agilent B1500A 之電壓源接到黑箱外殼，再由黑箱內殼之內部接點接線到 probe station 後，便可接探針接觸到樣品電極上進行電性之操控，而樣品對應之電性反應也將反向的從探針回饋到機台 Agilent B1500A 中，最後就可以在 Agilent B1500A 上的螢幕顯示出元件的電性量測結果，如元件電流--電壓關係圖或電容--電壓關係圖。室溫環境之電性量測系統如圖 3.7 所示。

圖 3.7、室溫電性量測系統示意圖。

### 3.3.3 可變溫環境下之電性量測系統

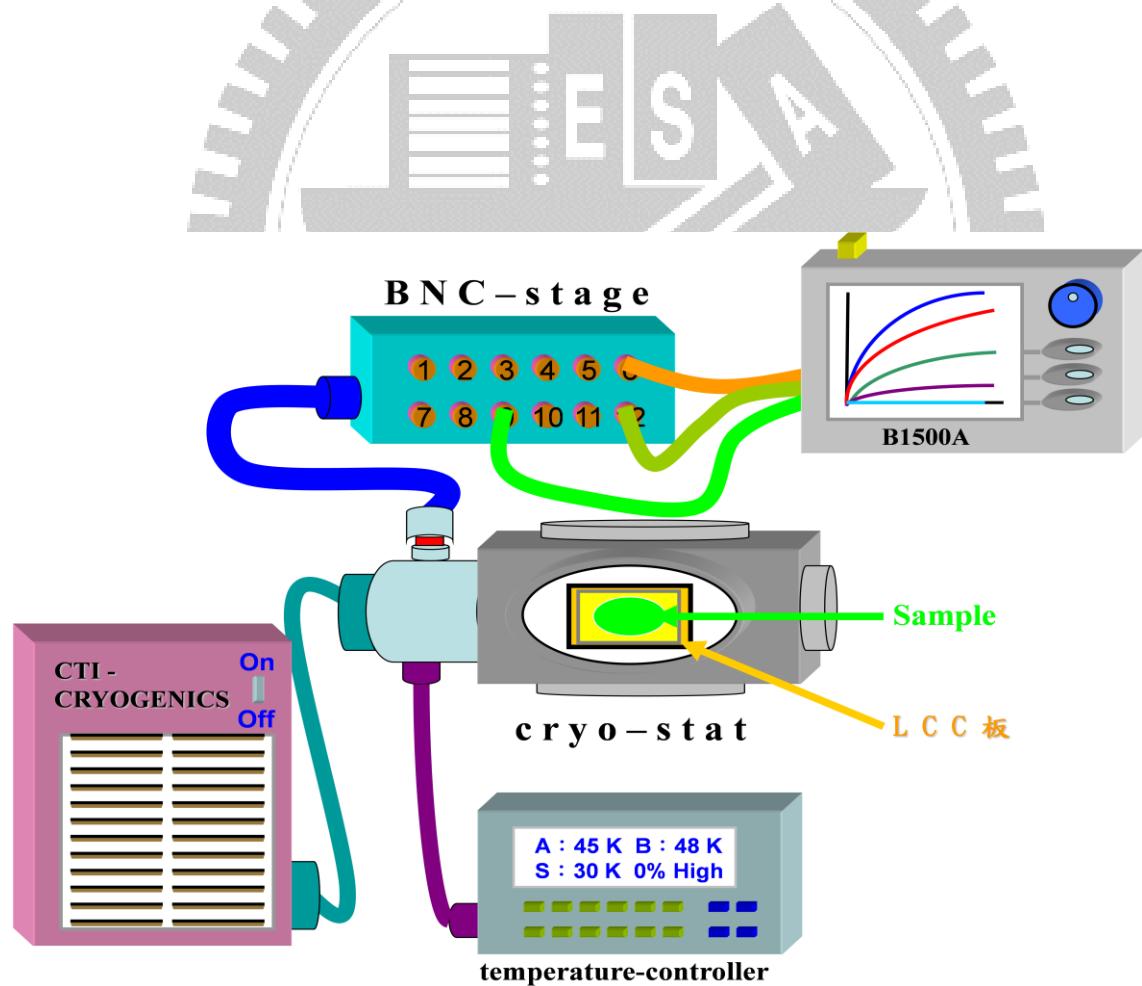

當進行可變溫環境下之電性量測時，都必須先將樣品利用銀膠或熔銅的方式，使樣品和 LCC 板緊密結合。接著再利用鎢線的方式，將樣品表面電極和 LCC 板內之電極以金線連結之。然後就可以將樣品 LCC 板放入 cryo-stat 腔體中抽取真空，並利用 CIT-cryogenics 來降低腔體內的溫度以及使用控溫器(temperature-controller)來控制樣品端之溫度，藉由此兩者間的運作便可以完成可調變溫度的量測環境。LCC 板外的電極可以利用導線連接到 BNC-stage 上，並利用 BNC-stage 上的數字定義所連接到之樣品元件之電極。最後就如同室溫電性量測般利用 B1500A 來當作實驗中之電源供應器及量測機台，就可以對不同環境溫度下之元件電性進行量測，此量測系統如圖 3.8 所示。

圖 3.8、可變溫之環境電性量測系統示意圖。

## 第四章

### 實驗結果與討論

此篇論文在這個章節中將各別針對『蕭基二極體』以及『場效電晶體』這兩部份來說明。在『蕭基二極體』量測部份著重於理解量子點內部之充-放電荷之動態行為所造成之結果，並以改變溫度以及頻率來當作變數去更加詳細地明瞭負微分電容之性質。而在『場效電晶體』實驗與量測部份，則是希望觀察到場效電晶體元件內部量子點造成的臨界電壓偏移所形成之記憶窗口，並利用溫度之變換去推測奈米晶記憶元件的特性，如保存時間、操作次數…等等。

#### 4.1 蕭基二極體元件之實驗結果

就如同 3.1.2 節中所提及的蕭基二極體之製程流程，主要步驟分為清洗、正面閘極金屬電極以及背面銅電極三部份，量測方式則同 3.3 節中所提及的一樣，以光激螢光、室溫與變溫環境下之電性為主。在此採用有量子點層之樣品 A，以及相似結構卻無量子點層之樣品 B 來作比較。因此可以更容易藉由兩個樣品於不同量測環境溫度以及外接訊號源之頻率下，在 I-V 曲線以及 C-V 曲線電性量測中之差異，來辨別出此電性上之差異的起因是否為量子點層所造成之結果。關於樣品 A、樣品 B 之詳細磊晶結構已於 3.1 節中圖 3.1 提及，在此不再贅敘。

#### 4.1.1 蕭基二極體元件之光激螢光頻譜

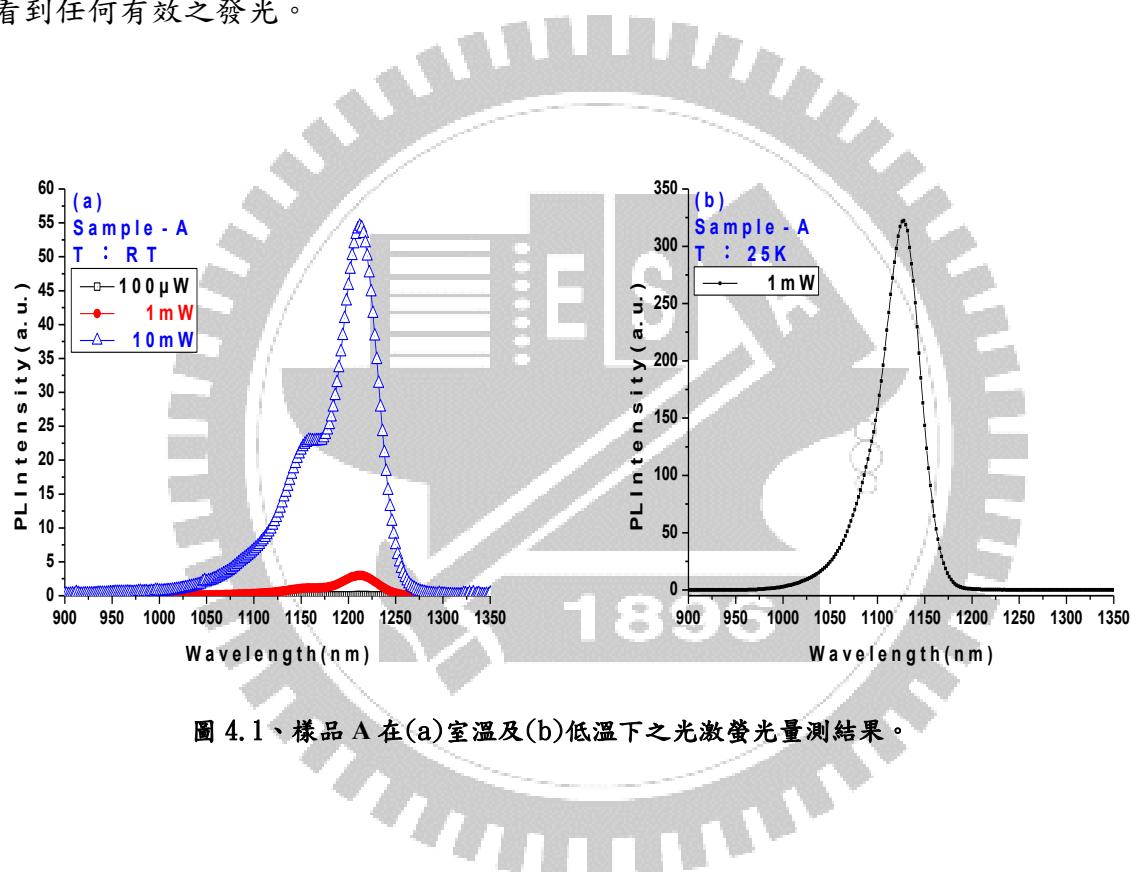

圖 4.1 則是樣品 A 在(a)室溫及(b)低溫環境下光激發螢光量測結果，從(a)中可看出樣品 A 在室溫環境下，於 1212 nm 以及 1158 nm 波長下皆有發光，但當入射雷射光之功率降至 100  $\mu\text{W}$  時就只剩下 1212 nm 處有發光，因此能合理推斷量子點之基態發光於 1212 nm 處，1158 nm 則是量子點中激發態之發光波長，而在(b)低溫環境下，就只剩下 1128nm 處的基態量子點之發光。另外，無量子點之樣品 B 中在此量測波段間，則無法觀看到任何有效之發光。

圖 4.1、樣品 A 在(a)室溫及(b)低溫下之光激螢光量測結果。

#### 4.1.2 蕭基二極體元件之 I-V 量測

本節一開始就先量測樣品 A 之蕭基二極體元件結構，在室溫狀況下之電流-電壓特性。並計算於室溫狀態下之理想因子(ideal factor)  $n$  藉以來觀看閘極之蕭基接觸之良好與否。圖 4.2 秀出樣品 A、樣品 B 在數個溫度下之 I-V 曲線結果。

圖 4.2、樣品 A、B 於 70、90、110、294 K 溫度下的 I-V 曲線結果。

圖 4.2 展示出了樣品 A、樣品 B 在 70 K、90 K、110 K、294 K 下之 I-V 曲線。從圖中可看出樣品 A、樣品 B 在 294 K 時兩者之 I-V 曲線幾乎重疊在一起，而在低溫環境 70 K、90 K、110 K 時，閘極導道後之行為有明顯的差異。閘極之導通電壓會隨著溫度提高而逐漸變小。為了解釋及方便計算蕭基二極體之理想因子，故將電流改以  $\log$  之方式呈現如圖 4.3 所示。

從圖 4.3 中可以觀看出樣品 A、樣品 B 在低溫環境下之電性行為有顯著的差異。從兩樣品的結構上來分析，可以合理地推斷此差異是由量子點層所導致。以 110 K 為例，在低溫環境下時，由於元件內載子數目不足，故量子點層之阻值偏大。而當閘極偏壓增大時，隨著量子點層內之累積電荷提升，其阻值會下降。故出現第一段之斜率。而當量子點層阻值低到可忽略時，元件將呈現理想二極體之 I-V 特性，故出現第二段斜率。第三段斜率則是因為高注入載子下，所形成之非理想特性。反觀樣品 B，因無量子點層之存在，故於低溫環境中呈現一段線性斜率。因此可以合理之推斷樣品 A、樣品 B 於低溫下電性表現之差異導因於量子點層的電性行為。接著利用式子(4.1)、(4.2) 去計算樣品 A、樣品 B 在這四個溫度下理想因子  $n$  之值，其結果如表 4.1 所示。

$$V_2 - V_1 = 2.3nV_T \log \frac{I_2}{I_1} \quad (4.1)$$

$$V_T = \frac{kT}{q} \dots \dots k = 1.38 \times 10^{-23} (J/K) \quad (4.2)$$

圖 4.3、(a)樣品 A。(b)樣品 B 於 70、90、110、294 K 溫度下的(logI)-V 曲線結果。

|        | 70 K | 90 K | 110 K | 294 K |

|--------|------|------|-------|-------|

| 樣品 A n | 2.65 | 2.4  | 1.72  | 1.18  |

| 樣品 B n | 1.57 | 1.41 | 1.25  | 1.08  |

表 4.1、樣品 A、樣品 B 於 70 K、90 K、110 K、294 K 下之理想因子 n 之值。

從表 4.1 中，可以觀看到在室溫(294 K)環境下，無論樣品 A、樣品 B 的理想因子 n 之值都介於 1~2 這合理之範圍內。且可從樣品 A、B 中看出理想因子都會隨著溫度愈低，導致元件內載子數目減少而逐漸抬高。在上述的結果中已觀察了蕭基二極體元件之樣品 A、樣品 B 於 70 K、90 K、110 K、294 K 此四個溫度下之 I-V 量測結果，從中可觀察到在低溫環境下，樣品 A、B 之電性行為影響造成了元件導通後的差異。此外雖說理想因子 n 之值會隨溫度降低而提高，但其值仍在合理值之範圍區間內，因此可相信此次蕭基二極體製程結果。接下來就要進行對 C-V 量測之結果觀察和分析。

#### 4.1.3 蕭基二極體元件之 C-V 電性量測

圖 4.4 (a)、(b)、(c)、(d) 分別代表著樣品 A 和樣品 B 在 70K、91K、110K 以及 294K 的溫度下，對外接弦波信號頻率為 1 kHz、5 kHz、20 kHz 時之電容-電壓曲線圖。從圖中可以明顯看出當量測溫度為 70~110 K 之間時，於樣品 A 中所觀察到的電容之起伏，無論是第一或第二次之起伏都沒有出現在無量子點層的樣品 B 中，因此可以合理地推測樣品 A 在此量測溫度中，由於準費米能階會因閘極電壓提高，而逐漸靠近量子點內之基態能階，造成在 C-V 曲線中第一次之電容起伏。而隨著溫度提高，量子點內能階對電荷捕捉/釋放速率變快，因此能在閘極電壓變高下，同時觀看到量子點層中之基態與激發態能階所造成的第一及第二次之電容隨頻率之起伏。圖 4.4 (d) 則可以看出樣品 A 在室溫環境下所觀測到的電容起伏之現象，也可在樣品 B 之室溫量測中觀看到，因此驗証了室溫環境中的似負微分電容現象，很可能和量子點的電性行為無關。

圖 4.4、樣品 A、B 在(a) 70K、(b) 91K、(c) 110K、(d) 294K，溫度下之 C-V 電性比較。

在圖 4.4 中已經藉由樣品 A、樣品 B 在不同溫度環境下，對不同頻率之電容-電壓曲線圖的比較，觀看到了當樣品 A、樣品 B 處於低溫量測環境下時，在電容反應上有非常明顯之差異。根據兩樣品唯一之差異在於量子點層之存在與否，故可合理推測量子點層乃導致，兩樣品於低溫環境電容差異之主因。為了驗証此推測，將樣品 A 於 70、90、110、294 K 溫度下，所得之 C-V 與 I-V 曲線圖結合在一起觀看，如圖 4.5 所示

圖 4.5、樣品 A 在(a) : 70 K、(b) : 90 K、(c) : 110 K、(d) : 294 K、下 C-V 及 I-V 曲線結合圖。

從圖 4.4 中可看出在樣品 A 中，當外接訊號源之測試頻率為 1 kHz 時，能在四個溫度下，都觀看到顯著的電容效應。因此在圖 4.5 中，只取 1 kHz 下之 C-V 曲線來觀察便足夠。圖 4.5(a)中可觀察到當溫度於 70 K 時，在元件閘極未導通前就有電容隨電壓之第一次起伏變化。而當溫度提升到 90 K 以及 110 K 時，電容開始隨電壓之變化出現第一及第二次之電容起伏，如圖 4.5(b)、(c)所示。而當溫度提昇至 294 K，可以明顯看到電容隨電壓改變之變化量主要出現在元件導通之後，如圖 4.5(d)所示。

在圖 4.5(d)中，由於所觀測到的電容起伏是當元件閘極導通後所產生。但當元件閘極導通時，電流途徑會影響到量子點內部的電荷存放，因此在理論上不太可能觀看的到量子點的效應，另一個認為在 294 K 環境下的起伏不是 NDC 的主要原因就是它並沒有負斜率的趨勢，反而比較像是在累積某缺陷內的電荷後又往上飆升，所以樣品 A 在室溫環境下觀察到的似 NDC 的現象比較可能的原因是其它元件內部的缺陷充放電荷所造成的。合理的推測是有其它元件上的缺陷也在室溫時參與了此電容的反應。簡而言之，到目前為止已經可以確信能在低溫環境下在樣品 A 中，觀測到量子點層對電荷捕捉與釋放行為所導致的電容起伏結果。為了更清楚理解這個現象，我們將在 70 K 以至 130 K 之間改以每 5 K 之溫度變化以及更多的弦波信號頻率去觀看樣品 A 的負微分電容現象，如圖 4.6 所示。

在圖 4.6 中，秀出了在各別在 70、77、82、91、100、110 K 溫度環境，外接信號源頻率分別為 1、5、10、20、50、100、200、400 kHz 下之蕭基二極體元件電容-電壓關係圖。為了能更清晰觀看頻率間之電容差異，圖 4.6 中，將在高頻率(600 kHz)弦波信號下所量測之電容值當作背景雜訊，並將所有不同頻率下所量測之電容值減去高頻下之背景雜訊後，所得之結果圖。

圖 4.6、樣品 A 在中溫度下的 C-V 曲線(70 K、77 K、82 K、91 K、100 K、110 K)。

圖 4.6 中可觀察到幾個較特殊的現象，如當溫度在 70 K 時可第一次觀看到由量子點層所引起，隨著頻率差異所導致較為明顯的電容差異起伏。而到了 77 K 時，則可在 1 kHz 的頻率下觀看到第二次電容起伏之出現。在 82 K 溫度環境時，可分別在 1 kHz 以及 5 kHz 頻率下看到第二次電容起伏，且在 1 kHz 頻率下第一次明顯觀看到元件負微分電容的現象。當溫度到達 91 K 時，可在 5、10、20 kHz 頻率下都觀看到負微分電容現象。而當溫度到達 100 K 時，可發現第一次電容之起伏，即便當外接訊號頻率高到 400 kHz 下也未消失。當溫度到達 110 K 時，則可觀察到第二次之電容起伏也似乎不隨頻率增高而消失。

從圖 4.6 中可以觀察到樣品 A，從 82 K 開始就可於低頻情況下，觀看到負微分電容的現象，而隨著溫度提昇 NDC 消失的頻率也似乎緩慢地提高了。而在 82 K 到 110 K 這個溫度區間中，也可以觀察到負微分電容愈來愈明顯。但當溫度高過 110 K 後即便外加弦波信號的頻率高到了 1 MHz 也消除不了 NDC 的存在，此外由於元件閘極的導通電壓，會隨溫度提高而降低，因此限縮了觀看元件內部量子點或其它結構之電荷累積行為，所導致的電容改變，其可以反應之電壓空間，此現象導致第二次電容起伏以及元件導通後之電容起伏逐漸隨溫度結合在一起。總結到目前為止，根據對樣品 A 以及無量子點層之樣品 B 在蕭基製程的量測結果比較中，可確信在溫度區間(70~110 K)下所觀察到之電容起伏都來自於量子點層之影響。

圖 4.6 中，當溫度為 100 K 與 110 K 下，可觀察到第一與第二次電容起伏間之電壓差距約 0.5 V。為了解釋此現象之成因，使用單量子點層之基態與激發態能階之模型，如圖 4.7 所示，並用結構中不同量子點層與表面閘極之間距去計算。根據樣品 A 之 PL 量測結果，可知基態與激發態之發光波長分別為 1212 nm 與 1158 nm，利用式子(4.3)，就可計算出基態與激發態之間的能階差  $\Delta E = 0.0477\text{eV}$ 。

$$\lambda(\mu\text{m}) \approx \frac{1.24}{E_g} \quad (4.3)$$

圖 4.7、樣品 A 之單量子點層基態與激發態能階模型。

其中假設電場均勻地分佈在整個空乏層寬度 655 nm 內，故可計算當閘極與量子點層之距離分別為 53、110、163 nm 下之電場，約佔全部電場強度的 7.97%、16.5%、24.5%。在此情況之下，如要將準費米能階由基態移至激發態時，所需要外加之電壓差分別為 0.598 V、0.289 V、0.195 V。故可推測圖 4.6 中，所觀測到的第一次與第二次之電容起伏之現象，是由樣品 A 結構中較靠近閘極之量子點層，其內部基態與激發態能階對電荷之捕捉與釋放行為所造成之結果。至於另外兩層之量子點訊號，在量測資料的計算下，則可發現，此兩層量子點內之基態能階訊號會和較靠近閘極之量子點基態能階訊號重疊，而此兩層之激發態能階之訊號則會互相影響抵消，故無法在電容-電壓曲線圖上作出區分。

既然已經確認了在此次製程樣品 A 中，由量子點所引起的 NDC 現象其出現的區間電壓和溫度，接下來就是利用式子(2.24)去 fitting 在不同溫度環境，固定電壓的情況下電容對頻率作圖所得之曲線。並藉由所得之常數 A、B、C 來理解其物理意義和成因。關於所使用的 fitting 方式將以圖 4.8 來解說。

圖 4.8、樣品 A 在 91 K 下(a)電容-電壓圖、(b)0.15 V 下電容-頻率圖、

(c)0.65 V 下電容-頻率圖、(d)參數 A、(e)參數 B、(f)參數 C。

圖 4.8(a)秀出溫度在 91 K 下之 C-V 曲線圖，在圖上標記了閘極電壓為 0.15、0.65 V 下之兩條 fitting 的實線箭頭，以及閘極偏壓為 0~0.35 V 之區間 1 和 0.6~0.75 V 之區間 2。當要取 fitting 參數 A、B、C 時，把定電壓下不同頻率時之電容值取出，作電容和頻率的關係圖，如圖 4.8(b)、(c)分別表示當閘極電壓為 0.15、0.65 V 下的電容和頻率之關係圖，利用式子  $A+B/(f^2+C)$  去 fitting 曲線，便可得到當下電壓之參數 A、B、C。最後將同溫度之不同閘極偏壓所得之參數 A、B、C 整合在一起，就可得到圖 4.8(d)、(e)、(f)。從圖 4.8(d)中觀看到參數 A 有兩次明顯的起伏，分別就在 0~0.35 V 之區間 1 和 0.6~0.75 V 之區間 2，如對應到圖 4.8(a)可發現此起伏和量子點層內之基態與激發態能階所導致的電容起伏處一致，且由於參數 A 為  $\alpha\epsilon_0/W$ 。故最後可推斷參數 A 之起伏，是由於量子點內基態與激發態能階在累積電荷下，所導致的空乏區寬度縮減之結果。而從圖 4.8(e)、(f)中，也可發現參數 B、C 之起伏也對應到量子點內之基態與激發態能階對電荷之行為。最後則是可以利用參數 C 去計算出量子點內能階對電荷之捕捉與釋放速率  $f_0$ 。此外在實驗中對參數 A 的 fitting 之誤差約 1%，參數 B、C 的誤差則約 10%。

以下討論將針對溫度為 70 K、77 K、82 K、91 K、100 K、110 K、120 K 此七個溫度環境且定電壓為 -0.1 V、0.0 V、0.05 V、0.1 V、0.15 V、0.2 V、0.25 V、0.3 V、0.35 V、0.4 V、0.45 V、0.5 V、0.6 V、0.65 V、0.7 V、0.75 V 等十六個電壓下的電容隨頻率之變化所形成的曲線去分析。其所得之參數 A、B、C 之結果如圖 4.9 所示。圖 4.9 中分別將不同溫度下之參數 A、參數 B、參數 C 之改變去做比較。由於  $A=\alpha\epsilon_0/W$  所以從圖 4.9(a)中可看出空乏寬度 W 會隨溫度提高而產生縮減，且縮減之次數也會隨溫度上升，從一次變為二次，正好對應到量子點層基態與激發態能階充放電荷下，所造成之空乏寬度之改變，而 W 開始改變之電壓點也隨溫度的提高而向負偏壓移動。圖 4.9(b)、(c)中則可發現參數 B、C 和電壓相依之曲線會隨著溫度的提升而慢慢從一個起伏變為兩個起伏，且起伏出現的位置和參數 A 的起伏一樣，也就是由量子點層內之基態與激發態能階對電荷之行為，所造成空乏層與累積電荷改變之整體影響的結果。

圖 4.9、樣品 A 在不同溫度影響下(a)參數 A。(b)參數 B。(c)參數 C 之改變。

在前面已分析了參數 A、B、C 彼此間的影響和隨溫度之改變情況。但還缺少了 NDC 現象中最重要之參數，對電荷捕捉率  $f_0$  的探討。對於  $f_0$  之計算只要利用式子(4.4)和所得的參數 C 之值便可求出。由於峰值電容會發生在量子點內能階半滿的情況之下，因此  $N_{dot}/n_{dot0} \approx 2$ ，而計算出來的  $\lambda$  約為  $L_{dot}$  的一百倍。故最後能整理成式子(4.5)。圖 4.10 分別表述在七個各別溫度下，不同電壓的捕捉率  $f_0$  之變化趨勢。

$$C = \frac{f_0^2}{4\pi^2} \left( \frac{L_{dot}}{\lambda} + \frac{N_{dot}}{n_{dot0}} \right)^2 \quad (4.4)$$

$$f_0^2 = \pi^2 C_{peak} \quad (4.5)$$

圖 4.10、 $f_0$  在不同溫度環境下，隨電壓變化之趨勢圖。

從圖 4.10 中可觀察到當出現兩次起伏的情況時，兩者之間對電荷的捕捉率  $f_0$  之值有著小許之差異。故符合前述中推測，兩次之電容起伏分別是由量子點層內基態與激發態能階，對電荷之充放電所造成之結果，因此  $f_0$  之值會有差異。圖 4.11 比較電荷捕捉率  $f_0$  和溫度的關係。

圖 4.11、溫度和電荷捕捉率  $f_0$  之關係。

在作圖 4.11 時並不是選取固定電壓的情況下去做比較，但仍可以觀察到元件中對電荷的捕捉率仍會呈現隨溫度上升而提高的情況，這樣的結果也符合在圖 4.6 中所觀看的現象一致。此外如將兩個  $f_0$  之數值和圖 4.6 做比較，可發現在出現第一個峰值  $f_0$  之電容其消失頻率大於所求  $f_0$  之值，而第二個峰值  $f_0$  其值和電容起伏的消失頻率相近，其原因在於兩個  $f_0$  的成因，分別為量子點內之基態與激發態能階對電荷之捕捉/釋放行為。而當溫度為 110K 時，對第二次電容起伏所求出的  $f_0$  之值為 494 kHz，但實際上此電容起伏並沒有在當頻率為 600 kHz 時消失，造成此一現象的原因在於，對  $f_0$  的計算是著重於量子點內部離散能階之間的捕捉及釋放電荷的速率，但當溫度高於 110K 之後，在實驗上已經無法去觀看量子點內累積電荷之改變，因此在溫度大於 110K 之情況下，拿式子(2.24)去計算電荷捕捉率  $f_0$  當然會造成誤差。同理在這裡我們可以再次地驗証到兩個峰值  $f_0$  的成因是完全不同的。第一個電荷捕捉率  $f_0$  主要是由層量子點內基態能階被電荷填入後所造成的空乏層寬度之顯著縮減所造成的結果，而第二個電荷捕捉率  $f_0$  則是由量子點內之激發態能階所貢獻之結果。

#### 4.1.4 實驗結果與討論

在對樣品 A 與樣品 B 的 I-V 量測中，發現了在低溫環境(70~110 K)下，有無量子點之蕭基二極體元件，其導通後之電性行為上有明顯之差異。藉由將電流改以  $\log$  方式呈現下之 I-V 曲線，可看到於低溫環境時，具量子點之元件其導通後的汲極電流會有三段之斜率與理想因子  $n$  值。故推測原因在於當量測環境溫度偏低時，量子點層內之載子數目不足故使量子點層如電阻般存在，當量子點內累積電荷隨偏壓而提升時，會使電阻值偏小而產生第一段導通斜率，而當電阻值低到可忽略時，又回復成理想二極體之電性而呈現第二段的導通斜率，最後是由於閘極偏壓太大而產生的高載子注入情況而產生之第三段斜率。

而在 C-V 量測中，先是觀察了樣品 A、B 於低溫環境時，有明顯之電容起伏差異，並藉由圖 4.5 中所示，可知室溫下之似 NDC 效應發生在蕭基接觸已經導通的情況之下，因此比較像是元件內部之缺陷對電荷累積及釋放下所造成之結果。另外在溫度區間為(70~110 K)的環境下觀看到樣品 A 之電容隨頻率之明顯變化，是發生在元件尚未導通之下，因此是較為可能由量子點所引起之現象，而根據變溫下之量測結果可發現此變化會由 70 K 時單一個明顯電容起伏之封包到 82 K 時變為兩個封包，甚至於到 120 K 之後其電容值不再隨頻率而變。為了對其進行分析，利用第二章中所介紹的式子(2.24)去找出 A、B、C 這三個參數。藉由兩樣品之比較結果和此三個參數與電容-電壓圖之比較以及最後所計算出來的電荷捕捉速率  $f_0$ 。可以發現在溫度變化下所出現的第一次的電容起伏和元件空乏層寬度縮減相關，且根據圖 4.7 的模型可推定它是由靠近閘極之量子點層內基態能階充/放電荷時所造成之結果。第二個  $f_0$  相關之第二次電容起伏則可推斷是由靠近閘極之量子點層內激發態能階充/放電荷時所造成之現象，至於其它量子點層內能階對電荷之捕捉/釋放行為在此實驗中並未觀察到，故還尚需後續之研究。最後由圖 4.11 可知量子點對電荷的捕捉速率會隨溫度提升而提高。此外於樣品 B 在所有的溫度環境之量測中，除了在閘極導通時所能觀看到電容值飆升之外，並沒有觀看到如樣品 A 在低溫環境下由量子點內之電荷儲存釋放所造成電容起伏，即所謂的負微分電容之現象。

## 4.2 場效電晶體元件之實驗結果

場效電晶體所使用的樣品，分別為量子點在二維電子氣上方的樣品 C，以及同結構卻無量子點的樣品 D，還有量子點在二維電子氣下方的樣品 E，以及同結構但無磊晶量子點的樣品 F。

### 4.2.1 場效電晶體元件之光激螢光頻譜

四個樣品之光激發螢光如圖 4.12 所示，圖 4.12(a)、(b)兩圖分別比較樣品 C、D、E、F 在不同溫度環境下的 PL 量測結果，從圖中可以觀察到樣品 C、E 在室溫或低溫下，都有明顯的量子點發光，而在樣品 D、F 中則無。此外當雷射功率調降至 100  $\mu\text{W}$ ，仍可在樣品 E 中，看到在波長為 1148 nm 以及 1222 nm 下之發光，因此我們可推測在樣品 E 中擁有兩群之發光源。另外兩圖中都可清楚的觀看到發光波長隨著溫度下降而藍移的現象存在。

圖 4.12、樣品 C、D、E、F 在 1 mW 功率下之(a)室溫(b)低溫的光激螢光量測結果。

## 4.2.2 場效電晶體元件之電性量測

### (一) 量子點在 2DEG 上方之樣品

以樣品 C 與樣品 D 為兩相比較之元件，其元件結構已示於圖 3.2。圖 4.13 秀出樣品 C 在閘極線寬在  $60\ \mu\text{m}$  下的 I-V 量測結果。從圖 4.13(a)中，可觀看到當固定汲極電壓為  $1.5\ \text{V}$  下，當閘極電壓從  $0.5\ \text{V}$  變為  $-2.0\ \text{V}$  時，汲極電流約從  $21\ \mu\text{A}$  變為  $16\ \mu\text{A}$ 。圖 4.13(b)秀出當固定汲極電壓為  $50\ \text{mV}$  的情況下，汲極電流和閘極電壓的相依性，從圖中可觀察到當閘極電壓在  $-2.0\sim0.25\ \text{V}$  時，汲極電流的變化並不大，當閘極電壓小於  $-2.0\ \text{V}$  後，由於元件開始漏電因此汲極電流反而上升，而當閘極電壓大於  $0.25\ \text{V}$  後，汲極電流則會因為閘極導通而下降。因此從圖 4.13(b)中，可大概預測在其它汲極偏壓下之結果，也就是說即使擴大閘極電壓的變化範圍，仍不可能有效地降低汲極電流值。最後圖 4.13(c)則是秀出元件閘極的蕭基接觸狀況，從圖中可看到閘極的導通電壓約在  $0.25\ \text{V}$ ，符合之前在圖 4.13(b)中所觀察到的現象，而所計算出來的理想因子  $n$  為  $1.63$ 。

圖 4.14 則是無量子點樣品 D 在閘極線寬在  $60\ \mu\text{m}$  下的電性量測結果，從圖 4.14(a)中，可觀看到當固定汲極電壓為  $1.5\ \text{V}$  下，當閘極電壓從  $0.5\ \text{V}$  變為  $-2.0\ \text{V}$  時，汲極電流約從  $238\ \mu\text{A}$  變為  $44\ \mu\text{A}$ 。圖 4.14(b)秀出固定汲極電壓為  $50\ \text{mV}$  的情況下，汲極電流和閘極電壓的關係圖，從圖中可看到當閘極電壓在  $-2.0\sim0.25\ \text{V}$  時，汲極電壓有明顯上升的趨勢，此原因在於二維電子氣層在此閘極電壓區間內，因電荷累積而導通。當閘極電壓大於  $0.5\ \text{V}$  後，同樣因為閘極導通而使汲極電流下降，而當閘極電壓小於  $-2.0\ \text{V}$  後，元件也同樣因為漏電而使汲極電流開始上升。而從圖 4.14(c)中，可觀察到樣品 D 的導通電壓也約在  $0.25\ \text{V}$ ，計算出來的理想因子  $n$  為  $1.28$ 。

理想上之場效電晶體 I-V 特性可藉由閘極電壓調控截止汲極電流。但在樣品 C、D 之電性量測上都觀察不到截止之情況發生。而兩樣品間最不同之處在於量子點層的存在，似乎影響了二維電子氣之導通狀況，也造成了理想因子之差距，為了研究量子點和二維電子氣之關係，則進行了量子點在二維電子氣下方之實驗。

此外無論是在對有量子點層結構之樣品 C 或者是無量子點層結構之樣品 D 而言。只要當元件閘極長度小於  $60 \mu\text{m}$  的情況之下，汲極電流隨閘極電壓之改變量小到可以忽略換句話說就是呈現電阻的形式。所以對樣品 C、樣品 D 之電性研究我們只取出  $60 \mu\text{m}$  來觀看的原因。推測是由於當閘極線寬變小時，就愈不可能利用閘極電壓去改變汲極電流。

圖 4.13、樣品 C 在線寬  $60 \mu\text{m}$  下之電性圖。

圖 4.14、樣品 D 在線寬  $60 \mu\text{m}$  下之電性圖。

## (二) 量子點在 2DEG 下方之樣品

樣品結構已示於圖 3.3。在此將有量子點之樣品 E 以及無量子點之樣品 F，在開極線寬  $16\mu\text{m}$  之電性量測結果以圖 4.15、圖 4.16 秀出。

圖 4.15、樣品 E 在  $16\mu\text{m}$  線寬下的電性量測。

圖 4.16、樣品 F 在  $16 \mu\text{m}$  線寬下的電性量測。

從圖 4.15(a)中，當固定汲極電壓為  $1.5 \text{ V}$  下，去觀看閘極電壓從  $0.5 \text{ V}$  變為  $-3.0 \text{ V}$  時，可發現汲極電流約從  $218 \mu\text{A}$  變為  $2 \mu\text{A}$ 。圖 4.15(b)中則可觀察到元件在當閘極電壓大於  $-1.5 \text{ V}$  時，可看到明顯由二維電子氣導通所引起之汲極電流提升，而當元件開始漏電時，汲極電流上升之量約在數  $\mu\text{A}$ ，而當閘極電壓開始導通時，汲極電流則會下降。圖 4.15(c)則是秀出元件閘極的蕭基接觸狀況，從圖中可看到閘極的導通電壓約在  $0.25 \text{ V}$ ，而所計算出來的理想因子  $n$  為  $1.36$ 。圖 4.15(d)中可觀察到較顯著的電容起伏都出

現在元件導通或二維電子氣充放電時，因此只能藉由和無量子點之樣品 F 比較來斷定是否有量子點所引起的電容反應。

從圖 4.16(a)中，當固定汲極電壓為 1.5 V 下，去觀看閘極電壓從 0.5 V 變為 -3.0 V 時，可發現汲極電流約從  $531 \mu\text{A}$  變為  $19 \mu\text{A}$ 。圖 4.16(b)中則可觀察到元件在當閘極電壓大於 -1.25 V 時，同樣可看到由二維電子氣導通所引起之汲極電流提升，當元件開始漏電時，汲極電流上升之量約在十幾  $\mu\text{A}$ ，而當閘極電壓開始導通時，汲極電流則會下降。圖 4.16(c)則是秀出元件閘極的蕭基接觸狀況，從圖中可看到閘極的導通電壓約在 0.25 V，而所計算出來的理想因子  $n$  為 1.34。圖 4.16(d)中也可觀察到較顯著的電容起伏都出現在元件導通或二維電子氣充放電時。

從圖 4.15 以及圖 4.16 比較中，兩樣品都可觀看到閘極電壓對汲極電流顯著的影響，其導因於明顯地二維電子氣層對電荷累積之效應。且兩元件的理想因子的值都在合理值之內並相近。但可惜的是並無法在兩者 I-V 以及 C-V 曲線比較上，觀看到由量子點所導致的差異。因此只能開始嘗試是否可在電壓間隔為 50 mV，且時間間隔為  $500 \mu\text{s}$  之雙向的 I-V 量測中，觀察看量子點之記憶窗的特性。其結果如圖 4.17 所示

圖 4.17、樣品 E、F 在  $16 \mu\text{m}$  線寬下之(a)室溫、(b)低溫環境下之記憶體特性量測。

圖 4.17(a)中秀出樣品 E、F 在室溫環境下  $16\mu\text{m}$  線寬的記憶窗特性量測結果。理論上希望觀看到隨著量子點的累積以及釋放電荷，造成臨界電壓偏移所出現的記憶窗口。但圖中似乎沒有明顯可以歸究於量子點層所造成之差異。而在圖 4.17(b)中可以看出在低溫環境下，由於載子數目下降致使元件逆向偏壓之汲極電流值大幅度地降低，而且兩個樣品在閘極電壓大於  $-0.8\text{ V}$  後都可以觀察到在橫方向上之臨界電壓偏移，而有無量子點的差異似乎只顯示在當閘極電壓大於  $-0.8\text{ V}$  後之汲極電流增加幅度之快慢而已。這樣的實驗結果和理論上所假設的狀況完全不符合，且對於此實驗之原理也還需要進一步的驗証之。

為了加強樣品 E、F 中元件閘極對 2DEG 通道中電流量的空乏能力，進行了 Recess 製程以期藉此觀察到元件中量子點的作用。關於 Recess 的製程，是在完成場效電晶體源極/汲極金屬退火步驟後，便利用(磷酸：雙氧水：水) = (1:3:50)的比例配製之溶液去蝕刻 Mesa 上的 GaAs 約六秒後，再進行完成場效電晶體製程便可以增強元件閘極的空乏通道之能力。對於樣品 E、樣品 F 進行 Recess 前後電性量測比較如圖 4.18 所示，圖中可看出在 Recess 前在  $-1.0\text{ V}$  閘極偏壓下的汲極電流值，約等同於 Recess 後之閘極偏壓在  $0.0\text{ V}$  之汲極電流值。可惜的是即使經過 Recess 製程後之元件，仍無法在雙向的 I-V 量測中觀看到臨界電壓偏移之記憶特性。

圖 4.18、樣品 E、F 在 Recess 前後之  $16\mu\text{m}$  I-V 曲線比較圖。

#### 4.2.3 樣品結構特性總結與討論

截至目前為止，本研究已經對四種之樣品結構去進行場效電晶體元件製程。其中又可將這四種樣品結構區分成(1)量子點層位於 2DEG 上方、(2) 量子點層位於 2DEG 下方、(3)無量子點層之相似結構這三種結構之大綱。根據在 4.2.2 節對電性量測結果中可以觀察到，當量子點層位於 2DEG 通道上方之元件結構樣品 C 以及相似之無量子點層結構樣品 D 都存在著閘極無法有效空乏二維電子氣通道中之累積電荷行為。反之，在量子點位於 2DEG 通道下方結構之樣品 E 以及部份相似之無量子點層結構樣品 F 則擁有良好的閘極空乏能力。經過交叉比對元件之結構後，可以將造成此閘極無法有效空乏二維電子氣層之原因，歸究於元件表面金屬閘極和二維電子氣通道之間的距離，即實驗之元件結構的設計問題。

雖說能在對樣品 E、樣品 F 之場效電晶體元件的電性量測中觀看到理想 MOSFET 之間極電壓對二維電子氣內載子的空乏能力，但是對兩個元件之記憶體能力測試下，即便是經過了 Recess 程序，加強閘極對通道影響的情況下，仍究觀看不到量子點層之捕捉/釋放電荷行為下所造成的臨界電壓偏移的現象產生。推測其主要原因就在於使用金屬閘極-二維電子氣通道-量子點層這種結構下，要去操控電荷在二維電子氣通道和量子點層之間的轉換是困難的，故無法觀看量子點層之記憶功能。

在前面已經說過了，造成即便閘極電壓對汲極電流之控制不良的主因在是在元件結構之設計問題，故此現象和量子點層的磊晶位置並無絕對之關係。因此只要能設計出擁有良好 MOS 元件電性之金屬—量子點層—2DEG 通道結構之樣品，似乎是唯一能較有效觀察到量子點記憶特性的方法。

## 第五章

### 總結與未來研究

在蕭基二極體實驗中，觀看到了樣品元件內部之奈米量子點層在儲存以及釋放離散能階上電荷時，所造成的電容起伏改變即所謂的負微分電容。此元件之 NDC 現象出現與否和溫度以及頻率呈現很強的相關性。在 4.1 節中，於樣品 A 上觀看到量子點層所造成的 NDC 現象只出現在特定溫度區間(70~110 K)下，而且在此溫度區間中 NDC 消失的頻率也會愈來愈高，即量子點對電荷的捕捉釋放時間會隨溫度提昇而下降。而當溫度高於 110 K 後，由於元件導通電壓向負電壓偏移以致於和量子點訊號出現電壓重疊而無法顯現出來。雖說此蕭基二極體之特性還有待加強，不過其清晰的量子點充放電之電性改變性質還是讓我們觀看到了做成奈米晶之記憶元件的可能性。

對於奈米晶場效電晶體之記憶元件製作，我們進行了兩種主要結構共四個樣品的實驗製程。從一開始金屬--量子點層--2DEG 通道結構中閘極對空乏汲極電流的問題，到金屬--2DEG 通道--量子點層之結構中對量子點儲存釋放電荷所造成的臨界電壓偏移的觀察，甚至以 Recess 的方式來加強閘極對汲極電流之空乏能力，都並未觀察到量子點所造成之記憶行為。其主要的原因還是在於以量子點層位於二維電子氣下方之結構製作元件，即使會擁有理想的 MOSFET 電性，但同樣地增加如何去控制量子點內之電荷行為的難度。可慶幸的是實驗發現造成元件閘極對汲極電流控制力問題的主因不是量子點層的位置而是表面閘極和 2DEG 通道的距離遠近。因此未來如果能藉此改善金屬--量子點層--2DEG 通道結構的 MOSFET 電性，將十分有可能可以達到我們對奈米量子點記憶元件之特性要求，進而觀察到量子點之儲存/釋放電荷行為下之記憶效應。

## 參考文獻

- [1] D. Kahng and S. M. Sze, “A floating gate and its application to memory devices”, *Bell Syst. Tech. J.*, 46, 1288 (1967)。

- [2] J. D. Blauwe, “ Nanocrystal nonvolatile memory devices ”, *IEEE Trans. Nano-Tech.*, 1, p.72~p.77 (2002)。

- [3] M. H. White, Y. Yang, A. Purwar, and M. L. French, ”A low voltage SONOS nonvolatile semiconductor memory technology”, *IEEE Int., Nonvolatile Memory Tech. Conference*, p.52~p.57 (1996)。

- [4] M. H. White, D. A. Adams, and J. Bu, “On the go with SONOS”, *IEEE Circuits & Devices Magazine*, 16, p.22~p.31 (2000)。

- [5] H. E. Maes, J. S. Witters, and G. Groeseneken, “Programming mode dependent degradation of tunnel oxide floating gate devices” , *IEEE Electron Devices Meeting Int.*, 33, p.544~p.547 (1987)。

- [6] S. Tiwari, F. Rana, K. Chan, H. Hanafi, C. Wei, and D. Buchanan, “Volatile and non-volatile memories in silicon with nano-crystal storage” ,*IEEE Electron Devices Meeting Int.*, p.521~p.524 (1995)。

- [7] J. J. Welser, S. Tiwari, S. Rishton, K. Y. Lee, and Y. Lee, “Room temperature operation of a quantum-dot flash memory”, *IEEE Electron Device Lett.*, 18, p.278~p.280 (1997)。

- [8] Y. C. King, T. J. King, and C. Hu, “MOS memory using germanium nanocrystals formed by thermal oxidation of  $Si_{1-x}Ge_x$ ”, *IEEE Electron Devices Meeting Tech. Dig. Int.*, p.115~p.118 (1998)。

- [9] R. Ohba, N. Sugiyama, K. Uchida, J. Koga, and A. Toriumi, “Nonvolatile Si quantum memory with self-aligned doubly-stacked dots”, *IEEE Trans. Electron Devices*, 49, p.1392~p.1398 (2002)。

- [10] A. Marent,T.Nowozin,M.Geller and D.Bimberg“The QD-Flash : a quantum dot-based memory device” *Semicond. & Sci. Tech.*, 26, 014026 (2011) 。

- [11] C.R. Müller,L. Worschech, J. Heinrich,S.Höfling, and A. Forchel“Room temperature memory operation of a single InAs quantum dot layer in a GaAs/AlGaAs heterostructure” *Appl.Phys.Lett.* 93, 063502 (2008) 。

- [12] E.S. Kannan,G.H. Kim, and D.A. Ritchie“Memory characteristics of InAs quantum dots embedded in GaAs quantum well” *Appl.Phys.Lett.* 95, 143506 (2009) 。

- [13] A.J. Chiquito,Y.A. Pusep, S. Mergulhao, and J. C. Galzerani “Capacitance spectroscopy of InAs self-assembled quantum dots embedded in a GaAs/AlAs superlattice” *J.Appl.Phys.*, 88, 1987 (2000) 。

- [14] S. Göpfert, L. Worschech,S. Lingemann,C. Schneider,D. Press,S. Höfling, and A. Forchel “ Room temperature single-electron memory and light sensor with three-dimensionally positioned InAs quantum dots” *Appl.Phys.Lett.*, 97,222112 (2010) 。

- [15] D.J. Mowbray and M.S. Skolnick “ New physics and devices based on self-assembled semiconductor quantum dots” *J. Appl. Phys.*, 38, p.2059~p.2076 (2005)

- [16] C.M.A. Kapteyn, M. Lion, R. Heitz and D. Bimberg “Many-particle effects in Ge quantum dots investigated by time-resolved capacitance spectroscopy” *Appl. Phys. Lett.* 77, p.4169~p.4171 (2000) 。

- [17] O. Engstrom, M. Kaniewska, Y. Fu, J. Piscator and M. Malmkvist “Electron capture cross sections of InAs/GaAs quantum dots” *Appl. Phys. Lett.*, 85,p.2908~p.2910 (2004) 。

- [18] V. V. Ilchenko,S. D. Lin,C. P. Lee and O. V. Tretyak “Deep level transient spectroscopy characterization of InAs self-assembled quantum dots” *J. Appl. Phys.* 89, p.1172~p.1174 (2001) 。

- [19] S. Schulz, S. Schnumll,C. Heyn and W. Hansen “Charge-state dependence of InAs quantum-dot emission energies” Phys. Rev. B, 69, 195317 (2004) 。

- [20] V. Y. Aleshkin, N. A. Bekin, M. N. Buyanova, A. V. Mural and B. N. Zvonkov “Determination of the density of states in quantum wells and quantum dot arrays by the capacitance-voltage method” Semicond., 33, p.1133~p.1138 (1999) 。

- [21] A.J. Chiquito, Y. A. Pusep, S. Mergulhao and J. C. Galzerani “Effect of photogenerated holes on capacitance-voltage measurements in InAs/GaAs self-assembled quantum dots” Phys. Rev. B, 61, p.4481~p.4484 (2000) 。

- [22] S.D. Lin, V. V. Ilchenko, V. V. Marin,“Observation of the negative differential capacitance in Schottky diodes with InAs quantum dots near room temperature” Appl. Phys. Lett., 90, 263114 (2007) 。

- [23] V.V. Ilchenko,V.V. Marin, S.D. Lin, K. Y. Panarin, A. A. Buyanin and O.V.Tretyak “Room temperature negative differential capacitance in self-assembled quantum dots” J. Appl. Phys., 41, 235107 (2008) 。

- [24] S. D. Lin,V. V. Ilchenko,V. V. Marin,K. Y. Panarin,A. A. Buyanin, and O. V. Tretyak “Frequency dependence of negative differential capacitance in Schottky diodes with InAs quantum dots” Appl. Phys. Lett., 93, 103103 (2008) 。

- [25] S. M. Sze “Physics of Semiconductor Devices” 2nd ed. New York : Wiley (1981) 。

- [26] 盧廷昌、王興宗 “Introduction to Semiconductor Lasers (半導體雷射導論)” 五南出版社 (2008) 。

- [27] 盧廷昌、王興宗 “Semiconductor Laser Technology (半導體雷射技術)” 五南出版社(2010) 。

- [28] J.M. Shieh, Y.F. Lai, Y.C. Lin and J.Y. Fang,“ Photoluminescence Principles , Structure and Application” 。奈米通訊 , 12, p.28~p.39 (2005) 。

[29] Sidney. Perkowitz “ Optical Characterization of Semiconductors ” New York: Academic (1993) °

[30] T. Wilson “Theory and Practice of Scanning Optical Microscopy.” New York : Academic (1954) °

[31] GD. Gilliland “photoluminescence spectroscopy of crystalline semiconductor” Material Sci. & Engineering R-Report, 18, p.99~p.399 (1997) °

[32] J. Wan, G. L. Jin, Z. M. Jiang, Y. H. Luo, J.L. Liu, and K. L. Wang “Band alignments and photon-induced carrier transfer from wetting layers to Ge islands grown on Si (001)” Appl. Phys. Lett., 78, p.1763~p.1765 (2001) °

# 簡 歷

姓名 : 王 參 豪 (Tsan-Hao Wang)

性別 : 男

出生年月日 : 民 國 七 十 六 年 七 月 二 十 六 日

籍貫 : 台 灣 新 竹 市

學 歷 :

國 立 聯 合 大 學 電 子 系 學 士 ( 2006.9 – 2010.6 )

國 立 交 通 大 學 電 子 工 程 系 碩 士 ( 2010.9 – 2013.4 )

碩 士 論 文 題 目 :

砷化銦量子點在蕭基二極體

與場效電晶體上之效應

Effects of InAs Quantum Dots on Schottky Diodes

and Field Effect Transistors