國立交通大學

機械工程學系

碩士論文

應用碳化鈦導電薄膜於微機電碰撞開關之可行性研

究

Feasibility study of Applying TiC Film on MEMS

Inertial Switch

研 究 生 : 吳族豪

指 導 老 師 : 徐文祥 教授

中華民國 一百零一年八月

應用碳化鈦導電薄膜於微機電碰撞開關之可行性研究

Feasibility study of Applying TiC Film on MEMS Inertial Switch

研 究 生 : 吳族豪

Student : Tsu-Hau Wu

指 導 老 師 : 徐 文 祥 教 授

Advisor : Wensyang Hsu

August 2012

Hsinchu, Taiwan, Republic of China

中華民國 一百零一年 八月

# 應用碳化鈦導電薄膜於微機電碰撞開關之可行性研究

研究生：吳族豪

指導教授：徐文祥

國立交通大學機械工程學系 碩士班

## 摘要

本論文研究重點在探討將碳化鈦鍍膜應用於微機電碰撞開關上之可行性，目標在增加碰撞開關使用壽命，並防止元件在常溫下氧化。

首先針對碳化鈦進行基本性質研究後發現，在 30 奈米相同厚度下碳化鈦鍍膜耐磨耗能力是鎳金屬鍍膜的 2 倍，硬度是鎳金屬鍍膜的 3 倍。在抗氧化、導電率等方面碳化鈦鍍膜使用環境溫度應低於 200°C，超過 300°C 時碳化鈦薄膜則完全氧化，且當隨著碳化鈦薄膜厚度增加，薄膜受溫度變化造成的電阻值波動越不明顯。

在此進一步設計一測試結構，並分別濺鍍碳化鈦與鎳金屬薄膜，進行碰撞磨耗及氧化保護實驗，發現濺鍍 30 奈米厚度的碳化鈦薄膜可比濺鍍鎳金屬薄膜的元件碰撞壽命提高 7 倍以上，經過 100°C 加熱後濺鍍碳化鈦薄膜比濺鍍鎳金屬薄膜的元件氧化時間延長 2 倍以上，且碳化鈦薄膜厚度增加，可進一步延長氧化時間。

# **Feasibility study of Applying TiC Film on MEMS Inertial Switch**

Student : Sung-Yueh Wu

Advisor : Wensyang Hsu

Department of Mechanical Engineering

National Chiao Tung University

## **Abstract**

---

This study, we present an inertial switch which employing titanium carbide (TiC) protective thin film to increase abrasion resistance, and simultaneously, autoxidation. Our objective is to enhance the life cycle of inertial switch.

Both 30 nanometer film thickness, TiC has better performance than Nickel in Microhardness and Microscratch tests. TiC coating shows Vickers hardness values increased by 300% than Nickel coating. And the volume of material removed, TiC coatings is 50% lower than Nickel coating.

The isothermal oxidation and conductivity of TiC film was carried out at low temperature of 100-500°C at atmospheric. Results shows that the TiC film at temperature higher than 300°C will completely oxidized, temperature lower than 200°C the conductivity varies unobvious. We also found that the resistance fluctuates according to the temperature change decrease when film thickness rising.

Design an MEMs switch for impact fatigue test and oxidation protect test. Impact fatigue test shows, both 30 nanometer thickness, coating TiC can improve the switch life cycle 700% than coating Nickel. And oxidation protect test shows, both 30 nanometer thickness, coating TiC can prolong oxidation time over 200% than coating Nickel.

## 誌謝

沒想到碩班的 2 年一下就結束了，想當初剛進實驗室，連咪聽都聽到睡著，而如今已經在撰寫論文的誌謝，仔細回想真有種不可思議的感覺。

首先我要感謝的當然是家人，從碩一開始，母親每天從不間斷的以電話關心，讓我做實驗疲勞之餘感受到溫暖，父親從小的言傳身教，讓我在數理邏輯能力能有良好的基礎，回家後與姐的遊戲與哈拉，也讓我忘卻實驗的一些煩惱，謝謝你們，沒有你們我走不到這一步!!

接著要感謝的是一徐文祥老師，老師的指導與建議，讓我每次在陷入瓶頸時都能找到解決的辦法，而且老師的邏輯與表達能力，也常讓我受益良多，在這短短的 2 年內，我從老師這裡學到的能力，定能讓我這輩子受用無窮，謝謝老師。

再來得感謝實驗室的好夥伴們!在研究中幫助我很多很多的一全學長、不用領錢的囧夫學長、超有想法的 Mike 學長、遠在天邊的 geigei 學長、繪圖超強的 A 犝學長，以及已畢業，做實驗一絲不苟的毅家大學長、帶我買耳機的豆哥、親切的小潘、咪聽的擋箭牌馬犧、匪夷所思的芋頭，還有同期的修課達人雷孟、前小遊戲之神琮閔、一直想當我媒人的鶴齡，碩一的、博懷、振淵、嘉珮、大捲，希望大家以後都能過得很好，謝謝你們!能認識你們真好!!

# 目錄

|                     |      |

|---------------------|------|

| 中文摘要 .....          | III  |

| 英文摘要 .....          | IV   |

| 誌謝 .....            | V    |

| 圖目錄 .....           | VIII |

| 表目錄 .....           | X    |

| 第一章 緒論 .....        | 1    |

| 1.1 研究動機 .....      | 1    |

| 1.2 文獻回顧 .....      | 2    |

| 1.2.1. 巨觀磨耗保護 ..... | 2    |

| 1.2.2. 微觀磨耗保護 ..... | 5    |

| 1.2.3. 鍍膜選擇 .....   | 7    |

| 1.3 研究目標 .....      | 8    |

| 第二章 測試結構設計 .....    | 10   |

| 2.1 測試元件概念設計 .....  | 10   |

| 2.2 碰撞懸臂樑理論分析 ..... | 11   |

| 2.3 測試元件細部設計 .....  | 13   |

| 2.4 ANSYS 模擬 .....  | 14   |

| 第三章 製程與量測 .....     | 16   |

| 3.1 碰撞懸臂樑製程規劃 ..... | 16   |

| 3.2 製程結果 .....      | 19   |

| 3.2.1. 上蓋 .....     | 19   |

| 3.2.2. 碰撞懸臂樑 .....  | 20   |

|        |                        |    |

|--------|------------------------|----|

| 3.3    | 量測 .....               | 21 |

| 3.3.1. | 沉積於基板量測濺鍍速率 .....      | 21 |

| 3.3.2. | 沉積於基板量測表面成份 .....      | 23 |

| 3.3.3. | 沉積於基板量測薄膜硬度與刮痕磨耗 ..... | 24 |

| 3.3.4. | 沉積於基板測試加熱抗氧化耐性 .....   | 26 |

| 3.3.5. | 沉積於基板量測導電率 .....       | 28 |

| 3.3.6. | 沉積於元件量測使用壽命 .....      | 31 |

| 3.3.7. | 沉積於元件量測接觸阻值 .....      | 37 |

| 3.3.8. | 沉積於元件量測耐氧化能力 .....     | 40 |

| 第四章    | 結論 .....               | 44 |

| 4.1    | 總結 .....               | 44 |

| 4.1.1. | 設計 .....               | 44 |

| 4.1.1. | 製造 .....               | 44 |

| 4.1.2. | 量測 .....               | 45 |

| 4.2    | 未來工作 .....             | 46 |

| 參考文獻   | .....                  | 47 |

# 圖 目 錄

|                                                                            |    |

|----------------------------------------------------------------------------|----|

| 圖 1 有鍍膜與無鍍膜之滾珠軸承(a)馬達轉動扭矩圖(b)平均消耗功率 .....                                  | 3  |

| 圖 2 碳化鈦、氮化鈦二種鍍膜於 D2、D3 工具鋼(a)碳化鈦與氮化鈦在不同工具鋼上之耐磨耗比較 (b)基材硬度對鍍膜硬度之影響長方圖 ..... | 4  |

| 圖 3 薄膜耐撞擊實驗(a)撞擊凹痕直徑與施加負載之作圖(b)撞擊點造成之表面缺陷 .....                            | 5  |

| 圖 4 MUMPS 製程結構與微機電馬達(a)MUMPS 製程中加入兩層碳化鈦薄膜(b)碳化鈦應用於微機電馬達示意圖 .....           | 6  |

| 圖 5 RF switch.....                                                         | 6  |

| 圖 6 電擊耐磨耗實驗圖(a)上電極經接觸磨耗後電極 Y1-Y2 剖面圖(b)加入 20% 鎳對使用壽命之增長 .....              | 7  |

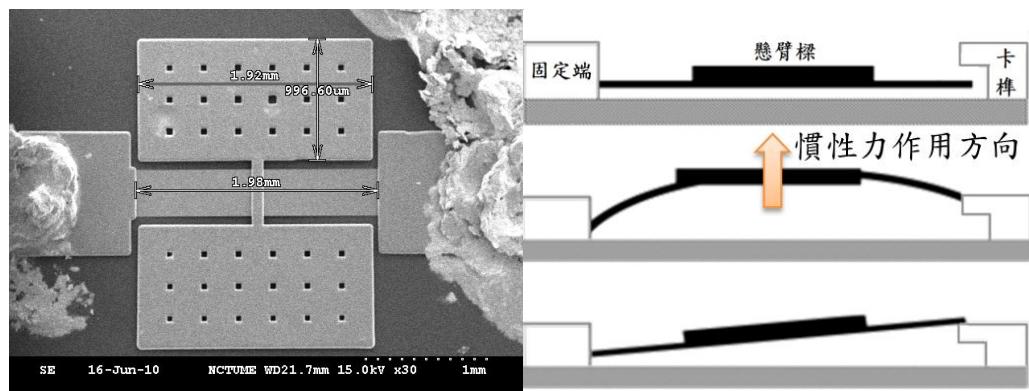

| 圖 7 卡桿式鎳基加速度開關(a)卡桿式鎳基開關上視圖(b)受慣性力作動圖 .....                                | 9  |

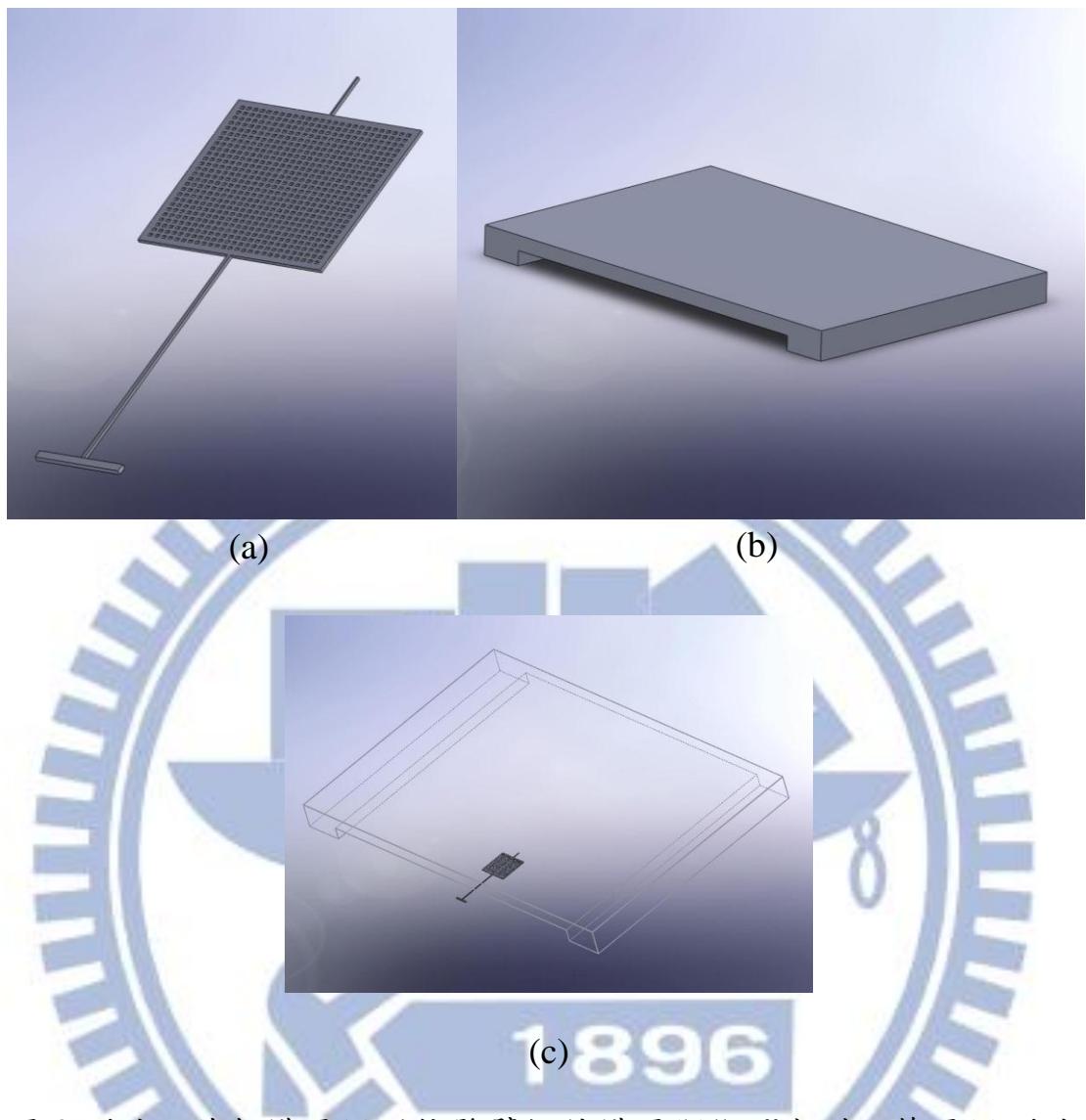

| 圖 8 測試元件架構圖(a)碰撞懸臂樑結構圖(b)“匚”字型上蓋圖(c)測試元件組合圖                                | 11 |

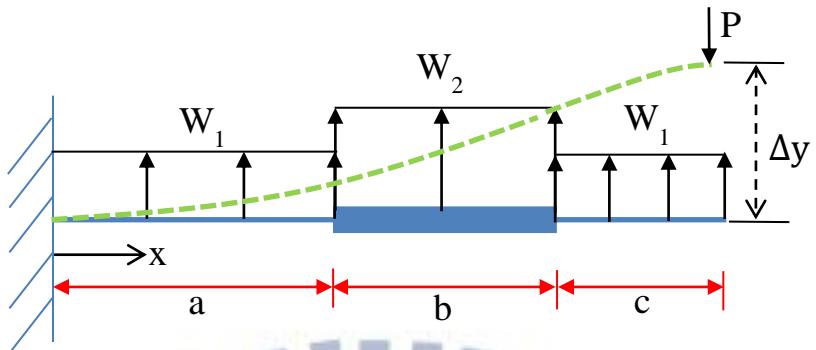

| 圖 9 碰撞懸臂樑之靜態分析模型 .....                                                     | 12 |

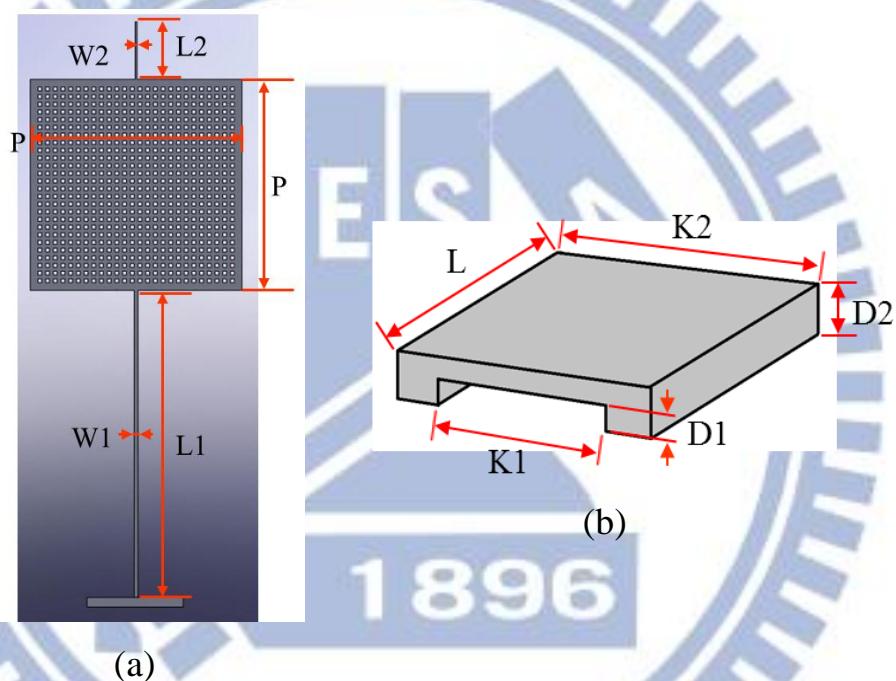

| 圖 10 碰撞磨耗尺寸標註圖(a)非卡桿式開關(b)“匚”字形上蓋 .....                                    | 13 |

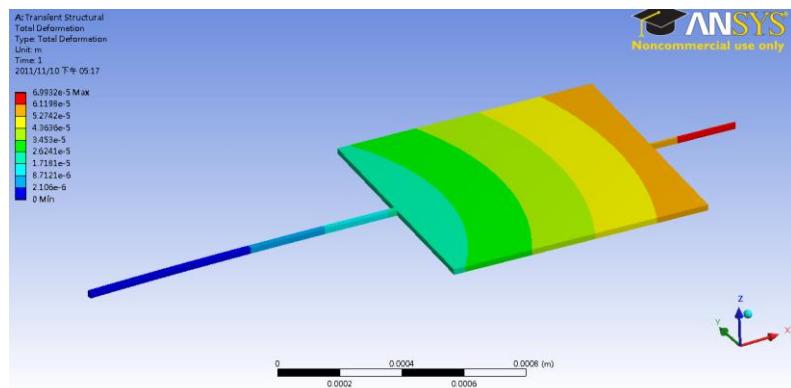

| 圖 11 碰撞懸臂樑 ANSYS 結構變形量模擬 .....                                             | 15 |

| 圖 12 碰撞懸臂樑製程規劃(a)上蓋製程(b)懸浮碰撞元件製程 .....                                     | 18 |

| 圖 13 上蓋製程結果 .....                                                          | 19 |

| 圖 14 碰撞懸臂樑製程結果 SEM 圖 .....                                                 | 20 |

| 圖 15 薄膜製程、量測機台(a)真空濺鍍機(b)表面粗糙度量測儀 .....                                    | 22 |

| 圖 16 濺鍍時間與厚度關係 .....                                                       | 22 |

| 圖 17 能量散射光譜儀 .....                                                         | 23 |

| 圖 18 30 奈米碳化鈦薄膜 XRD 成份分析 .....                                             | 24 |

| 圖 19 奈米刮痕磨耗 AFM 掃描圖 .....                                                  | 25 |

| 圖 20 單位磨損深度—荷載作圖 .....                                                     | 26 |

|                                                                                                 |    |

|-------------------------------------------------------------------------------------------------|----|

| 圖 21 加熱儀器與升溫流程(a)高溫爐(b)升溫曲線 .....                                                               | 27 |

| 圖 22 30 奈米碳化鈦薄膜受高溫處理後 X 光繞射曲線 .....                                                             | 28 |

| 圖 23 四點探針量測平台 .....                                                                             | 29 |

| 圖 24 加熱氧化導電率變化 .....                                                                            | 30 |

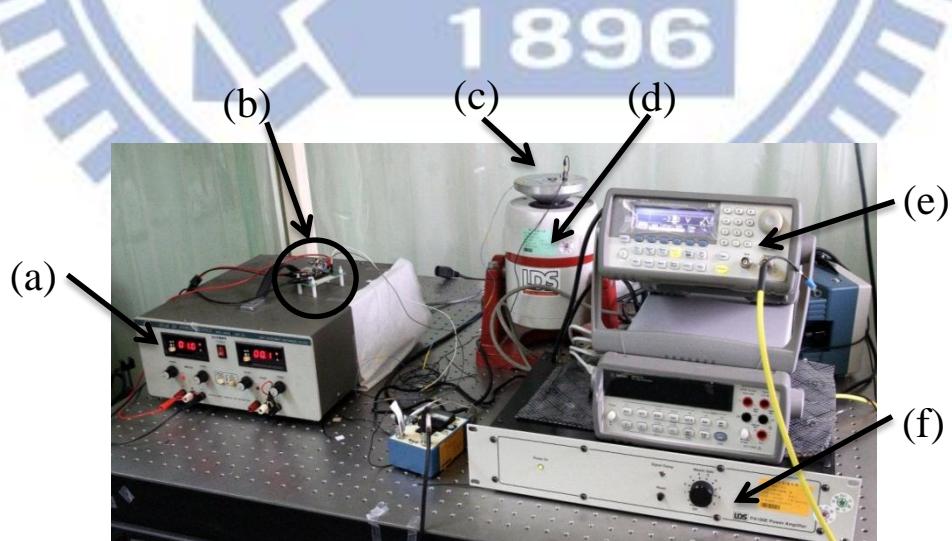

| 圖 25 碰撞實驗儀器架構圖(a)電源供應器(b)自製電路(c)碰撞開關(d)震盪器(e)訊號產生器(f)訊號放大器 .....                                | 32 |

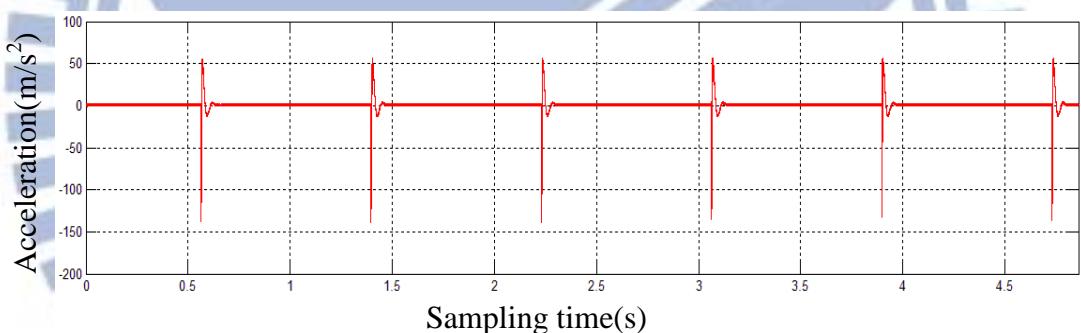

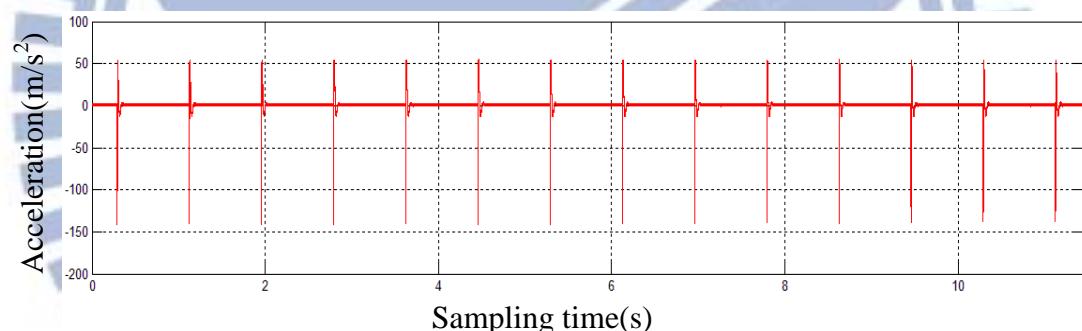

| 圖 26 19 奈米碳化鈦鍍膜碰撞開關訊號(a)初始(b)經過 12 萬次磨耗 .....                                                   | 33 |

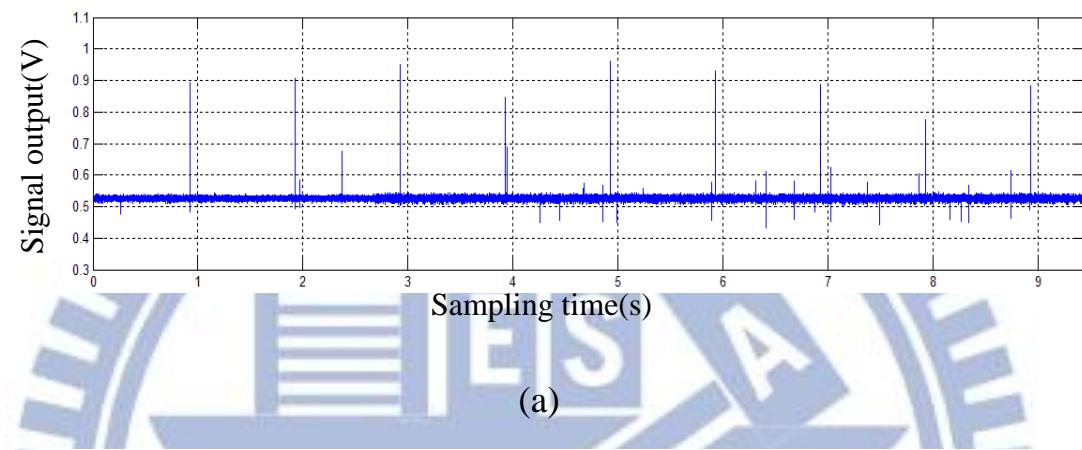

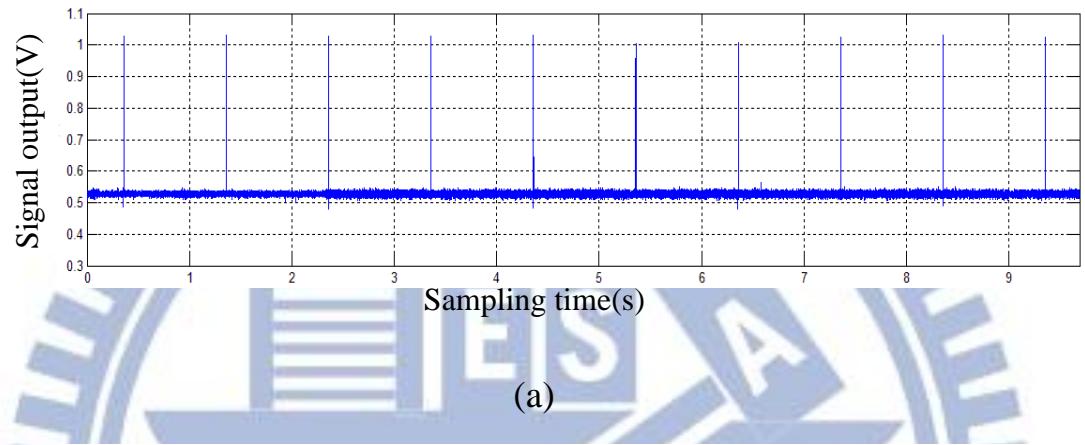

| 圖 27 30 奈米碳化鈦鍍膜碰撞開關訊號(a)初始(b)經過 113 萬次磨耗 .....                                                  | 34 |

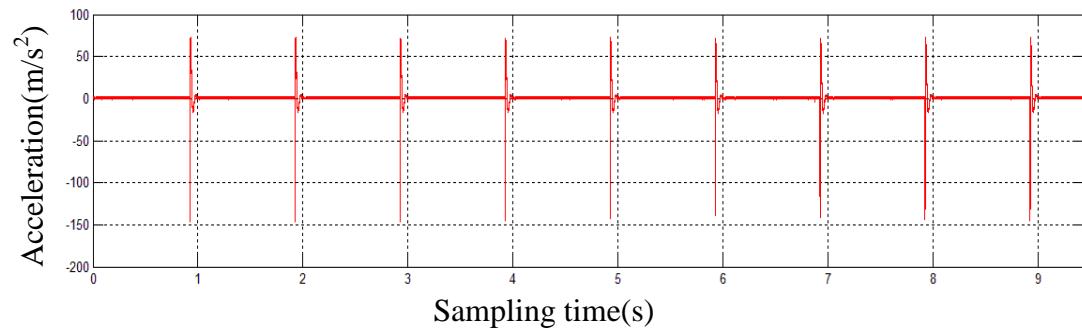

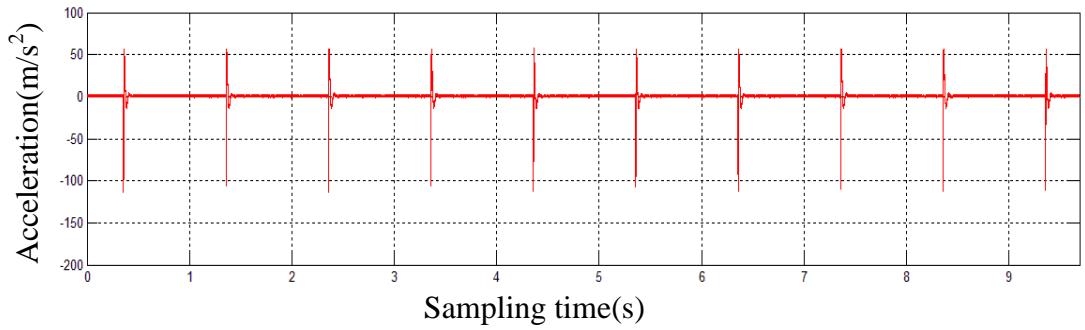

| 圖 28 30 奈米鎳金屬鍍膜碰撞開關訊號(a)初始(b)經過 15 萬次磨耗 .....                                                   | 35 |

| 圖 29 30 奈米鎳金屬鍍膜 SEM 圖(a)初始狀態未碰撞(b)經過 15 萬次磨耗 .....                                              | 36 |

| 圖 30 30 奈米碳化鈦鍍膜 SEM 圖(a)初始狀態未碰撞(b)經過 113 萬次磨耗 .....                                             | 36 |

| 圖 31 自製訊號擷取簡易電路 .....                                                                           | 37 |

| 圖 32 量測電路設計圖 .....                                                                              | 38 |

| 圖 33 碰撞開關不同鍍膜接觸阻值 .....                                                                         | 39 |

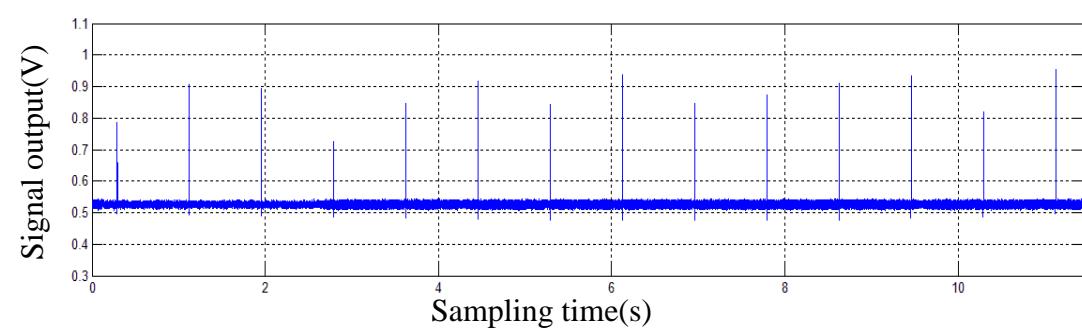

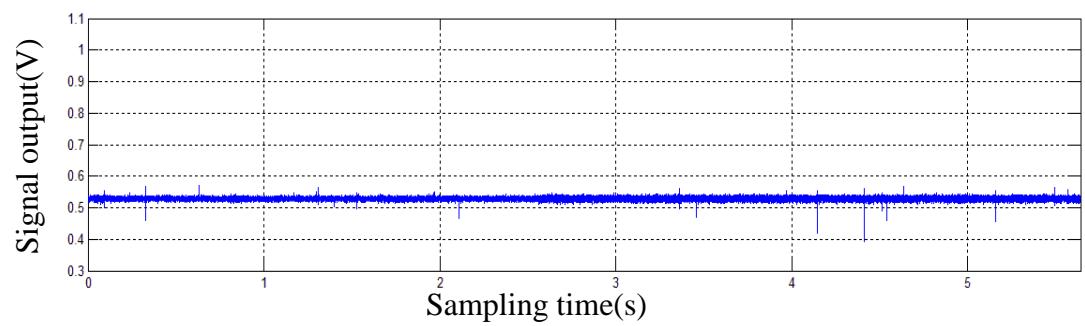

| 圖 34 30 奈米鎳金屬鍍膜元件 100°C 加熱前後訊號圖(a)加熱前(b)加熱 10 分鐘後                                               | 41 |

| 圖 35 30 奈米碳化鈦鍍膜元件 100°C 加熱前後訊號圖(a)加熱前(b)加熱 10 分鐘後(c)加熱 20 分鐘後 .....                             | 42 |

| 圖 36 碳化鈦薄膜經過 100°C 30 分鐘加熱(a)30 奈米碳化鈦薄膜加熱後元件變化(b)45 奈米<br>碳化鈦薄膜加熱後元件變化(c)45 奈米碳化鈦薄膜加熱後訊號圖 ..... | 43 |

# 表目錄

|                            |    |

|----------------------------|----|

| 表 1 D2、D3 工具鋼硬度表 .....     | 4  |

| 表 2 三種薄膜特性參數 .....         | 5  |

| 表 3 加入 20% 鎳對電極之影響 .....   | 7  |

| 表 4 各種常用耐磨耗鍍膜與純金之比較 .....  | 8  |

| 表 5 碰撞磨耗開關尺寸設計 .....       | 14 |

| 表 6 解析運算值與模擬值比較 .....      | 15 |

| 表 7 碳化鈦靶材比例與薄膜濺鍍製程參數 ..... | 22 |

| 表 8 碳化鈦奈米壓痕硬度與楊氏係數 .....   | 25 |

| 表 9 各溫度階段碳化鈦導電度變化 .....    | 30 |

# 第一章 緒論

微機電系統(Micro-Electro-Mechanical Systems, MEMS)在近年來是一個備受矚目的研究領域，因其具有微小化之優勢、積體化的製程方法、可結合現有的積體電路製程以及多樣性的應用範圍，使得這個領域有無限可能的潛力。

微機電領域的眾多分支中，慣性感測元件在人們的生活中扮演尤其重要的角色，應用的層面也越來越廣；低 G 值慣性開關，即用在硬碟防震系統、方向與位移感測；中 G 值慣性開關，常用在汽車安全裝置(安全氣囊)；而高 G 值慣性開關，則用於軍事裝置系統上。

## 1.1 研究動機

慣性開關的現有的文獻中，主體結構多大為金屬，雖然有優異的導電性，但不可避免的會產生氧化的現象，且在慣性開關領域中，為了延長電極與電極間相接觸的時間、縮短反應時間等許多的方法，都會造成元件的磨損。

因此，利用碳化鈦硬質薄膜具備高硬度、低摩擦力、抗腐蝕能力強、導熱效果好、高導電率和高熔點等等特性，來改善慣性感測開關也成了這次研究主要的方向。

## 1.2 文獻回顧

在減少接觸介面間相互磨耗常用之方法可概略分為兩種：液態潤滑和固態潤滑。而在微機電領域中，因為尺寸大幅縮小造成的尺寸效應使液體的黏滯性對微小元件影響嚴重，因而微機電領域中只能使用固態潤滑，且在微機電元件中，微小顆粒可能會造成電路短路，所以微機電領域中之潤滑方式為硬質鍍膜。

而對使用硬質薄膜做磨耗保護之文獻中，可依應用尺寸大小分類為巨觀磨耗保護[2-4]，與微觀磨耗保護[5,6]。

### 1.2.1. 巨觀磨耗保護

巨觀尺度常見的磨耗有三種：滾動磨耗、滑行磨耗、碰撞磨耗，僅分述如下：

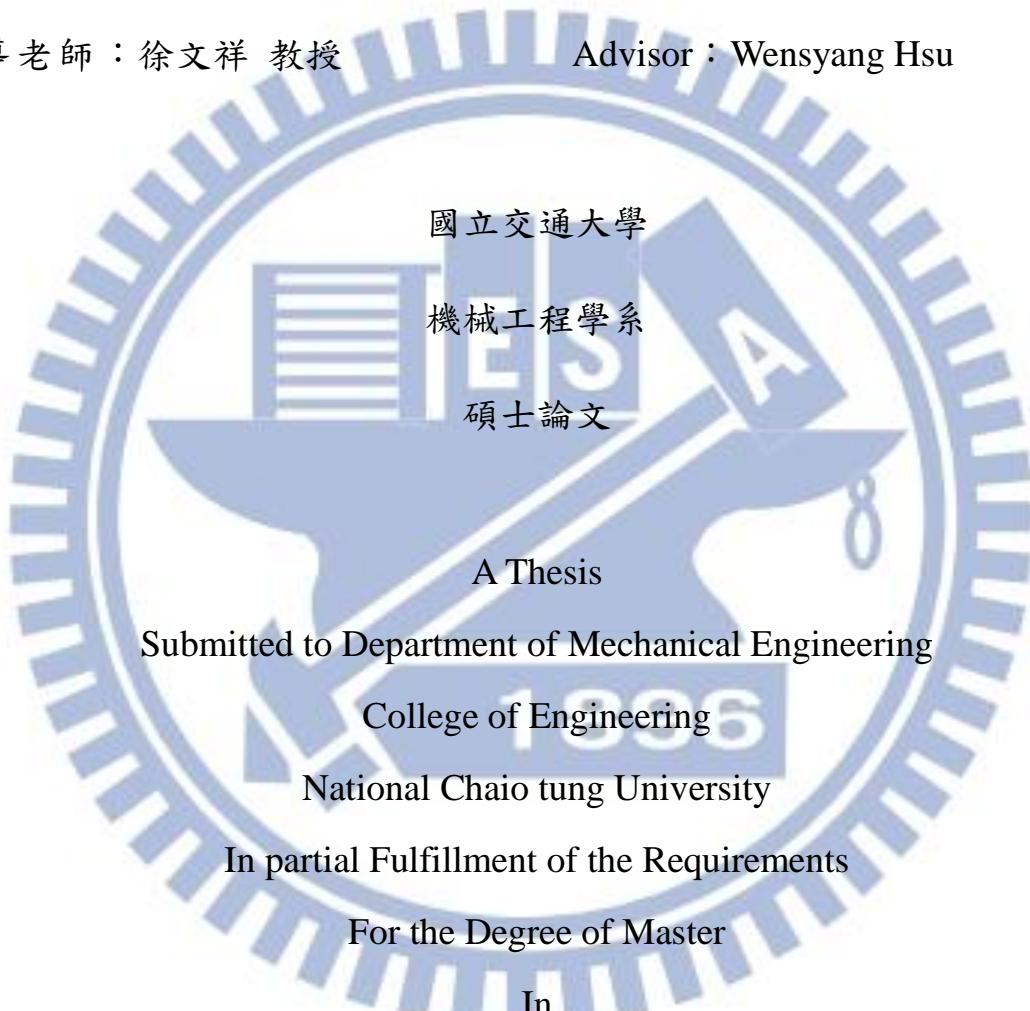

SAVAN 等人在 1993 年將使用於馬達上之轉滾珠軸承，AISI-400C 金屬滾珠鍍上碳化鈦[1]，進行實際驗證，如圖 1 (a)所示鍍上碳化鈦之滾珠軸承的馬達可降低明顯低馬達轉動阻力，並提高滾珠軸承壽命，圖 1 (b)為比較有無鍍膜對平均消耗功率之影響，其中無鍍膜之滾珠軸承馬達平均消耗功率為  $10.9 \text{ mW}$ ，而鍍上碳化鈦之滾珠軸承馬達平均消耗功率為  $6.2 \text{ mW}$ ，由此可知，鍍上碳化鈦可大幅降低馬達阻力與消耗功率。

圖 1 有鍍膜與無鍍膜之滾珠軸承(a)馬達轉動扭矩圖(b)平均消耗功率

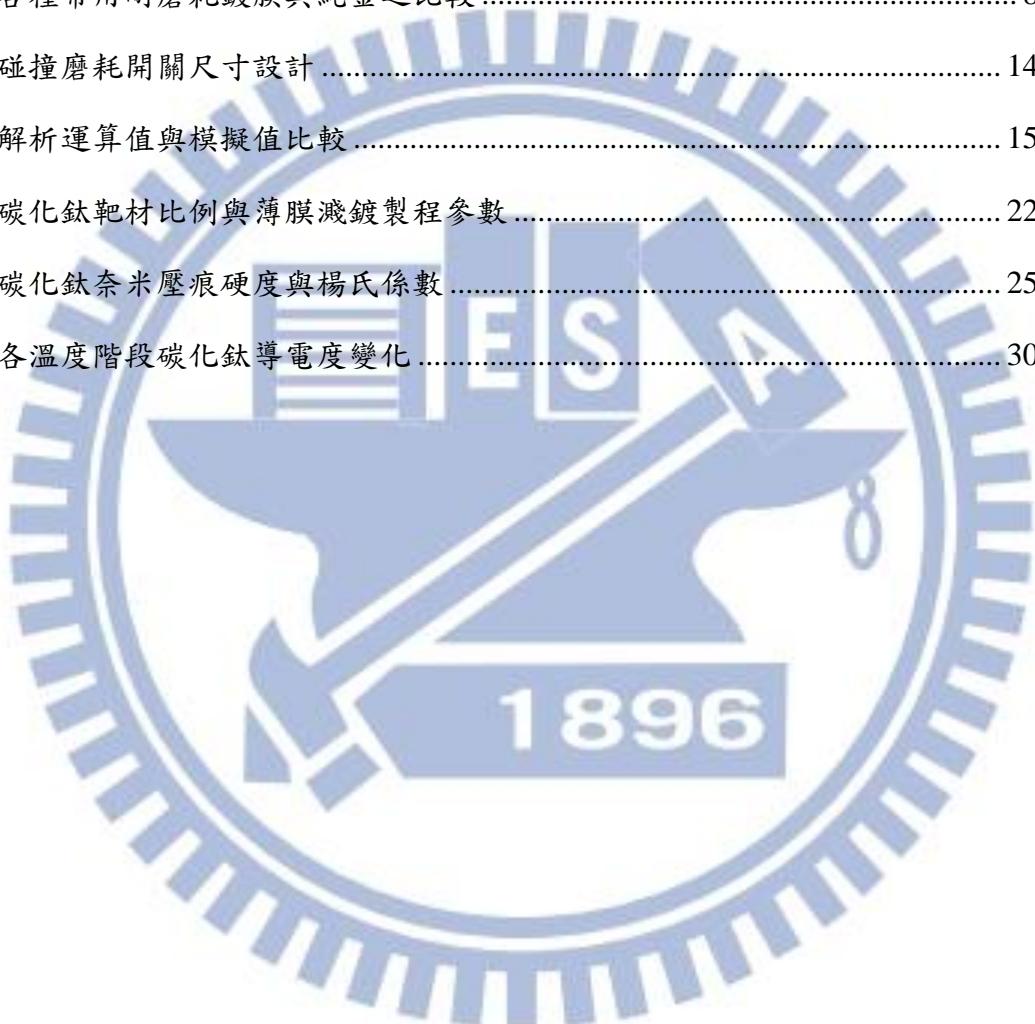

Zeghni 等人在 2004 年研究以濺鍍方式將 D2、D3 兩種工具鋼上均濺鍍氮化鈦、碳化鈦兩種硬質保護鍍膜[2]，並比較其耐磨特性，及基材硬度對薄膜之影響，其結果如圖 2 (a)，碳化鈦鍍膜比碳化氮鍍膜在抗磨耗能力上較強，而由圖 2 與表 1 相對照，則可看出基材之硬度會對薄膜硬度、耐磨耗程度有些微的影響。

圖 2 碳化鈦、氮化鈦二種鍍膜於 D2、D3 工具鋼(a)碳化鈦與氮化鈦在不同工具鋼上之耐磨耗比較 (b)基材硬度對鍍膜硬度之影響長方圖

表 1 D2、D3 工具鋼硬度表

| 工具鋼     | 硬度(Rc) |

|---------|--------|

| AISI D2 | 63     |

| AISI D3 | 60     |

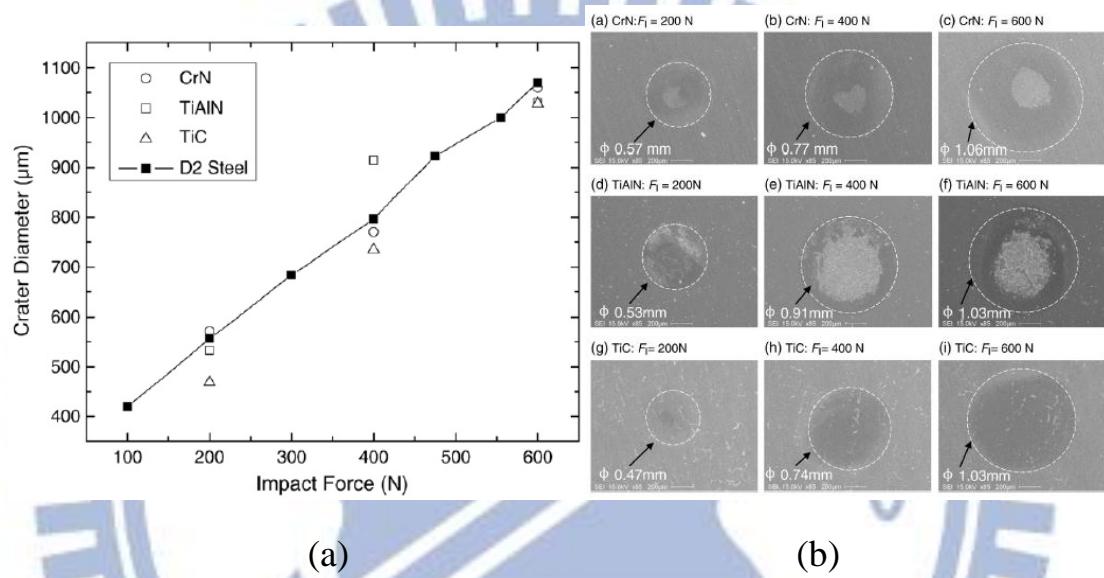

Su 等人在 2010 年，利用 PVD、CVD 製程在 D2 工具鋼上製備 CrN、TiAlN、TiC 等薄膜[3]，薄膜參數如表 2，並利用 ball-on-plate 測試機做撞擊試驗，並比較三種鍍膜之抗撞擊程度，其所得之結果如圖 3 所示，圖 3(a)為撞擊凹痕之直徑與施加負載之作圖，可發現碳化鈦的凹痕直徑在三種薄膜中是最小的，圖 3(b)為撞擊點之放大圖，圓圈中白色部分為薄膜受撞擊後所產生的缺陷，由此可看出碳化鈦在受撞擊時的抵抗力要高於其餘兩種薄膜。

表 2 三種薄膜特性參數

| 鍍膜種類 | 鍍膜厚度(μm) | 布氏硬度(GPa) | 維克氏硬度(GPa) | 楊氏係數(GPa) |

|------|----------|-----------|------------|-----------|

| 氮化鉻  | 7.1      | 18.9      | 18.2       | 312.1     |

| 氮化鋁鈦 | 2.9      | 29.7      | 26.2       | 315.9     |

| 碳化鈦  | 9.2      | 29.4      | 28.4       | 305.2     |

圖 3 薄膜耐撞擊實驗(a)撞擊凹痕直徑與施加負載之作圖(b)撞擊點造成之表面缺陷

### 1.2.2. 微觀磨耗保護

微觀尺度常見的磨耗有兩種：滑行磨耗、碰撞磨耗，僅分述如下：

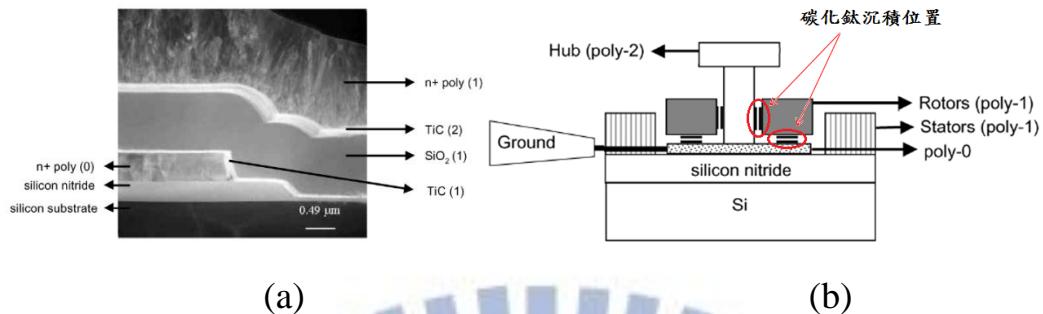

Radhakrishnan 等人在 2002 年，使用 MUMPS 製程過程中加入兩道階梯覆蓋性高之特殊鍍膜製程(PLD，pulsed laser deposition)沉積碳化鈦耐磨耗層[4]，應用於微機電馬達製程中減少其磨耗，如圖 4 所示，但研究中缺少量化分析。

圖 4 MUMPS 製程結構與微機電馬達(a)MUMPS 製程中加入兩層碳化鈦薄膜(b)碳化鈦應用於微機電馬達示意圖

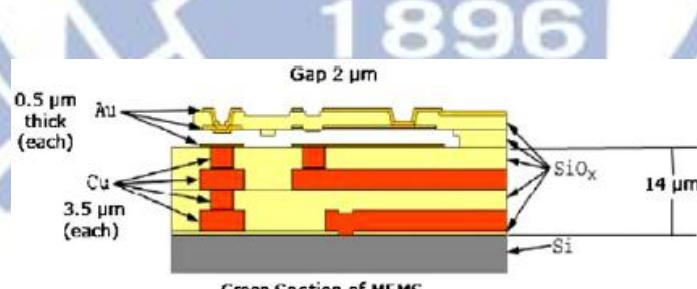

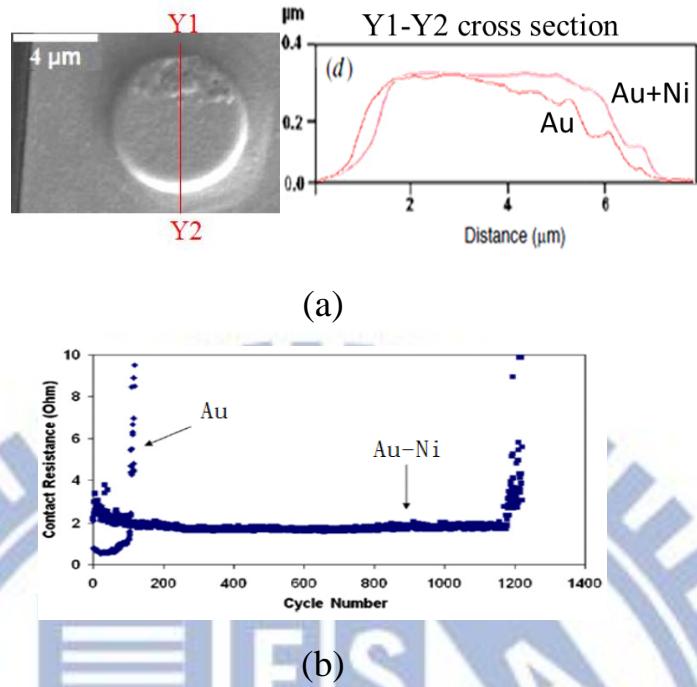

Yang 等人在 2007 年,於 RF switch 中,如圖 5,鍍上純金(pure Au)之抗氧化接觸電極參入 20% 鎳(Nickle)[5]，以克服原始純金接觸電極剛性不足，提升耐磨耗能力，如圖 6，此種強化磨耗方式優點為接觸端仍然為金屬，可降低接觸阻值，如表 3 所示，但對磨耗之抵抗能力提升有限。

圖 5 RF switch

圖 6 電擊耐磨耗實驗圖(a)上電極經接觸磨耗後電極 Y1-Y2 剖面圖(b)

加入 20% 鎳對使用壽命之增長

表 3 加入 20% 鎳對電極之影響

| 鎳含量(at. %) | 導電率( $\mu\Omega\text{-cm}$ ) | 硬度(GPa) | 理論值阻抗( $\Omega$ ) | 量測阻抗( $\Omega$ ) |

|------------|------------------------------|---------|-------------------|------------------|

| 0          | 3.8                          | 2.7     | 0.14              | 0.16~0.2         |

| 20         | 20.5                         | 6.1     | 0.6               | 0.9~1            |

### 1.2.3. 鍍膜選擇

表 4 中為常用於耐磨耗之鍍膜特性，其中碳化鈦在硬度、摩擦係數、導電率等方面均有不錯的表現，而氮化鋁鈦雖然硬度、摩擦係數與碳化鈦差異不大，但其導電率以及靶材價格則略為高於碳化鈦，且氮化鋁鈦在製程時組成比例較難控制，製成穩定性差，不易控制。

表 4 各種常用耐磨耗鍍膜與純金之比較

| 薄膜種類  | 硬度(GPa)                                    | 摩擦係數                                     | 導電率( $\mu\Omega\text{-cm}$ ) | 氧化溫度( $^{\circ}\text{C}$ )                |

|-------|--------------------------------------------|------------------------------------------|------------------------------|-------------------------------------------|

| 純金    | 2.7 <sup>[5]</sup>                         | 0.5 <sup>[14]</sup>                      | 3.8 <sup>[5]</sup>           | —                                         |

| TiC   | 23.64 <sup>[9]</sup> , 28.4 <sup>[5]</sup> | 0.28 <sup>[9]</sup>                      | 60~250 <sup>[6]</sup>        | 750 <sup>[12]</sup>                       |

| TiN   | 11.02 <sup>[9]</sup>                       | 0.3 <sup>[8]</sup> , 0.33 <sup>[9]</sup> | 270 <sup>[7]</sup>           | 900 <sup>[12]</sup> , 600 <sup>[13]</sup> |

| TiCN  | 14.09 <sup>[9]</sup>                       | 0.3 <sup>[8]</sup> , 0.4 <sup>[9]</sup>  | —                            | 600 <sup>[13]</sup>                       |

| CrN   | 18.2 <sup>[3]</sup>                        | 0.55 <sup>[8]</sup>                      | 50 <sup>[10]</sup>           | 800 <sup>[13]</sup>                       |

| TiAlN | 26.2 <sup>[3]</sup>                        | 0.2 <sup>[8]</sup>                       | 300 <sup>[11]</sup>          | 800 <sup>[13]</sup>                       |

### 1.3 研究目標

圖 7(a)為本實驗室所開發設計之鎳基卡桿式碰撞開關[15]，受慣性力作用時，懸臂樑與固定電極(卡桿)發生碰撞，並經慣性力量翻上固定電極，如圖 7(b)，這種接觸碰撞會造成懸臂樑與電極的磨損且因為整體結構均為鎳金屬，因此會有金屬氧化的現象，室溫下經長時間放置後，表面會生成鎳的氧化物，造成開關接觸阻值增大等問題，有鑑於這些問題，提升元件耐磨性及抗氧化性就變得很重要。

因此本文之目標為降低微機電碰撞開關元件之磨耗、延緩元件氧化速率、增加元件之工作壽命。而碳化鈦鍍膜可以有效改善接觸面間的磨耗問題，且文獻多為薄膜材料基本特性分析，微機電元件中無應用碳化鈦薄膜做碰撞防護之相關文獻，故本研究採用碳化鈦薄膜，並進行碳化鈦薄膜基本性質之分析，以及應用碳化鈦薄膜於設計的測試

元件上探討薄膜對元件的保護效果。

(a)

(b)

圖 7 卡桿式鎳基加速度開關(a)卡桿式鎳基開關上視圖(b)受慣性力作用圖

## 第二章 測試結構設計

### 2.1 測試元件概念設計

元件設計分為 2 部分，分別是碰撞懸臂樑與“ㄇ”字型上蓋，碰撞懸臂樑是修改本實驗室所開發之非卡榫式加速度開關[15]的設計參數而成，並為方便觀察，加入“ㄇ”字型上蓋，將原始非卡榫式左右碰撞方式改為上下碰撞。

碰撞懸臂樑結構如圖 8(a)所示，此矽基開關將採用 DRIE 乾蝕刻製程製作，並在原有鈦/銅導電層上，直接濺鍍上碳化鈦保護膜。

“ㄇ”字型上蓋結構如圖 8(b)，此上蓋同樣採用 DRIE 乾蝕刻製程製作，並濺鍍上鈦/銅導電層上及碳化鈦保護膜。

將製作完成之上蓋蓋於碰撞懸臂樑上方如圖 8(c)，即可進行碰撞磨耗測試。

圖 8 測試元件架構圖(a)碰撞懸臂樑結構圖(b)“U”字型上蓋圖(c)測試元件組合圖

## 2.2 碰撞懸臂樑理論分析

碰撞懸臂樑可分成三段利用材料力學估算整體懸臂樑的受力狀態，如圖 9 為碰撞懸臂樑靜態模型，實線和虛線分別為結構變形前與變形後的形狀，其中  $W$  即為慣性力， $P$  為與上蓋碰撞之反力， $\Delta y$  為懸臂樑變形量。

圖 9 碰撞懸臂樑之靜態分析模型

此靜態模型可由卡氏第二定理推算出整體懸臂樑之末端的位移

量  $\Delta y$  :

$$\Delta y = \frac{\partial U}{\partial P}$$

公式中，U 為總應變能為懸臂樑應變能之和，P 碰撞反力，總應變能 U 可由下式表示：

$$U = \int_0^a \frac{M(x)^2}{2EI_1} + \int_0^b \frac{M(x)^2}{2EI_2} + \int_0^c \frac{M(x)^2}{2EI_3}$$

公式中，E 為楊氏係數，I 為慣性矩。

當總應變能以對 P 偏微分後，將虛設力  $P=0$ ，即可得到懸臂樑之末端位移  $\Delta y$ ，因此在固定加速度下，即可利用修改  $\Delta y$  求出懸臂樑參數。

## 2.3 測試元件細部設計

由於施加於元件的加速度受到機台極限 50G 之限制，因此元件將以施加 17G 加速度時懸臂樑位移量達到  $70\mu\text{m}$  為條件來進行設計，經過 Matlab 進行解析解運算後，決定修改過之測試元件幾何尺寸如圖 10 (a) 所示，上蓋如圖 10 (b) 所示。尺寸值則如表 5 所示。

圖 10 碰撞磨耗尺寸標註圖(a)非卡榫式開關(b)“匚”字形上蓋

表 5 碰撞磨耗開關尺寸設計

|                                 |       |         |

|---------------------------------|-------|---------|

| 碰撞懸臂樑<br>(單位： $\mu\text{m}$ )   | L1    | 1600    |

|                                 | L2    | 300     |

|                                 | W1    | 20      |

|                                 | W2    | 10      |

|                                 | 懸臂樑厚度 | 10      |

|                                 | P     | 1100    |

|                                 | 碳化鈦厚度 | 由實驗測試   |

| “匱”字形上蓋<br>(單位： $\mu\text{m}$ ) | L     | 10000   |

|                                 | K1    | 12000   |

|                                 | K2    | 15000   |

|                                 | D1    | 500~550 |

|                                 | D2    | 1000    |

|                                 | 碳化鈦厚度 | 由實驗測試   |

## 2.4 ANSYS 模擬

將碰撞懸臂樑經過解析解運算後的元件尺寸輸入 ANSYS 以 17G 加速度來模擬懸臂樑變形，圖 11 為 ANSYS 模擬懸臂樑之變形量。由表 6 解析解與 ANSYS 模擬懸臂樑末端位移量值之比較可看出解析解與模擬值很接近，因此可驗證所設計的這組結構尺寸的可行性。

圖 11 碰撞懸臂樑 ANSYS 結構變形量模擬

表 6 解析運算值與模擬值比較

|           | 末端位移量值(μm) |

|-----------|------------|

| 解析解運算值    | 69.826     |

| ANSYS 模擬值 | 69.932     |

## 第三章 製程與量測

### 3.1 碰撞懸臂樑製程規劃

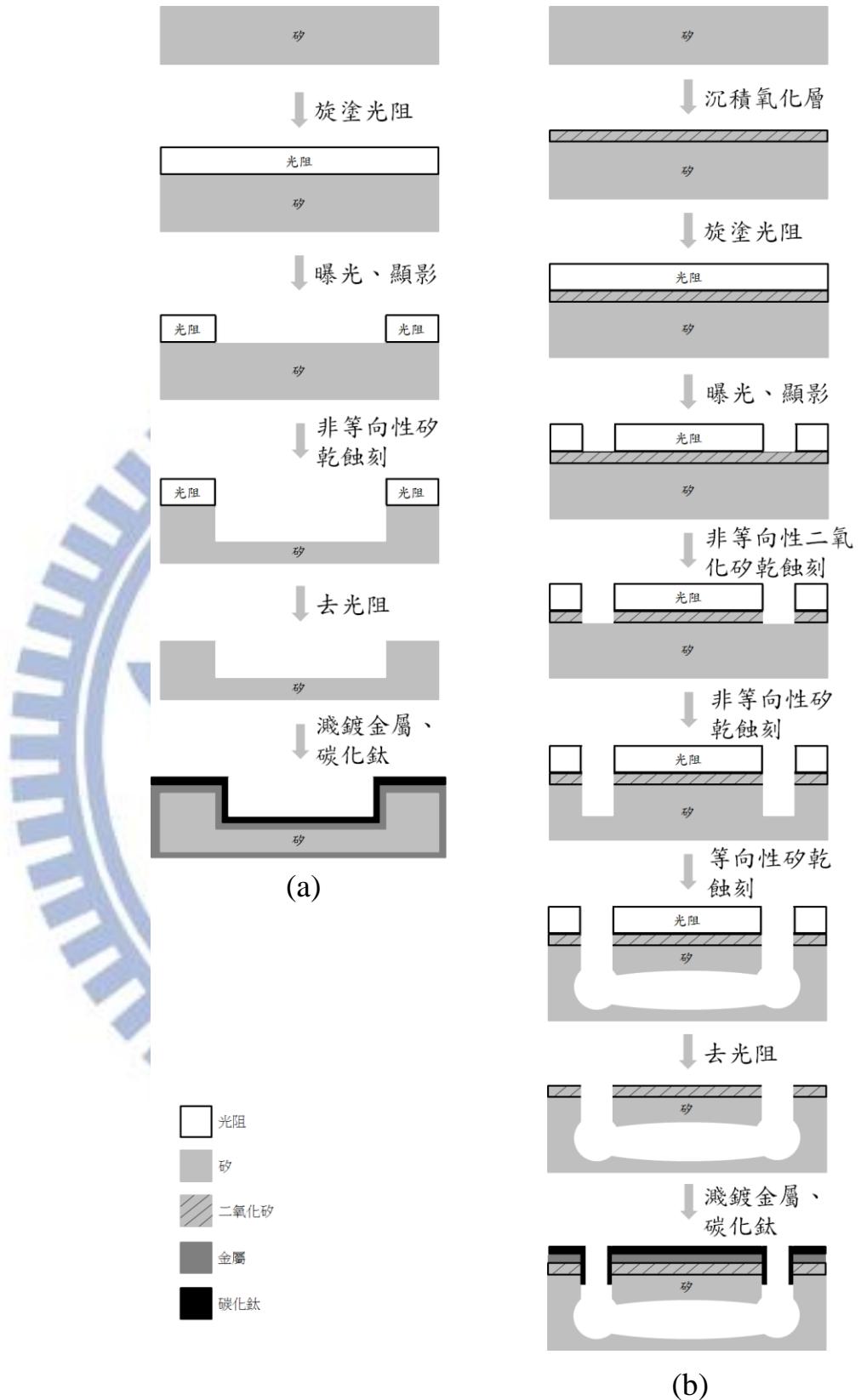

碰撞懸臂樑製程分為兩部分，第一部分為上蓋製作，第二部分為碰撞元件製作。

第一部分上蓋製作主要為將特殊規格( $1000\mu\text{m}$ )之 P-type 的矽晶圓以深蝕刻(DRIE)製程搭配光罩建立出的蝕刻孔，進行非等向性乾蝕刻，製程流程如下：

步驟 1：在 P-type 矽晶圓上旋塗光阻。

步驟 2：曝光顯影。

步驟 3：對矽非等向性蝕刻。

步驟 4：去光阻。

步驟 5：濺鍍鈦/銅金屬及碳化鈦保護膜。

製程流程示意如圖 12(a)。

第二部分碰撞元件部分主要是利用深蝕刻(DRIE)製程製作懸浮結構，採用 P-type 的矽晶圓進行非等向性乾蝕刻及等向性乾蝕刻。

P-type 的矽晶圓進行 ICP 深蝕刻及側向乾蝕刻，製程流程如下：

步驟 1：在 P-type 矽晶圓上沉積二氧化矽層。

步驟 2：旋塗光阻。

步驟 3：曝光顯影。

步驟 4：對氧化矽非等向性蝕刻。

步驟 5：對矽非等向性蝕刻。

步驟 6：對矽等向性蝕刻。

步驟 7：去光阻。

步驟 8：濺鍍鈦/銅金屬及碳化鈦保護膜。

製程流程示意圖如圖 12(b)所示：

圖 12 碰撞懸臂樑製程規劃(a)上蓋製程(b)懸浮碰撞元件製程

### 3.2 製程結果

測試元件製程結果分為上蓋與碰撞懸臂樑，2部分都是以矽為主結構，經過蝕刻製程製作而成，且在製作好的上蓋與懸臂樑上濺鍍鈦/銅金屬層增加導電性後，再濺鍍碳化鈦鍍膜或鎳金屬鍍膜。

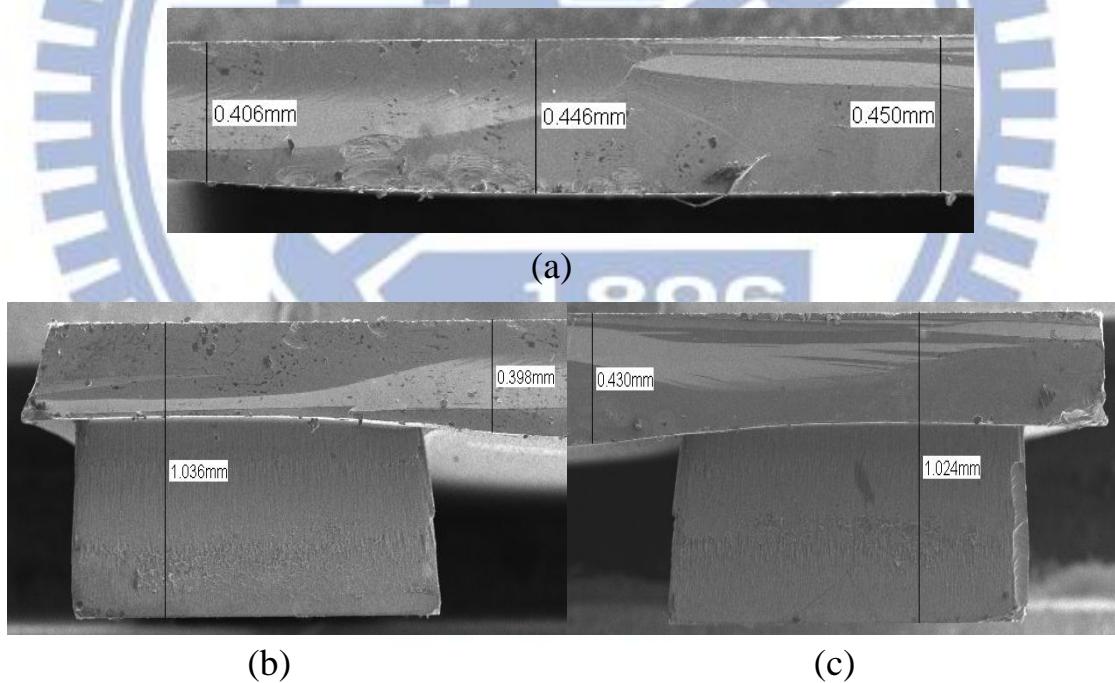

#### 3.2.1. 上蓋

由圖 13(a)可看出上蓋製程厚度與設計值誤差在 0.5% 以內，但由圖 13(b)、(c)中可看出在”ㄇ字型”內側凹陷處的兩端厚度較薄，可能原因為蝕刻氣體於角落流量分布不均勻所導致。

圖 13 上蓋製程結果

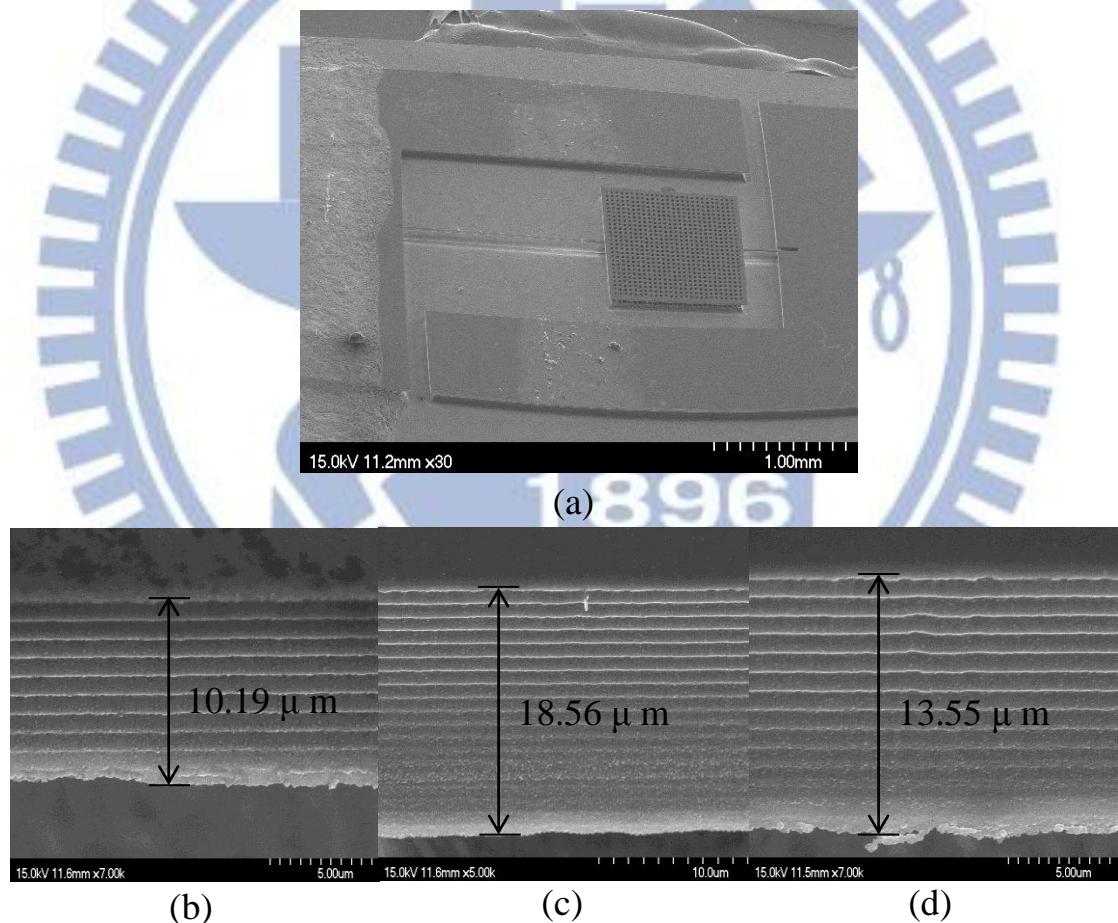

### 3.2.2. 碰撞懸臂樑

由圖 14(a)為懸臂樑整體結構製程結果，圖 14(b)、(c)、(d)分別為懸臂樑  $L_1$ 、 $P$ 、 $L_2$  三段的製程厚度，可看出三段懸臂樑厚度與設計值誤差約在 1.9%、85.56%、35.5%，製程誤差可能原因為，空氣流動區域面積較小，因此在做乾式蝕刻時蝕刻氣體進出較不易，因此蝕刻速率較慢厚度較厚。

圖 14 碰撞懸臂樑製程結果 SEM 圖

### 3.3 量測

量測部分將分為兩部分，分別為碳化鈦濺鍍於基板上，量測薄膜物理特性，以及碳化鈦濺鍍於元件上，量測鍍上薄膜前後元件之性能變化。

#### 3.3.1. 沉積於基板量測濺鍍速率

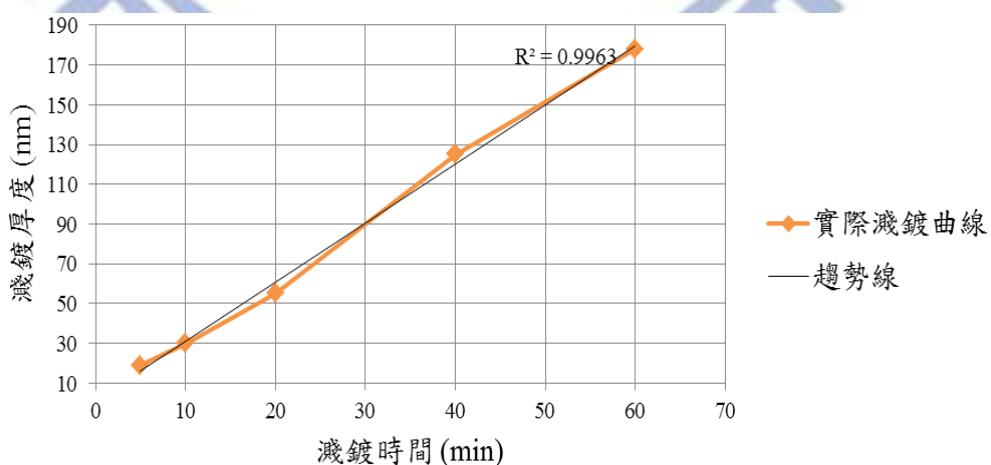

在沉積碳化鈦和鈦/銅薄膜時，將使用本實驗室之真空濺鍍機如圖 15(a)，來製備碳化鈦薄膜，碳化鈦靶材鈦與碳之比例參 Stüber 等人[16]所提出之比例，詳細靶材比例及濺鍍參數如表 7，但在濺鍍過程中由於儀器之限制，無法即時的獲知沉積厚度等參數，因此分別濺鍍 5、10、20、40、60 分鐘的碳化鈦鍍膜，並以本實驗室之表面粗糙度量測儀如圖 15 (b)，量測其薄膜沉積厚度並繪製時間與厚度曲線關係，結果如圖 16，可看出濺鍍時間與濺鍍厚度呈近乎線性關係，而線性的沉積速率可讓未來薄膜沉積於碰撞元件上的厚度控制更為精準。

表 7 碳化鈦靶材比例與薄膜濺鍍製程參數

|             |              |        |

|-------------|--------------|--------|

| 靶材比例        | 鈦 (Titanium) | 41.2%  |

|             | 碳 (Carbon)   | 58.8%  |

| 通入製程氣體      | 氣體種類         | Ar     |

|             | 氣體流量(sccm)   | 20     |

|             | 氣體壓力(m torr) | 4.5    |

| 濺鍍目標物       | 旋轉速度         | 20 rpm |

| 濺鍍靶材 DC Gun | 電流(A)        | 0.39   |

|             | 電壓(V)        | 280    |

|             | 功率(W)        | 100    |

圖 15 薄膜製程、量測機台(a)真空濺鍍機(b)表面粗糙度量測儀

圖 16 濺鍍時間與厚度關係

### 3.3.2. 沉積於基板量測表面成份

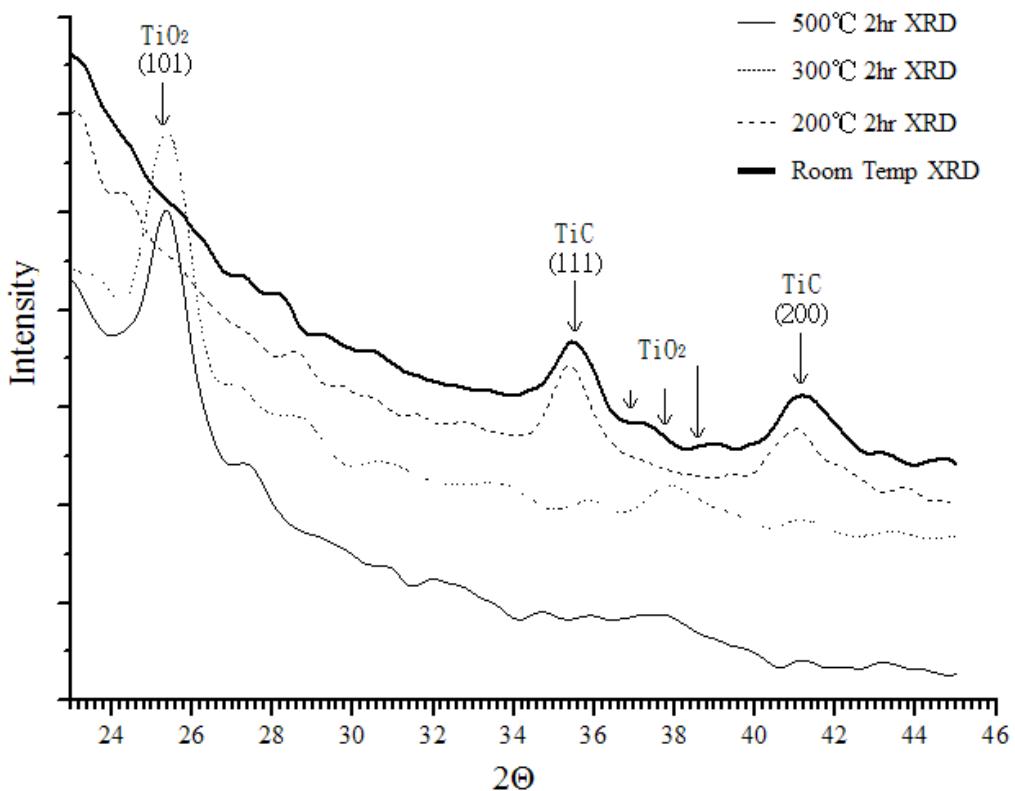

碳化鈦薄膜雖使用以固定比例燒熔之靶材做為濺鍍材料，但是當碳化鈦沉積時，薄膜成分會受腔體壓力、氣體流量、沉積速率……等環境因素所影響，因此為使薄膜受製程因素所影響之誤差降低，將使用奈米科技中心之 X 光繞射儀 (XRD, X-ray diffraction)，如圖 17，做薄膜表面成分之檢測，用以做為修改製程參數之考量。

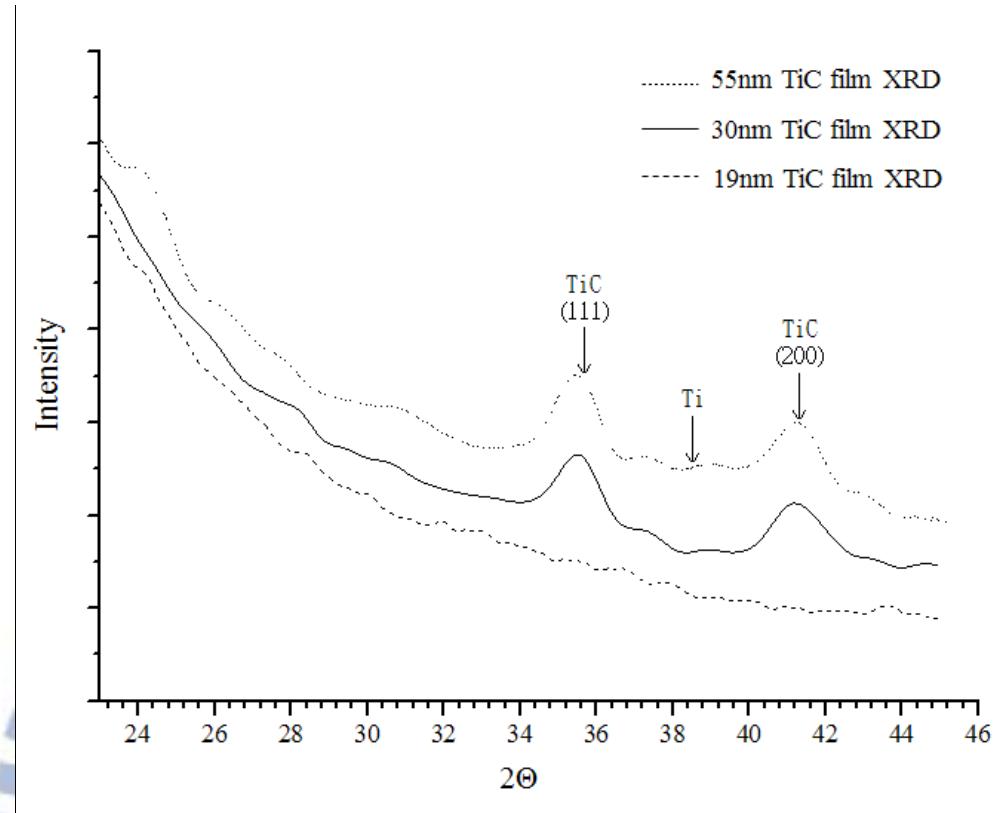

作為表面成分分析之試片為在矽晶圓上濺鍍 19、30、55 奈米之碳化鈦薄膜，但 19 奈米薄膜因沉積厚度不足鍍膜材料尚未形成結晶故 XRD 無反應，而 30 奈米 XRD 與 55 奈米薄膜有形成結晶，且結果一致如圖 18，圖中可看出濺鍍出的薄膜峰值出現位置成份為碳化鈦，並且峰值位置相較於箭頭位置(鈦:碳=50:50)有出現稍微向左平移的現象，參考 Voevodin 等人[17]的研究，可得知濺鍍出的薄膜成分比例約為 42% 鈦:58% 碳，薄膜比例與靶材比例約略一致。

圖 17 能量散射光譜儀

圖 18 30 奈米碳化鈦薄膜 XRD 成份分析

### 3.3.3. 沉積於基板量測薄膜硬度與刮痕磨耗

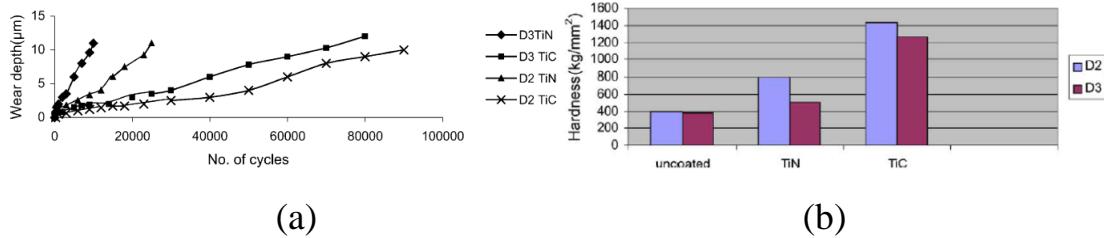

碳化鈦薄膜之硬度對其碰撞保護有重要的影響，且薄膜的楊氏係數亦會影響元件表現，因此在沉積薄膜後，使用奈米壓痕機(Nano Indenter)來測量實際薄膜硬度與楊氏係數，其結果由實驗得到之實際硬度與楊氏係數如表 8，由表中可看出碳化鈦鍍膜硬度為 16.7GPa，比鎳金屬的 4.9GPa 高出 3 倍左右，但低於文獻中的 23.64<sup>[9]</sup>，可能是因為製程參數不同造成。

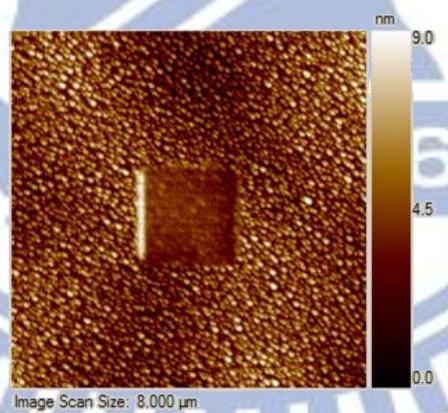

刮痕磨耗是利用奈米壓痕機探針施加固定力量，在固定範圍內反

覆磨耗，待有明顯刮痕時，再以原子力顯微鏡(AFM, Atomic force microscopy)掃描刮痕磨損區域，如圖 19，利用磨損痕區域之表面輪廓推算移除深度，計算公式如下：

$$\text{單位磨損深度} = \frac{\text{總磨損深度}}{\text{刮痕距離}}$$

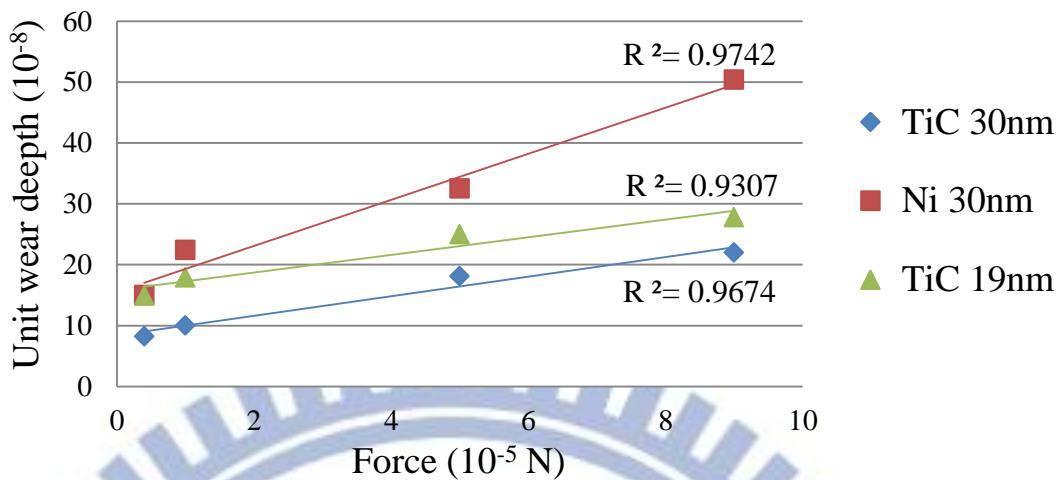

由於在不同探針力量下有不同的磨損深度，經計算後，單位距離的磨損深度與施加荷載作圖如圖 20，可看出力量與單位磨損深度均呈線性關係，且同為 30 奈米薄膜，在相同力量下鎳金屬的磨損深度約為碳化鈦之 2 倍，故可得知碳化鈦鍍膜在耐磨耗能力上比鎳金屬鍍膜高出 2 倍左右。

圖 19 奈米刮痕磨耗 AFM 掃描圖

表 8 碳化鈦奈米壓痕硬度與楊氏係數

|     | 硬度 (Gpa) | 楊氏系數 (Gpa) |

|-----|----------|------------|

| 鎳   | 4.95     | 186.04     |

| 碳化鈦 | 16.74    | 197.13     |

圖 20 單位磨損深度—荷載作圖

### 3.3.4. 沉積於基板測試加熱抗氧化耐性

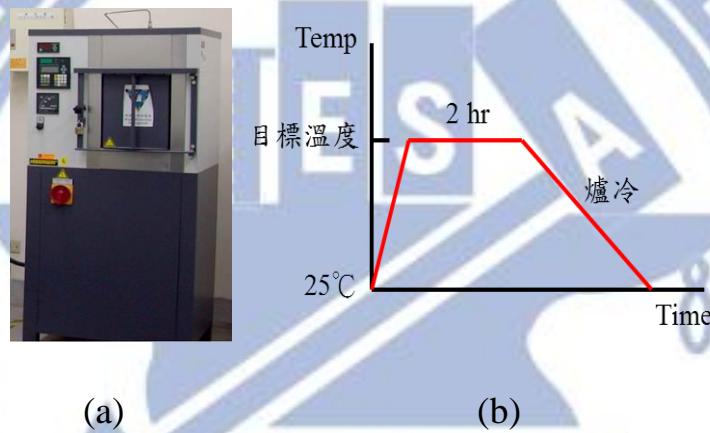

碳化鈦保護薄膜除了可以讓元件之磨耗率降低以增長元件使用壽命外，另一項對金屬結構元件重要的保護則是作為氧化保護層。作為氧化保護層，在文獻中碳化鈦在氧化保護上有不錯的表現，Mitsuo 等人對碳化鈦和氮化鈦等兩種工業中最常用之鍍膜做氧化測試[12]，得到之結果為在加熱至 750K(500°C)兩小時後，碳化鈦才氧化成二氧化鈦。

因此實驗將使用高溫爐，如圖 21(a)，來提高溫度使薄膜加速氧化，而實驗溫度則設定為 100°C、200°C、300°C、400°C、500°C，加熱方式為自由升溫至目標溫度後維持 2 小時，再以爐冷方式降溫取出試片，如圖 21(b)，並將加熱後的試片以 X 光繞射儀觀察薄膜成分變化，如

圖 22 可看出再加熱溫度在  $200^{\circ}\text{C}$  以內時薄膜成份都還只有碳化鈦峰值存在，而當溫度超過  $300^{\circ}\text{C}$  後成份峰值則轉變為二氧化鈦，因此推測碳化鈦膜再加熱超過  $300^{\circ}\text{C}$  後其薄膜應完全氧化，故碳化鈦薄膜的使用條件應在環境溫度  $200^{\circ}\text{C}$  以下，但這實驗結果與 Mitsuo 等人的  $500^{\circ}\text{C}$  有不小的差距，原因可能為 Mitsuo 等人製程方式與碳化鈦成份比例與我們不同所造成。

圖 21 加熱儀器與升溫流程(a)高溫爐(b)升溫曲線

圖 22 30 奈米碳化鈦薄膜受高溫處理後 X 光繞射曲線

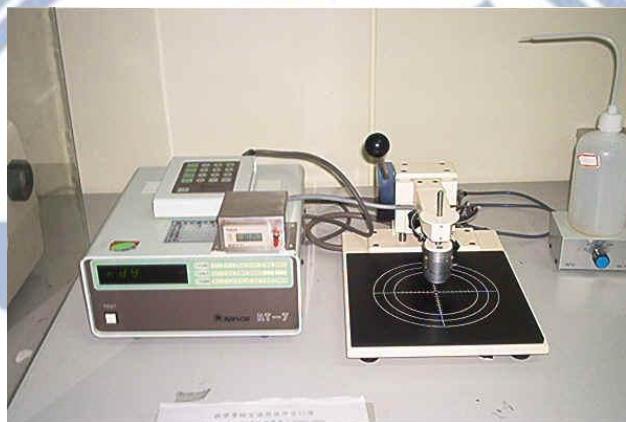

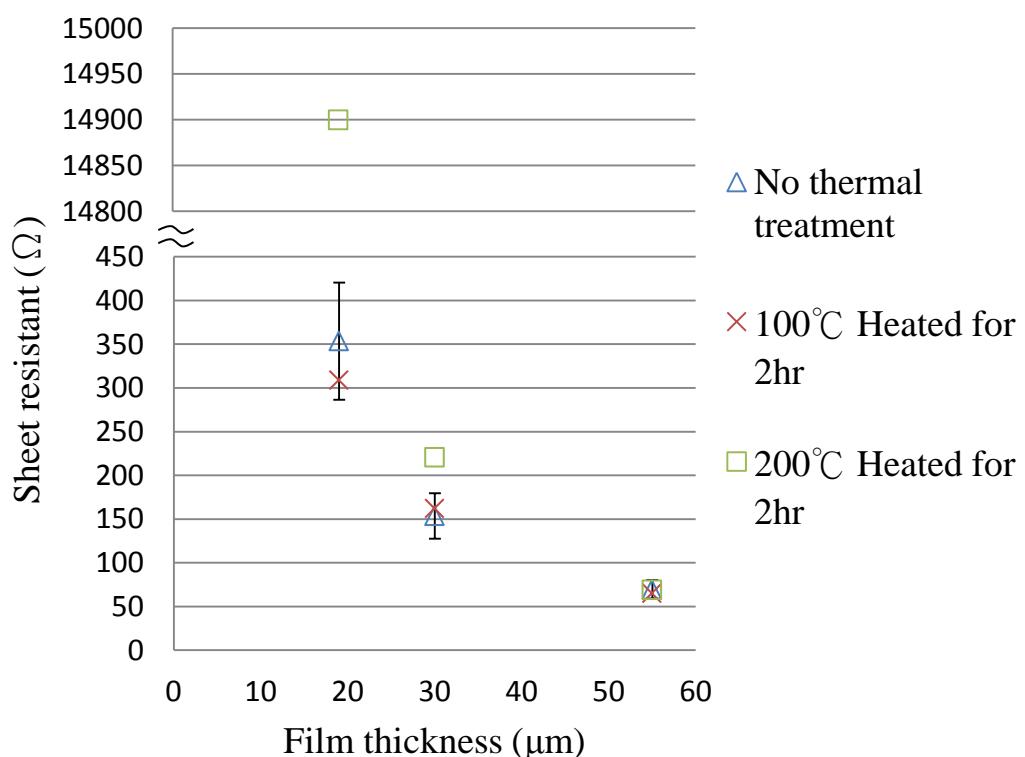

3.3.5. 沉積於基板量測導電率

加速度碰撞開關顧名思義當受加速度衝擊時，開關部分會因慣性作用與電極相碰觸，造成電路的導通發出訊號，故開關本身的導電能力也是極其重要的，在文獻[6]中已有提及碳化鈦之電阻值，但電阻值會隨著薄膜內部成分的不同、薄膜厚度、氧化……等等因素而改變，因此將使用四點探針量測平台，如圖 23，對薄膜導電率做量測並將前小節碳化鈦以 100°C、200°C、300°C、400°C、500°C 等溫度加熱過

的試片，量測其片電阻變化結果如

表 9，由表中可看到在碳化鈦薄膜加熱超過 300°C 時，所有不同厚度試片的片電阻值將趨近無限大，其原因如前小節所述應是薄膜完全氧化造成，而由圖 24 可明顯看出隨著薄膜厚度的增加，除了電阻值會降低外阻值的飄移量也會大幅下降。

圖 23 四點探針量測平台

圖 24 加熱氧化導電率變化

表 9 各溫度階段碳化鈦導電度變化

| 不同薄<br>膜厚度 | Sheet<br>resistance( $\Omega/\square$ )<br>@ 25°C | Sheet<br>resistance( $\Omega/\square$ )<br>@ 100°C 2hr | Sheet<br>resistance( $\Omega/\square$ )<br>@ 200°C 2hr | Sheet<br>resistance( $\Omega/\square$ )<br>@ 300~500°C<br>2hr |

|------------|---------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------------|

| 19 nm      | 353.5                                             | 309.2                                                  | 14.9K                                                  | N/A                                                           |

| 30 nm      | 153.4                                             | 162.5                                                  | 220.7                                                  | N/A                                                           |

| 55 nm      | 69.7                                              | 65.8                                                   | 69.3                                                   | N/A                                                           |

### 3.3.6. 沉積於元件量測使用壽命

將碳化鈦保護膜應用於碰撞開關中，最主要之目的即為希望提升元件使用壽命，因此將使用本實驗室之震盪器(shaker)，將濺鍍好薄膜的測試元件給定加速度與頻率，使元件碰撞並每間隔 5 萬次碰撞記錄其電訊號，待其電訊號量測不到時，再以掃描式電子顯微鏡(SEM, Scanning Electron Microscopy)觀察其磨損情形。

實際實驗儀器架設圖如圖 25，加速度產生則是先將碰撞開關試片黏貼於震盪器後，調整訊號產生器設定為脈衝波型，輸出至訊號放大器，再將放大過的訊號輸入震盪器轉換成固定的加速度震動，不過由於上蓋製程誤差的關係，造成每一組元件的加速度閾值會有所差異。輸出訊號則是因測試元件受震盪器固定加速度碰撞後，會使電阻值發生變化，經過自製電路的電壓轉換，可得到 0.5V~1.1V 之間的輸出訊號，再輸入電腦中繪圖。

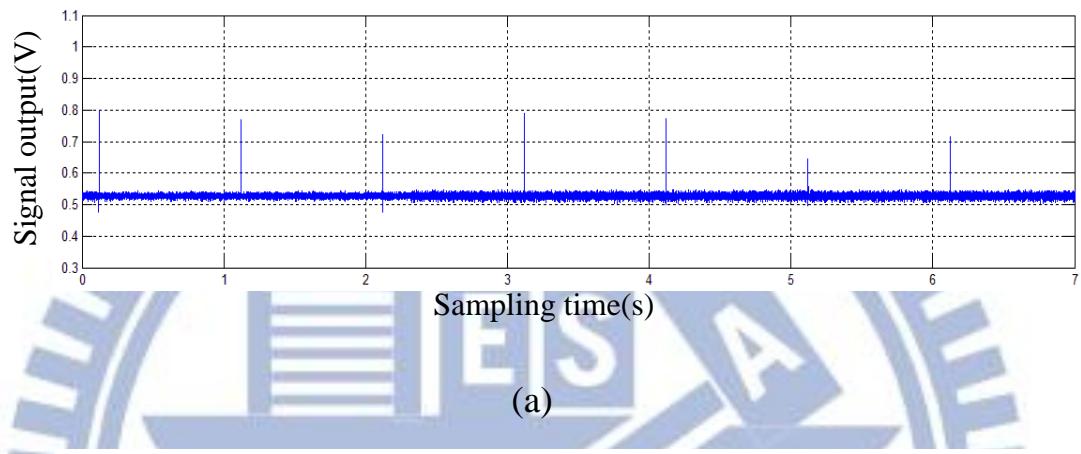

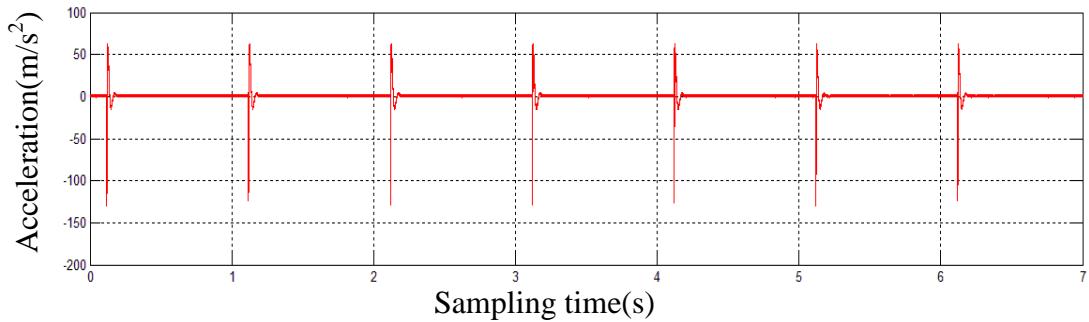

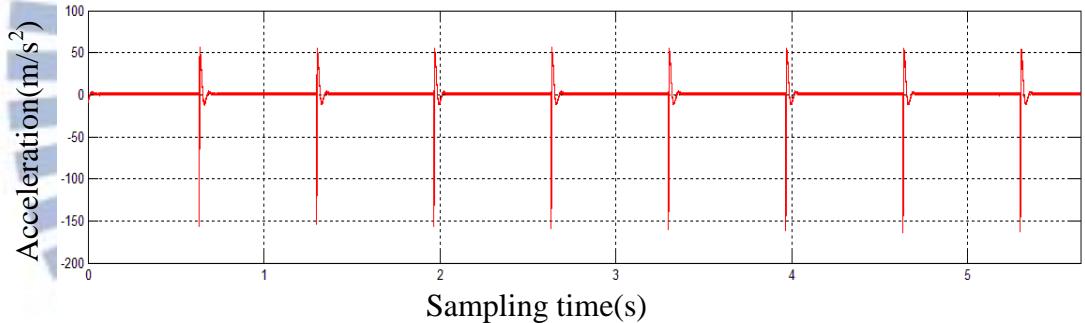

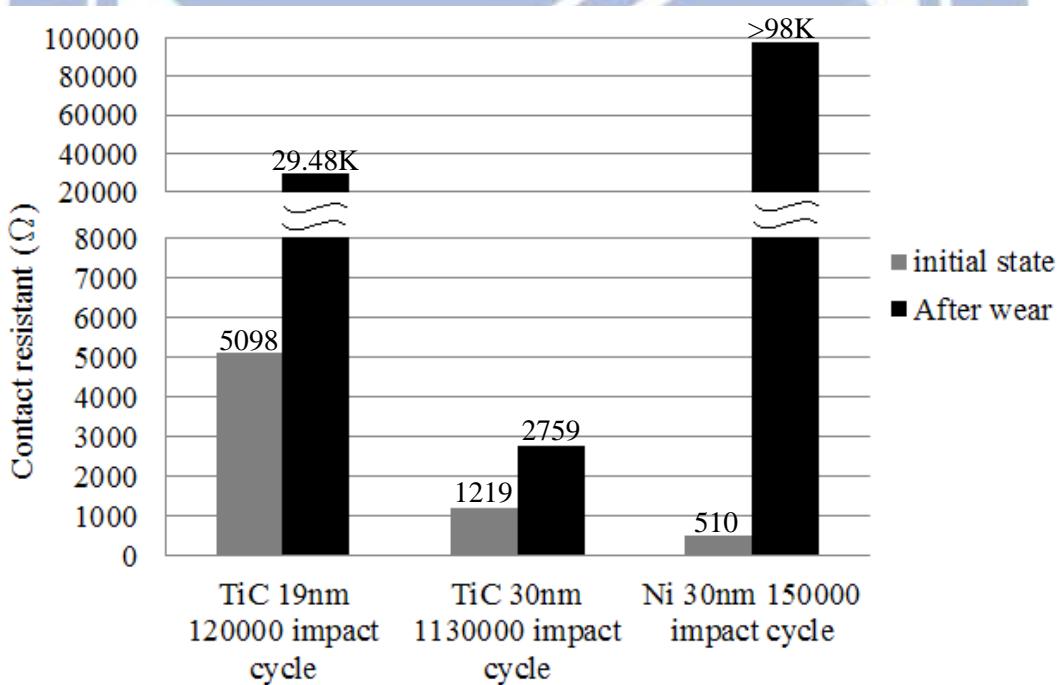

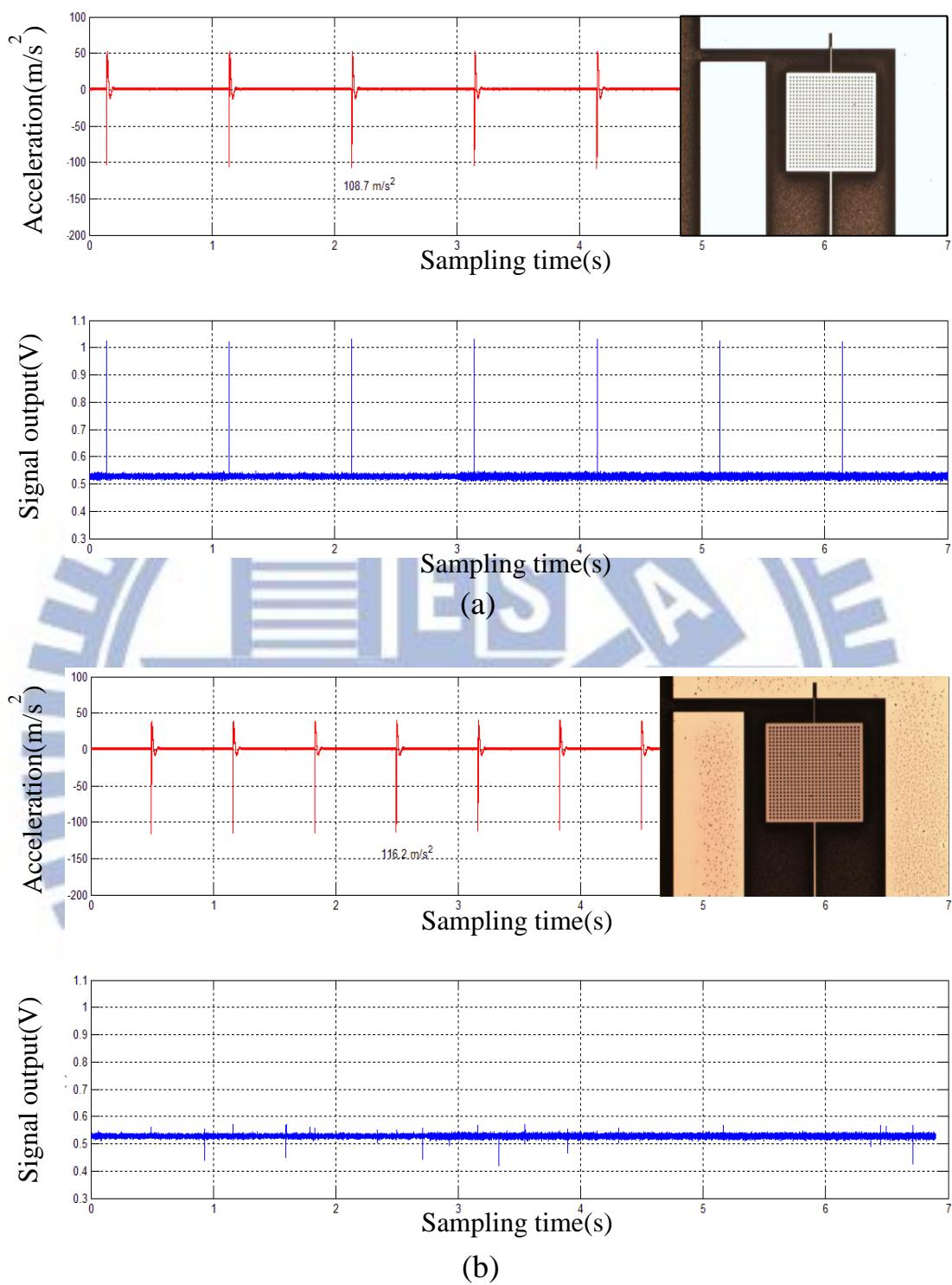

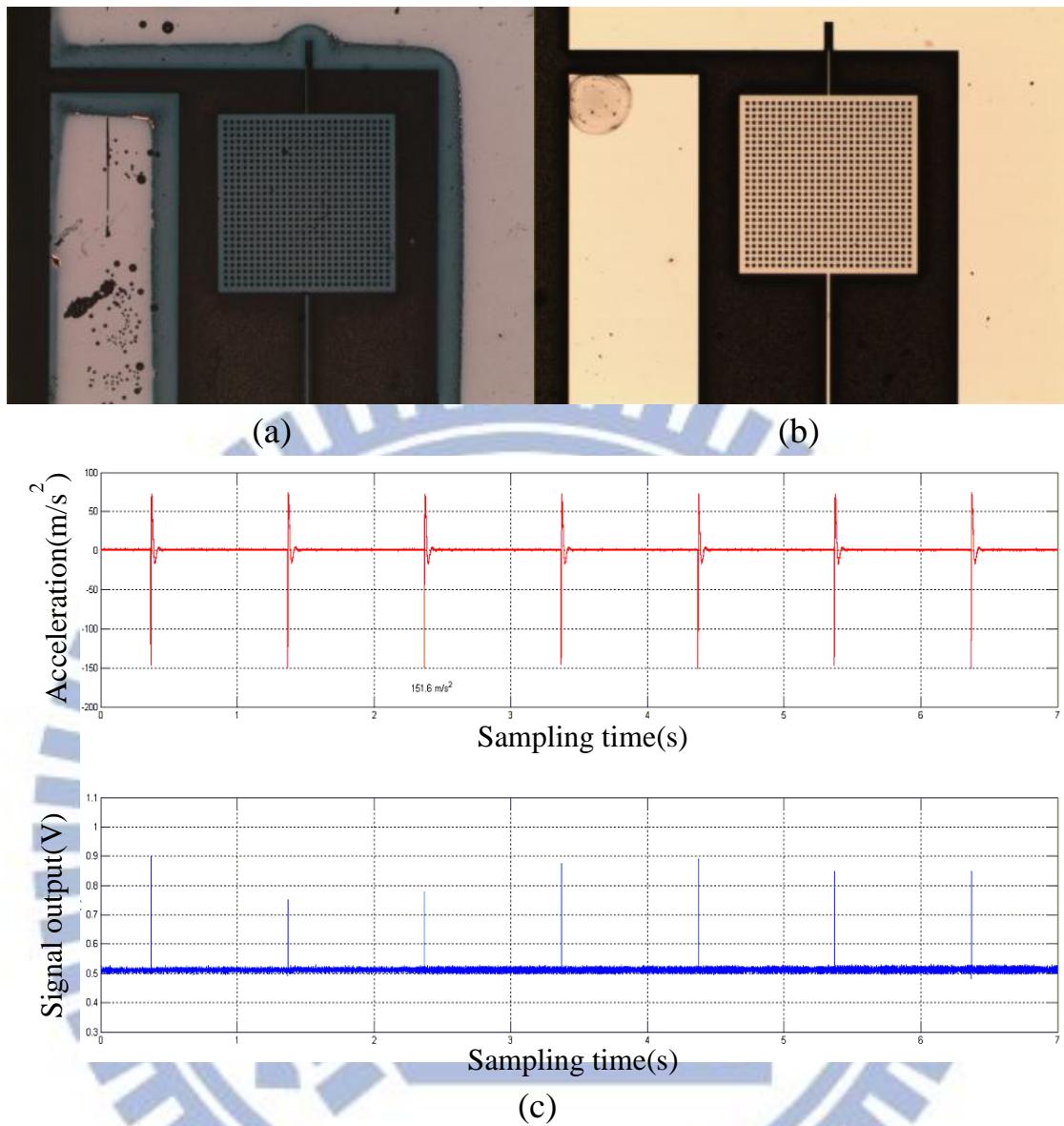

圖 26、圖 27、圖 28 為分別濺鍍 19 奈米碳化鈦、30 奈米碳化鈦、30 奈米鎳金屬薄膜的測試元件訊號圖。圖 26 為 19 奈米碳化鈦薄膜元件訊號，可看出元件初始訊號值大小不大，推測應是薄膜厚度較薄電阻值較大導致，且經過 12 萬次碰撞後訊號值已衰減至幾乎無法觀察，因此推測將薄膜加厚可以改善訊號較小問題。

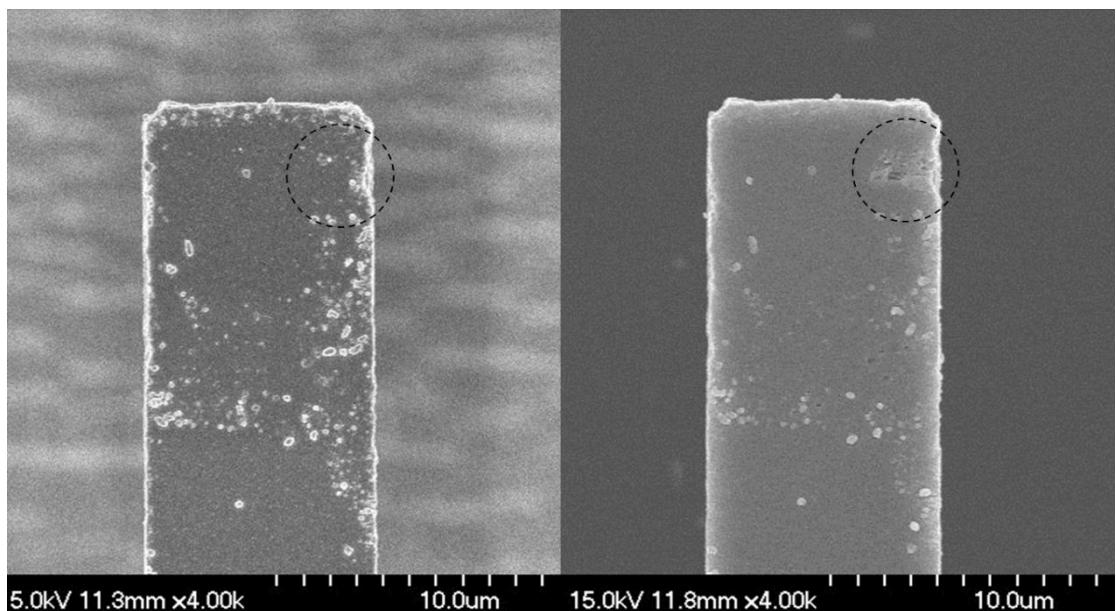

圖 27 為 30 奈米碳化鈦薄膜元件訊號，可看出元件初始訊號值比 19 奈米碳化鈦薄膜元件大，且經過 113 萬次碰撞後，元件訊號雖略有衰減但仍然存在。圖 28 為濺鍍 30 奈米鎳金屬薄膜元件，其初始訊號接近極限值，推測應是鎳金屬電阻值最低所致，但經過約 15 萬次碰撞後，其訊號衰減至無法觀察。比較圖 27 與圖 28 可看出同樣 30 奈米鍍膜，鎳金屬鍍膜的碰撞開關在初始狀態時訊號較穩定，訊號值也較大但鎳金屬鍍膜經過約 15 萬次碰撞後量測不到訊號值，而碳化鈦鍍膜經過 113 萬次碰撞後還可以量測到訊號，因次可得知相同鍍膜厚度下碳化鈦鍍膜使用壽命約高出鎳金屬鍍膜 7 倍以上。圖 29 與圖 30 為濺鍍鎳金屬之元件與濺鍍碳化鈦之元件經碰撞後的磨損 SEM 圖，可看出鍍上碳化鈦的元件懸臂樑磨損情形較輕微。

圖 25 碰撞實驗儀器架構圖(a)電源供應器(b)自製電路(c)碰撞開關(d)震盪器(e)訊號產生器(f)訊號放大器

(a)

(b)

圖 26.19 奈米碳化鈦鍍膜碰撞開關訊號(a)初始(b)經過 12 萬次磨耗

(a)

(b)

圖 27 30 奈米碳化鈦鍍膜碰撞開關訊號(a)初始(b)經過 113 萬次磨耗

(a)

(b)

圖 28 30 奈米鎳金屬鍍膜碰撞開關訊號(a)初始(b)經過 15 萬次磨耗

圖 29 30 奈米鎳金屬鍍膜 SEM 圖(a)初始狀態未碰撞(b)經過 15 萬次磨耗

圖 30 30 奈米碳化鈦鍍膜 SEM 圖(a)初始狀態未碰撞(b)經過 113 萬次磨耗

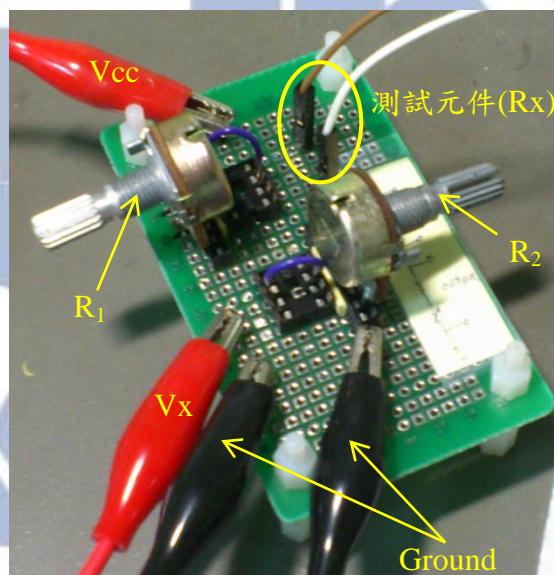

### 3.3.7. 沉積於元件量測接觸阻值

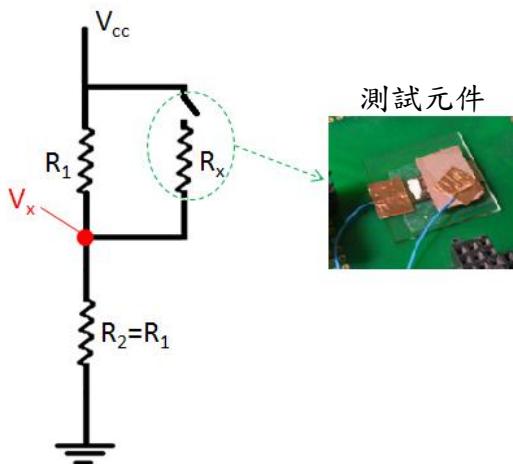

為量得開關接觸與否，因此設計一簡易量測電路來使輸出訊號因開關之狀態切換而有訊號變化，自製電路如圖 31，電路簡圖如圖 32。由於慣性開關在不同狀態下的阻值不同，可以將慣性開關視為一可變電阻，利用電路學的分壓定理以及負載效應，造成感測的  $V_x$  電壓值隨慣性開關的電阻值而變化，如圖 32 所示：

圖 31 自製訊號擷取簡易電路

圖 32 量測電路設計圖

設計與之匹配的固定電阻為  $R_1$ 、 $R_2$ ，電阻值均為 10K 歐姆，並設定  $V_{cc}$  電位為 1 伏特，所量測到的訊號值( $V_x$ )將可由相關電路公式可推出公式(1)：

$$V_x = \frac{R_2}{R_2 + (\frac{R_1 \times R_x}{R_1 + R_x})} \times V_{cc} \quad (1)$$

於理想的狀況下，受閾值加速度之前，結構不相接觸， $R_x$  電阻值為無限大，此時由於  $R_1$  電阻值與  $R_2$  相同， $V_x$  為 0.5 伏特；受閾值加速度之後，結構相接觸， $R_x$  電阻值下降，由於  $R_2$  電阻值遠大於  $R_1$  與  $R_x$  的並聯電阻，因此  $V_x$  電位會逼近  $V_{cc}$  為 1 伏特，反之，若碰撞開關磨耗後接觸阻值  $R_x$  大幅增加，則  $V_x$  量測訊號將回歸至 0.5 伏特。另外，觀察  $V_x$  變化的同時，可由公式(1)反推得知  $R_x$  接觸阻值如下：

$$R_x = \frac{(V_{cc} - V_x) \times R_1}{\frac{R_1 \times V_x}{R_2} - (V_{cc} - V_x)}$$

將實驗量測之數據帶入運算後，30 奈米碳化鈦鍍膜之初始阻值  $1219\Omega$  比同厚度鎳金屬鍍膜  $510\Omega$  大了 2.4 倍，但碰撞後鎳金屬鍍膜阻值大幅增加至  $98K\Omega$ ，導致開關無法測得訊號，而碳化鈦鍍膜之接觸阻值與始狀態約增加 2.3 倍上升至  $2759\Omega$ ，由接觸阻值推算碳化鈦鍍膜之元件使用壽命約在 400 萬次，而 19 奈米碳化鈦鍍膜之初始阻值達到  $5098\Omega$ ，且經過 12 萬次碰撞後上升至  $29.48K\Omega$ ，雖然仍有訊號，但訊號微弱。

圖 33 碰撞開關不同鍍膜接觸阻值

### 3.3.8. 沉積於元件量測耐氧化能力

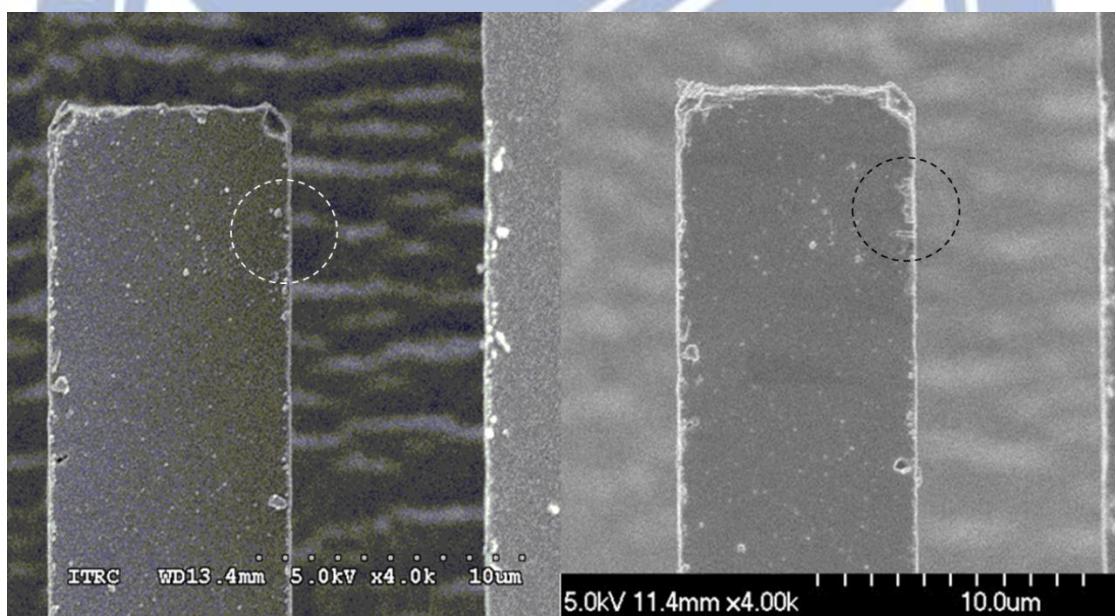

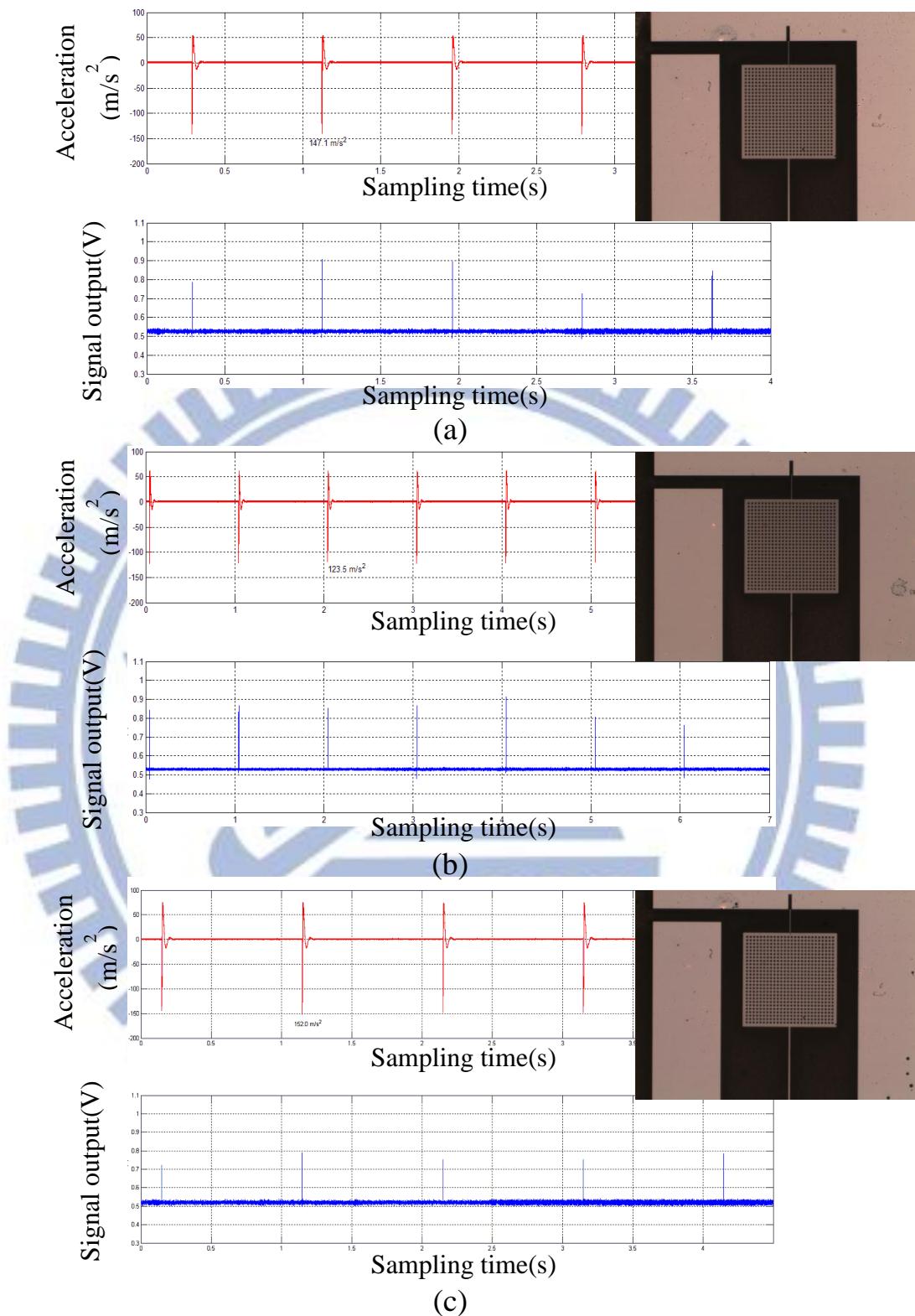

將鎳金屬與碳化鈦薄膜濺鍍於測試元件上，並用 3.3.4. 小節中之升溫方式以高溫爐加熱氧化後，進行衝擊實驗進行氧化保護能力的比較。

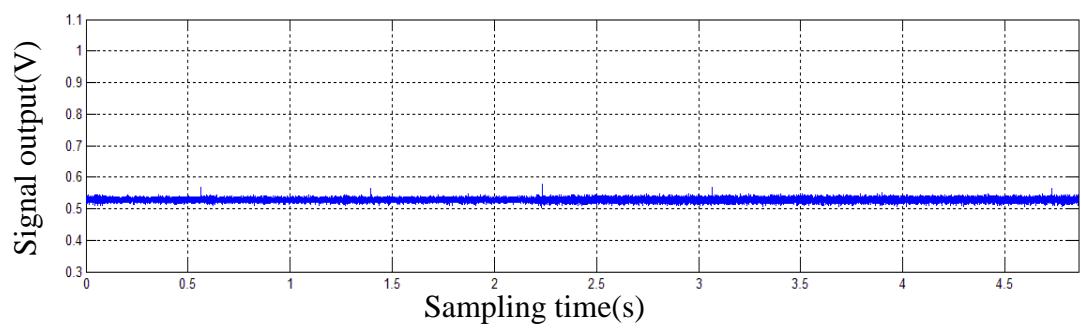

在 3.3.4. 小節中，已知碳化鈦薄膜使用溫度不可超過  $200^{\circ}\text{C}$ ，因此實驗以  $100^{\circ}\text{C}$  來加熱薄膜厚度 30 奈米的試片，結果由圖 34、圖 35 可看出，濺鍍鎳金屬的元件在經過  $100^{\circ}\text{C}$ 、10 分鐘加熱後，訊號值由初始的  $1.04\text{V}$  下降至無訊號變化，而濺鍍碳化鈦的元件則是經過 10 分鐘加熱後，訊號由初始的  $0.83\text{V}$  略微下降至  $0.799\text{V}$ ，且時間加長至 20 分鐘加熱後仍可測得訊號  $0.765\text{V}$ ，但經過 30 分鐘加熱後元件邊緣出現明顯氧化如圖 36(a)，邊緣出現氧化推測應是薄膜較薄階梯覆蓋性不足所致，因此將碳化鈦薄膜厚度增加至 45 奈米在進行實驗，結果如圖 36(b)邊緣氧化問題可獲得解決，且濺鍍 45 奈米碳化鈦薄膜元件經過 30 分鐘加熱後仍然有訊號  $0.84\text{V}$ ，如圖 36(c)因此可看出增加碳化鈦薄膜厚度可使元件耐氧化時間提升。

比較同為 30 奈米厚度的碳化鈦與鎳金屬鍍膜元件，發現濺鍍碳化鈦的元件在  $100^{\circ}\text{C}$  環境下，氧化時間為濺鍍鎳金屬元件的 2 倍，因此可得知碳化鈦氧化保護能力是鎳金屬的 2 倍以上。

圖 34 30 奈米鎳金屬鍍膜元件 100°C 加熱前後訊號圖(a)加熱前(b)加熱

10 分鐘後

圖 35 30 奈米碳化鈦鍍膜元件 100°C 加熱前後訊號圖(a)加熱前(b)加熱

10 分鐘後(c)加熱 20 分鐘後

圖 36 碳化鈦薄膜經過  $100^\circ\text{C}$  30 分鐘加熱(a)30 奈米碳化鈦薄膜加熱後元件變化(b)45 奈米碳化鈦薄膜加熱後元件變化(c)45 奈米碳化鈦薄膜加熱後訊號圖

## 第四章 結論

### 4.1 總結

首次成功利用沉積碳化鈦硬質鍍膜於元件表面來達到提升元件耐衝擊能力及耐氧化能力，以下會由設計、製程、量測三個部份的結果來總結之。

#### 4.1.1. 設計

我們將本實驗室所開發之非卡樺式碰撞開關重新設計結構尺寸與形狀，使原始 200G 加速度閾值降低至 17G 以符合震盪器加速度規格，增加碰撞磨耗之頻率縮短實驗時間，並改變懸臂樑之形狀，使碰撞點位於懸臂樑尖端集中磨耗利於觀察。

我們亦設計”ㄇ”字型上蓋，使碰撞方向由左右轉成上下式碰撞，這讓我們在碰撞磨耗後的觀察更加便利。

訊號量測則設計一簡易電路，利用匹配的電阻，使輸出電壓受碰撞開關電阻變化而改變。

#### 4.1.1. 製造

利用感應式耦合電漿離子矽蝕刻系統(ICP system)，將矽晶圓蝕刻出懸浮的碰撞懸臂樑，及”ㄇ”字型上蓋。

另外亦使用真空濺鍍機沉積碳化鈦薄膜，並控制沉積速率沉積出預期厚度的薄膜。

#### 4.1.2. 量測

量測可分為2部分，分別為碳化鈦沉積於基板與碳化鈦沉積於測試元件。

沉積於基板部分是利用X光繞射儀確認30奈米以上之碳化鈦薄膜沉積比例約為42%鈦:58%碳；並透過奈米壓痕機得知薄膜厚度30奈米時，碳化鈦之耐磨耗性比鎳強2倍以上；且使用高溫爐與四點探針搭配實驗得知碳化鈦薄膜使用溫度需低於200°C 以及電阻值及電阻飄移量會隨薄膜厚度增加而下降。

沉積於測試元件部分是比較濺鍍厚度30奈米的碳化鈦及鎳金屬測試元件後發現在耐衝擊能力碳化鈦比鎳金屬鍍膜高出7倍以上，且將元件以100°C 加熱時，濺鍍碳化鈦的元件耐氧化時間比鎳金屬元件提升2倍以上。

## 4.2 未來工作

關於利用碳化鈦鍍膜增加碰撞開關使用壽命，雖然已能透過量測數據證實鍍膜確有其效果，但能有許多因素尚未被考慮，諸如碰撞力量、碰撞面性質，可進一步實驗與討論來修正之。

碰撞力量則會影響碰撞磨耗速率，因此可以建立在不同力量下的磨耗速率曲線，使元件使用規範更加明確；而鍍膜沉積時的表面特性會影響鍍膜的附著率，在實驗中有發現上蓋因為使用 ICP 蝕刻製程製作，因此表面有許多細小缺陷，造成與懸臂樑碰撞時兩碰撞面表面性質不同，故亦可對這部分進行探討。

未來可將碳化鈦鍍膜應用於鎳基碰撞開關，以增加其使用壽命，但因鎳基卡桿式開關由於需配合震盪器之規格，本論文中亦有設計新的尺寸，但尺寸線寬較小製作不易故在論文中並無討論，未來可再將尺寸做修改後將碳化鈦鍍膜應用於開關上，並會將元件進行加熱、接觸阻值之量測，分析碳化鈦鍍膜對金屬基材的保護能力。

## 參考文獻

- [1] A. Savan, H.J. Boving, F. Fluehmann and H.E. Hintermann, Increased performance of bearings using Tic-coated balls, *supplement au Journal de Physique III*, 1993, Vol. 3

- [2] A.E. Zeghni and M.S.J. Hashmi, Comparative wear characteristics of tin and tic coated and uncoated tool steel, *Journal of Materials Processing Technology*, 2004, Vol. 155–156, 1923–1926

- [3] J.F. Su, X. Nie, T. Mulholland, Combinative influence of impact and pressing forces on coating failure behavior, *Surface & Coatings Technology*, 2010, Vol. 205, 1520–1526

- [4] G. Radhakrishnan, R.E. Robertson, P.M. Adams, R.C. Cole, Integrated TiC coatings for moving MEMS, *Thin Solid Films*, 2002, Vol. 420 –421, 553–564

- [5] Z. Yang, D. Lichtenwalner, A. Morris, S. Menzel, C. Nauenheim, A. Gruverman, J. Krim, A.I. Kingon, A new test facility for efficient evaluation of MEMS contact materials, *Journal of Micromechanics and Microengineering*, 2007, Vol. 17, 1788–1795

- [6] L.E. Hollander, J.R., Electrical Conductivity and Thermoelectric Effect in Single-Crystal TiC, *Journal Of Applied Physics*, 1961, Vol. 32,

- [7] Y. Igasaki, H. Mitsuhashi, K. Azuma, T. Muto, Structure and Electrical Properties of Titanium Nitride Films, *Japanese Journal Of Applied Physics*, 1978, Vol. 17, 85–96

- [8] E.J. Bienk, H. Reitz, N.J. Mikkelsen, Wear and friction properties of hard PVD coatings, *Surface & Coatings Technology*, 1995, Vol. 76–77, 475–480

- [9] T.H. Fang, S.R. Jian, D.S. Chuu, Nanomechanical properties of TiC, TiN and

TiCN thin films using scanning probe microscopy and nanoindentation, *Applied Surface Science*, 2004, Vol. 228, 365–372

[10] H.Y. Chen, S. Han, H.C. Shih, Microstructures and properties changes induced by a metal vapor vacuum arc chromium interlayer in chromium nitride films, *Materials Letters*, 2004, Vol. 58, 2924– 2926

[11] S.Y. Lee, S.C. Wang, J.S. Chen, J.L. Huang, Effects of deposition and post-annealing conditions on electrical properties and thermal stability of TiAlN films by ion beam sputter deposition, *Thin Solid Films*, 2006, Vol. 515, 1069–1073

[12] A. Mitsuo, S. Uchida, N. Nihira, M. Iwaki, Improvement of high-temperature oxidation resistance of titanium nitride and titanium carbide films by aluminum ion implantation, *Surface & Coatings Technology*, 1998, Vol. 103–104, 98–103

[13] 塗層膜種特性比較及其應用，日新高性能塗層(東莞)有限公司

[14] 連接器手冊第三卷，富士康

[15] 馬瑞彬，高 G 值慣性開關設計與製作，交大機械所碩士論文，2011

[16] M. Stüber, H. Leiste, S. Ulrich, H. Holleck, D. Schild, Microstructure and properties of low friction TiC—C nanocomposite coatings deposited by magnetron sputtering, *Surface & Coatings Technology*, 2002, Vol. 150, 218–226

[17] A.A. Voevodin, M.A. Capano, S.J.P. Laube, M.S. Donley, J.S. Zabinski, Design of a Ti/TiC/DLC functionally gradient coating based on studies of structural transitions in Ti–C thin films, *Thin Solid Films*, 1997, Vol. 298, 107–115