# 國立交通大學

材料科學與工程學系碩士班 碩士論文

銲錫厚度對錫銀銲錫接點中電遷移效應的影響 Effect of Solder Thickness on Electromigration on Sn2.3Ag Solder Joints

研究生:邱偉豪

指導教授:陳 智教授

中華民國101年9月

## 銲錫厚度對錫銀銲錫接點中電遷移效應的影響

研究生:邱偉豪 指導教授:陳 智教授

國立交通大學材料科學與工程學系碩士班

# 摘要

由於銲錫凸塊的大小隨著趨勢會變得越來越小,電遷移破壞 (electromigration failure)將是一個很重要的可靠性問題。3D-IC 將成為一個 重要的電子封裝技術及高性能結構,銲錫凸塊的高度將會下降至 10 微米以下。在這項研究中,我們對不同厚度的銲錫電遷移的影響進行觀察。我們 的試片結構主要上端是 3 微米的電鍍鎳再上層是 50 微米的銅柱,中間 Sn2.3Ag 銲錫接點的高度我們利用回銲熱處理把銲錫控制在 18 微米,10 微米,介金屬化合物開始接橋(bridged IMC)以及完全介金屬化合物(Full IMC) 四種厚度,下端為 27 微米厚的銅墊層。利用 Semi In-situ 的觀測方式,通電條件為 2.5× 10<sup>4</sup> A/cm² 和 3× 10<sup>4</sup> A/cm² 的電流密度並把環境溫度設為 100° C。研究的結果發現銲錫厚度越低的銲錫凸塊比較不容易出現孔洞,電 遷移破壞的時間相對也比較長。

ı

# Effect of solder thickness on electromigration in Sn2.3Ag solder joints

Graduate student: Khew Woei-Haw Advisor: Chih Chen

Department of Materials Science and Engineering

National Chiao Tung University

## **Abstract**

As the solder bump size becomes smaller, electromigration failure is a critical reliability issue. As 3D-IC will become an important packaging technology for high performance devices, the bump height will decrease below 10 micron. In this research, the effect of different solder thickness on electromigration failure mode is investigated. The solder joint consists four types thickness Sn2.3Ag solder joint, there are 18  $\mu$ m, 10 $\mu$ m, IMCs (Intermetallic compounds)started bridging and whole solders become IMC. Solder joint with 3  $\mu$ m electrical Ni/50  $\mu$ m copper column on the chip side and 27  $\mu$ m copper trace on the substrate side. The current density was about 2.5× 10<sup>4</sup> A/cm² and 3× 10<sup>4</sup> A/cm² and the testing temperature at 100°C. The result indicates that void was easily observed in solder joints with higher solder thickness, and electromigration failure time was shorter than the joints with lower bump height solders.

## 誌謝

首先我要感謝我的指導教授 陳智教授,老師悉心的指導讓我在研究上和待人處事上獲益良多。每當研究上遇到困難,老師都非常有耐心和我一起討論及解決問題,才能夠讓我的實驗順利完成。老師也積極的鼓勵我們出國參與國際研討會除了讓我拓展了國際觀以外也讓我體驗到這麼美好的出國經驗。非常感謝老師這兩年對我的關懷和教導,老師對學問的嚴謹更是我學習的典範,學生也不會忘記老師對我們一切的訓練及教誨,在將來的職場上一定會學以致用。在此我要對陳智老師至上我最高的謝意。我也非常感謝高振宏教授和陳信文教授能抽空參與我的口試並給予論文上和研究上的指導,使我的論文更加的完整。讓我從研究理論上有更多不同的看法。

#### 1896

能夠進入CC lab認識大家是多麼幸運的一件事情。在這兩年裡實驗室 裡共同的生活點滴,學術上的討論,經常一起聚餐和打球運動的日子 讓我們的感情更加的深厚,也讓我一直帶著愉快的心情走完我的學生 生涯。在這裡特別感謝幫忙我最多也特別關心我的翔耀學長,謝謝你 的鼓勵和這兩年在實驗室的陪伴。謝謝史丹利在這兩年陪我一起走完 碩士生涯,在實驗室一半以上的時間都和你一起做實驗打球,有你這 麼可靠樂觀的同學真的很幸運。謝謝寬寬哥每當我的實驗和報告遇到 困難的時候都很有耐心幫我想辦法,也經常陪我一起跑步減肥然後又吃大餐增肥。感謝阿丸幫我的口試報告修改到半夜,真的辛苦你了。謝謝棄儒和小手在實驗上的幫忙,你們的熱心幫忙真的很窩心,也恭喜我們順利走過這兩年。謝謝佳凌學姊在實驗儀器上經常的諒解才讓實驗能順利進行。謝謝朝駿每次帶我們去吃好吃的宵夜讓我更有動力運動。謝謝美麗的筱雲學姊經常請我喝飲料及一起開玩笑。感謝菜頭、QQ哥、道奇、建民及韋奇學長們不厭其煩的指出我研究中的缺失,且總能在我迷惘時為我解惑。實驗室的以撒、偉嵐、小莫、勇伯及天麟學長們當然也不能忘記,你們的幽默感讓實驗室增添了好多歡樂。也感謝玉龍、皆安及亦丞在口試期間的幫忙還有小云學妹的加油打氣,才讓我無所顧慮的好好準備口試。

最後在這論文的終點,我要將此獻給我的爸爸、媽媽、哥哥、妹妹以及 我的好朋友,謝謝你們無私的付出,在我背後一直給予我鼓勵讓我的學生

生涯畫下了美好的句點。

# 目錄

| 中文摘要         |                   | I   |

|--------------|-------------------|-----|

| 英文摘要         |                   | II  |

| 誌謝           |                   | Ш   |

| 目錄           |                   | V   |

| 圖目錄          |                   | VI  |

| 表目錄          | V                 | Ш   |

| 第一章 緒論       |                   | . 1 |

| 第二章 文獻回      | ]顧                | .6  |

| 2-1 電遷移      | 3理論               | .6  |

| 2-2 關鍵乘      | 積和反作用力            | 10  |

| 2-3 電流集      | 是積和反作用力<br>中效應    | 13  |

| 2-4 焦耳熱      | ·效應               | 15  |

|              | 度對電遷移的影響          |     |

| 2-6 無鉛鉺      | 星錫的電遷移測試          | 20  |

| 第三章 實驗方      | ES N              | 22  |

| 3-1 試片結      | 5構                | 22  |

| 3-2 試片通      | 直電前處理             | 23  |

| 3-3 凱文結      | · 構               | 24  |

| 3-4 利用電      | E阻溫度係數 TCR 校正實際溫度 | 25  |

| 3-5 測試係      | 件與方法              | 26  |

| 3-6 分析工      | -具與方法             | 27  |

| 第四章 結果與      | 寻討論               | 29  |

|              | ·構確認與成分分析         |     |

| 4-2 試片鉺      | 學錫厚度與破壞時間         | 35  |

| 4-3 試片微      | <b>佐結構破壞分析</b>    | 39  |

| 4-3.1 通以     | 1.9 安培微結構分析       | 39  |

| 4-3.2 通以     | 2.3 安培微結構分析       | 40  |

| 4-4 溫度感      | 测儀校正銲錫凸塊溫度        | 49  |

| 4-5 銲錫凸      | <b>,</b> 塊內的電流分佈  | 50  |

| 第五章 結論       |                   | 52  |

| <b>參</b> 老資料 |                   | 53  |

# 圖目錄

| 圖 1-1   | 封裝層級示意圖                                              | 4            |

|---------|------------------------------------------------------|--------------|

| 圖 1-2   | 覆晶結合示意圖                                              | 4            |

| 圖 1-3   | Kelvin structure 在半導體電性量測示意圖                         | 5            |

| 圖 2-1   | 電遷移在鋁線上的效應                                           | 9            |

| 圖 2-2   | 不同長度鋁導線藉由不同通電時間,計算因電遷移效應所導致的遷移量                      | 12           |

| 圖2-3    | 經500℃、0.5hrs熱處理之鋁薄膜導線,在不同電流密之飄移速度                    | 12           |

| 圖 2-4   | 電子流路徑改變造成電流集中效應                                      | 14           |

| 圖 2-5   | 模擬銲錫凸塊電流密度分布,電子流路徑改變造成電流集中效應                         | 14           |

| 圖 2-6   | 通電前後銲錫凸塊的溫度分佈圖                                       |              |

| 圖 2-7   | 三明治結構示意圖                                             | 19           |

| 圖 2-8   | 突出物(hillock)與空孔(valley)示意圖                           |              |

| 圖 2-9   | 銲錫接點 UBM 為銅的電遷移破壞變化                                  |              |

| 圖 2-10  | 銲錫接點 UBM 為鎳的電遷移破壞變化                                  | 21           |

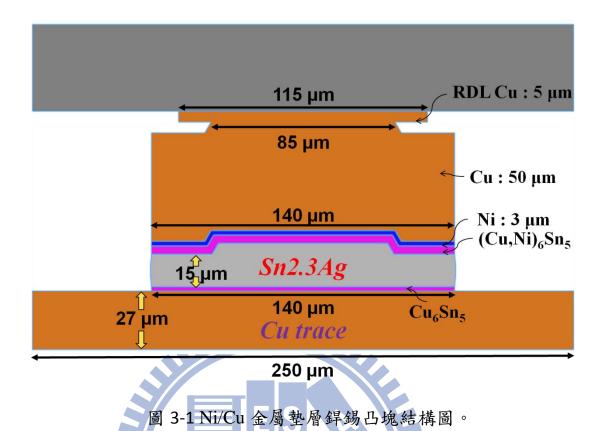

| 圖 3-1   | Ni/Cu 金屬墊層銲錫凸塊結構圖                                    | 28           |

| 圖 3-2   | 凱文結構示意圖                                              | 28           |

|         |                                                      | <b>-</b> • • |

| 圖 4-1   | 試片在 260°C 分別回銲 0min、10min、20min、30min、45min、2hr 側視 □ |              |

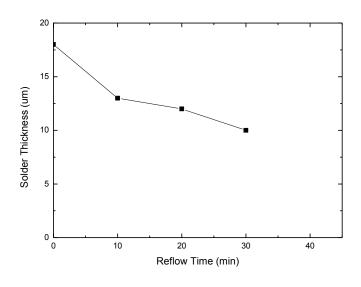

| 圖 4-2   | 銲錫厚度對回銲測試時間關係圖                                       | 31           |

| 圖 4-3-1 | 試片準備在 100°C 下通以 1.9 安培之未通電前初始結構剖面示意圖                 | 32           |

| 圖 4-3-2 |                                                      |              |

| 圖 4-3-3 |                                                      |              |

| 圖 4-4-1 |                                                      |              |

| 圖 4-4-2 |                                                      |              |

| 圖 4-5-1 |                                                      |              |

| 圖 4-5-2 | ·                                                    |              |

| 圖 4-6-1 |                                                      |              |

| 圖 4-6-2 | 100 °C、1.9 安培、原銲錫厚度 10μm 電子流向下剖面示意圖                  | 44           |

| 圖 4-7-1 | 100 °C、2.3 安培、原銲錫厚度 18μm 電子流向上剖面示意圖                  | 45           |

| 圖 4-7-2 | 100 °C、2.3 安培、原銲錫厚度 18μm 電子流向下剖面示意圖                  | 45           |

| 圖 4-8-1 |                                                      |              |

| 圖 4-8-2 | 100 ℃、2.3 安培、原銲錫厚度為介金屬化合物連接剖面示意圖                     | 47           |

| 圖 4-9-1 |                                                      |              |

| 圖 4-9-2 | $100^{\circ}\mathrm{C}$ 、 $2.3$ 安培、原銲錫厚度為全 $\mathrm{IMC}$ 電子流向下剖面示意圖 | 48 |

|---------|----------------------------------------------------------------------|----|

| 圖 4-10  | 100 ℃ 2.3 安培電流密度模擬圖                                                  | 52 |

# 表目錄

| 表 4-1   | 銲錫厚度與破壞時間較理 | 3 | 36 |

|---------|-------------|---|----|

| /X_ T⁻⊥ |             |   | Jυ |

## 第一章 緒論

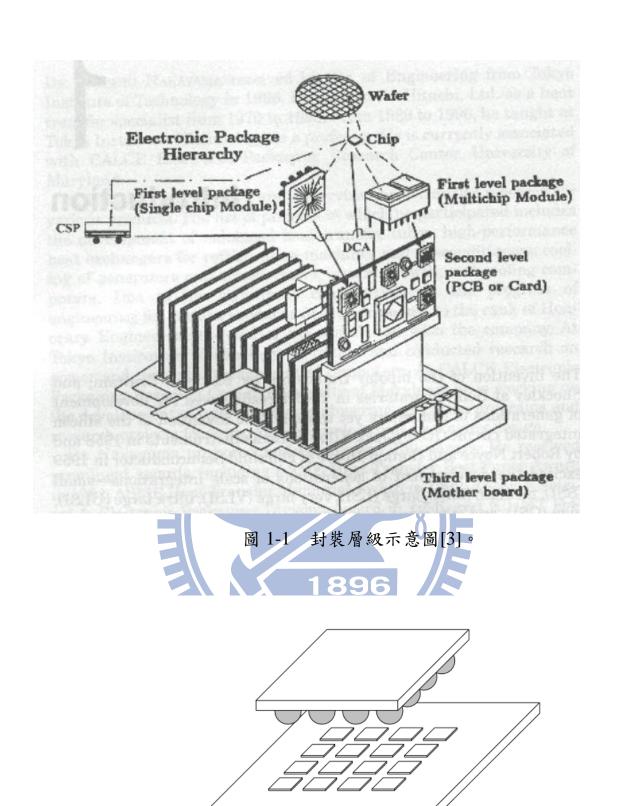

在1947年, John Bardeen和Walter Brattain在美國的貝爾實驗室製造出第一個具有放大電流效果的固態三極體[1],發明了第一個電晶體並揭開了半導體時代的序幕。1958年,Jack Kilby提出積體電路 (Integrated Circuit, IC)的概念[2],將所有元件做在一塊晶片上,東西變得很小,用途卻變得很大。之後隨著電子科技產品的蓬勃發展,電子元件的尺寸不斷朝微小化、高密度的方向發展。積體電路依照摩爾定律(Moore's Law)每18個月單位面積內電晶體的數目增加一倍,讓電子元件從微米(micron)等級製程到現今的奈米(nano)等級。隨著元件輸出輸入接點(input/output leads,I/O)密度增加,封裝形態往高密度I/O封裝發展,於新型態封裝技術中,覆晶(flip chip)封裝技術佔有極大技術優勢。

電子封裝主要目的可以供應電源(power distribution)、傳輸訊號(signal distribution)、散熱(heat dissipation)和保護晶片(protection and support)。電子 封裝技術可分成(Chip to Module)、(Module to PCB)以及(PCB to Mother Board)三種不同層級[3],如圖1-1所示。第一層(Chip to Module)將晶片接合 到導線上並完成其中的電路連線與密封保護之製程;第二層(Module to PCB) 是將第一層組合於印刷電路板上之製程;第三層(PCB to Mother Board)是將 電路板組裝於主機板上。而覆晶封裝技術屬於電子構裝第一層的構裝(chip

level packaging),如圖1-2所示,是將銲錫凸塊(solder bump)作為晶片與基板連接的接合技術,在金屬墊層上生成銲錫凸塊,並於基板上生成與銲錫凸塊相對應之接點,接著將翻轉之銲錫球對準基板上之接點將之接合。此技術具有提高密度、強化電性、最高輸出/入接點密度及減小體積等優點。

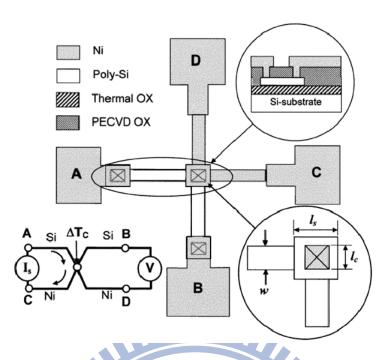

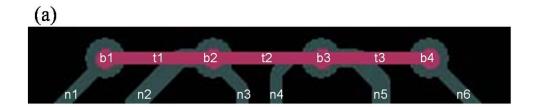

在電性量測方面,覆晶銲錫接點電遷移研究中大多都是利用離菊花環結構(Daisy chain structure)作為電性觀測,此結構定義銲錫接點破壞的時間為電路開路。離菊花環結構的試片設計與製作過程比較簡單可是對於覆晶銲錫接點內的微小變化極不敏感,無法精準觀測銲錫接點的電阻變化,只可偵測到銲錫接點的破壞·導致很容易造成電遷移破壞時間分析上的錯誤。而凱文銲錫結構(Kelvin bump probes)可以精準量測到指令範圍,且可避除接點的接觸電阻對電性量測的影響,在本研究作為電性量測的首選量測工具。而且之前研究[4]結果顯示,凱文銲錫凸塊結構的精確性符合研究孔洞生成與成長的需求,而且可以利用電阻變化量確實分辨出電遷移造成的不同階段孔洞成長。

由於銲錫凸塊的大小隨著趨勢會變得越來越小,所承受的電流密度也越來越大,電遷移破壞(electromigration failure)將是一個很重要的可靠性問題。 銲錫凸塊的金屬墊層會和銲錫反應生成介金屬化合物,而介金屬化合物的 高揚氏係數特性勢必是抗電遷移破壞的主要因素之一。此外,隨著電子元 件持續縮小的趨勢,銲錫凸塊的銲錫厚度也將會是重要考量之一。當銲錫厚度開始縮小的時候,銲錫的厚度是否會低於臨界長度而導致back stress應力的產生抑制電遷移效應。所以在這項研究中,我們將針對介金屬化合物的生成以及對不同厚度的銲錫作電遷移破壞測試並進行觀察與討論。

圖 1-2 覆晶結合示意圖

圖 1-3 Kelvin structure 在半導體電性量測示意圖

## 第二章 文獻回顧

#### 2-1 電遷移理論

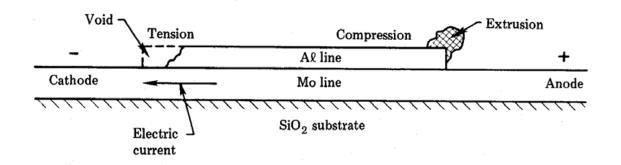

電遷移(electromigration)效應是指金屬導線在高電流密度下,金屬原子因為質量傳輸而產生的一種擴散現象。金屬內的原子會受到靜電力(electrostatic force)與電子風力(electron wind force)兩種作用力,靜電力會吸引帶正電的金屬離子往陰極端移動,而電子風力主要是來自於電子流動中和金屬原子碰撞而產生的動量轉換結果[5],讓金屬原子往陽極端移動。 圖2-1 為鋁導線的電遷移情形,這是一典型的Blech 結構[9],電遷移會導致在陽極端出現凸起或隆起物,在陰極端會生成孔洞。Blech 是導入此實驗方法者[7][8]。

在電遷移效應下造成的的原子質量傳送,固態金屬原子的擴散通量可表示為[6]:

$$J = -D \frac{\partial C}{\partial X} \sum_{i} C M_{i} F_{i}$$

(2.1)

上述式子第一項項表示化學勢梯度(chemical potential gradient)所造成的擴散,而第二項則代表各種的施加外力所引發的擴散。若我們只討論純物質的電遷移擴散機制,可忽略第一項的化學勢梯度造成的通量,只留下靜電

場對擴散原子的庫倫力(coulombic force)和電子與金屬原子之間動量傳送的電子風力,如此一來,可將第二項改寫為[6]:

$$\sum_{i} CM_{i}F_{i} = F_{el} + F_{wd}$$

(2.2)

其中電子風力較庫倫力的影響顯著,進而促使金屬原子從導體的

陰極端(cathode side)被推向陽極端(anode side)而產生遷移。電子風力可將它表示為:

$$F_{wd} = EZ^*e \tag{2.3}$$

e 表示基本電荷量

移通量式為[8]:

Z\*表示有效電荷數(對不同種類的金屬,有不同有效電荷數) 1896 將電子風力導入電遷移的原子通量式中,我們可以得到電遷

$$J_{EM} = N_m F_{EM} \tag{2.4}$$

N 表示原子濃度(atomic concentration)

m 表示原子的遷移率(mobility) 依照愛因斯坦方程式(Einstein equation)我們可以將原子遷移率表示成:

$$m = D/kT (2.5)$$

- D 表示擴散係數(diffusivity)

- k 表示波茲曼常數(Boltzmann,s constant)

- T 表示絕對溫度(absolute temperature)

因此, 電遷移的原子通量方程式可以表示為:

$$J_{EM} = N \frac{D}{kT} Z^* e E = N \frac{D}{kT} Z^* e \rho j$$

$$(2.6)$$

ρ 表示電阻係數(resistivity)

圖 2-1 電遷移在鋁線上的效應。[9]

#### 2-2 關鍵乘積和反作用力

Blech透過不同長度的鋁導線藉由不同的通電時間,計算因電遷移效應 所導致的遷移量,進而求得飄移速度(drift velocity)如圖2-2所示。圖2-3 顯 示鋁導線所呈現的電流密度(current density)與飄移速度(drift velocity)的函 數圖形[8]。從結果可以看出,鋁導線的飄移速度與電流密度呈現線性關係, 但此直線並無通過原點。因此說明一特定長度的鋁導線,電流密度大於一 特定的臨界值(threshold current density)電遷移效應才能產生原子的遷移而 造成毀壞。此電流密度的臨界值(threshold current density)將與鋁薄膜導線的 長度有關。因此在相同的條件下,一固定的鋁導線長度將會有一相對應的 電流密度臨界值。此現象是由於應力所產生的backstress 抑制了電遷移效應。 當電流流經鋁導線時陰極端的金屬原子將會擴散到陽極端累積。在這過程 中,若有鋁導線有一層原生氧化層(native oxide),將導致薄膜導線內部產生 一機械應力。這是因為當空位(vacancy)沿著晶界平衡的狀態下,鋁薄膜導 線內部的晶界(grain boundary)仍然是有效的空位(vacancy)來源。因此當擴散 發生時,金屬原子將會累積在陽極端,進而增加晶格(lattice site)數目,如此 一來便會造成陽極端壓縮應力(compressive stress)的生成。同理,鋁薄膜之 陰極端亦將會生成拉伸應力(tensile stress)。此種應力梯度(stress gradient)的 存在將會導致backstress 的產生。

而關鍵乘積(critical product)就是說明此現象,當 $j\Delta x < (j\Delta x)$ 。就不會有電遷移破壞產生,並可將他表示為:

$$Je\Delta X = \frac{\Delta\sigma\Omega}{Z*e\rho}$$

(2.7)

J 表示電流密度(current density)

$\Delta X$ 表示長度(Boltzmann,s constant)

Ω 表示原子體積(atomic volume)

e 表示基本電荷量

Δσ表示正向應力(normal stress)差

Z\*表示有效電荷數(effective charge)

ρ表示電阻係數(resistivity)

1896

圖2-2 不同長度的鋁導線藉由不同的通電時間,計算因電遷移效應所導致的

圖2-3 經500℃、0.5hrs 熱處理之鋁薄膜導線,在不同電流密之飄移速度。

### 2-3 電流集中效應(Current Crowding Effect)

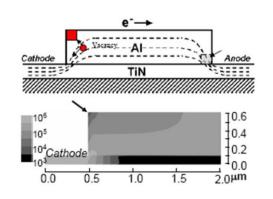

電流集中效應是指電子流的路徑改變而造成電子在某區域擁擠現象,使電流密度大於其他區域,如圖 2-4 所示。在覆晶銲錫接點也會有電流集中效應的情形。由於導線與銲錫凸塊的橫截面積大小不一樣,當電子流由導線進入銲錫凸塊時,通過的電流大小相同而造成在介面處會有相當大的電流密度改變。此現象讓電流集中在電流進入銲錫凸塊的進入端,此區域的電流密度會比整個銲錫凸塊內的平均電流密度大很多;從文獻[10]得知,利用有限元素模擬分析法,模擬銲錫凸塊內的電流密度分布, 結果發現銲錫內的最大電流密度大於銲錫內部的平均電流密度,如圖 2-5 所示。電流集中效應常發生在銲錫與 UBM 界面處,大部分電流會傾向靠近導線與銲錫凸塊的進入端,而不會均勻分布在銲錫凸塊。在電流密度的影響下造成電流集中並在導線進入銲錫凸塊的進入端容易發生電遷移破壞。

圖 2-4 電子流路徑改變造成電流集中效應。

圖 2-5 模擬銲錫凸塊電流密度分布,電子流路徑改變造成電流集中效應。

#### 2-4 焦耳熱效應

焦耳熱效應是指電子撞擊晶格中的原子時,原子會根據平衡位置而來回震盪,當溫度增加時,震盪的振幅增加,電子要通過時更容易受到阻擋,因此電阻率會隨著溫度增加,電子的動能與周圍原子的碰撞轉變為熱能此熱能可以表示為:

$$P = I^2 R = j^2 \rho V \tag{2.8}$$

P 表示熱能,

I 表示電流,

R 表示阻,

j表示電流密度,

V 表示金屬的體積

ρ表示金屬的電阻率

因此銲錫凸塊在通電下所產生的焦耳熱,除了造成溫度(如圖2-6)上升也使得電路阻值改變[11],以電阻溫度係數TCR (Temperature Coefficient of Resistance)表示為:

$$TCR = \left(\frac{R_1 - R_0}{R_0}\right) \left(\frac{1}{T_1 - T_0}\right) \tag{2.9}$$

$T_0$  表示參考溫度,

$T_1$  表示真實溫度,

$R_0$  表示 $T_0$ 下的電阻,

$R_1$  表示 $T_1$ 下的電阻;

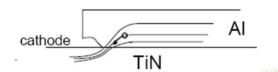

圖2-6(a)通電前銲錫凸塊的溫度分佈圖。(b)通電後銲錫凸塊的溫度分佈圖。(c)沿著(b)圖中虛線方向的溫度分佈。

#### 2-5 試片長度對電遷移的影響

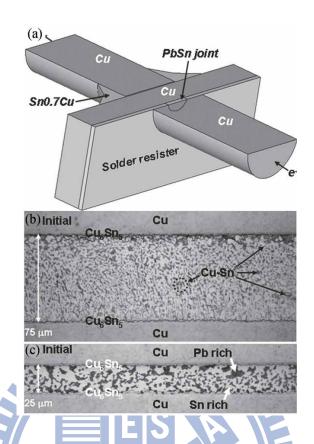

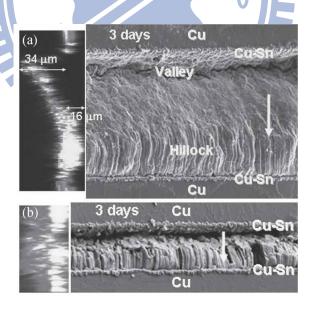

從文獻[12]發現共晶錫鉛中,對不同長度的試片進行電遷移測試,結果顯示其微結構與表面形態會受電遷移改變。作著利用三明治結構(圖 2-7),把試片厚度控制在 75μm 和 25μm,並在 150°C下通以 10<sup>4</sup>A/cm² 的電流密度。作者在陽極發現富鉛相而陰極發現富錫相,表面的錫原子受到電子流的驅動而移動到陽極端,因此在陽極端出現突出物(hillock),在陰極端出現孔洞(valley),如圖 2-8 所示,高度與通電的時間和接點厚度有關。此外,電子流驅動也導致相粗化現象,粗化的趨勢由陽極端往陰極端減少。由於此文獻採用的試片並非覆晶銲錫試片,因此本研究將會使用覆晶銲錫接點在電遷移測試下,利用不同銲錫厚度探討電流集中效應與焦耳熱效應,並對於破壞時間的影響。

圖2-7 (a)三明治結構示意圖 不同厚度共晶錫鉛試片(b) 75μm(c) 25μm

圖2-8突出物(hillock)與空孔(valley)示意圖

150°C , $10^4$ A/cm² 電流密度,(a) 75μm,(b) 25μm

#### 2-6 無鉛銲錫的電遷移測試

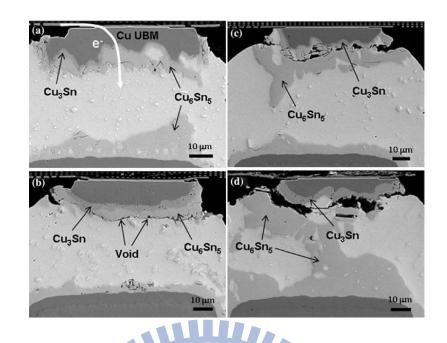

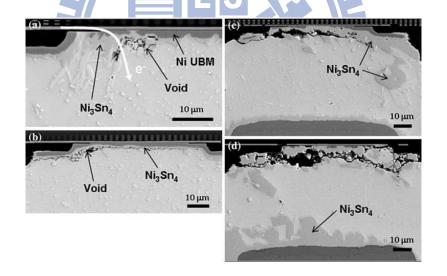

錫鉛共晶之所以長久以來廣泛地被運用於電子工業方面是因為它的成 本低、熔點低、具有優異的機械性質及良好的濕潤性。可是鉛金屬屬於重 金屬, 會造成人體和環境極大的危害。2003 年,歐盟公佈「廢電機電子 指令(Waste Electrical and Electronic Equipment, WEEE)」以及「危害物質 限用指令(Restriction of Hazardous Substance, RoHS) [13], 希望各國將確 保從2006 年7 月1 日起,銷售於市場的電子產品不含鉛、汞、鎘、六價鉻、 聚溴二苯醚 (PBDEs) 及聚溴聯苯 (PBBs)。隨著環保意識,無鉛銲錫開始 被越來越重視並對其電遷移效應視為極重要的可靠度問題[14][15][16]。 從 文獻[17]發現,共晶錫銀銲錫的金屬墊層若為銅,在電遷移測試的初期, Cu<sub>6</sub>Sn<sub>5</sub> 與銲錫的介面會出現孔洞。孔洞會沿著Cu<sub>6</sub>Sn<sub>5</sub> 與Cu<sub>3</sub>Sn 的介面擴展 而造成試片斷路(圖2-9);若共晶錫銀銲錫的金屬墊層為鎳,電遷移測試的 初期,Ni<sub>3</sub>Sn<sub>4</sub> 與銲錫的介面會出現孔洞,孔洞會沿著該介面擴展形成斷路 (圖2-10)。介金屬化合物的成長伴隨著體積的收縮會加速電遷移破壞。

圖2-9銲錫接點UBM為銅的電遷移破壞變化

(a)測試初期(b)孔洞生成(c)裂縫擴展(d)接點斷路

圖2-10銲錫接點UBM為鎳的電遷移破壞變化

(a)空洞生成初期(b)孔洞擴展(c)介金屬化合物與孔洞成長

#### (d)接點斷路

# 第三章 實驗方法

#### 3-1 試片結構

實驗的試片製備,是由本實驗室設計的無鉛銲錫覆晶封裝試片,其接點結構如圖 3-1 所示,上下端的銅導線為界線,上層銅導線的寬度為 100μm,厚度為 5μm 而下層銅導線寬度為 100μm,厚度為 27μm。上層銅導線連接著金屬墊層(under-bump-metallization),為 1μm 的 Ti/2μm 的 Cu/50μm 的 Cu Column/3μm Ni。Ti/Cu 層的製程方法是以濺鍍的方式,而中間有一層銅做為種子層,然後電鍍 50μm 厚的銅柱。鈍化層開口(Passivation Opening)利用黃光微影製程,因此直徑比銅柱稍短,為 85μm 厚,而銅柱的直徑為140μm。銲錫凸塊的銲料成分為 Sn-2.3wt.%Ag,銲錫球高度皆在 15μm 至20 μm 之間,直徑為140μm,其製程方法是把銲料電鍍在上端金屬墊層,然後用回銲方式對準基板上接點將之接合。凸塊間距(pitch)為 1mm,下端基板部分是 FR5 基板。

## 3-2 試片通電前處理

本研究因為要探討不同銲錫厚度對電遷移破壞的影響所以在試片進行 通電測試前將對試片分別在260°C下回銲 0分鐘、10分鐘、20分鐘、30分鐘、 45分鐘、2小時。然後觀察橫截面的形貌,利用軟體ImageJ分別量測試片接 點的銲錫平均厚度。經過觀察結果,決定選擇在260°C分別回銲 0分鐘、30 分鐘、45分鐘、2小時的試片作為通電測試試片。

本研究採用 Semi in-situ 的觀測方式,主要是為了確定試片初始結構和預期一致,以利觀測並比較通電測試後微結構變化。Semi in-situ 的優點在於能夠在初始先確認試片初始結構,並且可以邊量測電阻上升的不同階段邊觀測微結構變化。因此,在開始通電測試前必須把試片磨至通電所需觀察的剖面才能進行通電。首先,用不同號數的 SiC 砂紙由 1000、2000、4000做研磨,然後用 1µm 及 0.3µm 氧化鋁粉拋光將刮痕最小化。研磨過程中,必須定時利用 Keithley2400 電錶量測並觀測銲錫凸塊的電阻值是否接近初始的電阻值的一倍,來確定銲錫凸塊已磨至中間面。之後在試片的表面上濺鍍一層鉑金屬層,除了防止表面氧化,也可以增加試片的導電性以利於做電子顯微鏡的觀測。最後再利用 SEM6500 把試片的銲錫凸塊初始結構拍下以用來和通電後測試結果比較,才能開始進行通電測試。

#### 3-3 凱文結構

本研究中所使用之凱文結構示意圖(圖 3-2)。結構中包含四顆銲錫凸塊標示著 b1 到 b4 並由一條銅導線連接四個銅墊層。銲錫凸塊間距為 1mm,此外在基板上有六條銅導線依序標上 n1 到 n6 連接到此四顆銲錫凸塊,導線走向如圖所示。本研究中,我們定義電子流方向由板端往晶片端為 B2 既電子流向上,而電子流由晶片端往基板端為 B3 既電子流向下。電子流由 n3 進入通過 B2 至晶片,跨越銅導線往下至 B3 , 最後由 n4 流出如圖中箭頭所示。銲錫 B2 的電壓變化可由 n1 與 n2 測量得到,而銲錫 B3 的電壓變化可由 n5 與 n6 測量得到,連接 B2 與 B3 的上端銅導線電阻可由 n1 與 n6 測量得到。利用這樣的測量方式可在電遷移發生的同時測量兩顆電子流方向相反的銲錫凸塊與連接兩顆銲錫凸塊的銅導線的電阻變化。

The same of the sa

#### 3-4 利用電阻溫度係數校正實際溫度

本研究試片為了量測試片內部真實溫度,在基本端上以銅導線做為熱感應原件並與電遷移測試迴路分開。從文獻回顧 2-4 裡得知,量測試片內部實際溫度必須先求出銅導線的電阻溫度係數(TCR)。所以試片通電前,我們先將一片測試試片分別以均溫 50°C、100°C、150°C、200°C 在加熱爐裡通以0.1 安培量測其電阻,然後對電阻與溫度兩參數做線性圖線性迴歸法找出銅導線的電阻溫度係數(TCR)。得出電阻溫度係數(TCR)以後,在實際通電的試片進行通電測試時用一樣的量測方式並利用公式(2.8)得出銲錫凸塊通電時的實際溫度。

1896

#### 3-5 測試條件與方法

實驗測試方法為凱文結構所設計。首先,將試片分別放置 100°C 加熱盤上,以耐熱膠帶將其固定,然後做半小時的時效熱處理。待試片達穩定後,再分別施以 1.9 安培及 2.3 安培的電流進行通電測試。電流在銲錫凸塊內換算成電流密度為 2.5 x 10<sup>4</sup>A/cm<sup>2</sup>及 3 x 10<sup>4</sup>A/cm<sup>2</sup>。

通過凱文結構我們可以偵測到單顆銲錫凸塊的電性變化,因此在電性量測方面,我們利用凱文結構來觀測銲錫凸塊的電阻值。施加電流後同時量測、記錄銲錫凸塊的電阻值變化,當電子流向下的銲錫凸塊的電阻值上升初始值的 1.2 倍時,即停止加熱、通電等測試條件。而本實驗把電子流向下的銲錫凸塊的電阻初始值上升 1.2 倍的通電時間設為破壞時間(failure time)是因為本研究試片電子流向下的銲錫凸塊結構好處在於有銅柱分散電流的效果,而且還有鎳層阻擋層保護上層銅原子擴散入銲錫凸塊內防止銅消耗更利於觀察 back stress 的現象。因此觀測的重點主要放在電子流向下的銲錫凸塊上。

#### 3-6 分析工具與方法

在微結構金相觀測,本研究使用日本電子光學株式會社(Japan Electron Optics Laboratory, JEOL)的 6500 型熱場發掃描式電子顯微鏡(Field Emission Scanning Electron Microscope, FESEM)做為主要的觀察工具。背向散射電子(Backscatter Electron)產生的數量會因為不同元素差異而不同,可清楚區隔出試片中不同的相或不同元素的成分,藉由此特性我們用背向散射電子影相(Backscatter Electron Image)觀察試片側視的部分。另外本研究中將利用 X 光能量散佈分析儀(Energy Dispersive Spectrometer, EDS)做特定區域的成分分析,以確認試片內部各成分的組成。

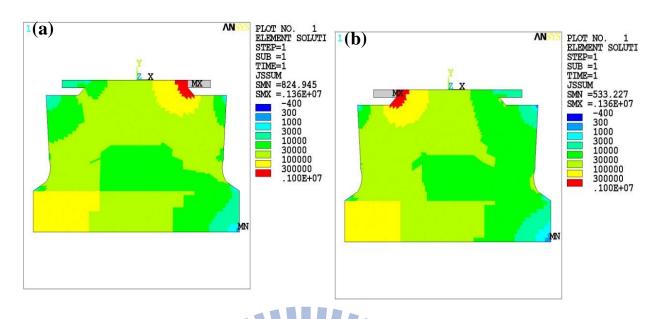

ANSYS 模擬軟體建立三維的數值分析模型。觀察通電初期,電流分布的狀況,分析破壞前,電阻上升之後,其內部電流的分佈,推測破壞階段中, 導致電阻上升與破壞發生的原因。ANSYS 的模擬分為三個步驟:前處理、求解、後處理。前處理為建立物體、定義材料、網格化,求解為施加邊界條件、初始條件、求解,後處理為顯示結果。模擬結果分為列表(list)與繪圖(plot)兩種方式。觀察的方式分為兩種;(1)觀察節點(node)的結果,如節點上的電位、電場;(2)觀察元素(element)上的結果,如電流密度。

圖 3-2 (a)凱文結構俯視圖。

(b)凱文結構剖面圖。

### 第四章 結果與討論

#### 4-1 試片結構確認與成分分析

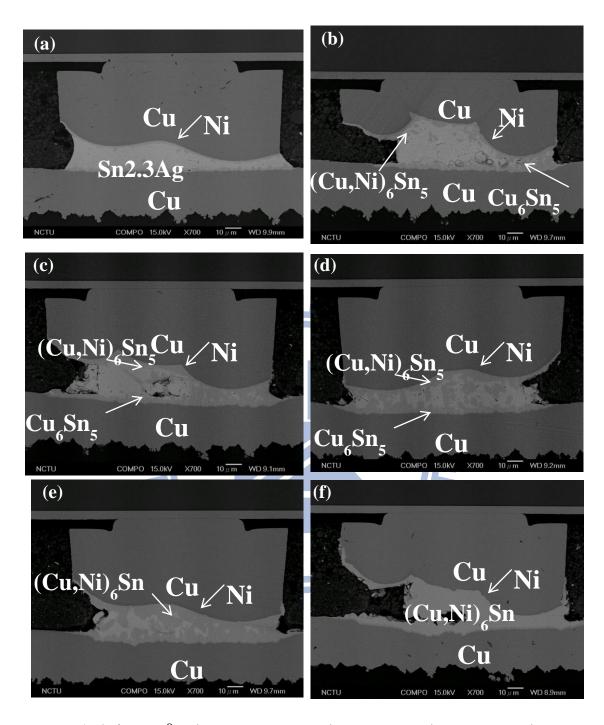

在試片進行通電測試前,將不同試片在260°C分別回銲 0分鐘、10分鐘、20分鐘、30分鐘、45分鐘、2小時。觀察橫截面(圖4-1),利用軟體ImageJ分別量測試片銲錫凸塊的銲錫平均厚度。將所有銲錫的厚度變化對時間做圖,如圖4-2所示。經過觀察結果,選擇銲錫厚度差異比較明顯的時間既在260°C分別回銲 0分鐘、30分鐘、45分鐘、2小時的試片作為通電測試的試片。

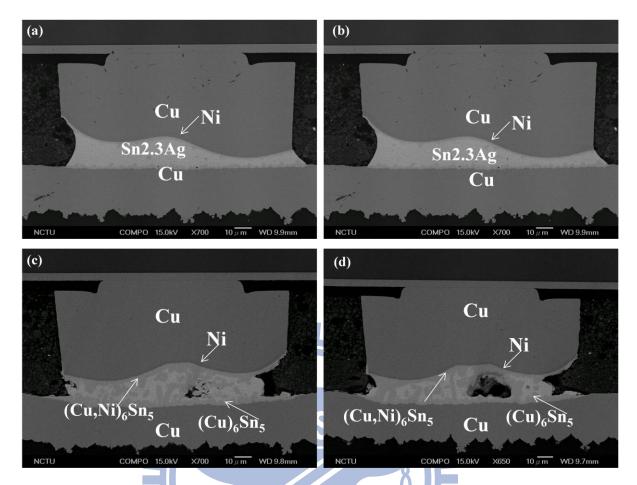

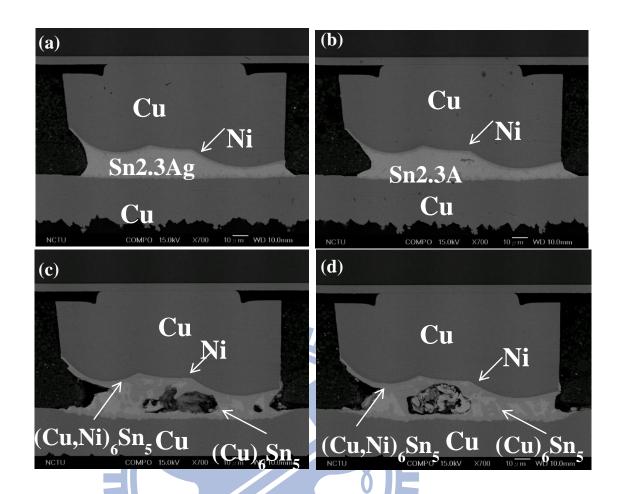

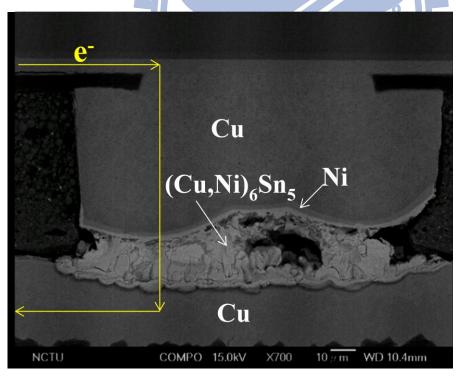

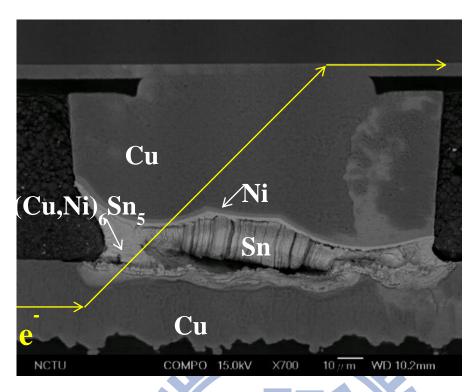

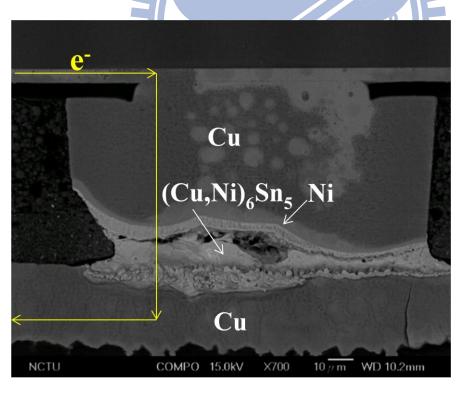

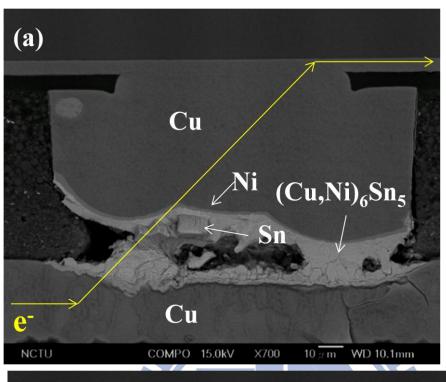

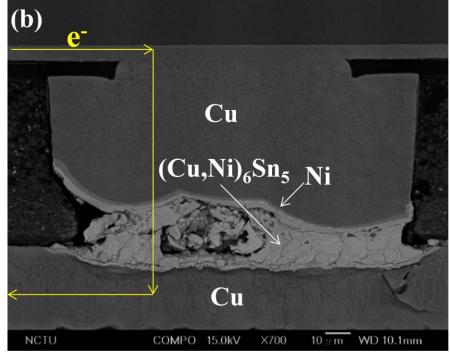

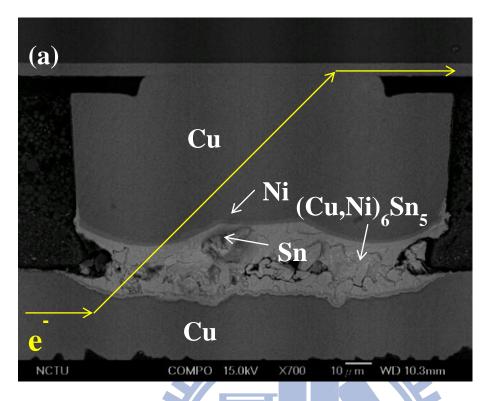

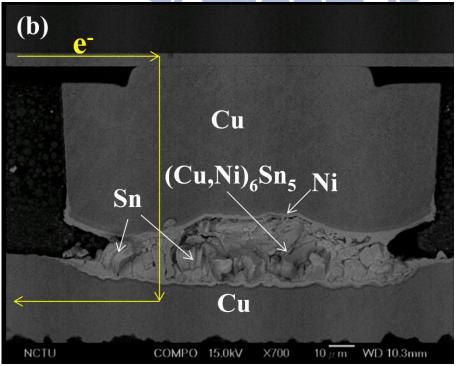

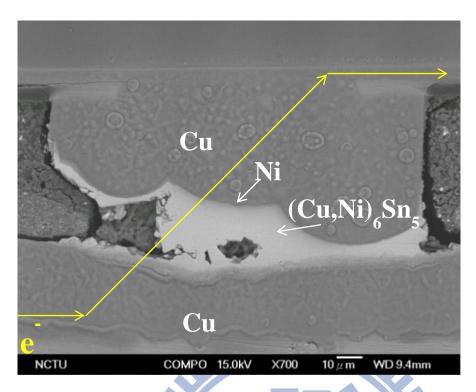

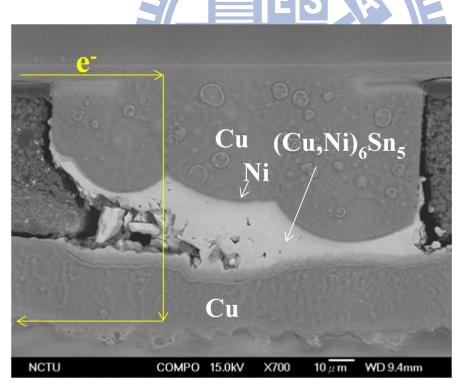

然後對四種不同銲錫厚度的試片分別觀察橫截面的形貌,確認IMCs (intermetallic compounds)的成長使銲錫的厚度和預期一致。圖4-3為各種不同試片在 $260\,^{\circ}$ C分別回銲0分鐘、30分鐘、45分鐘、2小時的橫截面圖,可以在通電測試後用來比較微結構變化。觀察橫截面圖發現給予試片回銲45分鐘的銲錫凸塊,上層與下層的介金屬化合物(Cu,Ni) $_6$ Sn $_5$ 已經開始連接起來。當試片回銲兩小時後,銲錫凸塊的銲錫全部轉為介金屬化合物(Cu,Ni) $_6$ Sn $_5$ 。為了確認IMC的成分和厚度,我們利用EDX分析,確認銲錫球上層的介金屬化合物成分為(Cu,Ni) $_6$ Sn $_5$ 下層的介金屬化合物成分為Cu $_6$ Sn $_5$ 。而在 $260\,^{\circ}$ C 回銲兩小時的試片,其銲錫凸塊的介金屬化合物為(Cu,Ni) $_6$ Sn $_5$ 。之後,我們再利用軟體Image j 對銲錫做厚度量測,得到其平均厚度分別為18µm、10µm、介金屬化合物bridging、銲錫全反應介金屬化合物。

圖 4-1 試片在 260 °C 分別回銲: (a) 0 分鐘、(b)10 分鐘、(c)20 分鐘、(d)30 分鐘、(e)45 分鐘、(f)2 小時剖面示意圖。

圖 4-2 銲錫厚度對回銲測試時間之關係圖。

圖 4-3-1 試片準備在 100°C 下通以 1.9 安培之未通電前初始結構剖面示意 圖:(a)電子流向上厚度為 18μm 的銲錫凸塊(b)電子流向下厚度為 18μm 的銲 錫凸塊(c) 電子流向上厚度為 10μm 的銲錫凸塊(d) 電子流向下厚度為 10μm 的銲錫凸塊。

圖 4-3-2 試片準備在 100°C 下通以 2.3 安培之未通電前初始結構剖面示意 1896 圖:(a)電子流向上厚度為 18μm 的銲錫凸塊 (b)電子流向下厚度為 18μm 的銲 錫凸塊、(c) 電子流向上厚度為 10μm 的銲錫凸塊、(d) 電子流向下厚度為 10μm 的銲錫凸塊。

圖 4-3-3 試片準備在 100 ℃ 下通以 2.3 安培之未通電前初始結構剖面示意 圖:(a)電子流向上IMC 開始連接的銲錫凸塊 (b)電子流向下 IMC 開始連接的 銲錫凸塊 (c)電子流向上銲錫全反應 IMC 的銲錫凸塊 (d) 電子流向下銲錫 全反應 IMC 的銲錫凸塊。

#### 4-2 試片銲錫厚度與破壞時間

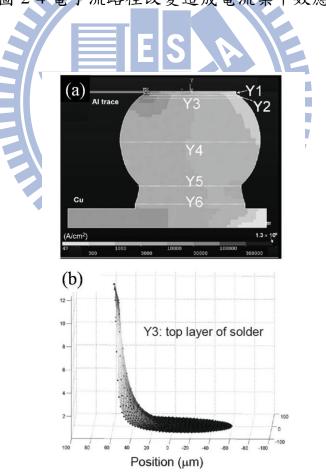

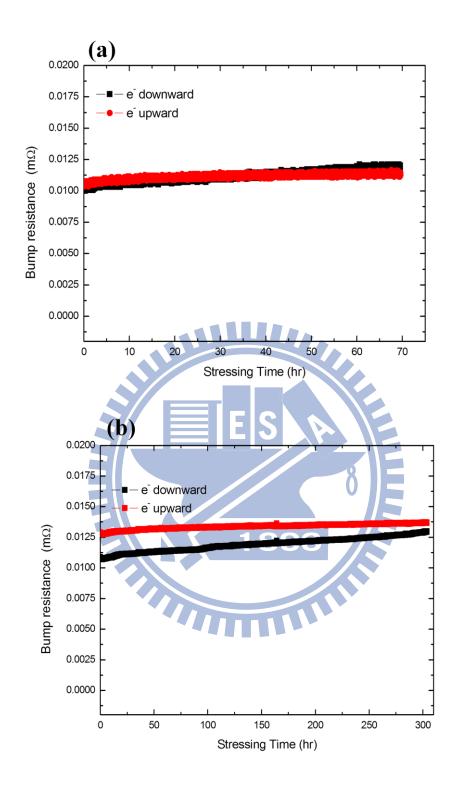

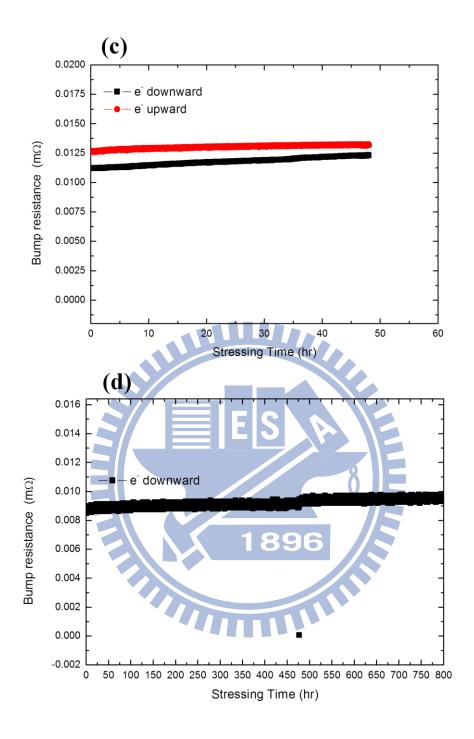

首先,我們把試片的破壞時間設定為電子流向下的銲錫凸塊的電阻初始 值上升 1.2 倍。然後,對不同試片進行通電測試後得出破壞時間做表。表 4-1 所示,我們發現當試片通以 1.9 安培的電流,高銲錫厚度的接點破壞時 間比低銲錫厚度的接點來得短。圖 4-4 為  $100^{\circ}$ C 下通入 1.9 安培和 2.3 安培 的電流,電子流向上和向下的銲錫凸塊的電阻變化對通電時間的曲線圖。 圖 4-3(a)為銲錫厚度為 18-μm 銲錫凸塊在電遷移測試 69 小時下當電子流向 下的凸塊的電阻上升 1.2 倍時的通電曲線圖;圖 4-3(b)銲錫厚度為 10-μm 接 點在電遷移測試302小時下當電子流向下銲錫凸塊電阻上升1.2倍時的通電 曲線圖。根據四組試片的通電曲線圖,我們發現銲錫厚度越高的試片,電 子流向下銲錫凸塊的電阻隨著時間增長上升越明顯,而且在 1.9 安培通電情 況下, 銲錫厚度的減少讓通電破壞時間明顯的增加許多。尤其在銲錫厚度 為 10µm 的時候當電流從 1.9 安培增大至 2.3 安培時我們發現破壞時間又縮 小了。從這結果我們可以利用關鍵乘機公式說明當銲錫厚度縮小至接近臨 界長度時,因為 back stress 應力的關係而讓破壞時間增長。當電流密度增加 的時候,其大小大於臨界電流密度而讓電遷移效應發生,因此破壞時間縮 小。在圖 4-3(d)中電子流向下銲錫凸塊的電阻並沒有隨著時間增長而上升, 雷遷移測試時間甚至是高銲錫厚度試片的18倍以上也還沒到達設定的破壞 標準。因此我們可以說明這條件下的銲錫厚度和電流密度都低於臨界長度和電流密度,電遷移受到 back stress 的影響而沒有發生。

表 4-2 銲錫厚度與破壞時間整理。

| 銲錫厚度(μm)    | 電流密度 (10 <sup>4</sup> A/cm <sup>2</sup> ) | 破壞時間(hr)    |

|-------------|-------------------------------------------|-------------|

| 18          | 2.5                                       | 69          |

| 10          | 2.5                                       | 302         |

| Bridged IMC | 2.5                                       | 760(未達 20%) |

| 18          | 3.0                                       | 45          |

| 10          | _3.0                                      | 44          |

| Bridged IMC | 3.0                                       | 860(未達 20%) |

圖 4-4-1 電子流向下的銲錫凸塊電阻上升 1.2 倍時的電阻曲線圖 (a)1.9 安培 銲錫厚度為 18μm (b)1.9 安培 銲錫厚度為 10μm

圖 4-4-2 電子流向下的銲錫凸塊電阻上升 1.2 倍時的電阻曲線圖 (c)2.3 安培 銲錫厚度為 18μm (d)2.3 安培 銲錫全反應成 IMC

#### 4-3 試片微結構破壞分析

由於本實驗的試片結構設計主要著重於金屬墊層的銅柱能使電子流均勻分布進入銲錫凸塊並減少電流集中效應。在電子流向下的銲錫凸塊,電子流會先從銅柱往下進入因此在設定電阻上升的破壞時間及微結構分析主要以電子流向下的銲錫凸塊為主。

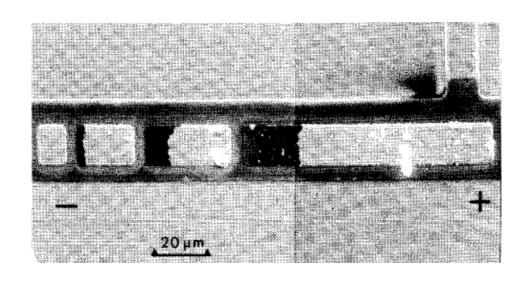

#### 4-3.1 通以 1.9A 微結構分析

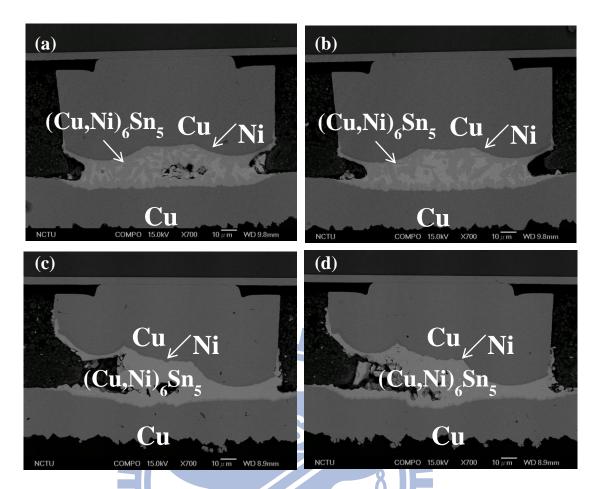

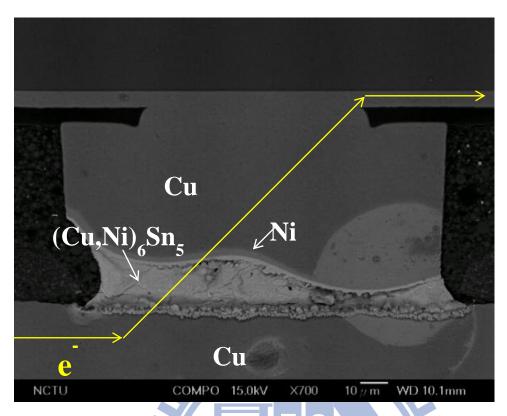

圖 4-5 是對應上一節圖 4-2 電阻變化曲線中的 SEM 橫截面圖。圖 4-5-1 中顯示的是通以 1.9 安培銲錫厚度為 18μm 且電子流向上銲錫凸塊經 69 小時通電測試後的橫截面 SEM 影像。圖中電子流由左下端進入銲錫凸塊,銅墊層中的銅原子隨著電子流推動擴散進入銲錫內部,讓銲錫凸塊的銲錫全形成介金屬化合物,根據 EDX 分析,此介金屬化合物的成分為(Cu,Ni)<sub>6</sub>Sn<sub>5</sub>。而圖 4-5-2 顯示的是電子流向下凸塊的橫截面 SEM 影像。圖中電子流由左上端進入銲錫凸塊,我們發現電子流進入端的鎳層,部分遭到破壞,銅墊層的銅原子還是可以進入銲錫內部反應,形成介金屬化合物(Cu,Ni)<sub>6</sub>Sn<sub>5</sub>而且我們也在銲錫凸塊左上角發現有孔洞形成,銲錫凸塊因為電遷移效應而留下孔洞在靠近電子流進入的陰極端,而在陽極端因為部分錫原子被聚集起來產生 hillock。根據 EDX 分析除了錫原子聚集產生的突出物(hillock)其成分為 Sn 以外,剩餘的銲錫皆反應成(Cu,Ni)<sub>6</sub>Sn<sub>5</sub>。

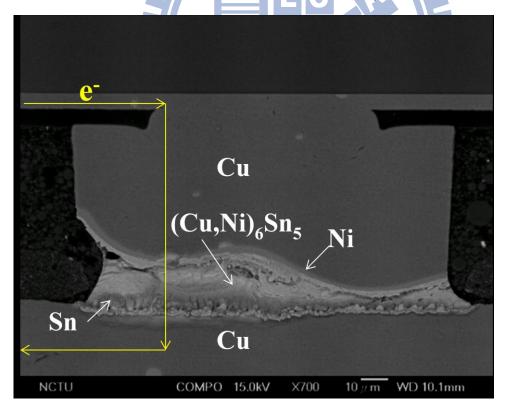

圖 4-6-1 為銲錫厚度為 10μm 且電子流向上的銲錫凸塊經 302 小時通電測試後的橫截面 SEM 影像。圖中的電子流由左下端進入銲錫凸塊,銅原子持續進入把剩餘 10μm 厚的銲錫反應成(Cu,Ni)<sub>6</sub>Sn<sub>5</sub> ,此外我們在這裡也看到陽極端處有 hillock 聚集。圖 4-6-2 顯示的是電子流向下銲錫凸塊的橫截面 SEM 影像。圖中電子流由左上端進入銲錫凸塊,我們發現電子流進入端的鎳層,並沒有像 18μm 厚的銲錫凸塊那樣遭到破壞,銅墊層的銅原子被鎳層阻擋進入銲錫內部反應。可是銲錫凸塊的剩餘銲錫依然全反應形成介金屬化合物而且我們也在銲錫凸塊陰極端發現部分孔洞形成,相信是錫原子電遷移所造成的孔洞,而介金屬化合物也可能因為焦耳熱效應讓下端的銅原子與剩餘銲錫反應成(Cu,Ni)<sub>6</sub>Sn<sub>5</sub> ,所以才看到下層銅墊層消耗比銲錫厚度為 18μm 的銲錫凸塊來得明顯。由於銲錫厚度的降低而接近於關鍵長度因此破壞時間相對的被拉長。

#### 4-3.2 通以 2.3A 微結構分析

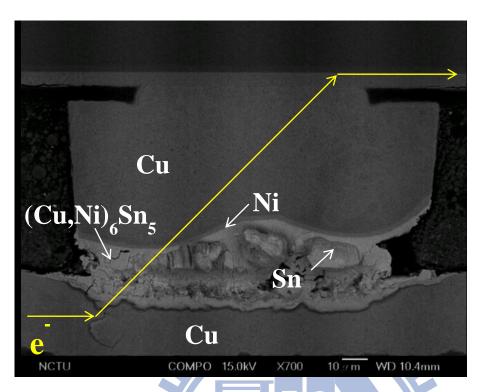

由於電遷移破壞與電流密度有很大的關聯性,通以 2.3 安培的銲錫凸塊其電流密度為 3 x 10<sup>4</sup>A/cm<sup>2</sup> 而通以 1.9 安培的銲錫凸塊其電流密度為 2.5 x 10<sup>4</sup>A/cm<sup>2</sup>, 電流密度差了 0.5 x 10<sup>4</sup>A/cm<sup>2</sup>。所以在銲錫凸塊通以 2.3 安培的 銲錫凸塊,其微結構變化更為顯著而且破壞時間也相對縮短許多。圖 4-7-1 中顯示的是通以 2.3 安培銲錫厚度為 18µm 且電子流向上銲錫凸塊經 45 小

時通電測試後的橫截面 SEM 影像。圖中電子流從左下端進入銲錫凸塊。由 於電流密度相當的大,除了讓銅墊層中的銅原子隨著電子流動擴散進入銲 錫內部以外,銲錫凸塊的錫原子也被大量流動到陽極端聚集成一塊很大的 hillock 富錫相,並在陰極端也留下了大孔洞。根據 EDX 分析, hillock 部 分的成分為 Sn 其餘地方都反應成(Cu,Ni)<sub>6</sub>Sn<sub>5</sub>。因此可以確認此現象是 Sn 原子的電遷移破壞而不是介金屬化合物的電遷移破壞。而圖 4-7-2 顯示的是 電子流向下凸塊的橫截面 SEM 影像。我們從圖中可以看見銅墊層的銅原子 一樣被鎳層阻擋進入銲錫內部反應。在銲錫凸塊陰極端發現孔洞形成,為 錫原子電遷移所造成的孔洞。介金屬化合物由於焦耳熱效應讓下端的銅原 子與銲錫反應成(Cu,Ni)<sub>6</sub>Sn<sub>5</sub>,所以在左下端電流密度較高的地方銅墊層的消 耗比右下來得多。造成孔洞的位置我們將在後面的模擬結果求出電流密度 分佈來解釋孔洞和突出物的位置,並且解釋電流密度集中區域所造成的焦 耳熱效應。接下來的 4 張圖圖 4-8,圖 4-8-1(b)和圖 4-8-2(b)顯示原銲錫厚度 為 10μm 及 IMC bridging 且電子流向下的銲錫凸塊經 44 小時及 18 小時通電 測試後電阻上升1.2倍的橫截面 SEM 影像;圖 4-8-1(a), 4-8-2(a)則顯示電子流 向上的銲錫凸塊的橫截面 SEM 影像。由於這兩種結構條件通電後的結果十 分相似因此把兩種條件的實驗結果放在一起加以說明。圖 4-8-1(a)和圖 4-8-2(a)的現像和通以 1.9 安培的情況很相似。 圖中電子流從左下端進入銲 錫凸塊。由於電流密度很大,在電遷移與焦耳熱效應下,銅墊層中的銅原 子快速的隨著電子流動擴散進入銲錫內部,把剩餘的銲錫都反應成介金屬 化合物。銲錫凸塊的錫原子也被流動到陽極端在某些區域聚集成 hillock 富 錫相,但是在陰極端並沒有發現孔洞。而圖 4-8-1(b)和圖 4-8-2(b)的微結構 變化結果也很相似,我們可以從兩張圖看出剩餘的銲錫在短時間內已經反 應成(Cu,Ni)。Sns 並在陰極端留下部分孔洞而且在陽極端也發現部分 hillock 富錫相。因此我們可以確認只要銲錫凸塊還有剩餘銲錫,不管多寡,只要 電流密度足以讓它發生電遷移現像,都會造成錫原子的電遷移破壞而不是 介金屬化合物的電遷移破壞,此現象在越大電流密度越顯著。銲錫厚度雖 然降低但從關鍵乘積的公式表示電流密度增加也會造成電遷移現像發生。 最後兩張圖 4-9-1,圖 4-9-2 為 100℃ 通以 2.3 安培、原銲錫厚度為全介金 屬化合物(Cu,Ni)<sub>6</sub>Sn<sub>5</sub>的橫截面SEM影像。此條件下由於通電測試進行了800 小時以上既其它銲錫厚度破壞時間的18倍以上電阻也還沒到達1.2倍,因 此我們把通電測試停下來觀測,從微結構的比較來判斷其原因。從微結構 來觀測,我們發現其微結構就算通了800小時以上的高電流密度也完全沒 變。因此我們可以確定介金屬化合物的高揚氏係數特性只要在沒有剩餘銲 錫情況下就可以有效的抗電遷移破壞。

圖 4-5-1 100 °C、1.9 安培、原銲錫厚度 18μm 電子流向上剖面示意圖。

圖 4-5-2 100 °C、1.9 安培、原銲錫厚度 18μm 電子流向下剖面示意圖。

圖 4-6-1 100 °C、1.9 安培、原銲錫厚度 10μm 電子流向上剖面示意圖。

圖 4-6-2 100 ℃、1.9 安培、原銲錫厚度 10 $\mu m$  電子流向下剖面示意圖。

圖 4-7-1 100 °C、2.3 安培、原銲錫厚度 18μm 電子流向上剖面示意圖。

圖 4-7-2 100 °C、2.3 安培、原銲錫厚度 18μm 電子流向下剖面示意圖。

圖 4-8-1 100 °C、2.3 安培、原銲錫厚度 10μm (a)電子流向上(b)電子流向下剖面示意圖。

圖 4-8-2 100 °C、2.3 安培、原銲錫厚度為 IMC 連接 (a)電子流向上(b)電子流向下剖面示意圖。

圖 4-9-1 100°C、2.3 安培、原銲錫厚度為全 IMC 電子流向上剖面示意圖。

圖 4-9-2 100 °C、2.3 安培、原銲錫厚度為全 IMC 電子流向下剖面示意圖。

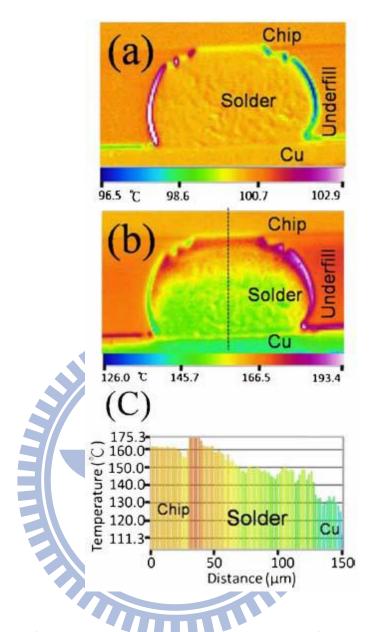

### 4-4 温度感測儀校正銲錫凸塊温度

在本研究中,試片熱源來自加熱盤和電流通過銅導線形成的焦耳熱效應。由於焦耳熱效應的影響,在100°C 通入電流,會造成試片內的實際溫度略高於環境溫度。因此,我們必須利用銅導線電阻溫度係數 (temperature coefficient of resistance, TCR) 來校正銲錫內實際溫度。

首先,金屬熱電阻的電阻值和溫度一般可以用以下的近似關係式表示,即:

$$R = R_{0(T0)} \left[ 1 + \alpha \cdot \Delta T \right] \tag{4.1}$$

R表示溫度T 時的電阻值;

Ro表示溫度To 時對應電阻值;

α 為電阻溫度系數;

1896

然後我們將試片放置於加熱爐中,通以0.1安培電流,然後改變加熱爐的溫度,從50℃到200℃,每隔50℃記錄銅導線相對應的電阻,通入小電流的目的是要去除銅導線本身因通電的焦耳熱效應而發熱。然後記錄到的銅導線電阻與加熱爐之溫度相對應。銅導線電阻對加熱爐溫度變化,再利用線性迴歸求得直線之方程式,我們就可求得銅導線電阻溫度係數。 結果得出通以2.3安培的溫升為68℃,1.0安培的溫升為40℃。

#### 4-5 銲錫凸塊內的電流分佈

圖 4-4 為 ANSYS 有限元素分析法對銲錫凸塊的模擬結果。模擬通以 1.9 安培和 2.3 安培的電流下其銲錫凸塊內的電流分佈情形。由於此兩種通電條 件得出的電流分佈情形十分相似因此只顯示圖 4-4 為模擬本次實驗的通電 測試,因此在試片結構,溫度設定以及利用 semi in-situ 的觀測方式皆以本 實驗的實驗跳件為準則。由於本研究試片銲錫凸塊的上層金屬墊層的銅柱 能使電子流均勻分佈進入銲錫凸塊並有效的減少電流集中效應,因此從模 擬結果中看出電子流在銅柱與銲錫的進入端並沒有嚴重的電流集中效應。 最大電流密度出現在電子流從導線進入銅柱的區域,而左下端的銅墊層為 電子流進出區域,其電流密度也比銲錫凸塊內的電流密度分佈來得大。在 銲錫區域部分,雖然電流集中的區域不在銲錫區域但是我們還是可以從結 果看出電子流進出的路徑區域比其他的區域來得大,因此可以從模擬結果 與實驗結果互相對應。我們回顧之前的微結構分析,孔洞不是出現在電子 流進入端以及電流密度較高的區域那是因為電流密度較高的區域銲錫已經 先反應成 IMC 而較低的區域還未反應成 IMC 因此產生電遷移破壞,而且電 流集中而產生的焦耳熱效應導致銅墊層在左下端的消耗也比右下端來得明 顯。因此,我們可以用此模擬結果來解釋孔洞出現的地方以及原因。

圖 4-10 Ni/Cu 墊層結構通 2.3 安培電流密度模擬圖:

# 第五章 結論

在不同的銲錫厚度通以相同的通電條件下,較高銲錫厚度的銲錫凸塊破壞時間會比低銲錫厚度的銲錫凸塊來得快。當固定電流密度期銲錫厚度降低於關鍵長度以下就會有 back stress 出現抑制電遷移效應。而銲錫全反應成介金屬化合物的情況下給予電流通電,其高揚氏係數特性能長時間而且穩定的抗電遷移破壞,所以其電遷移測試時間在所有試片里為最長。因此只要銲錫凸塊還有剩餘銲錫,只要電流密度足以讓它發生電遷移現像,都會造成錫原子的電遷移破壞而不是介金屬化合物的電遷移破壞;只要在沒有剩餘銲錫情況下就可以有效的抗電遷移破壞。

銅柱雖然能有效的使電子流均勻分布進入銲錫凸塊並減少電流集中效應但是只要通足以導致電遷移現像的電流密度還是會有電流集中效應在電子流進入端。本研究的大電流密度通電條件是加速電遷移破壞的主要原因。我們也從 ANSYS 模擬軟體模擬出的電流密度分佈也合理解釋了突出物 (hillock)孔洞(valley)出現的位置也說明了電流密度較大區域所造成的焦耳熱效應導致該區域銅墊層消耗比較快。

# 參考文獻

- Walter Brattain, "The Transistor, a Semi-Conductor Triode", <u>Physical Review</u>, 74, pp. 230-231, 1948.

- 2. Kilby, J. S. "Semiconductor solid circuits", <u>Electronics</u>, Vol. 32, pp. 110-111, 1959.

- 3. <u>Intel Technology Journal</u>, Vol. 9, Issue 4, 2005.

- 4. Y. W. Chang, S. W. Liang and Chih Chen, "Study of voids formation due to electromigration in flip-chip solder joints using Kelvin bump probes.", <u>Appl. Phys. Lett</u>, 89, 032103, 2006.

- H. B. Huntington and A.R. Grone, "Current-induced marker motion in gold wires", <u>J. Phy.</u>

& Chem. Solids, 20, 76, 1961.

- 6. K. N. Tu, J. W. Mayer and L.C. Feldman, "Electronic Thin Film Science", Macmillan, New York 1992.

- 7. I.A. Blech. and E. Kinsbron. "Electromigration in thin gold films on molybdenum surfaces", Thin solid films, 25,pp. 327,1975.

- 8. I. A. Blech. "Electromigration in thin aluminum films on titanium nitride" <u>J. Appl.</u> Phys , 47, pp.1203 ,1976.

- 9. James R. Black Proc. "Electromigration failure modes in aluminum metallization for semiconductor devices", <u>IEEE</u>, Vol. 57, 9, pp. 1587-1594, 1969.

- T. L. Shao, S. W. Liang, T. C. Lin, and Chih Chen, "Three-dimensional simulation on current-density distribution in flip-chip solder joints under electric current stressing", <u>J. Appl. Phys</u>, 98, pp. 044509, 2005.

- T. L. Shao, S. H. Chiu, Chih Chen, D.J. Yao, and C.Y. Hsu, "Thermal gradient in solder joints under electrical-current stressing", <u>Journal of Electronic Materials</u>, 33, pp. 1350-1354, 2004.

- 12. A. Lee, C.E. Ho, and K.N. Subramanian, "Electromigration induced microstructure and morphological changes in eutectic SnPb solder joints" J. Mater. Res., 22, pp. 3266, 2007.

- 13. European Union Waste in Electrical and Electronic Equipment (WEEE) Directive, 3rd Draft, May 2000.

- 14. Brook Chao, Seung-Hyun Chae, and Paul S. Ho J. "Electromigration enhanced intermetallic growth and void formation in Pb-free solder joints", <u>Appl. Phys</u>, 100, pp.

- 084909, 2006.

- 15. M. Ding, Guotao Wang, Brook Chao, and Paul S. Ho "Effect of contact metallization on electromigration reliability of Pb-free solder joints", J. Appl. Phys, 99, pp. 094906, 2006.

- 16. Y.H. Chen, T.L. Shao, P.C. Liu, and Chih Chen, "Electromigration in Pb-Free Solder Joints in Electronic Packaging" J. Mater. Res., 20, pp. 2432-2442, 2005.

- 17. Seung-Hyun Chae, Xue-feng Zhang, and Paul S. Ho, "Electromigration statistics and damage evolution for Pb-free solder joints with Cu and Ni UBM in plastic flip-chip packages", <u>Sci-Mater Electron</u>, 18, pp. 247-258, 2006.