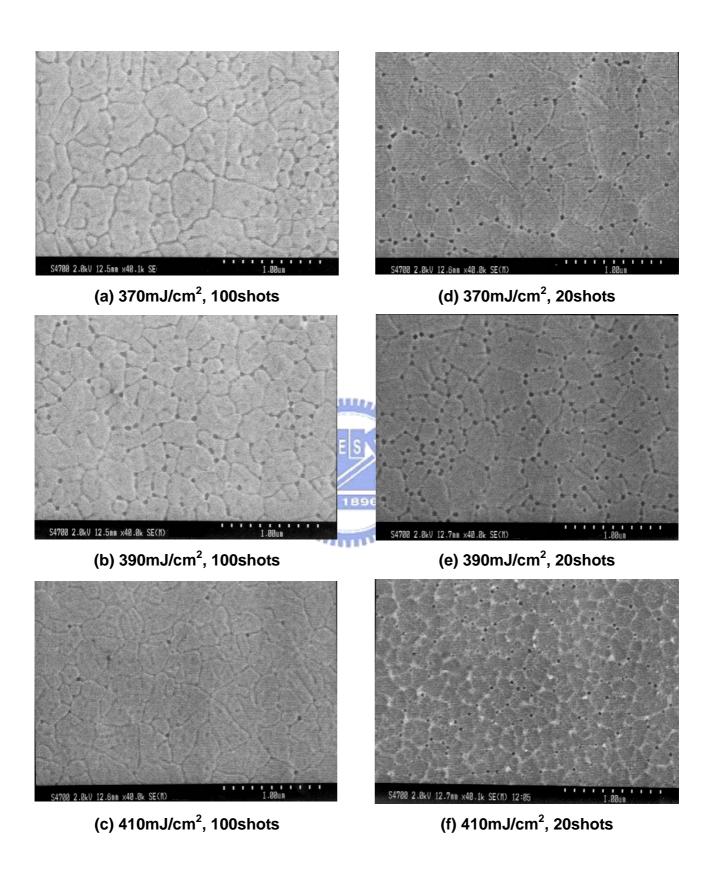

Figure 3.22. SEM micrographs of ELC poly- $Si_{0.77}Ge_{0.23}$  films irradiated at 400°C after modified Secco etching treatment.

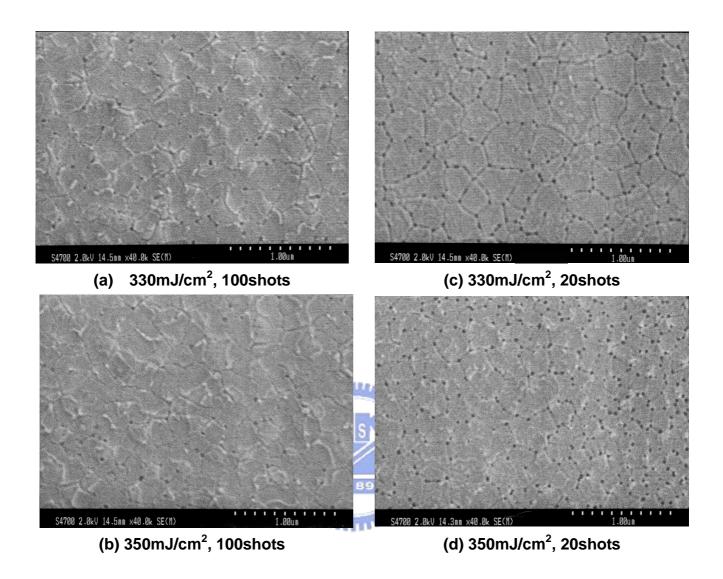

Figure 3.23. SEM micrographs of ELC poly-Si<sub>0.67</sub>Ge<sub>0.33</sub> films irradiated at 400°C after modified Secco etching treatment.

According to Figure 3.21 ~ Figure 3.23, the grain size increases with energy density due to the increasing melting depth, and then reaches a maximum value which means the SLG regime. After that, the grain size decreases due to amorphization and/or micro-crystallization, which result from the complete melting of the poly- $Si_{1-x}Ge_x$  thin film. This represents the laser crystallization mechanism of poly- $Si_{1-x}Ge_x$  thin film is similar to that of poly-Si thin film.

However, from the SEM images of the ELC poly-Si<sub>1-x</sub>Ge<sub>x</sub> thin film, it should be noted that some holes exist at the grain boundary and/or the border between grains. Moreover, the phenomenon becomes more apparent when the laser shot numbers decrease. These holes may be resulted from the Ge-rich region stripped by the modified Secco etching process. According to the excimer laser crystallization mechanism, grain boundary and film surface are the two regions where the solidification process terminates. Thus, during solidification process, the Ge atoms will segregate to the grain boundary at first and then progress toward the film. In other words, Ge segregation occurs not only at the film surface but also at grain boundary. For less laser shot numbers, the total melting period is relatively short. Most segregated Ge atoms will remain at the grain boundary rather than at the film surface due to the shorter total melting time. More holes can be seen at the grain boundary of the ELC poly-Si<sub>1-x</sub>Ge<sub>x</sub> thin film irradiated with less shot number. On the other hand, increase the numbers of laser shot leads Ge atoms to have more chances to segregate from grain boundary toward film surface. Hence, the holes are relatively unobvious in the ELC poly-Si<sub>1-x</sub>Ge<sub>x</sub> thin film irradiated with 100 shot number.

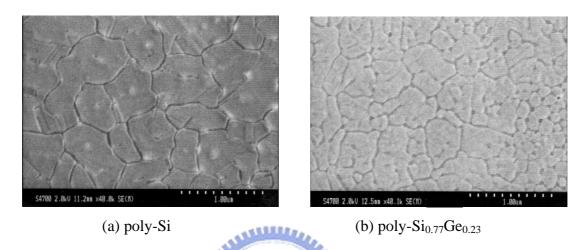

The SEM images of ELC poly-Si and poly-Si<sub>0.77</sub>Ge<sub>0.23</sub> thin films crystallized with optimum laser conditions are also shown in Figure 3.24. The thicknesses of the two thin films are both 500 Å. The laser crystallization was performed at 400°C and the laser energy density was adjusted respectively to lie in the super lateral growth regime. Compare with the ELC poly-Si<sub>1-x</sub>Ge<sub>x</sub> thin film, larger grain size, better crystallinity and fine grain structure are present in the ELC poly-Si thin film. These poor crystall structures of the ELC poly-Si<sub>1-x</sub>Ge<sub>x</sub> thin film may be attributed to the low melting point of the Ge atoms. The lower melting point of Ge atom will result in faster nucleation rate and/or more nucleation sites during excimer laser crystallization. It has been reported that the density of homogeneous nucleation site increased with the Ge atomic concentration [3.61]. Therefore, the nucleation site density of Si<sub>1-x</sub>Ge<sub>x</sub> is much higher than that of silicon. This leads to a smaller grain size in ELC

poly- $Si_{1-x}Ge_x$  thin film. Besides, the Ge segregation must also be responsible for the poor crystallinity of the ELC poly- $Si_{1-x}Ge_x$  thin film. This poor crystallinity of ELC poly- $Si_{1-x}Ge_x$  thin film will put a profound influence on the device performance of ELC poly- $Si_{1-x}Ge_x$  TFTs.

Figure 3.24. SEM images of ELC poly-Si and poly-Si<sub>0.77</sub>Ge<sub>0.23</sub> thin films crystallized with optimum laser conditions. The shot number is 100.

## 3.4 The Crystallization Mechanism of Excimer Laser Irradiated a- $Si_{1-x}Ge_x$ Thin Films

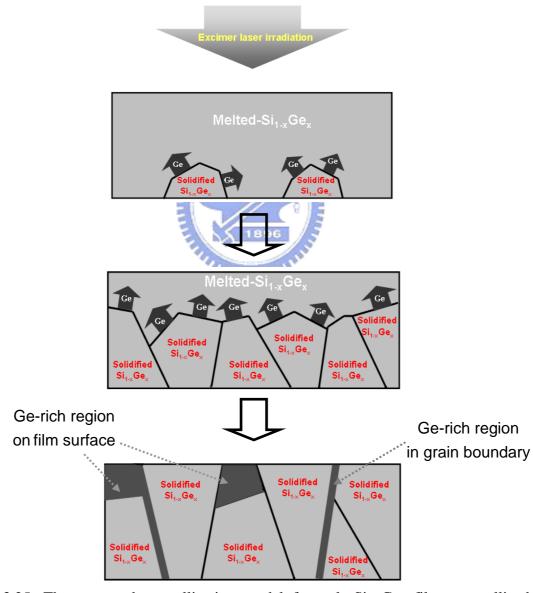

According to the material analysis results shown above, the phenomenon of Ge segregation at grain boundary and film surface will occur for the ELC poly-Si<sub>1-x</sub>Ge<sub>x</sub> thin films. Here a new crystallization mechanism suitable for the ELC poly-Si<sub>1-x</sub>Ge<sub>x</sub> thin films is proposed. Figure 3.25 illustrates the proposed crystallization model for poly-Si<sub>1-x</sub>Ge<sub>x</sub> films crystallized by excimer laser irradiation. The most possible reason responsible for the Ge segregation is the difference in melting point of these two atoms, Si and Ge. The melting temperatures of Si and Ge atoms are 1410°C and 936°C, respectively. Due to the difference of the melting point of Si and Ge atoms, the melting Ge atoms will be driven to progress

toward the liquid-solid interface during the initial solidification of  $Si_{1-x}Ge_x$  thin film because at this moment the temperature of the  $Si_{1-x}Ge_x$  thin film still maintains at the latent heat temperature, which is higher than the melting point of Ge atoms. And then, the un-solidified Ge atoms diffuse along with the propagation of the liquid-solid interface. When solidification process terminate, the Ge atoms also solidify and segregate at the last-solidified regions, where are the grain boundary and film surface. As a result, high Ge atomic concentration is observed at the grain boundary and film surface.

Figure 3.25. The proposed crystallization model for poly-Si<sub>1-x</sub>Ge<sub>x</sub> films crystallized by excimer laser irradiation.

## 3.5 Electrical Characterization of ELC poly-Si<sub>1-x</sub>Ge<sub>x</sub> TFTs

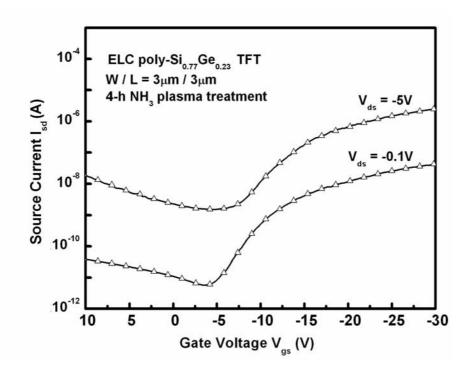

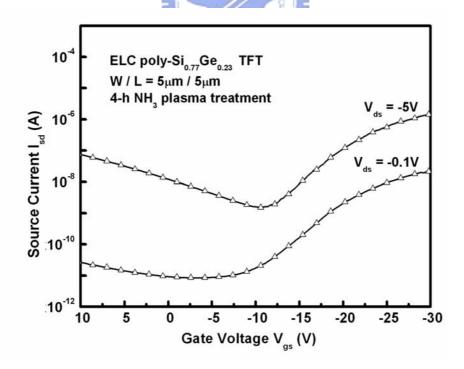

For device applications, the structural properties of the poly-Si<sub>1-x</sub>Ge<sub>x</sub> thin film are of major interest. These properties have a profound influence on the electrical characteristics of the fabricated poly-Si<sub>1-x</sub>Ge<sub>x</sub> TFTs. Figure 3.26 and Figure 3.27 display the typical transfer characteristics of p-channel poly-Si<sub>0.77</sub>Ge<sub>0.23</sub> TFTs fabricated by excimer laser crystallization with different device dimension (W/L =  $3\mu$ m/ $3\mu$ m,  $5\mu$ m/ $5\mu$ m), respectively. The electrical parameters including field-effect mobility ( $\mu$ FE), threshold voltage ( $V_{th}$ ), subthreshold swing, and on/off current ratio are extracted from the transfer characteristics. These electrical characteristics of poly-Si<sub>0.77</sub>Ge<sub>0.23</sub> and poly-Si TFTs are both summarized in Table 3.3. The threshold voltage is defined as the gate voltage required to achieve a normalized drain current of  $I_d = -(W/L) \times 10^{-8}$  A at  $|V_{ds}| = 0.1V$ . The field effect mobility is extracted from the maximum transconductance in the linear region of  $I_d$ - $V_g$  characteristics at  $|V_d| = 0.1V$ . The on/off current ratio is specified by the maximum drain current at  $|V_{ds}| = 5V$  and  $|V_{gs}| = 30V$  over the minimum drain current at  $|V_{ds}| = 5V$ .

**Table 3.3** The electrical characteristic of p-channel poly-Si<sub>0.77</sub>Ge<sub>0.23</sub> and poly-Si TFTs

| W/L<br>(μm/μm) | Device                                     | Mobility<br>(cm²/V-s) | Threshold<br>Voltage (V) | Subthreshold<br>Swing<br>(V/dec) | I <sub>on</sub> /I <sub>off</sub> @<br>V <sub>ds</sub> = -5V |

|----------------|--------------------------------------------|-----------------------|--------------------------|----------------------------------|--------------------------------------------------------------|

| 3/3            | Poly-Si                                    | 70                    | -6.24                    | 0.579                            | 1.7x10 <sup>7</sup>                                          |

|                | Poly-Si <sub>0.77</sub> Ge <sub>0.23</sub> | 2.1                   | -19.1                    | 2.89                             | 1.7x10 <sup>3</sup>                                          |

| 5/5            | Poly-Si                                    | 61                    | -5.18                    | 0.326                            | 9.8x10 <sup>7</sup>                                          |

|                | Poly-Si <sub>0.77</sub> Ge <sub>0.23</sub> | 2.4                   | -25.3                    | 3.82                             | 9.7x10 <sup>3</sup>                                          |

Figure 3.26. Typical transfer characteristics of p-channel poly-Si $_{0.77}$ Ge $_{0.23}$  TFTs fabricated by excimer laser crystallization. W = L =  $3\mu m$ .

Figure 3.27. Typical transfer characteristics of p-channel poly-Si $_{0.77}$ Ge $_{0.23}$  TFTs fabricated by excimer laser crystallization. W = L = 5 $\mu$ m.

As shown in Figure 3.26 and Figure 3.27, even after four hours NH<sub>3</sub> plasma treatment, the overall device characteristics of ELC poly-Si<sub>1-x</sub>Ge<sub>x</sub> TFTs are inferior to those of conventional ELC poly-Si TFTs. The ELC poly-Si<sub>1-x</sub>Ge<sub>x</sub> TFTs exhibited higher leakage current, larger threshold voltage, lower carrier mobility, and worse subthreshold swing. The properties of grain size, quality of the grains, and the grain size distribution of the ELC poly-Si<sub>1-x</sub>Ge<sub>x</sub> thin film will strongly influence the electrical characteristics of the resulting poly-Si<sub>1-x</sub>Ge<sub>x</sub> TFTs. Thus, the poor electrical properties of ELC poly-Si<sub>1-x</sub>Ge<sub>x</sub> TFTs may be ascribed to the high trap state density with and within the grains and the Ge segregation at grain boundaries and thin film surface as mentioned in the previous section. Besides, the high Ge atomic concentration in the active layer may be another reason of the degraded device properties due to the remarkable Si<sub>1-x</sub>Ge<sub>x</sub> alloy scattering.

In the previous section, it has been demonstrated that the ELC poly-Si<sub>1-x</sub>Ge<sub>x</sub> thin films exhibited smaller grain size and poorer grain quality in comparison with the ELC poly-Si thin films under the same laser irradiation conditions owing to the large amount of Ge atoms adding in the thin film. Thus, the device performance of the ELC poly-Si<sub>1-x</sub>Ge<sub>x</sub> TFTs is deteriorated because of the numerous defect state density and grain boundaries existing in the ELC poly-Si<sub>1-x</sub>Ge<sub>x</sub> thin films. It is known that grain boundaries cause trap and tail state which exert a negative influence on nearly all aspects of device performance including an increase in threshold voltage, a decrease in subthreshold slope, a decrease in mobility, an enlargement on leakage current, and poor device stability. The increase of the threshold voltage indicates that the devices whose channels have more defects simply require large gate voltage in order to fill the great number of traps before device can turn on. On the other hand, after trapping the free carriers, the defect states become electrically charged and created a potential energy barrier, which acted as potential barriers during carrier transport from drain to source [3.62]. This leads to the reducing number of free carriers available for electrical conduction, which result in a decrease in on-state current.

In addition to the high defect states in ELC poly-Si<sub>1-x</sub>Ge<sub>x</sub> thin films, the Ge segregation at the grain boundary and thin film surface during ELC process is also responsible for the degraded device performance of poly-Si<sub>1-x</sub>Ge<sub>x</sub> TFTs. As discussed in the previous section, the Ge segregation at film surface will result in a Ge-rich thin layer at the interface between the gate oxide and the active region. Unfortunately, the channel carrier transporting path is just occupied by this Ge-rich layer. The thin surface layer contains a relatively high density of Ge dangling and strain bonds. These Ge dangling and strain bonds also hider the carriers transport from drain to source. Form the viewpoint of energy band diagram, these Ge dangling and stain bonds lead to the formation of trapping states within the forbidden bandgap of the poly-Si<sub>1-x</sub>Ge<sub>x</sub>. The trapping states are electrically active and distributed at the upper, middle, and lower parts of the forbidden bandgap. According to the report by I.W. Wu et al [3.63], the threshold voltage and subthreshold swing of TFTs depended on the trapping states distributed at the middle of bandgap, and the field-effect mobility and leakage current were influenced by the tail states near the conduction band and valence band. Thus, the large amounts of Ge dangling and strain bonds inside the Ge-rich surface layer are responsible for the degraded characteristics of the ELC poly-Si<sub>1-x</sub>Ge<sub>x</sub> TFTs.

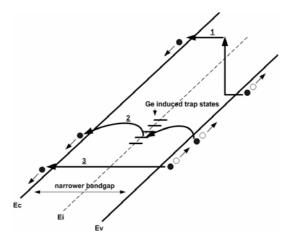

On the other hand, it could be noticed that the ELC poly- $Si_{1-x}Ge_x$  TFTs exhibit higher off-state current even though the carrier field–effect mobility is lower. Figure 3.28 displays the leakage current mechanism of poly- $Si_{1-x}Ge_x$  TFTs. According to the leakage current mechanism, the leakage current of poly- $Si_{1-x}Ge_x$  TFTs can be divided into three different regimes depending on the applied voltage, i.e. the electrical field in the channel. These three regimes are called thermionic emission, thermionic field emission, and band-to-band tunneling, respectively. At low drain bias ( $V_d \sim 0.1V$ ), the activation energy of a carrier emitted from the trap to contribute to conduction process is about the half of the bandgap of the poly- $Si_{1-x}Ge_x$ . Thus, thermal emission is the dominant leakage mechanism in the low field. As the drain bias increases, the high field in the drain depletion region reduces the barrier that

carrier must overcome. As such, the dominant leakage current mechanism is thermionic field emission. This process is accomplished by combination of emission and tunneling process. Further increase of drain bias presents almost no barrier to the carrier motion. At this moment, the dominant leakage mechanism is pure tunneling. No matter how large the applied voltage is, the leakage current in the three regimes are all exponentially dependent on the potential barrier height at the drain junction, which is related to the height of bandgap of the active layer. Reduce the energy bandgap of the active layer will increase the probability of carrier tunneling through the drain energy barrier to the channel region, leading to high leakage current. With the adding of Ge atom in Si, the energy bandgap become narrower. In addition to the narrower bandgap, the segregated Ge atoms also lead to large amounts of trap states at drain depletion junction. According to the leakage current mechanism, the tunneling probability of carrier emitted from the trap to contribute to conduction process is determined by the spatial and energetic of trap states as well as lateral electric field in the drain depletion region. The existence of trap states in the depletion region greatly lowers the necessary fields and reduces the barriers for the leakage current. Thus, compared with poly-Si TFTs, the carriers in the poly-Si<sub>1-x</sub>Ge<sub>x</sub> TFTs have more chances to tunneling through the energy bandgap at the drain depletion region, which result in a higher leakage current.

Figure 3.28. Schematic illustration of the leakage mechanism model in poly-Si<sub>1-x</sub>Ge<sub>x</sub> TFTs

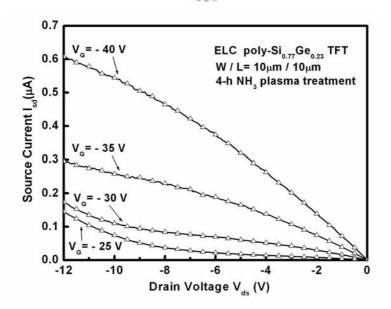

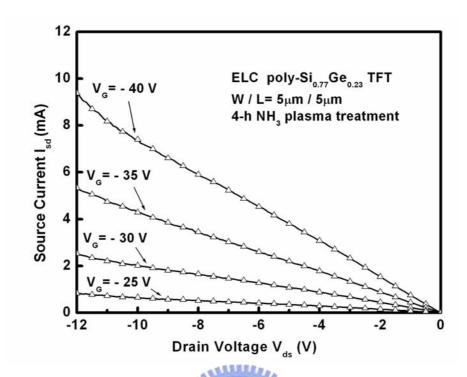

Typical output characteristics of p-channel poly-Si<sub>1-x</sub>Ge<sub>x</sub> TFTs fabricated by excimer laser crystallization with different device dimension (W/L=10μm/10μm, 5μm/5μm) are shown in Figure 3.29 and Figure 3.30, which the high gate bias are –25, -30, -35, and -40V, respectively. The laser conditions were controlled in the optimum regimes. The channel lengths and widths are 10μm and 5μm for the two devices, respectively. As shown in the figures, even under a relatively high gate bias, the smaller turn-on current and the lack of saturation are observed in the output characteristics of the ELC poly-Si<sub>1-x</sub>Ge<sub>x</sub> TFTs. It may also be attributed to the poor crystallinity as well as the Ge segregation of the ELC poly-Si<sub>1-x</sub>Ge<sub>x</sub> thin film. These Ge dangling and strain bonds also hider the carriers transport from drain to source, which resulting in a smaller on-state current. On the other hand, the floating-body substrate and charge trapping by defect states cause serious avalanche induced effects in poly-Si TFTs [3.64] – [3.65]. As the trap state density in the polycrystalline film increases, the avalanche phenomenon becomes more apparent. Thus, for the ELC poly-Si<sub>1-x</sub>Ge<sub>x</sub> thin film, the lack of saturation is also ascribed to the high trap state density in the ELC poly-Si<sub>1-x</sub>Ge<sub>x</sub> thin film.

Figure 3.29. Typical output characteristics of p-channel poly- $Si_{0.77}Ge_{0.23}$  TFTs fabricated by excimer laser crystallization.  $W=L=10\mu m$ .

Figure 3.30. Typical output characteristics of p-channel poly- $Si_{0.77}Ge_{0.23}$  TFTs fabricated by excimer laser crystallization.  $W = L = 5\mu m$ .

## 3.6 Summary

The deposition parameters and mechanisms of a-Si<sub>1-x</sub>Ge<sub>x</sub> thin film by LPCVD have been studied in detail in this chapter. To overcome the nucleation problem of the deposition of a-Si<sub>1-x</sub>Ge<sub>x</sub> thin film on SiO<sub>2</sub>, a thin seed Si layer must be pre-deposited on SiO<sub>2</sub> surface by exposing the SiO<sub>2</sub> to SiH<sub>4</sub> gas for a short time. A-Si<sub>1-x</sub>Ge<sub>x</sub> alloy demonstrates a lower deposition temperature compared to a-Si thin film. The deposition rate is enhanced as the Ge atomic concentration in the a-Si<sub>1-x</sub>Ge<sub>x</sub> thin film increases, which can be attributed to GeH<sub>4</sub> acted as a catalyst to enhance hydrogen desorption from the film surface. In addition, under a fixed gas flow ratio, the Ge atomic fraction in the Si<sub>1-x</sub>Ge<sub>x</sub> thin film increases as the deposition temperature decreases.

The mechanisms of excimer laser crystallization of LPCVD a-Si<sub>1-x</sub>Ge<sub>x</sub> thin film are also investigated. The effects of Ge atomic concentration and laser irradiation conditions for the ELC poly-Si<sub>1-x</sub>Ge<sub>x</sub> thin films have also been demonstrated. Several material analysis characterization results indicate that a-Si<sub>1-x</sub>Ge<sub>x</sub> thin film can be effectively crystallized by excimer laser irradiation. However, compare to the ELC poly-Si thin film, the ELC poly-Si<sub>1-x</sub>Ge<sub>x</sub> thin film exhibits poor crystallinity. Furthermore, Ge segregation at the grain boundary and film surface occurs in the ELC poly-Si<sub>1-x</sub>Ge<sub>x</sub> thin film. The most possible reason responsible for the Ge segregation is the difference in melting point of these two atoms, Si and Ge.

Low-temperature poly-Si<sub>1-x</sub>Ge<sub>x</sub> TFTs have been fabricated by excimer laser crystallization. In comparison with the ELC poly-Si TFTs, the ELC poly-Si<sub>1-x</sub>Ge<sub>x</sub> TFTs exhibited higher leakage current, larger threshold voltage, lower carrier mobility, and inferior subthreshold swing. It can be attributed to the worse crystallinity of the ELC poly-Si<sub>1-x</sub>Ge<sub>x</sub> thin film, which resulting from the different thermal properties of Si and Ge. On the other hand, the segregation of Ge atoms at the grain boundaries and thin film surfaces during ELC is also responsible for the deteriorated device performance.

The ELC poly- $Si_{1-x}Ge_x$  TFTs exhibit higher off-state current even though the carrier field–effect mobility is lower. Reduce the energy bandgap of the active layer, which resulting from the adding of Ge atoms in Si, will increase the probability of carrier tunneling through the drain energy barrier to the channel region, leading to high leakage current. Another possible reason responsible for the higher leakage is the inferior crystallinity of the poly- $Si_{1-x}Ge_x$  thin film.