undergoes partial melting at the surface of Si-film. It results the structure to consist with two layers: an upper large grained layer (whose thickness is related to the primary melt induced by the laser) and a lower fine-grained layer (related to the explosive crystallization) [4.13].

As the energy is further increased, the Si film will be achieve the maximum grain size, which is almost totally melted and only few unmelted crystalline clusters are sparsely distributed. When this condition occurs, the grains grow laterally around the seeds until they impinge on each other and then grain size in excess of 1-μm can be reached. This particular condition is often referred to as super lateral growth (SLG) [4.14]. The excellent performance in TFTs can be obtained with field-effect mobility in the range of 300-400 cm<sup>2</sup> cm<sup>2</sup>/V-s due to a good crystallinity with very few in-grain defects during the melt-regrowth process. [4.15]-[4.16].

However, at excess energy density, the Si film will be completely melted and a small grain structure will be appeared because the substantial undercooling of the liquid occurs before solidification via homogeneous nucleation and growth can take place [4.14]. Additionally, the combination in Si of strong optical absorption of the UV light and small heat diffusion length during the laser pulse (~100 nm) implies that Si surface region can be melted by high temperature but without appreciable damage (< 400 °C) of the substrate. This makes ELC process compatible with glass substrates that is one of the major advantage of this technique.

#### 4.1 Conventional SPC HVTFTs and Novel ELC HVLDMOS

Low-temperature polysilicon high-voltage thin film transistors (LTPS HVTFTs) are widely studied and discussed for liquid crystal displays, field emission displays,

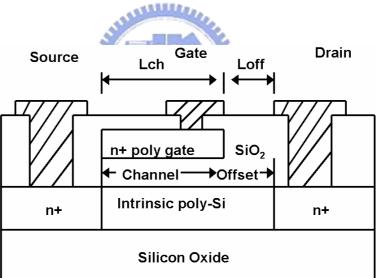

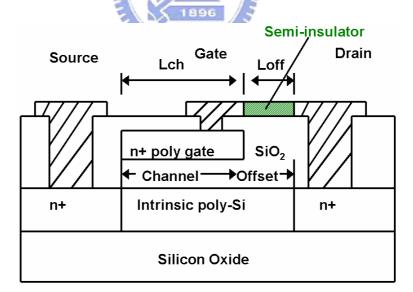

plasma displays, high speed printers, and so on [4.17], [4.18]. In recent years, a variety of HVTFT structures have been proposed in order to carry out the three-dimensional (3-D) circuit integrations and system-on-panel (SOP) applications. They include the offset-drain (OD), lightly-doped-drain (LDD), metal-field-plated (MFP), multi-gate (MG), and semi-insulating (SI) HVTFTs. As shown in Fig. 4-1, Offset-drain (OD) HVTFT has been established as a fundamental structure for high voltage operation in large area applications in 1982 [4.19], [4.20]. The drain region is offset from the channel region to provide high breakdown voltage by reducing the electrical field peaks in high voltage operation. However, the improvement in off state for high blocking capability accompanied with an undesirable high series resistance, which associated with the offset region and caused the degradation in on state performance. In 1988, a

Fig. 4-1. Schematic structure of offset-drain (OD) high-voltage thin film transistor (HVTFT) with a high resistance offset region from drain to source.

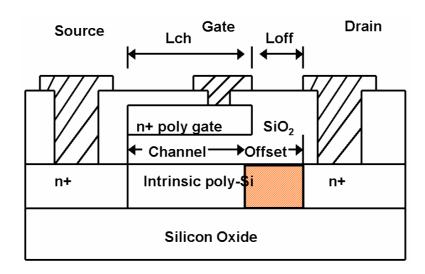

lightly doped drain (LDD) HVTFT has been proposed to utilize an ion implantation process in the offset region [4.21], [4.22]. As shown in Fig. 4-2, the lightly dope in offset region can improve the device on state performance due to an increased

conductivity in the offset region. But, the improvement in the on state performance by lightly dope may result in a degradation of the blocking voltage capability.

Fig. 4-2. Schematic structure of lightly doped drain (LDD) HVTFT with a lightly doping implantation in the offset region.

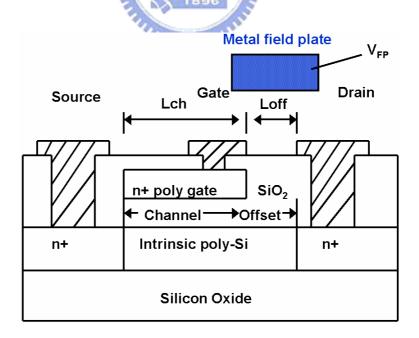

Fig. 4-3. Schematic structure of metal-field-plate (MFP) HVTFT with a metal field plate across the offset region.

In 1990, metal-field-plated (MFP) HVTFT has been developed by implementation of a metal field plate on top of the field oxide [4.23]. As shown in Fig. 4-3, this field plate covers the entire offset region, thus directly modulating the conductivity of the offset region. The major advantage of this structure is that the current pinching phenomenon can be eliminated and much improved the on state characteristics. However, the blocking voltage capability is reduced due to the potential discontinuity on both ends of the field plate, which will induce oxide failure. Moreover, it requires an additional external bias line to supply voltage to the field plate, which may lead to a significant increase in the complexity of display applications. In 1991, multi-gate (MG)

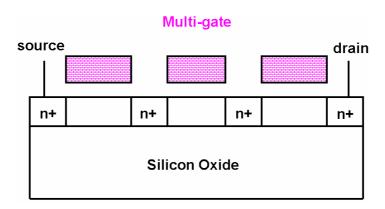

Fig. 4-4. Schematic structure of multi-gate (MG) HVTFT with many gate elements between the drain and source region.

HVTFT has been demonstrated with combination of several small TFTs in a device [4.24]. By this structure in Fig. 4-4, the drain voltage is divided equally across each elemental TFT thereby lowering the operation voltage in each element to cause large increase of breakdown voltage. However, it requires a large number of TFT elements to handle high voltage and thereby the parasitics from each elemental TFT are cumulative. Moreover, it also has the reliability problem as the high electric field is across the thin

gate dielectric.

In 1997, Semi-insulating (SI) HVTFT has been proposed with semi insulating field plate in lieu of metal field plate, which covers the entire offset region and connects the drain to the gate in Fig. 4-5 [4.25]. In the on state, the potential difference between the semi insulator and the underlying intrinsic polysilicon extends the electron accumulation layer under the gate into the offset region there by improving the on state performance. In the off state, the semi insulator acts to smooth the potential distribution across the entire offset region thereby reducing the field peaks near the gate and drain which are responsible for premature breakdown. However, such structure is susceptible to misalignment and the deposition of a semi insulator layer directly on silicon often induces surface contamination leading to large leakage currents and poor reproducibility. Moreover, the use of a semi insulator layer will decrease the switching speed due to the extra resistance-capacitance charging path.

Fig. 4-5. Schematic structure of semi-insulating (SI) HVTFT with connect of semi insulating field plate from drain to gate electrode over the offset region.

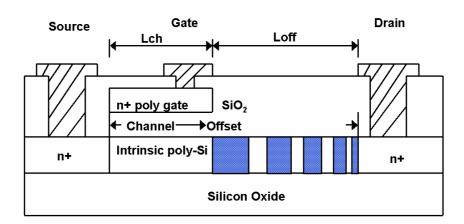

Although these devices provide the high blocking or current capability, most of them are not easy or effective to apply in the glass-compatible electronic systems. In this study, the low-temperature polysilicon high-voltage lateral double diffused MOS (LTPS HVLDMOS) has been demonstrated by combining the technology of thin film transistor into the power device at the first time. The power structure will led the LTPS HVLDMOS to possess the superior blocking capability from the reduced-surface-field (RESURF)—including of drift region (offset region), Pwell doping, field oxide, extended gate, and extended drain designs—against the previous HVTFTs with offset region only [4.26]. On the other hand, in order to obtain the high performance LTPS HVLDMOS, the influence and necessity of excimer laser crystallization for improving its current capability will be estimated as the following. Furthermore, since the hydrogen bonds under bias operation are unstable [4.27], the hydrogenation is temporarily not considered for avoiding an increase of issue complexity.

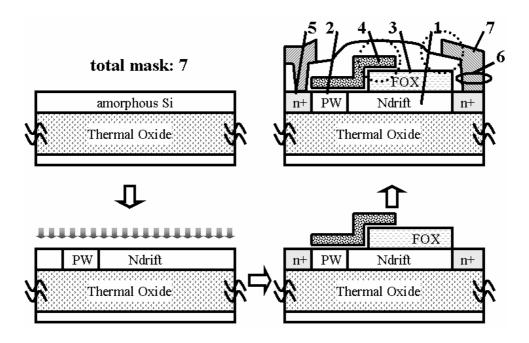

#### 4.2 Device Fabrication

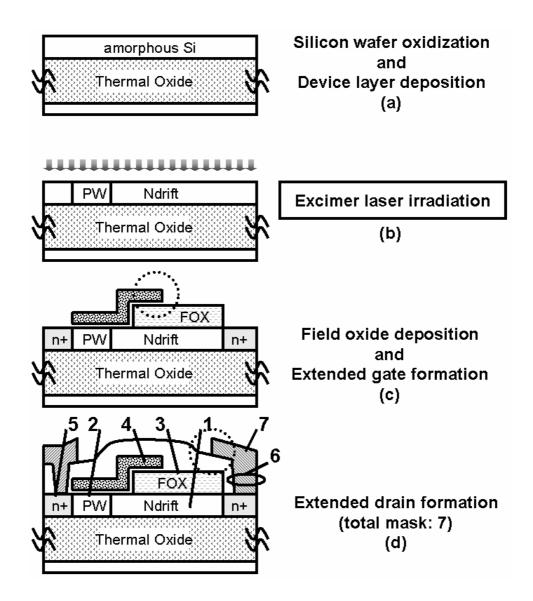

The key processes for fabricating high-performance LTPS HVLDMOS were illustrated by the sequence of Figs. 4-6 (a), (b), (c) and (d). At first, a 1.5- $\mu$ m-thick wet oxide was grown on a (100) silicon wafer to be as a glass base. A 1000-Å-thick amorphous silicon (a-Si) was deposited on it with the pure silane (SiH<sub>4</sub>) source by LPCVD at 550 °C to become the device layer in Fig. 4-6 (a). Secondly, the a-Si drift region was implanted with 50 KeV phosphorous dose of 7 × 10<sup>11</sup> cm<sup>-2</sup> to reduce the current path resistance. P-type well with 60 KeV boron dose of 3 × 10<sup>13</sup> cm<sup>-2</sup> was created to increase the depletion width in high doping N-type drift region (N<sub>p</sub>W<sub>p</sub>=N<sub>n</sub>W<sub>n</sub>). Then, the 1000-Å-thick a-Si was crystallized using KrF excimer pulse

Fig. 4-6. Key processes for fabricating the high performance LTPS HVLDMOS using excimer laser crystallization in the sequence of (a), (b), (c) and (d).

laser (λ=248-nm) with an energy density of 470 mJ/cm<sup>2</sup> and a shot density of 100 per area at room temperature in Fig. 4-6 (b). Thirdly, a 5000-Å-thick field oxide (FOX) was formed by plasma enhanced chemical vapor deposition (PECVD) at 350 °C to reduce the surface electric field (RESURF) from gate and drain edges in the drift region. A 1000-Å-thick gate oxide was deposited by PECVD at 350 °C and a 2000-Å-thick a-Si gate electrode was defined

across the FOX to split the Pwell/Ndrift junction electrical field. High dosage phosphorous and boron implantation were carried out to form n+ drain, source, gate and p+ butting regions in Fig. 4-6 (c). Finally, a 5000-Å-thick PECVD passive oxide was deposited and then all dopants were activated by furnace annealing at 600°C for 12 hrs without hydrogenation. A 5000-Å-thick aluminum was defined overlap the passive oxide and the extended metal drain was functioned to split the Ndrift/n+ drain junction electrical field in Fig. 4-6 (d). Moreover, the LTPS HVLDMOS except the laser treatment was also fabricated with the same conditions for comparison.

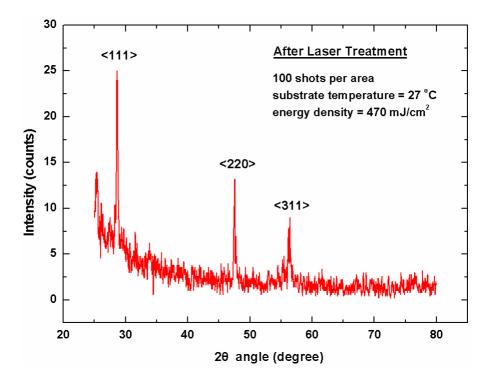

Fig. 4-7. X-ray diffraction spectra of polycrystalline silicon film crystallized by excimer laser annealing with an energy density of 470 mJ/cm<sup>2</sup> and a shot density of 100 per area at room temperature.

#### 4.3 Results and Discussion

#### 4.4.1 X-Ray Diffraction and SEM Photography

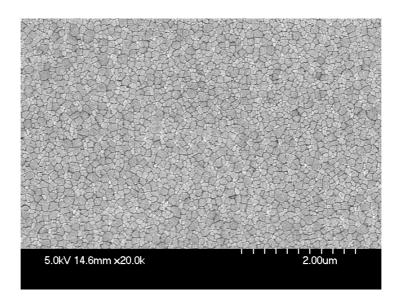

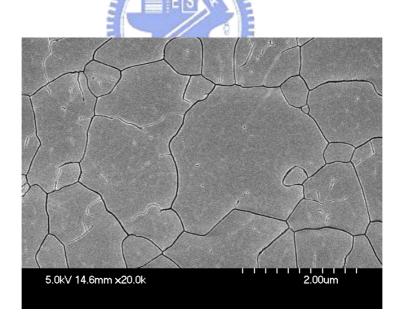

To investigate the mechanism of grain growth phenomenon, the poly-Si films after excimer laser treatment were evaluated by x-ray diffraction spectra. According to C. V. Thompson et al. experimental results [4.28]-[4.31], the grain growth in thin films is affected by anisotropy of the surface free energy. As shown in Fig. 4-7, it is known that the (111) peak intensity is the trend of minimum surface free energy and the (100) texture is the minimum Si/SiO<sub>2</sub> interface energy. In other words, it also could be thought that the magnitude of the free surface energy is larger than the magnitude of the Si/SiO<sub>2</sub> interface energy. The (111) peak intensity would be radically increased and the (220) peak simultaneously disappeared as the number of laser shots was increased. Figure 4-8 (a) and (b) showed the scanning electron microscopy (SEM) images of secco-etched poly-Si films after different laser energy fluence treatment. The films produced had a maximum grain size of 3-µm with strong (111) crystallographic orientation and a mono-modally distributed grain size of 1.5-µm, on average. The surface morphology of these films was very smooth and the crystallinity was excellent with minimal interface defects. The resulting of thin poly-Si film could be further improved with decreasing the film thickness, increasing the substrate temperature, increasing the average surface energy anisotropy, and increasing the average grain boundary mobility—such doping with phosphorus or arsenic in the n-drift region (offset region).

Fig. 4-8. (a) Scanning electron microscopy (SEM) image of Secco-etched poly-Si film crystallized in the partial melting regime by a low energy density of 435 mJ/cm<sup>2</sup> and a shot density of 100 per area at room temperature.

Fig. 4-8. (b) Scanning electron microscopy (SEM) image of Secco-etched poly-Si film crystallized in the super lateral growth (SLG) regime by a high energy density of 458 mJ/cm<sub>2</sub> and a shot density of 100 per area at room temperature.

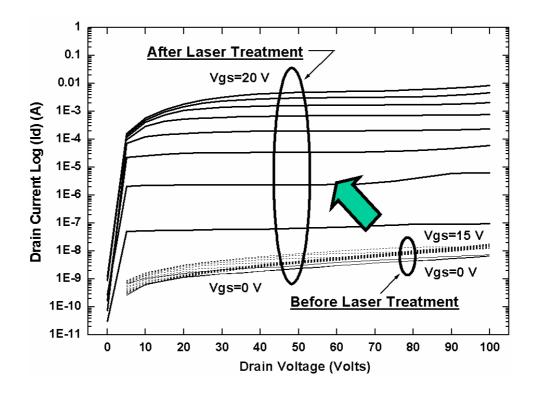

### 4.4.2 Transfer Characteristics before/after Excimer Laser Treatments for LTPS HVLDMOS

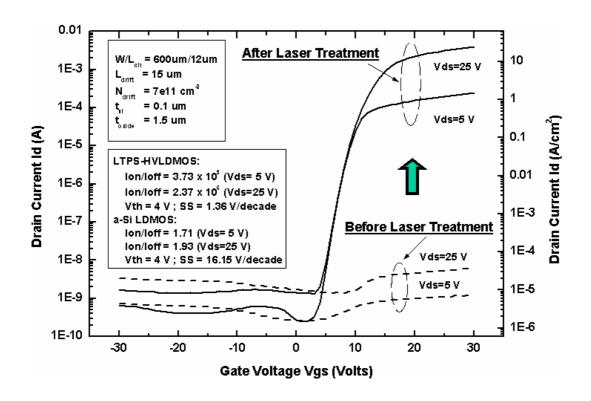

Figure 4-9 and Table 4-1 showed the gate transfer characteristics before and after excimer laser treatments for LTPS HVLDMOS. The device dimensions and doping concentration were listed: W=600- $\mu$ m; L<sub>ch</sub>=12- $\mu$ m; L<sub>drift</sub>=15- $\mu$ m; N<sub>drift</sub>=7 × 10<sup>11</sup> cm<sup>-2</sup>;  $t_{si}$ =0.1- $\mu$ m;  $t_{oxide}$ =1.5- $\mu$ m. For the conventional low voltage TFT, the  $I_{OFF}$  current would be increased as negative gate and positive drain voltage increased. This phenomenon, called anomalous leakage current, was generated via grain boundary traps by the field emission [4.32]. However, for the LTPS HVLDMOS, the negative gate bias current was almost constant regardless of the drain voltage increase even up to Vds=25 V. The reason was that the extended gate and drift region design could effectively reduce the Pwell/Ndrift junction electric field [4.33]. The threshold voltage after/before laser treatment was not changed at 4 volts due to the similar well concentrations, which replaced the channel defects domination in the intrinsic well region. The subthreshold swing (SS), depended on the number of the deep state [4.34], was significant improved from 16.15 V/decade to 1.36 V/decade after laser treatment. The ON/OFF current ratios (I<sub>ON</sub>/I<sub>OFF</sub>) after laser treatment showed the excellent promotion with the magnitudes of  $3.73 \times 10^5$  and  $2.37 \times 10^6$  against the magnitudes of 1.71 and 1.93 before laser treatment at Vds=5 V and Vds=25 V. Additionally, it was worth to mention that there was a valley near the gate bias of 0 V as the LTPS HVLDMOS after laser treatment biased at Vds=5 V but at Vds=25 V the phenomenon was not appeared. It was because the leakage current was generated less at enough low drain bias (0.1 V i Vds i 5 V) and limited by the drift region (offset region) even at Vds=-30 V. However, as the drain bias was large (10 V i Vds i 25 V), the leakage current was directly up to high value so that the valley will not appear.

Fig. 4-9. Transfer characteristics before and after excimer laser treatments for LTPS  $\frac{1}{12-\mu m} = \frac{1}{12-\mu m} = \frac{1}{12$

Table 4-1. Summary of the transfer characteristics before and after excimer laser treatments for LTPS HVLDMOS with optimal room temperature irradiation.

|                                                    | Before laser treatment | After laser treatment |

|----------------------------------------------------|------------------------|-----------------------|

| Threshold Voltage (V)                              | 4                      | 4                     |

| Subthreshold Swing (V/dec)                         | 16.15                  | 1.36                  |

| Max. I <sub>ON</sub> /I <sub>OFF</sub> at Vds=5 V  | 1.71                   | $3.73\times10^5$      |

| Max. I <sub>ON</sub> /I <sub>OFF</sub> at Vds=25 V | 1.93                   | $2.37\times10^6$      |

| Breakdown Voltage (V)                              | 285                    | 240                   |

## 4.4.3 Relationship between ON/OFF Current Ratio and Drift Length before/after Excimer Laser Treatments for LTPS HVLDMOS

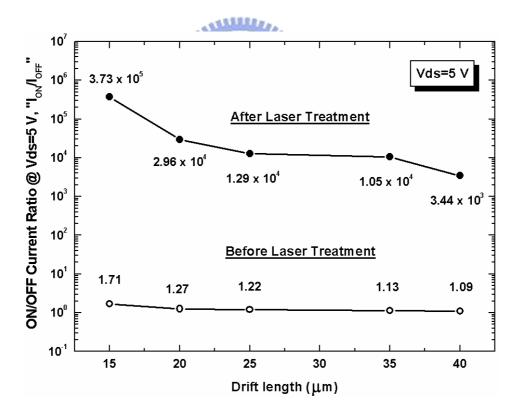

Figure 4-10 (a) and (b) showed the relationship of ON/OFF current ratios and drift length before and after excimer laser treatments for LTPS HVLDMOS at drain bias of 5-V and 25-V, respectively. The observed drift lengths ( $L_{drift}$ ) of LTPS HVLDMOS were varied from 15- $\mu$ m to 40- $\mu$ m with a step of 5- $\mu$ m. The on-state current ( $I_{ON}$ ) and off-state current ( $I_{OFF}$ ) of ON/OFF current ratio were defined at the gate biases of 30-V and -30-V, respectively. While the drain voltage was biased at small value of 5-V in figure 4-10 (a), the ON/OFF current ratios of LTPS HVLDMOS after excimer laser treatment

Fig. 4-10. (a) Relationship between ON/OFF current ratio and drift length before and after excimer laser treatments for LTPS HVLDMOS at the drain bias of 5-V.

were abruptly decayed about 29 times from  $3.73 \times 10^5$  to  $1.29 \times 10^4$  as the drift length variation from 15- $\mu$ m to 25- $\mu$ m. The ON/OFF current ratios of LTPS HVLDMOS before excimer laser treatment were also decayed abruptly about 1.4 times from 1.71 to 1.22 as the drift length variation from 15- $\mu$ m to 25- $\mu$ m but the decayed degree was much smaller than that after excimer laser treatment. As the drift length was extended from 25- $\mu$ m to 35- $\mu$ m, the decrease in ON/OFF current ratios was slow down and almost not changed regardless of the LTPS HVLDMOS after/before excimer laser treatment. After the drift length is over 35- $\mu$ m, the ON/OFF current ratios of LTPS HVLDMOS after excimer laser treatment started to decay about 3 times from 1.05 × 10<sup>4</sup> to 3.44 ×10<sup>4</sup> but that before excimer laser treatment was still almost not changed.

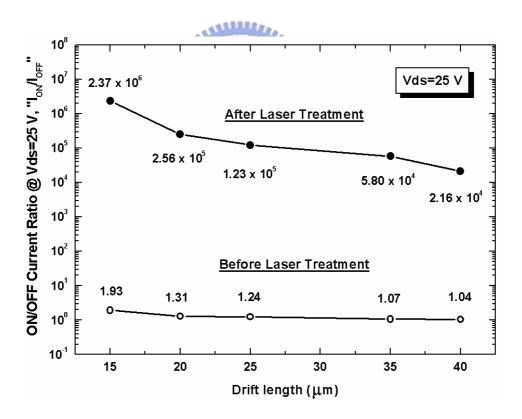

Fig. 4-10. (b) Relationship between ON/OFF current ratio and drift length before and after excimer laser treatments for LTPS HVLDMOS at the drain bias of 25-V.

While the drain voltage was biased at large value of 25-V in figure 4-10 (b), the ON/OFF current ratios of LTPS HVLDMOS after excimer laser treatment were abruptly decayed with the smaller magnitude of 19 times from  $2.37 \times 10^6$  to  $1.23 \times 10^5$  as the drift length variation from 15- $\mu$ m to 25- $\mu$ m. The ON/OFF current ratios of LTPS HVLDMOS before excimer laser irradiation was also decayed abruptly with smaller variation of 1.55 times from 1.93 to 1.24 compared to that at drain bias of 5-V. From the drift length extension of 25- $\mu$ m to 35- $\mu$ m, the decrease in ON/OFF current ratios was still slow down and almost not changed regardless of the drain bias of 5-V or 25-V after/before excimer laser treatment. After the drift length is over 35- $\mu$ m, the ON/OFF current ratios of LTPS HVLDMOS after excimer laser treatment started to decay about smaller 2.68 times from  $5.80 \times 10^4$  to  $2.69 \times 10^4$  but that before excimer laser treatment was still almost not changed. The ON/OFF current ratios variation at drain bias of 25-V was smaller than that at drain bias of 5-V so that the variations could be suppressed by higher drain voltage as the drift length extension.

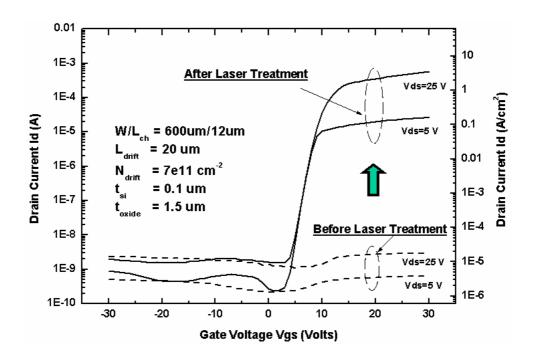

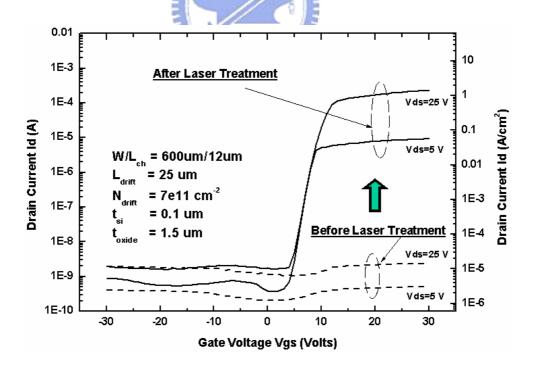

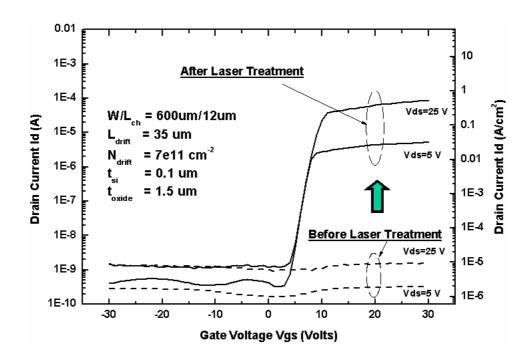

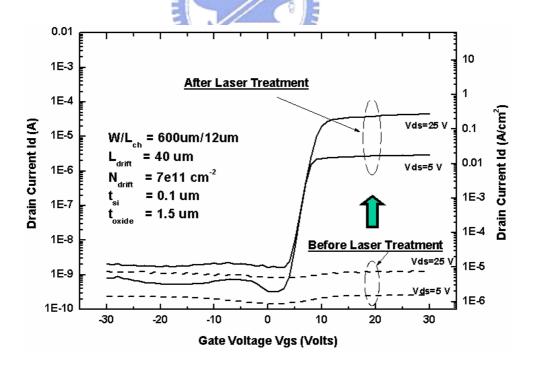

Above the mentioned results, the ON/OFF current ratios and its variations before excimer laser treatment were entirely much smaller than those after excimer laser treatment as the increase in the drift length. It was because the low quality poly-Si film before excimer laser treatment was dominated the whole resistance with large trapping defect density which resulting in a huge specific on-resistance of  $1.02 \times 10^6 \,\Omega$ -cm² at drift length of 15- $\mu$ m in the LTPS HVLDMOS. Thus, even if the drift length was extension about 3 times from 15- $\mu$ m to 40- $\mu$ m, the drift length extension with several times deviation was still finite. All gate transfer characteristics before and after excimer laser treatments for LTPS HVLDMOS from the drift length of 20- $\mu$ m to 40- $\mu$ m were showed in Fig. 4-11~Fig. 4-14.

Fig. 4-11. Transfer characteristics before and after excimer laser treatments for LTPS  $HVLDMOS \ with \ W/L_{ch}=600-\mu m/12-\mu m \ and \ L_{drift}=20-\mu m.$

Fig. 4-12. Transfer characteristics before and after excimer laser treatments for LTPS  $HVLDMOS \ with \ W/L_{ch}=600-\mu m/12-\mu m \ and \ L_{drift}=25-\mu m.$

Fig. 4-13. Transfer characteristics before and after excimer laser treatments for LTPS  $HVLDMOS\ with\ W/L_{ch}\!\!=\!\!600\text{-}\mu\text{m}/12\text{-}\mu\text{m}\ and\ L_{drift}\!\!=\!\!35\text{-}\mu\text{m}.$

Fig. 4-14. Transfer characteristics before and after excimer laser treatments for LTPS  $HVLDMOS \ with \ W/L_{ch}\!\!=\!\!600\text{-}\mu\text{m}/12\text{-}\mu\text{m} \ \text{and} \ L_{drift}\!\!=\!\!40\text{-}\mu\text{m}.$

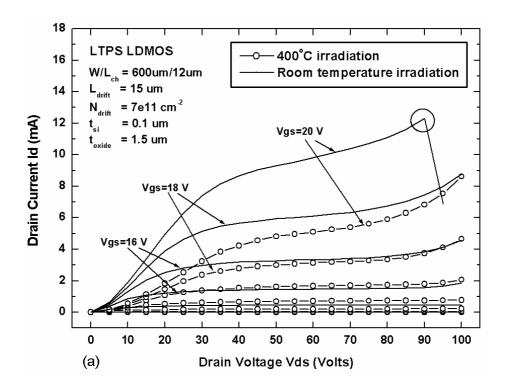

### 4.4.4 Output Characteristics before/after Excimer Laser Treatments for LTPS HVLDMOS

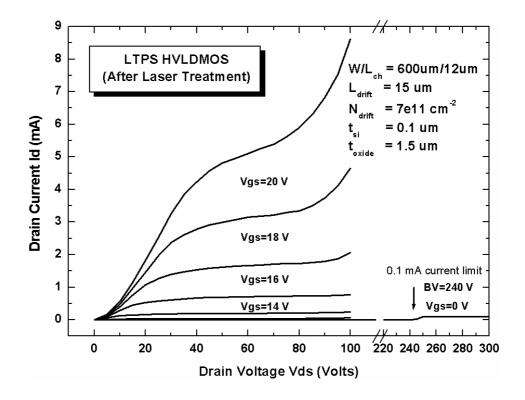

There are three distinct features of output characteristics, which are deliberately emphasized in laser annealed poly-Si devices. Firstly, at low gate voltage, the soft breakdown at high drain voltage is evidence of a floating substrate effect. Secondly, a moderate gate voltage, the output drain current does not saturate. This lack of saturation is directly attributable to modulation of the potential barrier at grain boundaries [4.44]. Thirdly, as the gate voltage is further increased, the output drain current does not tend to

Fig. 4-15. (a) Output characteristics after excimer laser treatments with the linear scale drain current for LTPS HVLDMOS with W/L<sub>ch</sub>=600- $\mu$ m/12- $\mu$ m and L<sub>drift</sub>=15- $\mu$ m. The breakdown voltage was measured by the protective current limit of 0.1 mA.

saturate and eventually the output conductance become negative. The negative output conductance does not occur in bulk silicon transistors. However, it has been observed in thin film transistors, attributed to self-heating, due to its low thermal conductivity of the insulating substrate [4.45], [4.46]. It is particularly apparent in short channel SOI devices at relatively high output power levels because of the high mobilities which can arise due to laser annealing.

Fig. 4-15. (b) Output characteristics before and after excimer laser treatments with the logarithm scale for LTPS HVLDMOS with W/L<sub>ch</sub>=600- $\mu$ m/12- $\mu$ m and L<sub>drift</sub>=15- $\mu$ m.

Figure 4-15 (a) and (b) showed the drain output characteristics before and after excimer laser treatments by the linear and logarithm scales for LTPS HVLDMOS. The logarithm scale block diagram, for observing small drain current, displayed that the current capability was greatly increased from 10<sup>-9</sup> to 10<sup>-3</sup> ampere after laser treatment. The safe-operating-area (SOA) was also enhanced with the low specific on-resistance

and large maximum voltage limit (Breakdown voltage) of 1.78  $\Omega$ -cm² (|Vgs-Vth|=15 V, Vds=20 V) and 240-V, respectively. The maximum power limit, which was mostly defined on the set of snapback boundary, was great in 0.41 Watts (1305 W/cm²) at Vgs=20 V and Vds=75 V. The latch-up voltage of parasitic bipolar could be suppressed up to 95 V drain voltage with high level saturation drain current of 1.5 mA at Vgs=16 V. In summary, the current driving capability of LTPS HVLDMOS after laser treatment exhibited the superior characteristics in the subthreshold swing,  $I_{ON}/I_{OFF}$  ratio, SOA, on-state resistance, maximum power limit, and latch-up voltage than that before laser treatment.

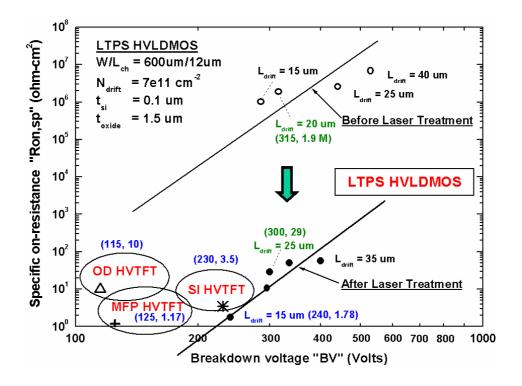

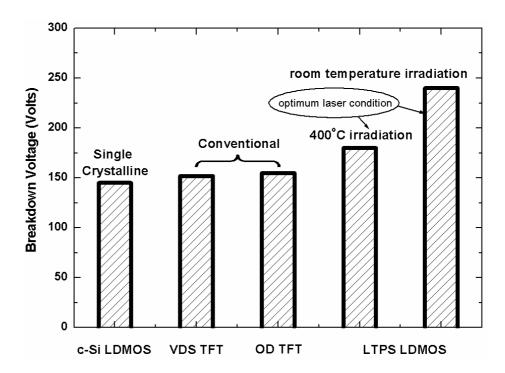

## 4.4.5 Comparison of LTPS HVLDMOS before/after Laser Treatments together with Conventional OD, MFP, and SI HVTFTs

Figure 4-16 showed the relationships of the specific on-resistance and breakdown voltage for LTPS HVLDMOS before/after laser treatments together with OD, MFP, and SI HVTFTs. The specific on-resistances of the above structures were all defined at the |Vgs-Vth|=15 V and Vds=20 V. The breakdown voltage was defined as a drain current of 1 nA/ $\mu$ m channel width at a gate voltage of 0 V. The drift lengths ( $L_{drift}$ ) of LTPS HVLDMOS after laser treatment were varied from 15- $\mu$ m to 35- $\mu$ m with a step of 5- $\mu$ m. The equation of specific on-resistance could be written as

$$R_{\text{on.sp}} = \left[ V/I \right] \times \left[ W \times \left( L_{\text{ch}} + L_{\text{drift}} \right) \right]$$

(Eq 4-1)

the symbol "V" and "I" were the drain voltage of 20-V and its corresponding current at |Vgs-Vth|=15 V. The symbol "W", " $L_{ch}$ ", and " $L_{drift}$ " indicated the device width, channel length, and drift length in the proposed HVLDMOS. As expected, the specific on -resistance of 29  $\Omega$ -cm<sup>2</sup> at 300-V ( $L_{drift}=25$ - $\mu$ m) after laser treatment was lower about

10<sup>5</sup> times than that of  $1.9 \times 10^6~\Omega\text{-cm}^2$  at 315-V ( $L_{drift}$ =20-μm) before laser treatment. The un-optimized LTPS HVLDMOS after laser treatment showed the better characteristics with  $1.78~\Omega\text{-cm}^2$  at 240-V ( $L_{drift}$ =15-μm) compared to the SI HVTFT with  $3.5~\Omega\text{-cm}^2$  at 230-V, MFP HVTFT with  $1.17~\Omega\text{-cm}^2$  at 125-V, and OD HVTFT with  $10~\Omega\text{-cm}^2$  at 115-V under solid phase crystallization (SPC) and  $4\sim12$  hrs hydrogenation [4.47], [4.48]. It was because the depletion width of the previous HVTFTs needed to firstly compensate its many grain boundary trap states and then extended to support the blocking voltage [4.49]. However, by laser treatment and the RESURF designs in LTPS

Fig. 4-16. Relationships of the specific on-resistance and breakdown voltage in the LTPS HVLDMOS before/after laser treatments against the previous OD, MFP, and SI HVTFTs. The (x, y) represented the coordinates in X-axis and Y-axis, which meant the values of breakdown voltage and specific on-resistance, respectively.

HVLDMOS, the grains could be grown relatively large with less in-grain defects from the molten phase and then the polysilicon depletion width could be effectively increased even in the high doping ( $\sim 10^{17}$  cm<sup>-3</sup>) drift region [4.26], [4.50].

#### 4.5 Summary

The high-performance LTPS HVLDMOS is successfully fabricated using the excimer laser crystallization process. The films produced have a maximum grain size of 3- $\mu$ m with strong (111) crystallographic orientation and a mono-modally distributed grain size of 1.5- $\mu$ m, on average. The threshold voltage after/before laser treatment is not changed at 4 volts due to the similar well concentrations, which replaced the channel defects domination in the intrinsic well region. The subthreshold swing (SS) is significant improved from 16.15 V/decade to 1.36 V/decade after laser treatment. The ON/OFF current ratios ( $I_{ON}/I_{OFF}$ ) after laser treatment show the excellent promotion with the magnitudes of 3.73  $\times$  10<sup>5</sup> and 2.37  $\times$  10<sup>6</sup> against the magnitudes of 1.71 and 1.93 before laser treatment at Vds=5 V and Vds=25 V. The ON/OFF current ratios and its variations before excimer laser treatment are entirely much smaller than those after excimer laser treatment as the increase in the drift length.

The ON/OFF current ratios variation at drain bias of 25-V is smaller than that at drain bias of 5-V so that the variations can be suppressed by higher drain voltage as the drift length extension. The current driving capability of LTPS HVLDMOS after laser treatment exhibits the superior characteristics in the subthreshold swing,  $I_{ON}/I_{OFF}$  ratio, SOA, on-state resistance, maximum power limit, and latch-up voltage than that before laser treatment. The specific on-resistance of 29  $\Omega$ -cm<sup>2</sup> at 300-V ( $L_{drift}$ =25- $\mu$ m) after laser treatment is lower about 10<sup>5</sup> times than that of 1.9 × 10<sup>6</sup>  $\Omega$ -cm<sup>2</sup> at 315-V

(L<sub>drift</sub>=20-μm) before laser treatment.

The LTPS HVLDMOS after laser treatment shows the better characteristics with  $1.78~\Omega\text{-cm}^2$  at  $240\text{-V}~(L_{drift}=15\text{-}\mu\text{m})$  compared to the SI HVTFT with  $3.5~\Omega\text{-cm}^2$  at 230-V, MFP HVTFT with  $1.17~\Omega\text{-cm}^2$  at 125-V, and OD HVTFT with  $10~\Omega\text{-cm}^2$  at 115-V. It possesses the superior current capability and blocking capability by the combination technology of power devices and thin film transistors. It is also verified that the eximer laser crystallization is very important to obtain the extreme current capability against the previous HVTFT structures. The LTPS HVLDMOS after laser treatment is attractive for the future 3-D circuit integrations and SOP applications.

#### Chapter 5

# LDMOS Devices of Low-Temperature Polycrystalline -Silicon Crystallized at 400 °C Substrate Heating

\_\_\_\_\_

Low-temperature poly-Si lateral double diffused metal oxide semiconductor (LTPS LDMOS) with high voltage and very low on-resistance has been achieved using excimer laser crystallization at 400 °C substrate heating for the first time. The ON/OFF current ratios were exhibited with  $2.96 \times 10^5$  and  $6.72 \times 10^6$  while operating at Vds=0.1 V and 10 V, respectively. The maximum  $R_{DS,ON}$  current limit was up to 10 mA and maximum power limit could be enhanced over 1 Watt at Vds=90 V and Vgs=20 V. The Ron,sp with dimensions of W/L<sub>ch</sub>=600- $\mu$ m/12- $\mu$ m could be significantly decreased  $6.67 \times 10^2$  times in the magnitude as compared with the conventional offset drain (OD) TFTs.

#### 5.1 Advanced LTPS LDMOS for 400 °C Irradiation

Low-temperature poly-Si high-voltage thin-film-transistors (LTPS HVTFTs) have been widely studied in order to realize the glass compatible driver circuits for light valves, high speed printers, liquid crystal displays, plasma displays, and so on [5.1]-[5.2]. High voltage thin film transistors (HVTFTs) differ from low voltage devices in that the drain is offset with respect to the gate edge. This offset drain (OD) structure reduces the electric field peaks associated with high voltage operation thereby increasing the breakdown voltage and reducing the off state leakage [5.3]. In the

absence of the offset region, most of the applied drain voltage appears across the gate oxide lead to a large electric field in the oxide region, and a correspondingly large filed in the silicon active layer underneath the gate electrode. The impact ionization charge can be generated in the heavily doped n+ region, but the offset region can be depleted much more significantly to support larger this voltage. So the breakdown voltage with offset region can be sustained by the impact generation in the silicon active layer just beyond the heavily doped n+ drain region. Nevertheless, these improvements are accompanied by degradation in the device on state performance due to the series resistance of the offset region.

Fig. 5-1. Schematic structure of various doping slit (VDS) thin film transistor (TFT) with a continuous shallow doping profile in the offset region.

As shown in Fig. 5-1, variable doping slots (VDS) TFT is proposed in 2002 and similar to the OD TFT except that an undoped intrinsic polysilicon offset region is replaced by a set of variable doping slots [5.4]. In this structure, the on state resistance is reduced, while alleviating the stringent requirement to dopant control in the OD TFT. Different doping levels between the slots and the intrinsic polysilicon will split the potential drop across the offset region, thereby avoiding the electric field crowding and

improving the trade off between the on state performance and the blocking capability. However, the previous works still exist a lot of issues—such as on-state degradation, gate dielectric reliability, circuit/operation complexity, and surface contamination—resulting in the unsuitable implementation of the integration electronic systems for future system-on-a-panel (SOP) applications.

In this letter, the LTPS LDMOS using excimer laser crystallization has been demonstrated by combination of the thin film transistor (excimer laser crystallization) and power device technologies (LDMOS architecture) for the first time. The excimer laser crystallization (ELC) is the promising technology to obtain the high current capability due to the large grains, less defects, and compatible glass substrate against the solid phase crystallization (SPC) of HVTFTs [5.5]. The LDMOS architecture is the promising design to obtain high blocking capability due to the reduced-surface-field (RESURF) against the only offset drain (drift) region of HVTFTs [5.6]. Hence, the LTPS LDMOS at room temperature irradiation can exhibit the better characteristics than the conventional HVTFTs. Moreover, the LTPS LDMOS at 400 °C irradiation can further present the close performance like the single crystalline silicon (c-Si) LDMOS.

#### 5.2 Experiments

Poly-Si devices have been attracted much attention in the field of large-electronics. Of the various approaches available, excimer laser annealing is a very promising technique for large-scale fabrication of high-performance poly-Si device on glass substrate with high throughput because of the large beam size and high beam energy. In addition, since the absorption coefficient of amorphous silicon (a-Si) is quite high in the UV-light region of the excimer laser, it is possible to recrystallize a-Si film without

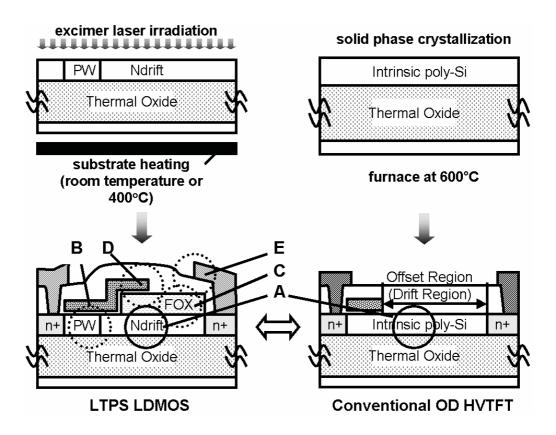

The fundamental structure of LTPS LDMOS under room temperature (RT) or 400°C irradiation was shown with the labels of RESURF design from "A" to "E" in Fig. 5-2. The conventional offset drain (OD) TFT structure was also exhibited for comparison. At first, a 1.5- $\mu$ m-thick wet oxide was grown on a silicon wafer. Then, an amorphous-silicon (a-Si) of 0.1- $\mu$ m thickness was deposited on it by low-pressure chemical vapor deposition (LPCVD) at 550 °C. Next, as shown in label "A", the 50 KeV phosphorous dose of 7 × 10<sup>11</sup> cm<sup>-2</sup> was implanted into the above a-Si drift region to reduce the current path resistance. However, the conventional OD TFT was lack of this drift implantation so as to possess the large on-resistance with its intrinsic region. At label "B", the high energy of 60 KeV boron dose of 3 × 10<sup>13</sup> cm<sup>-2</sup> was created as the buried P-well region to increase the depletion width in the N-drift region without adding the threshold voltage. The laser crystallization was performed using KrF excimer laser ( $\lambda$ =248 nm) with the energy densities from 400 to 470 mJ/cm<sup>2</sup> and 99 % overlapped shot density at room temperature or 400 °C substrate heating. However, the

conventional OD TFT was crystallized by furnace at 600 °C so as to possess the small grain sizes in its intrinsic region. After that, a 5000-Å-thick field oxide (FOX) at label "C" was formed by plasma enhanced chemical vapor deposition (PECVD) at 350 °C to reduce the surface electric field (RESURF). A 1000-Å-thick PECVD gate oxide and a 2000-Å-thick LPCVD a-Si gate were defined across the FOX to split the P-well/N-drift

Fig. 5-2. LTPS LDMOS structure fabricated by excimer laser crystallization under room temperature or 400°C irradiation. The broken circles represented the RESURF design and the solid circles indicated the drift with/without doping for reducing the resistance of drift region in LTPS LDMOS and OD TFT devices.

junction electric field at label "D". The 50 KeV phosphorous and boron doses of 5  $\times$   $10^{15}$  cm<sup>-2</sup> were carried out to form n+ drain, source, gate and p+ butting regions. Finally,

a 6000-Å-thick Al extended drain was defined to overlap the 5000-Å-thick passive layer and pass through the N-drift/n+ drain junction to split its electric field at label "E". All of the steps were compatible for the standard TFT fabrication and glass process with the maximum temperature of 600 °C.

#### **5.3** Results and Discussion

### 5.3.1 Transfer Characteristics of Conventional OD TFT and Novel LTPS LDMOS with Room Temperature Irradiation

Table 5-1 lists the transfer characteristics of the conventional OD TFT and the proposed LTPS LDMOS with optimal room temperature irradiation. The LTPS LDMOS was obtained from the following parameters: W=600- $\mu$ m, L<sub>ch</sub>=12- $\mu$ m, L<sub>drift</sub>=15- $\mu$ m,  $N_{drift}$ =7  $\times$  10  $^{11}$  cm  $^{-2}$ ,  $t_{si}$ =0.1- $\mu$ m, and  $t_{oxide}$ =1.5- $\mu$ m. The OD TFT was established from the parameters:  $W/L_{ch}=100-\mu m/16-\mu m$ ,  $L_{drift}=20-\mu m$ ,  $t_{si}=0.3-\mu m$ , and  $t_{oxide}=2-\mu m$  [5.4]. The difference of LTPS LDMOS without and with excimer laser crystallization (ELC) had been compared by Chang et al [5.12]. As shown in this table, the OD TFT exhibited the low threshold voltage (Vth) of 0.5-V from the intrinsic well region, which would make the device more sensitivity for signal noises. In order to avoid the phenomenon, the suitable high threshold voltage was required for circuit designs. The LTPS LDMOS presented a higher threshold voltage of 4-V at room temperature irradiation due to the doped P-well region with a dose of  $3 \times 10^{13}$  cm<sup>-2</sup> which was beneficial to increase the threshold voltage and operate stably. In respect of the subthreshold swing (SS), the LTPS LDMOS at room temperature irradiation had smaller value of 1.18-V than OD TFT one of 1.92-V. Before discussing the ON/OFF current ratios, the on-state current (I<sub>ON</sub>) and off-state current (I<sub>OFF</sub>) of ON/OFF current ratio were defined at the gate biases

of 35-V and -10-V, respectively. As listed in Table, the LTPS LDMOS at room temperature irradiation would display a better  $I_{ON}/I_{OFF}$  current ratios of  $2.19 \times 10^4$  and  $1.23 \times 10^6$  than OD TFT ones of  $3 \times 10^3$  and  $5 \times 10^3$  at the drain biases of 0.1-V and 10-V. The breakdown voltage (BV) of LTPS LDMOS at room temperature irradiation was also expressed a high value of 240-V than the conventional OD TFT with the breakdown voltage of 155-V. Thus, in terms of the on-state (Vth, SS,  $I_{ON}/I_{OFF}$ ) and off-state (BV) characteristics, the proposed LTPS LDMOS at room temperature irradiation was entirely better than the conventional OD TFT.

Table 5-1. Summary of the transfer characteristics for the conventional OD TFT and the proposed LTPS LDMOS under optimal room temperature irradiation.

| NAME OF THE PARTY.                                  | Conventional OD TFT | Room temperature<br>LTPS LDMOS |

|-----------------------------------------------------|---------------------|--------------------------------|

| Threshold Voltage (V)                               | 0.5                 | 4                              |

| Subthreshold Swing (V/dec)                          | 1.92                | 1.18                           |

| Max. I <sub>ON</sub> /I <sub>OFF</sub> at Vds=0.1 V | $3 \times 10^3$     | $2.19\times10^4$               |

| Max. I <sub>ON</sub> /I <sub>OFF</sub> at Vds=10 V  | $5 \times 10^3$     | $1.23\times10^6$               |

| Breakdown Voltage (V)                               | 155                 | 240                            |

### 5.3.2 Transfer Characteristics of LTPS LDMOS at RT and 400 °C Irradiations

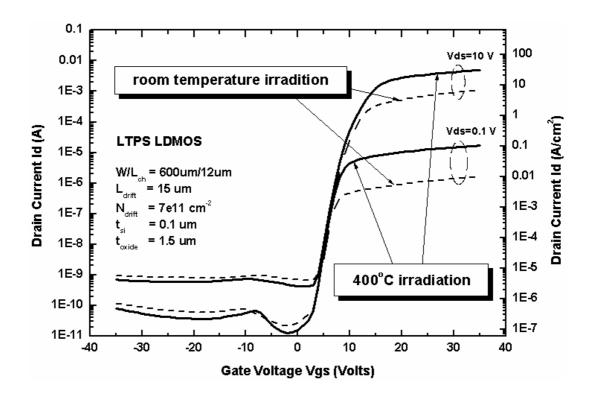

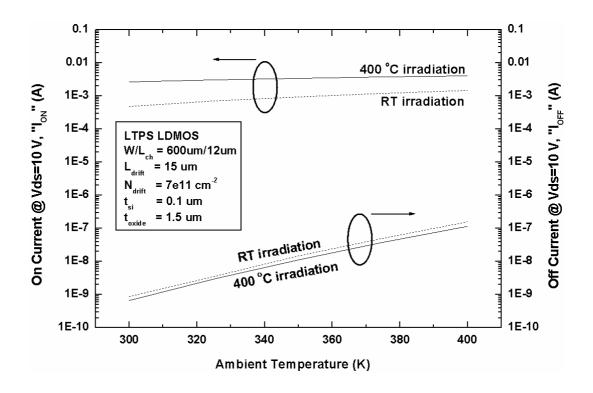

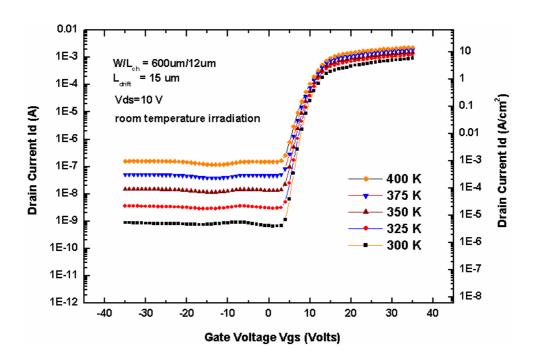

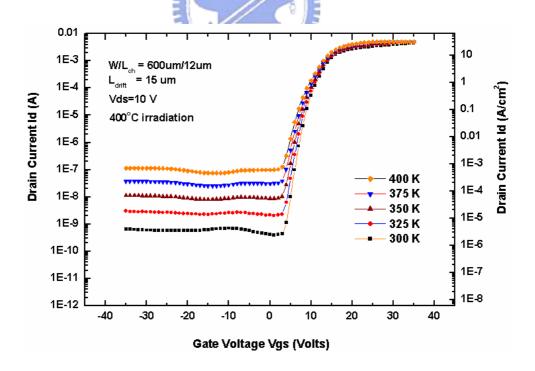

Figure 5-3 and Table 5-2 shows the transfer characteristics of LTPS LDMOS for optimal room temperature and 400 °C irradiations in the drift length of 15-μm. At the

negative gate bias (off state range), the I<sub>OFF</sub> leakage current at Vds=0.1 V was reduced about 1.47 times from 10<sup>-10</sup> A to 10<sup>-11</sup> A by 400 °C substrate heating during excimer laser irradiation. The I<sub>OFF</sub> at 400°C substrate heating was lightly lower than that at room temperature due to the reduction in the defect trap states [5.13]. As the drain voltage was up to 10 V, the decrease in I<sub>OFF</sub> leakage current was slow down from 1.47 times to 1.32 times for 400 °C irradiation. The anomalous I<sub>OFF</sub> leakage current could be restrained by the drift region (offset region) at the negative gate voltages regardless of the gate and drain voltage increase even up to Vgs=-35 V and Vds=10 V [5.14]. The threshold voltages in polycrystalline silicon devices were dominated by the defect trapping density unlike the threshold voltages of single crystalline by Fermi potential and intrinsic carrier density. But, in this case, the well region was no longer undoped and replaced by a P-type Boron implantation. The doped P-well region not only could suppress the source/drain punch-through but also could increase the domination in the threshold voltage. In addition, the threshold voltage for the proposed LTPS LDMOS device was evaluated and almost the same at 4 volts at 400 °C and room temperature irradiations. The reason was that the same concentrations in P-well regions resulted in the similar threshold voltage at 400 °C and room temperature irradiations. The subthreshold swing was reduced from 1.15 V/decade at 400 °C irradiation to 1.18 V/decade at room temperature irradiation. It was revealed the finite improvement of 2.5 % by 400 °C irradiation. As the gate voltage was increased to attain the on state, the  $I_{\rm ON}$ current at Vds=0.1 V could be raised about 10 times from  $10^{-6}$  A to  $10^{-5}$  A by 400 °C substrate heating during excimer laser irradiation. But, while the drain voltage was raised to 10 V, the increment of the drain currents between RT and 400 °C irradiations would be shorten from 10 times to 4 times. In summary, the I<sub>ON</sub>/I<sub>OFF</sub> current ratios through 400°C irradiation were further increased from  $2.19 \times 10^4$  to  $2.96 \times 10^5$  at

Fig. 5-3. Transfer characteristics of LTPS LDMOS for optimal room temperature and 400 °C irradiations with W/L<sub>ch</sub>=600- $\mu$ m/12- $\mu$ m and L<sub>drift</sub>=15- $\mu$ m.

Table 5-2. Summary of the transfer characteristics of LTPS LDMOS at room temperature and 400 °C irradiations with optimal laser conditions.

|                                                    | Room temperature     | 400 °C irradiation   |

|----------------------------------------------------|----------------------|----------------------|

|                                                    | LTPS LDMOS           | LTPS LDMOS           |

| Threshold Voltage (V)                              | 4                    | 4                    |

| Subthreshold Swing (V/dec)                         | 1.18                 | 1.15                 |

| Max. I <sub>ON</sub> /I <sub>OFF</sub> at Vds=5 V  | $2.19 \times 10^{4}$ | $2.96\times10^{5}$   |

| Max. I <sub>ON</sub> /I <sub>OFF</sub> at Vds=25 V | $1.23 \times 10^{6}$ | $6.72 \times 10^{6}$ |

| Breakdown Voltage (V)                              | 240                  | 180                  |

Vds=0.1 V and  $1.23 \times 10^6$  to  $6.72 \times 10^6$  at Vds=10 V, which were indicated about 14 and 5 times improvements for the room temperature ones, respectively.

### 5.3.3 Relationship between ON/OFF Current Ratio and Drift Length of LTPS LDMOS at RT and 400 °C Irradiations

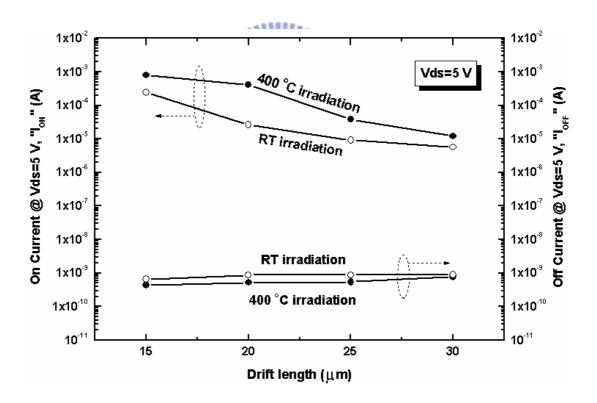

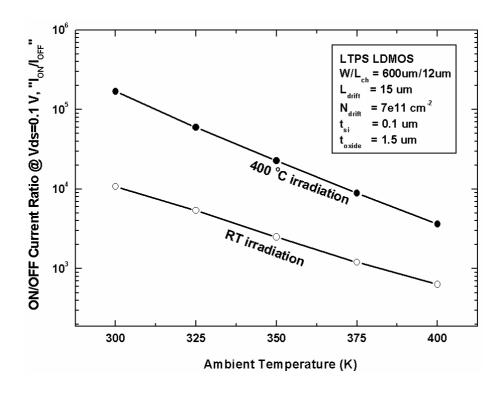

Figure 5-4 (a) shows the variations of I<sub>ON</sub> and I<sub>OFF</sub> currents with the drift length extension at drains bias of 5 V for LTPS LDMOS at room temperature and 400 °C irradiations. The on-state current (I<sub>ON</sub>) and off-state current (I<sub>OFF</sub>) of ON/OFF current ratio were defined at the gate biases of 30-V and -30-V, respectively. As the drift lengths increased from 15-µm to 30-µm, the on-currents of 400 °C irradiation exhibited the large value than that of room temperature irradiation. The off-currents for 400 °C irradiation also maintained the less leakages than that for room temperature irradiation even if the drift length is extended to 30-µm. It is worth to mention that the on-current deviations between room temperature and 400 °C irradiations were not stable with the increase in drift length. In order to explain the difference, the on-current deviations will be divided into the three ranges from the drift length of 15-µm to 30-µm. At the short drift length of 15-µm, the magnitude of on-currents was determined on the quality of polycrystalline silicon film. As the drift length extended to 20-µm, the 33 % increase of the drift length would also involve the magnitude of on-currents. At this experiment, the on current for 400 °C radiation could still held the high value due to its good crystallinity but the on current for room temperature irradiation started to exhibit the mechanism of drift length domination. As the drift length increased to the range from 25-µm to 30-µm, the percentage of the drift length extension was raised from 66 % to 100%. The device current mechanism would be predominated by the drift length so that the on current for 400 °C radiation was gradually close to the on current for room temperature radiation. The results were illustrated that the crystallinity domination was beneficial to obtain the high magnitude of on-currents but long drift length would suppress this mechanism. The long drift length increased the number of grain boundaries, which would non-linearly accelerate the total resistances in devices. Thus, in order to improve the phenomenon, the advanced growth technology for large grain size was necessary to reduce the number of grain boundaries in the drift region and promote the device performance. Additionally, as shown in figure, the off currents deviations were also presented the same phenomenon between room temperature and 400 °C irradiations.

Fig. 5-4. (a) Dependence of on and off currents on the drift length variation from 15-μm to 30-μm at drains bias of 5 V for LTPS LDMOS at optimal room temperature and 400 °C irradiations.

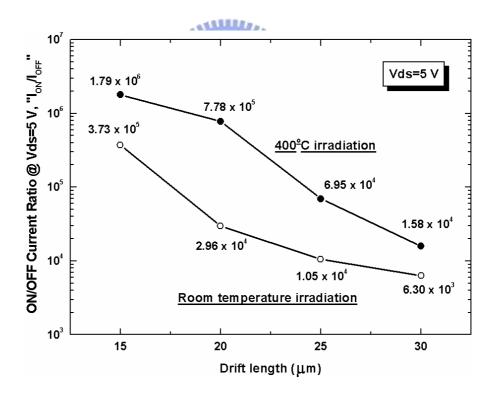

Figure 5-4 (b) shows the variations of ON/OFF current ratios with the drift length extension at drains bias of 5 V for LTPS LDMOS at room temperature and 400 °C irradiations. The ON/OFF current ratios at 400 °C irradiation entirely exhibited the better characteristics than those at room temperature irradiation. At the drift length of 15- $\mu$ m for crystallinity domination, the good quality of LTPS LDMOS at 400 °C irradiation presented a higher value of  $1.79 \times 10^6$ , which was about 4.80 times in the magnitude as compared with ON/OFF current ratio of  $3.73 \times 10^5$  at the room temperature irradiation. As the drift length increased to 20- $\mu$ m, the ON/OFF current ratio at room temperature irradiation was suffered from the drift length mechanism and decayed about 12 times from  $3.73 \times 10^5$  to  $2.96 \times 10^4$ . However, the ON/OFF current

Fig. 5-4. (b) Relationship between of ON/OFF current ratios and the drift length variation from 15-μm to 30-μm at drains bias of 5 V for LTPS LDMOS at optimal room temperature and 400 °C irradiations.

ratio at 400 °C irradiation was varied only about 2.26 times from  $1.79 \times 10^6$  to  $7.78 \times 10^5$  due to its superior crystallinity than that in room temperature irradiation. At the drift length of 25- $\mu$ m, the ON/OFF current ratios were gone into the strong mechanism of drift length domination regardless of room temperature or 400 °C irradiation. The ON/OFF current ratio at 400 °C irradiation could not sustain a high value and decrease sharply about 11.19 times from  $7.78 \times 10^5$  to  $6.95 \times 10^4$  but still higher than the ON/OFF current ratio of  $1.05 \times 10^4$  at room temperature irradiation. At the drift length of 30- $\mu$ m, the ON/OFF current ratio deviation between 400 °C and room temperature irradiation was very close to each other since the drift length mechanism was gradually dominated the device performance in spite of the quality of polycrystalline silicon film except the decrease in grain boundaries.

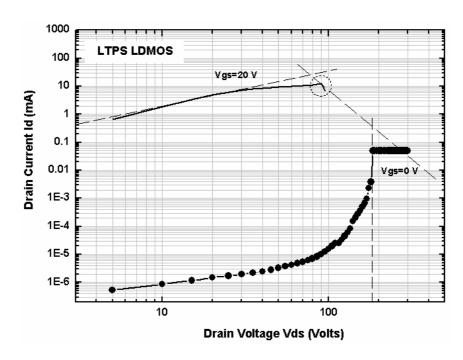

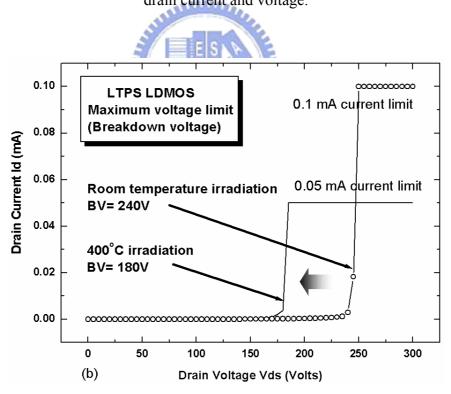

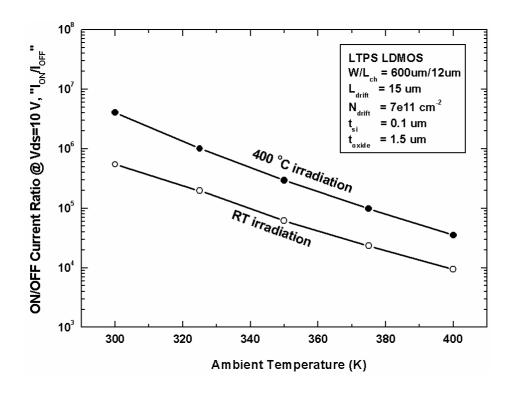

# 5.3.4 Output Characteristics of LTPS LDMOS at RT and 400 °C Irradiations

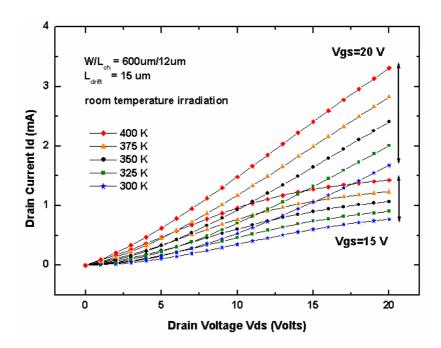

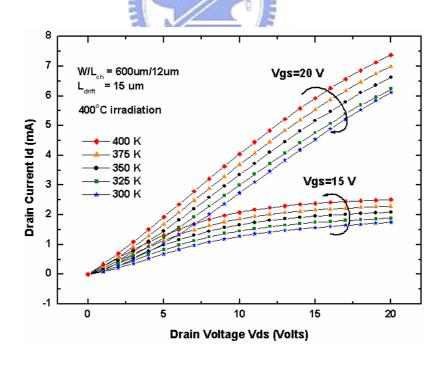

Figure 5-5 (a), (b), and (c) shows the output characteristics of LTPS LDMOS for optimal room temperature and 400 °C irradiations. The corresponding safe operating area (SOA) was described with the algorithmic scales of drain current and voltage in Fig. 5-5 (b). While the substrate was heated to 400 °C, the maximum R<sub>DS,on</sub> current limit was increased about 2 times from 5-mA to 10-mA at Vgs=20 V. The maximum power limit, where the LTPS LDMOS was burned out, was great in 1.11 Watts (6852 W/cm²) at Ids=12.3-mA, Vds=90 V, and Vgs=20 V. The latch-up current at Vgs=16 V could be suppressed up to 90-V drain voltage with 2 times drain current from 1.5 mA to 3 mA. Nevertheless, the latch-up voltage (kink voltage) at Vgs=16 V was slightly decreased about 0.95 times from 95-V to 90-V. The maximum voltage limit (breakdown voltage) was reduced about 0.75 times from 240-V to 180-V in Fig. 5-5 (c). The reason might be

the impact ionization path and effective ionization rate ( $\alpha$ ) were raised by the less intra/inter-gain defects so that the breakdown voltage was dropped below that of room temperature irradiation [5.15], [5.16]. But, on the whole, the safe operating area (SOA) could be still improved about twice (1.5 times) with 2 times enhancement of the maximum  $R_{DS,on}$  current and 0.75 times degradation of maximum voltage by the 400 °C irradiation relative to that at room temperature (RT) irradiation.

Fig. 5-5. (a) Output characteristics of LTPS LDMOS for optimal room temperature and 400 °C irradiations. The circle was indicated the maximum power limit point of 1.11 Watts.

Fig. 5-5. (b) Corresponding safe operating area (SOA) with the algorithmic scales of drain current and voltage.

Fig. 5-5. (c) Output characteristics of LTPS LDMOS for optimal room temperature and 400 °C irradiations. The breakdown voltages were measured by the protective limits of 0.1 mA and 0.05 mA for room temperature and 400°C irradiations, respectively.

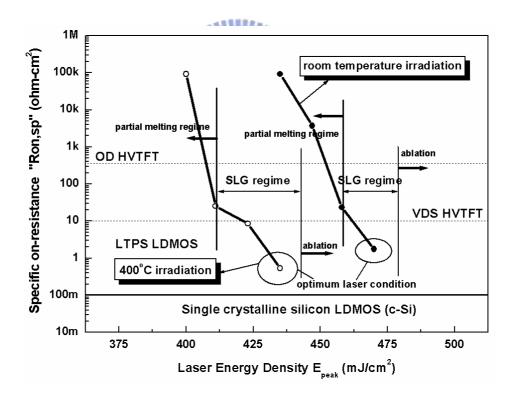

# 5.3.5 Comparison of LTPS LDMOS at RT and 400 °C Irradiations together with OD and VDS TFTs

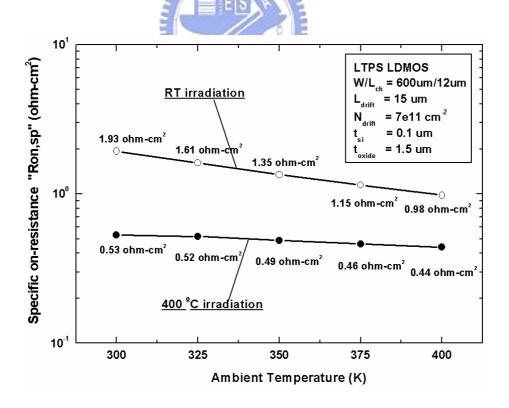

### **5.3.5.1** Specific On-Resistance

Figure 5-6 (a) shows the relationships between the specific on-resistance and laser energy density for LTPS LDMOS at RT/400 °C irradiations together with OD TFT, variable doping slot (VDS) TFT, and c-Si LDMOS. The specific on-resistances (Ron,sp) of all structures were defined at Vgs=20 V and Vds=20 V. The grain growth regimes were divided into three parts: partial melting, super lateral growth (SLG)—the expected regime for the largest grain size—and ablation of Si film regimes. As the results, the

Fig. 5-6 (a) Relationships of the specific on-resistance and laser energy density for LTPS LDMOS at RT/400 °C irradiations together with OD TFT, VDS TFT and c-Si LDMOS. The optimal laser conditions were located at 470 mJ/cm<sup>2</sup> and 435 mJ/cm<sup>2</sup> for room temperature and 400 °C, respectively.

LTPS LDMOS at room temperature irradiation exhibited the better Ron,sp of 1.78 ohm-cm<sup>2</sup> by the ELC process and RESURF design than the conventional OD TFT of 360 ohm-cm<sup>2</sup> and VDS TFT of 10 ohm-cm<sup>2</sup> by offset region and SPC process [5.4]. Nevertheless, the Ron,sp of room temperature irradiation still fell about 18 times behind the 0.10 ohm-cm<sup>2</sup> of c-Si LDMOS from Taurus and ATHENA/ATLAS simulators [5.17], [5.18]. Fortunately, while crystallizing at 400 °C, the Ron,sp of room temperature irradiation could be further reduced around 3 times from 1.78 ohm-cm<sup>2</sup> to 0.54 ohm-cm<sup>2</sup> at the optimal laser conditions of 470 mJ/cm<sup>2</sup> and 435 mJ/cm<sup>2</sup>, respectively. The Ron,sp of LTPS LDMOS could be greatly decreased from 18 times dropped to only 5 times higher than that of c-Si LDMOS. It was attributed that the solidification velocity at 400 °C irradiation could be reduced to about 1/5 and the crystallinity could become better as compared to that at room temperature irradiation [5.19].

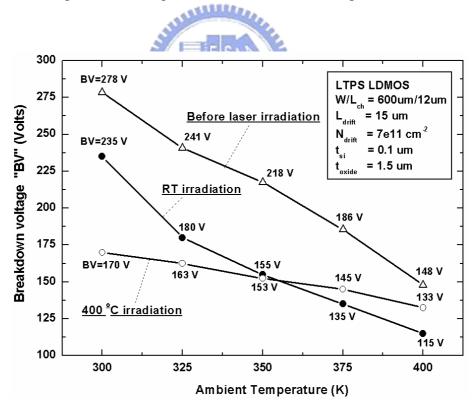

### 5.3.5.2 Breakdown Voltage

Figure 5-6 (b) shows the comparison of the breakdown voltages for the LTPS LDMOS at RT/400 °C irradiations together with OD TFT, VDS TFT, and c-Si LDMOS. The breakdown voltage was defined as a drain current of 1 nA/μm channel width at a gate voltage of 0 V. The Si atoms in the crystalline solids were arranged orderly unlike the segment order of polycrystalline ones. Consequently, the impact ionization path and effective ionization rate (α) of c-Si LDMOS is the longest and largest, which resulted in the minimum breakdown voltage of 145-V for comparison with the polycrystalline silicon devices [5.20], [5.21]. In regard to the conventional high-voltage TFT, the breakdown voltage of OD TFT (155-V) was slightly larger than that of VDS TFT (152-V). The reason was responsible for the slot dope in the offset region even though the VDS TFT had utilized a set of variable doping slots to alleviate the degradation in

blocking voltage capability. The proposed LTPS LDMOS at room temperature and 400 °C irradiations exhibited the excellent breakdown voltages of 240-V and 180-V, respectively. Therefore, according to the results of figure 5-6 (a) and (b), the LTPS LDMOS, regardless of room temperature or 400 °C irradiation, is really a promising power device in low temperature poly-Si application than the conventional high-voltage TFT.

Fig. 5-6 (b) Comparison of the breakdown voltages for the LTPS LDMOS at RT/400 °C irradiations together with OD TFT, VDS TFT, and c-Si LDMOS.

### 5.4 Summary

A new power device called LTPS LDMOS is reported for the first time to attain the high driving and high blocking capability with the excimer laser annealing at 400 °C substrate heating. The LTPS LDMOS presents a higher threshold voltage of 4-V due to the doped P-well region with a dose of  $3 \times 10^{13}$  cm<sup>-2</sup> which is beneficial to increase the threshold voltage and operate stably. The subthreshold swing is reduced from 1.15 V/decade at 400 °C irradiation to 1.18 V/decade at room temperature irradiation. It is revealed the finite improvement of 2.5 % by 400 °C irradiation. The ON/OFF current ratios through 400°C irradiation are further increased from  $2.19 \times 10^4$  to  $2.96 \times 10^5$  at Vds=0.1 V and 1.23  $\times$  10<sup>6</sup> to 6.72  $\times$  10<sup>6</sup> at Vds=10 V, which are indicated about 14 and 5 times improvements for the room temperature ones, respectively. At the short drift length, the magnitude of on-currents is determined on the quality of polycrystalline silicon film. As the drift length increases, the device current mechanism will be predominated by the long drift length which increases the number of grain boundaries, and non-linearly accelerates the total resistances in devices. Thus, the advanced growth technology for large grain size is necessary to reduce the number of grain boundaries in the drift region and promote the device performance.

The device can handle a much higher current of 10mA, and a better power limit of 1.11 Watts. The safe operating area (SOA) can be improved about twice (1.5 times) with 2 times enhancement of the maximum  $R_{DS,on}$  current and 0.75 times degradation of maximum voltage by the 400 °C irradiation relative to that at room temperature (RT) irradiation. While crystallizing at 400 °C, the Ron,sp of room temperature irradiation can be further reduced around 3 times from 1.78 ohm-cm<sup>2</sup> to 0.54 ohm-cm<sup>2</sup> at the optimal laser conditions of 470 mJ/cm<sup>2</sup> and 435 mJ/cm<sup>2</sup>, respectively. The proposed

LTPS LDMOS at room temperature and 400 °C irradiations exhibit the excellent breakdown voltages of 240-V and 180-V against the conventional OD TFT, VDS TFT, and c-Si LDMOS with breakdown voltage of 155-V, 152-V, and 145-V, respectively. The resultant characteristics for the 400 °C annealing ones are even very close to the c-Si LDMOS. Hence, the proposed LTPS LDMOS devices are very suitable for future system-on-a-panel (SOP) applications.

### Chapter 6

### Thermal Analyses on Single-Crystalline and Low-Temperature Polycrystalline Silicon Power Devices

.....

Recently, there are many potential applications, in spite of low voltage, high voltage, single crystalline silicon, and polycrystalline silicon elements, which are demanded or required to operate at elevated temperatures. For low voltage polycrystalline silicon elements, such in active matrix liquid crystal display (AMLCD's), the back illumination behind the liquid crystal display will increase the operating temperature of the hydrogenated amorphous silicon (a-Si:H) TFT's up to over 70 °C. The high temperature operation may degrade the device performance or seriously cause the device permanent failure. These phenomena will make the image lag or cause the white points appear in the screen. The effects of a high temperature ambient will be exacerbated by power dissipation, called self-heating, which will also cause additional temperature rise within the device [6.1]. For high voltage single crystalline silicon elements, such in the lateral double diffused metal oxide semiconductor (LDMOS) devices, the elevated temperature will lead to the principal deleterious influences of the increase in the forward-blocking mode leakage current and an increase in forward-driving mode on-resistance. Although power devices are often expected to run hotter than other component, the excessive temperature rise of an inherently problem device will often lead to catastrophic failure. Failure of a single power device can shut down a computer, bring to halt a motor-driven system, or stop a vehicle dead in its tracks. The self-heating will also result in an increase of the interconnect temperature

which is critical for electro-migration considerations. In silicon on insulator (SOI) devices, the operation temperature will be raised with increasing the buried oxide thickness and may suffer the metal contact separation [6.2]. The reduction of temperature effect in SOI technology may require the device structure with optimized film and buried oxide thickness. In a word, the accurate characterization of the thermal properties of power transistors is more critical to the reliability of the systems using these devices.

### **6.1** Self-Heating Effects in SOI Devices

In silicon on insulator (SOI) devices, the self-heating phenomenon will be more serious than in bulk devices due to its low thermal conductivity of the buried oxide beneath the silicon active layer. In generally, on current will reduce at large drain bias, relative to large power dissipation, due to the degradation in mobility. The kink effect, also called floating body effect or snapback effect, will be appeared at largest drain bias, relative to high electric field, due to the onset of parasitic bipolar turn-on. However, in comparison to bulk devices, the higher temperature will degrade the field-effect mobility so much from the increase in channel temperature and the onset of negative output conductance, called snapback, will happen more early in the saturation region [6.3]. However, at this time, the heat dissipation only can depend on the source, drain, and interconnect electrodes to conduct and cool down this additional temperature [6.4]. Furthermore, if the package has not been optimally designed to dissipate the heat, the self-heating may cause thermal runaway in the device and also could lead to the increase in the interconnect temperature at silicon-metal contact. The un-optimum package design will cause negative differential resistance in the terminal characteristics

of device and cannot adequately dissipate the heat produced in the device. Therefore, in order to prevent SOI devices from self-heating, the present packages used in bulk devices will be not suitable for SOI devices and necessary to be modified.

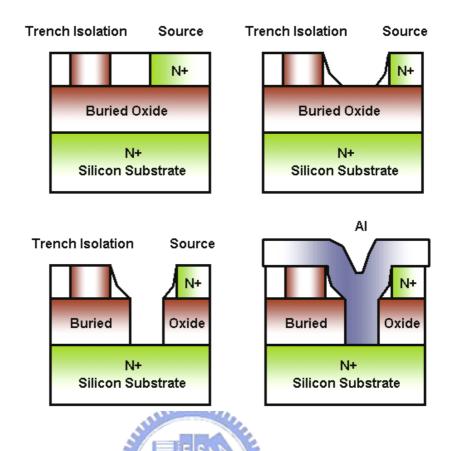

As shown in Fig. 6-1 (a), the contact through buried oxide layer (CTBOX) technique is mainly addressed to the improvement of the thermal performance of SOI devices. In this case, the source and substrate electrodes of a thin film SOI device are usually grounded and the BOX/substrate interface results too if substrate doping concentration is suitable without the depletion or accumulation effect, which depend on the substrate type. The equipotential lines distribution across the devices will be not significantly modified if the source metal layer directly contacts the silicon substrate through the buried oxide layer. Hence, this trench metal contact provides a high conductive thermal path to evacuate the heat generation in the silicon active layer through the silicon substrate. However, there is the most important technological limitation that the buried oxide thickness of CTBOX technique has to be lower than 2-µm thick. This is because a consequence of the dry etch process at thick BOX layers will shorten the graphite electrode life or lead to a re-entrant trench shape not suitable for aluminum deposition. Additionally, this technique cannot be used in full isolating layer—such as glass substrates, quartz substrates, or plastic substrates. For this reason, the proper optimizations of the device layout and package design seem to be the good candidates in the devices fabrication for the SOI technology manufacturability. A backside drain contact helps in dissipating the heat with a great area and also allows for minimum lead inductance on the drain side. As shown in Fig. 6-1 (b), the heat sink, which sometimes be mounted with the additional cooling fan in order to promote heat dissipation effectively, will be utilized and connected with the package of power devices for advanced heat dissipation.

Fig. 6-1. (a) Contact through buried oxide layer (CTBOX) technique process flow.

Fig. 6-1. (b) Power devices using a backside drain contact, heat sink, and even a forced air-cooling fan to help in dissipating the heat generation.

# 6.2 Comparison of Leakage Currents in Bulk and Different-Thickness SOI Devices at High Temperature Operation

At high temperature operation, the most significant effect of elevated temperature is an increase in the off state leakage current, which ultimately limits the upper operating temperature of the device. The silicon-on-insulator (SOI) devices are expected to exhibit lower parasitic leakage currents than their bulk silicon counterparts because of full dielectric isolation. Although many studies of high temperature properties for SOI devices have predominantly concentrated on the short-gate-length low-voltage SOI MOSFET's [6.5]-[6.7], there has been recent increasing interest in high-temperature performance of SOI high-voltage power transistors [6.8]-[6.10]. So several different design approaches have been proposed for high-voltage SOI lateral-double-diffused (LDMOS) transistors [6.11], it is instructive to evaluate these in the light of possible high-temperature applications.

While the applied bias is below avalanche voltage, the leakage current in the bulk-Si device increases with voltage in proportion to the depleted volume. At higher voltages, the SOI room-temperature leakage increases with voltage more steeply because of band-to-band tunneling [6.12]. At high temperature, the SOI leakage current increases less rapidly with voltage because of a weak temperature dependence of the tunneling current and enhanced generation current component so that the tunneling becomes insignificant at high temperature operation. Although the room-temperature leakage currents in SOI and bulk devices are almost similar, the SOI leakage current at high temperature is sometimes two orders of magnitude lower than bulk devices. Additionally, the much larger leakage current observes in thicker SOI power devices [6.9], whose magnitude is comparable to that found in bulk-Si transistors. Hence, the

low overall leakage current makes LDMOS transistors fabricated in thin SOI layers well suited for high-temperature power IC applications.

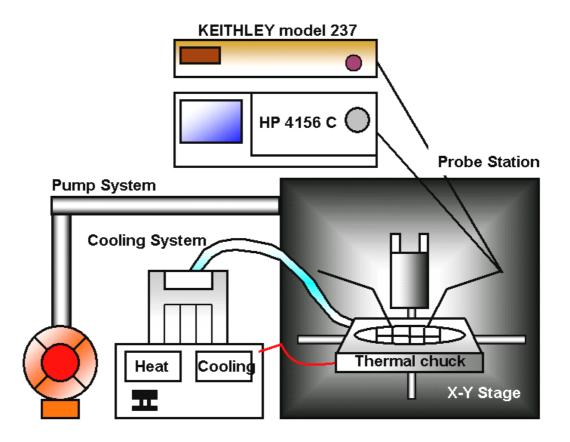

### **6.3** Experiments

The key processes for fabricating the novel LTPS LDMOS were shown in Fig. 6-2 (a). At first, an amorphous-silicon (a-Si) of 0.1-µm thickness was deposited by low-pressure chemical vapor deposition (LPCVD) on a 1.5-µm-thick wet oxide at 550  $^{\circ}$ C. The 50 KeV phosphorous dose of 7  $\times$  10<sup>11</sup> cm<sup>-2</sup> was implanted into the a-Si drift region to reduce its resistance. The high energy of 60 KeV boron dose of  $3 \times 10^{13}$  cm<sup>-2</sup> was created to increase the breakdown voltage without adding the threshold voltage. The laser crystallization was performed using KrF excimer laser ( $\lambda$ =248 nm) with the energy densities from 400 to 470 mJ/cm<sup>2</sup> and 99 % overlapped shot density at room temperature or 400 °C substrate heating. After that, a 5000-Å-thick field oxide (FOX) was formed by plasma enhanced chemical vapor deposition (PECVD) at 350 °C to reduce the surface electric field. A 1000-Å-thick PECVD gate oxide and a 2000-Å-thick LPCVD a-Si gate were defined across the FOX to split the P-well/N-drift junction electrical field. Finally, a 6000-Å-thick Al extended drain was defined on the 5000-Å-thick passive layer to split the N-drift/n+ drain junction electrical field. The novel poly-Si LDMOS fabrication (≤ 600 °C) was different from the high temperature (≅ 1100 °C) LDMOS processes. Figure 6-2 (b) illustrated the high temperature characteristics obtained using a HP 4156C low voltage analyzer, KEITHLEY model 237 high voltage analyzer, and Micromanipulator H1000 series high performance thermal chuck systems. In the on-state, the transfer and output characteristics were measured by HP 4156C under the gate biases from -35-V to 35-V and drain biases from 0-V to 20-V.

In the off-state, the blocking voltages were measured by KEITHLEY model 236 under grounded gate/source and drain biases from 100-V to 300-V. The thermal characteristics were measured by Micromanipulator thermal chuck systems under the temperatures from 300 K to 400 K.

Fig. 6-2. (a) Key process for fabricating the novel LTPS LDMOS using excimer laser crystallization with dimension of W/ $L_{ch}$ = 600- $\mu$ m/12- $\mu$ m plus a 15- $\mu$ m drift region.

Fig. 6-2. (b) Instruments for measuring the novel LTPS LDMOS using excimer laser crystallization with w 100-V/w 100-mA HP4156C, 1100V KEITHLEY model 237, and -65 °C~400 °C Micromanipulator H1000 high performance series thermal chuck systems.

### 6.4 Results and Discussion

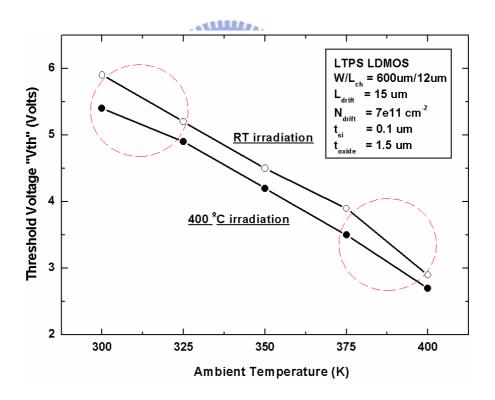

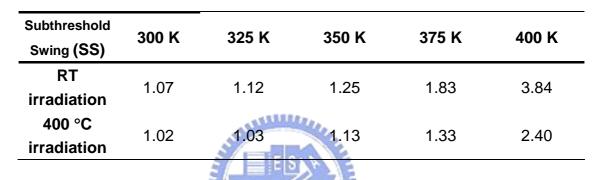

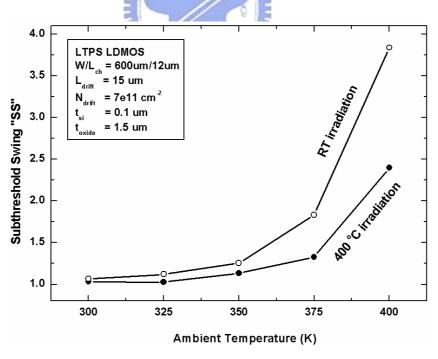

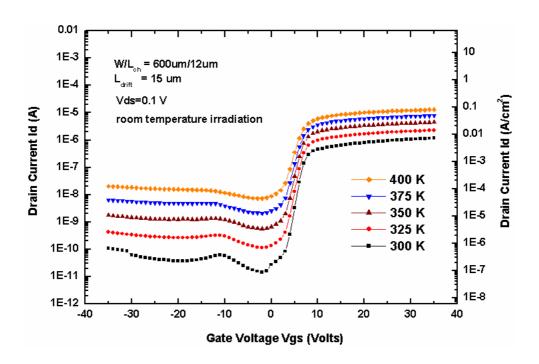

The various electrical characteristics of LTPS LDMOS at room temperature and 400 °C irradiations were shown over the temperature range of 300–400 K in this section. The on current ( $I_{ON}$ ), off current ( $I_{OFF}$ ), and subthreshold swing (SS) were raised as temperature increased. However, the threshold voltage (Vth) and specific on-resistance ( $R_{on,sp}$ ) were exhibited the negative temperature relation.

# 6.4.1 Transfer Characteristics of LTPS LDMOS at RT and 400 °C Irradiations over Ambient Temperature Range of 300–400 K

# 6.4.1.1 Relationship between ON/OFF Currents and Ambient Temperatures for LTPS LDMOS

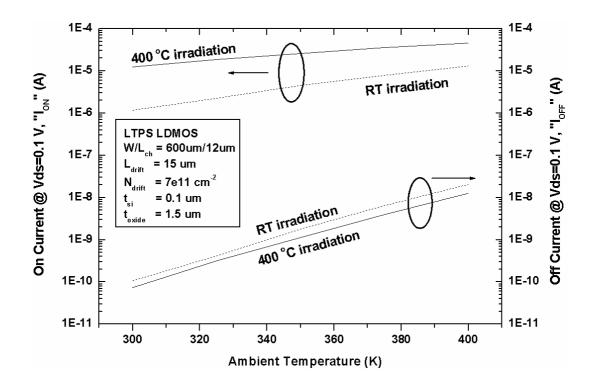

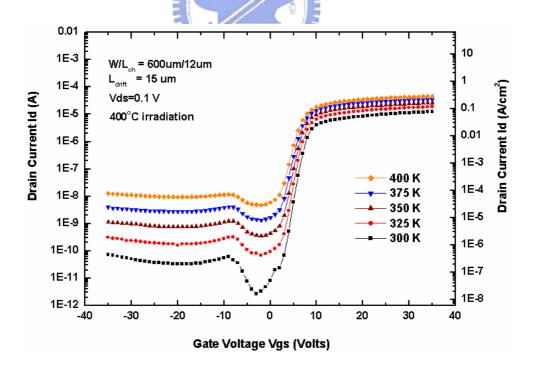

### 6.4.1.1.1 ON and OFF Currents at Drain Bias of 0.1 V

Figure 6-3 and Table 6-1 showed the  $I_{ON}$  and  $I_{OFF}$  currents at the drain bias of 0.1 V with increasing ambient temperature from 300 K to 400 K. The on-state current ( $I_{ON}$ ) and off-state current ( $I_{OFF}$ ) of ON/OFF current ratios were defined at the gate biases of 35-V and -35-V, respectively. For  $I_{ON}$  currents from the ambient temperature of 300 K to 400 K, the LTPS LDMOS at 400 °C irradiation demonstrated the less sensitivity with 3.68 times variation in ambient temperature than that at room temperature irradiation with 11.11 times variation. However, in the  $I_{OFF}$  currents as the increase in ambient temperature, the off state variations of LTPS LDMOS at room temperature and 400 °C irradiations were almost the same with the large values of 188 times and 172 times, respectively. At ambient temperature of 300 K, the difference of  $I_{ON}$  currents between

the room temperature and 400 °C irradiations was larger about 7 times than the difference of  $I_{OFF}$  currents between them. As the ambient temperature increased to 400 K, the difference of  $I_{ON}$  currents between the room temperature and 400 °C irradiations was shortened to about 2 times compare to the difference of  $I_{OFF}$  currents between them. The LTPS LDMOS at 400 °C irradiation exhibited superior characteristics with the higher  $I_{ON}$  current and lower  $I_{OFF}$  current as the increase in ambient temperature.

Table 6-1. Summary of on and off currents for LTPS LDMOS at RT and 400 °C Irradiations with Vds=0.1 V and over Ambient Temperature Range of 300 K-400 K.

| I <sub>ON</sub><br>(Vds=0.1 v) | 300 K    | 325 K 350 K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 375 K      | 400 K    |

|--------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------|

| Room                           |          | S I I I I I I I I I I I I I I I I I I I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |          |

| temperature                    | 1.17 E-6 | 2.27 E-6 4.51 E-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7.82 E-6   | 1.30 E-5 |

| irradiation                    |          | (°)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |          |