# Chapter 4

# Basic Characteristics of Pt/SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub>/HfO<sub>2</sub>/Si Structure using Layer-By-Layer Crystallization

#### 4-1. Introduction

Recently, the metal-ferroelectric-insulator-semiconductor (MFIS) structure has attracted much attention as a promising candidate for field effect transistor (FET)-type ferroelectric nonvolatile memories (FeMFETs). FeMFETs provides many benefits, including smaller cells, simpler process flows and the nondestructive readout operation (NDRO) feature. However, problems of inter-diffusion between the ferroelectric layer and the silicon substrate may arise from a poor-quality interface layer, reducing the retention time, when the ferroelectric layer is directly deposited on the Si substrate [52]. To solve this problem, a good insulator layer that acts as a diffusion barrier must be found; it must have properties, such as low leakage current and high dielectric constant. Insulating materials in the MFIS structure have been reported elsewhere; they include Si<sub>3</sub>N<sub>4</sub>, CeO<sub>2</sub>, Ta<sub>2</sub>O<sub>5</sub>, ZrO<sub>2</sub>, LaAlO<sub>3</sub>, HfO<sub>2</sub> and Pr<sub>2</sub>O<sub>3</sub> [12-19]. However, the trap-less ferroelectric layer and high-quality metal-ferroelectric interface are also required to ensure favorable retention characteristics [20-23].

In this work, layer-by-layer-crystallized SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub> ferroelectric films [53-55] were deposited by metaloganic decomposition (MOD) on a low-leaky HfO<sub>2</sub>/Si substrate, to fabricate an MFIS capacitor with a Pt/SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub>/HfO<sub>2</sub>/Si structure. MFIS structures with conventionally crystallized SBT films were used as control samples for comparison with layer-by-layer-crystallized and conventionally crystallized Pt/SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub>/HfO<sub>2</sub>/Si structures. Layer-by-layer-crystallized and conventionally crystallized Pt/SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub>/Pt/Ta/SiO<sub>2</sub>/Si MFM capacitors were also fabricated and characterized. The retention characteristics of the MFIS structure can be improved by layer-by-layer crystallization process. Additionally, the process promotes resistance to switching degradation at up to 10<sup>9</sup> cycles.

#### 4-2. Experiments

MFIS capacitors with ferroelectric SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub> and HfO<sub>2</sub> buffer layers were fabricated on 4-inch (100) p-type silicon wafers. The HfO<sub>2</sub> film was deposited by DC sputtering in Ar/O<sub>2</sub> (24/3 sccm) ambient at room temperature, using a 4-inch hafnium target. The deposited films

were then annealed at 900 °C for three minutes in oxygen atmosphere to yield a low-leaky  $HfO_2$  film. The thickness of the annealed film was about 14 nm, as measured using a multiple-wavelength ellipsometer. The SBT films for the layer-by-layer-crystallized MFIS structures were prepared on the  $HfO_2/Si$  substrates by layer-by-layer crystallization process. The wet films underwent a baking sequence at 120 °C, 250 °C and 400 °C each for 10 min, in air. Then, the deposited films were treated in an oxygen atmosphere at 750 °C for 10 s, by rapid thermal annealing (RTA). The heating rate was maintained at 10 °C/s in the RTA process. For comparison, the conventionally crystallized MFIS structures that underwent the aforementioned baking sequence were adopted as control samples herein. After these process had been repeated four times to yield the desired film thickness of about 320 nm, all films were crystallized by post deposition annealing (PDA) in an  $O_2$  atmosphere at temperatures from 750 to 850 °C for 3 min. Finally, 100-nm-thick Pt film was deposited by electron beam evaporation through a shadow mask with an area of 3.5  $\times 10^{-4}$  cm<sup>2</sup>, to serve as the top electrode.

The surface morphology and crystallinity of the SBT/HfO<sub>2</sub>/Si stack were analyzed by atomic force microscopy (AFM) and X-ray diffraction (XRD), respectively. The current density-electric field curves were measured using a Keithley 4200 semiconductor characterization system. The capacitance-voltage (C-V) characteristics and capacitance retention properties were evaluated using an HP4284A precision LCR meter at a frequency of 100 kHz. The program/erase endurance tests were performed by a system comprised of HP8110A 150MHz pulse generator, HPE5250A low leakage switch matrix, and HP 4284A precision LCR meter. The schematic system construction of retention and endurance tests is shown in Fig. 2-4 and this system is controlled a personal computer using Labview program through a GPIB interface and IEEE 488.2 cables. The flowcharts of the retention and endurance measurements are shown in Figs. 2-5 and 2-6, respectively.

#### 4-3. Results and Discussions

The experimental procedures were mentioned in the previous section. In the following we will first describe the electrical and dielectric characteristics of Al/HfO<sub>2</sub>/Si/Al MIS structure. The crystallinity and surface morphology of SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub>/HfO<sub>2</sub>/Si structure will then be characterized. Additionally, electrical properties of layer-by-layer-crystallized and conventionally crystallized MFIS capacitors will be characterized and compared. Moreover, inter-diffusion phenomena of layer-by-layer-crystallized and conventionally crystallized

SBT/HfO<sub>2</sub>/Si stacks will also be described and compared. Furthermore, the endurance characteristics of layer-by-layer-crystallized MFIS structure will be discussed.

#### 4-3-1. Characteristics of Al/HfO<sub>2</sub>/Si/Al MIS structure

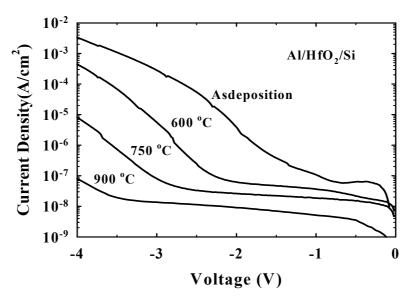

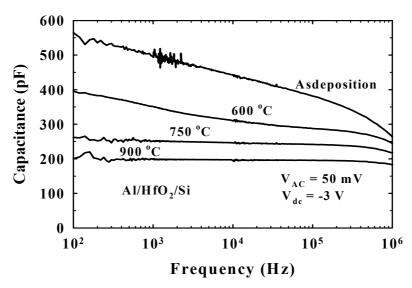

Normally, the HfO<sub>2</sub> film will crystallize at a high PDA temperature, leading to a high leakage current density. However, the interfacial layer will be formed at such a high temperature of 900 °C even though the HfO<sub>2</sub> film was annealed in the nitrogen ambient. When the HfO<sub>2</sub> film was annealed in the oxygen ambient, the thickness of interfacial layer will be increased, resulting in an increased equivalent oxide thickness (EOT) and a lower leakage current. The leakage currents of the HfO<sub>2</sub> films annealed at various temperatures in the oxygen ambient (Figure 4-1) indicate that the leakage property can be improved as the annealing temperature increased perhaps because of the increase of the thickness of interfacial layer. Additionally, the results concerning the frequency-dependence of accumulation capacitance of those films (Figure 4-2) reveal that the capacitance of the HfO<sub>2</sub> films decreased with increasing the annealing temperature, which is consistent with the results concerning the increase of the thickness of interfacial layer. However, for the application of MFIS stack, the formation of interfacial layer is helpful to reduce the current through the I-S interface, resulting in an improvement of data retention.

Fig. 4-1 Current-voltage characteristic of Al/HfO<sub>2</sub>/Si capacitor annealed at various PDA temperatures in oxygen ambient. The annealing time was about 180 s.

Fig. 4-2 Capacitance-frequency characteristic of Al/HfO<sub>2</sub>/Si capacitor annealed at various PDA temperatures in oxygen ambient. The annealing time was about 180 s.

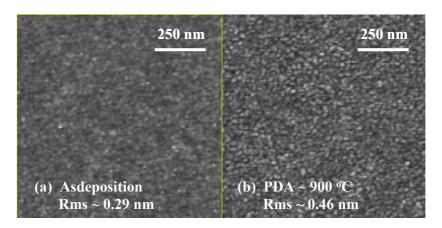

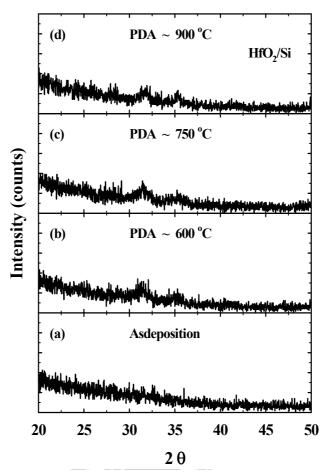

Figure 4-3 shows the surface morphology of the  $HfO_2$  films, including the asdeposited film and the film annealed at 900 °C for 180 s in oxygen ambient. The roughnesses of the asdeposited film and the annealed film (PDA ~ 900 °C) were around 0.29 nm and 0.46 nm, respectively. From the surface morphology of the annealed film, it is difficult to judge the crystallinity of the film; therefore, the XRD analysis of the  $HfO_2$  films was also performed. The relevant results are shown in Fig. 4-4. As can be seen from the result of the annealed film (PDA ~ 900 °C), a weak signal concerning the crystallinity of  $HfO_2$  film was found. The signal level is smaller and close to the value of background noise. From those results, we speculate that the  $HfO_2$  film annealed at 900 °C is partial crystallized.

Fig. 4-3 AFM images of HfO<sub>2</sub>/Si structure: (a) asdeposited film and (b) the film annealed at PDA temperature of 900 °C for 180 s in oxygen ambient.

Fig. 4-4 XRD patterns of HfO<sub>2</sub>/Si structure with 14-nm-thick HfO<sub>2</sub> films as a function of the PDA temperature.

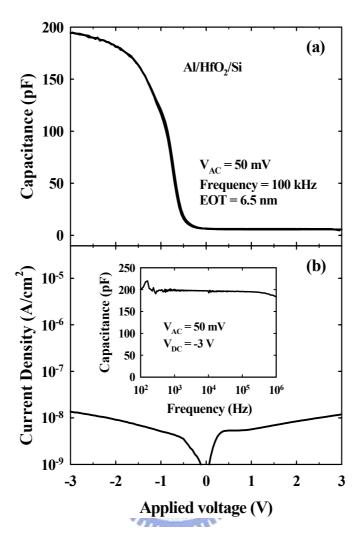

Figure 4-5(a) presents the high-frequency capacitance-voltage (C-V) characteristics of the Al/HfO<sub>2</sub>/Si structure with 14-nm-thick HfO<sub>2</sub> film annealed at 900 °C for 180 s in oxygen ambient, which has negligible trap-induced hysteresis and an equivalent oxide thickness (EOT) of about 6.5 nm, calculated from the accumulation capacitance. Additionally, Fig. 4-5(b) presents the current density-voltage (J-V) characteristics for the same MIS sample. The J-V curve reveals that the leakage current density was about  $1.0 \times 10^{-8}$  A/cm<sup>2</sup> at  $\pm$  3 V. These small values may be conducive to increasing the capacitance retention time of the MFIS structure by reducing the current through the insulator-silicon interface [20]. The inset in Fig. 4-5(b) presents the frequency-dependence of the capacitance characteristics of the MIS structure. The data were measured at a DC voltage of -3 V with a small signal of 50 mV. The capacitance-frequency (C-F) curve exhibits negligible frequency dispersion. These electrical characteristics indicate that the HfO<sub>2</sub> film can serve as a buffer layer in the MFIS structure.

Fig. 4-5 (a) Capacitance-voltage and (b) Current density-voltage characteristics of Al/HfO2/Si capacitor. The inset shows the capacitance-frequency characteristic of this capacitor. The HfO<sub>2</sub> film was annealed at 900 °C for 180 s in oxygen ambient.

#### 4-3-2. Crystallinity and surface morphology of SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub>/HfO<sub>2</sub>/Si structure

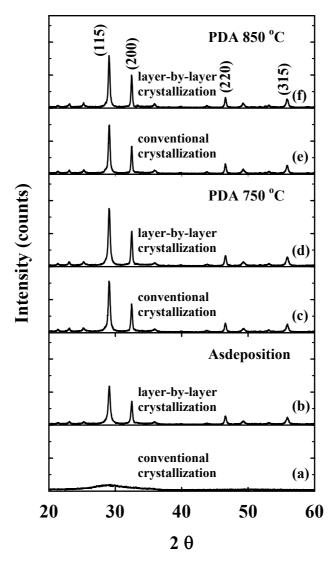

Figure 4-6 presents the XRD patterns of layer-by-layer-crystallized and conventionally crystallized Pt/SBT/HfO<sub>2</sub>/Si structures. For the layer-by-layer-crystallized MFIS structure, the XRD spectra of the as-deposited SBT/HfO<sub>2</sub>/Si structure included obvious (115) and (200) orientations. Additionally, the crystallinity of all of the annealed SBT films improved when PDA was conducted in an O<sub>2</sub> atmosphere at temperatures of 750 and 850 °C. These strong peaks associated with the predominant orientations in the XRD spectra verify that the SBT films with superior crystallinity can be obtained on top of the HfO<sub>2</sub> insulating layer.

Fig. 4-6 XRD patterns of SBT/HfO<sub>2</sub>/Si structure with conventionally crystallized and layer-by-layer-crystallized SBT films as a function of the PDA temperature.

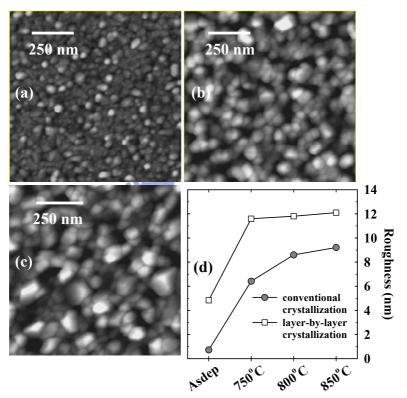

Figures 4-7(a) - 4-7(c) presents the AFM surface morphology of layer-by-layer-crystallized SBT films on HfO<sub>2</sub>/Si, obtained at various PDA temperatures. As can be seen from Fig. 4-7(a), a partial crystallized micro-structure was exhibited in the asdeposited film of layer-by-layer crystallized SBT/HfO<sub>2</sub>/Si stack and the roughness was around 4.84 nm. When the PDA temperature increased, the improved crystallinity of the layer-by-layer crystallized SBT/HfO<sub>2</sub>/Si stack was found, resulting in the increase of both the grain size and the surface roughness. Besides, the same trend was also found in the conventionally crystallized SBT/HfO<sub>2</sub>/Si stacks. The relevant results concerning the surface roughnesses of the both stacks are also shown in Fig. 4-7(d). The roughness of the layer-by-layer- crystallized

SBT/HfO<sub>2</sub>/Si structures exceeds that of the conventionally crystallized SBT/HfO<sub>2</sub>/Si structures, and that of the layer-by-layer-crystallized MFIS structure saturated when the PDA temperature exceeded 750 °C. However, the asdeposited film of conventionally crystallized SBT/HfO<sub>2</sub>/Si stack exhibits an amorphous micro-structure (not shown) with a roughness of around 0.72 nm. In contrast to the asdeposited film of conventionally crystallized MFIS stack, both a good crystallinity and a larger grain size present in the asdeposited film of the layer-by-layer-crystallized MFIS stack, which may lead to a larger roughness of layer-by-layer-crystallized MFIS stacks as PDA was performed.

Fig. 4-7 AFM images of layer-by-layer-crystallized SBT/HfO<sub>2</sub>/Si structure: (a) as-deposition, (b) PDA temperature of 750 °C and (c) PDA temperature of 850 °C. (d) Surface roughness of conventionally crystallized (full circles) and layer-by-layer-crystallized (open squares) SBT/HfO<sub>2</sub>/Si structures as a function of PDA temperature.

# **4-3-3.** Electrical properties of Pt/SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub>/Pt/Ta/SiO<sub>2</sub>/Si MFM and Pt/SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub>/HfO<sub>2</sub>/Si/Al MFIS structures

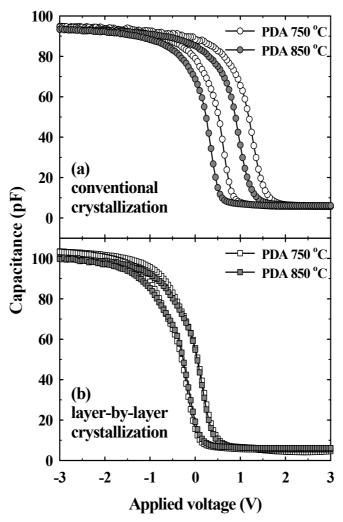

Figure 4-8 plots the C-V characteristics of layer-by-layer-crystallized and conventionally crystallized Pt/SBT/HfO<sub>2</sub>/Si structures. It was found that ferroelectric memory windows became narrow when the layer-by-layer-crystallized process was performed, which phenomenon was similar to that reported results for Pt/SBT/SiON/Si structure under

high-temperature RTA at 1000 °C [22]. The memory windows of the layer-by-layer-crystallized and the conventionally crystallized MFIS structures were about 0.34 V and 0.67 V at an operating voltage of ± 6.0 V. Compared to the C-V curve of the conventionally crystallized MFIS structure annealed at 750 °C, the results for the layer-by-layer-crystallized MFIS structure exhibit a negative voltage-shift. The results for the conventionally crystallized MFIS structure obtained when high-temperature PDA was conducted at 850 °C indicated similar behavior. These voltage shifts are probably caused by the reduction in the density of electron traps or ferroelectric oxide traps in the SBT/HfO<sub>2</sub>/Si structure. The mechanism is complex and its detailed is presently being investigated.

Fig. 4-8 Capacitance-voltage characteristics of (a) conventionally crystallized (circles) and (b) layer-by-layer-crystallized (squares) Pt/SBT/HfO<sub>2</sub>/Si structures. The open and full symbols represent the results of MFIS structure annealed at the PDA temperature of 750 °C and 850 °C.

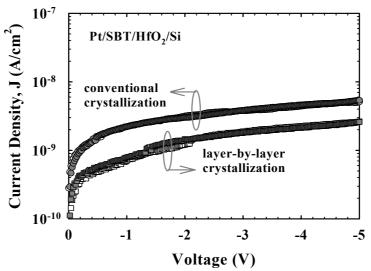

Figure 4-9 plots the current density-voltage (J-V) characteristics of layer-by-layer-crystallized and conventionally crystallized MFIS structures. The J-V curves reveal that the leakage current density of the layer-by-layer-crystallized MFIS structure is in the order of  $10^{-10} - 3.0 \times 10^{-9}$  A/cm<sup>2</sup> at an applied voltage of under 5.0 V. This leakage current density is lower than that of the conventionally crystallized MFIS structure. This lower leakage characteristic probably is caused by the suppression of current through the M-F interface or the improvement of the insulative property of I-S junction.

Fig. 4-9 Current density-voltage characteristics of conventionally crystallized (circles) and layer-by-layer-crystallized (squares) Pt/SBT/HfO<sub>2</sub>/Si structures. The open and full symbols represent the results of MFIS structure annealed at the PDA temperature of 750 °C and 850 °C.

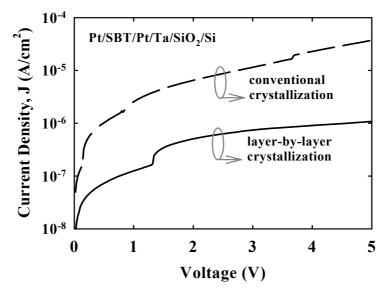

To study further, the current density-voltage (J-V) characteristics of layer-by-layer-crystallized and conventionally crystallized Pt/SBT/Pt/Ta/SiO<sub>2</sub>/Si MFM capacitors annealed in an atmosphere of O<sub>2</sub> at PDA temperature of 750 °C were investigated, and plotted in Fig. 4-10. Like the leakage properties of layer-by-layer-crystallized and conventionally crystallized MFIS structure, the layer-by-layer-crystallized MFM capacitor exhibits lower leakage than that of the conventionally crystallized MFM capacitor. However, this trend is different from the result of the surface roughness of MFIS stack (Fig. 4-7(d)). We speculate that layer-by-layer crystallization may result in a denser micro-structure of SBT film and

provide a more complete oxidation of the atoms (including Sr, Bi and Ta). Therefore, by reducing the metallic ion in the bulk of the SBT film, the leakage current of SBT films may be suppressed.

Fig. 4-10 Current density-voltage characteristics of conventionally crystallized (dashed line) and layer-by-layer-crystallized (solid line) Pt/SBT/Pt/Ta/SiO<sub>2</sub>/Si MFM capacitors annealed at PDA temperature of 750 °C.

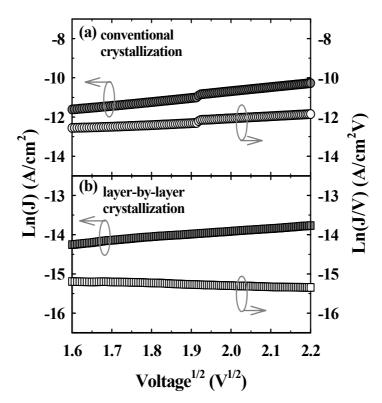

To elucidate the conduction mechanism, figure 4-11(a) shows the  $Ln(J/V)-V^{1/2}$  and  $Ln(J)-V^{1/2}$  plots of the conventionally crystallized MFM capacitor. Form the slope of  $Ln(J/V)-V^{1/2}$  and  $Ln(J)-V^{1/2}$  plots, the optical dielectric constant of the conventionally crystallized SBT film can be determined. The optical dielectric constant obtain from  $Ln(J/V)-V^{1/2}$  plot was estimated to be 15.26 and that obtained from  $Ln(J)-V^{1/2}$  plot was around 1.19. However, the value obtained from  $Ln(J)-V^{1/2}$  plot is too small and the order of this value is inconsistent with the reported result [56]. Therefore, we speculate that the dominant conduction mechanism of conventionally crystallized SBT film may be the Frenkel-Poole emission and the optical dielectric constant of the conventionally crystallized SBT film was about 15.26. Additionally, the plots for layer-by-layer-crystallized MFM capacitor were also shown in Fig. 4-11(b). As can be seen, the slope of  $Ln(J)-V^{1/2}$  plot shows a positive value and the  $Ln(J/V)-V^{1/2}$  plot of layer-by-layer-crystallized SBT film exhibits a negative gradient. It indicates that the Schottky emission is the dominant conduction mechanism of the layer-by-layer-crystallized MFM capacitors [57]. The optical dielectric constant of the layer-by-layer-crystallized SBT film was about 11.50. These dielectric constants are close to

the reported values [56]. The above discussions imply that the layer-by-layer crystallization can effectively suppress the leakage current through M-F interface and reduce the trap density of the SBT films. The retention time of MFIS structure is therefore longer since the currents through the M-F and I-S interface are suppressed [20].

Fig. 4-11  $Ln(J)-V^{1/2}$  (full symbol) and  $Ln(J/V)-V^{1/2}$  (open symbol) plots of (a) conventionally crystallized (circles) and (b) layer-by-layer-crystallized (squares) Pt/SBT/Pt/Ta/SiO<sub>2</sub>/Si MFM capacitors annealed at PDA temperature of 750 °C.

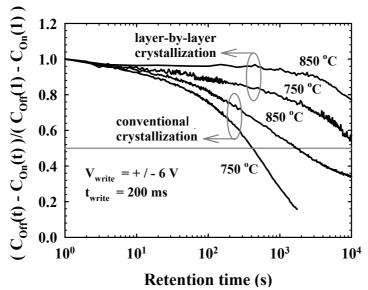

Figure 4-12 shows the capacitance retention characteristics of the layer-by-layer-crystallized Pt/SBT/HfO<sub>2</sub>/Si structures. It was found that layer-by-layer crystallization process can improve the retention properties. The retention times of the layer-by-layer-crystallized MFIS structures exceeded 10<sup>4</sup> s, when PDA was performed at temperatures between 750 and 850 °C. This result reveals that the retention properties are improved probably because of the suppression of the leakage current of the MFIS structure, and the reduction in the trap density of the SBT films [20, 23]. This finding is also consistent with the results of the leakage properties of the MFM capacitors.

Fig. 4-12 Capacitance retention characteristics of conventionally crystallized and layer-by-layer-crystallized Pt/SBT/HfO<sub>2</sub>/Si structure annealed at PDA temperature of 750 °C and 850 °C. C<sub>Off</sub>(t) and C<sub>On</sub>(t) represent the time-dependent capacitance as negative and positive write pulses was applied, respectively. The retention properties were measured at 0.0 V for layer-by-layer-crystallized MFIS structures, and at 0.7 V and 0.5 V for conventionally crystallized MFIS structures annealed at PDA temperature of 750 °C and 850 °C, respectively.

THE PARTY OF THE P

## 4-3-4. Inter-diffusion phenomena of SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub>/HfO<sub>2</sub>/Si stack

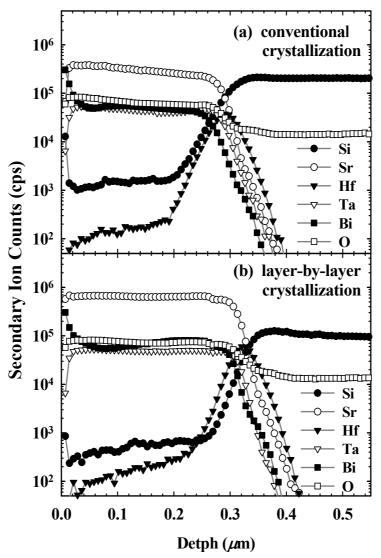

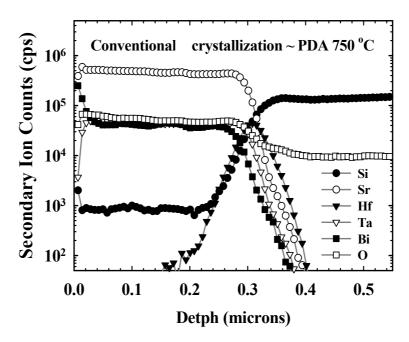

Figure 4-13 shows the depth profile of layer-by-layer-crystallized and conventionally crystallized SBT/HfO<sub>2</sub>/Si stack annealed at a PDA temperature of 850 °C, obtained using the secondary ion mass spectroscopy (SIMS). At such a high PDA temperature, the layer-by-layer-crystallized SBT/HfO<sub>2</sub>/Si stack exhibits the better inter-diffusion resistance than that of the conventionally crystallized one. For the layer-by-layer-crystallized SBT/HfO<sub>2</sub>/Si stack, the wet films first underwent a baking sequence in air and those were then treated in an oxygen atmosphere at 750 °C for 10 s. Under this lower thermal budget, we speculate that the atoms (including Si, Hf, Sr, Bi, Ta) may not diffuse seriously, because the depth profile of conventionally crystallized SBT/HfO<sub>2</sub>/Si stack (shown in Fig. 4-14) indicates that the stack also exhibits an adapted inter-diffusion resistance as the PDA was performed at 750 °C for 180 s. During the layer-by-layer crystallization process (annealing in oxygen ambient at 750 °C for 10 s), the atoms (including Sr, Bi, Ta) will be oxidized, leading to a crystalline phase of SBT film. Besides, the Si atom in both the buck of HfO<sub>2</sub> film and HfO<sub>2</sub>/Si

interface may be partial oxidized, which may suppress the diffusion of Si atom and result in an additional interfacial layer at HfO<sub>2</sub>/Si interface. This may be a possible explanation for the improvement of inter-diffusion resistance of the layer-by-layer-crystallized SBT/HfO<sub>2</sub>/Si stack. However, the diffusion of silicon atom into the SBT film may result in certain amount of traps in the ferroelectric films, thereby degrading the leakage current and the capacitance retention characteristics for the MFIS stack. All these findings are consistent with the above discussion in Figs. 4-9 and 4-12.

Fig. 4-13 SIMS depth profiles of (a) conventionally crystallized and (b) layer-by-layer-crystallized SBT/HfO<sub>2</sub>/Si stacks annealed at PDA temperature of 850 °C.

Fig. 4-14 SIMS depth profiles of conventionally crystallized SBT/HfO<sub>2</sub>/Si stacks annealed at PDA temperature of 750 °C for 180 s in oxygen ambient.

# 4-3-5. Endurance characteristics of Pt/SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub>/HfO<sub>2</sub>/Si/Al MFIS structure

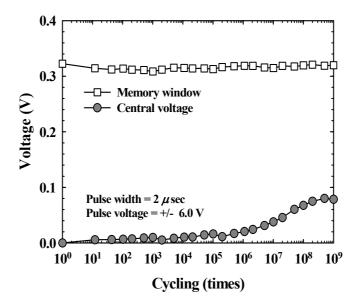

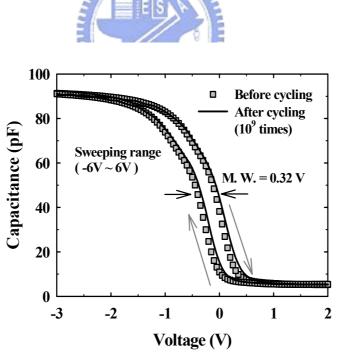

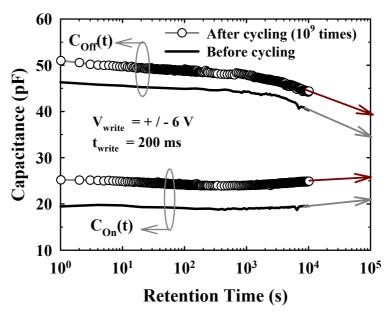

Pt/SBT/HfO<sub>2</sub>/Si stack annealed at a PDA temperature of 850 °C. A bipolar pulse train with an amplitude of 6 V and a pulse width of 2 μs was employed for testing the switching characteristics to study the endurance properties of this structure. The layer-by-layer-crystallized MFIS stack exhibits a favorable endurance characteristic with a negligible degradation of the memory window when the number of switching cycles exceeded 10<sup>9</sup>. A positive shift in the central voltage was also found until the number of program/erase switching cycles exceeded 10<sup>6</sup>. When the number of switching cycles was about 10<sup>9</sup>, the shift of the central voltage of C-V curve was approximately 0.07 V, probably because election traps were generated during the switching stress. The capacitance-voltage characteristics and capacitance retention characteristics of this layer-by-layer-crystallized Pt/SBT/HfO<sub>2</sub>/Si structure before and after cycling are investigated to study further the degradation after stress, as shown in Figs. 4-16 and 4-17. It was found that up to 10<sup>9</sup> program/erase switching cycles negligibly degrade the retention properties. The retention time of this structure following stress exceeded 10<sup>4</sup>s and the retention time extrapolated from the data was approximately 10<sup>5</sup>

S.

Fig. 4-15 Memory window (open squares) and central voltage (full circles) as a function of switching cycles for layer-by-layer-crystallized Pt/SBT/ HfO<sub>2</sub>/Si structure annealed at PDA temperature of 850 °C.

Fig. 4-16 C-V characteristics before (full squares) and after (solid line) 10<sup>9</sup> switching cycles for layer-by-layer-crystallized Pt/SBT/HfO<sub>2</sub>/Si structure annealed at PDA temperature of 850 °C. The memory window of both curve were around 0.32 V.

Fig. 4-17 Capacitance retention characteristics before (solid line) and after (open circles) 10<sup>9</sup> switching cycles for layer-by-layer-crystallized Pt/SBT/ HfO<sub>2</sub>/Si structure annealed at PDA temperature of 850 °C. The retention time exceeded 10<sup>4</sup> s and the extrapolated retention time was approximately 10<sup>5</sup> s.

## 4-4. Summary

In this chapter, a 320-nm-thick SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub> film was prepared on Si(100) substrate using a 14-nm-thick HfO<sub>2</sub> buffer layer, which has low-leaky properties and a high dielectric constant. The C-V characteristics of the layer-by-layer-crystallized and the conventionally crystallized Pt/SBT/HfO<sub>2</sub>/Si MFIS structures showed ferroelectric hysteresis. The memory windows of the layer-by-layer-crystallized and the conventionally crystallized MFIS structures were about 0.34 V and 0.67 V at an operating voltage of ± 6.0 V. The experimental results of MFM capacitors indicate that layer-by-layer crystallization can suppress the current through the metal-ferroelectric interface and reduce the trap density in the SBT films. Additionally, the MFIS structure with the layer-by-layer-crystallized SBT film exhibits favorable capacitance retention characteristics. When the PDA temperature was as high as 850 °C, the retention time of the layer-by-layer-crystallized MFIS structure exceeded 10<sup>4</sup> s and the extrapolated retention time was approximately 10<sup>5</sup> s. Moreover, the structure exhibits good switching characteristics with negligible degradations of the memory window and the retention time, when the number of switching cycles was about 10<sup>9</sup>.